Structure (2A)

Configuration

Young Won Lim 08/06/2012 Copyright (c) 2012 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

Young Won Lim 08/06/2012

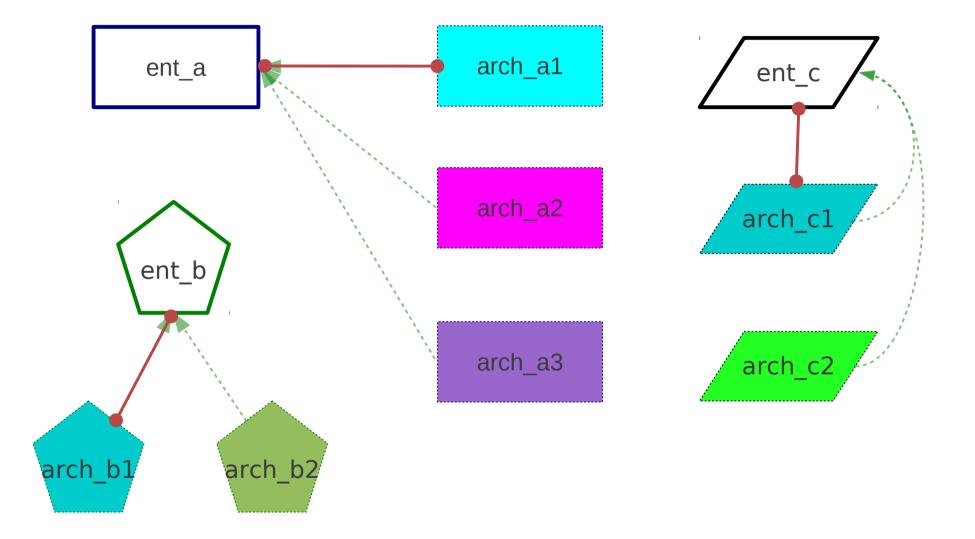

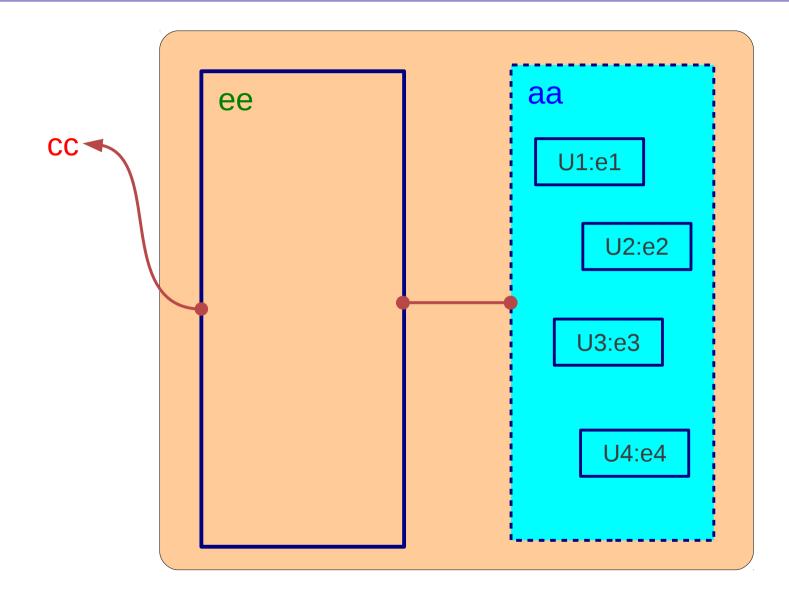

#### **Structural Hierarchy**

# Which Entity – Architecture pairs?

- Default Configuration

- Component Configuration

- entity-architecture configuration

- low level configuration

- Block Configuration

| 03: | comp3 | port | map | ( | ); |

|-----|-------|------|-----|---|----|

| U4: | comp4 | port | map | ( | ): |

end aa;

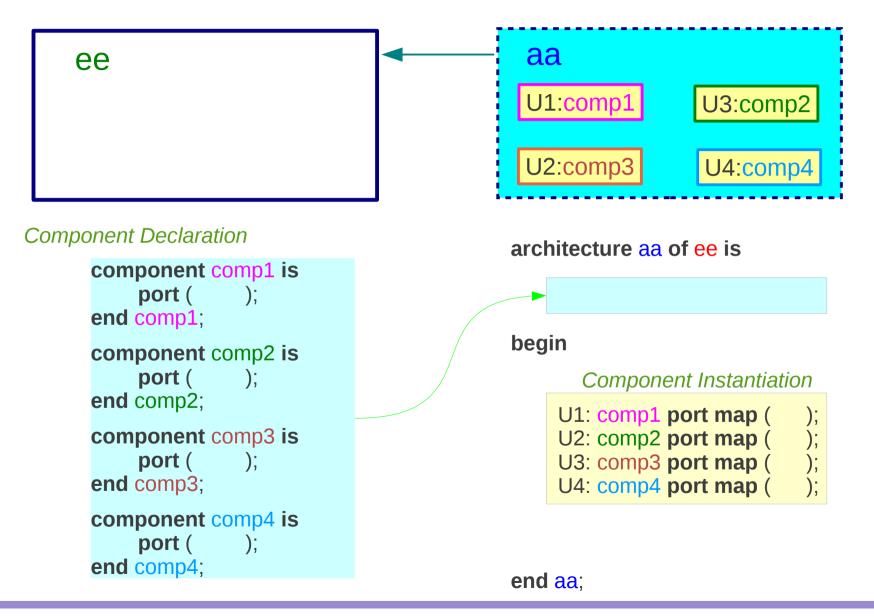

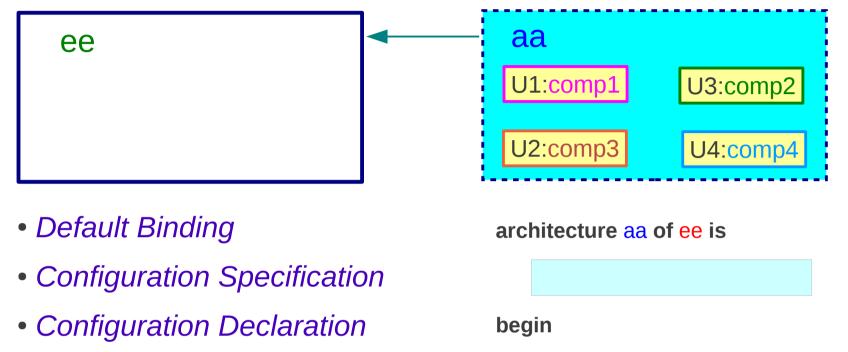

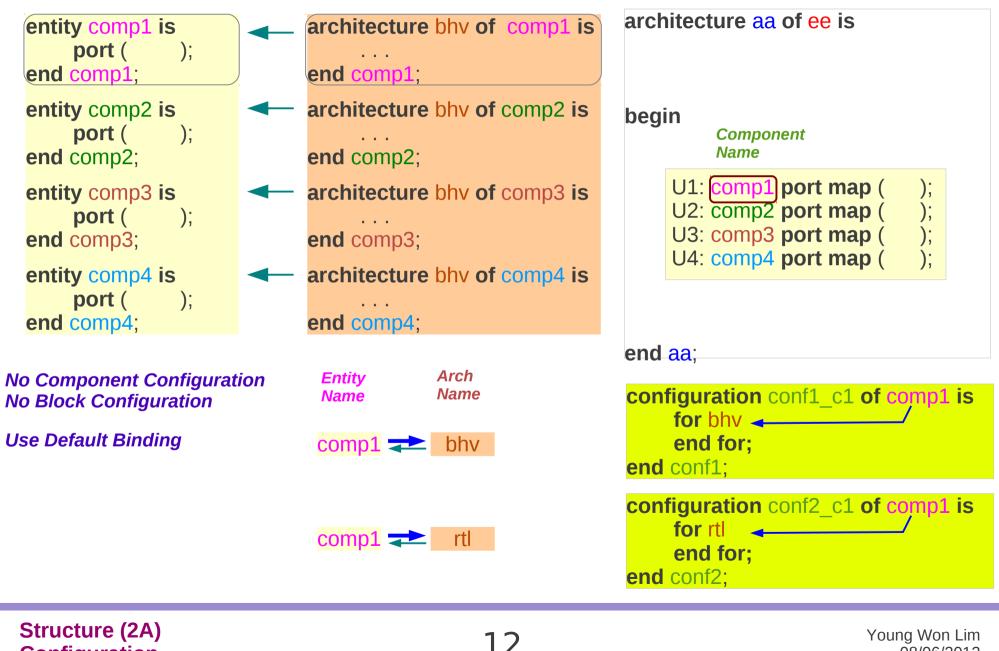

# **Default Binding**

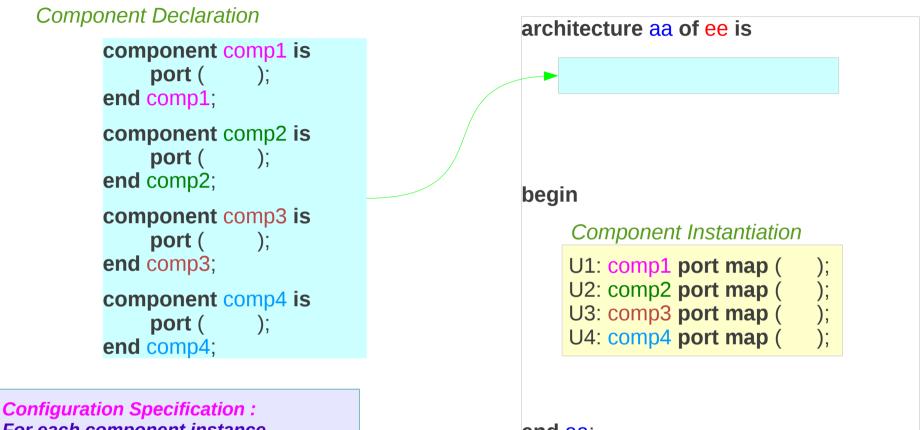

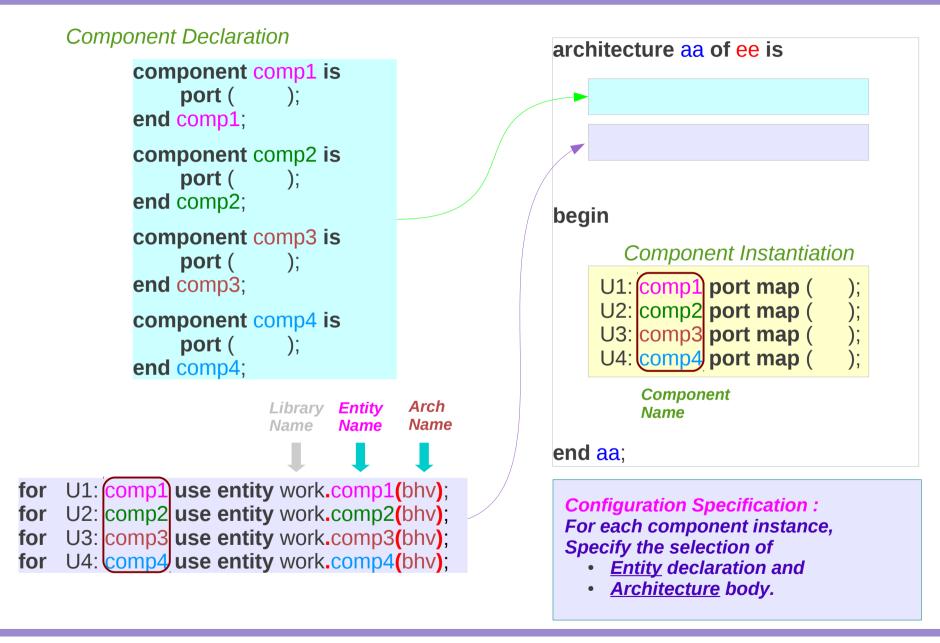

# Configuration Specification (1)

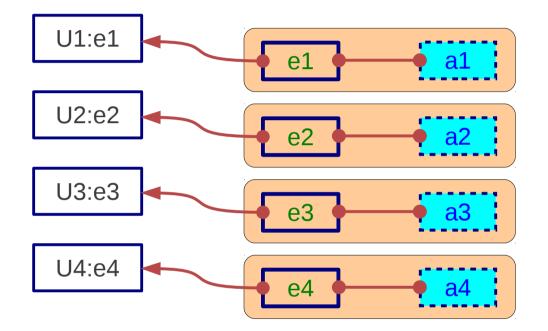

For each component instance, Specify the selection of

- Entity declaration and

- <u>Architecture</u> body.

end aa;

# Configuration Specification (2)

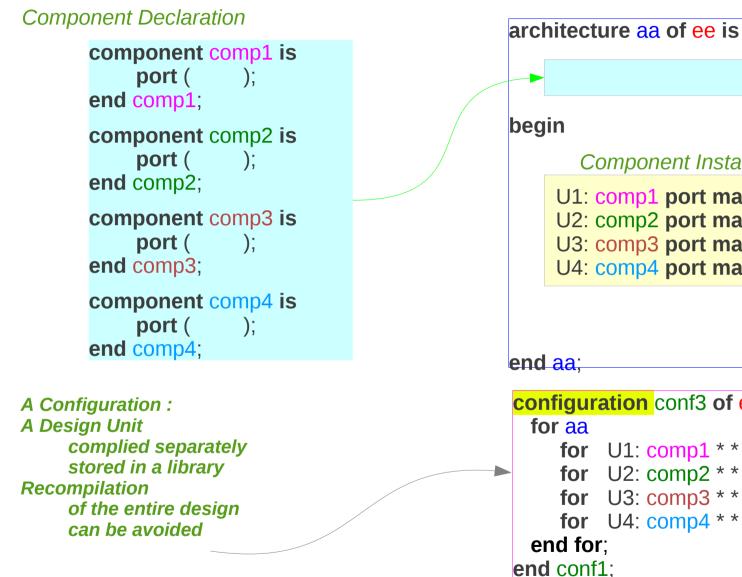

# Configuration Declaration (1)

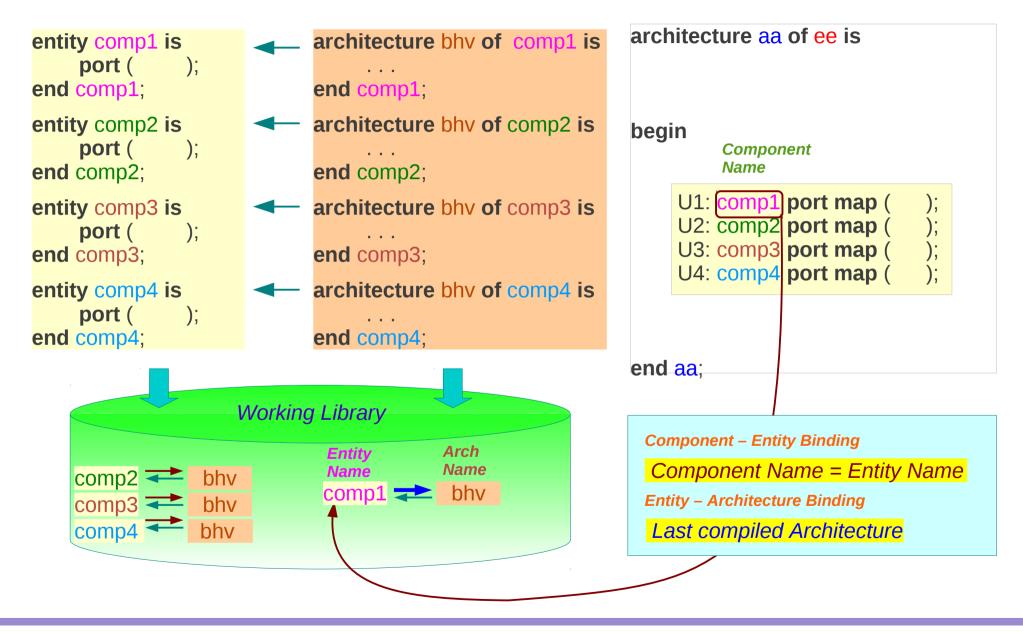

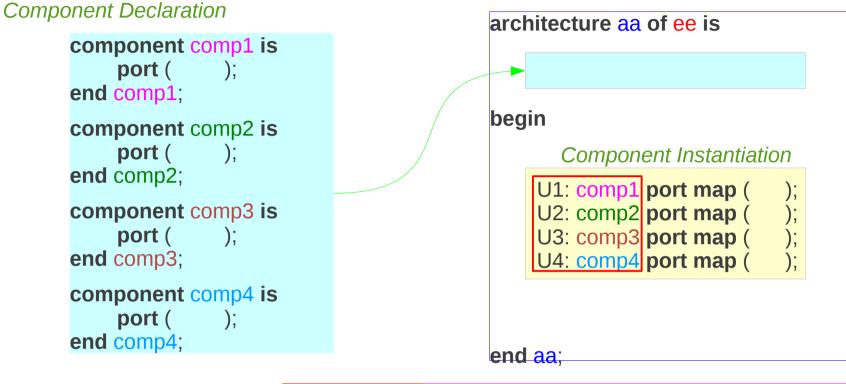

#### Component Instantiation U1: comp1 port map ( ); ); U2: comp2 port map ( ); U3: comp3 port map ( ); U4: comp4 port map ( configuration conf3 of ee is

for U1: comp1 \* \* \* ; **for** U2: comp2 \* \* \* **for** U3: comp3 \* \* \* for U4: comp4 \* \* \* ;

# Configuration Declaration (2)

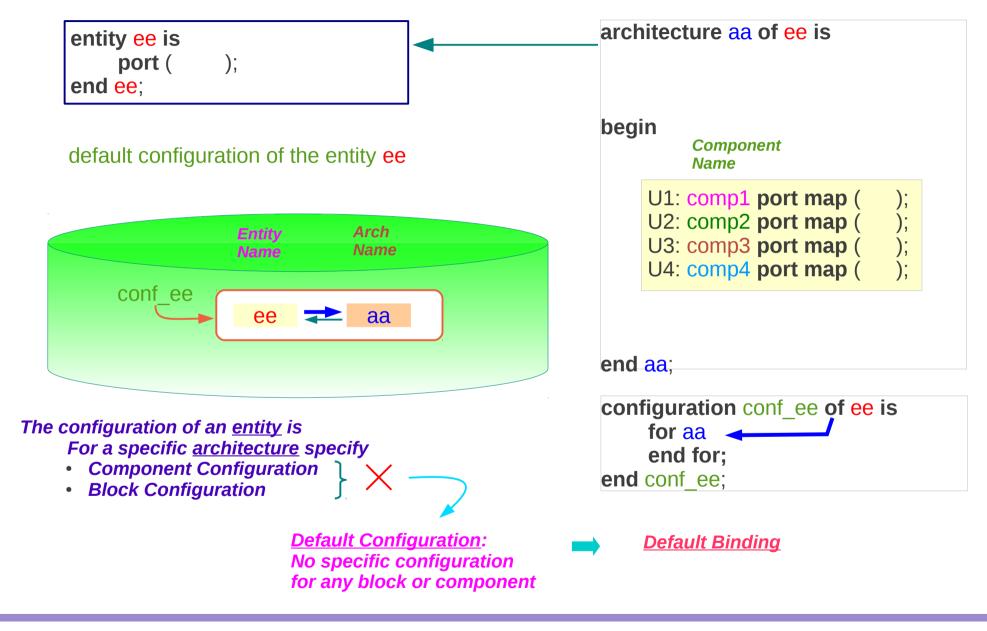

- Default Configuration

- Component Configuration

- entity-architecture configuration

- low level configuration

- Block Configuration

The configuration of an <u>entity</u> is For a specific <u>architecture</u> specify

- Component Configuration

- Block Configuration

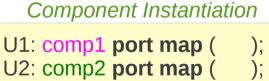

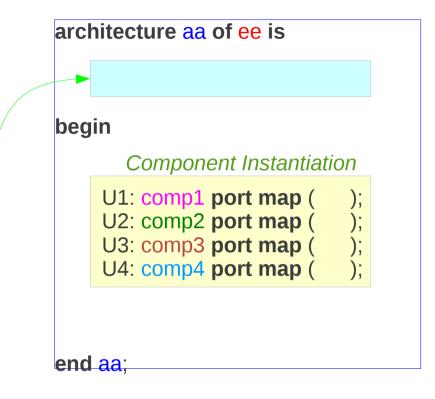

# Default Configuration (1)

# Default Configuration (2)

## Default Configuration (3)

Configuration

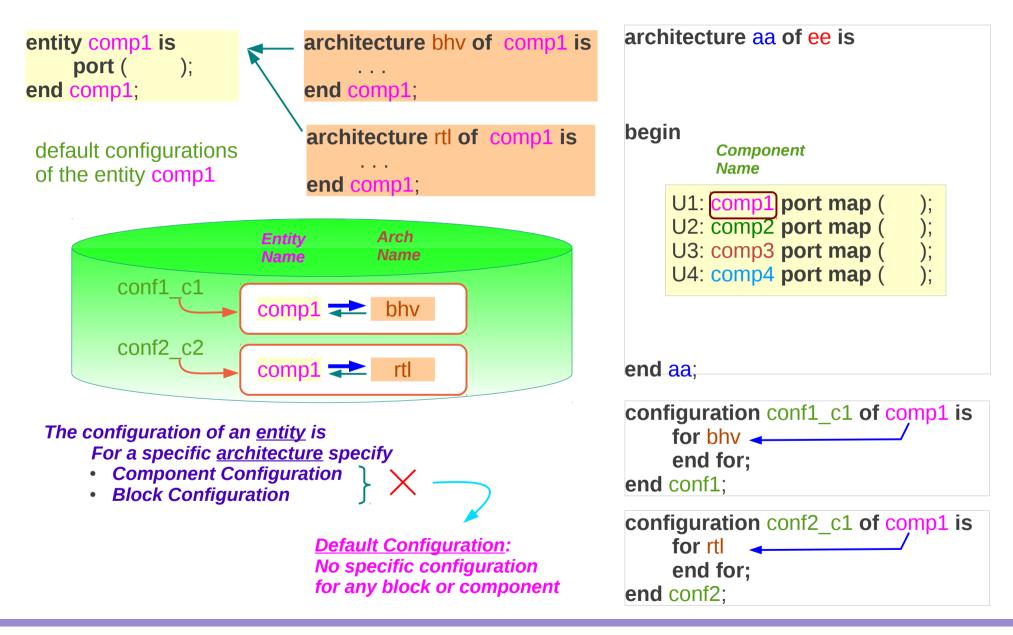

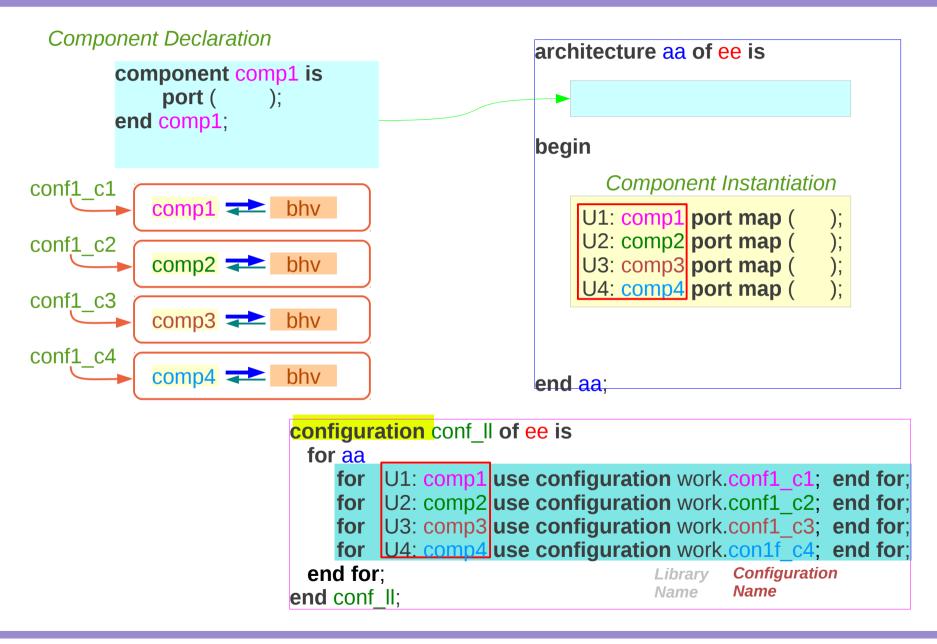

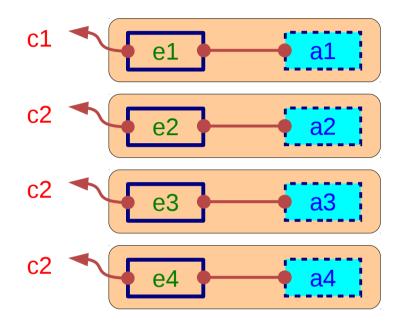

# **Component Configuration**

#### Default Configuration

- Component Configuration

- entity-architecture configuration

- low level configuration

- Block Configuration

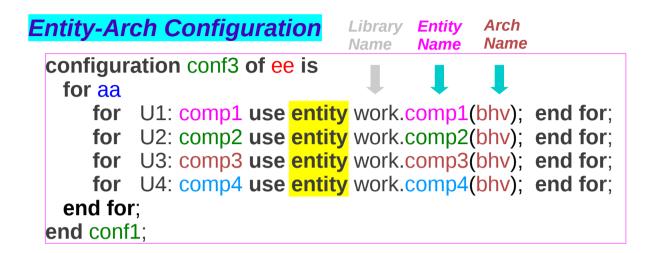

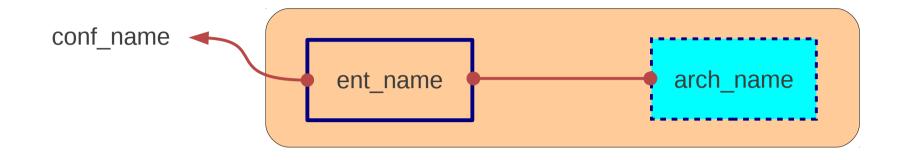

# **Entity – Architecture Configuration**

| configuration conf_ea of ee is |       |         |         |        |         |        |        |          |

|--------------------------------|-------|---------|---------|--------|---------|--------|--------|----------|

| for                            | aa    |         |         |        |         |        |        |          |

|                                | for   | U1: com | p1 use  | entity | work.   | .comp1 | (bhv); | end for; |

|                                | for   | U2: com | ip2 use | entity | work.   | .comp2 | (bhv); | end for; |

|                                | for   | U3: com | ip3 use | entity | work.   | .comp3 | (bhv); | end for; |

|                                | for   | U4: com | p4 use  | entity | work.   | comp4  | (bhv); | end for; |

| en                             | d for | •<br>ን  |         |        | Library |        | Arch   |          |

| end                            | conf_ | ea;     |         |        | Name    | Name   | Name   |          |

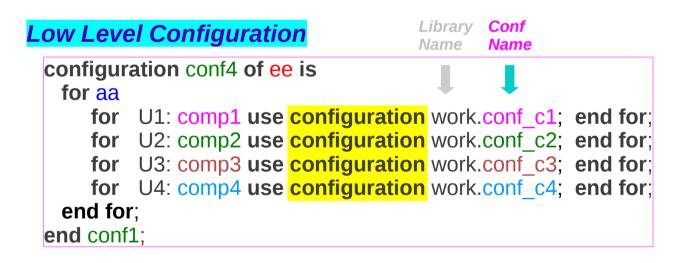

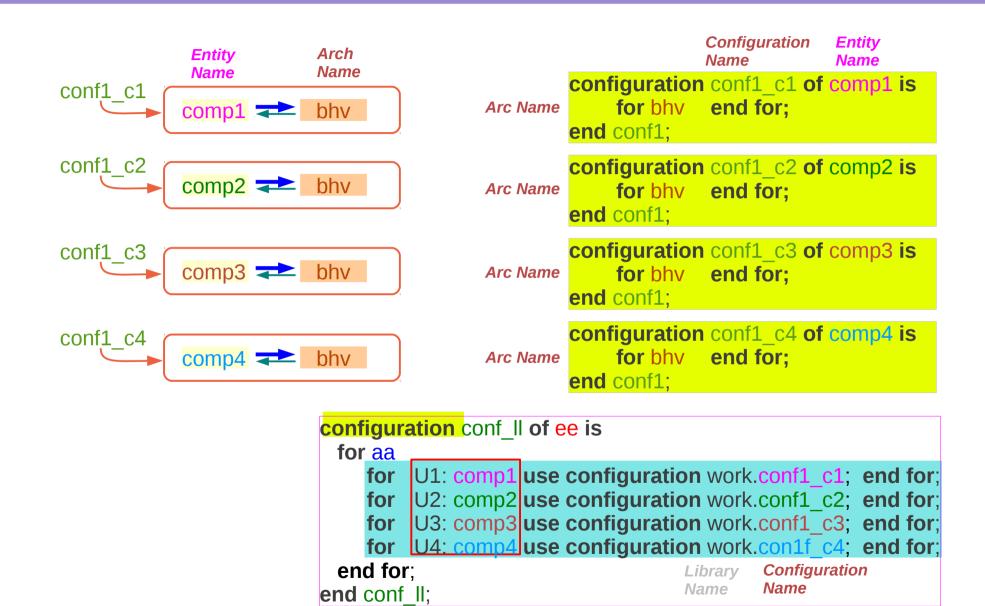

# Low Level Configuration (1)

# Low Level Configuration (2)

#### Sequential Assignment (1)

## Entity – Architecture Binding

| Structure ( | (2A) |

|-------------|------|

| Configurat  | tion |

## Configuration

#### Sequential Assignment (2)

#### Sequential Assignment (2)

### Sequential Assignment (1)

## **Default Binding**

### Sequential Assignment (1)

## Sequential Assignment (2)

### Sequential Assignment (2)

#### References

- [1] http://en.wikipedia.org/

- [2] J. V. Spiegel, VHDL Tutorial, http://www.seas.upenn.edu/~ese171/vhdl/vhdl\_primer.html

- [3] J. R. Armstrong, F. G. Gray, Structured Logic Design with VHDL

- [4] Z. Navabi, VHDL Analysis and Modeling of Digital Systems

- [5] D. Smith, HDL Chip Design

- [6] http://www.csee.umbc.edu/portal/help/VHDL/stdpkg.html

- [7] VHDL Tutorial VHDL onlinewww.vhdl-online.de/tutorial/