# Signals & Variables (2A)

Inertial & Transport Delay Models

Copyright (c) 2012 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

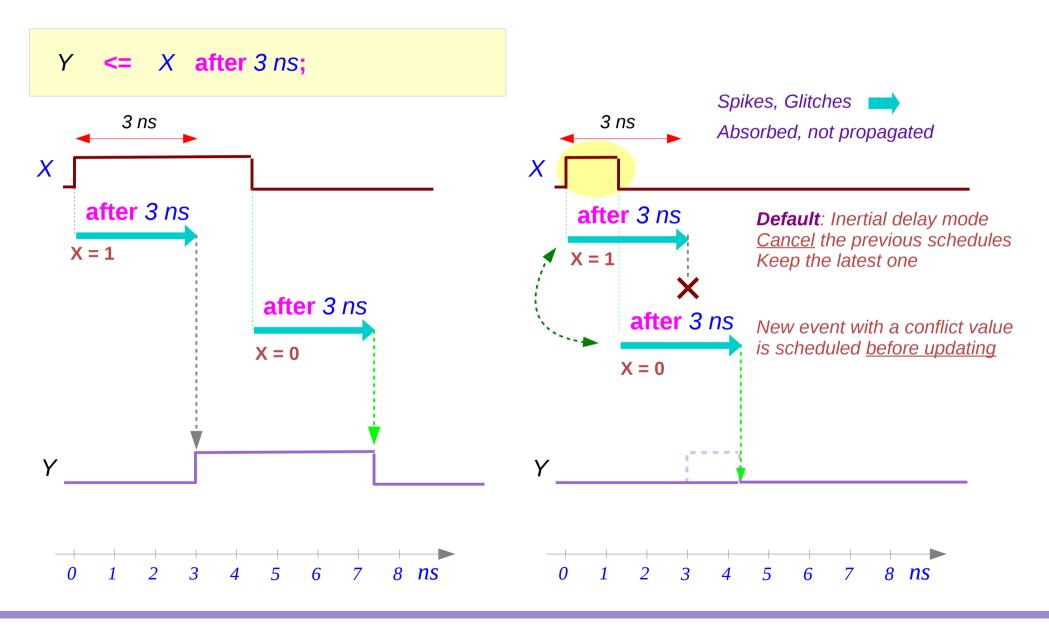

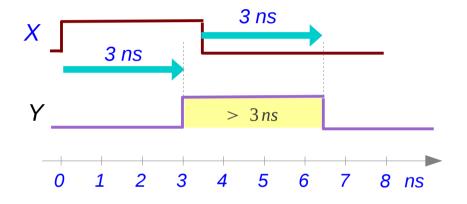

#### **Inertial Delay**

**Inertial & Transport**

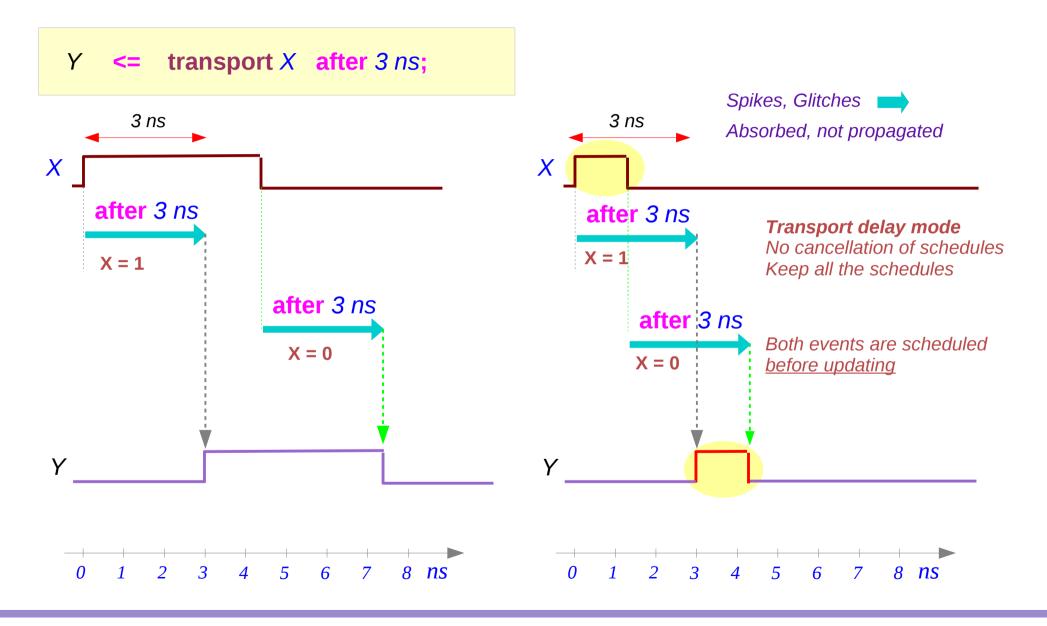

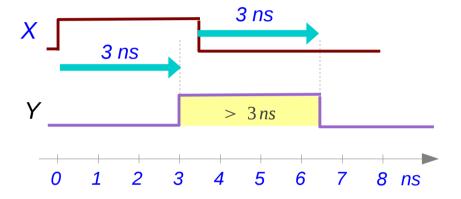

#### **Transport Delay**

**Inertial & Transport**

4

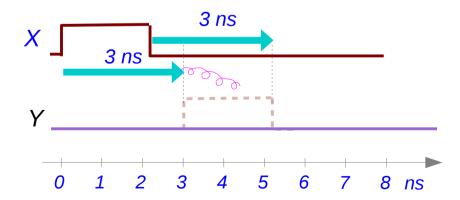

#### Inertial Delay & Transport Delay

**Inertial & Transport**

5

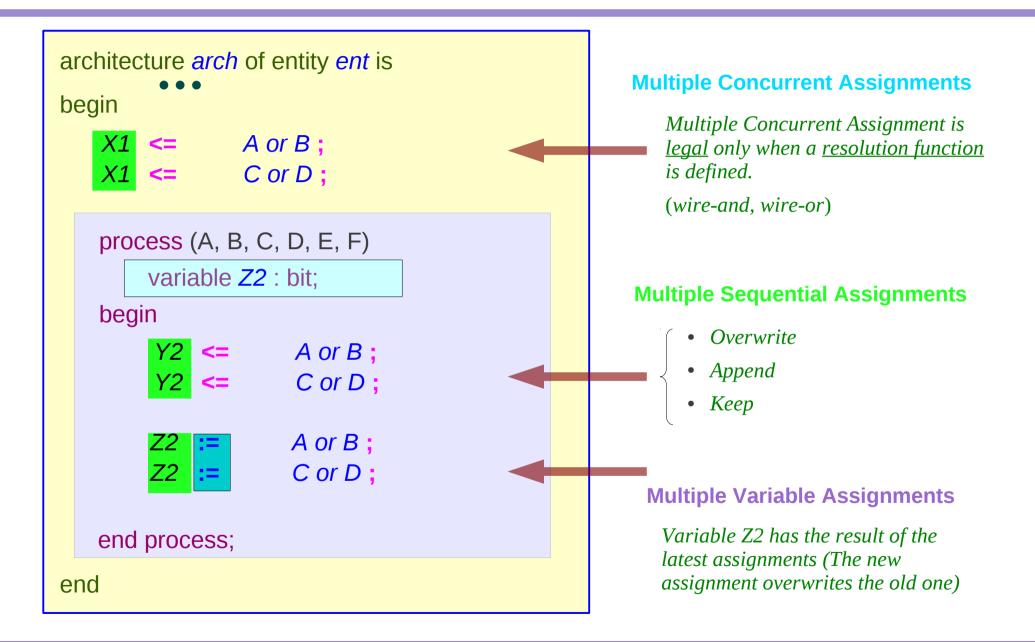

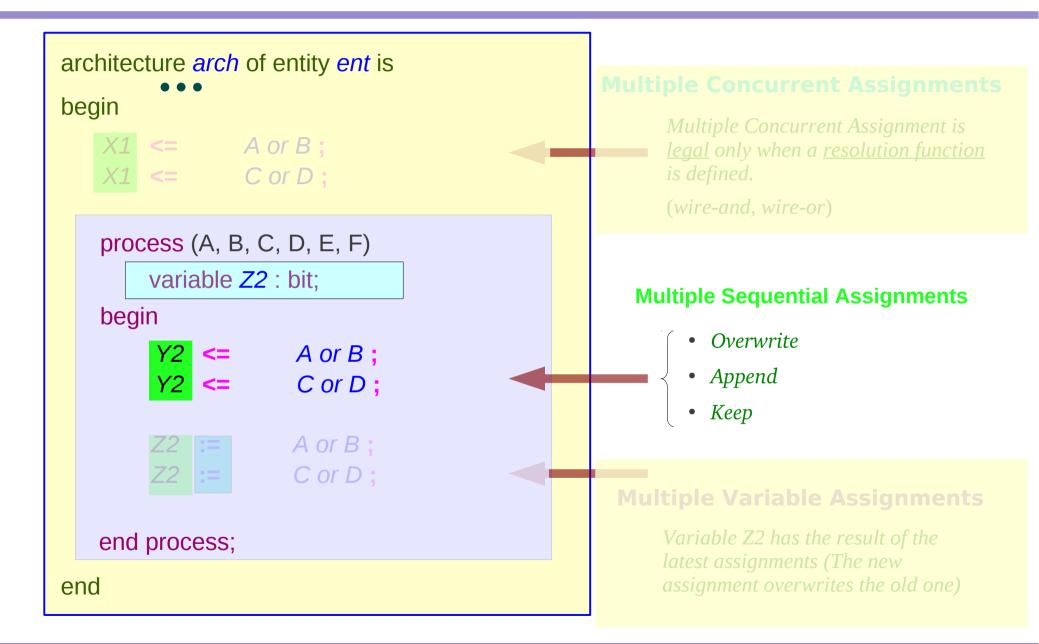

# Multiple Assignments to the Same Target

# **Multiple Sequential Assignments**

# Inertial & Transport Delay Model (1)

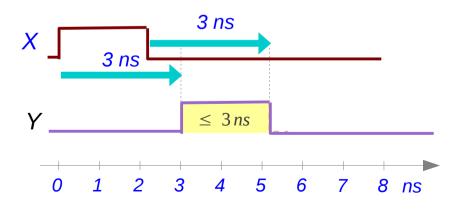

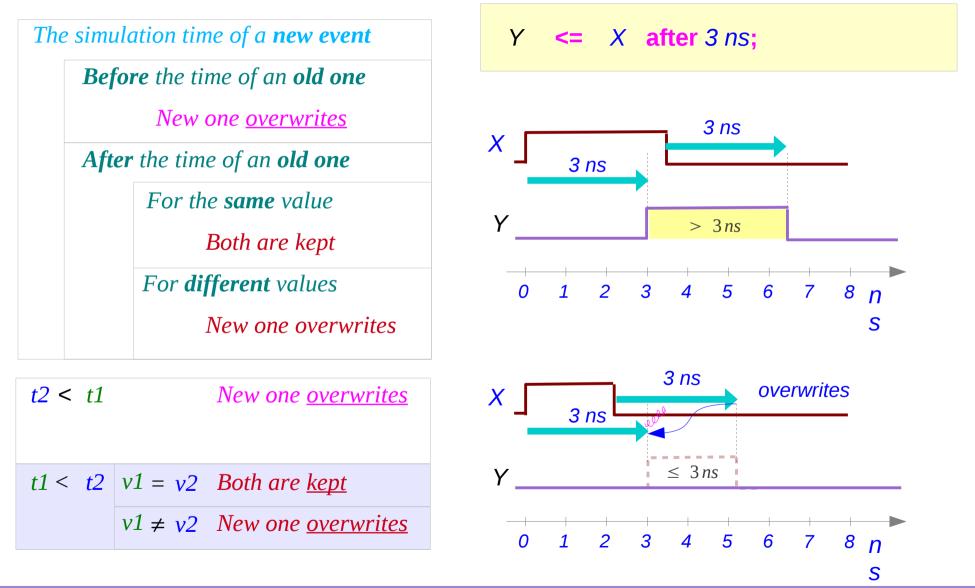

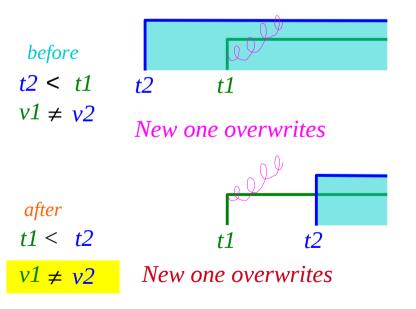

#### **Inertial Delay**

| e simu | lation time of a <b>new event</b> |  |

|--------|-----------------------------------|--|

| Bef    | ore the time of an old one        |  |

|        | New one <u>overwrites</u>         |  |

| Afte   | er the time of an <b>old one</b>  |  |

|        | For the same value                |  |

|        | Both are kept                     |  |

|        | For different values              |  |

|        | New one overwrites                |  |

|        |                                   |  |

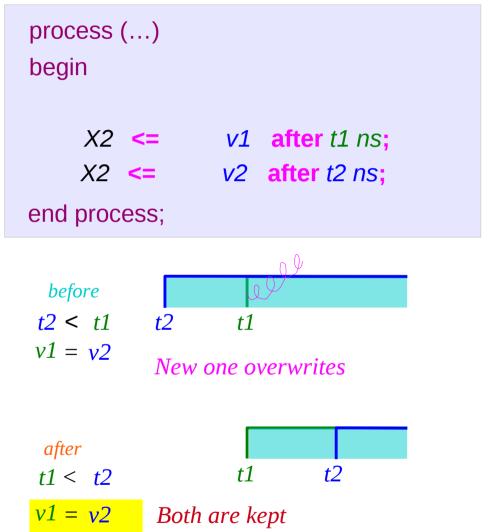

| t2 < t1 |              | New one <u>overwrites</u> |

|---------|--------------|---------------------------|

| t1 < t2 | v1 = v2      | Both are <u>kept</u>      |

|         | $v1 \neq v2$ | New one <u>overwrites</u> |

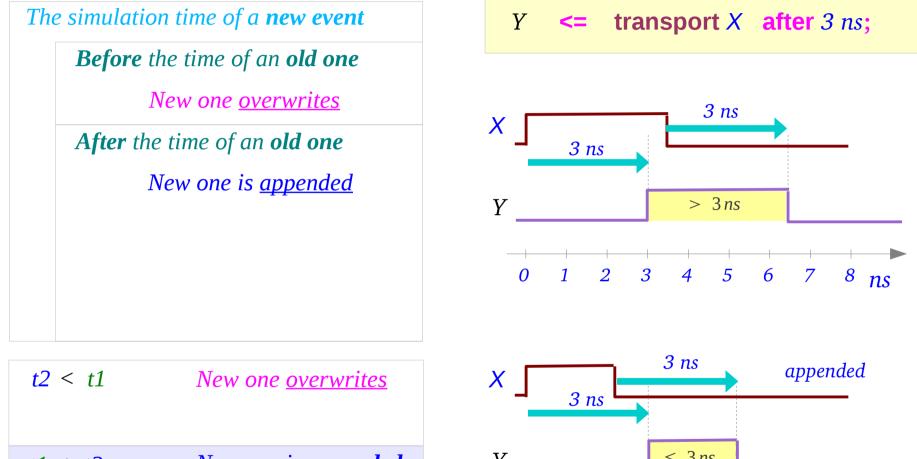

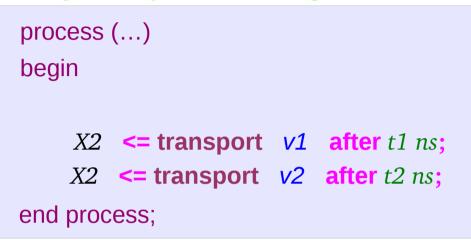

#### **Transport Delay**

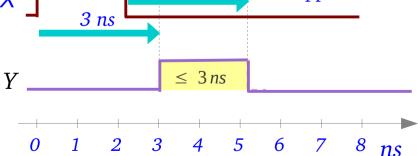

The simulation time of a **new event**

Before the time of an old one

*New one <u>overwrites</u>*

After the time of an old one

*New one is <u>appended</u>*

| t2 < t1        | New one <u>overwrites</u>  |

|----------------|----------------------------|

| t1 < <b>t2</b> | New one is <u>appended</u> |

### Inertial & Transport Delay Model (2)

#### **Inertial Delay**

### Inertial & Transport Delay Model (3)

#### **Transport Delay**

t1 < t2*New one is <u>appended</u>*

**Inertial & Transport**

# Inertial Delay (1)

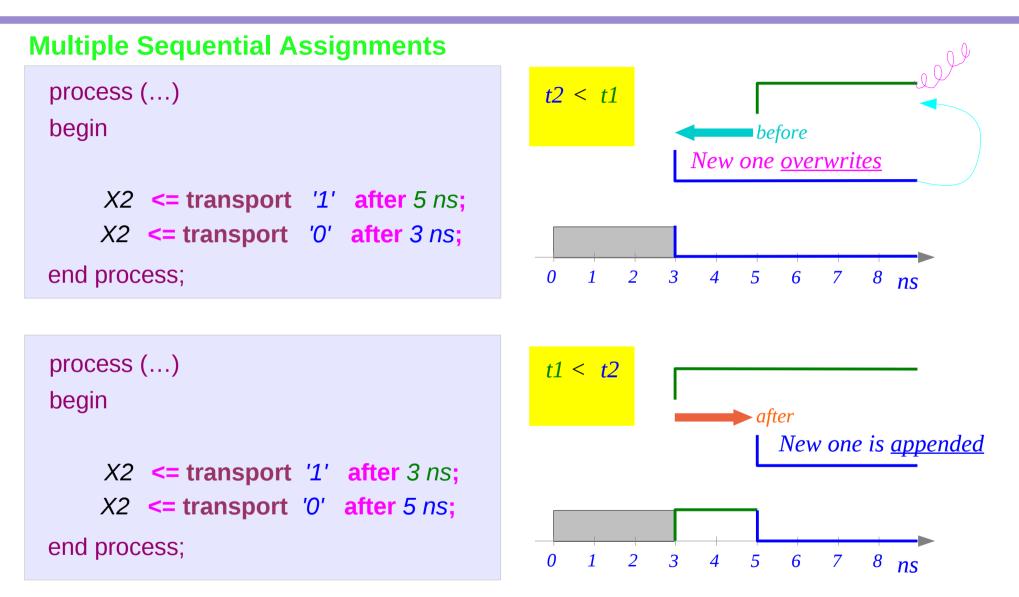

| Multiple Sequential Assignments                                |                                                   |

|----------------------------------------------------------------|---------------------------------------------------|

| process ()                                                     | t2 < t1                                           |

| begin                                                          | before                                            |

| X2 <= '1' after 5 ns;<br>X2 <= '0' after 3 ns;<br>end process; | New one <u>overwrites</u><br>0 1 2 3 4 5 6 7 8 ns |

|                                                                | Q 9                                               |

| process ()                                                     | t1 < t2                                           |

| begin                                                          | $v1 \neq v2$ after                                |

| X2 <= '1' after 3 ns;                                          | New one <u>overwrites</u>                         |

| X2 <= '0' after 5 ns;                                          |                                                   |

| end process;                                                   | 0 1 2 3 4 5 6 7 8 ns                              |

# Inertial Delay (2)

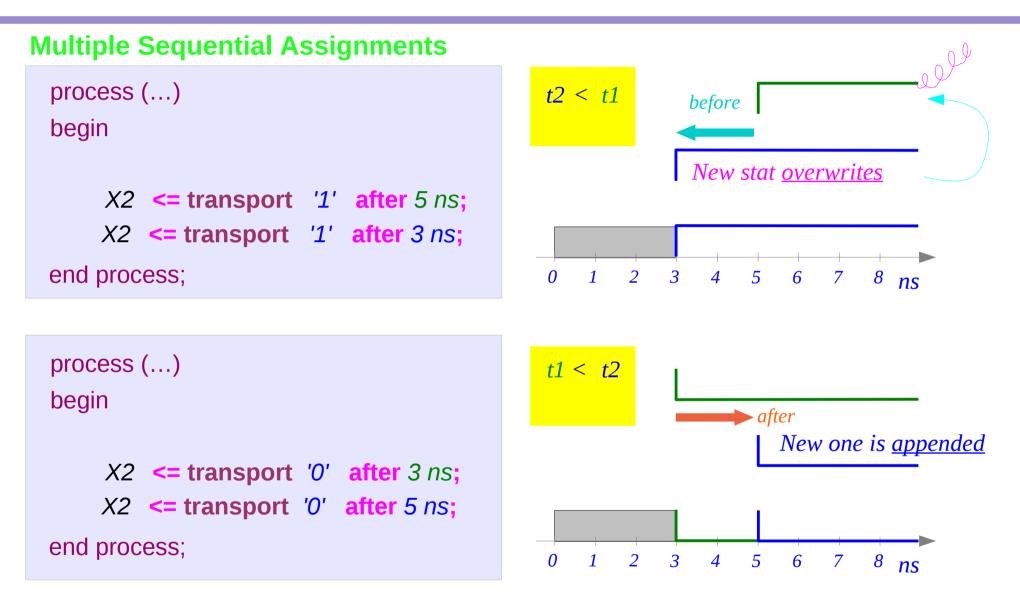

| Multiple Sequential Assignments                                |                            |

|----------------------------------------------------------------|----------------------------|

| process ()                                                     | t2 < t1                    |

| begin                                                          | before                     |

| X2 <= '1' after 5 ns;<br>X2 <= '1' after 3 ns;<br>end process; | New one <u>overwrites</u>  |

|                                                                |                            |

| process ()<br>begin                                            | t1 < t2 $v1 = v2$          |

| Sogni                                                          | after <u>Both</u> are kept |

| X2 <= '0' after 3 ns;                                          |                            |

| X2 <= '0' after 5 ns;                                          |                            |

| end process;                                                   | 0 1 2 3 4 5 6 7 8 ns       |

# Transport Delay (1)

# Transport Delay (2)

### **Inertial Delay**

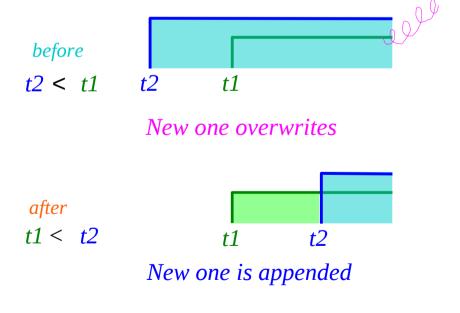

#### **Multiple Sequential Assignments – Inertial Delay**

t2 < t1v1 = v2New one overwrites $v1 \neq v2$ New one overwritest1 < t2v1 = v2Both are kept $v1 \neq v2$ New one overwrites

#### **Transport Delay**

#### **Multiple Sequential Assignments – Transport Delay**

#### *t*2 < *t*1 *New stat <u>overwrites</u>*

*t*1 < *t*2 *New stat is <u>appended</u>*

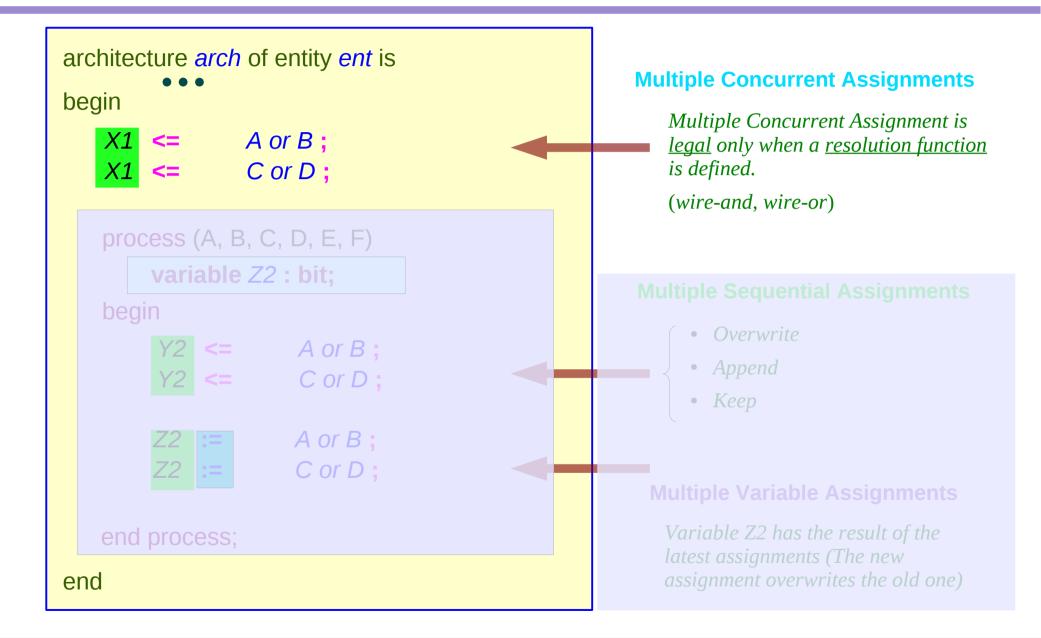

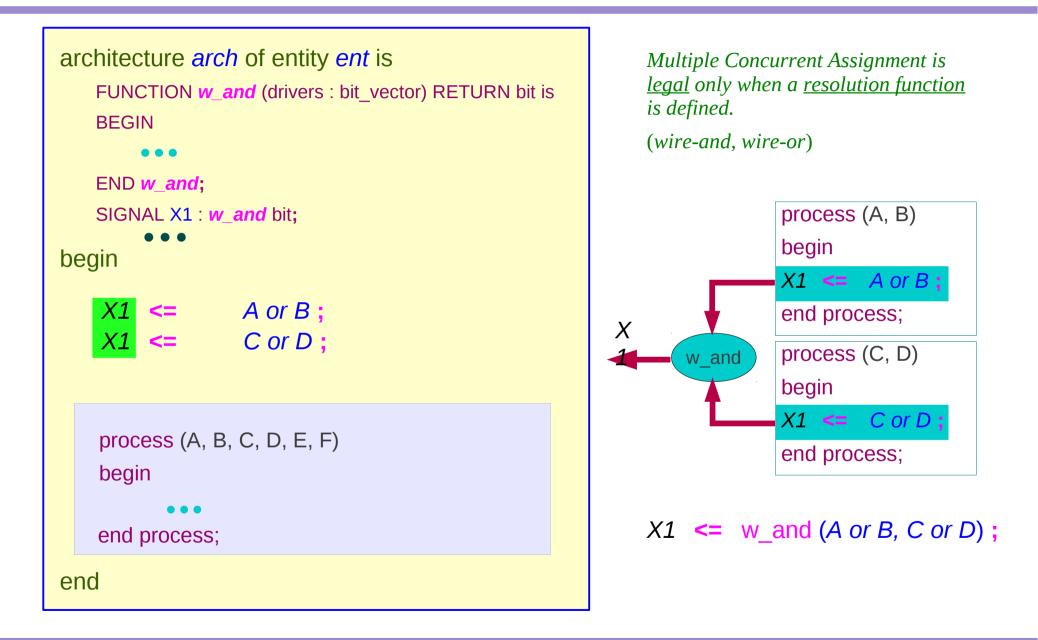

# **Multiple Concurrent Assignments**

# **Resolution Function**

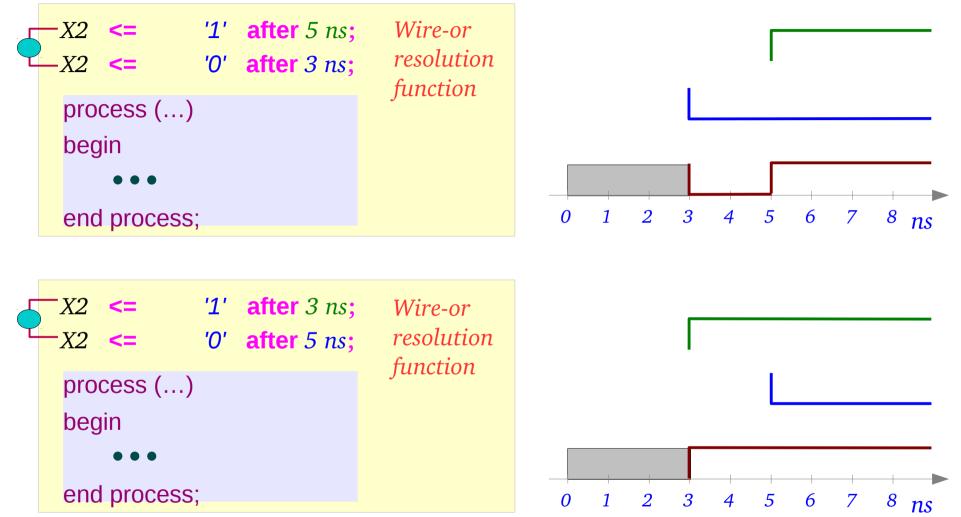

# **Inertial Delay**

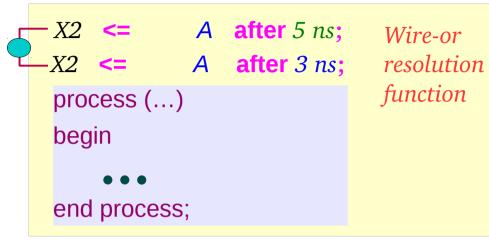

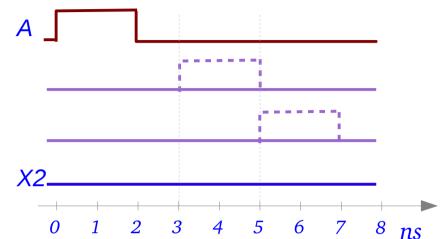

#### **Multiple Concurrent Assignments**

#### **Transport Delay**

#### **Multiple Concurrent Assignments**

end process;

function

**Inertial & Transport**

# **Inertial Delay**

#### **Multiple Concurrent Assignments**

| -X2 <=<br>-X2 <= | A after 3 ns;<br>A after 5 ns; | Wire-or<br>resolution |

|------------------|--------------------------------|-----------------------|

| process (        | )                              | function              |

| begin            |                                |                       |

| • • •            |                                |                       |

| end proces       | SS;                            |                       |

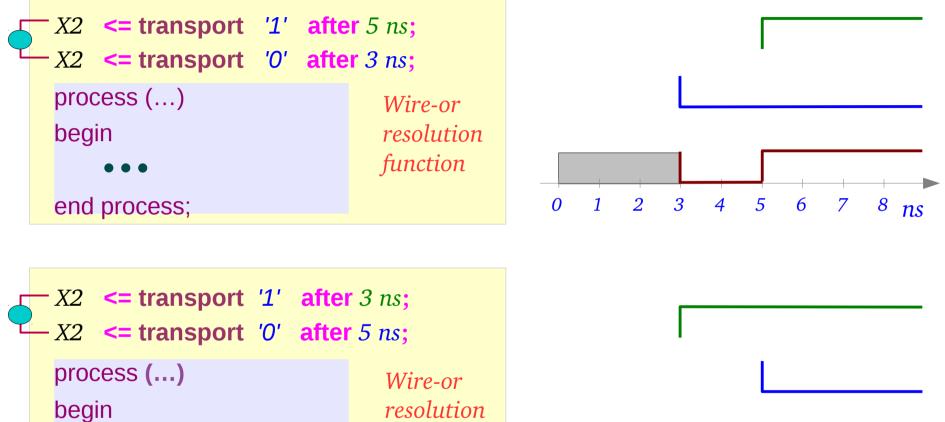

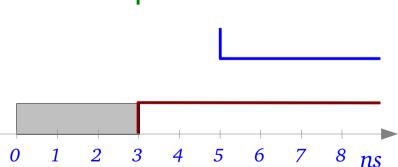

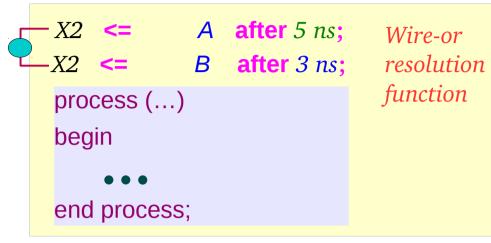

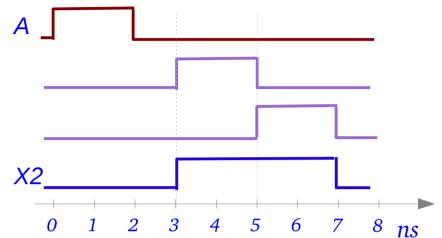

### **Transport Delay**

#### **Multiple Concurrent Assignments**

| -X2 <=<br>-X2 <= | A after 3 ns;<br>B after 5 ns; | Wire-or<br>resolution |

|------------------|--------------------------------|-----------------------|

| process (        | .)                             | function              |

| begin            |                                |                       |

| end proces       | SS;                            |                       |

#### References

- [1] http://en.wikipedia.org/

- [2] J. V. Spiegel, VHDL Tutorial, http://www.seas.upenn.edu/~ese171/vhdl/vhdl\_primer.html

- [3] J. R. Armstrong, F. G. Gray, Structured Logic Design with VHDL

- [4] Z. Navabi, VHDL Analysis and Modeling of Digital Systems

- [5] D. Smith, HDL Chip Design

- [6] http://www.csee.umbc.edu/portal/help/VHDL/stdpkg.html

- [7] VHDL Tutorial VHDL onlinewww.vhdl-online.de/tutorial/