Copyright (c) 2011 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

Young Won Lim 11/26/2011

Clock signal requires special care - special driver and distribution network

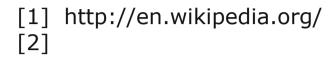

Derived clocks make things complicated

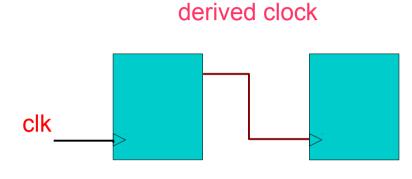

Use a synchronous enable signal

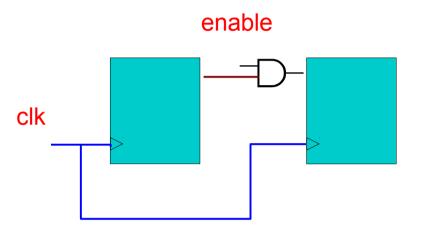

## Second and Minute Counter

4

### **Counter Template**

```

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric_std.all; -- for the unsigned type

entity COUNTER is

generic (

WIDTH : in natural := 32);

port (

: in std_logic;

RST

: in std logic;

CLK

: in std_logic;

EN

LOAD : in std_logic;

EN

()

DATA : in std_logic_vector(WIDTH1 downto 0);

LOAD

: out std_logic_vector(WIDTH-1 downto 0));

0

end entity COUNTER;

DATA

architecture RTL of COUNTER is

signal CNT : unsigned(WIDTH-1 downto 0);

begin

process(RST, CLK) is

begin

RST

if RST = '1' then

CNT <= (others => '0');

elsif rising edge(CLK) then

if LOAD = '1' then

CNT <= unsigned(DATA); -- type is converted to unsigned

elsif EN = '1' then

CNT \leq CNT + 1;

end if;

end if;

end process;

Q <= std_logic_vector(CNT); -- type is converted back to std_logic_vector

end architecture RTL;

```

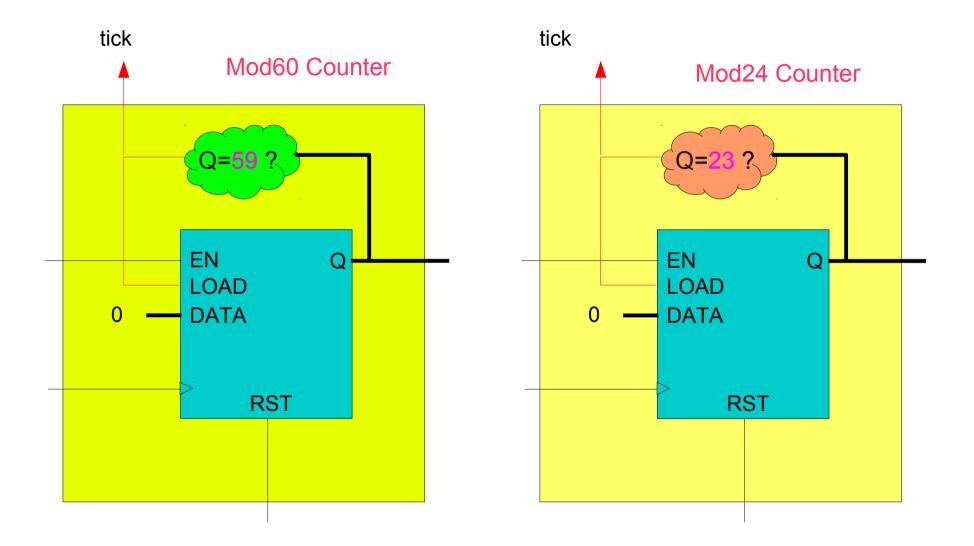

## Mod-60 and Mod-24 counter

#### **FF and Latch**

Young Won Lim 11/26/2011

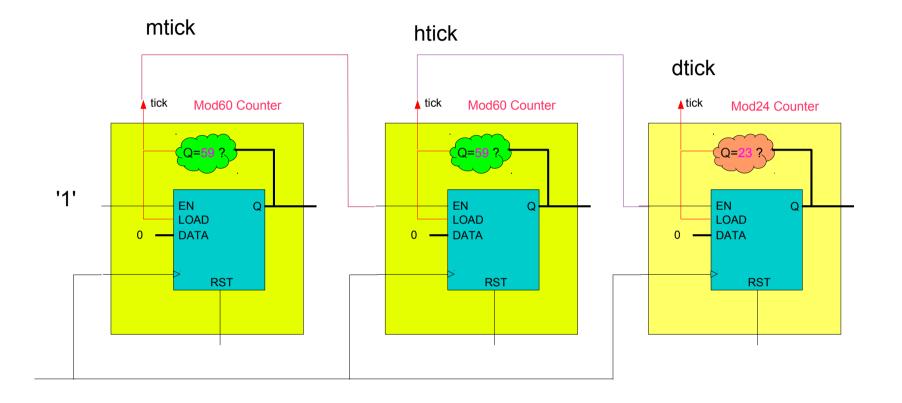

# Sec, Min, Hr Counters

7

#### **FF and Latch**

#### References