# Signals & Variables

| Copyright (c) 2012 Young W. Lim.                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License". |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

| Please send corrections (or suggestions) to youngwlim@hotmail.com.                                                                                                                                                                                                                                                                                                              |

| This document was produced by using OpenOffice and Octave.                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

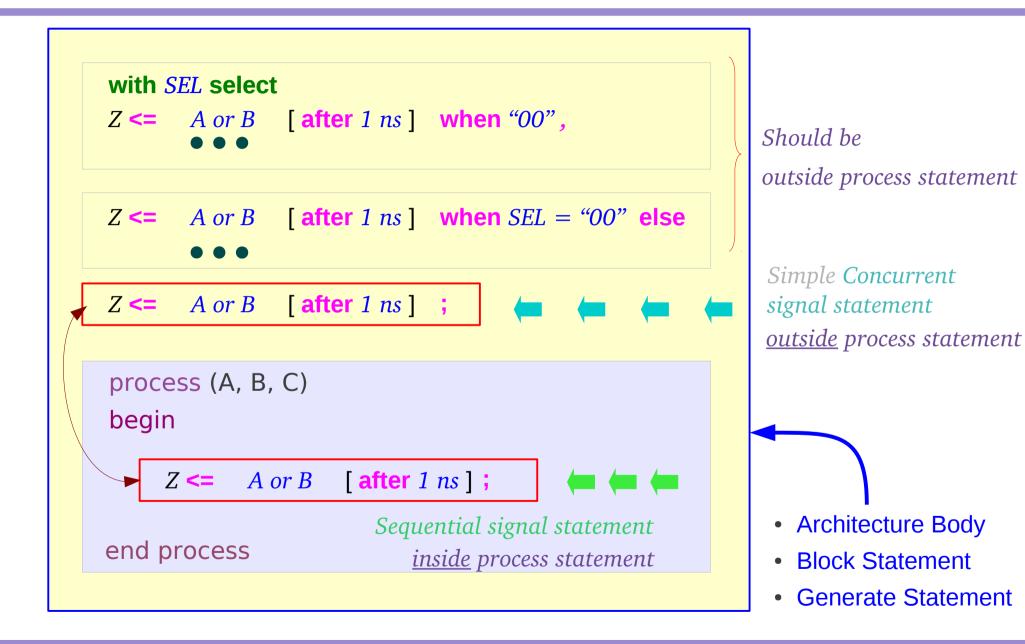

#### **Concurrent Statement**

- Block Statement

- Process Statement

- Component Statement

- Generate Statement

- Concurrent Signal Assignment

- Concurrent Assertion

- Concurrent Procedure Call

- Architecture Body

- Block Statement

- Generate Statement

- Conditional Signal Assignment

- Selected Signal Assignemnt

#### Sequential Statement

- Wait Statement

- Assertion Statement

- Report Statement

- Generate Statement

- Signal Assignment

- Variable Assignment

- Procedure Call

- If

- Case

- Loop

- Next

- Exit

- Return

- Null

- Case Statement

- If Statement

- Loop Statement

- Process Statement

- Subprogram Body

- Sequential Signal Assignment

- Conditional Signal Assignment

- Selected Signal Assignment

# Conditional Signal Assignment

```

Z \Leftarrow A \text{ or } B \quad [\text{ after } 1 \text{ } ns \text{ }] \quad \text{when } S0 = '1' \text{ else}

A \text{ or } C \quad [\text{ after } 2 \text{ } ns \text{ }] \quad \text{when } S1 = '1' \text{ else}

A \text{ or } D \quad [\text{ after } 3 \text{ } ns \text{ }] ;

Z \Leftarrow A \text{ or } B \quad [\text{ after } 1 \text{ } ns \text{ }] \quad \text{when } S0 = '1' \text{ else}

A \text{ or } C \quad [\text{ after } 2 \text{ } ns \text{ }] ;

Z \Leftarrow A \text{ or } B \quad [\text{ after } 1 \text{ } ns \text{ }] \quad \text{when } S0 = '1' ;

Z \Leftarrow A \text{ or } B \quad [\text{ after } 1 \text{ } ns \text{ }] \quad \text{when } S0 = '1' ;

```

- Concurrent Signal Assignment

- Conditional Signal Assignment

- Selected Signal Assignment

#### Selected Signal Assignment

Conditional Signal Assignment

```

Z \leftarrow A \text{ or } B [after 1 ns] when SEL = "00" else

A or C [after 2 ns] when SEL = "01" else

A or D [after 2 ns] when SEL = "10" else

A or E [after 3 ns] when SEL = "11" else

A or F [after 4 ns];

```

Selected Signal Assignment

```

with SEL select

Z <= A or B [after 1 ns] when "00",

A or C [after 2 ns] when "01",

A or D [after 3 ns] when "10",

A or E [after 4 ns] when "11",

A or F [after 5 ns] when others;</pre>

```

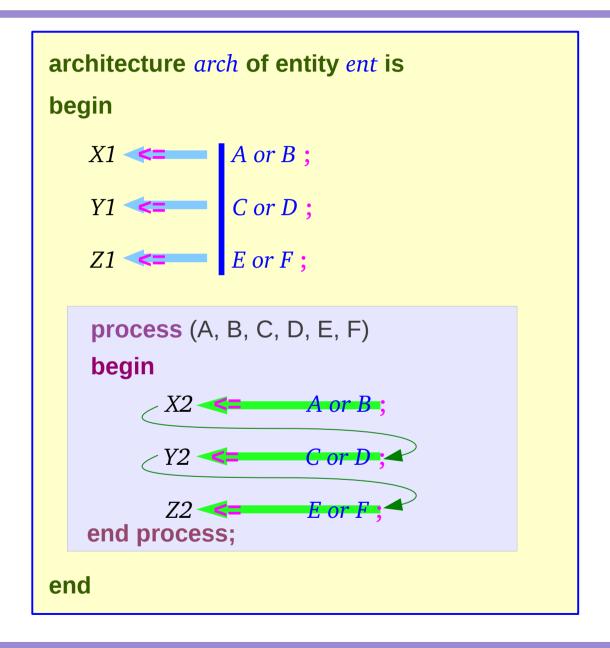

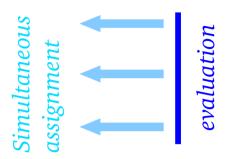

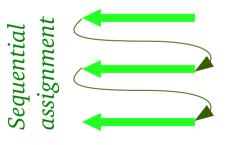

### Concurrent vs Sequential

#### **Order of Statements**

#### Simulation of parallel activities

#### The order of statements is important

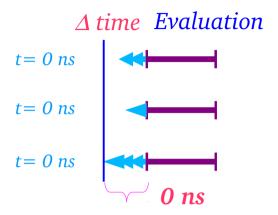

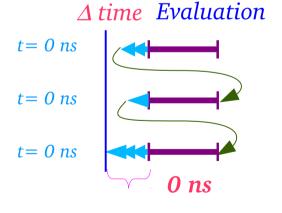

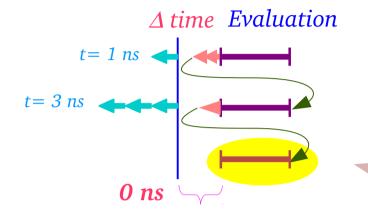

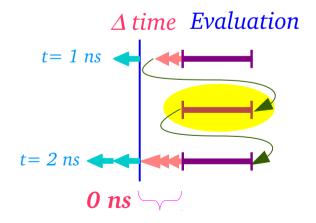

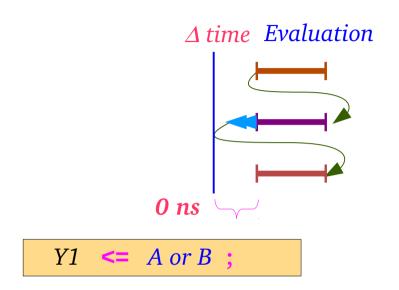

#### Simulation Time

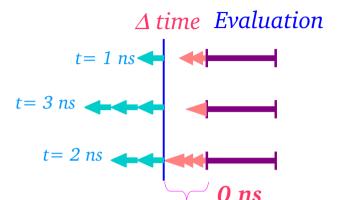

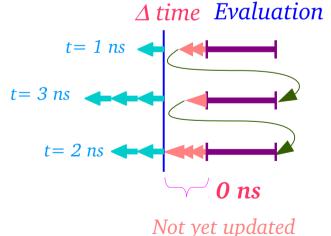

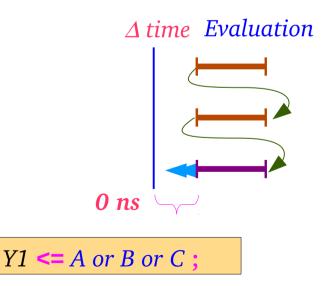

#### **Evaluation**

Simulation Time

is assumed to take no time

Unit: ms, ns, ps, ... Unitless Delta  $\Delta$

Real Delay

- used for a simulator to mimic parallel activities simulator

$$1\,ms\,=\,1000\,ns$$

$$1 ps \neq n \cdot \Delta$$

$1 \, ns = 1000 \, ps$

no integer n that make n delta equal to 1 ps.

$$n \cdot \Delta = \mathbf{0} \, ps = \mathbf{0} \, ns \cdots$$

Zero Delay

Zero Delay Assignment

$$X1 \leq A \text{ or } B$$

;

$X1 \leq A \text{ or } B \text{ after } 0 \text{ ns};$

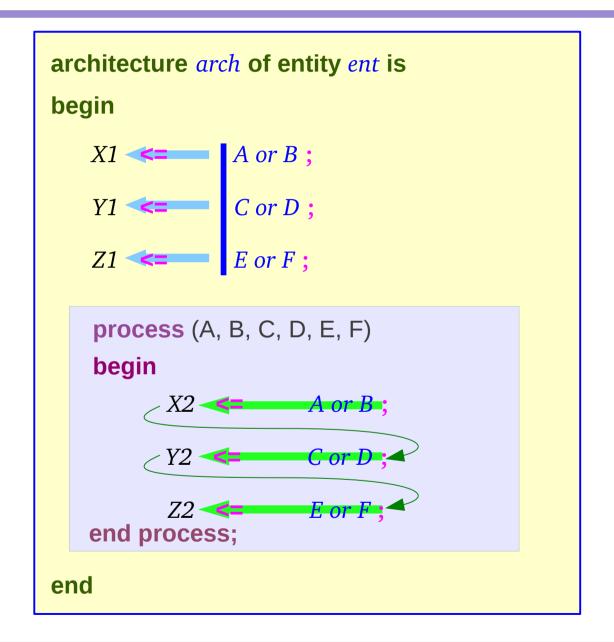

# Zero Delay Assignment

The exact no of delta is determined by the simulator and the context

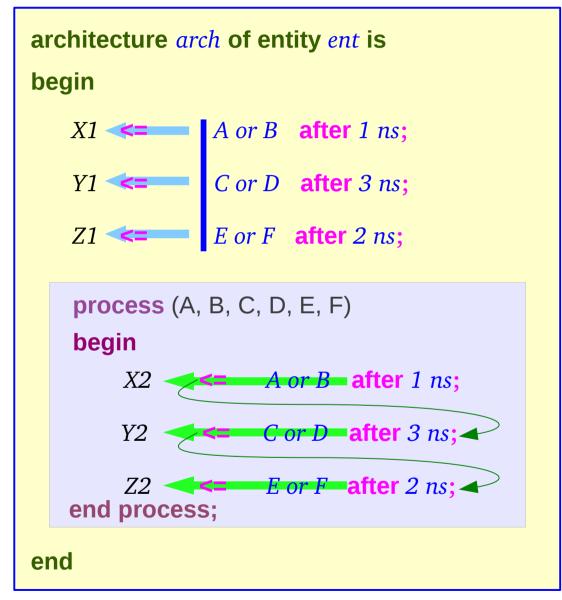

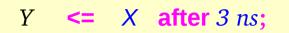

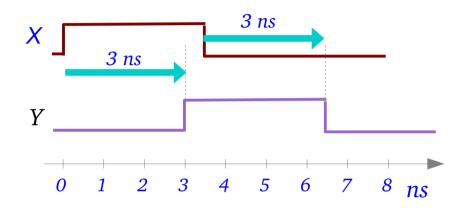

### Non-Zero Delay Assignment

The exact no of delta is determined by the simulator and the context

#### Inertial Delay & Transport Delay

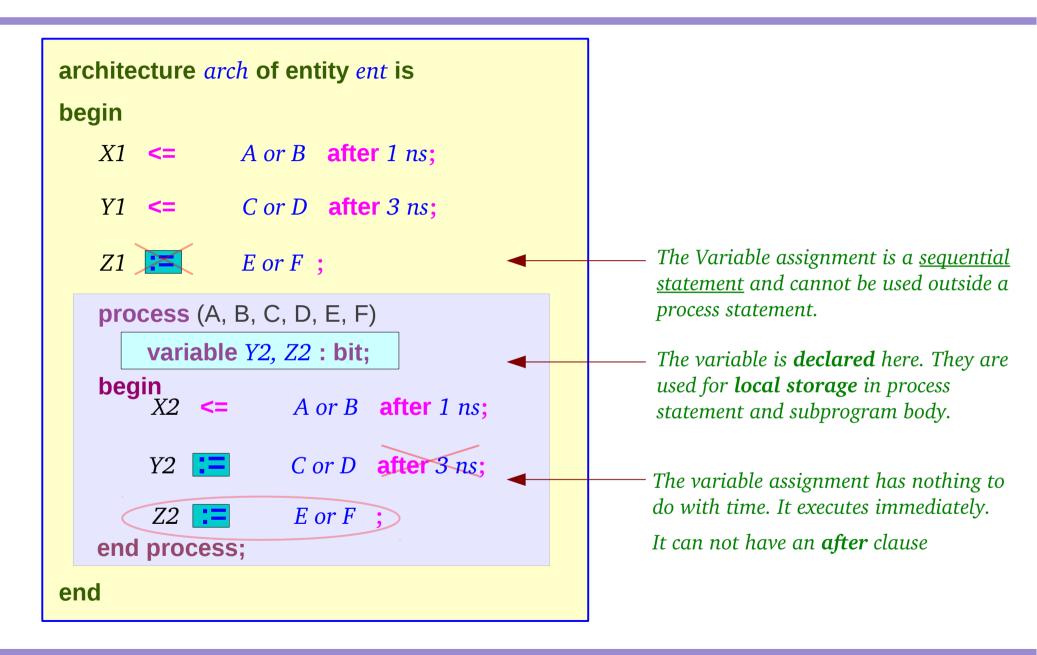

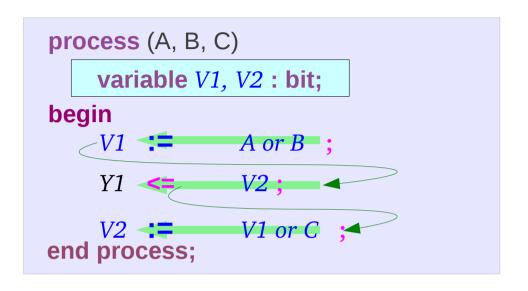

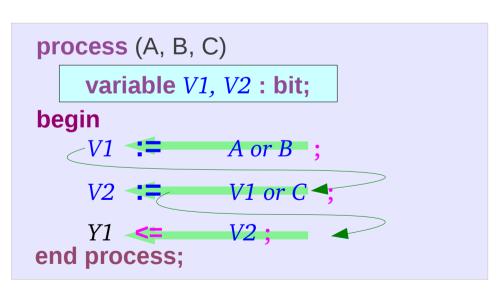

# Variable Assignment (1)

### Variable Assignment (2)

The variable assignment has nothing to do with time. It executes immediately.

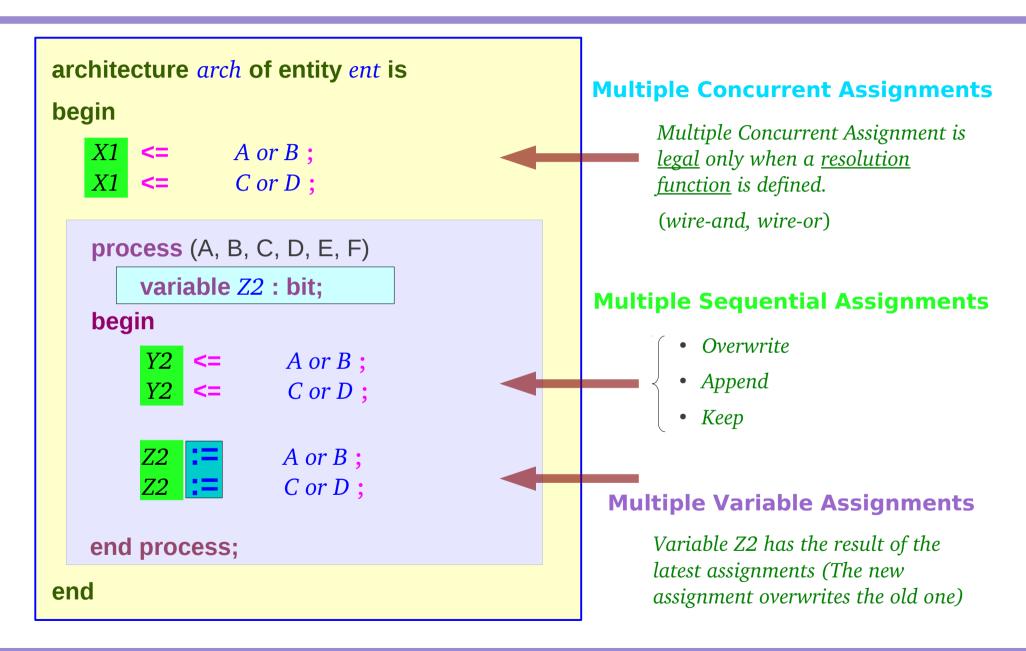

### Multiple Assignments to the Same Target

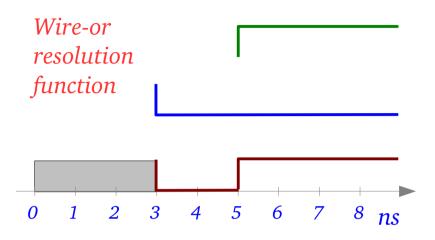

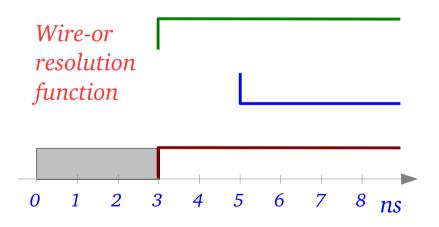

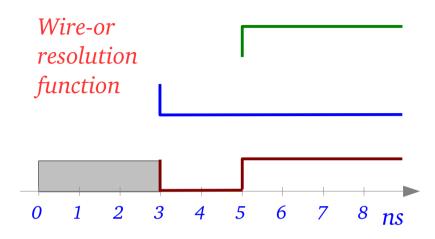

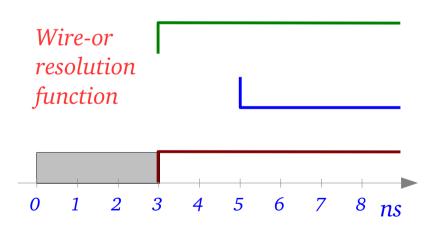

#### **Resolution Function**

```

architecture arch of entity ent is

FUNCTION w and (drivers : bit vector) RETURN bit is

BEGIN

Multiple Concurrent Assignment is

<u>legal</u> only when a <u>resolution</u>

<u>function</u> is defined.

END w and;

(wire-and, wire-or)

SIGNAL X1: w_and bit;

begin

\leftarrow A or B;

X1 \leq w_and(A \text{ or } B, C \text{ or } D);

\leftarrow C or D;

process (A, B, C, D, E, F)

begin

end process;

end

```

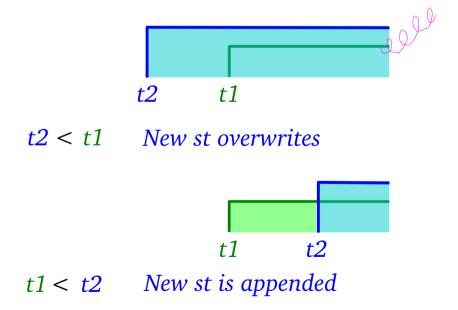

### **Inertial Delay**

#### **Multiple Concurrent Assignments**

### **Transport Delay**

#### **Multiple Concurrent Assignments**

```

X2 <= transport '1' after 5 ns;

X2 <= transport '0' after 3 ns;

process (...)

begin

end process;</pre>

```

```

X2 <= transport '1' after 3 ns;

X2 <= transport '0' after 5 ns;

process (...)

begin

end process;</pre>

```

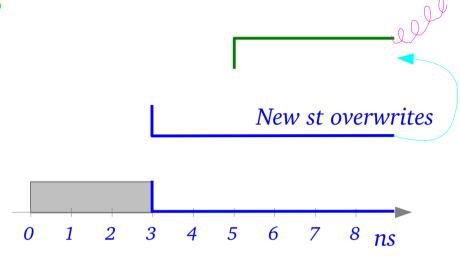

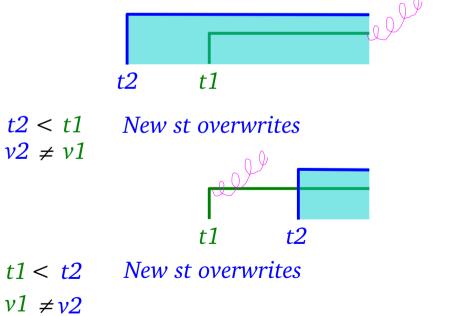

# Inertial Delay (1)

```

process (...)

begin

X2 <= '1' after 5 ns;

X2 <= '0' after 3 ns;

end process;

```

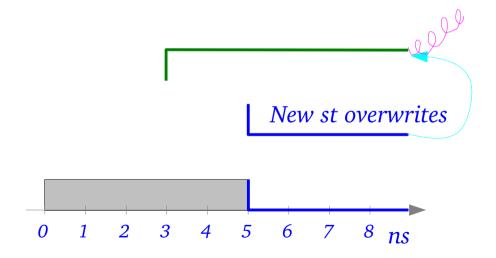

```

process (...)

begin

X2 <= '1' after 3 ns;

X2 <= '0' after 5 ns;

end process;

```

# Inertial Delay (2)

```

process (...)

begin

X2 <= '1' after 5 ns;

X2 <= '1' after 3 ns;

end process;

```

```

process (...)

begin

X2 <= '0' after 3 ns;

X2 <= '0' after 5 ns;

end process;

```

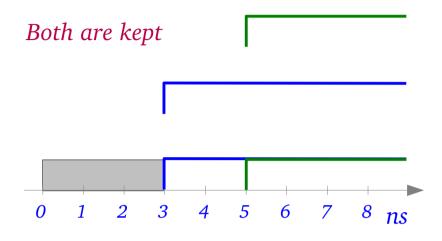

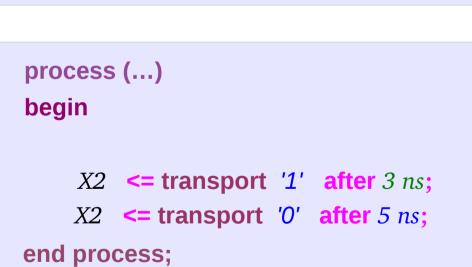

### **Transport Delay**

```

process (...)

begin

X2 <= transport '1' after 5 ns;

X2 <= transport '0' after 3 ns;

end process;

```

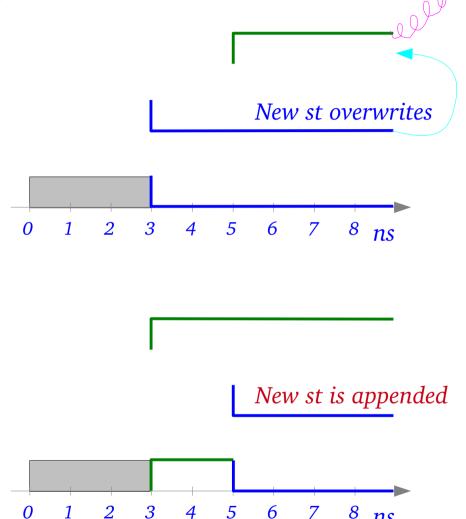

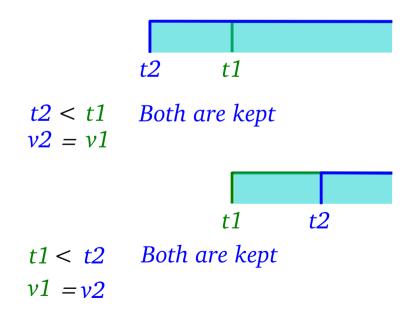

### **Inertial Delay**

```

process (...)

begin

X2 <= v1 after t1 ns;

X2 <= v2 after t2 ns;

end process;

```

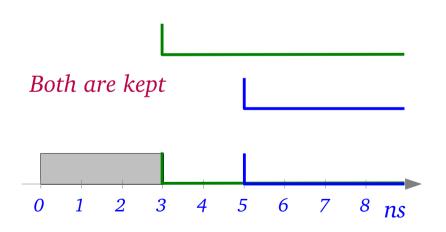

### **Transport Delay**

```

process (...)

begin

X2 <= transport v1 after t1 ns;

X2 <= transport v2 after t2 ns;

end process;

```

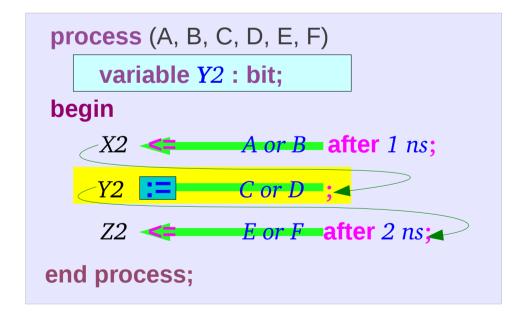

# Signals & Variable Assignment Example 1

#### References

- [1] http://en.wikipedia.org/

- [2] J. V. Spiegel, VHDL Tutorial, http://www.seas.upenn.edu/~ese171/vhdl/vhdl\_primer.html

- [3] J. R. Armstrong, F. G. Gray, Structured Logic Design with VHDL

- [4] Z. Navabi, VHDL Analysis and Modeling of Digital Systems

- [5] D. Smith, HDL Chip Design

- [6] http://www.csee.umbc.edu/portal/help/VHDL/stdpkg.html

- [7] VHDL Tutorial VHDL onlinewww.vhdl-online.de/tutorial/