#### IBA | Systems and Technology Group Hypervisor Overview Hypervisor (PR/SM) Logical View of 2 Book System - Virtualization layer at Operating System image level - Distributes physical resources Memory Memory Memory Channels L2 Cache L2 Cache EMIF Processors L1.5 L1.5 L1.5 L1.5 L1.5 L1.5 Logical processors dispatched on L1 L1 L1 L1 L1 L1 physical processors Dedicated / Shared PR/SM Affinities Share distribution based on weights

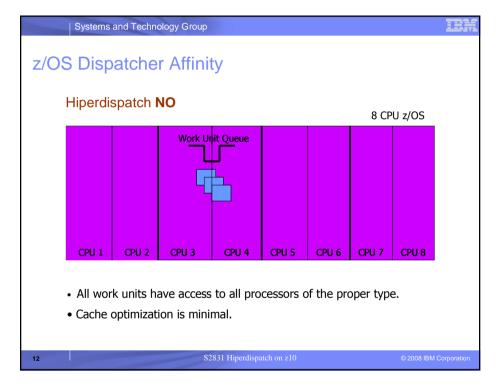

# Systems and Technology Group The motivation for HiperDispatch Hardware cache can be optimized when a given unit of work is consistently dispatched on the same physical CPU (or related set of CPUs) - In the past, System z hardware, firmware, and software have remained relatively independent of each other - But, the realities of modern processor and memory designs now make a change appropriate. • Different CPUs in the complex have different distances to the various sections of memory and cache (here, "distance" is measured in CPU cycles.) Memory access times can vary from less than 10 cycles to several hundred cycles depending upon cache level and whether the access is local or remote.

#### IBM

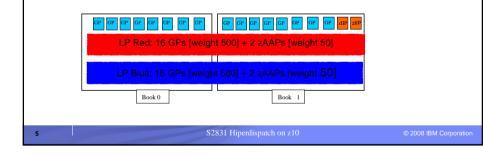

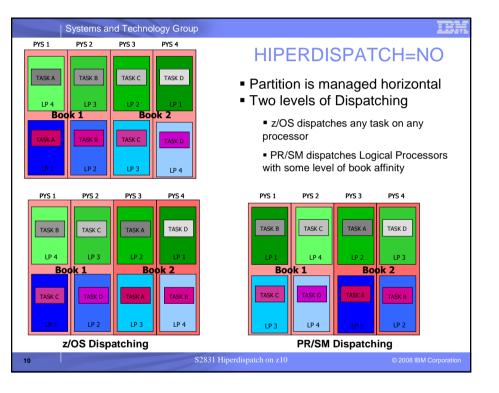

# Horizontal CPU management

- PR/SM guarantees an amount of CPU service to a partition based on weights

- PR/SM distributes a partition's share evenly across the logical processors

- Additional logicals are required to receive extra service which is left by other partitions. The extra service is also distributed evenly across the logicals.

- The OS must run on all logicals to gather all its share [z/OS Alternate Wait Management]

IEM

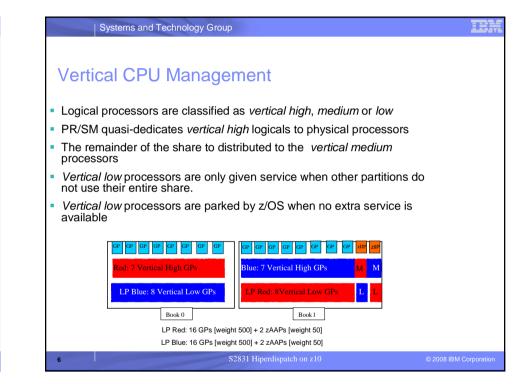

# HiperDispatch mode

### PR/SM

- Supplies topology information/updates to z/OS

- Ties *high priority* logicals to physicals (gives 100% share)

- Distributes remaining share to medium priority logicals

- Distributes any additional service to unparked *low priority* logicals

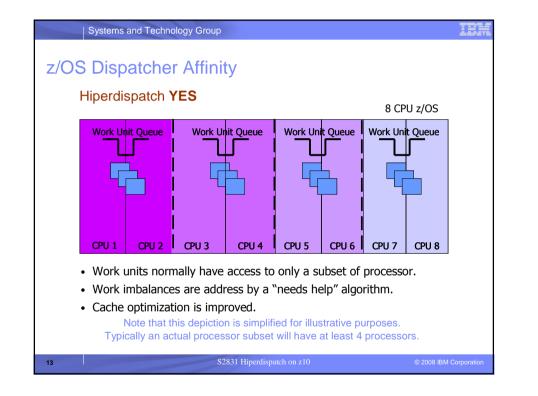

### z/OS

- Ties tasks to small subsets of logical processors

- Dispatches work to high priority subset of logicals

- Parks low priority processors that are not need or will not get service

- Hardware cache optimization occurs when a given unit of work is consistently dispatched on the same physical CPU

S2831 Hiperdispatch on z10

© 2008 IBM Corpora

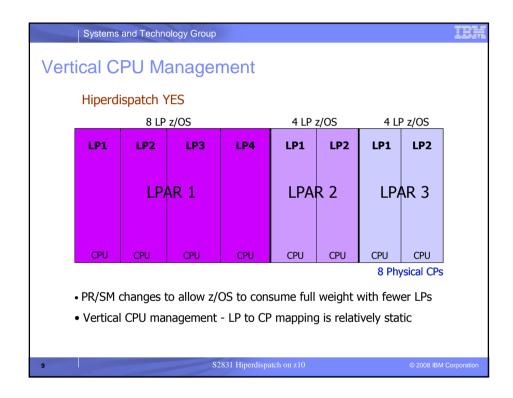

#### Systems and Technology Group Horizontal CPU Management Hiperdispatch NO 8 LP z/OS 4 LP z/OS 4 LP z/OS LP1 LP2 LP3 LP4 LP5 LP6 LP1 LP2 LP3 LP4 LP1 LP2 LP3 LP4 LP7 LP8 LPAR 2 LPAR 3 LPAR 1 CPU CPU CPU CPU CPU CPU CPU CPU 8 Physical CPs • Typical PR/SM 2-to-1 Logical Processor to physical CP overcommitment • High competition for physical processors • z/OS must use all LPs to consume full LPAR weight

# HIPERDISPATCH=YES DVC • Partition is managed vertical • PR/SM dispatching is reduced • z/OS dispatches work with

affinity to a small sets of processors

11

| PYS 1  | PYS 2  | PYS 3  | PYS 4  |  |

|--------|--------|--------|--------|--|

| TASK A | TASK B | TASK C | TASK D |  |

| TASK C | TASK D | TASK B | TASK A |  |

| LP 1   | LP 2   | LP 2   | LP 1   |  |

|        |        |        |        |  |

IBM

DVC A

IBM

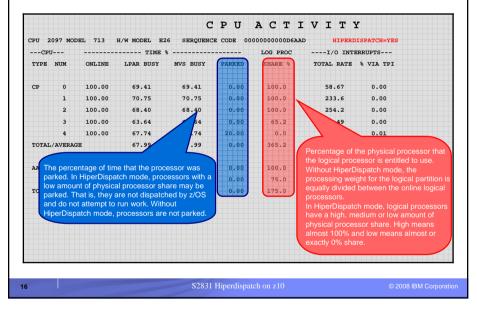

# **RMF CPU Activity Report**

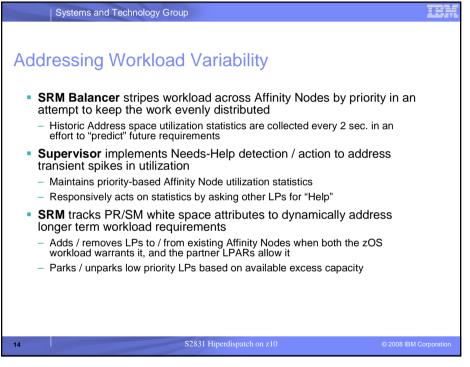

- In HiperDispatch mode, it is common to see very different utilizations across the logical processors

- Two new columns are added to the report:

- Parked %

15

- · Percent of the time the LP was in a parked state

- Logical Processor Share %

- Percent of a physical processor share that PR/SM will give to this LP if it can use it

- High Priority LPs have 100%

- Medium Priority LPs have between 1% and 100%

- Low Priority (discretionary) LPs have 0%

- MVS Busy Time definition:

Systems and Technology Group

# **RMF Monitor I CPU Report**

IER

IBN

# RMF CPU Report Example

|       |           |           |           |            |                      | C P U A      | CTIVII         | Y Y             |  |

|-------|-----------|-----------|-----------|------------|----------------------|--------------|----------------|-----------------|--|

|       | z/OS V1R8 |           |           | SYSTE      | SYSTEM ID UNKN       |              |                | DATE 11/26/2007 |  |

|       |           |           |           | RPT '      | RPT VERSION V1R8 RMF |              |                | TIME 22.33.43   |  |

| CPU : | 2097      | MODEL 732 | H/W MODEL | E40 SEQUEN | CE CODE 000          | 000000000DC6 | CE HIPERDIS    | PATCH=YES       |  |

| CP1   | CPU       |           | TIME %    |            |                      | LOG PROC     | I/O INTERRUPTS |                 |  |

| NUM   | TYPE      | ONLINE    | LPAR BUSY | MVS BUSY   | PARKED               | SHARE %      | RATE           | % VIA TPI       |  |

| 0     | CP        | 100.00    | 96.33     | 97.34      | 0.00                 | 100.0        | 5.80           | 48.75           |  |

| 1     | CP        | 100.00    | 95.96     | 97.07      | 0.00                 | 100.0        | 4.59           | 55.30           |  |

| 2     | CP        | 100.00    | 95.79     | 96.84      | 0.00                 | 100.0        | 5.10           | 55.18           |  |

| 3     | CP        | 100.00    | 95.46     | 96.68      | 0.00                 | 100.0        | 2.40           | 53.75           |  |

| 4     | CP        | 100.00    | 95.08     | 96.41      | 0.00                 | 100.0        | 8435           | 10.05           |  |

| 5     | CP        | 100.00    | 73.92     | 96.86      | 0.00                 | 70.0         | 20.74          | 4.95            |  |

| 6     | CP        | 100.00    | 74.33     | 97.13      | 0.00                 | 70.0         | 14.15          | 19.39           |  |

| 7     | CP        | 100.00    | 13.84     | 98.89      | 85.78                | 0.0          | 0.00           | 0.00            |  |

| TOT   | AL/AVE    | RAGE      | 80.09     | 96.94      |                      | 640.0        | 8488           | 10.14           |  |

Logical paritition share is 640% (6.4 CPUs) with 8 logical processors

5 LPs are *high priority* with 100% share

2 LPs are medium priority with 70% share

1 LP is low priority (discretionary) with 0% - it was parked 85.78% and busy 13.84%

liperdispatch on z10

© 2008 IBM Corporati

# Systems and Technology Group

#### 😢 RMF Data Portal - Mozilla Firefox: IBM Edition . 🗆 🛃 File Edit View Higtory Bookmarks Tools Help 🦛 • 🗼 • 🤁 💿 🏠 🕒 http://boetrx1:8803/ - - G- G 🕼 Google 🊾 IBM Corporate Intranet 🎆 IDE Management Sys... 🐭 Yahool Deutschland 🏧 z-OS Resource Meas... W Hauptseite - Wikipedia 🗀 IBM 📄 Dashboard - WCv2 RMF Monitor III Data Portal for z/OS Explore + 🥔 🛱 ← → → 20080215110900 - ▷ Overview RMF Report [,TRX1,MVS\_IMAGE] : CPC (Central Processor Complex) My View Time Range: 02/15/2008 11:09:00 - 02/15/2008 11:10:00 Partition Name: TRX1 CPU Type: 2097 CPU Model: 7 lome The Monitor III Data Portal displays in Weight % of Max: \*\*\*\* 4h MSU Average: 3 Capacity Grou the CPC report the logical processor share and – if HiperDispatch is active – the number of processors with high, medium and low share WLM Capping %: 0.0 4h MSU Maximum: 5 Capacity Group Proj Time until Capping: 0 CPU No: 00000000001EBAE # CP Process # AAP Processors: 1 # ICF Processors: 1 #IFL Processo Configured Partitions: 60 Wait Completion: NO % Canacity II # Dedicated IIPs: 0 # Dedicated AAPs: 0 # Shared physi # Shared physical IIPs: 1 Vary CPU management available: NO WLM LPAR ma Physical Total % of shared IIPs: 0.0 Physical Total % of shared AAPs: 0.0 Physical Total % of shared ICFs: 0.0 Physical Total Defined Actual Capping Processors Effective Logical LAPAR Physical # Colline # Online Current Logical Hope Displate: https://docume.colline Bigstate: https://docume.colline # Adv M Sub M Sub M Sub M Sub Notice % Total % % % Total % LPAR Name 15 15 0.0 0.3 0.4 CP 3 0.7 0.7 0.0 0.4 0.4 CP 3 0.7 0.7 0.0 0.4 0.4 CP 3 0.7 0.0 0.4 0.4 CP 3 0.0 0.0 0.0 0.0 CP 8 0.0 0.0 0.0 0.0 CP 8 0.1 0.1 0.0 0.0 CP 8 \*CP 132 3858 3858 800 89.8 800 69.5 999 42.0 999 42.0 10 3.3 TRX2 0 TRX1 0 3 NO 3.0 3 NO 7.0 0 NO 8.0 N/A 2 N/A N/A N/A N/A TE N/A 1 N/A N/A N/A 4 RMF 0 H05LP39 0 N/A NO 8.0 N/A H05LP54 0 0 TRX2CFA 0 0 NO 1.0 10 N/A N/A 1 18

IBA

### IBM

# HiperDispatch vs IRD CPU management

- Intelligent Resource Director (IRD) CPU management

- Automatically adjusts the number of <u>online</u> CPUs to achieve the minimum required to run the work of the partition.

- Actually varies the CPUs online/offline

- offline CPUs get no share distribution

- Reacts on a relatively long time scale (minutes)

- HiperDispatch mode

19

- automatically adjusts the number of <u>active</u> CPUs to achieve the minimum required to run the work of the partition.

- "Parks" unused processors. Parking is simply placing a CPU in a long-term wait until it is again needed to run work.

- Parked CPUs get no share distribution

- WLM can park/unpark CPUs over a relatively short time scale (seconds)

- IRD CPU management is disabled in HiperDispatch mode

© 2008 IBM Corporati

## Systems and Technology Group

# Special processing for SYSSTC

- Work classified to SYSSTC typically contains lots of short-running local SRBs required for transaction flow.

- Examples of address spaces recommended to be classified into SYSSTC are VTAM, TCP/IP and IRLM.

- SRBs classified into SYSSTC can execute on <u>any</u> available logical processor even HiperDispatch mode.

- WLM service policies should be reviewed with this in mind.

h on z10

IBM

# Controlling HiperDispatch

- HiperDispatch mode is enabled by specifying HIPERDISPATCH=YES in IEAOPTxx

- The default is HIPERDISPATCH=NO for compatibility

- But, HIPERDISPATCH=YES is recommended

- There is a HealthChecker routine to remind if HIPERDISPATCH=NO

- Control authority for global performance data must be enable for proper operation with HiperDispatch mode

- This option is selected in the logical partition security controls on the Hardware Management Console

- This is the default selection.

21

S2831 Hiperdispatch on z10

© 2008 IBM Corporatio