# **Burroughs** Corporation

το:

INTER-OFFICE CORRESPONDENCE

See Distribution attached

| CORPORATE UNIT                | LOCATION                                                             | DEPT.                     |

|-------------------------------|----------------------------------------------------------------------|---------------------------|

| Computer Systems Group        | Santa Barbara Plant                                                  | Systems Eng. Section 6311 |

| NAME.                         | a an ann a' <u>a' a staineanna an an ann ann an an ann ann ann a</u> | DA 11.                    |

| C. E. Wymore, Manager         |                                                                      | 30 March 1976             |

| <sup>FROM</sup><br>R. Matsuda | DEPT. & LOCATION<br>Systems Engine                                   | ering Section 6311 - SBP  |

| SUBJECT:                      |                                                                      | C.C.                      |

PRELIMINARY RELEASE OF THE M-PROCESSOR-3 ENGINEERING DESIGN SPECIFICATION

This preliminary release of the M-processor-3 (MP-3) Engineering Design Specification (EDS) is an editorial update of the 16 January version (Rev B). Also included in this release are the contents of the two inter-office memorandums:

1. Changes to M-Processor-3 EDS 3 February 1976, C.E. Wymore

2. Change to M-Processor-3 EDS: II 4 February 1976, C.E. Wymore

There were still other technical details which were unresolved as of the January Transfer of Information and those which have been resolved as of 26 March are also included in this release. Some of those issues are:

a. TIME-half microsecond time counter up to 24 bits (approximately 8 seconds);

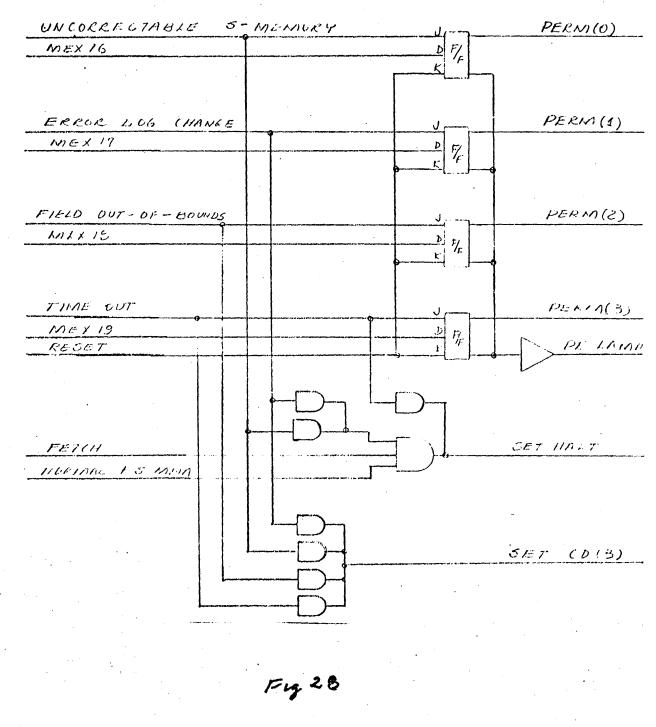

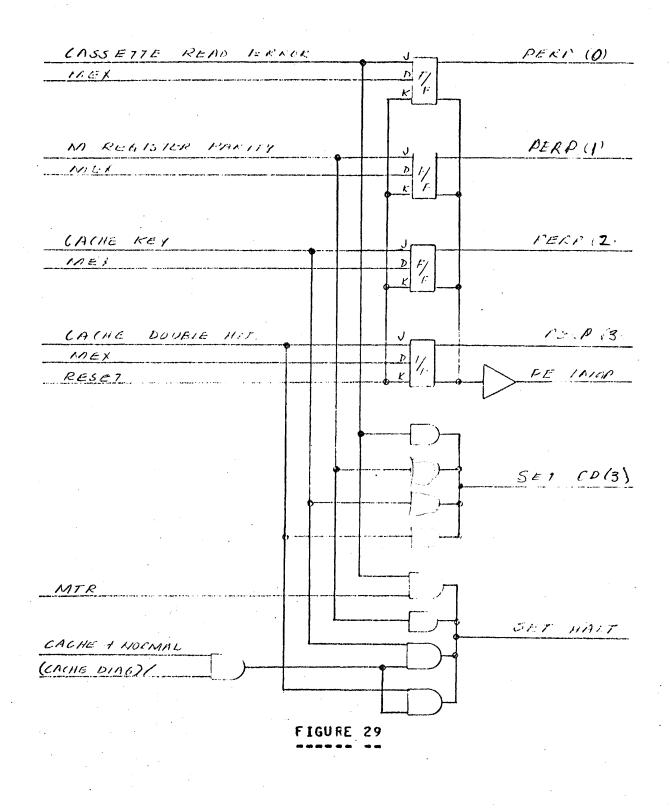

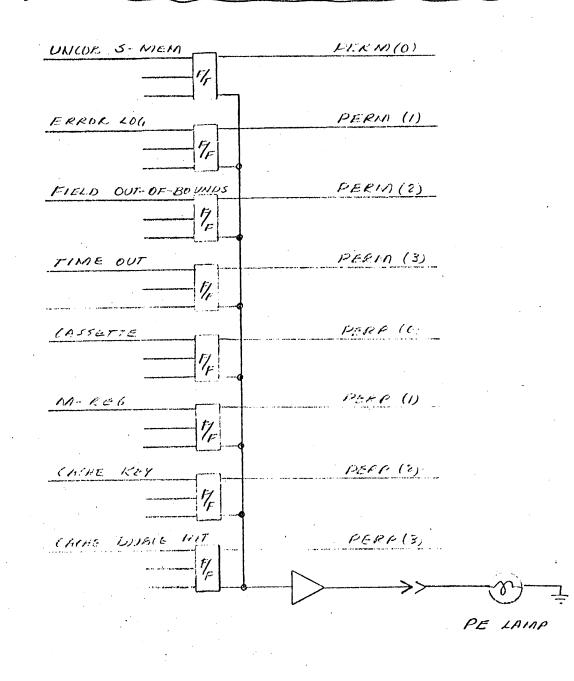

b. PERM and PERP register relationship with respect to Halt, CD(3), Console display, and clearing;

c. MSSW - can be dynamically changed;

d. Operation of A and M - register during TAPE mode;

- e. Skip on FA and BR comparison;

- f. Diagnostic Read/Write Memory micro (11D) echo variants

- g. CA-RC spreader 8 clocks for RC-RC, 4 clocks for RC-CA;

- h. Error log message finalization of the format;

- i. Increment A register new micro; and

- j. 18 Position Console Rotary Switch redefinition.

The EDS at this stage still needs more work in the description of the threephase or pipeline mechanism. Also, the general control logic philosophy and design needs more editing. Those figures for both sections must be drawn. Otherwise, for final release, the processor description will not be expanded. In many areas, the machine is much like the B1726 and it is assumed that the knowledge of it with this simple EDS is sufficient to describe the MP-3.

R Materia

R. Matsuda Systems Eng. Section 6311

Attachments

# M – PROCESSOR – 3

ENGINEERING DESIGN <sup>3</sup>SPECIFICATION

# 2 2 1 5 9 8 9 1

# R E V. 8

AS OF 10:00 FRIDAY 16 JANUARY 76

# REV. C

MARCH 26, 1976

# TABLE OF CONTENTS

| 1.0 INTRODUCTION                                    | PAGE | 1   |

|-----------------------------------------------------|------|-----|

| 1.1 PURPOSE                                         | PAGE | 1   |

| 1.2 EDS PHILOSOPHY                                  | PAGE | 1   |

| 1.3 PRODUCT IDENTIFICATION                          | PAGE | 1   |

| 1.4 RELATED SPECIFICATIONS, DOCUMENTS, AND DRAWINGS | PAGE | 1   |

| 2.0 GENERAL DESCRIPTION.                            | PAGE | 3   |

|                                                     |      | -   |

| 2.1 THREE PHASE MICRO EXECUTION                     | PAGE | 16  |

| 3.0 PRODUCT DESCRIPTION                             | PAGE | 19  |

| 3.1 PROCESSOR REGISTERS                             | PAGE | 19  |

| 3.1.1 M                                             | PAGE | 19  |

| 3.1.2 A-REGISTER                                    | PAGE | 19  |

|                                                     | PAGE |     |

|                                                     |      | 20  |

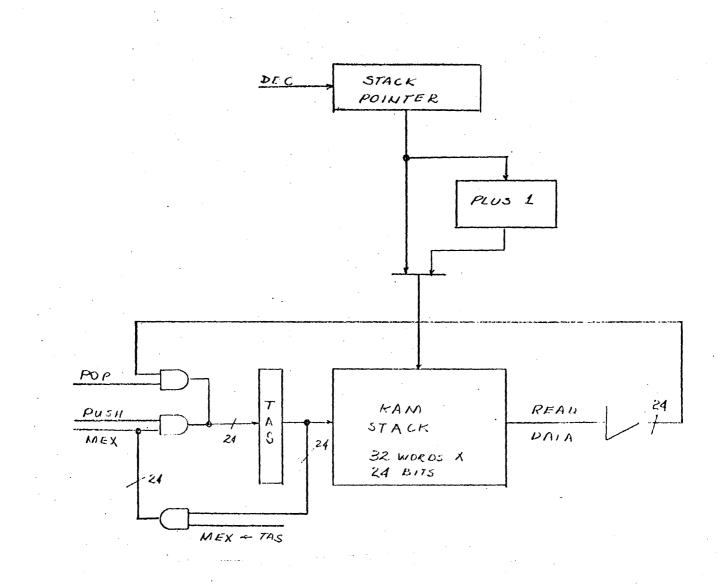

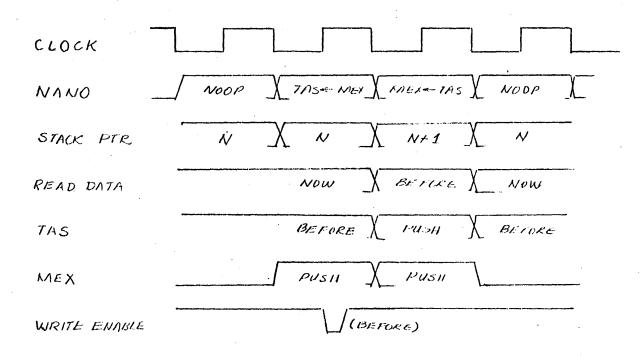

| 3.1.4 A-STACK                                       | PAGE | 20  |

| 3.1.5 X AND Y                                       | PAGE | 26  |

| 3.1.6 L                                             | PAGE | 26  |

| 3.1.7 T                                             | PAGE | 27  |

| 3.1.8 FA                                            | PAGE | 27  |

|                                                     |      |     |

| 3.1.9 FB                                            | PAGE | 28  |

| 3.1.10 SCRATCHPAD                                   | PAGE | 28  |

| 3.1.11 FLCN                                         | PAGE | 29  |

| 3.1.12 BR AND LR                                    | PAGE | 29  |

|                                                     | PAGE | 30  |

|                                                     |      |     |

| 3.1.13.1 CP (CYF, CPU, CPL)                         | PAGE | 30  |

| 3.1.13.2 CA, CB, CC, CD                             | PAGE | 30  |

| 3.1.14 MAXS                                         | PAGE | 32  |

| 3.1.15 U                                            | PAGE | 32  |

| 3.1.16 DATA                                         | PAGE | 33  |

|                                                     |      |     |

|                                                     | PAGE | 34  |

| 3.1.18 NULL                                         | PAGE | 34  |

| 3.1.19 CSH                                          | PAGE | 34  |

| 3.1.20 MSSW                                         | PAGE | 34  |

| 3.1.21 NULLA, NULLB, NULLC, NULLD, and NULLE        | PAGE | 35  |

| 3-1-22 RESERVED                                     | PAGE | 35  |

|                                                     |      |     |

| 3.2 24-BIT FUNCTION BOX                             | PAGE | 36  |

| 3.2.1 SUM                                           | PAGE | 36  |

| 3.2.2 DIFF                                          | PAGE | 37  |

| 3.2.3 XANY, XORY, XEOY                              | PAGE | 37  |

| 3.2.4 CHPX, CHPY                                    | PAGE | 38  |

| 3.2.5 MSKX, HSKY                                    | PAGE | 38  |

|                                                     |      |     |

| 3.2.6 BICN                                          | PAGE | 38  |

| 3.2.7 XYCN                                          | PAGE | 39  |

| 3.2.8 XYST                                          | PAGE | 39  |

| 3.2.9 INCN                                          | PAGE | 40  |

| 3.2.10 PERM (PARITY ERROR MEMORY)                   | PAGE | 40  |

|                                                     |      |     |

| 3.2.11 PERP (Parity Error Processor)                | PAGE | 43  |

| 3.2.12 TIME                                         | PAGE | 47  |

| 3.3 4-BIT FUNCTION BOX                              | PAGE | 47  |

| 3.4 M-INSTRUCTIONS                                  | PAGE | 47  |

| 3.4.1 REGISTER NOVE                                 | PAGE | 48  |

| 3.4.2 SCRATCHPAD MOVE.                              | PAGE |     |

|                                                     |      | 48  |

| 3.4.3 SWAP F WITH DOUBLEPAD WORD                    | PAGE | 49  |

| 3.4.4 STORE F INTO DOUBLEPAD WORD                   | PAGE | 50  |

| 3.4.5 LOAD F FROM DOUBLEPAD WORD                    | PAGE | 50  |

| 3.4.6 MOVE 8-BIT LITERAL                            | PAGE | 50  |

| 3.4.7 MOVE 24-BIT LITERAL                           | PAGE | 51  |

|                                                     | PAGE | 51  |

|                                                     |      |     |

| 3.4.9 READ/WRITE MEMORY                             | PAGE | 52  |

| 3.4.10 COUNT FA/FL                                  | PAGE | 53  |

| 3.4.11 SCRATCHPAD RELATE FA                         | PAGE | 54  |

| 3.4.12 EXTRACT FROM REGISTER T                      | PAGE | 54  |

| 3.4.13 SHIFT/ROTATE REGISTER T LEFT                 | PAGE | 54  |

| 3.4.14 SHIFT/ROTATE REGISTER X/Y I FFT/RIGHT        | PAGE | 55  |

|                                                     |      | , , |

|                                                     |      |     |

· M .

...

| 3.4.15 SHIFT/ROTATE REGISTERS XY LEFT/RIGHT                  | PAGE 56   |

|--------------------------------------------------------------|-----------|

| 3.4.16 NORMALIZE X                                           | PAGE 56   |

| 3.4.17 READ/WRITE CACHE                                      | PAGE 56   |

| 3.4.18 CALL                                                  | PAGE 61   |

| 3.4.19 BRANCH                                                | PAGE 62   |

| 3.4.20 BIAS.                                                 |           |

|                                                              | PAGE 62   |

| 3.4.21 SET CYF                                               | PAGE 63   |

| 3.4.22 4-BIT MANIPULATE                                      | PAGE 63   |

| 3.4.23 BIT TEST BRANCH FALSE                                 | PAGE 64   |

| 3.4.24 BIT TEST BRANCH TRUE                                  | PAGE 65   |

| 3.4.25 SKIP WHEN                                             | PAGE 65   |

| 3.4.26 CLEAR REGISTERS                                       | PAGE 67   |

| 3.4.27 BIND                                                  | PAGE 67   |

| 3.4.28 DVERLAY M-MEMORY.                                     | PAGE 67   |

|                                                              |           |

|                                                              | PAGE 68   |

| 3.4.30 CASSETTE CONTROL.                                     | PAGE 71   |

| 3.4.31 HALT                                                  | PAGE 71   |

| 3.4.32 NO OPERATION                                          | PAGE 72   |

|                                                              | PAGE 72   |

| 3.4.34 NANO MOVE                                             | PAGE 72   |

| 3.4.35 DIAGNOSTIC READ/WRITE NEMORY                          | PAGE 76   |

| 3.4.36 CLEAR CACHE                                           |           |

|                                                              | PAGE 83   |

| 3.4.37 INCREMENT A-REGISTER                                  | PAGE 83   |

| 3.5 CONTROL PANEL OPERATIONS                                 | PAGE 83   |

| 3.5.1 DIAGNOSTIC AND MAINTENANCE PANEL                       | PAGE 83   |

| 3.5.1.1 REGISTER SELECT SWITCH                               | PAGE 84   |

| 3.5.1.2 REGISTER GROUP SWITCH.                               | PAGE 85   |

| 3.5.1.3 M-INPUT SWITCH                                       | PAGE 85   |

| 3.5.1.4 INTERRUPT SWITCH                                     | PAGE 86   |

|                                                              |           |

|                                                              | PAGE 86   |

| 3.5.1.6 HALT SWITCH.                                         | PAGE 86   |

| 3.5.1.7 CLEAR SWITCH                                         | PAGE 87   |

| 3.5.1.8 START SWITCH                                         | PAGE 87   |

| 3.5.1.9 CASSETTE SELECT                                      | PAGE 87   |

| 3.5.1.10 INCREMENT SWITCH                                    | PAGE 87   |

| 3.5.1.11 SINGLE MICRO/CONTINUOUS                             | PAGE 87   |

| 3.5.1.12 DATA SWITCHES                                       | PAGE 87   |

| 3.5.1.13 STATE LIGHT                                         | PAGE 88   |

| 3-5-1-14 RUN LIGHT                                           |           |

|                                                              | PAGE 88   |

| 3-5-1-15 ERROR LIGHT                                         | PAGE 88   |

| 3.5.1.16 OVER TEMPERATURE LIGHT.                             | PAGE 88   |

| 3.5.1.17 DATA LIGHTS                                         | PAGE 88   |

| 3.5.2 RENOTE OPERATIONAL PANEL                               | PAGE 88   |

| 3.5.2.1 BOT LIGHT                                            | PAGE 89   |

| 3.5.2.2 START SWITCH AND LIGHT                               | PAGE 89   |

| 3.5.2.3 INTERRUPT SHITCH AND LIGHT                           | PAGE 89   |

| 3.5.2.4 CLEAR SWITCH                                         |           |

|                                                              | PAGE 89   |

| 3.5.2.5 TAPE/NORMAL SWITCH                                   | PAGE 89   |

| 3.5.3 LOAD/DISPLAY OPERATIONS.                               | PAGE 89   |

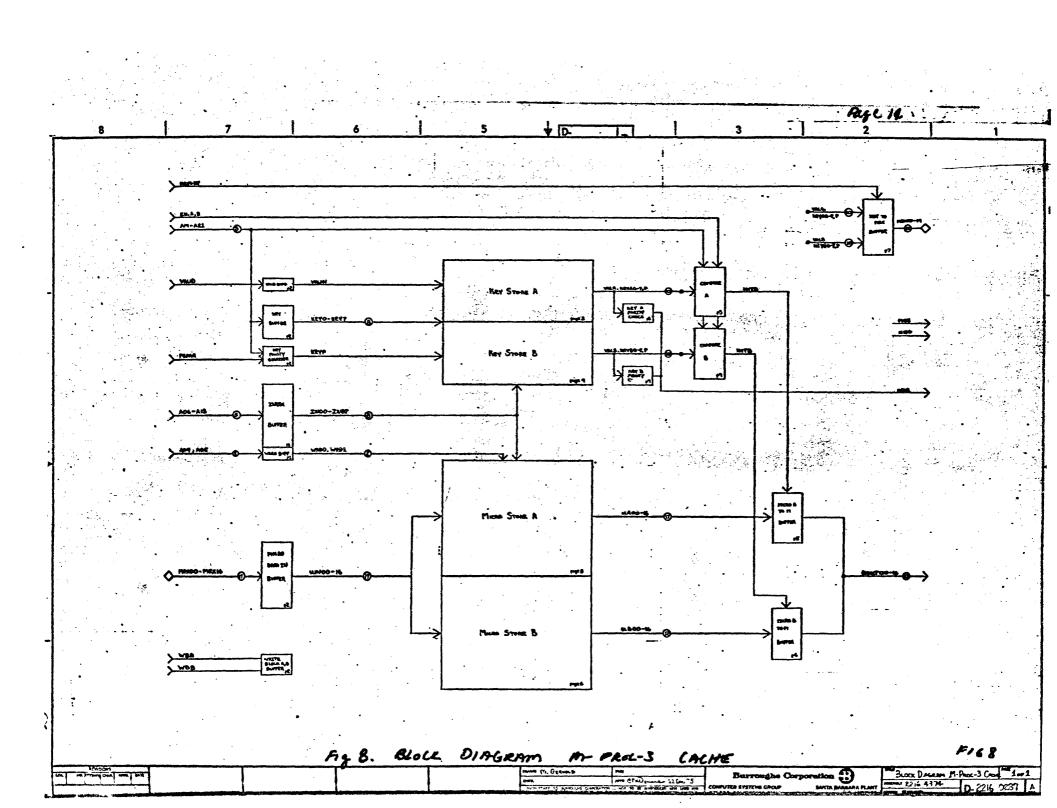

| 3.6 CACHE                                                    | PAGE 94   |

| 3.7 PROCESSOR CONTROL LOGIC                                  | PAGE 94   |

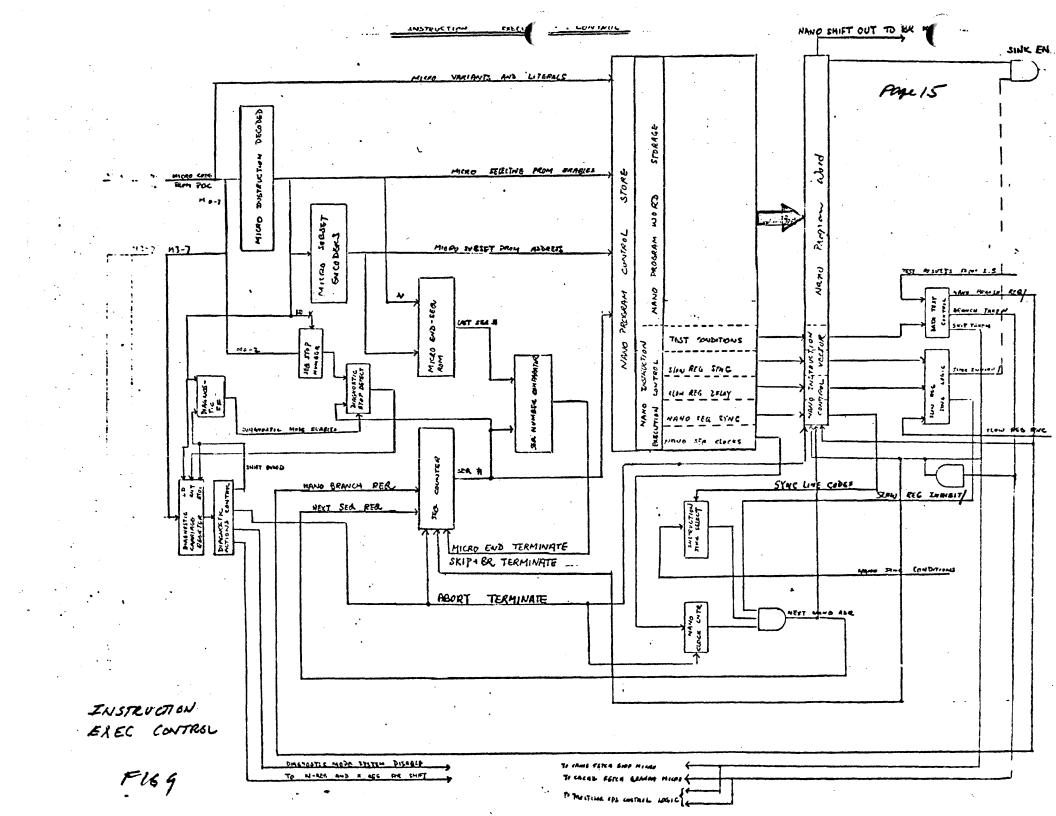

| 3.8.1 INSTRUCTION EXECUTION LOGIC (IEC)                      | PAGE 95   |

| 3.8.2 PROCESSOR OPERATIONAL CONTROLS                         | PAGE 95   |

| 3.8.2 Cont <sup>4</sup> d                                    | PAGE 97   |

| 3.9 PROCESSOR OPERATION CONTROL.                             |           |

|                                                              | PAGE 97   |

|                                                              | PAGE 97   |

| 3.9.2 CONSOLE SWITCH STATES ENCODER                          | PAGE 98   |

| 3.9.3 OPERATING HODE INTERLOCK                               | PAGE 100  |

| 3.9.4 PROCESSOR OPERATION CONTROL ROM (POCR)                 | PAGE 100  |

| 3.9.5 OPERATING PHASE COUNTER AND QUIESCENT PHASE DETECTOR . | PAGE 101  |

| 3.9.6 POC DECODE INHIBIT                                     | PAGE 101  |

| 3.9.0 INSTRUCTION EXECUTION CONTROL.                         | PAGE 101  |

| 3.10.1.0 MICRO TO NANO DECODE                                | PAGE 104  |

| 3-10-1-1-0 NANO PROGRAM CONTROL STORE (NPCS)                 | PAGE 104  |

|                                                              | 1 MUC 104 |

|                                                              |           |

× .

| .3.10-1-1-1 | NANO P   | PROGRAM WORD .  |         | •         |             | PAGE 104 |

|-------------|----------|-----------------|---------|-----------|-------------|----------|

| 3.10.1.1.2  | NANO E   | EXECUTION CONTR | ₹0L     |           |             | PAGE 105 |

|             |          | ATING ADDRESSES |         |           |             | PAGE 105 |

| 3.10-1-1-4  | SEQUEN   | NCE NUMBER CONT | FROLS.  |           | • • • • • • | PAGE 106 |

|             |          | ECUTION CONTROL |         |           |             | PAGE 106 |

|             |          | ATE CONTROLLER  |         |           |             | PAGE 106 |

|             |          | DURING NORMAL   |         |           |             | PAGE 107 |

|             |          | N TIMING        |         |           |             | PAGE 112 |

| 4.1 M-Ins   | truction | Performance.    | • • • • | • • • • • | • • • • • • | PAGE 115 |

. . .

•

•

#### COMPANY CONFIDENTIAL N=PROCESSOR=3 E.D.S. #2215 9891

# 1.0 INTRODUCTION

This EDS defines the functional characteristics of the B1820 M-Processor-3, hereinafter called "MP-3."

#### 1.1 PURPOSE

This EDS is prepared by Systems Engineering as a vehicle for inter-designer communication and project control. Its irtended audience is Systems Engineering, Diagnostics, and Software. It serves as input to the Product Spec which is exposed to other activities.

#### 1.2 EDS PHILOSOPHY

The present state of this document represents the hardware design as conceived implementing the inferred product specification. It will be periodically updated and once the design has been completed, signified by the engineering release to manufacturing, this cocument will reflect that machine and will not change.

### 1.3 PRODUCT IDENTIFICATION

| 2212 8631 | M-PROCESSOR-3                                |  |

|-----------|----------------------------------------------|--|

| 2212 8623 | CABINET-5 (control panel is part of cabinet) |  |

1.4 RELATED SPECIFICATIONS, DOCUMENTS, AND DRAWINGS

| P.S. #    | NAME       |                |

|-----------|------------|----------------|

|           |            |                |

| 1904 5681 | B1700/1800 | SYSTEM INDEX   |

| 1913 1739 | B1700/1800 | CENTRAL SYSTEM |

| 2212 9001 | MP-3       |                |

| 2212 9019 | CP-4       |                |

## COMPANY CONFIDENTIAL M-PROCESSOR-3 E.D.S. #2215 9891

| S.D.S. #  | NAME         |

|-----------|--------------|

|           |              |

| 2216 0683 | I/O Base=3   |

| 2216 0691 | 81820 System |

| S.P.S. #  | NAME  |

|-----------|-------|

|           |       |

| 2215 1962 | MP-2  |

| 2216 2762 | MBU-3 |

| E.D.S. | #   | NAME          | •             |

|--------|-----|---------------|---------------|

|        | -   |               |               |

| 2215 7 |     |               | Storage Board |

| 2215 8 | 513 | B1820 Clock S | ystem         |

| DOCUMENT | NAME      |

|----------|-----------|

|          |           |

| tbs      | <u>``</u> |

| DRAWING | NAME |

|---------|------|

|         |      |

| tbs     |      |

NOTE: A-SIZE REDUCTIONS OF "\*"-ED CRAWINGS ---- ARE INCLUDED IN THIS EDS.

COMPANY CONFIDENTIAL N=PROCESSOR=3 E.D.S. #2215 9891

# 2.0 GENERAL DESCRIPTION

MP-3 provides the combinatorial and arithmetic portion of the system along with other registers and hard storage that are appropriate for efficient operation.

MP-3 provides hardware sensitivity to a set of low-level micro-functions which are used in a program string to fetch and execute instructions. This micro-program is contained in a local high-speed cache memory, backed up by a somewhat slower but larger main memory (B1800 S-memory) or in both. Cache is an integral 4K byte memory.

Included in MP-3 are registers and pseudo registers which are addressable by the individual micro-operators.

The registers are normally addressed by a 4-bit group (row) number and a 2-bit select (column) number as shown in Table 1.

Some of the registers listed, such as the Pseudo Sum Register, can serve only as source registers while others are capable of serving both as source and destination registers. Also, some of the registers listed are actually subregisters which, although parts of larger registers, can be individually addressed and manipulated.

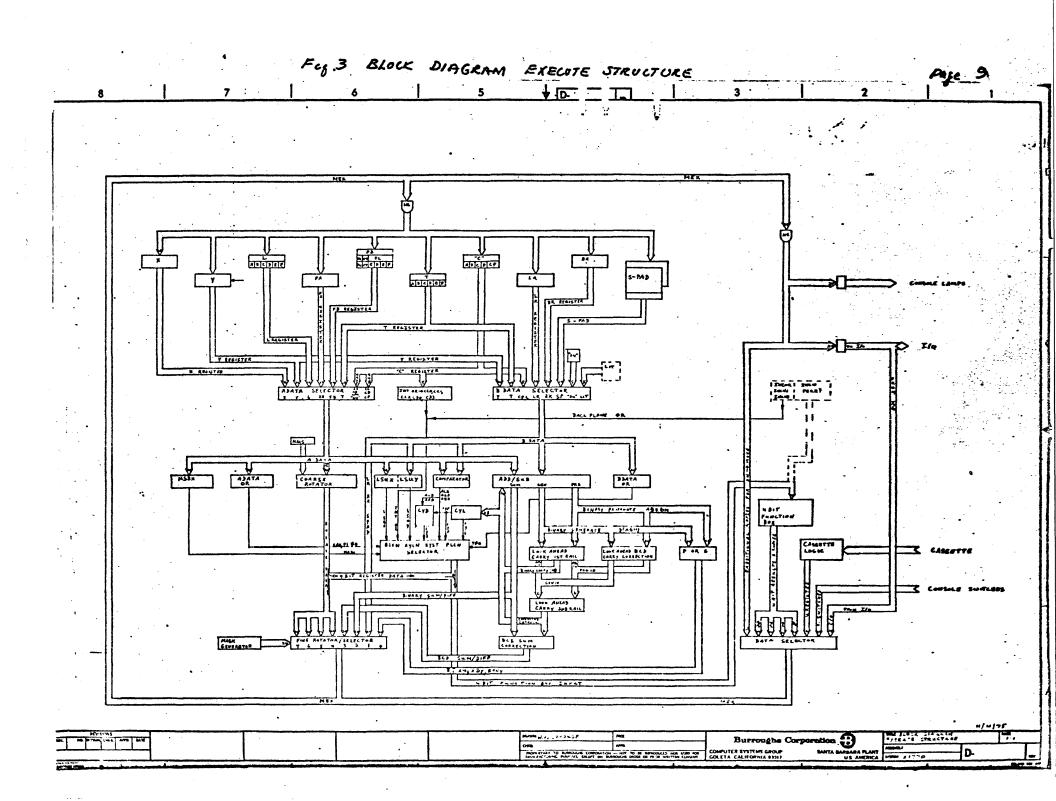

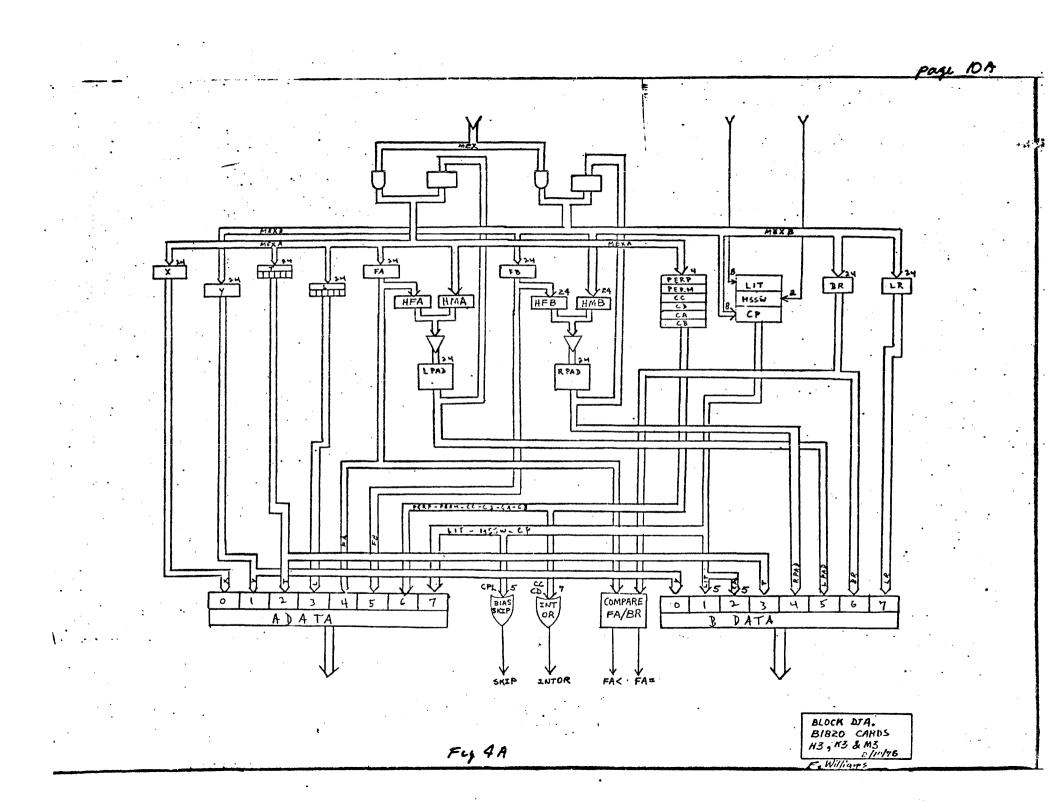

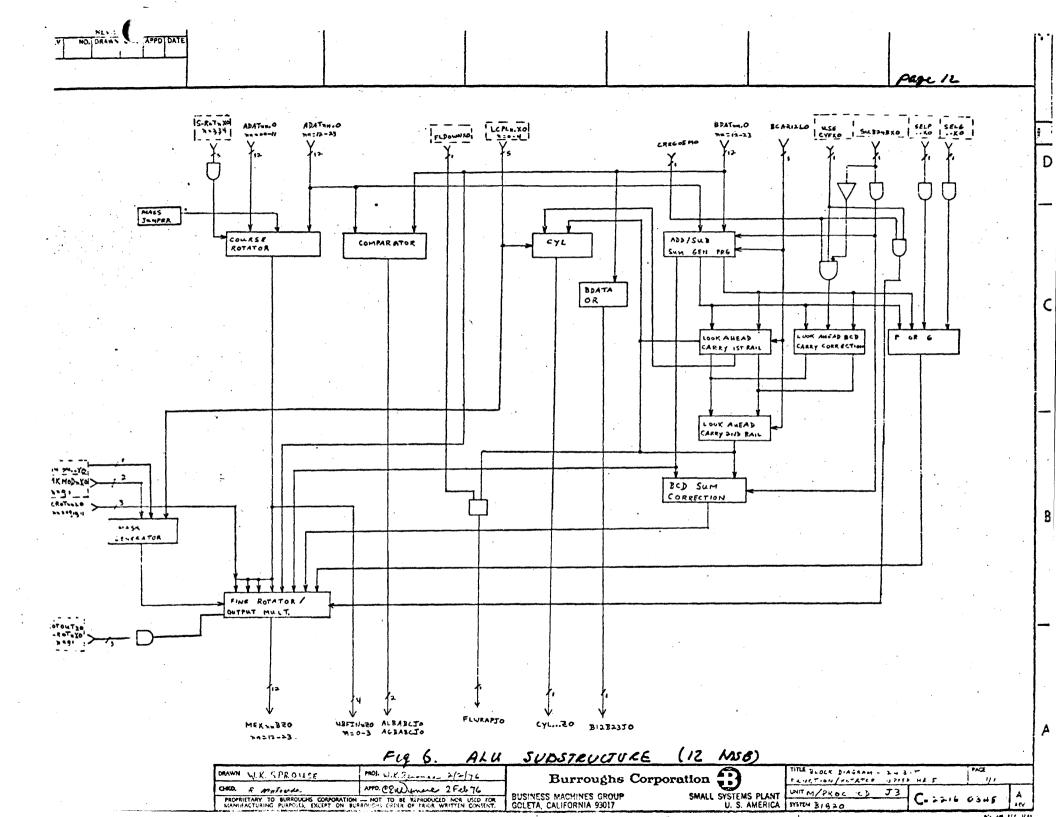

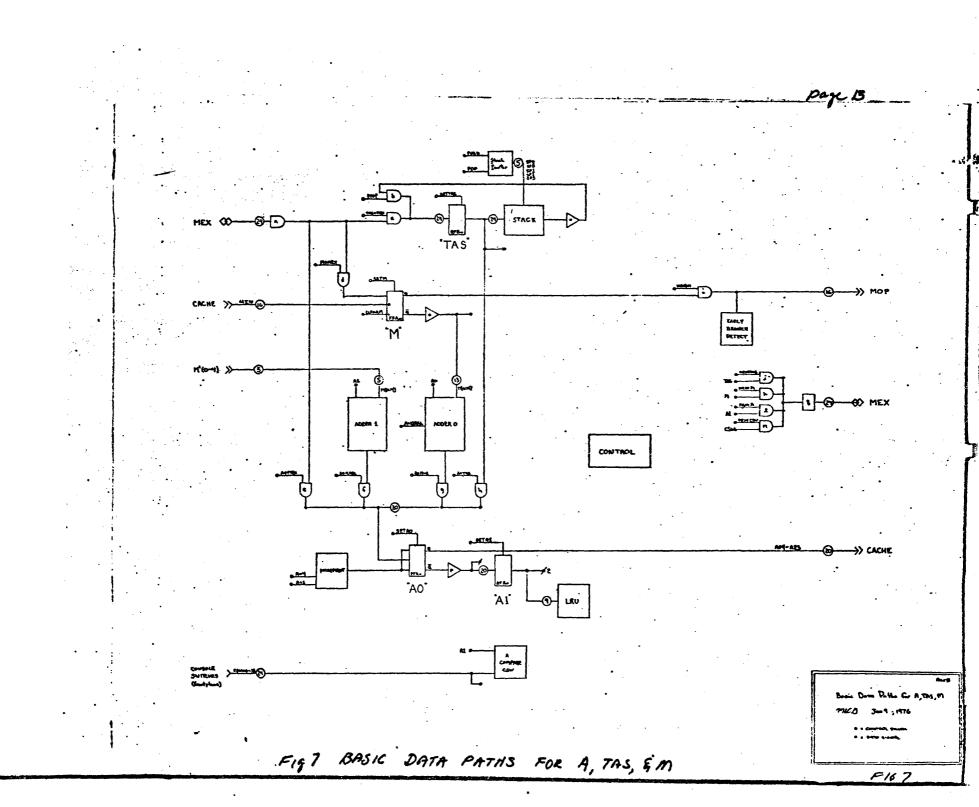

Table 2 summarizes the various conditions available by addressing particular pseudo source registers and actual registers; Figures 1 and 2 list the micro-instructions and their variants; and Figures 3-9 are diagrams of the major portions of MP-3.

·

.

# BURROUGHS CORPORATION Computer systems group Santa barbara plant

.

COMPANY CONFIDENTIAL M-PROCESSOR-3 E.D.S. #2215 9891

|         |        |          |     | SELECT NUMBER |              |       |

|---------|--------|----------|-----|---------------|--------------|-------|

|         |        | <u>.</u> | 0   | 1             | 2            | 3     |

|         | 0      | 1        | TA  | FU            | X            | SUM   |

|         | 1      | 1        | TB  | FT            | м <b>ү</b> с | CMPX  |

|         | 2      | 1 -      | TC  | FLC           | T            | CMPY  |

|         | 2<br>3 | 1        | TD  | FLD           | L            | XANY  |

|         | •      | . 1      |     |               |              |       |

|         | 4      | 1        | TE  | FLE           | ٨            | XEOY  |

|         | 5      | 1        | TF  | FLF           | M            | MSKX  |

|         | 6      | 1        | CA  | BICN          | BR           | MSKY  |

| ан<br>1 | 7      | ł        | СB  | FLCN          | LR           | XORY  |

|         |        | 1        |     |               |              |       |

| GROUP   | 8      | 1        | LA  | NULLA         | FA           | DIFF  |

| NUNBER  | 9      | 1        | LB  | RESERVED      | FB -         | MAXS  |

|         | 10     | 1        | LC  | PERM          | FL           | NULLC |

|         | 11     | 1        | LD  | PERP          | TAS          | U     |

|         |        | 1        |     | · · · ·       |              |       |

|         | 12     | 1        | LE  | XYCN          | CP           | NULLD |

|         | 13     | 1        | LF  | XYST          | NULLB        | DATA  |

|         | 14     | 1        | 0.0 | INCN          | CSW          | CMND  |

|         | 15     | . 1      | CD  | MSSW          | TIME         | NULL  |

| •       |        |          |     |               |              |       |

| TABLE 1 | N-PROCESSCR | REGISTER | SELECTION |

|---------|-------------|----------|-----------|

|         |             | *******  |           |

COMPANY CONFIDENTIAL M-PROCESSOR-3 E.D.S. #2215 9891

|          | 3 2 1 0: LSB                                                                                                                                         |             |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| BICN:    | I LSUY I CYF I CYD I CYL I                                                                                                                           |             |

|          | 3 2 1 0°LSB                                                                                                                                          |             |

| XYCN:    | 1 MSBX 1 X=Y 1 X <y 1="" x="">Y 1</y>                                                                                                                |             |

| •        | 3 2 1 0:LSB                                                                                                                                          |             |

| XYST:    | I LSUX I INT I Y neq 0 I X neq 0 I                                                                                                                   |             |

|          | 3 2 1 O:LSB                                                                                                                                          |             |

| FLCN:    | I FL=SFL 1 FL>SFL 1 FL <sfl 0="" 1="" fl="" i<="" neq="" td=""><td></td></sfl>                                                                       |             |

|          | 3 2 1 0°LSB                                                                                                                                          |             |

| INCN:    | I PORT I PORT I PORT I PCRT I<br>I DEVICE MISSING I HI PRIORITY I INTERRUPT I LOCKOUT I                                                              |             |

|          | 3 2 1 0:LSB                                                                                                                                          |             |

| 1        | ONTROL PANEL   100 MSECI I/O BUSI CONTROL PNL ISTATE LAMPI REAL TIME CLOCK I SERVICEI INTERRUPTFLIP-FLOPI INTERRUPTI REQUESTIIII INTERRUPTI          |             |

|          | 3 2 1 0:                                                                                                                                             | LSB         |

| CD: 1 R  | EMORY I MEMORY I MEMORY I MEMORY<br>EAD DATA 1 WRITE/SWAP ADDR I READ ADDR I WRITE/SWAP ADDR<br>RROR I (LR/8R CHECK) I (LR/8R CHECK) I (LR/8R CHECK) | 1<br>1<br>1 |

| t I<br>t | NTERRUPT 1 OUT OF BOUNDS 1 OUT OF BNDS 1 OUT CF BOUNCS<br>1 OVERRIDE 1 INTERRUPT 1 INTERRUPT                                                         | 1           |

| · . *    |                                                                                                                                                      |             |

|        | BURROUGHS CORPORATION<br>Computer systems group<br>Santa barbara plant                                                | COMPANY CONFIDENTIAL<br>N-PROCESSOR-3<br>E.D.S. #2215 9891        |                                    |  |  |  |  |  |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------|--|--|--|--|--|--|--|

|        | 3 2                                                                                                                   | 1                                                                 | 0:LSB                              |  |  |  |  |  |  |  |

| MSSW:. | I NULL I NULL I FROM C<br>I BIT I BIT I FROZEN                                                                        | SOURCE ISO: MICRO<br>ACHE OR I FROM<br>IN I OR FR<br>STER I M-REG | S-MEMORY 1<br>Ozen in 1            |  |  |  |  |  |  |  |

|        | 3                                                                                                                     | 2                                                                 | 1 0:LSB                            |  |  |  |  |  |  |  |

| PERMS  | I S-MEMORY 'I S-MEMORY<br>I MICRO- I FIELD CUT-<br>I INSTRUCTION I BOUNDS IN<br>I TIME-OUT I ADMINISTRA<br>I I MEMORY | THE I ERROR LOG                                                   |                                    |  |  |  |  |  |  |  |

|        | 3                                                                                                                     | 2                                                                 | 1 0°LSB                            |  |  |  |  |  |  |  |

| PERP:  | I CACHE KEY<br>I CACHE I PARITY ERRO<br>I DOUBLE HIT I ON KEY A<br>I OR KEY B                                         |                                                                   | I READ ERRCR I<br>I WHICH CANNET I |  |  |  |  |  |  |  |

PAGE

6

TABLE 2 (cont)

SUMMARY OF REGISTER CONDITIONS

E.O.S. 2216 9191

Page 7

|           | 8                                             | 1        | •<br>• • | •        | 7          |                       | ľ       |        | 6               |                    |              |                    |                                       | 5          | ;              |          | + 0-                                 |                                         |                | =        |            | 3          | •           |       | 1          |               | 2                                 | 1                                 |                                  | 1                                             |

|-----------|-----------------------------------------------|----------|----------|----------|------------|-----------------------|---------|--------|-----------------|--------------------|--------------|--------------------|---------------------------------------|------------|----------------|----------|--------------------------------------|-----------------------------------------|----------------|----------|------------|------------|-------------|-------|------------|---------------|-----------------------------------|-----------------------------------|----------------------------------|-----------------------------------------------|

|           |                                               | 1        | M        | c        |            | 1 . N                 | 1D      | .      |                 | ME                 |              |                    | .                                     | M          |                | 1        |                                      |                                         | . 1            |          |            |            | •           |       |            | •             |                                   |                                   |                                  |                                               |

|           | MICRO NAME                                    | 15       | 14       |          | 12         | 11 10<br>REGISTER     |         | 8      | 7<br>REG.       |                    | 5            | 4                  | 3                                     | 2          | GROUP          | •        | VARIANTS:                            |                                         |                |          |            | 100        |             |       |            | l             |                                   |                                   |                                  |                                               |

| 11        | RESISTER HOVE                                 | °        | 0        | •        | <u>1</u> . | SOURCE F              | EGISTE  | R      | SELEC           | T                  | SELEC        | <u>م</u>           | SIN!                                  | K REG      | WORD           |          | Heve Dr                              | P←R                                     | R-P            |          |            |            |             |       |            | •             |                                   | BOISTER D                         | RECT                             |                                               |

| 22        | MOVE                                          | l °      | 0        | 1        |            | SOURCE O              | R SINK  | ·      | SELE            | CT T<br>MANI       | DIR.         | 1/2                | ADI                                   | DRESS      | INIPULATE      |          | 1/2 DPW :<br>MENIP                   | LEFT                                    | RIGHT          |          | · · · · ·  | ļ          |             |       | THE        | ABL:37<br>680 | up [                              | <u>-</u>                          | <u> </u>                         | SUM  <br>CMPX                                 |

| 30        | 4 BIT                                         | •        | 0        | 1        | 1          | 4 BIT SOURI           | ELS     | INK    | SEL.<br>REG     |                    | ANTS         | DSP                | L                                     | ITERP      | <u></u>        | _        | VARIANTS:                            | S€T<br>+                                | AND -          | OR .     | EOR        | INC        | INC<br>TEST | DEC   | TEST       |               | 10100 FA                          | FT<br>FLC<br>FLD                  | L<br>L                           | CHPX<br>CHPY<br>XAXY                          |

| 40        | BIT TEST REL.<br>BRANCH FALSE<br>BIT TEST REL | •        | 1        | 0        | •          | 4 BIT SC<br>REGISTER  | URCE    | ·      | SEL.            | NUMB               | ER           | DSP<br>SIGN<br>DSP | DISPLA                                |            | r MAG          | _ļ       | DSP SIGN                             | +                                       | -              |          | ļ          | ļ          |             | ·     |            |               | ; II:                             | FLE                               | A ·                              | TEON                                          |

| 57        | BRANCH TRUE                                   | 0        | 1        | <u> </u> |            | A BIT SO              | URCS    |        | SEL.            | NUMBE              | R            | SIGN               | DISPLA                                | LEMEN      | T MAG.         | -        | SKIP TEST                            | ANY                                     |                | EQI      |            | a.v.       |             |       |            |               |                                   | FLCN                              | A<br>BR<br>LR                    | MSKY<br>MSKY<br>IORY                          |

| <u>кс</u> | SKIP WHEN                                     | •        | 1        | 1        | 0.         | 4 BIT SOUR            | CE & SI | INK    | SEL.            | VAR                | TIANTS       |                    | 1                                     |            | MASK           | $\dashv$ | VARIANTS:<br>R/W YARIANTS            | CLR/                                    | CLR/           | cury     | ALL        | 202/       | 224         | en y  |            | 1             | 8 LA<br>9 L8<br>0 LC              | NULL-A<br>RESV<br>PERM            | FA<br>FB<br>FL<br>TAS            | DIFF<br>HALS<br>NULL-C                        |

| 10        | READ/WRITE<br>MENICRY                         | 0        | 1        | 1        | 1          | VAR. VAR              | I HAVEN | -      | DATA<br>COD     | <b>G</b> 31        | GN           | WIDT               | TA TRA                                | NITU DE    |                |          | COUNT VARIAND                        | HOP                                     | FAT            | FLT      | FAT<br>FL+ | FAL        | FAL         | RL    | FAL<br>FL  | i<br>• 1      | 1 10                              | . PERP                            |                                  | WULL-D                                        |

| 3C        | MOVE 8 BIT                                    | 1        | 0        | 0        | 0          | REGISTER<br>REG. SEL. | IS Z    |        |                 | E 8 BIT            |              |                    |                                       | ERAL       |                |          | REG DELECT:                          | ÷                                       | ř_             | <u> </u> | L          |            |             |       |            | 1             |                                   | XYST<br>INCN<br>MSSW              | CP<br>NULL-S<br>CSW              | DATA<br>CMND<br>NULL                          |

| yr.       | MOVE 24 BIT<br>LITERAL                        | 1        | 0        | 0        | 1          | REGISTER<br>REG. SEL. | IS 2    |        | FULL            | ST SIGNI<br>24-BI  | <u>r u</u> r | ERAL               |                                       |            |                | _        |                                      |                                         |                |          | ļ          |            |             |       |            | NOTE:         |                                   |                                   | CARDING TO T                     | HE HARD WARE                                  |

| 100       | SHIFT/ROTATE                                  | 1        | 0        | 1        | 0          | SINK REG              |         |        | SINK            | T                  | /R<br>/RR    |                    | SHIFT,                                |            |                | _        | S/R VARIANTE                         | SHIFT                                   | POTATE         |          |            |            |             |       |            |               | TENDONS:                          | - 102 10                          |                                  |                                               |

| 110       | EXTRACT FROM<br>T REGISTER                    | 1        | •        | 1        | 1          | RIGHT BIT<br>EXTRACT  |         |        |                 | SINK RE            | <b>K</b>     | EXTRA              | ACTION 1                              | FIELD      | WIDTH          |          | SINK REG                             | ×                                       | Y              | т        | L          |            |             |       |            |               | 14 14                             | 10                                | D LE                             | LF .                                          |

| 120       | BRANCH REL<br>RORNARD                         | 1        | 1        | 0        | 0          | REI                   | ATINE   | DISPL  | ACEMEN          | T MA               | GNITU        | DE                 |                                       |            |                | _        |                                      | ·                                       |                |          |            |            |             |       |            |               | 414<br>23                         |                                   |                                  | 13-0<br>13-0<br>00                            |

| 13C       | BRANCH KEL.<br>REVENSE                        | 1        | 1        | o        | 1          | .REL                  | ATIVE   | DISPLA | CEMENT          | MAG                | NITUD        | e<br>              |                                       |            |                |          |                                      |                                         |                |          |            |            |             |       |            | THEOR         | //101041 BUT                      | C AC SAME                         | 4-DIT 0001                       | STERS HAVE                                    |

| 140       | GALL REJATIVE                                 | 1        | 1        | 1.       | ٥          | RELAT                 | NE CA   | LL AD  | DRESS           | MAGNIT             | UDE          |                    | •                                     |            |                | _        | ·.                                   |                                         |                |          |            |            |             |       | ·          |               |                                   | 5 45 NOT                          |                                  |                                               |

| 15C       | CALL RELATIVE<br>REVERSE                      | 1        | 1        | . 1      | 1          | RELATI                | VE CA   | LL AD  | DRESS           | MAGNI              | TUDE         |                    |                                       |            |                | -        | ļ                                    |                                         |                |          |            |            |             |       |            | <b>BICN</b>   | LSUT                              | CYF                               | CYD                              | CTL                                           |

| 10        | l                                             | L        |          |          |            | · .                   | · .     | · · ·  |                 |                    |              |                    | <u> </u>                              |            |                |          | TH BIGH!                             | <u>.</u>                                | • ·            |          |            |            |             |       |            | . MYCN        | MSBX                              | X=Y                               | X <y< td=""><td>x&gt;Y</td></y<> | x>Y                                           |

| ZD        | SUAP MEMORY                                   | 0        | ٥        | ه        | ٥          | 0 0                   | 1       | 0      | DATA<br>COD     | REG T              | GN           |                    | MAGNIT                                | UDE        | WIDTH          |          | TH BIGN!<br>RUG CODE:                | ×                                       | Y              | т        | L          |            |             |       | •          | XIST          | LSUX                              | INT                               | Y NEQ                            | O X NEQ O                                     |

| 3D        | REGISTER                                      | •        | 0        | 0        | o          | 0 · 0 ·               | 1       | 1      |                 |                    |              | REG                | FA<br>REG                             | FL<br>REG  | FU C<br>REG RI |          |                                      |                                         |                |          |            |            |             |       |            | FLCN          | FL = SFL                          | FL>SF                             | L FL (SF                         | L FL NEQ C                                    |

| 4D        | SHIFT/ROTATE                                  | 0        | ٥        | ٥        | •          | 0. 1                  | •       | •      | S/R DI<br>VARIA | RECTION X          | V/Y<br>IAR   |                    | T RIGHT                               |            |                | _        | X/Y VAR:<br>S/R VAR:                 | X<br>JFT-                               | Y<br>3FT→      | ROT      | ROT-+      |            |             |       |            | ZNCN          | PORT DEVI                         | E PORT N<br>PRIORIT               |                                  | PORT LOCKOUT                                  |

| SD        | SHIFT / ROTATE                                | •        | 0        | 0        | o          | 0 1                   | •       | 1      | SYR DIR<br>VARI |                    | LEF          | T OR               | RIGHT                                 | E COL      | AND Y          | _        | SVA DIR<br>VAR:                      | SFT 🔶                                   | SFT→           | ROT +    | R0T →      |            |             |       |            |               | MISSING                           |                                   |                                  |                                               |

| 10        | COUNT FA/FL                                   | 0        | ٥        | ٥        | ٥          | • 1                   | 1       | •      |                 | IT FA/F<br>ARIANTS | °L           |                    | MAGNIT                                |            | R              |          | COUNT PAPE VAR:                      | NØP                                     | FAt            | FLL      | FAT<br>FL+ | FAL<br>FLT | FAL         | PL4   | FAL<br>FLI | 33            | CONTROL P<br>STATE LAN<br>RUP-FLO | H REAL TIM<br>P CLCCK<br>LATERAUP | SERV. RAL                        | THITLES JOT                                   |

| 10        | EXCHANGE DPP                                  | ٥        | 0        | 0        | 0          | 0 1                   | 1       | 1      |                 | ADDRESS            |              |                    | sou<br>V                              | RCE DDRE   | DPW<br>SS      | Ī        | •                                    |                                         |                | · ,      |            |            |             |       |            |               | HEM REA                           | MELTE/ST                          | AP READ A:                       | DR PRITE/SWAP                                 |

| 10        | I SCRATINPAD<br>RELATE FA                     | •        | ٥        | 0        | 0          | 1 0                   | ٥       | 0      | $\square$       | $\wedge$           |              | IGN                |                                       | HALF       |                |          | DSP SIGN:                            | +                                       | <b>-</b> '     |          |            |            |             |       |            | 9             | ERROR<br>DITERRUP                 | UNT OF BL                         | K) (LR/BR C<br>3 OUT OF B        | HK) (LR/BR CHK)<br>DS OUT OF BDS<br>INTERRUPT |

| 10        | MONITOR                                       | 0        | 0        | 0        | 0          | 1 0                   | 0       | 1      |                 | ERAL               |              |                    |                                       |            |                | -        |                                      |                                         |                |          |            |            |             |       |            |               | C#6.46                            | Correct M                         | - DARITY EA                      | ALL CASSETTE                                  |

| 10D       | NANO MOVE                                     | 0        | •        | 0        | 0          | 1 0                   | 1.      | 0      | C/A<br>VAR      | SEQ I              | OPPIN<br>ENC | É ~                | WARDER                                | WOR        | 0 - REG        | 4        | WA VAC:<br>SED WUNDER<br>WORD PARTIN | CONTIN.                                 | A04027         | 2/10     | 3/11       | 4/12       | 5/13        | 6/19  | 7/15       | PERP          | DOUGLE HI                         | DARITY ER                         | MICRO MICRO                      | TER CORRECTABLE                               |

| 11D       | DIAG READ/WRITE                               | 0        | 0.       | 0        | 0          | 1 0                   | 1       | 1      | DATA            |                    | W            |                    | M/E<br>VAR                            | R/W<br>VAR | E CHO<br>VA R. | 1        | DATA REG:                            | X                                       | Y              | T        | L          | <u></u>    | •           |       |            |               | 3-MEMOR                           | S-MEM FA                          | 128 S-ME-10A                     | W UNCOMPLETING                                |

| , 12D     | ·                                             | †        |          |          |            |                       |         |        |                 |                    |              |                    | ·                                     |            |                |          | WE WAR<br>ECHO WAR<br>FW SIGN :      | RES                                     | R CHO<br>WRITE | A Det    | e un cue   |            |             |       |            | PERM          | TIME-OUT                          | CUT CF                            | The LOUGED                       | G. J-HEMBAY<br>EAROR W<br>MOC OPS             |

| 130       |                                               | <u> </u> |          |          |            |                       |         |        |                 |                    |              |                    |                                       |            |                | -+       | 100 5100.                            |                                         |                |          |            |            |             |       |            |               |                                   | 1                                 | 31 10-04                         | 30 miras                                      |

| 14D       |                                               |          |          |          |            |                       |         |        |                 |                    | •            |                    |                                       |            |                | -        |                                      |                                         |                | :        |            |            |             |       |            | 1855w         | AULL                              | Nuu<br>A.T                        | Source P<br>CACHE D<br>FROLEN    | 4 3- AND 1 04                                 |

| 15D       |                                               |          |          |          |            | <u> </u>              |         |        |                 |                    |              |                    | · · · · · · · · · · · · · · · · · · · |            |                |          |                                      |                                         |                |          |            |            |             |       |            | D4 =          | ANY CHE                           | R MORE O                          | F : CCD . CC1                    |                                               |

|           | <u> </u>                                      | •        |          |          |            | ±                     |         |        |                 |                    |              |                    |                                       |            |                |          | • •                                  | • · · · · · · · · · · · · · · · · · · · |                |          | ·          |            |             | ·     |            | -             | CD3, INCN 1                       | , INCN 3.                         | -                                |                                               |

|           |                                               |          |          |          |            |                       |         | •      |                 |                    |              |                    |                                       |            |                | ·        | •                                    |                                         |                |          |            |            |             |       |            |               |                                   |                                   |                                  |                                               |

|           | A(1.5.14)                                     | 1        |          |          |            |                       |         |        |                 |                    |              |                    |                                       |            |                |          | A TATANAN Y                          |                                         |                |          |            | B          |             |       | poration   | • 3           |                                   | - PRCLES                          |                                  |                                               |

| 2~~       |                                               | 1        |          |          |            |                       |         |        |                 |                    |              |                    |                                       |            |                | 1        |                                      |                                         |                |          |            | GOLETA CA  |             | 101.2 | SANT       | US AN         |                                   | 8.420                             | D. 2                             | 216-0321 3                                    |

| <b></b> ' ·     |                       | 1            |             | · .      | <b>_</b> : · |          | 1              | •      |                | ·        |         |          | 1        |               |          |          | •      | •                             |          |                     | F I        |              | - 0.7    |           |          | 1          | 9891                          |                                         | PN                     | <u> </u> |    |

|-----------------|-----------------------|--------------|-------------|----------|--------------|----------|----------------|--------|----------------|----------|---------|----------|----------|---------------|----------|----------|--------|-------------------------------|----------|---------------------|------------|--------------|----------|-----------|----------|------------|-------------------------------|-----------------------------------------|------------------------|----------|----|

|                 | 8                     |              |             |          | 7            |          |                |        |                | 6        |         |          | <u> </u> |               | 5        | -        |        | ¥ D-                          |          |                     | <u>-  </u> |              | . 3      | · · ·     |          | 1          | 2                             |                                         |                        | · 1      | j  |

|                 | MICRO NAME            | 5            | MC<br>I H I |          | 12           | 11       | 1M<br>10       | )<br>9 | 8              | 7        | ME<br>6 | 5        | 4        | а             | MF<br>2  | -<br>1   | •      | WARIANTS :                    |          |                     | 19         |              |          |           |          |            |                               |                                         |                        |          |    |

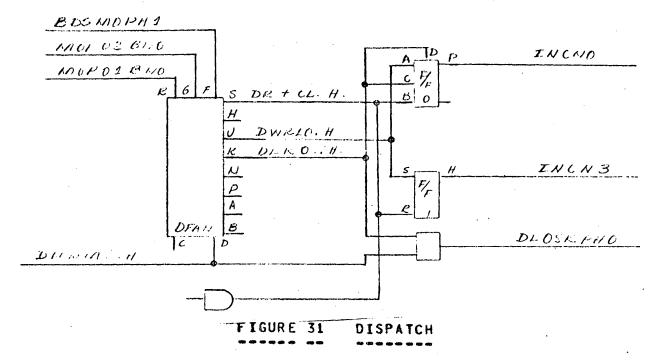

| 15              | DISPATCH              | 0            | 0           | 0        | 0            | 0        | 0              | 0      | 0              | 0        | 0       | 0        | 1        | DISP          | ATCH     |          | SKIP   | SKIP FLAG:                    | FAIL     | SUCC                | T          |              | 100      |           |          | 9 11       | NOTE:                         |                                         |                        |          |    |

| 2.E             | CASSETTE              | 0            | 0           | 0        | 0            | 0        | 0              | 0      | 0              | 0        | ò       | 1        | 0        | CASS          | ETTE     |          | HACE O | DISP VAR :<br>CASSETTE        |          |                     | STOP ON    |              | UNDEF    |           | STOP OF  | STOP O     | FOLLOWS:                      |                                         | REGISTER               | has men  | 14 |

|                 | CONTROL               | 0            |             | <br>0    | 0            | 0        |                | .0     | 0              | 0        | 0       |          | 1        | MANIP         | IAS      |          | TEST   | TEST FLAG :                   | TEST/    | TEST                | 1          | 1            | 1        | <u> </u>  | 1        | F3=B       | M PU MU S                     |                                         | ARD ROW                | STN      | -9 |

| 3E              | BIAS<br>STORE F WTO   |              |             |          |              |          | 0              |        |                |          |         |          |          |               | IANTS    |          | FLAG   | BIAS VAR :                    | UNIT     | F                   | <u>s</u>   | FS           | NO-OP    | FCP       | NO-OP    | NO-OP      | -                             |                                         |                        |          | -  |

| 4E              | DPW<br>LOAD F FROM    | 0            |             | <u> </u> | 0            | 0        | _ <b>i</b>     |        | 0              | •        | 1       | <u> </u> |          |               | DDRES    |          |        |                               | <u> </u> |                     |            |              |          |           |          |            | PU: UNCORREL<br>AV.: UNCORREL |                                         | ROR ON CP<br>R ON NON- |          |    |

| SE              | DPW<br>CARRY FF       | 0            |             | 0        | 0            | <u> </u> | 0              | 0      | 0              | 0        | 1       | •        |          |               | NOD RE!  | . 22     | CYE    |                               |          |                     |            |              |          |           |          |            | 1                             |                                         | RRECTED N D            |          |    |

| 6E              | MANIPULATE READ/WRITE | 0            | 0           | 0        | 0            | . 0      | <u>i</u> 0     | 0      | 0              | •        | 1       | 1        | 0        | CTD<br>BD PET |          | CYF<br>1 |        | Dran Lunger                   |          |                     |            | ļ            |          | DIAC      | 0100     | READ       | -                             |                                         | E LOADED AN            |          |    |

| ٦<br>٦          | CACHE                 | 0            | •           | 0        | •            | •        | <u>`</u>       | •      | 0              | 0        | 1       | 1        | 1        | SO PRIM       | VARI     | ANTS     | · .    | READ/WRITE<br>VAR:<br>PARITY: | RESV.    | RESV.<br>BAD        | RESV.      | RESV.        | RESV.    | DIAG      | MICEO    | READ       | W. 00-04                      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                        |          |    |

| 85              |                       |              |             |          |              |          |                |        |                |          |         |          |          |               |          |          |        |                               | <u> </u> |                     |            | ·            |          |           | ļ        | ļ          | ·] .                          |                                         |                        |          |    |

| ĴE              |                       | 1            |             |          |              |          | <u> </u>       |        |                | •        |         |          |          |               |          |          |        | ļ                             |          |                     | ļ          | ļ            |          |           | ļ        |            | 4                             |                                         |                        |          |    |

| 10 <del>5</del> |                       | 1            |             |          |              |          | •              |        |                |          |         |          |          | ļ             |          |          |        |                               |          |                     | ļ          | ļ            | ļ        |           | <u> </u> |            | 4                             |                                         |                        | •        |    |

| 11E             | · .                   | ŀ            |             |          | ·            |          | +              |        |                |          | •       | •        |          |               |          |          |        |                               |          | <br>                | ļ          |              |          |           |          |            |                               |                                         |                        |          |    |

| <u>I</u> ZE     |                       |              |             |          |              |          | i              |        |                |          |         |          |          |               |          |          |        |                               |          |                     |            |              |          |           |          | •          |                               | <b>v</b> .                              |                        |          |    |

| BŁ              |                       |              |             | •        | •            |          | *<br>•         |        |                |          |         |          |          |               |          |          |        |                               |          |                     |            |              |          |           |          |            | 1.                            |                                         |                        |          |    |

| ME              |                       | 1            |             |          |              |          | • .            | -      |                |          |         |          |          |               |          |          |        |                               |          |                     |            |              | 1        |           | 1.       |            | 1                             |                                         |                        | •        |    |

| 15E             |                       | 1            |             |          |              |          | ł              | •      |                |          |         |          |          |               |          |          |        |                               |          |                     | 1          |              |          |           | 1        | 1          |                               |                                         |                        |          |    |

| 1F              | HALT                  | 0            | 0           | 0        | 0.           | 0        | 0              | 0      | 0              | 0        | 0       | 0        | 0        | ò             | 0        | 0        | 1      | 1 .                           |          |                     | 1          | 1 .          |          | 1         | 1        | 1          | 1.                            |                                         |                        |          |    |

| 25              |                       | <del>†</del> |             |          |              |          | 1              |        |                |          |         |          |          |               |          |          |        |                               |          |                     |            |              | <u> </u> |           | 1        | <u> </u> . | 1 · ·                         |                                         |                        |          |    |

| зF              | NORMALIZE X           | 0            | 0           | 0        | 0            | 0        | ;0 .           | 0      | o <sup>:</sup> | 0        | 0       | 0        | 0        | 0             | <b>i</b> | 1        | 1      | ·                             |          |                     |            | 1            |          |           | 1        | <u>†.</u>  |                               |                                         | •                      |          |    |

| 4F              | BIND                  | 0            | 0           | 0        | o            | 0        | 0              | 0      | 0              | 0        | 0       | 0        | 0        | 0             | 1        | •        | 0      |                               |          |                     | <u> </u>   |              | <u> </u> | <u> </u>  | <u> </u> |            | -                             |                                         |                        |          |    |

| SF              | LLEAR                 | 0            | 0           | 0        | 0            | 0        | .0             |        | 0              | 0        | 0       | 0        | 0        |               | -<br>1   |          | 1      |                               |          |                     |            |              | †        |           |          | 1          | 4 -                           |                                         |                        |          |    |

|                 | CACHE                 | +-           |             |          |              |          |                |        |                |          |         |          |          | <u> </u>      |          |          |        |                               |          |                     |            | <del> </del> | <u>}</u> |           |          |            | 4                             |                                         |                        |          |    |

| 6F              |                       |              |             |          |              |          | - <del>-</del> |        |                |          | •       |          | <u>-</u> |               |          |          |        |                               |          |                     |            | ·            | }        | <u> </u>  |          |            | 1                             |                                         |                        | •        | •  |

| 76              |                       | 1            |             |          |              |          | -,             |        |                |          |         |          |          |               |          |          |        |                               |          | ·                   | ļ          | ļ            | ļ        | ļ         | ļ        |            | 4                             |                                         |                        |          |    |

| 8F              | INC A                 | 0            | 0           | 0        | 0            | 0        | 0              | 0      | 0              | 0        | 0       | 0        | 0        | 1             | 0        | 0        | 0      |                               |          |                     |            | ļ            | 1        | ļ         | ļ        | ļ          | 4                             |                                         |                        |          |    |

| 9 <b>F</b>      |                       |              |             |          |              |          | i              |        |                |          |         | •        |          |               |          |          |        |                               | L        |                     |            |              |          |           | L        |            |                               |                                         |                        |          |    |

| 10F             |                       |              |             |          | .            |          | !              |        |                |          |         |          |          |               |          |          |        |                               | l        |                     |            | 1            |          |           |          |            | 1                             |                                         |                        | •        | •  |

| 11F             |                       |              | •.          |          |              |          | i              |        |                |          |         |          |          |               |          |          |        |                               |          |                     |            |              |          |           |          |            | ].                            |                                         |                        |          |    |

| 128             |                       |              |             |          |              |          | 1              |        |                |          |         |          | •        |               |          |          |        |                               | 1        |                     |            |              |          | 1         |          |            | ]                             |                                         |                        |          |    |

| 13F             |                       | 1            |             |          |              |          | 1              |        |                |          |         |          |          |               |          |          |        |                               |          |                     |            |              |          |           | 1        |            | 1                             |                                         |                        |          |    |

| ŀĄF             |                       | 1            |             |          |              |          |                |        |                |          |         |          |          |               |          |          |        |                               |          |                     | 1          | 1            | 1        | 1         | 1        | 1          | 1                             |                                         |                        |          |    |

| 15F             |                       | 1            |             |          |              |          |                |        |                |          |         |          |          |               |          |          |        | 1                             | 1        |                     | 1          | 1            | 1        | 1         | 1        | 1          | 4                             |                                         |                        |          |    |

| ZERO            | NO OPERATION          | 0            | 0           | 0        | 0            | 0        | 0              | 0      | 0              | 0        | 0       | 0        | 0        | 0             | 0        | 0        | 0      | +                             | <b>.</b> | <b>I</b>            | 4          |              | I        | <b>J</b>  | J        | 1          |                               |                                         |                        |          |    |

|                 | L                     | 1            |             |          |              |          | •••            |        |                | <u>_</u> |         |          |          | L             |          |          | i      | •                             |          |                     |            |              |          |           |          |            |                               |                                         |                        |          |    |

| GV. NO          |                       | 1            |             |          |              |          |                |        |                |          |         |          | Т        |               |          |          | -      | A J LIE                       |          | a J.L.18<br>• 21104 |            |              | В        | urroug    | he Co    | poratic    | - 3                           | M-P                                     | ROCESSOR               | 3 MICRO  | is |

|                 |                       | 1            |             |          |              |          |                |        | · 1            |          |         | •        | 1        |               |          |          |        | HITAN TO RANDLAS C            | MORATIO  |                     |            | USED FOR     | COMPUTER | SYSTEMS G | ROUP     | SAN        |                               | LITTLE AIS                              |                        | D-2216   | 5- |

|     |    |       | •      |         |       |       | •<br>• |

|-----|----|-------|--------|---------|-------|-------|--------|

|     |    |       | A DAT  | A SELE  | CTORS | •     |        |

|     |    | CAR   | ) Ĥ.   | CARD    | ĸ     | LAR   | M      |

|     |    | 23    | . 16   | 15      |       | 7     | · 0    |

| Τ   | 0  | X     | X      | X       | ×     | X     | ×      |

| ſ   | ١. | . Y   | Y Y    | Y       | · Y   | Y Y   | Y .    |

| Ĩ   | 2  | TA    | TB     | TC      | TD    | TE    | TF.    |

|     | 3  | LA    | LB     | LC      | LD    | LE    | LF     |

| ٢Ţ  | 4  | FA    | FA     | FA      | FA    | FA    | FA     |

| ŗ[  | 5  | Fu    | FT     | FLC     | FL)   | FLE   | FLF    |

| ; [ | 6  | PERP  | PERM   | cc      | ()    | CA.   | CB     |

| ſ   | 7  | 8 LIT | BLIT   | MSSW    | -     | LP    | CP     |

|     |    | EA23  | 16 X 0 | EA 1508 | XO    | EA070 | 0 X 0  |

| • .  | · . |         | <u>)                                    </u> |        | •      |          | · •.       |

|------|-----|---------|----------------------------------------------|--------|--------|----------|------------|

| ·    | Ī   |         | 37                                           | ATA SE | LECTOR | 5        |            |

|      |     | CAR     | ) #                                          | CAR    | d K    | CAR      | > n        |

|      | 0   | У       | <u>y</u>                                     | Y      | Y      |          | ; y        |

|      | 1   |         |                                              | · -    |        | SLIT.    | SLIT       |

|      | 2   |         |                                              |        |        | · CPL    | CPL        |

| 0    | 3   | T       | <u>,</u> т                                   | Τ      | Τ,     | <u> </u> | <u>'</u> T |

| * X0 | 4   | LPAD    | LPAD                                         | LPAD   | LPA)   | LPAD     | LPAD       |

| 13   | 5   | R PAD   | RPAD                                         | R PA)  | R PAD  | RPAD     | RPAD       |

| SA   | 6   | BR      | BR                                           | BR     | BR     | BR       | BR         |

|      | 7   | LR      | LR                                           | LR     | LR     | LR       | LR         |

|      |     | E B 231 | 6 X 0                                        | 1      | EB 150 | 0 X O    | ·          |

ASEL N. X.

Fis **4**B A DATA & B DATA SELECTORS ASSIGNMENTS W.K. Sprome 2/8/76

er. In

u ta

COMPANY CONFIDENTIAL M-PROCESSOR-3 E.D.S. #2215 9891

# 2.1 THREE PHASE MICRO EXECUTION

Referring to Figure 10, the three phase execution of a micro is described below.

| and the second second | · ·          |                      |                 |             |             |

|-----------------------|--------------|----------------------|-----------------|-------------|-------------|

|                       |              | ****                 | ******          |             | *******     |

| IA-REGI               | -> ICACHE 1  | ->   M-REG!          | ->+ DECODE+     | -> I N-REG! | ->+EXECUTE+ |

| ******                | SHE MORYS    | 40 40 40 40 40 40 40 | * LOGIC*        | ******      | *LOGIC *    |

|                       |              |                      | * * * * * * * * |             | *******     |

| · · ·                 | ์ <b>น</b> * | C**                  | u               | • P 4       | u"a"        |

| •                     |              | >                    | •               | >           | ,           |

|                       |              |                      | 1               |             |             |

# FIGURE 10

The process of a micro-instruction in the machine has three steps. Assume a string of one clock micros. At the first clock, it is loaded into the instruction register (H); at the second, it is decoded and stored in the control register (N); and at the last clock, it is executed. At one clock time, all three steps are occurring, each to а different micro-instruction. Stated differently, while the fetch o f the micro-instruction (c) one beyond the next micro-instruction is being made to the M-register, the next micro-instruction (b) is being decoded into the N-register, and the present micro-instruction (a) is being executed. This microminstruction process will be referred to a s the 3-phased cycle.

Figures 11 through 20 show stylized 3-phase execution waveforms.

Figures 21 and 22 show a breakdown of the N=register; Figure 21 the Low order bits and Figure 22 the high order bits.

COMPANY CONFIDENTIAL N-PROCESSOR-3 E.D.S. #2215 9891

CLOCK 1 T1 1 T2 1 T3 1 T4 1 T5 1 N-REG 1 H1(1) 1 H2(1) 1 H3(1)+ 1 H3(1)+ 1 H4 1 -----1 12 M-REG 1 M 3 1 M4 1 M4 1 M5 Ł 1 M3 FETCH 1 M4 1 N5 1 M5 1 M 6 1 1 a5 A1 1 a2 1 a3 1 a4 1 a4 1 1 a3 1 a5 AO l a4 l a5 1 a 6 1

A1 = INSTRUCTION REG (address of instruction in M-REG, being decoded) A0 = CACHE ADDRESS REG (address of instruction being fetched from Cache aJ = Address of MJ MJ = Micro-instructions J

MJ(i) = ith nano instruction, of microminstruction J

\*MJ(i) held over for another clock

.

MJ --> MJ(i) : Micro J being decoded into its ith nano

FIGURE 11. SINGLE NANO MICRO-INSTRUCTION TIMINGS

.

.

. .

• • •

COMPANY CONFIDENTIAL M-PROCESSOR-3 E.D.S. #2215 9891

.

| N     | ŧ   | T 1      | 1     | T2        | 1 | <b>T</b> 3 | 1   | <b>T</b> 4 | ŧ | T 5   | 1 |       |

|-------|-----|----------|-------|-----------|---|------------|-----|------------|---|-------|---|-------|

| N-REG | 1   | M2       | <br>t | M2(1)     | 1 | H2(2)      | 1   | M2(3)      | 1 | M 3   | 1 | 1     |

| M-REG | 1 M | 2->M2(1) | 1     | M2->M2(2) | 1 | M2->M2(3)  | 1   | M 3        | 1 | M 4 . | i | ••••• |

| FETCH | 1   | M 3      | 1     | M 3       | 1 | M 3        | 1   | M4         | 1 | M5    | 1 | 1     |

| A 1   | 1   | a2       |       | a2        | 1 | a2         | 1   | a 3        | 1 | a 4   | 1 | 1     |

| AO    |     | a3       | 1     | a3        |   | a3         | . 1 | a4         | 1 | a 5   | 1 | ••••• |

# FIGURE 12 MULTI-NANO TIMINGS (3 NANO INSTRUCTION)

are missing. thru 22 Note: Figures 13

COMPANY CONFIDENTIAL

M=PROCESSOR=3

E.D.S. #2215 9891

### BURROUGHS CORPORATION Computer systems group Santa Barbara plant

# 3.0 PRODUCT DESCRIPTION

#### 3-1 PROCESSOR REGISTERS

#### 3.1.1 M

The M-register (micro-register) is a 16-bit register used to hold the active micro-instruction (M-instruction or micro-operator or M-op). The state of this register is decoded to enable the different control signals within the processor to perform the operations called for by the M-Op. The M-register is broken into 4 fields for decoding that are structured such that 61 distinct M-ops can be decoded.

The M-register is addressable as a source and as a sink (destination). When used as a sink register, the source is bit-ORed with the upcoming M-op. Exception: In TAPE mode, the source is not bit-ORed with the upcoming M-op.