Tiburon's Greg Pope on: Software Testophobia

FOR ELECTRONIC ENGINEERS & ENGINEERING MANAGERS

TEST

Silicon Foundry

# Analog designers still trail behind their digital counterparts

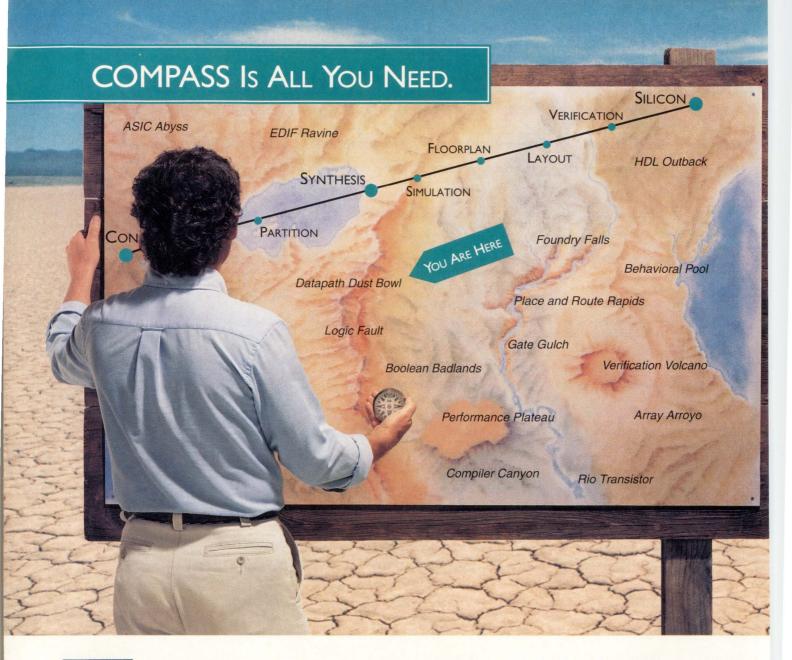

Synthes Tools

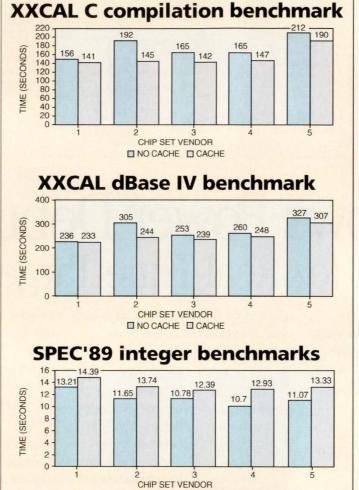

Performance analysis spots hardware/software bottlenecks

Windows demands drive PC chip set features

High-speed A-D converters shift to new architectures

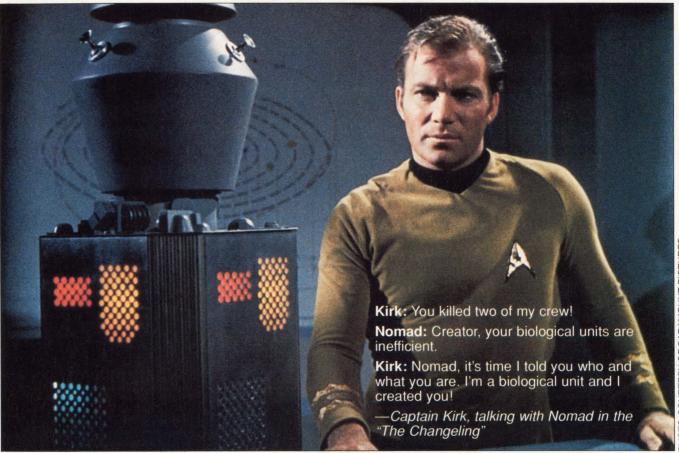

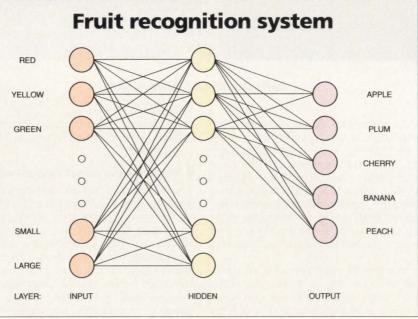

> Special Report on Future Computing Is neural computing the key to artificial intelligence?

# MAYBE YOU JUST NEED BETTER DRIVERS.

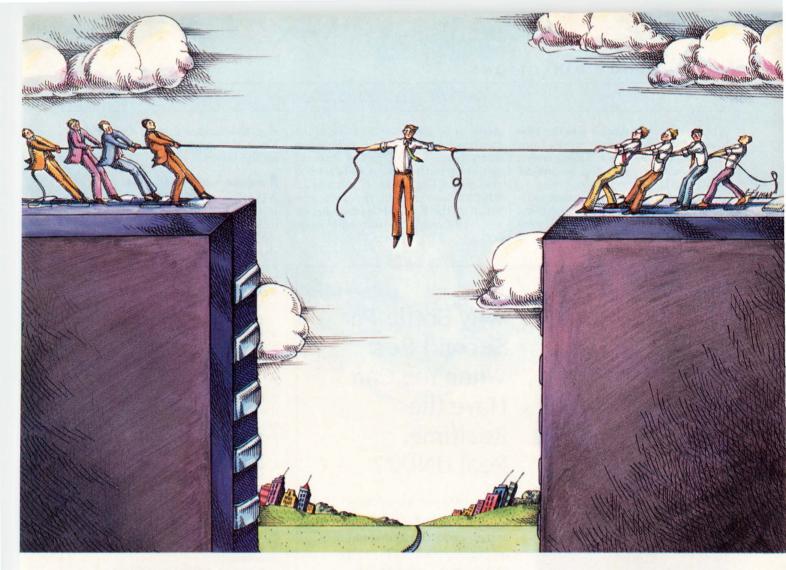

Stuck in a SCSI data-transfer bottleneck?

A first-class SCSI-2 VME board *could* get you out of that jam...*if* getting that board up and running doesn't leave your whole engineering team in gridlock.

That's why, when you buy a Rimfire SCSI-2 VME board from Ciprico, you don't just get a product. You get a partner.

As your partner, we'll help you write the drivers you need, and provide on-site installation. We'll even work with your engineering team to customize hardware or software for your special application needs.

And you get Rimfire's unmatched performance, quality and features. Like the new Rimfire 3870 and 3590 – the first VME boards with independent two-channel SCSI-2 architecture.

First-class hardware *and* first-class support and service. *That's* how you beat bottlenecks. And *that's* what Ciprico is all about.

### TURN TO CIPRICO WHEN YOU'RE IN A SCSI JAM.

CALL 1-800-SCSI-NOW Ciprico, Inc. 2800 Campus Drive

Minneapolis, MN 55441

Fax: (612) 551-4002

CALL (44) 635 873666 Ciprico (Europe) Ltd. 7 Clerewater Place, Lower Way Newbury, Berkshire RG13 4RF England Fax: (44) 635 871996

**CIRCLE NO. 1**

**CIPRICO**

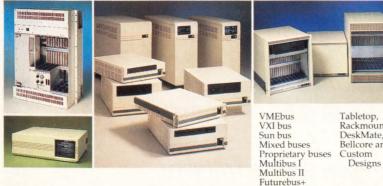

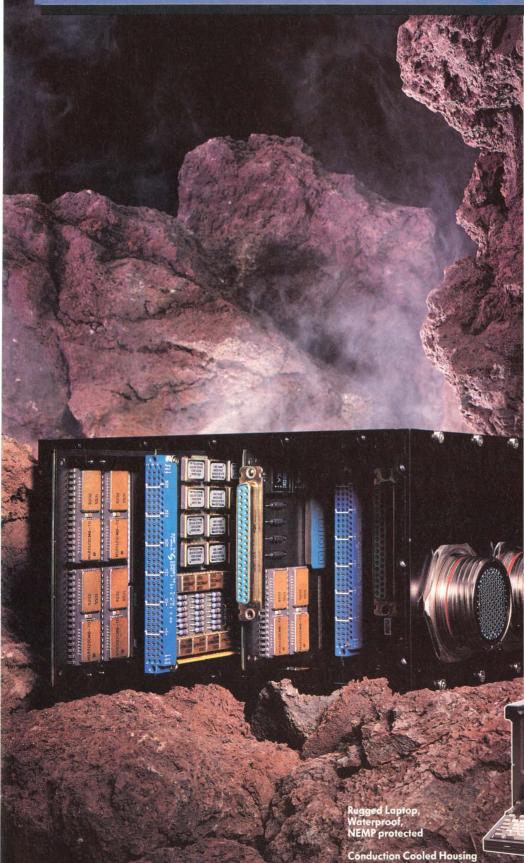

Innovative Technology In System Packaging the Enclosure

# One Thing Separates a Great System Enclosure from a Good One.

It's the innovative application of cutting-edge technology to your specific requirements. It's what we do at Electronic Solutions.

If you're the engineer responsible for the system packaging, you have your hands full dealing with power distribution, cooling, and safety concerns such as UL, CSA and VDE approvals. That's where Electronic Solutions can make your job easier! You can rely on our experience and expertise to quickly resolve the design issues you're facing-at a price that even your bean counters will be pleased with.

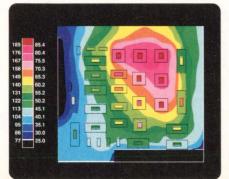

Airflow testing. Our in-house airflow/temperature testing facility allows us to carefully examine the environment inside a system enclosure, testing the effects of wire harness placement, fan size and location, and the characteristics of the airflow path itself. We can even test your complete system to fine tune air direction, cool hot spots, and reduce audible fan noise and power consumption.

Safety Agency Approvals. Bypass the costly maze of paperwork and testing! We can provide enclosures that are already UL listed, CSA certified, and GS approved through TUV certification. That big step allows you to install recognized boards and peripherals and win

Tabletop, Rackmount, DeskMate, Bellcore and

6790 Flanders Drive, San Diego, CA 92121 (619) 452-9333 FAX: 619-452-9464 Call Toll Free: (800) 854-7086 In Calif: (800) 772-7086

agency approval of your finished system with no additional effort or cost! As a self-testing facility for the agencies, we're equipped to handle every aspect of certification to reduce your costs and shorten your time to market.

EMI/RFI Testing. We subject our enclosures to in-house testing per MIL-STD-285, providing an attenuation profile of each unit. When it comes time for you to pursue FCC or VDE approval of your system, we can perform these tests for you and resolve any problems immediately.

Whether it's off-the-shelf or something special that's off-thedrawing board, there's only one way to get the enclosure that's just right for your system. That's to call Electronic Solutions and put our experience to work for you.

-KOR Electronics Garden Grove, CA

You'll find Synergy products built into the world's most demanding applications.

# The Goal:

Design the world's only multifrequency Radar Target Generator System able to simulate hostile threats on the military's diverse radar systems.

### The Problem:

To get the needed horsepower, sixteen 68040 CPU boards were required. However, with this many boards, VMEbus bandwidth limits would severely degrade system performance making the project unfeasible.

### **The Solution:**

Synergy's V420 dual 68040 SBC. After evaluating several products, KOR Electronics selected eight V420s which could deliver 320 MIPS without VMEbus bandwidth degradation.

"Not only did we meet our project performance goals, we were able to reduce our costs by 40%."

### **Unexpected Benefits:**

Synergy's dual '040 solution cut KOR's hardware requirements by 50% while vastly increasing system reliability. These unexpected benefits reduced system costs by 40%.

In Synergy, KOR also found a design partner with strong integration expertise and dependable customer support.

# "I recommend you call Synergy today."

Next time you need high performance SBCs, do as KOR Electronics did. Call Synergy Microsystems. You'll be as satisfied as they are.

High performance SBCs for demanding applications.

SYNERGY MICROSYSTEMS, Inc. 179 Calle Magdalena, Encinitas, CA 92024, 619-753-2191, Fax 619-753-0903

A PENNWELL PUBLICATION

VOL 31, NO 10 / OCTOBER 1992

FOR ELECTRONIC ENGINEERS & ENGINEERING MANAGERS

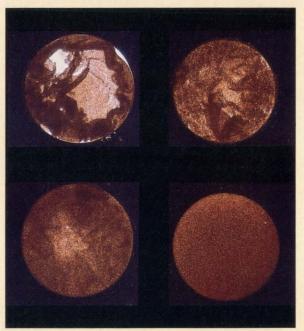

In the days of the '49ers, it was gold that was in "them thar hills." Today, up the road from Sutter's Mill, it's siliconand the latest rush is on-to analog design......107

Illustration by **Bill Morrison**

| Editorial        | 20  |

|------------------|-----|

| Advertiser Index | 150 |

### **COMING NEXT** MONTH

Designing for testability

Mezzanine bus strategies

Advances in datacom ICs

**Emulators**

Robotics and automation

# NEWS BRIEFS

ov and viget down to business . . . Intel deemphasizes Multibus . . . Altera supports user-selected design tools . . . Bus interface chips hit the street . . . Next finds big buy for 486 operating system . . . Pact eases setup of X Windows on PCs to networks . . . Intel enters FPGA game .... FPGA makers minimize handling.......10

# **TECHNOLOGY DIRECTIONS**

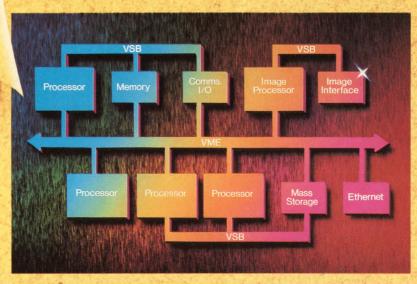

### **Computers & Subsystems**

| First Futurebus—to-VME bridge board appears        | .30 |  |

|----------------------------------------------------|-----|--|

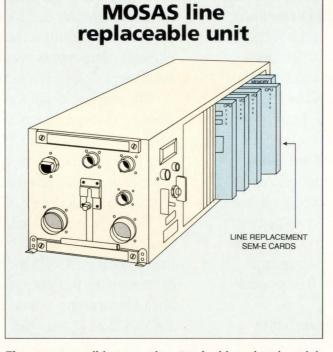

| MOSAS wants military to drive commercial standards | 38  |  |

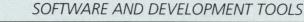

# Software & Development Tools

Real-time environments aimed at cost-sensitive 32-bit designs ....44

# **Integrated Circuits**

| Chip sets could unleash workstation clones              | 48 |

|---------------------------------------------------------|----|

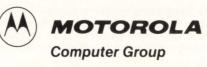

| Specialty PROMs count bursts, implement state machines  | 52 |

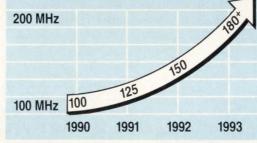

| Leaders in mixed-signal design to meet in San Francisco | 57 |

# **NEW PRODUCT DEVELOPMENTS**

| ASICs & ASIC Design Tools                              |    |

|--------------------------------------------------------|----|

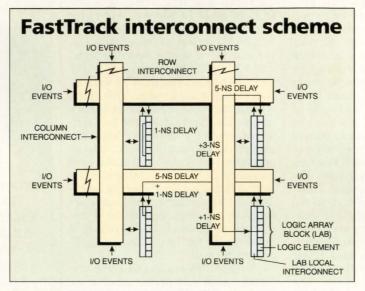

| Register-rich FPGA family has 9-ns interconnect delays | 34 |

| Computers & Subsystems          |   |

|---------------------------------|---|

| DSP chip set aimed at real time | 5 |

| Ps get PCMCIA adapter           | 7 |

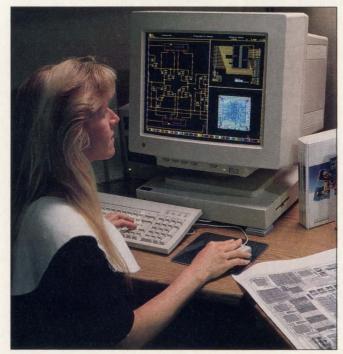

# **CAE/CAD** Design Tools

# **Software & Development Tools**

# **SPECIAL REPORT ON FUTURE COMPUTING**

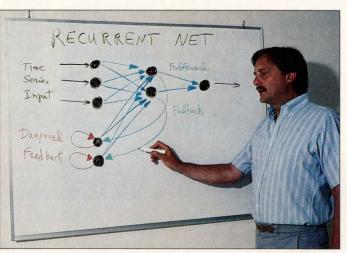

# Is neural computing the key to artificial intelligence?

Neural networks are touted as a technology that can predict everything from the outcome of a horse race to loan eligibility. Are we witnessing an artificial intelligence revolution or only headline-grabbing hype?

Page 30

Page 48

Page 87

**CONTINUED ON PAGE 5**

OURCEGAT

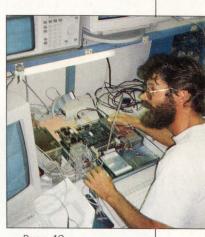

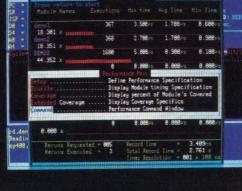

# integrating high level language debugging with in-circuit emulators.

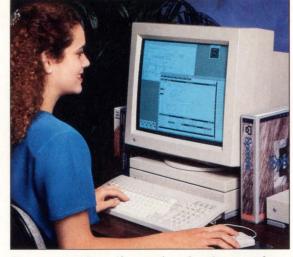

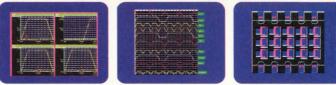

SourceGate is a window driven high level language debugger designed to support the Huntsville Microsystems 200 series of in-circuit emulators.

- User configurable windows can be sized, moved and duplicated anywhere on the screen.

- Code can be viewed in all displays (trace, single step, etc.) in one of three modes: Source only, Assembly only or both Source and Assembly.

- Watch windows display and monitor code variables.

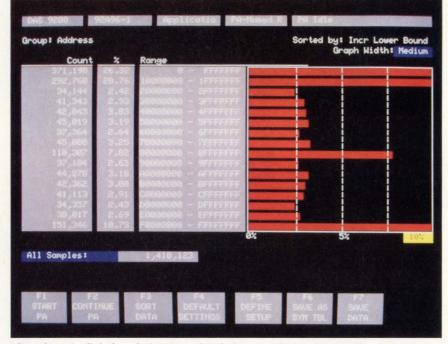

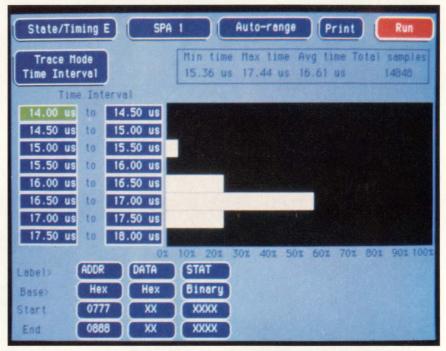

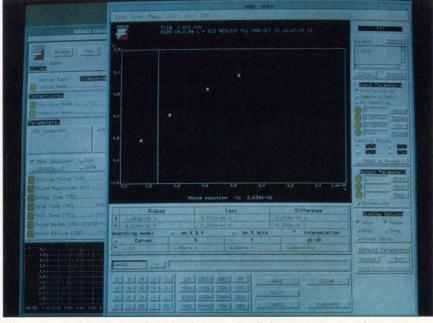

- Optional Performance Analysis Card for real-time software performance analysis and real-time software test coverage.

- Available for IBM PC family and UNIX systems including Apollo and SUN.

For more complete technical information, write to Huntsville Microsystems Inc., 3322 South Memorial Parkway, Huntsville, AL 35801 or call (205) 881-6005. Ask for *free* demo disk.

IBM is reg. T.M. International Business Machines, Inc. Unix is reg. T.M., Bell Laboratories, Inc.

| Vertication                                     |                                         |                                              |                                                                |                         |                   | interior Line           |  |

|-------------------------------------------------|-----------------------------------------|----------------------------------------------|----------------------------------------------------------------|-------------------------|-------------------|-------------------------|--|

| denot o                                         |                                         |                                              |                                                                |                         |                   |                         |  |

| c Abuf                                          | fer (16)                                | 48,75                                        |                                                                |                         | .28.40,69.63<br>S | ,72.69<br>Полодина Поло |  |

| float<br>double<br>char<br>long<br>int<br>short | x<br>9<br>a[38]<br>11<br>times<br>rvect | 3FC8<br>3FCC<br>3FD4<br>3FF2<br>3FF6<br>3FF6 | 17.27<br>17.2788888<br>"Huntsvill<br>0xFF563<br>8x1 1<br>8x8 8 | e Microayste<br>1845859 |                   | xFEN8xFEN8N8            |  |

| Linner                                          |                                         |                                              |                                                                | w Vindow A              | Stack<br>pain()   | trace window            |  |

| demo2:1                                         |                                         | = 8.88                                       |                                                                |                         |                   |                         |  |

| Available   | Emulators         |

|-------------|-------------------|

| 68000       | 68EC020           |

| 68008       | 68EC030           |

| 68010       | 68HC001           |

| 68020       | 68HC11 Family     |

| 68030       | including F1&D3   |

| 68302       | 8051 Family       |

| 68301/303   | DS5000            |

| 68330/333   | 8096/80196 Family |

| 68331/332   | 8085              |

| 68340       | 64180/Z180        |

| 6809/6809E  | Z80               |

|             | 68HC16 Family     |

| Now support | ting 68040 Series |

| 0000049E<br>002031FC                             | LG         EFFFFFFF         LTmm         PROVIDE         Provi |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18:<br>80488<br>88480<br>88400<br>88412<br>89414 | eboffer[] * tolex(1); /* Fill ASCII buffer */<br>MOVE H 10:00<br>MOVEAL 12:00<br>MOVEAL 12:,-(AT)<br>13:1 L (FebOlomSes::TOMEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                  | 48 - Bel S - Bel FE<br>(Traces   Balfri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -                                                | Conend 4]Tate Trigger: 0FF<br>Trigger:15:38<br>End Trieger0808H cycles after trigger<br>Trace Ovalifier: NDNE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11ne D:<br>68845 ec.<br>98845                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# CONTINUED FROM PAGE 3

Tiburon's Greg Pope on: Software testophobia

### TECHNOLOGY & DESIGN REPORTS

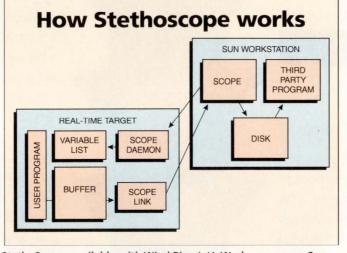

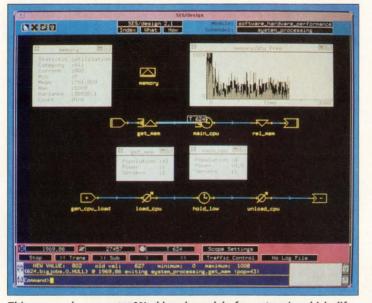

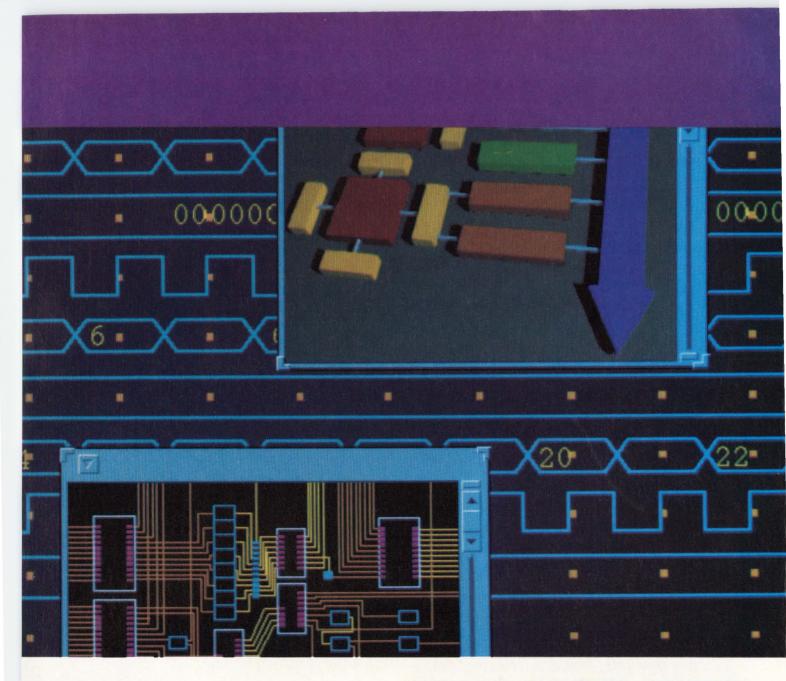

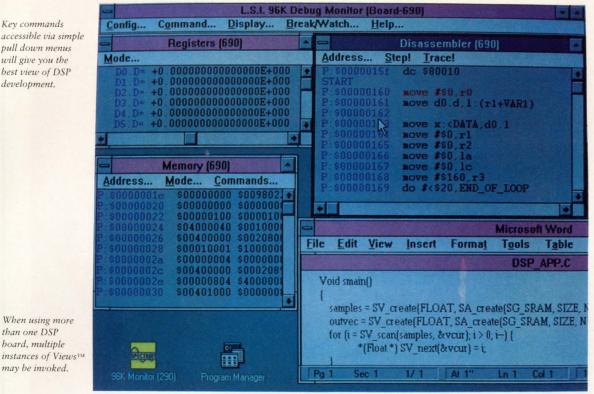

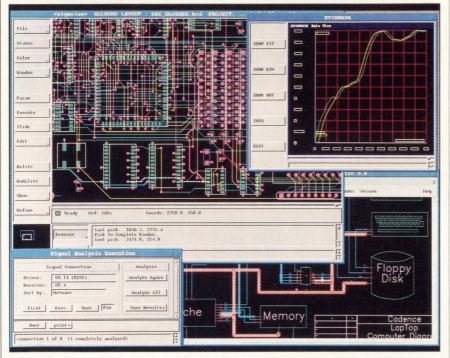

### Performance analysis spots hardware/ software bottlenecks

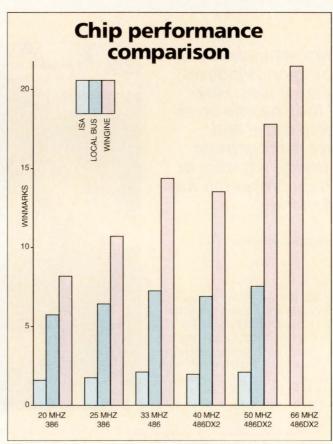

# Windows demands drive PC chip set features

# **COVER STORY**

# Analog designers still trail behind their digital counterparts

# DESIGN STRATEGIES

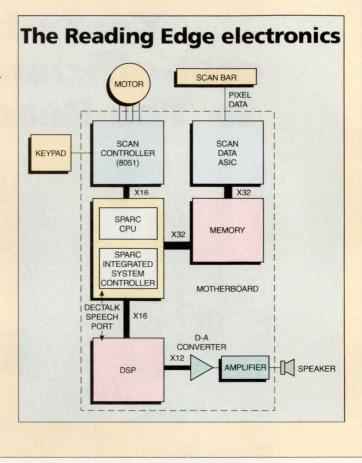

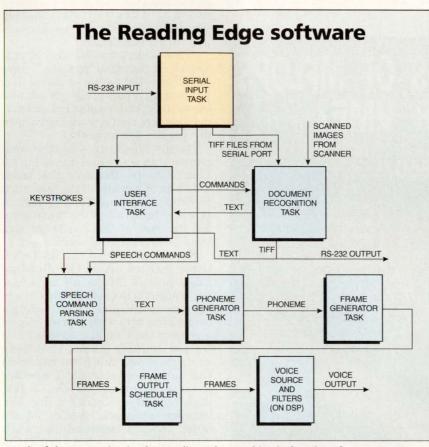

# Xerox brings cost-efficient strategy to The Reading Edge

Xerox Imaging Systems redesigns The Reading Edge, a machine that converts printed characters into synthesized speech for the blind and visually impaired.—*Jeffrey Child*......**123**

# PRODUCT FOCUS

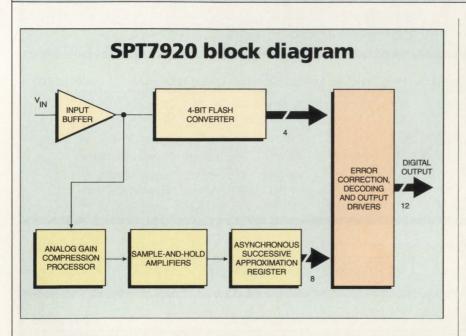

# High-speed A-D converters shift to new architectures

# COLUMN

Page 61

Page 73

Page 129

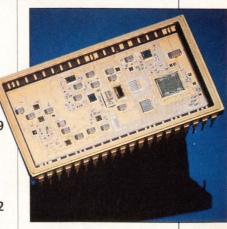

Think of it as peer pressure at its finest. All these companies want you to take some time off: Time off your design cycle, and your time to market. They're the Fusion29K<sup>™</sup> Partners, and their support helps make the 29K<sup>™</sup> Family of embedded RISC processors so fast and easy to use.

Fusion29K Partners include

over 100 reputable companies with more than 200 different support products. Together,

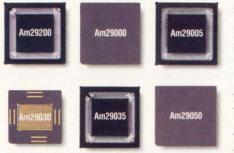

The 29K Family includes parts for every conceivable applicationfrom the brand new low cost, easy-to-use Am29200<sup>TM</sup> to the top-of-theline Am29050<sup>TM</sup> with on-chip floating point coprocessor. they provide everything you need to speed up the design process, every step of the way. From evaluation, to system and hardware design, software development, hardware and software integration, system debug—all the way to production.

have a whole arsenal of time and labor saving devices. You'll find emulators, simu-

lators, CASE and CAE tools, C compilers, machine and source level debuggers, logic analyzers, and manufacturing support of all kinds. All of the highest quality and performance standards.

And it won't take a lot of time to get acquainted with these development tools, since they include most of the hardware and software products you already know.

For more information on the 29K Family of embedded RISC processors and Fusion29K support, call AMD today: 1-800-292-9263 Ext. 3.

With this much support, you may be able to take some time off for yourself.

29K is a trademark and Fusion29K is a servicemark of Advanced Micro Devices. All other brand or product names are trademarks or registered trademarks of their respective holders.

# This is your chance to get the full power of embedded

FORCE Computers, Inc., 3165 Winchester Blvd., Campbell, CA 95008-6557, Prof.-Messerschmitt-Str. 1, W-8014 Neubiberg/München. All brands or products are trademarks of their respective holders. © 1992. FORCE Computers, Inc., 3165 Winchester Blvd., Campbell, CA 95008-6557, Prof.-Messerschmitt-Str. 1, W-8014 Neubiberg/München. All brands or products are trademarks of their respective holders. © 1992. FORCE Computers, Inc., 3165 Winchester Blvd., Campbell, CA 95008-6557, Prof.-Messerschmitt-Str. 1, W-8014 Neubiberg/München. All brands or products are trademarks of their respective holders. © 1992. FORCE Computers, Inc., 3165 Winchester Blvd., Campbell, CA 95008-6557, Prof.-Messerschmitt-Str. 1, W-8014 Neubiberg/München. All brands or products are trademarks of their respective holders.

# SPARC. Don't let it slip away.

This is one of those times when you just have to seize the day. Because opportunities like this are

rare indeed. You see.

FORCE is the only <sup>Choose from a range of systems,</sup> for a highly integrated solution. company licensed by Sun to put SPARC<sup>\*\*</sup>station 2 technology on VME.

So we're the only ones who can give you validated hardware and software compatibility. Allowing you to run SunOS<sup>™</sup> with any of your SPARCstation 2 applications and peripherals. Without a hitch.

We also have a whole new family

Our CPU-2CE

RISC microprocessor, de-

features a 40MHz SPARC of SPARC 2 products. With everything from our CPU-2CE (6U) board to the *microforce* single-slot system. We even have 20-slot

*tweing 28.5* We even have 20-slot systems that allow you to customize I/O. Giving you the perfect combination of real-time and UNIX.

And our SPARC products provide the broadest software offering of any RISC architecture. Including SunOS, real-time operating systems and a host of application software.

So if you want a better grasp of embedded SPARC, call for a free brochure. 800-237-8863, ext.5. Or in Europe, 49.89.608-14-0.

Because there's no reason to let all this power slip through your fingers.

**CIRCLE NO. 6**

# NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS

# OVI and VI get down to business

As special interest groups and committees study the feasibility of Verilog and VHDL working together, the bodies promoting the use of each HDL continue to operate as usual. Thirteen ASIC, EDA and Verilog end-user companies just elected Bill Fuchs, president and CEO of Simucad (Union City, CA) a Verilog HDL simulator company, to chair Open Verilog International (OVI). Meanwhile, vendor and user companies backing VHDL were making plans for the fall meeting of the VHDL International Users' Forum (VIUF), to be held later this month in Washington, DC. VIUF will convene under the leadership of VI president and CEO Michael Carroll and newly elected board chairman Harvey Jones of Synopsys. AT&T Bell Laboratories, CLSI Solutions, IBM, IKOS, Robert Bosch GMBH (Germany), Texas Instruments, and Toshiba (Japan) will be attending VIUF as new VI members.

In the meantime, a group of VHDL vendors and users is picking up efforts to generate support for the Cadence-backed initiative launched at DAC to incorporate standard Verilog modeling practices into VHDL, paving the way for the possible coexistence of the two HDLS. Known as VITAL (VHDL Initiative Toward ASIC Libraries), the initiative is now being coordinated by three industry representatives: Steve Schulz, member of the technical staff at the Defense Systems and Electronics Group at Texas Instruments (Dallas, TX); William Billowitch, president of VHDL Technology Group (Allentown, PA); and Erik Hayskens, head of CAD and test for the VLSI group at Alcatel NV and the European coordinator for VITAL

Being circulated among VITAL backers is a "discussion document" that's to be the foundation for a formal proposal to the appropriate VHDL standardization groups. —Barbara Tuck

# Intel deemphasizes Multibus

Over the past two years, Intel (Hillsboro, OR) has been relaxing its marketing efforts on behalf of Multibus products and putting its energies into its PC-based lineup. Recent reports have the company's next move as removing Multibus products from the sales staff's commission schedule. Customers interested in buying Multibus hardware need not contact the Intel sales force; instead they should call (800) 438-4769 for any engineering, design, pricing, or other information. To place an order, you'll have to go to your local distributor. With no commission coming, it's unlikely a call to your Intel salesperson will result in much action.

With hindsight, it can be seen that Intel has been bowing out of the Multibus business since the departure of former marketing head Mike Richmond. Current marketing manager Dick Binns stresses that Intel is focusing its systems strategy on whatever will strengthen its preeminent position in the PC-compatible world. It can easily be conjectured from this that Multibus will play a secondary role to the PC business.

-Warren Andrews

# Altera supports userselected design tools

In a move to broaden support for its programmable logic families, Altera (San Jose, CA) put a strategic partnership program with tool vendors into place a few weeks ago. Dubbed ACCESS (Altera Commitment to Cooperative Engineering Solutions and Sales), the program promises the company's full support for whatever design-tool option partners and customers choose. Initial partners include Data 1/0, Dazix, Exemplar, Logic Modeling, Mentor Graphics, MINC, and Synopsys.

"Altera recognizes the importance of supporting industry-standard platforms and design tools to enable our customers to create the design environments that meet the specific requirements of their projects," said vice-president of marketing Erik Cleage.

According to Michael Holley, senior staff engineer at Data I/O, "The significance of the ACCESS program is that it provides designers with the ability to utilize any of Altera's architectures in a known environment. In our case, ABEL customers will now have support for all of Altera's broad range of current products, and in addition we will have the ability to introduce new device support coincident with production software from Altera."

The ACCESS program operates through framework integration and cooperative engineering involving the exchange of information in advance of product introduction. Design information may be transferred via EDIF netlist into MAX+PLUS II from design capture and synthesis tools, or exported to selected simulation environments. —Barbara Tuck

# Bus interface chips hit the street

Buscon saw the introduction of samples of some long-awaited businterface chip sets, and the announcement of some new ones on the way. Texas Instruments (Houston, TX) finally unveiled silicon of its Futurebus+ protocol controller, jointly developed with Force Computers (Campbell, CA). National Semiconductor (Santa Clara, CA) also announced availability of its Newbridge/National Futurebus+ protocol controller.

Force has announced a new partnership with Cypress (San Jose, CA) for the design and manufacture of a next-generation VME interface IC that supports VME64, SSBLT and many of the features in what was to be Revision D of the 1014 specification.

Not satisfied with the minimalist Futurebus+ ICs that were made available last month by TI and National, Futurebus+ board maker Cable and Computer Technology (CCT-Anaheim, CA) has huddled with LSI Logic and will be jointly developing a new Futurebus+ protocol controller. The CCT/LSI controller is expected to include many of the bells and whistles not included by the others. The chip will be the only one to fully support the 896.1 version of cache coherency and to include packet- as well as handshakemode transfers. CCT has already built working boards with discrete (programmable logic) implementations of these functions, and antici-

Continued on page 12

# FROM IDT

∫dr74FCT 16373CTPV

# 46% BOARD SAVINGS

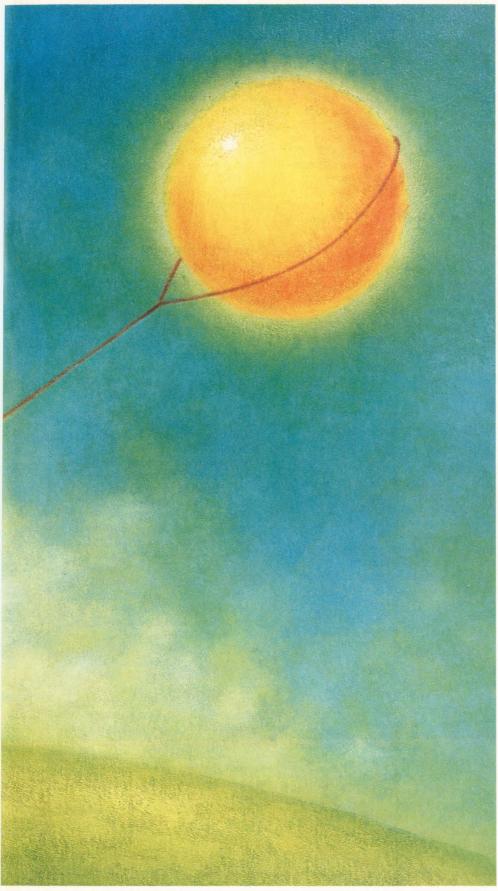

IDT's new 16-, 18-, and 20-bit Double-Density FCT-T Logic family offers the performance of two octal logic devices in one flow-through 48- or 56-pin high-density, JEDEC-standard, shrink small outline package (SSOP) or Cerpack, for twice the functionality in half the board space.

# A WIDEBUS" UPGRADE

IDT's Double-Density logic family is more than twice as fast as **ACT**, uses 35% less power than **ABT**, and it's form-, fit-, and function-compatible with both

ЮН

-32 mA

-24 mA

-8 mA

DOUBLE-DENSITY

**CONFIGURATION\***

**Balanced Drive**

**High Drive**

3.3V

of TI's Widebus families. The Double-Density family also offers typical pin-to-pin skew of 250ps and quiescent supply current at 0.05mA (typ.).

# **3 APPLICATION CHOICES** 5V High Output Drive

Ideal for low-impedance bus and backplane applications.

**5V Balanced Drive (Low Noise)** Contains on-chip, source-terminating resistors to minimize signal noise. These devices are ideal for driving point-to-point transmission lines and highly capacitive loads, such as a bank of DRAMs or SRAMs.

# **3.3V Low-Power Logic**

I lo zn I I

Designed for regulated or unregulated 3.3V power supplies, these devices use less power than 5V parts, without sacrificing high speed. 5V-to-3.3V unidirectional and bidirectional translators are also available.

# FREE SAMPLES

Call today for free samples and a copy of the **new**

High-Performance Logic Data Book and start your Double-Density logic design today!

\*Specs are for '244 device Double-Density is a trademark of IDT. All others are trademarks of their respective manufacture

1 200

# (800) 345-7015 • FAX: 408-492-8674 ASK FOR KIT CODE 3071

Integrated Device Technology, Inc.

# NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEWS

Continued from page 10

pates few problems in the chip versions. The CCT/LSI chips are expected to be available with both military and commercial screening grades.

In the meantime, there's a rumor that Motorola (Phoenix, AZ) may be working independently on its own Futurebus+ chips. The rumor has been fueled by the company's involvement with MOSAS and the greater interest it's expressed in Futurebus+. News is still sketchy about what kind of IC the company might be planningand when. Recently, Motorola terminated talks with at least one system maker to jointly develop a chip. It's believed it did so because it plans to develop its own chip (a MOSAS module, perhaps?).

-Warren Andrews

# NexT finds big buy for 486 operating system

One of the little-noticed but potentially significant players in the current operating system wars is Apple cofounder Steve Jobs' NexT Computer (Redwood City, CA). Next has been a marginal player in selling desktop computer systems ever since it introduced its first 68020-based machine almost five years ago. But inside the NeXT machine lies what may possibly be the big money maker-its Next-Step operating system. Built around the UNIX-like Mach operating system from MIT, NextStep features a built-in graphical user interface and an object-oriented application builder.

Now Next has done the smart thing and ported NextStep to the Intel 80486 in the form of Next-Step486, which is expected to ship early next year. That move has already attracted one very large potential customer, Chrysler (Highland Park, MI), which is reportedly ready to order 3,000 copies of Next-Step486. Validation of the touted ease of development with Next-Step in a large corporation such as Chrysler, which apparently wants to create its own mechanical CAD applications, could put another big player in the ring with those vying to become the heirs to UNIX.

—Tom Williams

# Pact eases setup of X Windows on PCs to networks

One of the major benefits of the X Windows client-server architecture is that a user can run any application anywhere on a network from his or her own local terminal or workstation. Dedicated X terminals have traditionally come with X Windows and networking capabilities built in, but when a PC is to be the X platform, the user has had to install the X Windows software and usually the network card and its software and make the two work together.

Now an agreement between AGE Logic (San Diego, CA) and Novell (Monterey, CA) has resulted in PCbased X-Server software created by AGE, with integrated support for TCP/IP networking from Novell. The result is what AGE calls "pushbutton install" support for three environments-PCs running DOS, Microsoft Windows and Texas Instruments Graphic Architecture (TIGA)-based graphics controllers. The bundled X Windows/TCP/IP package will run on a PC with a variety of networking boards supporting the TCP/IP protocol. The package also supports the Open Datalink Interface (ODI) and the Internetwork Packet Exchange (IPX) for ODI, which will work with the AGE/Novell bundle support token ring and ARCnet networks as well as Ethernet.

-Tom Williams

# Intel enters FPGA game

Intel (Folsom, CA) has announced its entry into high-density FPGA devices and development tools. Apparently Intel believes it can stake out a position in the FPGA market by offering simplicity-treating FPGAs like several PLDs on one chip. Intel's first device in its Flex-Logic FPGA family will be the iFX780. At the heart of the device are eight configurable function blocks. These blocks can be reconfigured either as logic or as memory. In a logic mode, a block has 24 inputs and 10 outputs, like a 24V10 device. In the memory mode, the block is configurable either as a high-speed SRAM or as ROM. These blocks are tied together by a global interconnect matrix. "The 100-percent global interconnect overcomes the traditional complex PLD routing limitations inherent in parts such as Altera's MAX and AMD's Mach," says David Stasaitis, product marketing manager at Intel.

The iFX780 also features some power-saving features. The nonvolatile, programmable elements of the device are shadowed by SRAM elements. On power up, contents of the device's nonvolatile elements are loaded into SRAM. The nonvolatile elements are then turned off, resulting in lower power consumption. Running out of SRAM, only 1.5 mA per MHz of current is drawn. To put that in perspective, when the device operates at 50 MHz it draws only 75 mA. This makes the iFX780 a fairly complex device in a 132-pin package drawing less power than a single CMOS 22V10 (a 24-pin device). The shadowing SRAM technology also permits the iFX780 to be configured in-system while it's running. Designers can download new code during debug, and test the part without removing it from the board. -Jeff Child

# FPGA makers minimize handling

FPGA users are starting to think about in-circuit programming for devices mounted in fine-pitch PQFP. Data 1/0's (Redmond, WA) director of software development, Dave Kohlmeier, says, "Manufacturers want to minimize handling when lead pitch gets down to 0.5 mm."

One FPGA maker who agrees is Lattice Semiconductor (Hillsboro, OR), which has applied its E2 process to a 2000-8000 PLD gate FPGA line called ispLSI.

Earlier this year, Cypress announced a flash 22V10, and Intel announced that a similar part was in the works. Presumably, either company's process could be extended to more complex devices. —Don Tuite

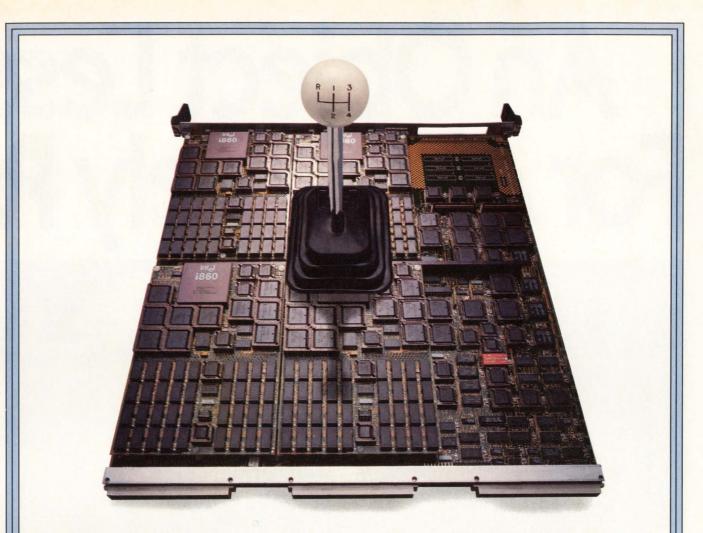

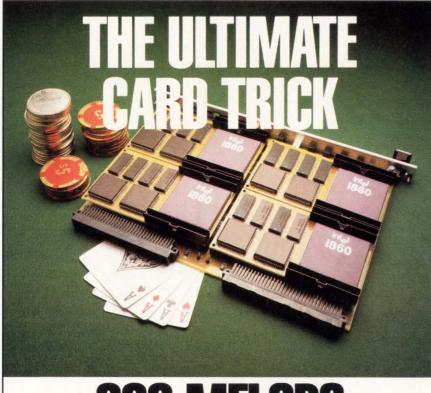

# THE ONLY ATTACHED PROCESSOR WITH FOUR ON THE BOARD AND 2.5 GIGAFLOP PERFORMANCE.

Mercury's MC860VS. The only attached processor that offers up to 32 Intel i860s in no more than 8 VME slots. So you get 80 Mflops to 2.5 Gflops of horsepower to handle demanding applications in defense signal processing and medical imaging. And all Mercury products can be configured in workstations and chassis systems to deliver scalable performance at a scalable price.

| So if you re building or buying a high per-             |

|---------------------------------------------------------|

| formance computing solution, take full advantage of     |

| Mercury's unparalleled investment in standards, inno-   |

| vative hardware, and software development environ-      |

| ment. And get the most complete, flexible, high perfor- |

| mance computing solutions available. If it's time       |

| you moved into the fast lane, it's time to call or      |

| write Mercury today for more information.               |

| Please send me more information on the  | e MC860VS right away.         |

|-----------------------------------------|-------------------------------|

| I want to learn more. Send me your whit | te paper                      |

| "Multiprocessing for the 1990s" and er  | nroll me in your              |

| Education Series program today.         |                               |

| Name                                    | is here and                   |

| Title                                   |                               |

| Company                                 |                               |

| Address                                 |                               |

| City/State/Zip                          |                               |

| Phone                                   |                               |

| Please send to                          |                               |

| 600 Suffolk Street,<br>Dept. K.         | Computer Systems. Inc         |

| Lowell, MA 01854                        | Computer Systems. Inc<br>CURY |

|                                         |                               |

| (508) 458-3100                          | CD 10/                        |

See us at DSPx Exposition & Symposium, Oct. 14-16, Booth #427

# An Object Less For Absolutely Pr

# The MACH<sup>™</sup> Family From AMD: The Fastest, Most Predictable High Density PLDs Available Today.

Oops! You're a couple of nanoseconds shy this time, and it's going to hurt. Perhaps next time you'll

choose a more predictable vehicle. And the most predictable high speed, high-density PLDs available are the MACH family from AMD.

Only the MACH Family offers you worst case delays of 15ns\* or

| Model<br>Number | Equiv.<br>Gates | Macro<br>Cells | Max.<br>Delay | System<br>Speed | I/O<br>Pins | Hard-Wired<br>Option |

|-----------------|-----------------|----------------|---------------|-----------------|-------------|----------------------|

| MACH 110        | 900             | 32             | 12ns          | 66.7 MHz        | 44          | MASC 110             |

| MACH 210        | 1800            | 64             | 12ns          | 66.7 MHz        | 44          | MASC 210             |

| MACH 120        | 1200            | 48             | 15ns          | 50 MHz          | 68          | MASC 120             |

| MACH 220        | 2400            | 96             | 15ns          | 50 MHz          | 68          | MASC 220             |

| MACH 130        | 1800            | 64             | 15ns          | 50 MHz          | 84          | MASC 130             |

| MACH 230        | 3600            | 128            | 15ns          | 50 MHz          | 84          | MASC 230             |

less. Because MACH parts are essentially PAL® devices, just like the kind you already know. Not some hybrid

PLD/FPGA, where you don't know how it performs — until it's too late. So you don't have to guess your delays or clock speeds, you just read them right off our datasheet.

But they're not just ordinary

\*In applications with a full 16 product terms. Every MACH part is specified using real-life conditions with all outputs switching.

# on In The Need edictable Speed.

PAL devices. They're bigger and better, with densities ranging from 900 to 3600 gates, all in our submicron CMOS technology.

Nor will you face unpredictable delays when you order. Because the entire MACH family is now shipping in volume.

Working with them is equally predictable. You don't have to learn any new techniques, just use the software and test equipment you already know. Like ABEL, CUPL, OrCad, and others. Not to mention the software and support from over 20 FusionPLD vendors — all prepared to bring your products to market on time.

And each MACH part can migrate easily to a pin-

compatible, hard-wired MASC<sup>™</sup> counterpart for high volume. So you can get the volume you need, without redesign, NRE, or unforeseen delays.

So call AMD today at **1-800-222-9323**. And let the MACH family make your design cycle a whole heck of a lot safer.

© 1992 Advanced Micro Devices, Inc. 901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088. PAL is a registered trademark, and MACH and MASC are trademarks of Advanced Micro Devices, Inc. All brand or product names mentioned are trademarks or registered trademarks of their respective holders.

# Can Your Current MCUs Meet These Specs?

Highest Integration Lowest Power Dissipation Low Voltage Largest Memory Smallest Packages

Your designs demand more from existing MCUs. As the leader in MCU technology, Mitsubishi offers you a breadth of 8- and 16-bit microcontrollers with the functions you want.

#### **Highest Integration**

Get the highest levels of on-chip functionality with a host of features you need most, including synchronous S I/O, UARTs, programmable I/Os, A-D/D-A converters, LCD and VFD drivers, PWM, special timers and more.

#### Lowest Power Dissipation

We offer the lowest power dissipation available today – 4mA at 3.0V at 8MHz, for our most highly integrated 16-bit MCUs. Low Voltage

For low voltage, our MCUs operate in the 2.7 to 5.5 volt range at 8MHz. For higher performance up to 25MHz, we offer 4.5 to 5.5 volt operation without paying the high power penalty.

### Largest On-Chip Memory

Utilize up to 2 Kbytes RAM and 32 Kbytes ROM or OTP with our 16-bit MCUs, and up to 1 Kbyte RAM and 32 Kbytes ROM in our 8-bit MCUs, with expanded memory planned for the future. EPROM and ROMless versions are also available.

### **Smallest Packages**

Get all these advantages in the smallest packages on the market. Mitsubishi offers a wide range of packaging options including 64- to 160-pin surface mount packages, with 0.50mm, 0.65mm and 0.80mm lead pitch. Shrink DIPs are available in 32- to 64-pin configurations.

For faster time to market, Mitsubishi provides development support tools for each phase of your product design.

For your best system solution, call Mitsubishi today at (408) 522-7498. For Eastern U.S. and Canada, call (408) 522-7499.

Since 1978, KADAK has provided products, documentation and technical support to those who absolutely insist on the best. It's one reason why more than 1,000 developers have come to count on KADAK for our AMX<sup>™</sup> real-time multitasking kernel and more.

You'll marvel at the comprehensive, simple-to-follow AMX manual that will assist you in the development of virtually any application. You'll also appreciate the

# Count on KADAK

AMX is a trademark of KADAK Products Ltd. All trademarked names are the property of their respective owners

prompt, courteous service you'll receive from KADAK product support people if you should ever need assistance.

All this, plus you will be given source code and automatic software updates for a full year after purchase. And, with AMX, there are no royalties to pay.

For further information on the KADAK Fax: (604) 734-8114

AMX Real-time Multitasking Kernel contact us at our offices. Phone: (604) 734-2796

**EXADAK** KADAK Products Ltd. Setting real-time standards since 1978. 206-1847 West Broadway, Vancouver, BC, Canada, V6J 1Y5

EDITOR-IN-CHIEF/ASSOCIATE PUBLISHER John C. Miklosz, Ph.D., (508) 392-2114

SENIOR EDITORS

Warren Andrews, Computers & Subsystems (508) 283-2102

Barbara Tuck, ASICs & ASIC Design Tools (516) 473-1661

Michael G. Donlin, CAE/CAD Tools (508) 392-2123

Tom Williams, Software & Development Tools (408) 335-5514

> Don Tuite, Integrated Circuits (415) 365-5656

Jeffrey Child, New Product Developments (508) 392-2126

CONTRIBUTING EDITOR Stephan Ohr, Analog & Miixed-Signal (908) 232-1380

> MANAGING EDITOR: Arlyn S. Powell, Jr.

CHIEF COPY EDITOR: Annette M. Staron-Wilson

COPY EDITOR: Kym Wilson Gilhooly

PRESENTATION MANAGER: **Richard Sarno**

EDITORIAL ASSISTANT: Claire Ellis

ART DIRECTOR: Jan Horner

AD TRAFFIC MANAGER: Kelly Rice. (508) 392-2198

**CIRCULATION DIRECTOR:** Robert P. Dromgoole, (918) 832-9213

**CIRCULATION MANAGER:** Paul Westervelt, (918) 832-9287

**REPRINTS:** June Bozarth, (918) 835-3161

PUBLISHER David L. Allen, (508) 392-2111 ASSOCIATE PUBLISHER/

NATIONAL SALES MANAGER: Tim L. Tobeck, (508) 392-2116

Advanced Technology Group Dr. Morris R. Levitt, Senior Vice-President Leslie P. Cypret, Vice-President, Administration One Technology Park Drive P.O. Box 990, Westford, MA 01886 Tel: (508) 692-0700 🛛 Fax: (508) 692-0525 Postmaster: Send change of address form 3579 to COMPUTER DESIGN Circulation Department,

Box 3466, Tulsa, OK 74101

ATTENTION RETAILERS: To carry Computer Design in your store, contact International Periodical Distributors at 1-800-999-1170, ext. 447 (dealer calls only).

**♥BPA**

# Pick up the number one real-time operating system.

# And run with it.

In today's competitive market, it's important to run with the best. And when it comes to real time, the iRMX<sup>®</sup> operating system is the clear favorite.

You see, iRMX has a 13-year track record for proven reliability. In fact, only DOS runs on more X86 systems. Now, iRMX for Windows provides the first real-time operating system with guaranteed response time that runs DOS and standard-mode Windows on the i386<sup>™</sup> and i486<sup>™</sup> architecture. That's right, true real time on a PC<sup>†</sup>

iRMX for Windows brings more than just

affordable hardware to real time. It also gives you a head start on development with access to the huge installed base of DOS applications and tools. In fact, you even have the option to run Windows<sup>††</sup> (including Windows 3.1).

So take the first step, call (800) GET-iRMX (800-438-4769)\* and ask for Lit. Pack. #2B. And start running real time with your favorite DOS and Windows software.

\*Outside the U.S.A and Canada, FAX (503) 696-4633. © 1992 Intel Corporation. iRMX is a registered trademark and i386 and i486 are trademarks of Intel Corporation. †iRMX runs on IBM and Compaq compatible i386 and i486 based PCs. ††All other products shown or mentioned are trademarks or registered trademarks of their respective owners.

### EDITORIAL

Here's my thanks to everyone who helped put the Analog & Mixed-Signal program together.

John C. Miklosz Associate Publisher/ Editor-in-Chief

# We're missing the Halloween party again

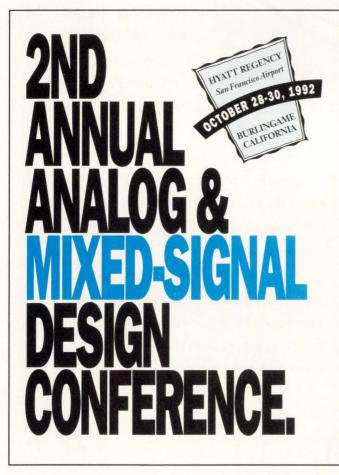

Tradition started a few years ago at the PennWell Advanced Technology Group. When Halloween rolls around, we have an office party where all of the different publications and service departments go all out in a costume and area-decorating competition. As you might guess, *Computer Design* doesn't take competition lightly, and we've gone to great lengths to come out number one. Unfortunately, we couldn't take part in the competition last year, and we'll miss the fun again this year, because the **Analog & Mixed-Signal Design Conference** falls in the last week of October and too many us are away when the costume and decorating work needs to be done. Missing the Halloween festivities and the laurels that we could gather drives us even harder to make sure that the Conference is truly world-class.

Well, October is here again and we think we've put together a great blend of tutorials, lectures and panel discussions for this year's Conference. You can find the details starting on page 57, so I won't reiterate here. What I would like to do is extend my personal thank you to all of the people involved in putting the program together. First, there's Ted Bahr of Miller Freeman, who first approached us with the offer to organize the technical program. It sounds like a cliche but Ted *is* a great guy to work with. Anastasia Kellow, John Huber and Chris McKim have also been great, and we learned a lot from them.

But the Conference wouldn't exist if it weren't for the many individuals and organizations giving their time to put presentations together. I don't have the room here to name everyone, but here's a shot at their company affiliations: AnaCAD, Analog Devices, Analogy, AT&T Bell Laboratories, Brooktree, Burr-Brown, Cadence Design Systems, Contec Microelectronics, Datel, Dazix/Intergraph, Deutsch Research, Elantec, Fujitsu Microelectronics, GEC Plessey Semiconductors, Gould AMI Semiconductors, Harris Semiconductor, International Micro Electronic Products (IMP), Linear Technology, LTX, Mentor Graphics, Micro Linear, MicroSim, National Semiconductor, NCR Microelectronics, Philips/Signetics, Quantic Laboratories, Racal-Redac, SGS-Thomson Microelectronics, Silicon Systems, VLSI Research, and Zeeland Technology.

And who convinced these people that they should give us their time? The credit there, and our thanks, goes to Steve Ohr. You've all become familiar with Steve through his column in *Computer Design* every month, and the select few of you who'll be able to break away from your jobs for three days to attend the Conference will see another side of him when you get the chance to say hello.

And finally, I'd like to thank Patti Kenney, our technical programs coordinator, who took on responsibility for the myriad details that we consider "merely" details and who always reminds us of *our* responsibilities. We'd have a tough time pulling it off without her.

# Front

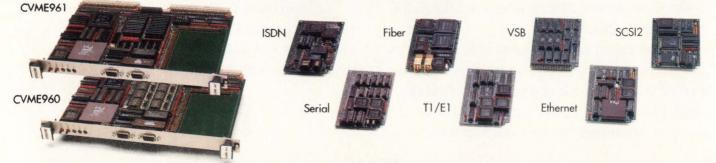

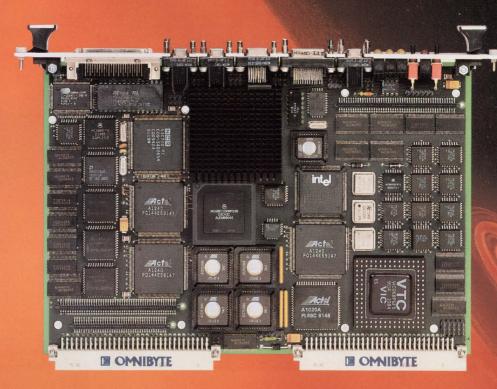

# The New Dual '040 VME SBC: Faster, More Efficient and Lower Cost Than Any Multi-board Solution

Get on-board multiprocessing and an astounding 40 MIPS throughput, when you power your system with Synergy's new SV420 single-slot SBC. The SV420's dual-CPU design means you'll need fewer boards in your VME chassis, with no VMEbus bandwidth bottlenecks between the '040s, and systemwide cost saving of more than 40%.

And even if you don't need multiprocessing right now, the SV420 still puts you out front. Use the second '040 as a super-smart DMA controller. When

Over a dozen smart, powerful I/O modules fit Synergy's '020, '030, '040 and Dual '040 SBC's

combined with the SV420's 66 MByte/sec VME64® circuitry, nothing communicates faster over the VMEbus.

Add even more onboard power by selecting from Synergy's big list of high-performance, intelligent plug-on I/O modules such as our latest Super-VSB module offering

40+ MB/sec over the VSB bus. Or choose another module, from a T1/E1 controller to a super-fast graphics engine, that plugs onto any Synergy SBC.

Better yet, just tell us what you need. We're the company you can talk to about your VME system

design problems. You'll find that we listen and deliver (every Synergy I/O module on our list started as a customer request). We mean business when we say customer support is our most important mission.

So if you want to be out front in system performance, just be up front with Synergy. Call us today.

Synergy Microsystems, Inc. 179 Calle Magdalena, Encinitas, CA 92024 (619) 753-2191 FAX: 619-753-0903

HARPER

# We've just tested the performance of our new i960 CF processor.

Make no mistake. This is no middle-of-the-road processor. It's our new superscalar i960<sup>™</sup> CF chip. And it delivers blistering speed to your high-end printing, imaging, communications and networking applications. Simply put, it outruns every 32-bit embedded processor on

© 1992 Intel Corporation. i960 is a trademark of Intel Corporation.

the market—and we have over 25 benchmarks to prove it.

You see, only our i960 RISC architecture brings superscalar processing with multiple operations per clock to embedded applications. Our new i960 CF processor is highly integrated with optimized data and instruction caches for throughput up to

twice that of our i960 CA chip. Which makes it the most advanced technology available for embedded applications.

If you're already using our i960 CA processor, you can quickly shift up to higher performance with full code and pin compatibility. And, of course, we offer a comprehensive array of Solutions960 development tools to further speed up your design process.

So step on it. Call 800-548-4725 and ask for literature packet A9A50 for complete benchmarks. And learn what your applications can do with a faster engine.

Advanced hardware is just the beginning. Cyclone Microsystems completes the development picture with C and Ada compilers, VxWorks and pSOS+ real time environments, source level debuggers, and a fantastic team of support engineers, waiting to help you create a masterpiece.

ARTFUL///

@ 1992 CYCLONE MICROSYSTEMS INC

25 Science Park, New Haven, CT 06511, Phone: 203-786-5536 Fax: 203-786-5025.

#### TECHNOLOGY VIEWPOINT

# Greg Pope on: Software testophobia

While the United States is the unequivocal leader in the global software market, it's no secret that our software is infested with bugs. The existence of this anomaly is possible only in the absence of serious international competition. Like the automobile industry in the 1950s and 1960s, and the semiconductor industry of the 1970s and 1980s, the American software industry has used its pioneering innovations to sustain a prolonged period of unchallenged and prolific growth.

This period is now over, however. Foreign software developers are beginning to produce high-quality code, so the U.S. software industry must re-evaluate its entire development methodology to retain its competitive edge. If quality doesn't become a priority, the industry will suffer the same fate as the automobile and semiconductor industries.

The issue of software quality transcends the domain of American economic competitiveness and impacts everyone living in an industrialized society. As heirs of the technological revolution, we unwittingly interface with several million lines of software code everyday. Making a phone call, for instance, depends on the existence of over 500,000 lines of reliable software code. Digital alarm clocks, stereo systems, traffic signals, aviation equipment, medical devices, televisions, and automatic braking systems all rely on quality software programs.

The need for reliable, bug-free software, then, is no longer an issue that belongs exclusively in the software testing laboratory. It's an issue that affects our economic position in the global marketplace, as well as our everyday safety and well-being.

### Why do we test?

The development of software applications and programs is a complex, arduous and tedious task, sometimes requiring several hundred thousand lines of software code for a single application. Because software development is still largely a human endeavor,

Greg Pope is the general manager of the test products group at Tiburon Systems, San Jose, CA.

there will be errors. If these errors aren't detected and corrected, they can cause the software to malfunction. Depending on the specific application, a software malfunction can be a minor nuisance or, in the case of systems controlling hazardous materials, result in injury or death.

The demand for efficient and thorough software testing is magnified by the advent of CASE tools, software re-engineering, object-oriented programming, and other automated software development methods. These new tools and methods have let programmers generate an unprecedented amount of code with increasing rapidity. The result is a backlog of software that can't be adequately tested with today's debugging tools and manual methods. Now more than ever, there are profound needs for better automated testing methodologies and increased attention to the importance of software quality.

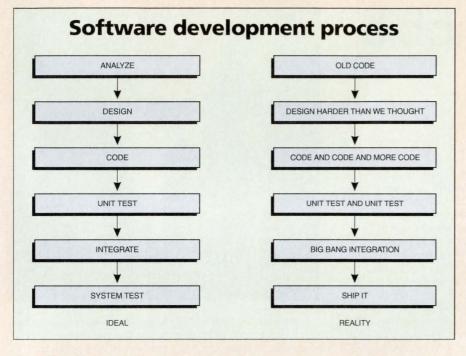

There exists in the American software industry a mythical six-stage software development process, or waterfall model, that's supposed to deliver an adequate project schedule. This schedule is predicated on several beliefs:

- System design requirements will remain frozen over the entire development period,

- Development resources will remain stable, and

- Software will be tested for up to half the period using state-of-the-art debugging tools.

At the completion of this development process, it's believed that the software will be bug-free and ready for market. In the real world, however, software testing is generally regarded as the stepchild of the software development process, rarely receiving the attention it deserves.

### Why don't we test?

Based on the assumption that software can never be perfect, software management has come to accept the notion that incomplete or flawed software is accept-

able. This dangerous line of reasoning is often used by management to compress testing cycles and ensure a timely delivery to market. The result is often defective software and a continual devaluation of the software testing process.

Too often, software testing is relegated to secondclass status in the development process because the system design is always more difficult and complex than originally planned. Additional code and significant design modifications are frequently required. Because the ship date must remain constant, delays in development frequently diminish the softwaretesting phase. The real-world software development process reinforces the all too commonly held assumption that software testing is inconsequential, an impediment to the development and financial goals of the software vendor.

The demands of a crowded and competitive marketplace require software vendors to deliver their products in a timely fashion. Because delays in ship dates can be devastating to a company's market share, management has come to accept the short-term solution of shipping incomplete and buggy software.

Beta testing and early adopter programs are often used as a substitute for thorough system testing, creating the potential for defects to go undetected. While beta testing was originally conceived as a method for evaluating the customer's software preferences, it has now grown into a bug detection methodology. The problem, however, is that a corporate beta tester rarely has the time to significantly evaluate the product; when bugs are detected, the user usually gets frustrated and discontinues evaluating the product without forwarding the relevant information to the test engineer.

Defective software is knowingly shipped by most software vendors with the assumption that fixes and repairs will occur in the next version of the product. If software vendors are unable to make the necessary

> repairs in the current version, one wonders how they will find time to make them in the next version.

> Yet the most insidious explanation for the prevalence of defective software is a complacent and undemanding software consumer. For whatever reason, users perpetuate the existence of software bugs by continually purchasing defective and incomplete products. We commonly accept the excuse that the "computer went down" as the scapegoat for what is really human incompetence or greed.

> The short-sighted practice of shipping defective software isn't without its consequences. Increased demand for customer support, angry customers, costly post-ship bug fixes, loss of market share, decreased stock value, merger/acquisition, and bankruptcy are all

potential effects of adopting a software development philosophy that views testing as a dispensable impediment to corporate success.

### Software "testophobia"

The software industry suffers from what I call "testophobia," an exaggerated, usually illogical fear of testing. Its symptoms include technical and business maladies. Test engineers who suffer from testophobia generally believe that bug repairs generate additional defects, creating a vicious cycle that perpetuates itself ad infinitum. Based on the myth that software testing can never be sufficient, these engineers experience a feeling of hopelessness.

Corporations whose software development teams suffer from testophobia experience late product deliveries, budget overruns, lost market share and profits, and a loss of user confidence. These symptoms, while not in themselves catastrophic, can collectively bring about the demise of any software vendor—witness the fall of Ashton-Tate.

Many of the causes of testophobia are rooted in an incomplete understanding of software testing methodologies and requirements. This misunderstanding proliferates among management because test engineers are perceived as a police force, a group that stands outside the software development process. The test group doesn't receive necessary management support because it's viewed as a bunch of spoilers that causes shipping delays.

Testophobia exists within the test group because comprehensive test designs and test tools are lacking. This factor, coupled with unrealistic test schedules and constant time-to-market pressure, creates a pessimistic test environment that often results in inadequate testing procedures and methodologies.

### Cures for testophobia

Like other phobias, the only way to overcome testophobia is to desensitize the patient by slowly exposing him or her to the thing feared. With software testophobia, this means the entire industry must begin to actively confront the issue of software quality and its related testing assumptions, methodologies and tools. This desensitization process begins when the testophobic community acknowledges that the quality of American software is inadequate, and the only means to maintain existing global market share is to make testing an integrated part of the development process.

The software consumer must also become a part of this process. Consumers, on the whole, don't accept inferior, untested and incomplete products. It's unlikely that someone would purchase an automobile whose clutch was inoperable or a vehicle that won't include windows and upholstery until next year's model is available. Likewise, it would be inappropriate for a pharmacist to dispense drugs that haven't been completely tested. How about discounted airfares on experimental aircraft? When the consumer attitude toward software quality begins to change, the software vendors will make quality a priority.

Borland International (Scotts Valley, CA), a company that's made a concerted effort to produce highquality software, has implemented a bounty game in which employees are paid significant cash awards for uncovering bugs in soon-to-be-released products. While this isn't an alternative to testing, it creates an environment that reinforces the importance of developing high-quality products.

Another solution that is currently gaining in popularity is harnessing the power of automated softwaretesting tools. If we use these tools to execute the more laborious and time-consuming tests, then test engineers will have more time to create the intelligent test cases that are necessary to produce better software.

The development of a legally binding definition of "reasonable" testing by industry experts and lawyers could provide consumers with a warranty that ensures the delivery of reliable, bug-free software. A related solution would be the creation of a center for software excellence, where all types of software can be independently tested and evaluated.

If we fear things in proportion to our ignorance of them, then it must be said that we are excessively ignorant about software testing issues. Fortunately, testophobia is not a permanent disorder. With a concerted educational effort, we can overcome our fear of testing and sustain our global dominance in the software market. Perhaps it's time to challenge ourselves to produce defect-free software within five years, before the offshore competition emerges with products that capture the lion's share of the market. There's nothing to be feared other than our own complacency.

80% of Fortune 500 companies are exploring neural networks."

Do they know something that you don't?

# DYNAMIND" 3.0

Everything you need to understand, build and use neural networks.

\$145

- · Multiple training algorithms-Back Prop, Madaline III and TrueTime" recurrent networks for forecasting

- Up to 8,000 inputs & outputs

- Up to 5,000 neurons per layer · Extensive control of network

- parameters

- · Remove Learned Patterns training option speeds up training

- · Diagnostic, menu-driven interface

- · Example-based User's Guide

- Mouse/keystroke access to

- **On-Line** Help

The complete solution for developing neural-network-based applications.

- · Bundles DynaMind 3.0 with NeuroLink", a library of neural network C-code routines

- · Embed run-time neural networks · Link multiple networks

- Create DFT neural networks

- Modularize complex problemsPrototype the Intel 80170NX neural network chip

- · No run-time license fee

- Compiles under Borland C 2.0 and Borland C++

# Free Brochure 1-800-747-3531

NEURODYNAMX, INC. • P.O. BOX 323 BOULDER, CO 80306 • FAX 303/442-2854

**CIRCLE NO. 17** COMPUTER DESIGN OCTOBER 1992 27

# Synchronous 4Mb At 100MHz,

CARGHER BRAM

# Cached DRAM. t Screams.

Matching low-cost DRAM technology with today's high-speed CPUs can be a design engineer's nightmare. Until now. Introducing the 100MHz 4Mb Cached DRAM from Mitsubishi.

# FIRST SYNCHRONOUS DRAM

Mitsubishi combined a fast, 4K x 4 SRAM and a 1M x 4 DRAM with a wide, 16 x 4 bit internal bus and a synchronous clock design, all into one tiny TSOP IC. The result is the industry's first synchronous DRAM with on-board cache.

# **100MHz OPERATION**

The Cached DRAM's large, 16 x 4 bit internal data path can transfer a 16-line data block in just one cycle, allowing the small on-chip cache to perform like a much larger external cache. The result is fast, 100MHz performance at a much lower cost than separate cache configurations. Plus, the Cached DRAM's fast copy-back scheme significantly reduces the miss cycle penalty time.

# COST-EFFICIENT, SMALL SIZE

The Cached DRAM die and package are only 7% larger than those of a standard 1M x 4 DRAM. And, since they are manufactured with the same process and on the same production line as Mitsubishi's standard 4Mb DRAMs, Cached DRAMs are highly cost-efficient to manufacture.

# LOW POWER OPERATION

With a clock that can be stopped to reduce power consumption to as low as 1mW, the Cached DRAM is ideal for portable and highly integrated applications where low power consumption, compact size and fast operation are essential.

### MITSUBISHI'S CACHED DRAM PERFORMANCE

| Part<br>Number | Cache Hit<br>Access/Cycle | Cache Miss<br>Access/Cycle | Direct Array<br>Access/Cycle | Package |

|----------------|---------------------------|----------------------------|------------------------------|---------|

| M5M44409TP-10  | 10ns/10ns                 | 70ns/280ns*                | 70ns/140ns                   | TSOP**  |

| M5M44409TP-15  | 15ns/15ns                 | 75ns/300ns*                | 75ns/150ns                   | TSOP**  |

| M5M44409TP-20  | 20ns/20ns                 | 80ns/320ns*                | 80ns/160ns                   | TSOP**  |

\*Cache hit cycles can resume after one miss access time, while the copy-back completes in the background.

\*\*TSOP Type II. Also available in reverse pin-out TSOP.

Not your ordinary nextgeneration DRAM, Mitsubishi's 4Mb synchronous

Standard 4Mb DRAM. Actual size

4Mb Cached DRAM

is only 7% larger than a standard 4Mb DRAM.

Cached DRAM sets a totally new standard for cost-effective, high performance memory. For more information and technical specifications, please call (408) 730-5900, ext. 2106 or 2226.

Availab

TECHNOLOGYCTIONS

COMPUTERS & SUBSYSTEMS

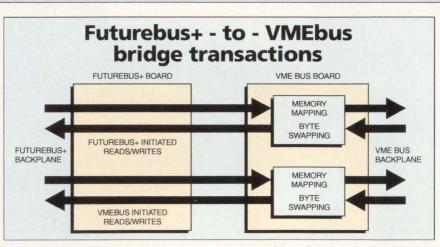

CCT is offering the first Futurebus+-to-VMEbus bridge, comprising two boards: a 12-SU Futurebus+ card and a 6U VME card. The boards provide the essential link between the two buses, offering Futurebus+ systems much needed I/O. The bridge allows multicage distributed processing, shared memory structures between cages and Futurebus+ access to any existing VMEbus I/O devices. With the bridge, the Futurebus+ system can become a master on the VMEbus system, and vice versa.

# First Futurebus+ -to-VME bridge board appears

Warren Andrews, Senior Editor

uturebus+ is just starting to see some commercial success, but it's still far from critical mass in terms of available products—particularly I/O products. To fill the gap, Cable and Computer Technology (CCT—Anaheim, CA) has released the first commercial Futurebus+-to-VMEbus bridge.

The company's timing is perfect. Digital Equipment Corporation (Maynard, MA) has already announced its Alpha-based workstation in a Profile B Futurebus+ format, which is expected to ship later this year. This may well be the first commercial system on the market, and purchasers will be hard-pressed to find any real I/O boards other than those supplied by Digital.

#### Some standard boards available

Thanks to the Navy's Next Generation Computer Resources (NGCR) project, there are a handful of standard Futurebus+ boards announced or available, but they're CPU boards or other hardware designed expressly for military use. In addition, since the initial NGCR contract was awarded before completion of the Futurebus+ specification, it calls for the original soft metric form factor, leading to boards that won't work in a 12-SU rack.

This potential deficiency in Futurebus+ 1/0 boards, however, was anticipated early in the definition of the bus, and a bridge specification has been in the works for more than a year. This document is now in draft stage, as 1014.1. In addition, it's been Digital's strategy from the beginning to provide users with 1/0 through a bridge to another bus specifically VME.

Digital has had little to say about making deals with third-party developers of bridge products like CCT, but it has certainly been in the forefront when it comes to sampling existing boards. Early hints of this interest could be seen when Digital tried most of the existing Futurebus+ cards in its own backplanes. While the company hasn't published any results of the tests it conducted, it did indicate it was able to get CCT's 68030 processor board up and running in minutes. No statement was made about the other boards tested.

"The Futurebus+-to-VMEbus bridge uses the same interface as the single-board computer we tested [CCT's 68030 board], and we have complete confidence in the implementation of the bridge product [made by CCT]," says Digital's Futurebus+ marketing manager, Steve Justus. This means Digital will be able to offer VME-based I/O to its customers. But perhaps more important, says CCT product line director of Futurebus Bruce Kimble, "It clearly shows the soundness of the Futurebus+ specification and demonstrates that manufacturers working independently of each other can produce boards that work together on the same backplane."

While Digital is gearing up to ship its Futurebus+-based workstation, CCT is providing the first Futurebus+-to-VME bridge board, promising a link between existing VME crates and the emerging world of Futurebus+. Even before the bridge specification has been completed, CCT has released its FBB-001 interconnection strategy.

The bridge specification, originally part of the Revision D upgrade of the 1014 VMEbus definition (on its way to becoming 1014.1), isn't expected to surmount the final obstacles in the standardization process until late this year or early next, but CCT's Kimble believes the existing document is tight enough to design a product around now. If minor changes appear in the specification, he says that they can be accommodated with only small changes to the board set.

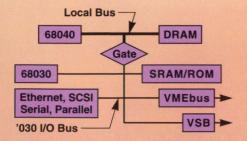

#### A and B connections

CCT's bridge lets any Futurebus+ Profile A or B system connect directly to standard VME devices. Either the Futurebus+ or VME system can be configured as a coprocessor in the overall design, or either can serve as the only processor on the other system. No other processor or system controller is required to make CCT's product work; the VME board that's part of the bridge performs the Slot 0 controller functions.

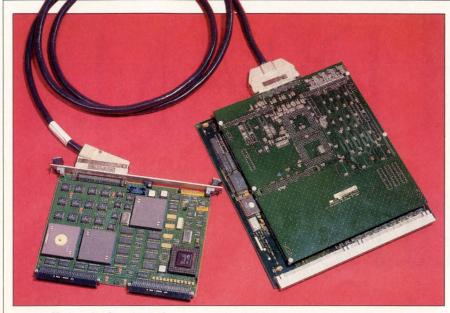

The bridge comprises two boards,

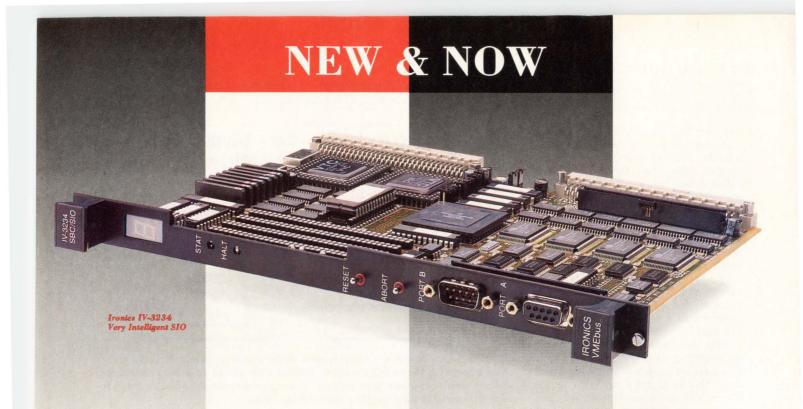

# 40 MIPS SIO, 16 Ports, Free '030

Finally, a smart SIO board that puts the intelligence where it really counts: on the serial communications controllers. *A full 40 MIPS worth!*

The result? *Processor power to spare!* The on-board 68030 is free because each channel has its own DMA and 16 byte FIFO controlled by a RISC core. With all 32 channels operating simultaneously at 64-Kbits/ second, over 95% of the main CPU's bandwidth is still available. Now that's intelligent!

The Ironics IV-3234 is not only smart, it's flexible. Standard features include synchronous and asynchronous modes, 1 or

4 MBytes of fast DRAM, and the most powerful VME interface in the industry. SCSI/Ethernet, VSB, and additional higher speed SIO ports (up to T1 rates) are optional. Choose from among the *best* development environments and real-time kernels.

So make the smartest choice for intelligent SIO...the Ironics IV-3234.

...and now, more SIO in less space with no hassles! Ironics' new Modular SIO system fits 16 ports, with 8-signals and modem controls on every port—in just one VMEbus slot!

Introducing Ironics MODULAR SIO—the most elegant, comprehensive Serial I/O protocol conversion and signal distribution system in the world

# Call our VME Product Hotline Today. 1-800-334-4812

IRONICS INCORPORATED • 798 Cascadilla Street Ithaca, New York 14850 USA • 607-277-4060 Fax 607-272-5787 IV-3234 and Very Intelligent SIO Controller are trademarks of Ironics, Inc. All other brands or products are trademarks of their respective holders.

**CIRCLE NO. 19**

### TECHNOLOGY DIRECTIONS

# COMPUTERS & SUBSYSTEMS

one for the Futurebus+ backplane and another for the VME system. The boards are interconnected with a round, 100-conductor, EMI-shielded cable which lets the two systems be separated by as much as six feet.

### Windowing technique

In operation, a memory windowing technique lets you move information from one system memory to the other. The Futurebus+ system can access memory and I/O in the VME system, for example, while a VME master can access Futurebus+ memory and I/O.

The windowing technique works by mapping memory addresses from the target system's address space onto the initiator's address space. The window size and location is programmable through a set of pagemap registers located on the bridge boards. The bridge permits flexible memory mapping, using a 4-kbyte page size with 8-kbyte page-map registers for Futurebus-to-VMEbus transfers and 32-kbyte page-map

CCT's Futurebus+-to-VMEbus bridge maps a memory address from one bus to the other. Inherent in the memory mapping scheme is the ability to swap bytes around when different processor types are used. The bridge also permits multiple crates to be tied together in a star or daisy-chain configuration.

registers for VMEbus-to-Futurebus+ transfers. The memory-mapped architecture also allows byte swapping when needed.

When a processor performs a ran-

dom-access read or write to an address within the window, the read or write is translated by the bridge board from its address space into a read or write on the target system.

reprints

Reprints of any article or advertisement appearing in *Computer Design* may be ordered from: June Bozarth, CSR Reprints, **PennWell Publishing Company**, P.O. Box 1260, Tulsa, Oklahoma, 74101, 1-800-331-4463 or 918-835-3161 Ext. 379.

Minimum order: 100 black and white copies, 500 four-color copies.

# TI's 7.5-ns '22V10. For those times you're torn between profit and performance.

rying to get the best performance on a tight budget can create a few hang-ups. Texas Instruments has a simple solution. Introducing the TIBPAL22V10-7. TI's newest highperformance programmable logic device that's designed to fit the bottom line as easily as it meets your design specs.

### High performance, low price

While competitive pricing is one of our '22V10's most outstanding features (less than \$17 when you purchase 5,000 or more), you'll be even more impressed by its performance.

At an incredibly fast 7.5 ns, our '22V10 supports system speeds up to 50 MHz with a variable term distribution that gives you more design freedom with complex functions. It's an excellent choice for high-end systems using the latest microprocessors. And since all this is achieved using our proven bipolar process, the '22V10 provides a universal architecture that's easy to work with using familiar design tools.

# Accurate, dependable and available today

Speed and ease of use mean nothing if difficult programming keeps your product from getting to market on time. That's why our '22V10 is designed for quick, dependable programming with your present tools. In fact, we're running at a 99.4% first-time programming success rate.

Best of all, our 7.5-ns '22V10 is available in volume *today* with just-intime and ship-to-stock delivery programs tailored to meet your needs. You'll also have the backing of our © 1992 TI 08-1287 global support network to help keep things running smoothly.