\*

6

0

# GOMPUTER DESIGN

## DATA COMMUNICATIONS

LASER PAGE PRINTERS FACE NEW COMPETITION

BIPOLAR BLOCKS STACK UP TO HIGH PERFORMANCE

MULTIBUS II OFFERS FLEXIBILITY FOR MULTIPROCESSOR DESIGNS

0

靈

0

\*

0

# AMD YOUR CRT.

AMD's CRT controller family wrings every last drop of performance out of your video screen. You get a dazzling, attractive display your customers will find irresistible.

## The Am8052. You'll wonder where the flicker went.

Thanks to on-board DMA and triple row buffers, you get vertical and horizontal split screens, with smooth-scrolling windows. All flicker-free.

You even get double-height and doublewidth characters, superscripts and subscripts.

## The Am8152A/53A. Make your display look its sparkling best.

You get cleaner, crispier characters with the 100MHz video system controller. And proportional spacing down to two pixels.

No other VLSI chip set gives you as much. And to top it off, the chips even take over many of the functions of the CPU. Like linked list manipulation for easier editing. Your CPU has better things to do.

## We'll put you as far ahead of the competition as we are.

Controllers. Bipolar and MOS microprocessors. Communication circuits. Signal processors. Nobody makes as many peripherals for as many microprocessors as AMD.

And every single chip meets or exceeds the International Standard of Quality.

If you want the most out of your tube, put the squeeze on AMD. We'll show

you several ways to put the sparkle in your customer's smile.

(408) 749-5000, outside California, call toll-free (800) 538-8450, Ext. 5000.

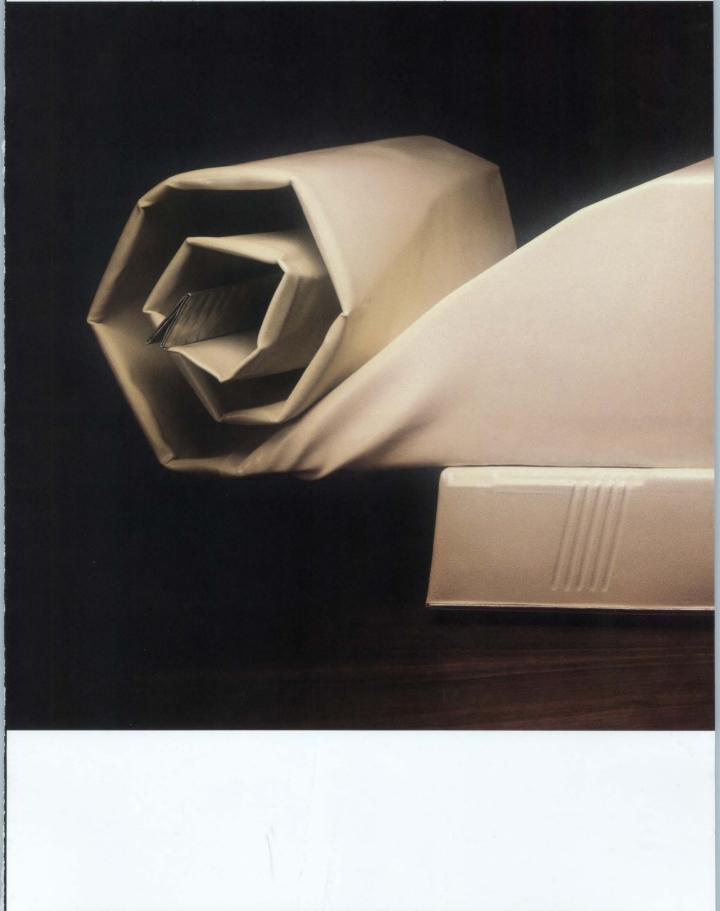

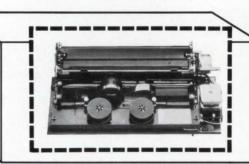

## **Beautiful Streamer**

Kennedy proudly announces Model 9600, the first member of a new family of advanced low cost formatted tape drives. A few of its many features include; Autoload; 800/1600 CPI dual density; streaming capability of 100 ips; a capstan motor which provides an amazing 45 ips true start/stop mode; PC boards which may be moved or replaced in any order on a common bus for upgrading to higher performance levels or different interfaces the list, fortunately, goes on and on. Write or <u>call today</u>.

An Allegheny International Company 1600 Shamrock Ave., Monrovia, CA 91016 (818) 357-8831 • ITT TELEX 472-0116 KENNEDY

## KENNEDY · GUALITY · COUNT ON IT

# **COMPUTER DESIGN**<sup>®</sup>

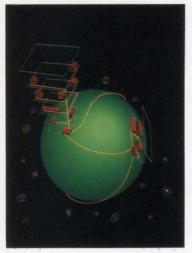

This month's cover was designed and illustrated at Coddbarrett Associates using a DICOMED D-38 design station and a D-48 high resolution film recorder.

## SPECIAL REPORT ON DATA COMMUNICATIONS

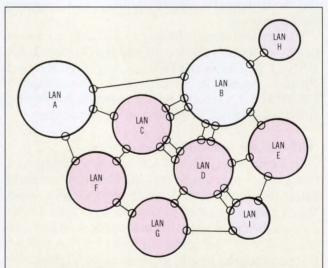

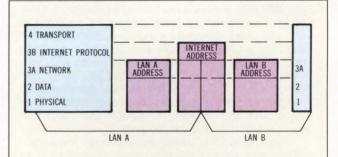

- **97** Network interconnection has become a software-intensive activity in data communications. As more local area networks are created, more opportunities arise for software solutions that tie LANs to wide area networks. Each new opportunity, in turn, presents a new challenge for the network designer. This special report explores the latest frontiers in network design.

- **99 LANs team up to widen the network connection** The next step in creating a global network is developing protocols to match those of different local area networks.

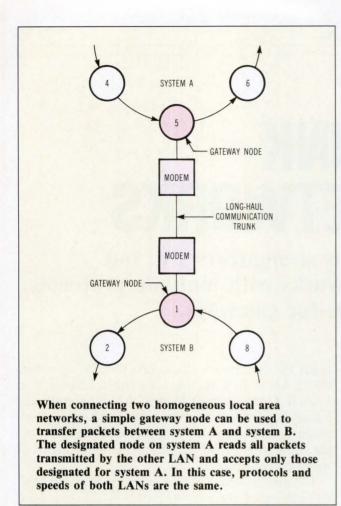

#### 125 Gateways link assorted networks

Connecting identical networks is straightforward, but handling different types of networks with multiple protocols, priorities, and multiplexing calls for gateways.

- **137 X.25 standard simplifies linking of different LANs** Interconnecting with the X.25 protocol allows networks to encompass different local area network configurations in wide area, packet-switching systems.

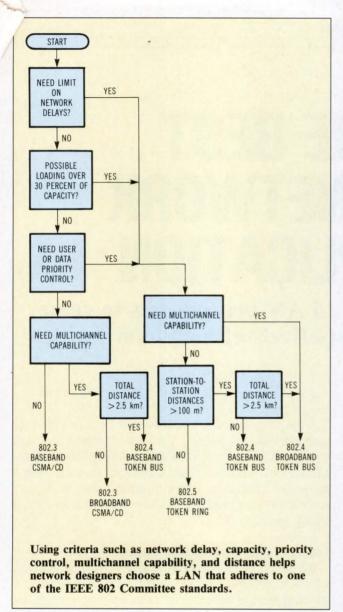

- **143** Choosing the best local area network for any application Regardless of the application, a LAN that adheres to some standard provides the most cost-effective, long-term approach to networking.

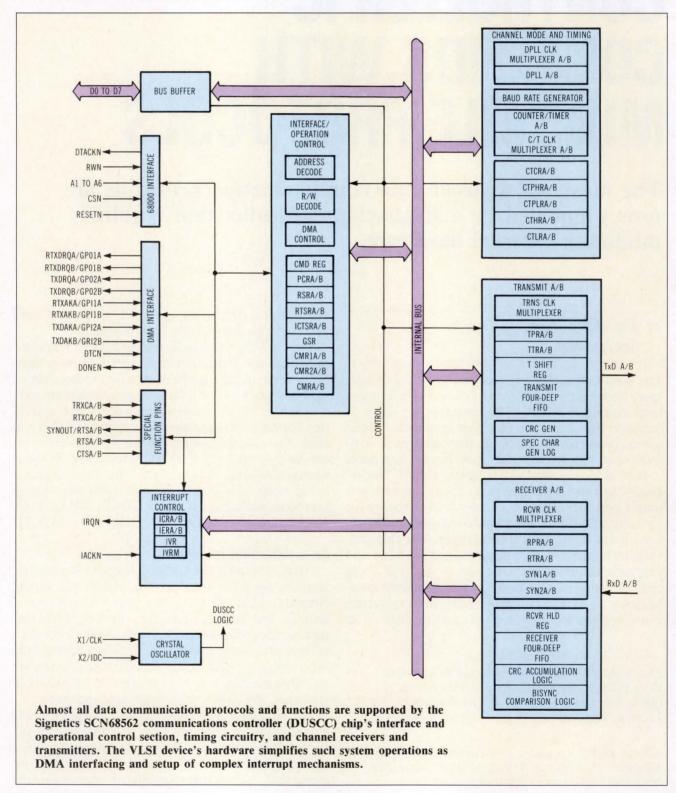

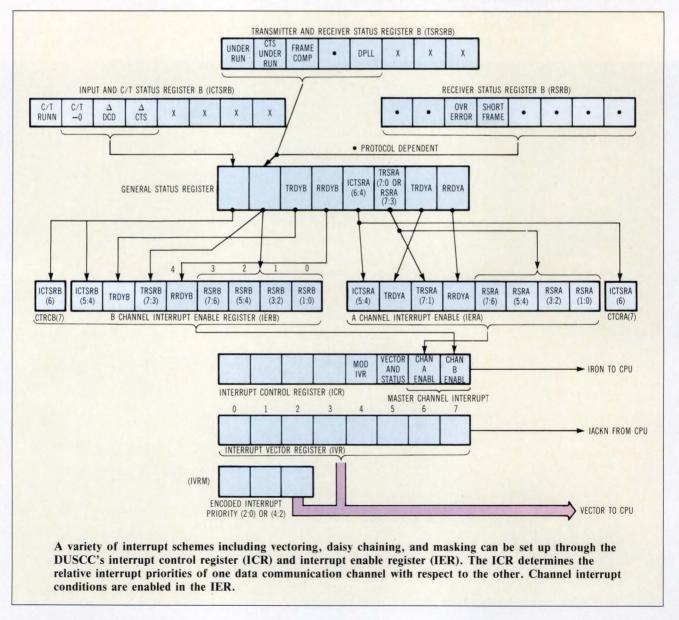

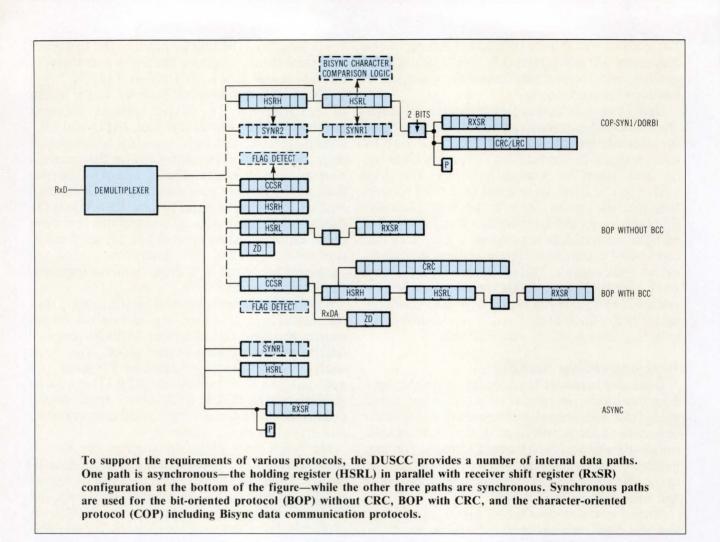

- **151** Controller IC contends with multiple protocols The most widely used data communication protocols are now supported by a single-chip controller that requires minimum external hardware.

## SYSTEM TECHNOLOGY

- 33 Peripherals: Options multiply for nonimpact page printers

- 46 Integrated circuits: DoD struggles to balance IC reliability and price

- 52 Integrated circuits: Standardization effort focuses on interchange of design data

- 65 Test & development: Changes in CAE/CAD requirements affect workstation design

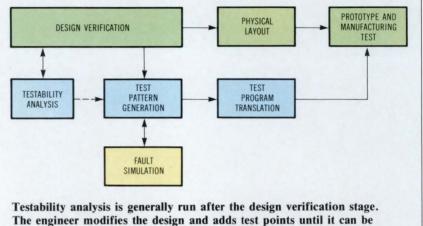

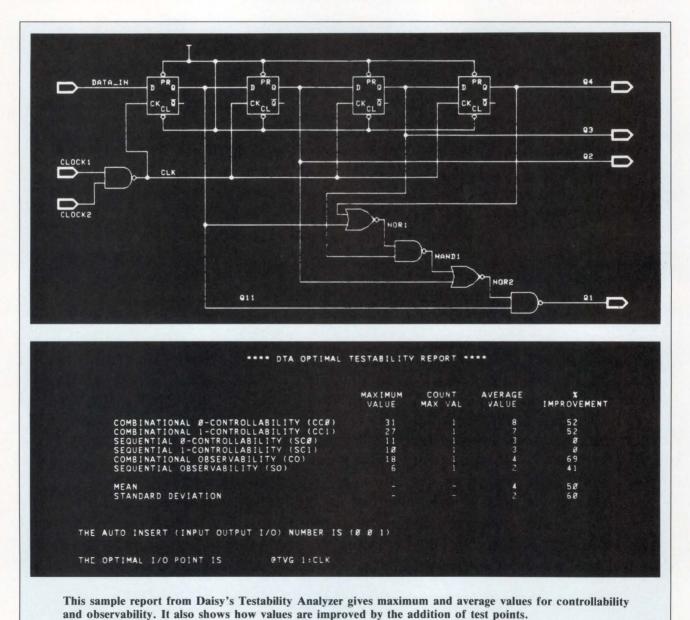

- 76 Test & development: Testability analysis becomes commonplace in CAE environment

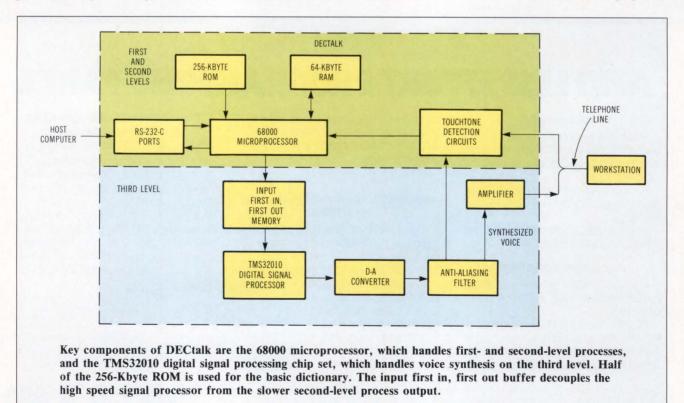

- 86 Control & automation: Voice output systems make it hard to distinguish real from synthetic

Page 46

Vol 24, No. 2

Feb 1985

Page 161

## SYSTEM DESIGN

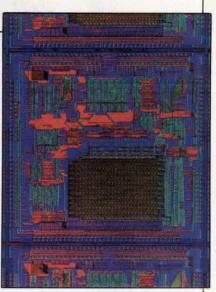

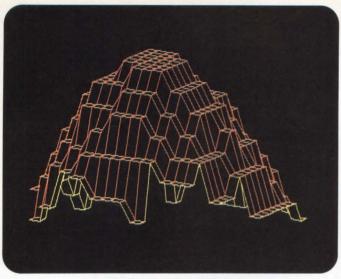

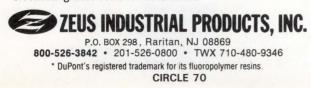

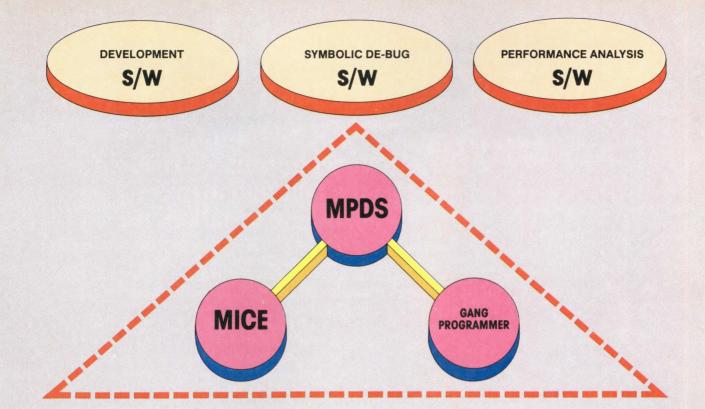

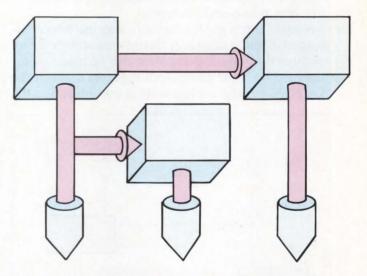

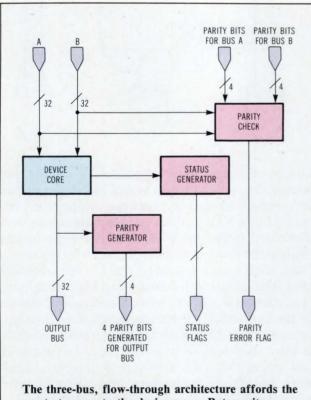

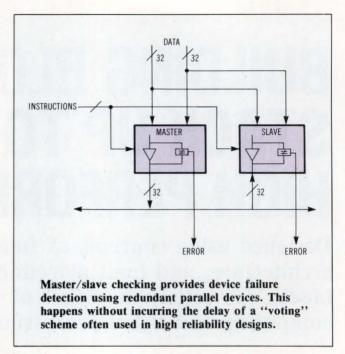

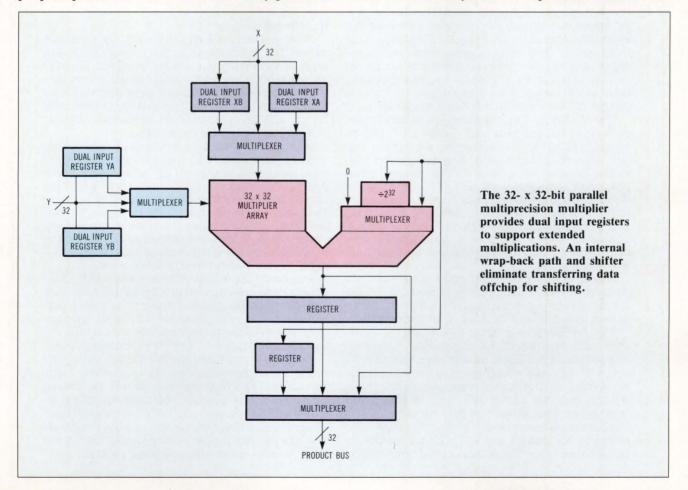

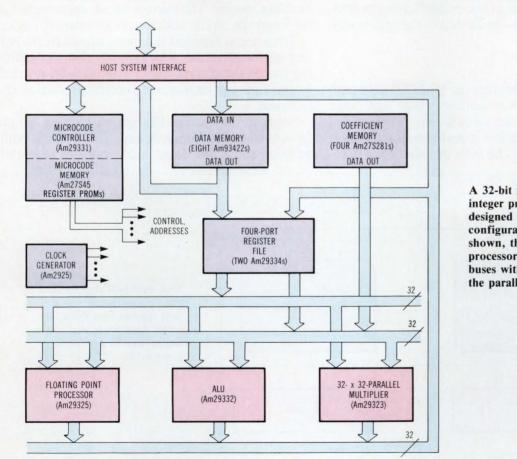

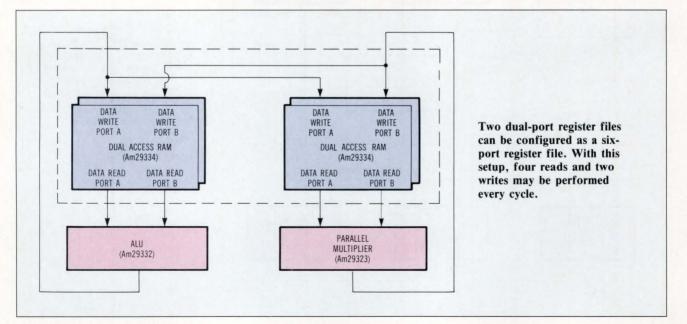

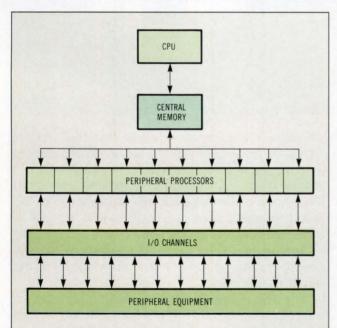

- **161** Integrated circuits: **Building blocks stack up to high performance** Designed using concepts of functional partitioning, three-bus architectures, and fault detection, a family of 32-bit building blocks can satisfy the needs of both general-purpose computing and signal processing.

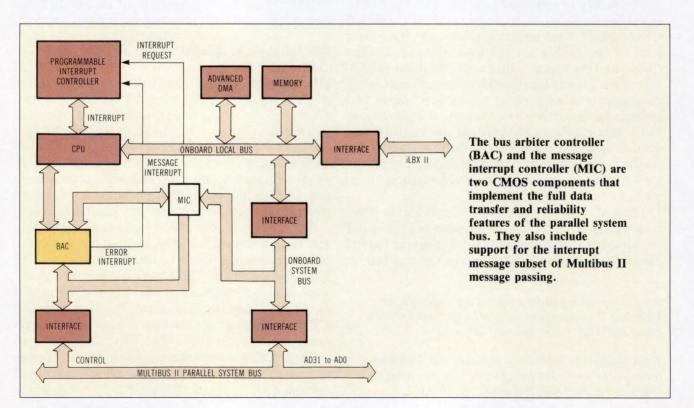

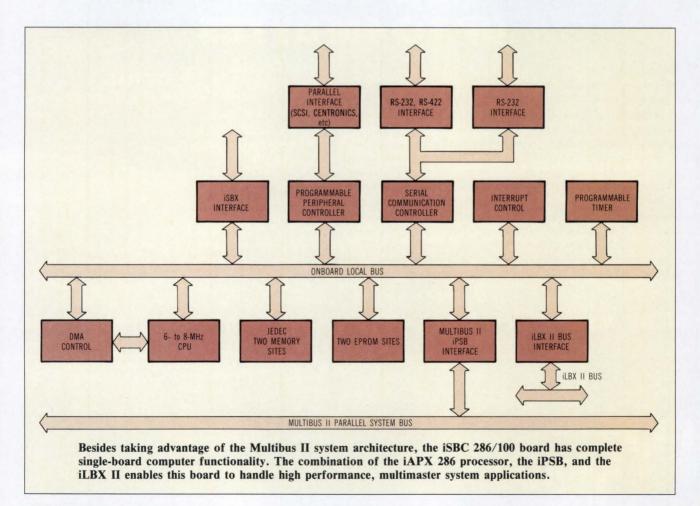

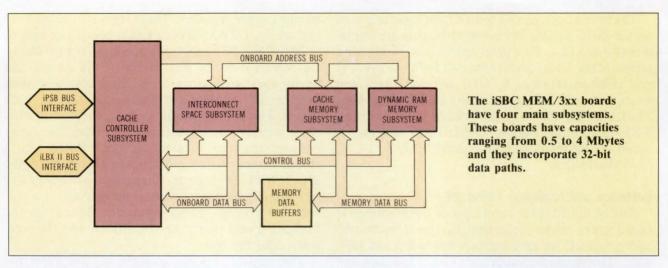

- 171 Interface: Multibus II designs exploit advanced bus concepts With several bus architectures available, designers face the problem of choosing one that provides the features and flexibility needed for new multiprocessor designs.

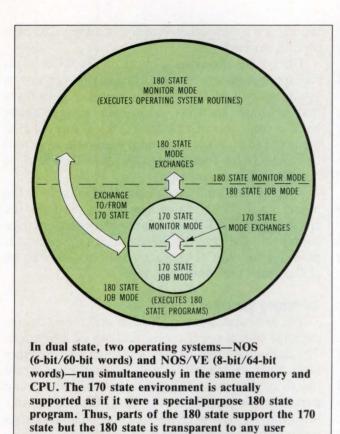

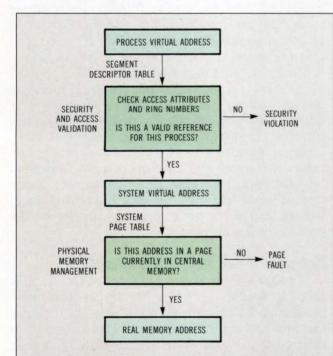

- **181** Computers: Computers tailored to efficient expansion Sharing utilities and applications as well as automatic code and data segmentation can give today's user needed power. Future computing, however, requires virtual machines that can handle multistate architectures.

## SYSTEM COMPONENTS

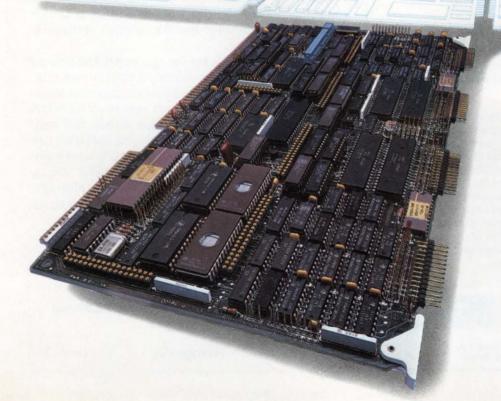

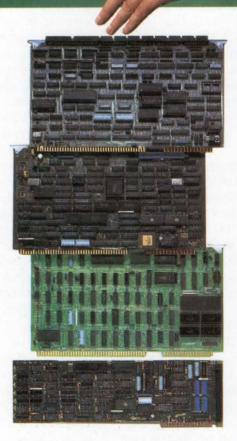

- 187 Computers: Range of configurations marks Multibus microcomputer

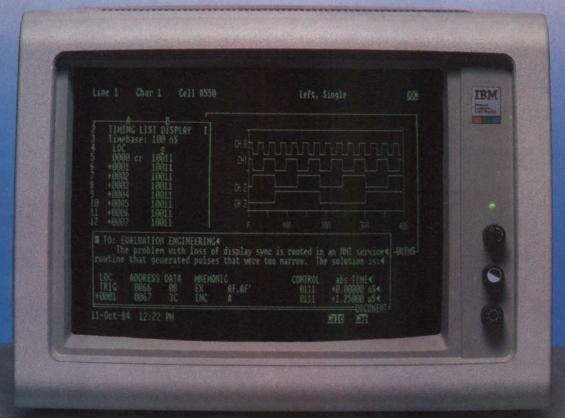

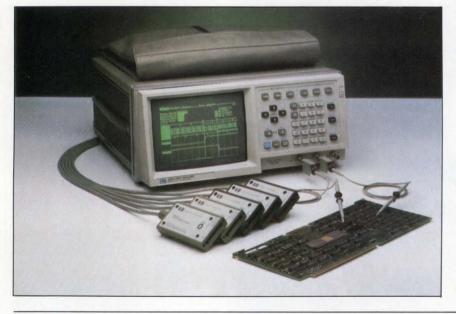

- **188 Test & development:** Logic analyzer furnishes two oscilloscope channels

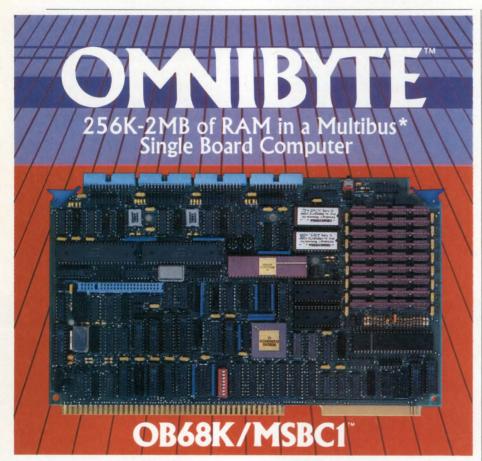

- **188** Microprocessors/microcomputers: Single-board supermicro handles 32-bit processing

- **190 Data communications:** Systems link PCs to LANs and mainframes

- **190 Peripherals:** Full-screen EL panel stirs up display waters

- **191 Peripherals:** Advanced touch screens expand input options

## DEPARTMENTS

- 5 Up front

- 13 Editorial

- 25 Letters to the editor

- 207 Literature

- 209 Market forecasts

- 210 Calendar

- 211 Designer's bookcase

- 212 System showcase

- 214 Advertisers' index

- 216 Recruitment

- 217 Reader inquiry card

- 217 Change of address card

POSTMASTER: CHANGE OF ADDRESS FORM 3579 to be sent to COMPUTER DESIGN, Circulation Department, P.O. Box 593, Littleton, MA 01460 (UPS 127-340).

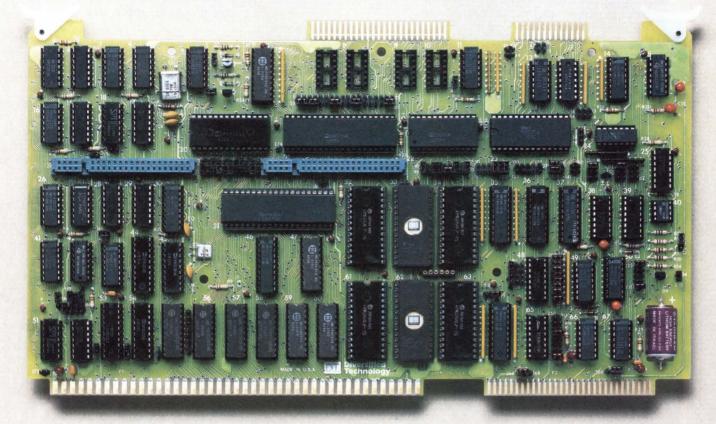

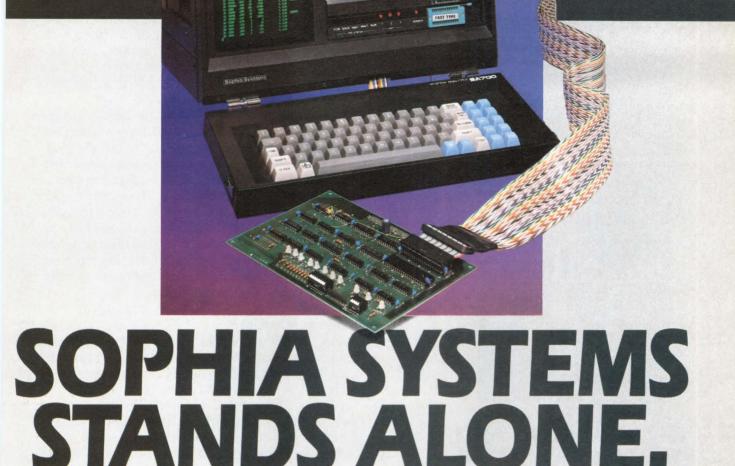

# California Serfboard

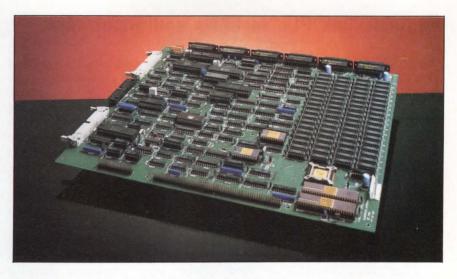

The versatile California Serfboard, MCS-1062, is the first serial I/O controller with eight intelligent slave channels. Plus all the features highlighted below.

That's double the typical capacity in a single cardslot. And the on-board CPU means performance and programmable flexibility that leaves the competition treading water.

#### **Product Highlights:**

- □ Eight individual channels, programmable for ASYNC, SYNC, or BITSYNC.

- □ Programmable timers for ASYNC data rates to 76.8K Baud.

- □ Wide range of modular interface adapters available, each field interchangeable. RS-232, RS-422/RS-423 Optical Current Loop, MIL 188-114.

- □ On-board Intel 8088 CPU. 96K bytes EPROM (using 27128's), 128K bytes RAM.

- □ Simple "handshake" architecture for user software interface.

- □ Dual Port RAM. Supports 8 or 16 bit memory accesses, 24 bit Multibus addressing.

- □ Standard Multibus architecture. One unit load, single card slot, vectored or nonvectored Bus Interrupts.

- Terminal I/0 firmware available. For complete specifications and ordering information, call or write: METACOMP, Inc., 9466 Black Mountain Road, San Diego, California 92126, (619) 578-9840, TWX 910-335-1736

METACOMP SDG. Ask for the hot sheet on the MCS-1062. The California Serfboard.

MCS-1062 is a trademark of METACOMP, Inc. Multibus is a trademark of Intel Corp. © Copyright 1984 METACOMP, Inc., all rights reserved.

## THE MULTIBUS BREAKTHROUGH PEOPLE

## **UP FRONT**

### Silicon Graphics predicts an end to current graphics standards

New workstations may render existing graphics standards obsolete, according to Silicon Graphics founder and chairman James H. Clark. "The problems normally addressed by graphics standards like CORE," the former Stanford University computer science professor pointed out, "involve communication between a graphics terminal and a host." But Clark said he expects that kind of system to be replaced by workstations such as Silicon Graphics' new Iris 2000 series. Built around VLSI "geometry engine" chips, the Iris workstations avoid using bit-mapped graphics in favor of a parallel pipelined architecture that calculates as many as 100,000 vertices/s. As such computationintensive workstations become more common. Clark said he thinks the current tendency to treat graphics protocols as common data structures will give way to lower level graphics primitives. Essentially geometric, these primitives will execute directly on future graphics hardware, such as Silicon Graphics' geometry engine. -W.E.S.

#### Microprocessor operating system standard makes the draft

The much-debated microprocessor operating systems interface standard may finally become official—at least in its basic form. Draft 6.2A will be considered by the IEEE's Standards Board next month. Work continues on language bindings for Pascal, Ada, C, Fortran, Cobol, and PL/M as well as an extension of the standard to handle memory management and device I/O. Computer designers who want to take part or comment on the standard should call MOSI chairman Don L. Jackson at 602/438-3163.-H.H.

### "Hackers' Mac" promises open architecture

Hobbyists and professionals in Palo Alto, Calif are developing a Macintosh-like computer with an open architecture. They hope it will encourage the manufacture of compatible products. The machine, appropriately called the "Hackers' Mac," will not be plug-compatible with the Macintosh, nor will its operating system be identical. It will, however, feature a multichannel DMA port and onboard expansion. The designers intend the architecture and operating system to be sufficiently compatible to allow porting applications from the "Hackers' Mac" to the Macintosh, with only a slight loss of features.—T.R.W.

### Semiconductor startup offers nonvolatile RAM cartridges

A new company with a new idea, Dallas Semiconductor (Dallas, Tex), is offering nonvolatile RAM cartridges that plug into computer memory boards. These cartridges—compatible with JEDEC-standard, 25-pin DIP sockets—can be used for software updates, system configuration, or secondary storage. The first cartridges available will provide 64 Kbytes, 128 Kbytes, or 256 Kbytes of RAM. They will use embedded lithium cells in DIPs to retain memory contents for up to 10 years, according to the company.—R.G.

### **UP FRONT**

#### Superminis battle for supremacy

To maintain their niches in the processing hierarchy, manufacturers of 32-bit computers are tweaking and tuning their machines for higher performance. Data General (Westboro, Mass) plans to push its MV/10000 to 3.5 million instructions per second, while Prime Computer (Natick, Mass) will squeeze 4 MIPS from its model 9955. Not to be outdone, Perkin-Elmer's Computer Systems Div (Oceanport, NJ) just dropped a price/performance bombshell: a 32-bit system based on the 3200 series processor for under \$17,000. At the high end of the series is the 3260 MPS, a tightly coupled 10-processor configuration that adds I/O processors to the CPU/multiple-APU array to gain performance. Another Perkin-Elmer machine, code-named "Cruncher," promises further competition for Digital Equipment Corp's VAX 8600 next month.—*P.K.*

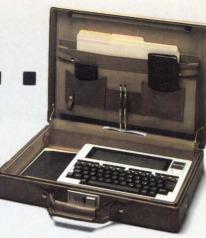

#### Portable applications targeted by 8-bit CMOS CPU

A new CMOS microprocessor from Hitachi America (San Bruno, Calif) aims at powering portable, low power CP/M systems while reducing chip counts and addressing larger memories than current 8-bit CPUs. The 6-MHz HD64180 will incorporate a memory management unit as well as a two-channel DMA controller. The onchip MMU will give the HD64180 direct access to 512 Kbytes of RAM, which can be refreshed by an onchip dynamic refresh circuit. The processor retains object code compatibility with the 8080 and Z80. Twelve additional instructions will provide a sleep mode, an 8-bit multiply with 16-bit result, immediate I/O address-to-register transfers, and block address increment and decrement.—T.R.W.

### **MS-DOS** fever hits minicomputers

It used to be that minicomputer programs were scaled down to run on microcomputers. Now, the reverse is also true. The MS-DOS microcomputer operating system has such an extensive array of application software written for it that new coprocessor systems run MS-DOS software on Digital Equipment Corp's Q-bus and Unibus-based minicomputers. Among the firms providing PDP-11 or VAX hardware to perform this chore are Logicraft (Nashua, NH), Decmation (Santa Clara, Calif), and Virtual Microsystems (Berkeley, Calif). The hardware uses Intel 8086/8088 microprocessors and DOS emulation while running under various DEC operating systems.—H.H.

#### Odd sample sizes no problem for new FFT algorithm

Whitman Engineering of Maitland, Fla has announced a fast Fourier transform algorithm that runs on the IBM PC, Texas Instruments Professional, Apple II, and other personal computers. The algorithm is incorporated in a software package called MADCAP (modular access design, computer aided processing) that includes a synthesizer/signal generator and special-function generators. Company president Joanne Smith describes the MADCAP package as "a signal processing laboratory in software." A special version of the MADCAP (continued on page 8)

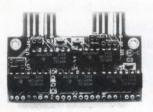

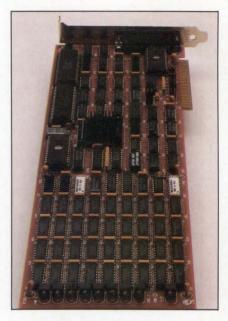

## 200 MB/second!

## World's Fastest Bulk Memory System

It's true. Dataram's WIDE WORD memory system delivers an incredible data rate of 200 MB/sec! Achieved by utilizing 80 or 160 bits per word and four-way interleaving.

Much faster than even the fastest minicomputers can handle...but not too fast for your real-time applications, image processing, array processing or data acquisition needs.

Multi-port capability enables you to bring WIDE WORD speed to your host minicomputer. Simply connect one port to your high-speed input; the other to your mini.

Our library of dedicated interfaces allows you to run with Digital Equipment, Data General, Ampex, Control Data, CSPI, Honeywell, Intel (MULTIBUS), MODCOMP, Motorola (VERSAbus), Perkin-Elmer, ROLM, and SEL. And, possibly even more importantly, we can work with you to develop a custom WIDE WORD interface.

WIDE WORD. 128 MB of high-performance memory in a compact 15<sup>3</sup>⁄<sub>4</sub>" system. Word lengths up to 160 bits. And, of course, a data rate of 200 MB/second.

Our new WIDE WORD brochure will tell you more. And you can have it at no charge by circling the Reader Response Number or calling us at (609) 799-0071.

WIDE WORD is a trademark of Dataram Corporation. MULTIBUS is a registered trademark of Intel Corporation. VERSAbus is a trademark of Motorola, Inc.

TM

## DATARAM

Princeton Road

Cranbury, NJ 08512

(609) 799-0071

TWX: 510-685-2542

CIRCLE 4

#### (continued from page 6)

package serves as a product development system for TI's TMS320 signal processing chip. The new algorithm's main advantage is its ability to process a wide range of sample sizes without distortion. The algorithm also processes a given odd sample size more quickly than other FFTs. Further, the smaller samples reduce memory requirements.—W.E.S.

#### Automation veteran forms CAE firm for mechanical design

Philippe Villers has done it again. The cofounder of Computervision (a manufacturer of computer aided design equipment) and of Automatix (a robotics company) now has created Cognition Corp. This company, temporarily quartered in Burlington, Mass, will develop and produce mechanical computer aided engineering equipment. After September, the company will move to Billerica, Mass, "close enough to Automatix to permit me to get to board meetings," says Villers, who remains chairman of the board of that company. By Villers' definition, CAE is "the preliminary or conceptual design stage, basically analysis and synthesis. It precedes CAD, which is the execution stage. CAE is for engineers, CAD is for designers and draftsmen." Villers says electrical CAE is only about three years old, grosses approximately \$200 million, and is growing at a rate of 70 percent annually. "Mechanical CAE needs to be born," he says, "and it eventually will be even bigger than electrical."—*S.F.S.*

### Digital Research forsakes Unix as 80286 port is validated

AT&T and Intel have validated Digital Research's (Pacific Grove, Calif) port of Unix System V, version 2, for the Intel 80286 microprocessor. The Digital Research version will be marketed by Microport Systems, Inc (Pacific Grove, Calif), a recent spin-off from Digital Research, as well as by Unisoft Systems (Berkeley, Calif) and Interactive Systems (Santa Monica, Calif). The spin-off marks Digital Research's disinvolvement with Unix. The firm reportedly wants to concentrate on the Graphics Environment Manager and its Concurrent DOS series of operating systems.—H.H.

#### Custom chip set to back up MAP standard

Two original supporters of General Motors' Manufacturing Automation Protocol are jointly developing a three-chip set that will implement the IEEE 802.4 token-passing network standard. Concord Data Systems of Waltham, Mass and Gould's AMI Semiconductors (Santa Clara, Calif) say the three-chip set will interface with major 8- and 16-bit microprocessors. The set comprises a data chip with baseband or broadband modem interface, a DMA interface chip, and a protocol controller chip linked by a private bus.—S.F.S.

COMPUTER DESIGN © 1985 (ISSN-0010-4566) is published monthly by PennWell Publishing Company, Advanced Technology Group, 119 Russell St., Littleton, MA 01460. Second-class postage paid at Littleton, MA 01460 and additional mailing offices. COMPUTER DESIGN is distributed without charge to U.S. and W. Europe-based engineers and engineering managers responsible for computer-based equipment and systems design. Subscription rate for others is \$600 in U.S.A. and \$85 elsewhere. Single-copy price is \$6.00 in U.S.A. and \$85.00 elsewhere. Microfilm copies of COMPUTER DESIGN are available and may be purchased from University Microfilms, a Xerox Company, 300 North Zeeb Rd., Ann Arbor, MI 48106. Officers of PennWell Publishing Company, 1421 S. Sheridan, Tulsa, OK 74101; P. C. Lauinger, Chairman; Philip C. Lauinger, Jr., President; Joseph A. Wolking, Executive Vice President; H. Mason Fackert, Carl J. Lawrence, Group Vice Presidents; L. John Ford, Vice President; V. John Maney, Vice President/Finance.

## HIGHER INTELLIGENCE

Could your Discover the develop-

design projects use help from a higher source? newest generation of intelligent microprocessor ment equipment from ZAX Corporation.

#### ZAX intro developmen

duces the first, true 32-bit universal microprocessor

system featuring ZAX ICD-series in-circuit emulators and DIGITAL'S MicroVAX I" super-microcomputer. The ZAX/VAX connec-tion delivers the highest level of power and flexibility by offering professional development systems and software integration products which support both multi-processor and multi-user capabilities, while maintaining full compatibility with larger VAX/VMS computer systems.

To find out more about how to THRUST your design projects to new heights, call the leader in microprocessor development systems —

ZAX Corporation • 800/421-0982 • 714/474-1170

Zax Corporation 2572 White Road. Irvine, California 92714 (714) 474-1170 • 800-421-0982 • TLX 183829

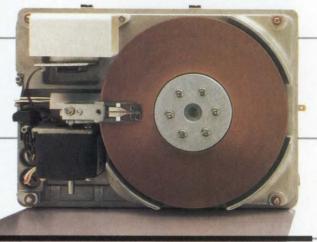

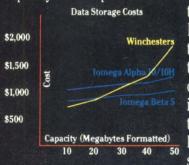

## WHEN IT COMES TO WINCHESTERS, WE RUN CIRCLES AROUND THE COMPETITION.

Tandon's made so many improvements in Winchesters that the rest of

the drive industry is dizzy just trying to keep up. We build a wide range of drives. Open-loop and high performance closed-loop models. In both full and half-height versions ranging from

12.8 to 36.2MB unformatted capacities. All are available in high quantities now, because Tandon's been ramping up capacities at a pace like never before. And we've kept up the pace of improving Winchester performance as well, so

the most advanced technology is ready when you need it.

As far as our current line is concerned, the low-cost TM500 line has become the most reliable full-height 12.8 and 19.1MB drives you can get. The new TM252 half-height 12.8MB surpasses the industry's most critical specifications. And our TM703 has been increased to 36.2MB to make it the ideal high capacity drive for desktop business systems.

Another part of our success revolves around our highly automated plated media plant in Northern California. Its buttoned-down efficiency and technological sophistication guarantee higher quality and higher volume production than ever.

What's more, our proprietary plated media is used in all our Winchesters, no matter what the capacity. It's more durable, more reliable. And it has six times more storage capacity than oxide media. At less than half the cost.

In fact, it's so good, other drive manufacturers are buying their plated media from us.

So all around, Tandon Winchesters have more capacity in less space at less cost. And that's a pretty good circle to run around in.

Tandon Corporation, 20320 Prairie, Chatsworth, CA 91311. (818) 993-6644, TWX: 910-494-1721, Telex: 194794. Regional Sales Offices: Boston (603) 888-8612 • New York (201) 851-2322 • Atlanta (404) 934-0620 • Chicago (312) 530-7401 • Dallas (214) 423-6260 • Irvine (714) 669-9622 • Santa Clara (408) 727-4545 • Kelsterback/ Frankfurt, West Germany 6107-2091, Telex: 411547 • Reading/London, England (0734) 664-676, Telex: 848411. Distributors: Hall-Mark, Kierulff, Schweber,

Gould...Innovation and Quality in Real-time Systems

## THE FIREBREATHERS. Leaders since the beginning of Real-time.

Legends have a way of being based on fact. Gould Firebreathers are legendary in the land of Real-time and our leadership and superiority are no myth.

Gould ignited the Real-time fire two decades ago. Since then, scientific and industrial computer users have been hot on Gould. In the simulation, energy, oil and gas, laboratory and computational markets, Gould Firebreathers are the choice of virtually all the leading companies that implement Real-time systems.

Gould had the first Real-time minicomputer in 1965. We again brought sophisticated Real-time users out of the Dark Ages with the first 32-bit Real-time mini in 1969 and the first supermini in 1975. And we're still the leader in superminicomputer performance. When it works and it's proven, history does repeat itself. Be a part of history in the making. Bring Gould into your Real-time realm. Firebreathing power from the beginning, for today...and tomorrow.

#### Gould Inc.,

**Computer Systems Division**, 6901 West Sunrise Boulevard, Fort Lauderdale, FL 33313 1-800-327-9716.

## FAREWELL TO AN OLD FRIEND

Those of you with a keen eye for detail may have noticed a change on the cover of *Computer Design*. At the beginning of the year, we removed the tag line, "The Magazine of Computer Based Systems," from beneath the magazine's logo. Unfortunately, our old friend who served us faithfully for many years became yet another victim of progress. We can assure you, though, the disappearance of the tag line does not signal any change in the magazine's role. Rather, it is an indication that, while our charter has stayed essentially the same, both the computer and magazine industries have undergone dramatic changes. We shall continue to do what we have always tried to do during 22 years of publication—provide the essential information you need to design better computer systems.

If you are reading your own copy of this magazine and not somebody else's, then you must be either an engineer or engineering manager involved in the design of computer systems. This role for readers of Computer Design never changed. Two things did change, however: the types of computer systems you design and the types of magazines that compete for your attention. Subsystems forming the nucleus of larger computer systems now exist at the chip, board, and box levels. And computer systems are designed and integrated not only by original equipment manufacturers, but also in many other types of organizations such as system houses and sophisticated end users. Furthermore, today's computer systems require both hardware and software design at all stages of the development. Moreover, most systems involve communications, information display, and storage in addition to digital processing.

One fact remains amid all this potential for confusion: wherever real design work must be done, design engineers will be doing it. Hence, the central role of *Computer Design*. While other magazines serve, say, software designers but not hardware designers, or value added resellers but not OEMs we continue to serve the design engineers and their managers wherever and however they design computer systems.

So why was our tag line added and why was it removed? Back in the days when the only processors were mainframes and minicomputers, people sometimes wondered whether *Computer Design* served people who designed computers or people who designed *with*  computers. The answer then, as today, was "both." But, in a sense, the magazine was ahead of its time. Obviously, there was a vast difference between the information needs of engineers who designed circuits at the device level and those who designed complete systems. Therefore, the tag line was added to show that *Computer Design* was aimed at the senior engineers and project managers

who designed at the system level. The development of the microprocessor and related chip-level subsystems, of course, blurred the distinction between system design and design at the component level. More recently, design automation of custom chip-level systems has obliterated any remaining distinctions between digital circuits and digital systems. So, we decided to bid farewell to our old friend the tag line.

Industry trends had conspired to make our tag line both misleading and seemingly arrogant. The line implied that the magazine was devoted only to system integration and not to system design. Also, it implied that it was the *only* magazine serving system integrators. However, during recent years, other magazines have emerged to compete with *Computer Design* in that area—though not in all areas. We think the magazine is unique in other ways, but we can no longer claim to be the only one serving system integrators. We think our uniqueness was better expressed in a longer tag line we have used in promotion pieces aimed at potential advertisers: "The only computer magazine that concentrates on design; the only design magazine that concentrates on computer systems."

Perhaps a new tag line—one that succinctly summarizes our purpose—will replace our old friend. But, for now, we believe that *Computer Design* says it all.

milal Elphil

Michael S. Elphick

## INMOS has natural answers

# High-volume production of our new 80ns how we accelerate your designs.

Some creatures are in their natural element when it comes to speed. It's breeding and conditioning that have enabled them to jump ahead of all other species. Speed is inherent in their sleek, natural design that surfaces with sudden bursts of energy, in play or in flight.

In keeping with the natural design for speed, our new 80ns  $64K \times 1$  DRAM has evolved as the fastest member of our entire high-performance DRAM family. This new DRAM chip is available with 80ns, 100ns or 120ns RAS access times and 130, 160 and 190 cycle times. The part also offers other exceptional features that are common

only to the INMOS DRAM line. CAS-before-RAS refresh, for example, as well as nibble mode are delivered as standard features and at no extra cost. We also furnish a military version of our new 64K DRAM that's qualified to MIL-STD-883C.

Our 16K x 4 DRAM is another outstanding chip in our DRAM selection. You can choose 100ns, 120ns or 150ns access time and count on exceptionally high memory bandwidth. In addition, we offer you our 8K x 8 DRAM with 120ns, 150ns or 200ns access time and pin-1 refresh. Its byte-wide organization can boost the performance of the latest microprocessor system.

## ON Speed. 64K DRAM is just one example of

You'll also get the flexibility in packaging you expect from our capable DRAM family. Anything from low-cost plastic DIPs to ceramic side-brazed editions, including leadless chip carriers.

The point is, it pays to go to the leader where DRAM development, production and delivery are simply faster by nature. To the company that can give you the world's broadest DRAM family line with more choices of speeds and organizations.

If you have questions on which member of our DRAM field can help you win your design race, just ask us.

We'll be quick with in-depth answers that will fill you in on the rest of our picture.

Colorado Springs, CO (303) 630-4000 — TWX 910-920-4904 • Atlanta, GA (404) 475-1936 — TWX 810-751-0015 • Burlington, MA (617) 273-5150 — TWX 710-332-8777 • Baltimore, MD (301) 995-0813 — TWX 710-862-2872 • Minneapolis, MN (612) 831-5626 — TWX 910-576-2740 • Dallas, TX (214) 669-9001 — TWX 910-997-0822 • San Jose, CA (408) 298-1786 — TWX 910-338-2151 • Los Angeles, CA (213) 530-7764 — TWX 910-347-7334 • Bristol, England 0272-290-861 — TLX 851-444723 • France (1) 887-2201 — TLX 201222 • Germany (089) 319-1028 — TLX 522645

inmos. ( and IMS are trademarks of INMOS' Group of Companies.

**CIRCLE 8**

Get the performance benefits of an 11/73 by using Able's Microverter Plus. At the same time, you can hang on to your investment in UNIBUS\* peripherals! You benefit because

- With MICROVERTER PLUS, you can use 18-bit UNIBUS DMA devices with up to 4 mb of Q-Bus memory

- MICROVERTER PLUS is compatible with PDP-11/73, ISI-11/23, and -11/23+ processors

- MICROVERTER PLUS is software transparent to RSTS/E, RSX-11, UNIX,\*\* and DSM\*

- MICROVERTER PLUS can help increase your communication capability

- All at a fraction of the cost of a new system

UPGRADE with a MICROVERTER PLUS from ABLE. Call us toll-free at 800/332-2253 (outside California), or 800/225-3332 (inside California)

ABLE COMPUTER, 3080 Airway Ave., Costa Mesa CA 92626 (714) 979-7030, TWX 910 595-1729, TELEX 668307

\*PDP, UNIBUS and DSM (DEC System M.U.M.P.S.) are trademarks of Digital Equipment Corporation. \*\* UNIX is a trademark of AT&T.

## **5 OR 10 TAP ACTIVE BUFFERED INPUTS AND OUTPUTS**

- LOW PROFILE HERMETIC METAL 14 PIN DIP

- HIGH RELIABILITY THICK FILM HYBRID CONSTRUCTION

- IDEAL FOR HOSTILE ENVIRONMENTS/ MILITARY GRADE COMPONENTS AVAILABLE

- U.S. MANUFACTURED ON AUTOMATED ASSEMBLY AND TEST EQUIPMENT FOR REPEATABILITY

- HIGH MTBF

- COMPLETE STANDARD PRODUCT LINE AND CUSTOM DESIGNS AVAILABLE

FOR MORE INFORMATION CONTACT... JO-ANN RICCI (408) 395-2300 X265

### HYTEK MICROSYSTEMS

980 UNIVERSITY AVENUE LOS GATOS, CA 95030

## **COMPUTER DESIGN**

*Editorial/Executive Offices:* The PennWell Building, Littleton, MA 01460, Tel: (617) 486-9501

Editor in Chief, Michael S. Elphick

Executive Editor, John Miklosz Managing Editor, Sydney F. Shapiro Assistant Managing Editor, Leslie Ann Wheeler Art Director, Emilie Whitcomb Senior Editor, John Bond Senior Editor, Peg Killmon Senior Editor, William E. Suydam, Jr. Senior Associate Editor. Malinda E. Banash Associate Editor, Jack Vaughan Copy Editors, Helen McElwee, Nancy E. Purcell, Leah A. Rappaport, Ann Marie Tisevich Editorial Assistants, Vickie Frechette, Susan M. Wheatley Special Features Editor, James W. Hughes Consulting Editor, Saul B. Dinman New York Field Office: 120 Mineola Blvd, Suite 510, Mineola, NY 11501, Tel: (516) 741-4780 Senior Editor, Nicolas Mokhoff Special Features Editor, Harvey J. Hindin Western Field Office: 540 Weddell Dr, Suite 8 Sunnyvale, CA 94089, Tel: (408) 745-0715 West Coast Managing Editor, Tom Williams Senior Editor, Bill W. Furlow Field Editor, Richard Goering Editorial Assistant, Robin L. Weatherwax Production Director, Linda M. Wright Production Manager, Philip Korn Production Assistant, Elizabeth Mogren Staff Artist, Jay Gordon Technical Art, Designline Ad Traffic Coordinator, Debra L. Stone Printing Services, Padraic Wagoner National Sales Manager, Frederick A. Stanley Circulation Director, Robert P. Dromgoole Business Development Manager, Leslie Ringe Promotion Director, Steve Fedor

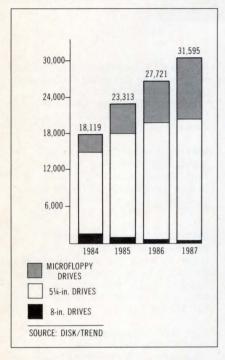

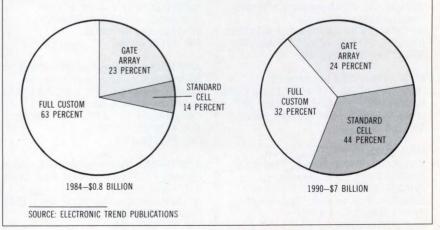

Marketing Services Coordinator, Linda J. Battle

Publisher, Frederic H. Landmann

### **PennWell**

Advanced Technology Group 119 Russell St, Littleton, MA 01460 Tel: (617) 486-9501

H. Mason Fackert, Group Vice President Daniel R. Campbell, Vice Pres. Admin. Kirk S. Campbell, Finance Director John M. Abernathy, MIS/DP Director Patricia M. Armstrong, Admin. Services Mgr.

## Microprocessor programming made simple.

"Keep it simple" was the principle of the 14th Century English philosopher William of Occam and it has even more validity today. Faced with the problems of sophisticated computer systems, designers have found that ever more complex programming languages are further complicating their tasks. Until now.

## Occam. Created for system design and implementation.

When we started designing our new VLSI family of 10-MIP transputers, we built on William's simple philosophy. To take advantage of the possibilities opened up by the transputer, we needed to create a language capable of properly addressing parallelism and multiprocessor systems.

With the ability to describe concurrency (whether timeshared or real) and to handle messagepassing at the lowest level of the language, all aspects of a system can be described, designed and implemented in occam. From interrupt handling through signal processing to screen editors to artificial intelligence. And on.

But occam is not limited to our

transputer family. It provides an efficient, responsive implementation language for systems built on today's microprocessors. It also opens up future possibilities with its performance-enhancing multiprocessor capabilities. And INMOS now offers a product to let you exploit occam's total capability in your system.

## Simplify your job with the Occam Programming System.

The Occam Programming System (OPS) gives you the tools for complete VAX / VMS software development. This package includes an integrated editor / checker, an optimizing VAX compiler and full documentation. This gives you a supportive environment for the development of occam programs

for execution on the VAX. Crosscompilers for 68000 and 8086-based systems will also be available.

What's more, the occam programs developed and proven on the OPS will give you a head start for work with the INMOS transputer. Extensions to the OPS will be available which will allow occam programs to run on the transputer.

And if you have a requirement to program the transputer in other popular high-level languages, other extensions will include compilers for C, Fortran, and Pascal.

#### Get started today.

Contact us for our information pack on occam, the Occam Programming System and the transputer. You'll be surprised how simple your life can be.

For quick response, call us at (303) 630-4000 or write: Occam, P.O. Box 16000, Colorado Springs, CO 80935.

inmos. and occam are trademarks of the Inmos Group of Companies

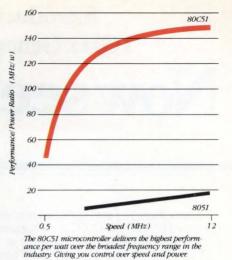

# WE COULDN'T OVERPOWER THE 8051. So we underpowered it.

The Intel 80C51 8-bit microcontroller. Featuring the powerful performance of the world standard 8051, but needing only one-tenth the energy.

The 80C51 is based on Intel's revolutionary CHMOS technology. Achieving the high performance and high integration of HMOS, with the low power advantages of CMOS.

The result is an 8051 pin-compatible microcontroller with the most powerful eight-bit CPU and the highest level of integration available. The 80C51 runs on an incredible 11mA at 8MHz clock frequency. Average power dissipation can be lowered into microamp range, by using one of two new software programmable power control modes. In the power down mode, current drain is 50 microamps.

On the performance side, the 80C51 has a maximum clock rate of 12MHz.The fastest data throughput of any CMOS microcontroller.

Its high integration capabilities include 4K byte ROM and 128 byte RAM, a Boolean Processor able to manipulate 256 individually addressable bits, a versatile serial port and a pair of 16-bit counter/timers.

All this helps to make the 80C51 ideal for high end eight-bit applications ranging from hand-held instruments

© 1984 Intel Corporation

to factory line powered controllers, to portable communications systems. A military version of the 80C51 will be available soon.

The 80C51 also boasts the world standard in development tools. Like the Series II/ICE<sup>™</sup>-51 emulator and the iPDS<sup>™</sup> system/ EMV-51. As well as a relocatable assembler

and high level languages. MCS-51 workshops are available, too. Go with the best. The 80C51. Call toll-free today at (800)538-1876. In California,(800)672-1833. Because now, running with the very

running with the very best requires very little energy.

## Introducing the HP 54100A/D 1GHz General Purpose Digitizing Oscilloscope. **Now see waveforms you've**

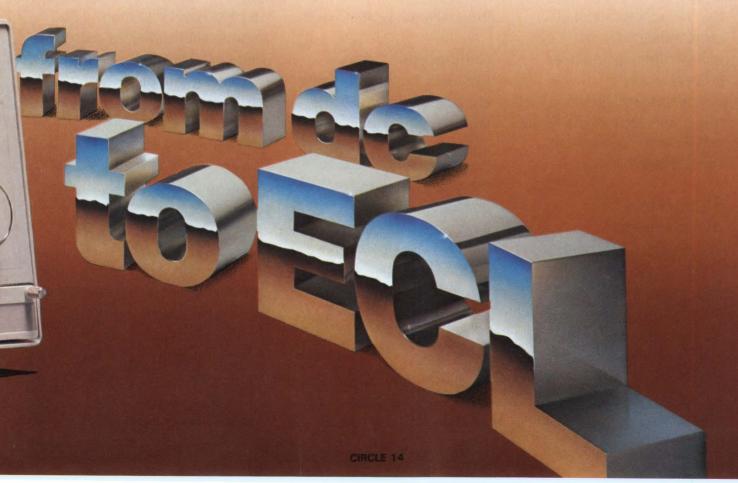

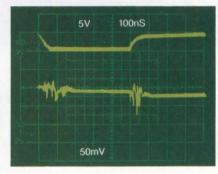

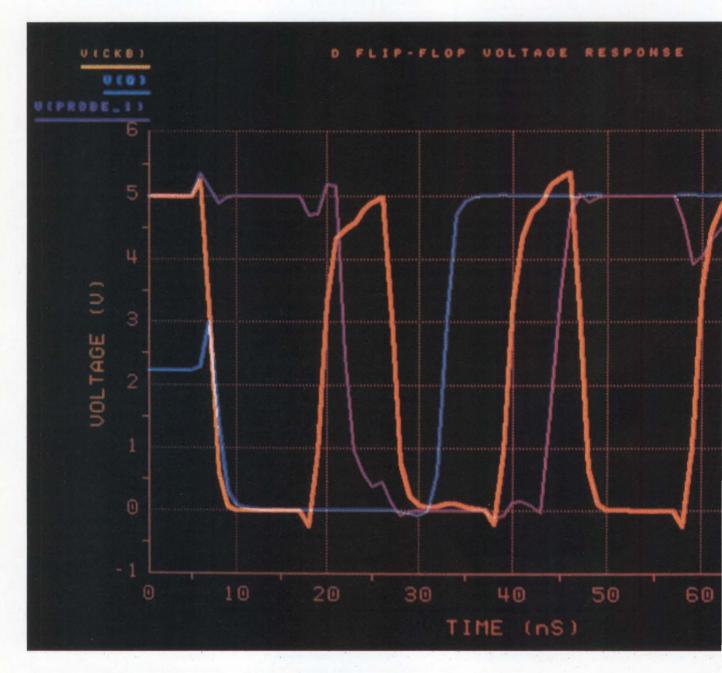

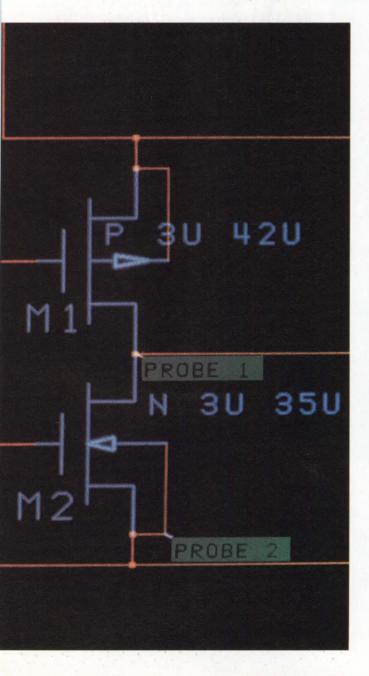

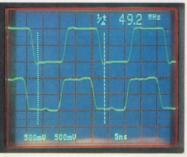

The waveform you see displayed here was captured by the new HP 54100A/D 1 GHz Digitizing Oscilloscope. It shows an intermittent extra pulse at the Q output of a D flip-flop. Plus, it automatically positions the event of interest in the center of the display and shows the events in negative time that led up to the trigger. The new HP 54100A/D can easily capture rare events like this and hold them for you to analyze with no blooming or fading. What's more, you get this with 10 psec resolution and 1 GHz bandwidth necessary to capture subnanosecond transistions in today's high speed logic designs. And it does all this at the touch of a button.

## The first truly general-purpose digitizing scope for dc to ECL.

With logic speeds pushing faster all the time, you. need a scope that can deliver reliable measurement results from dc all the way to ECL. The new HP 54100A/D 1 GHz Digitizing Oscilloscope gives you that versatility. It combines a fast 350 psec rise time with a crystal-controlled timebase, sophisticated onboard analysis firmware, and easily re-configured inputs. It lets you see low duty-cycle signals with clarity and brightness not previously possible. You can even take it out of the lab into production. Make it a vital part of your computer-based ATE test system for even greater productivity and usefulness through HP-IB.

### Complete one-button characterization of your high-speed waveforms.

With the HP 54100A/D Digitizing Oscilloscope, you can be productive as soon as you sit down in front of it. Simple keystroke sequences give you automatic pulse parameter measurements, automatic signal scaling and instrument setup, automatic hardcopy output (over HP-IB) and more. You can trigger on logic patterns,

HP-IB: Not just IEEE-488, but the hardware, documentation and support that delivers the shortest path to a measurement system.

## never seen before.

time-qualified patterns or state, or you can delay the trigger by edge count or absolute time. The HP 54100A/D unloads much of the setup and test burden

from you so you can devote your time to designing.

## Expanded probing capability and convenience.

Designed as a companion product to the HP 54100A/D, the new HP 54300A Dual 8:1 Probe Multiplexer expands your scope's two inputs to a total of 16. Use it as a frontend interface for your production ATE test system or as a bench test system for design characterization in your R&D lab.

## High frequency, high impedance probing.

Whether you're in R&D or production engineering, you know the need for better, more flexible probing schemes. With the HP 54100A/D or the HP 54300A Probe Multiplexer, you can choose from 1 GHz miniature probes, 50 ohm BNC inputs, or high-impedance 1 Mohm/300 MHz probes. Automatically setup and recall up to 100 test sequences of up to 99 steps each (3700 steps maximum), either from the front panel or under HP-IB control.

### Call HP today.

For more information on the HP 54100A/D1 GHz Digitizing Oscilloscope or the HP 54300A Probe Multiplexer, contact your local HP sales office listed in the telephone directory white pages. Ask for the electronic instruments department.

0801507

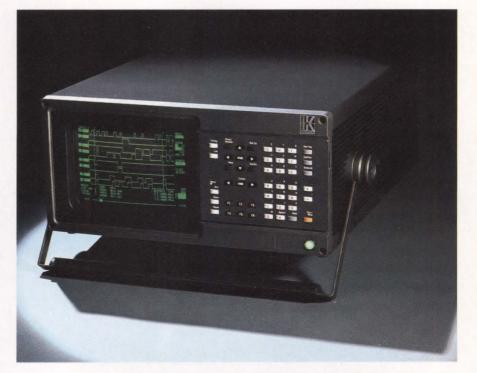

## **Kontron Logic Analyzers:**

Kontron's new Series III Logic Analyzer is the ideal tool for debugging digital products, taking you into the deepest forest, up the tallest trees, in pursuit of the rarest leaves bearing the most exotic bugs.

## Survey more of the "forest"

With memory depth of 8K, and up to 64 inputs, the Series III captures 4 times as many samples per recording as any major competitor. Capturing more samples means a better overview of the target system's operation, and clearer insights into the cause of system faults.

#### Choose your "trees"

Kontron's advanced triggering scheme doesn't force you to go through complicated routines for simple measurements. And, for more complex requirements, the Series III makes the most sophisticated measurements of any logic analyzer *ever.*

## Clutching leaves in the wind

Sampling rates to 100 MHz (standard) and 500 MHz (optional) are fast enough for capturing the briefest intermittents. Grab more data and multiply effective recording time with *transitional* recording and high resolution time measurement.

#### A better bug trap.

Every bug is different, and many can only be caught by combining advanced recording features. Kontron's Series III is *modular* and configurable to cover the broadest range of applications possible; from mainframe to microprocessor system development, and from high-speed custom IC design to GPIB and RS232 communications analysis.

## Locate Bugs Efficiently.

### Have it your way.

The Kontron Series III is available in stand-alone configurations, as an integral part of our Kontron Modular Workstations, or for maximum economy, as *the* Personal Logic Analyzer hosted on your IBM PC.

For more information, contact **KONTRON ELECTRONICS INC.** 630 Price Ave., Redwood City, CA 94063, 800/227-8834, (415/361-1012 in California).

We'll get you out of the woods.

ADVANCED ELECTRONIC INSTRUMENTATION

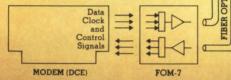

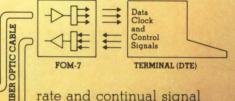

## This New Fiber Optic Modem will Extend a DCE Interface to Any Point in Your Local Area Network.

#### Plus a whole lot more.

channel

- •Can also be used for standard modem applications

- Automatically accepts or supplies DCE/DTE clocks

- •Fully supports all EIA handshaking signals •Provides secondary data

In short, you can use our new fiber optic modem between any two plug compatible units in your local area network. And it won't require any jury-rigging or looping clock and interface signals. That's because, from an operating standpoint, our fiber optic modem looks just like an EIA cable; whether you're going from a long-haul modem to a remote terminal or from a CPU port to a printer. And it's just about as easy to install as a cable — we even provide two separate connectors (DTE and DCE) on each modem. YOU determine how our modem will function simply by selecting which connector you use!

Once our fiber optic modem is installed and operating it'll really begin to shine. You'll benefit not only from the advantages inherent with fiber optics (traffic security plus noise immunity) but also from the exceptional operating performance. Our very low error

rate and continual signal quality monitoring means that you'll operate with a higher throughput and less downtime than ever before.

Versitron manufactures a complete line of fiber optic products for Local Area Networks. Our 20 years' experience in fiber optic is reflected in the performance capabilities of our products.

PWR BCVL CTS CTS DSB/ DCD SYNC ALARM RESET

For the full story on how our complete line of fiber optic products will solve your Local Area Network problems, give us a call at (202) 882-8464. Or write:

6310 Chillum Place, N.W., Washington, D.C. 20011, TWX: 710-822-1179 CIRCLE 16

## LETTERS TO THE EDITOR

#### **Checking the facts**

I was pleased to see that *Computer Design* is interested in covering new developments in symbolic processing—a technology that is coming of age and certainly has vast ramifications for our industry. In the November issue (p 45), John Bond introduced our new Explorer system as a significant new entry into this market.

Unfortunately, in comparing it to other dedicated Lisp machines on the market, he made a few factual errors. On the basis of these errors, he positioned the Explorer exclusively as a low cost delivery vehicle for artificial intelligence applications. As Bond pointed out, the Explorer is certainly smaller and less expensive than some of its competitors, making it an ideal delivery system. However, Explorer was designed to be a powerful development tool as well.

Bond refers to the Explorer's disk capacity as 112 Mbytes several times when, in fact, its capacity is significantly greater. The disk system for Explorer can consist of four tabletop or stackable enclosures, each of which can contain two 5<sup>1</sup>/<sub>4</sub>-in., 112-Mbyte drives for a total of 896 Mbytes of formatted disk storage. In addition, he states that while a full Zetalisp implementation is preferable for program development, TI chose Common Lisp instead because of the 112-Mbyte disk capacity.

Explorer does support a full Zetalisp implementation. Common Lisp, however, was chosen as the default Lisp dialect because it is an emerging industry standard. In addition, TI has added a more consistent and user-friendly interface to the MIT-based system software. And, as Bond very accurately reported, TI has provided several "toolkits," including natural language and relational table management systems, to enhance the development environment. Joe Watson

Texas Instruments PO Box 2909 Austin, TX 78769

#### Engineering shortage myth

In response to Mr Feerst's letter in the December issue, in my experience, the "engineering shortage" myth does not lie in the number of technically trained people turned out by the universities, but the use of these people after graduation.

Because management often believes in the "mass" approach to problem solving, it must keep salary costs down. Accordingly, the ranks are filled with young or underqualified people.

Those who have reached a level of competence as a result of years of expe-

rience, eventually find that they are at the top of the all-powerful "salary bracket." They are then often forced to leave what they know and do best, and go into management or sales, or leave the technical field entirely.

mun

On a national level, using masses of low priced technical people instead of rewarding individual achievement is self-defeating. Fathers who have been forced out of a career in design and development by artificially depressed salaries are not going to recommend a technical career to their sons. Eventually, certainly not now considering the waste of talent, a *real* shortage of engineers could be forced upon us.

The "solution" in Mr Young's letter is another of the many solutions proposed by management in attempts to maintain the status quo in which it can blame the lack of imagination and ability on the chimera of "engineering shortage." Until management is convinced it the waste of technical talent is a disgrace instead of "good business," it will continue to cry shortage to the future detriment of our country.

C.W. Spindler, Jr PO Box 11220 Elkins Park, PA 19117

#### What's in a name?

Who is this insignificant whelp, Michael S. Elphick? He doesn't have the stature or qualifications to review the merits of Mr. Iacocca! His comments about Professor Shannon's works are the epitome of the lay media's gall! (P.S. There is a much more esteemed member of the press with first initials M.S.—maybe you have heard of him, but I doubt it.) (Unsigned) Phoenix, Ariz

Unlike the author of this letter, the insignificant whelp has the courage to sign his comments. Fortunately, even in 1984, low status people were still able to criticize high status people. However, like Mr Iacocca, I am a graduate engineer with design experience. Several other editors of this "lay media" are engineers and one (John Miklosz, our Executive Editor) has a PhD. (P.S. I would not expect an advocate of corporate welfare to be a fan of a true blue capitalist like Malcolm S. Forbes. Besides, Forbes is even more opinionated than I am.) Michael S. Elphick Editor in Chief

#### Quality is the issue

In response to the December editorial on Mr Iacocca, I feel that Mr Elphick's comments were completely out of line. First of all, Mr Iacocca had no other choice than to go to the federal government for a loan guarantee because if he had not, we would all be paying for the welfare that the unemployed Chrysler workers would be collecting. Time was an issue and to negotiate with private banks would have taken too long. It was the government's responsibility to provide Chrysler with the guarantees it needed in order to prevent the economy from becoming worse than it already was. I would like to see someone from the computer industry save Evotek the way Mr Iacocca saved Chrysler.

The automotive industry has more influencing it than does the computer industry. Labor is a more important issue due to the unions that keep crippling the industry's efforts to solve quality problems. I wonder where the computer industry will be in 70 years? The automotive industry is also a heavy industry, the computer industry is not. Automobile manufacturers deal with more safety issues than computer markets.

To sight Mr Iacocca for your problems with the Pinto is like me blaming Ken Olson because my RL02 drive crashed. What does a Colt have to do with Chrysler? All they do is sell the car, not manufacture it! In fact, the car is made by Mitsubishi (a Japanese company of all things). Mr Iacocca is also responsible for the Mustang, one of the most renowned cars of all time.

I am aware of the problems that major industries in the United States are facing, and it appears that these problems are now surfacing in electronic and high-tech companies. Quality is a problem for many industries in this country. I know, I work in the storage products division of a

### LETTERS TO THE EDITOR

major computer company and we are constantly fighting for quality parts from our vendors.

Sure, Mr Iacocca had help from the government, but the debt is gone and Chrysler continues to grow and develop new and technically advanced automobiles. Why not write about the real issue of quality in US industries and stop the finger pointing?

W. Dale RobertsonDigital Equipment Corp333 South StShrewsbury, MA 01545-4112

Surprisingly, I find myself agreeing with Mr Robertson on many of the points he makes. But perhaps I am old-fashioned in believing a chief executive should be held accountable for the quality of the products he sells. Though Iacocca was demonstrably better than the managers who preceded him at Chrysler, I still believe that Mr Robertson treats him too kindly. Perhaps if Mr Iacocca had mentioned somewhere in his self-serving autobiography that he too was "constantly fighting for quality parts from our vendors," I might have as much respect for him as I do for Mr Robertson and other engineers at companies like DEC. Instead. Iacocca merely brags about how he superficially restyled the bodywork of marginally profitable cars so that he could jack up the price. Also, has Mr Robertson considered who pays the welfare for the 33 vice presidents and thousands of other workers fired by Iacocca after he ioined Chrvsler?

Michael S. Elphick Editor in Chief

#### Right man, wrong category

I have two comments regarding your editorial in the December issue of Computer Design. I regret your awkward experience with "Who's Who of American Women." I hope you advise Marguis of their error, as I don't believe the company intends to perpetrate such faux pas. Secondly, as for Lee Iacocca's award, I would have to agree that "entrepreneurship" is probably not the right category. I don't think the loan guarantee to Chrysler was fair to other struggling businesses either. However, I think that Iacocca may deserve some sort of award or recognition. A lot of people seem to think so. And he can hardly be blamed personally for design or construction defects in Chrysler's cars.

I myself am listed in "Who's Who in the West." I know what I did to get there, and think I deserve to be there. If I've any complaint with Marquis, it's about some fine colleagues who aren't there who I think should be.

Dave Fafarman 4330 Jana Vista St El Sobrante, CA 94803

#### Is this for real?

I read the December editorial in disbelief. I was amazed that you wasted your time with this obvious personal vendetta. Several thoughts occurred to me as I read it: 1) Who really cares whether or not you approve of the selections by "Who's Who?"

2) Do you really believe that Claude Shannon cared that you didn't attend?

3) I had a 1973 Pinto (of the alleged exploding vintage) which I loved. It was one of the most reliable and economical cars I have ever owned. Does that make the Pinto one of the most reliable cars made? Of course not! A sample of one from a population of millions cannot lead to any general conclusion. You state that you would call these cars lemons "except that the word suggests an isolated bad car rather than a typical product in the line." What evidence, except the isolated car incidents you give, support this comment? The same arguments apply to your Dodge. I could easily conclude from your article that you don't take care of your cars ("... after a water hose fell off and the engine overheated").

4) Your criticism of Marquis for sending you a letter for Who's Who of American Women is totally absurd. I can't imagine how many women in the industry have probably received letters addressed to "Mr so-and-so." In fact, I would bet your own magazine has been guilty of this same thing—multiple times.

Let me make it clear that I am not affiliated with Marquis, Ford, Chrysler or anyone else mentioned in your article. I simply do not care for sloppy journalism which uses isolated examples and totally unsubstantiated arguments. Whether you are writing an article or an editorial, your readers deserve substantiated facts—not your wife's opinion.

I don't know exactly what your gripe is against Who's Who, except that you don't like Iacocca. Regardless, *Computer Design* is not the place for this crap. Mark Forbes 140 Carlton Ave Los Gatos, CA 95030

Like Mr Forbes, I am skeptical of mother-in-law (or wife) surveys. That was why I quoted an independent survey of consumer satisfaction in the editorial. Also, Ford was forced by the federal government to recall the car twice, and it is not likely that this was done on the basis of a few isolated incidents. The whole point of my argument was that I spent an excessive amount of time and money repairing the car because of inadequate design. Incidentally, I hope Mr Forbes was careful to check all of his hose clamps before leaving for work this morning. Michael S. Elphick Editor in Chief

#### Thanks for getting it right

Thank you for taking the time to get it right in the December editorial covering "Who's Who" and Mr Iacocca. Your choices of Alan Shugart and Claude Shannon (and apologies) are certainly more understandable than those of the Who's Who committee.

Although Mr Iacocca's efforts were in a business arena, and a very large arena at that, his performance is primarily a management and finance endeavor. The automobile industry certainly does need saving. (Even the US auto worker tends to purchase foreign automobiles.)

It is encouraging to find other people who do not attend events. I hope that you find some events worth attending and pass those results on to the rest of us who are often not in a position to attend or not attend.

Ronald C. Edwards 2156 Sierra Ventura Dr Los Altos, CA 94022

## IF YOU THINK THAT SIGNETICS ONLY MAKES RUN-OF-THE-MILL PRODUCTS, IT'S TIME YOU TURNED THE PAGE.

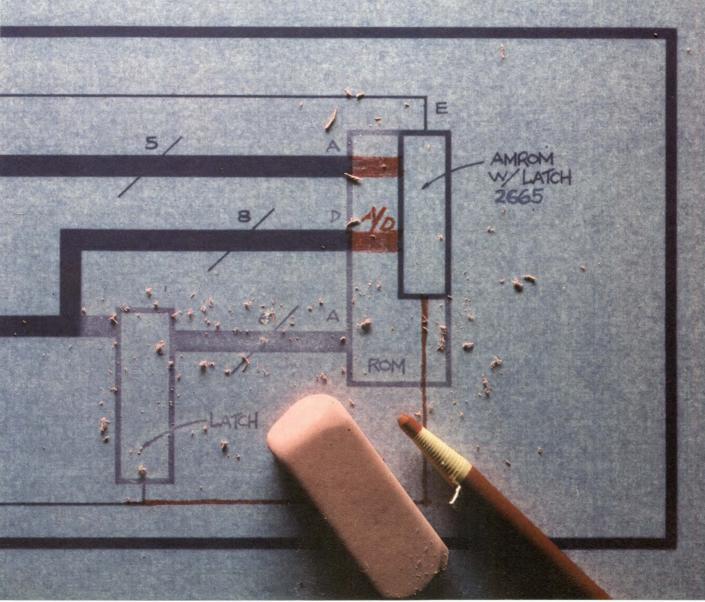

## A VERY FAST UPDATE ON MOS ROM DEVELOPMENTS.

We have nine different 150ns MOS ROM circuits - from 16K to 256K.

## VLSI from Signetics 800-227-1817 Ext. 916 F

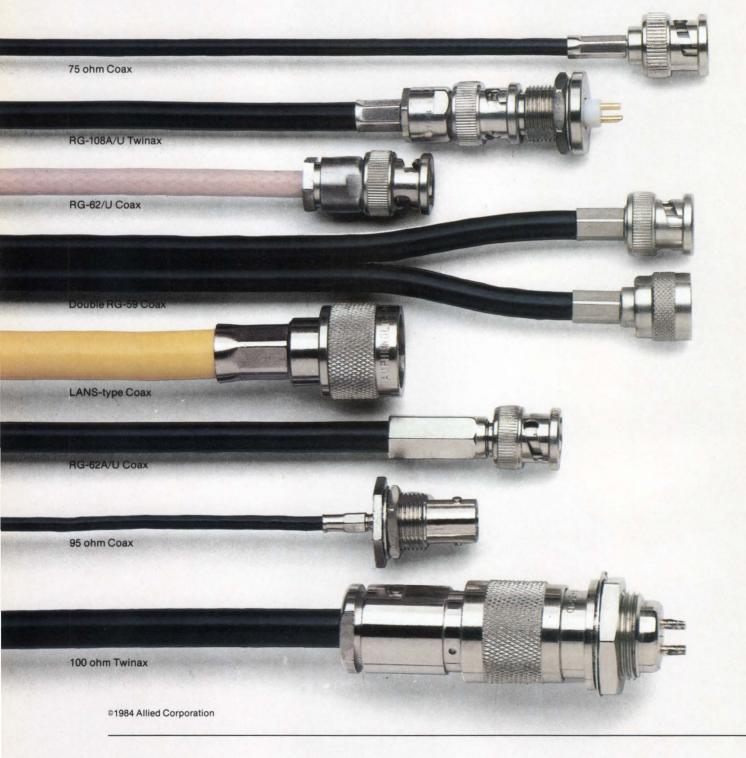

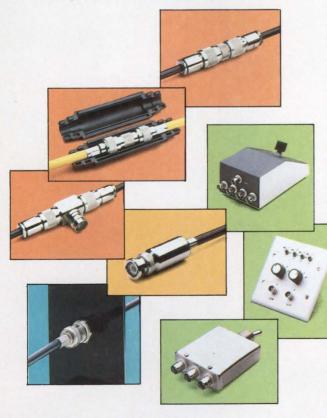

## At Amphenol Products it's only the beginning.

You can terminate most coaxial and twinaxial cables with minimal assembly time and effort using Amphenol® R.F. connectors. Our QUICKTRIM™ and SQUARE-CUT™ connector designs reduce cable preparation to a single cut. SURETWIST™ connectors thread directly onto the cable jacket. Our crimp designs offer low cost terminations using standard tooling.

Each design provides the ultra-reliable performance you require when interconnecting a host computer system with terminals, printers and other peripheral equipment. But top quality BNC and TNC plugs and jacks are only part of our computer connection capabilities.

We also provide a wide range of adapters and accessories to meet these functional requirements of your total data transmission system:

Splicing. Amphenol jack-jack and tee adapters provide easy, reliable splices of twinax, coax and LANS cable. To provide protection from electrical shock on LANS installations, silicon rubber boots cover splices and cable ends.

Isolation. Reduce noise by virtually eliminating "ground loop" or common mode current. Amphenol 31 Series isolated BNC and TNC feed through adapters and bulkhead receptacles provide uninterrupted signal paths and continuous shielding.

Termination. Eliminate open circuits on signal transmission lines when output plugs are disconnected. Amphenol 362 Series automatic coaxial terminators with self-contained resistive loads and automatic circuit insertion switches feature a unique make-before-break mechanism.

Switching. Help eliminate EMI and costly data transmission errors with Amphenol isolatedfrom-ground data switches. Available in panel mount, wall mount and desk top designs, these low cost, non-shorting switches are ideal for use in computer installations and local area networks.

For more information, technical assistance and prices...

Call the new connector company 1-800-323-7299

Amphenol Products world headquarters: Lisle, Illinois 60532

# INSTALL THE LAN OF THE FUTURE, NOW.

#### Proteon is today's only source for IBM<sup>®</sup> compatible token passing ring networks. It's called proNET<sup>®</sup> and it's from a leading independent manufacturer.

proNET is a high performance 10 megabit/second LAN with unprecedented reliability and fail-safe operation. It links many vendors including IBM, Digital Equipment, Sun Microsystems, Texas Instruments and in addition operates on the IBM cabling system. Plugging directly into UNIBUS,<sup>®</sup> Q-Bus,<sup>®</sup> Multibus<sup>®</sup> and Universal Bus it uses a combination of transmission media including twisted pair, infrared, co-axial and fiber optic.

The proNET system includes the hardware, software, cabling, installation, and service support. And it's comfortably priced; your investment can be modified, updated and easily expanded. One last point: the proNET token ring is available now.

Invest now in your token ring LAN. Call Proteon, Inc., 4 Tech Circle, Natick, MA 01760. (617) 655-3340.

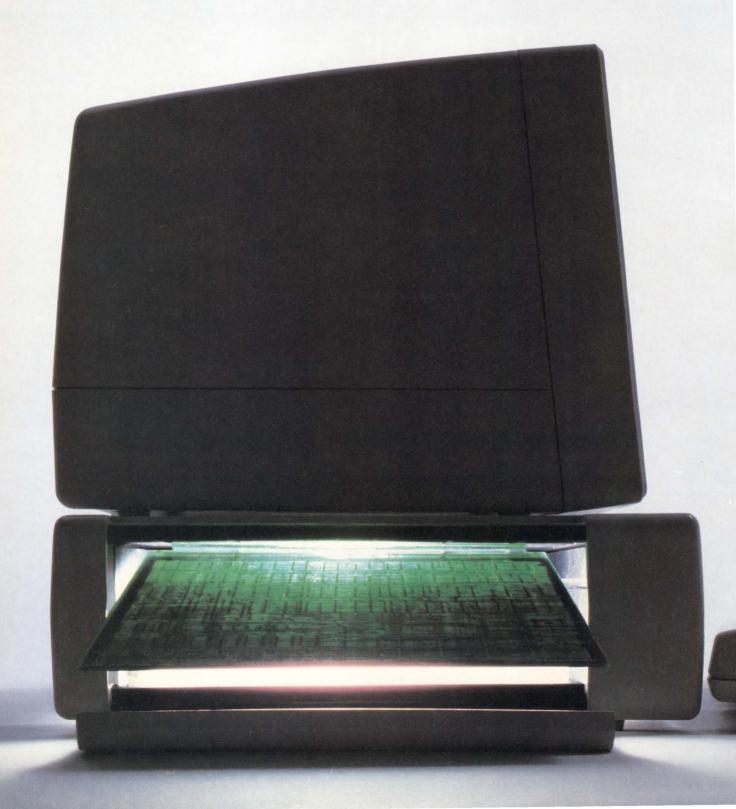

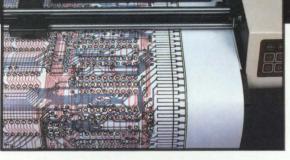

### **Options multiply for nonimpact page printers**

While the laser printer is experiencing a drop in cost and a surge in popularity, alternative technologies for nonimpact page printers are emerging. They will offer stiff competition and drive costs even lower. Foremost among the laser's competitors are magnetic and electro-optical printers. As in laser printing, these technologies are based on a modified electrophotographic technique, originally developed for copiers. With this technique, an image is formed on a photosensitive surface by electrical charges that can attract a toner. A printed image is produced when the toner is transferred to paper and fused under heat.

These nonimpact page printers differ from other nonimpact printers (such as those using ink jet and thermal technologies) because they use a photosensitive surface to transfer an image. This makes them best suited for printing a single page. In addition, since they have evolved from copier technology, they already incorporate automatic paper sheet handling. This is an option on other printers, hence, an added expense.

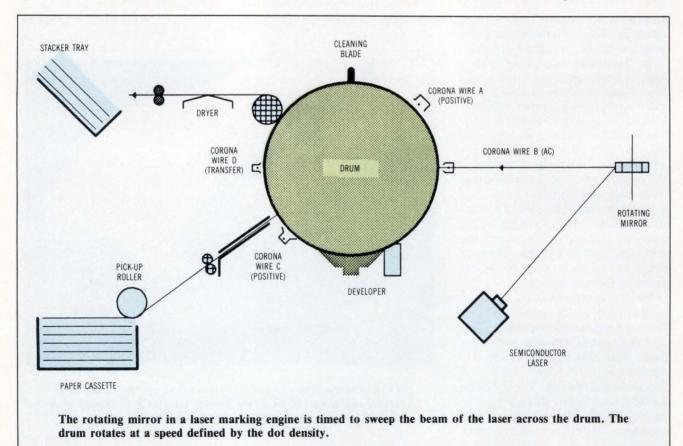

By combining the copier with a laser, mirrors, and lenses, it is possible to scan the laser in time with a video signal from a computer display. This forms a kind of screen printer. The resulting basic print engine is more properly called a marking engine since it marks the paper according to the signal it receives. To print actual data, such as an ASCII text stream, a controller must be added. The controller requires memory to buffer the data and intelligence to convert the ASCII code into dot arrays. The laser needs dot arrays to scan across the drum to form characters.

Most manufacturers of low cost laser printers buy the marking engine from a manufacturer of copiers and add their own controller and interface. With this approach, there is opportunity for many additional functions and features. These include ROM-based and downloadable fonts, bit-mapped graphics, and emulations of other standard letter quality printers. Since the basic task that the laser accomplishes is getting the electrically charged dot pattern from the computer onto the photosensitive surface (usually a drum), other technologies might be cheaper and better for marking engines. The critical factors are dot size (resolution), accuracy of dot placement, overall cost of the system, and reliability.

#### Variety in marking engines

In discussing nonimpact page printers, it is important to distinguish between the various marking engines with their different capabilities, and the controllers and interface electronics added by the different printer manufacturers. In the case of laser printers, there are three major suppliers of marking engines—Xerox, Canon, and Ricoh—but manufacturers have added a wide range of price/performance capabilities to these engines in the attempt to satisfy user needs. Although helium-neon or semiconductor lasers are commonly used in laser printers because of their speed, accuracy, and low power consumption, it is not altogether necessarv that a laser be used to sensitize the drum surface. First, materials other than the selenium are being developed as drum surfaces. Second, coherency of the light is not as critical as the intensity and the ability to precisely focus dots on the drum. The light source must also be turned on and off fast enough to provide sufficient printing speed. When the laser is scanned across a photosensitive drum by the rotating mirror, it acts much like a raster monitor.

For all these reasons the laser is a natural choice. But there are alternatives. Optical techniques based on liquid crystal shutters, LEDs, and beam scanning on a CRT can be used to project light onto the drum.

The cost of laser marking engines has been coming down with technological improvements to such alternatives as the selenium drum. One of *(continued on page 34)*

The Hewlett-Packard Laserjet printer is a desktop unit based on a marking engine by Canon. It has enough memory and intelligence to combine text and graphics with a 300-dot/in. resolution.

### Nonimpact page printers

(continued from page 33) these developments is the organic photoconductor material placed on a flexible belt instead of on a hard metal drum. A belt is used in the Ricoh (West Caldwell, NJ) LP4120 and is changed easily by the user. In another, stamped octagonal mirrors are used in laser printers, instead of precision machined ones. Sometimes the controller is added externally, and sometimes it is built into the printer package. The most basic function of the controller is to accept ASCII, bit-mapped, or graphic data from the computer and convert the data into a form that turns the laser beam on and off as the laser beam is scanned across the rotating drum. Moving mechanical parts, such as a mirror, require precise optical alignment to keep exact dot placement.

Dot placement is as important a factor in print quality as dot density or resolution. There is, however, some disagreement about where the optimal dot density lies. Many contend that at about 240 to 300 dots/in., the human eye loses the ability to distinguish between the dots. On the other hand, typesetters claim that the blackness of printer's ink is approached at about 700 to 800 dots/in. Serving the needs of the very high density user, of course, will increase the price paid for additional buffer memory and for more accurate optics.

The important aspect of dot placement is the ability to place four adjacent dots so that they are tangent to one another. This seems to leave the largest possible gap between the edges of the dots and leads to the belief that better resolution might be attained by slightly overlapping the dots. But, in both electrophotographic and magnetic printing, flux lines between adjacent dots (with the same charge or polarity) pick up toner and tend to fill in the gaps and smooth the edges between dots.

Another important factor in the quality of laser marking engines is the writing method used: scan-to-write or scan-to-erase. In scan-to-write, the laser places a charged dot at every point that should pick up toner-it is essentially writing with a black dot. Scan-to-erase starts with a fully charged surface and removes a charge at every point that should not pick up toner-essentially writing with a white dot. In both cases, low frequency noise can cause a scan line to vary somewhat from being perfectly straight across the page. In scanto-erase, this variation in the two lines on either side of the line to be left black would cause the width of that line to vary. Scan-to-erase, thus, cannot produce lines exactly one pixel wide and scan-to-write is inherently more accurate.

#### **Lights and magnets**

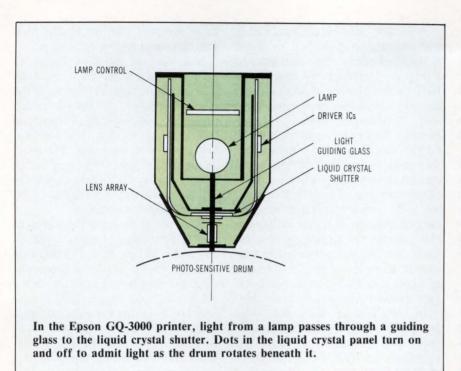

Alternative electrophotographic marking engines are addressing the laser's need for precisely aligned optics and a moving part (in the form of a rotating mirror). The liquid crystal shutter technology recently introduced by Epson retains the selenium drum and toner system of the laser

printer, but uses an incandescent light source behind a stationary liquid crystal shutter with an array of over 2000 dots. The dots are turned on and off as the data is fed to the array scan line by scan line. As the polarity of the liquid crystal changes, light to the drum is either admitted or blocked. According to Masahiko Mori, general manager of design for Epson's printer division in Kamisuwa, Japan, this method significantly reduces the number of moving parts and the cost, and increases reliability. But, he cautions, dot resolution has a practical limit of about 300 dots/in. Epson's introductory model, the GQ-3000, has a resolution of 240 dots/in.

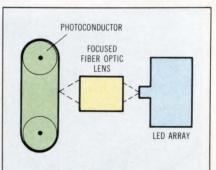

Two other approaches are the K-2 intelligent printer by Kentek (Allendale, NJ) and the Elpho 20 by Philips Peripherals (San Francisco, Calif). The K-2 uses a fixed array of 2084 LEDs focused on the drum through fiber optic lenses. In the Elpho 20, a CRT projection technique focuses the beam scanning across a monoline CRT onto the moving drum. Philips has achieved a dot density of 600 dots/in. with the Elpho 20, placing it close to the resolution demanded in phototypesetting applications.

Although magnetic printing uses a method for sensitizing the drum dif-

ferent from that used in electrophotographic systems, the engine works in essentially the same way. Magnetized dots on the drum pick up toner and transfer the image to paper.

Two manufacturers currently producing magnetic printers are Honeywell-Bull, represented in the United States by Cynthia Peripherals (Sunnyvale, Calif), and Ferix Corp (Fremont, Calif). The Cynthia 6000 series uses a hard steel drum with a proprietary surface alloy that picks up magnetic impulses from a stationary array of magnetic cores. The core array is manufactured in sections that are assembled inline and precisely aligned.

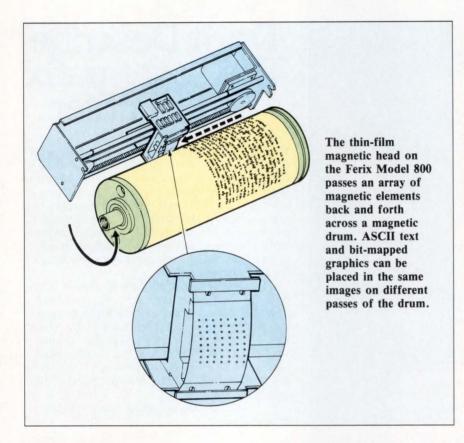

The Ferix new thin-film head technology is the basis for another magnetic printer technique. The head, a thin strip of metal manufactured by a wet chemistry process, consists of a 16 x 8 array of magnetic elements. Since the head is flexible, it is compliant to the drum, making critical alignment unnecessary. The magnetic elements are toroidal and focus the magnetic flux through the surface of the head strip onto the drum. The drum is coated with the mylar ferric oxide material used in a floppy disk.

In the current Ferix printer Model 800, the head array is moved back and forth across the drum like a

dot matrix printer. The technology can provide a higher dot density than currently achievable, and can eventually be implemented within a stationary array.

Magnetic printing brings with it a couple of inherent advantages. First, once the drum is magnetized, it stays that way until erased or written over. This means that once the image has been transferred, multiple copies of that page can be printed offline without tying up the computer. In addition, it is possible to write the page in two or more passes—once for text and then around again to add bitmapped graphics.

### The controller difference

If the function of the marking engine can be compared to that of a raster monitor, the task of the controller is essentially image processing. The controller also handles host and application interfacing, protocols, and in some cases performs job management tasks (eg, formatting, integrating text with graphics, font changes, and higher level graphics primitives).

Perhaps the most basic function provided by low cost electrophotographic and magnetic printer controllers is emulation of daisy wheel and high quality dot matrix printers. This is a feature needed to preserve the software investment and provide upward compatibility.

(continued on page 36)

Like the Ricoh LP4120 laser printer, the Kentek K-2 LED printer uses a belt of organic photoconductor. Light is supplied by a 2084-fixed LED array across the drum and focused through fiber optics.

### Nonimpact page printers

(continued from page 35)

The next most common function is to provide multiple fonts, which are most often supplied in plug-in ROM cartridges. Even at this level the printer will require control codes from the host that differ from those used in present printer driver software.

As the features and functions of the controller multiply, the requirement for software grows. In some cases, such as the 12/300 laser printer by Imagen (Sunnyvale, Calif), even fonts are no longer considered dot arrays, but are made up of high level graphic primitives.

One thing that laser/electrophotographic and magnetic printers have in common is that they are synchronous devices. Once they have started to print a page, they cannot be interrupted without ruining the scan. To work properly, they must print a page at a time, stopping only on an endof-page code. The computer must therefore supply enough data for a complete page description on one data transfer, and the printer must be able to buffer that data.

A full 8<sup>1</sup>/<sub>2</sub>- x 11-in. page printed at 240 dots/in. is equivalent to about 8.3 million pixels. This translates to a little over 1 Mbyte of memory to buffer a full bit map. Add to this the memory needed for program storage and ROM-based fonts, and the amount of memory can exceed the address space handling of some 16-bit microprocessors. Nevertheless, some manufacturers supply a full megabyte of memory space, such as Kentek in its K-2. Hewlett-Packard supplies varying amounts of buffer memory in the Laserjet for storing graphic bit maps. But few attempt to buffer a bit map of an entire page. The data rate of a common RS-232 or parallel interface would make this unacceptable.

In the Kentek K-2, the large amount of RAM is provided because fonts and emulation software are supplied on a floppy disk instead of in ROM cartridges. The files needed are called off-disk by the page description sent to the printer from the host. Depending on the capabilities of the printer, a page description can consist of simple text with a code for emulation and a few font changes,

or a complex file combining text, graphics, and forms definition.

Still, for the marking engine to scan, it must refer to a bit map buffered in memory. However, if the page description is stored in the printer in code form, the bit map can be created on-the-fly, then buffered and scanned in segments. The host, having transferred the page description, can do other things until the printer signals that it is ready for another page description.

Since a page description that results in a printed page of some 8 million pixels can be complex, the software used to create and interpret page descriptions plays a key role in the acceptance and integration of these printers. Software is needed to adapt such widely used applications as spreadsheets, word processing software, and database management programs to the printers. It is also necessary to give the ordinary user the ability to select options that satisfy the need to have a "what you see is what you get" transition from display terminal to printed page.

Hewlett-Packard's 2688A text and graphics page printer, for example, can be driven by a number of software packages that run on HP 3000 computers. An interactive formatting system, IFS/3000, allows the user to specify fonts, electronic forms, and page configurations from a menu of predefined forms or to develop customized formats. Graphics may be designed from existing Hewlett-Packard graphics software, such as HPDRAW, that is able to drive the 2688A; individual characters may be designed using an interactive design system. Such characters are defined as any dot pattern within a specified area. All this software must be run on the HP 3000, using specific graphics terminals to provide the "what you see is what you get" experience.

Page printer manufacturers that are addressing the OEM market on a wider basis have a tougher row to hoe. They must make their pagedefinition software flexible enough to adapt not only to a wide range of application packages, but also to different terminals. Such software does *(continued on page 38)*

### WORDS ARE ONLY WORDS ARE ONLY WORDS

### Words Alone Don't Describe The Lasergrafix 1200 Printer.

The QMS Lasergrafix 1200 is a breakthrough in electronic page printing. But words alone just don't describe it. Because QMS designed the Lasergrafix 1200 to do so much more than words. With a built in intelligent controller that takes simple print commands through your normal data stream. Built-in applications firmware eliminates the need for additional software – and frees your computer's resources for other work.

The difference is graphic – for all your business, scientific and individual printing needs. Create forms that have multiple typefaces and letters up to ten inches high – all on the same line. CAD/CAM. Bit mapped and vector graphics. Pie charts. Bar charts. Even barcodes. At a crisp resolution of 90,000 dots per square inch. With a printing speed of 12 pages per minute.

And, of course, letter quality word processing.

The Lasergrafix 1200 interfaces with just about any computer system. With versatility that lets you take business graphics to the limits of your imagination. Ask for a demonstration. You'll discover that the whisper-quiet performance of the Lasergrafix 1200 speaks softer than words.

And says a whole lot more.

COLOR SYSTEMS, INC. P.O. Box 81250 Mobile, AL 36689 Telephone (205)633-4300 Telex RCA 26 60 13 WHERE IMAGINATION LEADS

Send me the Lasergrafix 1200 Information Packet, samples of mixed fonts, graphics and everything else it does.

Please contact me to arrange a demonstration.

Title:

CD

Name: \_\_\_\_\_

Company:

Address:

Type of system you are now using: \_

Number of print workstations you are considering: \_

Prime applications for printer: .

QUALITY MICRO SYSTEMS, INC. P.O. Box 81250 · Mobile, AL 36689

### SYSTEM TECHNOLOGY/ PERIPHERALS

### Nonimpact page printers

(continued from page 36) not really exist as programs that can be compiled and executed in the normal sense; rather, it is embedded in a text stream that is sent to the printer to control the printer's functions.

Two companies that provide software to drive their controllers are Imagen (Sunnyvale, Calif) and Quality Micro Systems (Mobile, Ala). The imPRESS package by Imagen sends codes to the printer to control text, graphics, and orientation. The codes are entered as binary numbers.

An imPRESS page description will typically consist of 8 to 10 Kbytes of text, font changes, and vectors. The page description is then compiled into a page object of about 20 to 30 Kbytes. This page object resides in the printer's memory and converts to raster information on-the-fly as the Imagen 12/300 laser printer scans the drum. Robert Wallace, vice president of marketing at Imagen, stresses that the Imagen controller is not tied to laser technology. However, it can be adapted to other types of electrophotographic or magnetic systems by adding a different personality board.

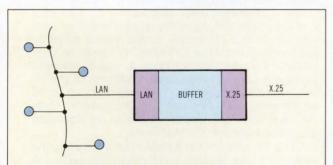

A software package such as im-PRESS is really an OEM tool that lets application or system designers adapt existing software or lets them design user interfaces to create page descriptions interactively on a CRT with a mouse or another input device. The program will generate a page description that contains the proper imPRESS binary codes. With this package, it would be possible, for example, to have a program that would take input data from a mouse and output imPRESS code to drive the printer.