**NOVEMBER 1984**

A PennWell Publication

GOMPUTER DESIGN THE MAGAZINE OF COMPUTER BASED SYSTEMS

## PERSONAL COMPUTERS FOR DESIGN AND DEVELOPMENT

ODUCT TYPE

1984

BIPOLAR LOGIC RUNS FAST ON LESS POWER

PROGRAMMING LANGUAGE COMBINES BEST OF THREE WORLDS

ONE CACHE PER CPU UPGRADES BUS AND MEMORY PERFORMANCE

# PER GRAM.

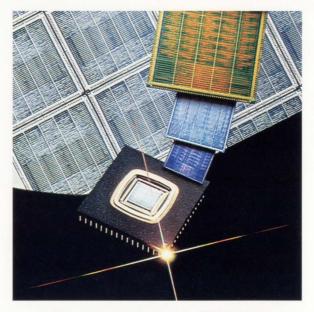

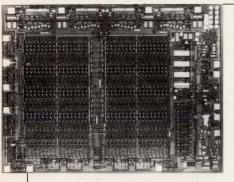

# 11,000 GATES

Never has so little meant so much.

In the last decade, we've opened more technological gates than anyone.

In both CMOS and bipolar.

Our 11,000 gate 2 micron CMOS array is just part of the story. We also offer TTL up to 2,000 gates. ECL to 3,000 gates. And 400 to 11,000 gate CMOS arrays. Not to mention our 100K- and 10KH-compatible ECL arrays.

Of course, a gate array is only as good as the people behind it. And at NEC, we have some of the best support engineers. Ready to help you take your design from start to finish.

With easy-to-use CAD tools. And sophisticated software capable of simulating up to 20,000 gates. All available at our 18 customer design centers, worldwide.

As for quality, we offer 100% burn-in, standard. At no extra cost. And you won't have to wait long to get it. Our turnaround is as quick as 8 weeks.

So next time you need a gate array, weigh your alternatives. Then call NEC.

## WE'RE TAKING ON THE FUTURE.

For the fastest response to your questions or for more detailed information, call us TOLL FREE at 1-800-556-1234, ext. 188. In California, call 1-800-441-2345, ext. 188.

NEC national sales offices: Woburn, MA (617) 935-6339 · Melville, NY (516) 423-2500 · Poughkeepsie, NY (914) 452-4747 · Ft. Lauderdale, FL (305) 776-0682 · Norcross, GA (404) 447-4409 · Columbia, MD (301) 730-8600 · Arlington Heights, IL (312) 577-9090 · Southfield, MI (313) 559-4242 · Bloomington, MN (612) 854-4443 · Austin, TX (512) 346-9280 · Dallas, TX (214) 931-0641 · Orange, CA (714) 937-5244 · Cupertino, CA (408) 446-0650

© 1984, NEC Electronics Inc.

## THE NEW STAR IN HIGH DENSITY ARRAYS.

Model 6470 Cartridge Recorder — the latest distinguished member of a

Kennedy didn't just pioneer the  $\frac{1}{4}$ " cartridge field — it started it, with the first practical recorder using the new  $\frac{1}{4}$ " 3M cartridge.

Model 6470 continues the tradition with the usual package of new features, such as:

- High Capacity Model 6470 can store up to 54 MBYTES of formatted data on one cartridge.

- Start/Stop with data streamings at 37.5 ips.

- Full Command Repertoire, utilizing either the Pico Bus or Pertec interface.

KENNEDY 6455

- Automatic Read Thresholds during read retry three different thresholds are automatically selected, a feature usually found only on large 9 track tape transports.

- Backward Compatibility Model 6470 will read tapes written by Model 6455.

- These are but a few of Model 6470's many features. Write or give us a call today for the complete story of the newest member of this oldest family.

An Allegheny International Company 1600 Shamrock Ave., Monrovia, CA 91016 (818) 357-8831 • ITT TELEX 472-0116 KENNEDY

KENNEDY 647

CIRCLE 2

## **COMPUTER DESIGN**<sup>®</sup>

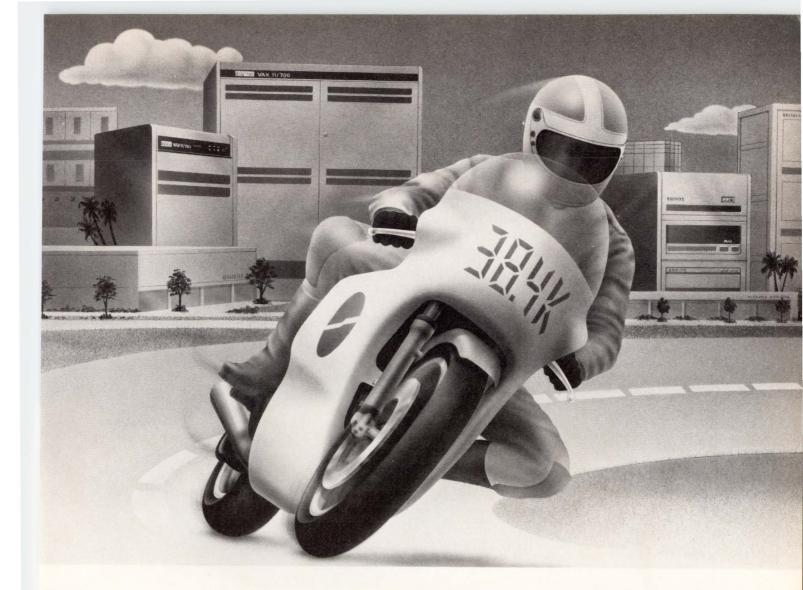

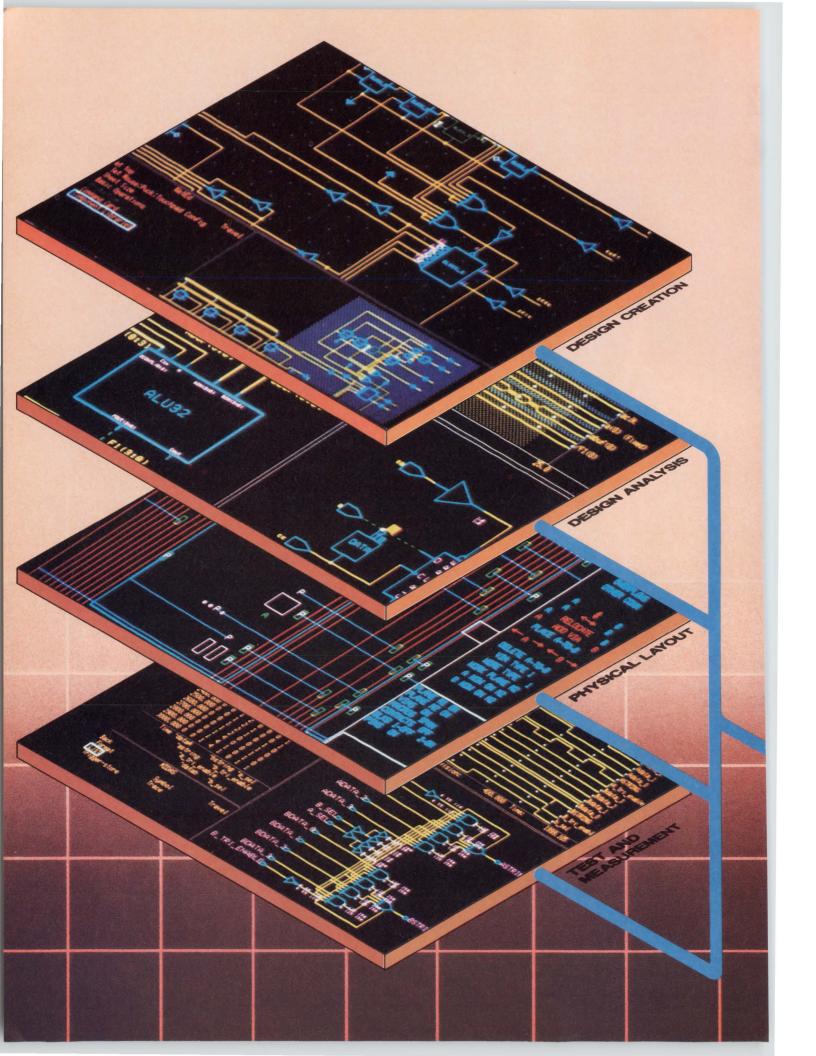

This month's cover was designed and created by Steve Branch at Coddbarrett Associates, Inc. It was executed using a Dicomed D-38 design station and a D-48 high resolution film recorder.

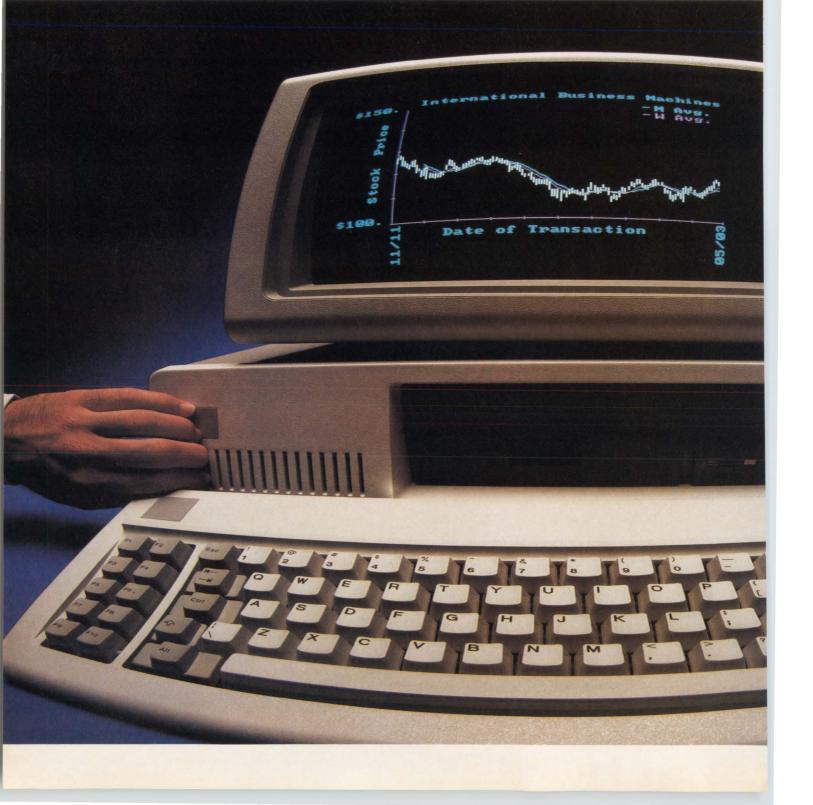

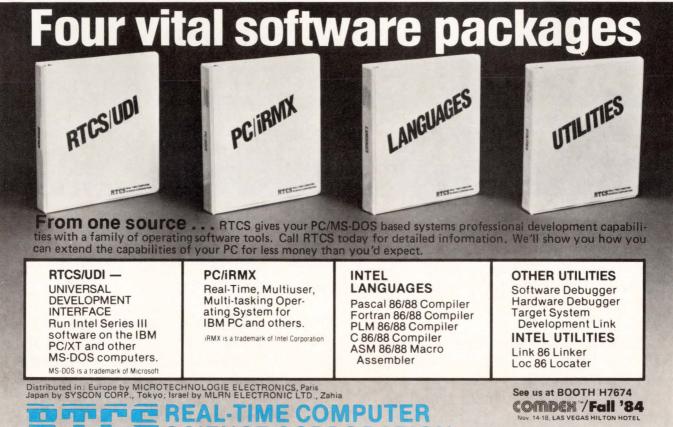

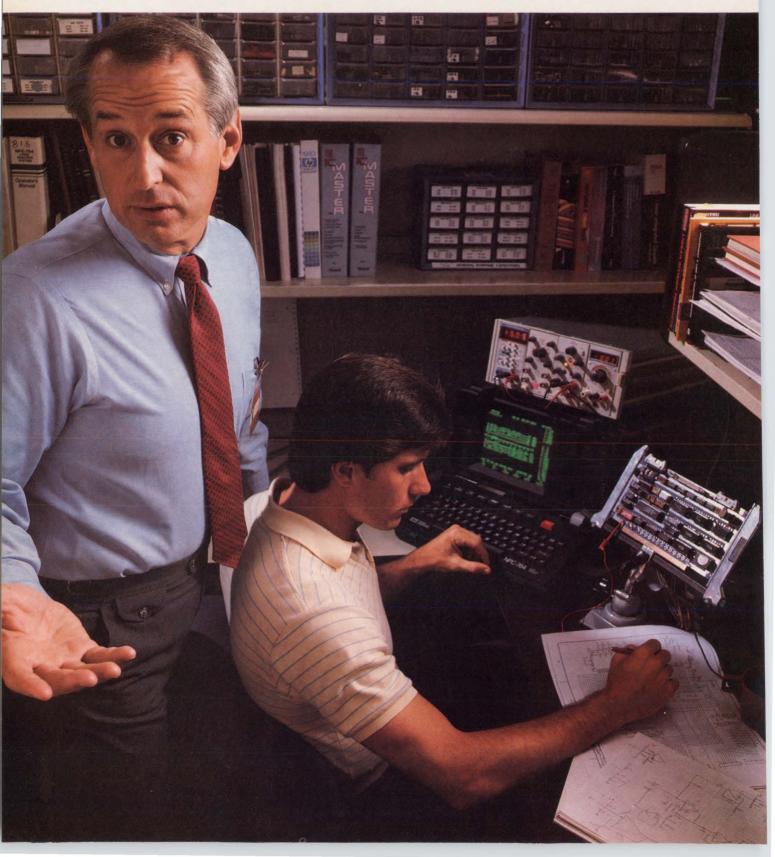

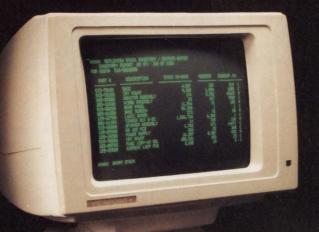

## SPECIAL REPORT ON PERSONAL COMPUTERS FOR DESIGN AND DEVELOPMENT

61 With the personal computer taking over business, home, and playtime chores, engineering jobs cannot be far behind. A multitude of entrepreneurial firms are filling the gap left by the major manufacturers of hardware and software development and test tools. The tools needed for such diverse tasks as logic design, printed circuit board layout, logic simulation, PLA and ROM programming, in-circuit emulation, and logic analysis are now available as add-ons for the ubiquitous IBM PC. While some of these do not match the performance of their standalone competitors, others do.

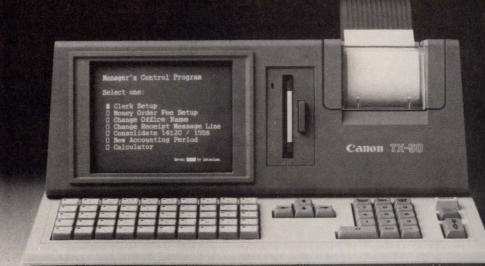

## 63 Personal computers have a go at engineering tasks

The lower entry cost of PC-based design, development, and test tools, compared to dedicated workstations, opens the doors to design automation for users with modest budgets.

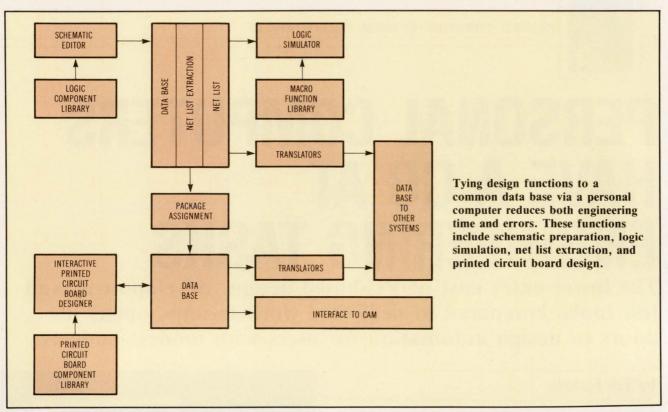

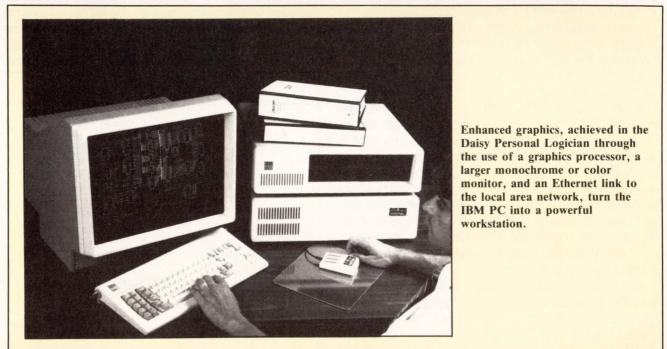

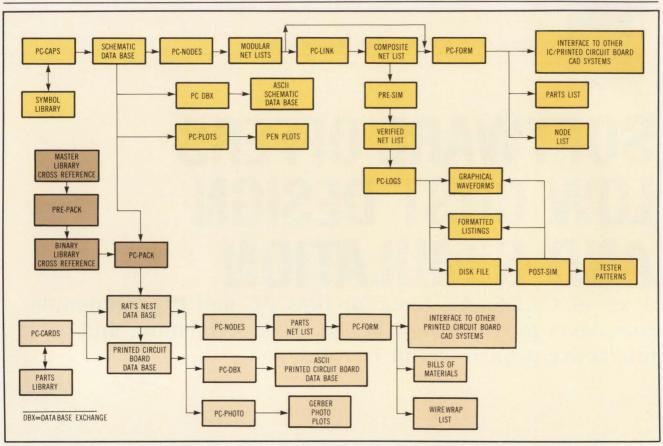

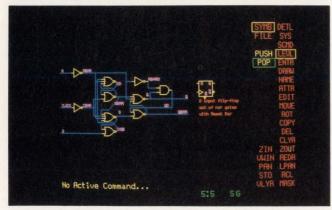

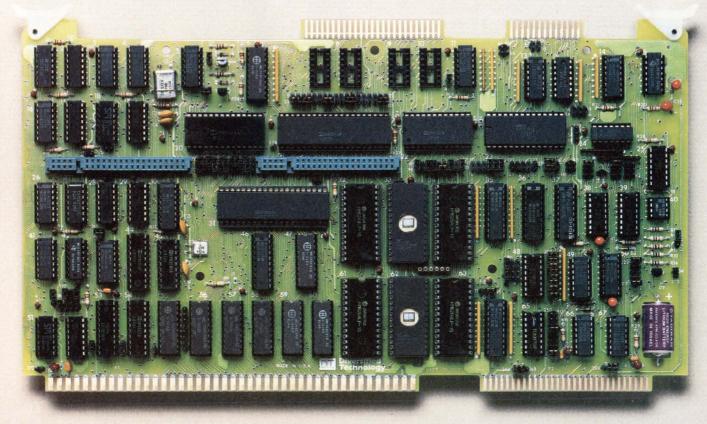

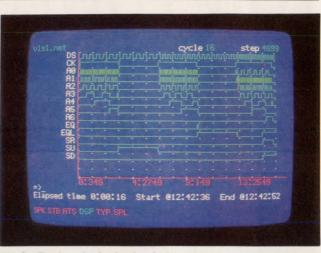

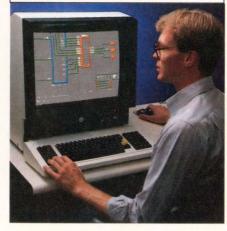

### 79 Software offers low cost design and simulation

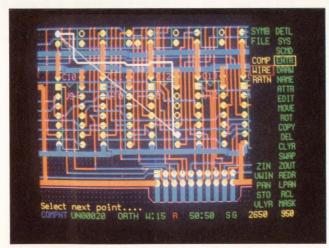

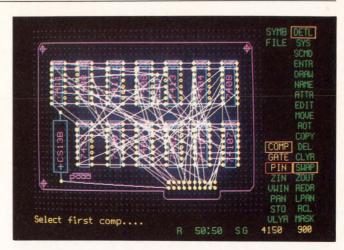

A set of CAD/CAE tools for IBM PC and PC-compatible computers provides logic design, logic simulation, and interactive printed circuit board design.

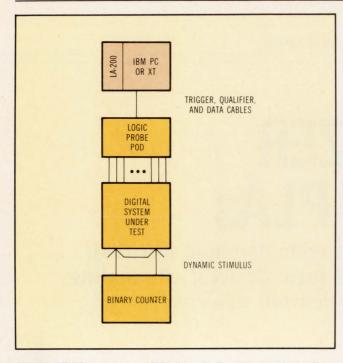

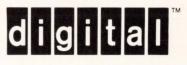

### 93 Logic analyzer checks out PLAs

PC-based test equipment can provide dynamic in-circuit testing of in-house programmed logic devices, eliminating reliance on static screening to weed out defective parts.

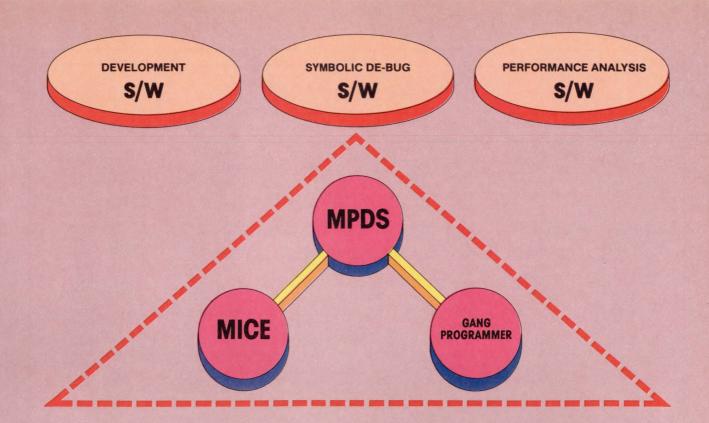

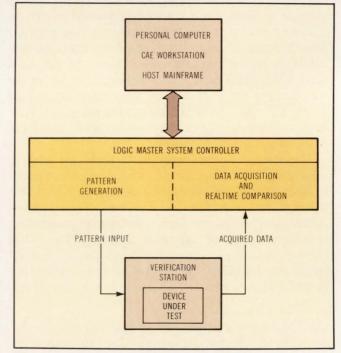

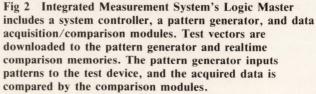

## 105 Interface simplifies IC test control

A test system that uses a simple command language brings interactive control to semicustom IC testing.

#### 119 Software package brings filter design to PCs

A set of programs running on the PC lets designers implement a variety of filters using the TMS32010 digital signal processing chip.

## SYSTEM TECHNOLOGY

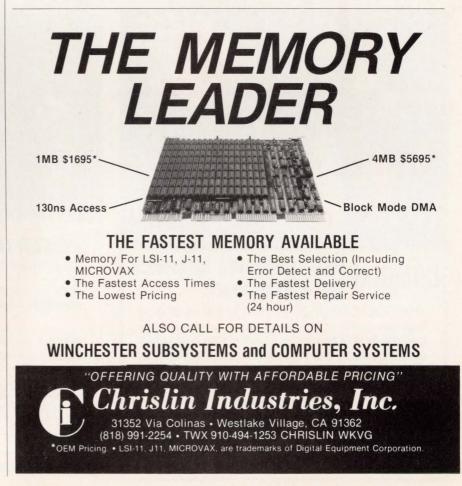

- **25 Memory systems:** Compatible memories bridge gaps for DEC minicomputers

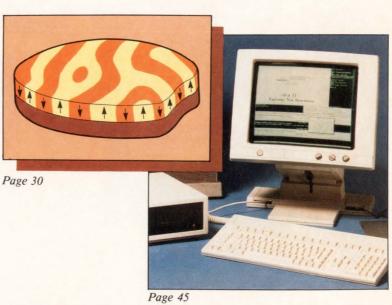

- **30 Memory systems:** Magnetic bubble memories making a comeback

- 34 Software: Graphics standards get boost from IBM announcement

- **38 Software:** Ada kit cuts compiler development time

- 45 Computers: Single-user symbolic processor cuts AI system costs

- **48 Integrated circuits:** Dense programmable logic takes aim at semicustom devices

Vol 23, No. 13

## SYSTEM DESIGN

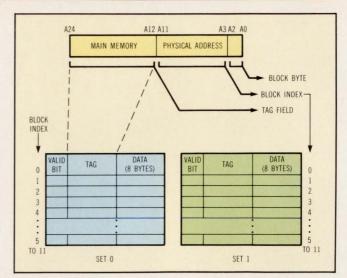

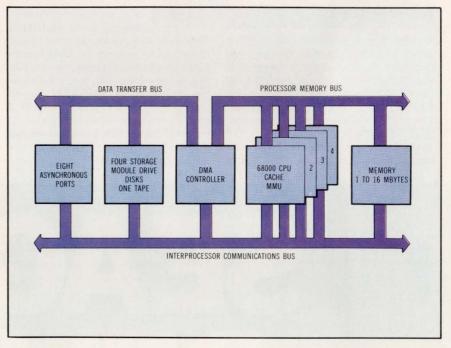

- 133 Memory systems: Cache boosts multiprocessor performance A cache for every CPU in a multiprocessor system reduces bus contention and memory latency. But efficient operation requires close attention to cache policy.

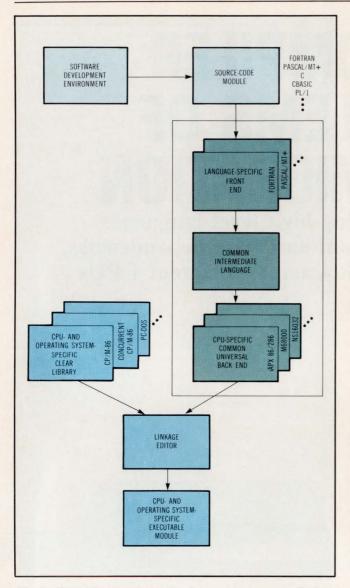

- 147 Software: Portable compiler eases problems of software migration A layered approach to compiling high level languages separates language specifics from hardware dependencies, providing source code portability across different CPUs and operating systems.

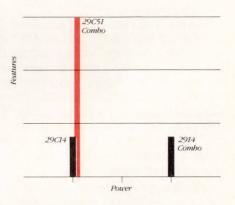

- 161 Integrated circuits: Speed up, power down for bipolar logic Bipolar logic-renowned for its high speed performanceuses improved processing techniques to produce chips that are not only fast, but consume little power.

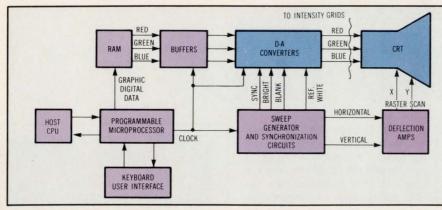

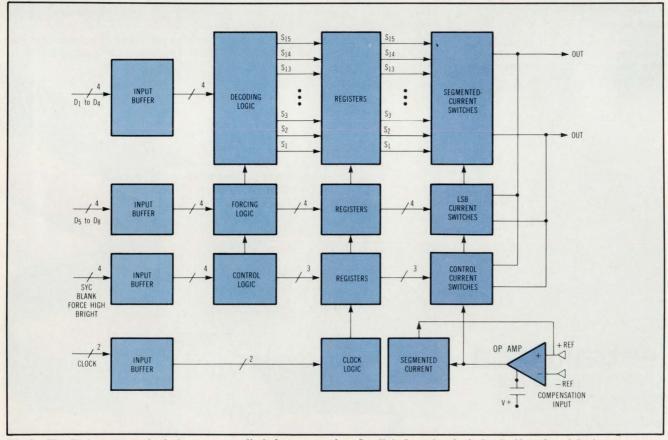

- 175 Interface: High speed D-A converters yield precision graphics Megasample-per-second chips improve resolution, precision, and flexibility of computer system displays.

- 183 Software: Forth efficiency blends with C and Pascal syntax A programming language developed for hardware designers combines interactivity with a structured, maintainable syntax and brings universal abilities to popular operating systems.

- **191** Integrated circuits: True floating point better and becoming cost competitive VLSI floating point chips have made true floating point representation practical for many applications. Although block floating point is still less expensive, true floating point provides higher accuracy and a better dynamic range.

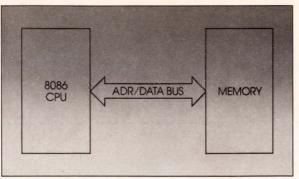

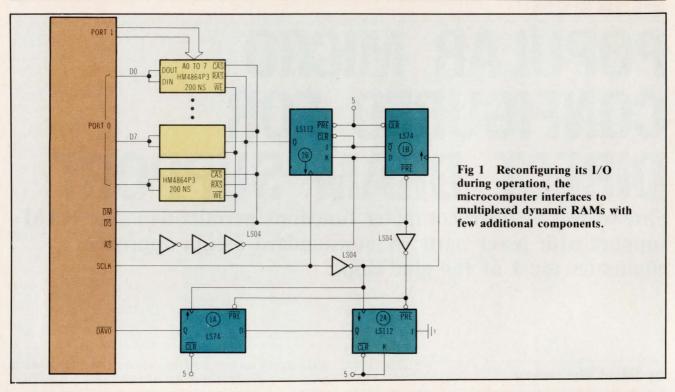

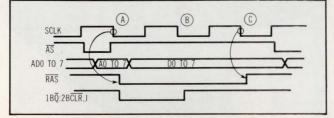

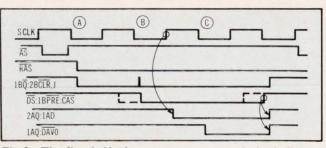

- 199 Microprocessors/microcomputers: Popular micro configured for direct DRAM support Shrewd use of microcomputer functions permits dynamic RAM support with fewer parts. A nonstandard design approach eliminates most of the glue chips.

## DEPARTMENTS

- **5** Up front

- **13** Editorial

- 252 Literature

- 255 Calendar

- 256 Designer's bookcase

- 257 System showcase

- 258 Advertisers' index

- 260 Recruitment

- 263 Reader inquiry card

- 263 Change of address card

## SYSTEM COMPONENTS

- 204 Computers: Portable PC-compatible sports full-size LCD

- 205 Computers: Unix-based 32-bit family tailors computer to application

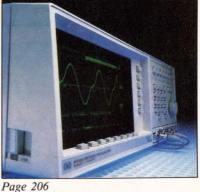

- 206 Test & development: Gigahertz-range digital oscilloscope provides clarity and precision

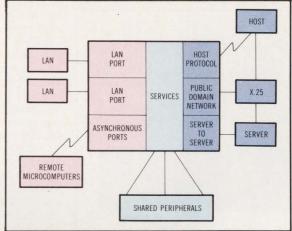

- **207** Data communications: Virtual networking unit builds a bridge to diverse facilities

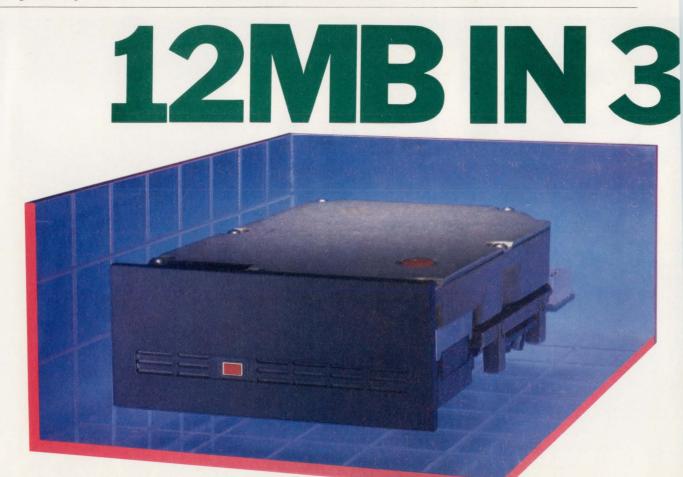

- 208 Memory systems: Winchester disk drives stretch 8-in. format

- 209 Interface: Controller caches in on sector algorithm

POSTMASTER: CHANGE OF ADDRESS FORM 3579 to be sent to COMPUTER DESIGN, Circulation Department, P.O. Box 593, Littleton, MA 01460 (UPS 127-340).

#### **COMPUTER DESIGN**/November 1984

3

203 Computers: Dual 68000-based supermicro runs fast with proprietary design

Page 133

Nov 1984

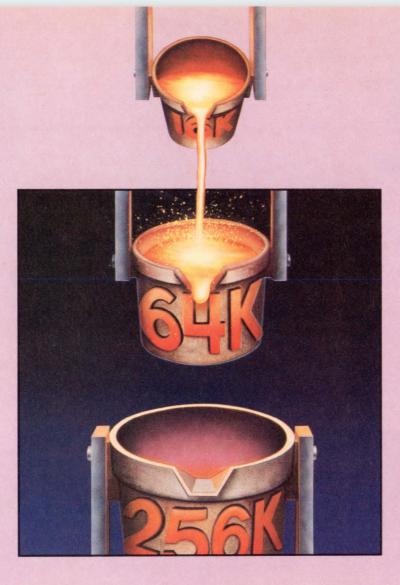

## Xicor E<sup>2</sup>PROMs. Forging Your Future.

If you're designing high-performance/highcapacity E<sup>2</sup>PROM systems, Xicor has guaranteed your future. With the right E<sup>2</sup>PROM – created for foresighted system designers.

Xicor's 64K E<sup>2</sup>PROM, the X2864A, offers the

design innovations that make it the right choice. For today and tomorrow. Innovations like automatic page write for super-fast, write-time performance. And DATA polling for write verification.

All in the JEDEC-standard footprint for 28-pin memories.

The X2864A also features an expandable architecture. Leaving pin one free to ensure your migration to 256K — without redesigning your system. Fact is, we'll be sampling our 256K E<sup>2</sup>PROMs in the first half of 1985.

That's sooner than anyone expected.

For more information, write us at 851 Buckeye Court, Milpitas, CA 95035. Or call (408) 946-6920

and ask for a copy of our free brochure.

## **UP FRONT**

## Fifth-generation computers and the emperor's new clothes

Not everybody at the recent Association for Computing Machinery's annual conference was enthusiastic about "the challenge of the fifth generation." The opening panel nearly glowed with optimism until an unscheduled speaker, former ACM president Dr Herbert Grosch, took to the podium. "The emperor is naked from the ankles up," Grosch thundered, referring to fifth-generation technologies. "All he's wearing is a heavy pair of wing-tipped shoes. Those are expert systems, and we've had them for 30 years. All the AI boys did is relabel them." Grosch admonished everyone to resist "greedy entrepreneurs" and "journalists with crazy stories," and declared that most of the technologies being discussed won't be available for decades.—R.G.

## Connection between incompatible systems made easier

Communication software packages from Advanced Computer Communications (Santa Barbara, Calif) and Network Research Corp (Santa Monica, Calif) are bringing users closer to the day when they can access various computers independent of their architecture or operating systems. Advanced Computer Communications' ACCES and Network Research's FUSION packages incorporate levels 3 through 7 of the ISO Open Systems Interconnection model. The latest addition to the ACCES family is a Virtual Terminal Service (VTS), a software package (written in C) that provides transparent communication between terminal and host on a multivendor, multi-operating system network. Meanwhile, Network Research has released its version 3.0 of FUSION for the VMS operating system and systems incorporating the TCP/IP protocols. FUSION is geared toward implementation in local area networks where incompatible processors and operating systems must be made compatible to network hardware from a variety of vendors.-N.M.

## Laser reveals logic states at chip level

Mechanical probing of VLSI chips to determine logic states may become obsolete. An IC laser logic analyzer developed by the startup Dataprobe, Inc (Santa Clara, Calif) and built off-shore by Mitsui & Co (Franklin Lakes, NJ) represents the first commercial use of a laser to analyze IC logic states. An external pattern generator is used to exercise a delidded IC while a helium-neon laser beam probes a circuit node, causing photocurrents in the illuminated transistor. Depending on the logic state, the coupling of the induced photocurrents to the power bus will differ. This variation in current determines the logic state of that node. More than 3 nodes/s can be automatically accessed to record logic states throughout the chip. Unlike mechanical probing, the system is noninvasive and does not disturb the passivation layer.—J.B.

## **UP FRONT**

## Cost sets pace for computer integrated manufacturing

Computer integrated manufacturing is at least 10 years in the future. Some recognized experts say even 15 may be optimistic. But that may not be the only problem. Speakers at the recent Autofact conference in Anaheim, Calif stressed the cost—crucial for small companies—and the need for technological breakthroughs. They point out that many of the smaller companies will find that less sophisticated automation will suffice. But 21st-century solutions for the major manufacturers will be based on revolutionary approaches, particularly more advanced artificial intelligence.—S.F.S.

## Custom building with 32-bit bipolar blocks

A family of VLSI bipolar 32-bit parts has been developed by Advanced Micro Devices (Sunnyvale, Calif). Called the Am29300 family, the parts differ from AMD's earlier bipolar bit-slice parts in that they are specifically intended as building blocks for 32-bit processors for which the designer can develop application-specific architectures and instruction sets. The family consists of a 32-bit ALU with an onchip 64-bit funnel shifter, a 64- x 18-bit register file, a floating point processor, and a 32- x 32-bit parallel multiplier. In addition, there is a 16-bit sequencer with realtime interrupt. The family is intended to fill a power/flexibility niche between standard 32-bit microprocessors and full custom CPUs.—T.W.

## Another Eagle leaves the nest

Putting serious pressure on disk drives in larger form factors, Fujitsu's latest ups the ante to 689 Mbytes. Retaining the actuators, heads, and media of its  $10\frac{1}{2}$ -in. Eagle drives (considered the epitome of Winchester technology), the new drive also provides an 18-ms average positioning time. Accompanying the 45 percent increase in capacity is an increase in transfer rate—from 1.8 to 2.4 Mbytes/s. Such a rate increase helps solve the throughput problems encountered in multi-user systems.—*P.K.*

## Datakits for budget-minded users

One Datakit virtual circuit switch (VCS) for some 100 physical connections and another that can switch up to 2500 virtual circuits are the latest additions by AT&T Network Systems (Morristown, NJ). The VCS product family is basically local area networks that use a star topology with a centralized short bus. This bus allows virtual circuits to be switched at an 8-Mbit/s rate using packet switching technology. Datakits can be connected using twisted-pair copper wire or fiber optic cable. While designed for telephone companies and extensively used within AT&T, the latest Datakit models are geared toward smaller businesses that prefer to maintain the compatibility and reliability provided by AT&T.—N.M.

## Dataram does more with memory

## ...and system managers too.

Dataram does more with memory so you can do more with your minicomputer system. No matter whose it is — DEC, Data General, Perkin-Elmer, VERSAbus, or others.

You can do more because Dataram ADD-IN memory provides more - more capacity, more capability, and more reliability. And that adds up to more performance per square inch than anyone else can deliver. More from Dataram also means more savings on power, space...and cost! All backed by a responsive spares program, a liberal warranty, and dial-up technical support.

Key to it all is Dataram experience. Gained from years of supplying memory to today's leading mini manufacturers...from supplying more memory units than any other company...and by a nearly 20-year commitment to memory technology.

Whether you're a system manager or a system builder, you should talk to Dataram before you make your next memory decision. Learn why we can provide everything you want in memory...and more.

Dataram Corporation D Princeton Road D Cranbury, NJ 08512 D (609) 799-0071 D TWX: 510-685-2542

CIRCLE 4

## **UP FRONT**

## Syte fades from view

Syte Information Technology, a startup based in San Diego, Calif, has abruptly closed its doors on the very eve of its first product shipment. Syte had been promised a \$4 million dollar second round of financing from its original investors if it could raise another \$2 million from outside sources. When it failed to do that, the investors pulled the plug. Still up for grabs, apparently, is the company's main technology, the Global Environment Manager (GEM). This operating system kernel can wed different operating system environments in different hardware systems—all transparent to the user. As of this date, Syte has reported no takers for the sale of GEM.—T.W.

## A "low cost" 64-bit supercomputer

Brought to you by the star in Tracy Kidder's book, Soul of a New Machine, is the Convex (Richardson, Tex) C-1. Steve Wallach's latest project introduces interactivity to supercomputers. The C-1 combines key characteristics of traditional supercomputers with the packaging of minicomputers. It opens up 64-bit scalar and vector processing at rates around 60 MIPS in a broad range of scientific applications. The price is under \$500,000.—P.K.

## T&M giants move slowly with EE software

The computer aided engineering workstation has been ignored by traditional automation and engineering companies for so long that a healthy crop of young companies has grown to near maturity serving that demand. Recently, however, on-the-job automation has grabbed the attention of major suppliers like IBM, Hewlett-Packard, and Tektronix. But, these companies are holding back on the introduction of CAE software for electrical engineers, probably until early 1985. One Hewlett-Packard spokesman says he feels that enough in-house software is ready for introduction on its workstation. He also notes that because the software has been developed for in-house use, the company is probably waiting for adequate documentation to be developed before announcing products. Tektronix may be in the same position. Many engineering companies have developed such software for internal use, but documentation is not up to customer standards. The question is will Tektronix and Hewlett-Packard move into the CAE engineering market quickly enough? Just a month ago, it looked as though the opportunity to serve the technical and scientific communities had been forfeited to IBM, with its announcement of the PC AT and the host of follow-up announcements of GPIB capabilities and graphics enhancements. Maybe it isn't too late for the others. -B.F.

COMPUTER DESIGN © 1984 (ISSN-0010-4566) is published monthly, with a thirteenth and fourteenth issue respectively in June and October by PennWell Publishing Company, Advanced Technology Group, 119 Russell St., Littleton, MA 01460. Second-class postage paid at Littleton, MA 01460 and additional mailing offices. COMPUTER DESIGN is distributed without charge to U.S. and W. Europe-based engineers and engineering managers responsible for computer-based equipment and systems design. Subscription rate for others is \$50 in U.S.A. and \$75 elswhere. Single copy price is \$5.00 in U.S.A. and \$7.50 elsewhere. Microfilm copies of COMPUTER DESIGN are available and may be purchased from University Microfilms, a Xerox Company, 300 North Zeeb Road, Ann Arbor, Michigan 48106. Officers of PennWell Publishing company, 1421 S. Sheridan, Tulsa, OK 74101; P. C. Lauinger, Chairman; Philip C. Lauinger, Jr., President; Joseph A. Wolking, Senior Vice President; H. Mason Fackert, Group Vice President; Carl J. Lawrence, Group Vice President; V. John Maney, Vice President/Finance; L. John Ford, Vice President.

COMPUTER DESIGN is a registered trademark. All rights reserved. No materials may be reprinted without permission. Phone (617) 486-9501.

##

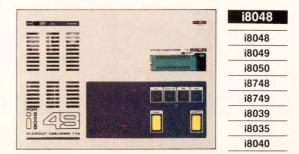

i8086/88 i8086 i8087 i8088

|   | 68000 |

|---|-------|

|   | 68000 |

|   | 68010 |

|   | 68008 |

| - |       |

| ÷ | Z80  |   |

|---|------|---|

|   | Z80  | - |

|   | Z80B |   |

|   | Z80H |   |

| - |      | - |

##

| i8085    |

|----------|

| i8085A   |

| i8085A-1 |

| i8085A-2 |

|          |

ZAX Zax Corporation 2572 White Road, Irvine, California 92714 (714) 474-1170 • 800-421-0982 • TLX 183829

Instead of a high priced development system . . . let

ZAX turn your IBM PC into a PROFESSIONAL

For more information call ZAX at 800-421-0982 or

714-474-1170. See us at Wescon, Booth #1325

**DEVELOPMENT SYSTEM!**

INTELL

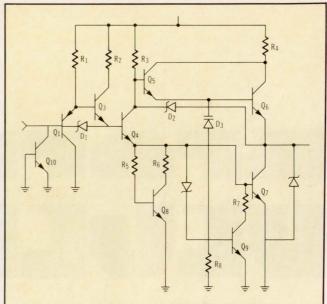

**ALTERNATIVE!**

CIRCLE 5

ZAX

THE

GENT

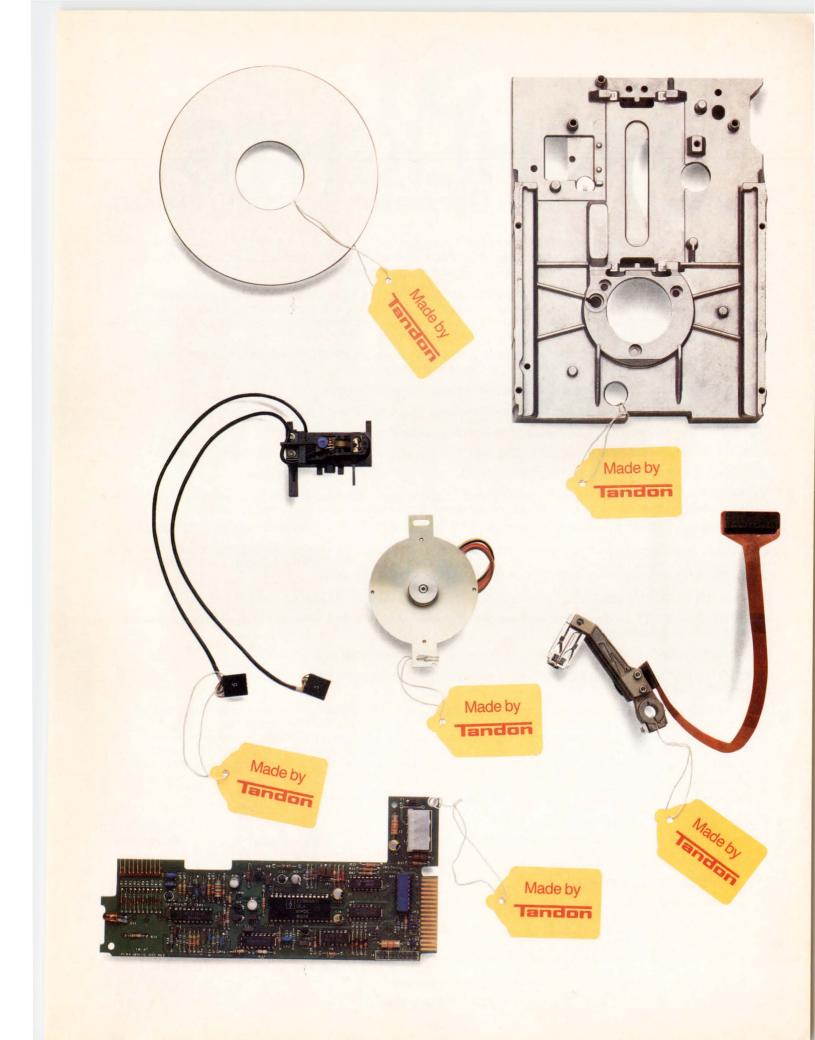

## **OUR DRIVES ARE MORE RELIABLE BECAUSE WE ONLY USE PARTS FROM RELIABLE COMPANIES.**

Reliability. It's one of those attributes that takes years to earn.

And it's one of the strongest elements you'll find in everything Tandon does. Whether it's parts or delivery or the way we handle our business.

Take our vertical integration story, for instance. That's always set us apart from other OEM suppliers. About 80% of the cost of our drives is made up of parts we manufacture ourselves. From the button heads to printed circuit boards to the plated media in our Winchesters.

Consequently, we have unyielding quality control. Tighter specs. An independence from outside suppliers so we get what we want when we need it, right from our own factories.

That's how we've become the most cost-

effective company in one of the most competitive markets around.

And because we're well aware of the investment you make in a drive, we've set our standards high. So high, in fact, you're absolutely assured of superior performance from every Tandon drive. And, naturally, at the lowest possible price.

Our floppy and Winchester manufacturing divisions are structured to be the highest quality, lowest cost producers.

Each one gives special attention to the demands of its customers. And each has the stable corporate background that gave us the ability to go from a garage start-up to the industry leader.

All in all, no one makes better disk drives than Tandon. Because reliability is the best part we've put in them.

## THE DRIVING FORCE BEHIND THE SMALL COMPUTER INDUSTRY.

Tandon Corporation, 20320 Prairie, Chatsworth, CA 91311. (818) 993-6644, TWX: 910-494-1721, Telex: 194794. Regional Sales Offices: Boston (603) 888-8612 • New York (201) 851-2322 • Atlanta (404) 934-0620 • Chicago (312) 530-7401 • Dallas (214) 423-6260 • Irvine (714) 669-9622 • Santa Clara (408) 727-4545 • Kelsterback/Frankfurt, West Germany 6107-2091, Telex: 411547 • Reading/London, England (0734) 664-676, Telex: 848411. Distributors: Hall-Mark, Kierulff, Schweber.

## S1 HGHLGHTS The World's First 4th Generation Operating System.

The S1<sup>™</sup> Operating System is an OEM's answer to product differentiation, a System House's answer to continuity and a programmer's dream come true. No other operating system in the world even comes close to the features and functionality of S1<sup>™</sup>. Some of the highlights are:

PORTABLE: The S1<sup>™</sup> Operating System, All Languages supported, and All Applications running on S1<sup>™</sup> can be ported to a newly announced chip architecture (even 32 bit) and running at full compiled speed within five (5) months. This is possible since the system and language compilers are written in a single common language called S L<sup>™</sup>. S1<sup>™</sup> and All Languages supported are machine independent.

FILE SYSTEM COMPATIBILITY: S1<sup>™</sup> can read and write files to and from: CP/M<sup>®</sup>, MP/M II<sup>™</sup>, MS-DOS<sup>™</sup>, UNIX<sup>®</sup>, XENIX<sup>®</sup>, p-System<sup>®</sup>, FLEX<sup>™</sup>, IBM 3741, DEC<sup>™</sup> Files 11 and others.

MULTIUSER - MULTITASKING: Complete support: even multitasking per user.

MULTIPROCESSING: Up to 256 processors simultaneously supported with any task running on any CPU.

NETWORKING: Remote Logon, Distributed File System, Intermachine Communications

EXTENSIVE GRAPHIC SUPPORT - FULL SCREEN MANAGEMENT - WINDOWING - BIT MAPPED DISPLAYS

FULL BIT MAPPED PRINTER & PLOTTER & TERMINAL SUPPORT - FULL SCREEN EDITING

EXTENSIVE UTILITIES: Assembler — relocating loader — linkage editor — high level assembly & language debuggers — sort — extensive O.S. managed error recovery — operating system debugging tools — desk calculator.

SUPPORTS ALL FORMS OF MEMORY MANAGEMENT, INCLUDING VIRTUAL MEMORY-BUT NOT REQUIRED

MODULAR: Unneeded system components can be omitted saving memory and load time such that the system can be configured for: REAL TIME — DATA ENTRY — PROFESSIONAL WORK STATION — PERSONAL — BUSINESS — MULTIUSER/MULTITASKING — DISTRIBUTED NETWORK — DEVELOPMENT.

UNIX® USER PROGRAM SOURCE COMPATIBILITY-RECORD LOCKING-EVEN BYTE LEVEL LOCKING

USER COMPATIBILITY: All configured versions of S1™ "Look" and "Respond" the same to all users, regardless of which chip or configuration is used.

VERY USER FRIENDLY: Menu driven, command driven, or prompting command processors.

PRESENTLY RUNNING ON: 68000, Z80<sup>®</sup>, 8080 and 8085. By Dec. 84: 8086/88—Jan. 85: 80186— March 85: 80286—June 85: 32016

LANGUAGES AVAILABLE: Pascal (ISO compatible) + Extensions, C (Kernighan + Ritchie) + Extensions; by Jan. 85: FORTRAN 77 + Extensions, BASIC (ANSI) + Extensions; by April 85: COBOL 74 + Extensions, Modula 2 + Extensions; by Sept. 85: PL/I + Extensions, Ada + Extensions, LISP + Extensions, SNOBOL + Extensions. All our languages are extended to provide many of the advantages of the S1<sup>TM</sup> Operating System (i.e.; 64 character file names) and are supersets of most popular language compilers, and can be made compatible with these languages using our available converters.

#### HIERARCHICAL DIRECTORIES & KEYED FILES (ISAM & VSAM & B-Tree)

#### **ELECTRONIC MAIL & FILE TRANSFER**

## SEMAPHORES AND LOCKS—REAL TIME SUPPORT

### UP TO 65,000 USER DEFINABLE SYMBOLS PER FONT

#### UNLIMITED NUMBER OF FONTS

\*Registered trademarks: CP/M of Digital Research; UNIX of Bell Laboratories; UCSD p-System of Regents of University of California; XENIX of Microsoft, Inc.: Z80 of Zilog, Inc.

Trademarks: MS-DOS of Microsoft, Inc.; FLEX of Technical System Consultants; Pick of Pick and Associates; MP/M II and PASCAL/MT + of Digital Research; S1 and SL of Multi Solutions, Inc. HP of Hewlett Packard; DEC™ of Digital Equipment Corporation; BASIC PLUS of Digital Equipment Corporation

COMDEX/Fall Booth 0739

Suite 207, 123 Franklin Corner Rd. Lawrenceville, N.J. 08648 609-896-4100 Telex 821073

## S1-The only operating system that does it all

## SHARING THE LOAD

Back-to-back editorials on management techniques might seem like overkill, but being the new kid on the block at Computer Design, it's natural that management concerns are high on my list of priorities. Faced with new challenges, I did what every good scientist or engineer does—research. I scurried off to a local book store and surveyed the shelves marked "Management." There were titles such as Managing for Results, by Peter Drucker (every manager should know Drucker) and Modern Management Techniques in Engineering R&D, written by a consultant and three PhDs. Now this last one was heavy stuff, but not exactly what I was looking for. My search ended with a book entitled Managing for Excellence, by David L. Bradford and Allan R. Cohen. This book proved to be much more than I expected. It helped clarify and confirm some ideas about the editorial approach Computer Design should follow in view of the complexity of the design, test, and manufacturing problems faced by builders of state-of-the-art computer-based products.

In their book, Bradford and Cohen go beyond the much-touted concept of quality circles. At the heart of their management philosophy is the concept of shared responsibility. At first glance, the two appear the same because everyone seems to get involved in the decisionmaking process. The quality circle, adapted to American industry, however, still casts most participants in the role of "recommenders" with a technical "hero" or an organizational "hero" calling the shots and riding to the rescue when "needed." But, in today's industrial world, engineering problems are often too technically complex for one individual to comprehend fully. What's more, many organizations are often too large and their elements too closely related for any one person to coordinate them effectively.

The concept of shared responsibility, on the other hand, demands that every participant assume a measure of responsibility for the success of the entire organization. For shared responsibility to work, however, everyone must measure up to their role. This requires active development of every participant's technical and/or organizational abilities to the highest levels possible—levels that exceed, at least in specific areas, those of "managers."

There's probably no better example of a complex management environment than the development cycle of a computer-based product. Each development phasefrom initial product specification to hardware design, programming, integration, production testing and manufacturing to marketing—requires a high level of expertise. Furthermore, the complex relationship between the different phases of the development cycle make the task of coordinating them overwhelming. Since no individual can be an expert in

every area, the manager as heroic technician or heroic organizer has become an anachronism in the business of making computer-based products. More so, perhaps, than in any other segment of industry.

Shared responsibility provides one solution. It requires that all participants have a thorough knowledge of their own areas of responsibility, as well as a knowledge of how their decisions affect others and how the decision of others affect them. Decisions made about product specifications, hardware, software, test capabilities, and manufacturing processes reverberate throughout the entire development organization. And a bad decision can produce "cracks" that are costly to patch.

If publications serving the engineering community aren't to become anachronisms—especially *Computer Design* which serves managers, senior engineers, and others that will have to make critical design decisions—we must always emphasize the relationships that exist within the design process and between the design process and the other phases of product development. The temptation to discuss hardware, software, testing, or whatever, in isolation is great. The editorial life is much simpler that way, but the resulting editorial product isn't all it could be. To make shared responsibility work we have to share in that responsibility by providing the new decision maker with the wide-ranging perspective needed.

John Miklosz Executive Editor

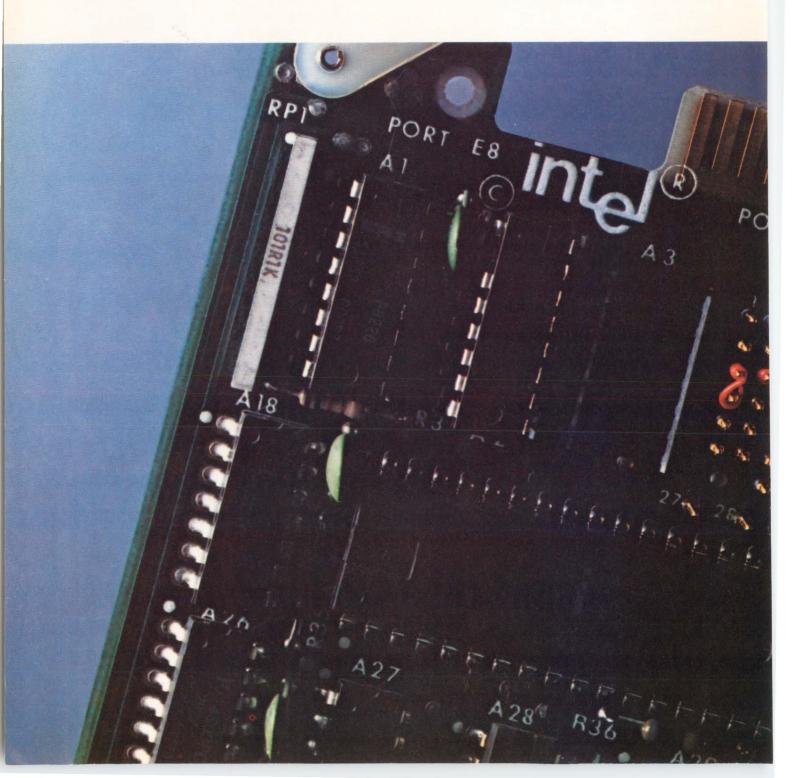

# THE BEST PLACE TO BOARD THE BUS.

Of course, we're talking about the MULTIBUS<sup>\*</sup> architecture. The most widely accepted, best supported bus architecture in the world.

But since you've already made the wise decision to use MULTIBUS as your road to riches, we're now going to show you the best place to start your journey.

Right here. Because as you might suspect, we know just about all there is to know about MULTI-BUS. After all, we invented it. And we have the largest selection of MULTIBUS products to be found. Anywhere.

For starters, there are our boards. We've produced over a million since 1976. Which should give you an indication of the experience we have in manufacturing quality boards. Quality that's not easily achieved.

Our boards are scrutinized at every level of integration. From chip through system level. And each board is tested to make sure it does its job in every one of its configurations. We even pull finished product from our warehouse for retesting and inspection. Just to make certain nothing slips by.

You can count on the road being smooth for a long time to come, too. Reliability is assured from start to finish. We continually monitor each board throughout its entire production life. Even going so far as lot sampling older boards and putting them through 5000-hour life test studies.

Then there's the selection. A big one. Over 115 different

© 1984 Intel Corporation

board-level products. Supporting 15 CPUs (from our 8080 to 80286). So you won't get stuck into one or even two design approaches. A tranquil thought when you consider how fast things change in the marketplace.

What's more, you can count on getting everything you need. From peripheral controllers to memory expansion, data communications and graphic boards. Plus card cages and software (including iRMX 86<sup>m</sup> the most popular real-time operating system in the MULTIBUS world).

One more fact about our MULTIBUS products. You can get fast service anywhere along the road. We've got one of the largest field engineering forces in the world. Over 600 factory-direct people. Not to mention localized support from our worldwide network of trained distributors.

So don't miss the bus. Travel safely. And arrive sooner. Call toll-free (800) 538-1876. In California, (800) 672-1833. Or write Intel, Lit. Dept. C-20, 3065 Bowers Ave., Santa Clara, CA 95051.

We'll be happy to welcome you aboard.

## **COMPUTER DESIGN**

The PennWell Building, Littleton, MA 01460, Tel: (617) 486-9501 Editorial/Executive Offices

Editor in Chief, Michael S. Elphick

Executive Editor, John Miklosz Managing Editor, Sydney F. Shapiro Senior Editor, John Bond Senior Editor, Peg Killmon Special Features Editor, James W. Hughes Senior Associate Editor, Malinda E. Banash Associate Editor, Jack Vaughan Assistant Managing Editor, Leslie Ann Wheeler Copy Editors, Helen McElwee, Leah A. Rappaport, Nancy E. Purcell, Jane E. Shattuck Editorial Assistants, Welma F. Brigham, Susan A. Livi New York Field Office: 230 Park Ave, Suite 907 New York, NY 10169, Tel: (212) 986-4310 Senior Editor, Nicolas Mokhoff Special Features Editor, Harvey J. Hindin Western Field Office: 540 Weddell Dr, Suite 8 Sunnyvale, CA 94089, Tel: (408) 745-0715 West Coast Managing Editor, Tom Williams Senior Editor, Bill W. Furlow Field Editor, Richard Goering

Production Director, Linda M. Wright Production Manager, Philip Korn Production Assistant, Elizabeth Mogren Staff Artist, Jay Gordon Technical Art, Designline Ad Traffic Coordinator, Debra L. Stone Printing Services, Padraic Wagoner

Circulation Director, Robert P. Dromgoole Promotion Director, Steve Fedor Marketing Services Coordinator, Linda J. Battle

Publisher, Frederic H. Landmann

## **PennWell**

Advanced Technology Group 119 Russell St, Littleton, MA 01460 Tel: (617) 486-9501

H. Mason Fackert, Group Vice President Saul B. Dinman, Editorial Director John M. Abernathy, MIS/DP Director Patricia M. Armstrong, Administrative Services Manager

# **New 4-bit raster DAC sharpens graphics** (and it's in an 18 lead DIP)

## 125MSPS, guaranteed, "graphics ready," just \$15\*

Give yourself a head start with a monolithic DAC designed specifically for raster scan systems—the TRW TDC1034 4-bit, 125 MSPS D/A converter. It directly drives CRTs to video compatible levels. Save on circuitry—no extra registering, buffering or deglitching. Save space—the 4-bit TDC1034 is an ultra-thin 18 lead DIP.

And you get terrific performance. This monolithic 4-bit DAC is ideal for either monochromatic or RGB color raster graphics (4096 colors!). Its high speed scans more pixels per picture to produce razor sharp high resolution displays. And because it's built with TRW's OMICRON-B<sup>™</sup> 1-micron bipolar process, you get high reliability and low power consumption (600mW).

The low-cost 4-bit TDC1034 is your one chip solution to high volume production of

CAD/CAM work stations, computer graphics, and high resolution video. If your application needs all the options that an 8-bit, 24 lead DIP offers, consider the TDC1018 the first monolithic 8-bit, 125MSPS D/A converter.

- Check these key performance features:

- ·Blank, sync and bright video controls

- Directly drives standard 75Ω load

- · Inherently low glitch

- Registered data and control inputs

- Power supply rejection ratio>50dB

- Differential logic for maximum speed, minimum noise

- RS-343 compatible

- Low power dissipation

- Single -5.2V power supply

- 1/8 LSB linearity (4-bit TDC1034)

- 1/2 LSB linearity (8-bit TDC1018)

- ECL compatible data and control inputs

These DACs are available from Arrow Electronics, Hall-Mark, and Hamilton/Avnet.

## Remember, you always get FULL SPEC PERFORMANCE from TRW LSI.

For a full data sheet or immediate information about our "graphics ready" DACs, call or write our Literature Service Department:

LSI Products Division, TRW Electronic Components Group, P.O. Box 2472, La Jolla, CA 92038, 619.457.1000

In Europe, call or write: TRW LSI Products, Konrad-Celtis-Strasse 81, 8000 Muenchen 70, W. Germany, 089.7103.115

In the Orient, phone: Hong Kong, 3.856199; Tokyo, 03.461.5121; Taipei, 751.2062

\*U.S. price in 1000s: TDC1034 CERDIP \$15; TDC1018 CERDIP \$36.00 © TRW Inc. – 1984 TRS-4116

LSI Products Division TRW Electronic Components Group

# IT WILL GROW ON YOU.

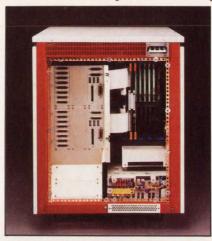

CONFIGURABLE ACCORDING TO USER NEEDS. As many as six processors can be installed in each enclosure. CPUintensive jobs utilize multiple Applications Processors. Systems with heavy disk usage can distribute this load among several File Processors. The number of user ports can be increased by adding more I/O Processors.

> MODULARITY EXTENDS TO DISK STORAGE. Compact 50 or 140 Mbyte Winchester modules simply plug in ... four per cabinet. Optional external SMD drives are also supported. File backup utilizes Winchester cartridges, ½-inch magnetic tape, or both.

0

9

Copyright, 1984, Convergent Technologies, Inc.

6

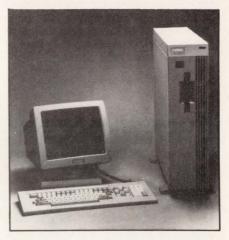

## MegaFrame". Now OEMs can offer a high-performance UNIX"-based system that can't run out of performance.

**OEMS can now deal cost-effectively** with the problems encountered when user applications produce computing demands that outstrip the capabilities of conventional systems.

Convergent Technologies' MegaFrame is a revolutionary new UNIX-based super-minicomputer—so innovative in its architecture that it represents the ultimate in multiuser systems design. It grows exponentially from a system offering minicomputer-level performance to an enormously powerful engine serving as many as 128 users with 36 parallel processors, 24 megabytes of RAM and gigabytes of disk storage.

No other system can match the MegaFrame's potential for field expansion. It enables manufacturers and systems builders to keep pace with today's requirements for more and more computing services...but *not* at the cost of discarding hardware or performing expensive CPU upgrades.

MegaFrame's architectural breakthrough. Dependence on traditional single-CPU shared-logic architecture is the root of systems bottlenecks.

Convergent's response: a novel system utilizing *multiple* specialized processors to distribute workloads for optimum performance—even if user needs are unpredictable or subject to rapid change.

MegaFrame's virtual memory Applications Processors each have a 32-bit CPU, up to 4 Mbytes of RAM and run a demand-paged version of UNIX System V. Up to 16 of them can operate in parallel.

The File Processors effectively function as back-end machines providing DBMS, ISAM and other disk-related services. Up to six File Processors each with four disks can operate in parallel.

Terminal and Cluster Processors can also be added—the latter serving front-end communications needs. They off-load communications from the other processors by running protocols such as SNA and X25 networks.

## Convergent Technologies Where great ideas come together

MegaFrame's daisy-chained cabinets offer total expansion potential of up to 36 slots. OEMs configure the system needed for specific applications simply by adding the correct number/combination of processors.

**Flexibility in applications development.** Inclusion of one or more Applications Processors allows running UNIX System V. All standard UNIX tools are provided, along with COBOL, FORTRAN-77, BASIC interpreter and compiler, plus Pascal.

The "least-cost solution" to serving a wide range of UNIX-systems needs, MegaFrame has won acceptance from OEMs in the U.S. and abroad. The uniqueness of its modular design, its versatility in providing upgrade-path options and its price/performance advantages give it market-share potential of outstanding dimensions. The system that will grow on you starts at a

The system that will grow on you starts at a very attractive price: about \$20,000 for a system that effectively supports 16 users. Send now for a comprehensive Information Package including reprints of magazine articles. It explains how Mega-Frame's growth potential can impact favorably on your plans for growth in the UNIX market.

Convergent Technologies, Data Systems Division, 3055 Patrick Henry Drive, Santa Clara, CA 95050. Phone: 408/980-0850. Telex: 176-825.

## MiniFrame<sup>™</sup> the entry-level multiuser UNIX system.

Starting at under \$5,000 for a single-user system, Convergent's MiniFrame offers outstanding capabilities for small to medium sized organizations running large UNIX-based applications. Utilizing an MC68010 microprocessor operating at 10Mhz, with no wait states, it provides impressive CPU speed – com-parable to VAX™-11/750 running the AIM<sup>™</sup> Benchmark. MiniFrame features virtual memory management, with demand-paged implementation of UNIX System V. It runs as many as eight terminals, with up to 50 Mbytes of integral mass storage. MiniFrame and MegaFrame are object-code compatible, allowing OEMs to offer a complete family of systems unrivaled in price/performance characteristics.

MiniFrame and MegaFrame are trademarks of Convergent Technologies, Inc. UNIX is a trademark of Bell Telephone Laboratories, Inc., VAX is a trademark of Digital Equipment Corp.

# give you 150 ns speed $\mu$ A power. Pick a winner.

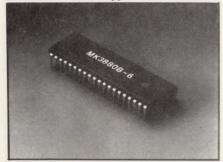

When you need the 256K ROM with state-of-the-art speed, Motorola has it—the 150 ns MCM63256.

On the other hand, you might be searching out the lowest-power 256K ROM available. Motorola has that, too—the 50 uA MCM65256.

#### Get a lot. Trade-off little.

Whether your requirements run to super speed or ultra-low power, Motorola satisfies them. And you don't make severe trade-offs to get the performance you need most.

The high-density HCMOS MCM65256 low-power leader's maximum power dissipation is only 50  $\mu$ A in standby with full rail inputs, 5 mA in standby with TTL inputs and just 50 mA, active. However it still offers a fast 350 ns access time, and just 100 ns max. from output enable.

Certainly speed is the biggest attraction of the high-performance N-channel HMOS MCM63256, yet maximum power dissipation is a low 15 mA, standby, and 100 mA active.

There's also a 200 ns version of the MCM63256, and matching highspeed 128Ks are available, too.

## All in the industry-standard 28-pin family.

Beyond the ideal differences in their speed and power, these advanced-technology ROMs share many common operating characteristics and benefits, including availability now in the JEDEC-standard 28-pin dual in-line package.

They utilize late-process programming to minimize prototype turnaround, and they require no clocking on the chip enable because they're static. They operate from single +5 volt supplies, shift automatically into the power-down mode, and offer user-selectable address and maskprogrammable chip and output enables.

#### **Rewards** offered.

You can buy 256K ROMs elsewhere, but you can't collect the rewards of top performance with fast turnaround at Motorola prices when you do. So reward yourself by ordering now through your Motorola sales office or authorized distributor.

At the least, before making a final decision, you owe yourself additional information. Write for it or send the completed coupon to Motorola Semiconductor Products Inc., P.O. Box 20912, Phoenix, AZ 85036. **Highest Speed**

MCM65256

MCM63256

|  |   | MCMES256 |   |

|--|---|----------|---|

|  | 3 | M61256   |   |

|  |   | 1        |   |

|  |   |          |   |

|  |   |          | _ |

Lowest Power

| N          |          |

|------------|----------|

| <b>A</b> ) | MOTOROLA |

|            |          |

## **Only One Company Makes Interfacing**

**Q-BUS**

**Q-BUS**

8" & 14" WINCHESTER—SMD I/0 • RL01/RL02, RP02/RP03, RK06/RK07 & RM02/RM05/RM80 emulations

WINCHESTER 51/4"-ST506/412 & DMA I/0 • RL01/RL02, RK06/RK07 emulations

8" & 14" WINCHESTER—SA4000 & PRIAM I/0 • RL01/RL02, RP02/RP03 emulations

CARTRIDGE—14" DISK—DIABLO 44B • RK05 emulation

FLOPPY DISKS—SA850 & SA450 I/0 • RX02 emulation

Compatible with DEC's family of RT-11, RSX-11, RSTS, UNIX and VMS operating systems.

## Your DEC Computer So Easy

1/2" TAPE—CONTROLLER/COUPLER PERTEC I/0 • TM-II, TSV05/TS-II/TU80 emulations

1/4 " TAPE—KENNEDY 6455 & CDC SENTINEL I/0 • TM-II/TS03, TS-II/TU-80/TSV05 emulations

8" & 14" WINCHESTER—SMD I/0 • RP02/RP03, RK06/RK07, RM02/RM05 emulations

UNIBUS

1/4" TAPE—CDC SENTINEL I/O • TS-II emulation

1/2" TAPE—CONTROLLER/COUPLER PERTEC I/0 • TM-II, TS-II/TU80 emulations

DISTRIBUTED LOGIC CORPORATION

1555 South Sinclair • P.O. Box 6270 • Anaheim, CA 92806 • (714) 937-5700 • TLX 6836051 64-A White Street • Red Bank, NJ 07701 • (201) 530-0044 Chester House, Chertsey Road • Woking, Surrey, England GU 21 5BJ • (04862) 70262/7 • TLX 859231 DILOGI G • FAX (04862) 62666 CIRCLE 15

## Mr. Systems Supplier: We packed more system into a smaller box and added industrial LAN capability at a lower cost.

We have a box for you. If you are systems people who need a more compact data collection station *plus* high or moderate speed local area networking.

Multidrop communications allows many sites to exchange data with one host processor. Larger systems, and systems requiring shorter response times, connect to the host by a 1Mbps cable. Smaller systems, and systems covering wide areas, connect by 9600 bps voice frequency lines. Single level Class B contact inputs can expand from 16 to 32. Outputs of up to 8

card readers can connect to a single unit. Expansion unit doubles available I/O. The Miniplex interfaces with a wide range of analog and digital I/O devices. Call or write Carl Rohr or Don Babbitt for complete specs.

## •Smaller MUX

- Integral modems

- •Multiple Interfaces

- Alternative networking

- Easy expansion

- •Custom packaged for your application: •Building automation

- Utilities

- Factory automation

Petrochemical

- •And many more

15 Ethan Allen Highway / Ridgefield, Connecticut 06877 / (203) 544-9371

Network Communications

CIRCLE 16

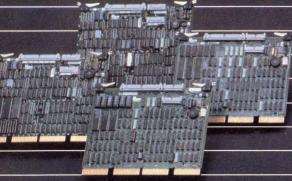

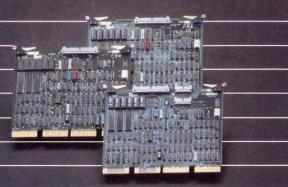

## **Compatible memories bridge gaps for DEC minicomputers**

The rapid expansion of main memory capacity in minicomputers has triggered calls for add-in and add-on memory and new demands for massive secondary storage. Demand for disk drives storing 300 Mbytes and more has soared, followed by a rise in demand for tape subsystems packing over 100 Mbytes on a single reel.

Independent manufacturers of minicomputer peripherals are thriving in this environment because of the rapid growth of the minicomputer industry and the inability of CPU manufacturers to dedicate sufficient resources to build the variety of storage devices that their customers demand. The sheer number of DEC minicomputer installations makes DEC compatibles a particularly busy area.

Along with these demands for larger storage capacities, concerns about how fast the data can be passed to and from the CPU have grown. Brought about by the increasingly multi-user, online nature of the minicomputer's typical application, storage peripheral manufacturers have shown intense awareness of access time and have devoted much attention to its improvement. Minicomputers have benefitted most from the resulting developments because of their relative position on the cost/ performance curve. Since half of the total equipment cost in a computer installation is typically devoted to peripherals, a system in the \$100,000 range can afford the relatively high price associated with high performance peripherals such as tape and disk drives.

#### **Speed-critical applications**

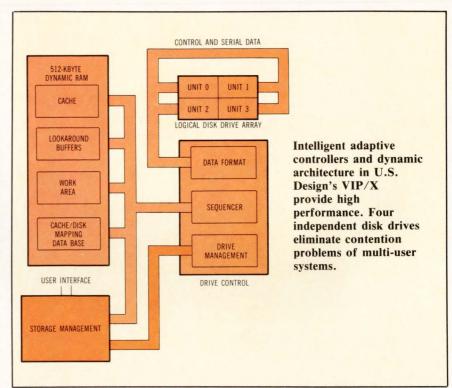

Several approaches result in more speed than can be achieved from a disk-based subsystem for realtime applications. U.S. Design Corp's (Lanham, Md) system can access 760 Mbytes of data in less than 10 ms. To

achieve this, the VIP/X manages multiple independent disk actuators. Its controller uses several microprocessors in conjunction with 512 Kbytes of onboard multiported cache memory. By operating each actuator independently, contention problems can be virtually eliminated in multiuser environments.

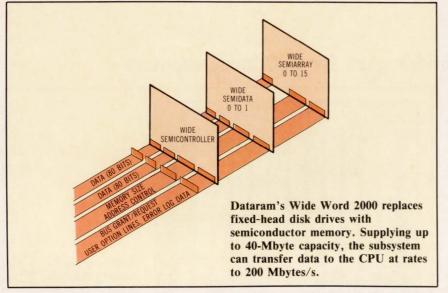

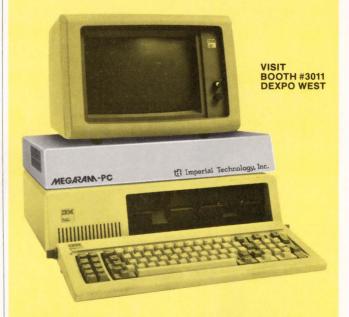

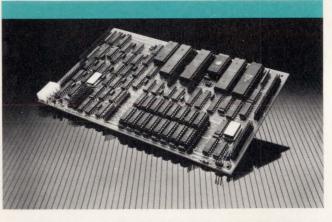

Another high speed approach uses solid state disk emulating systems. In this case, Imperial Technology Inc's (El Segundo, Calif) MegaRAM-11 supplies up to 16 Mbytes of data storage and directly emulates various DEC disk drives such as RK06 and RK07. Use of semiconductor memories eliminates the seek time that limits the access speed of disk drives. To serve applications in the 10-Mbyte/s range (typically the province of fixed-head disk subsystems), Dataram Corp (Cranbury, NJ) packages up to 40 Mbytes in a box that can supply data at a 200-Mbyte/s rate. Called Wide Word 2000, the memory subsystem uses 8-way interleaving and internal data words up to 160 bits wide to achieve these transfer rates. Typically, systems are dual-ported with one accepting high speed input and the other providing a link to the minicomputer.

To belong to the high performance minicomputer club, memory arrays must be large and provide fast access to data. Buying add-in and add-on *(continued on page 26)*

#### **Compatible memories**

(continued from page 25)

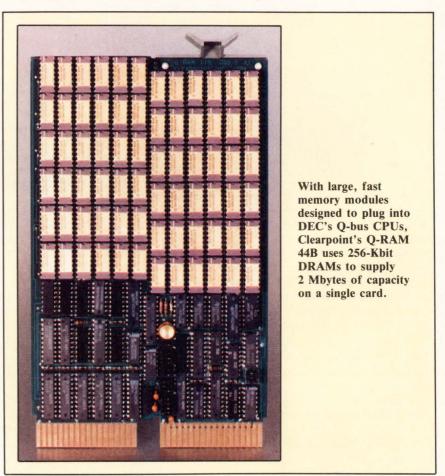

memories from outside vendors can save up to 50 percent, a major factor considering the size of most memories. Not only that, but these outside sources frequently use the latest in semiconductor technology (eg, 256-Kbit RAMs before they become available from the CPU vendor). Thus, memory can be extended without using more slots in the CPU backplane. These come in 64- to 1024-Kbyte versions for Q-bus machines and in 256 to 1024 Kbytes for Unibus and VAX systems.

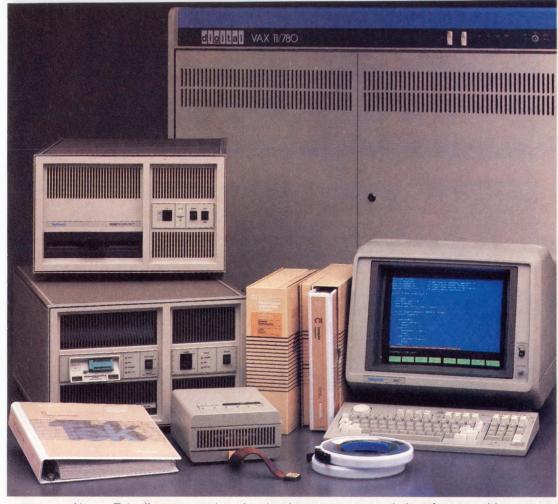

#### Faster, larger main memory

Equivalent to DEC's MS780-E, a field replacement memory system for VAX-11/780 uses 2048-Kbyte memory arrays to allow 32 Mbytes/backplane, instead of the original 16 Mbytes. Installed in the CPU cabinet with 4 Mbytes, EMCVT-780-4MB from EMC Corp (Newton, Mass) sells for less than \$27,000, 30 percent less than a comparable DEC upgrade. The system is fully compatible with the CPU and requires no modification the to VMS or Unix operating systems.

Raising main memory of the 11/750 to 8 Mbytes from its previous 2-Mbyte limit, a 2-Mbyte minimum upgrade kit from EMC can be field installed. The kit sells for \$11,500; additional 1-Mbyte cards are \$2450. National Semiconductor Corp, Memory Systems Div (Santa Clara, Calif) provides 256- to 1024-Kbyte memory arrays for both Unibus and VAX systems as well as 64- and 1024-Kbyte versions for Q-bus machines.

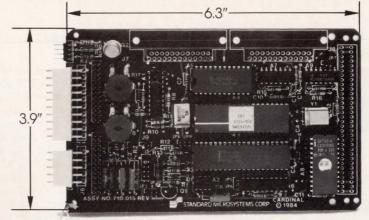

Implementing block mode DMA protocols on the Q-bus, ADAC Corp's (Woburn, Mass) 18MP-1024 supplies timing, control logic, refresh, parity control, and status register. Featuring 22-bit addressing, dual-height, half-quad 256-or 512-Kbyte 18 MP boards allow plugprogrammable selection of 18-bit addressing. General Robotics' (Hartford, Wis) MSV11-Q replaces two or more DEC MSV11-P modules. The 1-Mbyte single-quad height board has 255-ns read access time, 280-ns write time. A high speed MSV11-QH version performs about 40 percent faster. Capable of read and write access time of 60 ns, the Q-RAM 11B from Clearpoint, Inc, (Hopkinton, Mass) uses 64-Kbit DRAMs to supply 512-Kbyte capacity on a dualheight card. A 2-Mbyte module, the Q-RAM 44B uses 256-Kbit DRAMs and offers 85-ns read and 60-ns write access times.

#### Supporting mass storage demands

Virtual memory addressing capability of systems like the VAX runs to 2 Gbytes. Supported by the Digital Storage Architecture (DSA), disk drives and tape drives capable of handling masses of data can be mixed and matched to fit system needs. Storage Module Drive (SMD) Winchester disk drives and half-inch tape drives typically take care of online storage tasks. Transfer rates for disks run in the 2-Mbyte/s and up range with tape drives capable of rates to 160 kbytes/s.

Matching the capacity of DEC's top of the line RA81 disk drive, the Aquarius II, a high performance data storage system, meets capacity needs of VAX and PDP-11. Designed for use over VAX CMI, SBI, or Unibus, the unit from First Computer Corp (Westmont, III) supplies 474 Mbytes on a Fujitsu Eagle Winchester disk drive and provides magnetic tape backup using a GCR CacheTape drive from Cipher Data. The system accommodates up to three disk drives and sells for from \$29,990 to \$51,450.

A Winchester/cartridge tape combination, Emulex's Medley supplies 35 or 110 Mbytes of formatted storage as well as 70 Mbytes of streaming tape backup. Using the Small Computer System Interface, the subsystem is operating system- and diagnostics-transparent to Q-bus and Unibus systems. The host adapter uses DEC's mass storage control protocol to adapt to various disk drives without operating system patches.

Cyclone series subsystems from Qualogy Inc (San Jose, Calif) offer storage capacities from 36 to 120 Mbytes formatted for Q-bus computers. Fully compatible with DEC's DSA, the subsystems incorporate Maxtor's 5-¼-in. Winchester disk drives with a quarter-inch cartridge tape drive (Kennedy 6455) capable of storing Mbytes. Average access times of 30 ms on the disk drive are enhanced by a complex data buffering scheme on the controller/interface that facilitates fast transfer of data to and from the Q-bus.

GCR tape drives for DEC machines provide easy backup for large data bases. Aviv's (Woburn, Mass) GCR-125 Tri-Density tape system, for example, can pack 140 Mbytes on a single tape reel. Recording 6250/1600/800 bits/in. at 125 in./s, the drives connect with DEC and support Pertec and Telex interfaces.

Interfacing to VAX, PDP-11/70, and Unibus machines, the System Industries' (Milpitas, Calif) 9621 operates at twice the speed of DEC's TU80. At 50 in./s, the dual-density tape system records at either 1600 or 6250 bits/in. and transfers data at rates up to 312 kbytes/s. Its integrated formatter/controller connects to Unibus, 11/70 Cache, 11/750 CMI, and 11/780 SBI.

Digi-Data Corp's (Jessup, Md) half-inch magnetic tape systems store up to 138 Mbytes on a single reel. Compatible at the system level with VAX, PDP-11, and LSI-11, the startstop or streaming drives record at speeds from 12.5 to 125 in./s.

Designed for integration into various vendors' CPUs, GCR tape subsystems from California Computer Group (Costa Mesa, Calif) store 180 Mbytes on a single reel. Based on StorageTek's dual-density model 2920 Avalanche or Kennedy Co's tridensity model 9400 drives, the systems record on standard 10.5-in. reels of tape. Controllers from Emulex, Western Peripherals, Rianda, Spectra Logic, Macrolink, or Dylon serve as the drive-computer link.

#### Making the connection

Fixed-media Winchester drives from Control Data, Ampex, Century Data, Disk Tech One, Fujitsu, Kennedy, and Tecstor connect to Unibus systems over Distributed Logic Corp's (Garden Grove, Calif) DU218. This SMD interface-compatible RM02/RM05 controller provides software transparency with RSTS and RSX-11 operating systems. In addition, it is interchange compatible when used with removable pack drives such as the 80-Mbyte CDC 9762 and 300-Mbyte CDC 9766.

Emulating RM02, 03, 05, or RK06/07 disk drives, controllers from MDB Systems Inc (Orange, Calif) are software and diagnostic transparent to DEC operating systems as well as Unix and TSX. Interfacing SMD disk drives to Q-bus,

Unibus, and VAX systems, firmware in the controller accommodates changes in drives by interrogating a switch as to drive in use and emulation mode. It automatically structures the firmware to identify drives by number of cylinders, sectors, and heads as well as number of blocks in each logical unit.

Transfer rates to 2 Mbytes/s for disk and 800 kbytes/s for tape are supported by Spectra Logic's (Sunnyvale, Calif) Spectra 121 disk/tape controller for Unibus systems. These data rates are achieved by a dual sequencer design based on a 16-bit 29116 microprocessor. Emulating RM02/05, RM80, and RP06 disks and TS11 tape drives, the board is compatible with RT-11, RSX-11M, RSX-11M-Plus and RSTS/E operating systems. Separate buffering for tape and disk allows simultaneous transfers at full speed while eliminating data late errors.

All those attempting to slipstream DEC's systems with storage devices are aided by the relatively open system buses. While hardly in the public domain, information necessary to gain access to these proprietary buses is certainly not guarded with the fortitude that IBM applies. In addition, Digital's DSA readily accepts performance variables, making the job still easier for those who wish to supply mass storage needs.

> -Peg Killmon, Senior Editor

### SYSTEM TECHNOLOGY (continued on page 30)

### It pays to communicate

You can further your career by writing technical articles about the advanced work you're doing. Also, we pay an honorarium for all manuscripts that we publish. For a free copy of our Author's Guide, circle **502** on the Reader Inquiry Card

# EMULEX IMPROVES AND TAPE BACKUP BY

Emulex sets the pace with three great storage subsystems for the full range of DEC QBus and Unibus systems. Whether you need Winchester disk, cartridge disk, ¼" streaming tape, or a combination unit, you'll be a step ahead with Emulex.

## **INTRODUCING VAULT.**

Emulex rises above the competition with the Vault." This 70-MByte tape subsystem is built around the CDC Sentinel ¼" cartridge tape streamer and uses Emulex's own TC05 (QBus) or TC15 (Unibus) tape coupler to interface with your system. The Vault is totally software transparent to standard TS11 software. So this compact tape unit looks just like a big ½" TS11 subsystem to your operating system and diagnostics.

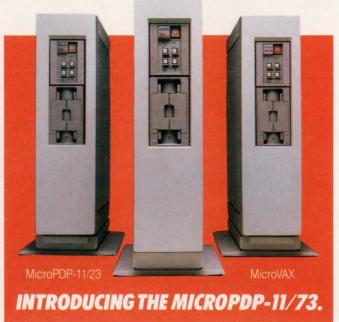

Vault comes complete with power supply in a single compact cabinet. It's the perfect backup unit for smaller QBus systems such as the MICRO/PDP-11 and MICRO/VAX.

## PRESENTING SABRE.

SABRE<sup>™</sup> is a sharp solution for LSI users who need more storage and backup. It packs 31.2 MBytes of main storage onto a 5¼" Winchester and 10.4 MBytes of backup onto a removable 8" cartridge disk.

## And since SABRE

is an exact RL02 emulation, all existing operating and diagnostic software can be used as is.

SABRE is 5¼" high and slips into any 19" RETMA enclosure. A desktop version is also available. Both come complete with power supply, host adapter and connecting cables.

SABRE needs only one-eighth the space and onequarter the power of four RL02s. And it eliminates the need for a separate system bootstrap, bus terminator and clock control board.

OEC, QBus, Unibus, TS11, MICRO/PDP11, MICRO/VAX, LSI and RL02 are trademarks of Digital Equipment Corporation CDC and Sentinel are trademarks of Control Data Corporation

GSA Contract #: GSOOK8401S5575

# DEC DISK STORAGE LEAPS AND BOUNDS.

## ANNOUNCING MEDLEY."

Emulex has another winning combination with the Medley" Winchester cartridge tape subsystem. It gives you either 35 or 110 MBytes of formatted storage and up to 70 MBytes of streaming tape backup. The Medley is fully software transparent to the operating system and diagnostic software of QBus and Unibus CPUs. And it uses the powerful and versatile Small Computer System Interface (SCSI) which keeps your options open for peripheral expansion.

> Medley is interfaced to the system with a TC05/ TC15 tape coupler and a UC02 (QBus) or UC12 (Unibus) host adapter. By using the Mass Storage Control Protocol (MSCP), the UC02 and UC12 allow the operating system to utilize the precise characteristics of the Winchester disk drive without patches or modifications to the operating system. For convenience, Medley's disk drive, tape drive

and power supply all fit into an attractive cabinet that easily mounts in a standard 19" rack. The Medley is also available in an attractive desktop version.

Find out how Emulex subsystems can keep you ahead of

the game. Call toll-free (800) 854-7112. In California (714) 662-5600. Or write Emulex Corporation, 3545 Harbor Blvd., P.O. Box 6725, Costa Mesa, CA 92626.

CIRCLE 17

## Magnetic bubble memories making a comeback

Bubble memories are demanded in more key computer equipment today than anyone could have predicted 20 years ago. For the most part, the type of equipment housing bubbles is designed for applications in harsh environments. Original predictions in the 1960s expected magnetic bubble memories to replace magnetic disks. Subsequent forecasts in the 1970s told of the bubble's demise as a nonvolatile memory alternative. Both claims have proved inaccurate in the reality of the 1980s.

Inherent advantages of magnetic bubble memory over other nonvolatile memories have held designers' interest. Now, 1-Mbit chips are readily available and 4-Mbit bubbles are slated for production in late 1985. In fact, experts expect bubble memory density to increase to 64 Mbits by 1988. Despite the fact that this potential capacity is provided in a much smaller package than movable disks can hope to occupy, only a handful of companies are active in magnetic bubble memory development. Only two American manufacturers (Motorola and Intel) and three foreign producers (Fujitsu, Hitachi, and Sagem) are offering bubble chips and the heavy support that these chips demand in both control circuitry and interfaces.

To be sure, bubble memories are not the simplest chips to produce. Invented by Andrew Bobeck at Bell Labs in the late 1960s, bubble memories have a history of support by several U.S. semiconductor companies. These have included Texas Instruments, National Semiconductor, Rockwell International, Bell Labs, Motorola, and Intel. Now, only Motorola and Intel remain in the running with the Japanese and the French. Even Bell Labs' Bobeck sadly admits that his research group no longer pursues development of magnetic bubble memories.

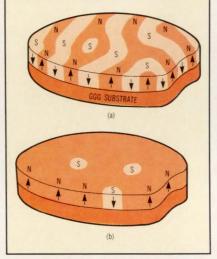

In 1966 Bobeck found that a magnetic thin film can store digital information by controlling the presence or absence of tiny magnetic domains in the film. These magnetic domains resemble bubbles, thus their name. They are formed perpendicular to the surface of a gadolinium gallium garnet substrate when a vertical magnetic field of appropriate intensity is applied. By changing the horizontal magnetic field, the bubbles can be moved within the film. The bubbles function as a memory when a one or zero is assigned to the presence or absence of a bubble at a given position in the thin film.

A magnetic garnet crystal grown on a gadolinium gallium garnet (GGG) substrate is used for the ferromagnetic film from which bubbles are formed. In the presence of a weak magnetic field, the magnetic domains form a serpentine pattern (a). When the field strength is increased, the domain becomes circular (b). By changing the horizontal magnetic field, the bubbles can be moved within the film.

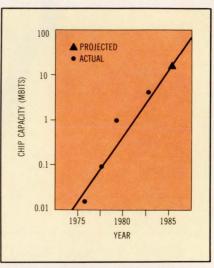

Bubble memory technology has made great advances in bubble density and chip size. Plotting the capacity attained by bubble devices as a function of the year in which they were introduced suggests that capacity will quadruple every two or three years. The projection is based on success in developing and manufacturing of bubble memories that use ion- implanted contiguous disk technology. With this technology, stress created by ion implantation induces an inplane anisotropy in the surface layer of the garnet chip. Domain walls forming near pattern boundaries when the in-plane magnetic field is applied have poles that attract the bubble domains. When the in-plane field rotates, the charged walls circulate around the nonimplanted area, causing the bubble domains to propagate.

This technology using ions implanted on contiguous disks offers a gain of 4 to 16 times the density of currently manufactured permalloy asymmetric technology. Now under research, this technology will require changes in manufacturing techniques or chip architecture before the bubble memory devices can be produced. According to Mark Kryder of Carnegie-Mellon University (Pittsburgh, Pa),

"The contiguous disk technology remains the most promising high density technology and will probably become dominant when the permalloy technology reaches its limits in producing bubble memory cells smaller than 4 to 6  $\mu$ m."

For bubble memories to see widespread use, their price per bit must become less than that of other magnetic media. In the last four years, bubbles have become the least expensive solid state alterable nonvolatile memory. Today, however, mechanical mass storage devices still cost less per bit than bubbles. Mechanical devices will remain more cost effective, according to Mark Eisele, marketing manager at Intel Corp (Santa Clara, Calif). "Bubble memories will never be lower in cost per bit than floppies or Winchesters; and the garnet used by bubbles as a memory storage substrate will never cost less than the plastic substrates used in diskettes," he says.

Bubbles' access times, however, can compete head-on with those of mechanical disks. Motorola, for instance, has a 1-Mbit chip with an *(continued on page 32)*

If you're trying to support more than 4 programmers doing 8086- or 8080-family software with stand-alone microprocessor development systems, here's a way to increase your productivity 25%:

Buy our MicroSET-86<sup>®</sup> or MicroSET-80<sup>®</sup> software cross-development tools and a DEC VAX or DG MV/Family system to run them on. You'll save enough on your first major project to pay for the computer system.

Of course, if you already have access to a VAX (or MV or any IBM-compatible main-frame), you're that much further ahead.

People with experience in cross-development know it's the best way to tackle big software projects. And only First Systems' MicroSET gives you the industry's most complete, most powerful cross-development tools, plus your choice of five efficient systems implementation languages.

## THE ONLY COMPLETE MULTILINGUAL DEVELOPMENT SYSTEM FOR THE 8086 FAMILY

MicroSET-86 lets you program in four powerful high-level languages: Pascal, C-86, FORTRAN-86, and PL/M-86.

An assembler is also available, although First Systems compilers generate such fast, compact code that you may find you have little need for it (benchmark data available on request). You also get a linker/locater that allows combining modules written in different languages.

Using our high-level Cross-Debugger to control execution on the target system, you can locate, fix, and re-test an erroneous line of code in a fraction of the time it takes using other methods. It's no wonder that MicroSET users routinely shave months off typical development schedules — while producing more reliable, more maintainable systems.

MicroSET-86 supports the entire 8086 family: 8086/8088/186/286 and 8087. It works with in-circuit emulators you may already own, and has a complete set of host-target communication programs and other valuable utilities not available elsewhere.

## ANNOUNCING NEW LANGUAGE-COMPATIBLE 8-BIT TOOLS

First Systems now supports cross-development of 8080/8085/Z-80 software with MicroSET-80, consisting of PL/M-80 compiler, assembler, linker/locater, cross-debugger, plus utilities.

Request complete information today. And take the first step toward your own free computer.

Intel is a trademark of Intel Corporation. VAX is a trademark of Digital Equipment Corporation. Z-80 is a trademark of Zilog, Inc. © 1983 First Systems Corp.

Products for productivity.

865 Manhattan Beach Blvd., Manhattan Beach, CA 90266 (213) 546-5581 TELEX: 298086 FIRSYS

## Magnetic bubble memories

(continued from page 30)

access time of 11.5 ms, better than many mechanical media having an equal amount of storage capacity. Access time of bubble memory devices depends on chip architecture, chip capacity, and the frequency of the drive or current used to access the data.

All current bubble memories use major-minor loop or block-replicate chip organization. In these organizations, data in parallel "minor loop" shift registers are accessed by another shift register (major loop or output path) that leads to a detector. The access time to the first bit in a block of data is roughly proportional to the number of bits in the minor loop. This, in turn, is proportional to the square root of the chip capacity.

To avoid an increase in access time while increasing chip capacity, manufacturers have put multiple detectors on a chip, and raised drive frequencies. Detectors occupy considerable space and require relatively expensive associated sense electronics. This places a limit on the number of detectors a chip can hold, according to Gus Hermann, marketing manager at Motorola.

As a result, manufacturers are offering full memory boards that contain all the necessary control, drive, and sense electronics, as well as subdividing memory capacities into 128-, 256-, 384-, and 512-Kbyte chunks. Motorola's 1-Mbit board and Fujitsu's Multibus-compatible circuit card are only two such examples. Fujitsu's FBC504M4M board, for instance (*Computer Design*, June 1, 1984, p 202), features a 12.5-ms access time and uses a single 5-V power source.

Intel has chosen a page size of 64 bytes, instead of the more commonly used 32 bytes, that uses fewer storage loops but more bits per loop. This ensures a higher reliability at the expense of a slower access time (40 ms). Intel's chip can operate over wider temperatures because its replicated bubble generator is less sensitive to temperature extremes and requires much less current than the nucleating generator used by other manufacturers. In addition, Intel's bubble memory chips become completely interchangeable at the component level with their support ICs.

According to Intel's Eisele, the bubble memory market has segmented into three temperature ranges, each suited to different applications. The most cost-effective bubble devices for commercial applications are rated for temperatures greater than 10 to 55 °C. In the 40 to 50 percent price premium are the industrial applications with bubbles operating at higher than the 0 to 70 °C range and military applications covering the full -20 to 85 °C range.

When introduced in the 1970s, bubbles were limited to switching systems and numerical control applications. Today, costs have gone down somewhat, and reliability has been enhanced. The mean-time between failures of bubble memory systems is now 1000 times better than that of the typical microfloppy disk drive. As a result of these improvements, bubble memories are now used in measuring instruments, medical equipment, building control and hotel systems. point-of-sale and banking terminals, as well as in automation equipment including personal computers, portable word processors, and facsimile machines.

This widespread demand has prompted manufacturers to include large capacity memories in their product lines. All producers are expected to sample 4-Mbit devices within the next year. Fujitsu is also aiming to develop 16-Mbit bubble memories in the future. The company claims these devices will be competitive with magnetic drum and disk units that have a storage capacity of up to 100 Mbytes.

One firm has already introduced a mass storage peripheral that uses a 1-Mbit bubble memory to replace floppy disk drives in computer systems specifically designed for high reliability applications and hostile environments. Hicomp Computer Corp of Redmond, Wash is offering 0.5 or 1 Mbyte of bubble memory in an enclosure the size of an 8-in.

The rate of progress of chip capacity for the years when bubble memories have been introduced can be extended to project that by 1988, a 64-Mbit magnetic bubble memory chip will be in production. By that time, the cost per bit for bubbles should settle at 3.5 cents per bit, as compared to 10 cents per bit today.

floppy disk drive (*Computer Design*, Oct 15, 1984, p 154). The MBM-1A can be interfaced to a computer system as either a floppy disk drive or as a block access peripheral.

Using a Shugart-compatible floppy disk controller, the unit can operate as an alternative to either four 5<sup>1</sup>/<sub>4</sub>or four 8-in. drives. In the block access mode, individual blocks of memory can be accessed in 512-byte block segments. An internal switching power supply guarantees protection from line surges and data dropouts.

After many years of contradictory predictions, it remains to be seen whether offerings such as these are a prelude to a new breed of magnetic storage devices, on par with rotating disks. One thing, however, is certain—as the appetite for online storage increases, and as equipment becomes smaller in size, magnetic bubble memories can become another viable choice for computer systems.

> -Nicolas Mokhoff, Senior Editor

SYSTEM TECHNOLOGY (continued on page 34) Solid-state magnetic-bubble memory from Bubbl-tec Mass storage that works where disks don't

> Once upon a time, computing was done only in nice, clean places, and a spinning disk could handle the mass storage job quite nicely.

But, no more. Now computers are down on the factory floor, up in airplanes and out in the field. For this new world of applications, you need *solid-state* mass storage, like Bubble-tec magnetic-bubble memory systems. They can stand up to the dirt, dust, temperature extremes, shock and vibration that knock out disks.

Bubbl-tec systems provide battery-free non-volatile mass storage from 32 Kbytes to 8 Mbytes, with extremely fast access to every data block, And our systems plug directly into your microcomputer bus—no need for another chassis or power supply.

> Since 1979, we've been shipping solid-state mass storage systems for every popular microcomputer bus, including Q, MULTI, STD, S-100, VERSA and VME. In fact we have more systems in the field than any other bubble-system supplier.

So, if you don't want to contend with disk deterioration, head crashes, and mechanical breakdowns, contact Bubbl-tec. Our mass storage solutions have a solid foundation.

VMEbus<sup>m</sup> Bubble Systems provide up to 8 megabytes of mass storage

STDbus Bubble Systems are

for 8088, 8085, Z80, 6809

6800 Sierra Court, Dublin, California 94568 Telephone: 415/829-8700 • TWX/Telex: 910/389-6890

#### CIRCLE 19

BUBBL-TEC INTERNATIONAL DISTRIBUTORS: West Germany: Scantec GmbH 089-859-8021 • Italy: Telcom 02-4047648 • France: Microel S.A. 6-9070824 • Switzerland: Micro-System-Technik, AG 01-520355 • Norway: HCA Melbye 02-106050 • Sweden: TH Elektronik AB 08-362970 • South Africa: Electronic Building Elements PTY, Ltd 12-46-9221/7

Bubbl-tec is a registered trademark of PC/M, Inc. • DEC is a registered trademark of Digital Equipment Corp. • MULTIbus is a registered trademark of Intel Corp. Q-Bus, RL02, RX02, RX01, TU58 are trademarks of Digital Equipment Corp. • VERSAbus and VMEbus are trademarks of Motorola, Inc.

Q-Bus™ Bubble Syste emulate DEC,\* RL02™

TU58

BX02TH BX01TH

minimu

### Graphics standards get boost from IBM announcement

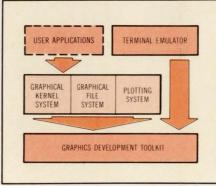

After a long wait for the American National Standards Institute and the International Standards Organization to put their stamps of approval on graphics standards, the industry is going ahead with *de facto* standards on its own. The die was cast when IBM announced its PC Professional Graphics Series, thus throwing its weight behind three proposed standards: the Graphical Kernel System, the Virtual Device Interface, and the Virtual Device Metafile. The Professional Graphics Series is a software package from Graphic Software Systems (GSS) in Wilsonville, Ore.

IBM could hardly have picked a supplier with closer ties to the standards-making process. Several GSS executives are members of the ANSI X3H3 committee, which is evaluating the GKS, VDI, and VDM standards. The chairman of the committee, Peter R. Bono, is GSS' director of strategic technology. GSS President Tom Clarkson and Vice

President Burt Perry are both voting members of the same committee. In working with GSS, IBM is virtually guaranteed that its products will be compatible with the standards ANSI approves.

"This is the first time in the graphics standards effort that a major supplier has endorsed the concept of standards," says GSS Marketing Director Mark Rawlins. And, Rawlins notes, the endorsement is a significant turnaround for IBM. IBM's PC Professional Graphics Series implements the proposed Graphical Kernel System standard as part of its own Graphical Kernel System. The Graphical File System implements the Virtual Device Metafile. The Graphics Development Toolkit provides a Virtual Device Interface.

"They are supplying software that is completely nonproprietary. It is almost in the public domain. Anyone can write to ANSI, get a functional specification, and do the job themselves," he says.

Because the VDI standard provides a device-independent interface, the user can mix and match peripherals from different suppliers. Moreover, an application is not restricted to a particular operating system, such as MS-DOS. An application written for the IBM graphics package can run with any environment once the code is recompiled and linked.

Since the GKS and VDI were already well on their way to becoming *de facto* standards, IBM's announcement should not shock the industry. Rather, it will strengthen current trends. A standard competing with GKS—Core—is still being pushed by the Association for Computing Machinery, but ISO and ANSI have chosen GKS. A number of companies are working on implementations of GKS and VDI.

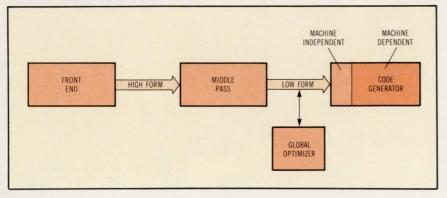

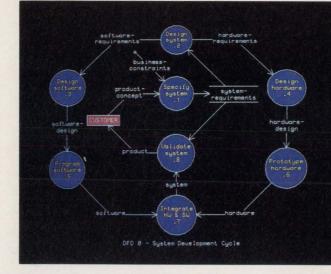

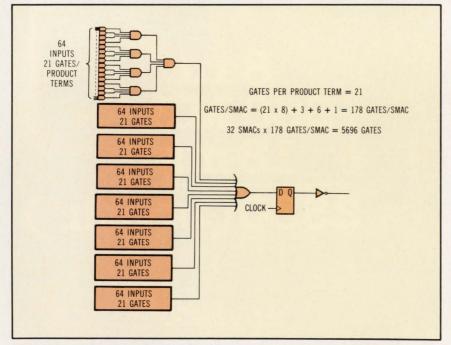

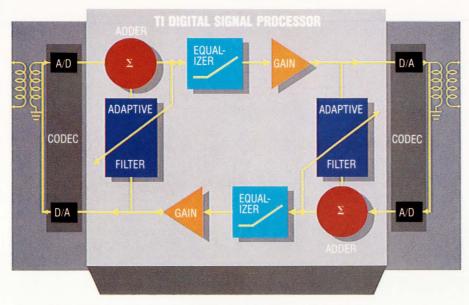

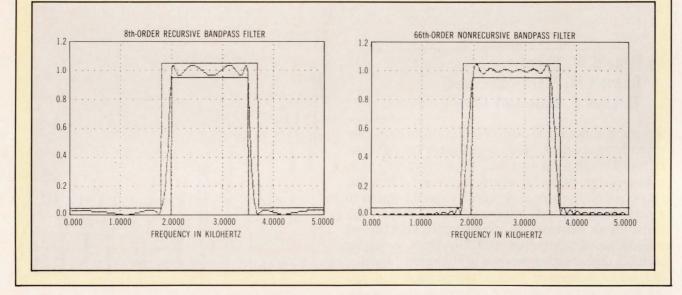

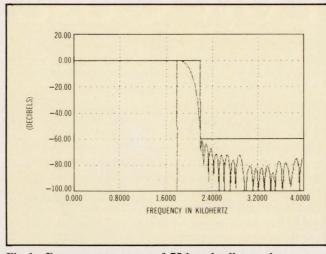

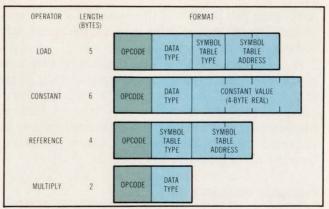

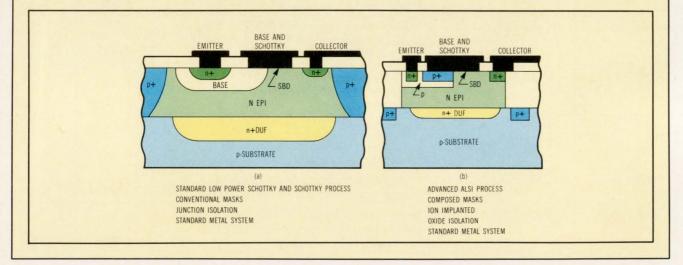

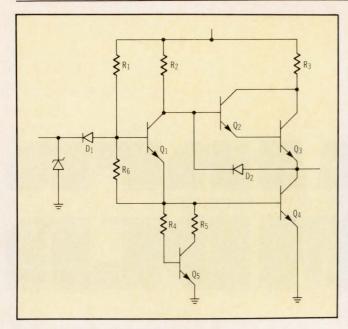

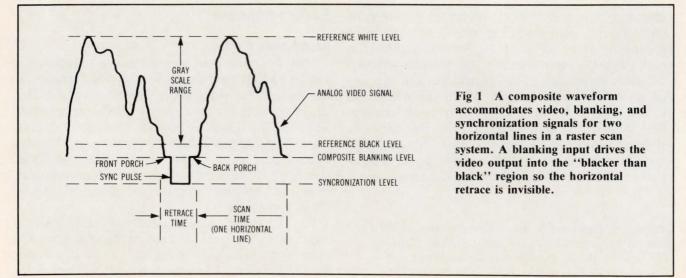

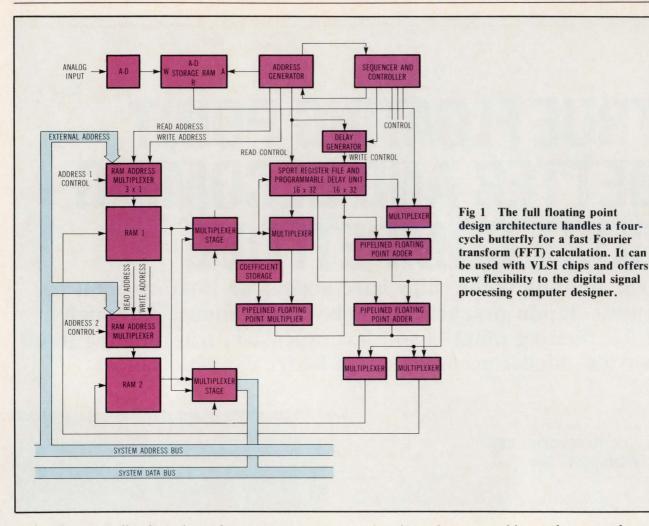

### Layers of standards