A PennWell Publication

OCTOBER 15, 1984

**DIGITAL SIGNAL PROCESSING**

**GONPUTER DESIGN** THE MAGAZINE OF COMPUTER BASED SYSTEMS

SI CONTROLLER SIMI LITIES DISK INTERFACING

DISTRIBUTED MICROS BOOST POWER OF TEXT/GRAPHICS SYSTEMS

**STD BUS BOARD CUTS DATA ACQUISITION COSTS**

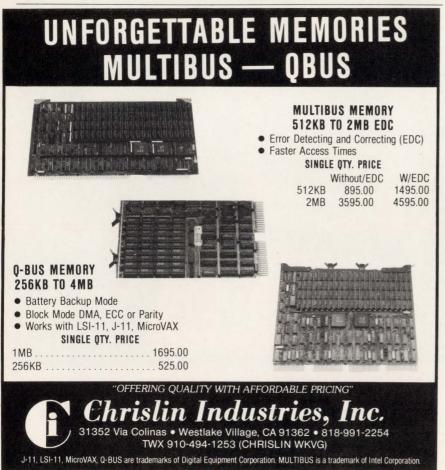

## IN OUR MEMORIES.

## THERE'S NO LAPSE

#### AT NEC, YOU'LL FIND QUALITY MEMORIES IN EVERY CATEGORY.

#### All in one place.

Chances are, we have the exact memories you're looking for. Leading-edge 25ns 16K static RAMs. 64K static RAMs. 128K UV EPROMs. New 256K DRAMs. And our remarkable one *megabit* ROM-the highest density ROM in the world.

These aren't promises of things to come. They're here. Now. And ready for your next design.

You can trust our memories. At NEC, quality is understood. Fact is, you can expect 100% burn-in, standard. And a guaranteed AQL of 0.1%. Which means, with NEC, your memories will be worry-free.

#### A complete package deal.

Be reminded, our memory devices come in a variety of packages. Standard and skinny. Plastic and ceramic DIPs. Flat packages and leadless chip carriers.

So if you have designs on the future, remember NEC. For a never-ending line of quality memories.

#### NEC Memory Products

|                         |      | Technologies             |      | Densities |    |    |    |    |     |     |     |      |      |    |

|-------------------------|------|--------------------------|------|-----------|----|----|----|----|-----|-----|-----|------|------|----|

| Type of Memory          | CMOS | <b>MMOS</b> <sup>1</sup> | NMOS | B/P       | IK | 2K | 4K | 8K | 16K | 32K | 64K | 128K | 256K | IM |

| Static RAM <sup>2</sup> | •    |                          |      |           |    |    |    |    |     |     | •   |      |      |    |

| Dynamic RAM             |      | •                        | •    |           |    |    |    |    | •   |     | •   |      | •    |    |

| ROM                     |      |                          |      |           |    |    |    |    |     | •   |     |      |      |    |

| PROM                    |      |                          |      | •         | •  |    | •  | •  | •   |     |     |      |      |    |

| EEPROM                  |      |                          |      |           |    |    |    |    | •   |     |     |      |      |    |

| UV EPROM                |      |                          |      |           |    |    |    |    | •   |     |     |      |      |    |

$^1$  MMOS refers to Mixed-MOS technology (CMOS and NMOS).  $^2$  High speed 4K and 16K devices available.

#### WE'RE TAKING ON THE FUTURE.

For a fast response about NEC Electronics' complete line of memory products, call TOLL FREE 1-800-556-1234, ext. 188. In California, call 1-800-441-2345, ext. 188. NEC sales offices: Woburn, MA (617) 935-6339 · Melville, NY (516) 423-2500 · Pughkeepsie, NY (914) 452-4747 · Pompano Beach, FL (305) 785-8250 · Columbia, MD (301) 730-8600 · Norcross, GA (404) 447-4409 · Arlington Heights, IL (312) 577-9090 · Southfield, MI (313) 559-4242 · Bloomington, MN (612) 854-4443 · Dallas, TX (214) 931-0641 · Orange, CA (714) 937-5244 · Cupertino, CA (408) 446-0650 © 1983, NEC Electronics

### MEMORIES OF THE FUTURE

C Short Manager - -----

## **Beautiful Streamer**

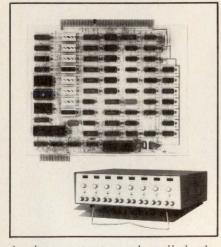

Kennedy proudly announces Model 9600, the first member of a new family of advanced low cost formatted tape drives. A few of its many features include; Autoload; 800/1600 CPI dual density; streaming capability of 100 ips; a capstan motor which provides an amazing 45 ips true start/stop mode; PC boards which may be moved or replaced in any order on a common bus for upgrading to higher performance levels or different interfaces the list, fortunately, goes on and on. Write or call today.

> ni <u>16681: "I</u>ng Berli, "Ing Sefel ng 15531, "Ing 56531 ng 56561 yang 16686 ing 15686 ing 1668 Ani 16681: Ang 166831 yang 166833 ang 166836 ing 166836 ing 166888 ing 166836 ing 166836 ing 166836 ing 166836

An Allegheny International Company 1600 Shamrock Ave., Monrovia, CA 91016 (818) 357-8831 • ITT TELEX 472-0116 KENNEDY

| ON   |      |        |       |       | PE     | WRITE ENBL | LOAD PT | st   | LECT     |

|------|------|--------|-------|-------|--------|------------|---------|------|----------|

|      | DIAG | SCAN   | START | RESET | NRZI   | DENSITY    | ON LINE | LOAD | RWND/UNL |

| OFF. |      | dir bi |       |       | REMOTE |            |         |      |          |

### KENNEDY · QUALITY · COUNT ON IT

CIRCLE 2

## **COMPUTER DESIGN**<sup>®</sup>

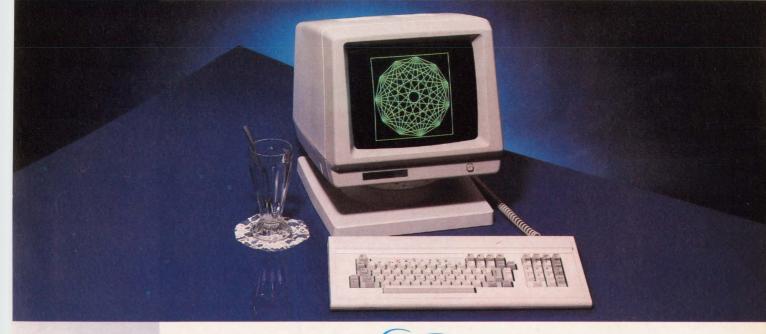

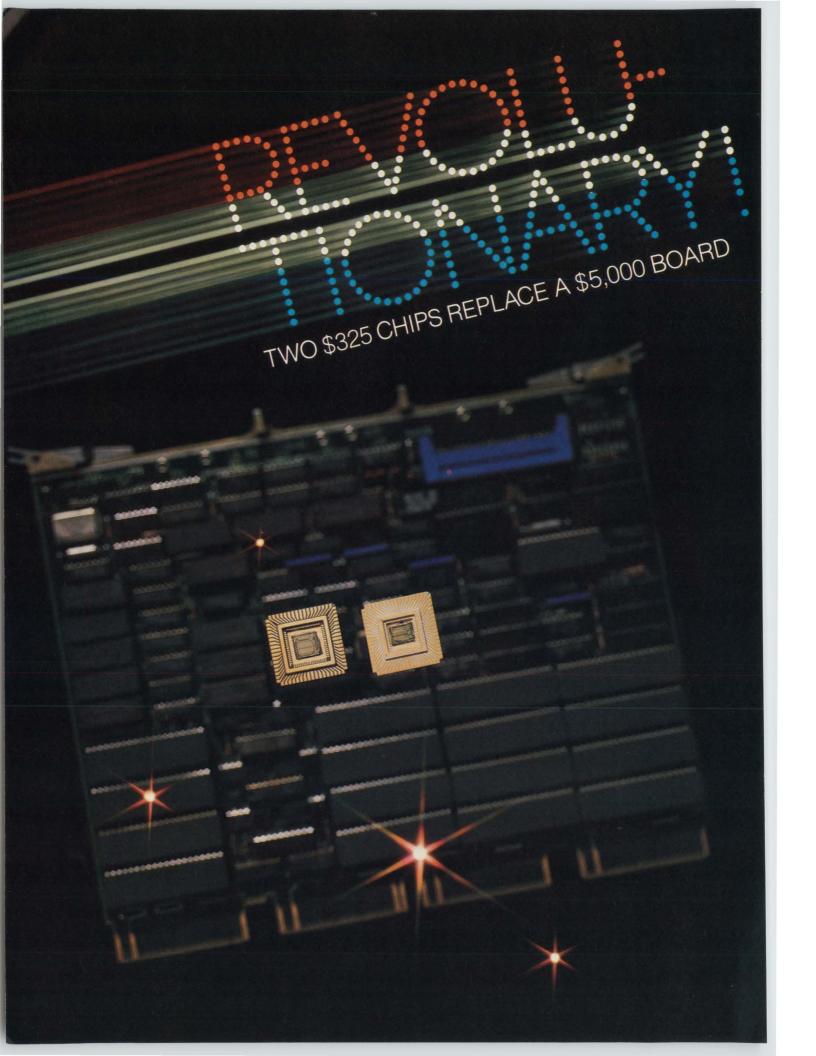

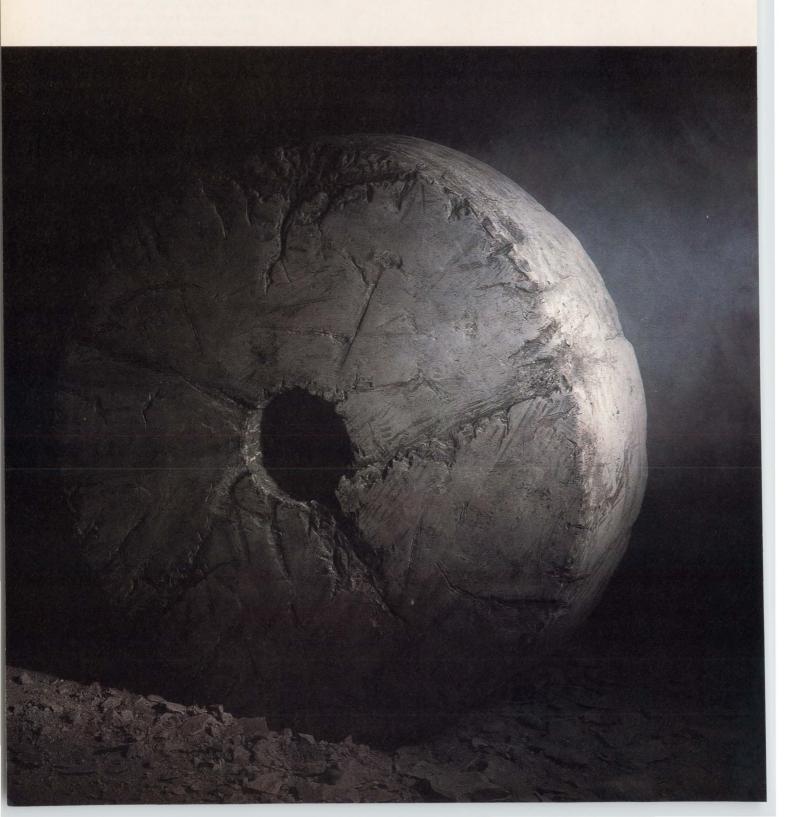

This month's cover was designed and created by Mary Codd and Steve Branch at Coddbarrett Associates, Inc. It was illustrated by Steve Branch and based on an idea from Advanced Micro Devices.

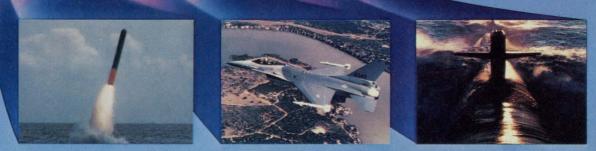

#### SPECIAL REPORT ON DIGITAL SIGNAL PROCESSING

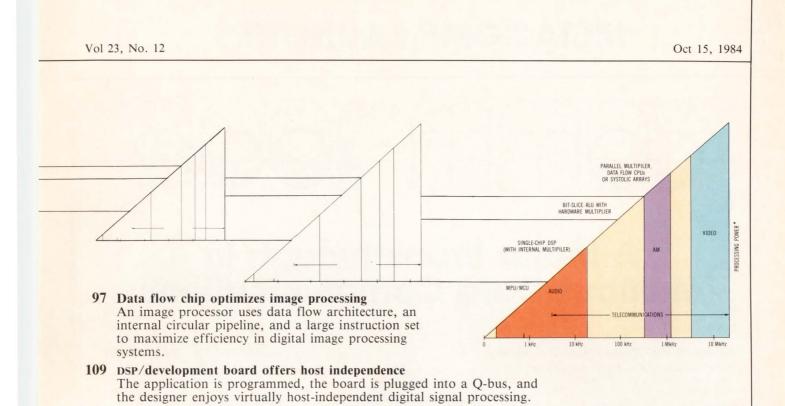

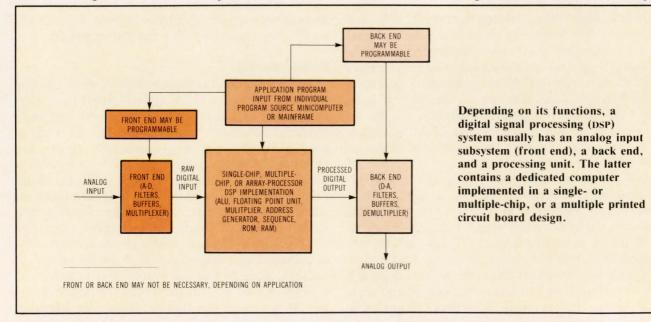

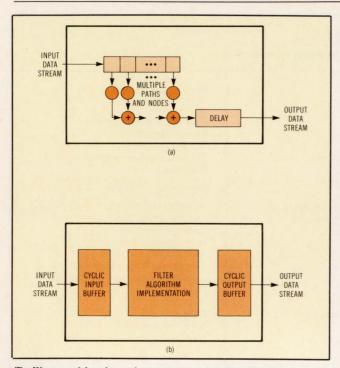

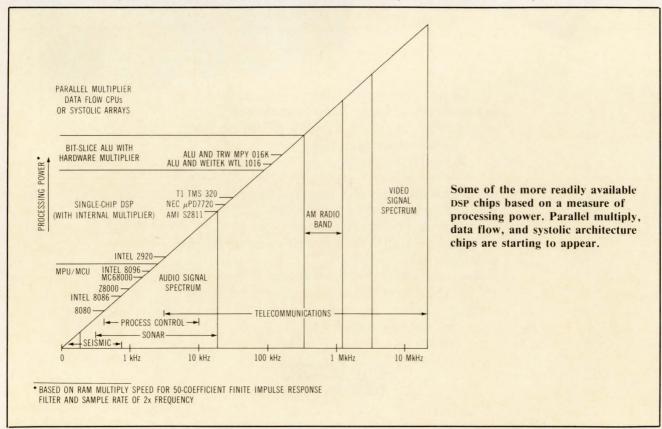

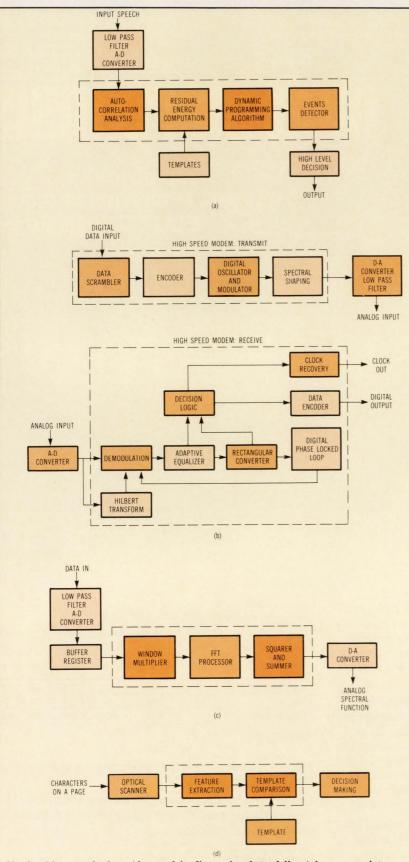

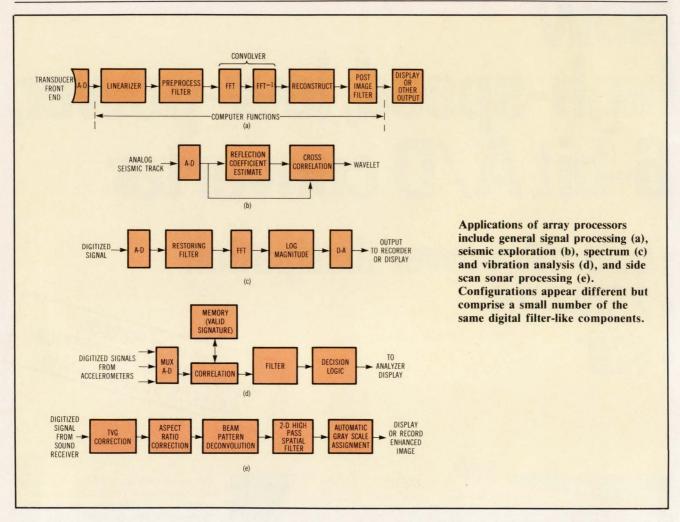

- **59** The spread of digital signal processing technology applications is accelerating. Together, VLSI, software, algorithms, development tools, and subsystems have rapidly increased DSP's involvement in such compute-intensive chores as image enhancement, speech recognition, and spectrum analysis. Moreover, cost has declined and reliability has increased. Computer designers need to know what DSP can do for their systems and what new signal processing functions they can expect. As DSP becomes more flexible, designers will have to decide first whether the DSP approach suits their needs and then choose from among the different DSP components and subsystems.

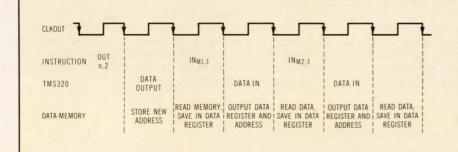

- **61 Digital signal processing moves into high gear** VLSI chips, software development tools, and algorithms now handle a variety of computer design applications.

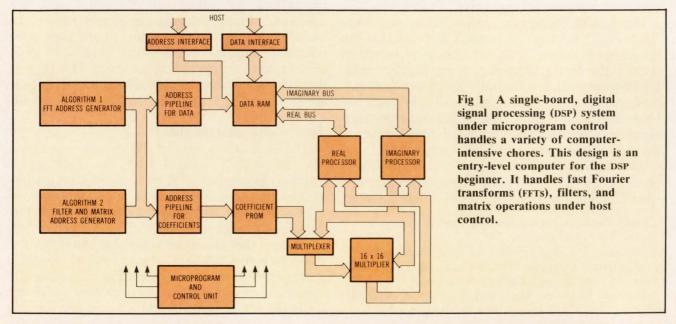

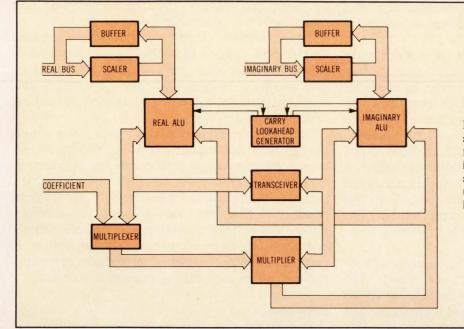

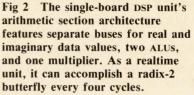

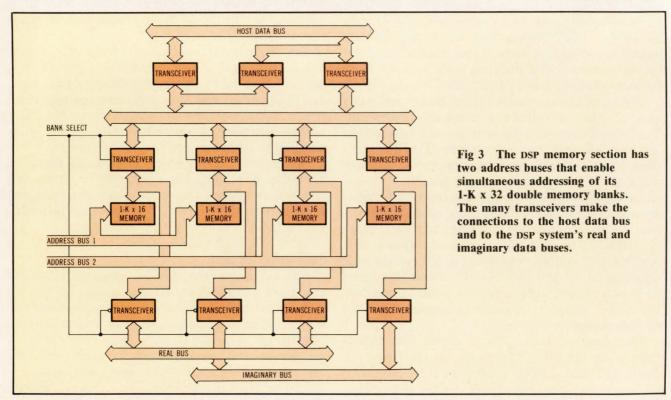

- 81 General-purpose board is designer's first step into DSP An entry-level, single-board computer performs 1-K complex point fast Fourier transforms, matrix operations, and filters.

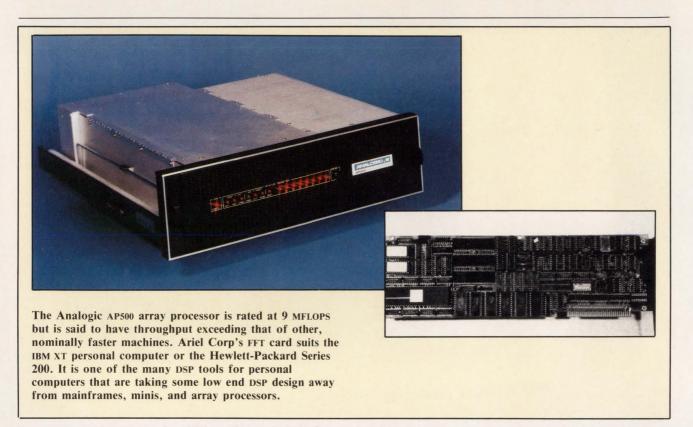

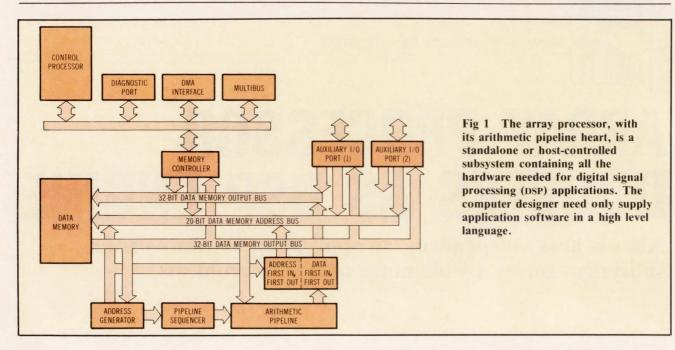

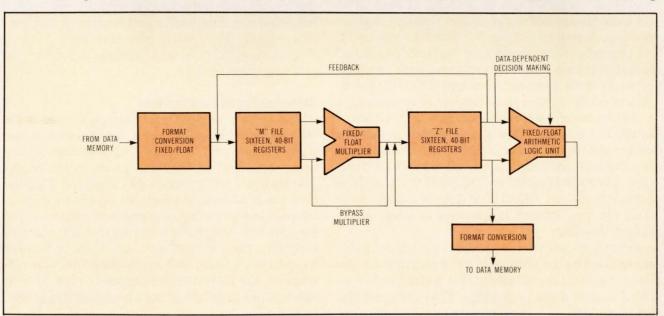

- **89** Array processor doubles as DSP engine Almost host independent, an application software-driven subsystem solves a wide range of design problems.

#### SYSTEM TECHNOLOGY

#### 33 Software:

Data bases add function to meet computer aided design needs

42 Software:

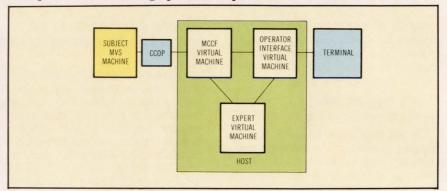

Artificial intelligence concepts are being put to practical use

- 46 Microprocessors/microcomputers: Multi-user systems prepare to do battle with PC AT

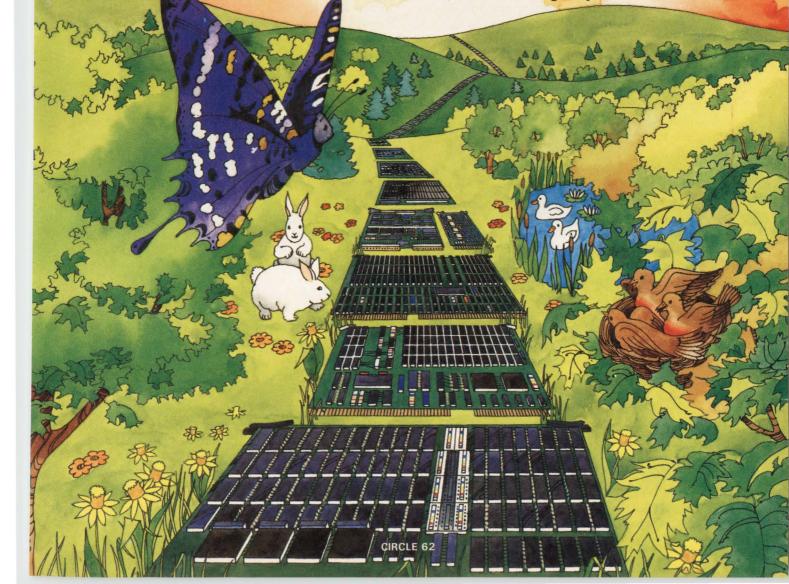

- 50 Test & development: Silicon compilation cuts costs of custom VLSI

#### SYSTEM DESIGN

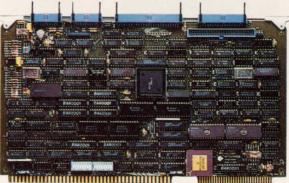

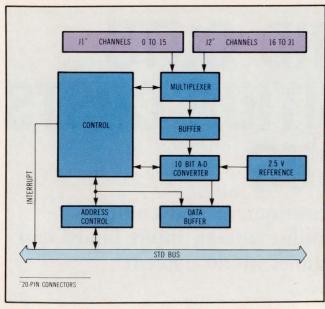

- 121 Control & automation: Analog board cuts data acquisition costs using STD bus In computer-based industrial measurement and control environments, an STD bus-compatible analog input board can cut the data acquisition cost per channel by 60 percent.

- 129 Integrated circuits: Winchester/floppy controller eases disk interfacing Chip performs seek overlaps and interleaved data transfers for high performance disk control. Other techniques such as disk caching and elevator sorting are easily supported.

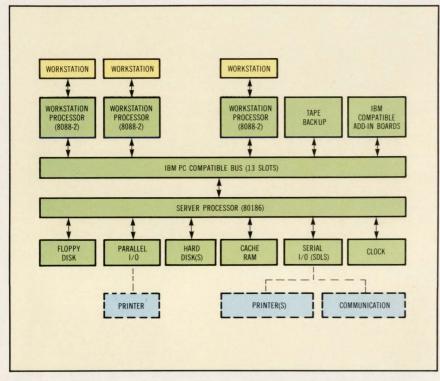

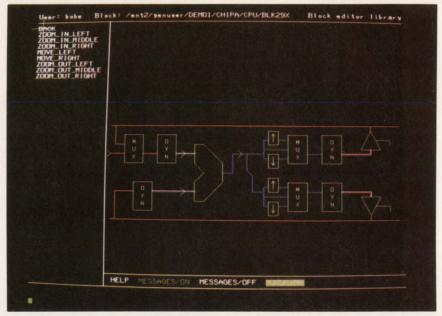

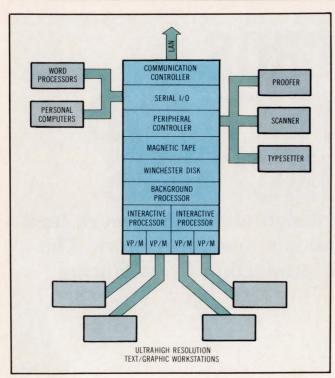

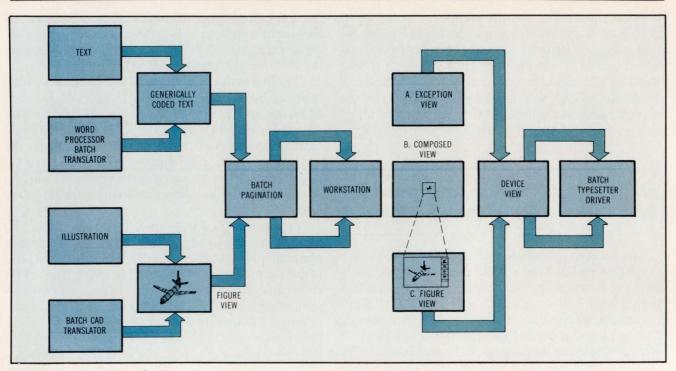

- 141 Computers: Multiple micros distribute text and graphics functions An integrated system distributes design and editing work load of technical publishing across multiple microprocessors. This architecture automates document production by enhancing traditional methods.

POSTMASTER: CHANGE OF ADDRESS FORM 3579 to be sent to COMPUTER DESIGN, Circulation Department, P.O. Box 593, Littleton, MA 01460 (UPS 127-340).

#### SYSTEM COMPONENTS

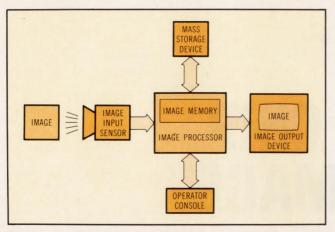

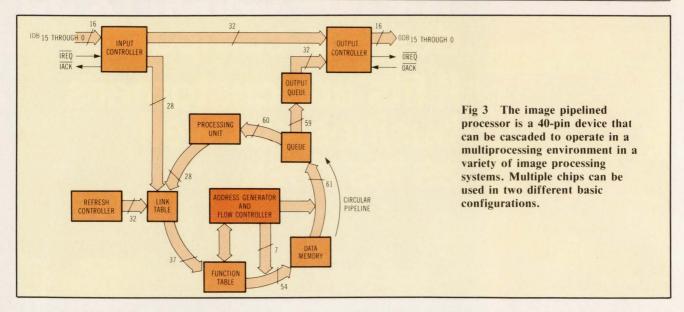

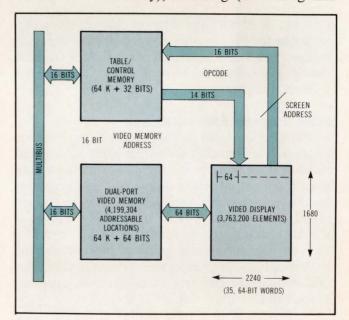

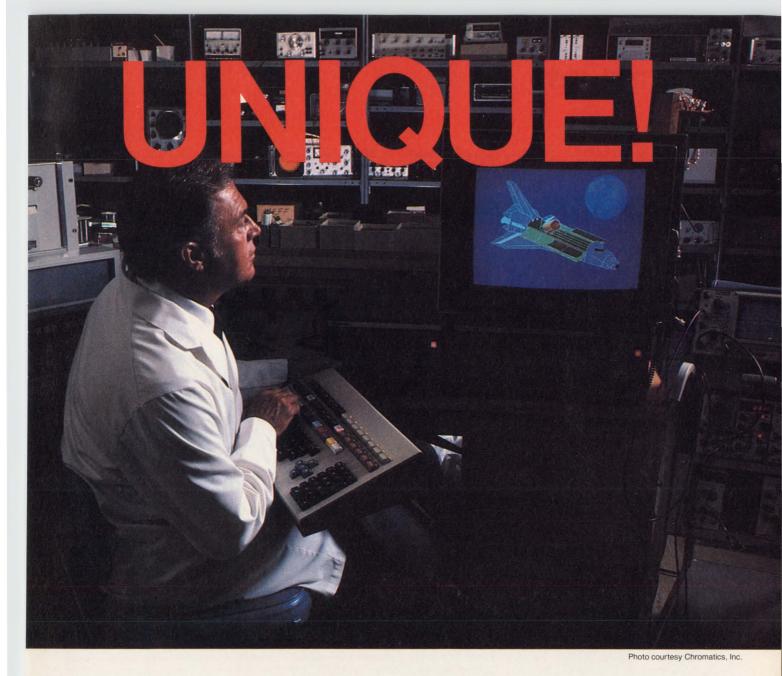

- 151 Computers: Image processing vaults beyond the world of 512 x 512 pixels

152 Test & development: In-circuit testers expose device timing errors

- **152** Microprocessors/microcomputers: Card family puts 8088 on STD bus

- 154 Memory systems: Bubble memory serves well in tough settings

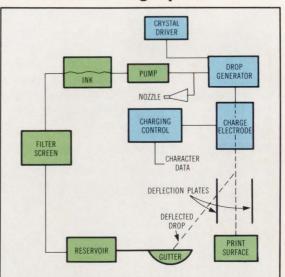

- **154 Peripherals:** Printer uses binary charge technology to combine text/graphics

- 155 Computers: Hardware/software standards merge in design workstation

- 155 Peripherals: Scanner digitizes graphics and reduces storage requirements

#### DEPARTMENTS

- 5 Up front

- 13 Editorial

- 24 Letters to the editor

- 178 Literature

- 180 Calendar

- 181 Designer's bookcase

- 182 System showcase

- 184 Advertisers' index

- 186 Recruitment

- 187 Reader inquiry card

- 187 Change of address card

### **METACOMP LAUNCHES**

#### BREAKING THE COMMUNICATIONS BARRIER

The COMM-2000 family is a powerful assortment of software and firmware products that perfectly integrate with METACOMP's MPA-2000<sup>TM</sup> CPU/Intelligent I/O Controller to provide the widest possible range of data communications protocol and networking support available to Multibus system integrators.

COMM-2000 plus MPA-2000 equals the complete hardware, software, and firmware solution to all your Multibus data communications problems.

Comm-2000 offers packet-switching, terminal I/O concentrator, network gateway emulation, and DLC protocol support.

Available capabilities include:

- X.25 with full CCITT 1980 recommended features

- IBM 3270 SNA protocols

- SDLC, HDLC (LAPB), BISYNC, and other DLCs

- LAN (XNS, TCP/IP, and others)

#### BREAKING THE TIME BARRIER

With the COMM-2000 family at your disposal, you can design Multibus systems that provide standard data communications facilities in the shortest possible time and with the least possible hassle. Because COMM-2000 combinations are endless ... easy, and readily available.

#### BREAKING THE SPACE BARRIER

Thanks to the modularity of the COMM-2000 family, your special hardware, software, and firmware combination can be integrated into a single board solution, giving you the most capabilities with tremendous savings in system capacity.

#### BREAKING THE SERVICE BARRIER

The ultimate ingredient of COMM-2000 is commitment. You can absolutely rely on METACOMP for service and customer support guaranteed to meet your requirements. At METACOMP, we pride ourselves on customer service that's unequaled by any other Multibus manufacturer.

#### BREAKING THE INFORMATION BARRIER

Here's an easy breakthrough you can make today. Write or call for complete details on COMM-2000. We will respond with a package of information that will promote your data communications breakthrough tomorrow.

METACOMP, INC., 9466 Black Mountain Road, San Diego, California 92126, 619 / 578-9840, TWX 910-335-1736.

## **METACOMP**<sup>™</sup>

COMM-2000 and MPA-2000 are trademarks of METACOMP, inc. Multibus is a trademark of Intel Corp. ©Copyright 1984 METACOMP, inc. All rights reserved 6/6/84.

#### THE MULTIBUS BREAKTHROUGH PEOPLE

CIRCLE 3

## **UP FRONT**

#### Intergraph workstation joins the 32-bit list

The 32-bit workstations announced by Tektronix (Beaverton, Ore) in September will have competition. Intergraph (Huntsville, Ala), is also introducing a 32-bit Unix-based workstation for computer aided design/computer aided engineering applications. In addition, the Intergraph workstation—Interpro 32—can be used as a personal computer when running an MS/DOS. It can also be a terminal emulator, and functions as a Digital Equipment Corp DT200, Tektronix 4014, or IBM 3270 Series terminal. Interpro 32 has a 15-in. color monitor with 1184- x 884-pixel resolution. Price tag is approximately \$20,000 per workstation.—R.G.

#### Team work speeds integration of design and debug tools

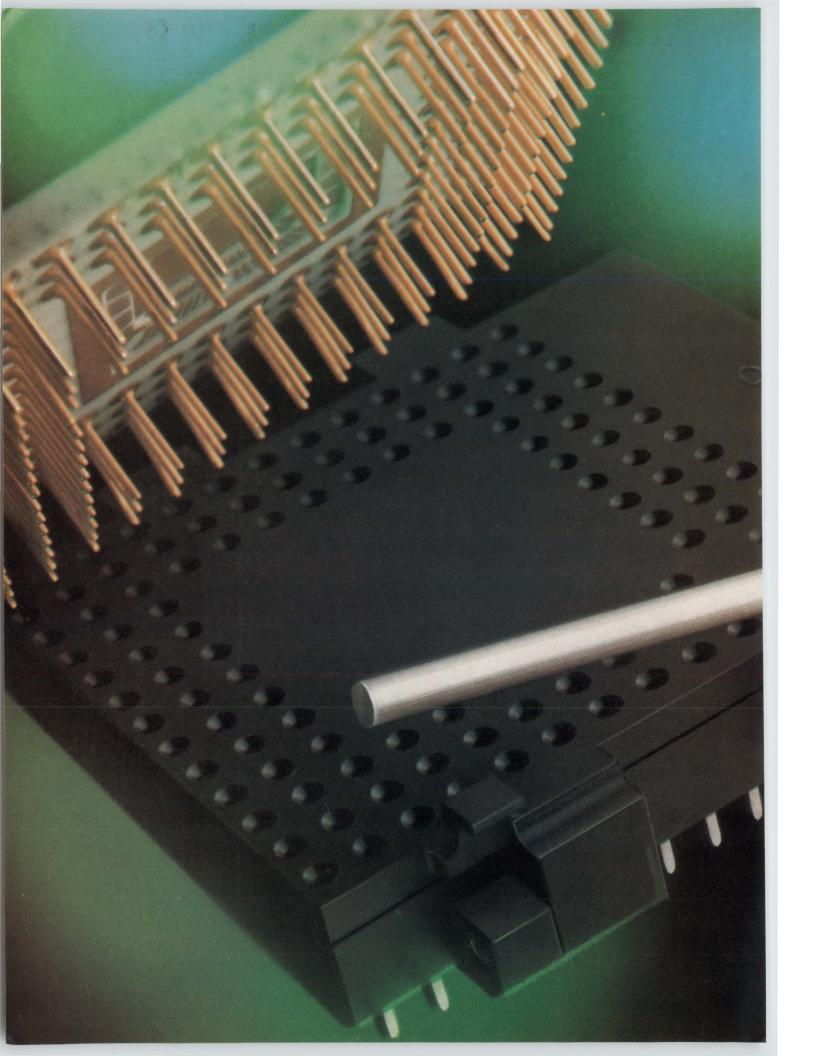

The union of designing and testing will move ahead as more makers of digital test tools join forces with workstation vendors. For example, Dolch Logic Instruments' (San Jose, Calif) recent unveiling of its CAESAR—short for computer aided engineering system analyzing resource—might not have drawn attention if it had not been coupled with the announcement of the firm's joint technology agreement with CAE Systems (Sunnyvale, Calif). Under the agreement, Dolch will provide its CAESAR tools (a variety of in-circuit emulation, logic analysis, and pattern generation hardware developed for Dolch's Atlas logic analyzer system) to CAE Systems on an OEM basis.

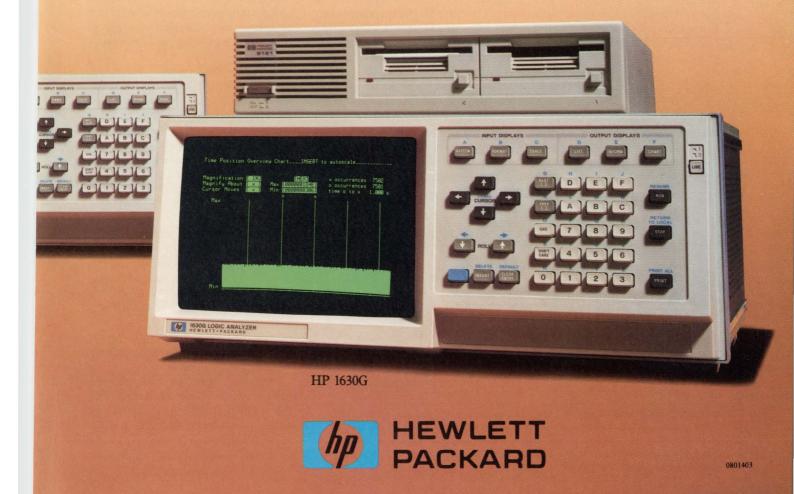

Since Northwest Instruments (Beaverton, Ore) announced an OEM agreement to supply its  $\mu$ Analyst logic analyzer to its Beaverton neighbor, Mentor Graphics, such workstation vendors as Valid Logic, Daisy, and CAE Systems have been scurrying around for suppliers of similar tools. The two major makers—Hewlett-Packard (Palo Alto, Calif) and Tektronix—would have no reason to strengthen competitors who will make the same kind of integrated design and test systems.

As a result, the candidates for joint agreements or acquisition are not many. Gould's Biomation/Millenium group of Santa Clara, Calif is an obvious possibility, but that firm is having problems keeping up with the competition and is looking at disappointing sales. An OEM agreement with a major workstation vendor would give it a shot in the arm, however. With Northwest Instruments already linked to Mentor (and developing a high channel count pattern generator expressly for Mentor), it is out of the running. An even closer link between Northwest and Mentor in the near future would be no surprise. One remaining candidate appears to be Nicolet/Paratronics of Fremont, Calif teamed with Applied Micro Systems (in view of the latter's recent acquisition by Nicolet). The two have had a relatively close and informal relationship for more than two years to promote an inexpensive system based on Paratronics' logic analyzer and Applied Micro Systems' emulator. Another possible candidate, Hilevel Technolgoy (Irvine, Calif), is known for its Emulyzer product. This firm is hot at work developing a pattern generator, and exploring the possibilities of acting as an OEM supplier of logic analysis, emulation, and pattern generation tools—J.M.

#### **UP FRONT**

#### Tektronix throws monkeywrench at Northwest

Dark clouds may be looming on the horizon for Northwest Instruments and in turn, for Mentor Graphics. The growth of several Beaverton-based design and test tool companies has been stoked with Tektronix alumni. Tektronix has treated its graduates with benign neglect because they did not present direct competition. But Tektronix has just filed suit against Northwest Instruments to restrain its new vice president of engineering, James Cavoretto, from (presumably) taking up where he left off at Tektronix. Since Cavoretto was involved with the company's oscilloscope effort, Tektronix' suit does not make sense. It appears to be a warning of Tektronix' future action, allowing the company to keep its integrated designs and test tool plans under wraps a little longer. Some key Tektronix people have joined the competition in this area, including Larry Sutter, president and CEO of Northwest (from Tektronix Design Automation Div) and Peter Strong, the new group vice president for test and measurement at Gould's Biomation/Millenium organization, also from Tektronix' design and automation group.-J.M.

#### Converter chip marries 80286s to 8088s

Designers of PC AT compatible systems, as well as those designing 80286 expansion boards for the standard PC, face a time-consuming technical problem—how to control slow 8-bit circuitry with a fast 16-bit processor. Help may be on the way. The EL-286-88 processor converter chip from Edsun Labs, Inc (Wayland, Mass) is an application-specific VLSI IC that converts 80286 processor signals into the equivalent signals of an 8088. It solves the bus interfacing problem by allowing an 80286 to drive circuitry design for the 8088 and will, according to the manufacturer, save the designer up to 9 months of product lead time. The EL-286-88 is scheduled to appear in Jan 1985, but a board version will be available to OEMs in Nov 1984 for prototyping—J.H.

#### Opening up ARCnet for the PC deluge

A line of products just announced by Datapoint Corp (San Antonio, Tex) includes a networking package for the IBM PC, a direct ARCnet interface for Datapoint's Vista-PC system, and a CP/M software support package for the ARCnet. The PC connection package is based on an Intelligent Network Executive interface card that connects to the PC. Card and software are priced at \$770. Datapoint was one of the first into the local area network fray, and first to offer LAN functions on a chip, via the ARCnet VLSI controller from Standard Microsystems Corp, (Hauppauge, NY). Claiming 6000 installed LANs, Datapoint can win a numbers game with any LAN vendor. But offering connection for PC-DOS and other environments—in essence opening up its formerly proprietary network—has become a prime goal for this manufacturer.—J. V. NO OTHER CUT-SHEET FEEDER GUARANTEES RELIABILITY LIKE WE DO

#### ELECTRONICS MAKES THE DIFFERENCE

When designing a cut-sheet feeder into your system, compare the Ziyad<sup>®</sup> Z-300 to all other cut-sheet feeders and the difference is obvious. The Ziyad Z-300 Intelligent Paper Processor<sup>™</sup> is electronic, and, with electronics comes reliability.

In fact, the Z-300 is the only cut-sheet, dual tray and envelope feeder that electronically captures both name and address from a typed letterhead and automatically delivers a typed envelope collated with your letter. This single feature alone makes all other sheet feeders obsolete.

#### **Electronics Means Reliability**

Our engineers have developed the most sophisticated combination of hardware and software ever integrated into a cut-sheet feeder. The result—the Z-300 with an MTBF of 6000 hours. More than three years of continuous operation. This proven performance has made us the leader in the industry. Ask any of the 22 world's leading manufacturers of word processing equipment who have chosen to sell the Z-300 under their own name. It's guaranteed reliable. And, that's why more than 100,000 Ziyad products will be sold this year.

#### **Electronics Makes The Difference**

Microprocessors, sensors, and three drive motors constantly monitor and drive paper and envelope flow through the Ziyad Z-300. If trays are empty or if a misfeed should occur, the Z-300 immediately stops—eliminating platen printing. It memorizes typing position and automatically alerts the operator with an audible and visual signal.

#### Integrate Ziyad Electronic Feeders Into Your System

Don't compromise your electronic word processing systems with any other sheet feeder.

Add the Ziyad Z-300 Intelligent Paper Processor.<sup>™</sup> For a "plug and play" standard feeder, or a special design for a custom system, put our Ziyad technical team to work for you. Call Sue Turner, 201/627-7600 today.

#### **UP FRONT**

#### Touchscreen computers tie to IBM PCs via an Ethernet

Up to 50 networked Hewlett-Packard (Palo Alto, Calif) Touchscreen computers and IBM PCs now can share such peripherals as ThinkJet and LaserJet printers through a local area network provided for HP by 3Com Corp (Mountain View, Calif). Dubbed EtherSeries/150, the LAN requires that at least one Touchscreen computer with a 15-Mbyte hard disk (Touchscreen MAX personal computer) to act as a file server. Each server can accommodate from two to eight users. EtherSeries/150 consists of four elements: EtherLink accessory board for accessing Ethernet; EtherShare/150, for allowing multiple users to share data and fixed disks; EtherPrint/150 for sharing printer facilities; and EtherMail/150 for providing fast electronic mail service. In addition, HP has expanded its mass drive offering to include double-density, double-sided  $3\frac{1}{2}$ -in. drives for a total storage capacity of 1.4 Mbytes.—*N.M.*

#### Waiting in the wings...a Brown Trout

Industry watchers have stepped up the scan rate in anticipation of the debut of a new high end processor from IBM. Much speculation has surrounded this machine series. Some believe this "Sierra" series will be delayed some six months beyond its previously expected January arrival because of the lack of aggressive high end competition. Others say that this is contradicted by recent price reductions in the 3080 line—usually a sure sign of imminent unveiling. In any event, it is anticipated that when the machine is unveiled, it will come in within the \$200,000/MIPS window. The first introduction in the series should provide 28.5-MIPS performance. Code-named Morgan, or Brown Trout, the dual-processor machine will act as a pivotal point for the series, with further announcements to come in on both the upper and lower performance sides.—P.K.

#### Artificial intelligence for the masses

Texas Instruments (Austin, Tex) is about to enter the artificial intelligence field with a dedicated Lisp processor for symbolic processing applications. The TI "Explorer" establishes new ground in price and size at the low end of the market. Explorer is NuBus-based and is a result of collaboration between TI and LISP Machine, Inc (Culver City, Calif). It is software-compatible with LMI's Lambda series machines. The microprogrammed 32-bit Lisp processor has 16- x 56-kbits of writable control store and a tagged architecture. Along with the Lisp compiler, numerous program development tools and toolkits are to be either provided or are already available.—J.B.

COMPUTER DESIGN © 1984 (ISSN-0010-4566) is published monthly, with a thirteenth and fourteenth issue respectively in June and October by PennWell Publishing Company, Advanced Technology Group, 119 Russell St., Littleton, MA 01460. Second-class postage paid at Littleton, MA 01460 and additional mailing offices. COMPUTER DESIGN is distributed without charge to U.S. and W. Europe-based engineers and engineering managers responsible for computer-based equipment and systems design. Subscription rate for others is \$50 in U.S.A. and \$75 elswhere. Single copy price is \$5.00 in U.S.A. and \$7.50 elsewhere. Microfilm copies of COMPUTER DESIGN are available and may be purchased from University Microfilms, a Xerox Company, 300 North Zeeb Road, Ann Arbor, Michigan 48106. Officers of PennWell Publishing company, 1421 S. Sheridan, Tulsa, OK 74101; P. C. Lauinger, Chairman; Philip C. Lauinger, Jr., President; Joseph A. Wolking, Senior Vice President; H. Mason Fackert, Group Vice President; Carl J. Lawrence, Group Vice President; V. John Maney, Vice President/Finance; L. John Ford, Vice President.

COMPUTER DESIGN is a registered trademark. All rights reserved. No materials may be reprinted without permission. Phone (617) 486-9501. 🖤 BPA

PYRAMID

### IF IT WEREN'T FOR UNIX WE NEVER COULD HAVE BUILT THE PYRAMIDS

Ordinary computers, yes. But not a Pyramid Technology 90x.

After all, here's a supermini not just capable of running UNIX,<sup>™</sup> but born to run it. And run it up to four times faster than the most popular UNIX host. For a lot less money.

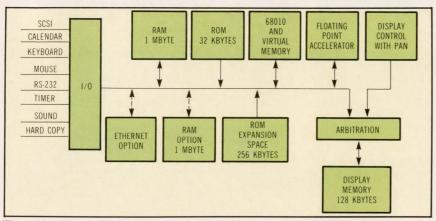

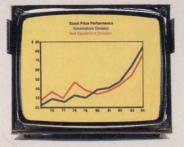

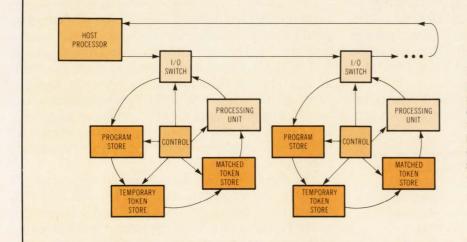

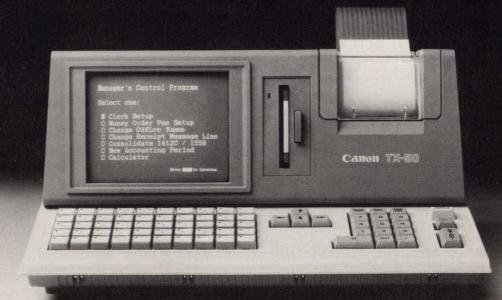

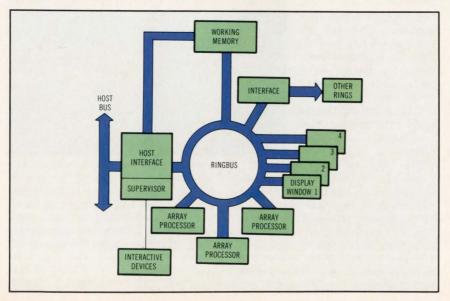

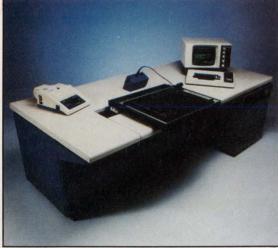

The secrets of this Pyramid are a thorough understanding of UNIX, a few fundamentals of RISC (Reduced Instruction Set Computer) theory, more registers than 30 VAXs, and a 32-bit proprietary architecture that outperforms a roomful of micros.

All combined to speed up UNIX just where it likes to slow down. For example, gone are 85% of performance-robbing memory references. The endless parameter shuffling of yesterday's technology has been replaced with a hardware register window. Even context switching takes less than one percent of the CPU's time.

It's amazing what hardware architects can do, given the chance. It's almost as startling as what our software wizards did.

They crafted OSx, a dual port of Berkeley's 4.2 BSD and Bell's System V. Because you can switch environments at will, no UNIX port offers more capabilities. With absolutely no loss of compatibility.

Well, almost. We do admit to one feature not compatible with other UNIX systems. Our single-source support. PYRAMI

One telephone number instantly connects you to both hardware and software experts. In-house pros, who spend their energy pointing you towards solutions. Not pointing fingers at each other.

So no matter how you see your requirements shaping up, contact Pyramid Technology, 1295 Charleston Road, Mountain View, California 94043. Or call (415) 965-7200.

Because when it comes to running UNIX, a Pyramid looks good from any angle.

## YOU WON'T FIND MANY SHUGART DRIVES AROUND THESE PARTS.

You find Shugart new generation drives where they were built to be. In all kinds of systems. Under all kinds of conditions. Running. And running and running.

Setting a world standard for quality. A standard that doesn't allow room for failure. Because you don't.

To insure the reliability of your system, we begin with our suppliers. They go through a lot. Learning and qualifying, even building drives themselves.

We also involve our manufacturing engineers. And our quality control experts. From the very beginning. The design stage.

With their full collaboration, every new drive is designed for top quality. Unbeatable reliability. And ease of assembly. Using the fewest number of parts possible.

In other words, the same un-

compromising quality you design into your system is designed and built into every new Shugart drive. Right from the start. So you can count on consistent reliability. For example, 20,000 hours MTBF for new generation Winchesters.

Of course, every Shugart drive is subject to the most stringent testing and inspection at every stage. But inspection doesn't insure quality. At Shugart, we believe there's only one way to insure a reliable product. By eliminating the cause of failure from the product design.

At Shugart, quality is designed in. Not inspected in.

Let us prove it. Call Doug Daetz, our Director of Corporate Quality at (408) 737-3009 for details.

Milpitas, CA (408) 263-2600; Costa Mesa, CA (714) 979-1935; Thousand Oaks, CA (805) 496-5388; Rochester, NY (716) 235-7190; Minneapolis, MN (612) 546-4411; Richardson, TX (214) 234-3568; Framingham, MA (617) 879-1700; Saddle Brook, NJ (201) 368-8445; Smyrna, GA (404) 436-0953; Markham, ONT (416) 475-2655; Paris, France (3) 946-42-66; Munich, West Germany (089) 786-021; London, U.K. (44) 4862-27272; Wanchai, Hong Kong (852) 5-733307. © 1984 Shugart Corporation Hamilton/Avnet, authorized distributor

Compact, modular design

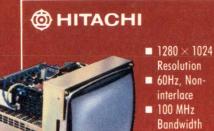

#### HM 4619

#### 🕲 HITACHI

- 1280 × 1024 Resolution

- 30Hz, interlaced

- 45MHz Bandwidth ■ 0.1/0.3 mm

- convergence

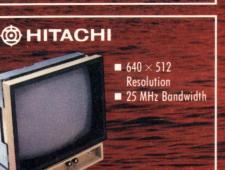

### HM 3619A

#### **OHITACHI**

■ 1024 × 1024 Resolution 40 MHz Bandwidth Compact

HM 3719

HM 2719

NEW

## **OHITACHI** Bridges The Gap In OEM **RGB** Color Monitors

HURDER AND STREET, S.A. K. HURBER

A STR. W. ST. W

The world of computer graphics is moving at incredible speed. Software advances dictate hardware advances; new applications demand new engineering specifications. "Limited standards" don't always fit the need

Hitachi is the totally integrated OEM source. Our complete range of RGB Color Monitors provide a very wide selection of power, resolution, size and price. More important, we can and do modify specifications to meet highly specialized individual OEM requirements.

Best of all, our "standard" monitors and our "not so standard" monitors all reflect clearly the world renowned Hitachi technology and our dedication to design excellence.

HITACHI.....the image speaks for itself.

#### The Image Speaks For Itself.

Hitachi America, Ltd. Hitachi America, Ltd. 59 Route 17S, Allendale, NJ 07401 3540 Arden Road, Hayward, CA 94545 (201) 825-8000 (415) 783-8400

Hitachi Europe, Ltd., Lee House (10th Floor) Hitachi Denshi Canada, Ltd. 65 Melford Drive London Wall, London EC245AS Scarborough Ontario, Canada M1B 2G6 (01) 606-7831 (416) 229-5900

### FEEDBACK LOOPS AND QUALITY CIRCLES

Most comparisons of Japanese and American management styles concentrate on the differences—as I did in my editoral, "Wa versus the Gunslingers" (*Computer Design*, Oct 1983, p 11). However, the real secret of the Japanese and Silicon Valley miracles may lie in a single feature that characterizes the most successful high technology companies. No matter where they are located, the best companies seem to have effective communication between management and the people in various departments and plant locations. This, in turn, leads to a common bond of trust within the organization and to a unified sense of purpose and direction.

In a small entrepreneurial company, internal communication occurs naturally because the founders begin with a common purpose and a small group of employees at a single location. As the organization grows, however, communication breaks down because people start to pull in different directions. It then becomes necessary to restore communication via some strategy such as the Japanese "quality circles."

When scanning a recent issue of the *Quality Circle Digest* recently, I was surprised to learn that about one million U.S. employees are already involved in quality circles or other problem solving groups. Until I read that, I had a lukewarm interest in the concept. To begin with, the topic of quality control—though important—tends to be boring. Also, I have an inherent distrust of organizations run by "facilitators and coordinators" because they usually turn out to be excessively bureaucratic. What finally aroused my curiosity, however, was a Quality Circle Institute survey of U.S. quality circles. This survey revealed that the major benefits of these groups were improved communications, teamwork, morale, and attitude—in addition to the expected quality and productivity benefits.

Once my interest was stirred, I became aware of other proponents of similar management styles. A source that convinced me that I had stumbled upon something significant was the testimony of Charles E. Sporck, president and CEO of National Semiconductor Corp. In his address to a local hearing of the Joint Economic Committee of the U.S. Congress held in Sunnyvale, Calif, Sporck described how his company had instituted a Quality Enhancement Strategy program (QUEST), which involves "techniques that somewhat resemble quality circles."

The QUEST program is not the only strategy National uses to encourage employee communication and involvement. Open offices, with shoulder-high, movable partitions and no doors, focus on the essentials for doing the job rather than nonessential trappings. "Answer line" forms placed throughout the buildings allow any employee to send managers direct, confidential messages and receive prompt responses.

National's Santa Clara, Calif headquarters has a closed-circuit television network that allows Sporck to speak directly to employees about key issues and give

immediate answers to questions. Also, Sporck says that when serious issues affecting the company are in the news, National sends letters to each employee's home. All this is in addition to Sporck's regular talks to large groups and frequent informal breakfast or dinner meetings with small groups of employees.

Of course, these strategies are not unique to National. In fact, most of the successful computer and semiconductor companies I have visited-especially those in Silicon Valley and on the Route 128 belt around Boston-have similar programs to ensure communication. Perhaps where Sporck differs from other high technology managers is in his giving such high priority to communication versus other strategies for innovation. He explains, "If I were to isolate the human factor for this analysis, and boil it down to one essential element, it would be the necessity to establish trust with employees. On that foundation of trust, the rest of the business structure can be built. Trust means there is a common understanding and agreement about the mission of the enterprise. That is achieved through continual communication . . . with a significant level of participation from employees in the definition and execution of that mission, and with employees sharing the results of the success of that mission."

[To learn more about quality circles and to get a copy of the magazine, call or write Janice Minch, Circulation Manager, *Quality Circle Digest*, PO Box Q, Red Bluff, CA 96080-1335. Tel: 916/527-6970 ext 103.]

what Elphih

Michael Elphick Editor in Chief

## **MEET THE STRONGEST**

here's a lot more to a Fujitsu gate array than glass, gold, and

aluminum; it's the human element that really sets our product apart.

When you order a Fujitsu gate array, you become part of a team. You work through your objectives with a highly-skilled design engineer who knows silicon the way you know logic.

That way, you combine your expertise with ours to shape the subtleties of silicon into product advantages. Instead of glitches.

This approach is a good part of the reason that since 1974, Fujitsu has produced more than 3,000 gate array designs - and every one of them has worked according to plan.

Our engineers can help you execute designs in a complete range of technologies - CMOS, TTL, ECLvou name it. Because the Fujitsu team's incredible versatility comes from a solid background within each of those technologies.

That's how you get numbers like these:

| CMOS                        |                |                     |               |  |  |  |

|-----------------------------|----------------|---------------------|---------------|--|--|--|

| TECHNOLOGY                  | GATE<br>LENGTH | PROP DELAY<br>TIME* | GATE<br>COUNT |  |  |  |

| STD CMOS                    | 3.6 µ          | 7.0 ns              | 700-3900      |  |  |  |

| H CMOS                      | 2.8 μ          | 5.0 ns              | 440-3900      |  |  |  |

| VH CMOS                     | 2.3 μ          | 2.5 ns              | 2600-8000     |  |  |  |

| *2-Input NAND Gate, F/O = 2 |                |                     |               |  |  |  |

#### BIPOLAR

| TECHNOLOGY | PROP DELAY<br>TIME* | GATE     | POWER<br>DISSIPATION<br>PER GATE |  |  |

|------------|---------------------|----------|----------------------------------|--|--|

| LSTTL      | 1.8 ns              | 500      | 2.3 mW                           |  |  |

| LSTTL      | 1.9 ns              | 240-1100 | 0.8 mW                           |  |  |

| LSTTL      | 0.95 ns             | 2000     | 0.65 mW                          |  |  |

\*3-Input NAND Gate, F/O = 1

## TEAM ON THE CIRCUIT.

There are now three fully equipped Fujitsu Gate Array Design Centers in the U.S.; in Boston, Dallas, and Santa Clara. There's a sophisticated telecommunications network between centers, and high-speed leasedline and satellite communications with FMI host computers in Japan. All that. and a firstclass gate array design team, too. With you as star player.

Call the FMI Design Center nearest you. We'll show you how to get our team on your circuit.

Boston Design Center 57 Wells Avenue Newton Centre Massachusetts 02159 (617) 964-7080

> Santa Clara Design Center 3320 Scott Boulevard Santa Clara, CA 95051 (408) 727-1700

> > Dallas Design Center 1101 East Arapaho Road Suite 225 Richardson, TX 75081 (214) 669-1616

Literature request line: 800-556-1234 (ext. 82) In California, 800-441-2345

FUJITSU MICROELECTRONICS, INC. Technology that works 3320 Scott Boulevard, Santa Clara, CA 95051 · (408) 727-1700

Teamwork is making a comeback in America. Cooperation on the production line helped America win World War II. We're in another kind of battle today — a fight for economic survival in an increasingly competitive world market. Cooperation in the workplace is helping us meet this challenge too.

In plants and offices throughout the country, management is asking employees for their ideas on how to increase productivity and improve the work environment. And workers and their unions are responding with a wealth of practical suggestions and a renewed spirit of cooperation.

For information about how others are working better by working together, contact:

Cooperative Labor-Management Programs U.S. Department of Labor Washington, D.C. 20216 202—523-6098

Printed by this publication as a public service Photograph: Lange Collection, Oakland Museum

**U.S. Department of Labor**

The PennWell Building, Littleton, MA 01460, Tel: (617) 486-9501 Editorial/Executive Offices

Editor in Chief, Michael S. Elphick

Executive Editor, John Miklosz Managing Editor, Sydney F. Shapiro Senior Editor, John Bond Senior Editor, Peg Killmon Special Features Editor, James W. Hughes Senior Associate Editor. Malinda E. Banash Associate Editor, Jack Vaughan Assistant Managing Editor, Leslie Ann Wheeler Copy Editors, Helen McElwee, Leah A. Rappaport, Nancy E. Purcell, Jane E. Shattuck Editorial Assistants, Welma F. Brigham, Susan A. Livi New York Field Office: 230 Park Ave, Suite 907 New York, NY 10169, Tel: (212) 986-4310 Senior Editor, Nicolas Mokhoff Special Features Editor, Harvey J. Hindin Western Field Office: 540 Weddell Dr, Suite 8 Sunnyvale, CA 94089, Tel: (408) 745-0715 West Coast Managing Editor, Tom Williams Senior Editor, Bill W. Furlow Field Editor, Richard Goering

Production Director, Linda M. Wright Production Manager, Philip Korn Staff Artist, Jay Gordon Technical Art, Designline Ad Traffic Coordinator, Debra L. Stone Printing Services, Padraic Wagoner

Marketing Director, Robert A. Billhimer Circulation Director, Robert P. Dromgoole Promotion Director, Steve Fedor Marketing Services Coordinator, Linda J. Battle

Publisher, Frederic H. Landmann

#### **PennWell**

Advanced Technology Group 119 Russell St, Littleton, MA 01460 Tel: (617) 486-9501

H. Mason Fackert, Group Vice President Saul B. Dinman, Editorial Director John M. Abernathy, MIS/DP Director Patricia M. Armstrong, Administrative Services Manager

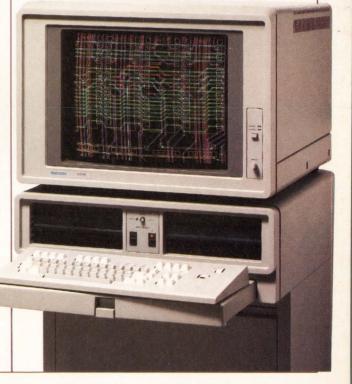

## What Lear Siegler Does Best We Also Do Special.

As standard products or OEM specials, Lear Siegler video display terminals convey the look and feel of quality your systems deserve.

With Lear Siegler terminals as your primary operator interface, your products will be more attractive, more reliable, easier to use, and more marketable than ever.

We will custom tailor Lear Siegler's superior performance, ergonomic design and exclusive High Touch<sup>™</sup> style to meet your exact requirements-from simple logo changes to completely unique terminal designs and proprietary firmware. Our dedicated OEM sales

Complete OEM design, engineering, assembly and testing are performed at Lear Siegler's Anaheim, CA. facility. and engineering groups are terminal experts who specialize in serving your needs. And they're backed by Lear Siegler's proven experience and reputation as an OEM supplier.

Call or write today for complete information on how Lear Siegler's OEM capabilities can work for you.

LEAR SIEGLER, INC. DATA PRODUCTS DIVISION 901 E. Ball Road Anaheim, CA. 92803 (714) 778-3500

## TOSHIBA. A LEA OF CMOS AND GET

A brand new perspective on filling your IC Microcomputer and Microprocessor needs.

Here's news for every design and purchasing department: Toshiba has developed one of the world's most comprehensive line-ups of CMOS and NMOS Microcomputers available today. In fact, we're the world's second largest manufacturer of 4-bit CMOS and NMOS Microcomputers. Our 8-bit devices—including the CMOS and NMOS 8048 and 8049 as well as the CMOS Z80 family—are meeting wide approval because they're tops in quality and are in high volume production now. And our 16-bit processors are on the way.

Throughout our entire product line, we have the experience, technology, quality, price, performance and availability to surprise you in a lot of pleasant ways.

AREA SALES OFFICES: WESTERN AREA, Toshiba America, Inc., (714) 752-0373; CENTRAL AREA, Toshiba America, Inc., (312) 945-1500; EASTERN AREA, Toshiba America, Inc., (617) 272-4352; NORTHWESTERN AREA, Toshiba America, Inc., (408) 244-4070. REPRESENTATIVE OFFICES: ALABAMA, Gien White Associates, (205) 883-7938; ANIZONA, Semper Fi Sales Company, (602) 991-4601; ARKANSAS, Technology Sales Company, (214) 380-0200; CALIFORNIA (Northern), Eirepco, Inc., (415) 962-0660; CALIFORNIA (Southern), Bager Electronics, Inc., (714) 957-3367; COLORADO, Duffy Associates, (303) 595-4244; CONNECTICUT, Datcom, Inc., (203) 288-7005; DELAWARE, Vantage Sales, (609) 663-6660; FLORIDA, Donato & Associates, (305) 352-0727, (813) 785-3327; GEORGIA, Glen White Associates, (404) 441-1447; IDAHO, Components West, (206) 271-5252; ILLINOIS, L-TEC, (312) 773-2900; INDIANA, Leslie M. DeVoe Company, (317) 842-3245; LOUISIANA, Technology Sales Company, (214) 380-0200; MAINE, Datcom, Inc., (617) 891-4600; MARYLAND, Glen White Associates, (301) 252-6360; MASSACHUSETTS, Datcom, Inc., (617) 891-4600; MICHIGAN, R.C. Nordstrom & Company, (313) 559-7373; MINNESOTA, Quantum Sales, Inc., (612) 884-4700;

## DING SOURCE NMOS MICROS. CLOSE.

Get close to the world's most respected name in MOS technology and make us your new source of CMOS and NMOS Microcomputers and Microprocessors.

Toshiba. This new perspective will do you a world of good.

| Device   | Technology                    | ROM (Bytes)          | RAM (Bytes)                 | Speed                         | Operating<br>Current (Max) | Standby<br>Current |

|----------|-------------------------------|----------------------|-----------------------------|-------------------------------|----------------------------|--------------------|

| TMP8048  | NMOS                          | 1K                   | 64                          | 6MHz                          | 135mA                      | 15mA               |

| TMP80C48 |                               | 1K                   | 64                          | 6MHz                          | 10mA                       | 10µA               |

| TMP8049  | NMOS                          | 2 <b>K</b>           | 128                         | 6MHz/11MHz                    |                            | 50mA               |

| TMP80C49 |                               | 2K                   | 128                         | 6MHz                          | 10mA                       | 10µA               |

| TMP80C50 | CMOS                          | 4K                   | 256                         | 6MHz                          | 15mA                       | 10µA               |

|          | 8-BIT                         | MICROPRO             | CESSOR-C.                   | MOS Z80A FA                   | MILY                       |                    |

| Device   | De                            | scription            | Technology                  | Operati<br>Curren             |                            |                    |

| TMPZ840  |                               | Z80A CPU             | CMOS                        | 15mA<br>(@ 4MF                |                            |                    |

| Also a   | vailable are                  | the popular Z<br>CLO | 80 peripherals<br>CK, DMA & | in CMOS inclu<br>S I/O.       | uding P I/O, CT            | тС,                |

|          | 8-1                           | BIT MICROP           | ROCESSOR-                   | -8085A FAMI                   | LY                         |                    |

| TMP8085A | NMOS                          | 8085A 3M             | Hz CPU plus                 | many of the po                | pular 8-bit peri           | pherals.           |

| 4        | -BIT SING                     | LE CHIP MIC          | CROCOMPU                    | FERS-TLCS                     | -47 FAMILY                 | 14                 |

|          | CS-47 Inclue<br>ruction, Inst |                      | verful Feature<br>• 12-     | s Including:<br>Bit Timer/Cou | nter                       |                    |

|          | VO Capabili                   |                      | • 6 In                      | nterrupts                     |                            |                    |

| Availabl | e Device Ty                   |                      |                             | vices With LC.                | D Drive                    |                    |

|          | Devices                       |                      |                             | vices With V.F                |                            |                    |

|          | Devices                       |                      |                             | ny ROM/RAN                    |                            |                    |

#### TOSHIBA AMERICA, INC. A WORLD STANDARD IN MOS.

MISSISSIPPI, Glen White Associates, (205) 883-7938; MONTANA, Components West, (206) 885-5880; NEVADA, Elrepco, Inc., (415) 962-0660; NEW HAMPSHIRE, Datcom, Inc., (617) 891-4600; NEW JERSEY, Necco 1, (201) 461-2789, Vantage Sales, (609) 663-6660; NEW MEXICO, Semper Fi Sales Company, (602) 991-4601; NEW YORK, Necco 1, (201) 461-2789, PI-tronics, (315) 455-7346; NORTH CAROLINA/SOUTH CAROLINA, Glen White Associates, (919) 848-1931, (615) 477-8850; NORTH/SOUTH DAKOTA, Quantum Sales, Inc., (612) 884-4700; OHIO, Del Steffen & Associates, (216) 461-8333, (419) 884-2313, (513) 293-3145; OXLAHOMA, Technology Sales Company, (214) 380-0200; OREGON, Components West, (503) 684-1671; PENNSYLVANIA, Del Steffen & Associates, (216) 461-8333, (419) 884-2313, (513) 293-3145; OXLAHOMD, Datcom, Inc., (617) 891-4600; OHEGON, Components West, (503) 684-1671; PENNSYLVANIA, Del Steffen & Associates, (216) 461-8333, (419) 884-2313, (513) 293-3145; OXLAHOMD, Datcom, Inc., (617) 891-4600; OHEGON, Components West, (503) 684-1671; PENNSYLVANIA, Del Steffen & Associates, (216) 461-8333, (419) 884-2313, (513) 293-3145; OXLAHOMD, Datcom, Inc., (617) 891-4600; VIRGINIA/WEST VIRGINIA, Glen White Associates, (804) 237-6291, (804) 295-0435, (804) 224-7764, (804) 224-0404; WASHINGTON, Components West, (206) 885-5880; WISCONSIN, L-TEC, (414) 774-1000; WYOMING, Duffy Associates, (303) 595-4244; CANADA, Electro Source Inc., (416) 675-4490.

## In 64K DRAMs, INMOS high performance and flexible ...including 8K x 8.

Look to INMOS for a wide selection of 64K DRAMs. We offer access times from 100ns. By-1, by-4, and by-8 organizations. Plus features that boost performance and simplify design. This is the family that lets you avoid compromises by giving you the performance and organization you want...at costs you can afford.

8K x8 — The cost and space saver. This newest member of the INMOS 64K DRAM family, available in a plastic package, offers access times of 120 and 150ns. The by-8 organization is a natural for microprocessor designs and other applications that require word width rather than memory depth...in process controllers, intelligent terminals, and buffer memories for example. And its pin 1 refresh makes it a very attractive alternative to 8K x 8 static RAMs. Because it combines low power and low cost with minimal support circuitry.

**16K x4** — The performance chip. With 100, 120, and 150ns access times, this organization makes a lot of sense in high-performance systems, such as high-resolution graphics, where high data rates are required. Packaged in plastic DIPs, the IMS2620 also gives you the right combination of cost, organization, and speed for microprocessor systems, terminals, and even arcade and home games. If you're upgrading from 16K x1 chips, it provides a factor of four reduction in chip count. And its "CAS before RAS" refresh assist function minimizes required support circuitry for cost and space savings.

64K x1 — The big-system choice. This DRAM also gives you a choice of 100, 120, and 150ns access times. What's more, it includes "Nibble Mode," which allows effective cycle times below 85ns. Available in a variety of packages, including plastic DIPs, ceramic DIPs, and chip carriers, it's ideal for systems requiring lots of memory depth.

Check the chart. You'll find the industry's broadest family of 64K DRAMs...and the right device for your requirements. Then call an INMOS distributor for all the details.

| Organization | Access Time (ns) | Cycle Time (ns) | Part No.   |

|--------------|------------------|-----------------|------------|

| 8Kx8         | 120              | 190             | IMS2630-12 |

|              | 150              | 240             | IMS2630-15 |

| 16Kx4        | 100              | 160             | IMS2620-10 |

|              | 120              | 190             | IMS2620-12 |

|              | 150              | 240             | IMS2620-15 |

| 64Kx1        | 100              | 160             | IMS2600-10 |

|              | 120              | 190             | IMS2600-12 |

|              | 150              | 230             | IMS2600-15 |

**INMOS Distributors:** Anthem Electronics, Arrow Electronics, Falcon Electronics, Future Electronics, Lionex Corp.

Colorado Springs, Colorado (303) 630-4000 — TWX 910/920-4904 • Roswi Georgia (404) 475-1936 — TWX 810-751-0015 • Burlington, Mass, Gi17 (27351) — TWX 710-332-8777 • Columbia, Maryland (301) 995-0813 — TWX 710-862-283 • Minneapolis, Minnesota (612) 831-5526 — TWX 910-9572-40 • Richardson, Texas (214) 669-9001 — TWX 910-997-0822 • Sam Jose, Calif, (408) 299-1766 — TWX 910-338-2151 • Torrance, Calif. (213) 530-7764 — TWX 910-347-7334 • Britsol, England 0272-200-861 — TLX 551-444723 • Immeuble Monaco (1) 887-2201 — TLX 201222 • Germany (089)

inmos, and IMS are trademarks of INMOS' Group of Com CIRCLE 12

## means organizations

**Vallin**

4Kx1

Oct. 30\_Nov. 2 Booth #2665/67

## The Executive 10/102 and 10/102G have all the features of DEC terminals plus some extra toppings.

The readability of a 14" screen. Your operators will love our big, high resolution, non-glare screen. They can choose a  $24 \times 80$  or 132-column format and enhance the display with double width/height characters. There's a full complement of video attributes including high/low intensity, blink, reverse and underline.

**Plug-for-plug DEC® compatibility. For hundreds less**. Not only does the Executive 10/102 cost less than DEC, you get the extra value of a tilt & swivel display. And a detached, low profile, sculptured keyboard that meets European standards and includes a separate, 14-key numeric keypad.

**Graphics mode emulation of Tektronix 4010/4014.** The Executive 10/102G runs all TEK<sup>®</sup> programs plus many other graphics software packages. In its native mode, the 10/102G adds arc and area fill features not available in the TEK 4010/4014 but required in many applications.

So if you're hungry for a more satisfying DEC-compatible terminal, call Esprit (Es-pree) toll-free at 800-645-4508. In NY State 516-293-5600.

<sup>®</sup>Registered trademarks: DEC, Digital Equipment Corporation. TEK, Tektronix Inc.

#### **LETTERS TO THE EDITOR**

#### Where were you?

Reading your editorial of August 1984, I wonder if we went to the same National Computer Conference. The temperature was indeed 110 degrees, but I did not notice any undue stress. In fact, I was still able to wear my suit all day (it is my office and I am lost without the pockets) and still remain comfortable. My second comment is, with all those free shuttle buses, why did you need to take a cab anywhere? I brought my wife along to Las Vegas and we went to shows in the evening, notably Gallagher, and were able to walk to the many attractions on the Strip near our hotel. After the fiasco at NCC in Anaheim, I would think Las Vegas would have been thought a blessing. Everything seemed to go quite well there this year. I believe the "Great Olympics Scare of '84," of course, had something to do with lessened travel in general, but was not a factor in the lower attendance at NCC.

To be frank, in your editorial there was no reference to what you consider more tolerable. Did you mean better climate, better facilities, less expensive accommodations, or what? Maybe we should have an NCC East and an NCC West. I do not have answers, but would be interested in other observations.

Richard Rorex Ampex Corp 200 N Nash St El Segundo, CA 90245

Yes, we did go to the same National Computer Conference, and I agree with Mr Rorex that the show itself was quite well organized—especially when compared to

last year's Anaheim fiasco with the overheated tents and the converted basement of the Disneyland Hotel. However, members of the trade press are expected to attend all sorts of other functions scattered throughout the city, in addition to the conference. That is why I directed my criticism primarily at the city of Las Vegas and not at the NCC organizers.

Leurener

The windstorm and power failure occurred just after I arrived at a press reception in the Hacienda casino. One of the more serious cab problems occurred after a business luncheon at a restaurant called The Library. Like Mr Rorex, I did use the shuttle buses whenever possible, and they were much more plentiful than at the Interface Conference earlier in the year. I heard that at that conference, the city restricted the number of shuttle buses to appease the cab fleet owners.

Like Mr Rorex, I do not claim to have all the answers. Perhaps, however, if we compare our experiences and state our personal priorities, the organizers will learn how to please more of the people more of the time. And, we may be able to accelerate the learning process if—as proposed in my editorial—we start to vote with our feet. Incidentally, AFIPS still has not announced the official attendance figures for NCC, so one can only assume that they were embarrassingly low.

Michael Elphick Editor in Chief

#### **Reader comment**

Congratulations on an excellent June 15, 1984 issue. I have browsed/read six articles, and they all scored "high" value to me. Outstanding! I only regret that there is generally so little time to learn and read.

I'm passing on my *Computer Design* magazine to a number of colleagues. Eventually, it lands in the local library of my technology group. Bjorn T. Cronhjort

Ericsson Information Systems AB Bromma Sweden

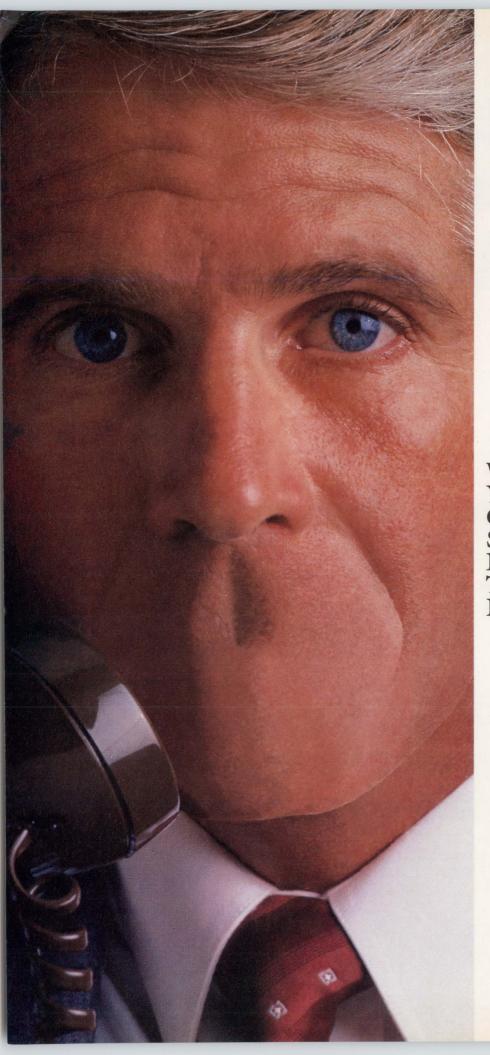

## "Frankly, gentlemen, their capabilities astound me."

"Thank you, sir. We'd like to mention their reliability as well; Numonics is rather famous for that. And their high resolution. And the flexible range of sizes and capabilities. Would you like to know more?"

The # 2200 Tablet has a user-specified resolution as high as .001", with standard features including versatile firmware for self diagnostics, HOST override of switch-settable functions, and matrix menuing. It operates in six programmable modes: point, stream, switch-stream, incremental, polled, or timed, and interfaces in RS232, IEEE, or byte parallel, with packed binary or standard format. Sizes range from 6" x 6" to 36" x 48".

The # 2210 Tablet is a simplified version of the 2200 and also comes in sizes from 6" x 6" to 36" x 48" and, like the 2200 all sizes have identical control electronics. A single card works for all. It digitizes up to 200 points per second, in the 6 programmable modes. It accepts downloads for changing default operating conditions. Standard pen; optional 1, 4 or 16 button cursors. This low-profile, self-diagnostic tablet interfaces with RS232, IEEE, or byte parallel, in standard or packed binary format.

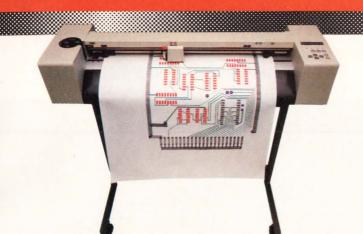

NUMONICS

The # 5624 Plotter with stand, uses a grit-roller transport system that produces smooth, accurate, controlled plots on D size cut-sheet paper or mylar. The new synchro-belt drive is quiet and fast, plotting almost 10" per second to a variety of commands for vectors, line types, circles, arcs, ASCII characters, symbols, hatching, etc. The ultimate machine for sophisticated plotting. Four turret mounted, self-capping pens.

The # 6412 10-pen Plotter is designed for business graphics or any application needing a wide range of colors, and line types, comprehensive command structure, accuracy, and high speed almost 18" per second. Pens have soft-landing and automatic-capping systems, with automatic speed control for different pen types. Accepts 11" x 17" medium. Rugged, industrial quality construction. The # 5424 Plotter with stand, also uses the grit-roller system, is a lower cost, single pen plotter that accepts non-sprocketed cut-sheet paper or mylar, 22" to 24" wide. Plots at almost 6" per second, is extremely accurate and has a similarly comprehensive command struc-

ture. It is designed and constructed for high durability.

----

-----

DEC

9%

HP

Dther

For further information, write:

418 Pierce St., Lansdale, PA 19446.

(215) 362-2766; TWX 510-661-6585 CIRCLE 16

ople - 23%.

COMPUTER DESIGN/October 15, 1984

15%

rudy

27

## MORE OUT OF THE TUBE.

AMD's CRT controller family wrings every last drop of performance out of your video screen. You get a dazzling, attractive display your customers will find irresistible.

### The Am8052. You'll wonder where the flicker went.

Thanks to on-board DMA and triple row buffers, you get vertical and horizontal split screens, with smooth-scrolling windows. All flicker-free.

You even get double-height and doublewidth characters, superscripts and subscripts.

### The Am8152A/53A. Make your display look its sparkling best.

You get cleaner, crispier characters with the 100MHz video system controller. And proportional spacing down to two pixels.

No other VLSI chip set gives you as much. And to top it off, the chips even take over many of the functions of the CPU. Like linked list manipulation for easier editing. Your CPU has better things to do.

### We'll put you as far ahead of the competition as we are.

Controllers. Bipolar and MOS microprocessors. Communication circuits. Signal processors. Nobody makes as many peripherals for as many microprocessors as AMD.

And every single chip meets or exceeds the International Standard of Quality.

The International Standard of Quality guarantees a 0.1% AQL on all electrical parameters, AC and DC, over the entire operating range. If you want the most out of your tube, put the squeeze on AMD. We'll show

you several ways to put the sparkle in your customer's smile.

(408) 749-5000, outside California, call toll-free (800) 538-8450, Ext. 5000.

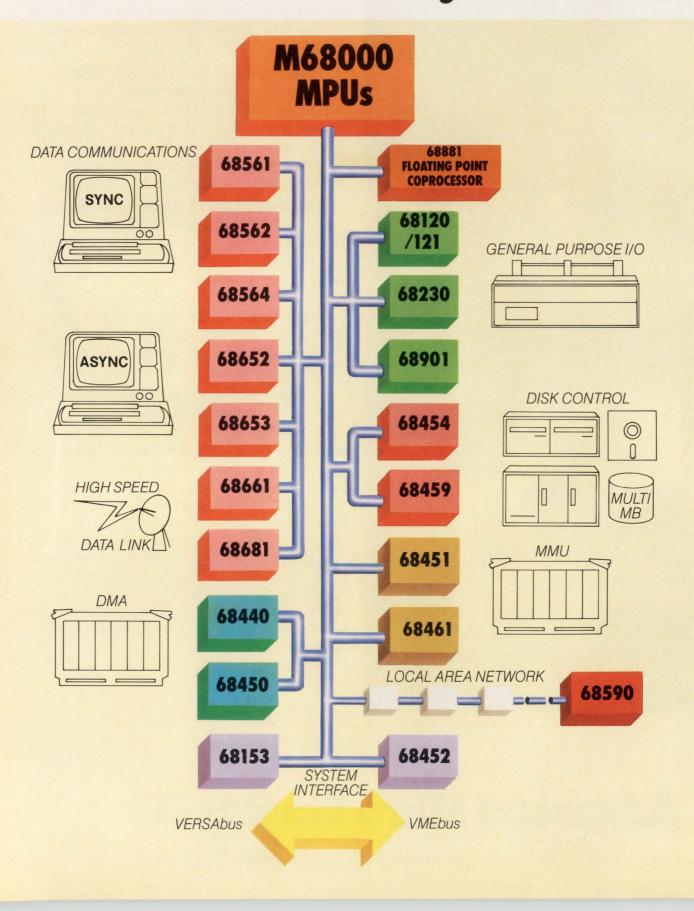

# For all these reasons, should be your next

# the M68000 Family high-performance system.

Make the systems connection and maximize the often-documented advantages of an M68000 Family microprocessor for your next highperformance system.

Any MPU standing alone, even the MC68000, is no more than potential to be exploited. The rest of the M68000 Family is devoted to that specific purpose.

This extensive family of compatible, easy-to-use MPU-peripheral devices is available from Motorola and the industry's most comprehensive complement of contractual alternate sources.

Data Comm, DMA Control, Local Area Network Control, Parallel, Serial and General Purpose I/O, Memory Management, Bus Control: all are there and more, to raise your systems above the competition in a hotly-competitive marketplace.

#### Critical for high-performance systems-DMA.

Moving data around fast, with minimal intervention from the processor is the responsibility of the 68440 Dual DMA and the 68450 DMA Controller. The 68440 is a two-channel high-speed solution, capable of a 5 Mbyte/sec transfer. The 68450 offers four independent DMA channels and extensive support for the movement of complex data structures.

#### Link your system to the outside world.

Whether to a terminal, a transmission line or another system, M68000 Family data communication devices link up your system efficiency and free the processor for more important work. The family offers one of the most popular data comm parts available – the 68661 Enhanced Programmable Communications Interface. It's a universal synchronous/asynchronous comm chip that interfaces easily to M68000 MPUs and directly to most 8-bit MPUs.

The 68681 Dual UART is another important available family peripheral. It provides two completely independent full duplex receiver/transmitter channels in a single package.

A Multi-Protocol Communications Controller, the 68652, contributes extensive flexibility, and basic microcomputer functions are provided by the 68901 Multi-Function Peripheral.

Still other aspects of M68000 Family data comm functionality available from Motorola include a Polynomial Generator Checker, a Parallel Interface/Timer, and two Intelligent Peripheral Controllers.

Additional 68000-compatible data communication parts are available and under development by other leading VLSI manufacturers.

#### Network and bus control.

Network and bus control requirements expand as multiple-processor operations increase and networking grows in popularity. The M68000 Family grows to meet these requirements with circuits like the 68590, scheduled for introduction this year. It's designed to meet all IEEE Ethernet<sup>™</sup> specifications for M68000 systems. And, with the VMEbus becoming a standard, a new VME Controller will be added to the family as well.

#### Disk control and memory management.

Management of data storage devices is the domain of the 68454 Intelligent Multiple Disk Controller. The extremely flexible IMDC can control any combination of up to four single- or dual-density floppy and hard disks of various formats.

Our 68451 is now seasoned by years of experience with multi-user, multi-task systems, because memory management was one of the first peripheral functions identified in processor systems. UNIX™ System V/68™ fully supports operation of the 68451 MMU. Now, the requirements of 32-bit demand-paged virtual environments are immediately satisfied by the MC68461 Memory Management Controller.

#### Floating point.

The Motorola 68881 Floating Point Coprocessor is a companion processor to the 68020 scheduled for sampling within the next few months. It's designed to provide support for the latest revision of the IEEE specification for floating point high-level calculations, and also can be used as a peripheral with the 16-bit M68000 Family processors. For additional information on the entire M68000 Family, write or fill out the coupon, and send it to Motorola Semiconductor Products, Inc., P.O. Box 20912, Phoenix, Arizona 85036. Do it today. Ethernet<sup>™</sup> is a trademark of Xerox Corporation. UNIX is a trademark of AT&T Bell Laboratories. System V/68 is a trademark of Motorola Inc.

#### M68000 FAMILY

| M68000                                    |             |               |

|-------------------------------------------|-------------|---------------|

| Function                                  | Designation | Device No.    |

| 16-bit Microprocessor                     | MPU         | 68000         |

| 8-bit Microprocessor                      | MPU         | 68008         |

| 16-bit Virtual Memory                     |             |               |

| Microprocessor                            | MPU         | 68010         |

| 16-bit Expanded                           |             |               |

| Virtual Memory                            |             |               |

| Microprocessor                            | MPU         | 68012         |

| 32-bit Virtual Memory                     |             |               |

| Microprocessor                            | MPU         | 68020         |

| Floating Point                            |             |               |

| Coprocessor                               | FPC-P       | 68881         |

| Dual Direct Memory                        |             |               |

| Access                                    | DDMA        | 68440         |

| Direct Memory Access                      |             |               |

| Controller                                | DMAC        | 68450         |

| Multi-Protocol Commu-                     |             |               |

| nications Controller                      | MPCC-2      | 68561†        |

| Dual Universal Serial                     |             |               |

| Communications                            | DUCCO       | 00500         |

| Controller                                | DUSCC       | 68562         |

| Serial I/O                                | SIO         | 68564†        |

| Multi-Protocol Commu-                     | MIDOO       | 00050         |

| nications Controller                      | MPCC        | 68652         |

| Polynomial Generator<br>Checker           | PGC         | 68653         |

| oneener                                   | FGC         | 00000         |

| Enhanced Program-                         |             |               |

| mable Communica-<br>tions Interface       | EPCI        | 68661         |

|                                           | EFCI        | 00001         |

| Dual Universal Asyn-<br>chronous Receiver |             | D. S. William |

| Transmitter                               | DUART       | 68681         |

| Intelligent Multiple Disk                 | DUARI       | 10000         |

| Controller                                | IMDC        | 68454         |

| Disk Phase Lock Loop                      | DPLL        | 68459+        |

| Memory Management                         | DILL        | 004051        |

| Unit                                      | MMU         | 68451         |

| Memory Management                         | IVIIVIO     | 00401         |

| Controller                                | MMC         | 68461         |

| Intelligent Peripheral                    | IVIIVIC     | 00101         |

| Controllers                               | IPC         | 68120/121     |

| Parallel Interface/Timer                  | PI/T        | 68230         |

| Multi-Function                            | 11/1        | 00200         |

| Peripheral                                | MFP         | 68901         |

| Local Area Network                        | 1711 1      | 00001         |

| Controller-Ethernet                       | LANCE       | 68590         |

| Bus Interrupter Module                    | BIM         | 68452         |

| Bus Arbitration Module                    | BAM         | 68153         |

| Dustribiliadon Module                     | DITIAL      | 00100         |

†Alternate source available only

MOTOROLA

####

## Because You need to run FORTRAN programs 10X to 100X faster...

Practical in terms of use: Mini-MAP's compiler allows you to program the array processor directly in FOR-TRAN. An assembler, a linker, and a debugger are also part of the package. Plus you can use our library of over 250 highly optimized scientific subroutines.

Practical in terms of throughput: Because it is an array processor, Mini-

MAP increases the computing speed of a mini or supermini computer as much as 10 to 100 times. Where it takes a typical minicomputer minutes to perform tasks such as image rotation, Mini-MAP reduces interactive response times to seconds. Your computer may require hours to perform each step of a trial-and-error-process such as simulation, but Mini-MAP, can zip through in mere minutes. DEC, PDP-11, LSI-11, and VAX-11 are trademarks of Digital Equipment Corp. Mini-MAP is a trademark of CSPL

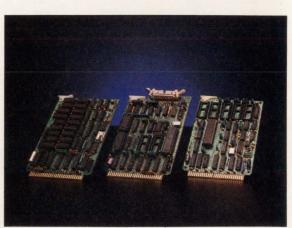

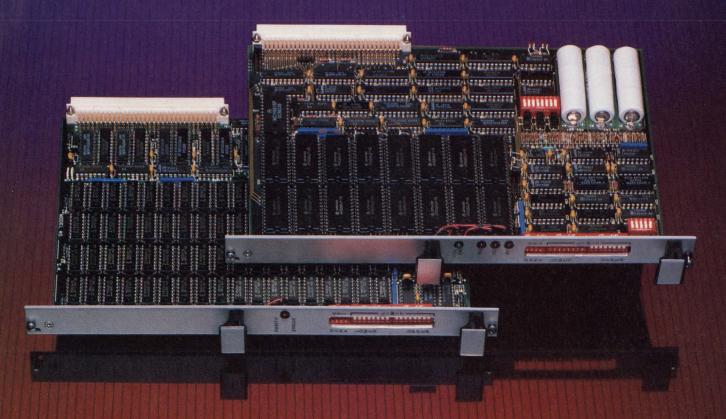

Mini-MAP is available as an economical, four-board set or as a packaged system. Now, with Mini-MAP. OEMs can offer their customers a better product at lower costs. Mini-MAP's low power demands, small size, and high reliability make the package extremely attractive. And end users will find our FORTRAN compiler and other software tools minimize program development costs.

Practical in terms of cost:

Some practical things to know about Mini-MAP:

32-bit DEC<sup>™</sup> floating point format □ Interfaces to DEC PDP-11, LSI-11, and VAX-11 series □ Up to 16 MBytes of data memory □ 1024 x 1024 2-D FFT in 8.8 seconds □ Extensive software tools plus dedicated applications assistance including training, convenient parts depots, and field service staff support our worldwide installations. To find out how Mini–MAP can work for you, **call toll free 1 800 325–3110**.

THE ARRAY PROCESSORS

40 Linnell Circle, Billerica, Massachusetts 01821 • 617/272-6020 • TWX 710-347 0176

CIRCLE 18

#### Data bases add function to meet computer aided design needs

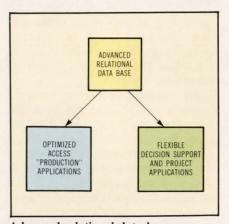

Developments now underway promise more advanced relational data bases capable of handling optimized access "production" tasks and flexible access decision support. Until these more efficient data bases appear, a variety of database techniques are being used.

Considerable design effort has already been expended on specialized data bases to store graphical data for rapid display. Manufacturers of engineering workstations have developed such data bases to support their equipment; for example, Apollo Computer's (Chelmsford, Mass) Graphic Metafiles for use with its engineering workstations. Similarly, Computervision (Bedford, Mass), a complete computer aided design (CAD) manufacturer, treasures its proprietary in-house graphics data bases.

Database developments are also driven by the needs of the even larger management information sector which seeks better ways to combine the data storage needs of executives and clerks. Database experts agree that the best long range solution for this type of storage will be universal data bases that can handle a variety of data at the same time. Such research is underway at companies like Computer Corp of America (Cambridge, Mass), Mitel (Ottowa, Canada), and in several university campuses.

With the spreading use of data bases, it has become apparent that computers perform two different types of activities: optimized access and decision support. High production data processing and engineering design graphics image displays require optimized access. Decision support systems aid management decision making and support basic engineering design procedures.

If the data base is for decision support, relational access is exceptionally capable and flexible. However, where

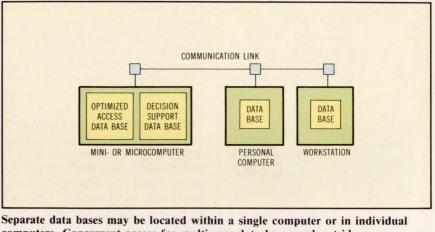

computers. Concurrent access for multi-user data bases and outside access through communication links are possible.

optimized access is necessary, existing relational data bases cannot satisfactorily handle many data processing production and graphics storage problems. Several different techniques are currently used to allow data bases to provide decision support and optimized access. Since relational data bases are frequently unable to handle optimized access, other more conventional or more specialized data bases are used for these activities. But relational types remain the best choice for decision support.

#### Separate data bases

It is common in business applications to maintain completely separate data bases for decision support and optimized access. Separate, independent data bases may occupy space in the same disk storage unit under the control of one computer, or they may each be in separate storage units attached to different computers. When computers or workstations are connected, separate data bases can be accessed by multiple users, sometimes concurrently. In many cases the same or similar information is stored in the separate data bases, especially when access to individually compiled data bases is through personal computers.

Separate data bases can be organized to minimize or eliminate data duplications by partitioning and storing all similar information in one data base. For example, Mentor Graphics (Beaverton, Ore) uses a specialized data base optimized for graphics presentations. Jack Bennett, a project leader at Mentor, explains that in this database scheme for computer aided engineering (CAE) circuit design applications, a separate relational data base stores supporting information about circuit properties and connections between components. This information can be readily accessed.

The relational data base stores circuit-related items such as net lists, components, pin configurations, and properties. Some applications must start with specific components, find all the pins attached to them, and then all the nets attached to those pins. Other applications start at the nets and work their way to the components. Still others allow users to browse through a circuit and randomly change individual component properties. Relational flexibility allows all these procedures to be followed with ease.

(continued on page 34)

#### Data bases add function

(continued from page 33)

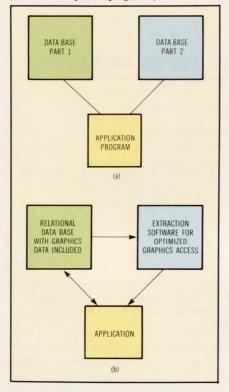

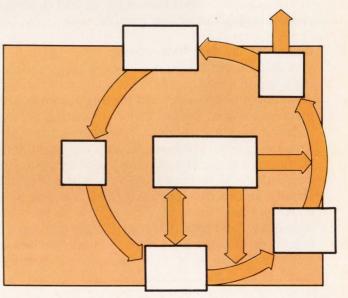

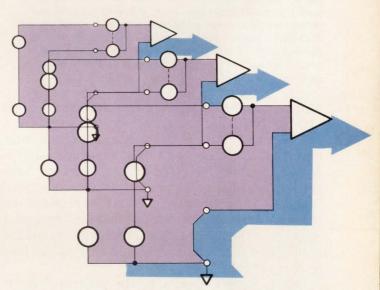

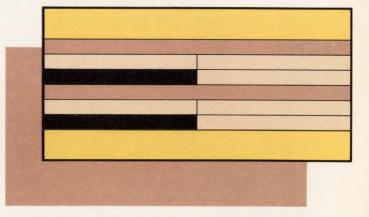

When stored information can be cleanly divided, the data base can be partitioned into separate parts, and only the appropriate part is accessed (a). Extraction software can provide optimized access to data stored in a relational data base. Decision support data is obtained directly from the data base, while optimized access is through the extraction software (b).

The basic requirement for a graphical data base is more straightforward—the stored information has to be put on the screen as quickly as possible. Suppose the components for a computer aided printed circuit board design are to be purchased from outside vendors. A relational data base can store needed information on component suppliers.

If the designer needs to know the total cost of the parts on the printed circuit, however, the graphics data must be correlated with costs and other project information. Graphical and nongraphical information must then be merged from the separately partitioned data bases. The two can be tied together through design application programs that access both data bases. From a graphical display, the user may select objects of interest. The application program can then query the graphics data base to identify those objects. With those identification codes, the application program can then query the relational data base and retrieve any information the user desires about the selected object.

According to Emran Quereshi, CAD database engineer at Mitel, (Kanata, Ontario, Canada), schematic entry terminals and printed circuit layout tools have been interfaced to a central relational data base, to commercial testers, and to other computer aided manufacturing (CAM) operations. Mitel's system, written in C, is VAX-compatible and is now in the testing stages.

#### **Extraction techniques**

Michael Stonebraker, a professor and database expert at the University of California at Berkeley, has proposed another way to tackle CAE data storage problems. Both the graphics and the supporting information would be kept in a relational data base. This provides an efficient way to extract the graphics data and allows fast display.

Take a data base designed specifically for graphics storage. Discard concurrent access, crash recovery, and other database controls and services. What remains is the access structure—the way that data is handled between main memory and disk storage so as to optimize movement of data between the two. In other words, the result is optimized extraction software.

Equipped with this extraction software, a relational data base can store information for graphics display, as well as for decision support. When displays are needed, the database stored graphics information is extracted and transformed into the most efficient form for main memory storage and use. For example, a designer may wish to browse through the portion of a design of an aircraft wing between the wing tip and the engine. To do that without suffering long waits for display changes, all the needed graphics data must be moved into main memory. Using the extraction capability, the revised main memory contents are quickly retransformed into database format once the design has been reviewed. Then, the memory contents are moved back into the relational data base.

#### **Relational access**

Decision support can also be effectively combined with optimized access by superimposing a relational "front end" on a nonrelational data base. A relational data base's flexibility in handling unpredictable inquiries is due to operations like Join. With this operation, users can tie together two groups of records, when no tie was planned. This makes possible the kind of queries needed for decision support.

By combining a query language that includes Join and other operations with an optimized access data base, decision support and access functions are possible. Where "production" activities are a primary concern, priority arrangements can be added to keep decision support queries from interfering with production schedules. Security aspects and access restrictions can also be handled at the relational front end. This is the

Advanced relational data bases are expected to provide a single unified basis for both optimized access and flexible decision support. Such data bases are not yet available.

approach used in such database products as RQL/32 from Perkin Elmer (Oceanport, NJ) and ENFORM from Tandem Computers (Cupertino, Calif).

These techniques for linking optimized access and decision support database uses involve extensive specialized software design efforts. General-purpose relational data bases that can handle both types of requirements would be a better solution. These new data bases are already under development. They will need new capabilities, including massive main memory buffer storage, multidimensional indexing, and a rich selection of primitive objects that includes geometrics, as well as familiar alphanumerics. Developments along these lines are being stimulated by the needs of CAD activities.

Most general-purpose data bases are best suited for accessing data residing on a disk. Thus, there are no commercial data bases designed to make full use of 5-Mbyte main memory buffer storage areas. But, CAD applications require the prompt display of massive amounts of data. Consequently, main memory buffer storage must be very large. This capability is currently under development.

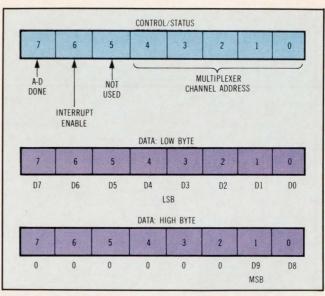

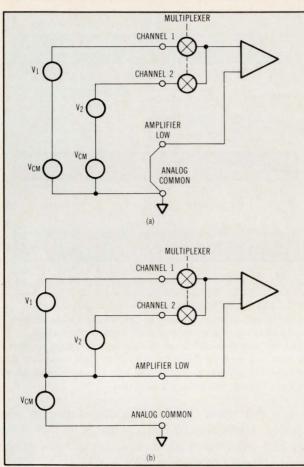

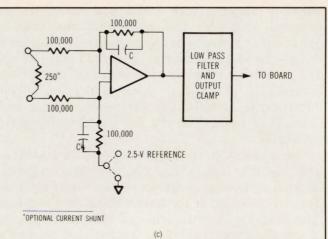

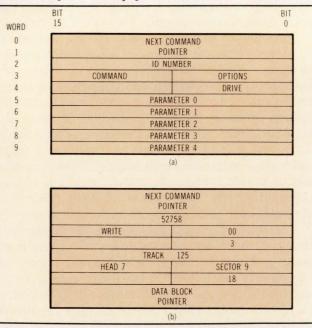

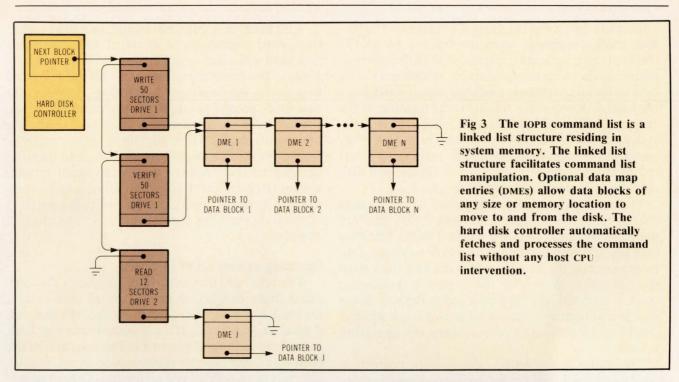

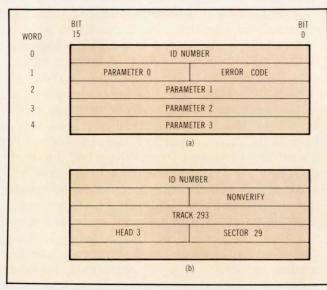

Existing relational data bases use one-dimensional indexing. This serves well where the items to be indexed are dollar figures or words. For example, a typical computer stored table contains columns with names, ages, salaries, and departments for each employee. Access is gained through a one-dimensional index of the selected key column.