## **OPERATION MANUAL**

USER'S GUIDE SOFTWARE SPECIFICATION GUIDE

# IN-CIRCUIT DEBUGGER

## Preliminary

## **ICD 278**

FOR

## **Z80**

## OPERATION MANUAL

Copyright© 1984, ZAX Corporation. All Rights Reserved under International and Pan-American Copyright Conventions. No part of this publication may be reproduced in any manner whatsoever without written permission from ZAX Corporation.

Prepared by

ZAX Corporation 2572 White Road, Irvine, California 92714

Operation Manual: Part No. 20-100-06, Rev.B includes;

User's Guide (278/Z80) : Part No. 20-100-XX Software Specification Guide (278/Z80): Part No. 20-100-XX Command Reference Guide : Part No. 20-100-03

Printed: June 1984

### LIST OF EFFECTIVE PAGES

THE TOTAL NUMBER OF PAGES IN THIS PUBLICATION IS 151, CONSISTING OF:

PAGE NO.

ISSUE DATE/REVISION LEVEL

| TITLE JUNE              | 1984/REV.B |

|-------------------------|------------|

| B JUNE                  | 1984/REV.B |

| I THROUGH VII JUNE      | 1984/REV.B |

| I THROUGH VII JUNE      | 1984/REV.B |

| I-1 THROUGH 1-6 JUNE    | 1984/REV.B |

| 2-1 THROUGH 2-8 JUNE    | 1984/REV.B |

| 3-1 THROUGH 3-40 JUNE   | 1984/REV.B |

| 4-1 THROUGH 4-2 JUNE    | 1984/REV.B |

| 4A-1 THROUGH 4A-4 JUNE  | 1984/REV.B |

| 4B-1 THROUGH 4B-2 JUNE  | 1984/REV.B |

| 4B-1 THROUGH 4B-2 JUNE  | 1984/REV.B |

| 4D-1 THROUGH 4D-4 JUNE  | 1984/REV.B |

| 4E-1 THROUGH 4E-12 JUNE | 1984/REV.B |

| 4F-1 THROUGH 4F-4 JUNE  | 1984/REV.B |

| 4G-1 THROUGH 4F-4 JUNE  | 1984/REV.B |

| 11 JUNE                 | 1984/REV.B |

| 5-1 THROUGH 5-12 JUNE   | 1984/REV.B |

| 6-1 THROUGH 6-20 JUNE   | 1984/REV.B |

|                         |            |

NOTE: THE PAGES AFFECTED BY CHANGES ARE NOTED BY \* AND INDICATED BY ISSUE DATES AND REVISION LETTERS PRINTED NEXT TO THE PAGE NUMBER. THE ORIGINAL ISSUE OF THIS PUBLICATION IS REVISION B, JUNE 1984.

## TABLE OF CONTENTS

PART I - USER'S GUIDE

.

Section

Page

| I   | INTRODUCTION and DESCRIPTION<br>Introduction<br>Description<br>ICD Major Components<br>Specifications (General)<br>Specifications (Emulation)                                                                                                                                                      | 1 – 1<br>1 – 2<br>1 – 3                                     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| II  | CONTROLS and COMPONENTS<br>Introduction<br>ICD Control and Component<br>Description<br>Top View<br>Side View<br>End View (A)<br>Baud Rate Switch Settings<br>End View (B)<br>External Break Connector<br>Event Trigger Connector<br>CPU Plug Probe<br>External Break Cable<br>External Break Cable | 2-1<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-5<br>2-6<br>2-7 |

| III | SYSTEM CONFIGURATION/START-UP<br>SEQUENCE and COMMAND GUIDE<br>Introduction<br>System Configuration<br>Start-up Sequence<br>Command Guide                                                                                                                                                          | 3-2<br>3-3                                                  |

| IV  | TECHNICAL REFERENCES<br>Introduction<br>A - Emulation Select Switch<br>B - Data Bus Emulation Connector                                                                                                                                                                                            | 4A-1                                                        |

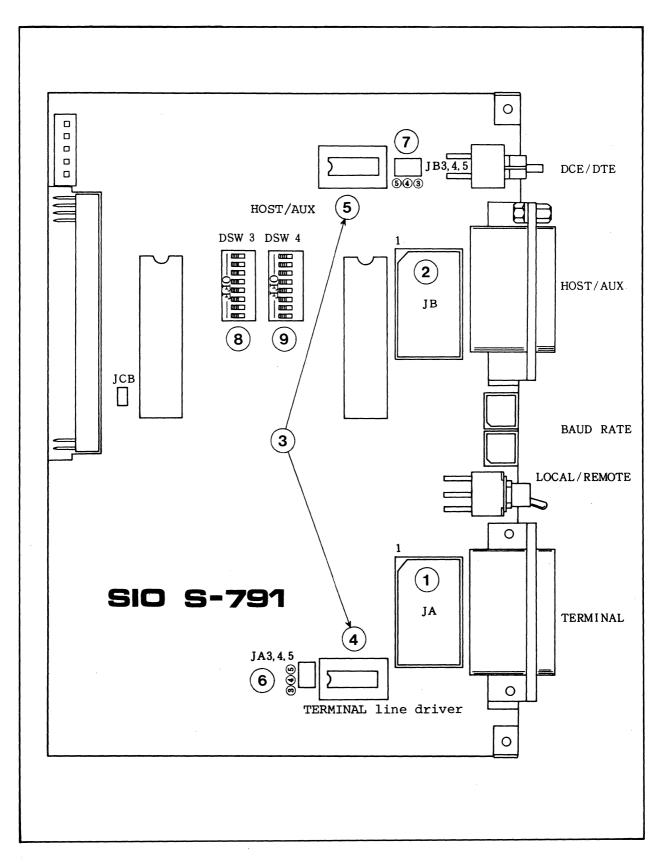

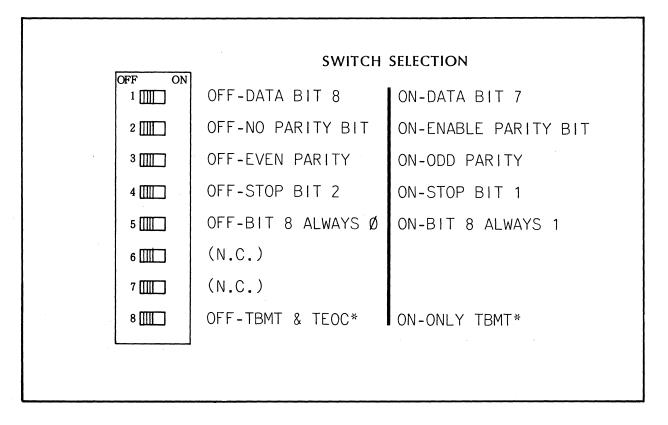

|     | C - Serial Interface<br>S-791 SIO Module Description<br>Transmission Format Switch                                                                                                                                                                                                                 |                                                             |

|     | Serial Interface<br>Specifications<br>RS-232C Interface (Terminal)<br>RS-232C Interface (Host/Aux)<br>Current Loop Interface<br>TTL Interface (Terminal)<br>TTL Interface (Host/Aux)<br>Control Signal Timing                                                                                      | 4C-3<br>4C-4<br>4C-5<br>4C-7<br>4C-9<br>4C-10<br>4C-12      |

i

Page

Section

IV (cont.)

| D | - | ICD Program Memory<br>User Memory<br>Memory Mapping                                                                                                                                                                                            | 4D-1<br>4D-2<br>4D-3                                                    |

|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

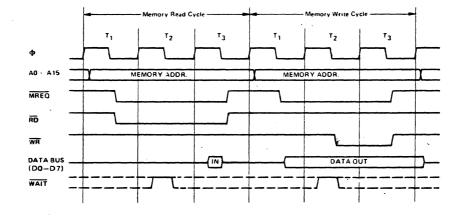

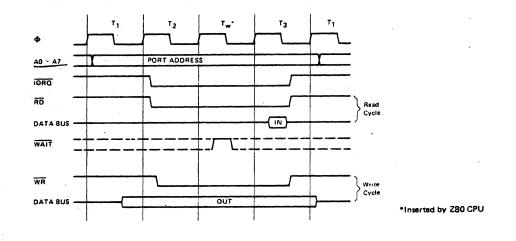

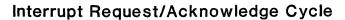

| E | - | CPU Emulation<br>ICD Program Memory Cycle<br>Z80 Machine Cycles<br>Clock Switch<br>Monitor Switch (Interrupt)<br>Bus Control<br>REFRESH Signal<br>Signal Timing                                                                                | 4E - 1 4E - 2 4E - 3 4E - 5 4E - 7 4E - 7 4E - 8 4E - 9 4E - 10 4E - 11 |

| F | - | Probes<br>Event Trigger Probe<br>Emulation Qualify<br>Output Probe<br>Map Control Probe                                                                                                                                                        | 4F-1<br>4F-2<br>4F-3                                                    |

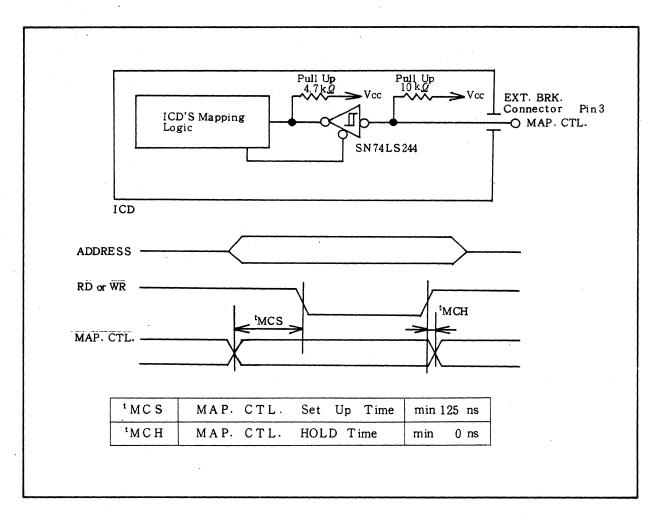

| G | - | Control Modules<br>Introduction and Description<br>S-730 Indicator Panel<br>S-791 Serial Interface Output<br>S-795 Realtime Trace Storage<br>S-793 Central Processing Unit<br>S-792 Emulation Memory Unit<br>ICD Disassembly/Module<br>Removal | 4G-1<br>4G-2<br>4G-3<br>4G-4<br>4G-5<br>4G-6<br>4G-7                    |

### PART II - SOFTWARE SPECIFICATION GUIDE

Section

Page

| -  | INTRODUCTION and DESCRIPTION<br>Introduction<br>Description                                                                                                        |                                           |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| V  | SOFTWARE COMMANDS<br>Introduction<br>ZICE Keywords<br>ZICE Format<br>Load Command<br>Save Command<br>Verify Command<br>Quit Command<br>Z Subcommands               | 5-2<br>5-3<br>5-5<br>5-6<br>5-7           |

|    | Z Log Subcommand<br>Z Batch Subcommand<br>Z Comment<br>Z Wait Subcommand<br>Directory Subcommand<br>Z Help Subcommand<br>Z Repeat Subcommand<br>Z Print Subcommand | 5-8<br>5-9<br>5-9<br>5-10<br>5-10<br>5-11 |

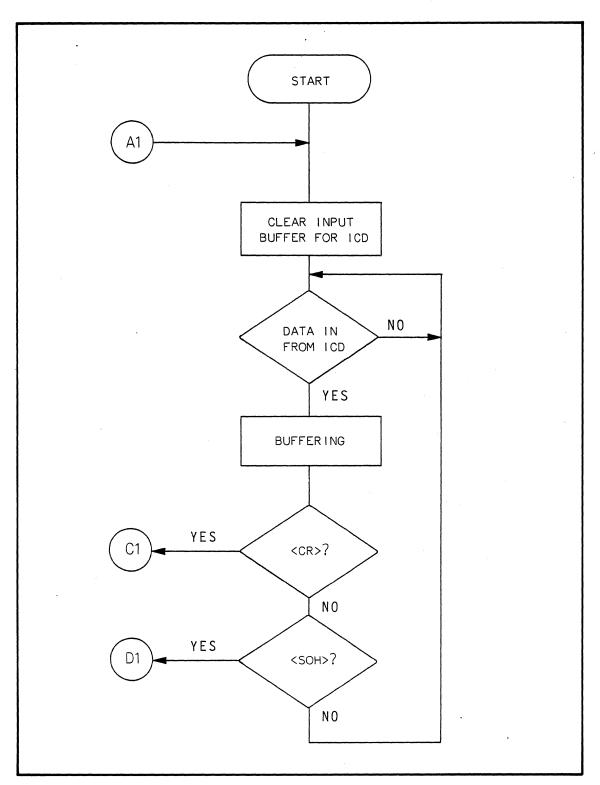

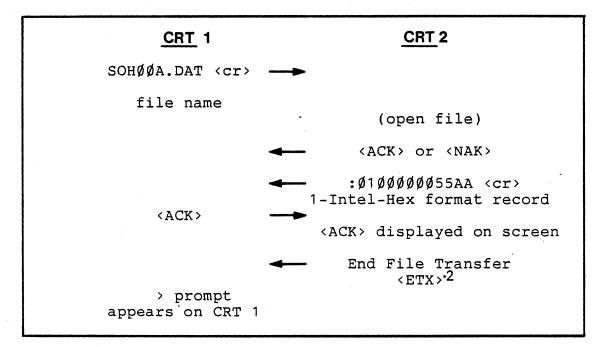

| VI | HOST COMPUTER SYSTEM COMMUNICATION<br>Introduction<br>Communication Terminology<br>System Configuration<br>Idle                                                    | 6-2<br>6-3                                |

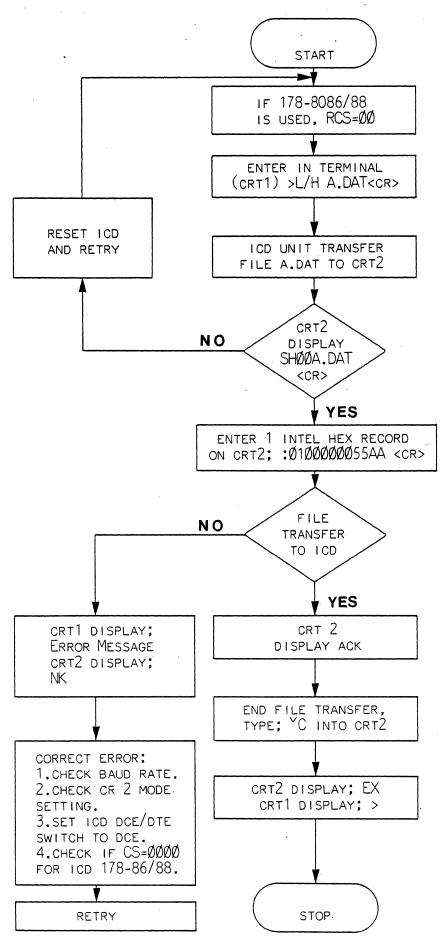

|    | Idle Program<br>Idle Program Flowchart                                                                                                                             | 6-4<br>6-5                                |

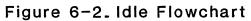

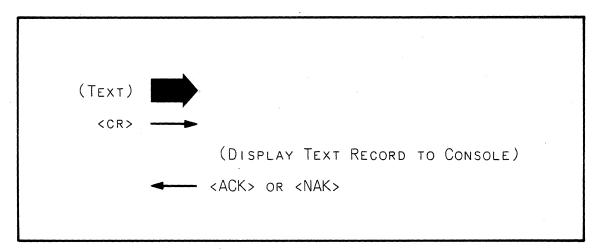

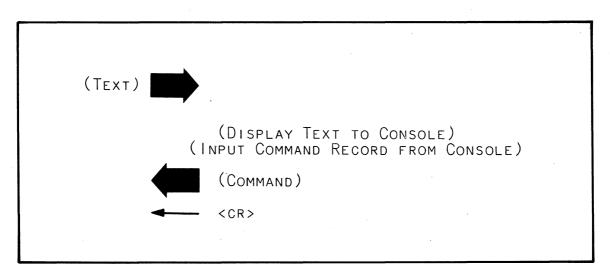

|    | Display Text<br>Display Text Sequence<br>Display Text Sequence Diagram<br>Display Text Program<br>Display Text Flowchart<br>Command Input Request Program          | 6-6<br>6-7                                |

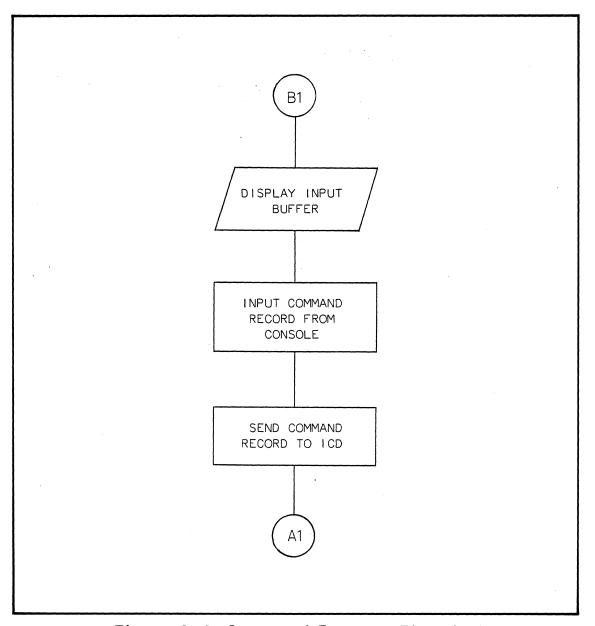

|    | Command Input Request Sequence<br>Command Input Request                                                                                                            | 6-8                                       |

|    | Sequence Diagram<br>Command Request Program<br>Command Request Flowchart<br>Object File Load/Verify                                                                |                                           |

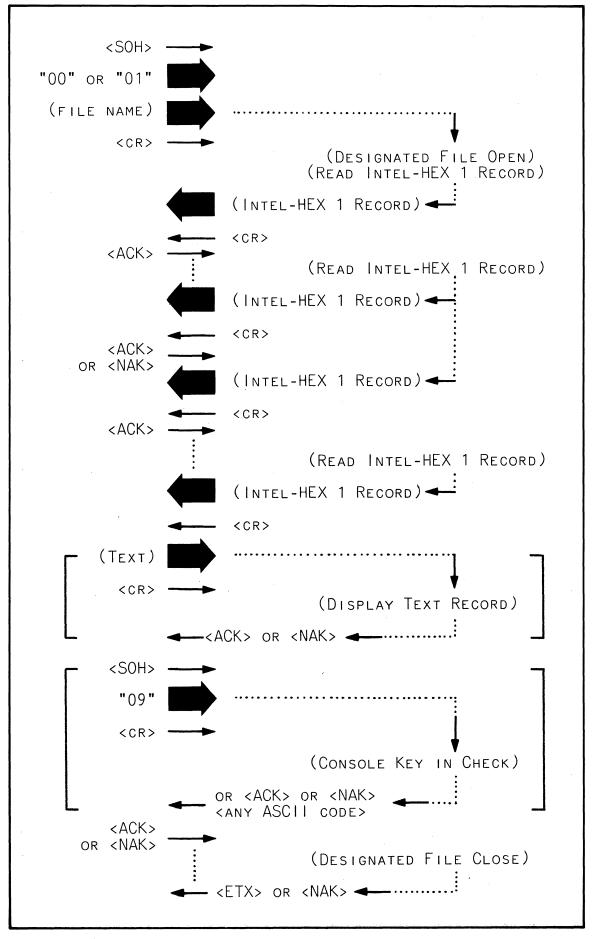

|    | Object File Load/Verify<br>Sequence                                                                                                                                | 6-10                                      |

|    | Object File Load/Verify<br>Sequence Cont<br>Object File Load/Verify                                                                                                | 6-11                                      |

|    | Sequence Diagram                                                                                                                                                   | 6-11                                      |

Section

VI (cont.)

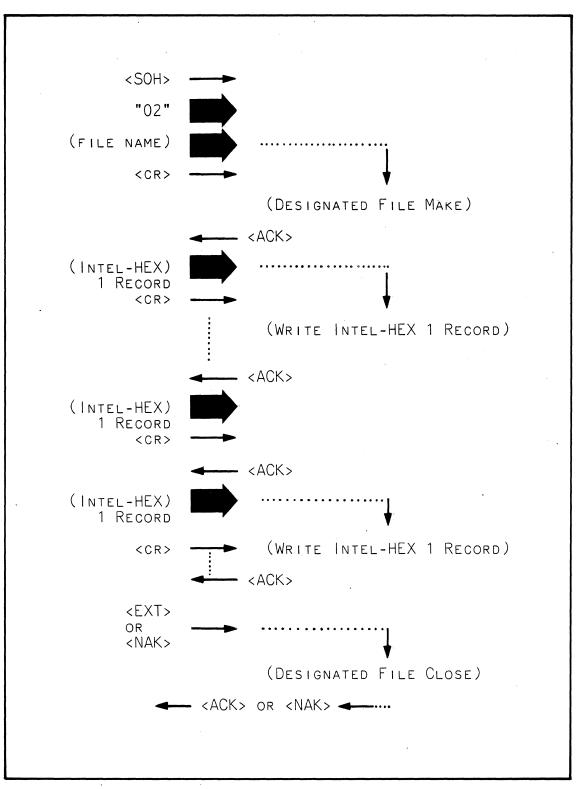

| Object File Save<br>Object File Save Sequence<br>Object File Save Sequence<br>Diagram                     |                              |

|-----------------------------------------------------------------------------------------------------------|------------------------------|

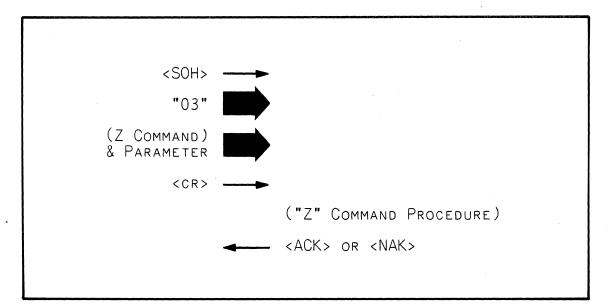

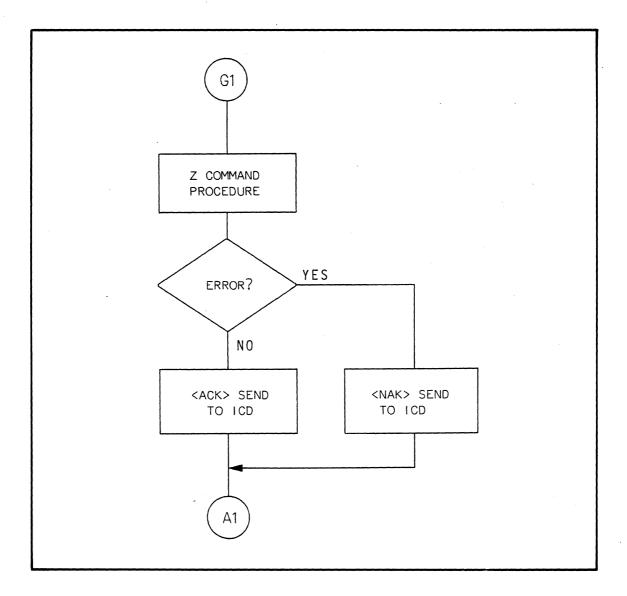

| Z Command<br>Z Command Sequence<br>Z Command Sequence Diagram<br>Z Command Program<br>Z Command Flowchart | 6-14<br>6-14<br>6-15<br>6-15 |

| Quit                                                                                                      |                              |

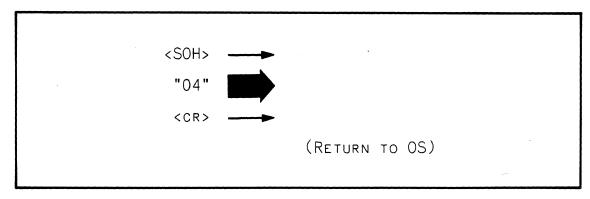

| Quit Sequence<br>Quit Sequence Diagram<br>Quit Program<br>Quit Flowchart<br>Display Symbolic Text         | 6-17<br>6-17<br>6-17<br>6-17 |

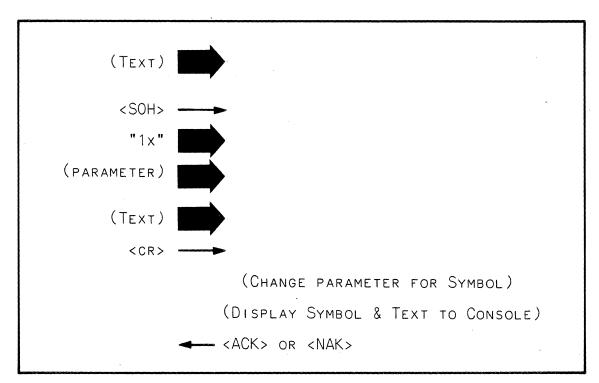

| Display Symbolic Text Sequence<br>Display Symbolic Text                                                   | 6-18                         |

| Sequence Diagram                                                                                          | 6-18                         |

| Display Symbolic Text Program                                                                             |                              |

| Display Symbolic Text Flowchart<br>Console Key Check                                                      | 6-19                         |

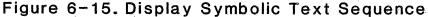

| Console Key Check Sequence<br>Console Key Check                                                           | 6-20                         |

| Sequence Diagram                                                                                          | 6-20                         |

Page

## LIST OF ILLUSTRATIONS

| Figure                                                      | Title                                                                                                                                                                                                       | Page.                                                 |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 2 - 1<br>2 - 2<br>2 - 3<br>2 - 4<br>2 - 5<br>2 - 6          | ICD Controls and Components<br>ICD Controls and Components, cont<br>ICD Controls and Components, cont<br>CPU Plug Probe<br>External Break Cable Diagram<br>Event Trigger Cable Diagram                      | 2-2<br>2-4<br>2-6                                     |

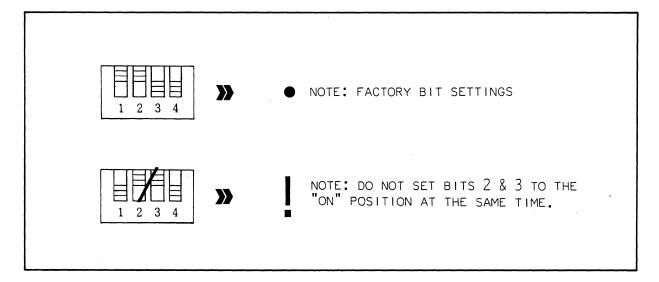

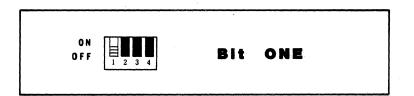

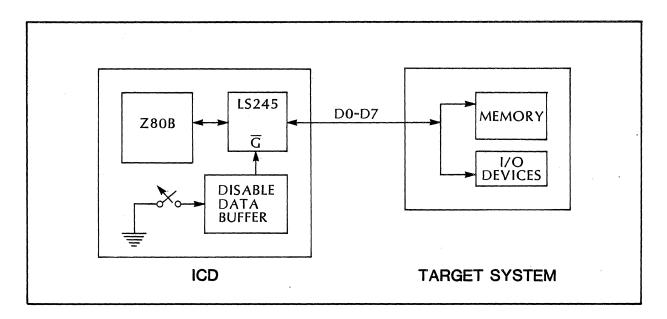

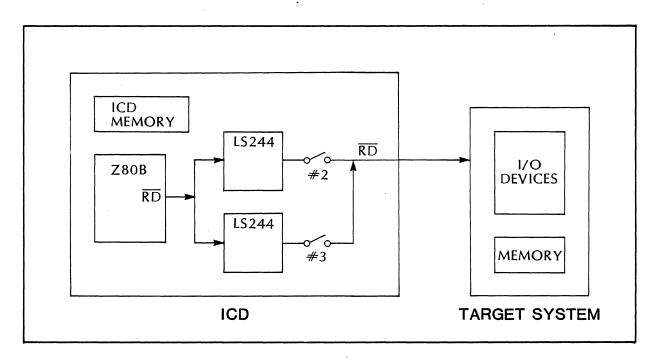

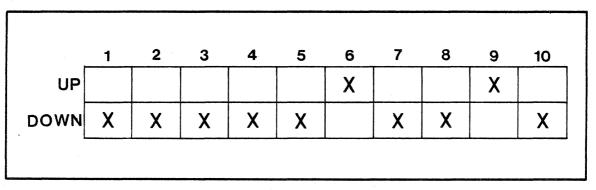

| 4-A.1<br>4-A.2<br>4-A.3<br>4-A.4<br>4-A.5<br>4-B.1          | Emulation Select Switch<br>E. S. Switch Factory Settings<br>Emulation Data Bus Block Diagram<br>Emulator READ Signal Block Diagram<br>Wait States<br>DB. EMUL (Data Bus Emulation)                          | 4A - 1<br>4A - 1<br>4A - 2<br>4A - 3<br>4A - 4        |

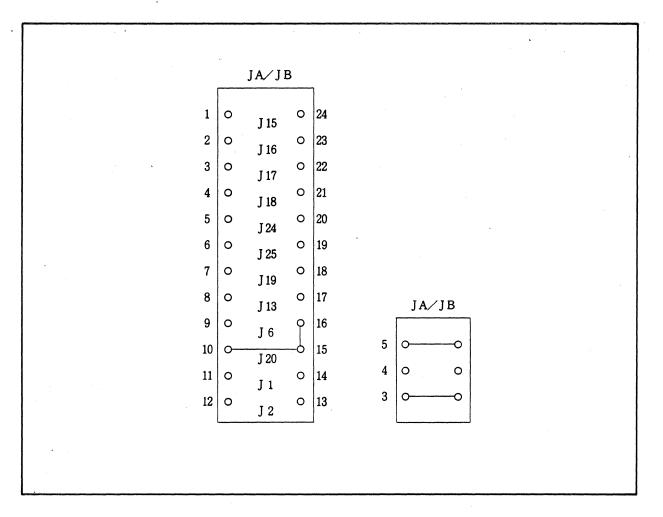

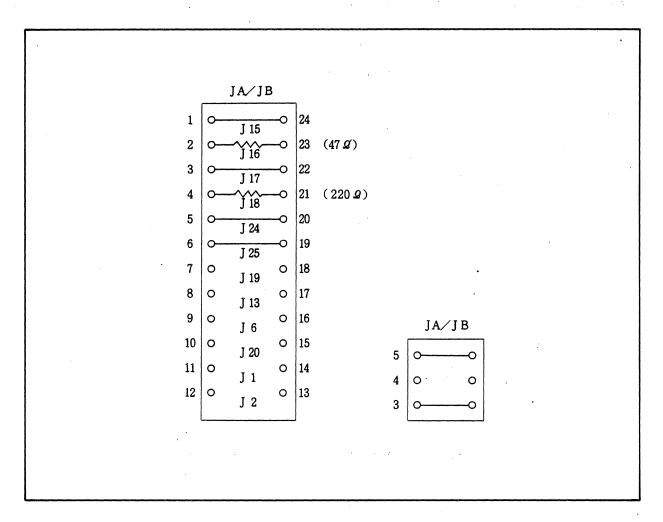

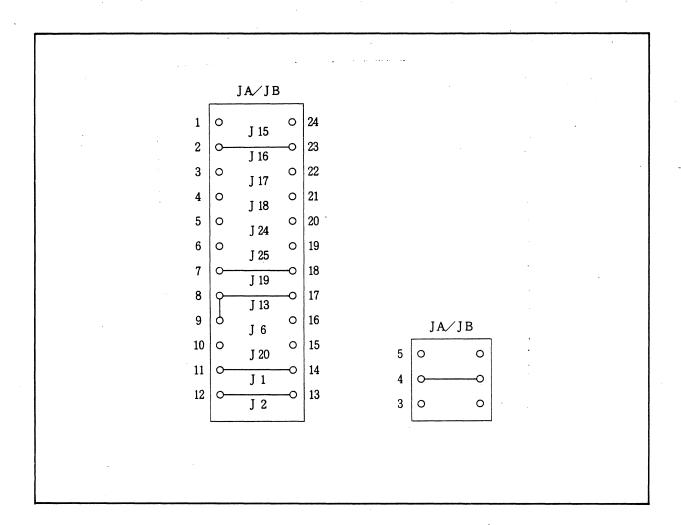

| 4-B.2<br>4-C.1<br>4-C.2<br>4-C.3<br>4-C.4                   | Connector<br>DB. EMUL Connector Configuration<br>S-791 SIO Module<br>Transmission Format Switch<br>RS-232C Standard Jumper Settings<br>CLI Standard Jumper Settings                                         | 4B-1<br>4B-2<br>4C-1<br>4C-2<br>4C-6<br>4C-8          |

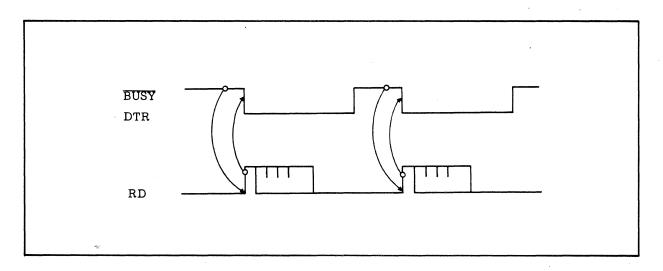

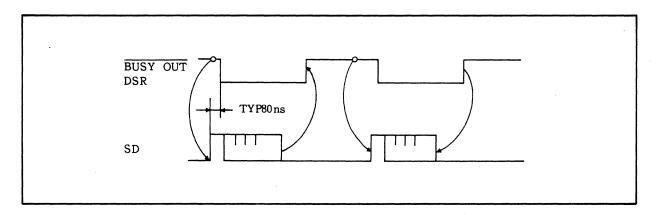

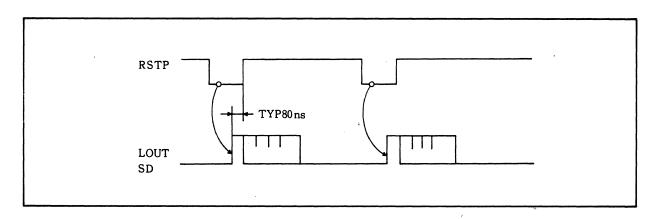

| 4-C.5<br>4-C.6<br>4-C.7<br>4-C.8                            | TTL Standard Jumper Settings<br>BUSY and DTR Input Signal Diagram<br>BUSYOUT and DSR Output Signal<br>Diagram<br>RSTP Output Signal Diagram                                                                 | 4C-11<br>4C-12<br>4C-13<br>4C-13                      |

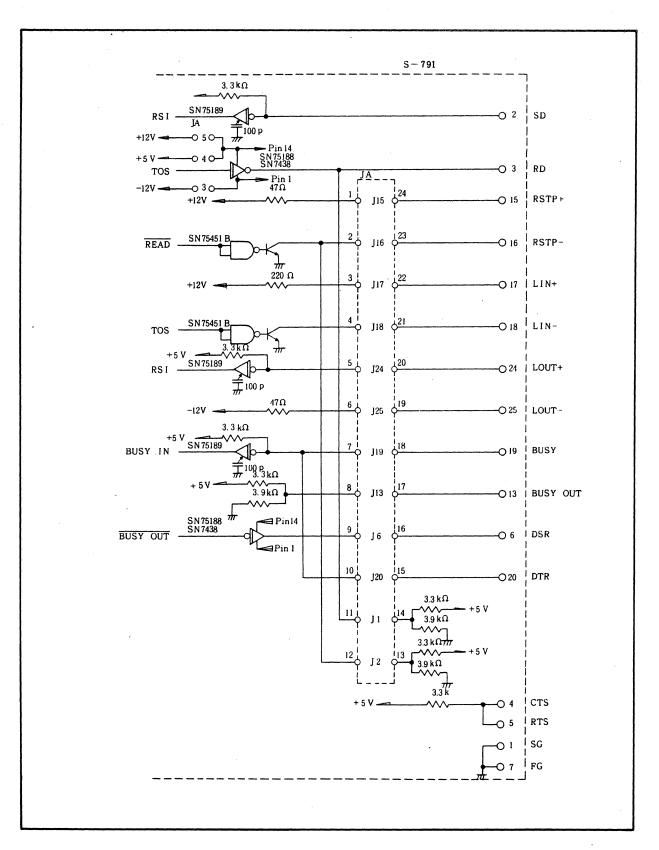

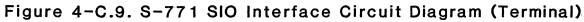

| 4-C.9<br>4-C-10                                             | S-771 SIO Interface Circuit<br>Diagram (Terminal)<br>Diagram (Host/Aux)                                                                                                                                     | 4C-14                                                 |

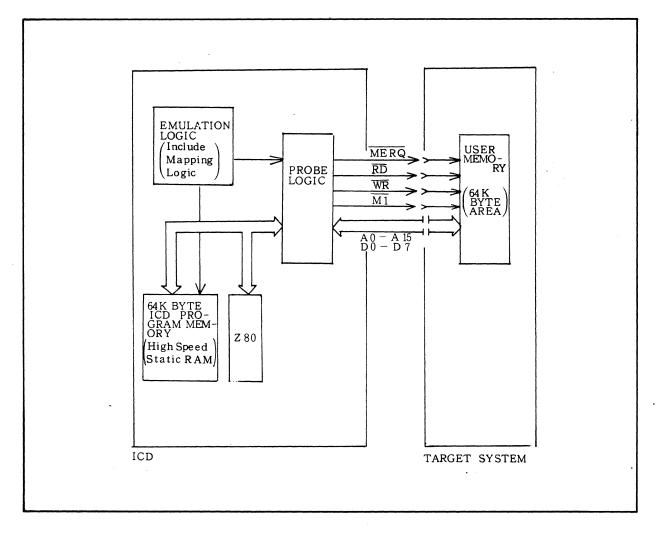

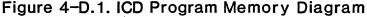

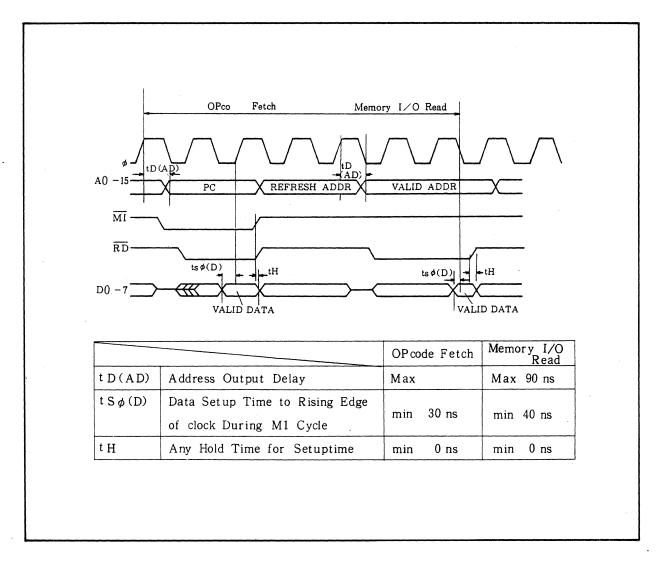

| 4-D.1<br>4-D.2<br>4-D.3                                     | ICD Program Memory Diagram<br>User Memory Timing Diagram<br>Mapping Configuration                                                                                                                           | 4D-1<br>4D-2<br>4D-3                                  |

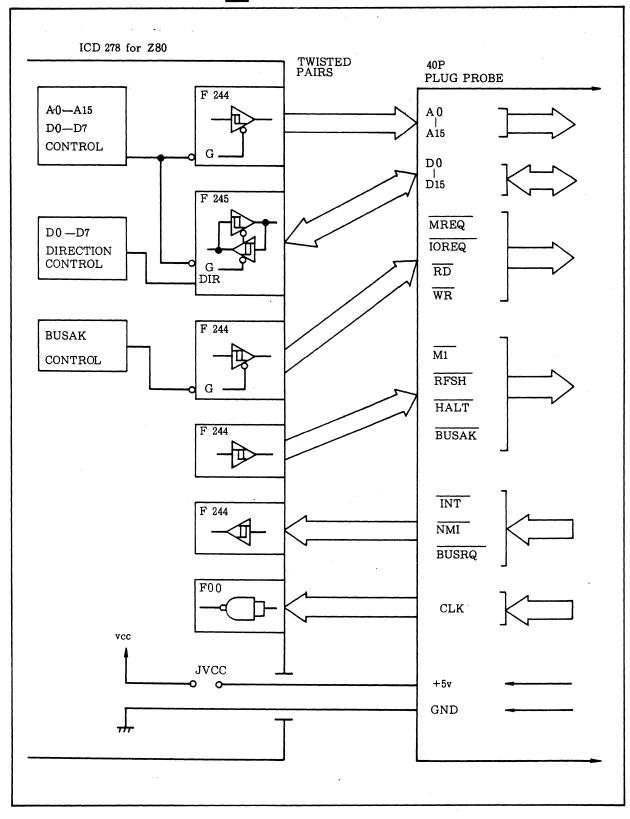

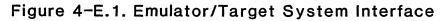

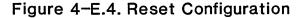

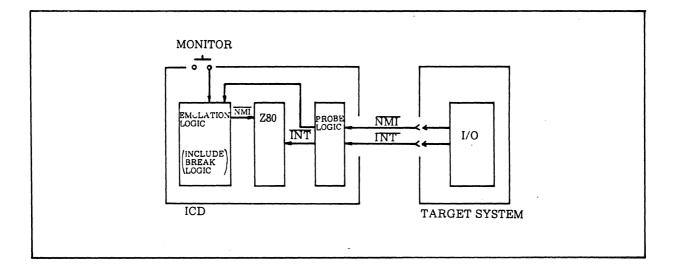

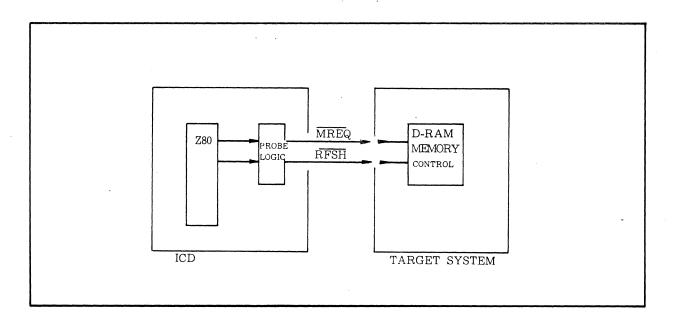

| 4-E.1<br>4-E.2<br>4-E.3<br>4-E.4<br>4-E.5<br>4-E.6<br>4-E.7 | Emulator/Target System Interface<br>Clock Configuration<br>Setting of Internal Clock<br>Reset Configuration<br>Interrupt Signal Configuration<br>BUSRQ Signal Configuration<br>REFRESH Signal Configuration | 4E-1<br>4E-5<br>4E-6<br>4E-7<br>4E-8<br>4E-9<br>4E-10 |

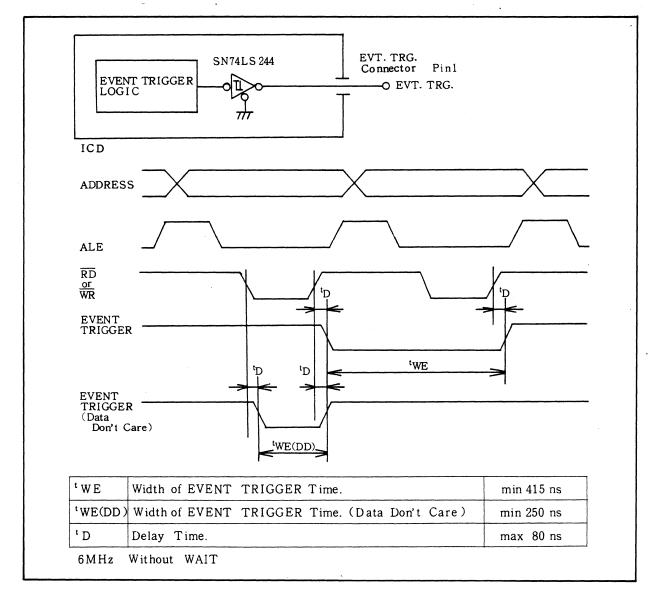

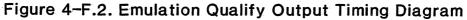

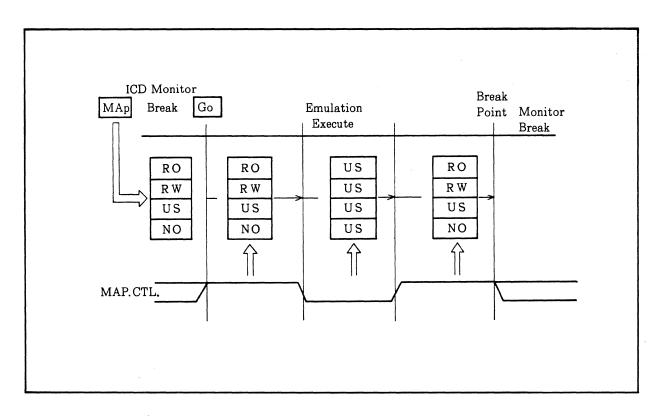

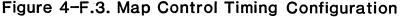

| 4-F.1<br>4-F.2<br>4-F.3                                     | Event Trigger Output Timing Diagram<br>Emulation Qualify Output Timing<br>Diagram<br>Map Control Timing Configuration                                                                                       | 4F-1<br>4F-2<br>4F-3                                  |

|                                                             |                                                                                                                                                                                                             |                                                       |

Figure

### Title

| <ul> <li>6-5 Command Input Request<br/>Sequence Diagram</li></ul>      |

|------------------------------------------------------------------------|

| 6-6 Command Input Request Flowchart 6-9<br>6-7 Object File Load/Verify |

| 6-7 Object File Load/Verity                                            |

|                                                                        |

| Sequence Diagram                                                       |

| 6-9 Object File Save Sequence Diagram 6-13                             |

| 6-11 Z Command Sequence Diagram                                        |

| 6-12 Z Command Flowchart                                               |

| 6-13 Quit Sequence Diagram 6-17                                        |

| 6-14 Quit Flowchart                                                    |

| 6-15 Display Symbolic Text                                             |

| Sequence Diagram                                                       |

| 6-16 Display Symbolic Text Flowchart 6-19                              |

| 6-17 Console Key Check Sequence Diagram 6-20                           |

## LIST OF TABLES

| Table             | Title                                                                 | Page                                  |

|-------------------|-----------------------------------------------------------------------|---------------------------------------|

| 2-1<br>2-2<br>2-3 | ICD Baud Rates<br>External Break Connector<br>Event Trigger Connector | 2-5                                   |

| 3-1<br>3-2        | System Configuration<br>Start-Up Sequence                             |                                       |

| 4-C.1             | RS232C Interface Pin Designation<br>(Terminal)                        | 4C-4                                  |

| 4-C.2             | RS232C Interface Pin Designation<br>(Host/Aux)                        |                                       |

| 4-C.3             | Current Loop Interface Pin<br>Designation (Term/Host/Aux)             | · · · · · · · · · · · · · · · · · · · |

| 4-C.4             | TTL Interface Pin Designation<br>(Terminal)                           |                                       |

| 4-C.5             | TTL Interface Pin Designation<br>(Host/Aux)                           |                                       |

| 4-C.1             | Emulator Bus Connector -<br>Pin Assignment                            |                                       |

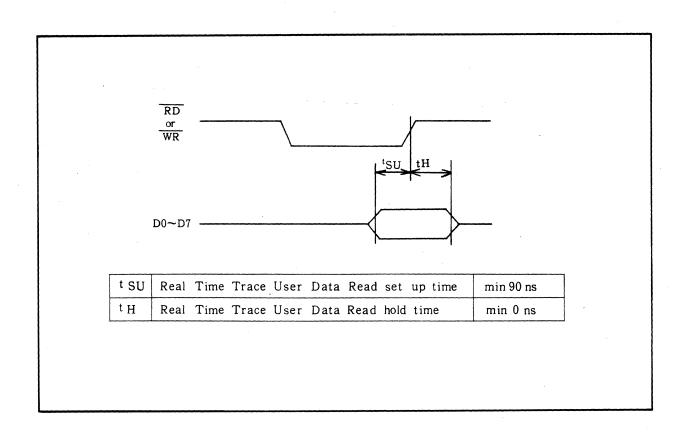

| 4-E.1             | ICD-278 Signal Timing Diagram                                         |                                       |

## SECTION I

#### INTRODUCTION and DESCRIPTION

#### INTRODUCTION

This Operation Manual contains information concerning the ZAX ICD-278 for Z80 IN-CIRCUIT EMULATOR. Revision and update information is contained in supplements issued periodically to Operation Manual recipients.

Part I of this manual acts as a USER'S GUIDE and describes the ICD-278, including controls, system configuration, and start-up sequence. A system command guide with general examples is included in Part I. This guide illustrates and explains the basic command syntax parameters and functions of the ICD commands. A complete listing of Technical References may also be found in Part I. ICD communication with a Host Computer system is contained in Part II; SOFTWARE SPECIFICATION GUIDE, and describes the proper connection, communication protocol and program construction.

Always refer to the specific information you are concerned with, as general knowledge of certain operations and procedures may not prove fully satisfactory in obtaining the desired results; moreover, the design engineer is highly encouraged to become familiar with the entire contents of this manual in order to thoroughly realize the ICD-278's capabilities.

#### DESCRIPTION

The ZAX ICD-278 IN-CIRCUIT EMULATOR functions as a standalone device for developing and maintaining hardware and software of Z80B microprocessors. The ICD-278 comes standard with 64K Bytes of static memory for mapping, displays in HEX/ASCII or disassembled Intel code with a 2K by 40 real time trace buffer and 29 major software commands.

For field applications, the ICD-278 can be connected to any communications device that has either RS232C or 20 mA current loop input.

## ICD Major Components

#### SPECIFICATIONS (General)

Dimensions

Probe Length

Weight

Power Requirements

Operating Temperature Storage Temperature Humidity

Processors

Memory Size

Memory Mapping

Real Time Trace Buffer

System Commands

Usable I/O Ports

Breakpoints

Communication Ports

Baud Rates

Operating Temperature Storage Temperature Humidity :300mm (11.8in) wide :210mm (8.2in) deep : 80mm (3.2in) high

:510mm (20in) long

:3.3kg (7.31b)

:115VAC/230VAC;50/60Hz

:0°C to 45°C :-10°C to 55°C :30% to 85%, relative (non-condensing)

:Z80 (to 6MHz) :i8085 (6MHz)

:64K-Bytes static RAM

:Full 64K byte

:2K x 32 bits

:29

:256

- :3(hardware), 8(software)

1(external probe)

- :2 RS232C/20ma current loop/TT1

- :14 usable to 19,200bps (factory set at 9,600bps)

:0°C to 45°C :-10°C to 55°C :30% to 85%

#### SPECIFICATIONS (Emulation)

#### Applied CPU

| z80  | : | 500K, | 2 | • 5 | MHz |

|------|---|-------|---|-----|-----|

| Z80A | : | 500K, | 4 | MB  | Ηz  |

| Z80B | : | 500K, | 6 | MB  | Ηz  |

Memory Area

- Program memory :The entire area of the program memory (64K-bytes) is open. This memory is composed of high-speed static RAM.

- User memory :The entire area of 64K-byte memory space is open to the target system.

Mapping :Both the program and user memory can be mapped in 1K-byte units. Four types of mapping modes are available;

:All 256 ports are open.

User Memory Emulation Read/Write Memory Emulation Read Only Memory Non Memory

I/O Port

Breakpoints

:3 Hardware, 8 Software and External trigger break.

Hardware Break : specification :

A,B,C Breaks

:A,B,C and Event trigger

:Specify enable/disable of A,B,C and Event breakpoints.

:Address 16 bits, BHE. Each bit may be

specified 0,1 or "don't care."

| Status: | OP code fetch<br>Memory access<br>Memory read<br>Memory write<br>I/O access<br>I/O read<br>I/O write<br>Execution of instruction |

|---------|----------------------------------------------------------------------------------------------------------------------------------|

| Arm:    | Break occurs only at the                                                                                                         |

m: Break occurs only at the breakpoint after an event trigger is generated.

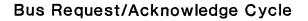

Event Trigger :Address 16 bits, BHE. Each bit may be break specified 0,1 or "don't care." Status: OP code fetch Memory access Memory write Memory read I/O access I/O read I/O write Instruction execution Data: 8 bits. Each bit may be specified 0,1 or "don't care." External Trigger break :Breakpoint; 1 channel - TTL level Functional specification; HIGH edge or LOW edge. Software Break :8 points; 0 - 7 User breakpoint :Any point may be specified by using the LDA, A instruction. Specification :Specify enable/disable of all software points. Function :A break is caused in the target system when the CPU reads 7FH as an OP code (which represents a LDA, A instruction). Its execution does not effect the registers or flags. Software breaks are suppressed when disabled. Realtime trace :The addresses, data and status during emulation may be stored in storage memory in realtime. Trace capacity :2K x 32 bits Fixed trace data :A0-15, D0-7, MREQ; IORQ, RD; WR, MI Trigger function :End monitor Begin monitor End event Begin event Center event Multiple event Realtime counter : Count bit width; 32 bit Count time; 716 sec, 6 MHz .

## **SECTION II**

#### **CONTROLS and COMPONENTS**

#### INTRODUCTION

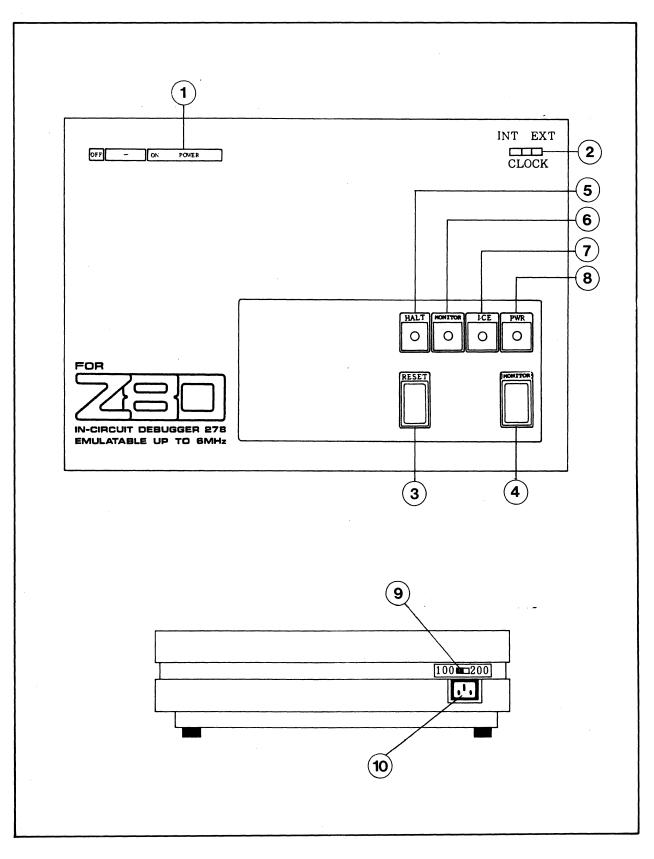

This section introduces the various controls, components and functions of the ICD-278. The system controls are represented by four different views of the unit. The user may also wish to examine the photographs of the ICD-278 found at the beginning of Section I.

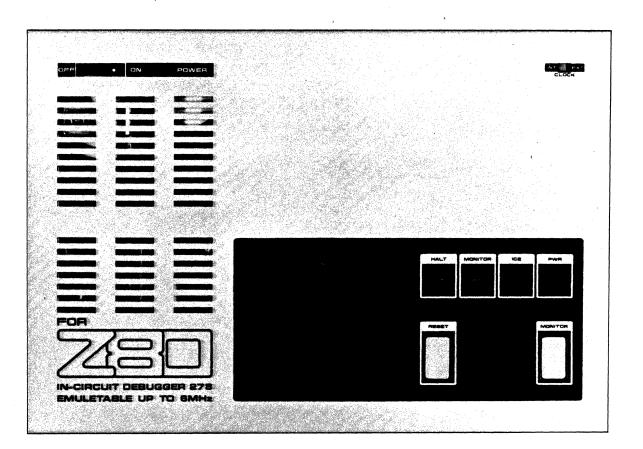

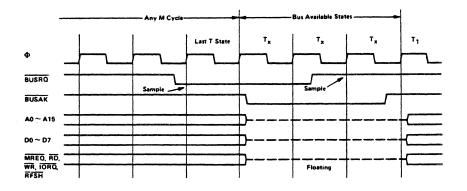

2 CLOCK select switch. This switch is used to select between the external target (EXT) and the internal clock (INT).

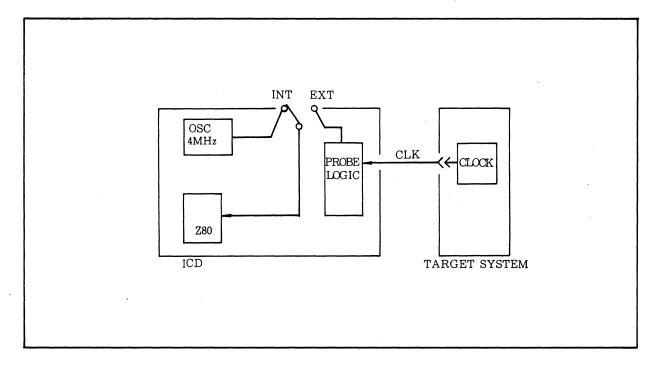

3 RESET switch. This momentary switch is used to reset the ICD-278 monitor. It is activated when the MONITOR lamp is on.

4 MONITOR break switch. This momentary switch is used to return control to the ICD monitor during emulation.

5 HALT lamp. This LED comes on when the ICD CPU has stopped after executing a HALT instruction or when BUSY ACKNOWLEDGE (BUSAK) is in progress.

6 MONITOR lamp. This LED comes on to indicate that control is currently in the ICD monitor. It is off during emulation.

7 ICE (In-circuit Enable) lamp. This LED comes on when the ICD is operating in the incircuit mode (I1 or I2) with the target system.

8 POWER lamp. This LED comes on when the ICD is on.

9 POWER select switch. This switch is used to select the proper power requirements for the ICD. Set the switch to 110/117V to run on a power supply of 110-120VAC or select 200/240V to run on a power supply of 200-240VAC. Set this switch BEFORE connecting the power plug.

10 Power connector. This connector is for the AC power plug.

Figure 2-1. ICD Controls and Components

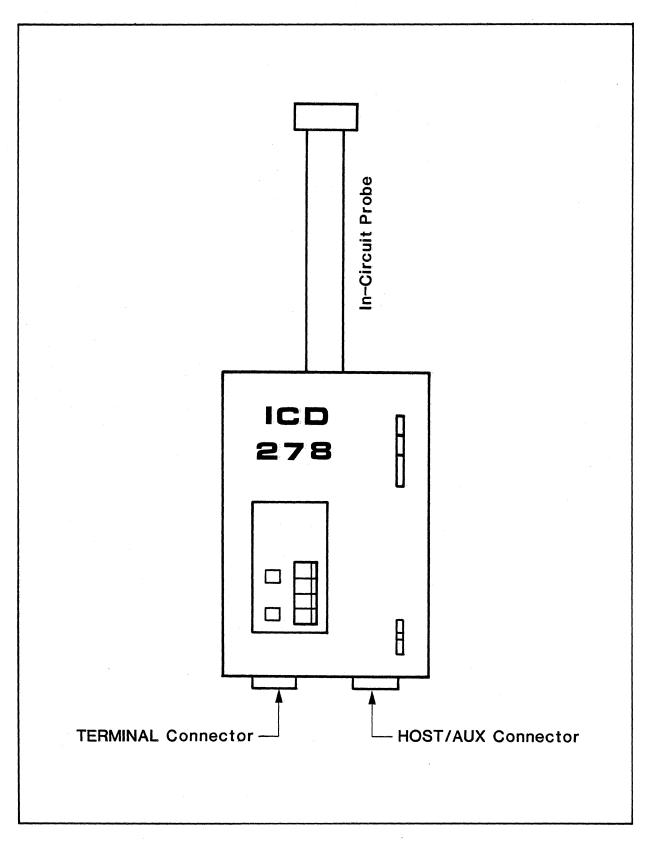

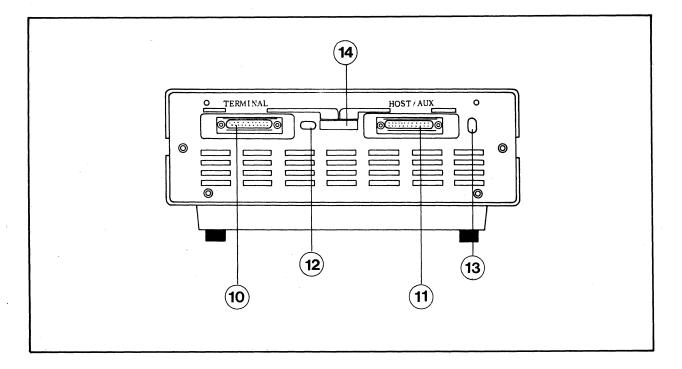

10 TERMINAL port connector. This connector attaches a console to the ICD-278. In a standalone configuration (LOCAL), it is used to input or output ICD operator commands. In REMOTE mode it is used for an auxiliary I/O.

HOST/AUX (Host/Auxiliary) port connector. This connector is used to connect a Host Computer system or auxiliary I/O to the ICD-278. In a standalone configuration (LOCAL), objects, registers or memory dumps interface to a host computer, printer, teletypewriter, etc., thru this port. In REMOTE mode it can be used to input or output ICD operator commands under control of the host computer.

12 LOCAL/REM (Local/Remote) select switch. This switch is used to select the ports through which the ICD operator commands are entered.

13 DCE/DTE select switch. This switch is used to set the HOST/AUX port to RS232C data terminal equipment(DTE) or data circuit-terminating equipment(DCE). Factory setting is DTE.

14 BAUDRATE set switch. This switch is used to set the baud rates for the TERMINAL and the HOST/AUX port (Table 2-1). To set the baud rate, turn dial using flat-head screwdriver or equivalent.

NOTE: There are 14 usable baud rates available. Baud rate switch numbers E and F are not recommended.

Factory setting = 1(9600bps) for TERMINAL and HOST/AUX ports.

| TERMINAL                    | HOST/AUX       |  |

|-----------------------------|----------------|--|

|                             |                |  |

| BAUD RATE SET<br>SWITCH NO. | BAUD RATE(BPS) |  |

| 0                           | 19, 200        |  |

| 1                           | 9, 600         |  |

| 2                           | 4, 800         |  |

| 3                           | 2, 400         |  |

| 4                           | 1, 200         |  |

| 5                           | 600            |  |

| 6                           | 300            |  |

| . 7                         | 150            |  |

| 8                           | 75             |  |

| 9                           | 110            |  |

| Α                           | 134. 5         |  |

| В                           | 200            |  |

| С                           | 1, 800         |  |

| D                           | 2, 000         |  |

| E                           |                |  |

| F                           |                |  |

|                             |                |  |

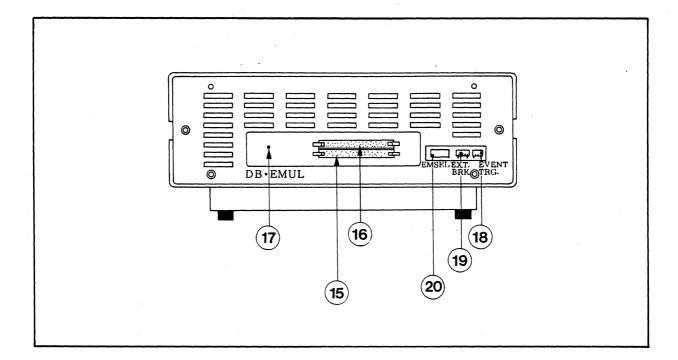

15 CPA In-circuit probe plug connector.

16 CPB In-circuit probe plug connector.

NOTE: It is not necessary to connect the in-circuit when running the ICD in the IO mode (in-circuit mode 0) only.

CAUTION: DO NOT REVERSE PLUG PROBE CONNECTIONS. CPA/CPB MISMATCH WILL CAUSE DAMAGE TO THE ICD-278.

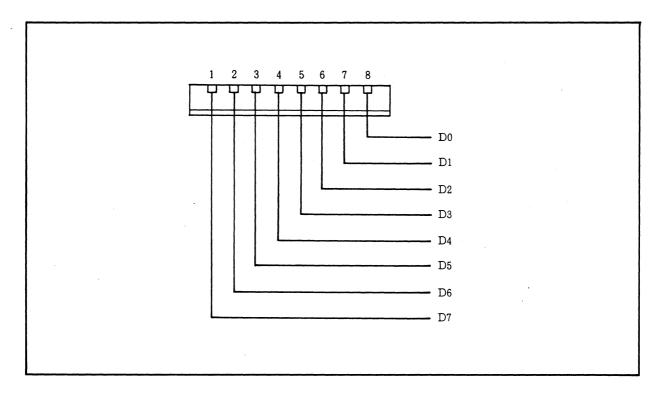

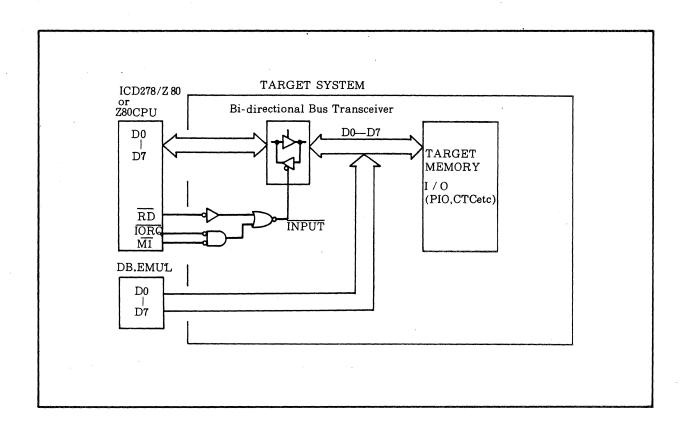

17 DB. EMUL (Data Bus Emulator) connector. This connects directly to the data bus of a target system (in-circuit) when decoding the 'RET I' instruction (See Technical References).

BEXT. BRK. (External Break) connector. This is used to connect an external break cable to the ICD (Table 2-2).

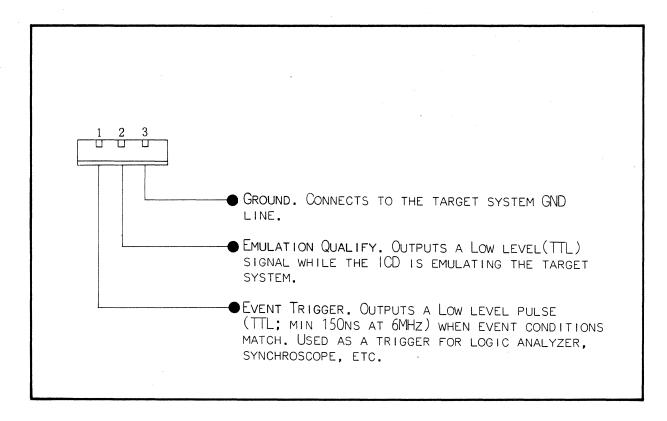

(Event Trigger) connector. This is used to 19 EVENT TRG. connect an event trigger cable to the ICD (Table 2-3).

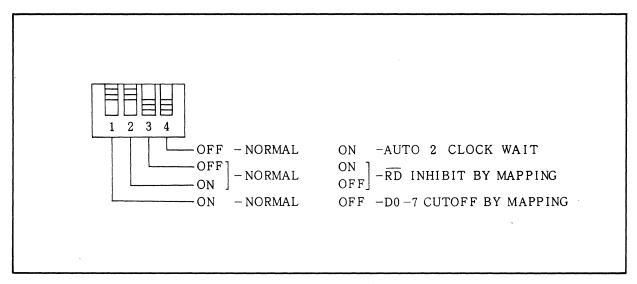

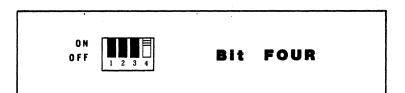

**20**E.M.SEL (Emulation Select) switch. This switch is used to set the machine cycle operation of the target system (See Technical References).

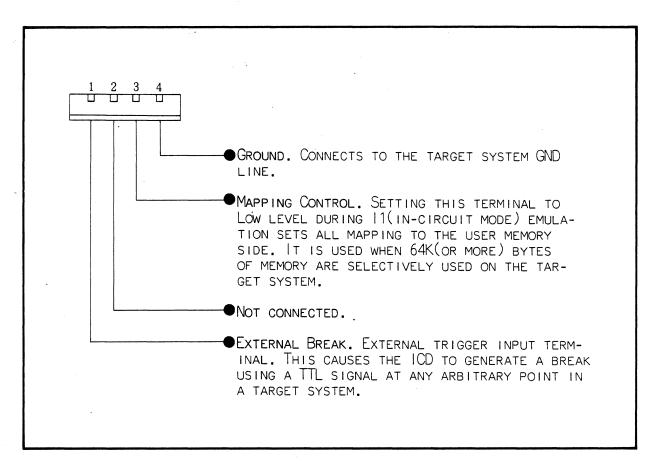

Table 2-2. External Break Connector Diagram

Table 2-3. Event Trigger Connector Diagram

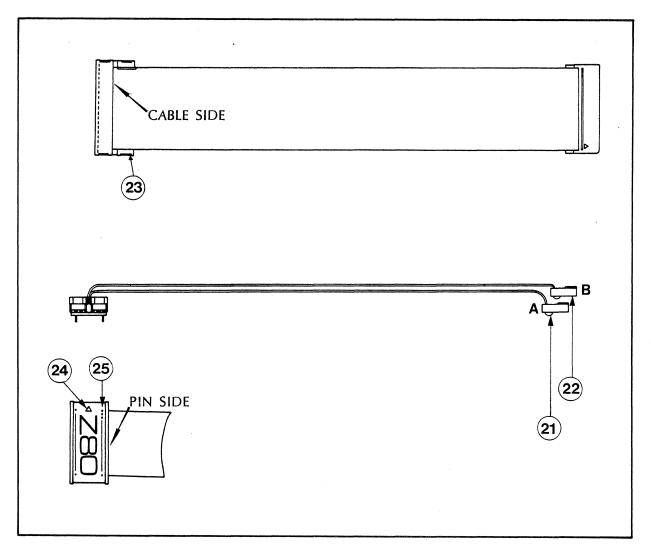

CSA/CSB In-circuit Probe Socket Connector (Figure 2-4) Connects CPA to CSA and CPB to CSB.

21 CSA In-circuit Socket A.

22 CSB In-circuit Socket B.

23 Pin #1 Plugs into CPU socket. Note proper polarity.

24 Polarity mark.

25 Pin #1.

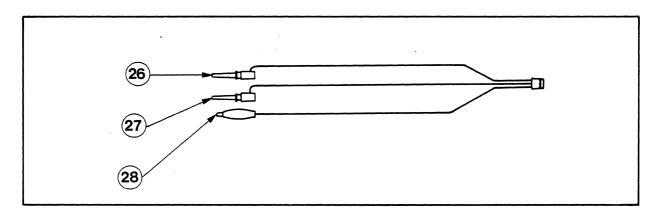

External Break Cable (Figure 2-5). Connects to the EXT. BRK. socket of the unit.

26 External Break Probe (red).

27 Map Control Probe (yellow).

28 Ground clip (black).

#### Figure 2-5. External Break Cable

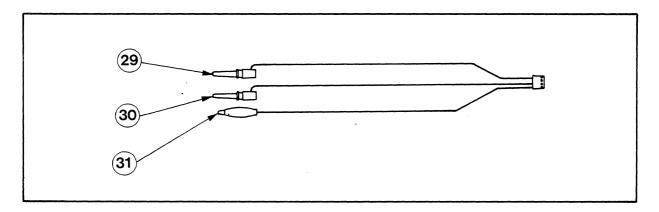

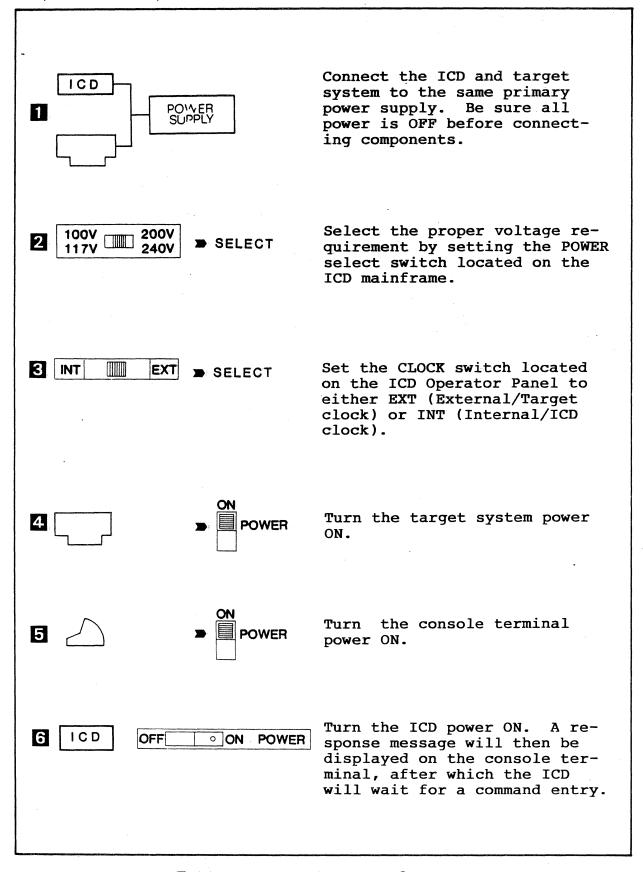

Event Trigger Cable (Figure 2-6). Connects to the Event TRG. socket of the unit.

29 Event Trigger Probe (green).

**30** Emulation Qualifier Probe (white).

**31** Ground clip (black).

## SECTION III

#### SYSTEM CONFIGURATION / START-UP / COMMAND GUIDE

This section introduces the user to the various ICD system configurations, including communication with host computer systems. Refer to this section when interfacing the ICD-278 to other devices. This sections also shows the correct startup procedure for the ICD-278.

Additionally, a complete listing of emulator commands and examples are included in this section. Before using the emulator, first construct the the proper system configuration for the ICD-278 and then execute the start-up sequence.

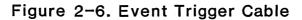

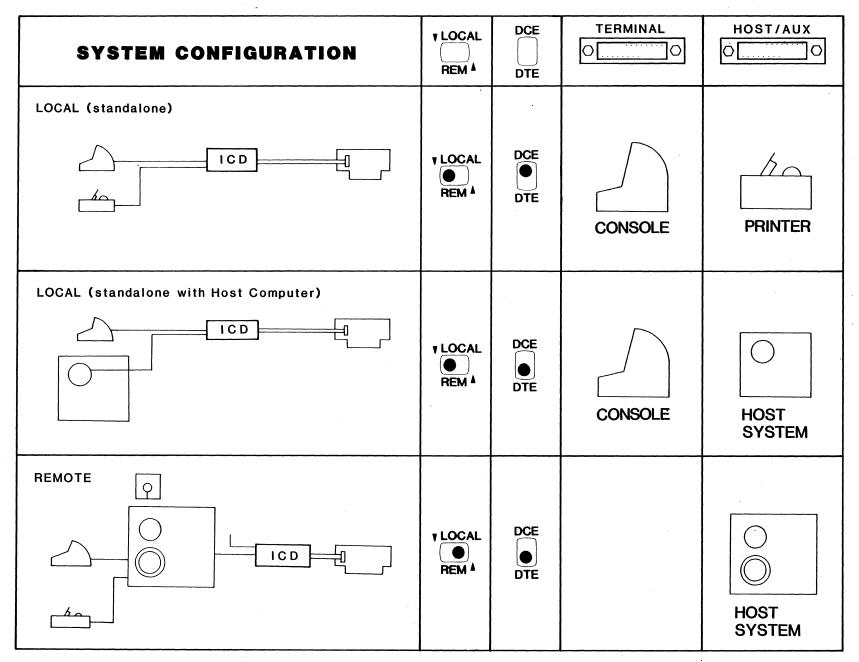

The ICD-278 may be set up to run in one of three different system configurations:

1) LOCAL Basis (standalone configuration)

In this mode the ICD-278 is connected to a console terminal thru which commands may be entered. The Host/ Aux port may be used to connect a printer, teletypewriter. Etc. Hardcopy operations may then be produced by issuing a "Print" command.

2) LOCAL Basis (standalone with host computer)

In this mode the ICD-278 performs object file input/ output with a host computer. ICD operator commands may be entered from the console terminal. The "User" command enables direct communication between the ICD console terminal and the host computer.

3) REMOTE Basis

In this mode input/output from the host computer is performed by the utility software program; ZICE. The ICD-278 may be furnished with the ZICE command for batch processing and other applications (see Part II, Software Specification Guide).

The three system configurations are illustrated by symbolic notation (Table 3-1). The start-up sequence is then performed (Table 3-2) after constructing the proper system configuration. The ICD-278 is initialized when its mainframe is first powered up or when the RESET switch is pressed after powering up.

Table 3-1. System Configuration

System Configuration Description

Use Table 3-1 to establish the correct system configuration for the LOCAL or REMOTE modes. Before constructing the system make sure that the power to each component is OFF.

First set the LOCAL/REM and DCE/DTE switches to the positions specified in the configuration diagram.

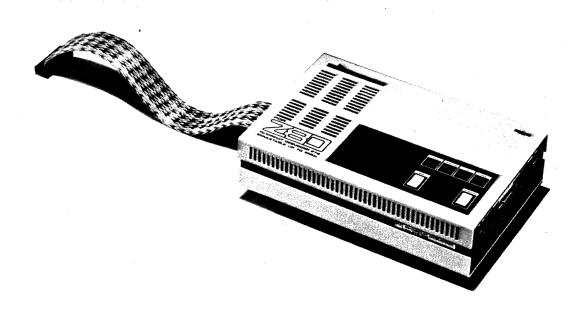

The ICD-278 uses three cables to connect it to various communication devices and the target system. The two blue-colored ribbon cables are used to connect the ICD to; 1) a console terminal through the TERMINAL port connector, and 2) an auxiliary printer or a host computer (Figure 2-2). Connect these cables to the device selected and then to the ICD HOST/AUX or TERMINAL port male sockets.

The CPU Plug Probe cable (Figure 2-4) connects the ICD to the target processor socket. Remove the existing CPU (Z80) from the target system and insert the plug probe (Z80 40-pin end) into the adaptor socket and then carefully insert the assembly into the target system CPU socket. Do not bend the pins.

NOTE: Do not place the cables close to the power supply or interference will result.

Next connect the CSA/CSB Incircuit sockets to the ICD CPA/ CPB connectors (Figure 2-3 and 2-4). The cable with the longest length (CSB socket B) MUST be connected to the UPPER (CPB) Incircuit plug probe connector on the ICD.

NOTE: THE CABLE WITH THE LONGEST LENGTH (CSB) MUST BE CON-NECTED TO THE UPPER INCIRCUIT PLUG PROBE CONNECTOR (CPB).

CAUTION: DO NOT REVERSE PLUG PROBE CONNECTIONS. MISMATCH OF CSA/CSB AND CPA/CPB WILL CAUSE SEVERE DAMAGE TO THE ICD-278.

Once the system is constructed, refer to the ICD start-up sequence illustrated in Table 3-2.

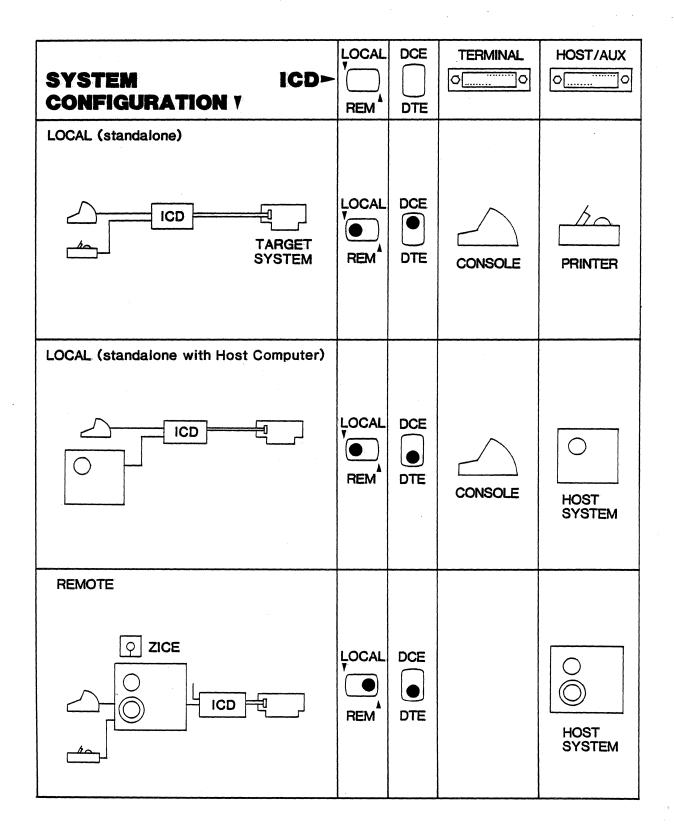

#### Table 3-2. ICD Start-up Sequence

#### COMMAND GUIDE

The information contained in this COMMAND GUIDE relates to the ZAX ICD-278 for Z80 series emulators.

This Command Guide contains two parts. Part one acts as a reference guide and details the format and parameters of each command. Part two is a quick-reference guide that omits the parameter explanations for the experienced operator.

The ICD-278 for Z80 is capable of executing 29 major software commands. A portion of these commands are divided into various sub-groups for a total of 61 different command formats.

\*Example of command format structure: History format display - displays in disassembled or machine cycle format; B M D , int.point , term.point (cr) <sup>M</sup> 4 :display in machine cycle format. D **Z**:display with assembled codes. int.point :display or search initiation storage 5 pointer [decimal 1 to 2047] term.point :display or search termination storage pointer [decimal 1 (default to 2047]

Where -

1 - Command name.

- 2 Command description.

- 3 Command format including available parameters.

- 4 User supplied keywords, showing input choices.

- 5 User supplied address/data keywords.

- 6 Address/data parameters.

- 7 Keyword/address/data explanations.

Z80 Command Reference Guide -Commands: 61

#### Assemble

Break status Hardware Break specification Hardware Break designation Software Break specification Software Break designation Software Break op code specification External Break op code specification External Break on/off designation External Break on/off designation Event Break designation Timeout Break designation Write protect Break designation Hardware arm/individual designation Break initialize Break event with passcount

Calculation Compare Disassemble Dump

Event status Event specification Event designation

Examine only Examine and change Fill Go

History - realtime trace status History - realtime trace counter reset History - monitor trigger storage History - event trigger History - format display History - search Identification Incircuit status Incircuit specification Load Move Mapping status Mapping specification Next

Offset status Offset specification Pin status Pin specification

Port examination Port examination and change Print Quit Register status Register reset Register change

Save Search Supervisor status Supervisor specification

Trace status Trace designation Trace specification

User Verify Zice

#### Command Notes:

- \*Keywords/key characters are displayed as; M / , etc, or as BOLD characters. They represent words, letters, and characters which must be entered. Any combination of upper/lower case letters may be used.

- \*Lowercase letters show items which the user must supply, such as "filename" in which the user would enter the name of a selected file.

- \*A vertical line "|" is shown to indicate a choice between separated information which must be selected, such as;

ON OFF

ON or OFF may be entered, but not both.

\*Include all punctuation such as commas, equal signs, colons, slashes, feature keys. Etc.

\*Available address/data parameters are given at the end of the explanations and grouped as "[hex16/hexdata/ L byte/ASCII 32, etc]."

These address/data parameters include;

| [hex16]<br>[hexdata] | <pre>:hexadecimal 16-bit memory address. :word or byte data (8/16 bit). Valid</pre> |

|----------------------|-------------------------------------------------------------------------------------|

| [nexuala]            | range is 0-F and X.                                                                 |

| [L byte]             | <pre>:number of bytes. Hexadecimal 16-bit,<br/>0-F.</pre>                           |

| [ASCII 32]           | :ASCII codes. All ASCII A thru Z char-<br>acters(32) are available.                 |

| decimal              | :decimal values are specified within the brackets.                                  |

\*Commands are divided into different sub-groups based on their operation. This is shown whenever one command can perform several different functions, such as the Event Command. In this case such sub-groups as Status, Designation and Specification are used.

Status means; COMMAND name (cr). Designation means; COMMAND name ON/OFF or ON/OFF/CLR. Specification means; COMMAND name address, data, etc.

Other sub-groups are individually identified by selective titles (i.e. COMMAND: change, reset, display, etc).

#### INTERRUPTION Process

Emulation stop with GO command :press MONITOR swith on Operator Panel.

Stop :pressing <ESC> key on console keyboard stops the corresponding command.

- Interrupt (SP) :pressing the (space) bar on the console keyboard interrupts sequence after one line is displayed on screen. To restart display, press (space) bar again.

- <DC3> :pressing the (CTR-S) key on the console keyboard immediately interrupts display.

#### INPUT STATEMENT CORRECTION

| Correction of<br>one character | : <del>(delete) Data is cancelled by the<br/>number of Rub out specifications and<br/>the corresponding characters are dis-<br/>played.</del> |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Backspace                      | : <bs>(backspace) Backspace operation is<br/>performed by the specified number and<br/>corresponding data cancelled.</bs>                     |

Cancellation of all data entry :<NAK> Pressing (CTL-U) cancels all entry data.

## Error Messages

| ERROR MESSAGE                   | COMMAND OCCURRENCE                      | DISPLAYED WHEN;                                                          |

|---------------------------------|-----------------------------------------|--------------------------------------------------------------------------|

| UNABLE BREAK ADDRESS            | Break<br>Go                             | a software break is specified<br>in the non-RAM area                     |

| MULTI BREAK ADDRESS             | Break<br>Go                             | a software break is duplicated<br>at the same address                    |

| WARNING UNABLE SOFT BREAK       | Break                                   | a software break is set at the<br>address presently not mapped<br>in RAM |

| *** FILE NOT FOUND              | All                                     | no file exists                                                           |

| *** DISK READ ERROR             | All                                     | a disk read error occurs                                                 |

| *** DISK WRITE ERROR            | All                                     | a sum check error occurs                                                 |

| *** NO DIRECTORY SPACE          | All                                     | no blank area available                                                  |

| C?>                             | All                                     | a command code error occurs                                              |

| P?>                             | All                                     | a parameter code error occurs                                            |

| /?>                             | All                                     | a modifier code error occurs                                             |

| MEMORY WRITE ERROR AT XXX       | Assemble,Examine<br>Load,Move,Fill      | there is a memory modification error.                                    |

| MEMORY TIMEOUT ERROR AT<br>XXXX | Assemble,Dump,Fill<br>Examine,Load,Move | memory I/O in the target system does not respond to ICD access.          |

| I/O TIMEOUT ERROR AT XX         | Port,Verify,Save<br>Compare,Search      | timeouts a waitstate                                                     |

| XXXX INPUT ERROR                | Examine,Assemble,<br>Port               | as an input error                                                        |

| BREAK BUSY                      | Break,Go                                | the break specification exceeds the limit                                |

#### THIS PAGE INTENTIONALLY BLANK

#### Commands

ASSEMBLE specification - changes Z80 assemble codes to Z80 machine codes and modifies the storage contents;

●>A mem.addr (cr)

xxxx (Z80 assemble code) (cr)

xxxx (cr)

mem.addr :memory address [hex16].

xxxx :ICD displays address then input Z80

assemble code.

EXAMPLE:

Move the data that resides in the Target System memory Ø-ØFFF, to the Emulator memory. Start at the ICD address,Ø;

>MØ, FFF,Ø,UP

BREAK status - displays the existing break status;

●>B (cr)

\_\_\_\_\_

Hardware BREAK specification - sets a hardware break;

●>B/ A|B|C stat , addr , passcount (cr)

A B C :hardware break name.

| stat >>> b | reak status;                                                      |

|------------|-------------------------------------------------------------------|

| М          | :memory access                                                    |

| Р          | :port access                                                      |

| MR         | :memory read                                                      |

| MW         | :memory write                                                     |

| PW         | :port write                                                       |

| PR         | :port read                                                        |

| OF         | :operation code fetch                                             |

| IA         | :interrupt acknowledge                                            |

|            |                                                                   |

| addr       | :break address [hex16].                                           |

| passcount  | <pre>:break passing count [decimal 1 (default)   to 65535].</pre> |

Hardware BREAK designation - turns on, off or clears a specified hardware breakpoint;

$\Rightarrow$  B/ A B C ON OFF CLR (cr)

A B C :hardware breakpoint name.

Software BREAK specification - sets a software break;

●>B/\_0-7 addr , passcount (cr)

0-7 :software break name

addr :break address [hex16]. passcount :specifies break passing count (loop counter) [decimal 1 (default) to 65535].

Software BREAK designation - turns on, off or clears a specified software break;

$\Rightarrow$  B/ 0-7 ON OFF CLR (cr)

0-7 :software break name

Software BREAK op code specification - specifies to place a software break in the enable (EN) state or the disabled (DI) state;

●>B S= EN DI (cr)

External BREAK hi/low designation - specifies an external break to occur at the HI or LOw edge;

●>B/X HI|LO (cr)

External BREAK designation - turns on, off or clears an external break;

●>B/X ON|OFF|CLR (cr)

Event BREAK designation - turns an event break on or off;

●>B/E ON OFF (cr)

\_\_\_\_\_

Timeout BREAK designation - turns a timeout break on or off;

●>B/T ON OFF (cr)

\_\_\_\_\_

Write protect BREAK designation - turns a write protect break on or off;

●>B/W ON OFF (cr)

\_\_\_\_\_

Hardware arm/individual BREAK specification - used with a specified hardware break name (A,B or C). Arm enables a break to occur after an event trigger takes place. INDividual allows a break to occur without regard to an event trigger;

$\rightarrow$  B/ A|B|C ARM IND (cr)

A|B|C :hardware break name

BREAK initialize - clears the event passing condition and resets the ARM specification;

●>B INI (cr)

BREAK event with passcount - specifies the number of software pass counts;

●>B/E passcount (cr)

### EXAMPLES (BREAK command):

DISPLAY BREAK STATUS WITHOUT HARDWARE BREAK ON;

DISPLAY A BREAK STATUS WITH HARDWARE BREAK ON;

SET BREAK STATUS WITH A 16-BIT PHYSICAL ADDRESS AND ISSUE A BREAK STATUS COMMAND;

>B/A M,000X\_111X\_XXX\_00000 >B A (ON) M XXX0 1 Ø IND (0000X\_111X\_XXX\_00000) T (ON) S (DI) W (OFF)

SET A SOFTWARE BREAK USING A HEXADECIMAL ADDRESS;

| >B/7 123<br>>B   | 84 |              |   |   |                             |

|------------------|----|--------------|---|---|-----------------------------|

| A (ON)<br>7 (ON) | Μ  | XXXØ<br>1234 | 1 | Ø | IND (0000X_111X_XXXX_00000) |

| T (ON)<br>S (DI) |    | 1234         | • | b |                             |

| W (OFF)          |    |              |   |   |                             |

SET ARM BREAK FOR HARDWARE BREAK A;

| >B/A ARM<br>>B<br>A (ON) M XXXØ<br>7 (ON) 1234<br>T (ON)<br>S (DI) | 1 | Ø | ARM (ØØØX_111X_XXXX_ØØØØ) |

|--------------------------------------------------------------------|---|---|---------------------------|

| W (OFF)                                                            |   |   |                           |

ENABLE A SOFTWARE BREAK;

| 7 (ON)  | XXXØ<br>1234 | 1 | Ø | ARM (ØØØX_111X_XXXX_ØØØØ) |

|---------|--------------|---|---|---------------------------|

| T (ON)  |              |   |   |                           |

| S (EN)  |              |   |   |                           |

| W (OFF) |              |   |   |                           |

CALCULATION - allows subtraction and addition of hex and decimal numbers. Both subtraction and addition operations can be performed on the same line.

●>C data ± data ± data ... (cr)

data

:operation data. Decimal valid for -8388608 to 8388607, hex valid for 0 to FFFFFF(H).

EXAMPLE:

EXECUTE MULTIPLE HANDLING OF SUBTRACTION AND ADDITION USING HEX AND DECIMAL DATA INTERCHANGABLY;

>C 1234+1234 H: ØØØ9A4 D: 2468

>C 1000H-FFFH H: 000001 D: 1

COMPARE - compares the contents of a specified memory and displays the unmatching data;

O beg.addr , end addr , comp.addr , UP PU (cr)

beg.addr :comparison beginning address [hex16]. end addr :ending comparison address [hex16/L byte]. comp.addr :memory address to be compared [hex16].

UP :use beg.addr for the user memory and comp.addr for the ICD program memory.PU :use beg.addr for the ICD program memory and comp.addr for the user memory.

EXAMPLE:

0001

Ø6

0001

8F

MEMORY COMPARISON ● NOTE: OF THE RANGE; Ø TO ØØØ1 1 - TARGET SYS MEMORY ADDRESS >00 Ø,FFF,ØØØ1,UP <CR> 2 - TARGET SYS MEMORY CONTENTS 3 - EMULATOR MEMORY ADDRESS 2 M 3 ADDRESS 4<sub>M</sub> ADDRESS 4 - EMULATOR MEMORY CONTENTS ØØØØ C3 ØØØØ FF

DISASSEMBLE - disassembles the memory contents and displays it;

●>DI beg.addr , end addr (cr)

| beg.addr | :beginning memory | y address [hex16].     |

|----------|-------------------|------------------------|

| end addr | :ending memory ad | ddress [hex16/L byte]. |

#### EXAMPLE:

| A, (HL)<br>A<br>NZ, Ø3ØØH<br>O (DE), A<br>C HL<br>C DE<br>Ø1Ø6H<br>P<br>A, (3AØØH) |

|------------------------------------------------------------------------------------|

|                                                                                    |

\_\_\_\_\_

DUMP - displays the memory contents in either byte or word units. The contents is represented by a hex number or ASCII code;

### ●>D/ W beg.addr , end addr (cr)

W :dump memory contents on a word basis (default is a byte basis).

beg.addr :beginning memory address [hex16].

end.addr :ending memory address [hex16/L byte].

EXAMPLE:

DUMP MEMORY CONTENTS FROM Ø TO 30;

>DØ,3Ø

0 1 2 3 4 5 6 7 8 9 A B C D E F 21 FF 00 11 34 12 77 12 13 23 B7 C2 06 00 C3 00 Ø 2 3 4 5 ASCII CODE ØØØ0 !...4.w..#7B..C. ði ØØ ØØ1Ø ØØ2Ø ØØ ØØ ØØ ..... . . . . . . . . . . . . . . . . . ØØ Ø..... . . . . . . . . . . . . . . . . ØØ3Ø ØØ

DUMP MEMORY CONTENTS INTO WORD;

| >D/W                         | AØØØ,                            | L4Ø |                                   |                                   |              |                                   |                                   |                                   |                                                                            |

|------------------------------|----------------------------------|-----|-----------------------------------|-----------------------------------|--------------|-----------------------------------|-----------------------------------|-----------------------------------|----------------------------------------------------------------------------|

| AØØØ<br>AØ1Ø<br>AØ2Ø<br>AØ3Ø | Ø<br>FØ7F<br>FØ17<br>DØØ<br>FØØD | 2   | 4<br>F8Ø5<br>FØØ5<br>FØØ9<br>FØØ5 | 6<br>9ØØF<br>24ØF<br>Ø1ØF<br>ØØØF | FØØ5<br>D21F | A<br>AFAF<br>BDAF<br>A74F<br>A7AF | C<br>FØØD<br>FØED<br>FØ25<br>FØ45 | E<br>ØØ1C<br>18ØF<br>Ø21F<br>52ØF | ASCII CODE<br>.P.!.XP//.P<br>.P/E.P.\$.P/=MP<br>.P/PRO'%P<br>.P%!.PS/'EP.R |

EVENT status - displays the current event status; >EV (cr) EVENT specification - sets or releases an event trigger; >EVST=stat A=addr D=data (cr) stat >>> event trigger status; М :memory access MR :memory read MW :memory write Ρ :port access PR :port read PW :port write OP :operation code fetch IA :interrupt acknowledge addr :directs event trigger at a specified break address [hex16]. data :specifies event data [hexdata]. \_\_\_\_ \_\_\_\_\_ EVENT designation - turns on, off or clears an event trigger; >EV ON OFF CLR (cr) EXAMPLES (EVENT command): SPECIFY AN EVENT HEX ADDRESS USING 'DON'T CARE'; >EV A=AXXØ >EV (0N)STATUS = ANYADDRESS = AXX0 (1010\_XXXX\_XXX\_00000)  $(XXXX_XXXX)$ DATA = XX SPECIFY EVENT DATA; >EV D=0010\_11XX >EV (ON) STATUS = 0FADDRESS = AXXØ (1010\_XXXX\_XXXX\_0000) = 2X DATA  $(\emptyset\emptyset\overline{1}\emptyset_11\overline{X}X)$ SET EVENT COMMAND USING ADDRESS, DATA AND STATUS: >EV A=00FF D=12 ST=MR >EV (ON) STATUS = MR ADDRESS = ØØFF (000\_0000\_1111\_1111)

= 12

Data

(0001\_001)

EXAMINE only - examines the memory contents and displays it in either ASCII or hex data;

●>E/ W addr (cr)

Ŵ

:examine memory contents on a word basis (the default is a byte basis).

addr :beginning address of examined memory [hex16].

EXAMINE and change - examines and changes the memory contents to either ASCII or hex data;

●>E/ W beg.addr = mod.data (cr)

| W           | <pre>:change memory contents on a word basis (the<br/>default is a byte basis).</pre> |

|-------------|---------------------------------------------------------------------------------------|

| beg.addr    | <pre>:beginning memory address to be changed [hex16].</pre>                           |

| mod.data    | :memory modification data [hexdata/ASCII32].                                          |

| note: multi | -display of data;                                                                     |

| xxxx xx=dat | a (cr) :displays data at next address after change.                                   |

|             | ,(cr) :displays data at same address<br>after change.                                 |

|             | $\bigwedge$ cr) : displays data at address decre-                                     |

mented by 1 after change.

/(cr) :terminates Examine command after

change.

When data is omitted, memory contents remain unchanged.

EXAMPLE:

EXAMINE AND CHANGE MEMORY IN EXAMINE AND CHANGE MEMORY IN BYTE DATA; WORD DATA; >E 0100 <CR> >E/W 100 <CR> 0100 FA = CHANGE DATA <cr> 0100 03FA = CHANGE DATA <CR>  $0101 \ 03 =$  $0102 \ 1F21 =$ 0102 21 = 0103 1F = 0104 FD = 0102 1121 = 0104 11FD = 0106 FDAB = 0108 200E =  $0105 \ 11 =$ 010A FECD =0106 AB =0107 FD =

FILL - used to fill memory with either hex or ASCII codes;

>F W beg.addr , end addr , data (cr)

W :fill memory contents on a word basis (the default is a byte basis).

beg.addr :beginning address to be filled [hex16]. end addr :end memory address [hex16/L byte]. (default = data to be filled from the beginning address is written).

data :specifies data to be filled [hexdata/ASCII32].

EXAMPLE:

FILL MEMORY WITH "Ø" FROM ADDRESS ØØØØ TO ØØFF;

>F ØØØ,ØØFF,Ø

FILL MEMORY WITH ASCII CHARACTER FROM Ø TO FF;

F ØØØ, ØFF, ZAX'

GO - executes the user program;

●>G beg.addr , end addr , end addr\* (cr)

beg.addr :beginning executable address [hex16].

end addr :ending executable address [hex16].

end addr\* :optional second end address [hex16].

EXAMPLE:

EXECUTE A USER PROGRAM STARTING AT OH;

>G Ø,₿

IF(SP) PC MC OP BC IY DF IX н ØØØB 11ØØBØ LD DE.ØBØØØH BØØØ FFFC ØØØØ AØØØ ØØØØ ØØØØ ØØ ØØØØ Ø Ø4ØØ <br />

<b

CONTINUE THE EXECUTION AFTER BREAK;

>G

PC. MC 0P SP AF BC IX IF(SP)DE IY HL 15DC 3AØØ3A LD A, (3AØØH) FFB6 3AØØ 141Ø BØØ1 9FØ1 ØØØØ ØØØØ ØØ Ø Ø 3ØØ <BREAK MONITOR>

HISTORY - implements the trigger modes (6 types) for realtime tracing, and displays or searches for the user program operation to be traced.

Realtime trace status (HISTORY) - displays the current trace status;

●>H (cr)

Realtime trace counter reset (HISTORY) - clears (resets) the realtime trace counter;

●>H CLR (cr)

Monitor trigger storage (HISTORY) - specifies the begin, end, center or multiple monitor trigger;

●>H BM EM CE ME , range (cr)

BM :begin monitor trigger storage. Trace section is initiated by emulation start and terminated at a predetermined breakpoint specified by the range.

- EM :end monitor trigger storage. After initiating emulation with the Go or Next command, the monitor will respond with a break when the trace is terminated. Maximum range is 2048.

- CE :center event trigger. Trace section is recognized both before and after the event point.

- ME :multiple event trigger. Trace is performed each time an event point is passed during loop processing.

range :trace range [decimal 1 to 2047]

End trigger (HISTORY) - sets the end monitor or end event trace specification;

●>H EM EE (cr)

ΕM :end monitor trigger. Emulation begins using the GO or NEXT command to start trace and ends when control returns to monitor by passing a breakpoint. EΕ :end event. Terminates trace after event point is passed. Trace range is 2047. HISTORY format display - displays in disassembled or machine cycle format; >H M D , int.point , term.point (cr) Μ :display in machine cycle format. D :display data with assemble codes. int.point :display or search initiation storage pointer [decimal 1 to 2047]. term.point :display or search termination storage pointer [decimal 1 (default) to 2047]. HISTORY search - searches for the contents of the real time trace buffer; ●>HS,/addr/data/cycle , int.point , term.point (cr) :search address [hex] (word address="addr W") addr data :search data [hexdata]. cycle >>> specifies the type of machine cycle; IA :interrupt acknowledge MR :memory read MW :memory write :port read PRΡW :port write :operation code fetch OF ΗA :halt acknowledge int.point :search initiation storage pointer [decimal 1 to 2047]. term.point :search termination storage pointer [decimal 1 (default) to 2047].

### EXAMPLES (HISTORY command):

DISPLAY THE HISTORY STATUS;

>H CLOCK COUNTER = ØØØØØØAA/ STORAGE MODE = EM STORAGE SIZE = 14/ 14

DISPLAY THE REAL TIME TRACE IN MACHINE CYCLE;

| >HM, 20<br>POINT<br>ØØ2Ø<br>ØØ19<br>ØØ18<br>ØØ17<br>ØØ16<br>ØØ15<br>ØØ14<br>ØØ13<br>ØØ14<br>ØØ13<br>ØØ12<br>ØØ11<br>ØØ10<br>ØØ09<br>ØØØ8<br>ØØØ5<br>ØØØ4 | ADDR<br>ØØØ3<br>ØØØ4<br>ØØØ5<br>ØØØ6<br>ØØØ85<br>ØØØ84<br>ØØØ82<br>ØØØ82<br>ØØØ8<br>ØØØ8<br>ØØØ8<br>ØØØ8<br>Ø | DT<br>11<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø<br>Ø | ፚኯ፟፟፟፟፟ቘቘኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯኯ |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------|--|

|                                                                                                                                                          |                                                                                                               |                                                                                                    |                                         |  |

| ØØØ6<br>ØØØ5<br>ØØØ4<br>ØØØ3                                                                                                                             | ØØØD<br>ØØØE<br>AØØØ<br>ØØØFi                                                                                 | BØ<br>7E<br>3A<br>77                                                                               | MR<br>M1<br>MR<br>M1                    |  |

.....

DISPLAY THE REALTIME TRACE IN MACHINE CYCLE AND DISASSEMBLE CODE;

| >H D<br>POINT<br>ØØ23<br>ØØ2Ø<br>ØØ17 | ADDR<br>ØØØØ<br>ØØØ3<br>ØØØ6 | DT<br>21ØØØ3<br>11ØØØ4<br>E5 | ST | OP<br>LD<br>LD<br>PUSH | HL,Ø3ØØH<br>DE,Ø4ØØH<br>HL |

|---------------------------------------|------------------------------|------------------------------|----|------------------------|----------------------------|

| ØØ16                                  | ØØ85                         | Ø3                           | MW |                        |                            |

| ØØ15<br>ØØ14                          | ØØ84<br>ØØØ7                 | ØØ<br>D5                     | MW | LD                     | HL.ØAØØØH                  |

| ØØ13                                  | ØØ83                         | Ø4                           | MW | -                      |                            |

| 0012                                  | ØØ82                         | ØØ                           | MW | 10                     | u daddau                   |

| ØØ11<br>ØØØ8                          | ØØØ8<br>ØØØB                 | 2100A0<br>1100B0             |    |                        | HL,ØAØØØH<br>DE,ØBØØØH     |

| ØØØ5                                  | ØØØE                         | 7E                           |    | ĽĎ                     | A, (HL)                    |

| 0004                                  | AØØØ                         | 3A                           | MR |                        | (1.11.) .                  |

| ØØØ3<br>ØØØ2                          | ØØØF<br>AØØØ                 | 77<br>3A                     | MW | LD                     | (HL).A                     |

|                                       |                              |                              |    |                        |                            |

SEARCH FOR THE CONTENTS OF REAL TIME TRACE FOR A MEMORY READ;

| >H S,///MR |         |    |

|------------|---------|----|

| POINT T    | Addr DT | ST |

| ØØ13       | Ø1Ø1 ØØ | MR |

| ØØ12       | Ø1Ø2 AØ | MR |

| ØØ1Ø       | 0104 00 | MR |

| 0009       | Ø1Ø5 BØ | MR |

| ØØØ7       | AØØØ FF | MR |

IDENTIFICATION - displays an ICD device name and a version of the installed firmware;

●>ID (cr)

INCIRCUIT status - displays the current incircuit mode;

●>I (cr)

INCIRCUIT specification - sets the ICD mapping mode;

●>I 0|1|2 (cr)

0

:System mode enables debugging (software only) using the ICD program memory. In this mode the target system I/O and interrupt signals are ignored.

:Partial mode. Enables debugging using the ICD program and target system memories. In this mode the specified mapping, I/O and interrupt signals all become valid.

2

1

:All mode. Enables debugging using only the target system memory. R/W and RO memories are operated as user memory (US).

note: default = current state displayed

LOAD - loads either a hex file on diskette or the object program (Intel format) from the specified port; ●>L/ T P A H filename , bias (cr) т :terminal port (ignore software handshake) P :terminal port (perform software handshake) А :auxiliary port Н :host port filename :(available with ZICE software only). :if omitted, starting address is specified bias [L byte]. EXAMPLE: LOAD THE TEST HEX FILE ON DISKETTE: > L TEST 100 >L/T ,100 200 MOVE - moves memory between the ICD and target system; ●>M beg.addr , end addr , mov.addr , UP|PU (cr) beg.addr :beginning memory address [hex16]. :ending memory address [hex16/L byte]. end addr :beginning address where data is transferred mov.addr to [hex16]. UP PU >>> optional parameter; UP :data is moved from the target memory to the ICD program memory. ΡU :data is moved from the ICD program memory to the target memory. EXAMPLE: MOVE MEMORY OF OH THROUGH FFFH: >M Ø.FFF.Ø.UP

MAPPING status - displays the current map status;

●>MA (cr)

```

_____

```

MAPPING specification - sets the ICD memory map. The target system or ICD program memory is specified on a 1K byte basis;

●>MA beg.addr , end addr = RO RW NO US (cr)

beg.addr :beginning address of mapping [hex16].

end addr :ending address of mapping [hex16/L byte]

note: default (beg.addr/end addr)=1K byte.

| RO | read only memory:  |

|----|--------------------|

| DW | .road/write memory |

| RW | :read/write memory                       |

|----|------------------------------------------|

| NO | :non memory area (a break occurs in this |

|    | area if accessed by a program)           |

| US | user (target system) memory:             |

EXAMPLE:

SPECIFY Ø TO FFF AS THE USER MEMORY;

>MA Ø, FFF = US

DISPLAY THE STATUS OF THE MEMORY MAP;

>MA IN-CIRCUIT MODE 1 (US=RW) ØØØØ-ØFFF = US 1ØØØ-FFFF = RW

DISPLAY THE STATUS OF THE MEMORY MAP WHEN THE INCIRCUIT MODE IS NOT 1;

>MA IN-CIRCUIT MODE Ø (US=RW) ØØØØ-ØFFF = US 1ØØØ-FFFF = RW NEXT - executes n-step All trace display from the current pointer;

●>N steps (cr)

steps

:specifies number of single steps [decimal 1

(default=1) to 15535].

EXAMPLE:

PERFORM A SINGLE STEP TRACE, FIVE STEPS FROM THE CURRENT PC;

>N 5

| PC   | MC      | OP |              | SP      | AF      | BC      | DE   | HL      | IX      | IY      | 1  | IF(SP) |

|------|---------|----|--------------|---------|---------|---------|------|---------|---------|---------|----|--------|

| Ø1Ø  | 3aøøaø  | LD | A, (ØAØØØH)  | ØØ2E    | Ø5ØE    | A5ØE    | Ø3Ø1 | 4312    | ØØØØ    | ØØØØ    | ØØ | Ø ØØ1A |

| Ø1Ø3 | 77      | цр | (HL),A       |         |         |         |      | • • • • |         | • • • • |    |        |

| 0104 | FEØ5    | CP | 5            |         | Ø542    | • • • • |      | • • • • |         | • • • • | •• |        |

| 0106 | C20001  | JP | NZ.0100H     | • • • • |         |         |      | iddd    | • • • • | ••••    | •• |        |

| 0109 | z iddad | Ш  | HL, DAOIOIDH | • • • • | • • • • |         |      | AØØØ    | • • • • | • • • • |    |        |

PERFORM A SINGLE STEP TRACE FOR FIVE STEPS CHANGING PC;

>R PC,200 >N 5

| PC MC<br>Ø2ØØ 3AØØ3A                       | OP<br>LD A, (3AØØH)        | SP<br>ØØ2E | AF<br>3A42 | BC<br>A5ØE | DE<br>Ø3Ø1 | HL<br>AØØØ         | 1X<br>ØØØ0 | IY<br>ØØØØ | l<br>ØØ | 1F(SP)<br>Ø ØØØØ |

|--------------------------------------------|----------------------------|------------|------------|------------|------------|--------------------|------------|------------|---------|------------------|

| 102103 100<br>102104 3A0103A<br>102107 100 | NOP<br>LD A,(3AØØH)<br>NOP | ••••       | ••••       | ••••       | ••••       | • • • •<br>• • • • | ••••       | ••••       | ••      | • • • • • •      |

| Ø2Ø8 3AØØ3A                                | LD A, (3AØØH)              | ••••       | ••••       | ••••       | ••••       | ••••               | ••••       | ••••       | •••     | · · · · · ·      |

OFFSET status - displays the current offset set value;

●>0 (cr)

OFFSET specification - sets a value (1 of 4) in an offset register for relative addressing. All offset registers can be used for ICD memory addressing parameters;

$\bullet$ >0 &1 &2 &3 &4 = addr (cr)

PIN status - displays the current pin status;

●>PI (cr)

\_\_\_\_\_

PIN specification - masks or unmasks the target system interruption signal when the incircuit mode is I1. Interruptions are ignored in the I1 mode and accepted in the I2 mode.

>PI level=EN DI (cr)

level >>> specifies bus request or interrupt level;

| BUSRQ | :bus request  |

|-------|---------------|

| NMI   | :non-maskable |

| INTR  | :interrupt    |

|       |               |

EN :interruption or hold signal enable. DI :interruption or hold signal disable.

note: default = current specification and mask states

are displayed.

EXAMPLE:

DISPLAY PIN STATUS;

>PI IN-CIRCUIT MODE 1 NMI (EN) = Ø BUSRQ (EN) INTR (EN) = Ø

DISABLE BUSREQUEST AND DISPLAY THE STATUS;

>PI BUSRQ = DI >PI IN-CIRCUIT MODE 1 NMI (EN) = Ø BUSRQ (DI) INTR (EN) = Ø PORT examination - examines the current port contents;

●>P port (cr)

port :conversion start port address [hex16/Lbyte].

PORT examination and change;

>P port = data (cr)

port :conversion start port address [hex16/Lbyte].

data

:port conversion data [hex16/ASCII 32].

note: multi-display of data is possible using the formats below;

| xxxx | xx : data | (cr) - display data at next address  |

|------|-----------|--------------------------------------|

|      |           | after change.                        |

|      |           | ,(cr) - display data at same address |

| •    |           | after change.                        |

|      |           | (cr) - display data at address that  |

|      |           | is decremented by 1 after the        |

|      |           | change.                              |

EXAMPLE:

EXAMINE AND WRITE OUT A PORT;

>P FF=12 12 34 56 78

READ AND CHANGE PORT IN BYTES USING MULTI-DISPLAY FORMAT;

>P 55 55 55:12 56 56:23 57 57:'B' 58 58:'D', 58 58:00, 59 59:12 58 58:/

READ AND CHANGE PORT IN WORDS USING MULTI-DISPLAY FORMAT;

>P 23 23 23:00 24 24:12 25 25:33 26 26:/ PRINT - outputs data sent from the ICD to the Terminal or Host/Aux ports simultaneously.

.

●>PR ON OFF (cr)

ON :output data to both Terminal and Host/Aux ports.

OFF :output data to the console only.

QUIT - returns control to the host system (valid when used with ZICE software only);

●>Q (cr)

\_\_\_\_\_

REGISTER status - displays the current register status;

●>R (cr)

EXAMPLE:

DISPLAY REGISTER WITH TITLES;

>R

| PC<br>ØØØØ | SP<br>ØØØØ | SZHPNC<br>ØØØØØØ | A<br>ØØ | BC<br>ØØØØ | DE<br>ØØØØ | ••••• |  | IF (SP)(HL)<br>Ø ØØ21 21 |  |

|------------|------------|------------------|---------|------------|------------|-------|--|--------------------------|--|

|------------|------------|------------------|---------|------------|------------|-------|--|--------------------------|--|

\_\_\_\_\_\_

REGISTER RESET - initializes all registers to 0 by pushing the RESET switch on the Operator Panel;

●>R (push)RESET (cr)

REGISTER change - changes the Z80 CPU register and program counter; ●>R reg = data (cr) req >>> register name; Α F С В D Ē Н L Т A' F' в' C! D' E۱ H ' L' I' ВC DH HLIX IΥ SP BC' DH' HL' CY S z HC P N IF(IFFI) :register change data [hexdata]. data EXAMPLE: CHANGE HL TO A VALUE OF ADDO; >R HL=A000 >R SP IF (SP)(HL) PC SZHPNC BC DE ØØØØ ØØØØ ØØ ØØØØ ØØØØ ØØ21 3A ØØØØØØ ØØ Ø \_\_\_\_ -----SAVE - saves a user program on diskette (HEX file) or dumps the user program to a specified port; ●>SA/ T|P|A|H filename, beg.addr, end addr, user addr, (cr) Т :terminal port (ignore software handshake) Ρ :terminal port (perform software handshake) Α :auxiliary port :host port Η filename :(available with ZICE software only). :beginning memory address [hex16]. beg.addr end addr :ending memory address [hex16/L byte]. user addr :beginning user program address [hex16]. EXAMPLE: GENERATE THE TEST. HEX FILE ON DISKETTE;

>SA TEST,Ø, 37FF,Ø

SEARCH - searches for the memory contents and displays the matched or unmatched address; ●>S/W /D beg.addr , end addr , data (cr) :search on a word basis (default is a byte /W basis). /D :search for unmatched data (default searches for matched data). beg.addr :beginning memory search address [hex16]. :ending memory search address [hex16/L byte]. end addr data :search data [hexdata/ASCII32]. EXAMPLE: >S Ø,L3Ø,12 ØØ12 >S/W 100,110,1234 >S/D Ø,10,00 ØØØ1 ØØØ2 0003 - -- ---ØØØ9 ØØØA ØØØB .... - ---\_ \_ ØØ1Ø

\_\_\_\_\_

SUPERVISOR status - displays the current supervisor state;

●>SU (cr)

SUPERVISOR specification - sets a breakpoint as a supervisor call. When executed, data is directly trans-ferred between the program being emulated and the ICD;

### $\Rightarrow$ SU/ C 7 U ON OFF (cr)

| С         | hardware break C as a supervisor call.                                               |

|-----------|--------------------------------------------------------------------------------------|

| 7         | software break 7 as a supervisor call.                                               |

| U         | :user software break as a supervisor call.                                           |

| ON<br>OFF | <pre>:set if used as a supervisor call. :set is not used as a supervisor call.</pre> |

EXAMPLE:

CHECK THE TERMINAL PORT INPUT STATE;

>DI 9000,900C 9000 1E01 LD E,1 9002 00 NOP OR A JP Z,90002H LD (HL),A 9ØØ3 B7 9004 CA0290 9007 77 INC B CP ØDH 9008 04 9009 FE0D RET Z LD (HL),A 9ØØB C8 9ØØC 77 >SU/7 ON >B/7 9002 >G 9000.9008

IF(SP)PC MC 0P SP AF BC DE IX IY 9008 04 INC B ØØ2E FFØ8 10ØE Ø3Ø1 ØØØØ 00 0 0000 AØØØ ØØØØ <br />

<b

TRACE status - displays the current trace mode;

●>T (cr)

\_\_\_\_\_

TRACE designation - makes the current trace mode valid invalid or clears the trace setting;

●>T ON OFF CLR (cr)

TRACE specification - sets the ICD trace mode;

>T/S A|J, beg.addr, end addr (cr)

/S :single step mode. In this mode the All or Jump trace is executed each time the space bar or (cr) is pressed.

all commands are traced and displayed.

jump trace (only branch command is traced and displayed).

beg.addr :beginning trace address [hex16]. end addr :ending trace address [hex16/] (default=FFFF).

EXAMPLE:

SET THE TRACE MODE;

>T A,1ØØ,4Ø5

DISPLAY TRACE STATUS;

>T (ON) ALL Ø1ØØ-Ø3ØØ

EXECUTE TRACE EXAMPLE;

>G 1ØØ

| PC MC<br>Ø1ØØ 21ØØAØ | OP<br>LD HL.ØAØØØH           | SP      | AF<br>ØØ23 | BC   | DE           | HL IX     | IY      | 1   | IF(SP)      |

|----------------------|------------------------------|---------|------------|------|--------------|-----------|---------|-----|-------------|

| Ø1Ø3 11ØØBØ          | LD HL,ØAØØØH<br>LD DE,ØBØØØH | ØØØ2    | 0023       | 1481 | 15Ø1<br>BØØØ | AØØØ ØØØØ | ØØØØ    | ØØ  | Ø 8185      |

| Ø1Ø6 D5              | PUSH DE                      | ØØØØ    | ••••       | •••• | DIDIDID      | ••••      | • • • • | ••  | 0000        |

| 0107 110003          |                              | 0000    | ••••       | •••• | Ø3ØØ         | ••••      | ••••    | ••  | . 8000      |

| Ø1ØA 7E              | LD A. (HL)                   | ••••    | FF23       | •••• | UJUU         | ••••      | • • • • | ••  | • ••••      |

| Ø1ØB 12              | LD (DE) A                    |         |            |      |              |           | ••••    | ••  | • ••••      |

| Ø1ØC 13              | INC DE                       |         |            |      | Ø3Ø1         |           |         | ••  | • • • • • • |

| Ø1ØD C1              | POP BC                       | ØØØ2    |            | BØØØ |              |           |         |     | . 8185      |

| Ø1ØE C3ØØØ4          | JP Ø4ØØH                     |         | • • • •    | •••• | • • • •      | ••••      | • • • • | • • |             |

| 0400 018016          | LD BC, 1680H                 | ••••    | ::::       | 168Ø |              | ••••      | ••••    | ••  |             |

| Ø4Ø3 8Ø              | ADD A.B                      | • • • • | 1511       |      | ••••         | ••••      | ••••    | ••  | • ••••      |

| Ø4Ø4 Ø3<br>Ø4Ø5 FØ   | INC BC                       | ••••    | ••••       | 1681 | ••••         | ••••      | ••••    | ••  | • ••••      |

RELEASE THE TRACE MODE;

>T CLR

NOTE: TRACE DISPLAYS ">" WITH THE <ESC> KEY TO ACCEPT A COMMAND.

NOTE: TRACE IS EXECUTED BY THE "GO" COMMAND, WHICH STARTS THE DISPLAY.

USER - allows the console terminal (connected to the ICD Terminal port) to be used as the terminal for the host system;

●>U code (cr)

code :terminator code

note: <ESC>,<NAK>,<SP>,<BS> and <cr> cannot be used as terminator codes.

#### EXAMPLE:

USER COMMAND WITH DESIGNATED TERMINATOR;

| >U !                         |                         |                            |                            |

|------------------------------|-------------------------|----------------------------|----------------------------|

| >A DIR B:<br>B: PIP<br>B: ED | COM : STAT<br>COM : ASM | COM : DUMP<br>COM : SYSGEN | COM : LOAD<br>COM : MOVCPM |

VERIFY - compares the object in the Intel format (from the host computer file or specified port) with the ICD memory contents;

## ●>V/ T|P|A|H filename, bias (cr)

| T<br>P<br>A<br>H                                                  | <pre>:terminal port (ignore software handshake) :terminal port (perform software handshake) :auxiliary port :host port</pre> |  |  |  |  |  |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| filename :object name to compare (valid with ZICE software only). |                                                                                                                              |  |  |  |  |  |

| bias                                                              | :bias of file or object to compare [hexdata].                                                                                |  |  |  |  |  |

| EXAMPLE:                                                          |                                                                                                                              |  |  |  |  |  |

| COMPARE THE                                                       | TEST.HEX FILE ON NOTE: "ADRS", "M" AND "O"                                                                                   |  |  |  |  |  |

DISKETTE WITH THE MEMORY CONTENTS; NUIL: "ADRS", "M" AND "U" INDICATE THE MEMORY ADDRESS, CONTENTS OF THE MEMORY ADDRESS AND OBJECT, RESPECTIVELY.

>V TEST ADRS M 0 ØØØØ

>V/T ,1000 ADRS M 0 02000

#### ZICE command

The Zice command is used exclusively for ZICE. When the ICD is used in the remote operation (host computer) the ZICE utility software is required for controlling the ICD. ZICE expands the commands not built into the ICD (see software specification for details).

#### ●>Z (Z command & parameter)

- Z commands include;

- ZB :batch processing. Executes commands of the filename. BAT file in the host system by batch processing.

- ZC :comment. Inserts a comment in a batch file

of the host system or in the middle of

repeat processing and outputs it to the

console.

- ZD :directory. Displays a directory of the \*.BAT

or \*.HEX file in the host system by directory

format.

- ZH :help. Displays command list.

- ZM :menu. Enter data by command menu method.

- ZP :print. Outputs the contents displayed on the console screen to a list device.

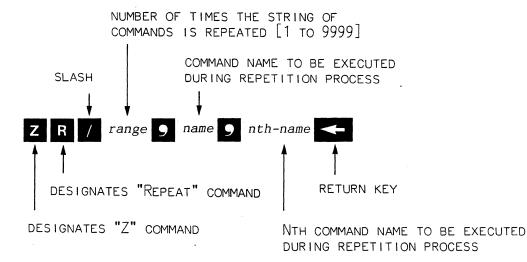

- ZR :repeat. Repeats a specified command.

- ZW :wait. Places a temporary pause in a repeat or batch subcommand.

## Quick-Commands

ASSEMBLE specification: >A mem.addr (cr) xxxx (Z80 assemble code) (cr) xxxx (cr)

BREAK status: >B (cr)

Hardware BREAK specification: >B/ A|B|C  $\underset{P}{MW}|_{PR}^{PW}|_{IA}^{OF}$ , addr, passcount (cr)

Hardware BREAK designation: >B/ A|B|C ON|OFF|CLR (cr)

Software BREAK specification: >B/ 0-7 addr, passcount (cr)

Software BREAK designation: >B/ 0-7 ON|OFF|CLR (cr)

Software BREAK op code specification: >B S= EN DI (cr)

External BREAK hi/low designation: >B/X HI LO (cr)

External BREAK designation: >B/X ON|OFF|CLR (cr)

Event BREAK designation: >B/E ON|OFF (cr)

Timeout BREAK designation:

>B/T ON|OFF (cr)

Write protect BREAK designation: >B/W ON|OFF (cr)

Hardware arm/individual BREAK specification: >B/ A|B|C ARM|IND (cr)

BREAK initialize: >B INI (cr)

BREAK event with passcount: >B/E passcount (cr)

```

CALCULATION:

>C data ± data ± data ... (cr)

COMPARE:

>CO beg.addr , end addr , comp.addr , UP PU (cr)

DISASSEMBLE:

>DI beg.addr , end addr (cr)

DUMP:

>D/ B|W|L beg.addr , end addr (cr)

EVENT status:

>EV (cr)

EVENT specification:

>EVST= M|MR|PR|OP A=addr D=data (cr)

PMWPWIA

EVENT designation:

>EV ON OFF CLR (cr)

EXAMINE only:

>E/ W addr (cr)

EXAMINE and change:

>E/ W beg.addr = mod.data (cr)

FILL:

>F W beg.addr , end addr , data (cr)

GO:

>G beg.addr , end addr , 2nd end addr (cr)

Realtime trace status (HISTORY):

>H (cr)

Realtime trace counter reset (HISTORY):

>H CLR (cr)

Monitor trigger storage (HISTORY):

>H BM \mid EM \mid CE \mid ME , range (cr)

Event trigger (HISTORY):

>H EM EE (cr)

HISTORY format display:

>H M D , int.point , term.point (cr)

HISTORY search:

>HS,/addr/data/ IA_MR_PR_OF , int.pointer , term.pointer (cr)

MW PW HA

```

```

IDENTIFICATION:

>ID (cr)

INCIRCUIT status:

>I (cr)

INCIRCUIT specification:

>I 0|1|2 (cr)

LOAD:

>L/ T P A H filename, bias (cr)

MAPPING status:

>MA (cr)

MAPPING specification:

>MA beg.addr , end addr = RO | RW | NO | US (cr)

MOVE:

>M beg.addr , end addr , mov.addr , UP PU (cr)

NEXT:

>N steps (cr)

OFFSET status:

>0 (cr)

OFFSET specification: