# High-Speed Serial Communication Controllers

Includes Specifications for the following parts: Z16C30 Z16C32

Product Specifications Databook

# High-Speed Serial Communication Controllers

**Includes Specifications** for the following parts:

Z16C30Z16C32

# Databook

,

# HIGH-SPEED SCC DATABOOK

# TABLE OF CONTENTS

| TITLE                                                              | PAGE |

|--------------------------------------------------------------------|------|

|                                                                    | I-1  |

| Z16C30 CMOS Universal Serial Controller (USC <sup>™</sup> )        | 1-1  |

| Z16C32 Integrated Universal Serial Controller (IUSC <sup>™</sup> ) | 2-1  |

| Application Notes and Support Products                             | 3-1  |

| Superintegration <sup>™</sup> Products Guide                       | S-1  |

| LITERATURE GUIDE AND THIRD PARTY SUPPORT                           | L-1  |

| ZILOG'S SALES OFFICES, REPRESENTATIVES AND DISTRIBUTORS            | Z-1  |

# Introduction

716039 GMBS Universel Serial Controller (USC<sup>®</sup>)

216032 Integrated Universal Serial Controller (USC)

**Application** Notes and **Support Products**

Superintegration<sup>®</sup> **Products Guide**

Literature Guide and Third Party Support

Zilog Sales Offices Representatives and Distributors

# INTRODUCTION

Zilog's Focus on Application Specific Products Helps You Maintain Your Technological Edge

Zilog's High-Speed SCC products are suitable for a broad range of applications, from generalpurpose use through high-end LANs and WANs. Whichever device you choose, you'll find a comprehensive feature set and easy-to-use development tools to speed your design time to production.

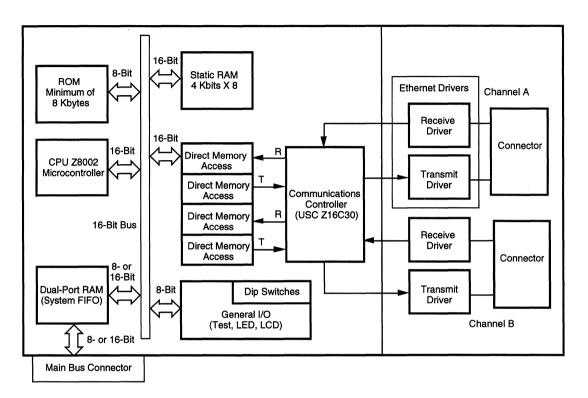

## Z16C30 CMOS USC<sup>™</sup> Universal Serial Controller

The USC Universal Serial Controller (USC) is a dual-channel multi-protocol datacommunications peripheral designed for use with any conventional multiplexed or non-multiplexed bus. The two independent full duplex channels can each operate up to 10 Mbps. The USC functions as a powerful serial-to-parallel, parallel-to-serial converter/controller and may be software configured to satisfy a wide variety of serial communications applications. The device contains a variety of new, sophisticated internal functions including two baud rate generators per channel, a digital phase-locked loop per channel, character counters for both receive and transmit in each channel, and 32-byte data FIFOs for each receiver and transmitter.

The USC handles asynchronous formats, synchronous byte-oriented formats such as BISYNC, and synchronous bit-oriented formats such as HDLC. This device supports virtually any serial data transfer application.

High-speed data transfers through DMA are supported by a Request/Acknowledge signal pair for each receiver and transmitter. The device supports automatic status transfer through DMA and allows device initialization under DMA control.

#### Z16C32 CMOS IUSC<sup>™</sup> Integrated Universal Serial Controller

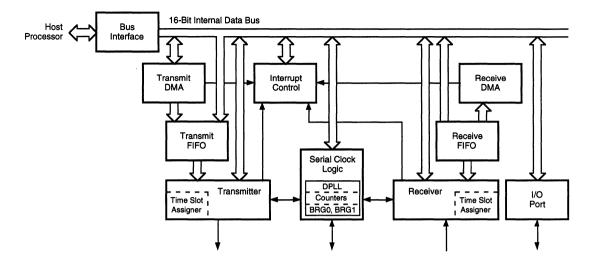

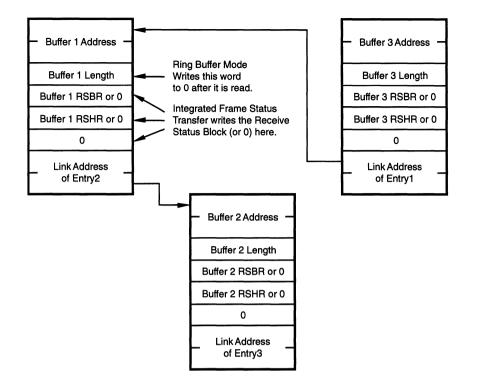

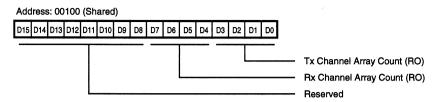

The Integrated Universal Serial Controller (IUSC) is a single-channel multiple protocol datacommunications device with on-chip DMA. The integration of a high speed serial communications channel with high performance DMA facilitates higher data throughput than is possible with discrete serial/DMA chip combinations. The buffer chaining capabilities combined with features like character counters, frame status block and buffer termination at the end of the frame facilitate sophisticated buffer management that can significantly reduce CPU overhead.

The IUSC is software configurable to satisfy a wide variety of serial communications applications. The 10 Mbit per second data rate and multiple protocol support make it ideal for applications in todays dynamic environment of changing specifications and ever increasing speed. The many programmable features allow the user to tune the device response to meet system requirements and adapt to future changes with software instead of redesigning hardware.

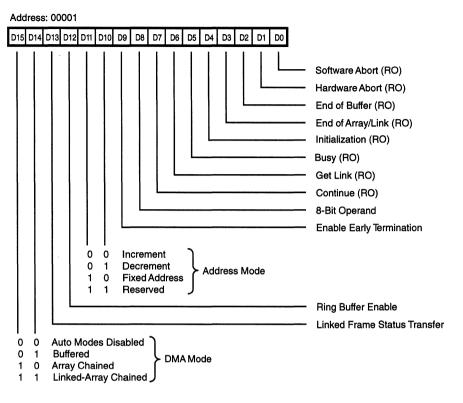

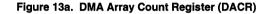

The on-chip DMA channels allow high-speed data transfers for both the receiver and the transmitter. The device supports automatic status transfer through DMA and allows device initialization under DMA control. Each DMA channel can transfer data words in as little as three 50 ns clock cycles and can generate addresses compatible with 32-, 24- or 16-bit memory ranges. The DMA channels may operate in any of four modes: single buffer, pipelined, array-chained, or linked-list. The array-chained and linked-list modes improve memory management and allow the IUSC to receive and transmit multiple frames without CPU intervention. To prevent the DMA from holding bus mastership too long, mastership time may be limited by counting the absolute number of clock cycles, the number of bus transactions, or both.

Introduction

1

# Z16C30 CMOS Universal Serial Controller (USC™)

Application Notes and **Support Products**

Superintegration" Products Guide

lieraine înde and Third Party Support

**Zilog Sales Offices** Representatives and Distributors

**PRODUCT SPECIFICATION**

# **Z16C30** CMOS USC<sup>™</sup> UNIVERSAL SERIAL CONTROLLER

## FEATURES

<sup>⊗</sup>ZiLŒ

- Two Independent, 0 to 10 Mbit/sec, Full Duplex Channels, Each with Two Baud Rate Generators and One Digital Phase-Locked Loop for Clock Recovery.

- 32-Byte Data FIFO's for Each Receiver and Transmitter

- 110 ns Bus Cycle Time, 16-Bit Data Bus Bandwidth

- Multi-Protocol Operation Under Program Control with Independent Mode Selection for Receiver and Transmitter.

- Async Mode with One to Eight Bits/Character, 1/16 to 2 Stop Bits/Character in 1/16 Bit Increments; Programmable Clock Factor; Break Detect and Generation; Odd, Even, Mark, Space or no Parity and Framing Error Detection. Supports One Address/Data Bit and MIL STD 1553B Protocols.

- Byte Oriented Synchronous Mode with One to Eight Bits/Character; Programmable Idle Line Condition; Optional Receive Sync Stripping; Optional Preamble Transmission; 16- or 32-Bit CRC and Transmit-to-Receive Slaving (for X.21).

- Bisync Mode with 2- to 16-Bit Programmable Sync Character; Programmable Idle Line Condition; Optional Receive Sync Stripping; Optional Preamble Transmission; 16- or 32-Bit CRC.

- Transparent Bisync Mode with EBCDIC or ASCII Character Code; Automatic CRC Handling; Programmable Idle Line Condition; Optional Preamble Transmission; Automatic Recognition of DLE, SYN, SOH, ITX, ETX, ETB, EOT, ENQ and ITB.

- External Character Sync Mode for Receive

- HDLC/SDLC Mode with Eight Bit Address Compare; Extended Address Field Option; 16- or 32-Bit CRC; Programmable Idle Line Condition; Optional Preamble Transmission and Loop Mode.

- DMA Interface with Separate Request and Acknowledge for Each Receiver and Transmitter.

- Channel Load Command for DMA Controlled Initialization.

- Flexible Bus Interface for Direct Connection to Most Microprocessors; User Programmable for 8 or 16 Bits Wide. Directly Supports 680X0 Family or 8X86 Family Bus Interfaces.

- Low Power CMOS

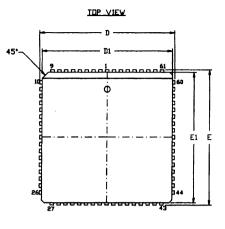

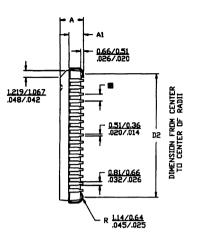

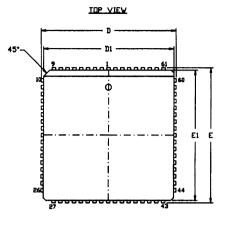

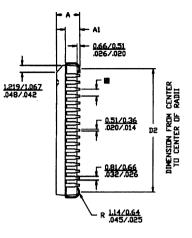

- 68-Pin PLCC Package

## **GENERAL DESCRIPTION**

The USC<sup>™</sup> Universal Serial Controller is a dual-channel multi-protocol data communications peripheral designed for use with any conventional multiplexed or non-multiplexed bus. The USC functions as a serial-to-parallel, parallel-to-serial converter/controller and may be software configured to satisfy a wide variety of serial communications applications. The device contains a variety of new, sophisticated internal functions including two baud rate generators per channel, a digital phase-locked loop per channel, character counters for both receive and transmit in each channel and 32-byte data FIFO's for each receiver and transmitter.

Zilog now offers a high speed version of the USC with improved bus bandwidth. CPU bus accesses have been shortened from 160 ns per access to 110 ns per access. The USC has a transmit and receive clock range of up to 10 MHz (20 MHz when using the DPLL, BRG, or CTR) and data transfer rates as high as 10 Mbits/sec full duplex.

The USC handles asynchronous formats, synchronous byte-oriented formats such as BISYNC and synchronous bit-oriented formats such as HDLC. This device supports virtually any serial data transfer application.

## **GENERAL DESCRIPTION** (Continued)

The device can generate and check CRC in any synchronous mode and can be programmed to check data integrity in various modes. The USC also has facilities for modem controls in both channels. In applications where these controls are not needed, the modem controls may be used for general-purpose I/O. The same is true for most of the other pins in each channel.

Interrupts are supported with a daisy-chain hierarchy, with the two channels having completely separate interrupt structures.

High-speed data transfers through DMA are supported by a Request/Acknowledge signal pair for each receiver and transmitter. The device supports automatic status transfer through DMA and also allows device initialization under DMA control.

To aid the designer in efficiently programming the USC, support tools are available. The Technical Manual describes in detail all features presented in this Product

Specification and gives programming sequence hints. The Programmer's Assistant is a MS-DOS disk-based programming initialization tool to be used in conjunction with the Technical Manual. There are also available assorted application notes and development boards to assist the designer in the hardware/software development.

# Note: All reserved bits must be programmed to zero when written to.

#### Notes:

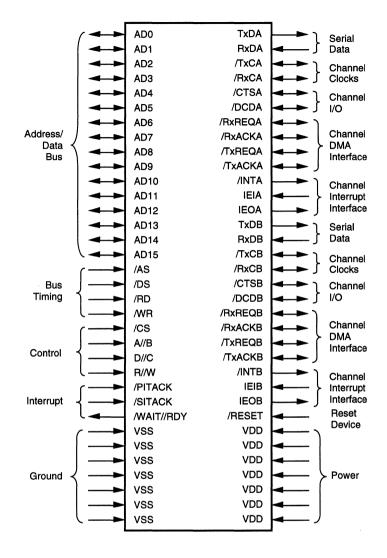

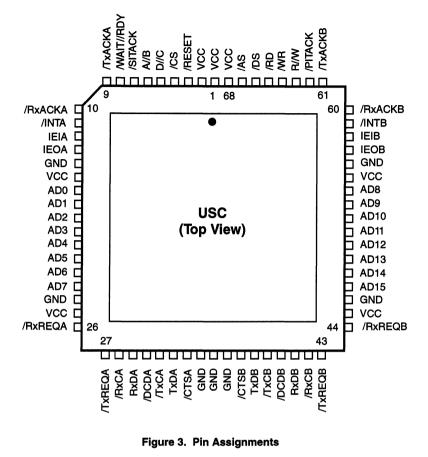

All Signals with a preceding front slash, "/", are active Low, e.g., B/W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>cc</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>SS</sub> |

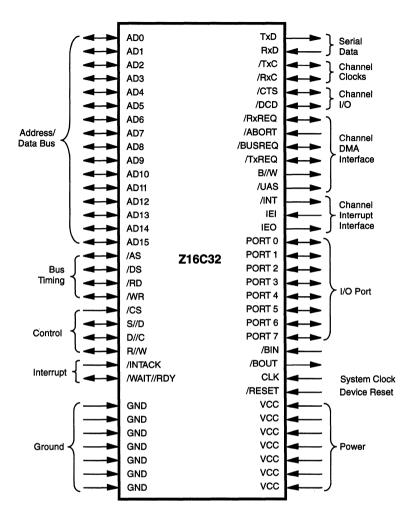

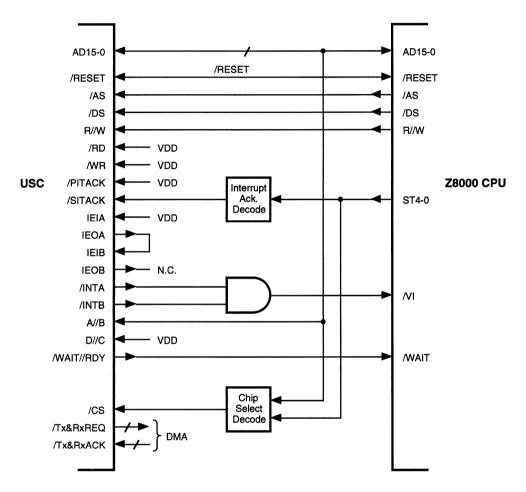

Figure 2. Pin Functions

1

## **GENERAL DESCRIPTION** (Continued)

#### **PIN DESCRIPTION**

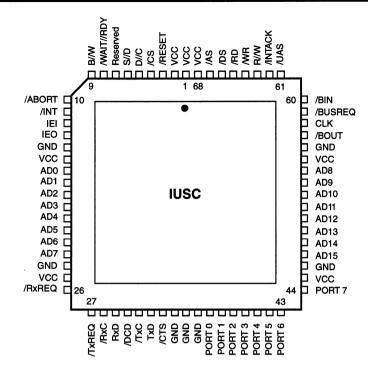

The device contains 13 pins per channel for channel I/O, 16 pins for address and data, 12 pins for CPU handshake and 14 pins for power and ground.

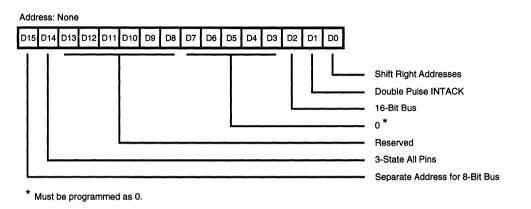

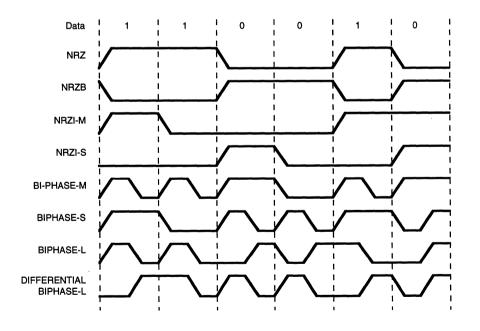

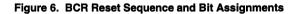

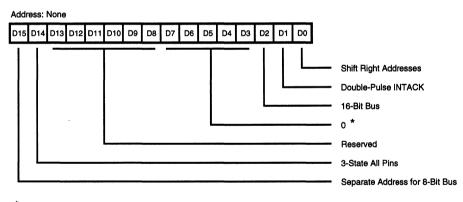

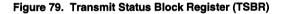

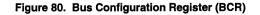

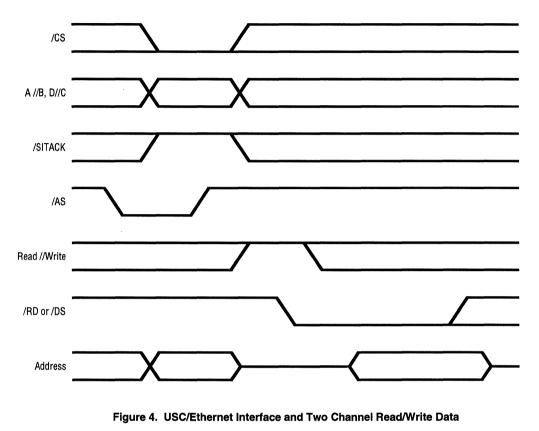

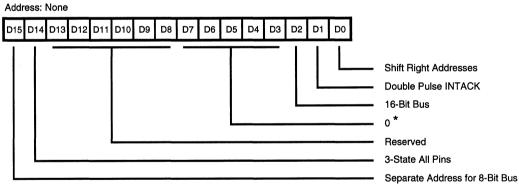

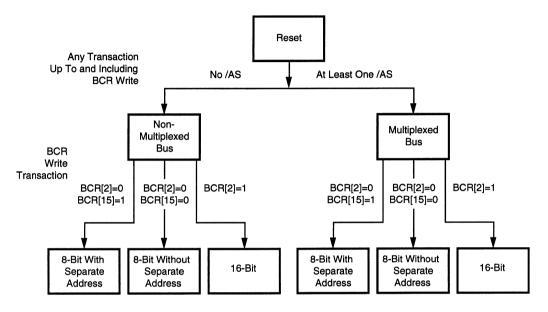

Three separate bus interface types are available for the device. The Bus Configuration Register (BCR) and external connections to the AD bus control selection of the bus type. A 16-bit bus is selected by setting BCR bit 2 to a 1. The 8-bit bus is selected by setting BCR bit 2 to zero and tying AD15 - AD8 to  $V_{ss}$ .

The 8-bit bus with separate address is selected by setting BCR bit 2 to zero and, during the BCR write, forcing AD15 to a 1 and forcing AD14-AD8 to zero.

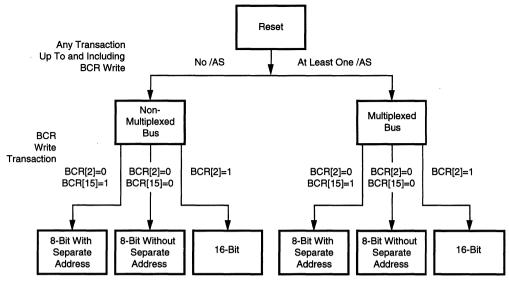

The multiplexed bus is selected for the USC if there is an Address Strobe prior to or during the transaction which writes the BCR. If no Address Strobe is present prior to or during the transaction which writes the BCR, a non-multiplexed bus is selected (See Figure 6).

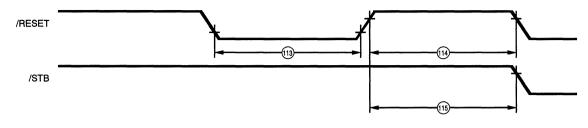

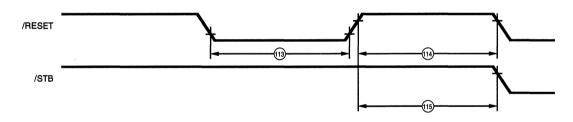

**/RESET** *Reset* (input, active Low). This signal resets the device to a known state. The first write to the USC after a reset accesses the BCR to select additional bus options for the device.

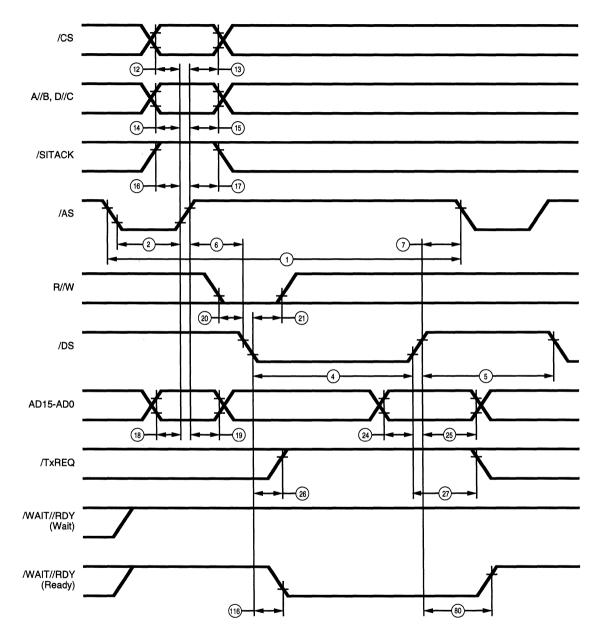

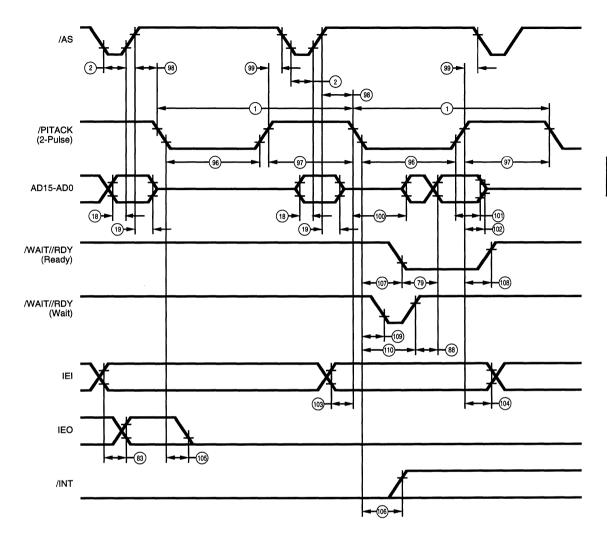

**/AS** Address Strobe (input, active Low). This signal is used in the multiplexed bus modes to latch the address on the AD lines. The /AS signal is not used in the non-multiplexed bus modes and should be tied to  $V_{nn}$ .

#### Z16C30 CMOS USC™ UNIVERSAL SERIAL CONTROLLER

# 2ilas

**/DS** Data Strobe (input, active Low). This signal strobes data out of the device during a read and may strobe an interrupt vector out of the device during an interrupt acknowledge cycle. /DS also strobes data into the device on the state of R//W.

**/RD** *Read Strobe* (input, active Low). This signal strobes data out of the device during a read and may strobe an interrupt vector out of the device during an interrupt acknowledge cycle.

**/WR** *Write Strobe* (input, active Low). This signal strobes data into the device during a write.

**R//W** *Read/Write* (input). This signal determines the direction of data transfer for a read or write cycle in conjunction with /DS.

**/CS** *Chip Select* (input, active Low). This signal selects the device for access and must be asserted for read and write cycles, but is ignored during interrupt acknowledge and fly-by DMA transfers. In the case of a multiplexed bus interface, /CS is latched by the rising edge of /AS.

**A//B** Channel A/Channel B Select (input). This signal selects between the two channels in the device. High selects channel A and Low selects channel B. This signal is sampled and the result is latched during the BCR (Bus Configuration Register) write. It programs the sense of the /WAIT//RDY signal appropriate for different bus interfaces.

**D//C** Data/Control Select (input). This signal, when High, provides for direct access to the RDR and TDR. In the case of a multiplexed bus interface, D//C High overrides the address provided to the device.

/SITACK Status Interrupt Acknowledge (input, active Low). This signal is a status signal that indicates that an interrupt acknowledge cycle is in progress. The device is capable of returning an interrupt vector that may be encoded with the type of interrupt pending during this acknowledge cycle. This signal is compatible with 680X0 family microprocessors.

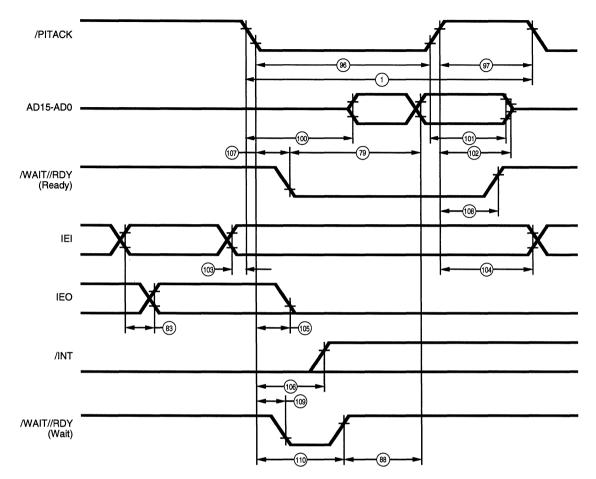

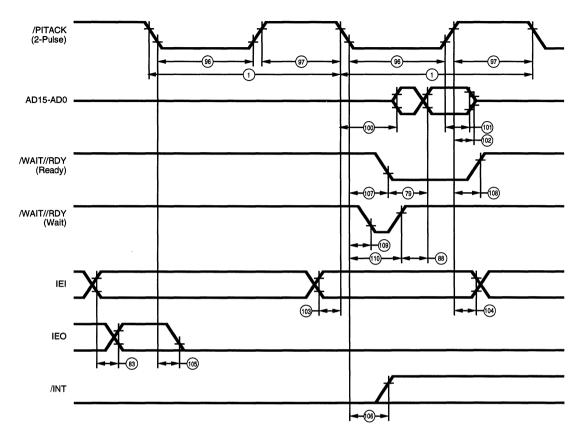

**/PITACK** *Pulsed Interrupt Acknowledge* (input, active Low). This signal is a strobe signal that indicates that an interrupt acknowledge cycle is in progress. The device is capable of returning an interrupt vector that may be encoded with the type of interrupt pending during this acknowledge

cycle. /PITACK may be programmed to accept a single pulse or double pulse acknowledge type. This programming is done in the BCR. With the double pulse type selected, the first /PITACK is recognized but no action takes place. The interrupt vector is returned on the second pulse if the no vector option is not selected. The double pulse type is compatible with 8X86 family microprocessors.

**(WAIT//RDY** *Wait/Data Ready* (output, active Low). This signal serves to indicate when the data is available during a read cycle, when the device is ready to receive data during a write cycle, and when a valid vector is available during an interrupt acknowledge cycle. It may be programmed to function either as a Wait signal or a Ready signal using the state of the A//B pin during the BCR write. When A//B is High during the BCR write, this signal functions as a wait output and thus supports the READY function of 8X86 family microprocessors. When A//B is Low during the BCR write, this signal functions as a ready output and thus supports the DTACK function of 680X0 family microprocessors.

AD15-AD0 Address/Data Bus (bidirectional, active High, tri-state). The AD signals carry addresses to, and data to and from, the device. When the 16-bit non-multiplexed bus is selected, AD15-AD0 carry data to and from the device. Addresses are provided using a pointer within the device that is loaded with the desired register address. When selecting the 8-bit non-multiplexed bus (without separate address) only AD7-AD0 are used to transfer data. The pointer is used for addressing, with AD15-AD8 unused. When selecting the 8-bit non-multiplexed bus (with separate address), AD7-AD0 are used to transfer data with AD15-AD8 used as address bus. When the 16-bit multiplexed bus is selected, addresses are latched from AD7-AD0 and data transfers are sixteen bits wide. When selecting the 8-bit multiplexed bus (without separate address) only AD7-AD0 are used to transfer addresses and data, with AD15-AD8 unused. When the 8-bit multiplexed bus with separate address is selected, only AD7-AD0 are used to transfer data, while AD15-AD8 are used as an address bus.

**/INTA, /INTB** Interrupt Request (outputs, active Low). These signals indicate that the channel has an interrupt condition pending and is requesting service. These outputs are NOT open-drain.

## PIN DESCRIPTION (Continued)

**IEIA, IEIB** Interrupt Enable In (inputs, active High). The IEI signal for each channel is used with the accompanying IEO signal to form an interrupt daisy chain. An active IEI indicates that no device having higher priority is requesting or servicing an interrupt.

**IEOA, IEOB** Interrupt Enable Out (outputs, active High). The IEO signal for each channel is used with the accompanying IEI signal to form an interrupt daisy chain. IEO is Low if IEI is Low, an interrupt is under service in the channel, or an interrupt is pending during an interrupt acknowledge cycle.

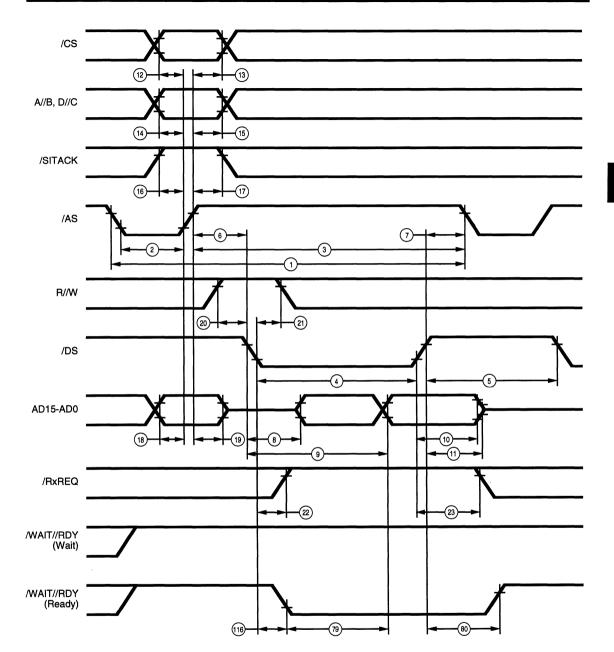

**/TxACKA, /TxACKB** *Transmit Acknowledge* (inputs or outputs, active Low). The primary function of these signals is to perform fly-by DMA transfers to the transmit FIFOs. They may also be used as bit inputs or outputs.

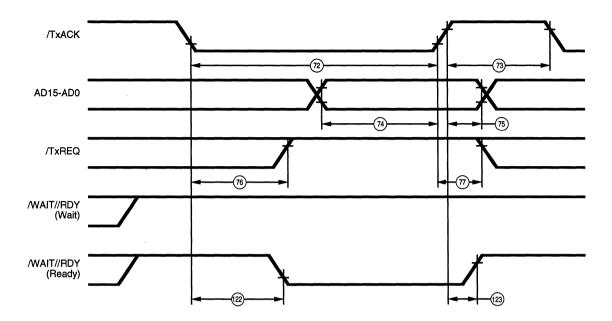

**/RxACKA, /RxACKB** *Receive Acknowledge* (inputs or outputs, active Low). The primary function of these signals is to perform fly-by DMA transfers from the receive FIFOs. They may also be used as bit inputs or outputs.

**TxDA, TxDB** *Transmit Data* (outputs, active High, tristate). These signals carry the serial transmit data for each channel.

**RxDA, RxDB** *Receive Data* (inputs, active High). These signals carry the serial receive data for each channel.

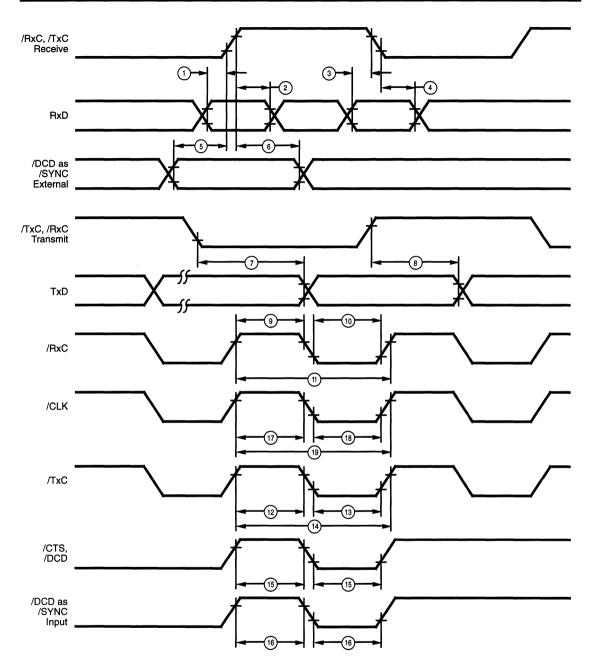

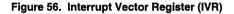

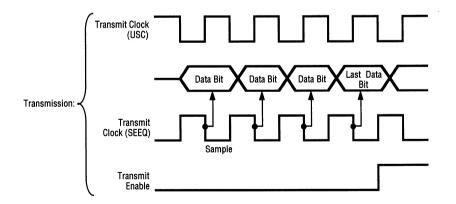

**/TxCA**, **/TxCB** Transmit Clock (inputs or outputs, active Low). These signals are used as clock inputs for any of the functional blocks within the device. They may also be used as outputs for various transmitter signals or internal clock signals.

**/RxCA, /RxCB** *Receive Clock* (inputs or outputs, active Low). These signals are used as clock inputs for any of the functional blocks within the device. They may also be used as outputs for various receiver signals or internal clock signals.

**/TxREQA, /TxREQB** *Transmit Request* (inputs or outputs, active Low). The primary function of these signals is to request DMA transfers to the transmit FIFOs. They may also be used as simple inputs or outputs.

**/RxREQA, /RxREQB** *Receive Request* (inputs or outputs, active Low). The primary function of these signals is to request DMA transfers from the receive FIFOs. They may also be used as simple inputs or outputs.

**/CTSA, /CTSB** *Clear To Send* (inputs or outputs, active Low). These signals are used as enables for the respective transmitters. They may also be programmed to generate interrupts on either transition or used as simple inputs or outputs.

**/DCDA, /DCDB** Data Carrier Detect (inputs or outputs, active Low). These signals are used as enables for the respective receivers. They may also be programmed to generate interrupts on either transition or used as simple inputs or outputs.

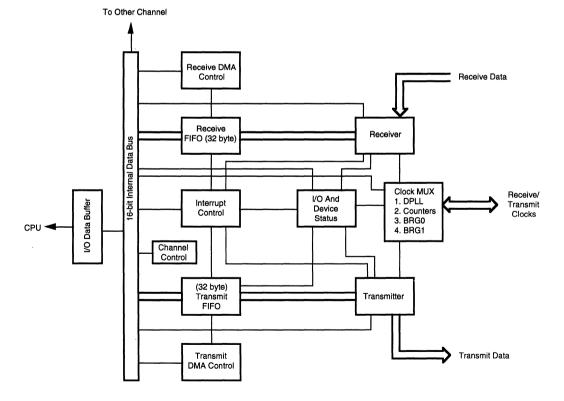

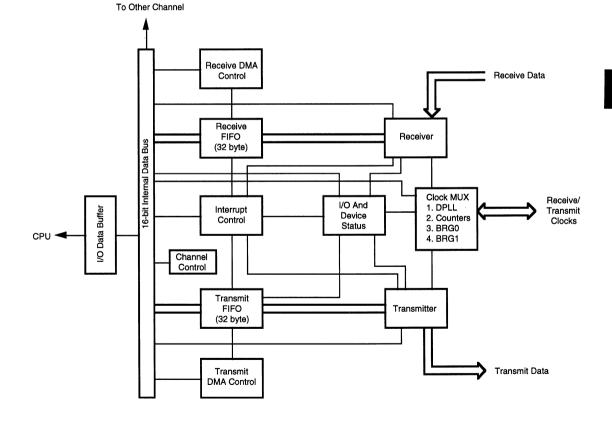

## ARCHITECTURE

The USC internal structure includes two completely independent full-duplex serial channels, each with two baud rate generators, a digital phase-locked loop for clock recovery, transmit and receive character counters and a full-duplex DMA interface. The two serial channels share a common bus interface. The bus interface is designed to provide easy interface to most microprocessors, whether they employ a multiplexed or non-multiplexed, 8-bit or 16-bit bus structure. Each channel is controlled by a set of thirty 16-bit registers, nearly all of which are readable and writable. There is one additional 16-bit register in the bus interface used to configure the nature of the bus interface. The BCR functions are shown in Figure 4.

## DATA PATH

Both the transmitter and the receiver in the channel are actually microcoded serial processors. As the data shifts through the transmit or receive shift register, the microcode watches for specific bit patterns, counts bits, and at the appropriate time transfers data to or from the FIFOs. The microcode also checks status and generates status interrupts as appropriate.

# FUNCTIONAL DESCRIPTION

The functional capabilities of the USC are described from two different points of view: as a data communications device, it transmits and receives data in a wide variety of data communications protocols; as a microprocessor peripheral, the USC offers such features as read/write registers, a flexible bus interface, DMA interface support and vectored interrupts.

## **Data Communications Capabilities**

The USC provides two independent full-duplex channels programmable for use in any common data communication protocol. The receiver and transmitter modes are completely independent, as are the two channels. Each receiver and transmitter is supported by a 32-byte deep FIFO and a 16-bit message length counter. All modes allow optional even, odd, mark or space parity. Synchronous modes allow the choice of two 16-bit or one 32-bit CRC polynomial. Selection of from one to eight bits-percharacter is available in both receiver and transmitter, independently. Error and status conditions are carried with the data in the receive and transmit FIFOs to greatly reduce the CPU overhead required to send or receive a message. Specific, appropriately timed interrupts are available to signal such conditions as overrun, parity error, framing error, end-of-frame, idle line received, sync acquired, transmit underrun, CRC sent, closing sync/flag sent, abort sent, idle line sent and preamble sent. In addition, several useful internal signals such as receive FIFO load, received sync, transmit FIFO read and transmission complete may be sent to pins for use by external circuitry.

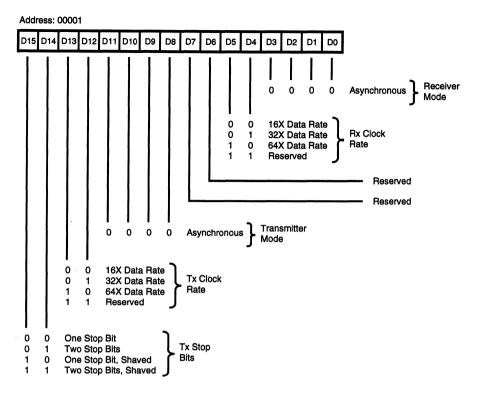

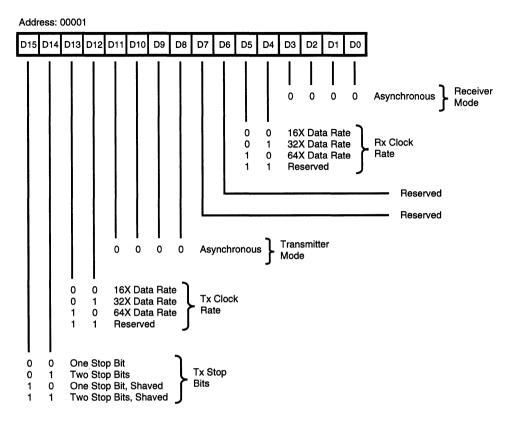

**Asynchronous Mode.** The receiver and transmitter can handle data at a rate of 1/16, 1/32, or 1/64 the clock rate. The receiver rejects start bits less than one-half a bit time and will not erroneously assemble characters following a framing error. The transmitter is capable of sending one, two, or anywhere in the range of 1/16th to two stop bits per character in 1/16 bit increments.

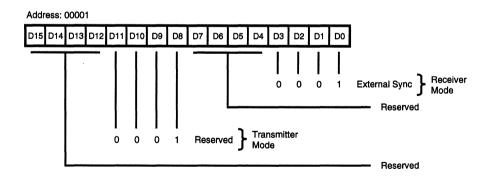

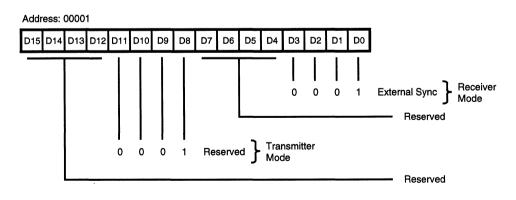

**External Sync Mode.** The receiver is synchronized to the receive data stream by an externally-supplied signal on a pin for custom protocol applications.

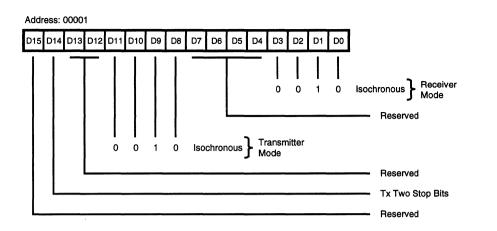

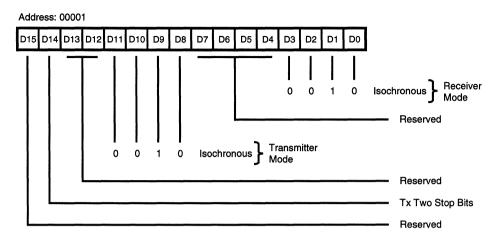

**Isochronous Mode.** Both transmitter and receiver may operate on start-stop (async) data using a 1x clock. The transmitter can send one or two stop bits.

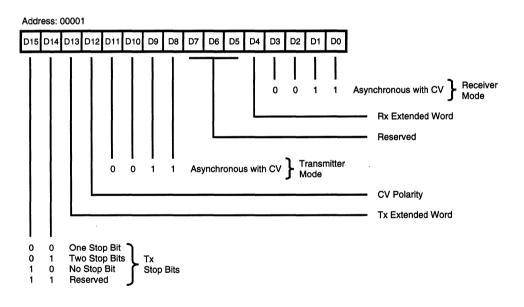

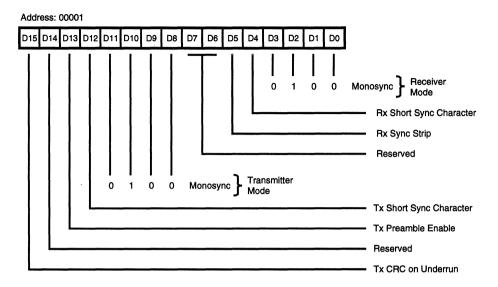

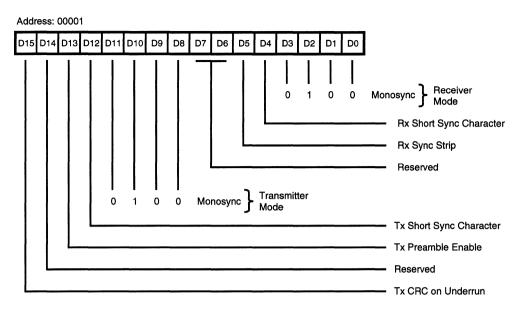

Asynchronous With Code Violations. This is similar to Isochronous mode except that the start bit is replaced by a three bit-time code violation pattern as in MIL-STD 1553B. The transmitter can send zero, one or two stop bits. **Monosync Mode.** In this mode, a single character is used for synchronization. The sync character can be either eight bits long with an arbitrary data character length, or programmed to match the data character length. The receiver is capable of automatically stripping sync characters from the received data stream. The transmitter may be programmed to automatically send CRC on either an underrun or at the end of a programmed message length.

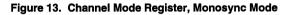

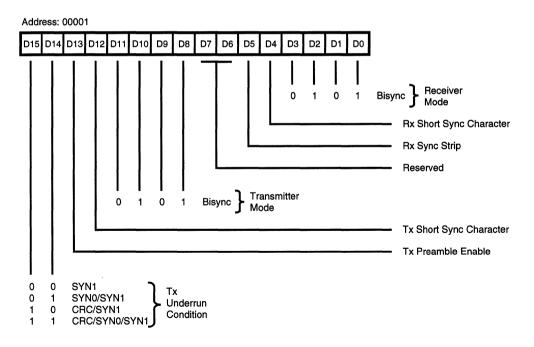

**Bisync Mode.** This mode is identical to monosync mode except that character synchronization requires two successive characters for synchronization. The two characters need not be identical.

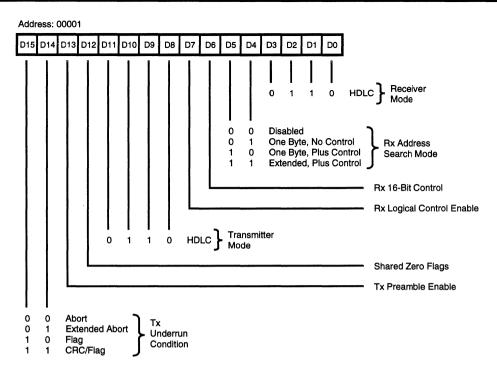

**HDLC Mode.** In this mode, the receiver recognizes flags, performs optional address matching, accommodates extended address fields, 8- or 16-bit control fields and logical control fields, performs zero deletion and CRC checking. The receiver is capable of receiving shared-zero flags, recognizes the abort sequence and can receive arbitrary length messages. The transmitter automatically sends opening and closing flags, performs zero insertion and can be programmed to send an abort, an extended abort, a flag or CRC and a flag on transmit underrun. The transmitter can also automatically send the closing flags with optional CRC at the end of a programmed message length. Shared-zero flags are selected in the transmitter and a separate character length may be programmed for the last character in the frame.

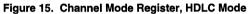

**Bisync Transparent Mode.** In this mode, the synchronization pattern is DLE-SYN, programmable selected from either ASCII or EBCDIC encoding. The receiver recognizes control character sequences and automatically handles CRC calculation without CPU intervention. The transmitter can be programmed to send either SYN, DLE-SYN, CRC-SYN, or CRC-DLE-SYN upon underrun and can automatically send the closing DLE-SYN with optional CRC at the end of a programmed message length.

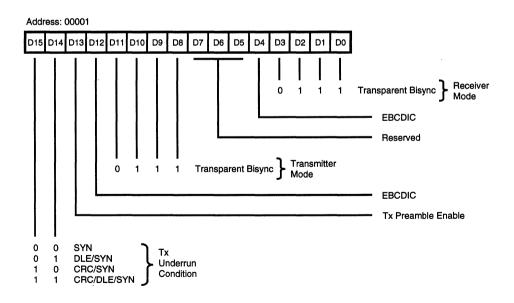

**NBIP Mode.** This mode is identical to async except that the receiver checks for the status of an additional address/ data bit between the parity bit and the stop bit. The value of this bit is FIFO'ed along with the data. This bit is automatically inserted in the transmitter with the value that is FIFO'ed with the transmit data.

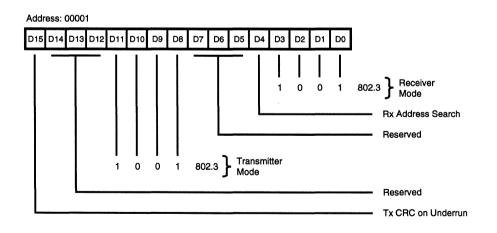

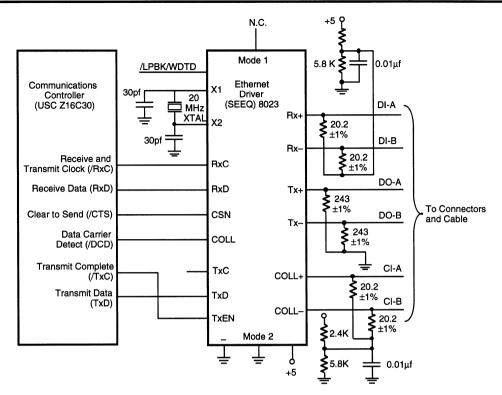

**802.3 Mode.** This mode implements the data format of IEEE 802.3 with 16-bit address compare. In this mode, /DCD and /CTS are used to implement the carrier sense and collision detect interactions with the receiver and transmitter.

# <sup>®</sup>ZiLŒ

ceiver.

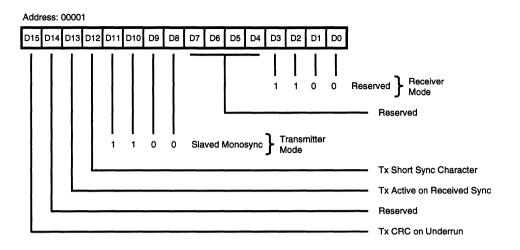

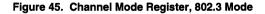

Slaved Monosync Mode. This mode is available only in the transmitter and allows the transmitter (operating as though it were in monosync mode) to send data that is byte-synchronous to the data being received by the re-

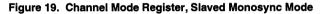

HDLC Loop Mode. This mode is also available only in the transmitter and allows the USC to be used in an HDLC loop configuration. In this mode, the receiver is programmed to operate in HDLC mode so that the transmitter echoes received messages. Upon receipt of a particular bit pattern (actually a sequence of seven consecutive ones) the transmitter breaks the loop and inserts its own frame(s).

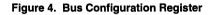

## **Data Encoding**

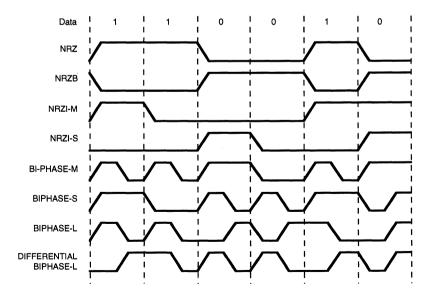

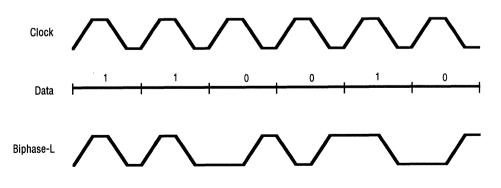

The USC may be programmed to encode and decode the serial data in any of eight different ways as shown in Figure 5. The transmitter encoding method is selected independently of the receiver decoding method.

**NRZ.** In NRZ, a 1 is represented by a High level for the duration of the bit cell and a 0 is represented by a Low level for the duration of the bit cell.

NRZB. Data is inverted from NRZ.

**NRZI-Mark.** In NRZI-Mark, a 1 is represented by a transition at the beginning of the bit cell. That is, the level present in the preceding bit cell is reversed. A 0 is represented by the absence of a transition at the beginning of the bit cell.

**NRZI-Space.** In NRZI-Space, a 1 is represented by the absence of a transition at the beginning of the bit cell. That is, the level present in the preceding bit cell is maintained. A 0 is represented by a transition at the beginning of the bit cell.

**Biphase-Mark.** In Biphase-Mark, a 1 is represented by a transition at the beginning of the bit cell and another transition at the center of the bit cell. A 0 is represented by a transition at the beginning of the bit cell only.

**Biphase-Space.** In Biphase-Space, a 1 is represented by a transition at the beginning of the bit cell only. A 0 is represented by a transition at the beginning of the bit cell and another transition at the center of the bit cell.

**Biphase-Level.** In Biphase-Level, a 1 is represented by a High during the first half of the bit cell and a Low during the second half of the bit cell. A 0 is represented by a Low during the first half of the bit cell and a High during the second half of the bit cell.

# FUNCTIONAL DESCRIPTION (Continued)

**Differential Biphase-Level.** In Differential Biphase-Level, a 1 is represented by a transition at the center of the bit cell, with the opposite polarity from the transition at the center of the preceding bit cell. A 0 is represented by a transition at the center of the bit cell with the same polarity as the transition at the center of the preceding bit cell. In both cases there may be transitions at the beginning of the bit cell to set up the level required to make the correct center transition.

### **Character Counters**

Each channel in the USC contains a 16-bit character counter for both receiver and transmitter. The receive character counter may be preset either under software control or automatically at the beginning of a receive message. The counter decrements with each receive character and at the end of the receive message the current value in the counter is automatically loaded into a four-deep FIFO. This allows DMA transfer of data to proceed without CPU intervention at the end of a received message, as the values in the FIFO allow the CPU to determine message boundaries in memory. Similarly, the transmit character counter is loaded either under software control or automatically at the beginning of a transmit message. The counter is decremented with each write to the transmit FIFO. When the counter has decremented to zero, and that byte is sent, the transmitter automatically terminates the message in the appropriate fashion (usually CRC and the closing flag or sync character) without requiring CPU intervention.

## **Baud Rate Generators**

Each channel in the USC contains two baud rate generators. Each generator consists of a 16-bit time constant register and a 16-bit down counter. In operation, the counter decrements with each baud rate generator clock, with the time constant automatically reloaded when the count reaches zero. The output of the baud rate generator toggles when the counter reaches a count of one-half of the time constant and again when the counter reaches zero. A new time constant may be written at any time but the new value will not take effect until the next load of the counter. The outputs of both baud rate generators are sent to the clock multiplexer for use internally or externally. The baud rate generator output frequency is related to the baud rate generator input clock frequency by the following formula:

Output frequency = Input frequency/(time constant + 1)

This allows an output frequency in the range of 1 to 1/65536 of the input frequency, inclusive.

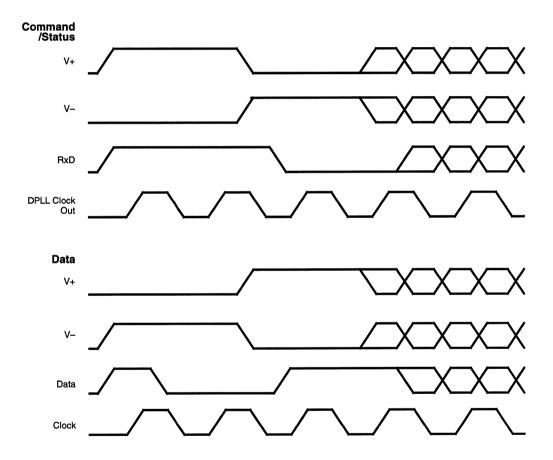

## **Digital Phase-Locked Loop**

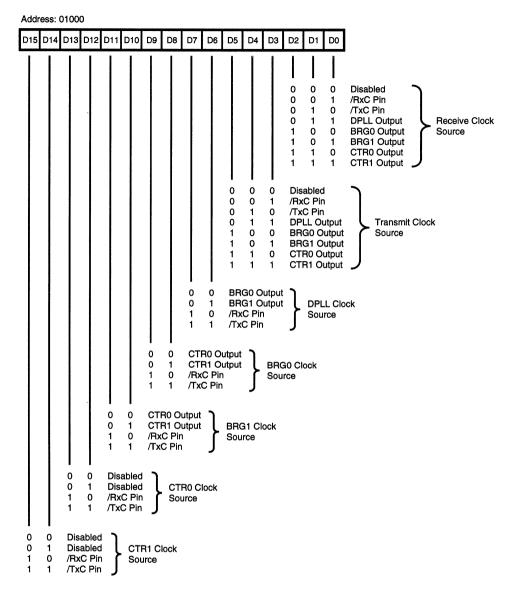

Each channel in the USC contains a Digital Phase-Locked Loop (DPLL) to recover clock information from a data stream with NRZI or Biphase encoding. The DPLL is driven by a clock that is nominally 8, 16 or 32 times the receive data rate. The DPLL uses this clock, along the data stream, to construct a clock for the data. This clock may then be routed to the receiver, transmitter, or both, or to a pin for use externally. In all modes, the DPLL counts the input clock to create nominal bit times. As the clock is counted, the DPLL watches the incoming data stream for transitions. Whenever a transition is detected, the DPLL makes a count adjustment (during the next counting cycle), to produce an output clock which tracks the incoming bit cells. The DPLL provides properly phased transmit and receive clocks to the clock multiplexer.

#### Counters

Each channel contains two 5-bit counters, which are programmed to divide an input clock by 4, 8, 16 or 32. The inputs of these two counters are sent to the clock multiplexer. The counters are used as prescalers for the baud rate generators, or to provide a stable transmit clock from a common source when the DPLL is providing the receive clock.

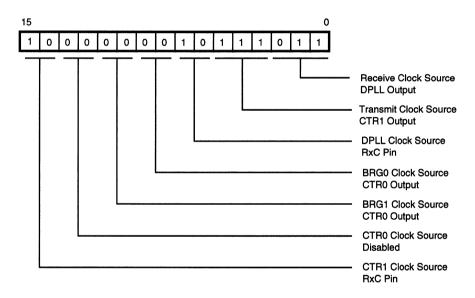

## **Clock Multiplexer**

The clock multiplexer in each channel selects the clock source for the various blocks in the channel and selects an internal clock signal to potentially be sent to either the /RxC or /TxC pin.

## **Test Modes**

The USC can be programmed for local loopback or auto echo operation. In local loopback, the output of the transmitter is internally routed to the input of the receiver. This allows testing of the USC data paths without any external logic. Auto echo connects the RxD pin directly to the TxD pin. This is useful for testing serial links external to the USC.

## **I/O INTERFACE CAPABILITIES**

The USC offers the choice of polling, interrupt (vectored or non-vectored) and block transfer modes to transfer data, status and control information to and from the CPU.

## Polling

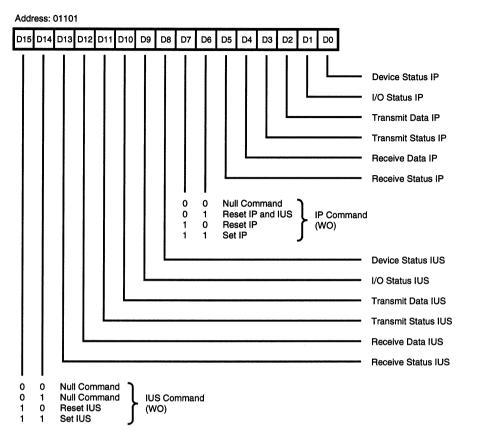

All interrupts are disabled. The registers in the USC are automatically updated to reflect current status. The CPU polls the Daisy Chain Control Register (DCCR) to determine status changes and then reads the appropriate status register to find and respond to the change in status. USC status bits are grouped according to function to simplify this software action.

### Interrupt

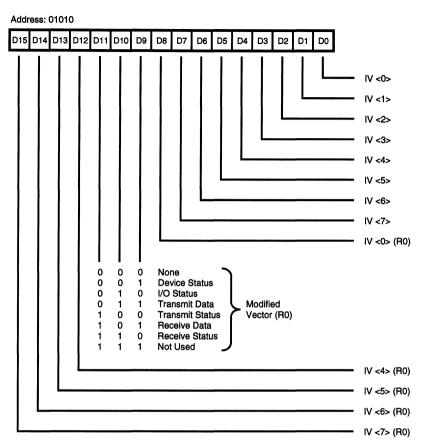

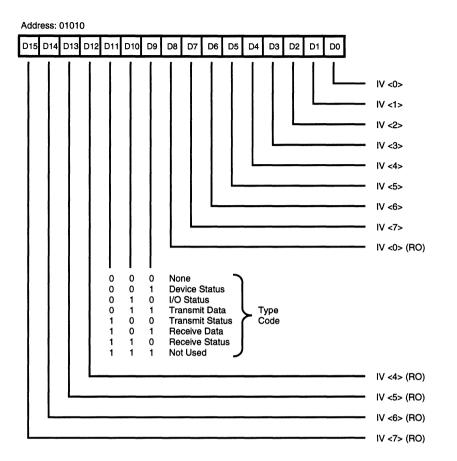

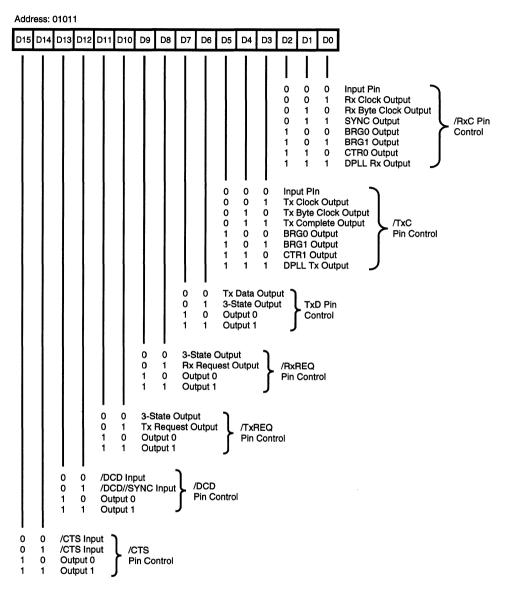

When a USC responds to an interrupt acknowledge from the CPU, an interrupt vector may be placed on the data bus. This vector is held in the Interrupt Vector Register (IVR). To speed interrupt response time, the USC modifies three bits in this vector to indicate which type of interrupt is being requested.

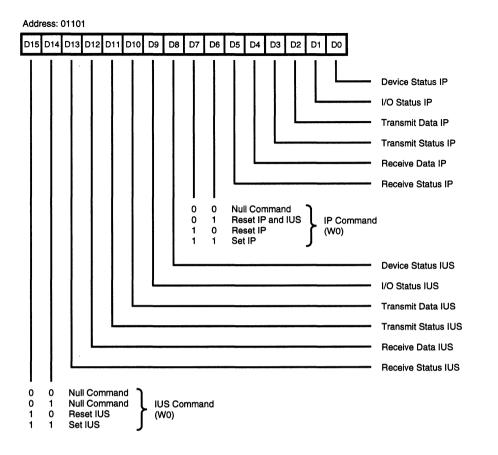

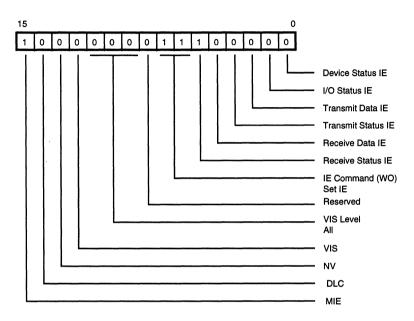

Each of the six sources of interrupts in each channel of the USC (Receive Status, Receive Data, Transmit Status, Transmit Data, I/O Status and Device Status) has three bits associated with the interrupt source: Interrupt Pending (IP), Interrupt-Under-Service (IUS) and Interrupt Enable (IE). If the IE bit for a given source is set, that source can request interrupts. Note that individual sources within the six groups also have interrupt enable bits which are set for the particular source. In addition, there is a Master Interrupt Enable (MIE) bit in each channel which globally enables or disables interrupts within the channel.

The other two bits are related to the interrupt priority chain. A channel in the USC may request an interrupt only when no higher priority interrupt source is requesting one, e.g., when IEI is High for the channel. In this case the channel activates the /INT signal. The CPU then responds with an interrupt acknowledge cycle, and the interrupting channel places a vector on the data bus.

In the USC, the IP bit signals that an interrupt request is being serviced. If an IUS is set, all interrupt sources of lower priority within the channel and external to the channel are prevented from requesting interrupts. The internal interrupt sources are inhibited by the state of the internal daisy chain, while lower priority devices are inhibited by the IEO output of the channel being pulled Low and propagated to subsequent peripherals. An IUS bit is set during an interrupt acknowledge cycle if there are no higher priority devices requesting interrupts.

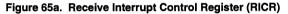

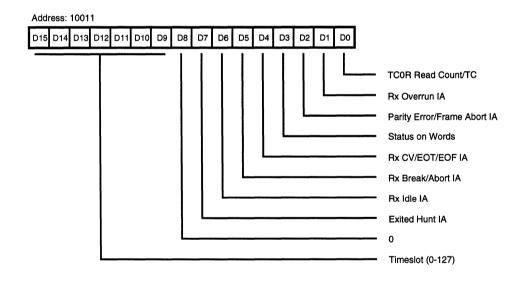

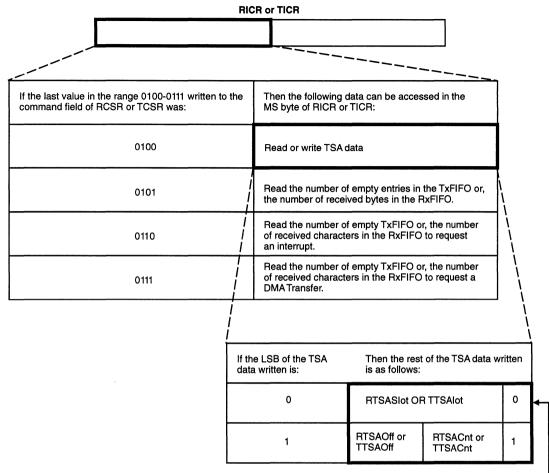

There are six sources of interrupt in each channel: Receive Status, Receive Data, Transmit Status, Transmit Data, I/O Status and Device Status, prioritized in that order within the channel. There are six sources of Receive Status interrupt, each individually enabled: exited hunt, idle line, break/ abort, code violation/end-of-transmission/end-of-frame, parity error and overrun error. The Receive Data interrupt is generated whenever the receive FIFO fills with data beyond the level programmed in the Receive Interrupt Control Register (RICR).

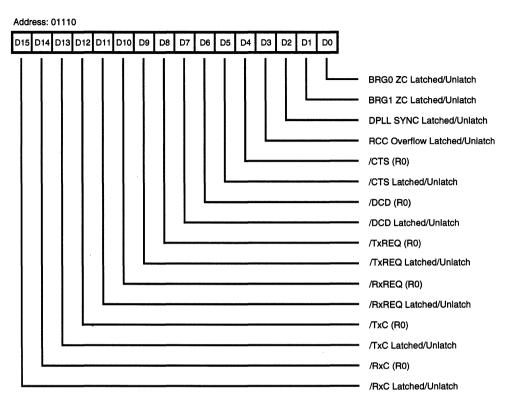

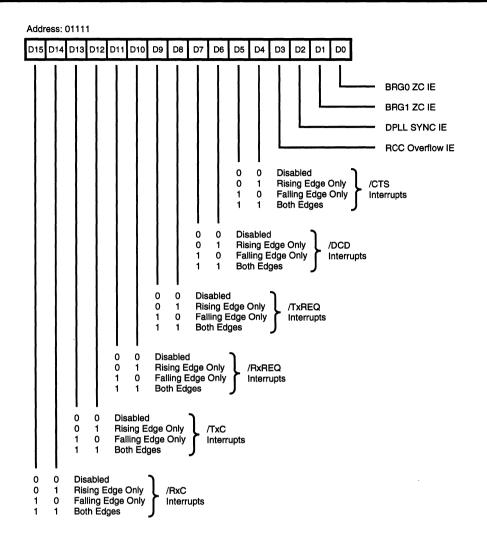

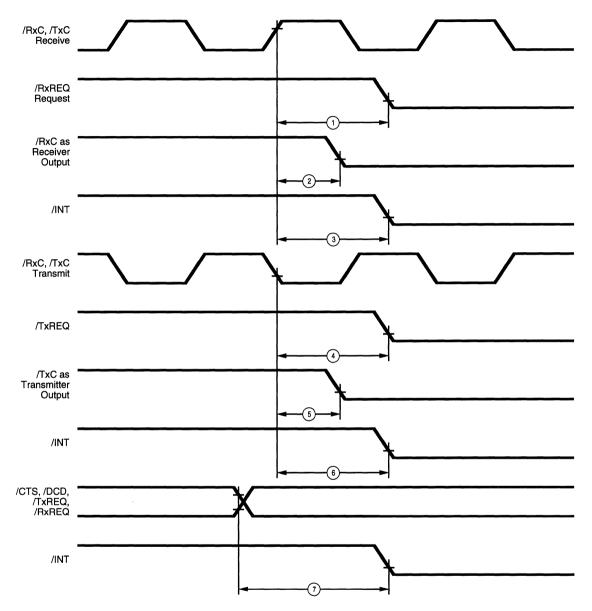

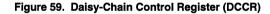

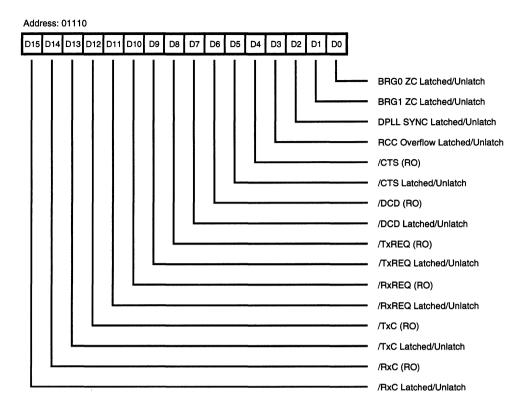

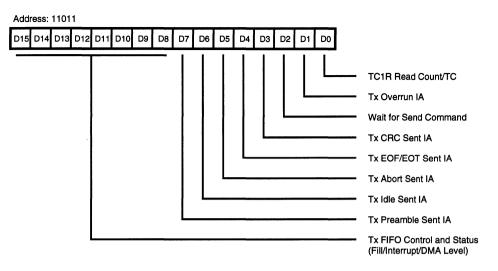

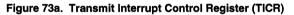

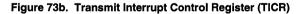

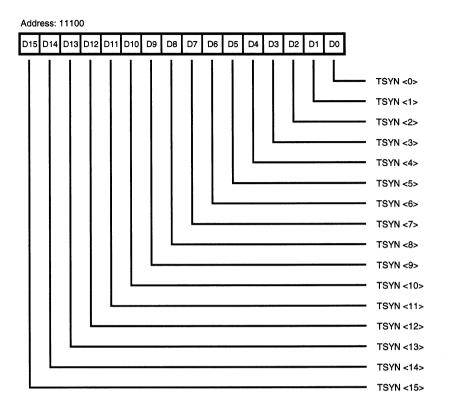

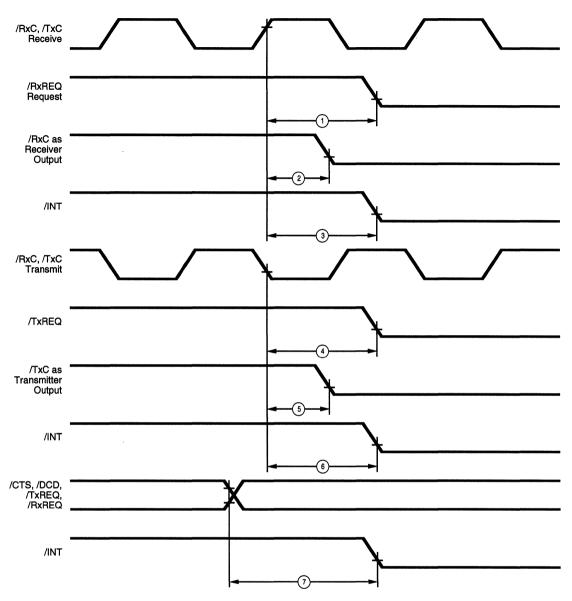

There are six sources of Transmit Status interrupt, each individually enabled: preamble sent, idle line sent, abort sent, end-of-frame/end-of-transmission sent, CRC sent and underrun error. The Transmit Data interrupt is generated whenever the transmit FIFO empties below the level programmed in the Transmit Interrupt Control Register (TICR). The I/O Status interrupt serves to report transitions on any of six pins. Interrupts are generated on either or both edges with separate selection and enables for each pin. The pins programmed to generate I/O Status interrupts are /RxC, /TxC, /RxREQ, /TxREQ, /DCD and /CTS. These interrupts are independent of the programmed function of the pins. The Device Status interrupt has four separately enabled sources: receive character count FIFO overflow, DPLL sync acquired, BRG1 zero count and BRGO zero count.

#### **Block Transfer Mode**

The USC accommodates block transfers through DMA through the /RxREQ, /TxREQ, /RxACK and /TxACK pins. The /RxREQ signal is activated when the fill level of the receive FIFO exceeds the value programmed in the RICR. The DMA may respond with either a normal bus transaction or by activating the /RxACK pin to read the data directly (fly-by transfer). The /TxREQ signal is activated when the empty level of the transmit FIFO falls below the value programmed in the TICR. The DMA may respond either with a normal bus transaction or by activating the /TxACK pin to write the data directly (fly-by transfer). The /RxACK and /TxACK pin functions for this mode are controlled by the Hardware Configuration Register (HCR). Then using the /RxACK and /TxACK pins to transfer data, no chip select is necessary; these are dedicated strobes for the appropriate FIFO.

## PROGRAMMING

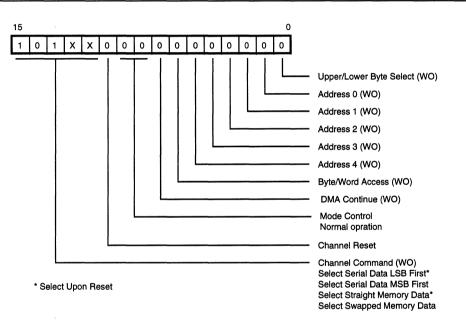

The registers in each USC channel are programmed by the system to configure the channels. Before this can occur, however, the system must program the bus interface by writing to the Bus Configuration Register (BCR). The BCR has no specific address and is only accessible immediately after a hardware reset of the device. The first write to the USC, after a hardware reset, programs the BCR. From that time on the normal channel registers may be accessed. No specific address need be presented to the USC for the BCR write; the USC knows that the first write after a hardware reset is destined for the BCR.

In the multiplexed bus case, all registers are directly addressable through the address latched by /AS at the beginning of a bus transaction. The address is decoded from either AD6-AD0 or AD7-AD1. This is controlled by the Shift Right/Shift Left bit in the BCR. The address maps for these two cases are shown in Table 1. The D//C pin is still used to directly access the receive and transmit data registers (RDR and TDR) in the multiplexed bus; if D//C is High the address latched by /AS is ignored and an access of RDR or TDR is performed.

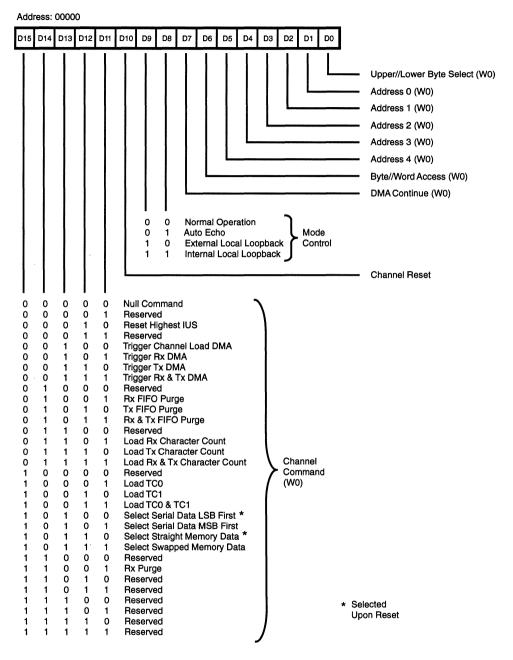

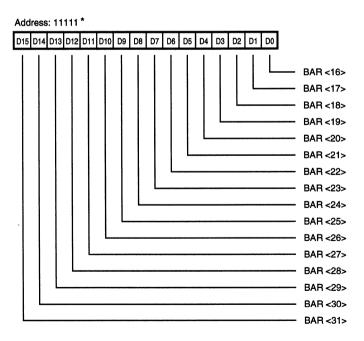

In the non-multiplexed bus case, the registers in each channel are accessed indirectly using the address pointer in the Channel Command/Address Register (CCAR) in each channel. The address of the desired register is first written to the CCAR and then the selected register is accessed; the pointer in the CCAR is automatically cleared after this access. The RDR and TDR are accessed directly using the D//C pin, without disturbing the contents of the pointer in the CCAR.

| Table 1. | Multiplexed | <b>Bus Address</b> | Assignments |

|----------|-------------|--------------------|-------------|

|----------|-------------|--------------------|-------------|

| Address Signal           | Shift Left | Shift Right |

|--------------------------|------------|-------------|

| Byte//Word Access        | AD7        | AD6         |

| Address 4                | AD6        | AD5         |

| Address 3                | AD5        | AD4         |

| Address 2                | AD4        | AD3         |

| Address 1                | AD3        | AD2         |

| Address 0                | AD2        | AD1         |

| Upper//Lower Byte Select | AD1        | AD0         |

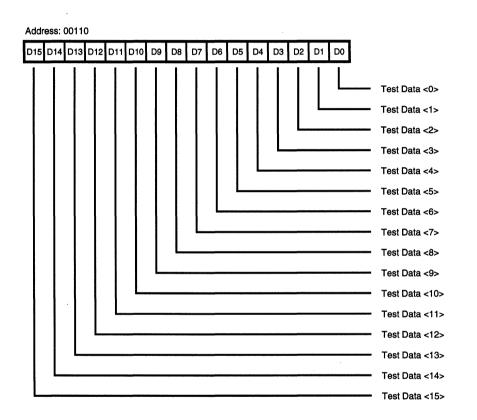

There are two important things to note about the USC. First, the Channel Reset bit in the CCAR places the channel in the reset state. To exit this reset state either a word of all zeros must be written to the CCAR (16-bit bus) or a byte of all zeros must be written to the lower byte of the CCAR (8-bit bus). The second thing to note is that after reset, the transmit and receive clocks are not connected. The first thing that should be done in any initialization sequence is a write to the Clock Mode Control Register (CMCR) to select a clock source for the receiver and transmitter.

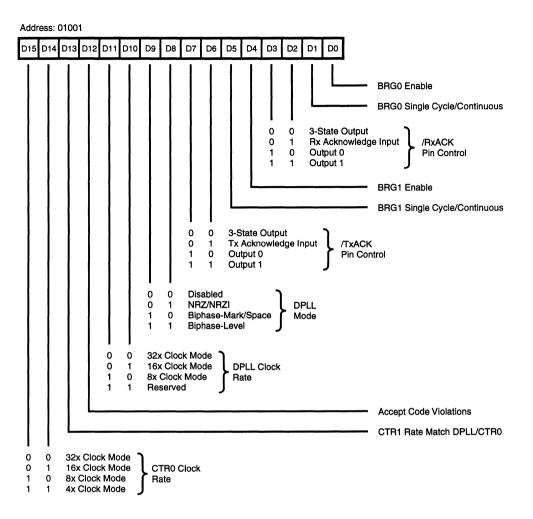

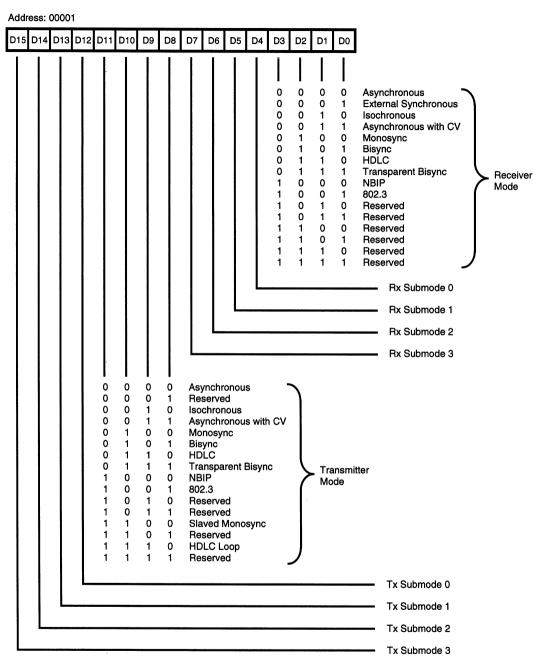

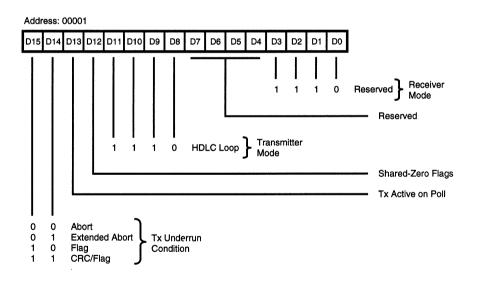

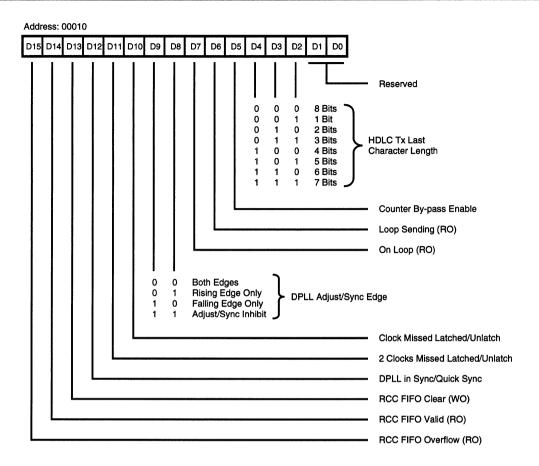

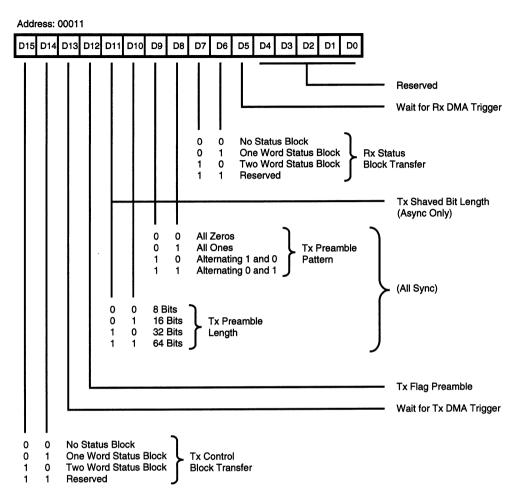

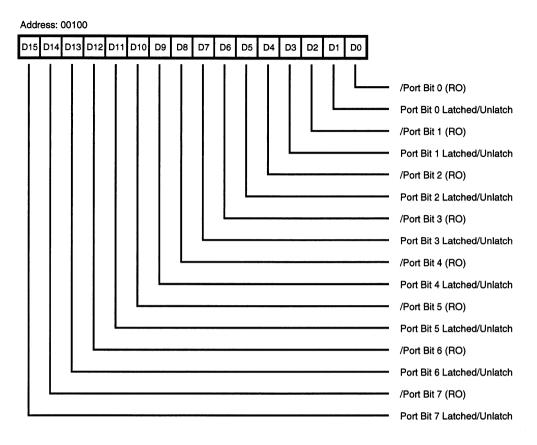

The register addressing is shown in Table 2. and the bit assignments for the registers are shown in Figure 6.

Note:

The presence of one transaction with an /AS active, between reset up to and including the BCR write, chooses a multiplexed type of bus.

| Addres<br>A4-A0                  | S                          |                                                                                                                                   | Address<br>A4-A0        | 3                   |                                                                                             |  |  |

|----------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------|---------------------------------------------------------------------------------------------|--|--|

| 00000                            | CCAR                       | Channel Command/Address Register                                                                                                  | 10010                   | RCSR                | Receive Command/Status Register                                                             |  |  |

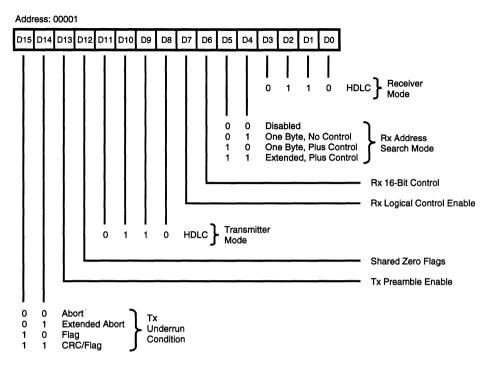

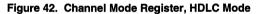

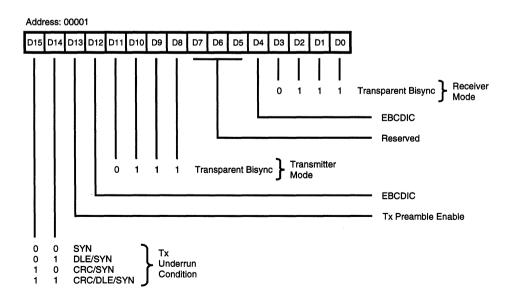

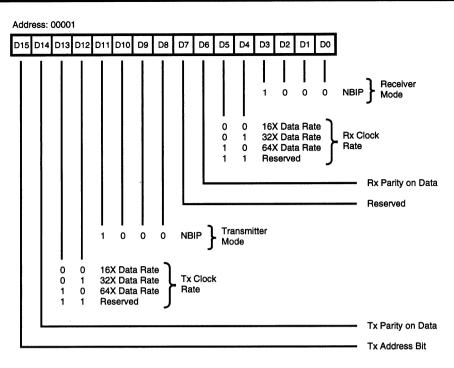

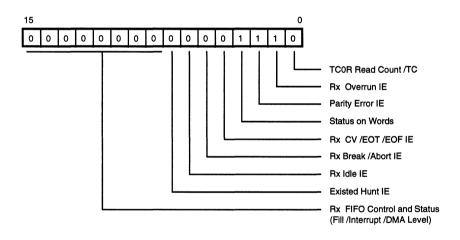

| 00001                            | CMR                        | Channel Mode Register                                                                                                             | 10011                   | RICR                | Receive Interrupt Control Register                                                          |  |  |

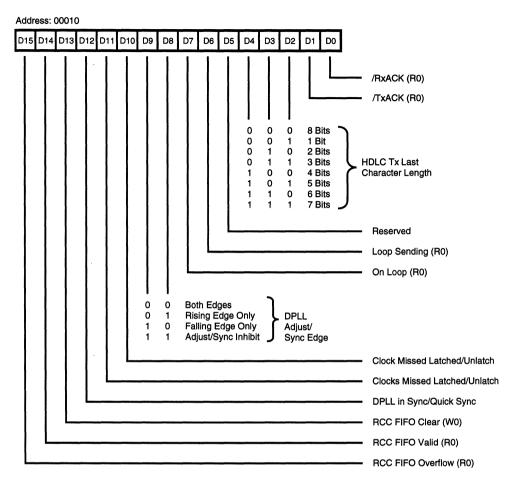

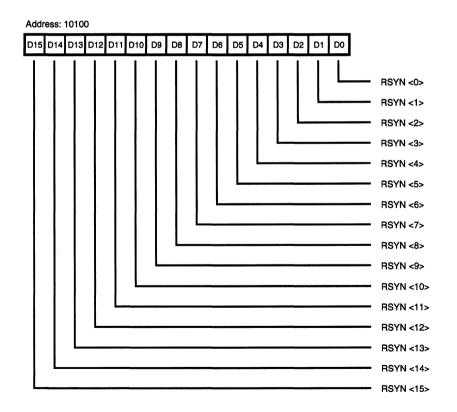

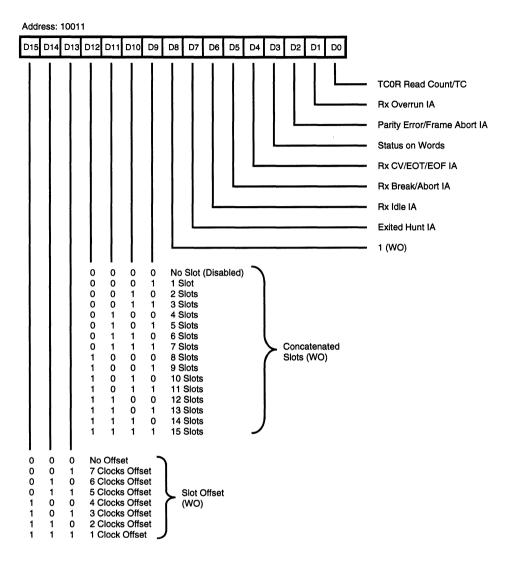

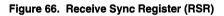

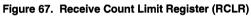

| 00010                            | CCSR                       | Channel Command/Status Register                                                                                                   | 10100                   | RSR                 | Receive Sync Register                                                                       |  |  |

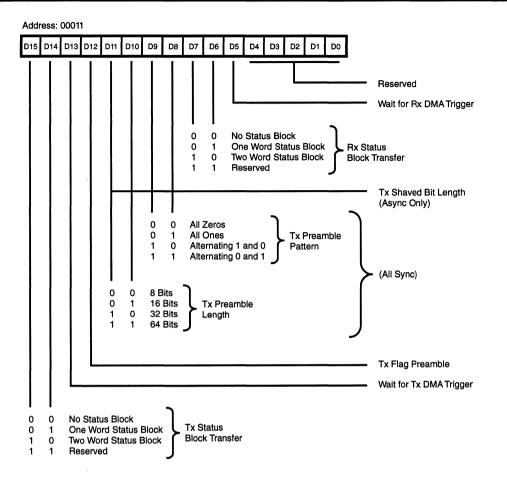

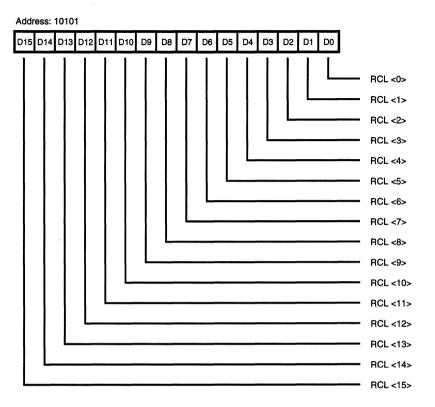

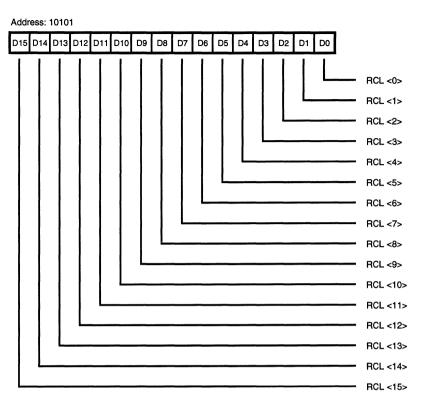

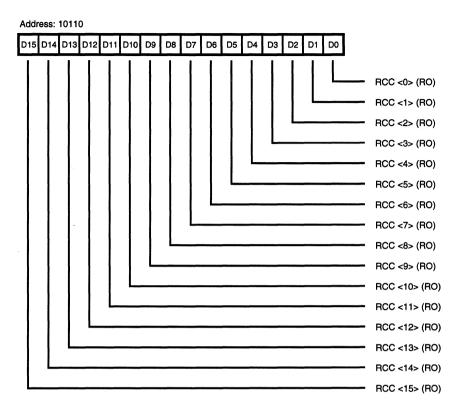

| 00011                            | CCR                        | Channel Control Register                                                                                                          | 10101                   | RCLR                | Receive Count Limit Register                                                                |  |  |

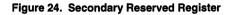

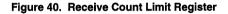

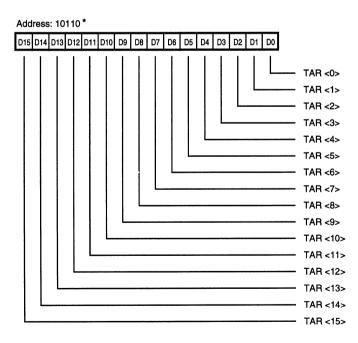

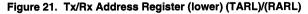

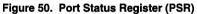

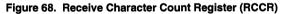

| 00110                            | TMDR                       | Test Mode Data Register                                                                                                           | 10110                   | RCCR                | Receive Character Count Register                                                            |  |  |

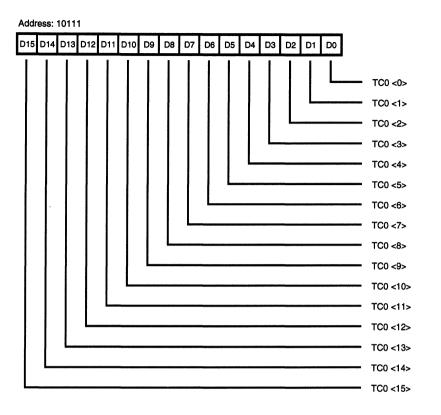

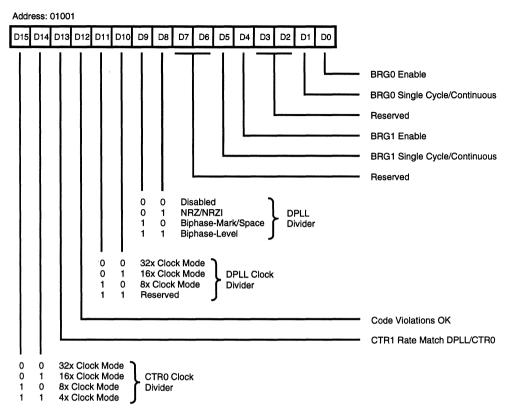

| 00111                            | TMCR                       | Test Mode Control Register                                                                                                        | 10111                   | TCOR                | Time Constant 0 Register                                                                    |  |  |

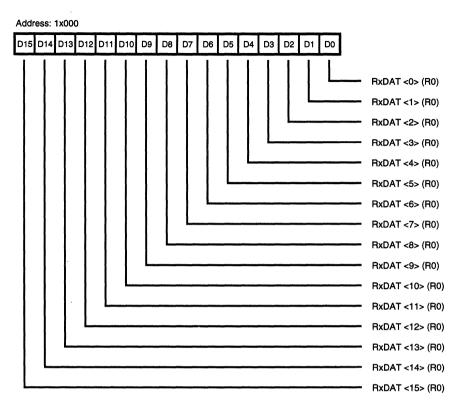

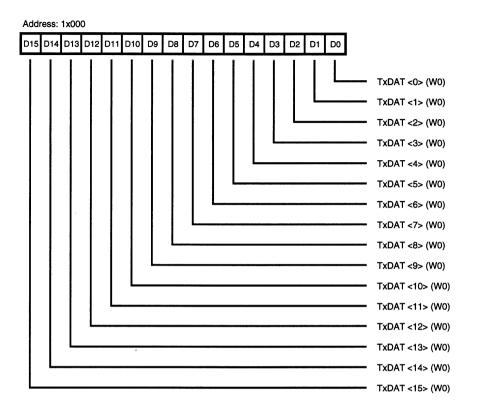

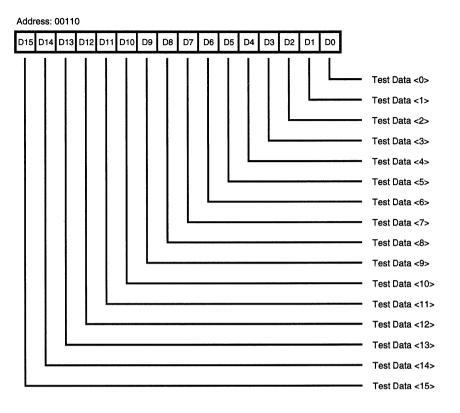

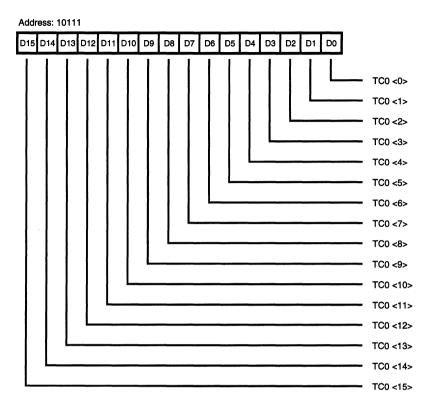

| 01000                            | CMCR                       | Clock Mode Control Register                                                                                                       | 1X000                   | TDR                 | Transmit Data Register (Write Only)                                                         |  |  |

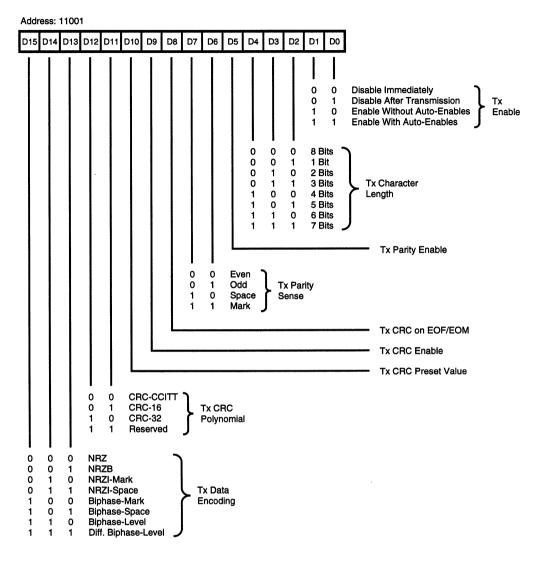

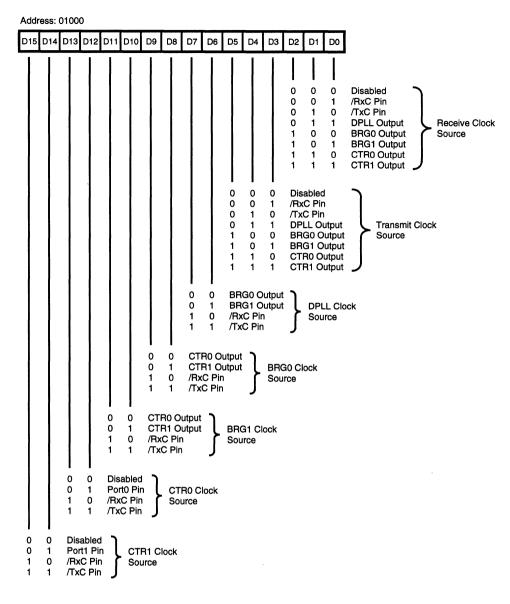

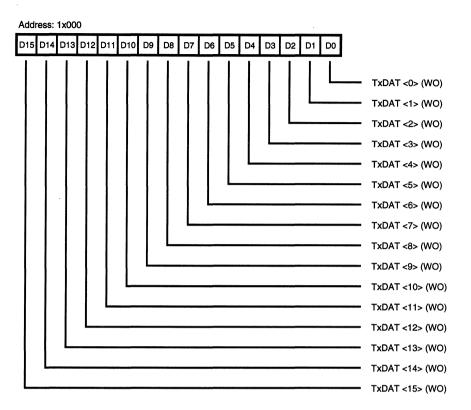

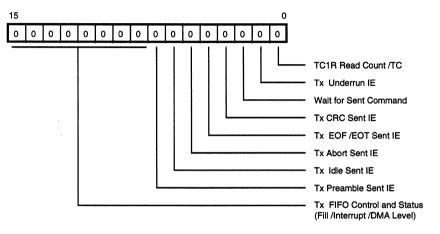

| 01001                            | HCR                        | Hardware Configuration Register                                                                                                   | 11001                   | TMR                 | Transmit Mode Register                                                                      |  |  |

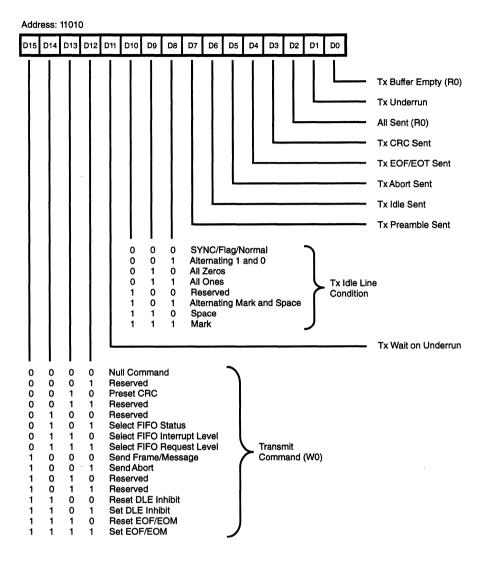

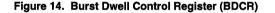

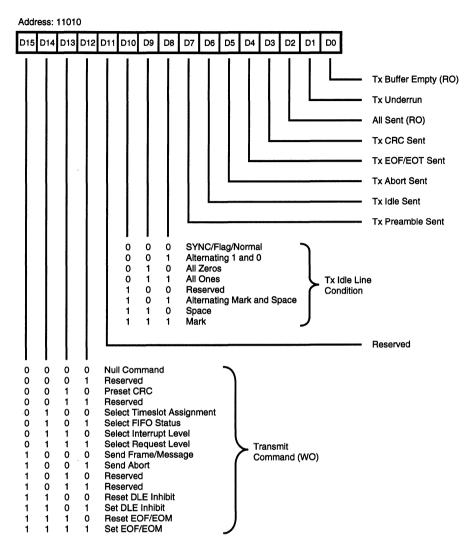

| 01010                            | IVR                        | Interrupt Vector Register                                                                                                         | 11010                   | TCSR                | Transmit Command/Status Register                                                            |  |  |

| 01011                            | IOCR                       | I/O Control Register                                                                                                              | 11011                   | TICR                | Transmit Interrupt Control Register                                                         |  |  |

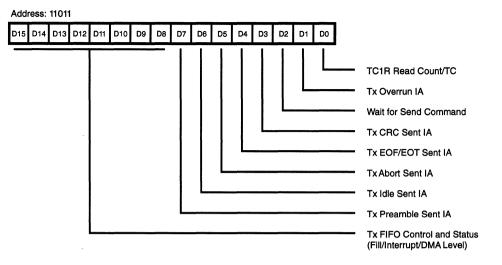

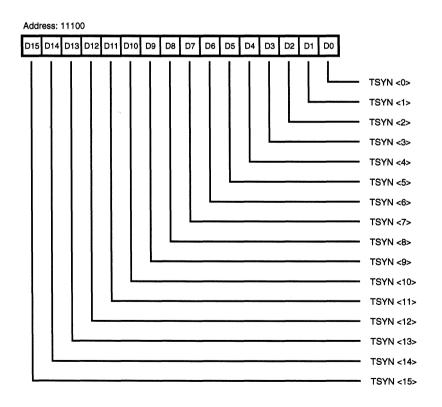

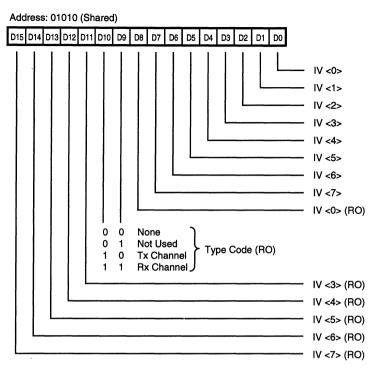

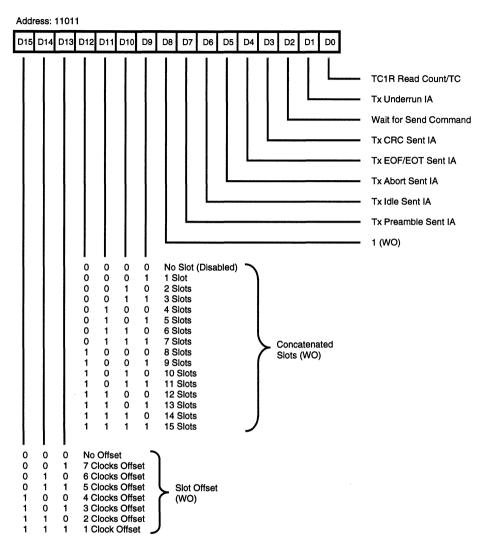

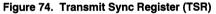

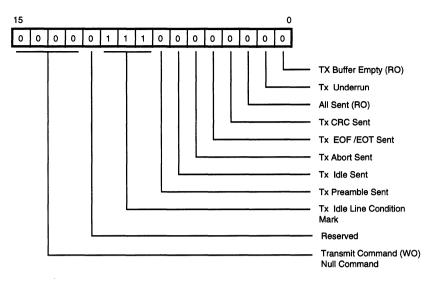

| 01100                            | ICR                        | Interrupt Control Register                                                                                                        | 11100                   | TSR                 | Transmit Sync Register                                                                      |  |  |

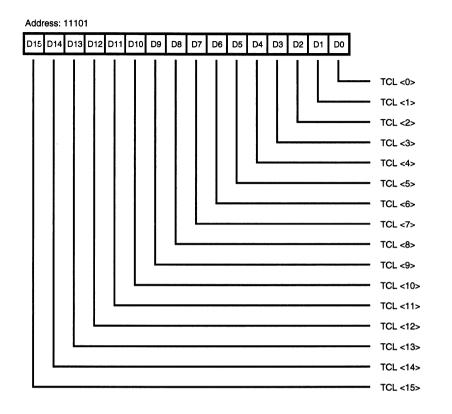

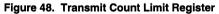

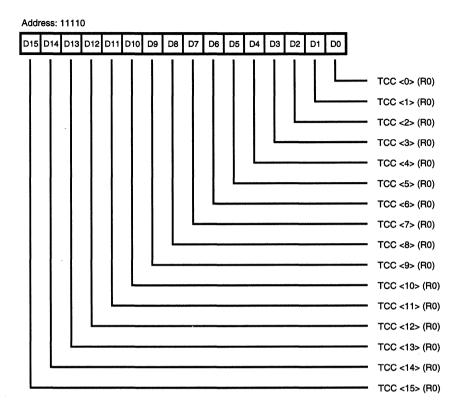

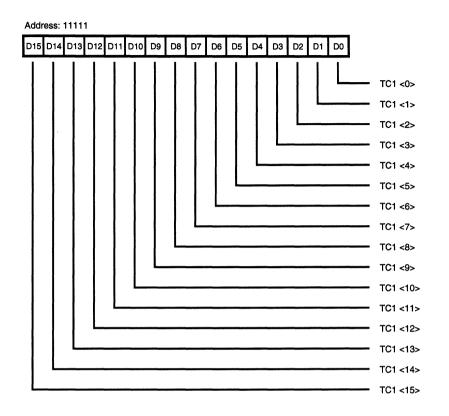

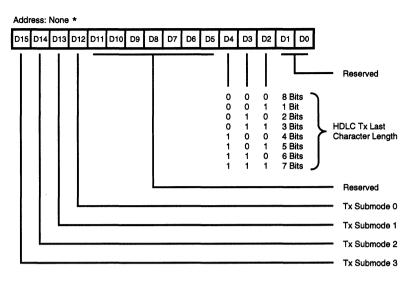

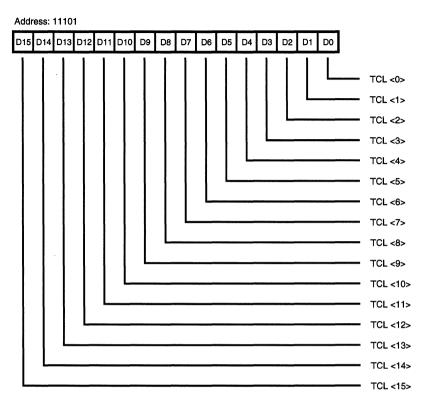

| 01101                            | DCCR                       | Daisy-Chain Control Register                                                                                                      | 11101                   | TCLR                | Transmit Count Limit Register                                                               |  |  |

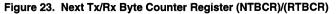

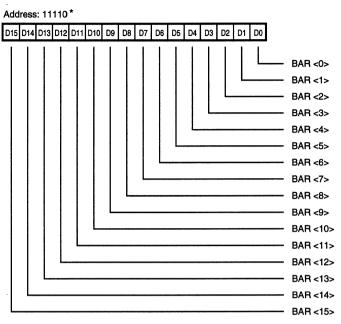

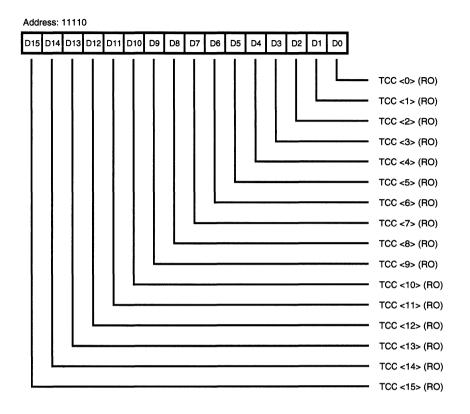

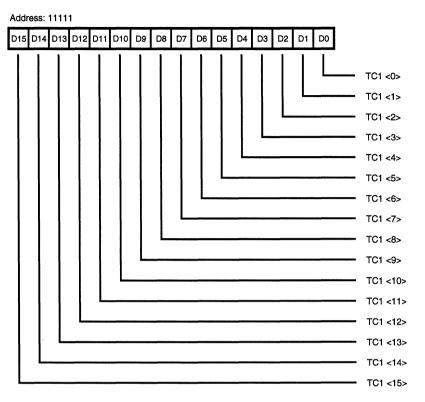

| 01110<br>01111<br>1X000<br>10001 | MISR<br>SICR<br>RDR<br>RMR | Misc Interrupt Status Register<br>Status Interrupt Control Register<br>Receive Data Register (Read Only)<br>Receive Mode Register | 11110<br>11111<br>XXXXX | TCCR<br>TC1R<br>BCR | Transmit Character Count Register<br>Time Constant 1 Register<br>Bus Configuration Register |  |  |

#### Table 2. Register Address List

1

## CONTROL REGISTERS

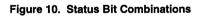

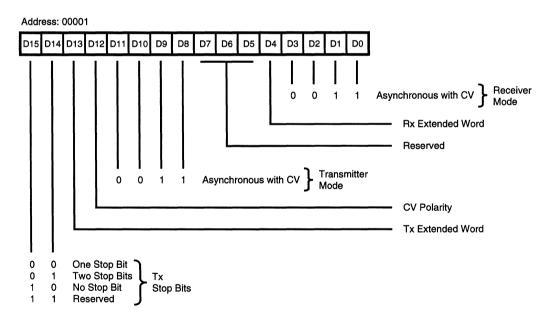

Figure 9. Channel Mode Register, Asynchronous Mode

Figure 10. Channel Mode Register, External Sync Mode

Figure 11. Channel Mode Register, Isochronous Mode

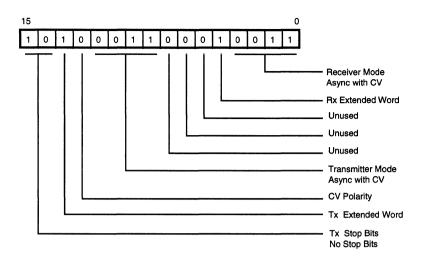

Figure 12. Channel Mode Register, Asynchronous Mode with Code Violation (MIL STD 1553)

Figure 17. Channel Mode Register, NBIP Mode

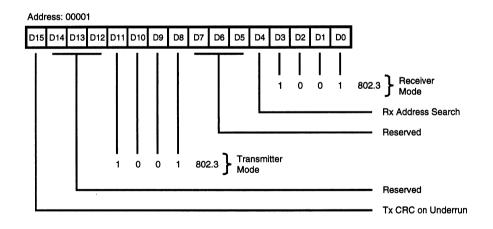

Figure 18. Channel Mode Register, 802.3 Mode

Figure 20. Channel Mode Register, HDLC Loop Mode

Figure 21. Channel Command/Status Register

Figure 22. Channel Control Register

Figure 23. Primary Reserved Register

211 (75

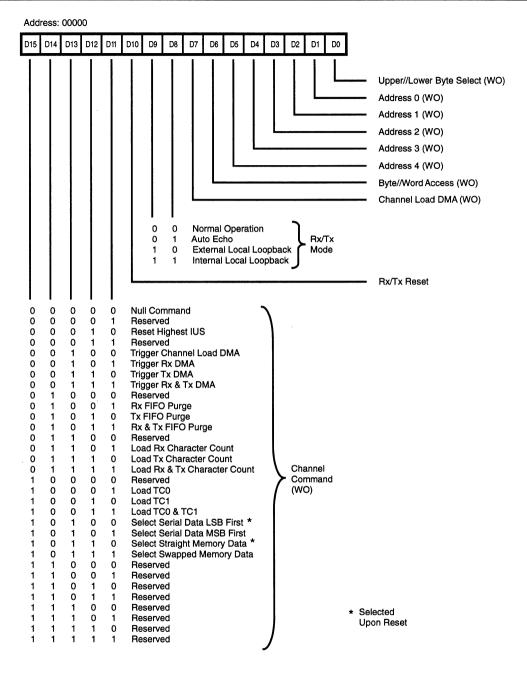

|  | Address: | 00111 |

|--|----------|-------|

|--|----------|-------|

| D15 D14 | D13 | D12 | 2 D11 | D10 | D D9 | D | 8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                               |            |

|---------|-----|-----|-------|-----|------|---|---|----|----|----|----|----|----|----|----|-------------------------------|------------|

|         |     |     |       |     |      |   |   |    |    |    |    |    |    |    |    |                               |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 0  | 0  | 0  | 0  | Null Address                  |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 0  | 0  | 0  | 1  | High Byte of Shifters         |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 0  | 0  | 1  | 0  | CRC Byte 0                    |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 0  | 0  | 1  | 1  | CRC Byte 1                    |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 0  | 1  | 0  | 0  | Rx FIFO (Write)               |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 0  | 1  | 0  | 1  | Clock Multiplexer Outputs     |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 0  | 1  | 1  | 0  | CTR0 and CTR1 Counters        |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 0  | 1  | 1  | 1  | Clock Multiplexer Inputs      |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 1  | 0  | 0  | 0  | DPLL State                    |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 1  | 0  | 0  | 1  | Low Byte of Shifters          |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 1  | 0  | 1  | 0  | CRC Byte 2                    |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 1  | 0  | 1  | 1  | CRC Byte 3                    |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 1  | 1  | 0  | 0  | Tx FIFO (Read)                |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 1  | 1  | 0  | 1  | Reserved                      |            |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 1  | 1  | 1  | 0  | I/O and Device Status Latches | <b>-</b> . |

|         |     |     |       |     |      |   |   |    |    |    | 0  | 1  | 1  | 1  | 1  | Internal Daisy Chain          | Test       |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 0  | 0  | 0  | 0  | Reserved                      | Registe    |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 0  | 0  | 0  | 1  | Reserved                      | Addres     |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 0  | 0  | 1  | 0  | Reserved                      |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 0  | 0  | 1  | 1  | Reserved                      |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 0  | 1  | 0  | 0  | Reserved                      |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 0  | 1  | 0  | 1  | Reserved                      |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 0  | 1  | 1  | 0  | Reserved                      |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 0  | 1  | 1  | 1  | Reserved                      |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 1  | 0  | 0  | 0  | 4044H                         |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 1  | 0  | 0  | 1  | 4044H                         |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 1  | 0  | 1  | 0  | 4044H                         |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 1  | 0  | 1  | 1  | 4044H                         |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 1  | 1  | 0  | 0  | 4044H                         |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 1  | 1  | 0  | 1  | 4044H                         |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 1  | 1  | 1  | Ó  | 4044H                         |            |

|         |     |     |       |     |      |   |   |    |    |    | 1  | 1  | 1  | 1  | 1  | 4044H                         |            |

|         |     |     |       |     |      |   |   |    |    |    |    |    |    |    |    | )                             |            |

|         |     |     |       | •   |      |   |   |    |    |    |    |    |    |    |    |                               |            |

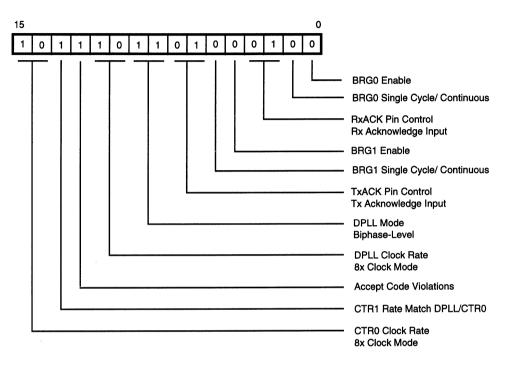

Figure 27. Clock Mode Control Register

í

Figure 28. Hardware Configuration Register

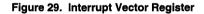

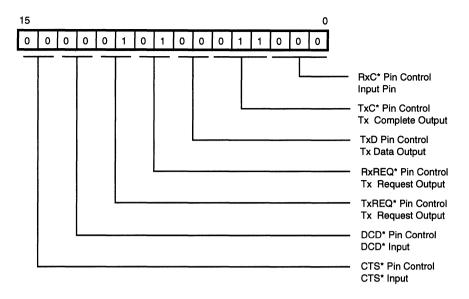

Figure 30. I/O Control Register

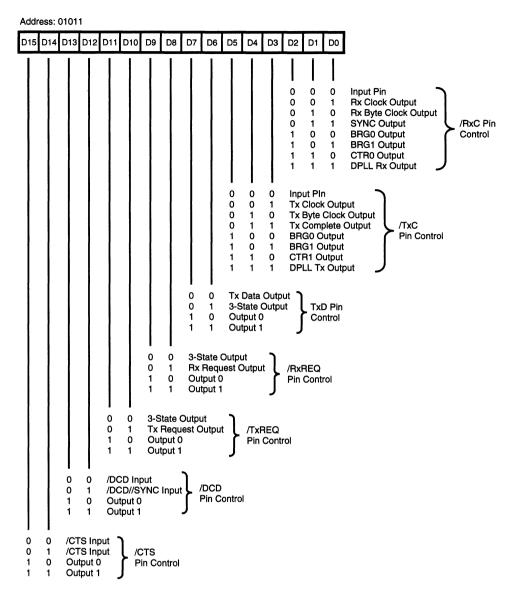

Figure 31. Interrupt Control Register

Figure 32. Daisy-Chain Control Register

Figure 33. Miscellaneous Interrupt Status Register

Figure 34. Status Interrupt Control Register

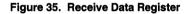

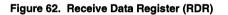

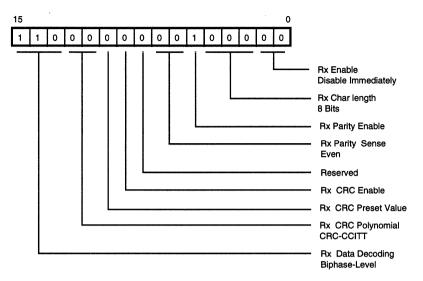

Figure 36. Receive Mode Register

Figure 41. Receive Character Count Register

í

Figure 43. Transmit Data Register

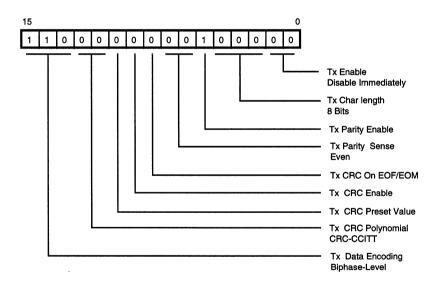

Figure 44. Transmit Mode Register

Figure 45. Transmit Command/Status Register

Figure 46. Transmit Interrupt Control Register

í

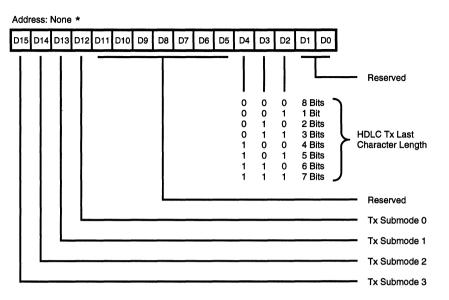

Figure 49. Transmit Character Count Register

## ⊗ Zilas

1

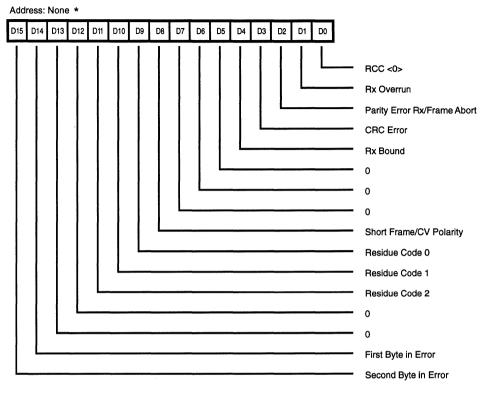

| Image: Second secon | CC <0><br>x Overrun<br>arity Error/Frame Abort<br>RC Error<br>x CV/EOT/EOF<br>CC FIFO Overflow<br>hort Frame/CV Polarity<br>esidue Code 1<br>esidue Code 1<br>esidue Code 2<br>rst Byte in Error<br>econd Byte in Error |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

\* Refer to Figure 22 (Channel Control Register) Bits 6-7 for Access Method

\* Refer to Figure 22 (Channel Control Register) Bits15-14 for Access Method

\* Must be programmed as zero.

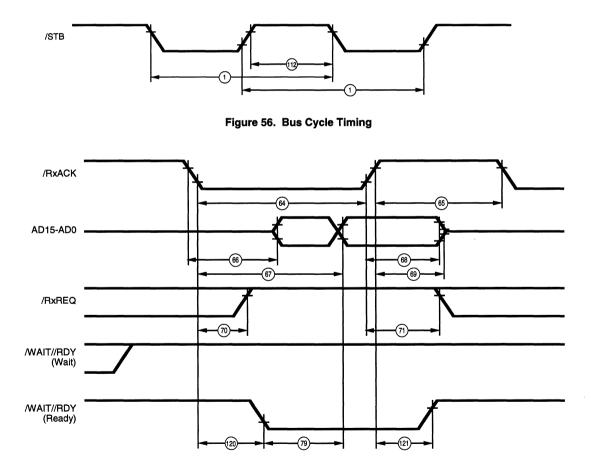

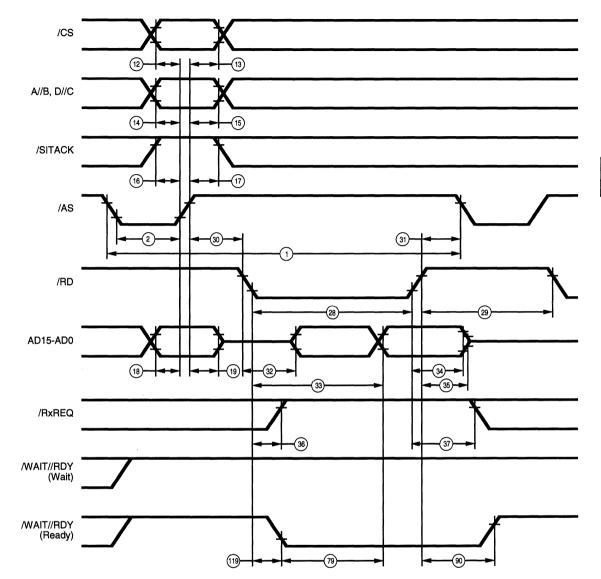

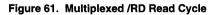

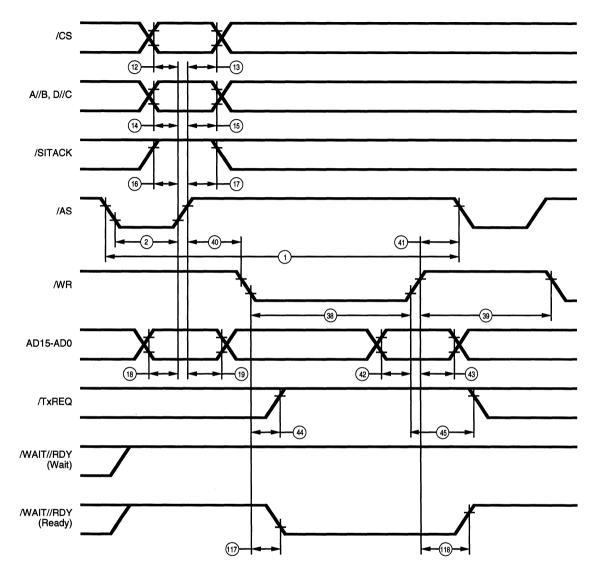

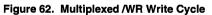

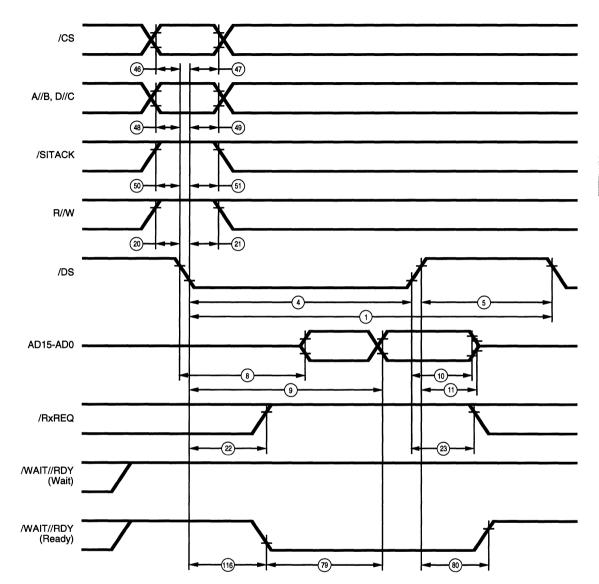

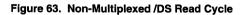

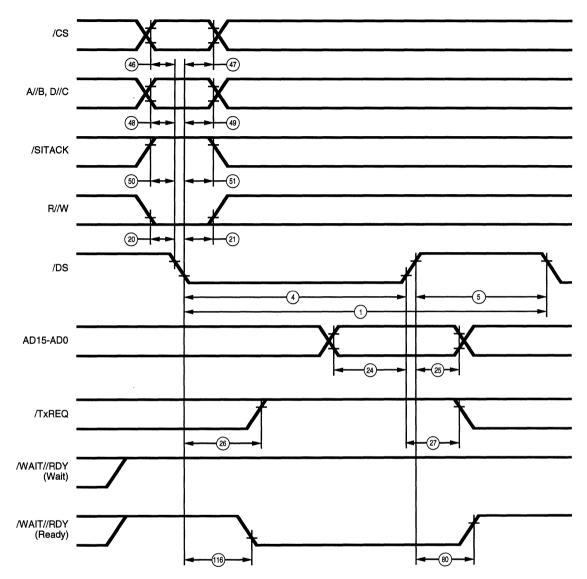

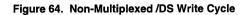

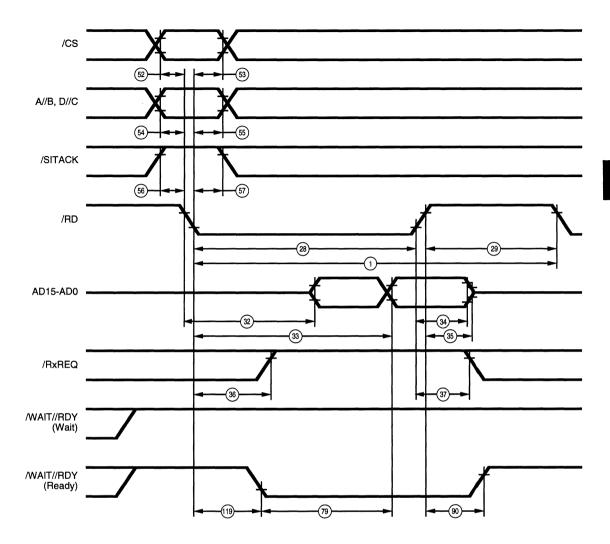

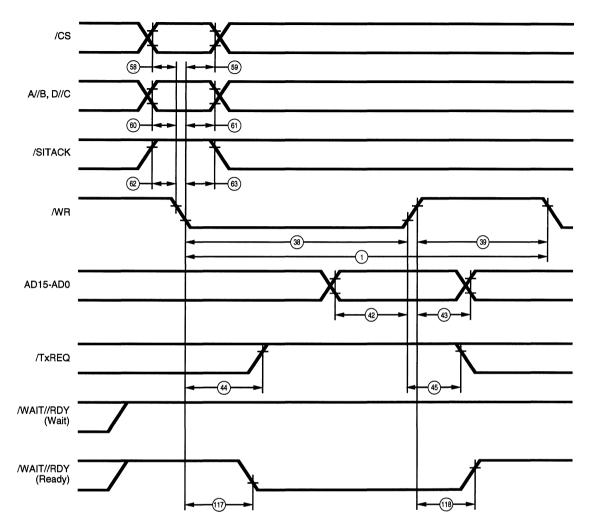

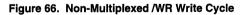

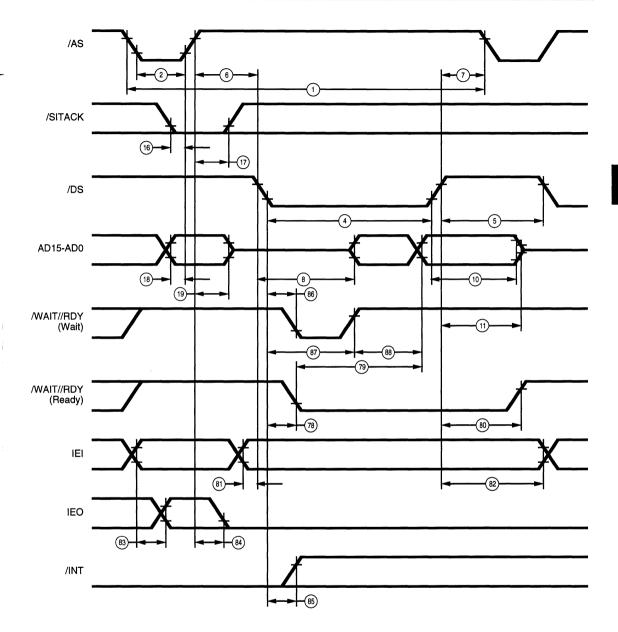

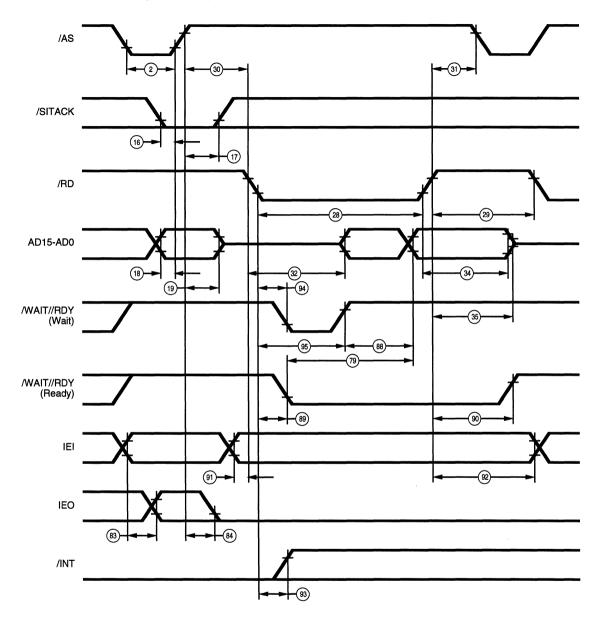

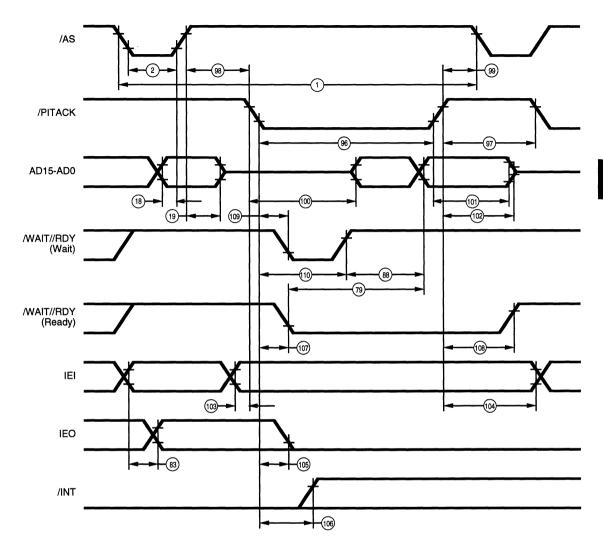

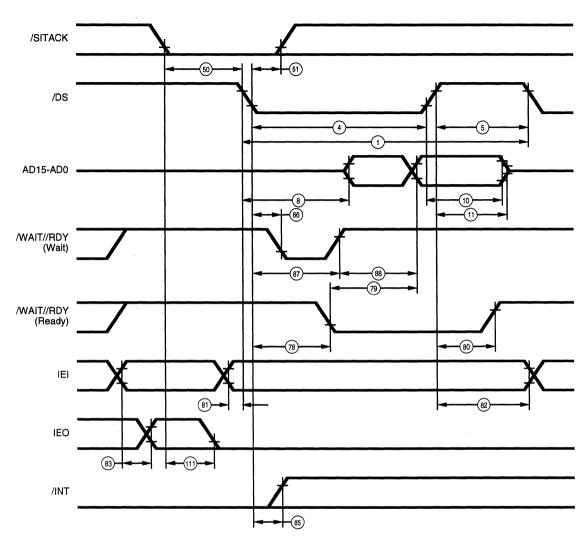

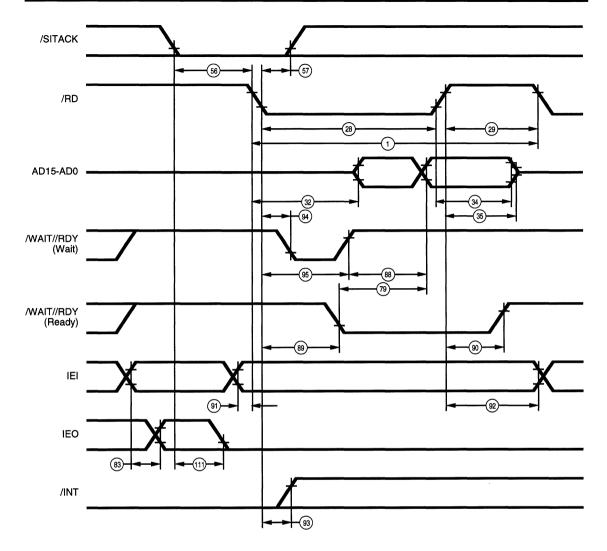

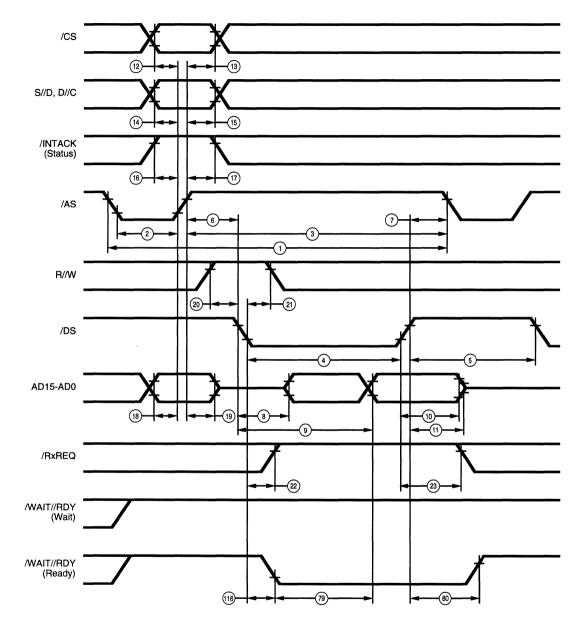

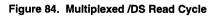

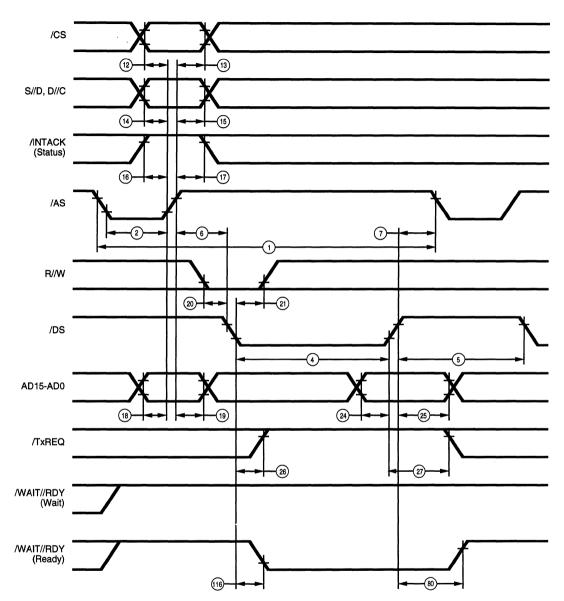

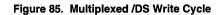

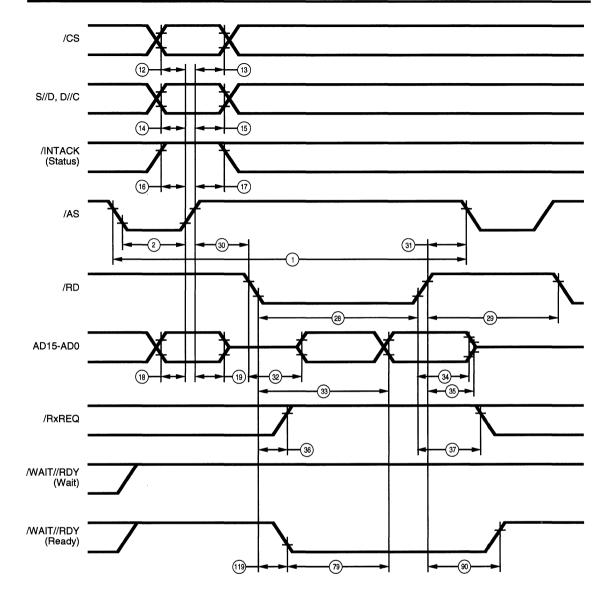

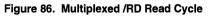

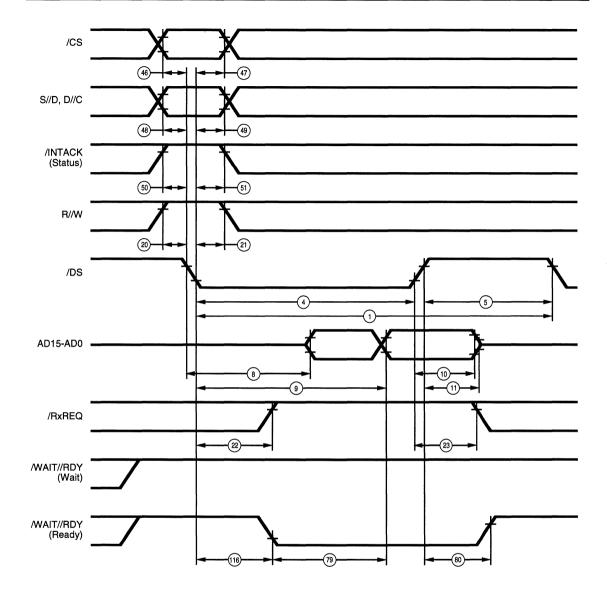

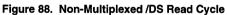

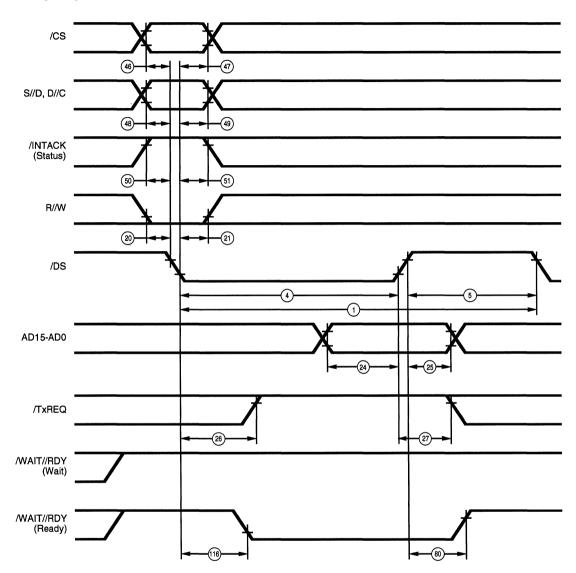

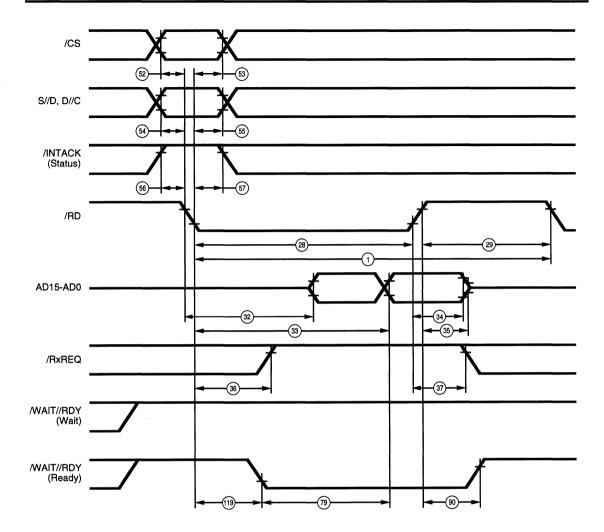

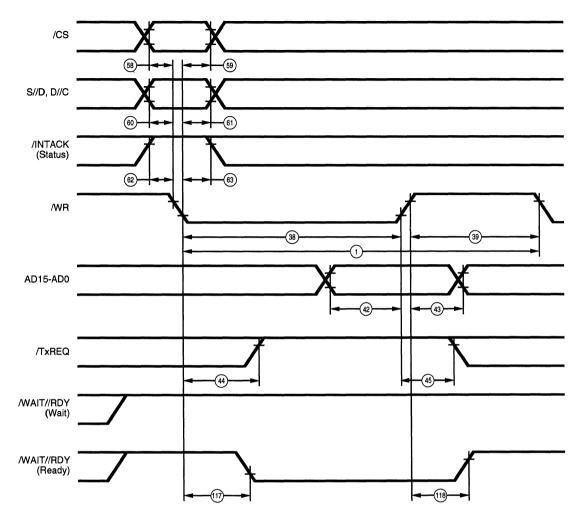

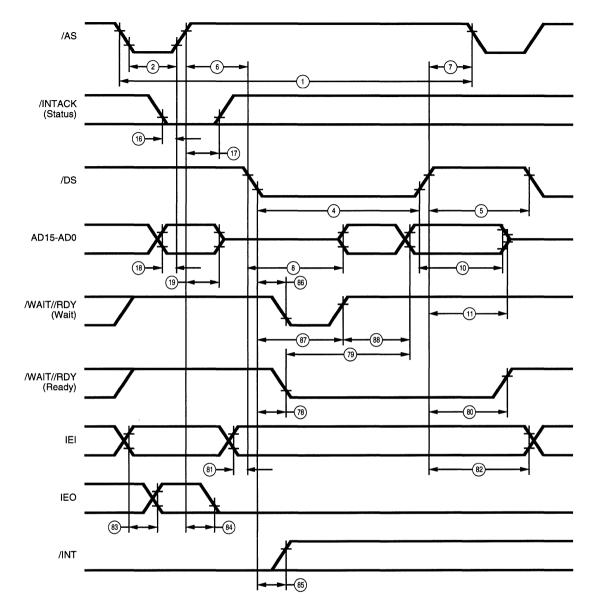

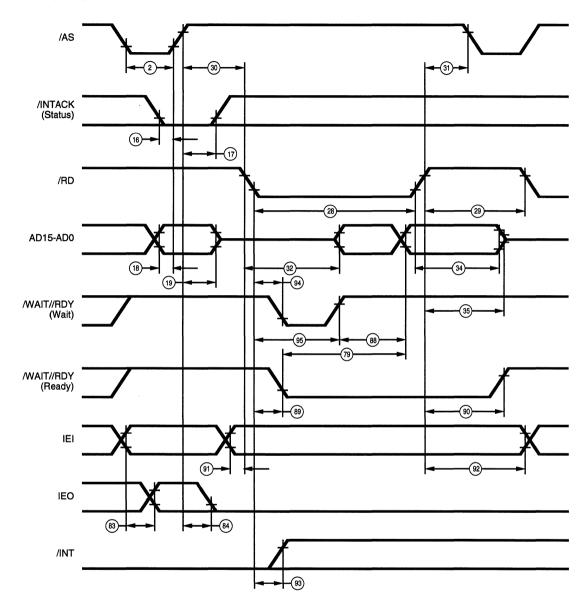

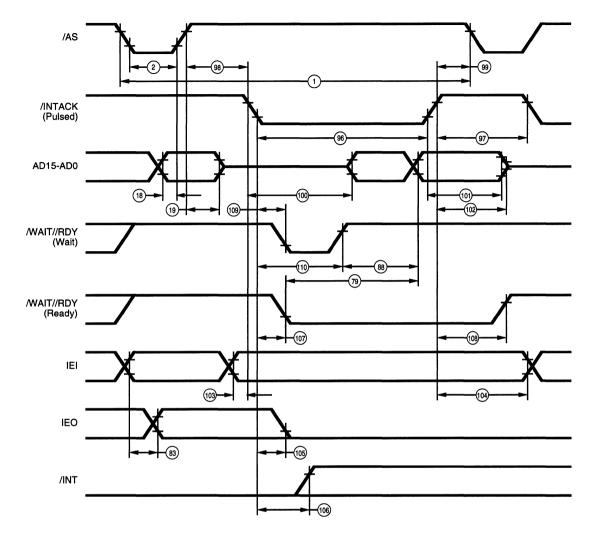

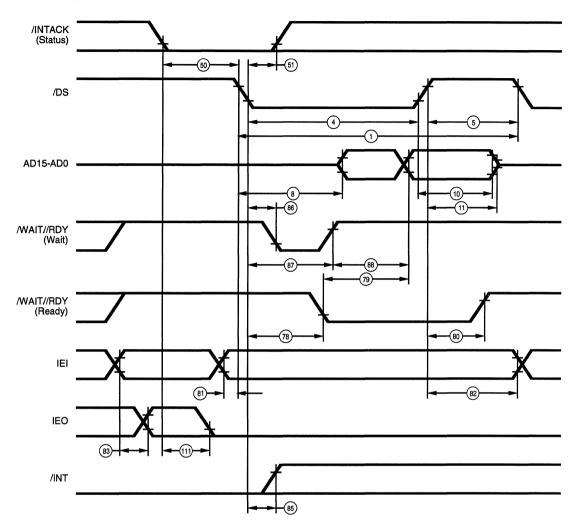

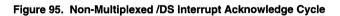

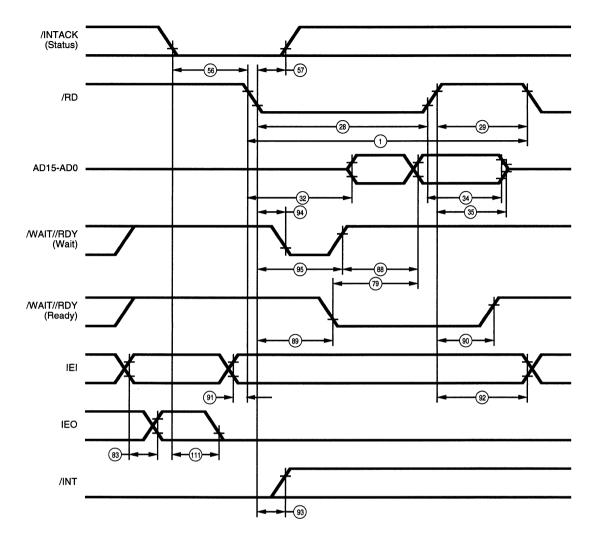

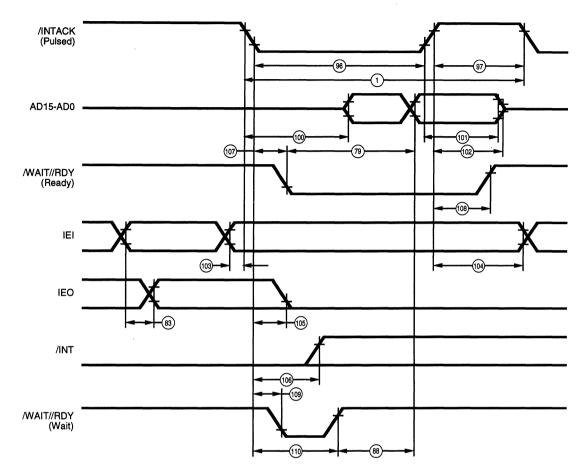

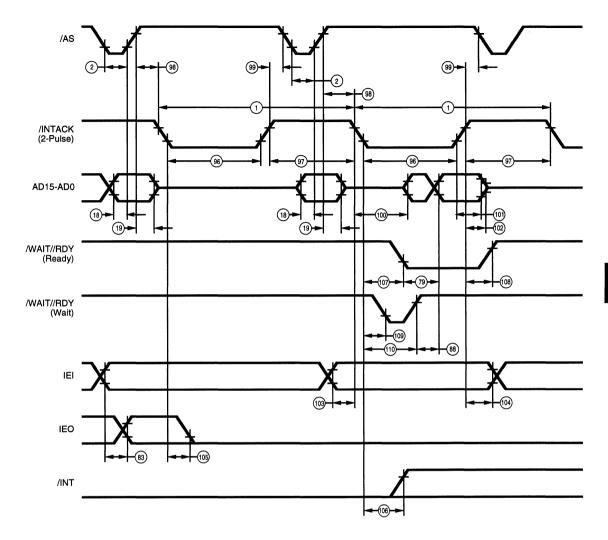

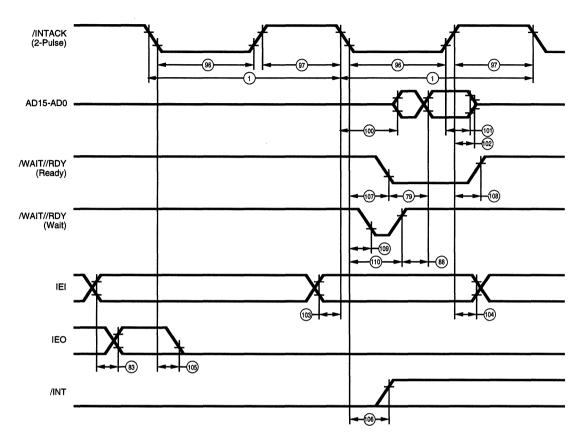

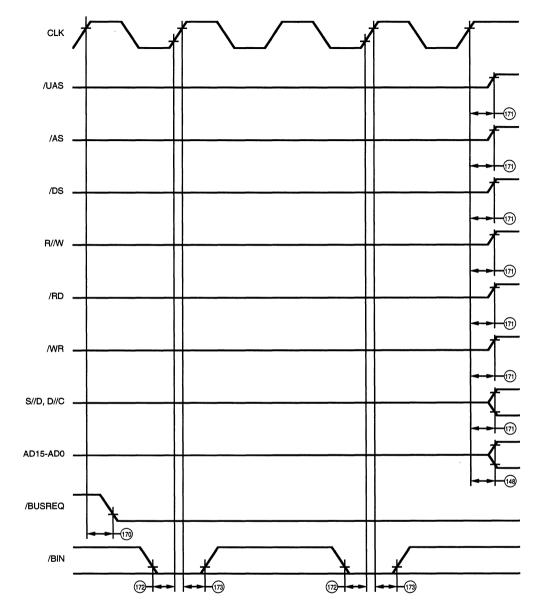

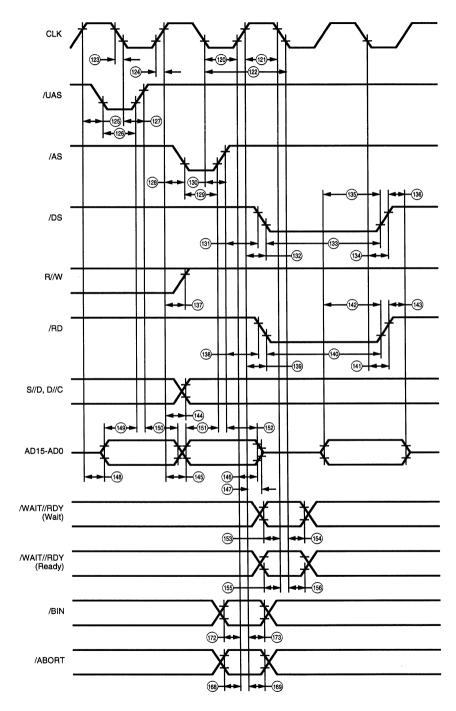

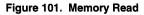

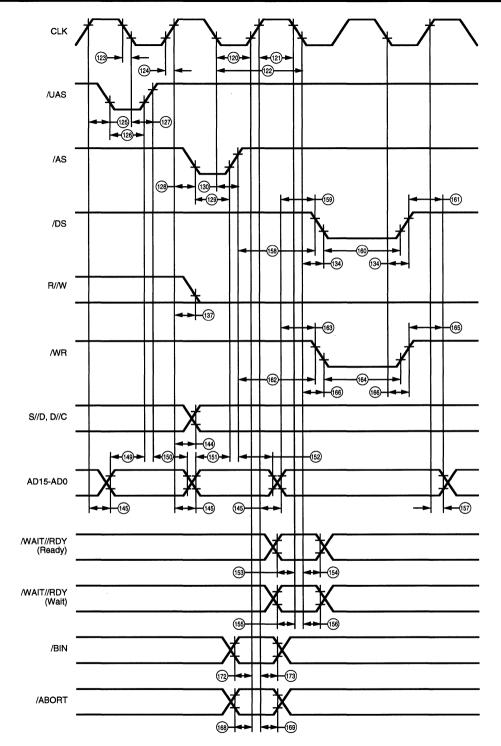

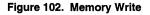

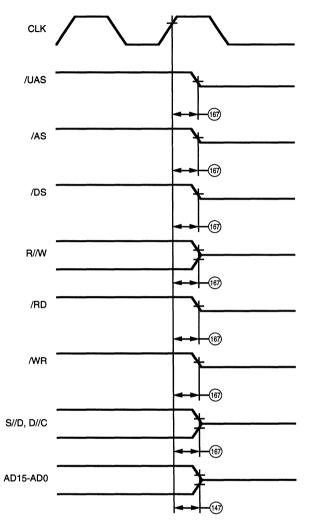

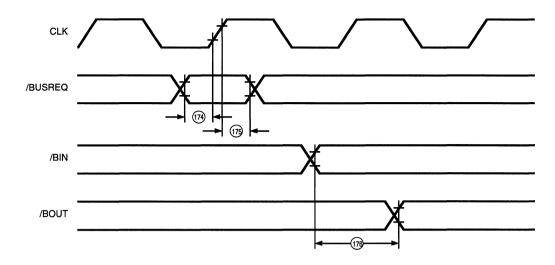

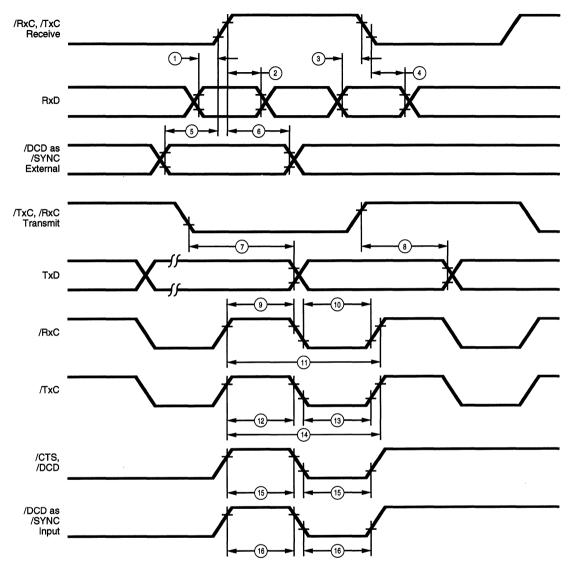

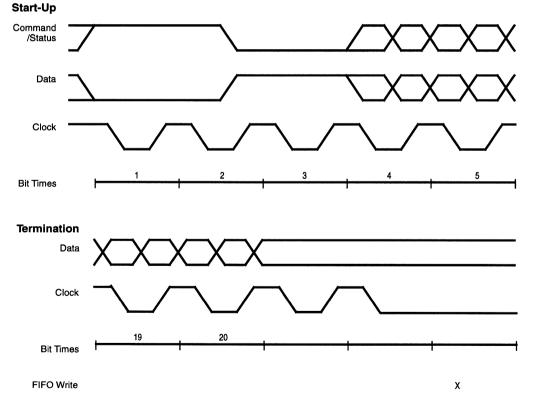

## **USC TIMING**

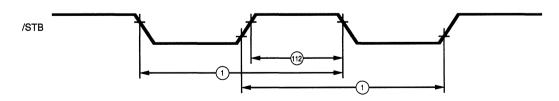

The USC interface timing is similar to that found on a static RAM, except that it is much more flexible. Up to eight separate timing strobe signals may be present on the interface: /DS, /RD, /WR, /PITACK, /RxACKA, /RxACKB, /TxACKA and /TxACKB. Only one of these timing strobes may be active at any time. Should the external logic

activate more than one of these strobes at the same time the USC will enter a pre-reset state that is only exited by a hardware reset. Do not allow overlap of timing strobes. The timing diagrams, beginning on the next page, illustrate the different bus transactions possible, with the necessary setup, hold and delay times.

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                                | Description                                                                  | Min        | Max                       | Units            |

|-------------------------------------------------------|------------------------------------------------------------------------------|------------|---------------------------|------------------|

| V <sub>cc</sub><br>T <sub>stg</sub><br>T <sub>A</sub> | Supply Voltage (*)<br>Storage Temp<br>Oper Ambient Temp<br>Power Dissipation | 0.3<br>65° | +7.0<br>+150°<br>†<br>2.2 | V<br>C<br>C<br>W |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Notes:

\* Voltage on all pins with respect to GND.

† See Ordering Information.

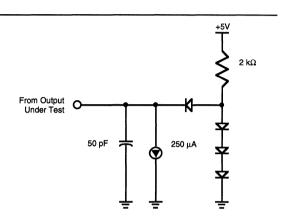

## STANDARD TEST CONDITIONS

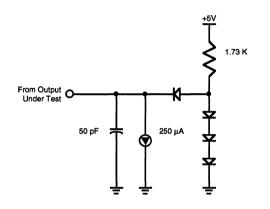

The DC Characteristics and Capacitance section below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pin (Figure 54). Standard conditions are as follows:

- +4.5 V < V<sub>cc</sub> < +5.5 V

- GND = 0 V

- T<sub>A</sub> as specified in Ordering Information

Figure 54. Standard Test Load

### CAPACITANCE

| Symbol                               | Parameter                 | Min | Max | Unit | Condition           |

|--------------------------------------|---------------------------|-----|-----|------|---------------------|

| CIN                                  | Input Capacitance         |     | 10  | pf   | Unmeasured pins     |

| 0                                    | Output Capacitance        |     | 15  | pf   | returned to Ground. |

| C <sub>out</sub><br>C <sub>i/o</sub> | Bidirectional Capacitance |     | 20  | pf   |                     |

#### Note:

f = 1 MHz, over specified temperature range.

### MISCELLANEOUS

Transistor Count - 174,000

## **TEMPERATURE RATINGS**

Standard =  $0^{\circ}$ C to  $\pm 70^{\circ}$ C Extended =  $-40^{\circ}$ C to  $+85^{\circ}$ C

## DC CHARACTERISTICS Z16C30

| Symbol            | Parameter                      | Min                  | Тур | Max                  | Unit | Condition                                                |

|-------------------|--------------------------------|----------------------|-----|----------------------|------|----------------------------------------------------------|

| V <sub>IH</sub>   | Input High Voltage             | 2.2                  |     | V <sub>cc</sub> +0.3 | V    | ······································                   |

| V                 | Input Low Voltage              | -0.3                 |     | ŏ.8                  | V    |                                                          |

| V <sub>oH</sub> 1 | Output High Voltage            | 2.4                  |     |                      | V    | $I_{0\mu} = -1.6 \text{ mA}$                             |

| V <sub>OH</sub> 2 | Output High Voltage            | V <sub>cc</sub> -0.8 |     |                      | V    | I <sub>oH</sub> = –1.6 mA<br>I <sub>oH</sub> = –250 μA   |

| V <sub>OL</sub>   | Output Low Voltage             |                      |     | 0.4                  | V    | $I_{01} = +2.0 \text{ mA}$                               |

|                   | Input Leakage                  |                      |     | ±10.00               | μA   | 0.4 < V <sub>IN</sub> < +2.4V                            |

| l <sub>ol</sub>   | Output Leakage                 |                      |     | ±10.00               | μA   | 0.4 < V <sub>out</sub> < +2.4V                           |

|                   | V <sub>cc</sub> Supply Current |                      | 7   | 50                   | mА   | $V_{\rm CC} = 5 V V_{\rm IH} = 4.8 V V_{\rm IL} = 0.2 V$ |

Note:

$V_{cc}$ = 5V ± 10% unless otherwise specified, over specified temperature range.

# AC CHARACTERISTICS Z16C30

| No | Symbol    | Parameter                             | Min | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Units | Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|-----------|---------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | Тсус      | Bus Cycle Time                        | 110 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ns    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2  | TwASI     | /AS Low Width                         | 30  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ns    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |