# Wireless Databook

V-Chip INTERNET TV

Consume

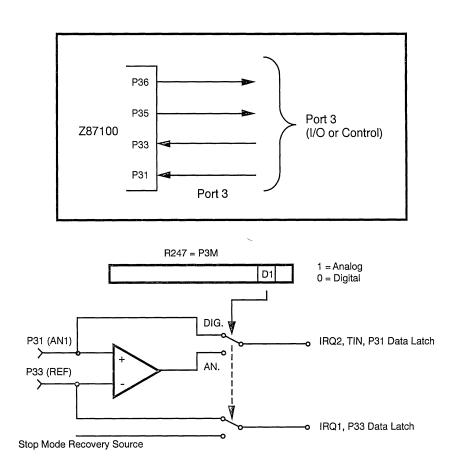

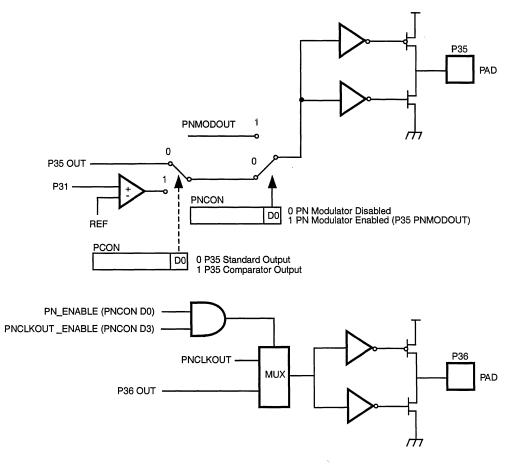

MARIN

000000

ŧ ‡

5-5555

Includes Specifications for the following Parts:

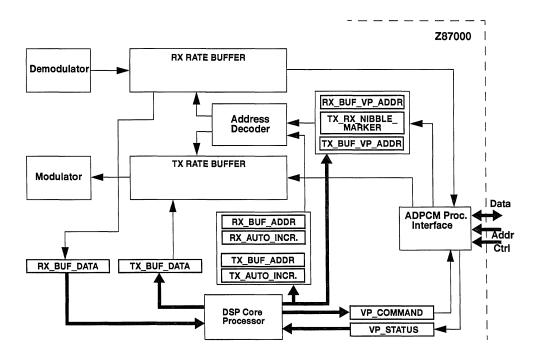

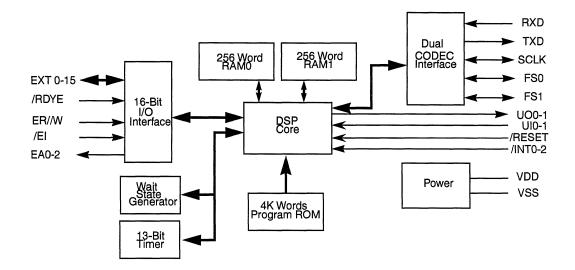

Z87000 Z87L00 Z87010 Z87L10 Z87100 Z87200

Zilog

# Wireless Databook

Includes Specifications for the following Devices:

- **Z87000/Z87L00**

- **Z87010/Z87L10**

- **Z8710**0

- **Z87200**

I 1996 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of merchantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc.

Zilog's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Zilog prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 FAX 408 370-8056 Internet: http://www.zilog.com

# INTRODUCTION

# ZILOG'S FOCUS ON APPLICATION-SPECIFIC PRODUCTS HELPS YOU MAINTAIN YOUR TECHNOLOGICAL EDGE

#### **Comprehensive Wireless Solutions**

Zilog's Wireless family of products provides comprehensive solutions for a wide range of high-volume wireless systems—from telephony to automated meter reading, and narrowband to spread-spectrum technology. Zilog develops its own application technology in house, so the Zilog Wireless products are individually tailored to their end-product application for high-performance and cost-effective results.

#### **Total Customer Support**

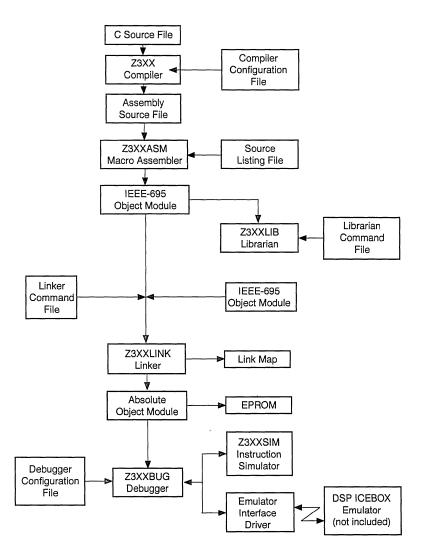

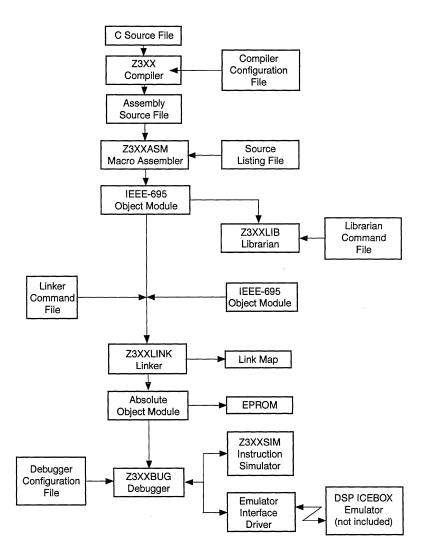

Zilog's customer support program dramatically shortens the design-to-production cycle. Our worldwide, dedicated engineering team works with you to develop your solutions using a comprehensive suite of development tools. Every Zilog Wireless controller has an In-Circuit Emulator (ICE-BOX<sup>™</sup>), application board, and C programming language compiler for complete and individualized product support.

. . ~

# WIRELESS DATABOOK TABLE OF CONTENTS

| TITLE PAG                                                                                                                        | E |

|----------------------------------------------------------------------------------------------------------------------------------|---|

| Z87000/Z87L00 SPREAD SPECTRUM CONTROLLERS 1-1                                                                                    |   |

| Z87010/Z87L10 Audio Encoder/Decoders                                                                                             |   |

| Z87100 PN MODULATOR WIRELESS TRANSMITTER                                                                                         |   |

| Z87200 SPREAD-SPECTRUM TRANSCEIVER 4-1                                                                                           |   |

| Wireless Technical Article<br>Digital Chip Set Brings Superior Range, Voice Clarity, and<br>Noise Immunity to Corldess Telephony |   |

| Wireless Product Family                                                                                                          |   |

| SUPPORT PRODUCT INFORMATION<br>Z8700000TSC EMULATION MODULE                                                                      |   |

| Additional Information<br>Zilog's Sales Offices Representatives & Distributors                                                   |   |

# Z87000/Z87L00 Spread Spectrum Controllers

1978 CONTRACT Na bol Contract (1970) (1) States of the state of t unitation of the states of the second sec Second olekon erekitet i saskalli. Maaigal it sook oot interkondi. guiden o gelgade Al Lohertos Sil an gestate estate gotti. 1111 - archaich ett fi uccharaeceuge fi

210gie 1.Nexture Acide Ordscheg Inferentier

# Z87000/Z87L00 Spread Spectrum Controllers

Communications Functions

Control (AFC) Loop FSK Demodulator FSK Modulator Symbol Synchronizer

---

п

Buffers

16.384 MHz Base Clock

Transceiver Circuitry Provides Primary Cordless Phone

Digital Downconversion with Automatic Frequency

Time Division Duplex (TDD) Transmit and Receive

On-Chip A/D and D/A to Support 10.7 MHz IF Interface

Bus Interface to Z87010 ADPCM Processor

Static CMOS for Low Power Consumption

□ 3.0V to 3.6V, -20°C to +70°C, Z87L00

4.5V to 5.5V, -20°C to +70°C, Z87000

# FEATURES

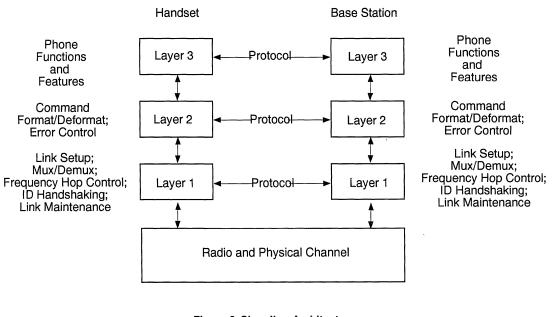

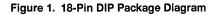

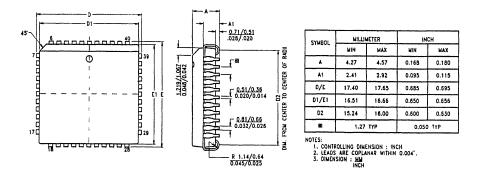

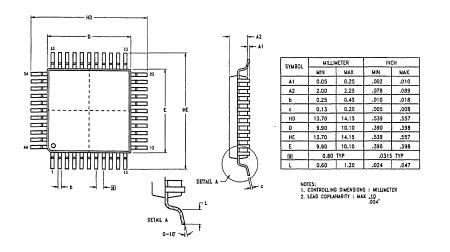

| Device | ROM<br>(KWords) | RAM*<br>(Words) | I/O<br>Lines | Package<br>Information     |

|--------|-----------------|-----------------|--------------|----------------------------|

| Z87000 | 12              | 512             | 32           | 84-Pin PLCC<br>100-Pin QFP |

| Z87L00 | 12              | 512             | 32           | 100-Pin QFP                |

#### Transceiver/Controller Chip Optimized for Implementation of 900 MHz Spread Spectrum Cordless Phone

- Adaptive Frequency Hopping

- Transmit Power Control

- Error Control Signaling

- Handset Power Management

- Support of 32 kbps ADPCM Speech Coding for High Voice Quality

- DSP Core Acts as Phone Controller

- Zilog-Provided Embedded Transceiver Software to Control Transceiver Operation and Base Station-Handset Communications Protocol

- User-Modifiable Software Governs Phone Features

# GENERAL DESCRIPTION

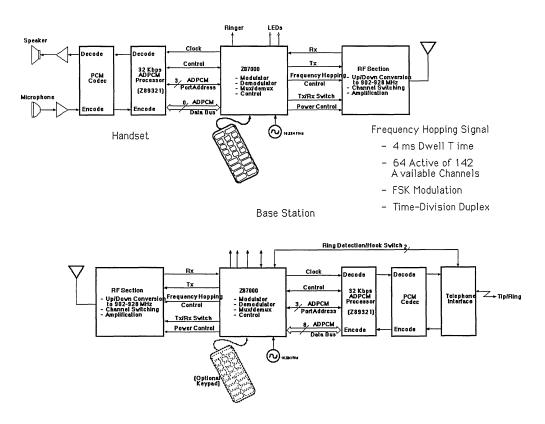

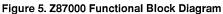

The Z87000/Z87L00 FHSS Cordless Telephone Transceiver/Controllers are expressly designed to implement a 900 MHz frequency hopping spread spectrum cordless telephone compliant with United States FCC regulations for unlicensed operation. The Z87000 and Z87L00 are distinct 5V and 3.3V versions, respectively, of the device. For the sake of brevity, all subsequent references to the Z87000 in this document also apply to the Z87L00, unless specifically noted. The Z87000 supports a specific cordless phone system design that uses frequency hopping and digital modulation to provide extended range, high voice quality, and low system costs. The Z87000 uses a Zilog 16-bit fixed-point two's complement static CMOS Digital Signal Processor core as the phone and RF section controller. The Z87000's DSP core processor further supports control of the RF section's frequency synthesizer for frequency hopping and the generation of the control messages needed to coordinate incorporation of the phone's handset and base station.

#### **GENERAL DESCRIPTION** (Continued)

Additional on-chip transceiver circuitry supports Frequency Shift Keying modulation/demodulation and multiplexing/demultiplexing of the 32 kbps voice data and 4 kbps command data between handset and base station. The Z87000 provides thirty-two I/O pins, including four wakeup inputs and two CPU interrupt inputs. These programmable I/O pins allow a variety of user-determined phone features and board layout configurations. Additionally, the pins may be used so that phone features and interfaces are supported by an optional microcontroller rather than by the Z87000's DSP core.

In combination with an RF section designed according to the system specifications, Zilog's Z87010/Z87L10 ADPCM Processor, a standard 8-bit PCM telephone CODEC and minimal additional phone circuity, the Z87000 and its embedded software provide a total system solution.

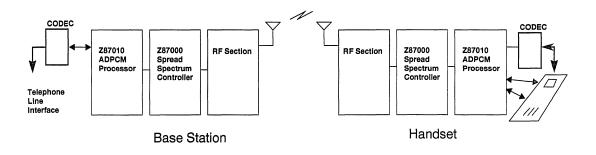

Figure 1. System Block Diagram of a Z87000/Z87010 Based Phone

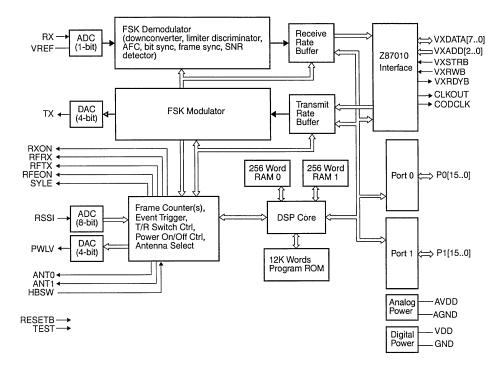

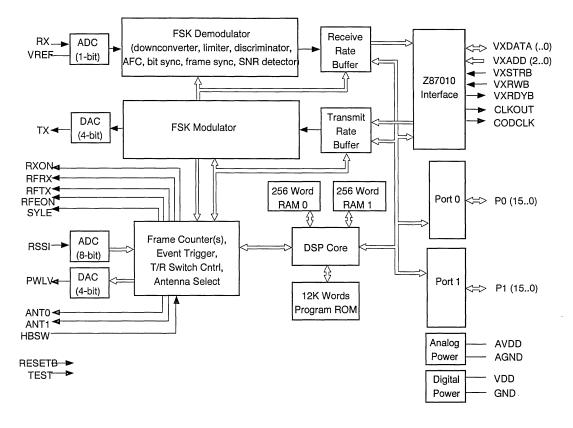

Figure 2. Z87000 Functional Block Diagram

DS96WRL0501

#### **PIN DESCRIPTION**

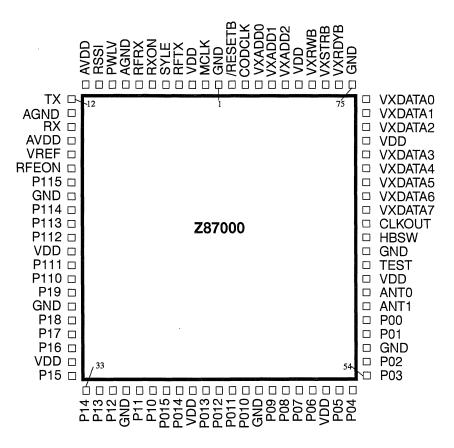

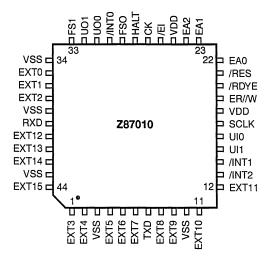

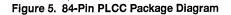

Figure 3. 84-Pin PLCC ROM Pin Configuration (Z87000 only)

| Pin Number                                              | Symbol           | Function                               | Direction    |

|---------------------------------------------------------|------------------|----------------------------------------|--------------|

| 1,19,27,36,46,<br>56,63,75                              | GND              | Ground                                 | _            |

| 2                                                       | MCLK             | Master clock (16.384 MHz)              | Input        |

| <u>-</u><br>3,23,31,41,51,                              | V <sub>DD</sub>  | Digital                                |              |

| 61,71,79                                                | ♥ DD             | Digital                                | -            |

| 4                                                       | RFTX             | RF transmit switch control             | Output       |

| 5                                                       | SYLE             | RF synthesizer load enable             | Output       |

| 6                                                       | RXON             | Demodulator "on" indication            | Output       |

| 7                                                       | RFRX             | RF receive switch control              | Output       |

| 8,13                                                    | AGND             | Analog ground                          | -            |

| 9                                                       | PWLV             | RF transmit power level                | Output       |

| 10                                                      | RSSI             | RF receive signals strength indicator  | Input        |

| 11,15                                                   | AV <sub>DD</sub> | Analog V <sub>DD</sub>                 | -            |

| 12                                                      | ТХ               | Analog transmit IF signal              | Output       |

| 14                                                      | RX               | Analog receive IF signal               | Input        |

| 16                                                      | V <sub>REF</sub> | Analog reference voltage for RX signal | Output       |

| 17                                                      | RFEON            | RF module on/off control               | Output       |

| 18,20,21,22,24,<br>25,26,28,29,30,<br>32,33,34,35,37,38 | P115             | General-purpose                        | Input        |

| 59,60                                                   | ANT1             | RF diversity antenna control           | Input/Output |

| 62                                                      | TEST             | Main test mode control                 | Input        |

| 64                                                      | HBSW             | Handset/Base Control                   | -            |

| 65                                                      | CLKOUT           | Clock output to ADPCM Processor        | Output       |

| 76                                                      | VXRDYB           | ADPCM processor ready signal           | Output       |

| 77                                                      | VXSTRB           | ADPCM processor data strobe            | Input        |

| 78                                                      | VXRWB            | ADPCM read/write control               | Input        |

| 80,81,82                                                | VXADD2           | ADPCM processor address bus            | Input        |

| 83                                                      | CODCLK           | Clock output to codec                  | Output       |

| 84                                                      | /RESETB          | Reset signal                           | Input        |

|                                                         |                  |                                        |              |

# Table 1. 84-Pin PLCC Pin Description Summary

#### **PIN DESCRIPTION** (Continued)

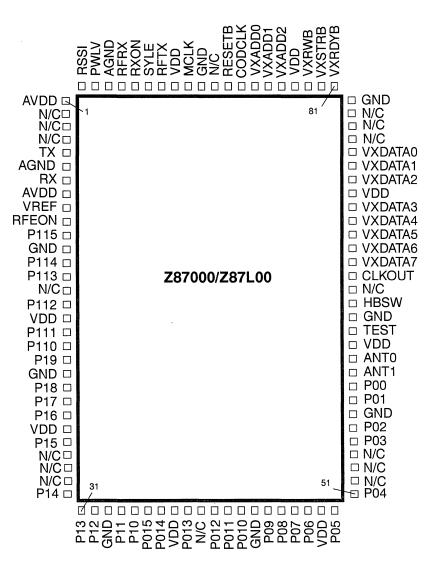

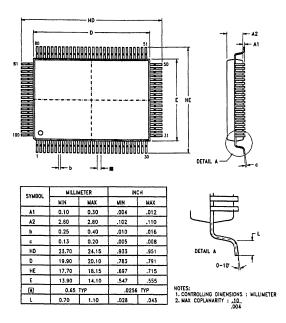

Figure 4. 100-Pin QFP Pin Configuration

| No                                                      | Symbol           | Function                               | Direction    |

|---------------------------------------------------------|------------------|----------------------------------------|--------------|

| 1,8                                                     | AV <sub>DD</sub> | Analog V <sub>DD</sub>                 | -            |

| 2,3,4,15,27,28,<br>29,40,52,53,54,<br>66,77,78,79,90    | N/C              | No connection                          | _            |

| 5                                                       | TX               | Analog transmit IF signal              | Output       |

| 6,98                                                    | AGND             | Analog ground                          |              |

| 7                                                       | RX               | Analog receive IF signal               | Input        |

| 9                                                       | VREF             | Analog reference voltage for RX signal |              |

| 10                                                      | RFEON            | RF module on/off control               | Output       |

| 11,13,14,16,18,<br>19,20,22,23,23,<br>26,30,31,32,34,35 | P1[150]          | General-purpose I/O port 0             | Input        |

| 17,25,38,49,62,<br>73,84,93                             | V <sub>DD</sub>  | Digital                                | -            |

| 36,37,39,41,42,<br>43,45,46,47,48,<br>50,51,55,56,58,59 | P0[150]          | General-purpose I/O port 0             | Input        |

| 60,61                                                   | ANT[10]          | RF diversity antenna control           | Input/Output |

| 63                                                      | TEST             | Main test mode control                 | Input        |

| 65                                                      | HBSW             | Handset/bast control                   | Input        |

| 67                                                      | CLKOUT           | Clock output to ADPCM processor        | Output       |

| 68,69,70,71,72,<br>74,75,76                             | VXDATA[7]        | ADPCM processor data bus               | Input        |

| 81                                                      | VXRDYB           | ADPCM processor ready signal           | Output       |

| 82                                                      | VXSTRB           | ADPCM processor data strobe            | Input        |

| 83                                                      | VXRWB            | ADPCM processor read/write control     | Input        |

| 85,86,87                                                | VXADD[20]        | ADPCM processor address bus            | Input        |

| 88                                                      | CODCLK           | Clock output to codec                  | Output       |

| 89                                                      | /RESETB          | Reset signal                           | Input        |

| 92                                                      | MCLK             | Master clock input (16.384 MHz)        | Input        |

| 94                                                      | RFTX             | RF transmit switch control             | Output       |

| 95                                                      | SYLE             | RF synthesizer load enable             | Output       |

| 96                                                      | RXON             | Demodulator "on" indication            | Output       |

| 97                                                      | RFRX             | RF receive switch control              | Output       |

| 99                                                      | PWLV             | RF transmit power level                | Input        |

| 100                                                     | RSSI             | RF receive signal strength indicator   | Input        |

#### Table 2. 100-Pin QFP Pin Configuration

| Symbol                             | Parameter                | Min  | Max                   | Units |

|------------------------------------|--------------------------|------|-----------------------|-------|

| V <sub>DD</sub> , AV <sub>DD</sub> | DC Supply<br>Voltage(1)  | -0.5 | 7.0                   | V     |

| V <sub>IN</sub>                    | Input Voltage(2)         | -0.5 | $V_{DD} + 0.5$        | V     |

| V <sub>OUT</sub>                   | Output Voltage(3)        | -0.5 | V <sub>DD</sub> + 0.5 | V     |

| T <sub>A</sub>                     | Operating<br>Temperature | -20  | +70                   | °C    |

| T <sub>STG</sub>                   | Storage<br>Temperature   | -65  | +150                  | °C    |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended period may affect device reliability.

#### Notes:

1. Voltage on all pins with respect to GND.

2. Voltage on all inputs WRT VDD

3. Voltage on all outputs WRT VDD

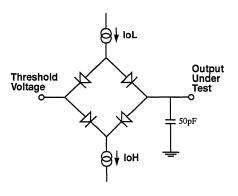

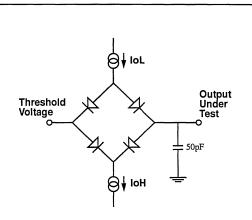

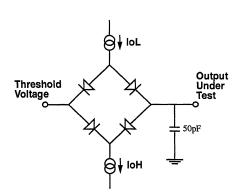

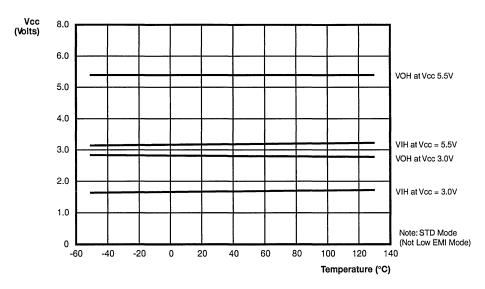

#### STANDARD TEST CONDITIONS

The electrical characteristics listed below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pins. Standard test conditions are as follows:

- 3.0V < V<sub>DD</sub> < 3.6V (Z87L00)

- 4.5V < V<sub>DD</sub> < 5.5V (Z87000)

- GND = 0V

- T<sub>A</sub> = -20 to +70 °C

Figure 5. Test Load Diagram

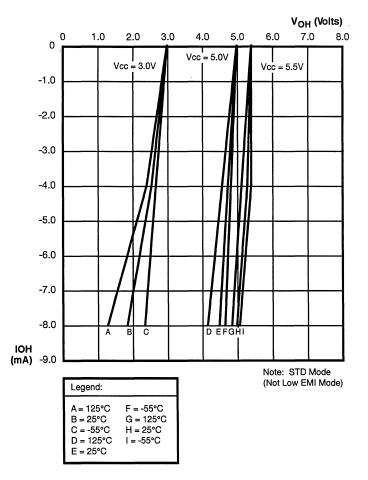

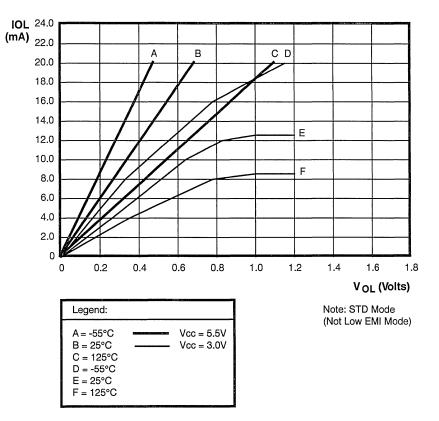

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol                             | Parameter                                    | Min      | Max                   | Units |

|------------------------------------|----------------------------------------------|----------|-----------------------|-------|

| V <sub>DD</sub> , AV <sub>DD</sub> | Supply Voltage                               | 4.5      | 5.5                   | V     |

| VIH                                | Input High Voltage                           | 2.0      | V <sub>DD</sub> + 0.3 | V     |

| VIL                                | Input Low Voltage                            | GND -0.3 | 0.8                   | V     |

| ОН                                 | Output High Current                          |          | -2.0                  | mA    |

| OL1                                | Output Low Current                           |          | 4.0                   | mA    |

| OL2                                | Output Low Current, Ports (limited usage, 1) |          | 12.0                  | mA    |

| Τ <sub>A</sub>                     | Operating Temperature                        | -20      | +70                   | °C    |

1. Maximum 3 pins total from P0[15..0] and P1[15..0]

# Table 4. 3.3V $\pm$ 0.3V Operation (Z87L00)

| Symbol          | Parameter                                    | Min                 | Max                  | Units |

|-----------------|----------------------------------------------|---------------------|----------------------|-------|

| V <sub>DD</sub> | Supply Voltage                               | 3.0                 | 3.6                  | V     |

| VIH             | Input High Voltage                           | 0.7 V <sub>DD</sub> | V <sub>DD</sub> +0.3 | V     |

| V <sub>IL</sub> | Input Low Voltage                            | GND -0.3            | 0.1 V <sub>DD</sub>  | V     |

| ОН              | Output High Current                          |                     | -1.0                 | mA    |

| OL1             | Output Low Current                           |                     | 2.0                  | mA    |

| OL2             | Output Low Current, Ports (limited usage, 2) |                     | 6.0                  | mA    |

| Γ <sub>A</sub>  | Operating Temperature                        | -20                 | +70                  | °C    |

# DC ELECTRICAL CHARACTERISTICS

Conditions for DC characteristics are corresponding operating conditions, and standard test conditions, unless otherwise specified.

#### Table 5. 5V $\pm$ 0.5V Operation (Z87000)

| Symbol           | Parameter                     | Test Condition                            | Min | Max | Units |

|------------------|-------------------------------|-------------------------------------------|-----|-----|-------|

| V <sub>OH</sub>  | Output High Voltage           | V <sub>DD</sub> min, I <sub>OH</sub> max  | 2.4 |     | V     |

| V <sub>OL1</sub> | Output Low Voltage            | V <sub>DD</sub> min, I <sub>OL1</sub> max |     | 0.6 | V     |

| V <sub>OL2</sub> | Output Low Voltage, Ports (1) | V <sub>DD</sub> min, I <sub>OL2</sub> max |     | 1.2 | V     |

| l_               | Input Leakage                 | $V_{IN} = 0V, V_{DD}$                     | -2  | 2   | μA    |

| I <sub>CC</sub>  | Supply Current                |                                           | ·   | 80  | mA    |

| I <sub>CC2</sub> | Standby Mode Current (2)      | - 19 19                                   |     | 4   | mA    |

| NI - 4           |                               |                                           |     |     |       |

Notes:

1. Maximum 3 pins total from P0[15..0] and P1[15..0]

2. 2.3 mA typical at 25°C, 5 volts.

#### Table 6. $3.3V \pm 0.3V$ Operation (Z87L00)

| Symbol           | Parameter                    | Test Condition                            | Min | Max | Units |

|------------------|------------------------------|-------------------------------------------|-----|-----|-------|

| V <sub>OH</sub>  | Output High Voltage          | V <sub>DD</sub> min, I <sub>OH</sub> max  | 1.6 |     | V     |

| V <sub>OL1</sub> | Output Low Voltage           | V <sub>DD</sub> min, I <sub>OL1</sub> max |     | 0.4 | V     |

| V <sub>OL2</sub> | Output Low Voltage, Ports(1) | V <sub>DD</sub> min, I <sub>OL2</sub> max |     | 1.2 | V     |

| l                | Input Leakage                | $V_{IN} = 0V, V_{DD}$                     | -2  | 2   | μA    |

| lcc              | Supply Current               |                                           |     | 55  | mA    |

| I <sub>CC2</sub> | Standby Mode Current(2)      |                                           | 1.4 |     | mA    |

| Notos            |                              |                                           |     |     |       |

Notes:

1. Maximum 3 pins total from P0[15..0] and P1[15..0]

2. 1.6 mA typical at 25°C, 3.3 volts.

# ANALOG CHARACTERISTICS

| Table 7. | 1-Bit ADC | (Temperature: -20/+70°C) |

|----------|-----------|--------------------------|

|----------|-----------|--------------------------|

| Parameter                        | Minimum                      | Typical                       | Maximum                       | Units |

|----------------------------------|------------------------------|-------------------------------|-------------------------------|-------|

| Resolution                       | -                            | 1                             | -                             | bit   |

| Power dissipation                | 0.54                         | 1.0                           | 2.75                          | mW    |

| ·                                | (70°c)                       | (40°c)                        | (-20°c)                       |       |

| Power dissipation, Stop mode     | 0.06                         | 0.2                           | 1.1                           | mW    |

|                                  | (70°c)                       | (40°c)                        | (-20°c)                       |       |

| Sample frequency                 |                              | 8.192                         | -                             | MHz   |

| Sample window(1)                 | 29                           | 31                            | 33                            | ns    |

| Bandwidth                        |                              | 60                            | -                             | MHz   |

| Supply Range(=AV <sub>DD</sub> ) |                              |                               |                               |       |

| Z87L00                           | 3.0                          |                               | 3.6                           | V     |

| Z87000                           | 4.5                          |                               | 5.5                           | v     |

| Acquisition time                 | 2                            | 3                             | 8                             | ns    |

| Settling time                    | 8                            | 10                            | 18                            | ns    |

| Conversion time                  | 4                            | 6                             | 18                            | ns    |

| Aperture delay                   | 2                            | 3                             | 8.5                           | ns    |

| Aperture uncertainty(2)          | -                            | -                             | 0.5                           | ns    |

| Input voltage range (p-p)        | 800                          | 1000                          | 1200                          | mV    |

| Reference voltage                |                              |                               |                               |       |

| Z87L00                           | 1.7 (AV <sub>DD</sub> = 3V)  | 1.9 (AV <sub>DD</sub> = 3.3V) | 2.1 (AV <sub>DD</sub> = 3.6V) | V     |

| Z87000                           | 2.7 (AV <sub>DD</sub> =4.5V) | 3.0 (AV <sub>DD</sub> = 5V)   | 3.3 (AV <sub>DD</sub> = 5.5V) | V     |

| Input resistance                 | 10                           | 18                            | 25                            | KOhm  |

| Input capacitance                | -                            | 10                            | -                             | pF    |

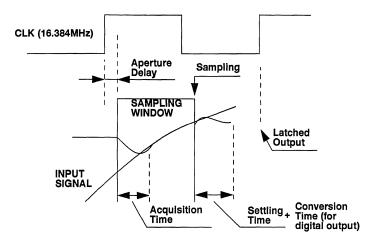

Notes:

Window of time while input signal is applied to sampling capacitor; see next figure. Uncertainty in sampling time due to random variations such as thermal noise.

Figure 6. 1-Bit ADC Definition of Terms

| Table 8. 8-bit ADC (Temperature -20/+70°C) |         |                    |         |       |

|--------------------------------------------|---------|--------------------|---------|-------|

| Parameter                                  | Minimum | Typical            | Maximum | Units |

| Resolution                                 | -       | 6                  | -       | bit   |

| Integral non-linearity                     | •••     | 0.5                | 1       | LSB   |

| Differential non-linearity                 |         | -                  | 0.5     | LSB   |

| Power Dissipation (peak)                   |         | 35                 | 70      | mW    |

| Sample window                              | 5       | -                  | 120     | ns    |

| Bandwidth                                  | •       | -                  | 2       | Msps  |

| Supply Range (=AV <sub>DD</sub> )          |         |                    |         |       |

| Z87L00                                     | 3.0     | 3.3                | 3.6     | V     |

| Z87000                                     | 4.5     | 5.0                | 5.5     | V     |

| Input voltage range                        |         | 0-AV <sub>DD</sub> |         | V     |

| Conversion time                            | 0.5     | -                  | -       | μs    |

| Aperture delay                             | 2       | 3                  | 8.5     | ns    |

| Aperture uncertainty                       | -       | -                  | 1       | ns    |

|                                            |         |                    |         |       |

-

-

Notes:

Input resistance

Input capacitance

1. 8-bit ADC only tested for 6-bit resolution.

25

10

Kohm

pF

-

-

| Parameter                                       | Minimum        | Typical                                     | Maximum         | Units |

|-------------------------------------------------|----------------|---------------------------------------------|-----------------|-------|

| Resolution                                      | -              | 4                                           | -               | bit   |

| Integral non-linearity                          | -              | 0.25                                        | 0.5             | LSB   |

| Differential non-linearity                      | -              | 0.25                                        | 1               | LSB   |

| Settling time (1/2 LSB)                         | -              | -                                           | 22.5            | ns    |

| Zero error at 25°C                              | -              | 1                                           | 2               | mV    |

| Conversion time (input change to output change) | 14             | 19                                          | 76              | ns    |

| Power dissipation, 25 pF load                   | 1.2<br>(70°c)  | 20<br>(40°c)                                | 24.1<br>(-20°c) | mW    |

| Power dissipation, 25 pF load, Stop mode        | 0.18<br>(70°c) | 1.0<br>(40°c)                               | 1.1<br>(-20°c)  | mW    |

| Conversion time (input change to output change) | 14.5           | 19.1                                        | 75.8            | ns    |

| Rise time (full swing)                          | 11             | 15                                          | 71              | ns    |

| Output slew rate                                | 8              | 67                                          | 96              | V/µs  |

| Output voltage range                            | -              | 0.2 AV <sub>DD</sub> to 0.6AV <sub>DD</sub> | -               | V     |

| Supply Range (=AV <sub>DD</sub> )               |                |                                             |                 |       |

| Z87L00                                          | 3.0            | 3.3                                         | 3.6             | V     |

| Z87000                                          | 4.5            | 5.0                                         | 5.5             | V     |

| Output load resistance                          |                | 330                                         |                 | Ohm   |

| Output load capacitance                         | -              | 25                                          | -               | pF    |

All digital pins (all pins except  $V_{DD},\,AV_{DD},\,GND,\,AGND,\,V_{REF},\,RX,\,TX,\,RSSI$  and PWLV) have an internal capacitance of 5 pF.

The RX analog input pin has an input capacitance of 10 pF.

The RSSI analog input pin has an input capacitance of 10 pF.

# AC ELECTRICAL CHARACTERISTICS

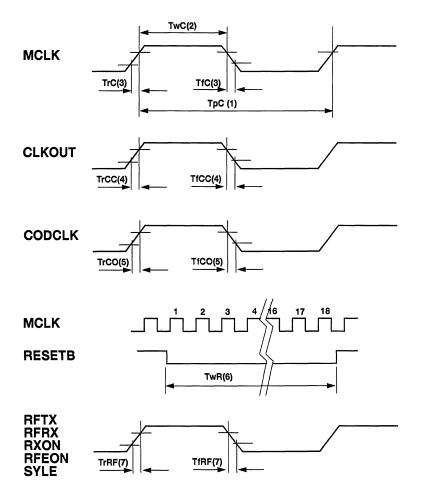

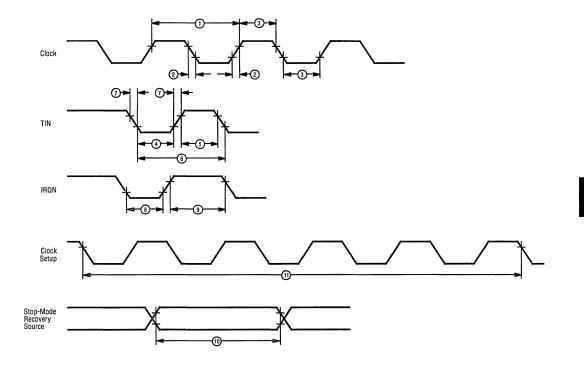

#### **Clocks, Reset and RF Interface**

| No.   | Symbol     | Parameter                             | Min | Max                                   | Units |

|-------|------------|---------------------------------------|-----|---------------------------------------|-------|

| 1     | ТрС        | MCLK input clock period (1)           | 61  | 61                                    | ns    |

| 2     | TwC        | MCLK input clock pulse width          | 20  | 40                                    | ns    |

| 3     | TrC, TfC   | MCLK input clock rise/fall time       |     | 15                                    | ns    |

| 4     | TrCC, TfCC | CLKOUT output clock rise/fall time    | 2   | 6                                     | ns    |

| 5     | TrCO, TfCO | CODCLK output clock rise/fall time    | 2   | 6                                     | ns    |

| 6     | TwR        | RESETB input low width                | 18  | · · · · · · · · · · · · · · · · · · · | ТрС   |

| 7     | TrRF, TfRF | RF output controls rise/fall time (2) | 2   | 6                                     | ns    |

| otes: |            |                                       |     |                                       |       |

Table 10. Clocks, Reset and RF Interface

1. MCLK is 16.384 MHz  $\pm$  25 ppm

2. RF Controls are RFTX, RFRX, RXON, RFEON, SYLE.

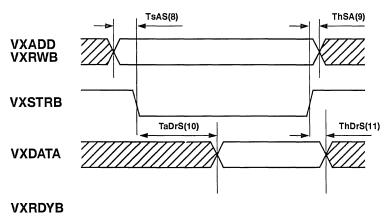

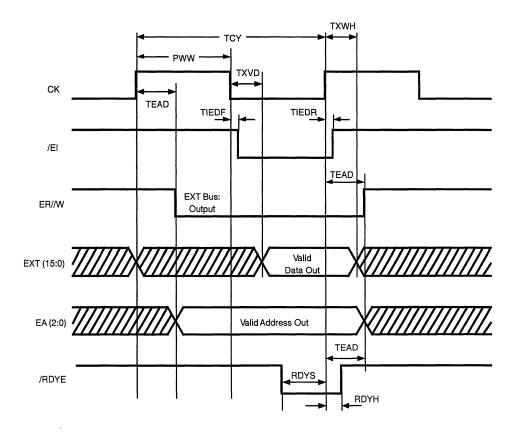

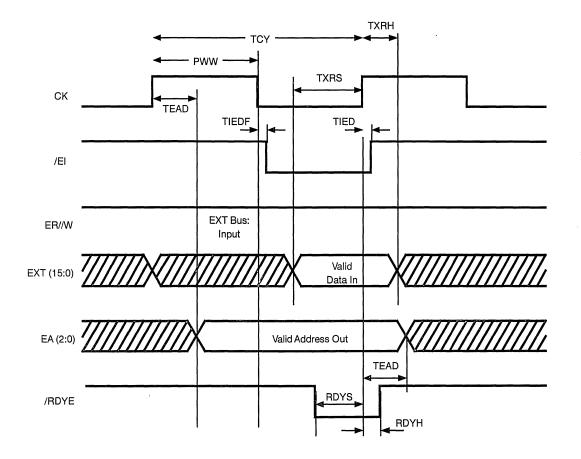

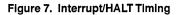

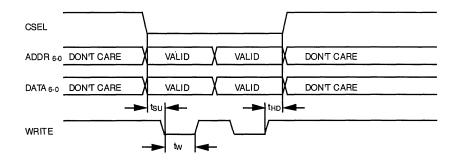

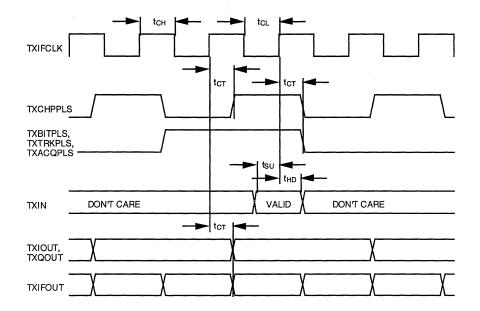

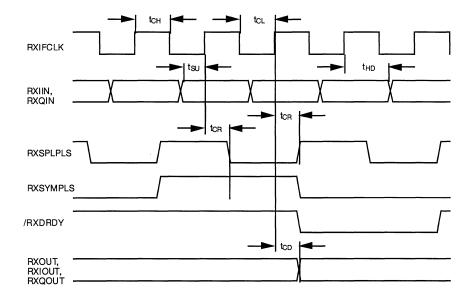

#### **ADPCM Processor Interface**

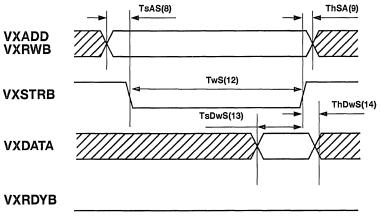

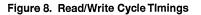

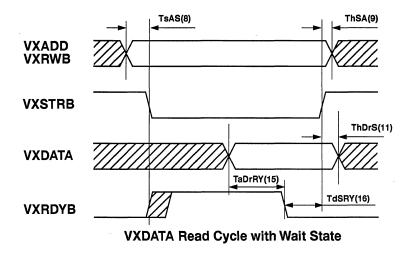

The Z87000 is a peripheral device for the ADPCM Processor. The interface from the Z87000 perspective is composed of an input address bus, a bidirectional data bus, strobe and read/write input control signals and a ready/wait output control signal. READ CYCLES refer to data transfers from the Z87000 to the ADPCM Processor.

WRITE CYCLES refer to data transfers from the ADPCM Processor to the Z87000.

#### Table 11. Read Cycles

| Signal Name | Function                  | Direction             |  |

|-------------|---------------------------|-----------------------|--|

| VXADD[20]   | Address Bus               | ADPCM Proc. to Z87000 |  |

| VXDATA[70]  | Data Bus                  | Bidirectional         |  |

| VXSTRB      | Strobe Control Signal     | ADPCM Proc. to Z87000 |  |

| VXRWB       | Read/Write Control Signal | ADPCM Proc. to Z87000 |  |

| VXRDYB      | Ready Control Signal      | Z87000 to ADPCM Proc  |  |

#### Table 12. Write Cycles

| No. | Symbol | Parameter                                          | Min | Max    | Units |

|-----|--------|----------------------------------------------------|-----|--------|-------|

| 8   | TsAS   | Address, Read/Write setup time before Strobe falls | 10  |        | ns    |

| 9   | ThSA   | Address, Read/Write hold time after Strobe rises   | 3   |        | ns    |

| 10  | TaDrS  | Data read access time after Strobe falls           |     | 30 (1) | ns    |

| 11  | ThDrS  | Data read hold time after Strobe rises             | 8.5 | 40 (2) | ns    |

| 12  | TwS    | Strobe pulse width                                 | 20  | -      |       |

| 13  | TsDwS  | Data write setup time before Strobe rises          | 10  |        | ns    |

| 14  | ThDwS  | Data write hold time after Strobe rises            | 3   |        | ns    |

| 15  | TaDrRY | Data read valid before Ready falls                 | 22  |        | ns    |

| 16  | TdSRY  | Strobe high after Ready falls                      | 0   |        | ns    |

#### Notes:

1. Requires wait state on ADPCM Processor read cycles

2. Requires no write cycle directly following read cycle on ADPCM Processor

# **AC TIMING DIAGRAMS**

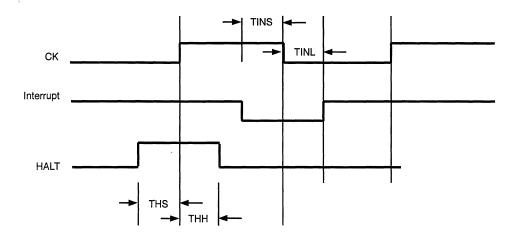

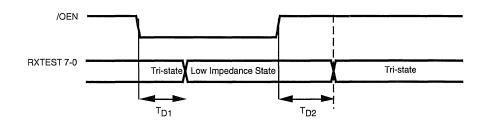

Figure 7. Transceiver Output Signal

VXDATA Read Cycle

VXDATA Write Cycle

# AC TIMING DIAGRAMS (Continued)

Figure 9. Read/Write Cycle Timing with Wait State

### **PIN FUNCTIONS**

V<sub>DD.</sub> Digital power supply.

GND. Digital ground.

AV<sub>DD</sub>. Analog power supply.

AGND. Analog ground.

$V_{\mbox{\scriptsize REF}}$  (analog reference). This signal is the reference voltage used by the high speed analog comparator to sample the RX input signal.

**RX** (analog input). This is the RX IF receive signal from the RF module, input to the analog comparator and FSK demodulator. It is internally biased to the  $V_{REF}$  DC voltage. The IF signal from the RF module should be AC coupled to the RX pin.

**TX** (analog output). This is the IF transmit signal to the RF module, output from the FSK modulator and transmit 4-bit D/A converter.

**RXON** (output; active high or low programmable). This pin reflects the programming of the demodulator turn-on time.

**RFRX** (output; active high or low programmable). Control for the receive switch on the RF module. Active during receive periods.

**RFTX** (output; active high or low programmable). Control for the transmit switch on the RF module. Active during transmit periods.

**RFEON** (output; active high or low programmable). On/off control for the RF module. Active (on) during wake periods. Inactive (off) during sleep periods on the handset.

**RSSI** (analog input). Receive signal strength indicator from RF module, input to the RSSI 8-bit ADC.

**PWLV** (analog output). Power level control for RF module, output from the transmit power 4-bit DAC.

**SYLE** (output). RF synthesizer load enable: latches new frequency hopping control word of external RF synthesizer. Programmable polarity.

**ANT[1..0]** (output). Control for optional antenna diversity on the RF module.

MCLK (input). Master clock input.

**CLKOUT** (output). Clock output for external ADPCM processor.

**CODCLK** (output). Clock output for external voice CO-DEC.

/RESETB (input, active low). Reset signal.

**VXADD[2..0]** (input). Address bus controlled by external ADPCM processor. The Z87000 acts as peripheral of the Z87010 ADPCM processor.

VXDATA[7..0](input/output). Read/write data bus controlled by external Z87010 ADPCM processor.

**VXSTRB** (input). Data strobe signal for the VXDATA bus, controlled by external Z87010.

**VXRWB** (input). Read/write control for the VXDATA bus, controlled by external Z87010.

VXRDYB (output, active low). Ready control for the VX-DATA bus. This signal is driven high (de-asserted) by the Z87000 to insert wait states in the Z87010 ADPCM processor accesses.

**TEST** (input, active high). Main test mode control. Must be set to GND.

**HBSW** (input with internal pull-up). Control for handset/base configuration. Must be driven high or not connected for handset, low for base.

**P0[15..0]** (input/output). General-purpose I/O port. Direction is bit-programmable. Pins P0[3..0],when configured in input mode, can also be individually programmed as wakeup pins for the Z87000 (wake-up active low; signal internally debounced and synchronized to the bit clock).

| P0 0 | WAKEUP0 |  |

|------|---------|--|

| P0 1 | WAKEUP1 |  |

| P0 2 | WAKEUP2 |  |

| P0 3 | WAKEUP3 |  |

| 100  | WAREOF  |  |

**P1[15..0]** (input/output).General-purpose I/O port. Direction is bit-programmable. Pins P114 and P115, when configured in input mode, also behave as individually maskable interrupt pins for the core processor (positive edge-triggered).

| P1 14 | INT0 |

|-------|------|

| P1 15 | INT2 |

# FUNCTIONAL DESCRIPTION

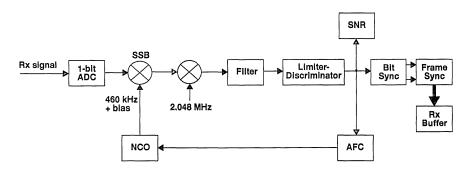

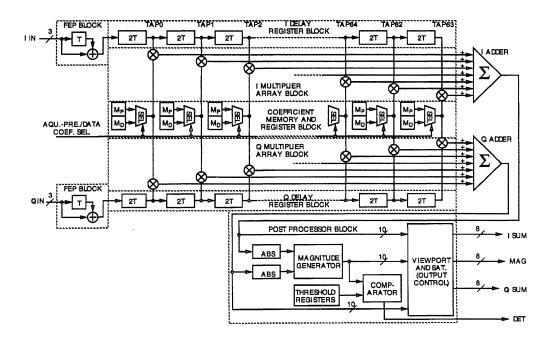

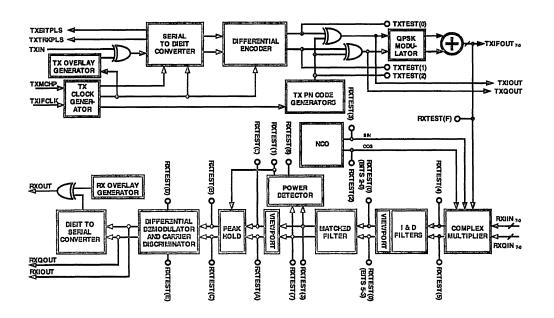

The functional partitioning of the Z87000 is shown in Figure 2. The chip consists of a receiver, a transmitter, and several additional functional blocks.

The receiver consists of the following blocks:

- Receive 1-bit ADC

- Demodulator, including:

- IF Downconverter

- AFC (Automatic Frequency Control)

- Limiter-Discriminator

- Matched Filter

- Bit Synchronizer

- Bit Inversion

- Frame Synchronizer (unique word detector)

- SNR Detector

- Receive Frame Timing Counter

- Receive Buffer and Voice Interface The Transmitter Consists of the Following Blocks:

- Transmit Buffer and Voice Interface

- Transmit Frame Timing Counter (used on base station only)

- Modulator, including:

- NCO

- Bit Inversion

Transmit 4-Bit DAC

In Addition, there are the following Shared Blocks.

- Event Trigger Block, Controlling:

- Transmit/Receive Switch

- Power On/Off Switches (Modulator, Demodulator, RF Module)

- Antenna Switch Control (used on Base Station only for Antenna Diversity)

- 4-Bit DAC for Setting Transmit Power Level

- 8-Bit ADC for Sampling the Received Signal Strength Indicator (RSSI)

- DSP Core Processor

- Two 16-Bit General-Purpose I/O Ports

- Z87010 ADPCM Processor Interface

#### **Basic Operation**

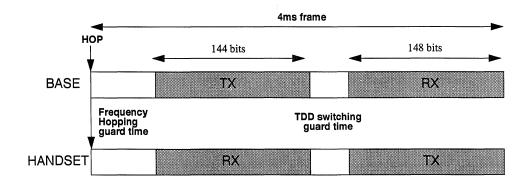

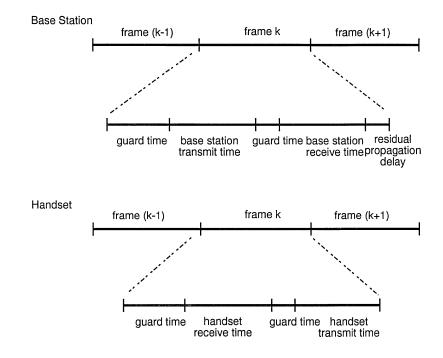

The transmitter and receiver operate in time-division duplex (TDD): handset and base station transmit and receive alternately. The TDD duty cycle lasts 4 ms and consists of the following events:

- At the beginning of the cycle, the frequency is changed (hopping)

- The base station transmits a frame of 144 bits while the handset receives

- The handset then transmits a frame of 148 bits while the base receives.

Figure 1. Basic Time Duplex Timing

### **Receive 1-Bit ADC**

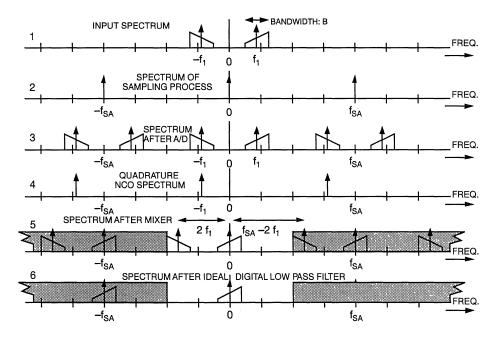

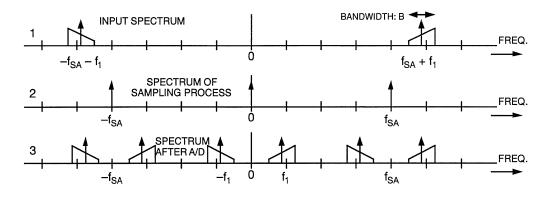

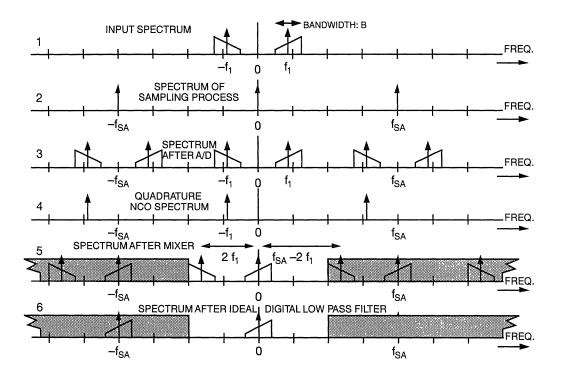

The incoming receive signal at the RX analog input pin is sampled by a 1-bit analog-to-digital converter at 8.192 MHz.

The receive signal is FSK-modulated (Frequency Shift Keying) with a carrier frequency of 10.7 MHz (Intermediate Frequency, or IF). The instantaneous frequency varies between 10.7 MHz plus or minus 32.58 kHz. Since the data rate is 93.09 kbps, there are 88 samples per data bit. This oversampled data is further processed by the demodulator to retrieve the baseband information.

The 1-bit converter is implemented with a fast comparator, which determines whether the RX signal is larger or smaller than a reference signal (VREF). The Z87000 internally generates the DC level of both VREF and RX input pins. The received signal at 10.7 MHz should thus be AC coupled to the RX pin via a coupling capacitor. To ensure accurate operation of the converter, the user should also attach to the VREF pin a network whose impedance matches the DC impedance seen by the RX pin.

#### Demodulator

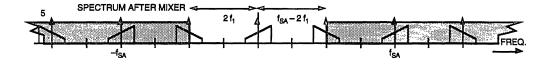

The demodulator includes a two-stage IF downconverter that brings the sampled receive signal to baseband.

The narrow-band 10.7 MHz receive signal, sampled at 8.192 MHz by the 1-bit ADC, provides a 2.508 MHz useful image. The first local oscillator used to downconvert this IF signal is obtained from a Numerically Controlled Oscillator (NCO) internal to the Z87000, at the nominal frequency of 460 kHz. The resulting signal is thus at 2.048 MHz (= 2.508 MHz - 460 kHz). A second downconversion by a 2.048 MHz signal brings the receive signal to baseband.

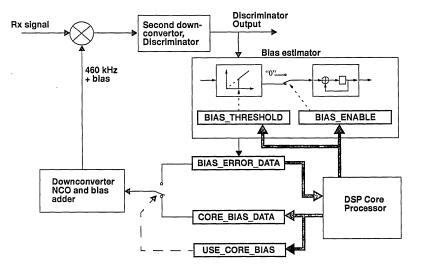

The exact frequency of the 460 kHz NCO is slightly adjusted by the Automatic Frequency Control (AFC) loop for exact downconversion of the end signal to the zero frequency. The AFC circuit detects any DC component in the output of the limiter-discriminator (see below) when receiving a known sequence of data (preamble). This DC component is called the "frequency bias". The bias estimate out of the AFC can be read by the DSP processor on every frame and subsequently filtered. The processor then adds or subtract this filtered bias to/from the NCO control word to correct the NCO frequency output.

Figure 2. Demodulator Block Diagram

The main element of the demodulator is its limiter-discriminator. The limiter-discriminator detects the frequency variations (ideally up to  $\pm$  32.58 kHz) and converts them to "0" or "1" information bits. First, the data is processed through low-pass filters to eliminate high frequency spurious components introduced by the 1-bit ADC. The resulting signal is then differentiated and fed to a matched filter. In the matched filter, an integrate-and-dump operation is performed to extract the digital information from its background noise.

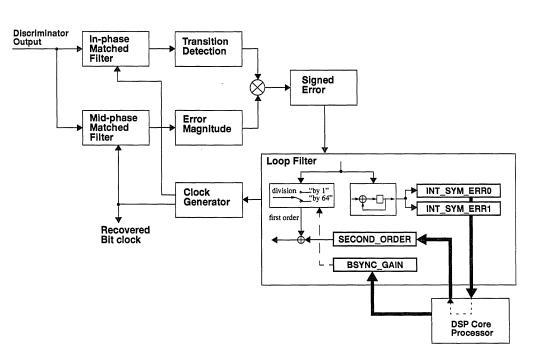

The symbol clock is provided by the bit synchronizer. The bit synchronizer circuit detects 0-to-1 and 1-to-0 transitions in the incoming data stream in order to synchronize a digital phase-lock loop (DPLL). The PLL output is the recovered bit clock, used to time the receiver on the base station, and both receiver and transmitter on the handset.

To ensure enough transitions in the voice data stream, a pseudo-random bit inversion operation is performed on the outgoing voice data. The inversion is then reversed on the demodulated data.

# FUNCTIONAL DESCRIPTION (Continued)

Since the data is packed in frames sent alternately from base and handset every 4 ms (TDD), additional synchronization means are necessary. This is realized in a frame synchronizer, based on detection of a "unique word" following the preamble.

The receiver also features a signal-to-noise ratio detector, which allows the DSP software to detect noisy channels and eliminate them from the frequency hopping cycle. The SNR information is also used by the Z87000 software as a measure the current range between handset and base station. This information allows the adaptive power control algorithm to provide sufficient output power to the RF transmitter.

#### **Receive Frame Counter**

The receive frame counter is responsible to keep track of time within the frame. It is initialized by the frame synchronizer logic on detection of the unique word. It is then clocked by the recovered bit clock from the bit synchronizer.

On the base station, the receive frame counter is used as time base for the receiver. On the handset, it is used as time base for both receiver and transmitter.

#### **Receive Rate Buffer and Voice Interface**

The voice signal is generated at the fixed rate of 32 kips by the Z87010 processor, and transmitted/received in bursts of 93.09 kips across the air. Data buffers in the transmitter and receiver are thus necessary to absorb the rate differences over time. These buffers are called "rate buffers". They can store up to 144 data bits and are organized as an array of 36 4-bit nibbles.

The receive rate buffer stores the received data from the demodulator. Incoming bits are arranged in 4-bit nibbles and transferred to successive locations of the rate buffer. When the last location is reached, transfers resume from the beginning (circular buffer). The system design guarantees that no buffer overrun nor enduring can occur.

The receive rate buffer can be read by the DSP core processor of the Z87000 or by the Z87010 chip. On the Z87000 side, the buffer can be read as a random-access memory: the processor writes the nibble address in an address register and reads the 4-bit data from a data register. On the Z87010 side, a voice processor interface logic handles the addressing to automatically present the successive voice nibbles to the Z87010 in the order they were received.

# Zilog

#### **Transmit Rate Buffer and Voice Interface**

The transmit rate buffer stores the data to be modulated. The data is sourced from the Z87010 or the Z87000 core processor. As for the receive rate buffer, the Z87010 sees a unique pipe to write to, while the Z87000 DSP core accesses the rate buffer as random-access memory. The modulator reads from the rate buffer as from a circular buffer.

#### **Transmit Frame Timing Counter**

On the handset, transmission does not start until the receiver has synchronized itself to the signal received from the base station. The transmission timing is based on the recovered clock. No additional counter is necessary.

On the base station, the situation is different. Transmission timing is based on a local clock, while the reception's timing is based on the clock recovered from the incoming received signal. Two counters, respectively clocked by local and recovered clocks, are necessary to track the transmit and receive signals.

Note that the receive clock on the base station tracks the handset's transmit clock, which is also the handset's receive clock and tracks the transmit clock of the base station. As a result, receive and transmit clocks of the base station have exactly the same frequency; only their phases differ.

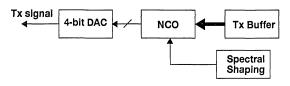

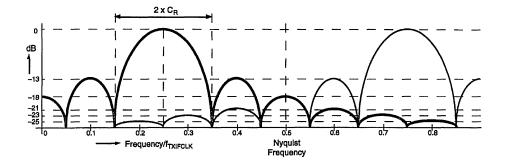

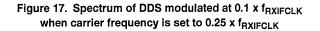

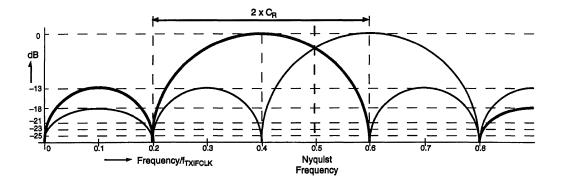

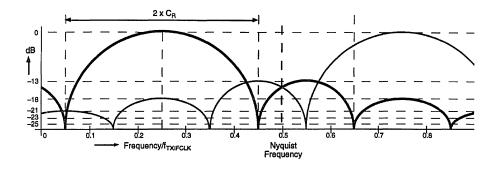

#### Modulator

The modulator consists of a numerically controlled oscillator (NCO) which generates an FSK (Frequency Shift Keying) signal at the carrier frequency of 2.508 MHz. The carrier frequency is shifted plus or minus 32.58 kHz for a "1" or a "0" data bit. To facilitate conformance to FCC regulations, the transitions from "1" to "0" or vice-versa are smoothed in order to decrease the amplitude of the side lobes of the transmit signal. In practice, the jump from one frequency to the next is performed in several smaller steps.

The carrier frequency is adjustable by the DSP core processor in order to provide additional frequency adjustment between base and handset. This is provided in case of a frequency offset too large for possible correction by the AFC.

The modulator also includes bit inversion logic as discussed in the receiver section.

Figure 3. Modulator Block Diagram

### Transmit 4-Bit DAC

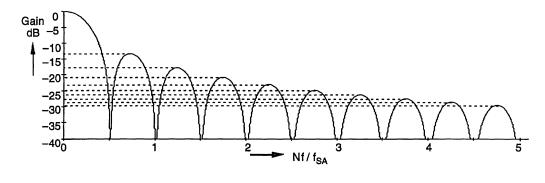

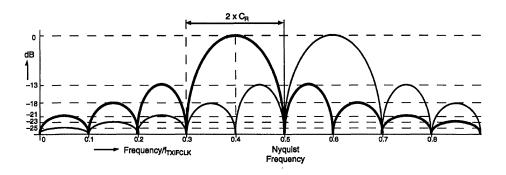

The transmit DAC clocks one new NCO value out of the Z87000 every 8.192 MHz period. Only the 10.7 MHz alias frequency component of the transmit signal (2.508 + 8.192 MHz image) is filtered, amplified and upconverted to the 900 MHz ISM band by the companion RF module.

### **Event Trigger Block**

The event trigger block is responsible for scheduling the different events happening at the bit and frame levels. The event trigger block receives input from the frame counters as well as the register interface of the DSP core processor.

The event trigger schedules the following events:

- Start of the 4 ms frame: a synthesizer load enable pulse is issued on the SYLE pin

- Power-up of the modulator section and transmission of the frame on handset and base station

- Use of the bit inversion as function of mode

- Power-up of the demodulator section and reception of the frame on handset and base station

- Control of RFTX and RFRX output pins, to be used as TDD control signals switching the antenna as well as transmitter and receiver chains on the RF module

- Control of RFEON pin, to be used as general on/off switch on the RF module

- Control of the Z87000 sleep mode

### 4-Bit DAC for Setting Transmit Power Level

In order to save battery life, the Z87000 only transmits the amount of RF power needed to reach the remote receiver with a sufficient SNR margin. The on-board transmit power 4-bit DAC provides 4 different voltage levels to the power amplifier in the RF module for that purpose. This DAC is directly controlled by the Z87000 software through an output register.

# 8-Bit ADC for Sampling the Received Signal Strength Indicator (RSSI)

RSSI information is typically generated from the last stage of the RF receiver. The RSSI is sampled once per frame by the 8-bit ADC and used by the Z87000 software to compute the necessary Transmit Power Level voltages.

#### **DSP Core Processor**

A DSP core processor constitutes the heart of the Z87000. The DSP runs the application software which performs the following functions:

- Register initialization

- □ Implementation of high-level phone features; control of phone user interface (keypad, Led, etc.)

- Control of the Z87010 ADPCM Processor

- □ Control of the phone line interface

- Ring detection by DSP processing

- □ Communication protocol between handset and base station supporting voice and signalling channels

- □ Control of the RF synthesizer and adaptive frequency hopping algorithm

- Control of the RF power and adaptive power algorithm

- Control of the demodulator (bit synchronizer loop filter, AFC bias estimate filtering)

- Control of the modulator (carrier frequency) and adaptive frequency alignment

- Signalling between base and handset to support above features

The DSP core is characterized by an efficient hardware architecture that allows fast arithmetic operations such as multiplication, addition, subtraction and multiply-accumulate of two 16-bit operands. Most instructions are executed in one clock cycle.

#### FUNCTIONAL DESCRIPTION (Continued)

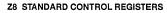

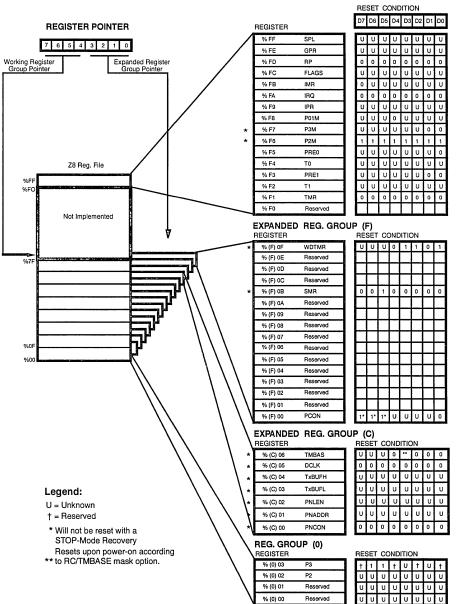

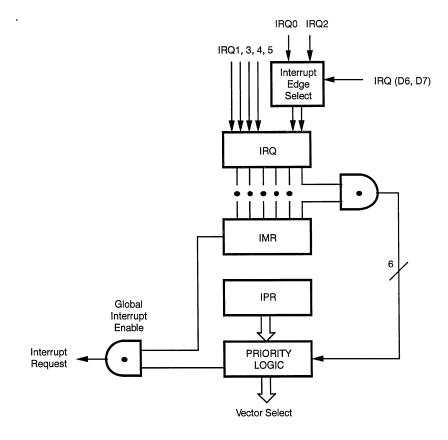

The DSP core is operated at the internal speed of 8.192 MHz. It has an internal RAM memory of 512 16-bit words divided in two banks. Six register pointers provide circular buffering capabilities and dual operand fetching. Three vectored interrupts are complemented by a six-level stack. One interrupt is used by the transceiver, while the two remaining vectors are mapped into port P1. In the phone system, one of these interrupts is customarily reserved for the Z87010 ADPCM Processor. The other interrupt can be used for custom purposes.

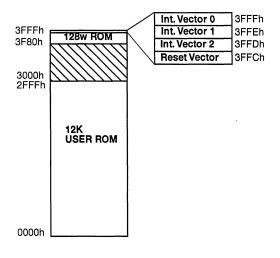

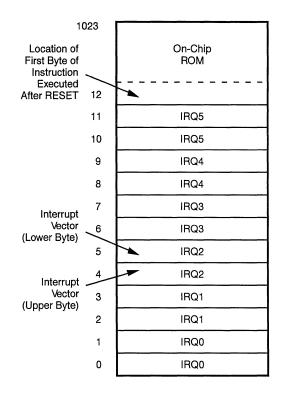

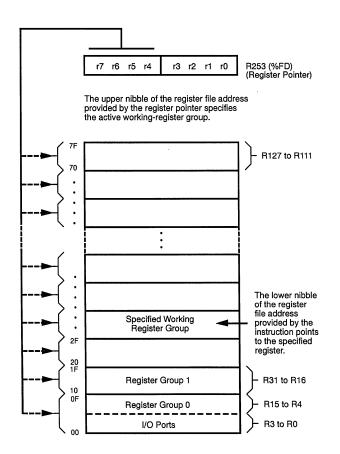

The Z87000 has a (12K+128) x 16-bit internal ROM including 4 words for interrupt and reset vectors. The ROM is mapped at addresses 0000h to 2FFFh, 3F80h to 3FFFh, as shown in Figure 13.

Figure 4. ROM Mapping

#### Two 16-Bit General-Purpose I/O Ports

Two 16-bit general-purpose I/O ports are directly accessible by the DSP core. These input and output pins are typically used for:

- Implementation of the phone's user interface (keypad, LED, optional display, etc.)

- Control of phone line interface (on/off hook, ring detect)

- Control of battery charging and detection of low battery conditions

- Implementation of additional features for customizing of the phone

#### Z87010 Interface

In addition to providing clock signals to the Z87010 processor, the Z87000 interfaces to the Z87010 through two different paths:

A command/status interface

#### A data interface

The command/status interface consists of two dual-port registers accessible by both Z87000 and Z87010 DSP core processors. On the Z87000 side, the registers are mapped into the DSP core processor's register interface. To allow access by the Z87010, the internal command/status registers can also be decoded on the pinto of the Z87000. Arbitration logic resolves access contentions.

The data interface allows the Z87010 processor direct access to the Z87000's receive and transmit rate buffers. The rate buffers are decoded on the pin to of the Z87000, and dedicated voice processor interface logic handles the addressing within the rate buffers.

The physical interface between Z87000 and Z87010 consists of an 8-bit data bus, a 3-bit address bus and control signals, as summarized in the following:

| VXDATA[7.0] | Data bus           |  |

|-------------|--------------------|--|

| VXADD[2.0]  | Address bus        |  |

| VXSTRB      | Data Strobe        |  |

| VXRWB       | Read/Write Control |  |

| VXRDYB      | Read Control       |  |

This bus is controlled by the Z87010. Although in the system the Z87010 is enslaved to the Z87000 master, at the physical level the Z87000 acts as a peripheral of the Z87010.

The mapping of the command status and data interfaces from the Z87010 side is given below.

| Interface               | Address<br>(VXADD [2.0]) | Read<br>/Write | Data<br>(VXDATA[7.0]) |

|-------------------------|--------------------------|----------------|-----------------------|

| Transmit<br>rate buffer | 1                        | W              | 3210                  |

| Receive<br>rate buffer  | 1                        | R              | 3210                  |

| Command                 | 0                        | R              | 76543210              |

| Status                  | 0                        | W              | 76543210              |

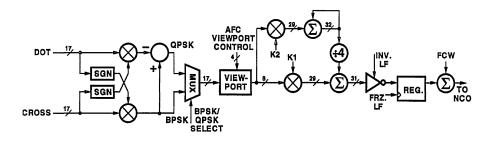

#### Automatic Frequency Control Loop (Receiver) and Modulator

#### AFC Loop

The AFC loop consists of a bias estimator block, which determines frequency offsets in the incoming signal, an adder, to add this bias to the 460 kHz frequency control word driving the NCO, and various interface points to the DSP core processor. In particular, the DSP can read the bias estimate data and substitute its own calculated bias value to the NCO.

The bias estimator accumulates the discriminator output values (image of instantaneous frequency) that exceed a programmable threshold (BIAS\_THRESHOLD). The processor can freeze the bias calculation any time by resetting the BIAS\_ENABLE control bit.

The accumulated bias, available in BIAS ERROR DATA, can be used directly to correct the NCO frequency. Alternately, the estimated bias can be read by the DSP, further processed, and written to the CORE\_BIAS\_DATA field. The DSP controls which value is used by setting the USE\_CORE\_BIAS field. The selected value is added to the 460 kHz signal which downconverts the receive IF signal.

The CORE BIAS DATA and BIAS\_ERROR DATA are two's complement numbers in units of 125 Hz.

In addition to correcting the difference in clock frequencies on the receiver using the AFC loop, a Z87000-base system can also modify the frequency of the remote transmit IF signals. The software has access to this frequency through the MOD\_FREQ register fields.

Figure 5. AFC Loop and Processor Control

### **Modulator Control**

The MOD\_FREQ fields specify the carrier center frequency (should be programmed to 2.508 MHz) and deviation for the FSK signal (should be programmed to  $\pm$  32.58 kHz). In addition, wave shaping is performed on bit transitions, in order to satisfy FCC regulations. Up to four different intermediate deviation values are programmable for each of the two FSK states. The MOD\_FREQ fields are programmable in units of 62.5 Hz.

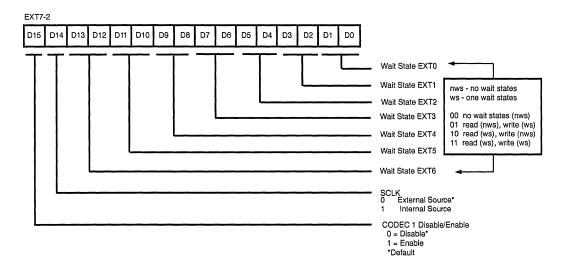

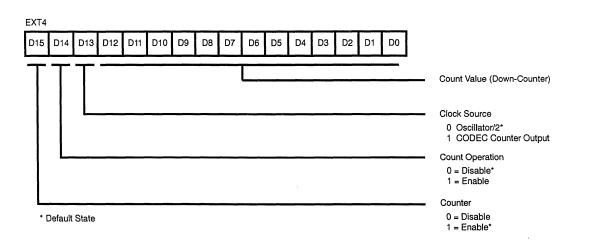

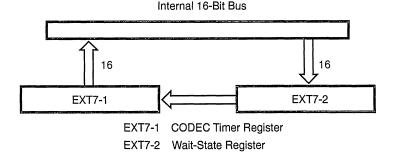

Table 1. AFC and Modulator Control Fields

| Field           | Register   | Bank | EXT  |

|-----------------|------------|------|------|

| BIAS_THRESHOLD  | CONFIG1    | 3    | EXT0 |

| BIAS_ENABLE     | SSPSTATE   | 3    | EXT2 |

| BIAS_ERROR_DATA | BIAS_ERROR | 2    | EXT2 |

| CORE_BIAS_DATA  | CORE_BIAS  | 2    | EXT4 |

# **Bit Synchronizer**

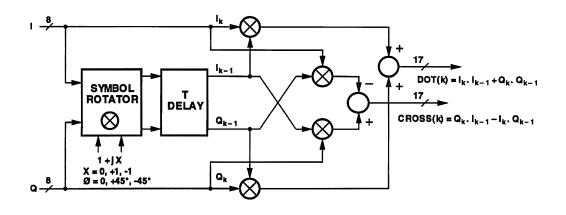

The bit synchronizer circuit is an implementation of the Data-Transition-Tracking Loop (DTTL), best described in "Telecommunications Systems Engineering", by W. Lindsey and M. Simon (Dover 1973; oh. 9 p. 442). Its operation is summarized in the following block diagram.

Figure 6. Bit Synchronizer Loop and Processor Control

The loop filter is controlled by the DSP core processor. The DSP core can implement a first order loop by setting the SECOND\_ORDER field to zero. Typically, the BSYNC\_GAIN would then be set to "divide-by-1" operation to provide a wide closed loop bandwidth and thus a quick acquisition of the bit clock. When the bit clock is in phase with the input data, the loop bandwidth can be narrowed to maintain tracking of the receive clock with minimum impact from signal noise. To reduce the loop bandwidth, the BSYNC GAIN can be set to "divide-by-64" the first order gain, while the integrated tracking error (available to the DSP in fields INT\_SYM\_ERR0 and INT\_SYM\_ERR1) can be used by the DSP software to adjust the SECOND ORDER term.

The bit synchronizer relies on transitions in the received bit stream to operate. The bit inversion logic guarantees enough transitions for all transferred data.

At the handset, the bit synchronizer must track both frequency and phase of the receive signal's data clock. At the base, only the phase must be tracked. The frequency is inherently correct since the base is the source of the system's data clock.

#### Table 2. Bit Synchronizer Control Fields

| Field        | Register     | Bank | EXT  |

|--------------|--------------|------|------|

| BYSNC_GAIN   | SSPSTATE     | 3    | EXT2 |

| INT_SYM_ERR1 | BIT_SYNC     | 1    | EXT2 |

| INT_SYM_ERR0 | INT_SYM-ERR0 | 0    | EXT6 |

| SECOND_ORDER | BIT_SYNC     | 1    | EXT2 |

### Frame Counters

The handset only has one frame counter, which times all receive and transmit events. The base station has distinct transmit and receive frame counters. When used in this document without any explicit reference to either base or handset, the terms "receive frame counter" and "transmit frame counter" refer to both sides. For the handset, both terms refer to the same unique counter.

The frame counters are clocked at the bit rate, or 93.09 kHz (2.048 MHz/22). Each count lasts one bit =  $1000/93.09 = 10.74 \ \mu$ s.

Each frame lasts 4 ms, which corresponds to (372 + 8/22) bits; the frame counters count from 0 to 371, with the last count lasting a bad longer than the other ones; at the end of count 371, the counters wrap around to 0.

The "hop" command pulse is asserted to pin SYLE during count "0" of the frame counter (transmit frame counter on the base station).

# Frame Synchronizer, Timings and RF Interface

The frame synchronizer tracks the received frames and resets the receive frame counter. The synchronization is performed by recognizing certain data patterns present in the receive bit stream: a comparison is done on the fly between the data pattern and the incoming bit stream; when the data match, the frame counter is reset.

Two possible 16-bit data patterns are pre-programmed in the Z87000. One is named UW (Unique Word) and is used in acquisition mode for first-time synchronization to an incoming signal. UW can also be used to track an acquired signal. The second pattern is named SYNC\_D and is used to track the received data frames while voice is being transferred. The transition from tracking UW to tracking SYNC\_D is controlled by the DSP processor through the SYNC\_SEARCH\_WORD field.

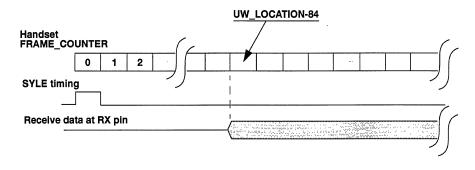

#### **UW Synchronization**

When the Z87000 matches the UW, the receive frame counter is reset to the value of UW\_LOCATION. This value is programmable by the DSP processor. On the handset, where the receive frame counter is used to derive all timings, UW\_LOCATION actually defines the guard time between the frequency hop command and the beginning of data reception, which starts at FRAME\_COUNTER = (UW\_LOCATION - 84) as shown in the next figure.

On the base station, data reception starts when the receive frame counter equals (UW\_LOCATION - 84), but this has less significance since the hop pulse is synchronized with the transmit frame counter and there is no fixed relationship between transmit and receive frame counters. On the base station, the UW\_LOCATION should be set to 301.

Figure 7. Frame Counter and UW\_LOCATION on Handset

Two modes of search are programmable through the SYNC\_SEARCH\_MODE field: "full search" and "window search". The full search is used by the handset when first acquiring the signal from the base station. In full search, the handset is in receive mode and continuously looks for a match with the UW. When a match is found and the time reference established (UW\_LOCATION is set), the DSP processor on the handset detects the synchronization (see below), switches to Time Division Duplex mode (TDD) and starts receiving and transmitting alternately. The search mode should also be switched to "window search" by the DSP software.

The window search mode only searches for a match in a certain time window centered around the expected match time. The window size is programmable by the DSP processor in the WINDOW\_SIZE field. If the matching does not occur at the expected time, due to so-called "bit slips", the receive frame counter timing is adjusted. Note: although the bit synchronizer is meant to keep track of time and prevent bit slips when the phone is operating continuously in TDD mode, bit slips are still possible when the handset is in standby mode, and only receives once in a while (see description of sleep mode).

### SYNC\_D Synchronization

When the DSP processor switches the Z87000 operation to voice mode, the frame synchronization parameters should be modified by the DSP software to:

- SYNC\_SEARCH\_MODE = window search

- SYNC\_SEARCH\_WORD = SYNC\_D pattern

In this mode, the receiver searches for the SYNC\_D pattern in windows of the incoming data stream. The window size is determined by the WINDOW\_SIZE field. The transition to voice mode proceeds in two steps, through an intermediate mode. The mode is set by the DSP processor by programming the MULTIPLEX\_SWITCH field. The three modes are:

- SMUX: initial mode. This mode allows acquisition, AFC operation, UW synchronization and signalling; ADPCM Processor access disabled; bit inversion disabled.

- STMUX: intermediate mode. This mode allows SYNC\_D frame synchronization and signalling; ADPCM Processor access disabled; bit inversion enabled.

- TMUX: voice mode. This mode allows voice transmission, SYNC\_D frame synchronization and signalling; ADPCM Processor access enabled; bit inversion enabled.

In order to detect synchronizations, the software has access to the SYNC\_ACQ\_IND status field. This field is set by the Z87000 matching hardware every time a match is detected within the right time window. The software must reset the "IND" bit by setting the SYNC\_ACQ\_CLEAR field.

In addition, the software can track the frame timing by reading the frame counter value, available in the FRAME\_COUNTER field. On the base station, where two frame counters are in use, this field returns the value of the transmit frame counter.

Every time the frame counter wraps around to 0, a frame start indicator bit is set (FRAME\_START\_IND status field). The software must reset this "IND" bit by setting the FRAME\_START\_CLEAR field. If the FS\_INT\_ENABLE bit is set, frame starts also trigger interrupts to the DSP processor.

1-28

The following table summarizes the fields allowing control of frame synchronization and basic frame timing.

Table 3. Frame Synchronizer Control Fields

| Field             | Register   | Bank | Ext  |

|-------------------|------------|------|------|

| SYNC_SEARCH-MODE  | SSPSTATE   | 3    | EXT2 |

| SYNC_SEARCH_WORD  | SSPSTATE   | 3    | EXT2 |

| UW_LOCATION       | RX_CONTROL | 2    | EXT1 |

| WINDOW_SIZE       | CONFIG1    | 3    | EXT0 |

| MULTIPLEX_SWITCH  | SSPSTATE   | 3    | EXT2 |

| SYNC_ACQ_IND      | SSPSTATUS  | 3    | EXT3 |

| SYNC_ACQ_CLEAR    | SSPSTATE   | 3    | EXT2 |

| FRAME_COUNTER     | SSPSTATUS  | 3    | EXT3 |

| FS_INT_ENABLE     | CONTROL    | 1    | EXT6 |

| FRAME_START_IND   | SSPSTATUS  | 3    | EXT3 |

| FRAME_START_CLEAR | SSPSTATE   | 3    | EXT2 |

| SYNC_SEARCH-MODE  | SSPSTATE   | 3    | EXT2 |

### **RF** Interface

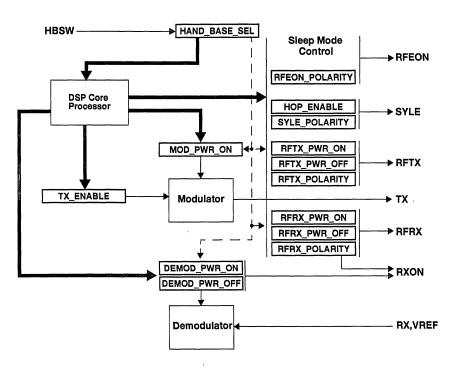

Several control fields are available in the Z87000 register set to control the timing and polarity of the RF module interface signals.

A first field, RFEON\_POLARITY, controls the polarity of the RFEON pin. This pin should be used to control the power of the RF module. It is asserted by the Z87000 when the RF module is in use, and de-asserted in sleep mode. The sleep mode is used by the handset to save battery life when no phone call is in process (See "Sleep mode" on page 21).

The SYLE pin (Synthesizer Load Enable), which carries a "load enable" pulse that tells an external RF synthesizer to generate the next RF channel, is controlled by two fields. The HOP\_ENABLE field is a global enable signal for the SYLE signals. The SYLE POLARITY field defines the polarity of the SYLE pin. The system designer should ensure that the leading edge of the SYLE pulse triggers channel hopping.

In addition to the SYLE signal, the interface to the most RF synthesizers includes two more input lines, "data" and "clock", for serial programming of the data values defining the RF channel. In order to allow interfacing to various popular synthesizers, the Z87000 does not have dedicated clock and data lines with fixed timing. Instead, two general I/O pins from ports P0 and P1 can be controlled in software by the DSP core to realize any particular interface timing. This flexibility is made possible by the high speed, singlecycle architecture of the DSP core.

The transmitter control includes a global enable signal for all transmit functions: TX\_ENABLE. The transmission start is controlled by the MOD\_PWR\_ON field. On the base station, the value programmed in MOD\_PWR\_ON is referenced to the transmit frame counter.

Two additional fields, RFTX PWR ON and RFTX PWR OFF, define the duty cycle of the RFTX output pin. On the base station, these fields are referenced to the transmit frame counter. The RFTX\_POLARITY bit defines the polarity of the RFTX pin. This pin can be used to control the transmit section and power amplifier of the external RF module.

On the receive side, two fields define the internal timing of the receiver. The start of reception is controlled by the DEMOD\_PWR\_ON field. Stop of reception (and receiver power down) is controlled by the DEMOD\_PWR\_OFF field. On the base station, these fields are referenced to the receive frame counter. The RXON output pin follows the timing defined by the DEMOD PWR ON and OFF fields.

RFRX PWR ON Two additional fields. and RFRX\_PWR\_OFF, define the duty cycle of the RFRX output pin. On the base station, these fields are referenced to the TRANSMIT (!) frame counter. The RFRX\_POLARITY bit defines the polarity of the RFRX and RXON pins. The RFRX pin can be used to control the receive section of the external RF module.

### **OPERATION** (Continued)

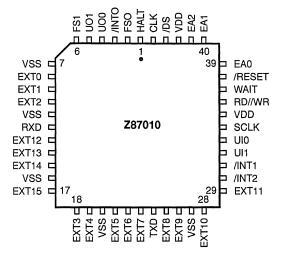

The various timing control registers reviewed in this paragraph should be programmed differently for handset and base station. If the same ROM code is used on base and handset, the software can determine which station it runs on by reading the HAND\_BASE\_SEL bit, which reflects the state of the HBSW pin. The following figure and table summarize the RF interface control fields.

| Field            | Register       | Bank | Ext  |

|------------------|----------------|------|------|

| RFEON_POLARITY   | RX_PWR_CTRL    | 2    | EXT6 |

| HOP_ENABLE       | SSPSTATE       | 3    | EXT2 |

| SYLE_POLARITY    | CONFIG1        | 3    | EXT0 |

| TX_ENABLE        | SSPSTATE       | 3    | EXT2 |

| MOD_PWR_ON       | MOD_PWR_CTRL   | 2    | EXT5 |

| RFRX_PWR_ON/OFF  | RFRX_PWR_CTRL  | 0    | EXT7 |

| DEMOD_PWR_ON/OFF | DEMOD_PWR_CTRL | 2    | EXT6 |

| RFRX_POLARITY    | RFRX_PWR_CTRL  | 0    | EXT7 |

| RFTX_PWR_ON/OFF  | RFTX_PWR_CTRL  | 2    | EXT7 |

| RFTX_POLARITY    | RFTX_PWR_CTRL  | 2    | EXT7 |

| HAND_BASE_SEL    | SSP_STATUS     | 3    | EXT3 |

1-30

#### Zilog

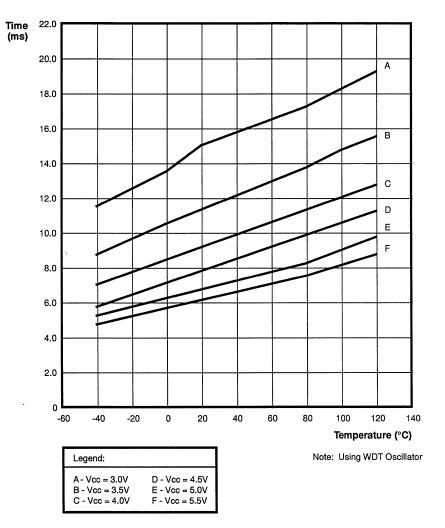

### Sleep Mode

To save the phone's battery life on the handset, the Z87000 can be operated in sleep mode while the phone is not in use. The sleep mode is entered by software command. The sleep mode first needs to be enabled by setting the SLEEP\_WAKE field. Then a GO\_TO\_SLEEP command puts the processor to sleep by temporarily stopping its clock. The sleep period can be set to last between 4 ms and 1.02 s by programming the SLEEP\_PERIOD field. In sleep mode, the RFEON pin is de-asserted.

The processor comes out of sleep mode in one of two ways. Either the sleep counter counts down to zero, or one of the enabled pins from port P0 is asserted prior to normal expiration of the counter. Four port pins (P0[0..4]) can be individually enabled to provide the wake-up function by setting the appropriate bits in P0\_WAKE\_ENABLE. Typically, these port pins are connected to the telephone keypad.

When the processor core wakes up, the software needs to know how much time it was actually asleep, in order to restore synchronization to the base station's hopping sequence. For that purpose, the current value of the sleep counter is available to the processor in SLEEP\_REMAINING. A value of zero indicates normal expiration of the sleep counter.

In order to guarantee a good operation of the wake-up pins, the wake-up signals are hardware-denounced by the Z87000. Furthermore, these signals are internally synchronized to the bit clock. This ensures that the processor has enough time (one bit time = 10.74 ms) to read a stable value of the remaining sleep time and synchronize correctly to the base station's hopping sequence.

| Table 5. | . Sleep Mode Control Fie |      |  |

|----------|--------------------------|------|--|

| Field    | Register                 | Bank |  |

| Field            | Register | Bank | Ext  |

|------------------|----------|------|------|

| SLEEP_EAKE       | SSPSTATE | 3    | EXT2 |

| GO_TO_SLEEP      | SSPSTATE | 3    | EXT2 |

| SLEEP_PERIOD     | CONFIG2  | 3    | EXT1 |

| SLEEP_REMAINING  | CONFIG2  | 3    | EXT1 |

| P0_WAKEUP_ENABLE | CONTROL  | 1    | EXT6 |

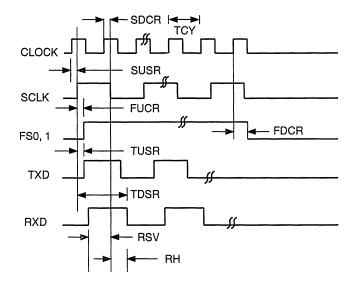

### ADPCM Processor Interface and Rate Buffers

The interface to the ADPCM Processor (Z87010) consists of clock control, command/status interface and data interface. The data interface gives the ADPCM Processor access to the rate buffers.

### **Clock Interface**

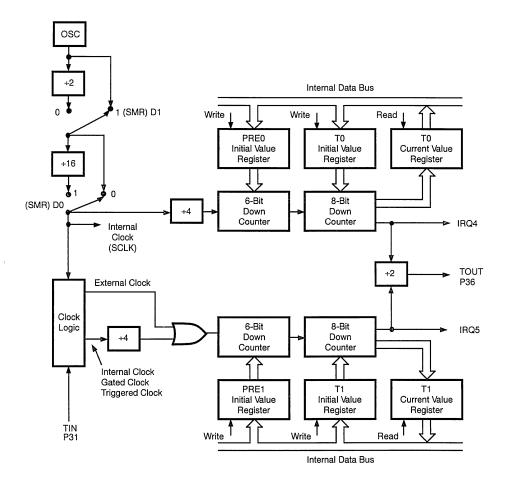

The Z87000 generates the Z87010 clock at 16.384 or 8.192 MHz, as set in VP\_CLOCK. In addition, the clock can be stopped and restarted with the VP\_STOP\_CLOCK field in order to reduce power consumption (Note: a software handshaking between Z87000 and Z87010 is necessary before stopping and after restarting the clock).

In addition to providing the Z87010 main clock, the Z87000 generates a CODCLK signal which will be used by the codec and by the Z87010 to synchronize its data transfers with the Z87000. On the base station, the CODCLK is simply obtained by dividing the 16.384 MHz input clock.

On the handset, the CODCLK is synchronized to the base station's CODCLK signal through the receive bit sync logic. This ensures that production and consumption of voice data is happening at identical rates on handset and base, eliminating buffer overrun and underrun situations.

### **Command/Status Interface**

The Z87000 sends commands to the Z87010 through the VP\_COMMAND write-only field. It reads the Z87010 status in the VP\_STATUS read-only field. Both fields are located at the same address in the Z87000 register interface. A communication protocol should be established in software to ensure correct reception of all commands. Dedicated hardware ensures data integrity when both Z87000 and Z87010 simultaneously access the same register.

#### Table 6. ADPCM Processor Control Fields

| Field           | Register | Bank | Ext  |

|-----------------|----------|------|------|

| VP_CLOCK        | CONFIG1  | 3    | EXT0 |

| VP_STOP_CLCOCKS | SSPSTATE | 3    | EXT2 |

| VP_COMMAND      | VP_INOUT | 2    | EXT0 |

| VP_STATUS       | VP_INOUT | 2    | EXT0 |

### **Data Interface and Rate Buffers**

The digitized voice data is communicated between the Z87000 and Z87010 through the rate buffers and ADPCM Processor data interface. The transmit and receive rate buffers each contain 36 4-bit nibbles.

To write to the transmit rate buffer, the Z87000 core processor must first set the nibble address in the TX\_BUF\_ADDR register field, then write the nibble data through TX\_BUF\_DATA. If the TX\_AUTO\_INCREMENT bit is set, the address is automatically incriminated (modulo 51 = the number of nibbles in rate buffer + 15 additional data words accessible through TX\_BUF\_DATA; for more information, see Register Description) after each data write. This allows the DSP core to write successive nibbles without resetting the address each time.

### **OPERATION** (Continued)

The operation of the receive rate buffer is identical. The Z87000 core processor must set the nibble address in RX\_BUF\_ADDR, then read the nibble from RX\_BUF\_DATA. If the RX\_AUTO\_INCREMENT bit is set, the read address is automatically incriminated (modulo 36 = number of nibbles in rate buffer) after each data read. This allows the DSP core to read successive nibbles without resetting the address each time.

Through its register interface, the Z87000 also controls which rate buffer addresses the Z87010 ADPCM Processor can access. The nibble addresses are contained in the TX\_BUF\_VP\_ADDR and RX\_BUF\_VP\_ADDR register fields. After the Z87010 writes or reads a nibble to or from transmit or receive rate buffer, the corresponding "VP\_ADDR" is automatically incriminated (modulo 36) to the next accessible address. The locations of accessible addresses are individually controlled by the Z87000 in the three TX\_RX\_NIBBLE\_MARKER register fields. A marker bit equal to "1" enables the Z87010 to access the corresponding address; a bit equal to "0" causes the Z87010's read or write access to skip to the next nibble that has a marker bit equal to "1".

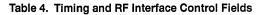

Figure 9. Rate Buffers Access and ADPCM Processor Interface

Table 7. Data and Control Access to Rate Buffers

| Field               | Register      | Bank | Next |

|---------------------|---------------|------|------|

| RX_AUTO_INCREMENT   | RATE_BUF_ADDR | 1    | EXT0 |

| RX_BUF_ADDR         | RATE_BUF_ADDR | 1    | EXT0 |

| TX_AUTO_INCREMENT   | RATE_BUF_ADDR | 1    | EXT0 |

| TX_BUF_ADDR         | RATE_BUF_ADDR | 1    | EXT0 |

| RX_BUF_DATA         | RATE_BUF_DATA | 1    | EXT0 |

| TX_BUF_DATA         | RATE_BUF_ADDR | 1    | EXT1 |

| TX_BUF_DATA         | RATE_BUF_DATA | 1    | EXT1 |

| RX_BUF_VP_ADDR      | RATE_BUF_DATA | 1    | EXT1 |

| TX_BUF_VP_ADDR      | RATE_BUF_DATA | 1    | EXT1 |

| TX_RX_NIBBLE_MARKER | RATE_BUF_DATA | 1    | EXT1 |

## **Additional Features**

### **Power Control**

The Z87000 features several means of measuring and controlling power levels. One input pin (RSSI) connects an external "receive signal strength indicator" to a half flash 8bit ADC in the Z87000. This ADC is sampled once per frame during the receive portion of the TDD cycle. The RSSI value can be accessed in software in the RSSI\_DATA register field. With external multiplexing, the 8-bit ADC can be used for additional purposes.