# PROGRAMMER'S LANGUAGE MANUAL

9002

MICROCOMPUTER TERMINAL SYSTEM

Zentec Part No. 88-403-01 REV B

# PROGRAMMER'S LANGUAGE MANUAL 9002 MICROCOMPUTER TERMINAL SYSTEM

Zentec Corporation 2390 Walsh Avenue Santa Clara, California 95050

## **Table of Contents**

|     |                                                                                                                                                          | Page           |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.0 | Introduction                                                                                                                                             | 1              |

| 2.0 | System and Software Organization                                                                                                                         | 2              |

|     | <ul><li>2.1 Memory Organization</li><li>2.2 The Basic ROM</li><li>2.3 List Structure</li><li>2.4 Device Operation</li></ul>                              |                |

| 3.0 | Hardware and Software Register                                                                                                                           | 4              |

|     | <ul><li>3.1 Hardware Registers</li><li>3.2 Software Registers</li></ul>                                                                                  | 5              |

| 4.0 | System List Structures                                                                                                                                   | 6              |

| 5.0 | System Basic Sub-Routines                                                                                                                                | 8              |

|     | <ul><li>5.1 Cursor Move Routines</li><li>5.2 Viewable Screen Functions</li><li>5.3 Microcomputer Routines</li><li>5.4 Two-Page Option Routines</li></ul> | 11<br>15<br>22 |

| 6.0 | Device Oriented Routine                                                                                                                                  | 23             |

|     | 6.1 ZENTEC 9002 Keyboard                                                                                                                                 |                |

| 7.0 | System Support Routines                                                                                                                                  | 24             |

|     | <ul><li>7.1 ZENTEC Assembler</li><li>7.2 ZIM</li></ul>                                                                                                   |                |

| 8.0 | Appendix                                                                                                                                                 | 35             |

### **List of Illustrations**

|            |                                         | Page  |

|------------|-----------------------------------------|-------|

|            | FIGURES                                 |       |

| Figure 2–1 | System Memory Organization              | 3     |

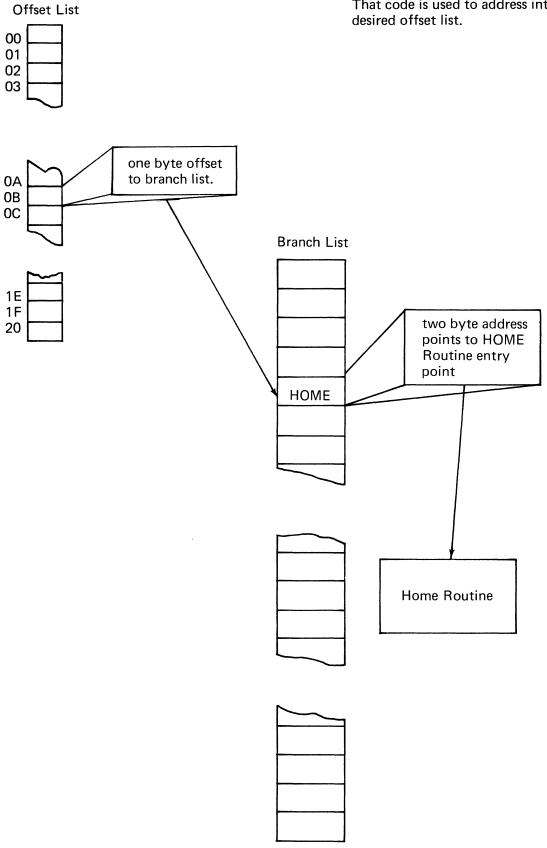

| Figure 4—1 | Branch & List Geographical Descriptions | 7     |

|            | TABLES                                  |       |

| Table 7–1  | Operation Codes                         | 25-32 |

#### 1.0 INTRODUCTION

The intent of this document is to give the Assembly Language programmer the information necessary to program the Zentec 9002 Display System.

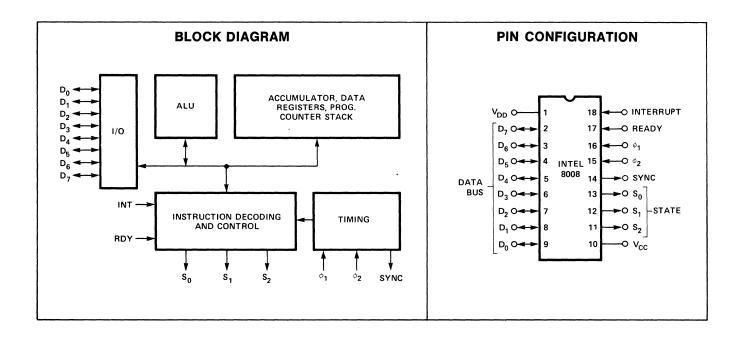

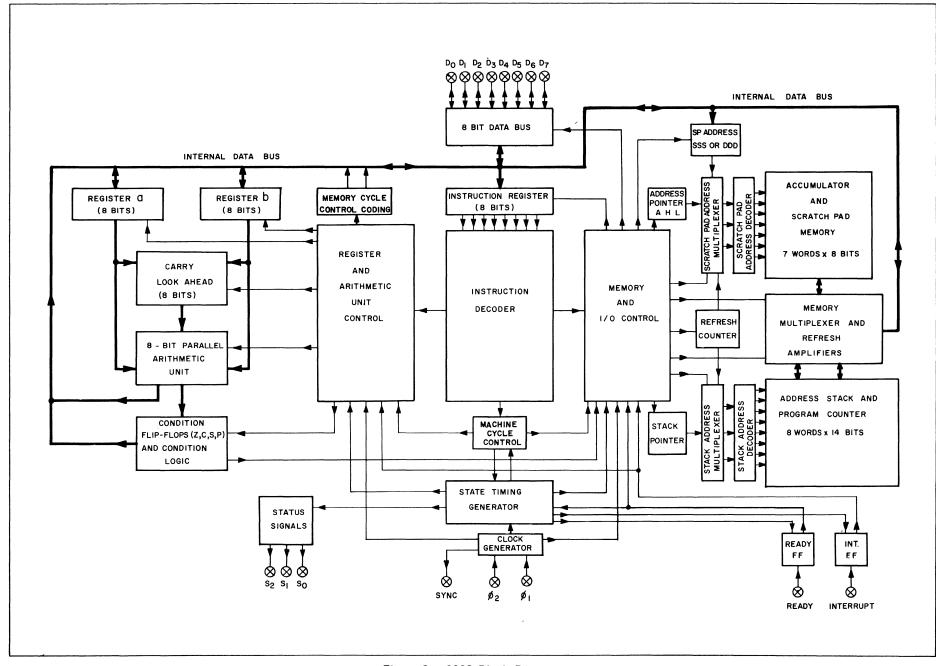

The Zentec 9002 Display System uses the Intel 8008 microcomputer. The information presented in this document may not be meaningful unless the reader is familiar with the Intel 8008. The instruction set of the Intel 8008, as described in the MCS-8 Users Manual is OCTAL oriented. The Zentec 9002 is oriented to hexadecimal representation. Appendix 7-A contains a cross-reference from the 9002 Assembler Language to the INTEL instruction set. Machine codes are included, in both binary (OCTAL form) and in hexadecimal form.

The purpose for hexadecimal code is to relate programmers to other hexadecimal systems as all IBM systems and Interdata machines. No attempt has been made to relate to OCTAL representation except that which appears in Appendix 7-A.

The Intel machine uses RAM which is data destructive when power is removed. In order to protect the code that is necessary for system operation, Read Only Memory (ROM) and Programmable Read Only Memory (PROM) are used. In Section 2.0 the memory organization is described. It is described in terms of decimal addresses but in fact we use hexadecimal addresses internally. The system is essentially arranged in 4 sections of 4,096 decimal bytes each. The first section is devoted to ROM code. The second section is devoted to the refresh RAM that is displayed on the screen. The last two sections are optional RAM space for use by customers for their own application code or for use with the disk option or as telecommunication buffers. Figure 2–1 graphically describes the memory organization.

Hardware and software registers are described in Section 3.0. They are described in some detail and should be carefully studied by the application programmer so that he is aware of the precise meanings of the registers and their locations.

Section 4.0 describes the system list structures. List structures are a convenient mechanism to reduce the amount of code and the amount of space necessary to not only perform functions but to easily change functions. This technique is used throughout Zentec 9002 system code. Appendix 4-0-A graphically describes a list path.

Section 5 describes all the Basic Systems Sub-routines. These routines have been built to support the system package already developed and have been designed to be used by the application programmer in developing his own modules. Each routine acts as a closed sub-routine and is described separately. The term "registers affected" describes all the registers that are modified by the specific function. Any registers not modified can be used to store data during the function operation without expectation of that data being destroyed. The term "example" indicates the Zentec assembler mnemonic to perform that function. The term "results" describes the values that can be expected in the registers at the completion of that function operation. Where relevant, software registers that have been modified, with identifiable results, are depicted.

Section 6.0 describes Device Oriented Routines. It is our intent to describe code sequences, in Zentec assembler format, for all supported devices. This will include key-board handling, disk operation, telecommunications and printer use. The routines described will not necessarily be the ones used by the system but will be tested and can be used directly by the application programmer.

Section 7.0 System Support Routines will describe in detail each of the Zentec packages designed to support the application programmer.

#### 2.0 SYSTEM AND SOFTWARE ORGANIZATION

#### 2.1 Memory Organization

Three forms of memory exist in the 9002: ROM, PROM and RAM. The first 4096 bytes are committed to ROM or PROM. The basic ROM, a set of sub-routines designed for both system and user use is located from decimal address 2048 to 4095. The Tele-Communications package (GT1) is also a ROM, and is located at decimal address 0 to 2047. Locations 0 through 511 decimal hold the 9002 executive, the branch list, and five offset lists.

The space from 4096 thru 16383 is system structured as RAM, although parts of that space can be used as additional ROM or PROM area for customer optioned routines. Hardware and programming registers and system RAM work space is located at 4096 to 4143. The display control line, always the bottom line on the screen, is located in the next eighty bytes from 4144 to 4223. The first page of the display, 1920 bytes, or 24 lines of 80 characters each, is located at 4224 to 6143. The optional second page of 1920 bytes is located at 6144 to 8063. The next 48 bytes, from 8064 to 8111 are reserved for additional hardware and software registers to support optional devices. The space from 8112 thru 8191 is available for user use and is a part of the second page option. The space from 8192 through 16383 is available as additional user RAM space, however the Super Text option will reside from 14,336 through 16,383.

#### 2.2 The Basic ROM

The Basic ROM is a set of forty odd sub-routines designed to reduce programming effort in handling data on the screen and in performing terminal oriented functions. The ROM takes up precisely 2048 bytes. The routines were intended for use by the system, but are in fact easily used by application programmers. Section 5.0 describes these routines and how they are entered.

#### 2.3 List Structure

The 9002 system list structures were designed to reduce programming effort by providing an easily changed, easily added to mechanism to perform desired system functions. A new routine can be inserted at any available location. To insert the routine in the list structure requires two bytes to specify the entry point of the new routine, as well as a single byte offset for each offset list the function is to be related. The current list structures are keyboard RS-232 or merely byte oriented. The advantage to the list approach is the ease of maintenance and ease of entry of new routines within the system. See Section 4.0 for more detailed list information.

#### 2.4 Device Operation

The 9002 system does not use the Intel 8008 family input/output instructions. Devices are instead tied to RAM registers which are interrogated by the system program, and where appropriate by the user program, as necessary. As an example, all keyboard entered characters appear at a single byte location in the memory (X'1002'). It is the programmer's responsibility to see that his programs are written to access the keyboard input byte often enough to guarantee no loss of keyboard information.

As mentioned previously, the hardware takes a passive role in system operation in that the program has almost complete control of system operation, exclusive of RAM and screen refresh. This philosophy gives the programmer significant freedom in performing operations, but added responsibility in accomplishing tasks.

| 0-2047          | System Executive and Lists GT1 - Tele-Communications |

|-----------------|------------------------------------------------------|

| Hex (0000-01FF) | GTT - Tele-Communications                            |

| 2048-4095       | Basic ROM                                            |

| Hex (0800-0FFF) |                                                      |

| 4096-6143       | Hardware and Software Registers                      |

| Hex (1000-17FF) | Display Page One                                     |

| 6144-8191       | Display Page Two                                     |

| Hex (1800-1FFF) | Optional Device Registers                            |

| 8192-10239      | Additional RAM                                       |

| Hex (2000-27FF) |                                                      |

| 10240-12287     | Additional RAM                                       |

| Hex (2800-2FFF) |                                                      |

| 12288-14335     | Additional RAM                                       |

| Hex (3000-37FF) | / dartional 11/10                                    |

| 14336-16383     | Additional RAM                                       |

| Hex (3800-3FFF) | or Optional ROM                                      |

Figure 2—1 SYSTEM MEMORY ORGANIZATION

#### 3.0 HARDWARE AND SOFTWARE REGISTERS

All system registers are located in RAM. The reason: To allow programs, both system and application, to be able to control system supported devices such as the display, the keyboard, the RS-232 interface, and certain optional interfaces.

#### 3.1 HARDWARE REGISTERS

- 3.1.1 Cursor The cursor register is a two byte register. The first byte establishes the row or line member, and the second byte refers to the column. In the standard machine, the row number can range from X'00' to X'18'. Row number X'00' is reserved for the control line. With the two-page option, the row value range is X'00' to X'4F', or eighty bytes. The cursor register is located at X'1000' and X'1001'. Values in these registers are generated by programming.

- 3.1.2 Keyboard Input The keyboard input register is located at X'1002'. It is theoretically possible to get 255 different codes through this register. One code, X'FF', is used as the normal quiesced state for this register and cannot be used as an input code. The standard keyboard, using upper and lower case with control characters generates 128 codes. By depressing the control key and any alpha key (and a few special characters), an additional 32 characters can be generated. The eleven key numeric pad generates an additional eleven codes. Thus the standard keyboard provides 171 out of the possible 255 acceptable codes. The keyboard input register has no overrun protection. That is, if multiple characters are keyed and the program in control does not use them, the succeeding keystroked characters overlay one another. No indication of overrun exists. After each character is accepted by the/a program, an X'FF' value should be loaded into the register by the program. Characters can be inserted through the keyboard at a maximum rate of sixty characters per second.

- 3.1.3 Function Register The function register currently has but one use: an error beep. When the high-order or left-most bit of this register is 'changed', an error tone is produced for approximately two seconds. The bit transition, from off to on or on to off triggers the error tone. All other bits in the function register are reserved. The function register is located at X'1003'.

- 3.1.4 Prior Condition Register The prior condition register is used to establish the initial screen polarity and blinking characteristics for the line scans. Special control characters placed within the refresh RAM area will vary the screen polarity, tone and blinking characteristics, but it is necessary to establish 'initial' conditions or the first refresh RAM location of each line of the screen would be committed to establishing 'current' screen characteristics. The high-order 3 bits, bits numbered 7, 6 and 5 are reserved and must be zero. Bit 4 is used to establish an underscore; Bit 3 is used to make data appear as blanks; Bit 2 reverses screen polarity from dark background to light background; Bit 0 provides a half-tone value for dark background polarity; and Bit 1 provides blinking characters. The prior condition register is located at X'1004'.

- 3.1.5 Page Register The page register is used to adjust the screen window of 24 lines to any contiguous set of 24 lines within the range of 48 lines available when the double-page option is in the system. The lowest value acceptable in this register is X'00', but under system operating conditions should not be less than X'01'. The high value should be held at X'19'. Any value above X'19' will give unexpected, unacceptable results. The page register is changed from value X'01' for page one to X'19' for page two. It is varied by the value at location X'1010' to perform scrolling.

3.1.6 RS-232 — The RS-232 interface is made up of six byte registers: a one byte input buffer; a one byte output buffer; a one byte input flag register; a one byte output flag register; a one byte input sense register; and a one byte output sense register. The RS-232 interface operates one byte at a time, and ranges in speed from 110 baud to 9600 baud. One RS-232 is standard, and a second dual RS-232 is optional. The standard RS-232 is located at X'100C' thru X'100F' and X'102E' and X'102F'.

#### 3.2 SOFTWARE REGISTERS

- 3.2.1 Branch Area The branch area is used by the system executive to cause branches into the various function routines in the system. It is located at X'1008' thru X'100A'. Location X'1008' must always contain a X'44'.

- 3.2.2 TAS The third address (TAS) is a two byte field used as a temporary work area for 16 bit values. Two of the basic routines use TAS. TAS overlays the value portion of the Branch Area. It is located at X'1009' and X'100A'.

- 3.2.3 Scroll Value The scroll value is the amount added to or subtracted from the value in the Page Register to vary the starting line of data on the screen. This value is X'02' unless modified by the user. The scroll value is located at X'1010'.

- 3.2.4 Input Buffer Pointer The system executive supports a five position buffer to smooth keyboard input. The input buffer pointer holds the next available buffer address. The input buffer pointer is located at X'1011'.

- 3.2.5 Protected Cursor Flag The protected cursor flag is used to allow the cursor to be positioned under a protected character. The flag is tested as zero or non-zero. The protected cursor flag is located at X'1012'.

- 3.2.6 Line Space Count The line space count is used to speed character inserts. This value defines the number of available spaces from the last character, on the line holding the cursor, to the end of the line. This value is used exclusively in 'insert' sub-mode. The line space count is located at X'1014'.

- 3.2.7 Local Mode Save The local mode save location holds the code representing the mode and sub-mode that was in control prior to entering 'Control' mode. It is used to reestablish the proper mode and sub-mode at return from 'Control' mode. The local mode save is located at X'1015'.

- 3.2.8 Current Mode The current mode code is maintained for program control and list control purposes. It is located at X'1016'.

- 3.2.9 Character Previous Hold The character previous hold maintains the value of the last keyboard character acted upon. It is used for special double-character sequences. It is located at X'1017'.

- 3.2.10 Character Current Hold The character current hold maintains the value of the keyboard character currently being processed. It is located at X'1018'.

- 3.2.11 Keyboard Input Buffer The keyboard input buffer is a five byte buffer used by the system to support keyboard input at its maximum rate, while allowing functions of various speeds to be performed. The keyboard buffer is located at X'1019' thru X'101E'.

- 3.2.12 FAS The first address (FAS) is a two byte field used to hold the 16 bit binary value of the current cursor address. All cursor manipulation programs operate with FAS, and the value then converted into Row and Column values which are then inserted into the cursor hardware registers. FAS is located at X'1020' and X'1021'.

- 3.2.13 SAS The second address (SAS) is a two byte field used as a temporary work area for 16 bit values, A number of the basic routines use SAS. SAS is located at X'1022' and X'1023'.

- 3.2.14 Open work areas Locations X'1024' thru X'102D' are used by various basic routines as unnamed temporary work spaces. All unspecified locations in the area from X'1000' thru X'102F' are reserved for future hardware options and for programming enhancements.

#### 4.0 SYSTEM LIST STRUCTURES

The Intel 8008 family use a two byte address for all calls and branches. The two byte address is, of course, the starting point of a programmed routine. The 9002 system strings all function or routine addresses together in one contiguous list, two bytes per entry. This list is the branch list and is the backbone of the 9002 list structure. Whenever a new routine is created, its initial entry point address is attached to the branch list. To acquire any specific address, one would need only the offset in bytes from the start of the branch list and the address of the start of the branch list. The value generated by summing these two values is the address of the pointer to the routine desired. To get to any desired routine then one merely needs a list of offsets because the system branch list address is known. In the 9002 standard system, five offset lists exist; one for each mode and sub-mode REP and INS FORM, REP and INS TEXT and one for the Control Mode. The 9002 offset lists are each 33 bytes in length. The first 32 offsets (one byte each) are directly related to the value of the 32 function codes generated from the keyboard. The function code keys generate hexadecimal numbers from X'00' to X'1F'. As an example, the 'HOME' key generates a code of X'0B'. Therefore it would be appropriate to place the 'HOME' routine branch table offset into the twelfth or 'OB'th entry of the desired offset list. When the 'HOME' key is depressed, and the desired offset list is entered, the 'HOME' routine address offset is found. Summing that offset value with the start of the branch table generates the address of the two byte field whose value is the address of the start of the 'HOME' routine. By picking up that address and inserting it properly in a branch instruction, that branch can be executed to enter (and perform) the 'HOME' routine function. As stated, the first 32 bytes of each offset list are associated with the codes generated by pressing the 32 keyboard function keys. The 33rd entry is the offset to the address in the branch table of all other keyboard keys. The branch list, and each of the offset lists must in and of themselves be contiguous but they may be separated from each other. See Figure 4-1 for graphical description.

Home key, when depressed creates a 'OB' code as keyboard input character. That code is used to address into the desired offset list.

Figure 4—1

BRANCH & LIST GEOGRAPHICAL DESCRIPTION

#### 5.0 SYSTEM BASIC SUB-ROUTINES

#### 5.1 CURSOR MOVE ROUTINES

#### CRIGHT Moves Cursor One Position to Right.

Moves cursor (on screen) one position to right. If cursor is at last column to right, cursor is moved to first position to left of the next line. If cursor is on last available line at last column, cursor is moved to first position of first line. Cursor will automatically bypass any 'protected' byte locations, unless location X'1012' is non-zero.

Registers affected — All.

Example - Call CRIGHT.

Results — All registers indeterminate. Both actual, terminal cursor registers and binary cursor location (FAS) are properly up dated. Where double-page option exists, page adjustment to cursor position is also up dated.

#### 5.1-1

#### CLEFT Moves Cursor One Position to Left.

Moves cursor (on screen) one position to left. If cursor is at first column to left, cursor is moved to last column on right of next preceding line. If cursor is on first line, first column to left (true HOME) it will not be moved. Unless location X'1012' is non-zero, cursor will not stop at a 'protected' byte location, but will continue going left. If True Home is found to be protected, cursor will search right and stop at first available not protected byte location.

Registers affected — All.

Example — Call CLEFT.

Results — All registers indeterminate. Both actual, terminal cursor registers and binary cursor location (FAS) are up dated. Where double-page option exists, page adjust is also made.

CUP Moves Cursor One Line Up.

Moves cursor (on screen) one line up. If cursor is already at top-most line, it will not be moved. Cursor will not stop at a protected byte unless location X'1012' is non-zero. Attempt to move cursor to top-line, if it is protected, and location X'1012' is zero, will result in cursor moving to right on top line until a non-protected byte location is found.

Registers affected - All

Example - Call CUP

Results — All registers indeterminate. Hardware cursor registers (X'1000-1001') and software cursor register (FAS) are up dated. Where double-page option exists, adjustment is made automatically.

5.1-3

CDOWN Moves Cursor One Line Down

Moves cursor (on screen) one line down. If cursor is at bottom-most line, it is moved to top-most line. Cursor will not stop at a protected byte, unless location X'1012' is non-zero.

Registers affected — All.

Example - Call CDOWN.

Results — All registers indeterminate. Hardware cursor registers (X'1000-1001') and software cursor register (FAS) are up dated. Where double-page option exists, page adjustment is made automatically.

5.1-4

RETURN Moves Cursor to first position next line.

Moves cursor from current position to the left-most position of next line. If current cursor position is on last displayable line, cursor is moved to true HOME. Cursor will not stop at protected byte but will scan right to first non-protected location.

Registers affected — All.

Example — Call RETURN.

Result — All registers indeterminate. Hardware and software cursor registers up dated. Where necessary, page is adjusted.

HOME Cursor is moved to HOME location.

Cursor is moved from current location to left-most position, top-line of current screen image. If that position is protected, cursor will scan right until first unprotected byte is found.

Registers affected - All.

Example - Call HOME.

Result — All registers indeterminate. Hardware and software cursor registers up dated.

5.1-6

TAB Move Cursor to Next Tab Stop.

Cursor is moved from current location to next tab stop to right. If there are no more stops on the line, or if no stops exist, the cursor is moved to the left-most position. of the next line. In this case it always acts precisely like RETURN.

Registers affected — All.

Example - Call TAB.

Result — All registers indeterminate. Hardware and software cursor registers are up dated.

5.1-7

BTAB Move Cursor to Next Previous Tab Stop.

Cursor is moved from current location to next previous tab stop. If the next previous tab stop on this line is a protected byte, the cursor will scan right to the first available non-protected byte.\* If there is no next previous tab stop on this line, or no tab stops at all, the cursor will move to the left-most position of the current line. If already at the left-most position, the cursor will move to the last position of the next preceding line and scan left. In no case will the cursor move past true HOME in its backward scan.

Registers affected — All.

Example — Call BTAB.

Result — All registers indeterminate. Hardware and software cursor registers are updated.

\* The cursor cannot ever move left past a protected byte at the tab stop location, by using this function.

#### ATAB Auto Tab Forward.

Moves the cursor to the right to the first unprotected byte beyond the next set of protected byte (s). If the right scan searches beyond the last displayable character, the cursor is set at true HOME.

Registers affected — All.

Example — Call ATAB.

Result — All registers indeterminate. Hardware and software cursor registers are updated.

5.1-9

#### ABTAB Auto Tab Backward.

Moves the cursor to the left past the next preceding set of protected byte (s), and past all the unprotected bytes until it reaches the left-most byte of that unprotected set. If at initial cursor scan, the next preceding byte is not protected, the scan ends at the left-most byte of the current unprotected set.

Registers affected — All.

Example - Call ABTAB.

Result — All registers indeterminate. Hardware and software cursor registers are updated.

#### 5.2 VIEWABLE SCREEN FUNCTIONS

CLEAR Clears all viewable memory.

Clears all viewable memory to blanks. No exceptions.

Registers affected — All.

Example - Call CLEAR.

Result — All registers indeterminate. Cursor is repositioned to true Home location. Where necessary first page is set. All cursor registers are up dated.

NEWFRM Clears viewable memory of all unprotected data.

All viewable memory with exception of Control line and protected bytes is cleared to blanks.

Registers affected - All

Example — Call NEWFRM.

Result — All registers indeterminate. Cursor is repositioned to true Home. Where necessary, first page is set. All cursor registers are up dated.

5.2-2

EOS Erase to End of Screen.

Blanks screen from current cursor location to last screen displayable position. Protected bytes are not blanked unless the value at X'1016' is X'80' or greater.

Registers affected — All.

Example - Call EOS

Result – All registers indeterminate. Cursor remains at same position.

5.2-3

EOL Erase to End of Line.

Blanks screen from current cursor location to end of line. Protected bytes are not blanked unless the value at X'1016' is X'80' or greater.

Registers affected — All.

Example - Call EOL.

Result — All registers indeterminate. Cursor remains at same location.

#### BLANK Screen Blanking, Protected and Unprotected.

That portion of the screen ranged from the value (binary address) in FAS up to but not including the value in SAS is blanked. Both protected and unprotected areas are blanked. Indeterminate results can be expected if the value in FAS is not less than that in SAS.

Registers affected - All.

Example — After establishing FAS and SAS, Call BLANK.

Result — All bytes in the area specified are changed blanks (X'20'). Register values at completion are indeterminate.

5.2-5

#### CMESSA Control Label Insertion.

The control label at the extreme lower right of the visible screen is loaded by this routine. Any new label can be loaded to that area by specifying the address of the right-most byte of an eight position label, in the register pair H and L. Then call this routine.

Registers affected — All.

Example — LBI RH, (label address +7) LBI RL, (label address +7) Call CMESSA.

Result — Register values at completion are indeterminate. The new label appears properly.

5.2-7

#### DELBYT Delete Byte.

Deletes byte at cursor location, and moves all data to the right, to the end of the line or to the next protected byte to the left one byte. The last byte on the line or the last unprotected byte in the current field is then blanked.

Registers affected — All.

Example — Call DELBYT.

Result – All registers indeterminate. Cursor is not moved.

#### DELFLD Delete Field.

From current cursor location, a scan is made to the left until either the start of line is reached or a protected byte is found. Then the scan is made to the right until either the end of line is reached or a protected byte is found. Within the established range, all unprotected bytes are blanked. The cursor is then repositioned at the left-most unprotected byte of the range.

Registers affected — All.

Example - Call DELFLD.

Result — All registers indeterminate. Hardware and software cursor registers are up dated.

5.2-9

#### INSERT Insert Byte.

From the current cursor location, all data to the right, to the end of the line or to the next set of protected byte (s), is moved right one position. If the last position on the line was affected, that last position is changed to a blank. The keyed character is then inserted at the current cursor location. The cursor is advanced automatically.

Registers affected — All.

Example - Call INSERT.

Result — All registers indeterminate. Cursor position advanced one position to right.

5.2-10

#### DLINE Delete Line.

Cursor is moved to extreme left position of current line. A search is made of successive lines to find an all blank line. When found, all lines from the one following the cursor line, up to and including the all blank line are moved up one line. Thus all following moved lines overlay their next preceding line. If no all blank line is found, the last line is blanked at completion of the move. If the cursor is on the last line, it is blanked.

Registers affected — All.

Example - Call DLINE.

Result — All registers indeterminate. Hardware and software cursor registers are updated.

ILINE Insert Blank Line.

Cursor is moved to extreme left position of current line. A search is made of successive lines to find an all blank line. When found, all preceding lines, up to and including the cursor line are moved down one line. The cursor line is then blanked. If no all blank lines are found, the last available line is blanked, and operation proceeds normally. If the cursor is on the last available line, the move is not performed, the last line is blanked, the routine is exited normally.

Registers affected - All.

Example - Call ILINE.

Result — All registers indeterminate. Hardware and software cursor registers are up dated.

5.2-12

#### 5.3 MICROCOMPUTER ROUTINES

#### LDFAS Load First Address

The two byte value at address X'1020' is the absolute binary address of the current cursor location. It is known as FAS, or First Address. As the binary counterpart of the current cursor location is used so often, FAS has special load and store routines. Calling LDFAS will load the H and L registers with the value in FAS. That value will also be loaded in registers D and E.

Registers affected -D, E, H and L.

Example — Call LDFAS.

- Result The value in FAS (assume X'189C') will be loaded into registers D and E and also registers H and L. Register D will contain X'18', E will contain X'9C', H will contain X'18', and L will contain X'9C'.

- Other A portion of the LDFAS routine can be used to load registers H and L from almost any addressable memory pair (note exception), by loading the address of the value desired into registers H and L, and then performing a call to location LDFAS +4.

Example – LBI RH, XX LBI RL, YY

Call LDFAS +4

Where XX is the high order byte of the desired location and YY is the low order byte of the desired location.

- Result Same as in basic LDFAS routine, register pair D and E, H and L are loaded with the value located at XX YY.

- Exception Load results will be indeterminate, and almost certainly wrong, if the memory pair addressed crosses a hexadecimal century boundary, i.e. if the memory address to be loaded ends in X'FF'.

STFAS Store First Address.

The two byte value in register pair H and L is stored at FAS (absolute binary address X'1020').

Registers affected – D, E, H and L.

Example - Call STFAS.

Result — At completion, FAS contains value that was in register pair H and L. Register pair D and E also contains value originally in H and L. Register pair H and L contains the address of FAS +1.

Other — A portion of the STFAS routine can be used to store the value in register pair D and E into FAS.

Example - Call STFAS +2.

Result — Same as basic STFAS result.

5.3-2

#### LDSAS Load Second Address

The two byte space at address X'1022' is used as temporary storage by a significant number of the Basic Call routines. Calling LDSAS will load the register pair H and L with the value in SAS.

Registers affected -D, E, H and L.

Example - Call LDSAS.

Result — The value in SAS will be loaded in register pairs D and E, and H and L.

5.3-3

STSAS Store Second Address.

The two byte value in register pair H and L is stored at SAS (absolute binary address X'1022').

Registers affected — D, E, H and L.

Example — Call STSAS.

Result — At completion, SAS and the register pair D and E will contain the value initially held in register pair H and L. H and L will contain the address of SAS+1.

LDTAS Load Third Address.

The two byte space at address X'1009' is used at temporary storage by several Basic Call routines. Calling LDTAS will load the register pair H and L with the value in TAS.

Registers affected - D, E, H and L.

Example - Call LDTAS.

Result – The value in TAS will be loaded into register pairs D and E, and H and L.

STTAS Store Third Address.

The two byte value in register pair D and E is stored at TAS (absolute binary address X'1009').

Registers affected -D, E, H and L.

Example — Call STTAS.

Result — At completion, TAS and the register pair D and E will contain the value initially held in register pair D and E. Register pair H and L will contain the address of TAS+1.

5.3-6

LDCURS Load Cursor.

The two byte terminal cursor value (discontinuous binary — column and row) located at X'1000' is loaded into the register pair D and E.

Registers affected — D, E, H and L.

Example — Call LDCURS.

Result — At completion, the register pair D and E contain the value from memory address X'1000'. Register pair H and L contain the value X'1000'.

BUMPHL Increase value in registers H and L by one.

The two byte binary value in register pair H and L is increased by one.

Registers affected — H and L.

Example - Call BUMPHL.

Result – 16 bit binary value in register pair H and L increased by one.

5.3-8

DECHL Decrease value in registers H and L by one.

The two byte binary value in register pair H and L is decreased by one.

Registers affected - H and L.

Example - Call DECHL.

Result – 16 bit binary value in register pair H and L decreased by one.

5.3-9

SUBREG Subtract paired register value from another paired register value.

Subtracts 16 bit value in register pair B and C from 16 bit value in register pair D and E and stores 16 bit result in register pair B and C.

Registers affected -A, B, C, D, and E.

Example — After establishing registers B, C, D and E,

Call SUBREG.

Result — Registers D and E will remain as they were just prior to entry to this routine. Registers D and C will hold the new result value.

CONV Converts Binary Cursor Value in FAS to Hardware Cursor Value.

Takes the 16 bit binary current cursor value from FAS, and converts it to row and column discontinuous binary value of terminal, and stores the value in the terminal Hardware register for showing the cursor on the screen.

Registers affected - All.

Example - Call CONV.

Result — Registers A, B, C are indeterminate. Paired registers D and E will contain the new Hardware cursor value, and paired registers H and L will contain the value X'1001'.

5.3-11

RECON Generates Binary Cursor value in FAS from value in Hardware Cursor Register.

Takes the Row/Column current Hardware cursor value and converts it to a 16 bit binary value and stores that value at FAS.

Registers affected — All.

Example - Call RECON.

Result — Registers A, B and C are indeterminate. Register pair D and E contain the new 16 bit binary value representing the current cursor location, and register pair H and L contain the address of FAS+1.

5.3-12

COMPER 16 bit Comparator Routine with High, Low or Equal Results.

The value in register pair B and C is compared against the value in register pair D and E. At completion, Register B holds the High, Low or Equal result.

Registers affected -A, B, C, D and E.

Example — After loading the values to be compared in register pairs B, C and D, E then,

Call COMPER.

Result — Register A is indeterminate. Registers C, D, E, H and L are unchanged. Register B contains:

X'02' if value in register pair D and E is numerically greater than value in B and C.

X'01' if value in register pair D and E is less than value in B and C.

X'00' if values are equal.

ADD2 Adds single byte value to double byte value.

Performs addition of value in register C to value in register pair D and E. Results are placed in register pair D and E.

Registers affected -A, D and E.

Example — After loading 16 bit value in registers D and E, and loading add value in register C, then,

Call ADD2.

Result — Register A is indeterminate. Registers B, C, H, and L are not changed. Register pair D and E contain the new value.

#### 5.3-14

SUBT2 Subtracts single byte value from double byte value.

Performs subtraction of value in register C from value in register pair D and E. Results are placed in register pair D and E.

Registers affected -A, D and E.

Example — After loading 16 bit value in registers D and E, and loading subtract value in register C, then,

Call SUBT2.

Result — Register A is indeterminate. Registers B, C, H, and L are not changed. Register pair D and E contain the new value.

#### 5.3-15

RMOVE Moves Data in RAM, low-order to high-order addresses.

Moves from minimum of one byte to maximum of 256 bytes from any addressable area in memory to any RAM location(s) in memory. The move is byte by byte, moving the leftmost byte of the 'from' block to the leftmost byte location of the 'to' block first, then incrementing addresses and moving each additional byte until all bytes of move have been made. Register pair D and E must be loaded with the starting location of the 'to' block. Register pair H and L must be loaded with the starting location of the 'from' block. Register C is loaded with the value X'01' to X'FF' to move from 1 to 255 bytes. Loading register C with X'00' will cause 256 bytes to be moved.

Registers affected — All.

Example — After loading register pair H and L with the 'from' location, and after loading register pair D and E with the 'to' location, and after loading register C with move count then,

Call RMOVE.

Result — Register A and B are indeterminate. Register C is X'00'. Register pair D and E point to the last byte plus one of the 'to' area. Register pair H and L point to the last byte plus one of the 'from' area.

5.3-16

LMOVE Moves Data in RAM, high-order to low-order addresses.

Moves from minimum of one byte to maximum of 256 bytes from any addressable area in memory to any RAM location(s) in memory. The move is byte by byte, moving the rightmost byte of the 'from' block to the rightmost byte location of the 'to' block first, then decrementing addresses and moving each additional byte until all bytes of move have been made. Register pair D and E must be loaded with the starting location of the 'to' block. Register pair H and L must be loaded with the starting location of the 'from' block. Register C is loaded with the value X'01' to X'00' will cause 256 bytes to be moved.

Registers affected - All.

Example — After loading register pair H and L with the 'from' location, and after loading register pair D and E with the 'to' location, and after loading register C with move count, then,

Call LMOVE.

Result — Registers A and B are indeterminate. Register C is X'00'. Register pair D and E point to the last byte moved minus one, of the 'to' area. Register pair H and L point to the last byte minus one of the 'from' area.

5.3-17

SMOVE Special Move for data going to Control Line.

The Control Line (bottom line of screen — always) has a special function associated with the high-order bit of each byte on that line (Addresses X'1030' - X'107F'). The Special Move inserts data on that line without affecting the high-order bits. In all other respects this move is treated as an 'LMOVE' function. Thus, data moved to the control line must be addressed from the right side rather than the left, etc. See LMOVE for additional information.

Registers affected — All.

Example — After loading register pair D and E with the 'to' location, and loading register pair H and L with the 'from' location, and loading register C with move count,

Call SMOVE.

Result — See LMOVE for results.

5.3-18

#### 5.4 TWO-PAGE OPTION ROUTINES

UPAGE Show Page Two on Screen.

Hardware page register (X'1005') is set to X'19'.

Registers affected - H, L.

Example — Call UPAGE.

Result – Register pair H and L contain X'1005'.

Note — Two page option required.

DPAGE Show Page One on Screen.

Hardware page register (X'1005') is set to X'01'.

Registers affected — H, L.

Example - Call DPAGE.

Result – Register pair H and L contain X'1005'.

Note — Two page option required.

DSCROL Scroll page data downward.

Screen view 'window' of data is moved upward, but page data appears to move downward. Hardware page register value is decreased by value in location X'1010'. Page register value may not be less than X'.01'.

Registers affected -A, B, C, H and L.

Example - Call DSCROL.

Result — Registers A, B and C are indeterminate. Register pair H and L contain X'1005'.

Note - Two page option required.

USCROL Scroll page data upward.

Screen view 'window' of data is moved downward, but page data appears to move upward. Hardware page register value is increased by value in location X'1010'. Page register value may not exceed X'19'.

Registers affected -A, B, C, H and L.

Example - Call USCROL.

Result — Registers A, B and C are indeterminate. Register pair H and L contain X'1005'.

Note - Two page option required.

5.4-4

#### 6.0 DEVICE ORIENTED ROUTINE

The routines in this section are tested and can be used either directly or as examples by the interested programmer. Routines similar to these are used in the ZENTEC 9002 where necessary.

#### 6.1 ZENTEC 9002 KEYBOARD

Instructions in this example routine are written in ZENTEC assembler format. A translator table between the ZENTEC assembler statements and INTEL's MCS-8 statements will be found in Appendix 7A.

The following is a 'CALLed' sub-routine.

\* Keyboard Character Pick Routine

| PICK  | LBI  | RH, 10 | Load Registers H and L with Keyboard Input Register Address |

|-------|------|--------|-------------------------------------------------------------|

|       | LBI  | RL, 02 |                                                             |

| PICKA | LB   | RA     | Load Accumulator from Memory                                |

|       | CI   | RA, FF | Is NULL character present?                                  |

|       | BE   | PICKA  | Yes, then branch and try again                              |

|       | STBI | M, FF  | Store the NULL character                                    |

|       | RET  | •      | Return with Data Character in Register A                    |

This routine will hang the CPU until a character appears from the keyboard.

7.0 System Support Routines

7.1 ZENTEC Assembler

Table 7–1

Operation Codes

#### **OPERATION CODES:**

| ZENTEC ASSEMBLY<br>STATEMENT |                           | MCS-8<br>EQUIVALENT       | MCS-8<br>BINARY CODES<br>OCTAL FORM |   | HEXADECIMAL |

|------------------------------|---------------------------|---------------------------|-------------------------------------|---|-------------|

| Load                         | Register – Data moves fro | om 2nd Register into 1st. |                                     |   |             |

| LR                           | RA,RA                     | LAA                       | 11 000 000                          | = | C0          |

|                              | RA,RB                     | LAB                       | 11 000 001                          | = | C1          |

|                              | RA,RC                     | LAC                       | 11 000 010                          | = | C2          |

|                              | RA,RD                     | LAD                       | 11 000 011                          | = | C3          |

|                              | RA,RE                     | LAE                       | 11 000 100                          | = | C4          |

|                              | RA,RH                     | LAH                       | 11 000 101                          | = | C5          |

|                              | RA,RL                     | LAL                       | 11 000 110                          | = | C6          |

| LR                           | RB,RA                     | LBA                       | 11 001 000                          | = | C8          |

|                              | RB,RB                     | LBB                       | 11 001 001                          | = | C9          |

|                              | RB,RC                     | LBC                       | 11 001 010                          | = | CA          |

|                              | RB,RD                     | LBD                       | 11 001 011                          | = | СВ          |

|                              | RB,RE                     | LBE                       | 11 001 100                          | = | CC          |

|                              | RB,RH                     | LBH                       | 11 001 101                          | = | CD          |

|                              | RB,RL                     | LBL                       | 11 001 110                          | = | CE          |

| LR                           | RC,RA                     | LCA                       | 11 010 000                          | = | D0          |

|                              | RC,RB                     | LCB                       | 11 010 001                          | = | D1          |

|                              | RC,RC                     | LCC                       | 11 010 010                          | = | D2          |

|                              | RC,RD                     | LCD                       | 11 010 011                          | = | D3          |

|                              | RC,RE                     | LCE                       | 11 010 100                          | = | D4          |

|                              | RC,RH                     | LCH                       | 11 010 101                          | = | D5          |

|                              | RC,RL                     | LCL                       | 11 010 110                          | = | D6          |

| LR                           | RD,RA                     | LDA                       | 11 011 000                          | = | D8          |

|                              | RD,RB                     | LDB                       | 11 011 001                          | = | D9          |

|                              | RD,RC                     | LDC                       | 11 011 010                          | = | DA          |

|                              | RD,RD                     | LDD                       | 11 011 011                          | = | DB          |

|                              | RD,RE                     | LDE                       | 11 011 100                          | = | DC          |

|                              | RD,RH                     | LDH                       | 11 011 101                          | = | DD          |

|                              | RD,RL                     | LDL                       | 11 011 110                          | = | DE          |

| LR                           | RE,RA                     | LEA                       | 11 100 000                          | = | E0          |

|                              | RE,RB                     | LEB                       | 11 100 001                          | = | E1          |

|                              | RE,RC                     | LEC                       | 11 100 010                          | = | E2          |

|                              | RE,RD                     | LED                       | 11 100 011                          | = | E3          |

|                              | RE,RE                     | LEE                       | 11 100 100                          | = | E4          |

|                              | RE,RH                     | LEH                       | 11 100 101                          | = | E5          |

|                              | RE,RL                     | LEL                       | 11 100 110                          | = | E6          |

| LR                           | RH,RA                     | LHA                       | 11 101 000                          | = | E8          |

|                              | RH,RB                     | LHB                       | 11 101 000                          | = | E9          |

|                              | RH,RC                     | LHC                       | 11 101 001                          | = | EA          |

|                              | RH,RD                     | LHD                       | 11 101 010                          | = | EB          |

|                              | RH,RE                     | LHE                       | 11 101 011                          | = | EC          |

|                              | RH,RH                     | LHH                       | 11 101 100                          | = | ED          |

|                              | RH,RL                     | LHL                       | 11 101 101                          | = | EE          |

|                              | 111,111                   | LIIL                      | 11 101 110                          | _ | LL          |

|         | EC ASSEMBLY<br>EMENT                                        | MCS-8<br>EQUIVALENT                           | MCS-8<br>BINARY CODES<br>OCTAL FORM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | HEXADECIMAL                            |

|---------|-------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| LR      | RL,RA<br>RL,RB<br>RL,RC<br>RL,RD<br>RL,RE<br>RL,RH<br>RL,RL | LLA<br>LLB<br>LLC<br>LLD<br>LLE<br>LLH<br>LLH | 11 110 000 = 11 110 001 = 11 110 010 = 11 110 011 = 11 110 100 = 11 110 101 = 11 110 110 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | F0<br>F1<br>F2<br>F3<br>F4<br>F5       |

| Load E  | Syte — Data moves from Memory                               | to Register                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

| LB      | RA<br>RB<br>RC<br>RD<br>RE<br>RH<br>RL                      | LAM<br>LBM<br>LCM<br>LDM<br>LEM<br>LHM<br>LHM | 11 000 111 = 11 001 111 = 11 010 111 = 11 100 111 = 11 101 111 = 11 101 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 110 111 = 11 11 | C7<br>CF<br>D7<br>DF<br>E7<br>EF       |

| Store E | Byte — Dtat moves from Register                             | to Memory                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

| STB     | RA<br>RB<br>RC<br>RD<br>RE<br>EH<br>EL                      | LMA<br>LMB<br>LMC<br>LMD<br>LME<br>LMH<br>LMH | 11 111 000 = 11 111 001 = 11 111 010 = 11 111 110 = 11 111 101 = 11 111 110 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | F8<br>F9<br>FA<br>FB<br>FC<br>FD<br>FE |

| Load E  | Byte Immediate — Immediate to I                             | Register                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

| LBI     | RA,nn<br>RB,nn<br>RC,nn<br>RD,nn<br>RE,nn<br>RH,nn<br>RL,nn | LAI<br>LBI<br>LCI<br>LDI<br>LEI<br>LHI<br>LLI | 00 000 110 = 00 001 110 = 00 010 110 = 00 101 110 = 00 101 110 = 00 101 110 = 00 110 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 06<br>0E<br>16<br>1E<br>26<br>2E<br>36 |

| Store I | Byte Immediate — Immediate to                               | Memory                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

| STBI    | M,nn                                                        | LMI                                           | 00 111 110 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3E                                     |