# 1981 PRODUCT HANDBOOK

# WESTERN DIGITAL PRODUCT HANDBOOK

1

## Making The Leading Edge Work For You

This is our first complete Product Handbook and, naturally, we're proud of it. We're proud of the products detailed in these pages. We're proud of our people, who have taken these products from concept to market. And we're proud of the hundreds of Western Digital customers who have used these products to achieve a competitive advantage in their own markets.

The rate of innovation in this industry is breathtaking. And Western Digital has played an important role in the microelectronic revolution. Our guiding principle though, goes beyond extending the limits of the leading edge; we're dedicated to making the leading edge *work*. The proof is in our products.

And like our products, this handbook has been designed with you in mind. We've gone to great lengths to make it complete, accurate and useful. Now we would like your critical appraisal, to help us improve it. And our products. Let me hear from you directly. Or use the postcard at the back at this handbook.

harts Masse

Charles W. Missler Chairman of the Board President and Chief Executive Officer

# EDGE INDEX

### **TELECOMMUNICATIONS DIVISION**

## COMPUTER PRODUCTS DIVISION

## ADVANCED SYSTEMS DIVISION

### CONTROL SYSTEMS DIVISION

GENERAL INFORMATION Quality Assurance Package Data Representatives and Distributors Terms of Sale

## **FUNCTIONAL INDEX**

## **TELECOMMUNICATIONS DIVISION**

| Part Number | Description                                                   | Page |

|-------------|---------------------------------------------------------------|------|

| TR1402      | Programmable UART                                             | 17   |

| TR1602      | Programmable UART                                             | 17   |

| TR1863      | Programmable UART                                             | 17   |

| TR1865      | Programmable UART                                             | 17   |

| PR1472      | Programmable SAR                                              | 25   |

| PR1482      | Programmable SAT                                              | 39   |

| FR1502      | FIFO Buffer Register                                          | 55   |

| UC1671      | ASTRO—Full Duplex Synch or Asynch                             | 67   |

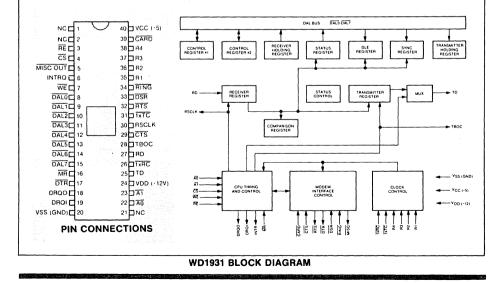

| WD1931      | ASTRO—Compatible with SDLC                                    | 81   |

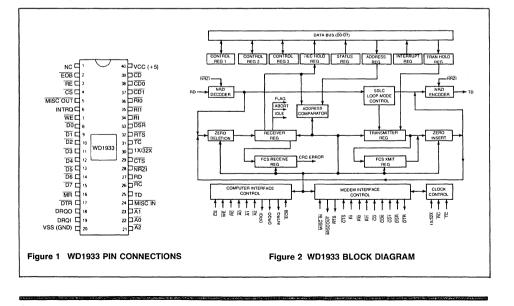

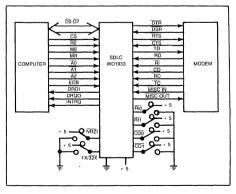

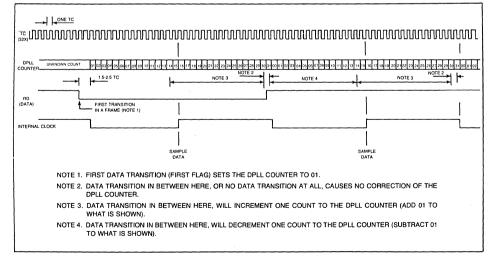

| WD1933      | SDLC—Parallel to Synch Serial                                 | 99   |

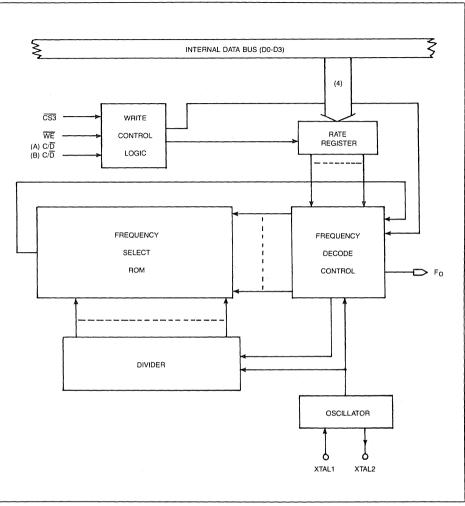

| BR1941      | Dual Baud Rate Generator                                      | 115  |

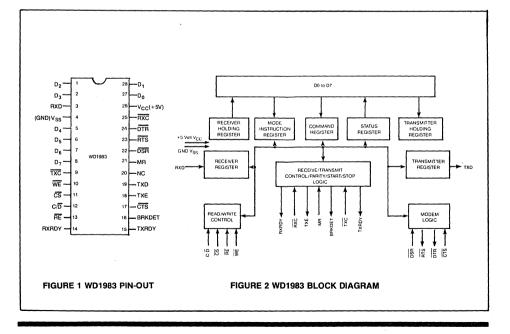

| WD1983      | Programmable BOART                                            | 123  |

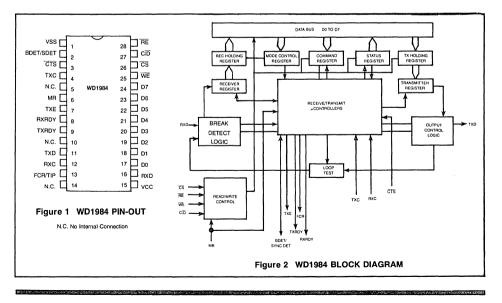

| WD1984      | Multi-Character Synchronous/Asynchronous Transmitter/Receiver | 189  |

| WD1993      | ARINC 429-1 ASART Controller                                  | 171  |

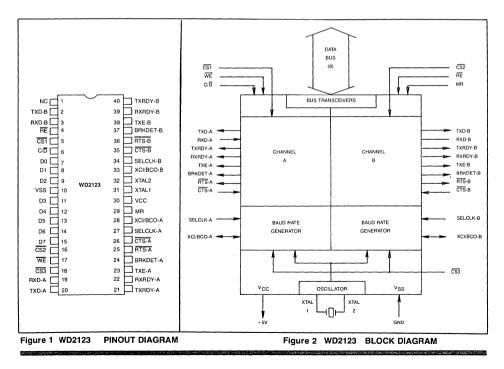

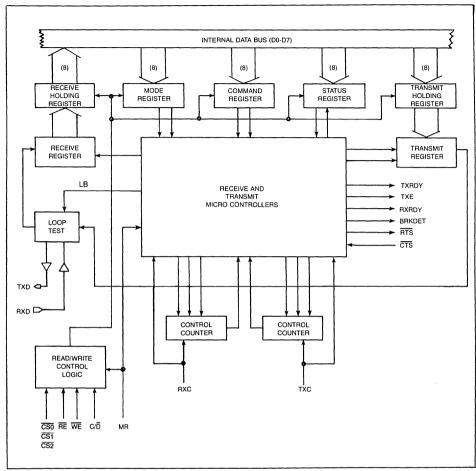

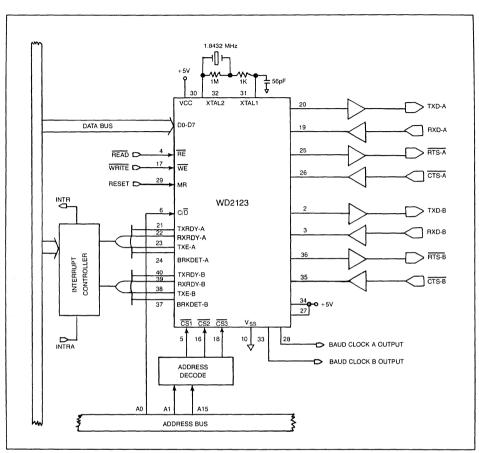

| WD2123      | Deuce Dual Channel BOART                                      | 151  |

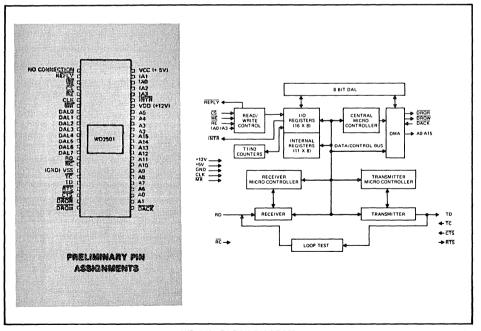

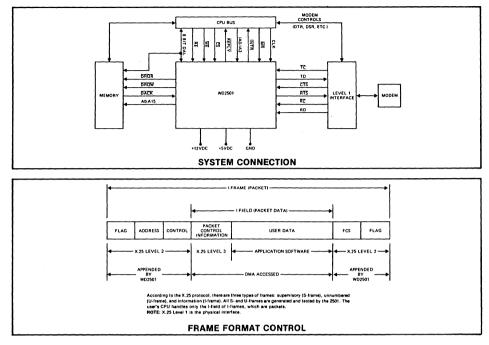

| WD2501      | Packet Switching Controller, CCITT X.25-LAP                   | 291  |

| WD2511      | Packet Switching Controller, CCITT X.25-LAPB                  | 291  |

| WD25001XC   | Pac-Kit                                                       | 303  |

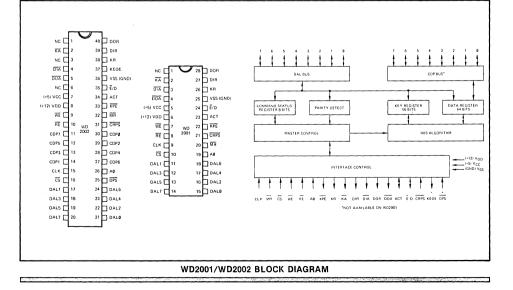

| WD2001      | Single Port Data Encryption Device                            | 261  |

| WD2002      | Dual Port Data Encryption Device                              | 261  |

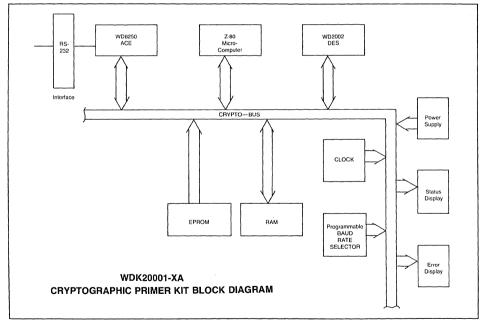

| WD20001XA   | Cryptographic Primer Kit                                      | 273  |

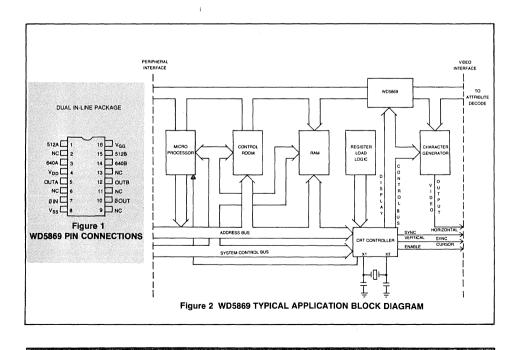

| WD5869      | Shift Register                                                | 63   |

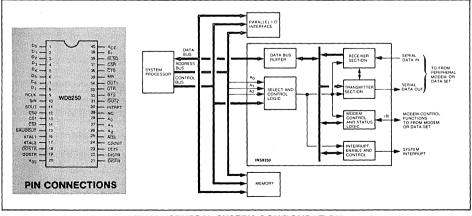

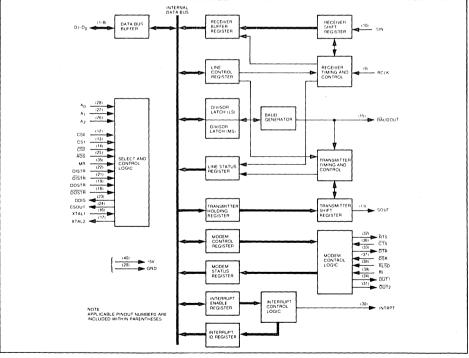

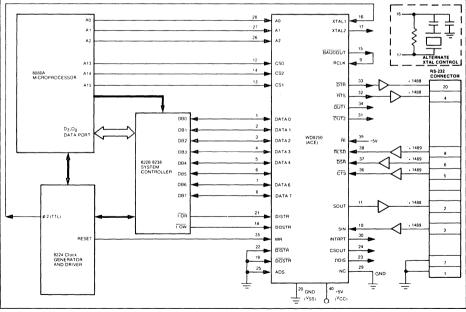

| WD8250      | ACE Async Communications Element                              | 135  |

## COMPUTER PRODUCTS DIVISION

| Part Number | Description                                | Page |

|-------------|--------------------------------------------|------|

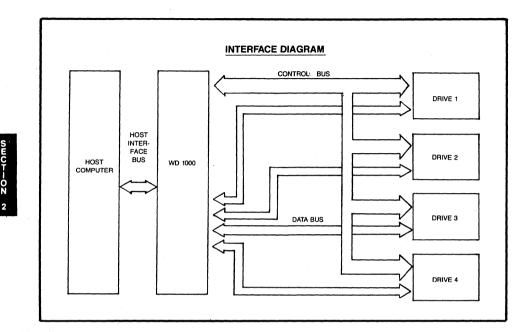

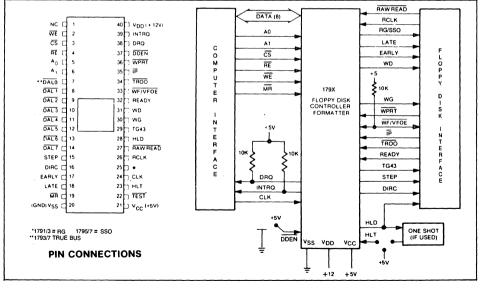

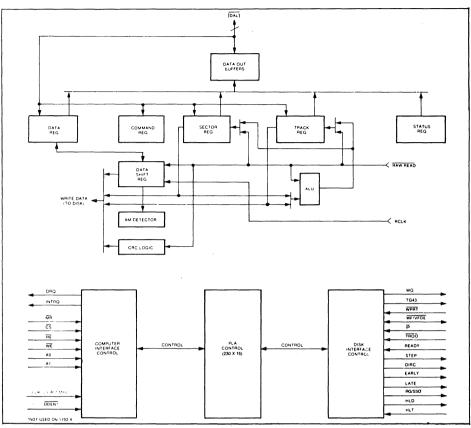

| WD1000      | Winchester Controller Board                | 327  |

| WD1100      | Winchester Controller Chip Set             | 329  |

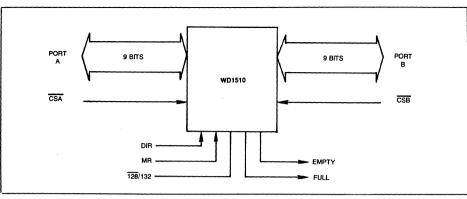

| WD1510      | LIFO/FIFO Buffer Register                  | 425  |

| WD1691      | Floppy Support Logic                       | 399  |

| FD1771      | Floppy Disk Controller—Single Density      | 371  |

| FD1791      | FDC—Single/Dual Density, Inverted Data Bus | 331  |

| FD1792      | FDC—Single Density, Inverted Data Bus      | 331  |

| FD1793      | FDC—Single/Dual Density, True Data Bus     | 331  |

| FD1794      | FDC—Single Density, True Data Bus          | 331  |

| 1 |   |   |  |  |

|---|---|---|--|--|

|   | ŝ | 5 |  |  |

|   |   |   |  |  |

|   | 5 | í |  |  |

|   | l |   |  |  |

|   | ç | ) |  |  |

|   | ì | 1 |  |  |

A

| FD1795 | FDC-Dual Density/Side Select, Inverted Data Bus |

|--------|-------------------------------------------------|

| FD1797 | FDC—Dual Density/Side Select, True Data Bus     |

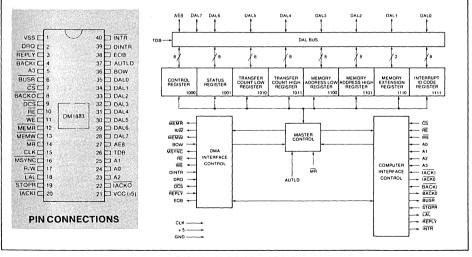

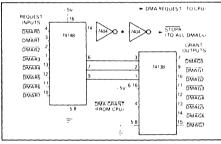

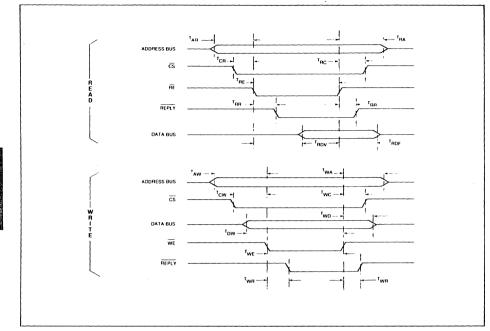

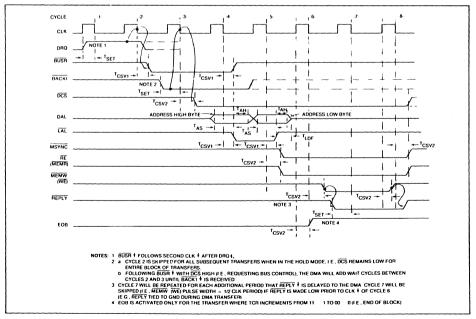

| DM1883 | Direct Memory Access Controller                 |

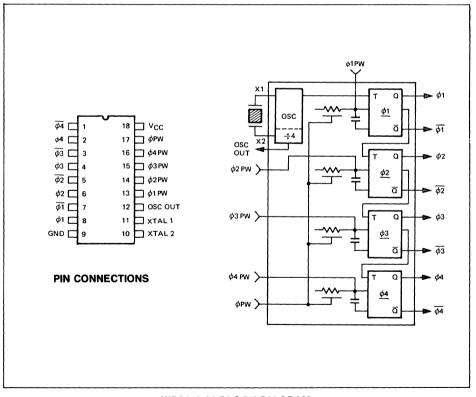

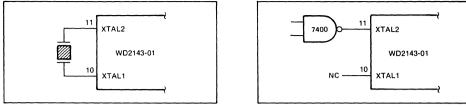

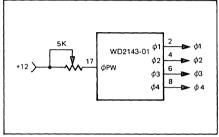

| WD2143 | Four Phase Clock Generator                      |

## **ADVANCED SYSTEMS DIVISION**

| Part Number | Description                              | Page |

|-------------|------------------------------------------|------|

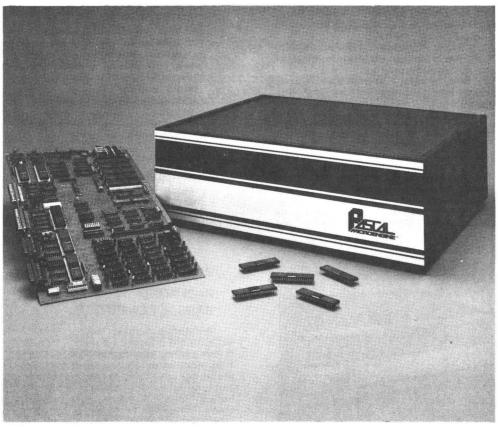

| WD0090      | Pascal MICROENGINE Computer System       | 433  |

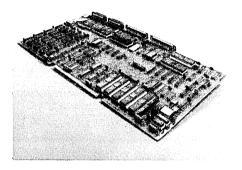

| WD0900      | Pascal MICROENGINE Single Board Computer | 437  |

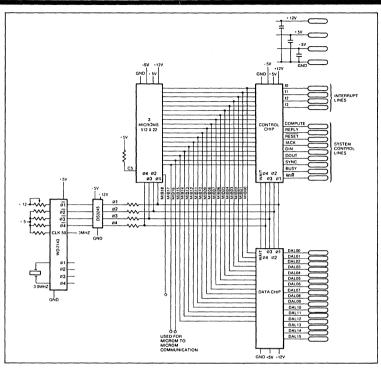

| WD9000      | Microprocessor Chip Set                  | 441  |

| WD9810      | Pascal System Software                   | 443  |

| WD9810      | Pascal Compiler                          | 445  |

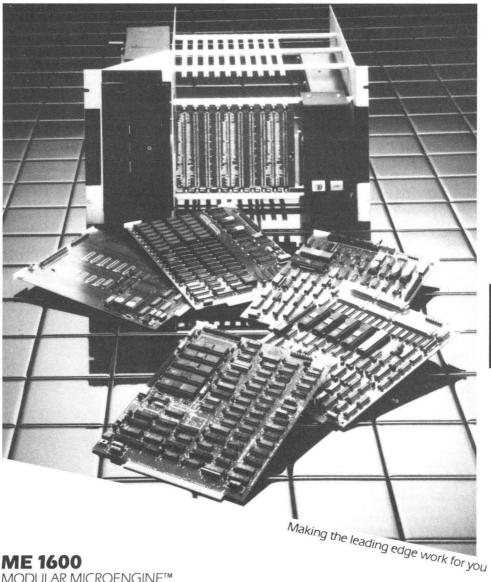

| ME1600      | Modular MICROENGINE                      | 447  |

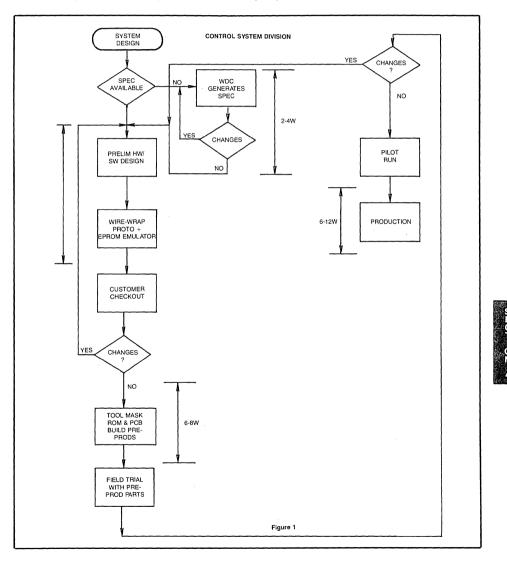

## CONTROL SYSTEMS DIVISION

| Part Number | Description                                    | Page |

|-------------|------------------------------------------------|------|

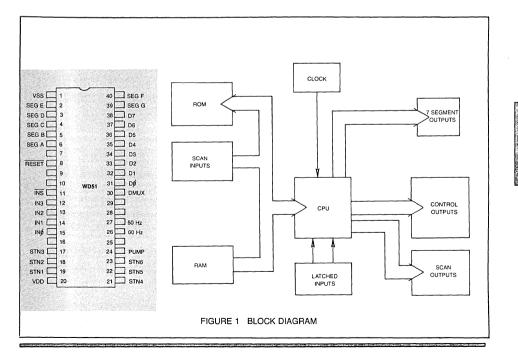

| WD51        | Irrigation Controller                          | 463  |

| WD55        | Industrial Timer/Controller                    | 471  |

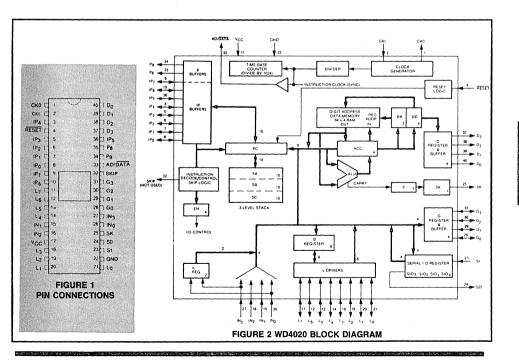

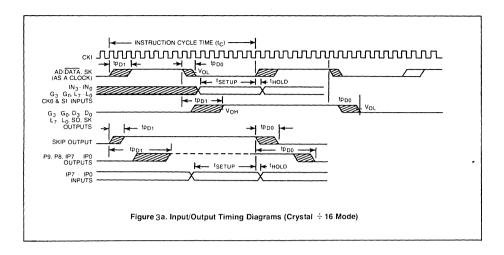

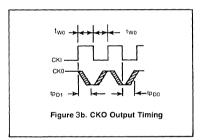

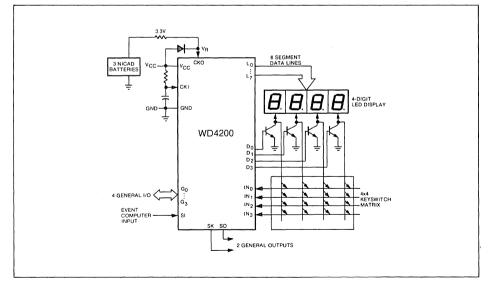

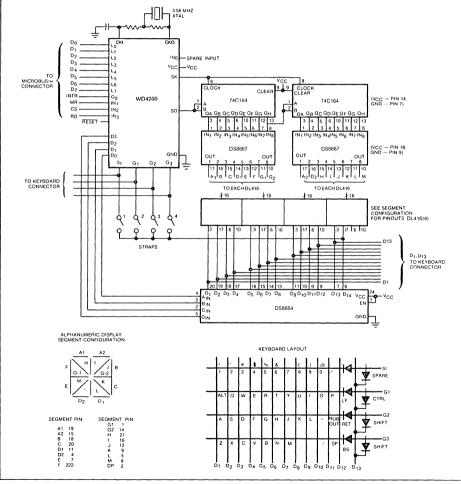

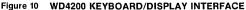

| WD4020      | ROMIess version of WD4200                      | 487  |

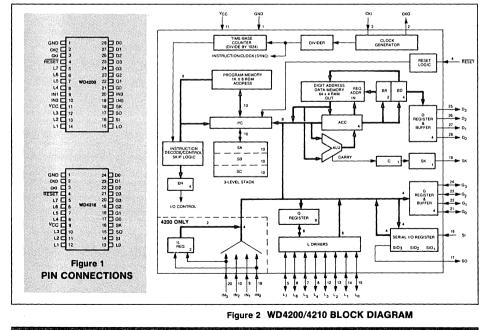

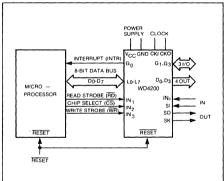

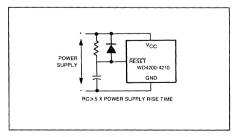

| WD4200/4210 | Single Chip 4-Bit Microcontroller, COPS Family | 495  |

### Introduction to

## TELECOMMUNICATIONS

The Telecommunications Division of Western Digital has established a strong market leadership position by developing state-of-the-art standard and custom products which provide cost effective solutions for the complex needs of its customers in the rapidly growing field of digital communications.

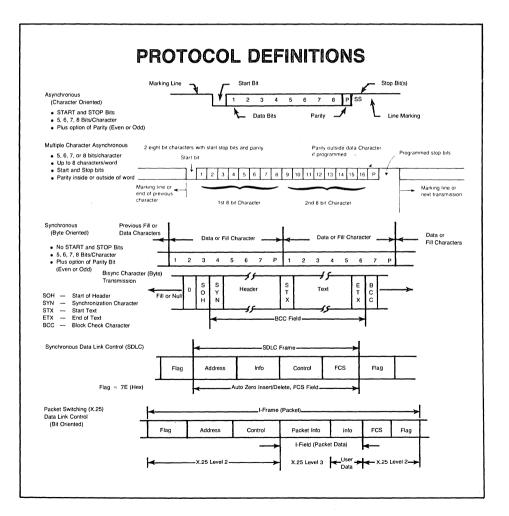

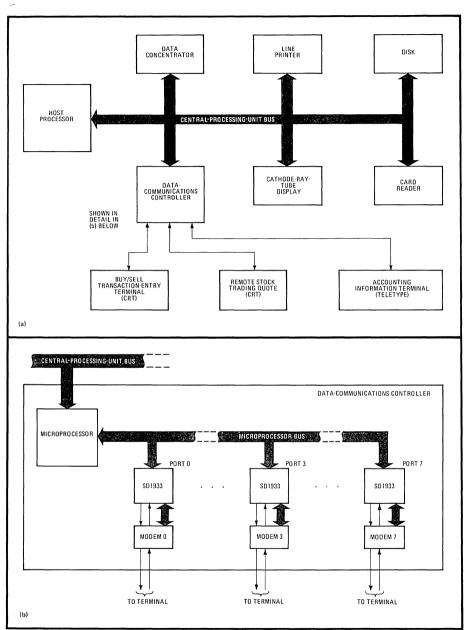

### GENERAL DATA COMMUNICATIONS

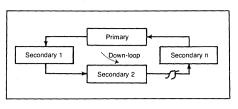

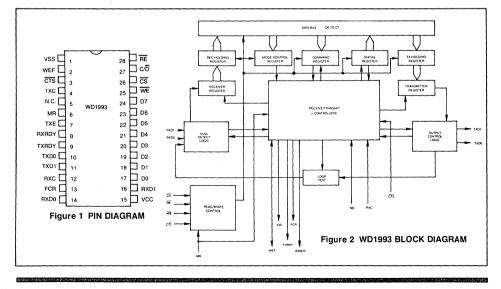

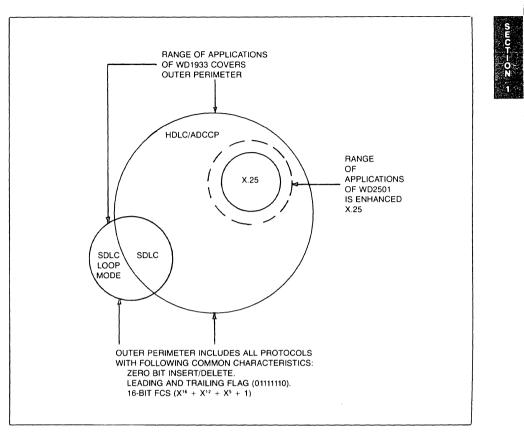

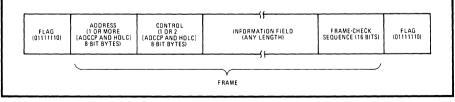

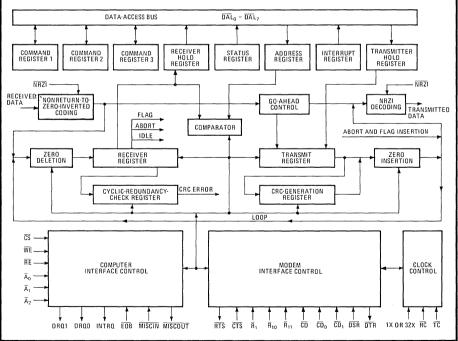

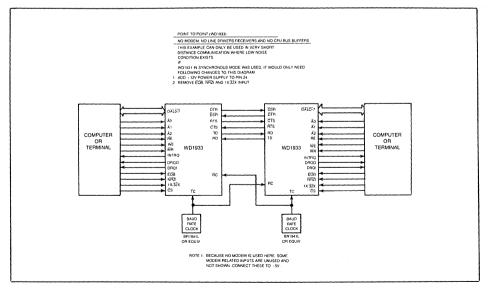

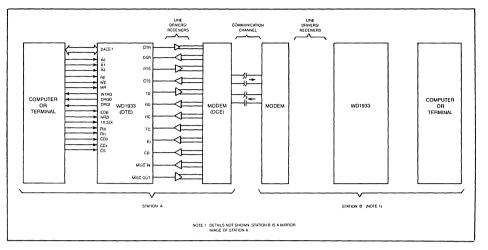

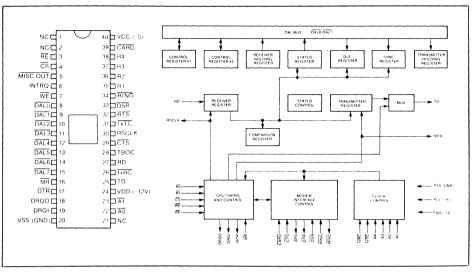

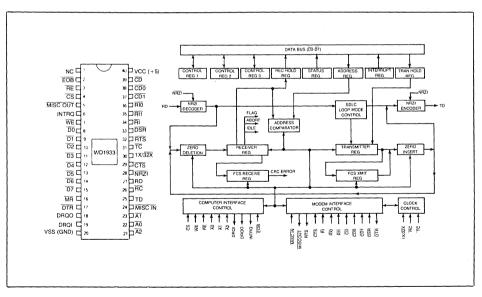

In the General Data Communications product line, our product offerings have been expanded to cover more advanced protocols such as the WD1933 for SDLC/HDLC and the WD1993 for the ARINC 429 which is for avionic use onboard aircraft. With these offerings, Western Digital now has the broadest line of protocol controllers in the industry. Future editions of this catalog will introduce dual devices with multiple system functions per package as well as complete board products.

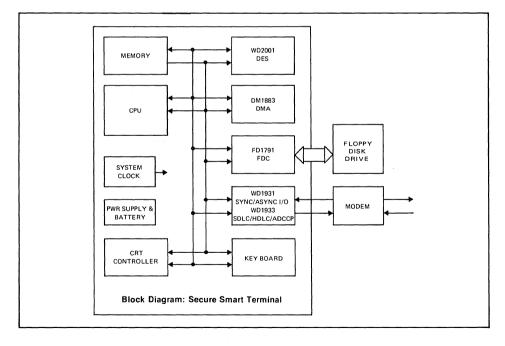

### SECURITY PRODUCTS

Western Digital has introduced the WD2001/2002, the first high-speed LSI implementation of the data encryption algorithm which has been standardized by the National Bureau of Standards. Because of this early market entry the WD2001 has been chosen by companies all over the world for use in their new designs. Future product offerings will include more advanced LSI devices with increased functionality as well as encryption system products.

### NETWORK PRODUCTS

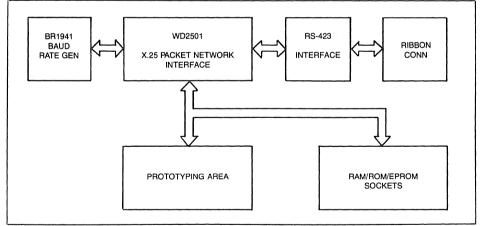

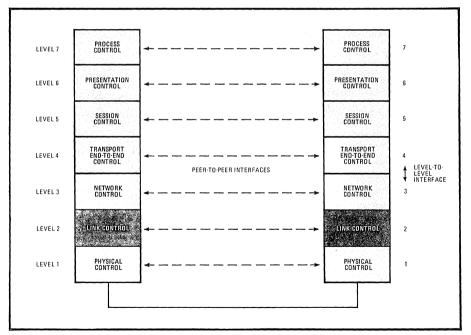

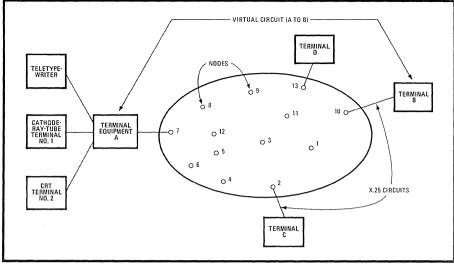

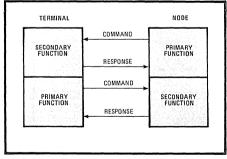

One of the most strategic products announced in this catalog is the X.25 Packet Switching Controller, the WD2501. Packet switching is an advanced form of digital network technology that is being heralded as one of the most strategic technologies of the 1980's, and Western Digital's visible leadership in this field will lead to significant growth opportunities in both public networks and "local network" markets such as the "office of the future" and advanced manufacturing applications. The Division is developing both standard proprietary products and custom versions. **Table of Contents**

SHCT-OZ 1

## **TELECOMMUNICATIONS DIVISION**

D - ----

|                                           |                           | Page |

|-------------------------------------------|---------------------------|------|

| CROSS REFERENCE, PIN COMPATIBLE AN        | D FUNCTIONAL              | 12   |

| PRODUCT SELECTION CHART                   |                           | 13   |

| GENERAL DATA COMMUNICATIONS PRODU         | UCTS                      | 15   |

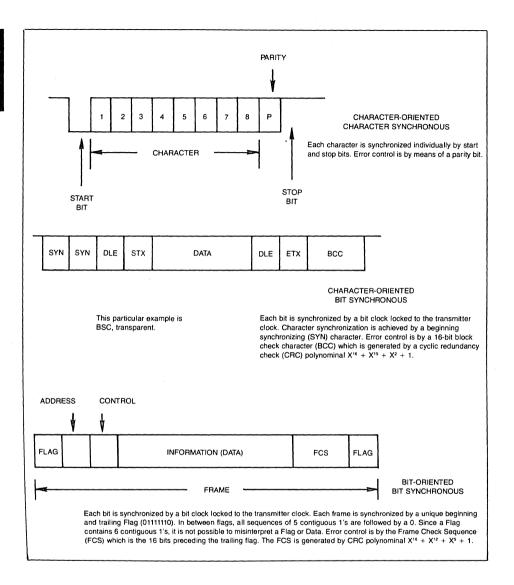

| Family and Protocol Definitions           |                           | 16   |

| Data Sheets                               |                           |      |

| UARTS                                     | TR1402/1602/1863/1865     | 17   |

| PSAR                                      | PR1472                    | 25   |

| PSAT                                      | PT1482                    | 39   |

| FIFO                                      | FR1502                    | 55   |

| SHIFT REGISTER                            | WD5869                    | 63   |

| ASTRO                                     | UC1671                    | 67   |

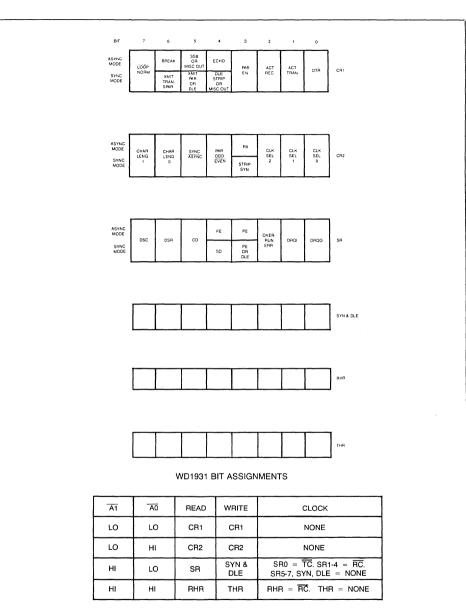

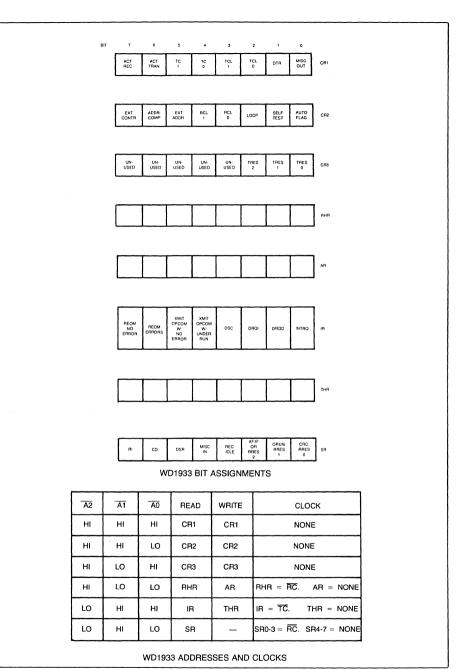

| USART                                     | WD1931                    | 81   |

| HDLC                                      | WD1933                    | 99   |

| DUAL BAUD RATE GENERATOR                  | BR1941                    | 115  |

| BOART                                     | WD1983                    | 123  |

| ACE                                       | WD8250                    | 135  |

| DEUCE                                     | WD2123                    | 151  |

| ARINC 429-1 Controller                    | WD1993                    | 171  |

| MULTI-CHARACTER USART                     | WD1984                    | 189  |

| Technical Note                            |                           | 205  |

| Using the new Data Link Control Chips     |                           | 207  |

| Data Link Control Chip supports all three | e bit oriented protocols. | 215  |

| Applications Notes                        |                           | 221  |

| Asynchronous Receiver/Transmitter-TF      | 31602/1863                | 223  |

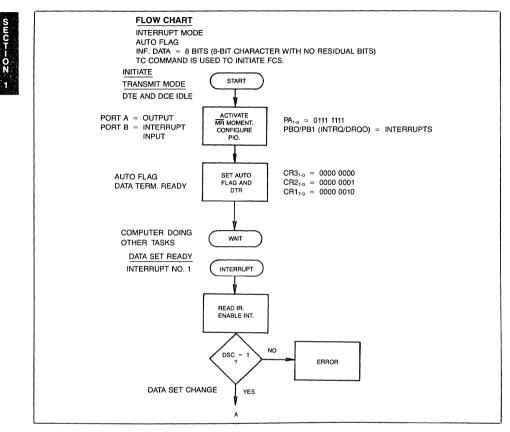

| WD1931/1933 Compatibility Application     | Note                      | 235  |

Page 259

| SECURITY PRODUCTS                      |              | 259 |

|----------------------------------------|--------------|-----|

| Data Sheets                            |              |     |

| Data Encryption Devices                | WD2001/2     | 261 |

| Cryptographic Primer Kit               | WDK20001-XA  | 273 |

| Technical Note                         |              | 275 |

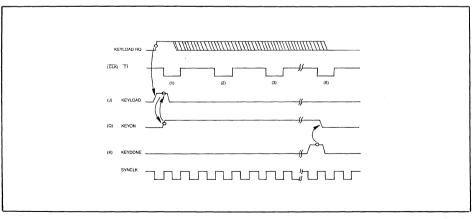

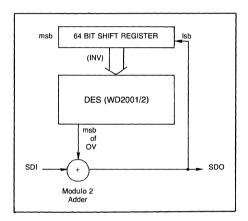

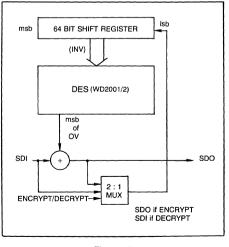

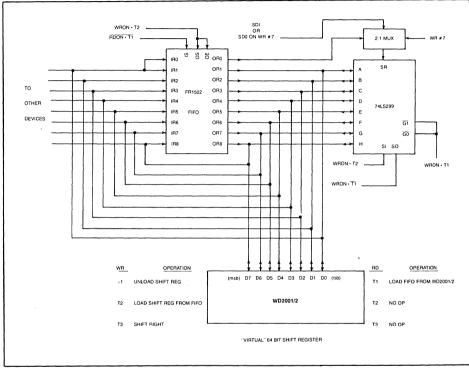

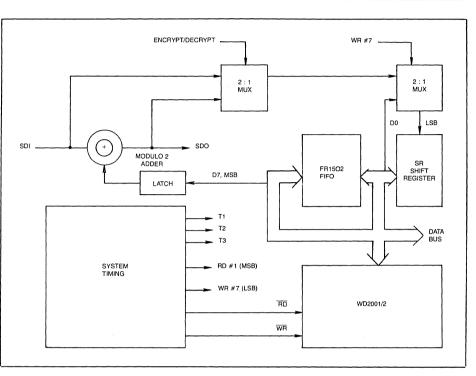

| Cipher Feedback Cryptography           |              | 277 |

| Applications Note                      |              | 279 |

| One Bit Cipher Feedback in a Synchrono | ous System   | 281 |

| NETWORK PRODUCTS                       |              | 289 |

| Data Sheets                            |              |     |

| Packet Network Interface Devices       | -WD2501/11   | 291 |

| Pac-Kit                                | -WDK25001-XC | 303 |

| Technical Note                         |              | 305 |

| Chip opens door to Packet Switching    |              | 307 |

| BOARD PRODUCT NUMBERING SYSTEM         |              | 319 |

| Board Product Numbering                |              | 321 |

|                                        |              |     |

## FUNCTIONALITY COMPATIBILITY GUIDE (PARTIAL LIST)

| WD     | SIGNETICS | FAIRCHILD         | INTEL | MOTOROLA | AMI  | SMC   | HARRIS | ZILOG | MOSTEK |

|--------|-----------|-------------------|-------|----------|------|-------|--------|-------|--------|

| WD1931 | 2651      |                   |       |          |      |       |        |       |        |

|        | 2661      | 6852              | 8251A | 6852     | 6852 | 8251A |        | SIO   | 3884   |

|        |           | 6854              |       |          |      |       |        |       |        |

| WD1933 | 2652      | 6856              | 8273  | 6854     | 6854 | 5025  |        | SIO   | 3884   |

| WD1993 |           |                   |       |          |      |       | 429    |       |        |

| WD2001 |           | 9414 <sup>1</sup> | 8294  | 6859     | 6894 |       |        |       |        |

| FR1502 |           | 33512             |       |          |      |       |        |       |        |

PLEASE CONTACT FACTORY FOR APPLICATIONS ASSISTANCE.

NOTES: 1. Four chip set.

## PIN COMPATIBLE REPLACEMENT GUIDE

| WD                  | SMC                             | GI                      | NAT      | ті                   | AMI   | INTEL | SIGNETICS | HARRIS | INTERSIL |

|---------------------|---------------------------------|-------------------------|----------|----------------------|-------|-------|-----------|--------|----------|

| TR1402              | COM2502<br>COM2502H             | AY-5-1013A<br>AY-6-1013 |          | TMS6010 <sup>4</sup> | S1757 |       | 2536      |        |          |

| TR1602              | COM2017<br>COM2017H             |                         |          | TMS60114             |       |       |           |        |          |

| TR1863              | COM1863<br>COM8017              | AY-3-1014A              |          |                      |       |       |           | HM6402 | IM6402   |

| TR1865              | COM8018                         | AY-3-1015D              |          |                      |       |       |           |        |          |

| PR1472              |                                 | AY-3-1472B <sup>4</sup> |          |                      |       |       |           |        |          |

| PT1482              |                                 | AY-3-1482B <sup>4</sup> |          |                      |       |       |           |        |          |

| UC1671              | COM1671                         |                         | INS1671  |                      |       |       |           |        |          |

| WD8250              |                                 |                         | INS8250  |                      |       |       |           |        |          |

| WD1983 <sup>1</sup> |                                 |                         | INS8251A |                      |       | 8251A |           |        |          |

| BR1941 <sup>2</sup> | COM5016<br>COM5036 <sup>3</sup> |                         |          |                      |       |       |           |        |          |

PLEASE CONSULT FACTORY FOR MAXIMUM OPERATING FREQUENCIES AND HIGH-RELIABILITY SCREENING.

NOTES: 1. WD1983 is ASYNC only.

- 2. Many frequency selections available. Consult factory for details.

- Frequency selection is mask programmable—consult factory for details.

- 3. Pin 10 on BR1941 is a "no connection".

- 4. Discontinued product.

## **PRODUCT SELECTION CHART**

| _         |                         | ARINC  | UA     | RTS    | E      | BOA    | RT     | S      | PSAR/PSAT |        | USART  |        | DLO    |

|-----------|-------------------------|--------|--------|--------|--------|--------|--------|--------|-----------|--------|--------|--------|--------|

| GENERAL D | ATA                     | W      | Т      | Т      | W      |        |        | W      | Ρ         | Р      | U      | W      | W      |

| COMMUNIC  | ATIONS                  | D      | R      | R      | D      | D      | D      | D      | R         | Т      | С      | D      | D      |

| PRODUCTS  |                         | 1      | 1      | 1      | 1      | 2      | 8      | 1      | 1         | 1      | 1      | 1      | 1      |

|           |                         | 9<br>9 | 6<br>0 | 8<br>6 | 9<br>8 | 1<br>2 | 2<br>5 | 9<br>8 | 4<br>7    | 4<br>8 | 6<br>7 | 9<br>3 | 9<br>3 |

|           |                         | 3      | 2      | 3/5    | 3      | 2      | 0      | 4      | 2         | 2      | 1      | 1      | 3      |

|           | ARINC 429               |        |        |        |        |        |        |        |           |        |        |        |        |

|           | ASYNCH                  | •      | ٥      | 0      |        | 0      | •      | •      | 0         | •      | ٥      | 0      |        |

|           | ISOCH                   |        | 0      | 0      | •      | 0      | 0      |        | 0         | 0      | 0      |        |        |

| PROTOCOL  | SYNCH (BI-SYNC)         |        |        |        |        |        |        | 0      | •         | 0      | 0      | •      |        |

|           | SDLC                    |        |        |        |        |        |        |        |           |        |        |        | •      |

|           | HDLC                    |        |        |        |        |        |        |        |           |        |        |        | 0      |

|           | ADCCP                   |        |        |        |        |        |        |        |           |        |        |        | 0      |

|           | FULL DUPLEX             | 0      | •      | •      | 0      | 0      | •      | •      |           |        | 0      | •      | 0      |

|           | MAXIMUM 100 kHz         |        |        |        |        |        |        |        |           |        |        |        |        |

|           | 320 kHz                 |        | 0      |        |        |        |        |        |           |        |        |        | ٥      |

|           | 500 kHz                 |        |        |        |        |        |        |        |           |        |        |        |        |

| FEATURES  | 640 kHz                 | 0      |        |        | 0      |        |        |        | 0         | 0      |        |        |        |

|           | 1000 kHz                |        |        | 0      |        | 0      | 0      | . 0    |           |        | 0      | 0      | 0      |

|           | 1500 kHz                |        |        | 0      |        |        |        |        |           |        |        |        |        |

|           | 2500 kHz                |        |        | 0      |        |        |        |        |           |        |        |        | 0      |

|           | 3500 kHz                |        |        | 0      |        |        |        |        |           |        |        |        |        |

|           | SELECTABLE CLOCK        |        |        |        |        |        |        |        |           |        |        |        |        |

|           | BOTH TRANSMIT AND       |        |        |        |        |        |        |        |           |        |        |        |        |

|           | RECEIVE                 |        | 0      | •      |        |        |        |        |           |        |        |        |        |

|           | INDEPENDENT TRANSM      | IT     |        |        |        |        |        |        |           |        |        |        |        |

|           | AND RECEIVE             | •      |        |        | 0      | 0      | •      |        | 0         | 0      | 0      | 0      | 0      |

|           | 1X                      |        |        |        | 0      | •      | 0      | 0      | . 0       | 0      | 0      | 0      | 0      |

|           | 4X                      | 0      |        |        |        |        |        | 0      |           |        |        |        |        |

|           | 16X                     |        | 0      | e      | ٥      | 0      |        | 0      | 0         | 0      |        |        | 0      |

|           | 32X                     |        |        |        |        |        |        |        | . 0       | 0      | ۰      |        | 0      |

|           | 64X                     |        |        |        | 0      | 0      | •      |        | 0         | 0      | ۰      | 0      |        |

|           | 128X                    |        |        |        |        |        |        |        |           |        | 0      |        |        |

|           | 256X                    |        |        |        |        |        |        |        |           |        | 0      |        |        |

|           | WORD LENGTH SELECT      |        |        |        |        |        |        |        |           |        |        |        |        |

|           | 5,6,7,8 BIT             | 0      | 0      | 0      | ۰      | 0      | 0      | •      | 0         | •      | •      | 0      | •      |

|           | STOP BIT SELECT 1,1.5,2 | 2      | 9      | •      | 0      | •      | •      | ۰      | 6         | •      | 9      | 0      |        |

|           | PARITY SELECT ODD/      |        |        |        |        |        |        |        |           |        |        |        |        |

|           | EVEN                    | 0      | 0      | 0      | 0      | •      | •      | 0      | ٥         | 0      | 0      | •      |        |

|           | MATCH/SYN GENERATE      |        |        |        |        |        |        |        |           | 0      | •      | •      | •      |

|           | MATCH/SYN DETECT        |        |        |        |        |        |        |        | 0         |        | 0      | 0      | •      |

|           | BREAK DETECT            | •      |        |        | •      | •      | 0      | •      |           |        |        |        |        |

|           | DOUBLE BUFFERING        | 9      | 0      | 0      | •      | 0      | 0      | •      | •         |        |        | ٠      | 0      |

|           | TTL COMPATIBLE          | •      | •      |        | 0      | 0      | •      | 0      | 0         | 0      | •      |        | •      |

13

SUCH-OZ 1

# **PRODUCT SELECTION CHART**

|           |                     | ARINC | UA | RTS | E | BOA | RT | s | PSAR | /PŜAT | US    | ART | DLC    |

|-----------|---------------------|-------|----|-----|---|-----|----|---|------|-------|-------|-----|--------|

| GENERAL I | ΤΔΤΔ                | W     | Т  | Т   | w | w   | w  | w | Р    | Р     | U     | W   | W      |

| COMMUNIC  | ATIONS              | D     | R  | R   | D | D   | D  | D | R    | Т     | С     | D   | D      |

| PRODUCTS  | 6                   | 1     | 1  | 1   | 1 | 2   | 8  | 1 | 1    | 1     | 1     | 1   | 1      |

|           |                     | 9     | 6  | 8   | 9 | 1   | 2  | 9 | 4    | 4     | 6     | 9   | 9      |

|           |                     | 9     | 0  | 6   | 8 | 2   | 5  | 8 | 7    | 8     | 7     | 3   | 3<br>3 |

|           |                     | 3     | 2  | 3/5 | 3 | 3   | 0  | 4 | 2    | 2     | 1     | 1   |        |

|           | ERROR CHECKING      |       |    |     |   |     |    |   |      |       |       |     |        |

|           | FRAMING             |       | •  | 9   | ۰ | •   | •  | • | •    | ø     | 0     | •   | 0      |

|           | OVERRUN             | •     | ø  | 0   | 0 |     |    | 0 |      | 0     |       |     | •      |

|           | UNDERRUN            |       |    |     |   |     |    | • |      |       | 0     | ٥   | •      |

|           | CRC GENERATE AND    |       |    |     |   |     |    |   |      |       |       |     |        |

| <u></u>   | CHECK               |       |    |     |   |     |    |   |      |       |       |     | •      |

|           | PROCESSOR INTERFACE |       |    |     |   |     |    |   |      |       |       |     |        |

|           | UNIDIRECTIONAL      |       | 0  | 6   |   |     |    |   |      |       |       |     |        |

|           | BIDIRECTIONAL       | ø     |    |     | 0 |     | 0  | 0 |      |       | 0     |     | •      |

|           | CONTROL             |       |    |     |   |     |    |   |      |       |       |     |        |

|           | PROGRAMMING         |       |    |     |   |     |    |   |      |       |       |     |        |

|           | DEVICE PINS         |       | 0  |     |   |     |    |   | 0    | 0     |       |     |        |

|           | BIDIRECTIONAL BUS   | •     |    |     | 0 | 0   | 0  | • |      |       | •     | •   | 0      |

|           | MODEM INTERFACE     |       |    |     |   |     |    |   |      |       |       |     |        |

|           | NUMBER OF SIGNALS 8 |       |    |     |   |     |    |   |      |       |       |     |        |

|           | 6                   |       |    |     |   |     | •  |   |      |       |       | •   |        |

|           | 4                   |       |    | •   |   |     |    |   |      |       |       |     |        |

|           | 2                   |       |    |     |   | •   |    |   |      |       |       |     |        |

|           | SELF LOOP TEST      | 0     |    |     |   |     | 0  | 0 |      |       | 0     | •   | •      |

|           | NRZI OPTION         |       |    |     |   |     |    |   |      |       |       |     |        |

|           | DIGITAL PHASE LOCK  |       |    |     |   |     |    |   |      |       |       |     | •      |

|           | LOOP                |       |    |     |   |     |    |   |      |       | 0     | •   |        |

| SPECIAL   | ON BOARD BAUD RATE  |       |    |     |   |     |    |   |      |       |       |     |        |

| FEATURES  | GENERATOR           |       |    |     |   | •   | •  |   |      |       |       |     |        |

|           | EXTENDED WORD SIZE  | 0     |    |     |   |     |    | 6 |      |       |       |     |        |

|           | TWO FULL DUPLEX     | -     |    |     |   |     |    | - |      |       |       |     |        |

|           | CHANNELS            |       |    |     |   | 0   |    |   |      |       |       |     |        |

|           |                     |       |    |     |   |     |    |   |      |       | ····· |     |        |

# General Data Communications Products

## DATA COMMUNICATION FAMILIES

| UART  | — | Universal Asynchronous Receiver-Transmitter             |

|-------|---|---------------------------------------------------------|

| PSAT  | — | Programmable Synchronous/Asynchronous Transmitter       |

| PSAR  | — | Programmable Synchronous/Asynchronous Receiver          |

| USART | — | Universal Synchronous/Asynchronous Receiver-Transmitter |

| BOART |   | Bus Oriented Asynchronous Receiver-Transmitter          |

| DLC   | — | Data Link Controller                                    |

|       |   |                                                         |

#### WESTERN DIGITAL c aRPAR Δ т / Л

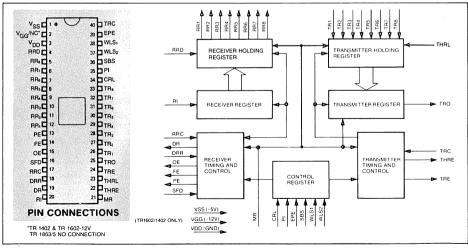

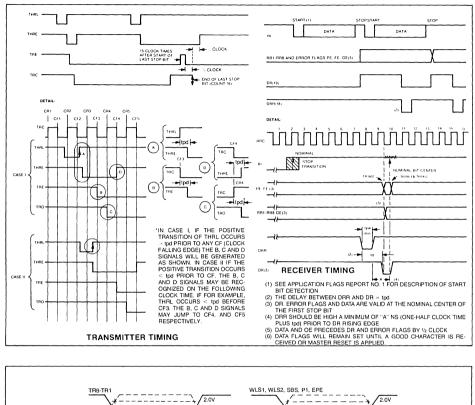

## TR1602/TR1402/TR1863/TR1865 Universal Asynchronous Receiver/Transmitter (UART)

### FFATURES

- DUAL POWER SUPPLY TR1602/TR1402 0

- SINGLE POWER SUPPLY +5VDC ON TR1863/5 0

- D.C. TO 1 MHZ (64 KB) (STANDARD PART) ^ TR1863/5

- FULL DUPLEX OR HALF DUPLEX OPERATION ^

- AUTOMATIC INTERNAL SYNCHRONIZATION • OF DATA AND CLOCK

- AUTOMATIC START BIT GENERATION

- EXTERNALLY SELECTABLE Word Length Baud Rate Even/Odd Parity (Receiver/Verification -Transmitter/Generation) Parity Inhibit

One, One and One-Half, or Two Stop Bit Generation (11/2 at 5 Bit Level for TR1602, TR1863/5)

AUTOMATIC DATA RECEIVED/TRANSMITTED STATUS GENERATION Transmission Complete Buffer Register Transfer Complete Received Data Available Parity Error Framing Error Overrun Error

- MARCH, 1981 BUFFERED RECEIVER AND TRANSMITTER 0 REGISTERS

- THREE-STATE OUTPUTS ^ **Receiver Register Outputs** Status Flags

- TTL COMPATIBLE

- TR1865 HAS PULL-UP RESISTORS ON ALL INPUTS

### APPLICATIONS

- PERIPHERALS 0

- TERMINALS 0

- MINI COMPUTERS

- FACSIMILE TRANSMISSION

- MODEMS •

- CONCENTRATORS

- 0 ASYNCHRONOUS DATA MULTIPLEXERS

INCOMPANY AND INCOMPANY AND INCOMPANY

- CARD AND TAPE READERS ۰

- ۰ PRINTERS

- DATA SETS

- CONTROLLERS •

- 0 **KEYBOARD ENCODERS**

- REMOTE DATA ACQUISITION SYSTEMS

- ASYNCHRONOUS DATA • CASSETTES

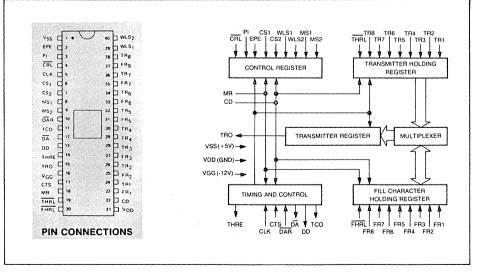

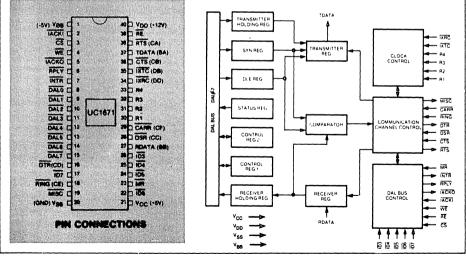

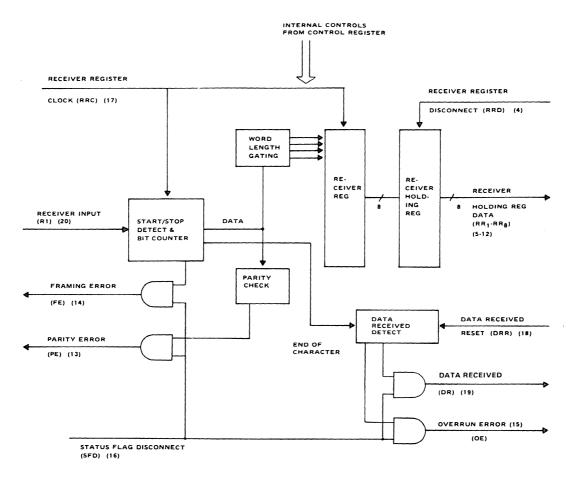

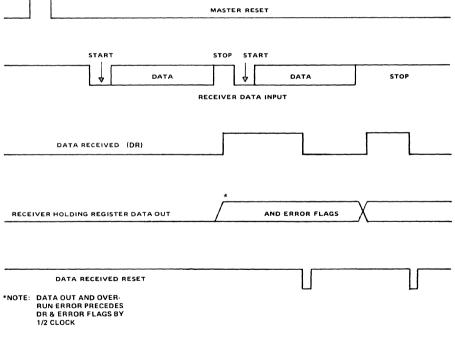

### TR1602/TR1402/TR1863/TR1865 BLOCK DIAGRAM

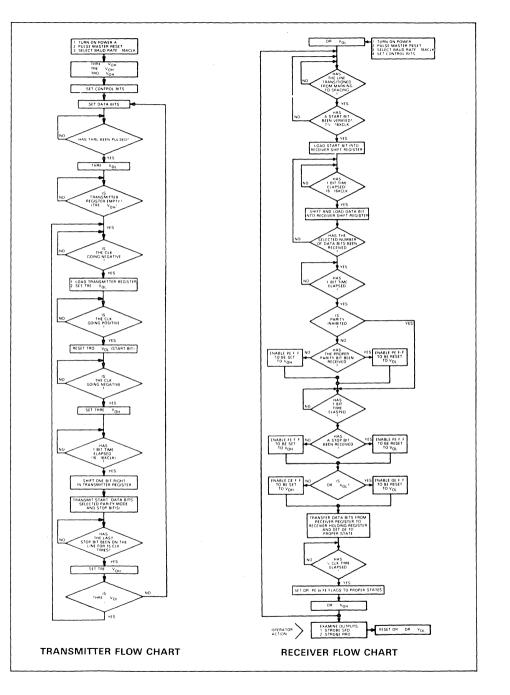

### GENERAL DESCRIPTION

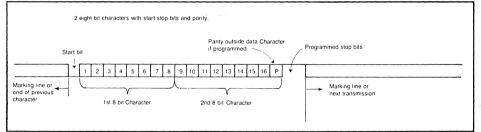

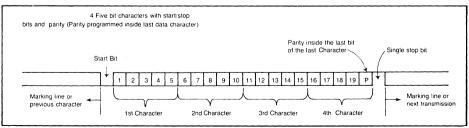

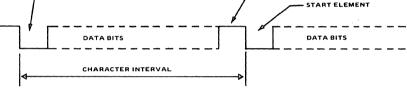

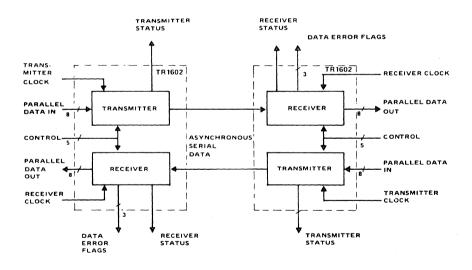

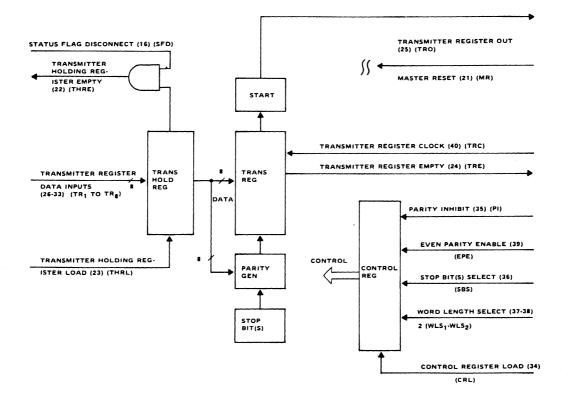

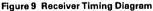

The ASYNCHRONOUS RECEIVER/TRANSMITTER is a general purpose, programmable MOS/LSI device for interfacing an asynchronous serial data channel of a peripheral or terminal with parallel data of a computer or terminal. The transmitter section converts parallel data into a serial word which contains the data along with start/stop bits, and optional parity. The receiver section converts a serial word with start, data, optional parity, and stop bits, into parallel data, and it verifies proper code transmission by checking parity and receipt of a valid stop bit. Both the receiver and the transmitter are double buffered. The array is compatible with bipolar logic. The array may be programmed as follows: The word length can be either 5, 6, 7, or 8 bits; parity generation and checking may be inhibited, the parity may be even or odd; and the number of stop bits may be either one or two, with one and one-half when transmitting a 5 bit code. The TR1863/5 is pin- and function-compatible to the TR1402 and TR1602 except that it is +5V only and can operate up to 3.5 MHz (218.75K Baud). The standard TR1863/5 operates at 1.0 MHz (62.5K Baud).

### PIN DEFINITIONS

| PIN DEFINI |                                      |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER     |                                      | SYMBOL                               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1          | V <sub>SS</sub> POWER SUPPLY         | VSS                                  | +5 volts supply                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2          | VGG — TR1602/TR1402<br>NC — TR1863/5 | VGG<br>NC                            | -12 volts supply<br>No Connection (open)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3          | VDD POWER SUPPLY                     | GND                                  | Ground = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4          | RECEIVER REGISTER<br>DISCONNECT      | RRD                                  | A high level input voltage, $V_{IH}$ , applied to this line disconnects the RECEIVER HOLDING REGISTER outputs from the RR <sub>1-8</sub> data outputs (pins 5-12).                                                                                                                                                                                                                                                                                       |

| 5-12       | RECEIVER HOLDING<br>REGISTER DATA    | RR <sub>8</sub> -<br>RR <sub>1</sub> | The parallel contents of the RECEIVER HOLDING REGISTER appear on these lines if a low-level input voltage. $V_{IL}$ , is applied to RRD. For character formats of fewer than eight bits received characters are right-justified with RR1 (pin 12) as the least significant bit and the truncated bits are forced to a low level output voltage, $V_{OL}$ .                                                                                               |

| 13         | PARITY ERROR                         | PE                                   | A high level output voltage, $V_{OH}$ , on this line indicates that the received parity does not compare to that programmed by the EVEN PARITY ENABLE control line (pin 39). This output is updated each time a character is transferred to the RECEIVER HOLDING REGISTER. PE lines from a number of arrays can be bussed together since an output disconnect capability is provided by Status Flag Disconnect line (pin 16).                            |

| 14         | FRAMING ERROR                        | FE                                   | A high-level output voltage, $V_{OH}$ , on this line indi-<br>cates that the received character has no valid stop<br>bit, i.e., the bit (if programmed) is not a high level<br>voltage. This output is updated each time a character<br>is transferred to the Receiver Holding Register, FE<br>lines from a number of arrays can be bussed together<br>since an output disconnect capability is provided by<br>the Status Flag Disconnect line (pin 16). |

| 15         | OVERRUN ERROR                        | OE                                   | A high-level output voltage, V <sub>OH</sub> , on this line indi-<br>cates that the Data Received Flag (pin 19) was not<br>reset before the next character was transferred to<br>the Receiver Holding Register. OE lines from a<br>number of arrays can be bussed together since an<br>output disconnect capability is provided by the<br>Status Flag Disconnect line (pin 16).                                                                          |

| 16         | STATUS FLAGS<br>DISCONNECT           | SFD                                  | A high-level input voltage, VIH, applied to this pin<br>disconnects the PE, FE, OE, DR and THRE allowing<br>them to be buss connected.                                                                                                                                                                                                                                                                                                                   |

**МПСТ-02**

| PIN<br>NUMBER | NAME                                  | SYMBOL  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|---------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

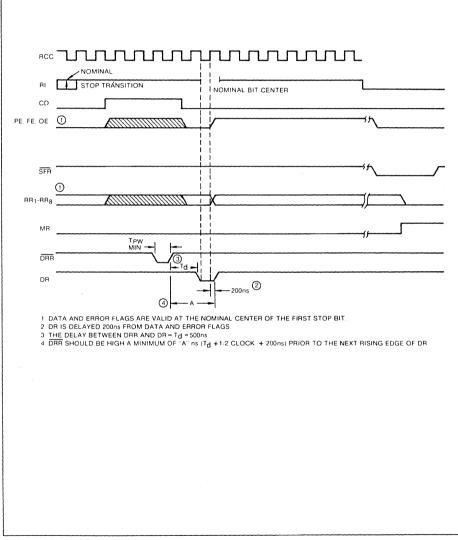

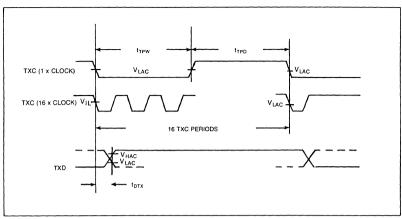

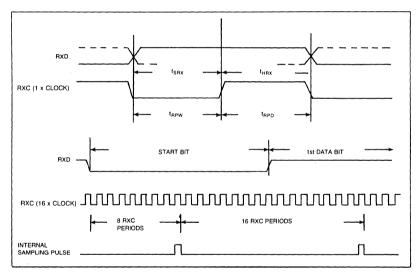

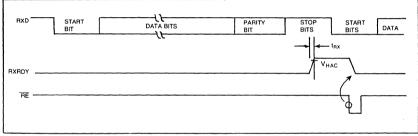

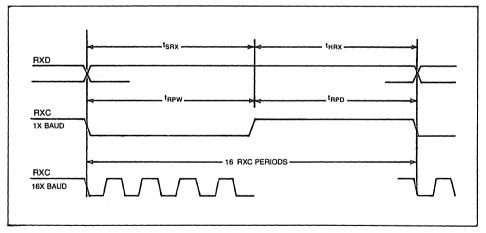

| 17            | RECEIVER REGISTER<br>CLOCK            | RRC     | The receiver clock frequency is sixteen (16) times times the desired receiver shift rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18            | DATA.RECEIVED RESET                   | DRR     | A low-level input voltage, $V_{IL},$ applied to this line resets the DR line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 19            | DATA RECEIVED                         | DR      | A high-level output voltage, V <sub>OH</sub> , indicates that an<br>entire character has been received and transferred<br>to the RECEIVER HOLDING REGISTER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 20            | RECEIVER INPUT                        | RI      | Serial input data received on this line enters the<br>RECEIVER REGISTER at a point determined by the<br>character length, parity, and the number of stop bits.<br>A high-level input voltage, VIH, must be present<br>when data is not being received.                                                                                                                                                                                                                                                                                                                                                                                                 |

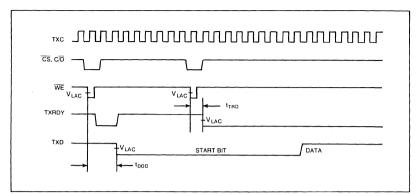

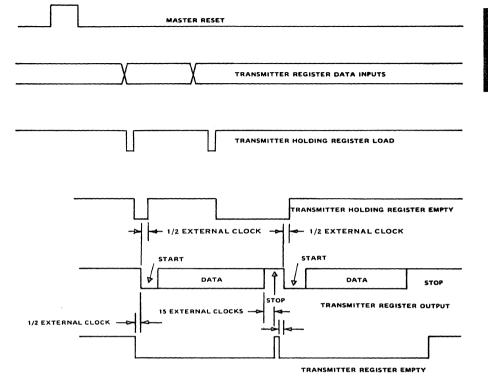

| 21            | MASTER RESET                          | MR      | This line is strobed to a high-level input voltage, $V_{IH}$ , to clear the logic. It resets the Transmitter and Receiver Holding Registers, the Transmitter Register, FE, OE, PE, DR and sets TRO, THRE, and TRE to a high-level output voltage, $V_{OH}$ .                                                                                                                                                                                                                                                                                                                                                                                           |

| 22            | TRANSMITTER HOLDING<br>REGISTER EMPTY | THRE    | A high-level output voltage, V <sub>OH</sub> , on this line indi-<br>cates the TRANSMITTER HOLDING <b>REGISTER</b><br>has transferred its contents to the TRANSMITTER<br>REGISTER and may be loaded with a new character.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 23            | TRANSMITTER HOLDING<br>REGISTER LOAD  | THRL    | A low-level input voltage, V <sub>IL</sub> , applied to this line<br>enters a character into the TRANSMITTER HOLD-<br>ING REGISTER. A transition from a low-level input<br>voltage, V <sub>IL</sub> , to a high-level input voltage, V <sub>IH</sub> , trans-<br>fers the character into the TRANSMITTER REGIS-<br>TER if it is not in the process of transmitting a char-<br>acter. If a character is being transmitted, the transfer<br>is delayed until its transmission is completed. Upon<br>completion, the new character is automatically<br>transferred simultaneously with the initiation of<br>the serial transmission of the new character. |

| 24            | TRANSMITTER REGISTER<br>EMPTY         | TRE     | A high-level output voltage, $V_{OH}$ , on this line indicates that the TRANSMITTER REGISTER has completed serial transmission of a full character including STOP bit(s). It remains at this level until the start of transmission of the next character.                                                                                                                                                                                                                                                                                                                                                                                              |

| 25            | TRANSMITTER REGISTER<br>OUTPUT        | TRO     | The contents of the TRANSMITTER REGISTER (START bit, DATA bits, PARITY bit, and STOP bits) are serially shifted out on this line. When no data is being transmitted, this line will remain at a high-level output voltage, $V_{OH}$ . Start of transmission is defined as the transition of the START bit from a high-level output voltage VOH, to a low-level output voltage, $V_{OL}$ .                                                                                                                                                                                                                                                              |

| 26-33         | TRANSMITTER REGISTER<br>DATA INPUTS   | TR1-TR8 | The character to be transmitted is loaded into the TRANSMITTER HOLDING REGISTER on these lines with the THRL Strobe. If a character of less than 8 bits has been selected (by WLS, and WLS,), the character is right justified to the least significant bit, RR1, and the excess bits are disregarded. A high-level input voltage, V <sub>1</sub> H, will cause a high-level output voltage, V <sub>0</sub> H, to be transmitted.                                                                                                                                                                                                                      |

| PIN<br>NUMBER | NAME                     | SYMBOL     | FUNCTION                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|---------------|--------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 34            | CONTROL REGISTER<br>LOAD | CRL        | A high-level input voltage, VIH. on this line loads the<br>CONTROL REGISTER with the control bits (WLS <sub>1</sub> ,<br>WLS <sub>2</sub> , EPE, PI, SBS). This line may be strobed or<br>hard wired to a high-level input voltage, VIH.                                                                                                  |  |  |  |

| 35            | PARITY INHIBIT           | ΡI         | A high-level input voltage, VIH, on this line inhibit<br>the parity generation and verification circuits an<br>will clamp the PE output (pin 13) to $V_{OL}$ . If parity i<br>inhibited, the STOP bit(s) will immediately follo<br>the last data bit of transmission.                                                                     |  |  |  |

| 36            | STOP BIT(S) SELECT       | SBS        | This line selects the number of STOP bits to be trans<br>mitted after the parity bit. A high-level input voltag<br>$V_{IH}$ , on this line selects two STOP bits, and a low<br>level input voltage, $V_{IL}$ , selects a single STOP bi<br>The TR1602 and TR1863 generate 1½ stop bits<br>when word length is 5 bits and SBS is High VIH. |  |  |  |

| 37-38         | WORD LENGTH SELECT       | WLS2 -WLS1 | sive of parity) as follows:<br>$\frac{WLS_2}{V_{IL}} \frac{WLS_1}{V_{IL}} \frac{Word Length}{5 bits}$ $\frac{V_{IL}}{V_{IL}} \frac{V_{IL}}{1} \frac{6 bits}{7 bits}$                                                                                                                                                                      |  |  |  |

| 39            | EVEN PARITY ENABLE       | EPE        | $ \begin{array}{ccc} V_{IH} & V_{IH} & 8 \mbox{ bits} \\ This line determines whether even or odd PARITY is to be generated by the transmitter and checked by the receiver. A high-level input voltage, V_{IH}, selects even PARITY and a low-level input voltage, V_{IL}, selects odd PARITY. \\ \end{array} $                           |  |  |  |

| 40            | TRANSMITTER REGISTER     | TRC        | The transmitter clock frequency is sixteen (16) times the desired transmitter shift rate.                                                                                                                                                                                                                                                 |  |  |  |

⇒ <u>ح</u>امس

ABSOLUTE MAXIMUM RATINGS NOTE: These voltages are measured with respect to GND

| Storage Temperature            | -55°C to +125°C (Plastic) |

|--------------------------------|---------------------------|

| V <sub>CC</sub> Supply Voltage |                           |

| Input Voltage at any pin       | 0.3V to +7.0V             |

|                                |                           |

Operating Free-Air Temperature

T<sub>A</sub> Range ......0° C to 70° C Lead Temperature (Soldering, 10 sec.) ..... 300° C

### ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5V \pm 5\%, V_{DD} = 0V, V_{GG} = -12V \pm 5\%, TR1602/TR1402)$   $(V_{CC} = 5V \pm 5\% TR 1863/5)$

-65°C to +150°C (Ceramic)

| SYMBOL                          | PARAMETER                                                                                                         | TR1602/TR1402 |                          | TR1863/5 |                 |                                                                                                                                                                                                                                |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------|--------------------------|----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | OPERATING CURRENT                                                                                                 | MIN           | MAX                      | MIN      | MAX             | CONDITIONS                                                                                                                                                                                                                     |

| ICC<br>IGG<br>VIH<br>VIL        | Substrate Supply Current<br>Gate Supply Current<br>LOGIC LEVELS<br>Logic High<br>Logic Low<br>OUTPUT LOGIC LEVELS | VSS — 1.5V    | 60 ma<br>-10 ma<br>0.8V  |          |                 | $V_{CC} = 5.25V$<br>$V_{GG} = -12.6V$<br>$V_{CC} = 4.75V$                                                                                                                                                                      |

| VOH<br>VOL<br>IOC<br>IIL<br>IIH | Logic High<br>Logic Low<br>Output Leakage<br>Low Level Input Current<br>High level Input Current                  | VSS — 1.0V    | 0.4V<br>10 µа<br>-1.6 ma |          | 10ua<br>*-1.6ma | V <sub>SS</sub> = 4.75V, I <sub>OH</sub> = 100 µa<br>V <sub>SS</sub> = 5.25V, I <sub>OL</sub> = 1.6 ma<br>V <sub>OUT</sub> = 0V, SFD = RRD = V <sub>IH</sub><br>V <sub>IN</sub> = 0.4V<br>V <sub>IN</sub> = 3.75V, TR1865 only |

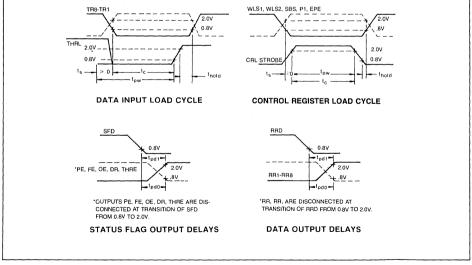

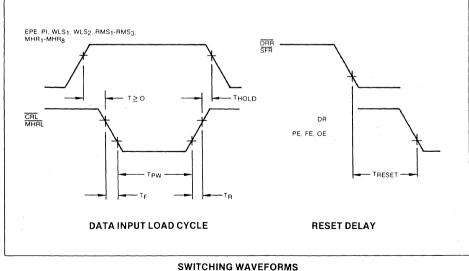

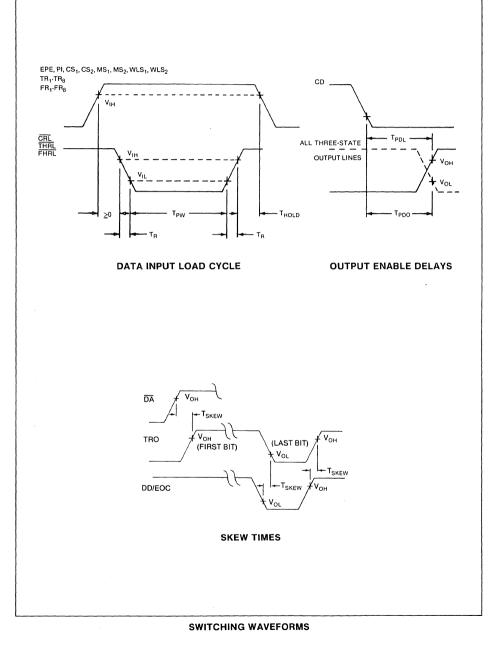

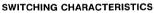

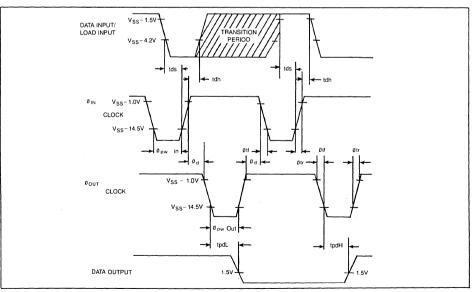

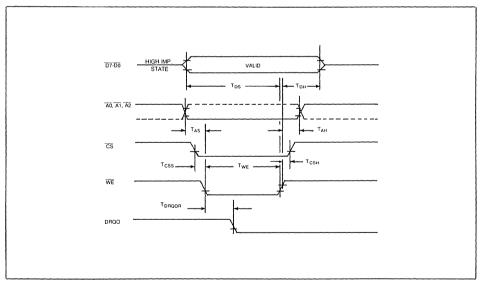

### SWITCHING CHARACTERISTICS

### (See "Switching Waveforms")

| SYMBOL           | PARAMETER                    | MIN    | MAX     | CONDITIONS                                |

|------------------|------------------------------|--------|---------|-------------------------------------------|

| fclock           | Clock Frequency              |        |         | $V_{CC} = 4.75V$                          |

| 0.000            | TR1402                       | DC     | 320 KHz | with internal pull-ups on all inputs      |

| 1 1              | TR1602                       | DC     | 320 KHz | with internal pull-ups on all inputs      |

|                  | TR1863-00                    | DC     | 1.0 MHz |                                           |

| 1                | TR1863-02                    | DC     | 2.5 MHz |                                           |

|                  | TR1863-04                    | DC     | 3.5 MHz |                                           |

| {                | TR1865-00                    | DC     | 1.0 MHz | with internal pull-ups on all inputs      |

|                  | TR1865-02                    | DC     | 2.5 MHz | with internal pull-ups on all inputs      |

| 1                | TR1865-04                    | DC     | 3.5 MHz | with internal pull-ups on all inputs      |

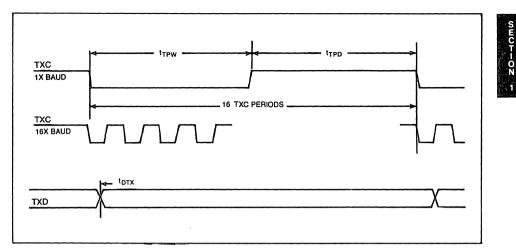

| tpw              | Pulse Widths                 |        |         |                                           |

|                  | CRL                          | 200 ns |         |                                           |

|                  | THRL                         | 200 ns |         |                                           |

|                  | DRR                          | 200 ns |         |                                           |

|                  | MR                           | 500 ns |         |                                           |

| t <sub>c</sub>   | Coincidence Time             | 200 ns |         |                                           |

| thold            | Hold Time                    | 20 ns  | İ       |                                           |

| tset             | Set Time                     | 0      |         |                                           |

|                  | OUTPUT PROPAGATION<br>DELAYS |        |         |                                           |

| tpd0             | To Low State 1602/1402       |        | 650 ns  |                                           |

| <sup>t</sup> pd1 | To High State 1602/1402      |        | 650 ns  | C <sub>L</sub> = 20 pf, plus one TTL load |

| tpd0             | To Low State 1863/1865       |        | 250 ns  |                                           |

| tpd1             | To High State 1863/1865      |        | 250 ns  | $C_L = 20  pf$ , plus one TTL load        |

|                  | CAPACITANCE                  |        |         |                                           |

| cin              | Inputs                       |        | 20 pf   | f = 1 MHz, V <sub>IN</sub> = 5V           |

| C <sub>O</sub>   | Outputs                      |        | 20 pf   | $f = 1 \text{ MHz}, V_{IN} = 5V$          |

SUCT-OR 1

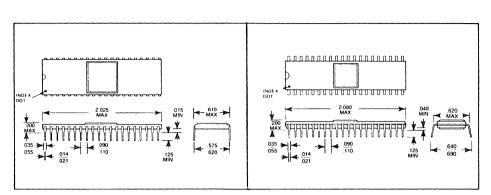

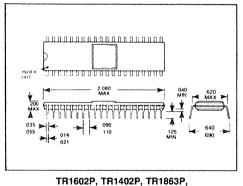

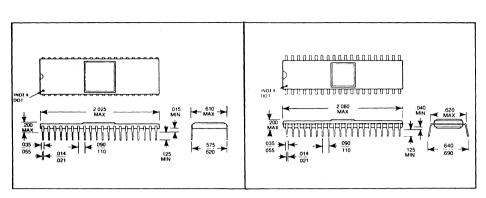

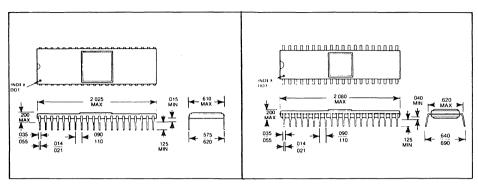

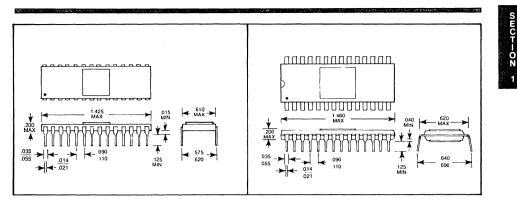

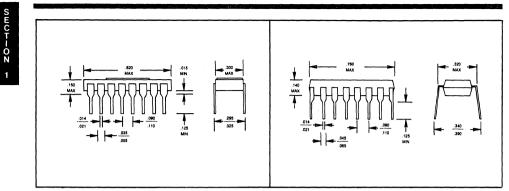

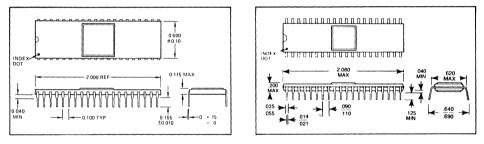

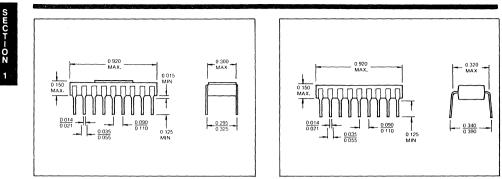

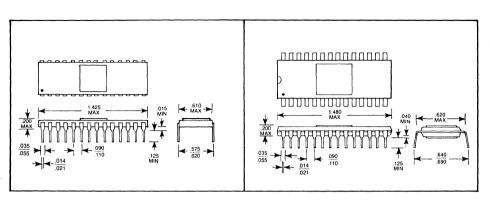

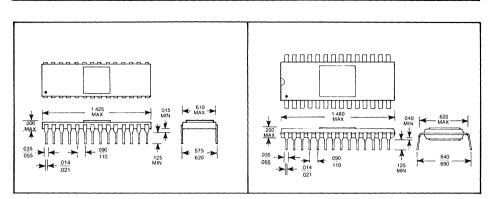

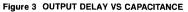

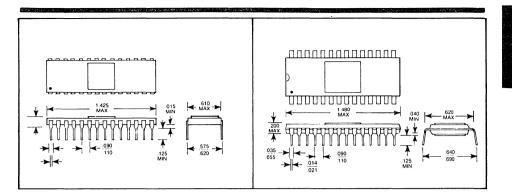

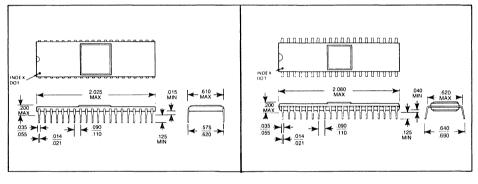

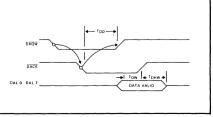

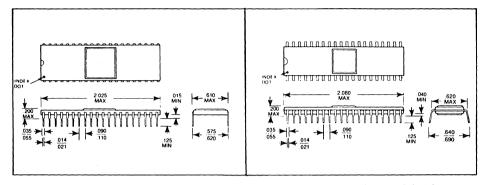

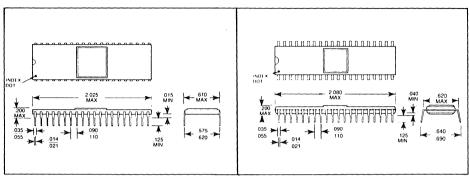

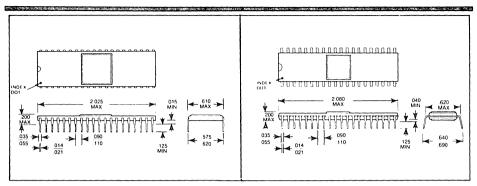

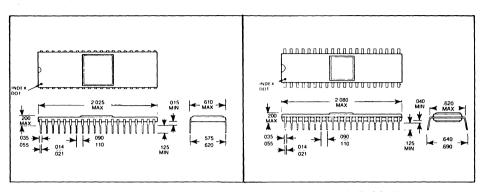

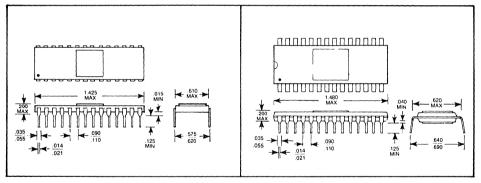

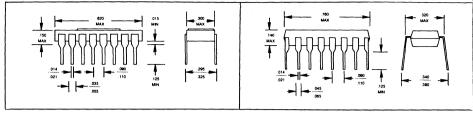

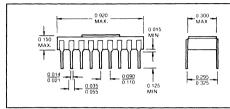

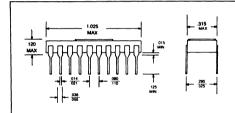

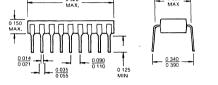

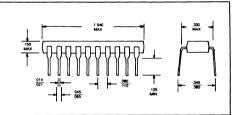

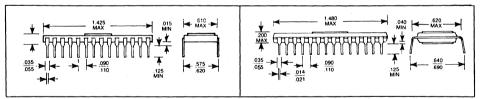

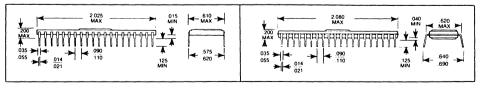

TR1602A, TR1402A, TR1863A, TR1865A CERAMIC (HERMETIC) PACKAGE

TR1602B, TR1402B, TR1863B, TR1865B PLASTIC PACKAGE

TR1865P PLASTIC PACKAGE

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Digital Corporation for its use; nor any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation for charge said circuitry at any time without notice.

WESTERN DIGITAL

3128 REDHILL AVENUE, BOX 2180 NEWPORT BEACH, CA 92663 (714) 557-3550,TWX 910-595-1139

# WESTERN DIGITAL

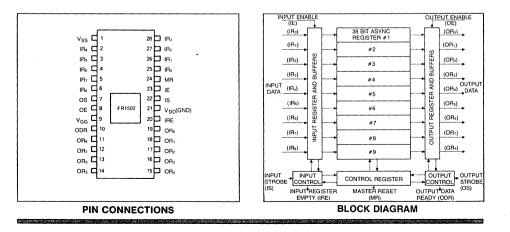

## PR1472-01 (PSAR) Programmable Synchronous & Asynchronous Receiver

### FEATURES

- SYNCHRONOUS, ASYNCHRONOUS OR ISOCHRONOUS OPERATION

- DC TO 640K BITS/SEC (1X CLOCK) PR1472-01; DC TO 100K BITS/SEC PR1472

- PROGRAMMABLE MATCH (FILL) CHARACTER WITH MATCH DETECT FLAG.

- INTERNAL OR EXTERNAL CHARACTER SYN-CHRONIZATION

- NINE BIT WIDE RECEIVER HOLDING REGISTER

- SELECTABLE 5, 6, 7 OR 8 BITS PER CHARACTER

- EVEN/ODD OR NO PARITY SELECT

- PROGRAMMABLE CLOCK RATE; 1X, 16X, 32X OR 64X

- AUTOMATIC START AND STOP BIT STRIPPING

- AUTOMATIC CHARACTER STATUS AND FLAG GENERATION

- THREE STATE OUTPUTS BUS STRUCTURE CAPABILITY

- DOUBLE BUFFERED

- TTL & DTL COMPATIBLE INTERNAL ACTIVE PULLUP

- COMPATIBLE TRANSMITTER, PT1482

### GENERAL DESCRIPTION

The Western Digital PR1472 (PSAR) is a programmable receiver that interfaces variable length serial data to a parallel data channel. The receiver converts a serial data stream into parallel characters with a format compatible with all standard Synchronous, Asynchronous, or Isochronous data communications media.

Contiguous synchronous serial characters are compared to a programmable Match-Character Holding Register, character synchronized and assembled. Programming the Asynchronous or Isochronous Mode provides assembly of characters with start and stop bit(s) which are stripped from the data. Four internal registers, in conjunction with Three-State Outputs provide full system versatility.

The PSAR is a TTL compatible device. The use of internal active pull-up devices and push-pull output drivers, provides direct compatibility with all forms of current sinking logic. Western Digital also offers a Compatible Transmitter, PT1482.

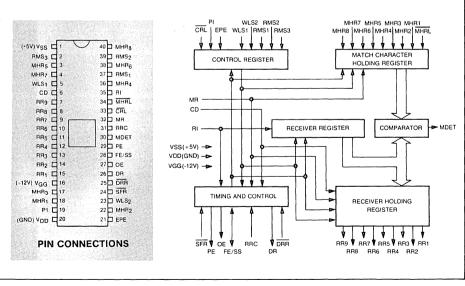

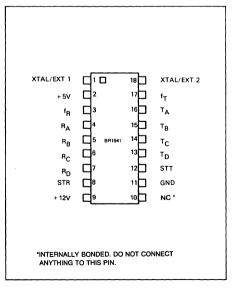

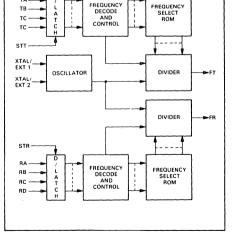

PR1472 BLOCK DIAGRAM

| PIN<br>NUMBER                    | I/O NAME                                    | SYMBOL                                                  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                          |                                                                  |                                                                                                                                                                                       |  |

|----------------------------------|---------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                                | V <sub>SS</sub> POWER SUPPLY                | V <sub>ss</sub>                                         | +5 Volt Supply                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                          |                                                                  |                                                                                                                                                                                       |  |

| 37, 39, 2                        | RECEIVER MODE<br>SELECT                     | RMS₁, RMS₂,<br>RMS₃                                     | A low-level input voltage, $V_{IL}$ , applied to CD (pin<br>6) enables RMS <sub>1</sub> , RMS <sub>2</sub> , and RMS <sub>3</sub> inputs. The<br>Receiver Mode Select Inputs, in conjunction with<br>the Control Register Load and Chip Disable,<br>select the Receiver operating mode. RMS <sub>1</sub> , RMS <sub>2</sub> ,<br>and RMS <sub>3</sub> may be strobed or hard-wired to the<br>appropriate input voltage. |                                                                          |                                                                  |                                                                                                                                                                                       |  |

|                                  |                                             |                                                         | <b>RMS</b> ₃                                                                                                                                                                                                                                                                                                                                                                                                            | <b>RMS₂</b>                                                              | RMS <sub>1</sub>                                                 | Selected Operating Mode                                                                                                                                                               |  |

|                                  |                                             |                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                        | 0                                                                | ASYNCH OR ISOCH,                                                                                                                                                                      |  |

|                                  |                                             |                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                        | 1                                                                | 1X CLOCK<br>ASYNCH OR ISOCH,                                                                                                                                                          |  |

|                                  |                                             |                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                        | 0                                                                | 16X CLOCK<br>ASYNCH OR ISOCH,                                                                                                                                                         |  |

|                                  |                                             |                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                        | 1                                                                | 32X CLOCK<br>ASYNCH OR ISOCH,                                                                                                                                                         |  |

|                                  |                                             |                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                       | х                                                                        | 0                                                                | 64X CLOCK<br>SYNCH-EXTERNAL                                                                                                                                                           |  |

|                                  |                                             |                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                       | x                                                                        | 1                                                                | CHARACTER<br>SYNCHRONIZATION<br>SYNCH-INTERNAL<br>CHARACTER<br>SYNCHRONIZATION                                                                                                        |  |

|                                  |                                             |                                                         | NOTE: When operating in asynchronou<br>isochronous mode with 1X clock th<br>no protection against false start bit                                                                                                                                                                                                                                                                                                       |                                                                          |                                                                  |                                                                                                                                                                                       |  |

|                                  |                                             |                                                         | A high-level input voltage, V <sub>IH</sub> , applied to C<br>ables RMS₁, RMS₂ and RMS₃.                                                                                                                                                                                                                                                                                                                                |                                                                          |                                                                  |                                                                                                                                                                                       |  |

| 18,22<br>17, 36, 3,<br>38, 4, 40 | MATCH-CHARACTER<br>HOLDING REGISTER<br>DATA | MHR1, MHR2,<br>MHR3, MHR4,<br>MHR5, MHR6,<br>MHR7, MHR8 | , A low-level input voltage, V <sub>L</sub> , applied to CD (pin<br>6) enables the inputs <u>to the</u> Match-Character<br>Holding Register Load, MHRL. Parallel 8-bit char-                                                                                                                                                                                                                                            |                                                                          |                                                                  |                                                                                                                                                                                       |  |

| 5,23                             | WORD LENGTH<br>SELECT                       | WLS1, WLS2                                              | enables<br>CRL. P<br>Contro<br>WLS <sub>1</sub> a<br>length                                                                                                                                                                                                                                                                                                                                                             | s the inp<br>arallel 8<br>I Registe<br>nd WLS                            | outs of the<br>bit chater with the<br>selecter selecter (5) to e | e, $V_{IL}$ , applied to CD (pin 6)<br>ne Control Register Load,<br>racters are input into the<br>he CRL Strobe (pin 4),<br>the transmitted character<br>ight (8) bits defined by the |  |

|                                  |                                             |                                                         | WLS<br>Vil<br>Vil<br>Vil<br>Vill                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>IH</sub> |                                                                  | Selected Word Length<br>5 BITS<br>6 BITS<br>7 BITS<br>8 BITS                                                                                                                          |  |

|                                  |                                             |                                                         | the app                                                                                                                                                                                                                                                                                                                                                                                                                 | propriate                                                                | e input v                                                        | e strobed or hard-wired to<br>oltage. A high-level input<br>o CD disables WLS, and                                                                                                    |  |

| PIN<br>NUMBER | I/O NAME                                     | SYMBOL  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------|----------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 6             | CHIP DISABLE                                 | СD      | This line controls the disable associated with bus-<br>able inputs and Three-State outputs. A high-level<br>input voltage, $V_{IH}$ , applied to this line disables<br>inputs and removes drive from push-pull output<br>buffers causing them to float. Drivers of disables<br>outputs are not required to sink or source cur-<br>rent. The I/O Lines controlled by Chip Disable are<br>defined below:                                                                                                                                                                                                                                                                     |  |  |  |

|               |                                              |         | Input Lines Three-State Output Lines<br>CRL DRR PE RRI-RRs<br>EPE SFR FE<br>PI MHRL OE<br>WLSIWLS2 MHRI-MHRs<br>RMSI-RMS3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 7-15          | RECEIVER HOLDING-<br>REGISTER DATA<br>OUTPUT | RR₀-RRı | A low-level input voltage, $V_{IL}$ , applied to CD (pin<br>6) enables the Receiver Holding Register out-<br>puts, RR <sub>1</sub> -RR <sub>9</sub> . The parallel data character, in-<br>cluding parity (RR <sub>9</sub> ), appears on these lines.<br>Program control selection of a word length less<br>than eight (8) bits will cause the most significant<br>bits of the character to be forced to a low-level<br>output voltage, $V_{OL}$ . The character will be right<br>justified. RR <sub>1</sub> (pin 15) is the least significant bit<br>of the character. A high-level input voltage, $V_{IH}$ ,<br>applied to CD disables RR <sub>1</sub> -RR <sub>9</sub> . |  |  |  |

| 16            | V <sub>GG</sub> POWER SUPPLY                 | Vgg     | – 12 Volts Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 19            | PARITY INHIBIT                               | PI      | A low-level input voltage, $V_{IL}$ , applied to CD (pin 6) enables the EPE and PI inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 21            | EVEN PARITY ENABLE                           | EPE     | The Even Parity Enable Input and the Parity<br>Inhibit Input to the Control Register, in conjunc-<br>tion with the Control Register Load and Chip Dis-<br>able, select even, odd or no parity to be verified by<br>the receiver. A high-level input voltage, V <sub>IH</sub> , app-<br>lied to EPE selects even parity and a low-level<br>input voltage, V <sub>IL</sub> , select odd parity if a low-level<br>input voltage is applied to Parity Inhibit and Chip<br>Disable. Pl and EPE may be strobed or hard-wired<br>to the appropriate input voltage.                                                                                                                |  |  |  |

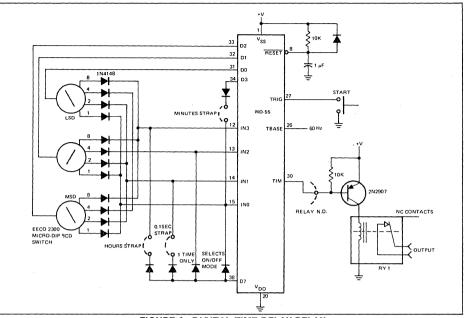

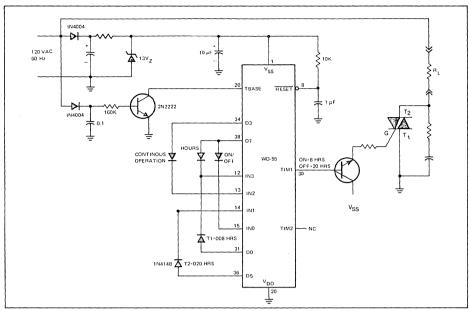

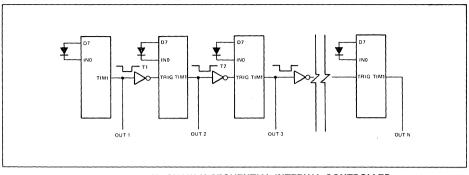

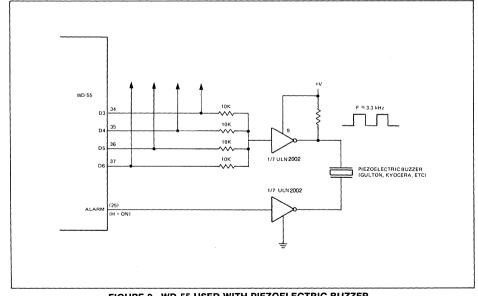

| -             |                                              |         | PI EPE Selected Parity Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |