## VMIVME-7486 486 PC/AT VMEbus CPU

**Product Manual**

12090 South Memorial Parkway Huntsville, Alabama 35803-3308, USA (256) 880-0444 ◆ (800) 322-3616 ◆ Fax: (256) 882-0859 © Copyright December 1999. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, Instant OPC wizard logo, IOMax<sup>™</sup>, IOWorks Access, IOWorks Foundation, IOWorks man figure, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(ler), *VMEaccess, VMEmanager, VMEmonitor*, VMEnet, VMEnet II, and *VMEprobe* are trademarks. The I/O Experts, The I/O Systems Experts, The Soft Logic Experts, and The Total Solutions Provider are service marks of VMIC.

(IOWorks man figure)

The I/O man figure, IOWorks, UIOC, Visual IOWorks, and WinUIOC are registered trademarks of VMIC.

ActiveX is a trademark and Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

Celeron and MMX are trademarks, and Intel and Pentium are registered trademarks of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers' Group.

Other registered trademarks are the property of their respective owners.

VMIC All Rights Reserved This document shall not be duplicated, nor its contents used for any purpose, unless granted express written permission from VMIC.

| V | Л | • |

|---|---|---|

|   |   |   |

#### **RECORD OF REVISIONS**

| REVISION<br>LETTER                             | DATE                             | I                 | PAGES INVOLVED          | CHANGE       | NUMBER        |

|------------------------------------------------|----------------------------------|-------------------|-------------------------|--------------|---------------|

| А                                              | 02/11/94                         | Release           |                         | 94-01        | 154           |

| В                                              | 11/22/94                         | Revised           |                         | 94-05        | 516           |

| С                                              | 05/01/96                         | Cover and page i  | i                       | 96-03        | 310           |

| D                                              | 09/10/96                         | Cover and pages   | iii through xiii        | 96-00        | 339           |

| Е                                              | 12/09/99                         | Reformat and chan | ge area code to 256     | 99-09        | 962           |

|                                                |                                  |                   |                         |              |               |

| VMIC<br>12090 South Memo<br>Huntsville, AL 358 | orial Parkway<br>03-3308 • (256) | 880-0444          | DOC. NO. 500-007486-000 | REV LTR<br>E | PAGE NO.<br>3 |

VMIVME-7486 486 PC/AT VMEbus CPU Product Manual

# **Table of Contents**

| Table of Contents                  | 5  |

|------------------------------------|----|

| List of Figures                    | 9  |

| List of Tables                     | 11 |

| Safety                             |    |

| VMIC Safety Summary                |    |

| Safety Symbols                     | 16 |

| Chapter 1 - Introduction           | 19 |

| About This Manual                  | 20 |

| Product Family                     | 21 |

| References                         | 23 |

| PC/AT Features                     | 24 |

| VMEbus Features                    | 27 |

| Chapter 2 - Installation and Setup | 29 |

| Unpacking Procedures               | 30 |

| Hardware Setup                     | 31 |

| Physical Installation              | 33 |

| VMEbus Connector Pinout            | 34 |

| IDE Connector Pinout               | 36 |

| BIOS Setup                         | 38 |

| Quick BIOS Setup                   | 38 |

| BIOS Features                      | 39 |

| Auto Detect                        | 39 |

| User-Definable Hard Disk Types     | 39 |

| Supports Nonstandard Systems       | 39 |

|                                    |    |

| Shadow RAM Support                    | 40 |

|---------------------------------------|----|

| Typematic Rate and Delay              | 40 |

| Num Lock                              | 40 |

| Boot Sequence and POST Control        | 40 |

| Fast Gate A20 Support                 | 40 |

| BIOS Utilities                        | 40 |

| Accessing the BIOS Utilities          | 41 |

| Using the BIOS Setup Program          | 41 |

| Standard CMOS Setup                   | 44 |

| Date and Day Configuration            | 44 |

| Time Configuration                    | 44 |

| Hard Disk Configuration.              | 44 |

| Floppy                                | 45 |

| Monitor.                              | 45 |

| Keyboard                              | 45 |

| Memory Display                        | 46 |

| Advanced CMOS Setup                   | 46 |

| Typematic Rate and Delay              | 47 |

| Above 1 MB Memory Test                | 47 |

| Memory Test Tick Sound                | 47 |

| Memory Parity Error Checking          | 47 |

| Hit <del> Message Display</del>       | 47 |

| Hard Disk Type 47 RAM Area            | 48 |

| Wait for <f1> If Any Error</f1>       | 48 |

| System Boot Up Num Lock               | 48 |

| Floppy Drive Seek At Boot             | 48 |

| System Boot Up Sequence               | 48 |

| Internal Cache Memory                 | 49 |

| Fast Gate A20                         | 49 |

| ROM Shadow                            | 49 |

| Boot Sector Virus Protection          | 49 |

| Auto-Configuration                    | 49 |

| AT Bus Clock Source                   | 50 |

| Shadow RAM Cache                      | 50 |

| Auto Configuration with BIOS Defaults | 50 |

| Auto Detect Hard Disk                 | 50 |

| Exiting BIOS Setup                    | 51 |

| Configuring Operating Systems         | 52 |

| General Rule Regarding Operating Systems       | 52 |

|------------------------------------------------|----|

| General Rule Regarding Operating Systems       | 52 |

| Configuration Examples                         | 53 |

| Configuring MS-DOS for the VMIVME-7486         | 53 |

| Configuring Windows for the VMIVME-7486        | 54 |

| Chapter 3 - PC/AT Functions                    | 55 |

| CPU Register Model                             | 56 |

| Physical Memory                                | 57 |

| Memory and Port Maps                           | 58 |

| Memory Map                                     | 58 |

| I/O Port Map                                   | 59 |

| PC/AT Interrupts                               | 63 |

| I/O Ports                                      | 68 |

| Video Graphics Adapter                         | 69 |

| Chapter 4 - VMEbus Functions                   | 71 |

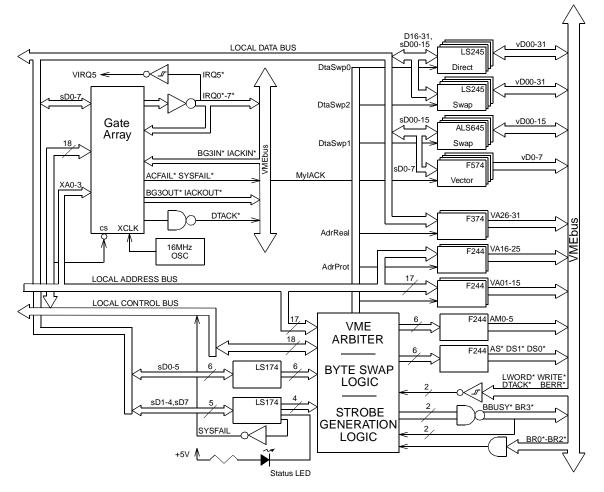

| VMEbus Access                                  | 72 |

| Byte Ordering                                  | 74 |

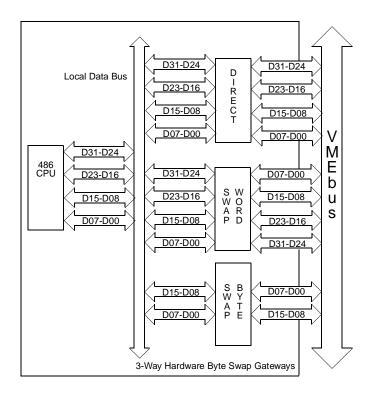

| Byte Swapping                                  | 74 |

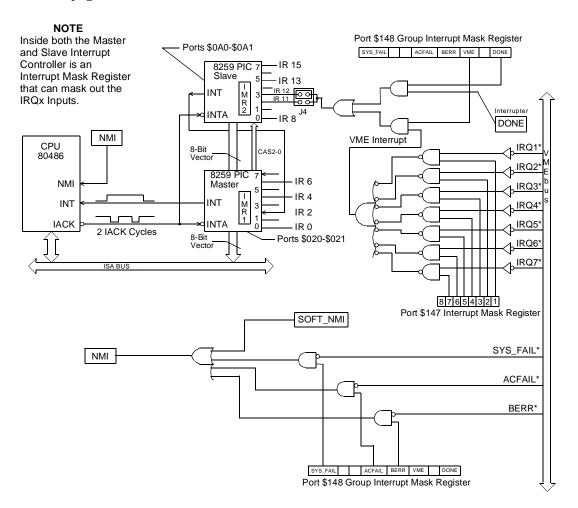

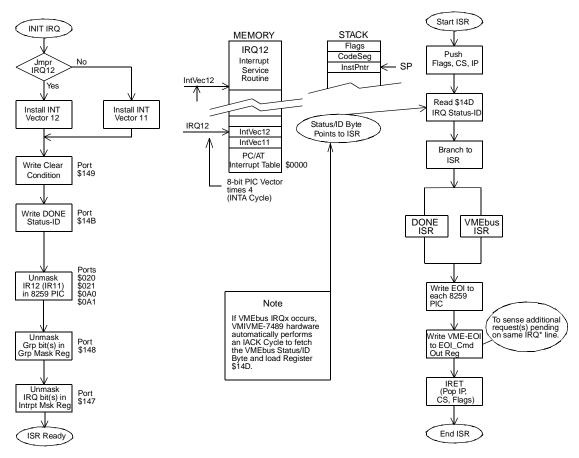

| Interrupt Handling                             | 79 |

| Nonmaskable Interrupts                         | 79 |

| Soft NMI                                       | 79 |

| ACFAIL, SYSFAIL, and BERR NMIs                 | 80 |

| NMI Processing                                 | 80 |

| Maskable Interrupts                            | 81 |

| Condition Polling                              | 82 |

| Interrupter                                    | 84 |

| Requester                                      | 85 |

| System Controller                              | 86 |

| System Registers                               | 87 |

| Register Map                                   | 87 |

| Register Details                               | 88 |

| VMEbus Access Control Register                 | 88 |

| VMEbus Access Control Register: Status LED bit | 89 |

| VMEbus Access Control Register: ROR bit        | 89 |

| VMEbus Access Control Register: SysFail bit    | 89 |

| VMEbus Access Control Register: Big Endian bit | 90 |

| VMEbus Access Control Register: VME Enable bit | 90 |

| VMEbus Standard Access Register                           | 91  |

|-----------------------------------------------------------|-----|

| VMEbus Extended/AM Access Register                        | 92  |

| Interrupt Mask Register                                   | 93  |

| Group Interrupt Mask Register                             | 94  |

| Clear Condition Register                                  | 94  |

| DONE Status-ID Register                                   | 95  |

| Group Interrupt Status Register                           | 95  |

| Soft NMI Select Register                                  | 96  |

| IRQ Status-ID Register                                    | 96  |

| EOI Command Register                                      | 96  |

| Interrupt Level Select Register                           | 97  |

| IRQ* Status Register                                      | 98  |

| Interrupter Status-ID Register                            | 98  |

| Appendix A - Ethernet Option                              |     |

| Ethernet Mezzanine Software Compatibility                 | 100 |

| Ethernet Mezzanine Driver Software                        | 101 |

| Ethernet Mezzanine Diagnostic Software                    | 102 |

| Technical Details                                         |     |

| Appendix B - Flash Memory Option                          | 105 |

| Preparing the Flash Memory Mezzanine                      | 106 |

| Copying Files to Flash Memory Mezzanine                   |     |

| Configuring the VMIVME-7486 to Boot from the Flash Memory |     |

| Mezzanine                                                 | 109 |

| Re-Programming the Flash Memory Mezzanine                 | 110 |

| Technical Details                                         | 111 |

| Programming                                               | 112 |

| Maintenance                                               | 113 |

| Maintenance Prints                                        | 113 |

# List of Figures

| Figure 1-1 VMIVME-7486 Board View                               |

|-----------------------------------------------------------------|

| Figure 1-2 VMIVME-7486 Partial Block Diagram                    |

| Figure 1-3 VMIVME-7486 System VMEbus Functions                  |

| Figure 2-1 I/O Port and Jumper Locations                        |

| Figure 2-2 AMI BIOS Setup Opening Screen                        |

| Figure 2-3 BIOS Setup Warning Screen                            |

| Figure 2-4 Standard CMOS Setup Screen                           |

| Figure 2-5 Advanced CMOS Setup Screen                           |

| Figure 2-6 BIOS Setup Write to CMOS and Exit Screen.         51 |

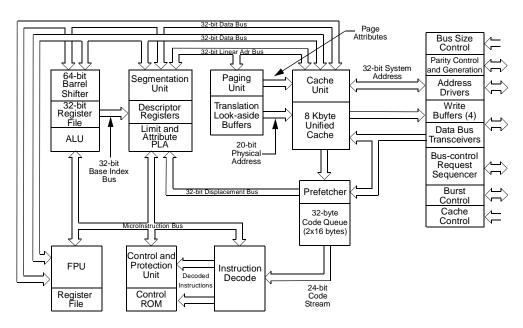

| Figure 3-1 80486 CPU Block Diagram                              |

| Figure 3-2 Interrupt Logic Diagram                              |

| Figure 4-1 VMIVME-7486 VMEbus Interface Block Diagram           |

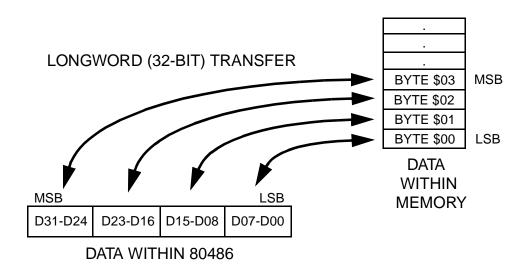

| Figure 4-2 Byte Relationships using the Little Endian 8048675   |

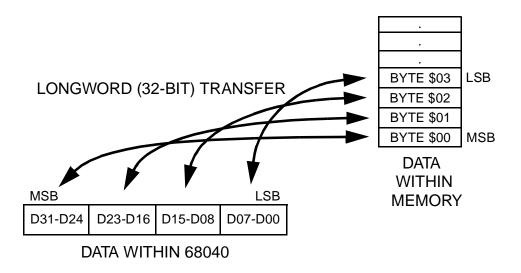

| Figure 4-3 Byte Relationships using the Big Endian 6804076      |

| Figure 4-4 80486-to-VMEbus Data Byte Lanes                      |

| Figure 4-5 Interrupt Response Flow Chart.                       |

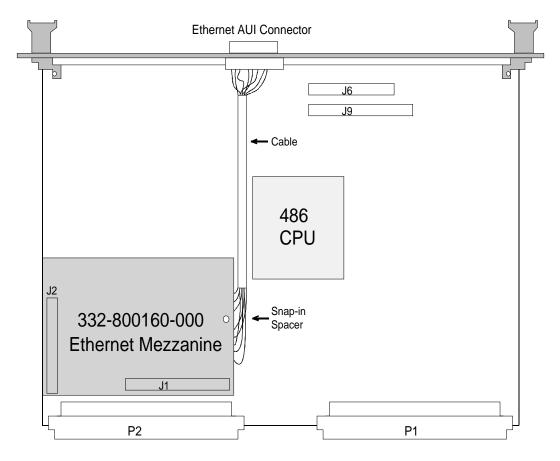

| Figure A-1 Location of the Ethernet Mezzanine                   |

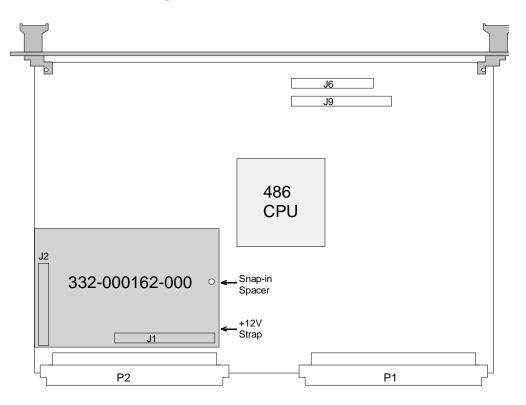

| Figure B-1 Location of +12V Strap                               |

VMIVME-7486 486 PC/AT VMEbus CPU Product Manual

## List of Tables

| Table 1-1 PC/AT I/O Features         26                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------|

| Table 2-1         VMIVME-7486 Jumper Header Functions & Factory Settings         32                                                    |

| Table 2-2 VMEbus P1 & P2 Connector Pin Assignments         34                                                                          |

| Table 2-3 IDE/ATA Hard Drive Header Pin-out         36                                                                                 |

| Table 2-4 BIOS Setup Keystroke Actions         42                                                                                      |

| Table 2-5 VMEbus Window Addresses         52                                                                                           |

| Table 3-1         VMIVME-7486         Real Mode Memory Map         58                                                                  |

| Table 3-2         VMIVME-7486         1         MByte         RAM         Protected         Mode         Memory         Map         58 |

| Table 3-3         VMIVME-7486 4         MByte         RAM         Protected         Mode         Memory         Map         59         |

| Table 3-4 VMIVME-7486 16 MByte RAM Protected Mode Memory Map         59                                                                |

| Table 3-5         VMIVME-7486         I/O         Address         Map         60                                                       |

| Table 3-6 PC/AT Hardware Interrupts         63                                                                                         |

| Table 3-7 PC/AT Interrupt Vector Table         64                                                                                      |

| Table 3-8 Common Supported Graphics Video Resolutions         69                                                                       |

| Table 4-1 VMEbus Byte Assignment to the Data Lines                                                                                     |

| Table 4-2 Byte Swap Modes    78                                                                                                        |

| Table 4-3 VMIVME-7486 VMEbus Register Map         87                                                                                   |

| Table 4-4 Valid VMEbus AM Codes         92                                                                                             |

| Table 4-5 IRQ Level IPL Values         97                                                                                              |

VMIVME-7486 486 PC/AT VMEbus CPU Product Manual

# Safety

## Contents

| VMIC Safety Summary | <br>    | <br> | <br> |     |     |       |   |       |       |    | <br>14 |

|---------------------|---------|------|------|-----|-----|-------|---|-------|-------|----|--------|

| Safety Symbols      | <br>••• | <br> | <br> | ••• | ••• | <br>• | • | <br>• | <br>• | •• | <br>16 |

### VMIC Safety Summary

**Note** The following general safety precautions must be observed during all phases of the operation, service, and repair of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of this product. VME Microsystems International Corporation assumes no liability for the customer's failure to comply with these requirements.

#### Ground the System

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

#### Do Not Operate in an Explosive Atmosphere

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

#### **Keep Away from Live Circuits**

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### Do Not Substitute Parts or Modify System

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VME Microsystems International Corporation for service and repair to ensure that safety features are maintained.

#### **Dangerous Procedure Warnings**

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

WARNING

**WARNING** Dangerous voltages, capable of causing death, are present in this system. Use extreme caution when handling, testing, and adjusting.

## Safety Symbols

General definitions of safety symbols used in this manual:

| Symbol | Description                                                                                                                                                                                                                                                                                                                         |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Instruction manual symbol: the product is marked with this symbol when it is<br>necessary for the user to refer to the instruction manual in order to protect against<br>damage to the system.                                                                                                                                      |

| ţ      | Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1000 volts are so marked).                                                                                                                                                                                                                        |

|        | Protective conductor terminal. For protection against electrical shock in case of a fault. Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment.                                                                                                                  |

|        | Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common,<br>as well as providing protection against electrical shock in case of a fault. Before<br>operating the equipment, terminal marked with this symbol must be connected to<br>ground in the manner described in the installation (operation) manual. |

|        | Frame or chassis terminal. A connection to the frame (chassis) of the equipment which normally includes all exposed metal structures.                                                                                                                                                                                               |

|        | Alternating current (power line).                                                                                                                                                                                                                                                                                                   |

|        | Direct current (power line).                                                                                                                                                                                                                                                                                                        |

|        | Alternating or direct current (power line).                                                                                                                                                                                                                                                                                         |

| Symbol  | Description                                                                                                                                                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WARNING | The WARNING sign denotes a hazard. It calls attention to a procedure, a practice, a condition, or the like, which, if not correctly performed or adhered to, could result in injury or death to personnel.                                     |

| U.      | The CAUTION sign denotes a hazard. It calls attention to an operating procedure, a practice, a condition, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system. |

| Note    | The Note sign denotes important information. It calls attention to a procedure, a practice, a condition or the like, which is essential to highlight.                                                                                          |

VMIVME-7486 486 PC/AT VMEbus CPU Product Manual

## Introduction

## Contents

| bout This Manual | 20 |

|------------------|----|

| roduct Family    | 21 |

| eferences        | 23 |

| C/AT Features    | 24 |

| MEbus Features   | 27 |

### Introduction to the VMIVME-7486

The VMIVME-7486 single-board microcomputer is a complete IBM PC/AT 80486 compatible microcomputer with the additional benefits of Eurocard construction and full compatibility with the VMEbus Specification Rev. C.1.

VMIC's VMIVME-7486 has two operating modes: a standard PC/AT compatible mode, and a VMEbus controller mode. Upon power-up it functions as a standard PC/AT. It executes a PC/AT-type power-on self-test, then boots up MS-DOS, Windows, OS/2, NextStep, XENIX, or any other PC/AT compatible operating system. Its keyboard and video console interaction with the user is typical of a PC/AT. This PC/AT mode of the VMIVME-7486 is discussed in Chapter Three, *PC/AT Functions* on page 55of this manual.

After booting, the VMIVME-7486 may take on the additional functions of a VMEbus controller and interact with other VMEbus modules. The VMEbus controller functions are available by programming the VMIVME-7486's VMEbus interface registers according to Chapter Four, *VMEbus Functions* on page 71 of this manual.

With VMIC's VMIVME-7420 VMEaccess software, the VMIVME-7486 programmer may quickly and easily control VMEbus slave boards simply by linking to a library of VMIVME-7486 VMEbus interrupt and control functions.

#### **About This Manual**

Because this product bridges the traditionally divergent worlds of Intel-based PCs and Motorola-based VMEbus controllers, some confusion over *conventional* notation and terminology may exist. We have made every effort to make this manual consistent by adhering to conventions typical for the Motorola/VMEbus world; nevertheless, users in both camps should review the following notes:

- Hexadecimal numbers are listed Motorola-style, prefixed with a dollar sign: \$F79, for example. By contrast, this same number would be signified 0F79H according to the Intel convention, or 0xF79 by many programmers. Less common are forms such as F79<sub>h</sub> or the mathematician's F79<sub>16</sub>.

- An 8-bit quantity is termed a *byte*, a 16-bit quantity is termed a *word*, and a 32-bit quantity is termed a *longword*. The Intel convention is similar, although their 32-bit quantity is more often called a *double-word*.

- Motorola programmers should note that Intel processors have an I/O bus that is completely independent from the memory bus. Every effort has been made in the manual to clarify this by referring to registers and logical entities in I/O space by prefixing I/O addresses as such. Thus a register at *I/O \$140* is not the same as a register at *\$140*, since the latter is on the memory bus while the former is on the I/O bus.

- Intel programmers should note that addresses are listed in this manual using a linear, *flat-memory* model rather than the old segment:offset model associated with Intel Real Mode programming. Thus, a ROM chip at a segment:offset address of C000:0 will be listed in this manual as being at address \$C0000. For reference, here are some quick conversion formulas:

Segment: Offset to Linear Address

Linear Address =  $(Segment \times 16) + Offset$

Linear Address to Segment:Offset

Segment =  $((Linear Address \div 65536) - <remainder>) \times 4096$

$Offset = < remainder > \times 65536$

Where <remainder> = the remainder of (Linear Address  $\div$  65536)

Note formu

**Note** There are many possible segment:offset addresses for a single location. The formula above will provide a unique segment:offset address by forcing the segment to an even 64 Kbyte boundary, e.g. \$C000, \$E000, etc. When using this formula, make sure to round the offset calculation properly!

### **Product Family**

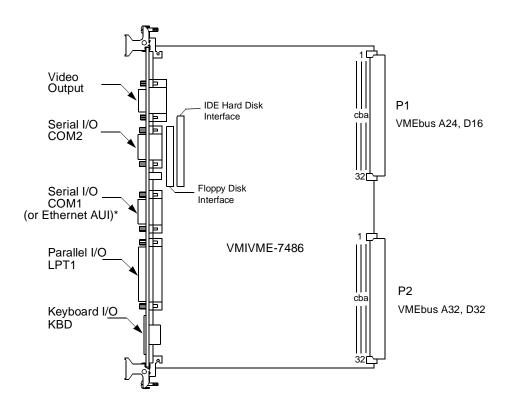

Figure 1-1 shows a simplified view of the VMIVME-7486 board. The VMIVME-7486 is one member of VMIC's line of PC/AT compatible VMEbus controllers, all of which combine a standard PC/AT architecture with the ability to control VMEbus slave boards.

\* Serial port COM1 is unavailable if the Ethernet Mezzanine option is ordered, since the Ethernet AUI connector replaces the COM1 connector. See Appendix A, *Ethernet Option* on page 99 for Ethernet Mezzanine option details.

Figure 1-1 VMIVME-7486 Board View

The VMIVME-7486 is VMIC's baseline PC/AT compatible VMEbus controller and includes such features as standard serial and parallel ports, 16 Mbyte RAM capacity, and super-VGA video.

The VMIVME-7489 is similar to the VMIVME-7486 PC/AT compatible VMEbus controller, but adds external cache memory, high-speed 16550 compatible serial ports, an enhanced bi-directional parallel port, up to 32 Mbytes of RAM, and a PC/104 expansion site.

The VMIVME-7487 does not contain the VMIVME-7489's enhanced I/O, but adds full multiprocessing support with mailbox registers, dual-ported memory, and a master/slave VMEbus interface chip.

VMIC also has other support products for the PC/AT compatible VMEbus controller line. The VMIVME-7450 is a dual-slot module which holds one 3.5 inch floppy drive and one 3.5 inch hard drive. The VMIVME-7432 is a PC/104 module with a VMEbus 6U form factor that allows a half-length PC ISA bus expansion board to be used in a VMEbus chassis along with the VMIVME-7489. The VMIVME-7432 is also compatible with the VMIVME-7450.

VMIC's VMIVME-7420 VMEaccess software includes a linkable library of functions to simplify the integration and development of high performance VMEbus systems using a VMIC PC/AT compatible VMEbus controller. The library includes functions for such low-level chores as setting up VMEbus data transfers, processing interrupts and conditions, and handling errors. VMEaccess is highly recommended for programmers who plan to use any VMIC PC/AT compatible processor for VMEbus control.

#### References

For the most up-to-date physical description and specifications for the VMIVME-7486, please refer to VMIC specification number 800-017486-000.

There are many books widely available on the subject of general PC/AT use and programming. Some reference sources which may be particularly helpful in using or programming the VMIVME-7486 are listed below.

i486 Microprocessor Programmer's Reference Manual and the Intel 486DX Microprocessor Data Book Intel Corporation Literature Sales Dept. P.O Box 58130 Santa Clara, CA 95052-8130

VMEbus Specification Rev. C1 and The VMEbus Handbook VITA - VFEA International Trade Association 10229 N. Scottsdale Road, Suite B Scottsdale, AZ 85253

### **PC/AT Features**

The VMIVME-7486 performs all the functions of a standard IBM PC/AT motherboard with the following features:

- Single-Slot 6U Size

- High performance 80486 processor Available in speeds from 33 MHz to 66 MHz Standard 8 Kbyte internal cache High performace math coprocessor on 80486DX versions

- Up to 16 Mbytes of RAM

- Super-VGA video 1 Megabyte of video DRAM Resolutions up to 1024x768, non-interlaced, 256 colors

- Battery-backed clock/calendar

- Front panel reset switch, and indicators for hard drive activity, power, and status

- On-board ports for keyboard, IDE hard drive, floppy drive, serial and parallel  $\rm I/O$

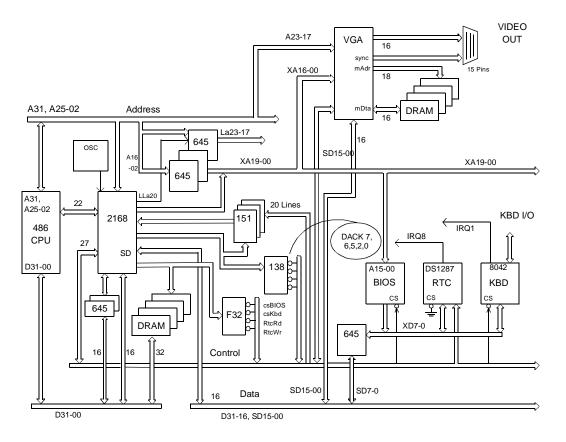

The VMIVME-7486 also supports standard PC/AT I/O features such as those listed in Table 1-1 on page 26. Figure 1-2 on page 25 also shows a partial block diagram of the VMIVME-7486, emphasizing the I/O features.

PC/AT Features

Figure 1-2 VMIVME-7486 Partial Block Diagram

| I/O Feature                                                 | MS-DOS Identifier | Physical Access                                         |

|-------------------------------------------------------------|-------------------|---------------------------------------------------------|

| Two Serial Ports<br>(16450-compatible RS-232C)              | COM1, COM2        | Front Panel<br>DB9P (male) X 2                          |

| One Parallel Port<br>(standard Centronics TTL)              | LPT1              | Front Panel<br>DB25S (female)                           |

| AT-style Keyboard Controller<br>with PS/2-style Adapter     | KBD               | Front Panel PS/2-Style<br>Mini-DIN Circular<br>(female) |

| Real-time Clock/Calendar<br>with Battery and Watchdog Timer | Date, Time        |                                                         |

| SuperVGA Video Controller<br>with 1 Megabyte DRAM           | Display           | Front Panel DB15HD<br>High Density (female)             |

| Floppy Disk Controller<br>(2 drives maximum)                | Drives A, B       | 34-pin Header<br>Flat Cable type                        |

| IDE Fixed Disk Controller<br>(2 drives maximum)             | Drives C, D       | 40-pin Header<br>Flat Cable type                        |

| Hardware Reset                                              | Cold Boot         | Front Panel Pushbutton                                  |

| IBM/PC Sound                                                | Веер              | On-board Small Speaker                                  |

#### Table 1-1 PC/AT I/O Features

#### VMEbus Features

The VMIVME-7486 incorporates the following VMEbus functions:

- Single-slot, 6U-height VMEbus board

- Complete 6-line Address Modifier (AM-Code) programmability

- 32-bit data interface with 3-way byte/word swap in hardware

- User-configured interrupt handler

- User-configured interrupter

- System Controller mode (jumper enabled) as level 3 single-level arbiter

- Complete VMEbus access through Real-mode memory window, or Protected-mode linear addressing above local DRAM

- Front panel "vital sign" indicators (+5V Power, programmable SYSFAIL\* signal)

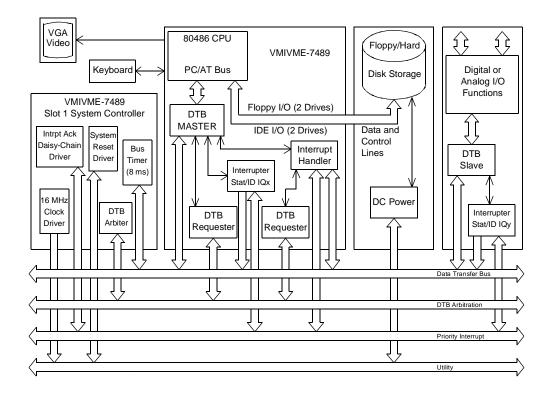

Figure 1-3 VMIVME-7486 System VMEbus Functions

Figure 1-3 shows the VMIVME-7486 functions in a typical VME bus system. The VMIVME-7486 is a versatile single-board solution for VME bus control with familiar PC/AT operation.

# Installation and Setup

## Contents

| Unpacking Procedures          | <br>30 |

|-------------------------------|--------|

| Hardware Setup                | <br>31 |

| Physical Installation         | <br>33 |

| VMEbus Connector Pinout       | <br>34 |

| DE Connector Pinout           | <br>36 |

| BIOS Setup                    | <br>38 |

| Configuring Operating Systems | <br>52 |

|                               |        |

### Introduction

This chapter describes unpacking, inspection, hardware jumper settings, connector definitions, installation, system setup, and operation of the VMIVME-7486.

### **Unpacking Procedures**

**CAUTION** Some of the components assembled on VMIC's products may be sensitive to electrostatic discharge and damage may occur on boards that are subjected to a high energy electrostatic field. When the board is placed on a bench for configuring, etc., it is suggested that conductive material be inserted under the board to provide a conductive shunt. Unused boards should be stored in the same protective boxes in which they were shipped.

Upon receipt, any precautions found in the shipping container should be observed. All items should be carefully unpacked and thoroughly inspected for damage that might have occurred during shipment. The board(s) should be checked for broken components, damaged printed circuit board(s), heat damage, and other visible contamination. All claims arising from shipping damage should be filed with the carrier and a complete report sent to VMIC together with a request for advice concerning the disposition of the damaged item(s).

### **Hardware Setup**

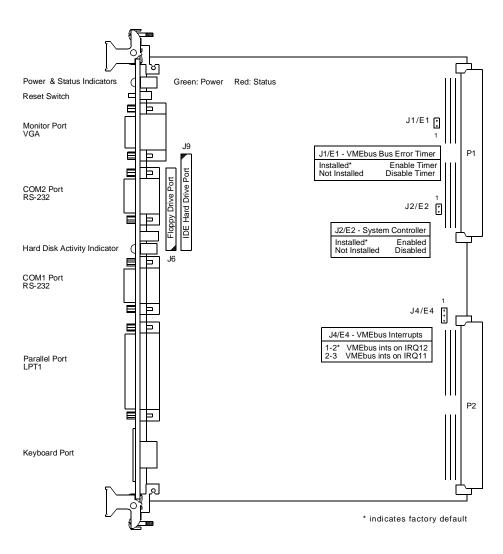

The VMIVME-7486 has been tested for system operation and shipped with factory-installed header jumpers. Figure 2-1 illustrates the physical location of the user-configurable jumpers and connectors on the board. Table 2-1 on page 32 lists each jumper designator, its function, and the factory-installed default configuration.

Figure 2-1 I/O Port and Jumper Locations

| Header Number | FUNCTION                                                                                   | FACTORY SETTING                                     |

|---------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------|

| J1/E1         | Enable VMEbus Bus Error 10 $\mu$ S Timeout Timer                                           | Installed                                           |

| J2/E2         | Enable System Controller                                                                   | Installed                                           |

| J4/E4         | Selects VMEbus interrupts through either IRQ11 or IRQ12 of the PC/AT interrupt controller. | 1-2: Select IRQ12<br>(Default)<br>2-3: Select IRQ11 |

| Table 2.4 |                 | lumper Header | Eurotiono | 9 Easton Sotting  | ~ |

|-----------|-----------------|---------------|-----------|-------------------|---|

|           | VIVI VIVIE-7400 | Jumper neauer | Functions | & Factory Setting | 5 |

**Note** Any other jumper locations are reserved for VMIC use only and should not be altered from the factory default settings.

### **Physical Installation**

CAUTION Do not install or remove board while power is applied.

De-energize the equipment and insert the board into an appropriate slot of the chassis. While ensuring that the board is properly aligned and oriented in the supporting board guides, slide the board smoothly forward against the mating connector until firmly seated. Note that if a drive module or other similar expansion module is to be used, it must typically be mounted and connected to the VMIVME-7486 first. Follow the instructions for the expansion module and ensure all connectors are properly mated before inserting the whole assembly into the VMEbus.

#### VMEbus Connector Pinout

The VMIVME-7486 conforms to the VMEbus physical specification for a 6U x 4HP dual Eurocard (dual height, single-slot width). It can be plugged directly into any standard chassis accepting this type of board.

The VMIVME-7486 may be attached to a dual P1/P2 VMEbus backplane or a single P1 backplane. For 16-bit data transfers and 24-bit addressing a single P1 backplane is sufficient, but for 32-bit data transfers and 32-bit addressing a dual P1/P2 backplane is required.

Front panel connections for the parallel, video, and serial ports are typical for any PC/AT. The keyboard connector is a standard mini-DIN PS/2 style connector; an adapter is supplied to connect a keyboard with a larger connector to the VMIVME-7486.

Table 2-2 shows the pin assignments for the VMEbus P1 and P2 connectors. Note that only Row B of connector P2 is used: all other pins on P2 are reserved and should not be connected. A detailed discussion of VMEbus hardware signals (such as the Bus Grant and Interrupt Acknowledge Daisy Chains) is included in Chapter Four.

| Pin<br>Number | P1 Row A<br>Signal | P1 Row B<br>Signal | P1 Row C<br>Signal | P2 Row B<br>Signal |

|---------------|--------------------|--------------------|--------------------|--------------------|

| 1             | D00                | BBSY*              | D08                | +5V                |

| 2             | D01                | BCLR* (Not Used)   | D09                | GND                |

| 3             | D02                | ACFAIL*            | D10                | Reserved           |

| 4             | D03                | BG0IN* (Ignored)   | D11                | A24                |

| 5             | D04                | BG0OUT* (Ignored)  | D12                | A25                |

| 6             | D05                | BG1IN* (Ignored)   | D13                | A26                |

| 7             | D06                | BG1OUT* (Ignored)  | D14                | A27                |

| 8             | D07                | BG2IN* (Ignored)   | D15                | A28                |

| 9             | GND                | BG2OUT* (Ignored)  | GND                | A29                |

| 10            | SYSCLK             | BG3IN*             | SYSFAIL*           | A30                |

| 11            | GND                | BG3OUT*            | BERR*              | A31                |

| 12            | DS1*               | BR0* (Ignored)     | SYSRESET*          | GND                |

| 13            | DS0*               | BR1* (Ignored)     | LWORD*             | +5V                |

| 14            | WRITE*             | BR2* (Ignored)     | AM5                | D16                |

| 15            | GND                | BR3*               | A23                | D17                |

| Table 2-2 | VMEbus P1 | & P2 Connector | Pin Assignments |

|-----------|-----------|----------------|-----------------|

|-----------|-----------|----------------|-----------------|

| Pin<br>Number | P1 Row A<br>Signal | P1 Row B<br>Signal | P1 Row C<br>Signal | P2 Row B<br>Signal |

|---------------|--------------------|--------------------|--------------------|--------------------|

| 16            | DTACK*             | AM0                | A22                | D18                |

| 17            | GND                | AM1                | A21                | D19                |

| 18            | AS*                | AM2                | A20                | D20                |

| 19            | GND                | AM3                | A19                | D21                |

| 20            | IACK*              | GND                | A18                | D22                |

| 21            | IACKIN*            | SERCLK (Ignored)   | A17                | D23                |

| 22            | IACKOUT*           | SERDAT* (Ignored)  | A16                | GND                |

| 23            | AM4                | GND                | A15                | D24                |

| 24            | A07                | IRQ7*              | A14                | D25                |

| 25            | A06                | IRQ6*              | A13                | D26                |

| 26            | A05                | IRQ5*              | A12                | D27                |

| 27            | A04                | IRQ4*              | A11                | D28                |

| 28            | A03                | IRQ3*              | A10                | D29                |

| 29            | A02                | IRQ2*              | A09                | D30                |

| 30            | A01                | IRQ1*              | A08                | D31                |

| 31            | -12V               | +5V STDBY          | +12V               | GND                |

| 32            | +5V                | +5V                | +5V                | +5V                |

Table 2-2 VMEbus P1 & P2 Connector Pin Assignments (Continued)

## **IDE Connector Pinout**

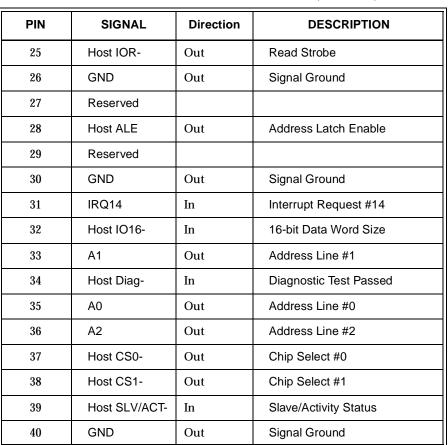

Table 2-3 describes the pin assignment for the IDE/ATA hard drive header (J9 on Figure 2-1). Like the floppy header it has an odd-numbered row and an even-numbered row (20-pins per row, 40-pins total).

| PIN | SIGNAL      | Direction | DESCRIPTION             |  |

|-----|-------------|-----------|-------------------------|--|

| 1   | Host RESET  | Out       | Reset Drive             |  |

| 2   | GND         | Out       | Signal Ground           |  |

| 3   | Host DATA7  | In/Out    | Bidirectional Data 07   |  |

| 4   | Host DATA8  | In/Out    | Bidirectional Data 08   |  |

| 5   | Host DATA6  | In/Out    | Bidirectional Data 06   |  |

| 6   | Host DATA9  | In/Out    | Bidirectional Data 09   |  |

| 7   | Host DATA5  | In/Out    | Bidirectional Data 05   |  |

| 8   | Host DATA10 | In/Out    | Bidirectional Data 10   |  |

| 9   | Host DATA4  | In/Out    | Bidirectional Data 04   |  |

| 10  | Host DATA11 | In/Out    | Bidirectional Data 11   |  |

| 11  | Host DATA3  | In/Out    | Bidirectional Data 03   |  |

| 12  | Host DATA12 | In/Out    | Bidirectional Data 12   |  |

| 13  | Host DATA2  | In/Out    | Bidirectional Data 02   |  |

| 14  | Host DATA13 | In/Out    | Bidirectional Data 13   |  |

| 15  | Host DATA1  | In/Out    | Bidirectional Data 01   |  |

| 16  | Host DATA14 | In/Out    | Bidirectional Data 14   |  |

| 17  | Host DATA0  | In/Out    | Bidirectional Data 00   |  |

| 18  | Host DATA15 | In/Out    | Bidirectional Data 15   |  |

| 19  | GND         | Out       | Signal Ground           |  |

| 20  | Key         | None      | Unused, Keying Position |  |

| 21  | Reserved    |           |                         |  |

| 22  | GND         | Out       | Signal Ground           |  |

| 23  | Host IOW-   | Out       | Write Strobe            |  |

| 24  | GND         | Out       | Signal Ground           |  |

Table 2-3 IDE/ATA Hard Drive Header Pin-out

| Table 2-3 IDE/ATA Hard Drive | Header Pin-out (Continued) |

|------------------------------|----------------------------|

|------------------------------|----------------------------|

Up to two IDE hard drives are directly supported in a multitude of storage capacities. User selection of the type of hard drive(s) and specific storage format is done during general BIOS Setup procedures.

For convenient disk storage for the VMIVME-7486, VMIC has drive modules that support a floppy drive and hard drive in a VMEbus 6U form factor. Power is drawn from the VMEbus P1 connector and ribbon cables from the VMIVME-7486 connect directly to the floppy and hard disk drives.

### **BIOS Setup**

The VMIVME-7486 has an on-board setup program that controls many configuration options. These options are saved in a special nonvolatile, battery-backed memory chip and are collectively referred to as the board's "CMOS configuration". The CMOS configuration controls many details concerning the behavior of the hardware from the moment power is applied.

#### Quick BIOS Setup

The BIOS Setup program has many powerful options, but only a few are critical for normal VMIVME-7486 operation, and these are stored as default values in the BIOS Setup program. What follows is a summary of the procedure necessary to load the default BIOS Setup values and configure the system for normal VMIVME-7486 operations. For more detailed descriptions of all the BIOS Setup options, read the subsequent sections on BIOS Features and BIOS Utilities.

- 1. Reboot the system. This may be accomplished either by applying power to the system, pressing the front panel reset switch, or pressing <CTRL+ALT+DEL> from the keyboard if the system is already running.

- Press <DEL> to enter the setup program as soon as the screen displays the Press

<Del> to run Setup message. You may have to press <F1> to clear the keyboard error first

- 3. When the opening screen appears (see Figure 2-2 on page 41), press <F2> or <F3> repeatedly to select a readable screen color.

- 4. Select the **Auto Configuration with BIOS Defaults** option and confirm at the prompt by pressing <Y> then <ENTER>.

- 5. After the default values are loaded, press any key to continue.

- 6. Select the **Auto Detect Hard Disk** utility and confirm the auto-detect settings for the hard disks. Note that if no hard disk is present, it may take up to a minute to determine this fact.

- 7. Select the **Standard CMOS Setup** utility and confirm at the warning screen (see Figure 2-3 on page 43).

- 8. From the Standard CMOS Setup screen, set the date and time.

- 9. From the Standard CMOS Setup screen, configure the floppy drive type(s) (and the hard drive type if it was not properly auto-detected). The type of drive must be properly entered or boot errors will occur.

- 10. Press <ESC> to return to the opening screen.

- 11. Select the Write to CMOS and Exit option and confirm.

- 12. The VMIVME-7486 will automatically reboot with the new values in effect.

## **BIOS OVERVIEW**

The system BIOS (Basic Input/Output System) is a collection of device drivers, initialization routines, system data, and other code that controls the interface between the operating system (e.g., MS-DOS, UNIX, XENIX, etc.) and the system hardware.

Several types of BIOS may exist in a PC system. Every PC has a system BIOS like that described above. Usually a video BIOS also exists to control the interface between the video adapter and the CPU. In addition, option ROMs (which can also be BIOS ROMs) may be present to control specific hardware devices, such as hard drives or network interfaces.

PC/AT compatible systems, also called ISA (Industry Standard Architecture) systems, must have a place to store system information when the computer is turned off. The original IBM AT had 64 bytes of nonvolatile memory storage in CMOS RAM. All PC/AT compatible systems have at least 64 bytes of CMOS RAM, which is usually part of the real-time clock device. The VMIVME-7486, for example, has 114 bytes of CMOS RAM. The BIOS Setup program uses this nonvolatile storage area to keep configuration data – this is why the term *CMOS Setup* is often used synonymously with *BIOS Setup*.

The system BIOS of the VMIVME-7486 is stored in a ROM (Read Only Memory) chip. The BIOS is located at physical address \$F0000 and occupies 64 Kbytes of main memory, thus occupying the topmost 64 Kbytes of the 1 Mbyte Real Mode addressing space. An image of this BIOS also appears in the topmost 64 Kbytes of Protected Mode address space, beginning at address \$FFFF 0000.

#### **BIOS Features**

#### Auto Detect

The BIOS automatically detects all system DRAM, the type of microprocessor used in the system, and on-board floppy, IDE, serial I/O, and parallel I/O controllers. It automatically configures on-board controllers to prevent conflicts with controllers in I/O expansion slots.

#### **User-Definable Hard Disk Types**

The BIOS Setup allows the user to define hard disk types for both hard drives in a system.

#### **Supports Nonstandard Systems**

The BIOS can be configured to bypass keyboard, floppy, and video boot errors so specialized systems (such as file servers) without keyboards, floppies, or monitors can be configured easily.

#### **Shadow RAM Support**

The BIOS can selectively shadow 32 Kbytes of ROM at \$C0000 and \$C8000. The 64 Kbyte system BIOS ROM at \$F0000 is automatically shadowed to RAM.

ROM shadowing is a technique whereby the contents of ROM are copied from slow ROM to RAM, where the data can be accessed more than four times faster. Often the ROM is only eight bits or sixteen bits wide while the RAM is as wide as the processor's memory bus. In any case the wider and speedier RAM shadow is accessed much faster than the narrower and slower ROM.

In the BIOS Setup, shadow RAM settings appear on the Advanced CMOS Setup screen. Each option permits an address segment to be shadowed from ROM to RAM.

#### **Typematic Rate and Delay**

The BIOS Setup can configure the repetition speed of a keystroke and the time delay before the repeating starts.

#### Num Lock

The keyboard's **Num Lock** function may be set to on or off after system boot by the BIOS Setup.

#### **Boot Sequence and POST Control**

The BIOS Setup allows the VMIVME-7486 to boot from drive C: or drive A: first. Various elements of the power-on self-test may also be disabled in order to speed up the reboot process.

#### Fast Gate A20 Support

The BIOS supports the Fast Gate A20 option of the VMIVME-7486. Normally, the keyboard controller is used to switch between Real and Protected addressing modes with Gate A20. Fast Gate A20 substitutes a faster method for address mode switching using I/O ports.

#### **BIOS Utilities**

The BIOS in the VMIVME-7486 includes an advanced setup program that not only allows CMOS configuration, but contains other useful utilities as well. Here is a summary of the BIOS Setup functions:

- Automatic CMOS setup and configuration

- Manual CMOS setup and configuration

- · Automatic hard disk setup and configuration

#### Accessing the BIOS Utilities

The BIOS Setup program may only be activated immediately after power up, reset, or reboot. To access the opening screen, perform the following steps:

- 1. Reboot the system. This may be accomplished either by applying power to the system, pressing the front panel reset switch, or pressing <CTRL+ALT+DEL> from the keyboard if the system is already running.

- 2. Press the <DEL> key during subsequent power-on self-testing (POST processing). The keystroke will generate a keyboard error, and the BIOS will stop execution and inquire whether the user wants to enter setup. You may have to press <F1> to clear the keyboard error first.

- 3. Press <DEL> to enter the setup program and display the opening screen as shown in Figure 2-2 on page 41.

|           | AMIBIOS SETUP PROGRAM AMI BIOS SETUP UTILITIES<br>(c) 1992 American Megatrends Inc., All Rights Reserved |                                                             |                  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------|--|--|

|           | << STANDARD C<br>ADVANCED C<br>AUTO CONFIGURATION<br>AUTO DETECT<br>WRITE to CMC<br>DO NOT WRITE to      | MOS SETUP<br>WITH BIOS DEFAULTS<br>HARD DISK<br>DS and EXIT |                  |  |  |

| Standa    | d CMOS Setup for Changing                                                                                | g Time, Date, Hard Disk '                                   | Type, etc.       |  |  |

| Esc: Exit | Arrow keys: Select                                                                                       | F2/F3: Color                                                | F10: Save & Exit |  |  |

Figure 2-2 AMI BIOS Setup Opening Screen

#### Using the BIOS Setup Program

While running the setup program, the following keystroke actions are defined. Note that some keystrokes only work with certain screens.

| Keystroke                                                                                   | Action                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <esc></esc>                                                                                 | Returns to previous screen (or exit from Opening Screen).                                                                                                                                                                             |

| Cursor Keys                                                                                 | Moves the cursor from one option to the next.                                                                                                                                                                                         |

| <pg up=""><br/><pg dn=""><br/><ctrl-pgup><br/><ctrl-pgdn></ctrl-pgdn></ctrl-pgup></pg></pg> | Modifies the default value of the options for the highlighted<br>parameter. If there are fewer than ten options, <ctrl-pgup> and<br/><ctrl-pgdn> operate just like plain <pg up=""> and <pg dn="">.</pg></pg></ctrl-pgdn></ctrl-pgup> |

| <f1></f1>                                                                                   | Displays help messages.                                                                                                                                                                                                               |

| <f2></f2>                                                                                   | Changes background colors.                                                                                                                                                                                                            |

| <f3></f3>                                                                                   | Changes foreground colors.                                                                                                                                                                                                            |

| <f5></f5>                                                                                   | Restores the values resident when the current Setup session<br>began. These values are taken from CMOS memory if CMOS<br>memory was uncorrupted at the start of the session. Otherwise,<br>they will be the default values.           |

| <f6></f6>                                                                                   | Loads all features in the Advanced CMOS Setup screen with the BIOS Setup defaults.                                                                                                                                                    |

| <f7></f7>                                                                                   | Loads all features in the Advanced CMOS Setup screen with the<br>Power-On defaults, which are the same as the BIOS defaults on<br>the VMIVME-7486.                                                                                    |

| <f10></f10>                                                                                 | Saves all changes made to BIOS Setup and returns to DOS.                                                                                                                                                                              |

#### Table 2-4 BIOS Setup Keystroke Actions

**Note** The default value for <F5>, <F6>, and <F7> is always *N*. To execute these options, press <Y> then <ENTER>.

The Setup Utility is divided into the following options:

- Standard CMOS Setup

- Advanced CMOS Setup

- Auto Configure with BIOS Defaults

- Auto Detect Hard Disk

- Exit and Save CMOS Settings

- Exit Without Saving

Figure 2-2 on page 41 shows the **Standard CMOS Setup** option highlighted in the menu list area and the corresponding status message in the message area. The first two CMOS setup options allow manual configuration of the VMIVME-7486. The **Auto Configuration with BIOS Defaults** option restores the VMIVME-7486 with all its factory default CMOS settings (see the section Quick BIOS Setup on page 38 for an example using this option). The **Auto Detect Hard Disk** option is very convenient for configuring a hard drive of unknown type. The last two options exit from the Setup Screen.

Each time the user selects **Standard CMOS Setup** or **Advanced CMOS Setup**, the warning screen shown in Figure 2-3 is displayed. Press any key to remove the warning message and proceed to the selected setup screen.

Figure 2-3 BIOS Setup Warning Screen

| AMIBIOS SETUP PROGRAM WARNING INFORMATION<br>(c) 1992 American Megatrends Inc., All Rights Reserved |                                                            |  |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| Improper Use                                                                                        | of Setup May Cause Problems!!                              |  |

| If System Hangs, Rebo                                                                               | oot System and Enter Setup by Pressing the <del> key</del> |  |

| Do any of the                                                                                       | following After Entering Setup                             |  |

| (i)                                                                                                 | Alter Options to make System Work                          |  |

| (ii)                                                                                                | Load BIOS Setup Defaults                                   |  |

| (iii)                                                                                               | Load Power-On Defaults                                     |  |

|                                                                                                     |                                                            |  |

| Hit <esc> to S</esc>                                                                                | Stop now, Any other Key to Continue.                       |  |

|                                                                                                     | 1 / 5 5                                                    |  |

|                                                                                                     |                                                            |  |

|                                                                                                     |                                                            |  |

|                                                                                                     |                                                            |  |

#### Standard CMOS Setup

The Standard CMOS Setup screen permits the user to configure and set system components such as the time and date, floppy/hard disk drives, video adapter type, and keyboard type. **Standard CMOS Setup** is the topmost option on the setup opening screen. Press <ENTER> when this option is highlighted and a screen similar to the one shown in Figure 2-4 appears after the warning screen.

|                                                                              | AMIBIOS SETUP PROGRAM STANDARD CMOS SETUP<br>(c) 1992 American Megatrends, Inc., All Rights Reserved |      |                      |       |       |                  |      |     |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|----------------------|-------|-------|------------------|------|-----|

| Date (mm/date/year)<br>Time (hour/min/sec)                                   | : Thu, Jan 31 1991<br>: 15 : 23 : 15                                                                 |      | ase merr<br>Ext. Mem | 5     |       | 640 KB<br>: 0 KB |      |     |

| Hard disk C: type<br>Hard disk D: type<br>Floppy drive A:<br>Floppy drive B: | : Not Installed<br>: Not Installed<br>: Not Installed<br>: Not Installed                             | Cyln | Head                 | WPcom | LZone | Sect             | Size |     |

| Primary display<br>Keyboard                                                  | : Not Installed<br>: Not Installed                                                                   | Sun  | Mon                  | Tue   | Wed   | Thu              | Fri  | Sat |

|                                                                              |                                                                                                      | 30   | 31                   | 1     | 2     | 3                | 4    | 5   |

|                                                                              |                                                                                                      | 6    | 7                    | 8     | 9     | 10               | 11   | 12  |

| Month                                                                        | : Jan, Feb, , Dec                                                                                    | 13   | 14                   | 15    | 16    | 17               | 18   | 19  |

| Date                                                                         | : 01, 02, 03, , 31                                                                                   | 20   | 21                   | 22    | 23    | 24               | 25   | 26  |

| Year                                                                         | : 1901, 1902, , 2099                                                                                 | 27   | 28                   | 29    | 30    | 31               | 1    | 2   |

|                                                                              |                                                                                                      | 3    | 4                    | 5     | 6     | 7                | 8    | 9   |

Figure 2-4 Standard CMOS Setup Screen

#### **Date and Day Configuration**

Move the cursor to the **Date** field with the cursor keys and set the date and day by pressing <PG UP> or <PG DN>.

#### **Time Configuration**

Move the cursor to the **Time** field with the cursor keys and set the time by pressing <PG UP> or <PG DN> to change values upward or downward.

#### Hard Disk Configuration

Hard disk drive types are identified by the following seven parameters:

- Drive Type

- Number of Cylinders

- Number of Heads

- Write Pre-compensation

- Landing Zone

- Number of Sectors

- Capacity

For drive types 1 through 46 the BIOS Setup utility automatically prescribes the remaining six parameters. The parameters for type 47 under hard disk C: and hard disk D: can be different. Drive type 47 thus allows two different user-defined hard disk drives to reside in the computer system. The user must enter the correct drive parameters when using type 47. Values for user-defined type hard disks may be easily determined using the **Auto Detect Hard Disk** option from the opening screen (described on page 50).

The Not Installed disk option should be selected for diskless microcomputer applications, diskless workstations, and SCSI hard drives.

#### Floppy

Floppy drive A: and floppy drive B: may each have one of five settings:

- 360 KB 5-1/4 inch

- 1.2 MB 5-1/4 inch

- 720 KB 3-1/2 inch

- 1.44 MB 3-1/2 inch

- 2.88 MB 3-1/2 inch

- Not Installed (used for diskless workstations)

#### Monitor

The **Primary display** settings are:

- Monochrome

- Color 40x25

- VGA/PGA/EGA

- Color 80x25

- Not Installed (used for network file servers)

#### Keyboard

The possible keyboard settings are **Installed** and **Not Installed**. If **Not Installed** is selected, the BIOS does not test for the presence of a keyboard in the system, permitting keyboardless systems such as embedded VMEbus controllers to boot normally.

#### **Memory Display**

The memory display is not configured by the user since the BIOS automatically senses and reports system memory. Memory is reported in 64 Kbyte increments. The BIOS will report up to 640 Kbytes in the **Base Memory** field and 65,472 Kbytes in the **Extended Memory** field. Extended memory is addressed from just above the 1 Mbyte Real Mode boundary to the 64 Mbyte level.

#### **Advanced CMOS Setup**

The **Advanced CMOS Setup** option of the BIOS Setup utility allows the user to configure more advanced components of memory configuration, peripheral support, and power management. **Advanced CMOS Setup** is the second option on the setup opening screen. When this option is selected, the screen shown in Figure 2-4 appears after the warning screen.

| (c) 1992 Am                                                        | erican Megatrei | nds Inc., All Rights Reserved                |           |

|--------------------------------------------------------------------|-----------------|----------------------------------------------|-----------|

| Typematic Rate Programming                                         | : Disabled      | AT Bus Clock Source                          | : SCLK/4  |

| Typematic Rate Delay (msec)                                        | : 500           | Shadow RAM Cacheable                         | : Enabled |

| Typematic Rate (Chars/Sec)                                         | : 15            |                                              |           |

| Above 1 MB Memory Test                                             | : Disabled      |                                              |           |

| Memory Test Tick Sound                                             | : Enabled       |                                              |           |

| Memory Parity Error Check                                          | : Enabled       |                                              |           |

| Hit <del> Message Display</del>                                    | : Enabled       |                                              |           |

| Hard Disk Type 47 RAM Area                                         | : 0:300         |                                              |           |

| Wait for <f1> If Any Error</f1>                                    | : Enabled       |                                              |           |

| System Boot Up Num Lock                                            | : On            |                                              |           |

| Floppy Drive Seek At Boot                                          | : Disabled      |                                              |           |

| System Boot Up Sequence                                            | : A:, C:        |                                              |           |

| Internal Cache Memory                                              | : Enabled       |                                              |           |

| Fast Gate A20 Option                                               | : Enabled       |                                              |           |

| Video ROM Shadow C000, 32K                                         | : Enabled       |                                              |           |

| Adaptor ROM Shadow C800, 32K                                       | : Disabled      |                                              |           |

| Boot Sector Virus Protection                                       | : Disabled      |                                              |           |

| Auto-Configuration                                                 | : Enabled       | ĺ)                                           |           |

|                                                                    |                 | <u> </u>                                     |           |

|                                                                    |                 |                                              |           |

| Esc: Exit Arrow keys: Sel (Cnt<br>F5: Old Values F6: BIOS Setup De |                 | Modify F1: Help F2: Color<br>wer-On Defaults |           |

| Figure 2-5 | Advanced | CMOS | Setup | Screen |

|------------|----------|------|-------|--------|

|------------|----------|------|-------|--------|

Note

Note The values shown in Figure 2-4 represent the factory defaults.

The **Advanced CMOS Setup** is equipped with a series of help screens. Access help by pressing <F1> while the feature under question is selected. The help screen will display the settings available for a particular configuration feature and provide special help for some options.

#### **Typematic Rate and Delay**

**Typematic Rate Delay** and **Typematic Rate** control the speed at which a keystroke is repeated. When a key is pressed and held down, the character is displayed and begins to repeat after the time set by the **Typematic Rate Delay**. The actual rate of repeat is set by the **Typematic Rate** value. Available delay options are: 250, 500, 750, and 1000 milliseconds. Available rate options are: 6, 8, 10, 12, 15, 20, 24, and 30 characters per second. The **Typematic Rate Programming** option enables or disables typematic control. Note that some keyboards do not respond to typematic programming – on such keyboards, the typematic settings simply have no effect.

#### Above 1 MB Memory Test

The **Above 1 MB Memory Test** option, when enabled, will execute the POST memory routines on the RAM above 1 Mbyte (if present on the system). If disabled, the BIOS will only check the first 1 Mbyte of RAM. This option should normally be disabled on the VMIVME-7486 to avoid unwanted VMEbus accesses through the Protected Mode VMEbus Window, which exists just beyond available extended memory.

#### **Memory Test Tick Sound**

The **Memory Test Tick Sound** option will enable or disable the ticking sound during the memory test.

#### **Memory Parity Error Checking**

**Note** The **Memory Parity Error Checking** option should *ALWAYS BE ENABLED* to allow the VMIVME-7486 to process VMEbus interrupts.

The **Memory Parity Error Checking** option enables or disables parity error checking for all system RAM. This setting should always be enabled on the VMIVME-7486 in order to enable the NMI interrupts used for VMEbus interrupt processing.

Hit <Del> Message Display

Disabling the Hit <Del> Message Display option will prevent the message:

Hit <Del> if you want to run Setup

from appearing when the system boots. Even with this message disabled, the system still responds normally to the *<DEL>* key request for setup; it just doesn't display the message.

#### Hard Disk Type 47 RAM Area

In the Hard Disk Drive configuration in Standard CMOS Setup, there is a user-definable hard disk type (type 47) which can be used to configure a non-standard hard disk drive for either drive C: or D:. Ordinarily, the data for disk type 47 is stored in \$0300 in lower system RAM, but it can be kept in the top 1 Kbyte of applications memory, starting at address \$9FC00. These settings take effect only if the shadow RAM options are disabled.

#### Wait for <F1> If Any Error

Before the system boots, the BIOS executes POST (Power-On Self-Test), a series of system diagnostic routines. If any of these tests generate a nonfatal error and the system can still function, the BIOS will respond with an appropriate error message followed by:

Press <F1> to continue...

If the **Wait for** <**F1**> **if Any Error** option is disabled, nonfatal errors will not generate the above statement, but the BIOS will still display the appropriate error message. Thus, the nonfatal errors will not halt the POST to wait for a user response.

#### System Boot Up Num Lock

If the **System Boot Up Num Lock** option is disabled, the NUM LOCK on an enhanced keyboard will be off when the system is booted, causing the numeric keypad arrow keys to serve as cursor movement keys. The BIOS default is NUM LOCK on.

#### **Floppy Drive Seek At Boot**

The **Floppy Drive Seek at Boot** option determines whether or not a seek test is performed on the floppy drive(s) at system boot time. This feature is disabled by default to promote a fast boot and to decrease the possibility of damaging the floppy drive heads from excessive seek testing.

#### System Boot Up Sequence

The BIOS normally attempts to boot from floppy drive A: (if present), and if unsuccessful, it attempts to boot from hard disk drive C:. This sequence can be reversed. If set to C:, A:, the system attempts to boot from the hard drive C: then floppy drive A:. The latter speeds up the boot process slightly, but prevents booting from a floppy.

#### Internal Cache Memory

The **Internal Cache Memory** option enables or disables the 80486 processor's internal 8 Kbyte cache memory. The cache is enabled by default for faster processing speed.

#### Fast Gate A20

**Fast Gate A20** controls the ability to access memory addresses above 1 Mbyte by enabling or disabling access to the processor address line A20. To remain PC/XT compatible and be able to access conventional memory (from 0 to 1024 Kbytes), address line A20 must always be low. Disable **Fast Gate A20** to force address line A20 low.

Some application programs enter and exit Protected Mode through the BIOS. Using the BIOS, all RAM accesses to extended memory addresses above 1 Mbyte require that Gate A20 be enabled via the keyboard controller chip. For this software, Gate A20 must be repeatedly enabled and disabled via the keyboard controller chip. Such mode switching is a slow process.

**Fast Gate A20** provides an alternate, faster method of enabling and disabling Gate A20 found in the chip set and some software products. Enable this BIOS option to use Fast Gate A20. **Fast Gate A20** is enabled by default.

#### **ROM Shadow**

ROM shadow is a technique for relocating BIOS code from slower ROM to faster RAM. The BIOS is then executed from the faster RAM.

The BIOS permits shadowing of the 32 Kbyte video BIOS at \$C0000 and also the 32 Kbyte option ROM space at \$C8000. If a shadowing option is enabled, the code that resides in that particular segment of ROM will be shadowed to faster RAM. The 64 Kbyte system ROM at \$F0000 is automatically shadowed. By default, **Video ROM Shadow** is enabled and **Adaptor ROM Shadow** is disabled.

#### **Boot Sector Virus Protection**

When the **Boot Sector Virus Protection** option is enabled, the VMIVME-7486 system BIOS intercepts calls to the disk subsystem that would overwrite the boot sector of the hard drive. When such a request is intercepted, the user will be prompted to confirm the action. This can help prevent the system from being infected by certain viruses that attempt to rewrite the boot sector, but it also slows down disk accesses slightly in order for double-checking. The option is therefore disabled by default.

#### Auto-Configuration

The **Auto-Configuration** feature simply enables or disables the **Auto Configuration with BIOS Defaults** option from appearing on the opening screen. The **Auto-Configuration** feature is enabled by default.

#### AT Bus Clock Source