# V7 VGA Technical Reference Manual

6/30/88

We make a clear difference.

# V7VGA Technical Reference Manual

6/30/88

Written by:

#### Dean A. Hays Video Seven Cupertino, California

with contributions from:

Michael Abrash Dave Miller Tom Wilson

IBM is a trademark of International Business Machines Corporation Hercules is a trademark of Hercules Computer Technology MS-DOS is a trademark of Microsoft, Incorporated MultiSync is a trademark of Nippon Electric Company MultiScan is a trademark of SONY

#### Copyright 1987, 1988

Video Seven Incorporated 46335 Landing Parkway Fremont, California 94538

(415) 656-7800

This document may not, in whole or in part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine readable form without prior written consent from VIDEO SEVEN INCORPORATED.

# Table of Contents

| Chapter 1.0 | Intro                                                 | duction1-1                                               |

|-------------|-------------------------------------------------------|----------------------------------------------------------|

|             | 2.1<br>2.2<br>2.3                                     | Scope.1-1Chip Revisions Covered.1-1Intended Audience.1-1 |

| Chapter 2.0 | Over                                                  | view                                                     |

|             | 2.1                                                   | Features2-2                                              |

| Chapter 3.0 | Regis                                                 | ster Definitions                                         |

|             | 3.2<br>3.3<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10 | I/O Port Summary                                         |

| Chapter 4.0 | BIOS                                                  | S 4-1                                                    |

|             | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                | BIOS Overview                                            |

| Chapter 5.0 | Supp                                                  | ort Software                                             |

|             | 5.1<br>5.2                                            | Utilities                                                |

| (continued) |                                                       |                                                          |

|             |                                                       |                                                          |

-----

# Table of Contents

\*\*\*\*\*\*

| Chapter 6.0 | V7VGA Programming                 |

|-------------|-----------------------------------|

|             | 6.1General Information            |

| Appendix A  | Register Initialization TablesA-1 |

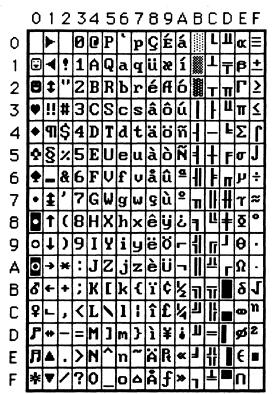

| Appendix B  | Character FontsB-1                |

| Appendix C  | Connector PinoutsC-1              |

| Appendix D  | Jumper / Switch Settings D-1      |

|             |                                   |

# List of Figures

| Figure 3-4 | Display Memory Plane Mapping 3-24            |

|------------|----------------------------------------------|

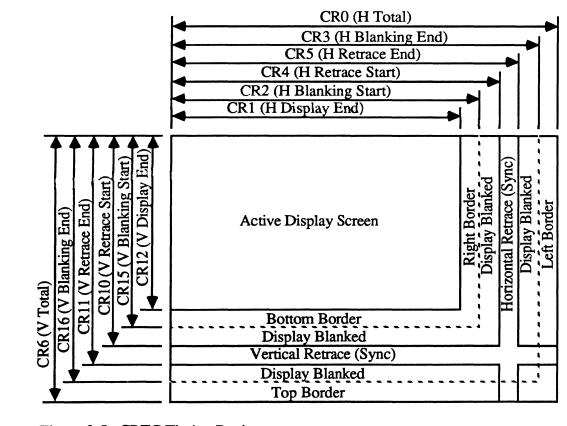

| Figure 3-5 | CRTC Timing Registers                        |

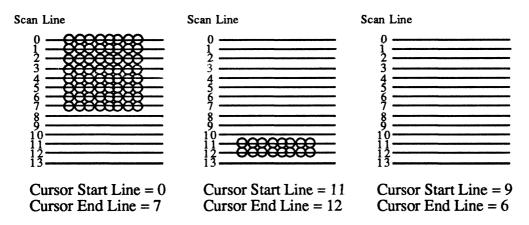

| Figure 3-6 | CRTC Cursor Programming Examples             |

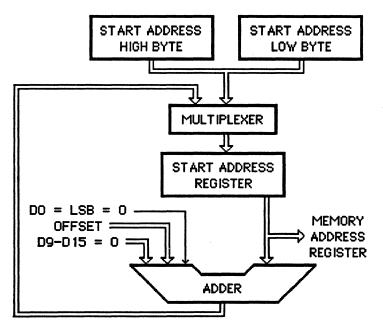

| Figure 3-7 | CRTC Offset Register Operation               |

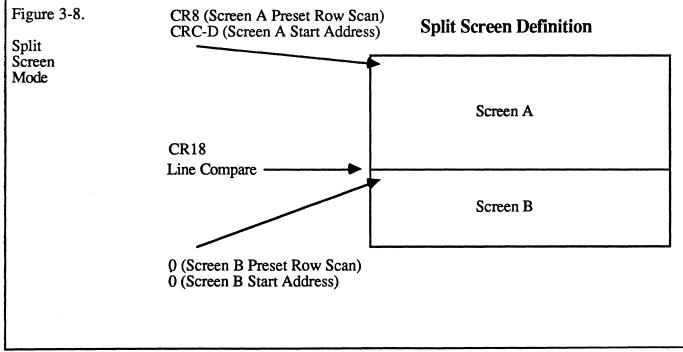

| Figure 3-8 | Split Screen Mode                            |

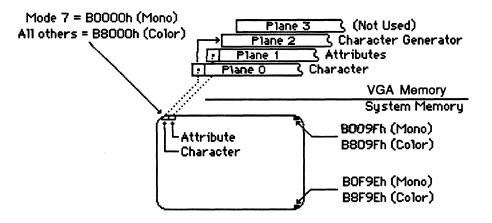

| Figure 6-1 | Text Mode Video Memory Mapping (Mode 3)6-2   |

| Figure 6-2 | Attribute Byte Layout                        |

| Figure 6-3 | Character Font Addresses                     |

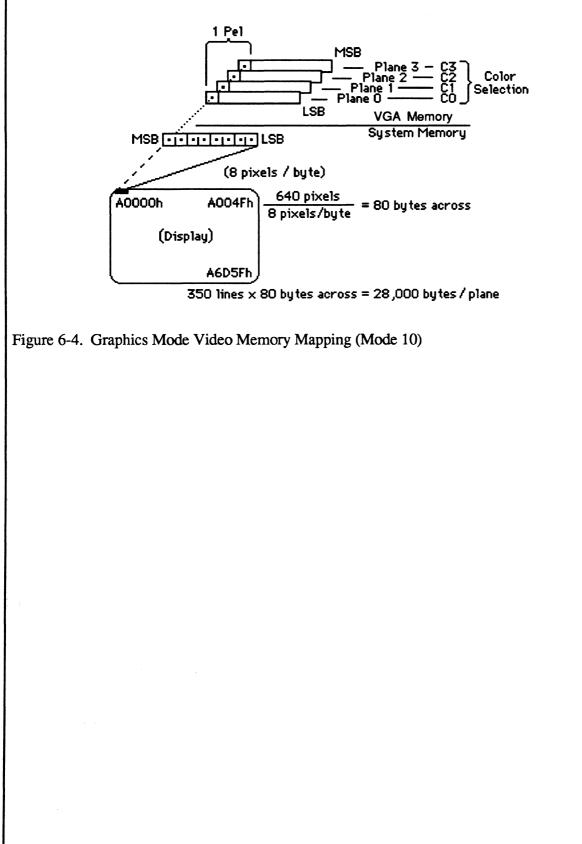

| Figure 6-4 | Graphics Mode Video Memory Mapping (Mode 10) |

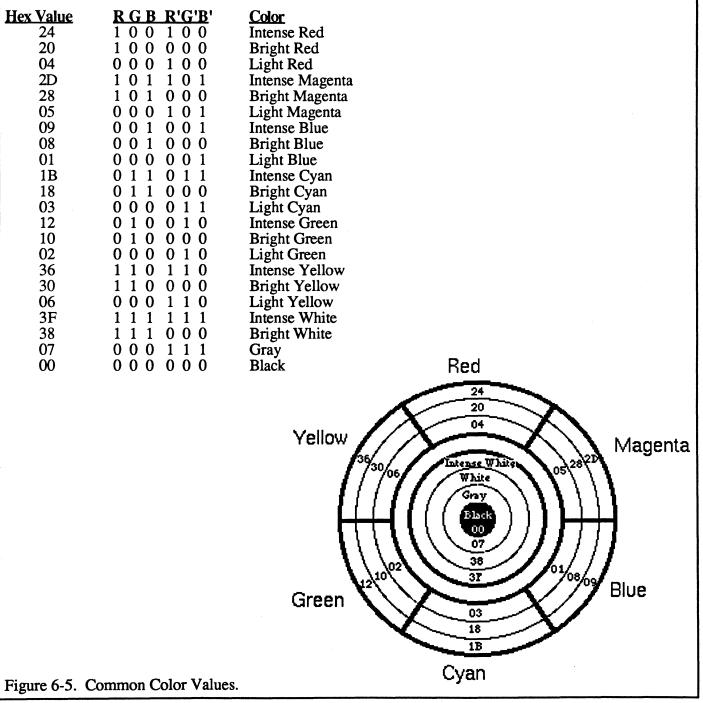

| Figure 6-5 | Common Color Values                          |

| Figure 6-6 | Split Screen Mapping                         |

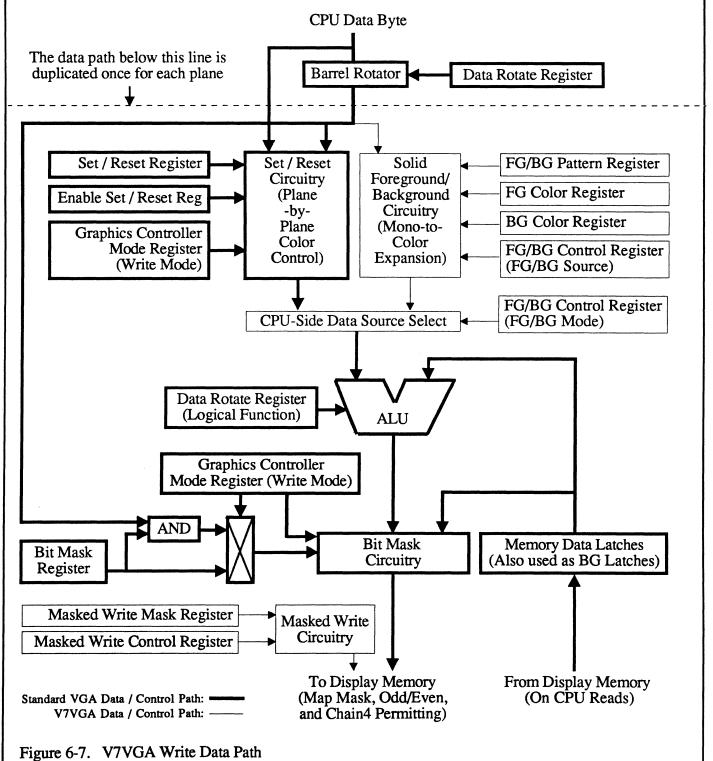

| Figure 6-7 | V7VGA Write Data Path                        |

# List of Tables

| Table 4-1              | BIOS Functions (Functional Order)                              |

|------------------------|----------------------------------------------------------------|

| Table 4-2<br>Table 4-3 | BIOS Functions (Numerical Order)                               |

| Table 4-4              | VGA BIOS Data Area                                             |

| Table 4-5              | VGA BIOS Save Environment                                      |

| Table 4-6              | Secondary Save Pointer Data Area                               |

| Table 4-7              | Video Seven Extensions                                         |

| Table 4-8              | Video Parameter Mode Table Format                              |

| Table 4-9              | Standard Video Parameter Table 4-38                            |

| Table 6-1              | Text Character Attributes                                      |

| Table 6-2              | Common Color Value Calculation                                 |

| Table 6-3              | V7VGA User-Programmable Extension Register Summary 6-48        |

|                        |                                                                |

| Table A-2              | Analog Display Initialization Data                             |

| Table A-3              | Video Seven Proprietary Text Modes Initialization Data         |

| Table A-4              | Video Seven Proprietary Graphics Modes Initialization Data A-6 |

|                        |                                                                |

|                        |                                                                |

|                        |                                                                |

|                        |                                                                |

|                        |                                                                |

|                        |                                                                |

|                        |                                                                |

|                        |                                                                |

|                        |                                                                |

# CHAPTER Image: Image

# Introduction

#### 1.1 Scope of Document

This manual provides technical coverage of the V7 VGA chip. Topics include the modes of operation of the V7 VGA, the major components and registers, the BIOS functions, and programming information including examples. In addition, detailed information is presented on each of the V7 VGA registers.

The following definitions are used throughout this manual:

Industry Standard Enhanced Graphics Adapter. EGA Industry Standard Color Graphics Display Adapter. CGA Industry Standard Monochrome Display Adapter. MDA MGA Video-Seven Monochrome Graphics Adapter. Hercules<sup>™</sup> Graphics Card (MGA Compatible). HGC ED/ECD Industry Standard Enhanced Color Display. Industry Standard Color Display. CD Industry Standard Monochrome Display. MD AD/ACD Analog Display / Analog Color Display MS Multiple-Frequency Color Display (MultiSync<sup>™</sup>, MultiScan<sup>™</sup>, etc.)

#### **1.2** Chip Revisions Covered

This manual documents the following chip revisions:

| Revision 0 - Available Jan | 1988 | (L1Axxxx) |

|----------------------------|------|-----------|

| Revision 1 - Available Mar | 1988 | (L1A4080) |

| Revision 2 - Available Apr | 1988 | (L1A4152) |

| Revision 3 - Available May | 1988 | (L1A4199) |

#### **1.3 Intended Audience**

This manual is directed toward the technically sophisticated audience. It assumes the reader is familiar with assembly language programming on the 80286 or similar microprocessor, and understands the fundamentals of video display terminology.

# CHAPTER 2

# Overview

The V7VGA chip is hardware / software compatible with the IBM VGA and provides improved performance and additional functionality. The V7VGA supports high resolution graphics and alphanumeric display modes for both monochrome and color, and for high resolution displays such as the NEC Multisync<sup>™</sup> and Sony MultiScan<sup>™</sup> monitors. Additional functions are also available, including hardware cursor, highresolution 256-color modes, extended attribute control, masked-write capability (with V-Rams), and extensive enhancements to the ability to manipulate foreground / background data patterns.

The V7VGA implements all control and data registers of the VGA. It also implements all of the data manipulation capabilities and data paths of the VGA.

All memory cycles not used to refresh the display or video memory are allocated to process CPU memory requests. A one-to-one interleave can be achieved between CPU and display refresh accesses to the video memory for typical VGA-compatible modes using V-Rams. Various interleave settings from 1:1 to 1:4 may be programmed depending on dot clock frequency, mode of operation, and ram access time.

Hardware support is provided to display a 32x32 pixel pattern for use as a mouse pointer. Additional text cursor controls are provided (blink disable and OR/XOR mode control).

# 2.1 Features

The following is a list of the major features of the V7VGA:

- Fast host access to video memory: every cycle for all VGA standard modes using V-Rams

- 32-bit video ram access for display refresh

- 16-bit CPU access (memory, I/O, and BIOS)

- High speed operation (up to 65 MHz dot clock rate)

- Increased video resolutions:

Text: up to 132 columns or 60 lines 8 or 9-bit character widths

Graphics: up to 1024x768 four bit/pixel and 800x600 eight bit/pixel

- Allows up to eight fonts to be loaded simultaneously (any two selectable at once)

- Hardware graphics cursor (mouse pointer)

- Supports memory configurations of 256 KB, 512 KB or 1 MB using either 256Kb or 1Mb ram chips

- Supports both D-Ram and V-Ram configurations

- Supports multiple monitor types including NEC MultiSync<sup>™</sup> and Sony MultiScan<sup>™</sup>.

- Host CPU-readable registers for save/restore

- Scan-line doubling for improved readability of 200-line graphics modes on high-resolution monitors

- Data path enhancements for foreground / background data manipulation

- Extended underlining control

- Masked-write capability (with V-Rams)

CHAPTER

# **Register Definitions**

The following sections present information on the registers of the V7VGA chip. The register name is shown first (full name and an abbreviation), along with the port address and index if applicable. Below that is a figure illustrating the register configuration and a discussion of the register contents.

Note: In all register descriptions in this chapter, unused and reserved bits return 0 when read, except where specifically indicated otherwise. One general exception is that all reserved extension registers read back bits 3-0 as 1.

## V7VGA I/O PORT SUMMARY

| Port Address           | VGA Mode                              | <br>· · · · · · · · · · · · · · · · · · · |   |

|------------------------|---------------------------------------|-------------------------------------------|---|

|                        |                                       |                                           |   |

| 000 1000               |                                       |                                           |   |

| 2B0/3B0                |                                       |                                           |   |

| 2B1/3B1                |                                       |                                           |   |

| 2B2/3B2                |                                       |                                           |   |

| 2B3/3B3                | 0.201                                 |                                           |   |

| 2B4/3B4                | CRTC Index (RW)                       |                                           |   |

| 2B5/3B5                | CRTC Data (RW)                        |                                           |   |

| 2B6/3B6                |                                       |                                           |   |

| 2B7/3B7                |                                       |                                           |   |

| 2B8/3B8                |                                       |                                           |   |

| 2B9/3B9                |                                       |                                           |   |

| 2BA / 3BA              | Feature Ctrl(W), Display Status(R)    |                                           |   |

| 2BB/3BB                |                                       |                                           |   |

| 2BC / 3BC              |                                       |                                           |   |

| 2BD / 3BD              |                                       |                                           |   |

| 2BE / 3BE              |                                       | <br>                                      |   |

| 2BF / 3BF              |                                       |                                           |   |

|                        |                                       |                                           |   |

| 2C0 / 3C0              | Attr Ctrlr Index/Data (W), Index (R)  |                                           |   |

| 2C1 / 3C1              | Attr Ctrlr Index/Data (W), Data (R)   |                                           |   |

| 2C2 / 3C2              | Misc Output (W), Feature (R)          |                                           |   |

| 2C3 / 3C3              | Video Subsystem Enable (RW)           |                                           |   |

| 2C4 / 3C4              | Sequencer/Extensions Index (RW)       |                                           |   |

| 2C5 / 3C5              | Sequencer/Extensions Data (RW)        |                                           |   |

| 2C6/3C6                | Palette Pixel Mask (RW)               |                                           |   |

|                        | Palette Index Rmode(W), DACstate(R)   |                                           |   |

| 2C8/3C8                | Palette Index Wmode (RW)              |                                           |   |

| 2C9/3C9                | Palette Data (RW)                     |                                           |   |

| 2CA / 3CA              | Feature Control (R)                   |                                           |   |

| 2CB / 3CB              |                                       |                                           |   |

| 2CC / 3CC              | Misc Output (R)                       |                                           |   |

| 2CD / 3CD              |                                       |                                           |   |

| 2CE / 3CE              | Graphics Controller Index (RW)        |                                           |   |

| 2CF / 3CF              | Graphics Controller Data (RW)         |                                           | · |

|                        |                                       |                                           |   |

| 2D0/3D0                | · · · · · · · · · · · · · · · · · · · |                                           |   |

| 2D0/3D0                |                                       |                                           |   |

| 2D2 / 3D2              |                                       |                                           |   |

| 2D2 / 3D2<br>2D3 / 3D3 |                                       |                                           |   |

| 2D3 / 3D3<br>2D4 / 3D4 | CRTC Index (RW)                       |                                           |   |

| 2D4 / 3D4              | CRTC Data (RW)                        |                                           |   |

| 2D5/3D5<br>2D6/3D6     |                                       |                                           |   |

| 2D0/3D0<br>2D7/3D7     |                                       |                                           |   |

| 2D8/3D8                |                                       |                                           |   |

| 2D9 / 3D9              |                                       |                                           |   |

| 2D9 / 3D9<br>2DA / 3DA | Feature Ctrl(W), Display Status(R)    |                                           |   |

| 2DR/3DR<br>2DB/3DB     | a culture Cultury, Display Status(IV) |                                           |   |

| 2DB / 3DB<br>2DC / 3DC |                                       |                                           |   |

| 2DC / 3DC<br>2DD / 3DD | -                                     | L                                         | 1 |

| 2DD / 3DD<br>2DE / 3DE |                                       |                                           |   |

| 2DE / 3DE<br>2DF / 3DF |                                       |                                           |   |

| 20r / 30r              |                                       |                                           |   |

|              |                  | VGAC                                                      | OMP         | ATIBLER    | EGISTERS   |             |                        |                        |

|--------------|------------------|-----------------------------------------------------------|-------------|------------|------------|-------------|------------------------|------------------------|

| PAGE         | ABBREV           | VGA/EGA REGISTER NAME                                     | BITS        |            | READ/WRITE | INDEX       | MONO PORT              | COLOR PORT             |

| 3-6          | MISC             | Miscellaneous Output                                      | 8           | VGA        | RW         |             | 3C2(W),3CC(R)          | 3C2(W), 3CC(R)         |

| 3-7          | FC<br>FEAT       | Feature Control<br>Feature Read (Input Status 0)          | 3<br>4      | VGA<br>VGA | RW<br>R    |             |                        | 3DA(W),3CA(R)          |

| 3-9          | STAT             | Display Status (Input Status 0)                           | 7           | VGA<br>VGA | R          |             | 3C2<br>3BA             | 3C2<br>3DA             |

| 3-10         | DACMASK          | Color Palette Pixel Mask                                  | 8           | DAC        | RW         |             | 3C6                    | 3C6                    |

| 3-11         | DACSTATE         |                                                           | 2           | VGA        | R          |             | 3C7                    | 3C7                    |

|              | DACRX            | Color Palette Read-Mode Index                             | 8           | DAC        | W          |             | 3C7                    | 3C7                    |

| 3-13         | DACWX<br>DACDATA | Color Palette Write-Mode Index                            | 8<br>18     | DAC<br>DAC | RW<br>RW   | <br>00-FF   | 3C8<br>3C9             | 3C8                    |

|              |                  | Color Palette Regs 0-255                                  |             |            |            | 00-FF       |                        | 3C9                    |

| 3-15<br>3-16 | VSE<br>ALTVSE    | Video Subsystem Enable<br>Video Subsystem Enable (Alt)    | 1<br>1      | VGA<br>VGA | RW<br>RW   |             | 3C3<br>102             | 3C3<br>102             |

| 3-17         | ROMMAP           | Video Subsystem Control                                   | 5           | EXT        | W          |             | 46E8                   | 46E8                   |

| 3-18         | CACHE            | I/O Cache                                                 | 5+8         | IOU        | RW         | 0-F         | 4BC4-4BC5              | 4BC4-4BC5              |

| 3-5          | EXPAN            | Expansion Connector Ports                                 | 8           | EXT        | RW         |             | 2E9,AxE8               | 2E9,AxE8               |

| 3-20         | SRX              | Sequencer / Extensions Index                              | 7           | VGA        | RW         |             | 3C4                    | 3C4                    |

| 3-21<br>3-22 | SRO<br>SR1       | Reset<br>Clocking Mode                                    | 2<br>6      | VGA<br>VGA | RW<br>RW   | 00<br>01    | 3C5<br>3C5             | 3C5<br>3C5             |

| 3-24         | SR2              | Plane Mask                                                | 4           | VGA        | RW         | 02          | 3C5                    | 3C5                    |

| 3-25         | SR3              | Character Map Select                                      | 6           | VGA        | RW         | 03          | 3C5                    | 3C5                    |

| 3-26         | SR4              | Memory Mode                                               | 4           | VGA        | RW         | 04          | 3C5                    | 3C5                    |

| 3-27         | SR6<br>SR7       | Extensions Control<br>Reset Hor Character Counter         | 1<br>0      | VGA<br>VGA | RW<br>W    | 06<br>07    | 3C5<br>3C5             | 3C5<br>3C5             |

| 3-30         | CRX              | CRTC Index                                                | 6           | VGA        | RW         |             | 3B4                    | 3D4                    |

| 3-30         | CRA<br>CR0       | Horizontal Total                                          | в<br>8      | VGA<br>VGA | RW         | 00          | 3B4<br>3B5             | 3D4<br>3D5             |

| 3-32         | CR1              | Horizontal Display End                                    | 8           | VGA        | RW         | 01          | 3B5                    | 3D5                    |

| 3-33         | CR2              | Horizontal Blanking Start                                 | 8           | VGA        | RW         | 02          | 3B5                    | 3D5                    |

| 3-34<br>3-35 | CR3<br>CR4       | Horizontal Blanking End<br>Horizontal Retrace Start       | 5+2+1<br>8  | VGA<br>VGA | RW<br>RW   | 03<br>04    | 3B5<br>3B5             | 3D5<br>3D5             |

| 3-36         | CR5              | Horizontal Retrace End                                    | 5+2+1       | VGA        | RW         | 05          | 3B5                    | 3D5<br>3D5             |

| 3-37         | CR6              | Vertical Total                                            | 8           | VGA        | RW         | 06          | 3B5                    | 3D5                    |

| 3-38         | CR7<br>CR8       | Overflow<br>Screen A Preset Row Scan                      | 8<br>5+2    | VGA<br>VGA | RW<br>RW   | 07<br>08    | 3B5<br>3B5             | 3D5<br>3D5             |

| 3-40         | CR9              | Character Cell Height                                     | 5+2<br>5+3  | VGA<br>VGA | RW         | 08          | 3B5<br>3B5             | 3D5<br>3D5             |

| 3-41         | CRA              | Cursor Start                                              | 5+1         | VGA        | RW         | ŎÁ          | 3B5                    | 3D5                    |

| 3-42         | CRB              | Cursor End                                                | 5+2         | VGA        | RW         | 0B          | 3B5                    | 3D5                    |

| 3-43         | CRC<br>CRD       | Screen A Start Address High<br>Screen A Start Address Low | 8<br>8      | VGA<br>VGA | RW<br>RW   | 0C<br>0D    | 3B5<br>3B5             | 3D5<br>3D5             |

| 3-45         | CRE              | Cursor Location High                                      | 8           | VGA        | RW         | 0E          | 3B5                    | 3D5                    |

| 3-46         | CRF              | Cursor Location Low                                       | 8           | VGA        | RW         | 0F          | 3B5                    | 3D5                    |

| 3-47         | LPENH<br>LPENL   | Light Pen High                                            | 8           | VGA        | R          | 10          | 3B5                    | 3D5                    |

| 3-48<br>3-49 | CR10             | Light Pen Low<br>Vertical Retrace Start                   | 8<br>8      | VGA<br>VGA | R<br>W, RW | 11<br>10    | 3B5<br>3B5             | 3D5<br>3D5             |

| 3-50         | CR11             | Vertical Retrace End                                      | <b>4</b> +4 | VGA        | W, RW      | 11          | 3B5                    | 3D5                    |

|              | CR12             | Vertical Display End                                      | 8           | VGA        | RŴ         | 12          | 3B5                    | 3D5                    |

| 3-52         | CR13<br>CR14     | Offset<br>Underline Row Scan                              | 8<br>5+2    | VGA<br>VGA | RW<br>RW   | 13<br>14    | 3B5<br>3B5             | 3D5                    |

| 3-55         | CR14<br>CR15     | Vertical Blanking Start                                   | 3+2<br>8    | VGA<br>VGA | RW         | 14          | 3B5                    | 3D5<br>3D5             |

| 3-55         | CR16             | Vertical Blanking End                                     | 8           | VGA        | RW         | 16          | 3B5                    | 3D5                    |

| 3-56         | CR17             | CRT Mode Control                                          | 7           | VGA        | RW         | 17          | 3B5                    | 3D5                    |

| 3-58         | CR18<br>CR1F     | Line Compare<br>V7VGA Identification                      | 8<br>8      | VGA<br>VGA | RW<br>R    | 18<br>1F    | 3B5<br>3B5             | 3D5<br>3D5             |

| 3-60         | CR22             | Graphics Ctrlr Data Latches                               | 8           | VGA        | R          | 22          | 3B5                    | 3D5                    |

| 3-61         | CR24             | Attribute Ctrlr Index/Data Latch                          | 7           | VGA        | R          | 24          | 3B5                    | 3D5                    |

| 3-62         | CR3x             | Clear Vertical Display Enable FF                          | 1           | VGA        | W          | 3x          | 3B5                    | 3D5                    |

| 3-64         | GRX              | Graphics Controller Index                                 | 4           | VGA        | RW         |             | 3CE                    | 3CE                    |

| 3-65<br>3-66 | GR0<br>GR1       | Set/Reset<br>Enable Set/Reset                             | 4<br>4      | VGA<br>VGA | RW<br>RW   | 00<br>01    | 3CF<br>3CF             | 3CF<br>3CF             |

| 3-67         | GR2              | Color Compare                                             | 4           | VGA        | RW         | 02          | 3CF                    | 3CF                    |

| 3-68         | GR3              | Data Rotate                                               | 5           | VGA        | RW         | 03          | 3CF                    | 3CF                    |

| 3-69<br>3-70 | GR4<br>GR5       | Read Map Select<br>Mode                                   | 3<br>7      | VGA<br>VGA | RW<br>RW   | 04<br>05    | 3CF<br>3CF             | 3CF<br>3CF             |

| 3-70         | GR5<br>GR6       | Mode<br>Miscellaneous                                     | 4           | VGA<br>VGA | RW         | 05          | 3CF                    | 3CF                    |

| 3-73         | GR7              | Color Don't Care                                          | 4           | VGA        | RW         | 07          | 3CF                    | 3CF                    |

| 3-74         | GR8              | Bit Mask                                                  | 8           | VGA        | RW         | 08          | 3CF                    | 3CF                    |

| 3-76         | ARX              | Attribute Controller Index                                | 6           | VGA        | RW         |             | 3C0 (3C1)              | 3C0 (3C1)              |

| 3-77         | AR0-F            | Internal Palette Regs 0-15                                | 8<br>7      | VGA<br>VGA | RW<br>RW   | 00-0F<br>10 | 3C0 (3C1)              | 3C0 (3C1)              |

| 3-78<br>3-80 | AR10<br>AR11     | Mode Control<br>Overscan Color                            | 8           | VGA<br>VGA | RW         | 11          | 3C0 (3C1)<br>3C0 (3C1) | 3C0 (3C1)<br>3C0 (3C1) |

| 3-81         | AR12             | Color Plane Enable                                        | 6           | VGA        | RW         | 12          | 3C0 (3C1)              | 3C0 (3C1)              |

| 3-82         | AR13             | Horizontal Pixel Panning                                  | 4           | VGA        | RW         | 13          | 3C0 (3C1)              | 3C0 (3C1)              |

| 3-83         | AR14             | Color Select                                              | 4           | VGA        | RW         | 14          | 3C0 (3C1)              | <b>3C0</b> (3C1)       |

|              |                  |                                                           |             |            |            |             |                        |                        |

## **V7VGA EXTENSION REGISTERS**

|       |                   |                |     |                                                                         | -         |                 |            |                  |             |              |

|-------|-------------------|----------------|-----|-------------------------------------------------------------------------|-----------|-----------------|------------|------------------|-------------|--------------|

| PAGE  | ABBREV<br>ER80-82 | <u>IATIONS</u> |     | V7VGA REGISTER NAME<br>(TEST, GPOS1-2 in VEGA VGA)                      | BITS<br>0 | REG TYPE        | READ/WRITE | INDEX<br>80-82   | PORT<br>3C5 |              |

| 3-76  | ER83              | ARX            | *   | Attribute Controller Index                                              | 7         | EXTENSION       |            | 83               | 3C5         |              |

|       | ER84-86           |                |     | (WRC,TC,BWC in VEGA VGA)                                                | Ó         |                 |            | 84-86            | 3C5         |              |

| 1     | ER87-89           |                |     | (ROMC.HSPS, FONTC in VEGA VGA)                                          | Õ         |                 |            | 87-89            | 3C5         |              |

| 1     | ER8A              | SBHP           |     | -reserved- (Screen B H Pixel Pan)                                       | 3         | EXTENSION       |            | 8A               |             | *****000     |

| 1     | ER8B              | SBPR           |     | -reserved- (Screen B Preset Rowscan)                                    | 5         | EXTENSION       | •          | 8B               |             | xxx00000     |

|       | ER8C              | SBSH           |     | -reserved- (Screen B Start Address H)                                   | 8         | EXTENSION       |            | 8C               |             | 00000000     |

|       | ER8D              | SBSL           |     | -reserved- (Screen B Start Address L)                                   | 8         | EXTENSION       |            | 8D               |             | 000000000    |

| 3-86  | ER8E              | REV            |     | V7VGA Revision Code                                                     | 8         | EXTENSION       |            | 8E               |             | 01110000     |

| 3-86  | ER8F              | REV            |     | V7VGA Revision Code                                                     | 8         | EXTENSION       |            | 8E<br>8F         |             | 01110000     |

| 5-00  | ER90-93           |                |     | (CR10-11,LPENH/L in VEGA VGA)                                           | Ő         |                 |            | 90-93            | 3C5         |              |

| 3-87  | ER94              | PPA            |     | Pointer Pattern Address                                                 | 8         | EXTENSION       |            | 90-95            |             | 11111111     |

| 5-07  | ER94<br>ER95      | 114            |     | (CADJ in VEGA VGA)                                                      | Ő         |                 |            | 95               | 3C5         |              |

|       | ER95<br>ER96      | CW             |     | -reserved- (Caret Width)                                                | 8         | EXTENSION       | <br>R/W    | 96               | 3C5         |              |

|       | ER90<br>ER97      | CH             |     | -reserved- (Caret Height)                                               | 8         | EXTENSION       |            | 90<br>97         | 3C5         |              |

|       | ER97<br>ER98      | СХН            |     | -reserved- (Caret H Position High)                                      | 3         | EXTENSION       |            | 98               | 3C5         |              |

|       | ER98<br>ER99      | CXL            |     |                                                                         | 8         | EXTENSION       |            | 99               | 3C5         |              |

| 1     | ER99<br>ER9A      | CYH            |     | -reserved- (Caret H Position Low)<br>-reserved- (Caret V Position High) | 2         | EXTENSION       |            |                  | 3C5         |              |

| ł     | ER9A<br>ER9B      | CYL            |     | -reserved- (Caret V Position High)<br>-reserved- (Caret V Position Low) | 8         | EXTENSION       |            | 9A<br>9B         | 3C5         |              |

| 3-89  | ER9B<br>ER9C      | PXH            |     | Pointer Horizontal Position High                                        | 3         | EXTENSION       |            | 9С               | 3C5         |              |

| 3-90  | ER9C<br>ER9D      | PXL            |     | Pointer Horizontal Position Low                                         | 8         | EXTENSION       | R/W        | 9D               | 3C5         |              |

| 3-90  | ER9D<br>ER9E      | PYH            |     | Pointer Vertical Position High                                          | 2         | EXTENSION       | R/W        | 9E               | 3C5         |              |

| 3-91  | ER9E              | PYL            |     | Pointer Vertical Position Low                                           | 8         | EXTENSION       |            | 9E<br>9F         | 3C5         |              |

| 3-92  | ER9F<br>ERA0      | GRLO           |     | Graphics Ctrlr Memory Latch 0                                           | 8         | EXTENSION       |            | яг<br><b>А</b> 0 | 3C5         |              |

| 3-93  | ERAU<br>ERAI      | GRL1           |     | Graphics Ctrlr Memory Latch 1                                           | 8         | EXTENSION       |            | A0<br>A1         | 3C5         |              |

| 3-95  | ERA1<br>ERA2      | GRL2           |     | Graphics Ctrlr Memory Latch 1<br>Graphics Ctrlr Memory Latch 2          | 8         | EXTENSION       |            | A1<br>A2         | 3C5         |              |

| 3-96  | ERA2<br>ERA3      | GRL3           |     | Graphics Ctrlr Memory Latch 2<br>Graphics Ctrlr Memory Latch 3          | 8         | EXTENSION       | R/W        | A2<br>A3         | 3C5         |              |

| 3-90  | ERA4              | CLK            |     | Clock Select                                                            | 6         | EXTENSION       |            | A3<br>A4         |             | <br>xxx0xxxx |

| 3-98  | ERA5              | CURS           |     | Cursor Attributes                                                       | 3         | EXTENSION       |            | A5               |             | 0xxx0xx0     |

| 3-90  | ERA6-A9           |                |     | (ISR,SWITCH,NMI1-2 in VEGA VGA)                                         | 0         |                 |            | A6-A9            | 3C5         |              |

| 1     | ERAA-AC           |                |     | (unused,NSTAT1-2 in VEGA VGA)                                           | Ő         |                 |            | AA-AC            |             |              |

|       | ERAD-AF           |                |     | (PG256,CACHE,STATE in VEGA VGA)                                         |           |                 |            | AD-AF            | 3C5         |              |

|       | ERB0-BF           |                |     | (Scratch Registers 0-F in VEGA VGA)                                     | 0         |                 |            | B0-BF            | 3C5         |              |

|       |                   |                |     | -                                                                       |           |                 |            |                  |             |              |

|       | ERCO-E9           |                |     | -reserved for V7VGA extensions-                                         | 0         |                 |            | C0-E9            | 3C5         |              |

| 3-99  | EREA              |                | # # | Switch Strobe                                                           | 0         | EXTENSION       |            | EA               | 3C5         |              |

|       | EREB              | NMICTRL        |     | Emulation Control                                                       | 8         | EXTENSION       | R/W        | EB               |             | 00000000     |

| 3-102 |                   | FGLAT0         |     | Foreground Latch 0                                                      | 8         | EXTENSION       | R/W        | EC               | 3C5         |              |

| 3-102 |                   | FGLAT1         |     | Foreground Latch 1                                                      | 8         | EXTENSION       | R/W        | ED               | 3C5         |              |

| 3-102 |                   | FGLAT2         |     | Foreground Latch 2                                                      | 8         | EXTENSION       | R/W        | EE               | 3C5         |              |

| 3-102 |                   | FGLAT3         |     | Foreground Latch 3                                                      | 8         | EXTENSION       | R/W        | EF               | 3C5         |              |

| 3-103 |                   | FFGLD          |     | Fast Foreground Latch Load                                              | 8         | EXTENSION       |            | FO               | 3C5         |              |

| 3-104 |                   | FLLSTATE       |     | Fast Latch Load State                                                   | 4         | EXTENSION       | R/W        | F1               | 3C5         |              |

| 3-105 |                   | FBGLD          |     | Fast Background Latch Load                                              | 8         | EXTENSION       | R/W        | F2               | 3C5         |              |

| 3-106 |                   | MWCTRL         |     | Masked Write Control                                                    | 2         | EXTENSION       | R/W        | F3               |             | ******       |

| 3-107 |                   | MWMASK         |     | Masked Write Mask                                                       | 8         | EXTENSION       | •          | F4               | 3C5         |              |

| 3-108 |                   | FBPAT          |     | Foreground/Background Pattern                                           | 8         | EXTENSION       |            | F5               | 3C5         |              |

| 3-109 |                   | RAMBANK        |     | 1 Mb RAM Bank Select                                                    | 8         | EXTENSION       |            | F6               |             | 00000000     |

| 3-110 |                   | SWITCH         |     | Switch Readback                                                         | 8         | EXTENSION       | •          | F7               | 3C5         |              |

| 3-111 |                   | CLKCTRL        |     | Extended Clock Control                                                  | 8         | EXTENSION       | •          | F8               |             | xxx00x00     |

| 3-113 |                   | PGSEL          |     | Extended Page Select                                                    | 1         | EXTENSION       |            | F9               |             | ******       |

| 3-114 |                   | FGCOLOR        |     | Extended Foreground Color                                               | 4         | EXTENSION       | •          | FA               | 3C5         |              |

| 3-115 |                   | BGCOLOR        |     | Extended Background Color                                               | 4         | EXTENSION       |            | FB               | 3C5         |              |

| 3-116 |                   | COMPAT         |     | Compatibility Control                                                   | 8         | EXTENSION       |            | FC               |             | 0000x0x0     |

| 3-119 |                   | TIMING         |     | Extended Timing Select                                                  | 8         | EXTENSION       |            | FD               |             | 00000000     |

| 3-121 |                   | FBCTRL         |     | Foreground/Background Control                                           | 3         | EXTENSION       |            | FE               |             | xxxx00xx     |

| 3-122 | ERFF              | 16BIT          |     | 16-Bit Interface Control                                                | 8         | EXTENSION       | R/W        | FF               | 303         | xxx00000     |

| + D1  | uplicated V       | GAÆGA res      | eis | ter also accessible as extension register                               | for s     | tate save/resto | re         |                  |             |              |

\* Duplicated VGA/EGA register also accessible as extension register for state save/restore

\*\* Writes to this register cause the dipswitch settings on bus bits 15-8 to be strobed into the Switch Readback register (ERF7)

# Miscellaneous Registers

The miscellaneous registers are those not contained in the other major functional blocks (Sequencer, Attribute Controller, Graphics Controller, and CRT Controller).

| <u>Page</u><br>3-6<br>3-7            | <u>Abbreviation</u><br>MISC<br>FC                | Register Name<br>Misc Output Register<br>Feature Control Register                                                                                                                        | <u>Port Addresses</u><br>3C2 (W), 3CC (R)<br>3?A (W), 3CA (R) |

|--------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 3-8<br>3-9                           | FEAT<br>STAT                                     | Input Status Register 0 (Feature Read)<br>Input Status Register 1 (Display Status)                                                                                                       | 3C2 (R)<br>3?A (R)                                            |

| 3-10<br>3-11<br>3-12<br>3-13<br>3-14 | DACMASK<br>DACSTATE<br>DACRX<br>DACWX<br>DACDATA | Color Palette Pixel Mask<br>Color Palette State<br>Color Palette Read Mode Index Register<br>Color Palette Write Mode Index Register<br>Color Palette Data                               | 3C6 (RW)<br>3C7 (R)<br>3C7 (W)<br>3C8 (RW)<br>3C9 (RW)        |

| 3-15<br>3-16                         | VSE<br>ALTVSE                                    | Video Subsystem Enable<br>Alternate Video Subststem Enable                                                                                                                               | 3C3 (RW)<br>102 (W)                                           |

| 3-17                                 | ROMMAP                                           | ROM Mapping and Video Subsystem Control                                                                                                                                                  | 46E8 (W)<br>56E8 (W)<br>66E8 (W)<br>76E8 (W)                  |

| 3-18                                 | CACHE                                            | I/O Data Cache                                                                                                                                                                           | 4BC4-4BC5 (RW)                                                |

| -                                    | EXPANSION                                        | Expansion Connector (long-slot boards only)                                                                                                                                              | 2E9 (RW)                                                      |

|                                      |                                                  | Expansion Connector (long-slot boards only)<br>Expansion Connector (long-slot boards only)<br>Expansion Connector (long-slot boards only)<br>Expansion Connector (long-slot boards only) | A4E8 (W)<br>A5E8 (W)<br>A6E8 (W)<br>A7E8 (W)                  |

| Note: '                              | 2' in the above port                             | address is 'B' in monochrome mode and 'D' in col                                                                                                                                         | or mode (see MISC[0])                                         |

Note: '?' in the above port address is 'B' in monochrome mode and 'D' in color mode (see MISC[0]).

Note: the ports above indicated as 'expansion connector' ports are not defined in this document. The port address ranges indicated are decoded by boards that provide the expansion connectors (i.e., read accesses to 2E9 will drive the bus even if no expansion board is installed). This capability is provided for compatibility with the IBM 'Display Adapter' (VGA) designed for use in the PC/AT bus. Contact Video Seven for availability of future products for use with these connectors.

I/O Port 3C2 (W) Miscellaneous Output Register I/O Port 3CC (R) Bit # Description 3C2 Access **3CC Access** Reset By Reset State msb Vertical Retrace Polarity W Hard Reset 7 R 6 W Horizontal Retrace Polarity R Hard Reset 5 Page Select W R Hard Reset 4 -reservedreads back 0 . 3 W Clock Select Bit-1 R Hard Reset

This register was write-only at I/O port 3C2 in the EGA. Reading I/O port 3C2 returns the contents of the Feature Read Register (FEAT) (also called Input Status 0). For state save/restore and VGA compatibility, the V7VGA allows this register to also be read at I/O port 3CC.

W

W

W

R

R

R

#### **Bit Descriptions** Bit 7 Vertical Retrace Polarity: 0 = active high (positive), 1 = active low (negative)Bit 6 Horizontal Retrace Polarity: 0 = active high (positive), 1 = active low (negative)Bit 5 Page Bit for Odd/Even: This bit acts as the lsb of the display memory address when in the 'Odd/Even' modes (SR4 bit-2 = 1). Setting this bit to 0 selects odd memory locations; setting it to 1 selects even locations. This bit is set for modes 0, 1, 2, 3, and 7 (text modes). This bit has no effect if chain (GR6 bit-1) or chain4 (SR4 bit-3) are enabled.

#### Bit 4 Reserved (reads back 0)

Clock Select Bit-0

CRTC I/O Address

Enable Ram

2

1

0

lsb

#### **Bit 3-2** Clock Select: These bits select the clock source as follows:

| CIOCK SCIELI. THESE DIES SCIELT THE LIOCK SOUTCE AS                                                                                                                                                                                                                          | 10110w3.                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit-3         Bit-2         Clock Source (CLK[4]=0)           0         0         25.175 MHz (X25M pin)           0         1         28.332 MHz (X28M pin)           1         0         Feature Connector Input (FCLK pin)           1         1         0 MHz (XRESM pin) | Clock Source (CLK[4]=1)<br>50.350 MHz (XD0M pin)<br>65.000 MHz (XD1M pin)<br>Feature Connector Input (FCLK pin)<br>40.000 MHz (XD2M pin)                                                                                     |

| register (extension register ERA4). This field show                                                                                                                                                                                                                          | ald not be changed except during                                                                                                                                                                                             |

| processor. When this bit is set to 1, display RAM                                                                                                                                                                                                                            | will respond at addresses set by the                                                                                                                                                                                         |

| 0 sets the CRTC to 3BxH and the Input Status Reg<br>1 sets the CRTC to 3DxH and the Input Status Reg<br>In register descriptions, port addresses 3Bx or 3Dx<br>'3?x'. The registers affected by this bit are the Dis                                                         | gister 1 to 3BAH (monochrome mode).<br>gister 1 to 3DAH (color mode).<br>as selected by this bit are indicated as<br>play Status register, Feature Control                                                                   |

|                                                                                                                                                                                                                                                                              | Bit-3         Bit-2         Clock Source (CLK[4]=0)           0         0         25.175 MHz (X25M pin)           0         1         28.332 MHz (X28M pin)           1         0         Feature Connector Input (FCLK pin) |

MISC

0

0

0

-

0

0

0

0

Hard Reset

Hard Reset

Hard Reset

| I/O P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ort 3?                                                                                                                                                                                                                                                                                                                                                                                               | A (W) Feature C                                                                                       | ontrol Register                       |              |             | FC             |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------|--------------|-------------|----------------|--|

| I/O P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ort 30                                                                                                                                                                                                                                                                                                                                                                                               | CA (R)                                                                                                |                                       |              |             |                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |                                       |              |             |                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit #                                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                           | 3?A Access                            | 3CA Acces    | s Reset By  | Reset State    |  |

| msb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                                                                                                                                                                                                                                                                                                                                                                                    | -unused-                                                                                              | -                                     | -            |             |                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                                                                                                                                                                                                                                                                                                                                                                    | -unused-                                                                                              | -                                     | -            |             |                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                                                                                                                                                                                                                                                                                                                                    | -unused-                                                                                              | -                                     | -            |             |                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                                                                                                                                                                                                                                                                                                                                                                                    | -unused-                                                                                              | -                                     | -            |             |                |  |