# MOCHERSOARD MANUAL

#### REPAIR AGREEMENT

The Motherboard sold hereunder is sold "as is", with all faults and without any warranty, either expressed or implied, including any implied warranty of fitness for intended use or merchantability. However, the above notwithstanding, VECTOR GRAPHIC, INC., will, for a period of ninety (90) days following delivery to customer, repair or replace any Motherboard that is found to contain defects in materials or workmanship, provided:

- 1. Such defect in material or workmanship existed at the time the Motherboard left the VECTOR GRAPHIC, INC., factory;

- 2. VECTOR GRAPHIC, INC., is given notice of the precise defect claimed within ten (10) days after its discovery;

- 3. The Motherboard is promptly returned to VECTOR GRAPHIC, INC., at customer's expense, for examination by VECTOR GRAPHIC, INC., to confirm the alleged defect, and for subsequent repair or replacement if found to be in order.

Repair, replacement or correction of any defects in material or workmanship which are discovered after expiration of the period set forth above will be performed by VECTOR GRAPHIC, INC., at Buyer's expense, provided the Motherboard is returned, also at Buyer's expense, to VECTOR GRAPHIC, INC., for such repair, replacement or correction. In performing any repair, replacement or correction after expiration of the period set forth above, Buyer will be charged in addition to the cost of parts the then-current VECTOR GRAPHIC, INC., repair rate. At the present time the applicable rate is \$35.00 for the first hour, and \$18.00 per hour for every hour of work required thereafter. Prior to commencing any repair, replacement or correction of defects in material or workmanship discovered after expiration of the period for no-cost-to-Buyer repairs, VECTOR GRAPHIC, INC., will submit to Buyer a written estimate of the expected charges, and VECTOR GRAPHIC, INC., will not commence repair until such time as the written estimate of charges has been returned by Buyer to VECTOR GRAPHIC, INC., signed by duly authorized representative authorizing VECTOR GRAPHIC, INC., to commence with the repair work involved. VECTOR GRAPHIC, INC., shall have no obligation to repair, replace or correct any Motherboard until the written estimate has been returned with approval to proceed, and VECTOR GRAPHIC, INC., may at its option also require prepayment of the estimated repair charges prior to commencing work.

Repair Agreement void if the enclosed card is not returned to VECTOR GRAPHIC, INC. within ten (10) days of end consumer purchase.

# VECTOR 1 MOTHERBOARD

# TABLE OF CONTENTS

| SUBJECT              | PAGE  |

|----------------------|-------|

| PARTS LIST           | BELOW |

| FEATURES             | 1     |

| PARTS LAYOUT DRAWING | 1     |

| S-100 BUS LISTING    | 2     |

| WARRANTY             |       |

#### PARTS LIST

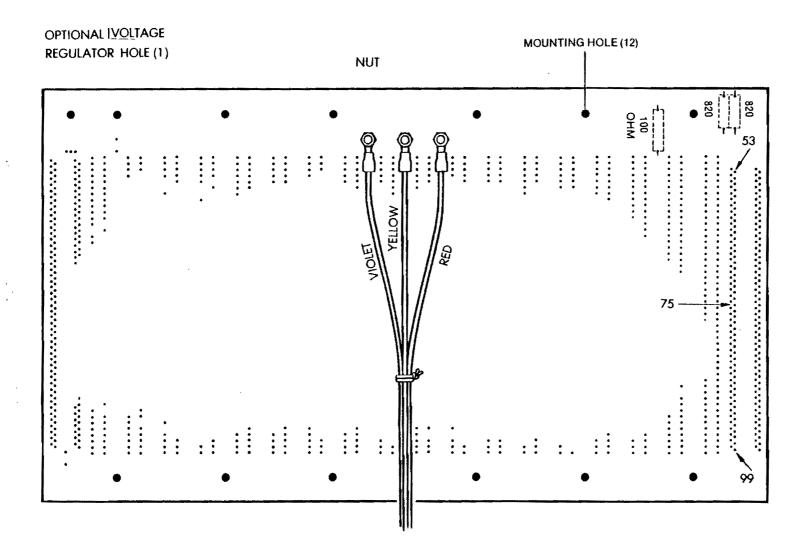

| QTY. | DESCRIPTION                                                   |

|------|---------------------------------------------------------------|

| 1    | PRINTED CIRCUIT BOARD                                         |

| 2    | 820 OHM 1 WATT RESISTORS (STRIPES OF GRAY, RED, BROWN)        |

| 1    | 100 OHM 2 WATT RESISTORS (STRIPES OF BROWN, BLACK, BROWN)     |

| 1    | 7805/340T-5 REGULATOR                                         |

| 1    | #6-32X3/8 SCREW, NUT AND LOCKWASHER                           |

| 41   | 330 OHM 1/4 WATT RESISTORS (STRIPES OF ORANGE, ORANGE, BROWN) |

| 41   | 470 OHM 1/4 WATT RESISTORS (STRIPES OF YELLOW, VIOLET, BROWN) |

THE VECTOR 1 MOTHERBOARD HAS 18 SLOTS, IS BASED ON THE POPULAR S-100 BUS STRUCTURE AND IS DESIGNED TO PROVIDE A NUMBER OF FEATURES NOT PREVIOUSLY AVAILABLE.

IN ACCORDANCE WITH VECTOR GRAPHIC INC.'S COMMITMENT TO HIGH PERFORMANCE STANDARDS AND TOP QUALITY PRODUCTS, OUR MOTHERBOARDS ARE NOW SUPPLIED WITH BUS TERMINATORS. WITH THE INCREASED USE OF LOW POWER SCHOTTKY TTL AND ITS REDUCED NOISE IMMUNITY, BUS TERMINATION BECOMES A DESIRABLE FEATURE. NOT TO BE CONFUSED WITH SO CALLED "ACTIVE" TERMINATORS, FULL TIME TERMINATION IS PROVIDED.

#### **FEATURES**

MOST POPULAR "ALTAIR/IMSAI" S-100 BUS STRUCTURE

CAN BE USED TO RETROFIT YOUR SECTIONED ALTAIR MOTHERBOARD

POSITIONS FOR 18 .125" X 0.25" 100 PIN EDGE CONNECTORS

ACCEPTS EITHER SOLDER PINS OR WIRE WRAP PINS

MOST POPULAR 0.25" CENTER TO CENTER SPACING BETWEEN PIN ROWS

0.75" CENTER TO CENTER SPACING BETWEEN CONNECTORS

EXTRA HEAVY 0.93" WARP RESISTANT, AEROSPACE QUALITY G-10 EPOXY BOARD

FULL GROUNDPLANE REDUCES NOISE ON BUS LINES

PLATED THROUGH HOLES FOR MORE RELIABLE CONNECTIONS

TRACES ON BACK OF BOARD ONLY

LESS RISK OF SHORTS FROM CONDUCTIVE ITEM BEING INADVERTENTLY DROPPED DURING OPERATION

MUCH EASIER TO TROUBLE SHOOT

REDUCED CAPACITANCE BETWEEN TRACES

SOLDER MASKED TO REDUCE RISK OF SOLDER BRIDGES DURING ASSEMBLY

BUS TERMINATION

POWER RATING: 20 A FOR +8 VOLT TRACE; 25 A FOR +16V TRACES

BOARD SIZE 15" X 8.5"

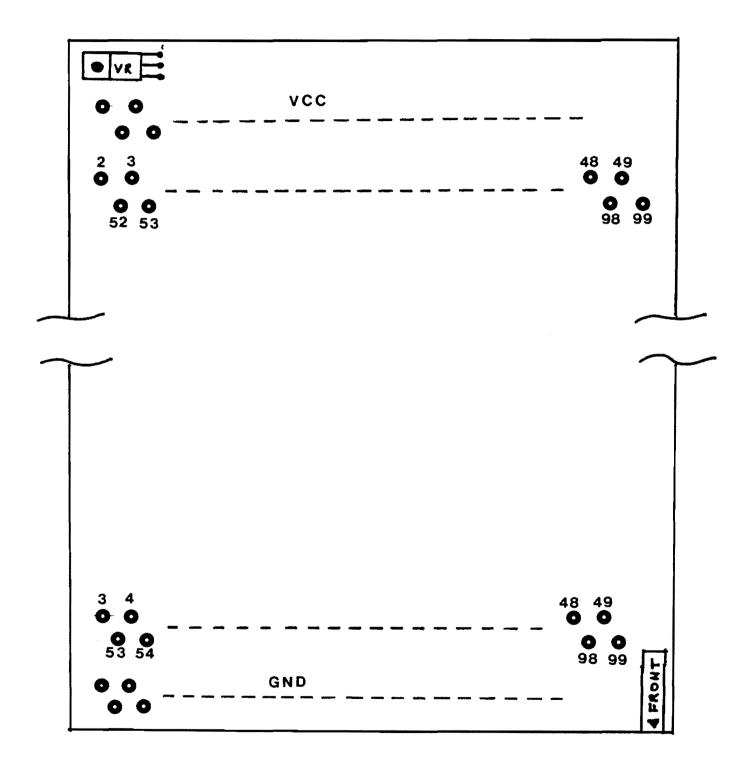

# 5 - MOTHERBOARD BOTTOM

### MOTHERBOARD USERS MANUAL

#### BUS TERMINATION

THE TERMINATORS PROVIDED ARE 330 OHM PULL-UP (TO +5V) AND 470 OHM PULL-DOWN (TO GND).

# TABLE 1

#### LINES TERMINATED

| 24 - 2          | 38 - D04     | 76 - PSYNC     | 86 - A14        |

|-----------------|--------------|----------------|-----------------|

| 25 - 1          | 39 - DO5     | 77 - PWR       | 87 - All        |

| 29 - A5         | 40 - DO6     | 78 - POBIN     | 88 - DO2        |

| 30 - A4         | 41 - DI2     | 79 <b>-</b> A0 | 89 - DO3        |

| 31 - A3         | 42 - DI3     | 80 - Al        | 90 <b>-</b> DO7 |

| 32 - Al5        | 43 - DI7     | 81 - A2        | 91 - DI4        |

| 33 - Al2        | 47 - SMEMR   | 82 - A6        | 92 - DI5        |

| 34 - A9         | 49 - CLK     | 83 - A7        | 93 - DI6        |

| 35 <b>-</b> DO1 | 54 - EXT CLR | 84 - A8        | 94 - DI1        |

| 36 - DOO        | 68 - MWRITE  | 85 - Al3       | 95 - DIO        |

| 37 - A10        |              |                |                 |

# S-100 BUS

| 1.  | +8V     | UNREGULATED INPUT TO +5V REGULATORS               |

|-----|---------|---------------------------------------------------|

| 2 • | +16V    | UNREGULATED INPUT TO +12V REGULATORS              |

| 3.  | XRDY    | ANDED WITH PRDY AND GOES TO 8080 RDY              |

| 4 • | VIO     | VECTORED INTERRUPT REQUEST O                      |

| 5.  | VI1     | VECTORED INTERRUPT REQUEST 1                      |

| 6.  | VI2     | VECTORED INTERRUPT REQUEST 2                      |

| 7.  | VI3     | VECTORED INTERRUPT REQUEST 3                      |

| 8.  | VI4     | VECTORED INTERRUPT REQUEST 4                      |

| 9.  | VI5     | VECTORED INTERRUPT REQUEST 5                      |

| 10. | VI6     | VECTORED INTERRUPT REQUEST 6                      |

| 11. | VI7     | VECTORED INTERRUPT REQUEST 7                      |

| 12. | XRDY2   |                                                   |

| 13. |         |                                                   |

| 14. |         |                                                   |

| 15. |         |                                                   |

| 16. |         |                                                   |

| 17. |         |                                                   |

| 18. | STA DSB | STATUS BUFFER DISABLE                             |

| 19. | C/C DSB | COMMAND/CONTROL BUFFER DISABLE                    |

| 20. | UNPROT  | INPUT TO MEMORY PROTECT CIRCUITRY ON MEMORY BOARD |

| 21. | SS      | INDICATES MACHINE IS IN SINGE STEP MODE           |

| 22. | ADD DSB | ADDRESS BUFFER DISABLE                            |

| 23. | DO DSB  | DATA OUT (FROM CPU) BUFFER DISABLE                |

| 24. | Φ2      | PHASE TWO CLOCK TTL LEVELS                        |

| 25. | Φ1      | PHASE ONE CLOCK TTL LEVELS                        |

| 26. | PHLDA   | HOLD ACKNOWLEDGE, BUFFERED 8080 OUTPUT            |

27. PWAIT WAIT ACKNOWLEDGE, BUFFERED 8080 OUTPUT INTERRUPT ENABLE, BUFFERED 8080 OUTPUT 28. PINTE 29. A5 BUFFERED ADDRESS LINE 5 (32) 30. A 4 BUFFERED ADDRESS LINE 4 (16) 31. A3 BUFFERED ADDRESS LINE 3 (8) 32. BUFFERED ADDRESS LINE 15 (32768) A15 33. A12 BUFFERED ADDRESS LINE 12 (4096) 34. A 9 BUFFERED ADDRESS LINE 1 (2) 35. DO 1 BUFFERED DATA OUT LINE 1 36. DOO BUFFERED DATA OUT LINE O 37. A10 BUFFERED ADDRESS LINE 10 (1024) 38. D04 BUFFERED DATA OUT LINE 4 39. DO 5 BUFFERED DATA OUT LINE 5 40. D06 BUFFERED DATA OUT LINE 6 41. DI2 DATA INPUT LINE 2 42. DI3 DATA INPUT LINE 3 43. DI7 DATA INPUT LINE 7 44. SMI LATCHED 8080 M1 STATUS 45. SOUT LATCHED 8080 OUT STATUS 46. SINP LATCHED 8080 INP STATUS 47. SMEMR LATCHED 8080 MEMR STATUS 48. SHLTA LATCHED 8080 HLTA STATUS 49. CLOCK 2 MHZ CLOCK, CRYSTAL CONTROLLED 50. GND LOGIC AND POWER GROUND RETURN · 51 · +8V UNREGULATED INPUT TO +5V REGULATORS 52. -16V UNREGULATED INPUT TO NEGATIVE REGULATORS SSW DSB 53. SENSE SWITCH DISABLE

CLEAR SIGNAL FOR I/O DEVICES

54.

EXT CLR

| 55. | RTC         | REAL TIME CLOCK OR 48K FAST RESET                  |

|-----|-------------|----------------------------------------------------|

| 56. | STSTB       | STROBE SIGNAL (BY 8224 CLOCK CHIP 8800B D/C BOARD) |

| 57. | DIGI        | ENABLE SIGNAL FOR CPU DI DRIVERS 8800B             |

| 58. | FRDY        | 8800B FRONT PANEL READY SIGNAL                     |

| 59. |             |                                                    |

| 60. |             |                                                    |

| 61. |             |                                                    |

| 62. |             |                                                    |

| 63. |             |                                                    |

| 64. |             |                                                    |

| 65. |             |                                                    |

| 66. | 48K REFRESH |                                                    |

| 67. | PHANTOM     |                                                    |

| 68. | MWRT        | WRITE ENABLE SIGNAL FOR MEMORY                     |

| 69. | PS          | INDICATES IF ADDRESSED MEMORY IS PROTECTED         |

| 70. | PROT        | INPUT TO MEMORY PROTECT CIRCUITRY ON MEMORY BOARD  |

| 71. | RUN         | INDICATES MACHINE IS IN RUN MODE                   |

| 72. | PRDY        | ANDED WITH XRDY AND GOES TO 8080 RDY               |

| 73. | PINT        | INPUT TO 8080 INTERRUPT REQUEST                    |

| 74. | PHOLD       | INPUT TO 8080 HOLD REQUEST                         |

| 75. | PRESET      | CLEAR SIGNAL FOR CPU                               |

| 76. | PSYNC       | BUFFERED 8080 SYNC SIGNAL                          |

| 77. | PWR         | BUFFERED 8080 WRITE ENABLE SIGNAL                  |

| 78. | PDBIN       | BUFFERED 8080 BDIN SIGNAL                          |

| 79. | AO          | BUFFERED ADDRESS LINE 0 (1)                        |

| 80. | Al          | BUFFERED ADDRESS LINE 1 (2)                        |

| 81. | A 2         | BUFFERED ADDRESS LINE 2 (4)                        |

| 82. | A 6         | BUFFERED ADDRESS LINE 6 (64)                       |

| 83. | A 7            | BUFFERED ADDRESS LINE 7 (128)    |

|-----|----------------|----------------------------------|

| 84. | A8             | BUFFERED ADDRESS LINE 8 (256)    |

| 85. | A13            | BUFFERED ADDRESS LINE 13 (8192)  |

| 86. | A14            | BUFFERED ADDRESS LINE 14 (16384) |

| 87. | A11            | BUFFERED ADDRESS LINE 11 (2048)  |

| 88. | D O 2          | BUFFERED DATA OUT LINE 2         |

| 89. | D03            | BUFFERED DATA OUT LINE 3         |

| 90. | D07            | BUFFERED DATA OUT LINE 7         |

| 91. | DI4            | DATA INPUT LINE 4                |

| 92. | DI5            | DATA INPUT LINE 5                |

| 93. | D16            | DATA INPUT LINE 6                |

| 94. | DII            | DATA INPUT LINE 1                |

| 95. | DIO            | DATA INPUT LINE O                |

| 96. | SINTA          | LATCHED 8080 INTA STATUS         |

| 97. | <del>SVO</del> | LATCHED 8080 WO STATUS           |

| 98. | SSTACK         | LATCHED 8080 STACK STATUS        |

| 99. | POC            | LO DURING POWER UP, RESET        |

|     |                |                                  |

100. GND LOGIC AND POWER GROUND RETURN

♥ = PHI