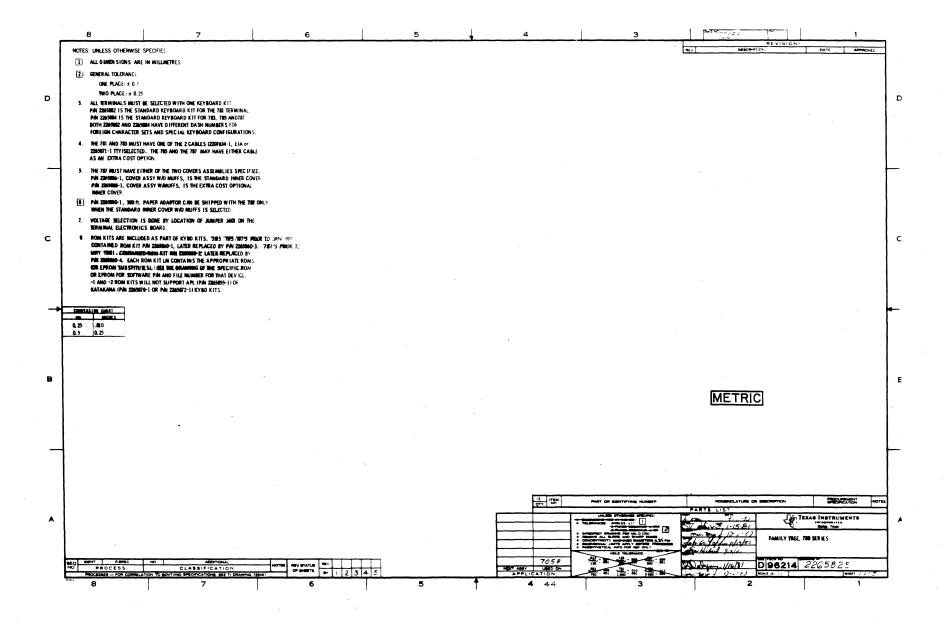

780 Series Electronic Data Terminal Family

# Maintenance Manual

Manual No. 2265862-9701

TEXAS INSTRUMENTS

# Copyright © 1981 Texas Instruments Incorporated All Rights Reserved — Printed In U.S.A.

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

No copies of the information or drawings shall be made without the prior consent of Texas Instruments Incorporated.

INSERT LATEST CHANGED PAGES. DESTROY SUPERSEDED PAGES

# LIST OF EFFECTIVE PAGES

e: The portion of the text affected by the changes is indicated by a vertical bar in the outer margins of the page.

780 Series Electronic Data Terminal Family

Part No. 2265862-9701

Original Issue: 15 March 1981

Total number of pages in this publication is 314 consisting of the following:

| Page<br>No.     | Change<br>No. | Page<br>No.     | Change<br>No. | Page<br>No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Change<br>No. |

|-----------------|---------------|-----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Front Cover     | 0             | 7-1 — 7-114     | 0             | Business Reply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0             |

| Effective Pages | 0             | 8-1 — 8-28      | 0             | Back Cover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0             |

| Preface         | 0             | A-1 — A-21      | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| iv-viii         | 0             | B-1 — B-17      | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| 1-1 — 1-6       | 0             | C-1 — C-9       | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| 2-1-2-6         | 0             | D-1 — D-7       | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| 3-1 — 3-16      | 0             | E-1 - E-3       | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| 4-1 — 4-11      | 0             | User's Response | o             | The second secon | <b>4</b>      |

| 5-1 — 5-29      | 0             |                 |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| 6-1 — 6-36      | 0             |                 | Ī             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

|                 |               |                 |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

|             | CHAN   | GE NO | <b>FICES</b> | <b>3</b>    |  |

|-------------|--------|-------|--------------|-------------|--|

| Revision    |        | ECN   |              |             |  |

| Letter Date | Number | Level |              | Description |  |

|             |        |       |              |             |  |

|             |        |       |              |             |  |

|             |        |       |              |             |  |

|             | :      |       |              |             |  |

|             |        |       |              |             |  |

|             |        |       |              |             |  |

Address all correspondence regarding orders to:

Texas Instruments Incorporated Digital Systems Group P.O. Box 1444, M/S 7793 Houston, TX 77001

# **Preface**

### SCOPE OF MANUAL

This manual contains descriptions, installation and operating instructions, communications protocol, theory of operation and maintenance procedures for the 780 Series, *Silent 700\** Electronic Data Terminals. The information in this manual is intended to help in maintaining and servicing these terminals. The troubleshooting information is designed to help isolate problems in a major replaceable assembly.

Section 1 contains a general description of each model in the 780 Series. It also includes specifications and a brief description of the options offered with each terminal.

Section 2 provides installation and interfacing information.

Section 3 contains terminal operating information.

Section 4 describes terminal communications features.

Section 5 describes in detail the theory of operation.

Section 6 covers preventive maintenance procedures and tests that can be used to isolate problems.

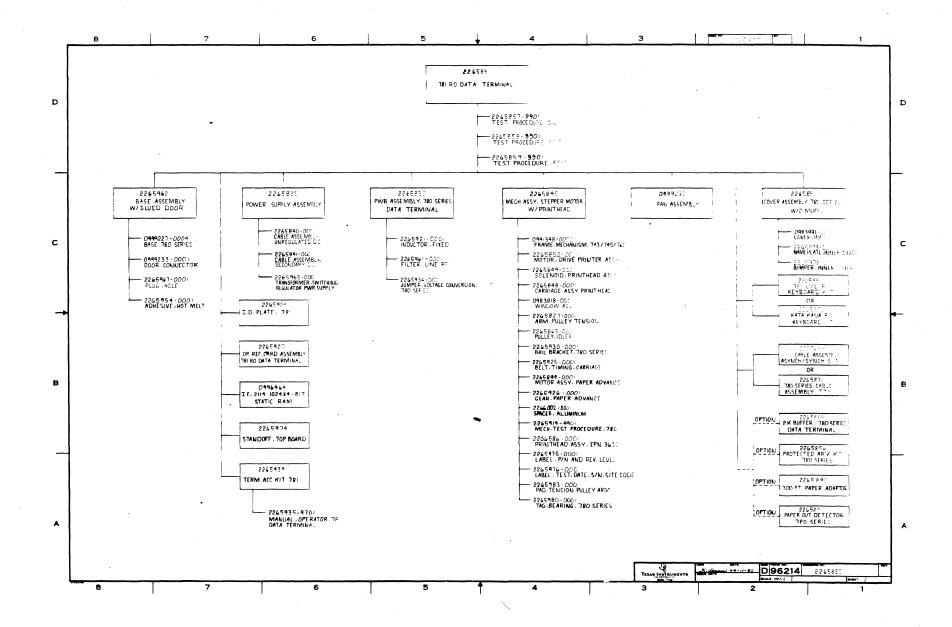

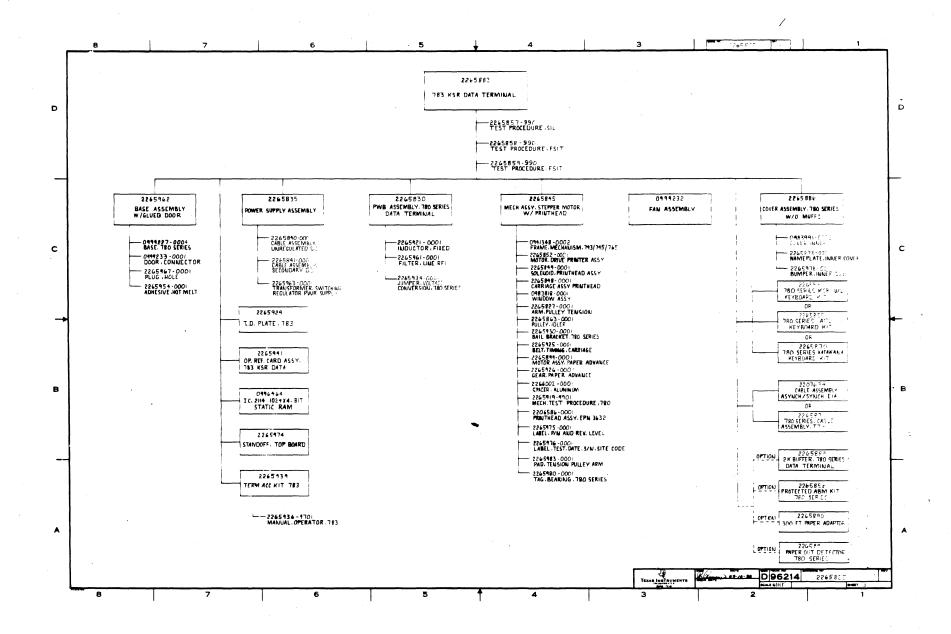

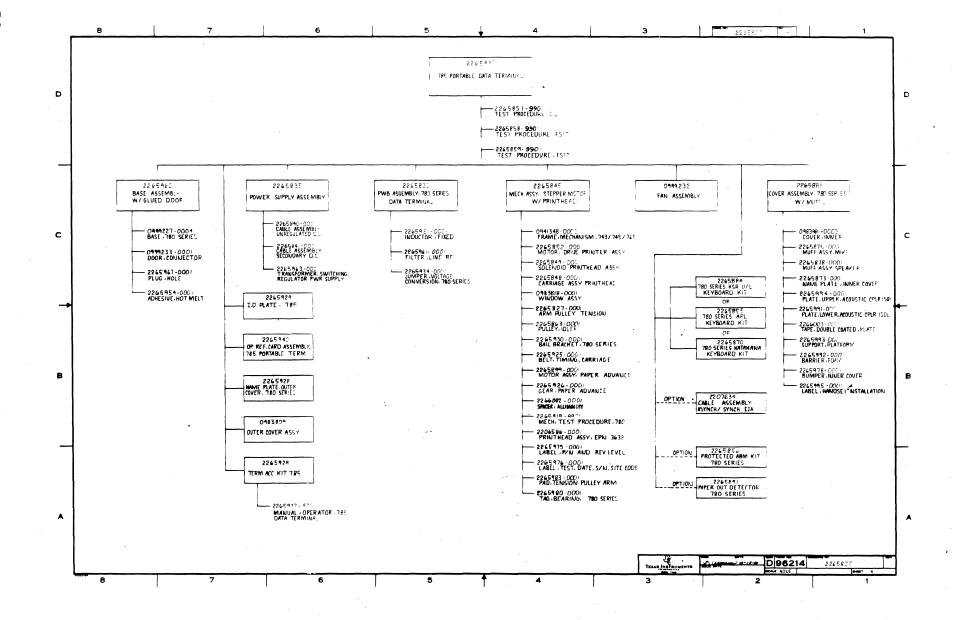

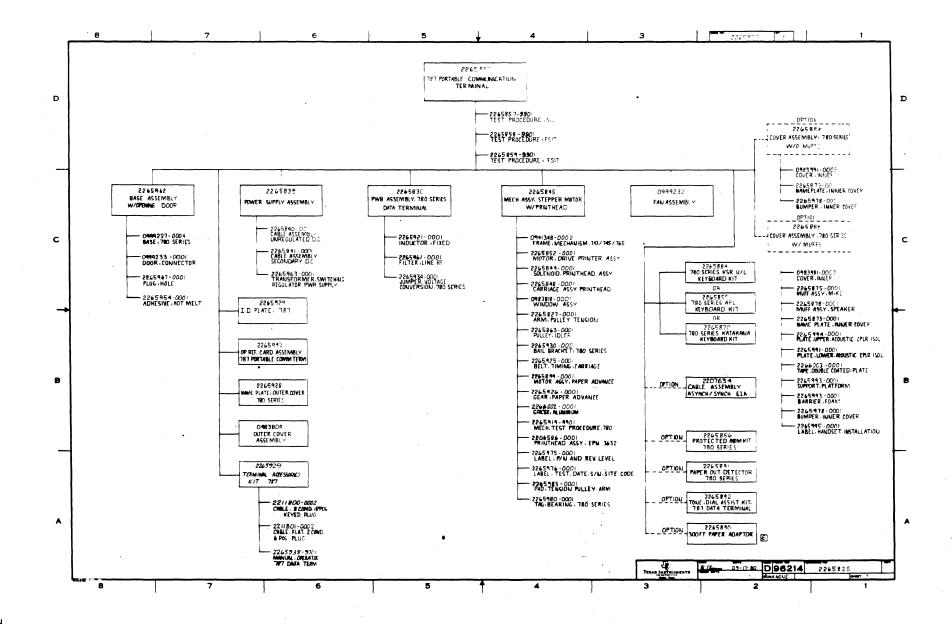

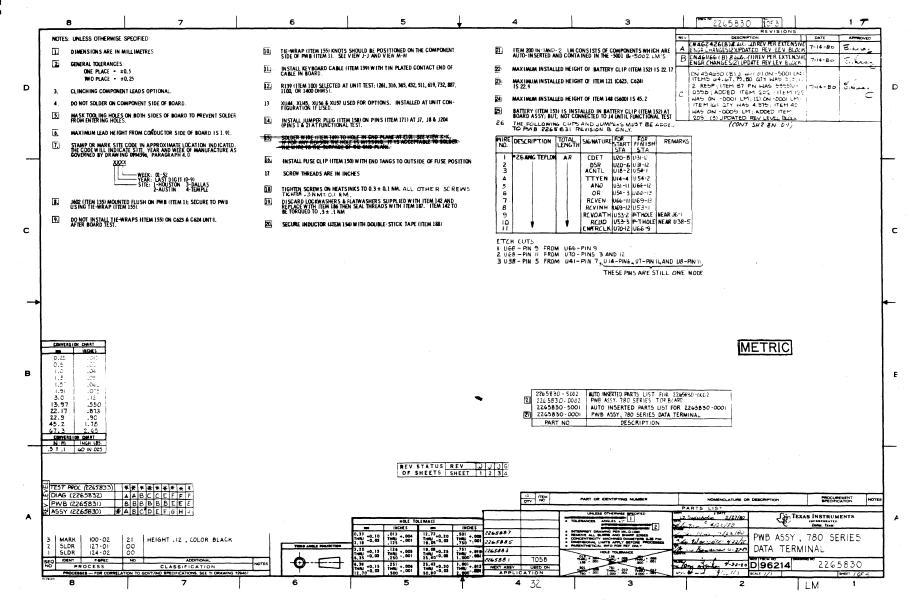

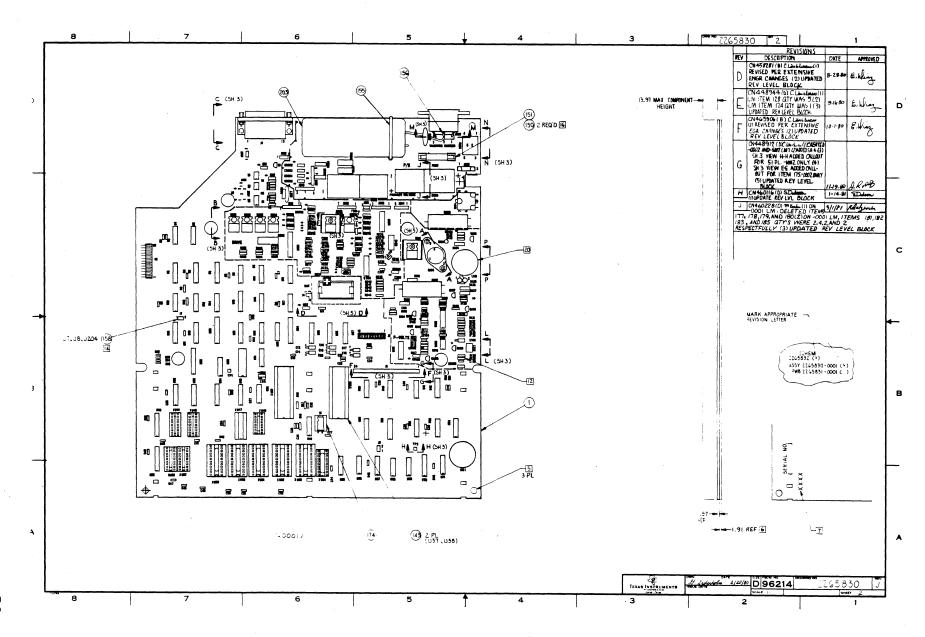

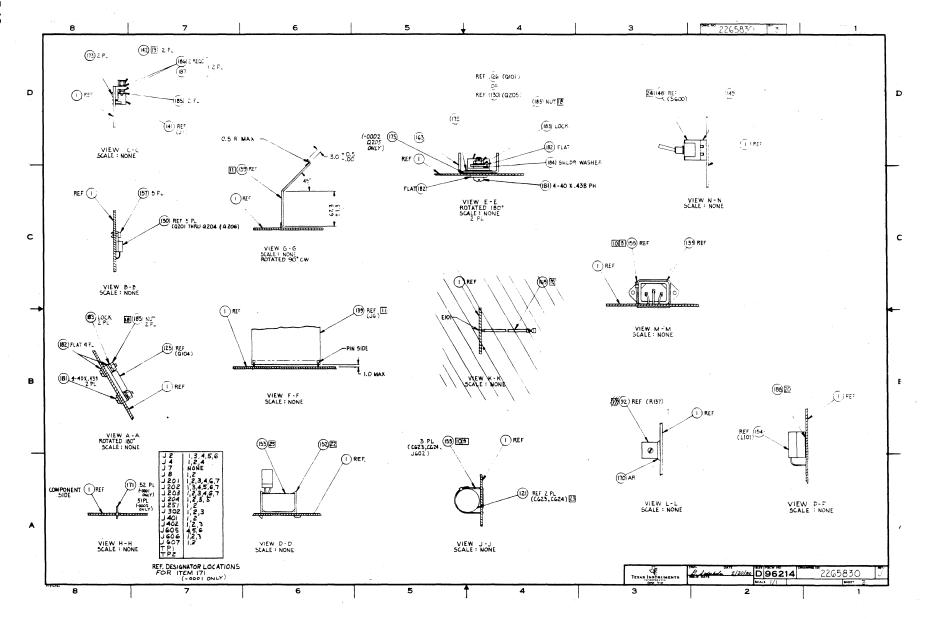

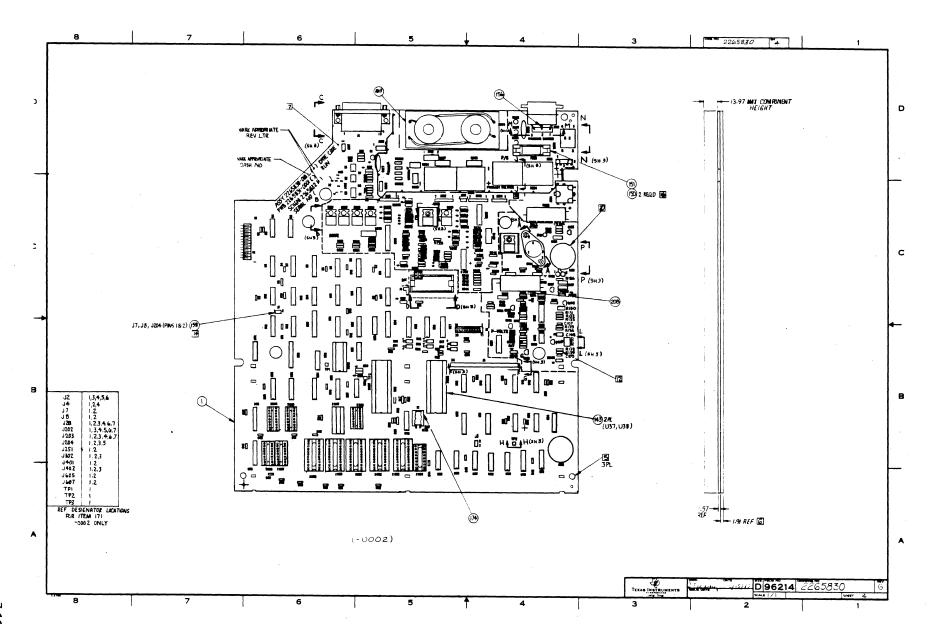

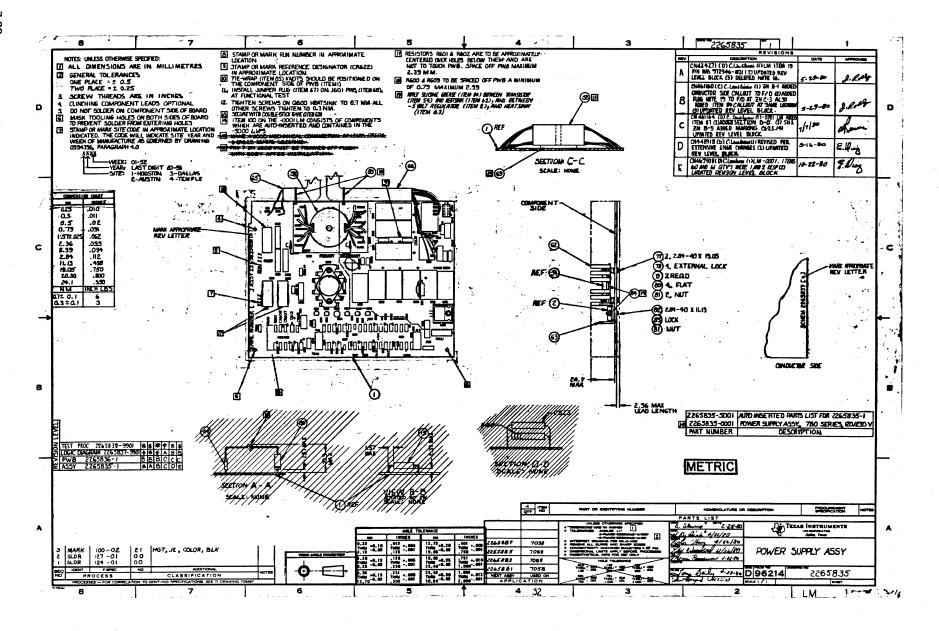

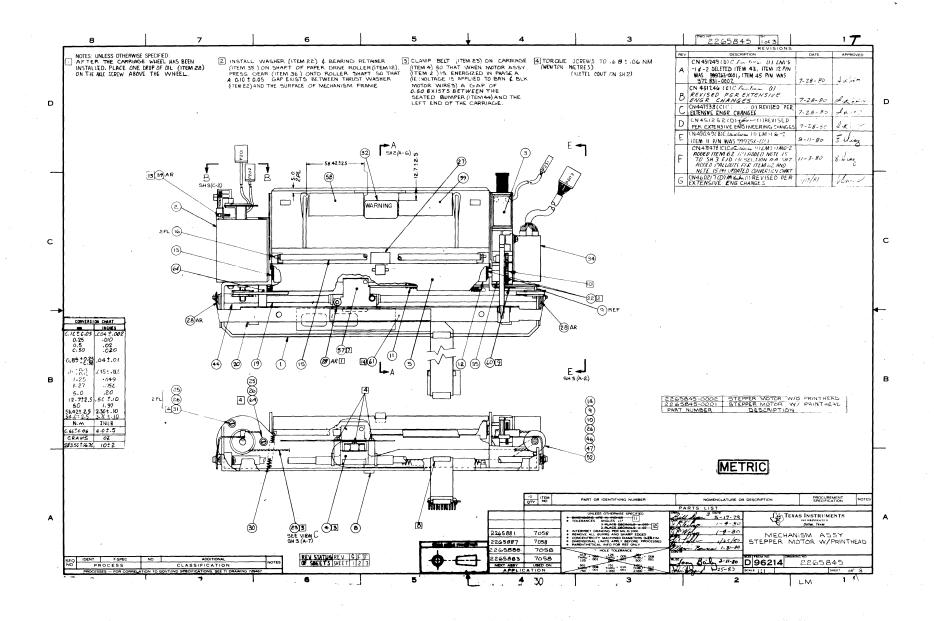

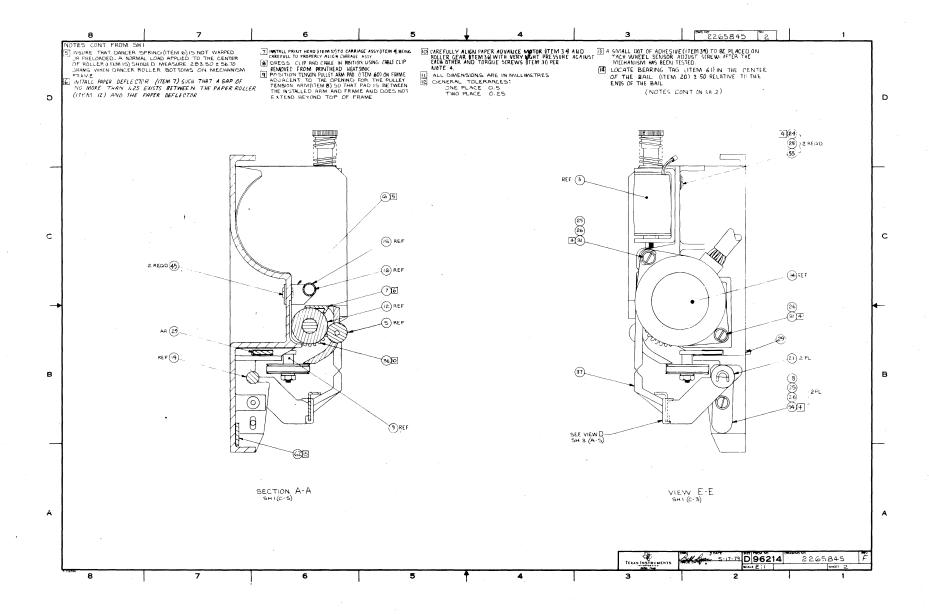

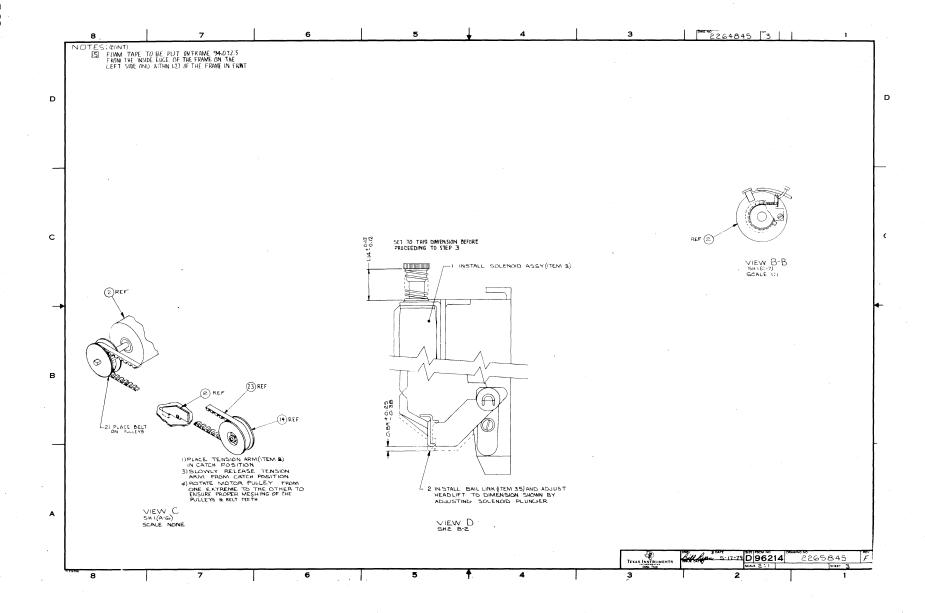

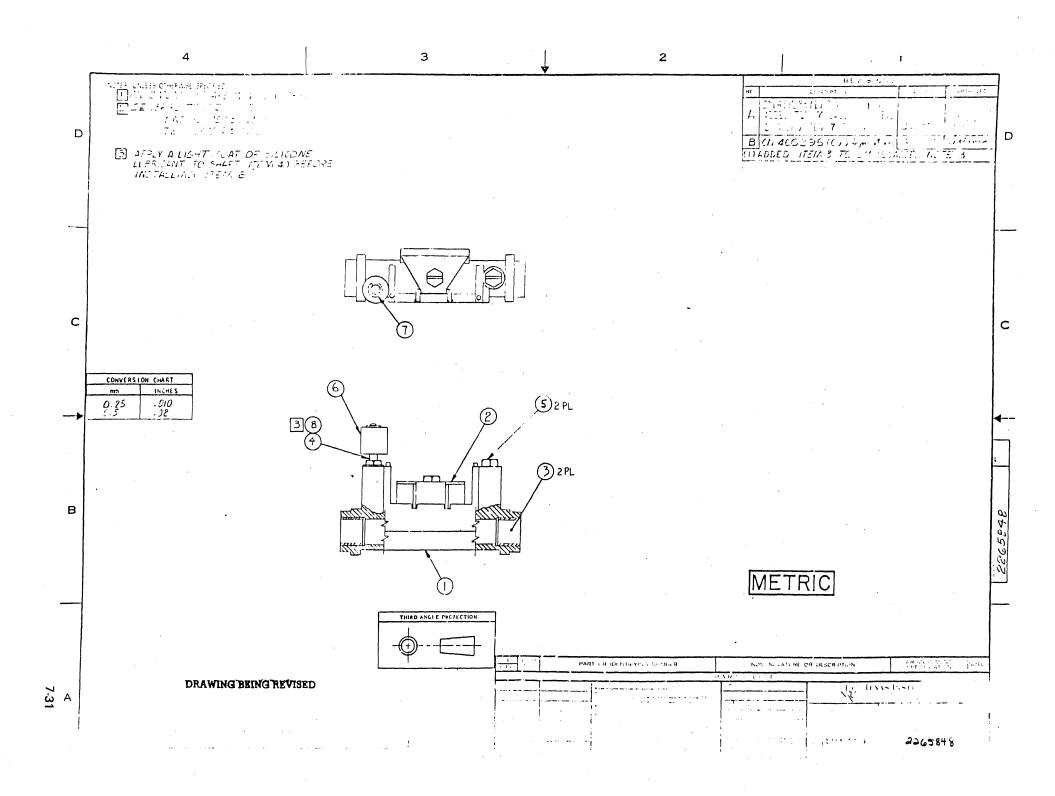

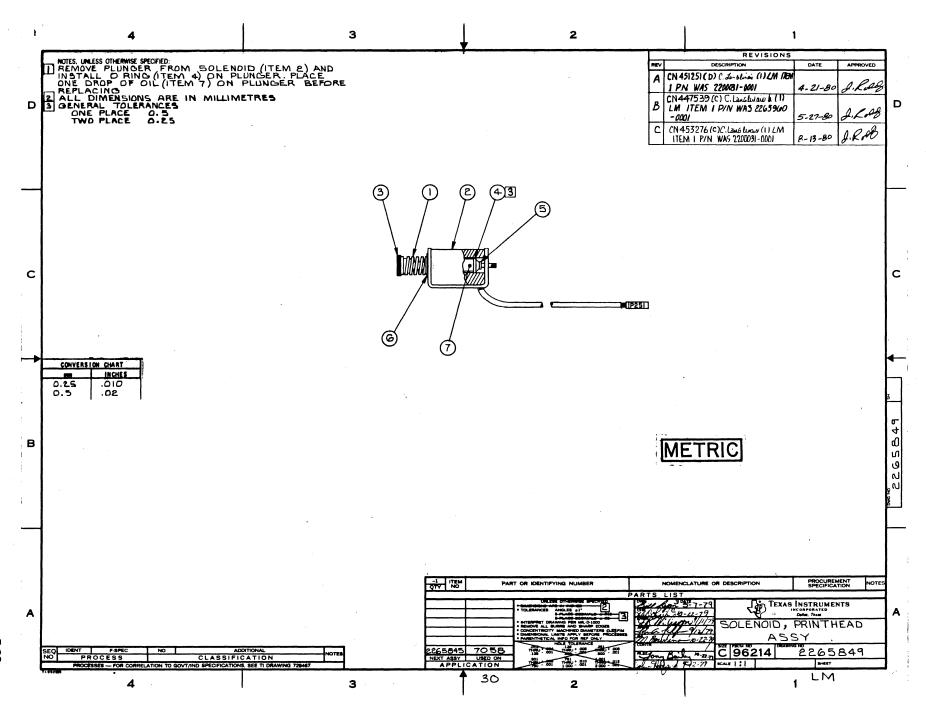

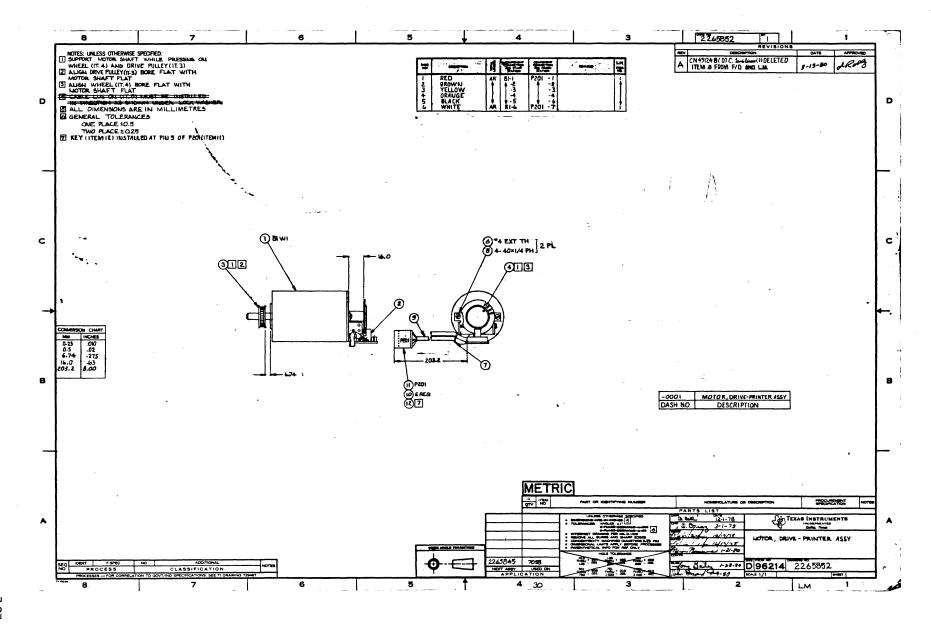

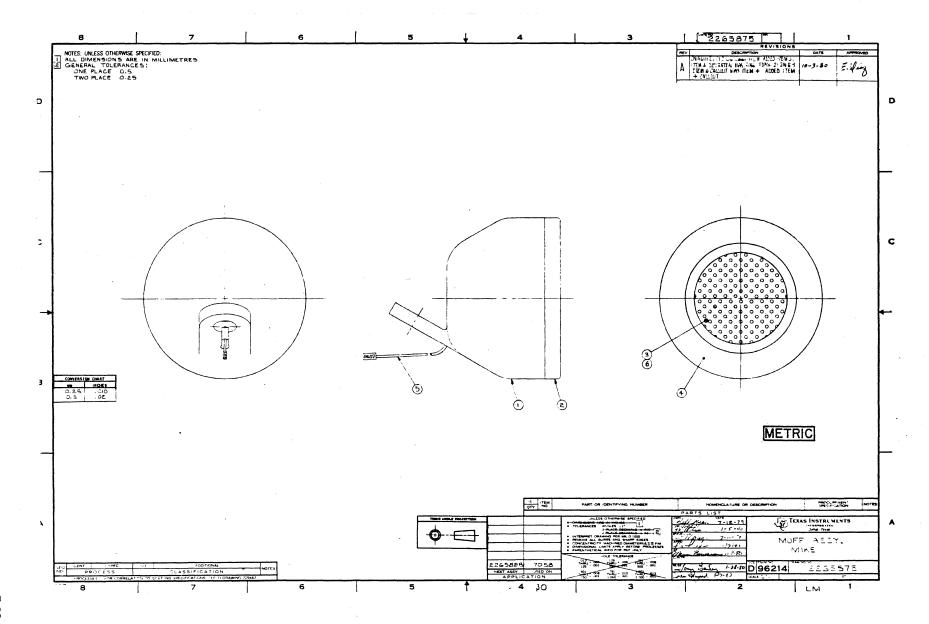

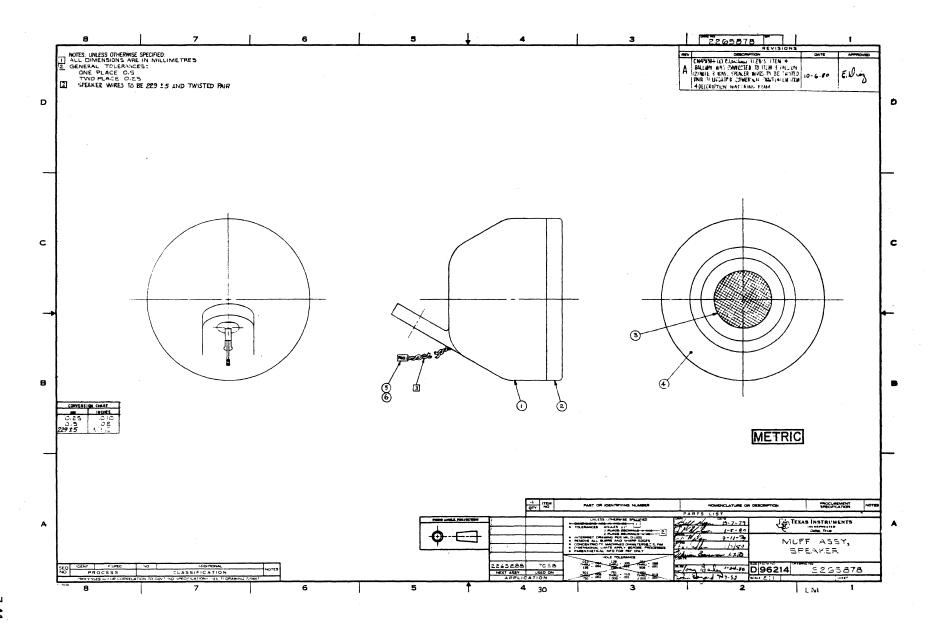

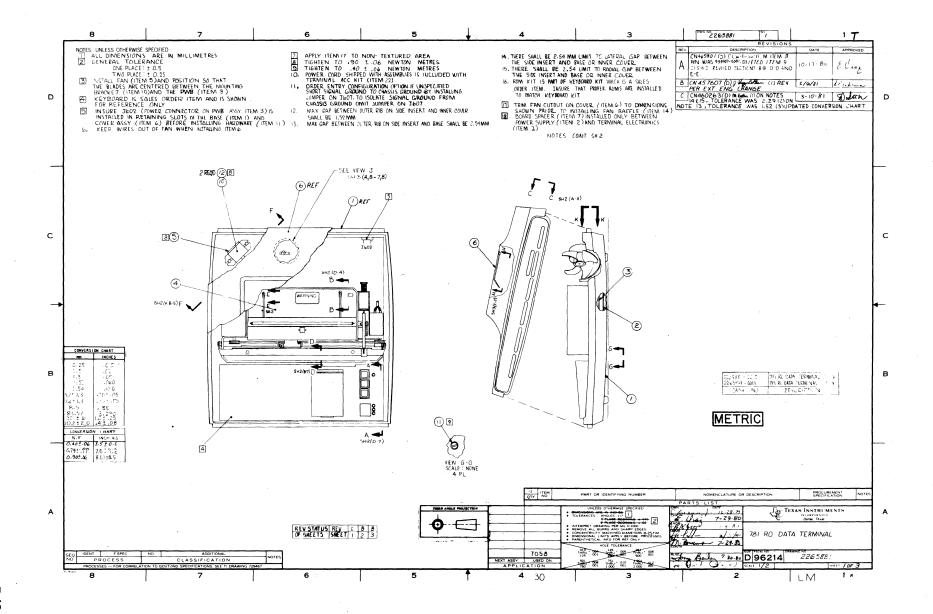

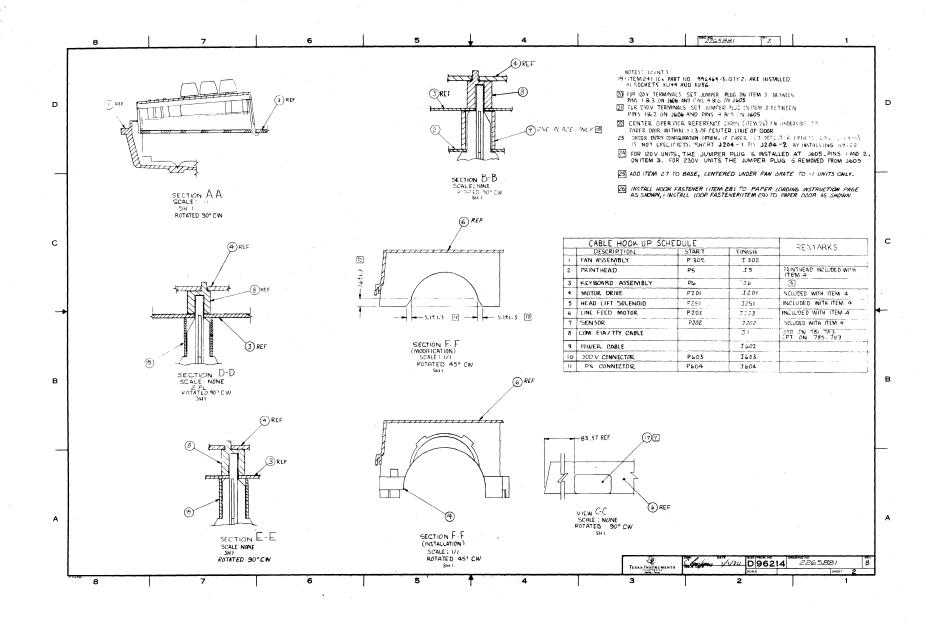

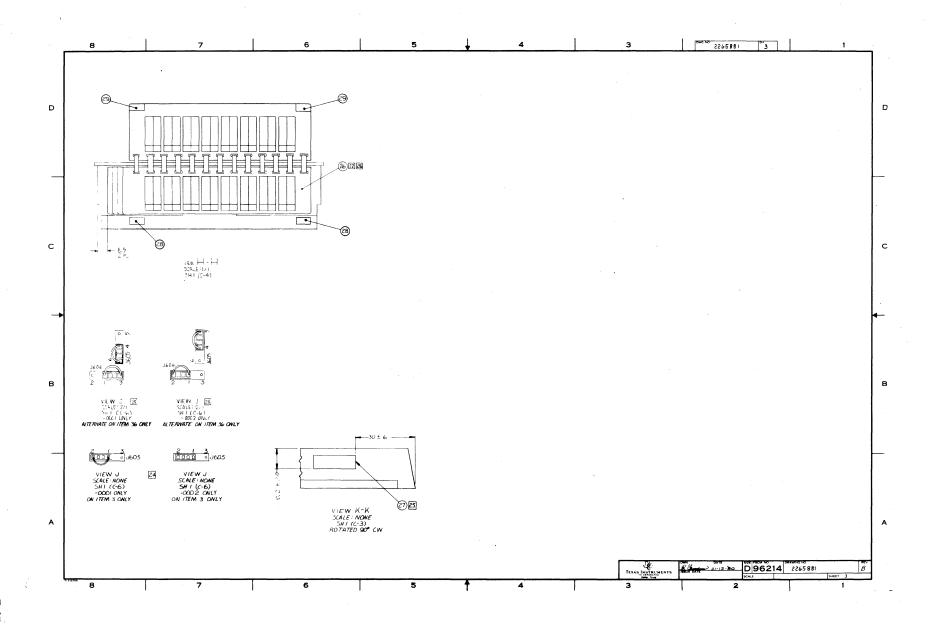

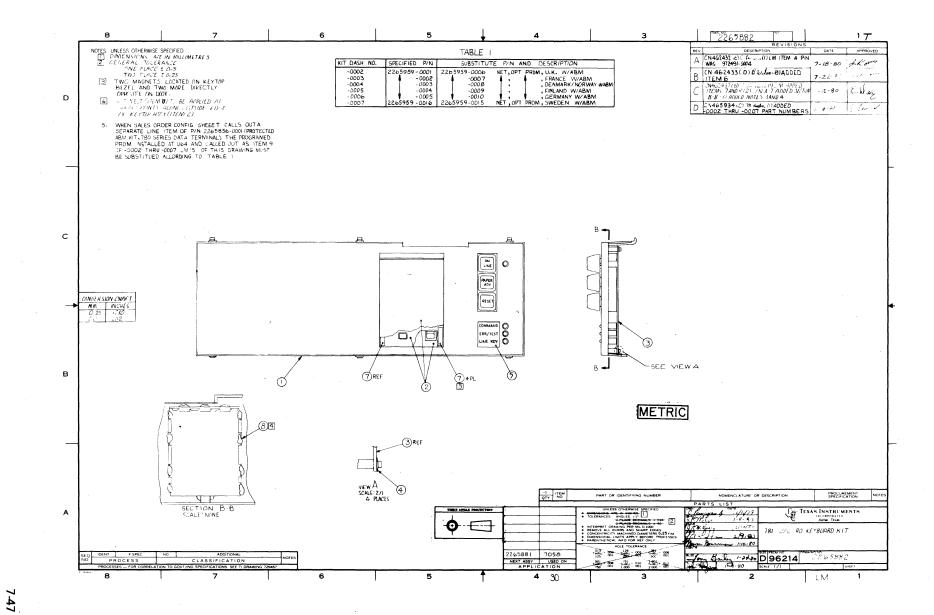

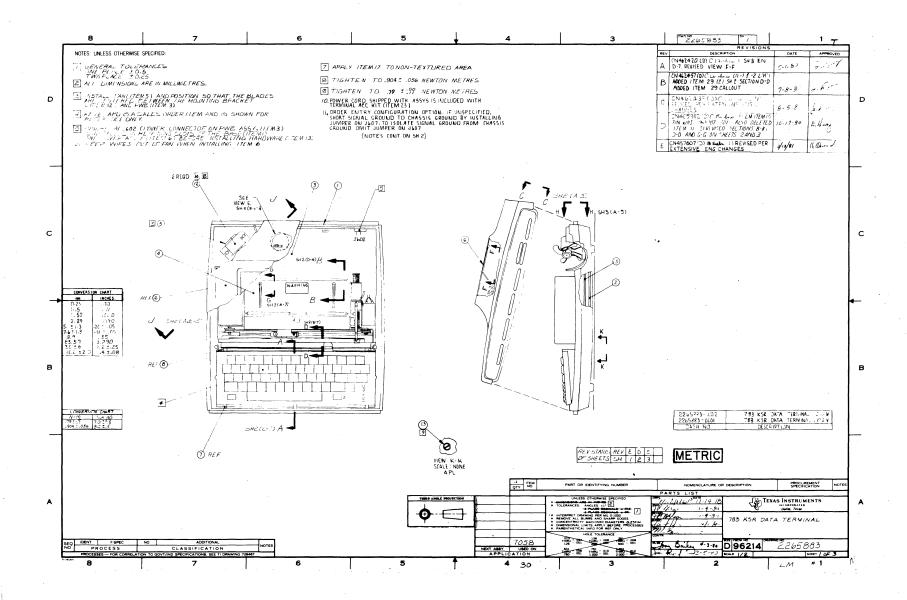

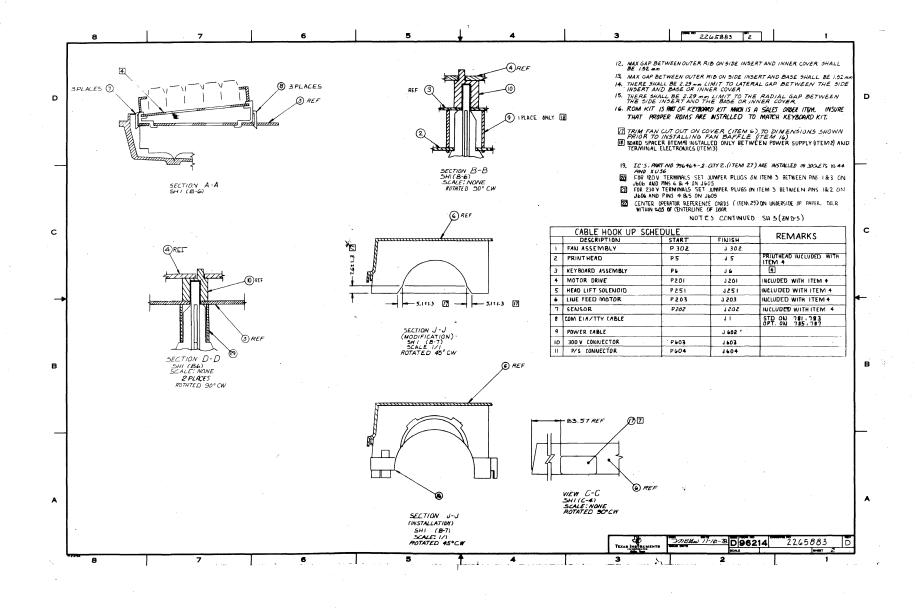

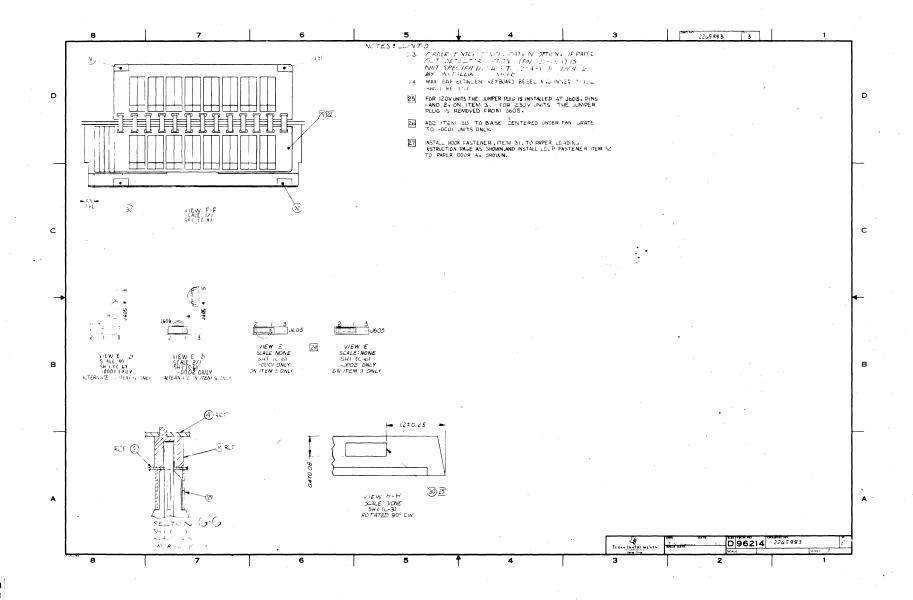

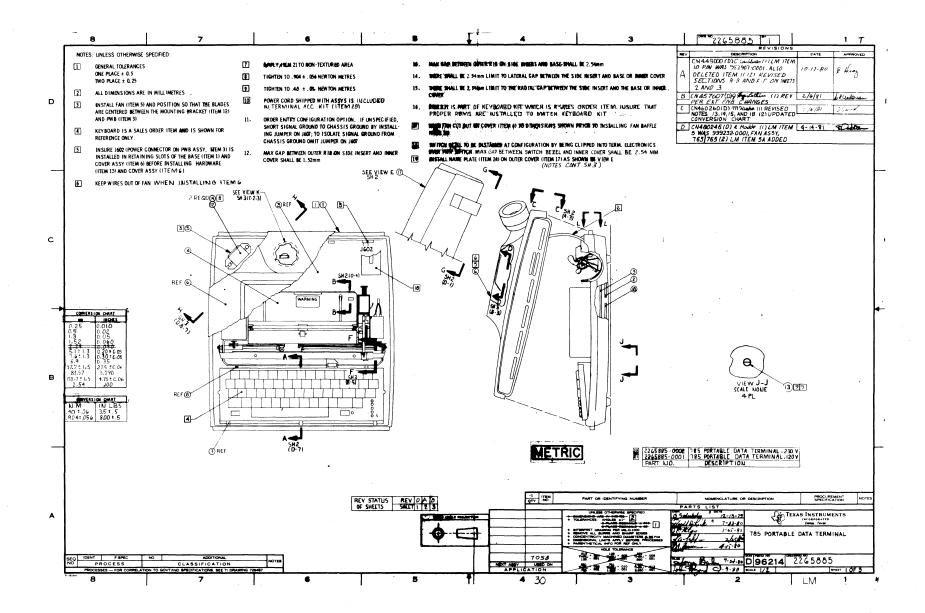

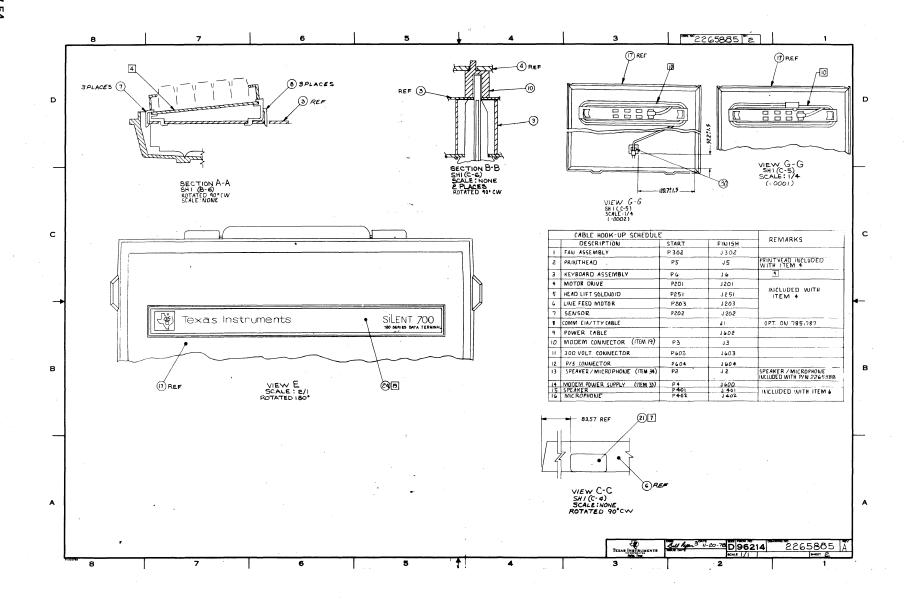

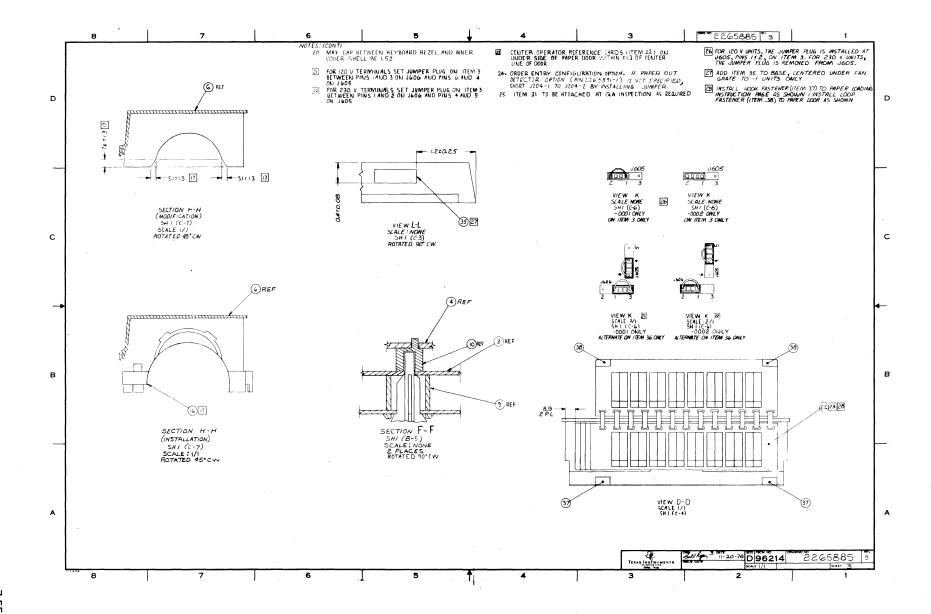

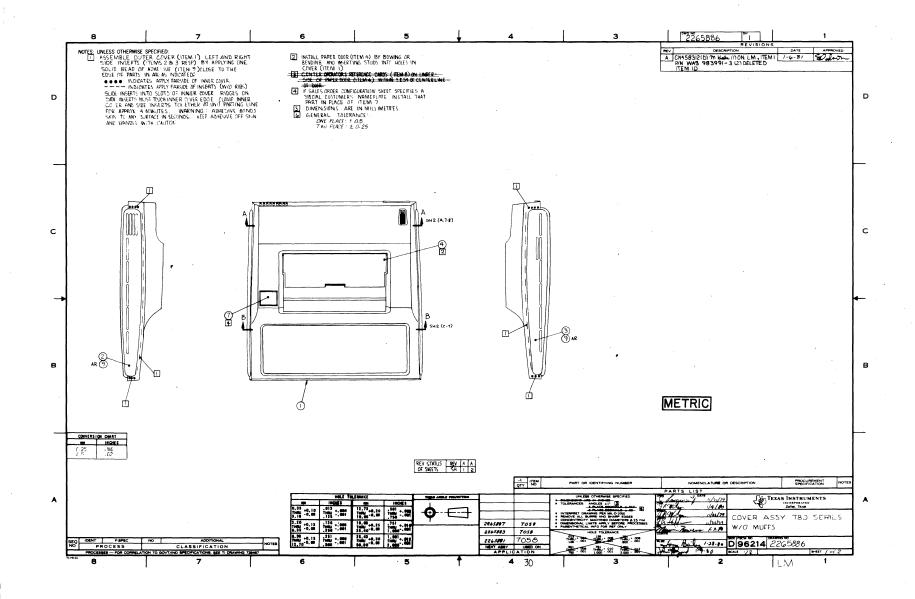

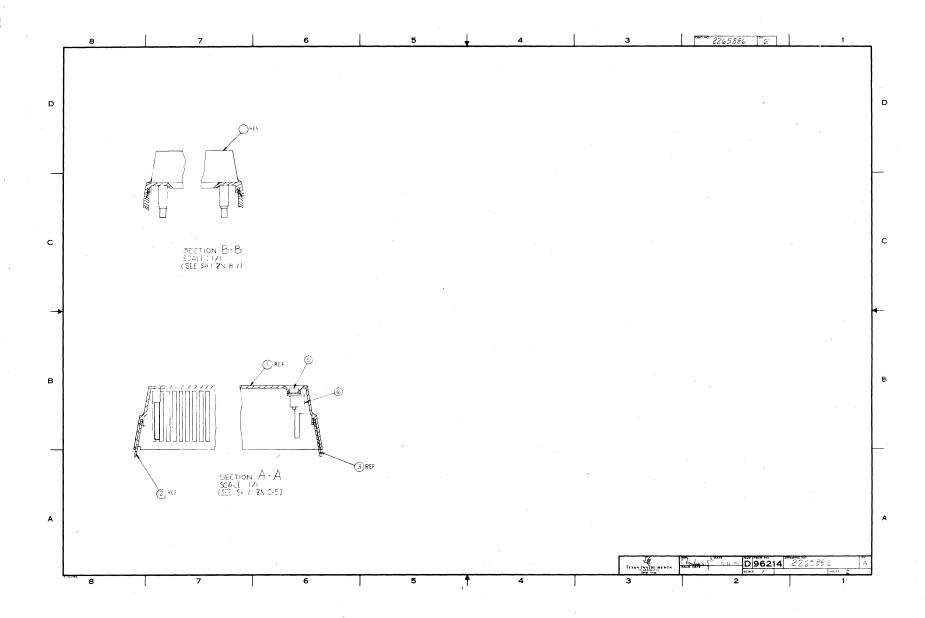

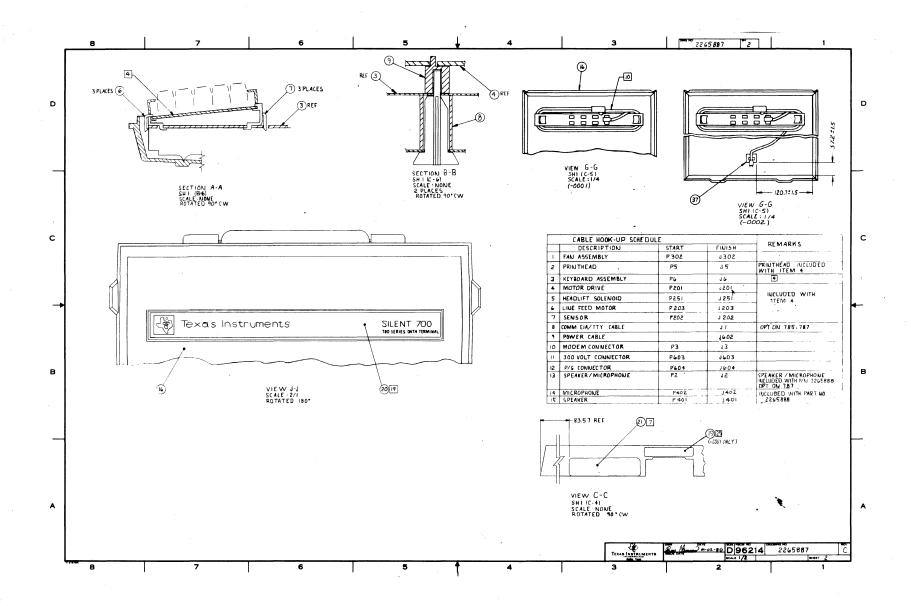

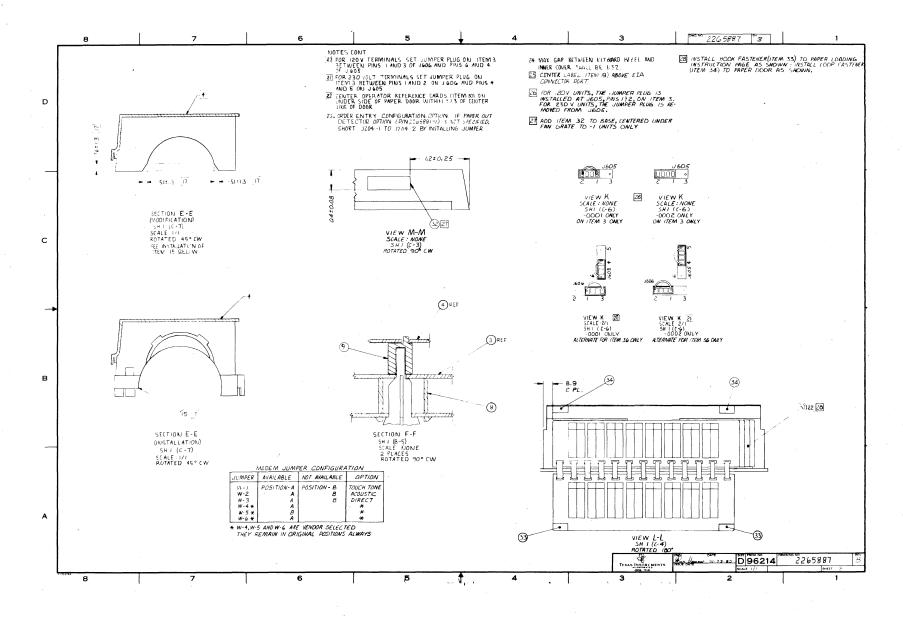

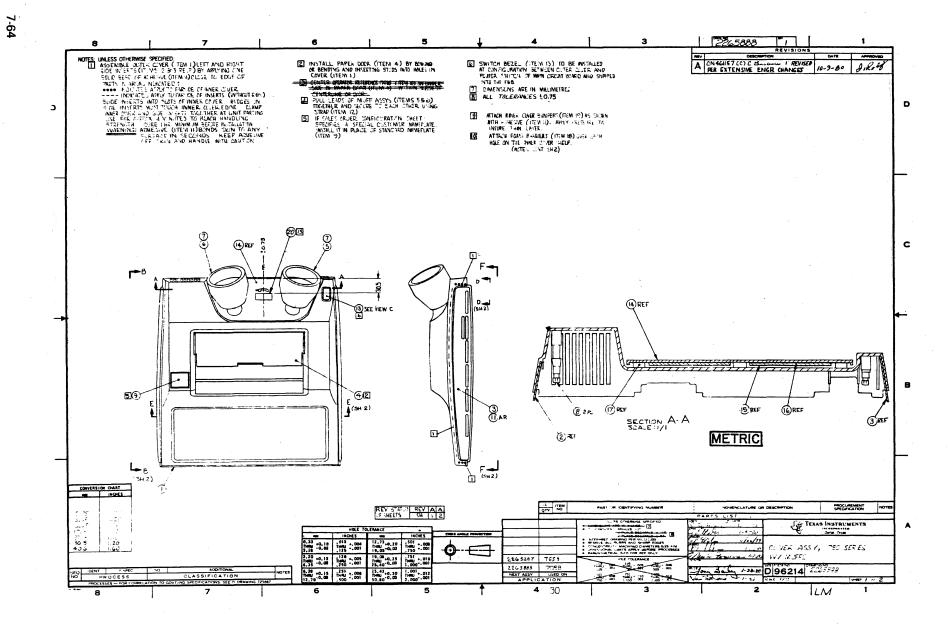

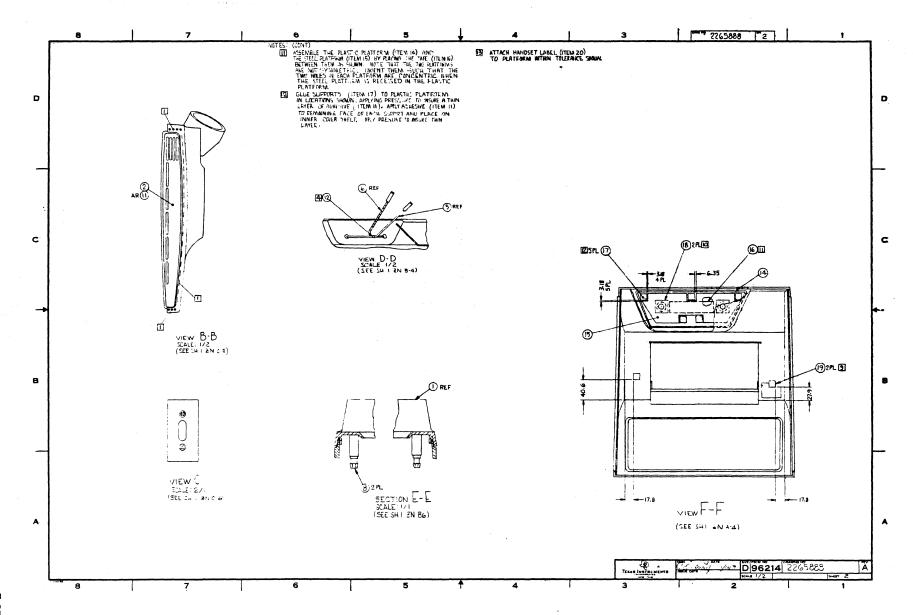

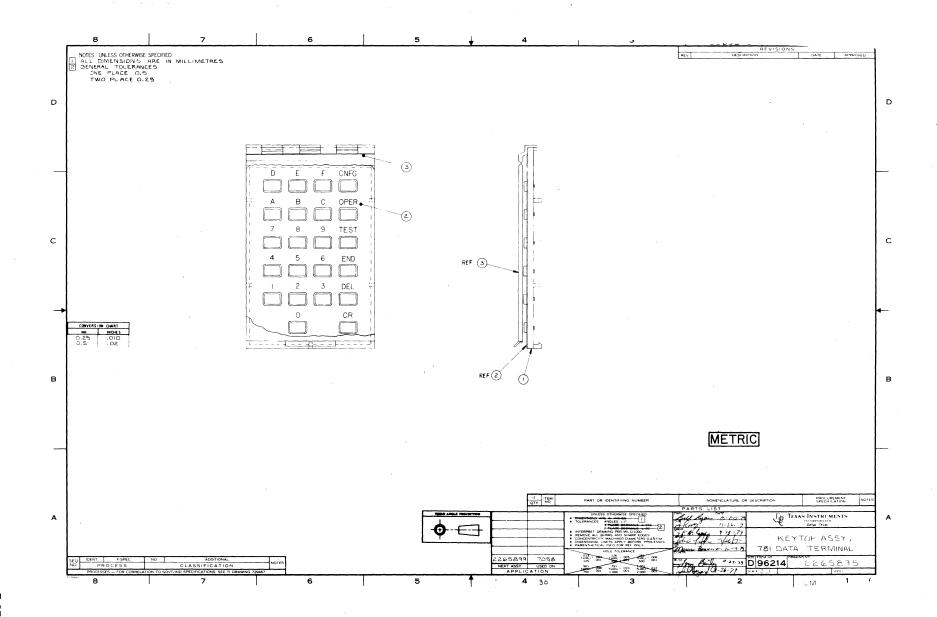

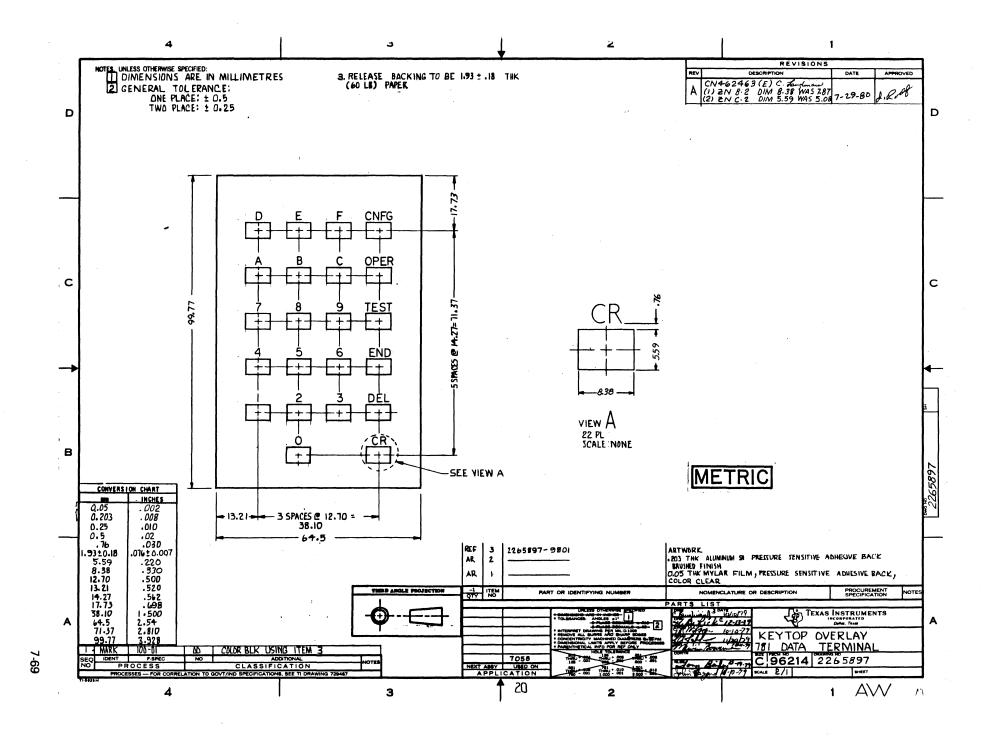

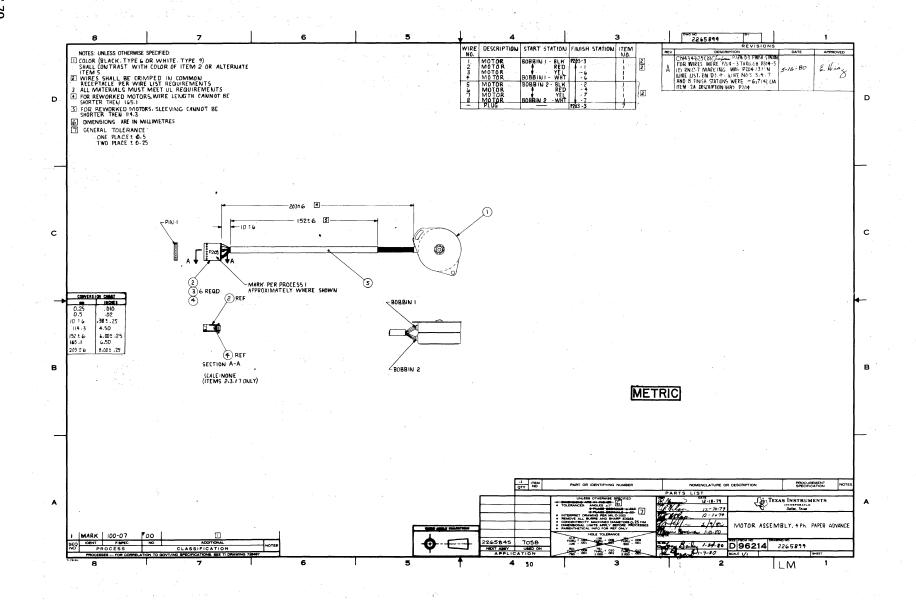

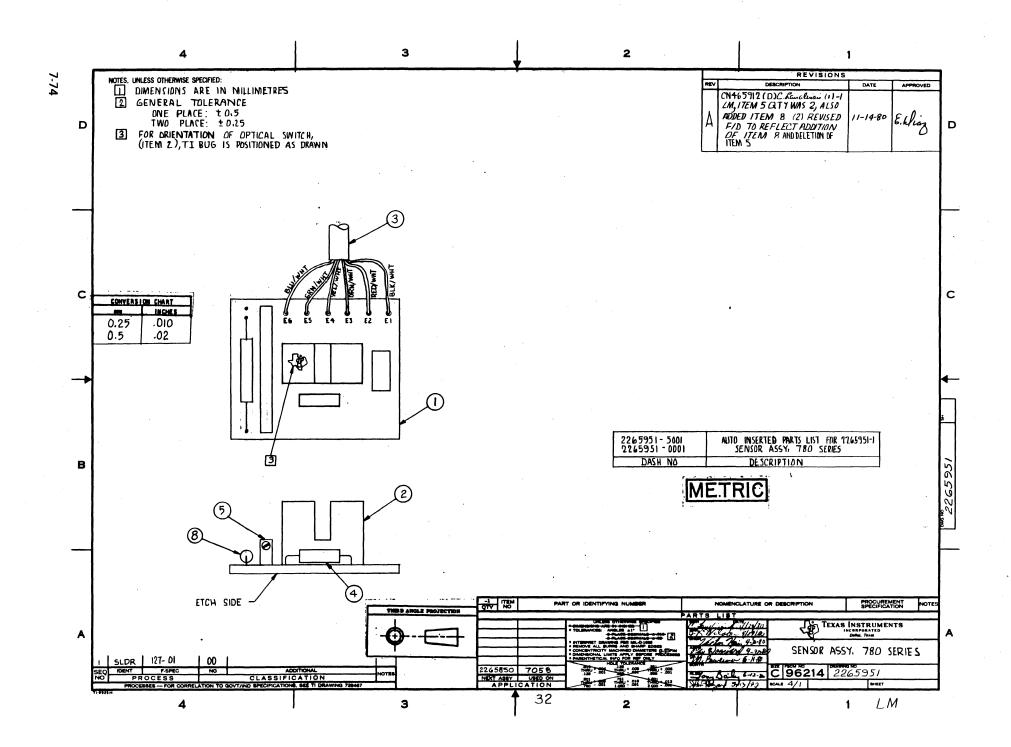

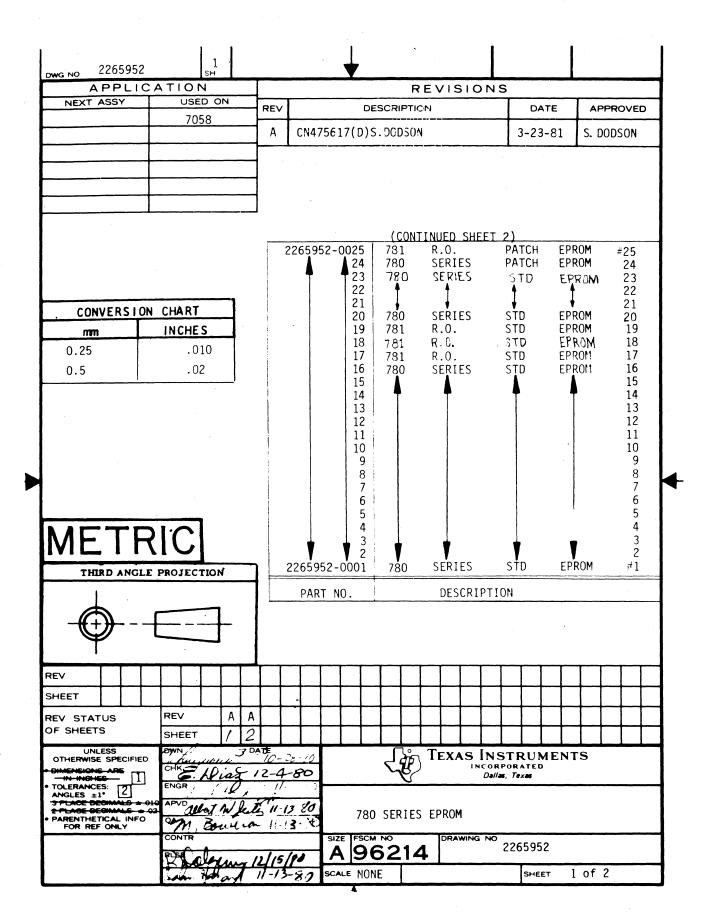

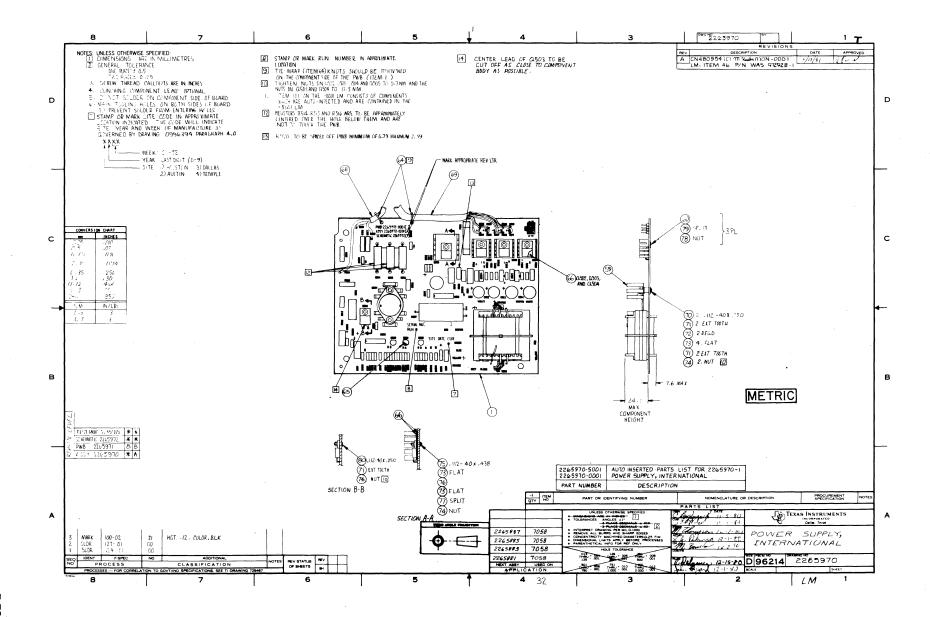

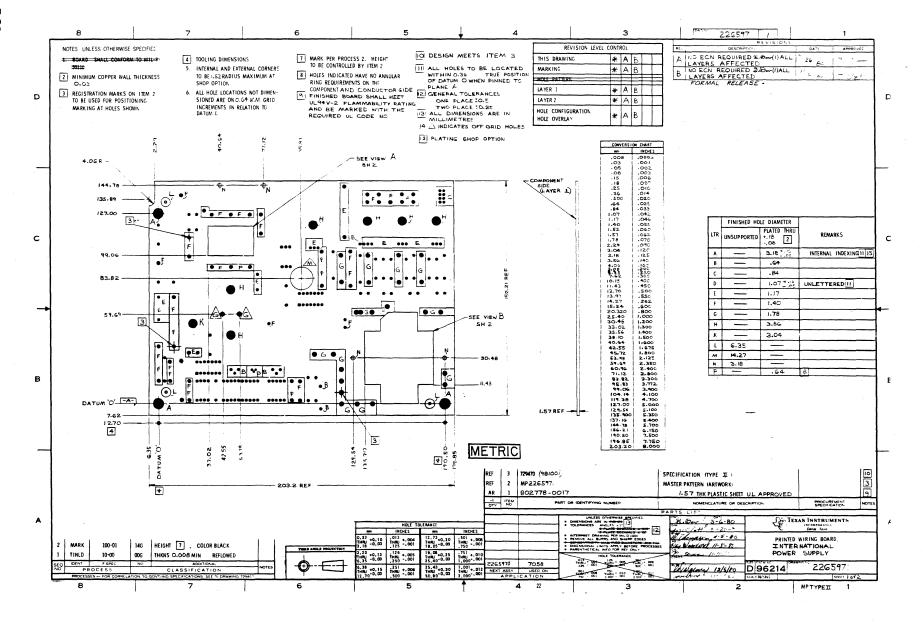

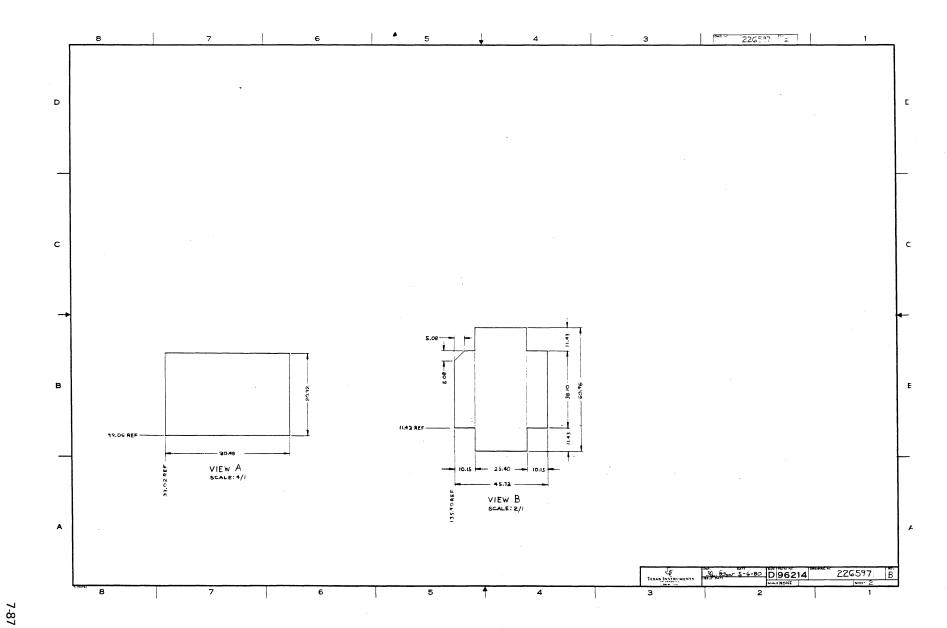

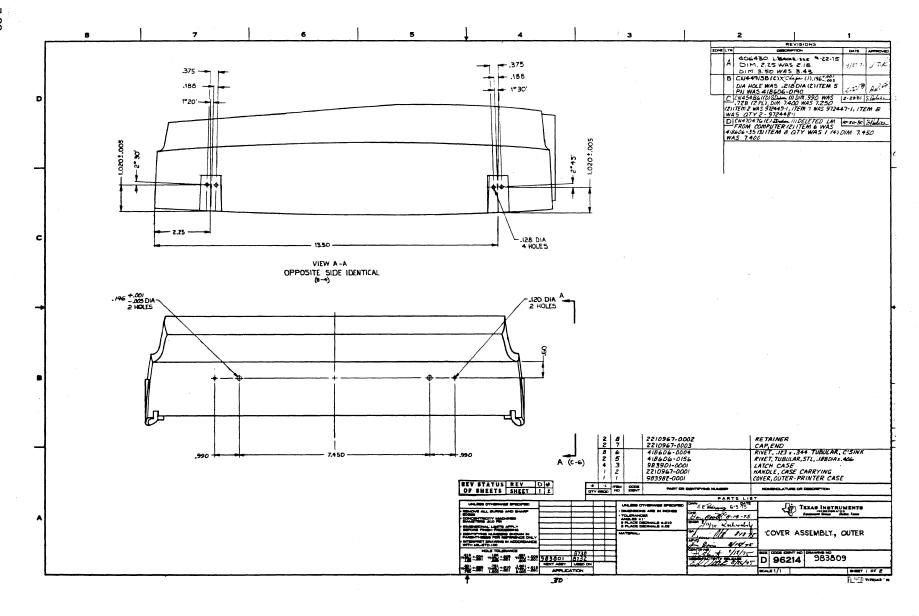

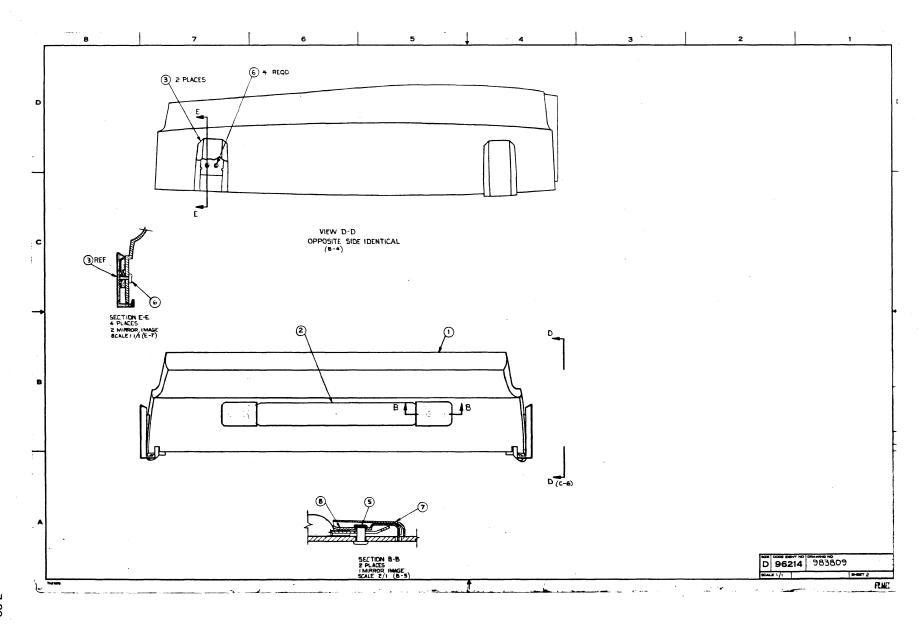

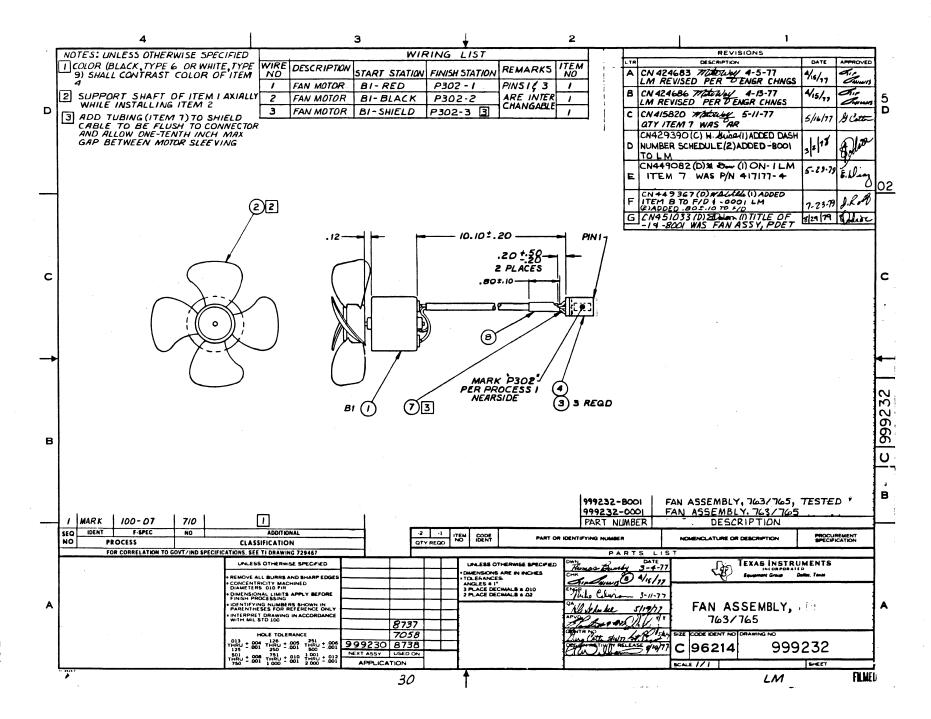

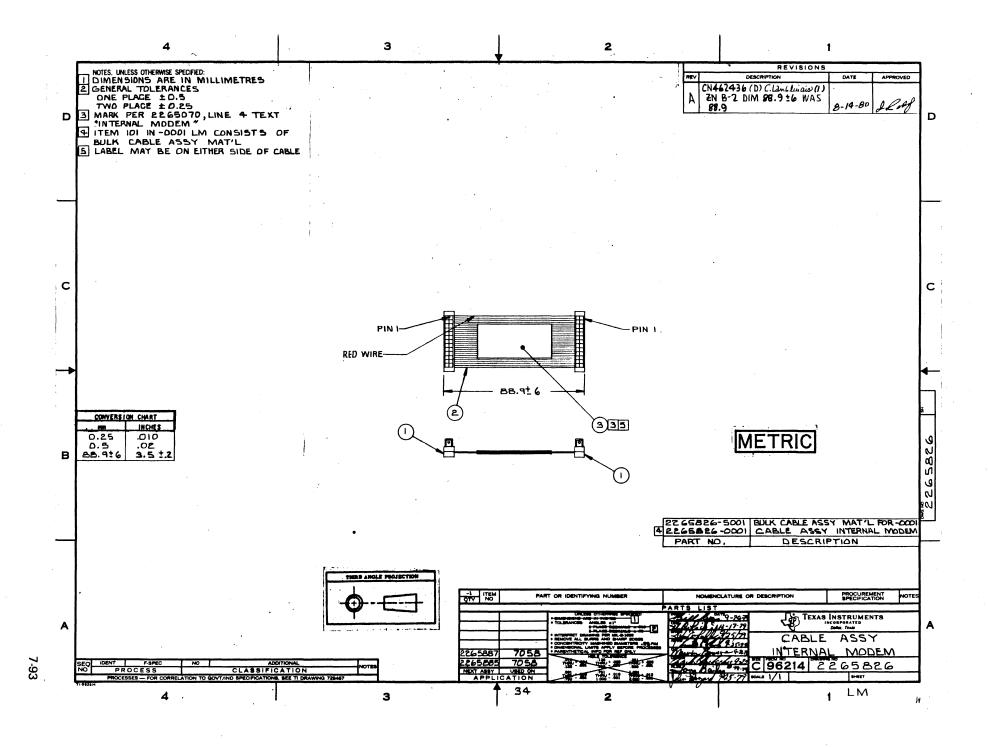

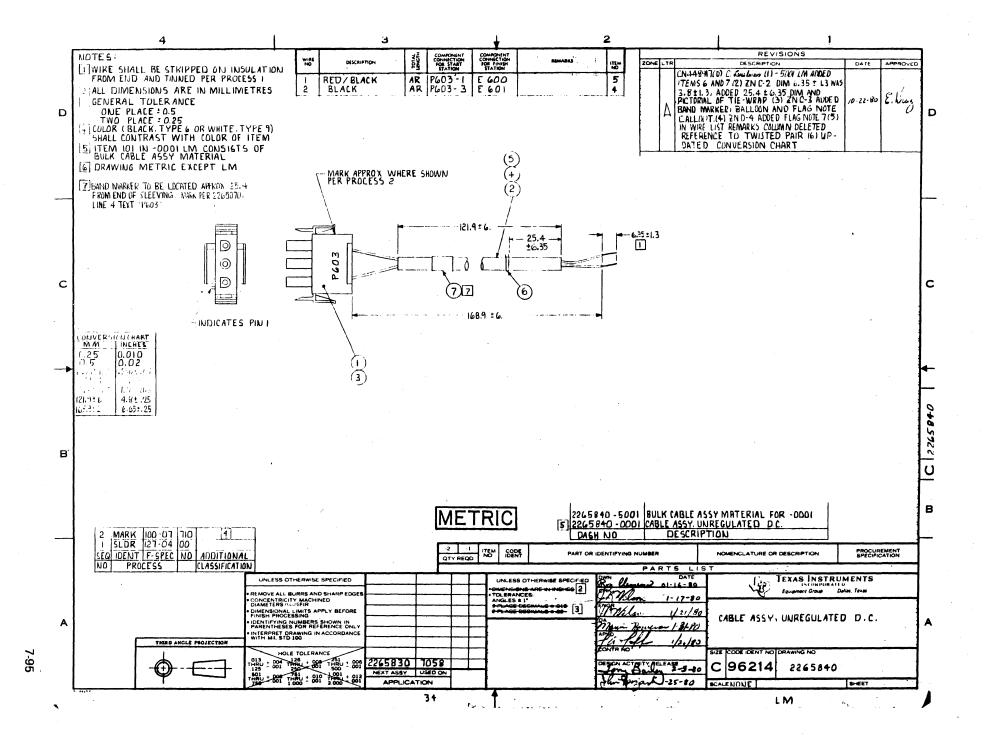

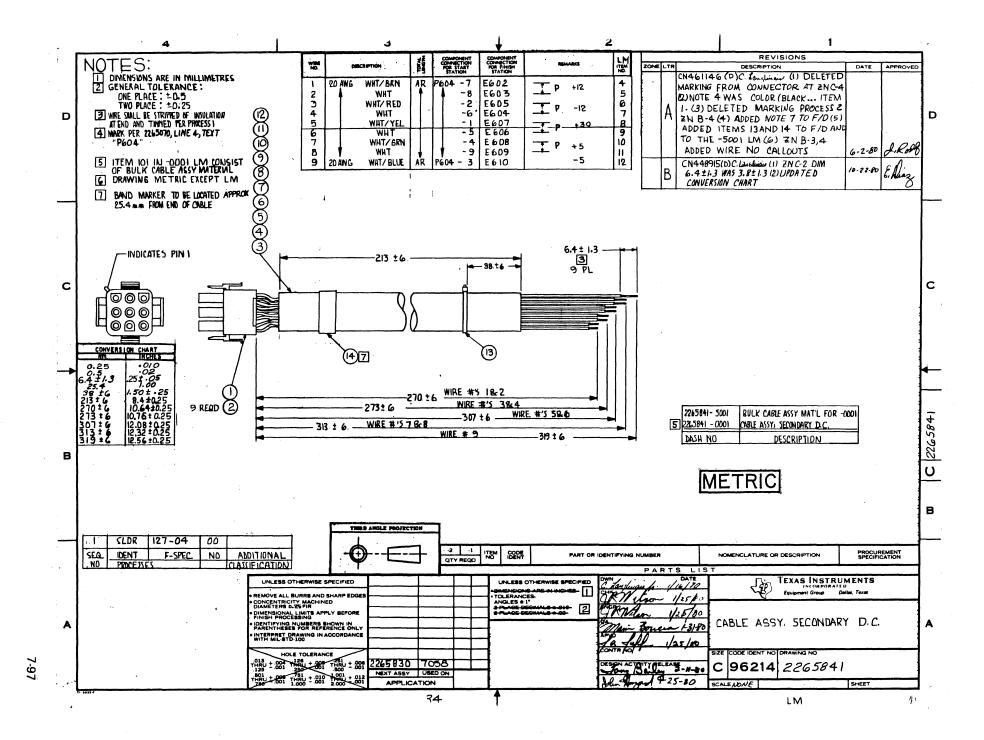

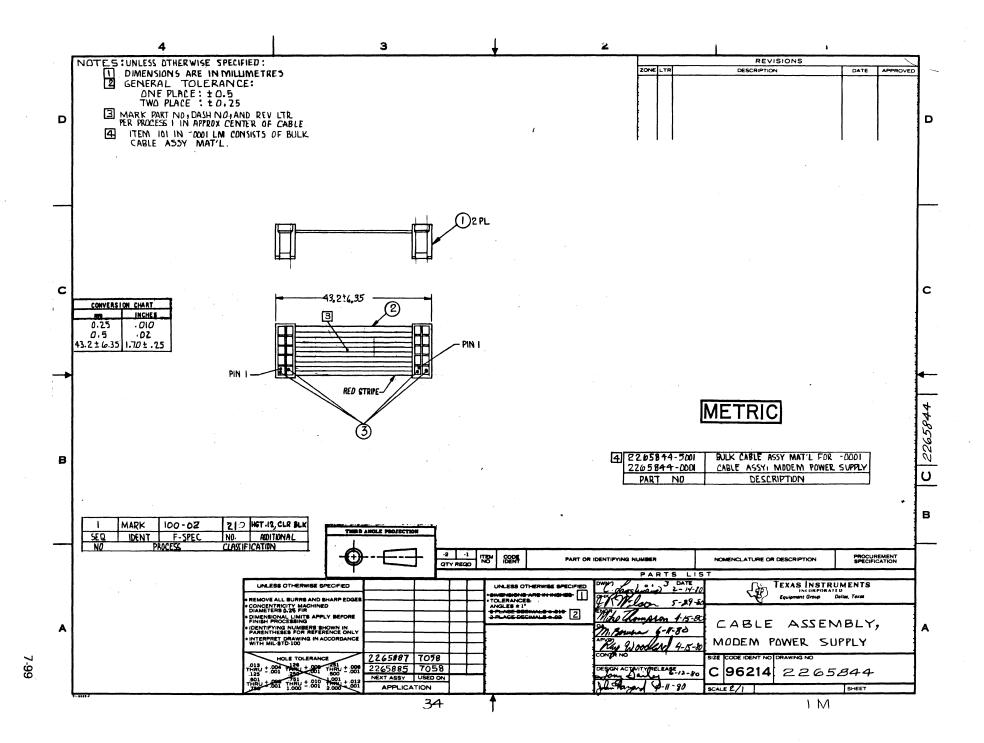

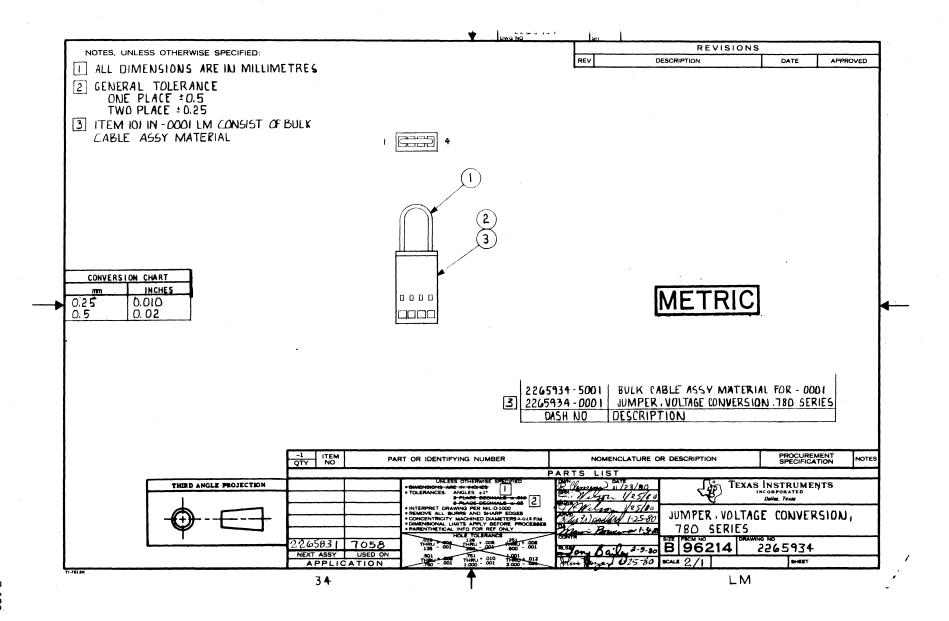

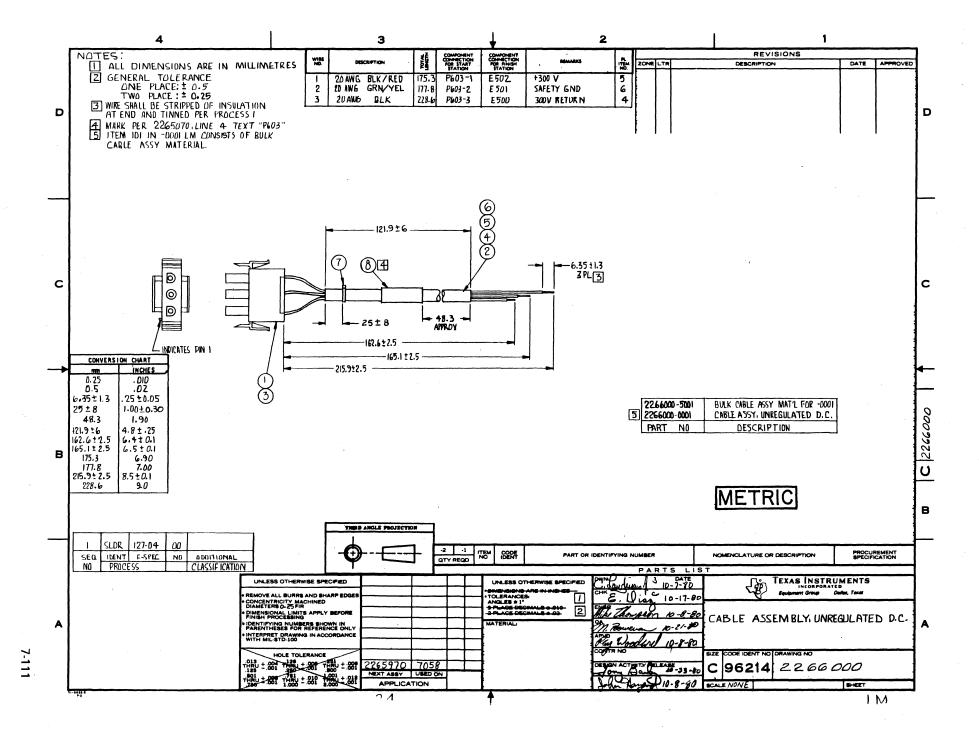

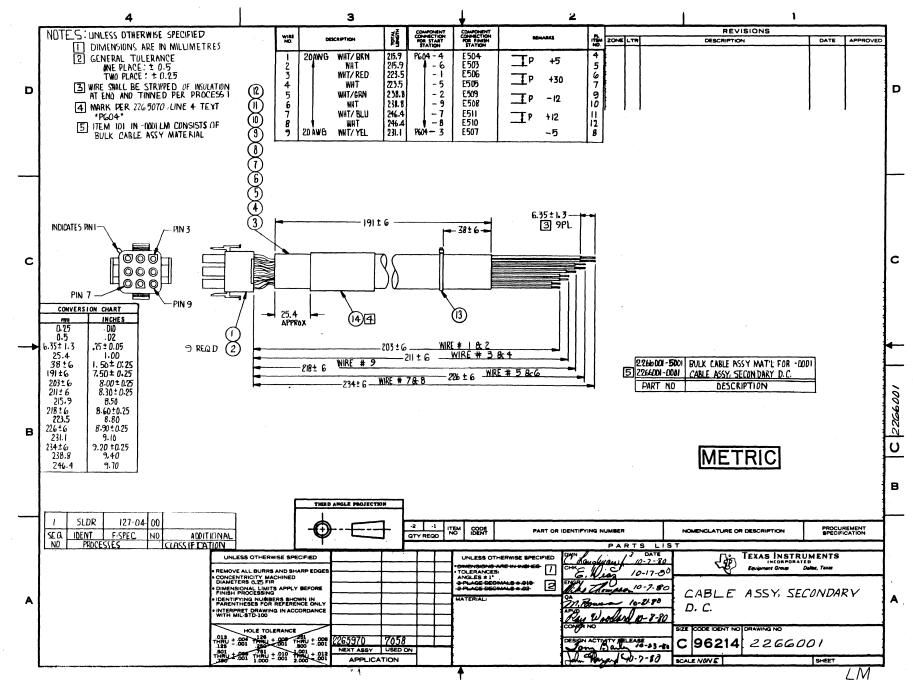

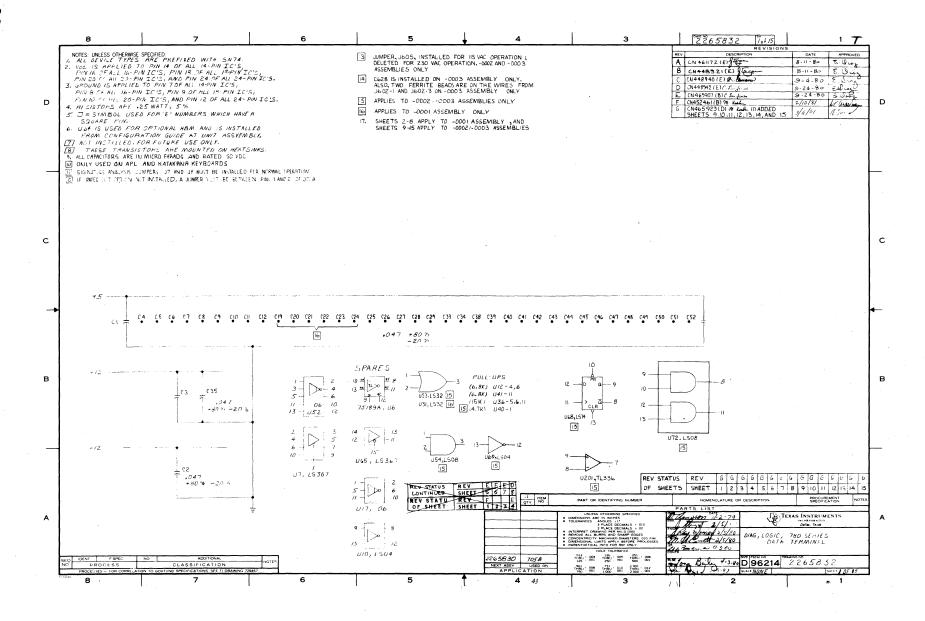

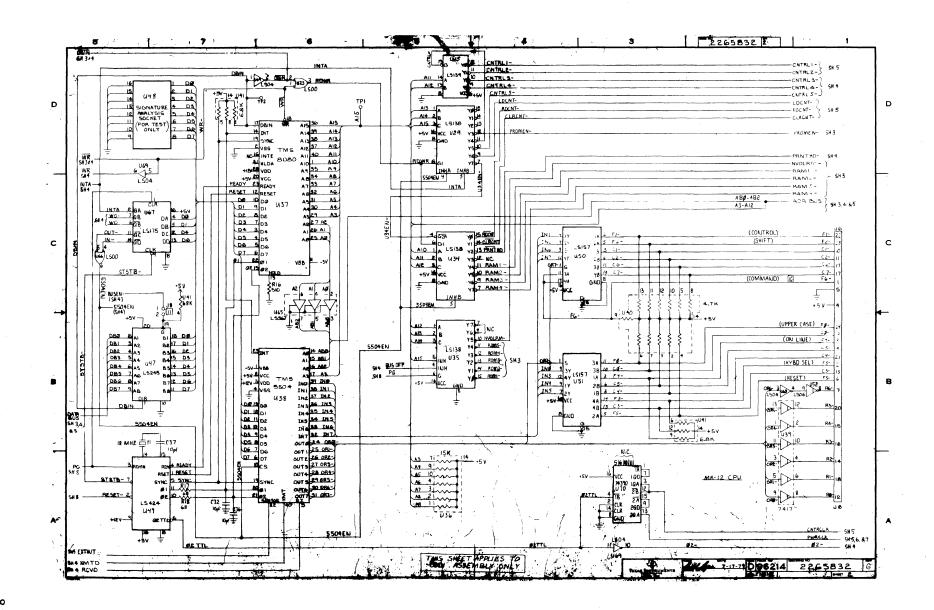

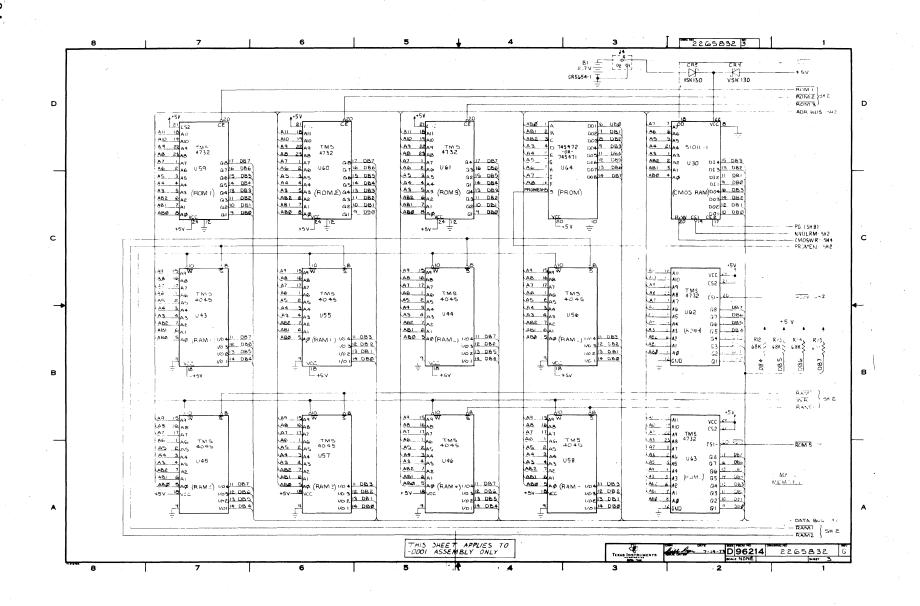

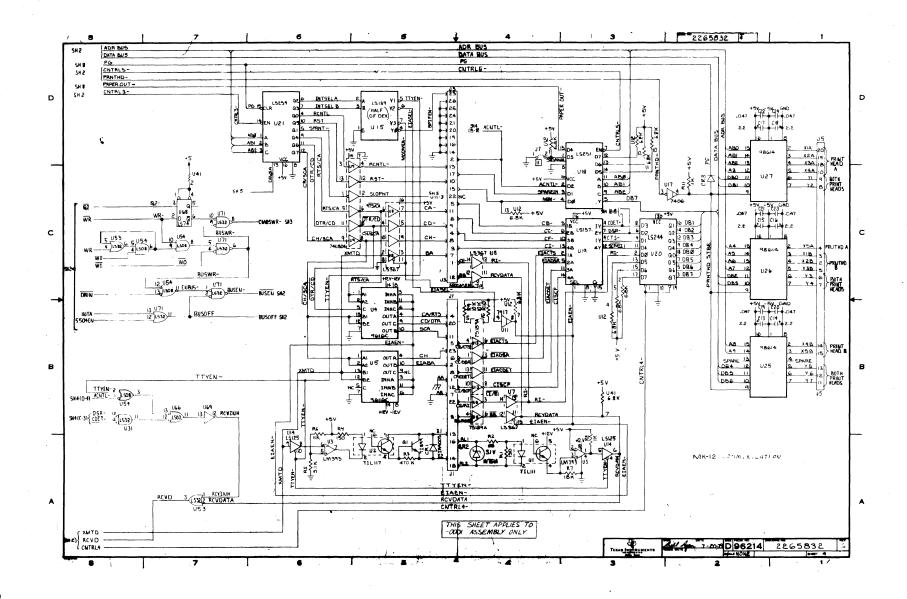

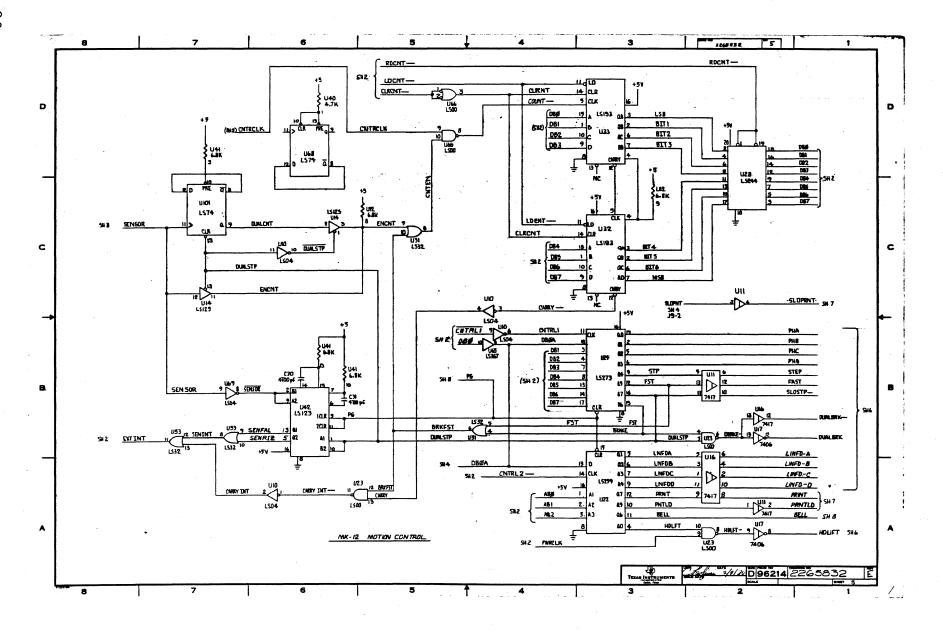

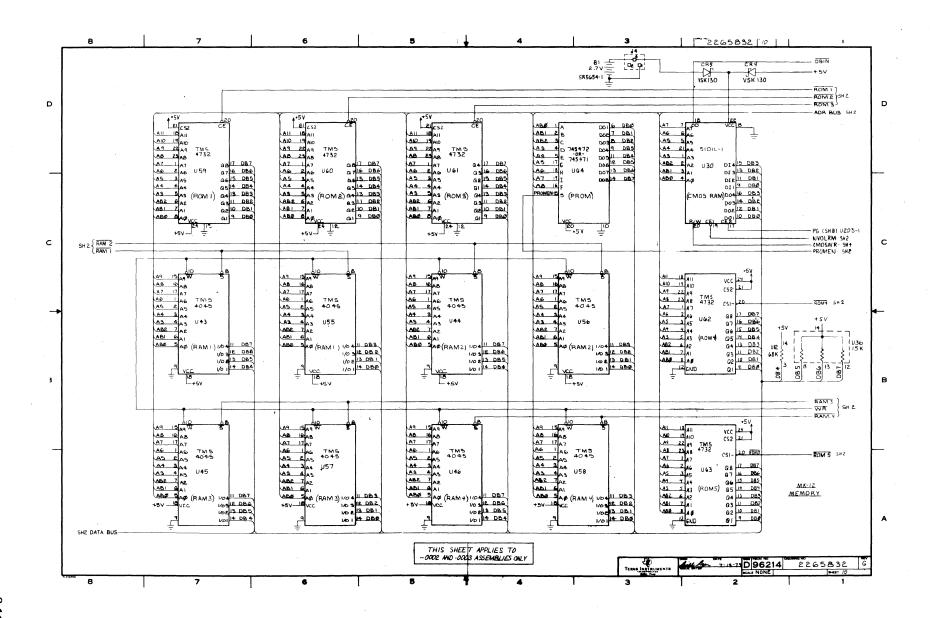

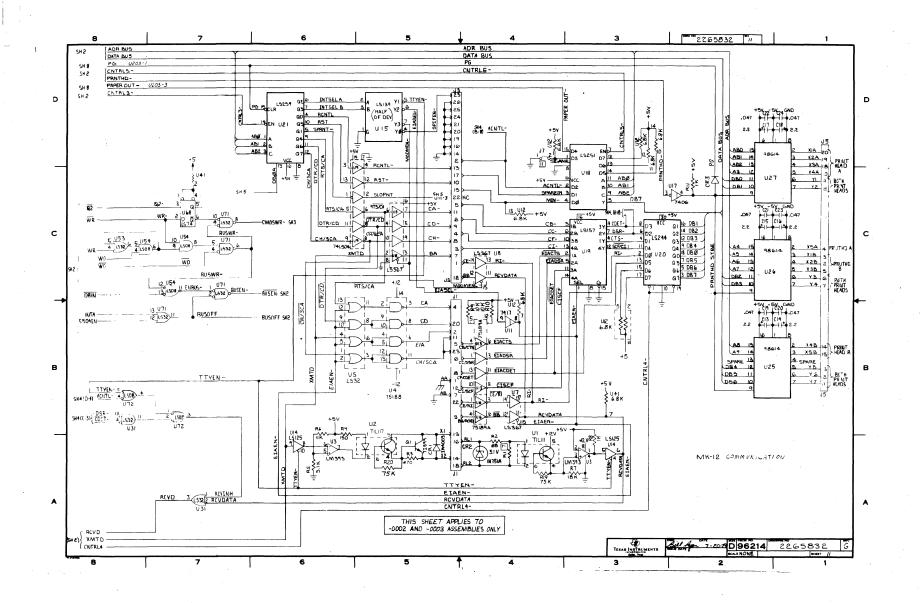

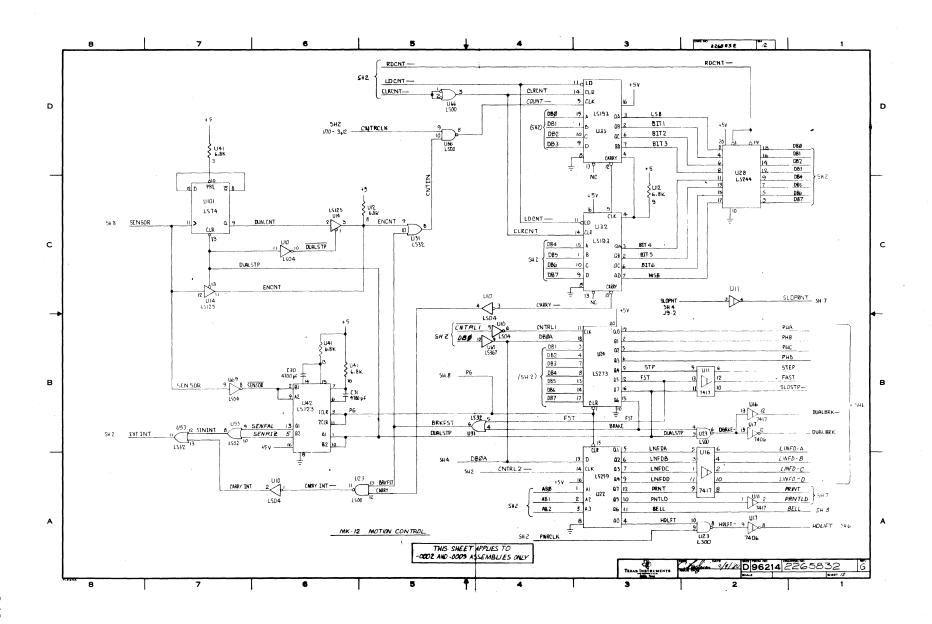

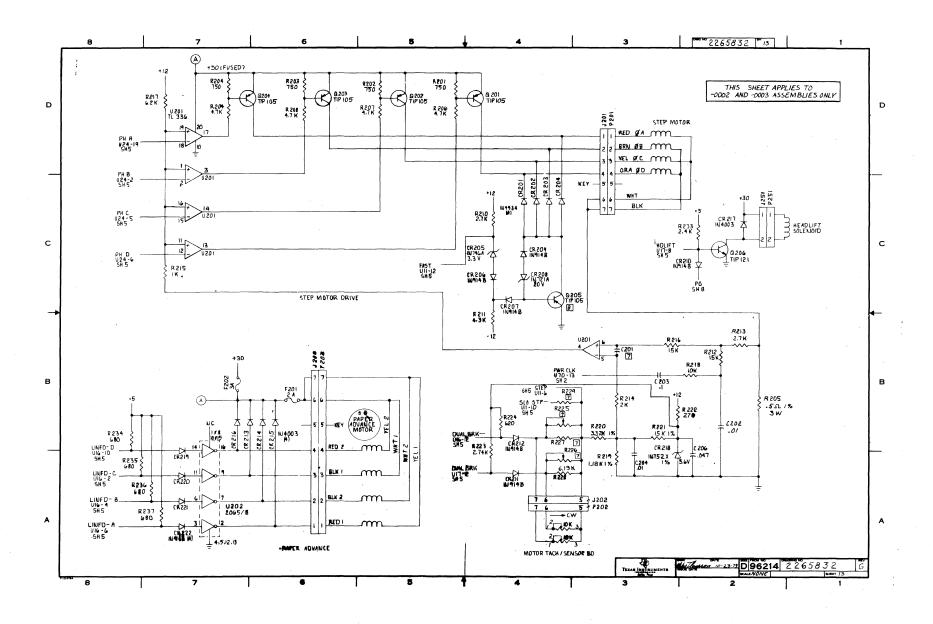

Section 7 contains assembly drawings and associated lists of material.

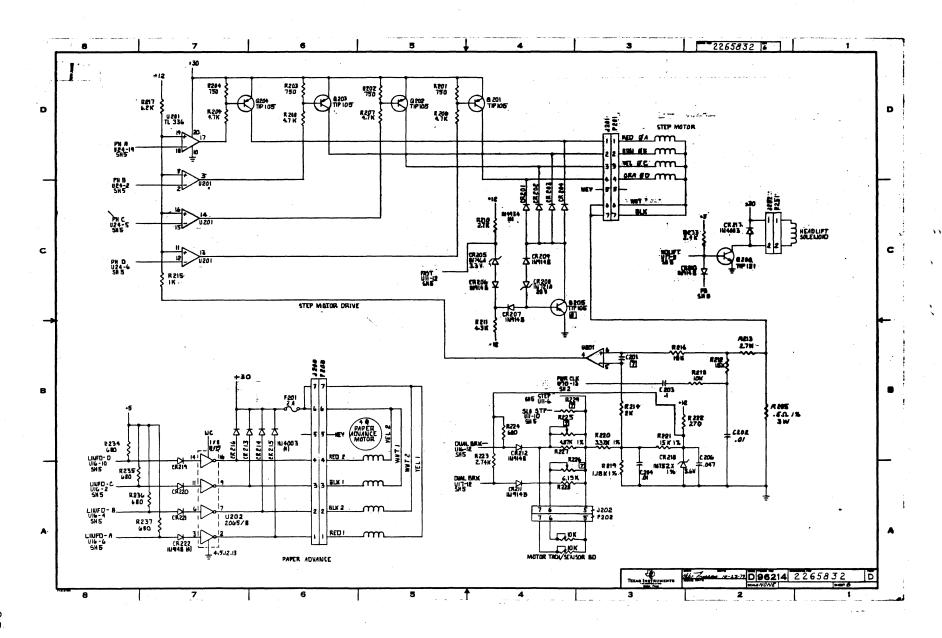

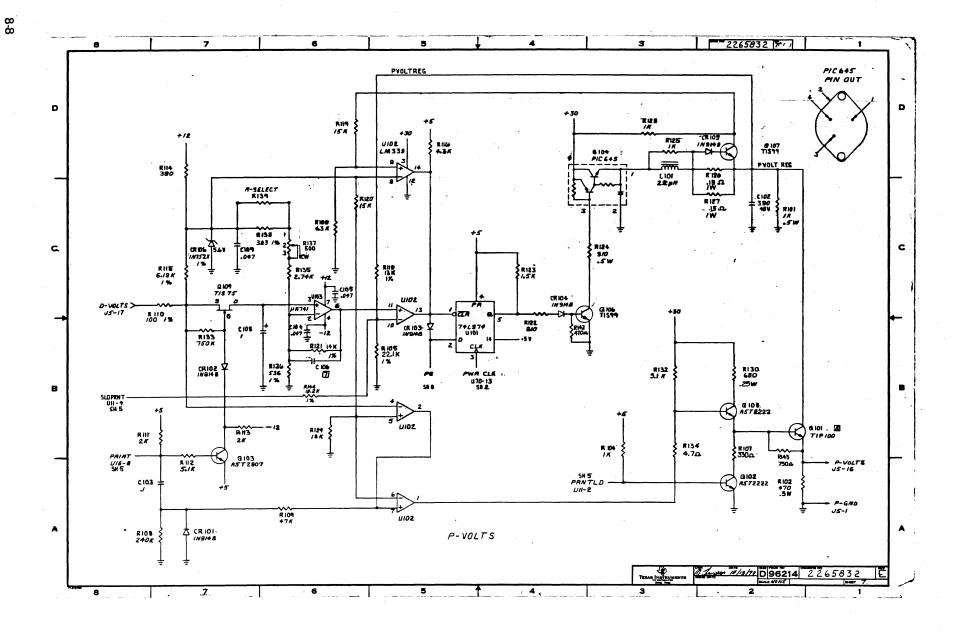

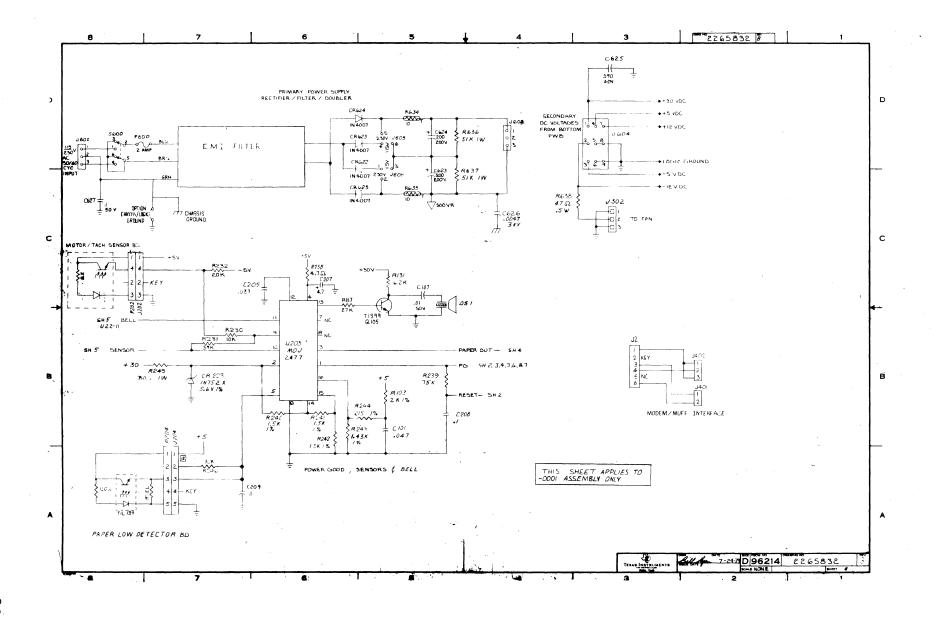

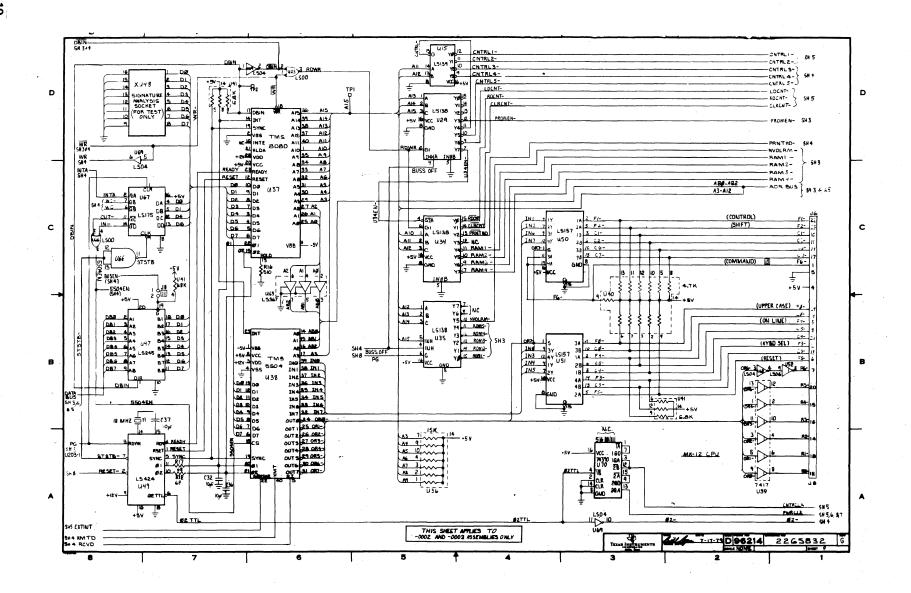

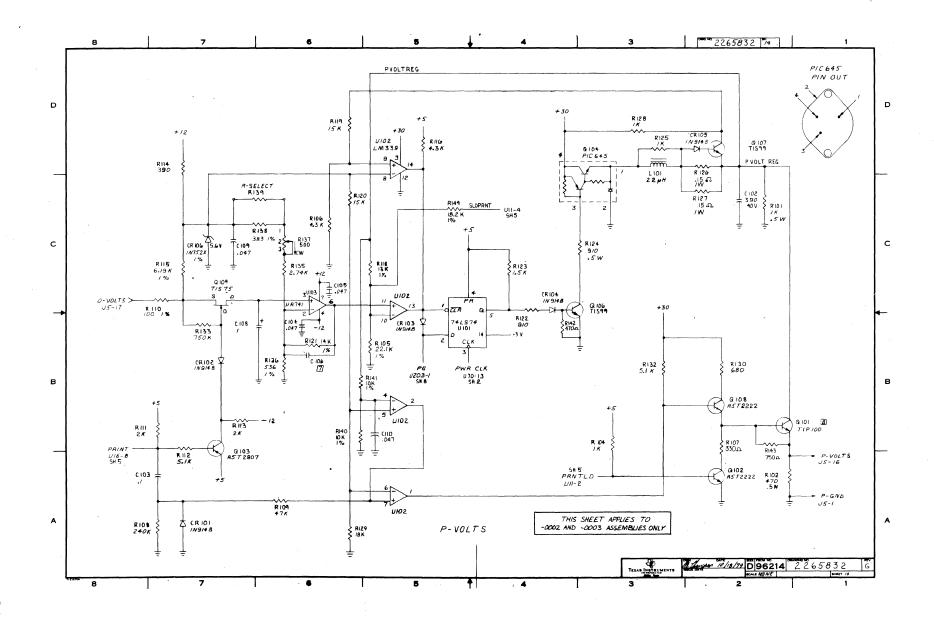

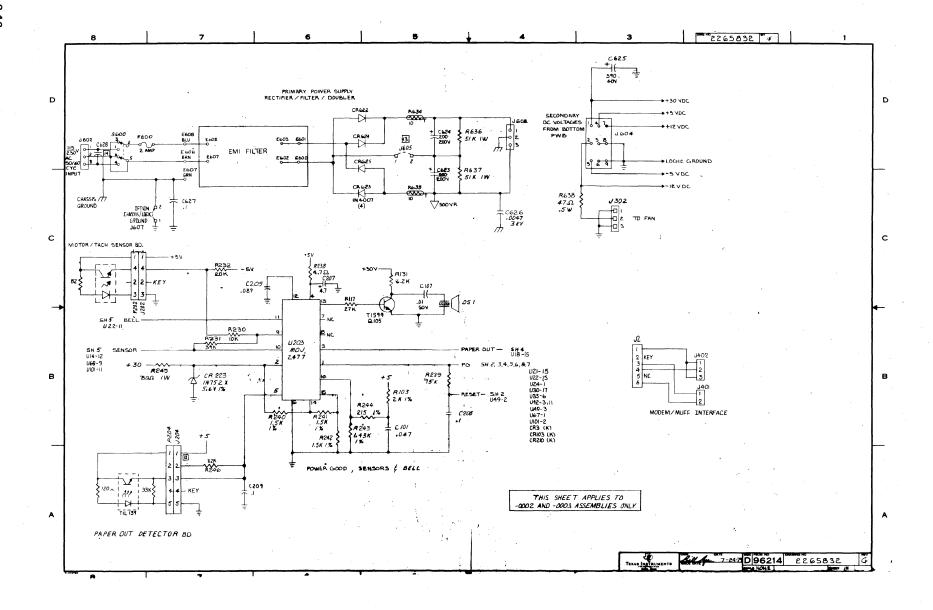

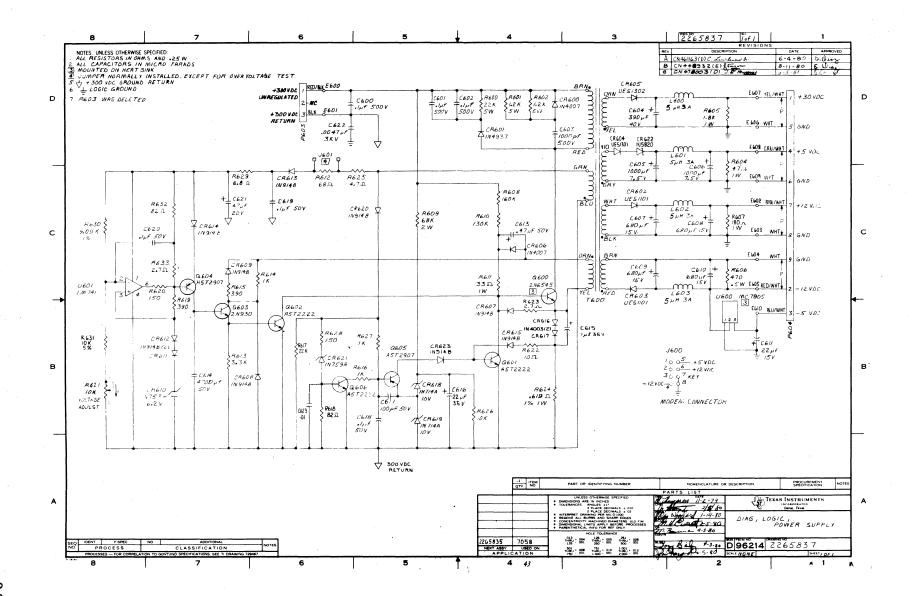

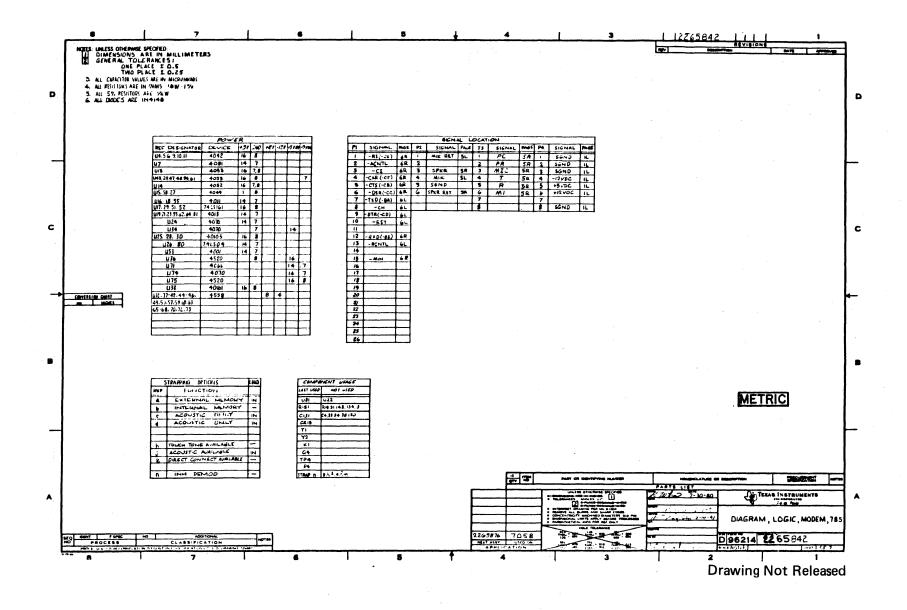

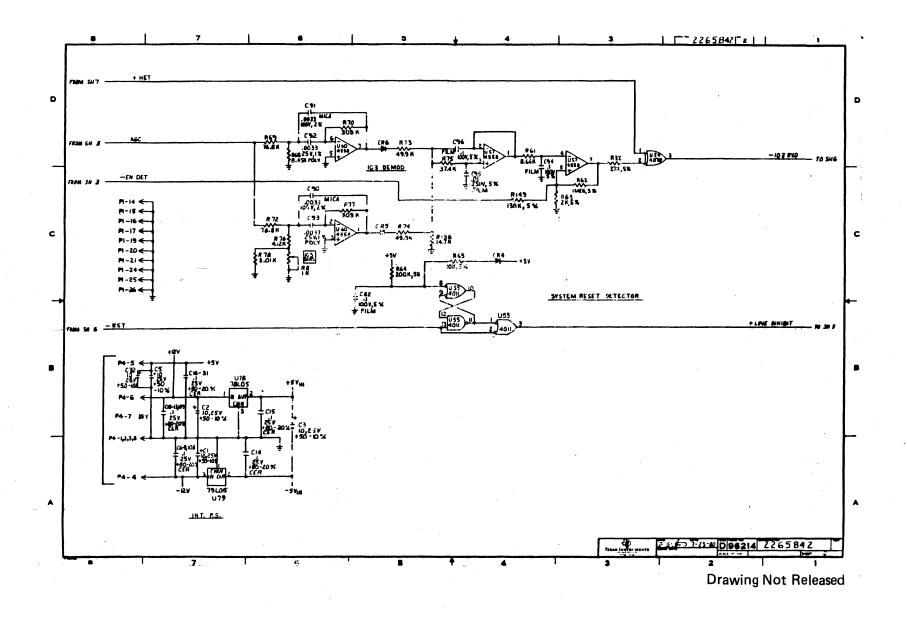

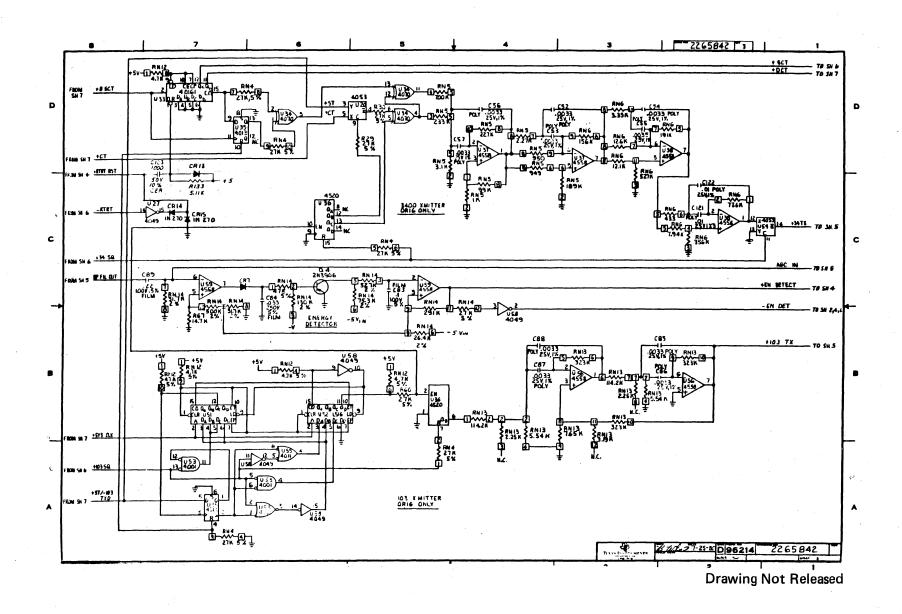

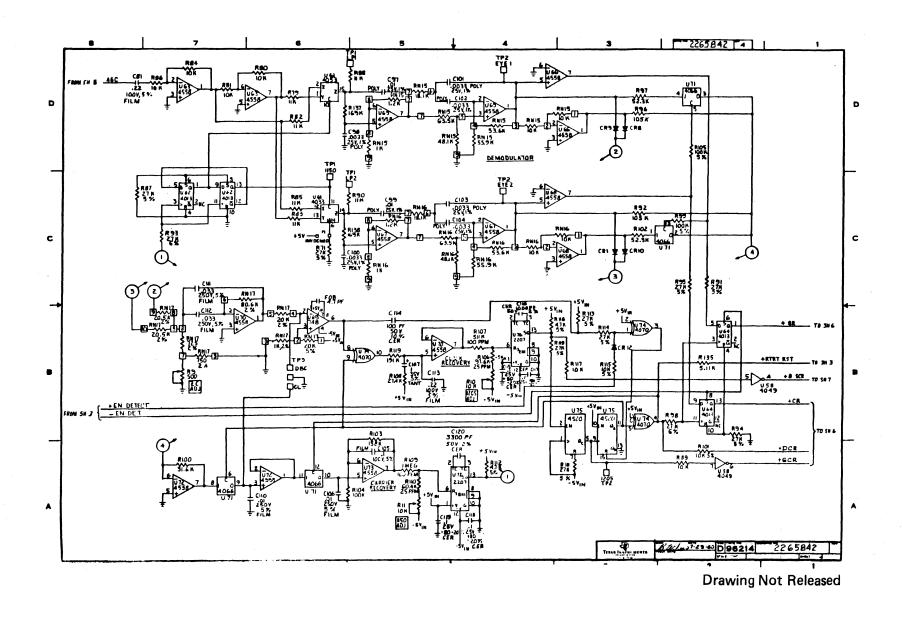

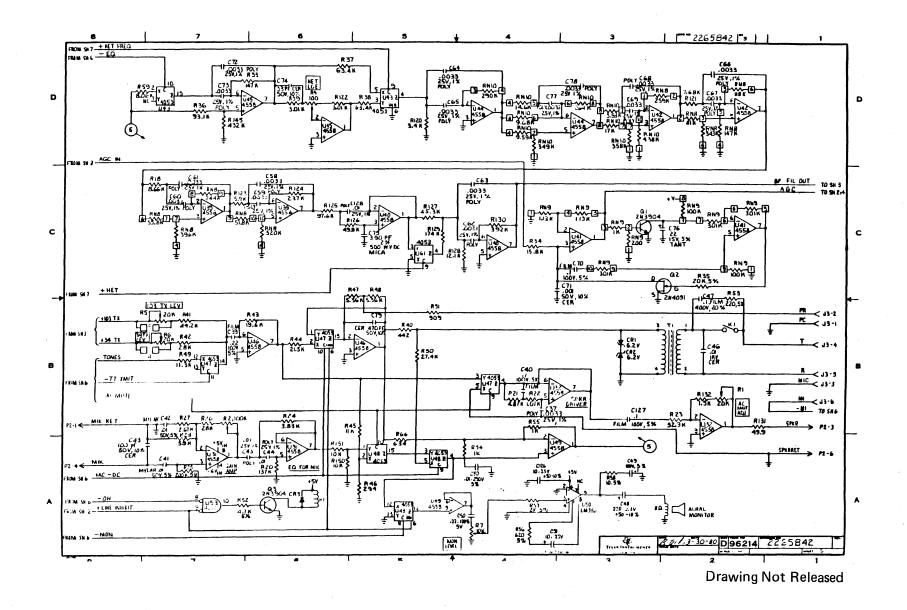

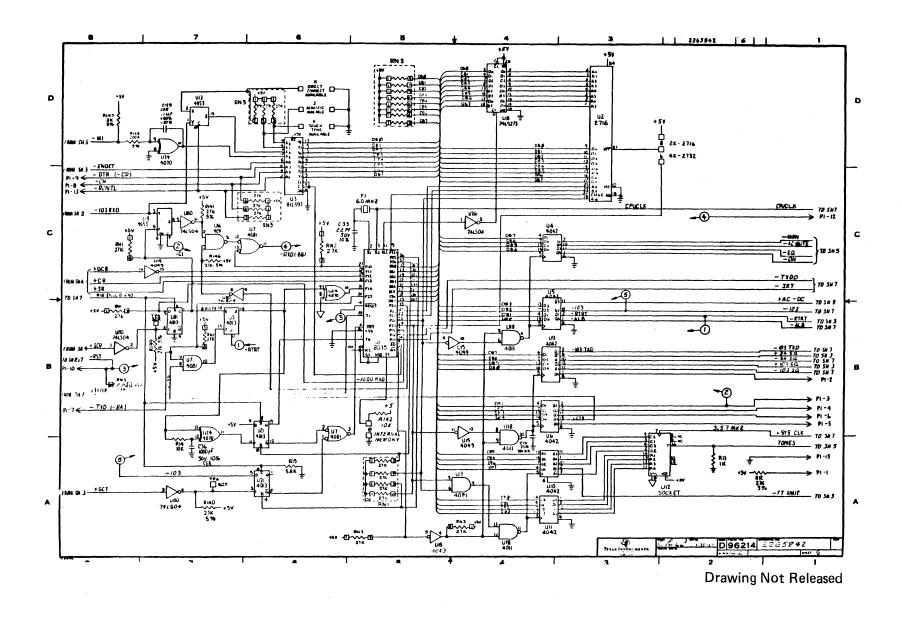

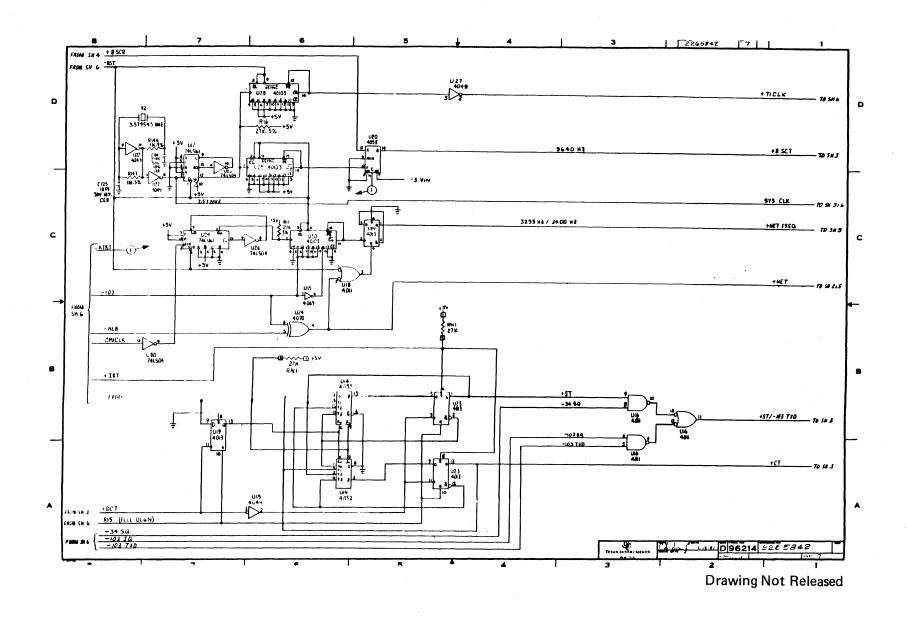

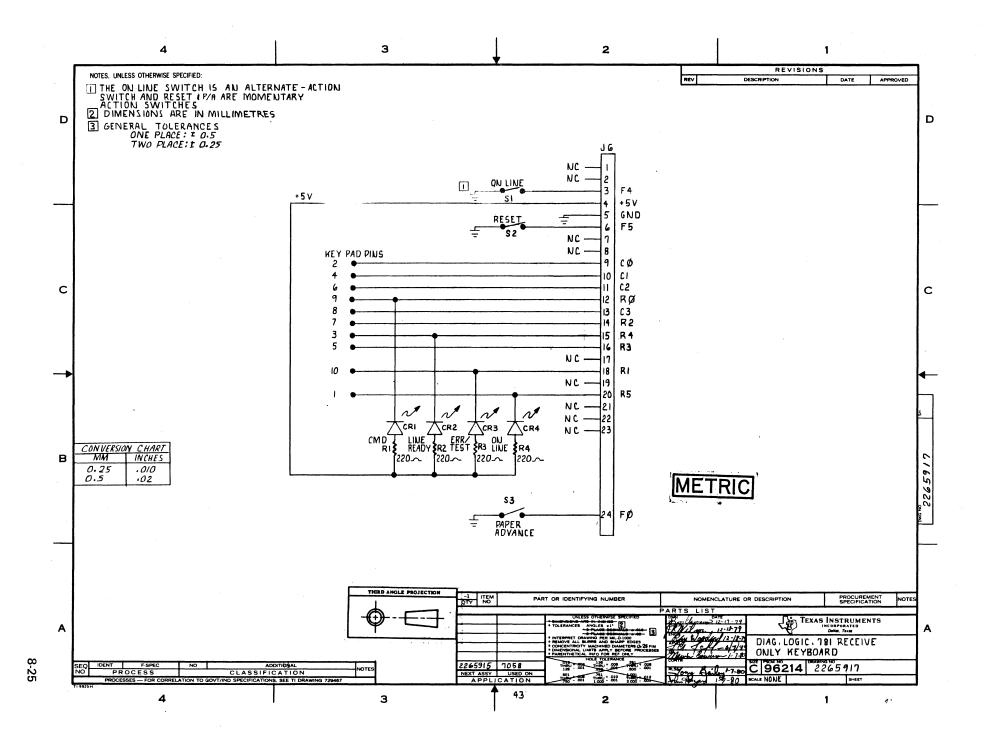

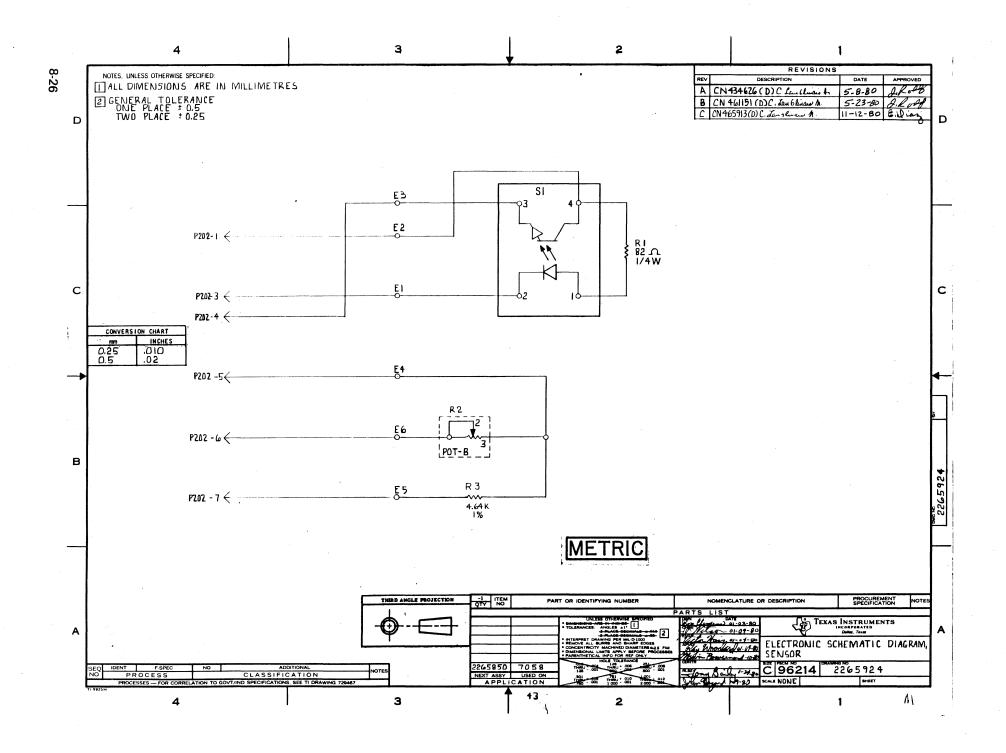

Section 8 provides the schematic diagrams.

The appendixes provide additional information on the microprocessor and I/O controller, the character sets and foreign keyboards, recommended data set options and cabling information, a glossary of signals, and quick reference cards.

### **REFERENCES**

Other TI manuals concerning the 780 Series terminals include:

- Model 781 Operating Instructions, TI Part No. 2265935-9701,

- Model 783 Operating Instructions, TI Part No. 2265936-9701,

- Model 785 Operating Instructions, TI Part No. 2265937-9701,

- Model 787 Operating Instructions, TI Part No. 2265938-9701.

The operating instructions are furnished with the respective terminal when shipped from the factory.

Operator Reference Cards which provide terminal operating information in a condensed format are attached to the inside of the paper door. Additional Quick Reference Cards can be ordered by the following TI Part Numbers:

Model 781 Operator Reference Cards, TI Part No. 2265927,

Trademark of Texas Instruments Incorporated.

- Model 783 Operator Reference Cards, TI Part No. 2265941,

- Model 785 Operator Reference Cards, TI Part No. 2265942,

- Model 787 Operator Reference Cards, TI Part No. 2265943.

# **USER'S RESPONSE**

If you have corrections or suggestions to improve this manual, please fill out the User's Response sheet found in the back of this manual. Simply remove the sheet, add your comments, fold and mail (no postage is necessary when mailed in the United States). We appreciate your comments and may contact you, if appropriate, to answer any questions you may pose.

# **Table of Contents**

| Section | Title                     | Page  | Section | Title Page                       |

|---------|---------------------------|-------|---------|----------------------------------|

| 1       | Equipment Description     |       | 3.2     | Operator Interface 3-1           |

|         |                           |       | 3.2.1   | KSR Operator's Panel 3-1         |

| 1.1     | Introduction              | . 1-1 | 3.2.2   | RO Operator's Panel 3-6          |

| 1.2     | General Description       |       | 3.3     | Terminal Configuration 3-7       |

| 1.3     | 780 Series Data Terminals | . 1-1 | 3.3.1   | Configuration Entry 3-7          |

| 1.3.1   | Model 781                 | . 1-1 | 3.3.2   | Configuration Report 3-11        |

| 1.3.2   | Model 783                 | . 1-2 | 3.4     | Operating Status 3-11            |

| 1.3.3   | Model 785                 | . 1-2 | 3.4.1   | Operating Error Codes 3-12       |

| 1.3.4   | Model 787                 | . 1-2 | 3.4.2   | Audible Status 3-13              |

| 1.4     | Options                   | . 1-3 | 3.4.3   | Automatically Printed            |

| 1.5     | Physical Dimensions       | . 1-4 |         | Status Reports 3-13              |

| 1.5.1   | Size                      | . 1-4 | 3.4.4   | Online Reporting 3-14            |

| 1.5.2   | Weight                    | . 1-4 | 3.4.5   | Operator Reference Cards 3-14    |

| 1.6     | Environmental Limits      | . 1-4 | 3.5     | Control Functions 3-14           |

| 1.6.1   | Non-Operating Environment | . 1-4 | 3.6     | Self-Tests 3-15                  |

| 1.6.2   | Operating Environment     | . 1-5 | 3.6.1   | Power-Up Diagnostics 3-15        |

| 1.7     | Specifications            | . 1-5 | 3.6.2   | Maintenance Diagnostics 3-15     |

| 1.7.1   | Printer                   | . 1-5 | 3.7     | Reports 3-15                     |

| 1.7.2   | Keyboard                  | . 1-5 |         | <u> </u>                         |

| 1.7.3   | Modem                     | . 1-6 | 4       | Communications                   |

| 2       | Equipment Installation    |       | 4.1     | Introduction 4-1                 |

|         |                           |       | 4.1.1   | EIA Transmission Rates           |

| 2.1     | Preliminary Checkout      |       | •       | and Distortion 4-1               |

| 2.2     | Power Connection          |       | 4.1.2   | EIA Interface Signal Levels 4-1  |

| 2.3     | Communications Interface  |       | 4.1.3   | Transmission Codes 4-2           |

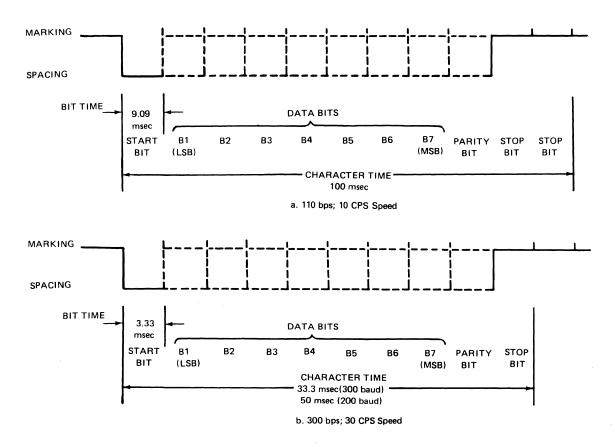

| 2.3.1   | EIA Operation             | . 2-4 | 4.1.4   | Character Structure 4-3          |

| 2.3.2   | TTY (DC) Current Loop     |       | 4.1.5   | EIA Communications               |

|         | Operation                 |       |         | Interface 4-4                    |

| 2.3.3   | Internal Modem Operation  | . 2-5 | 4.1.6   | External Data Set Capability 4-5 |

|         |                           |       | 4.2     | Communications Modes 4-5         |

| 3       | Operation                 |       | 4.2.1   | Full-Duplex Data Set             |

|         |                           |       |         | Operation 4-5                    |

| 3.1     | Operating Modes           |       | 4.2.2   | Half-Duplex Data Set             |

| 3.1.1   | LOCAL                     |       |         | Operation 4-6                    |

| 3.1.2   | ONLINE                    |       | 4.2.3   | Half Duplex with Reverse         |

| 3.1.3   | COMMAND                   | . 3-1 |         | Channel Data Set Operation 4-7   |

# **TABLE OF CONTENTS (Concluded)**

| Section | Title                                      | Page  | Section | Title Page                           |

|---------|--------------------------------------------|-------|---------|--------------------------------------|

| 4.2.4   | Half-Duplex Data Set Operation with No LTA | . 4-7 | 6       | Maintenance                          |

| 4.2.5   | Non-Data Set Operation                     |       | 6.1     | Introduction                         |

| 4.2.6   | DC Current Loop Operation                  |       | 6.2     | Self-Tests 6-1                       |

| 4.3     | Communications Features                    |       | 6.2.1   | Power-Up Diagnostics Tests 6-1       |

| 4.3.1   | Answerback Memory (ABM)                    | . 4-8 | 6.2.2   | Maintenance Tests 6-1                |

| 4.3.2   | Automatic Operation Control                |       | 6.2.3   | Test Procedure Instructions 6-1      |

| 4.3.3   | Communication Line BREAK                   |       | 6.3     | Reports 6-4                          |

| 4.3.4   | Communication Line                         |       | 6.3.1   | CONFIG Report 6-5                    |

|         | READY/BUSY                                 |       | 6.3.2   | ERROR Report 6-5                     |

|         | Status Reporting                           | 4-11  | 6.3.3   | CR Report 6-6                        |

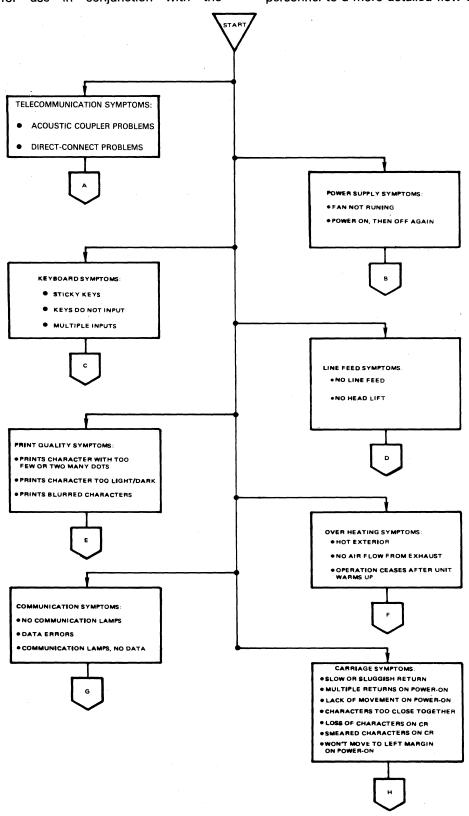

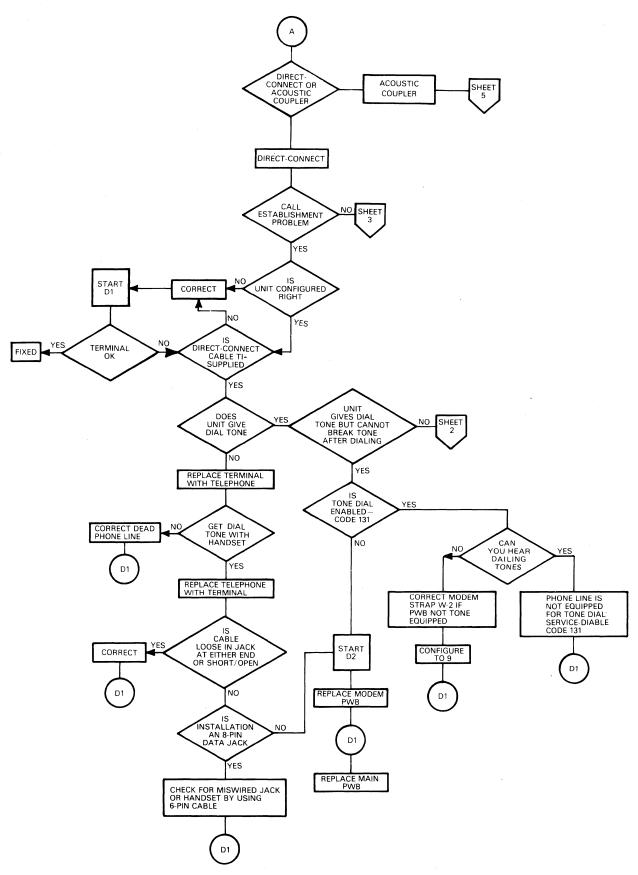

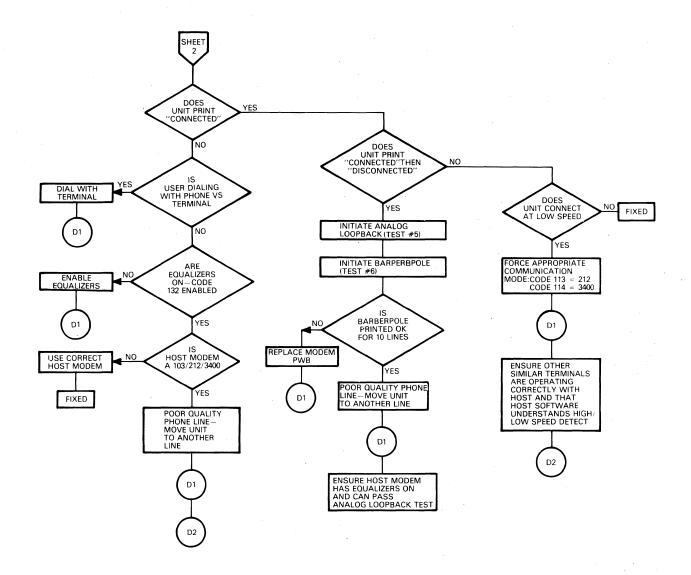

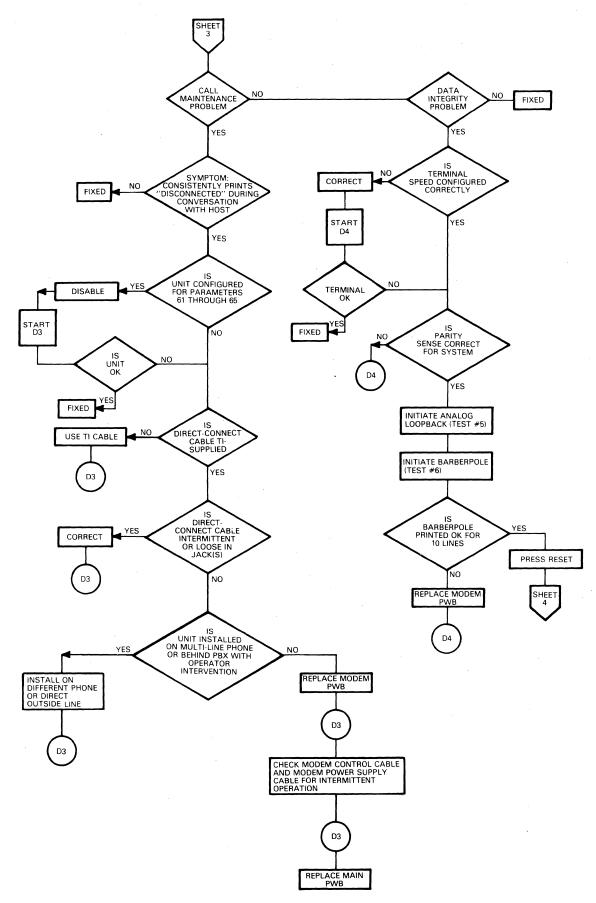

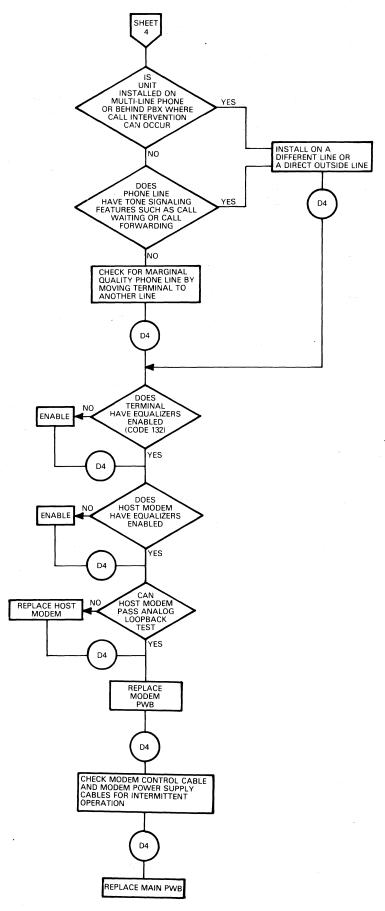

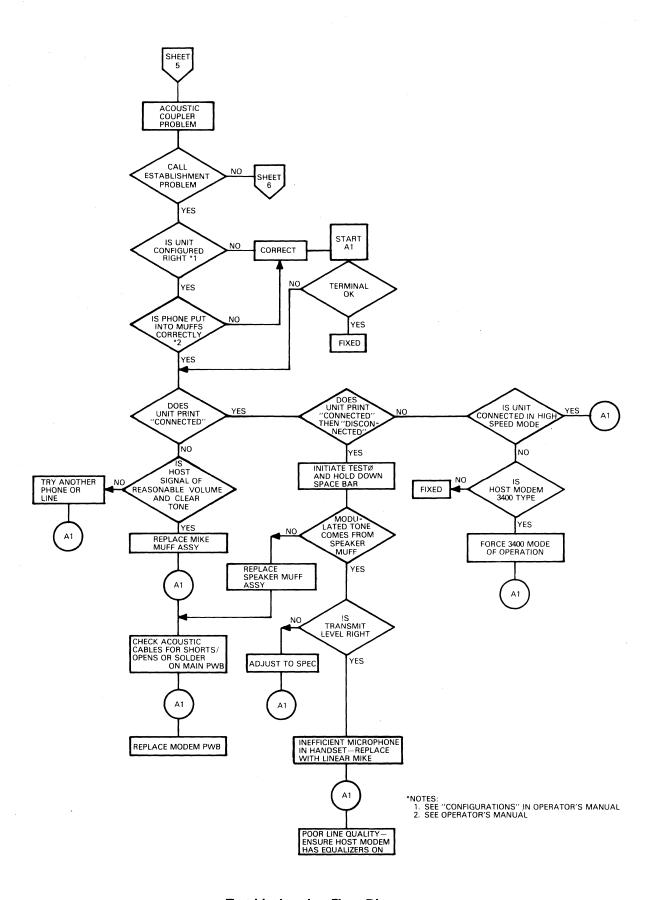

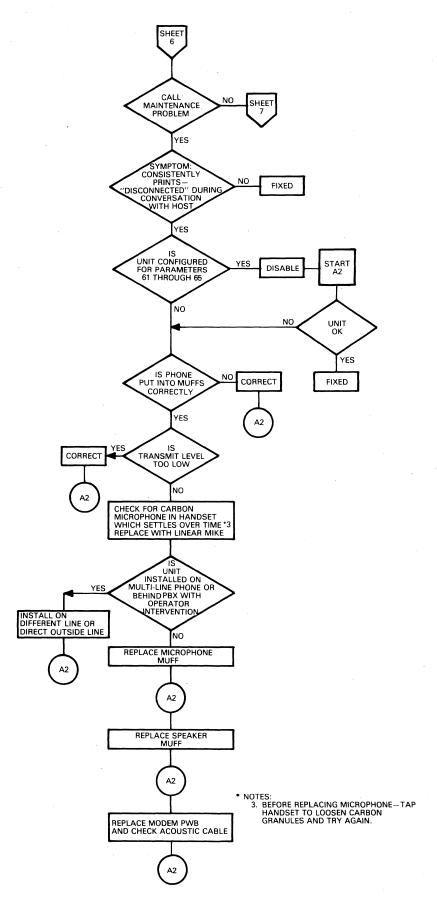

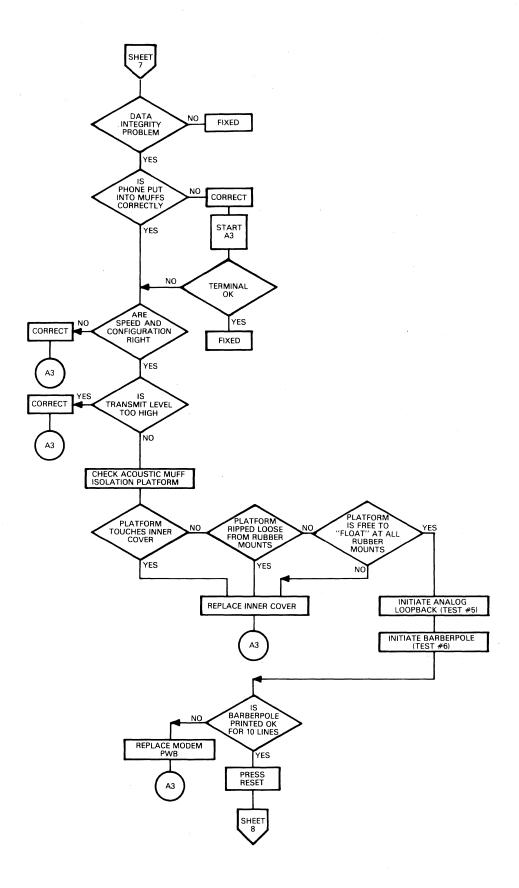

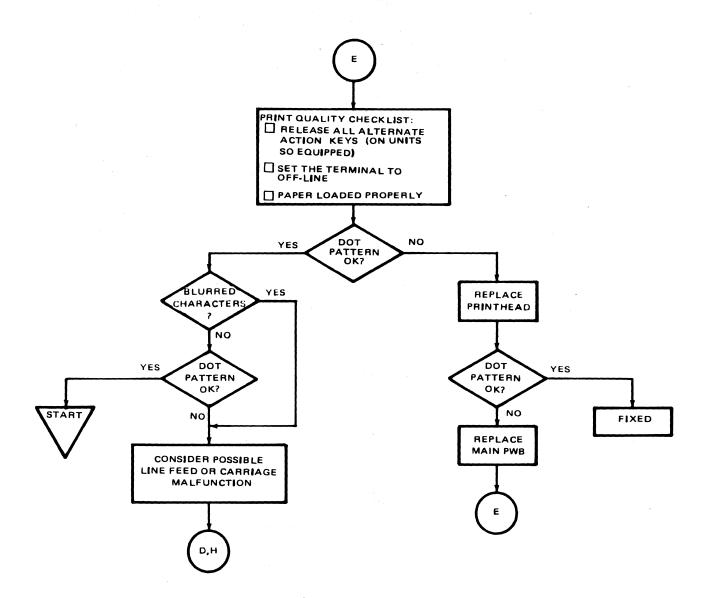

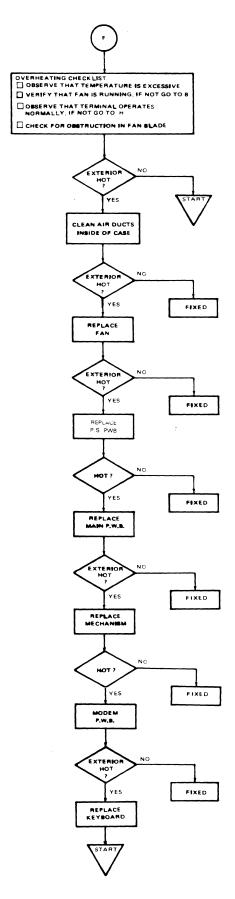

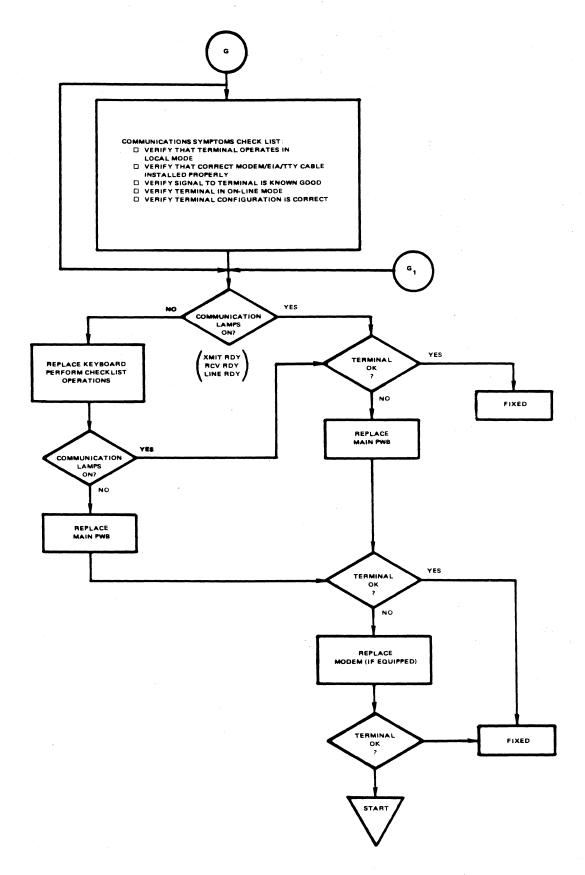

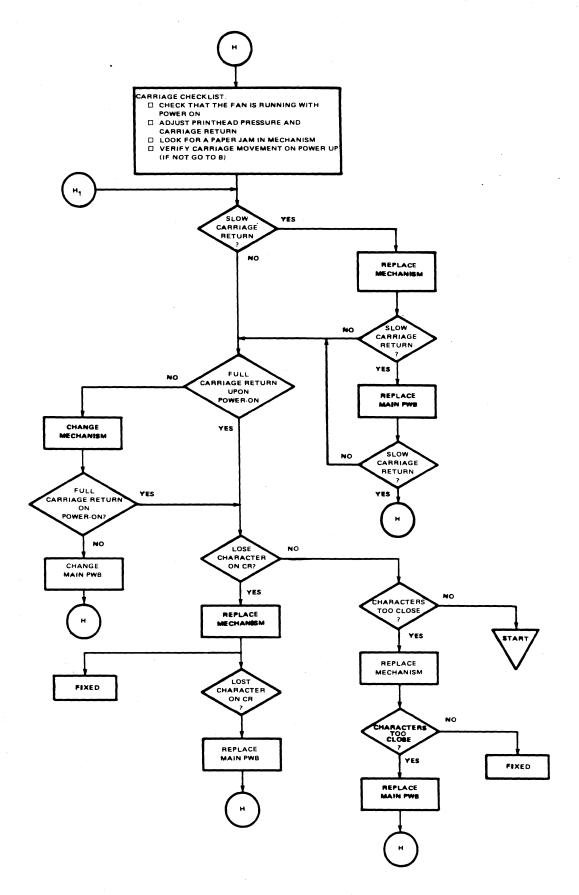

|         |                                            |       | 6.4     | Troubleshooting Flow Diagrams 6-8    |

| 5       | Theory of Operation                        |       | 6.5     | Subassembly Replacement 6-24         |

|         |                                            |       | 6.5.1   | Terminal Cover 6-24                  |

| 5.1     | Functional Description                     | . 5-1 | 6.5.2   | Printer Mechanism 6-24               |

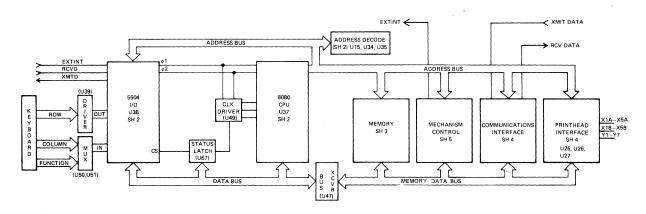

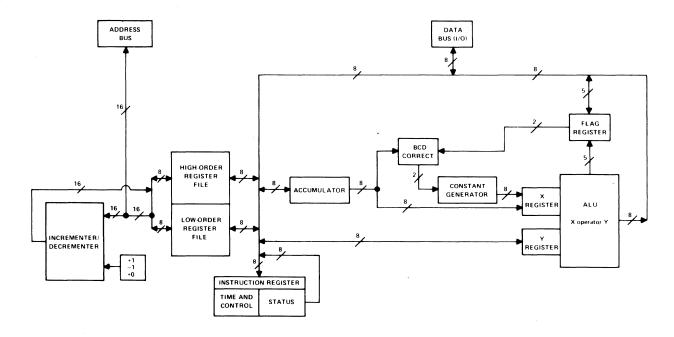

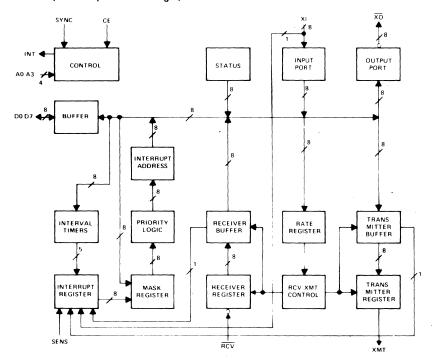

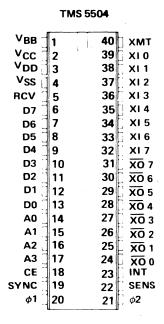

| 5.2     | Terminal Controller                        | . 5-1 | 6.5.3   | Printhead 6-26                       |

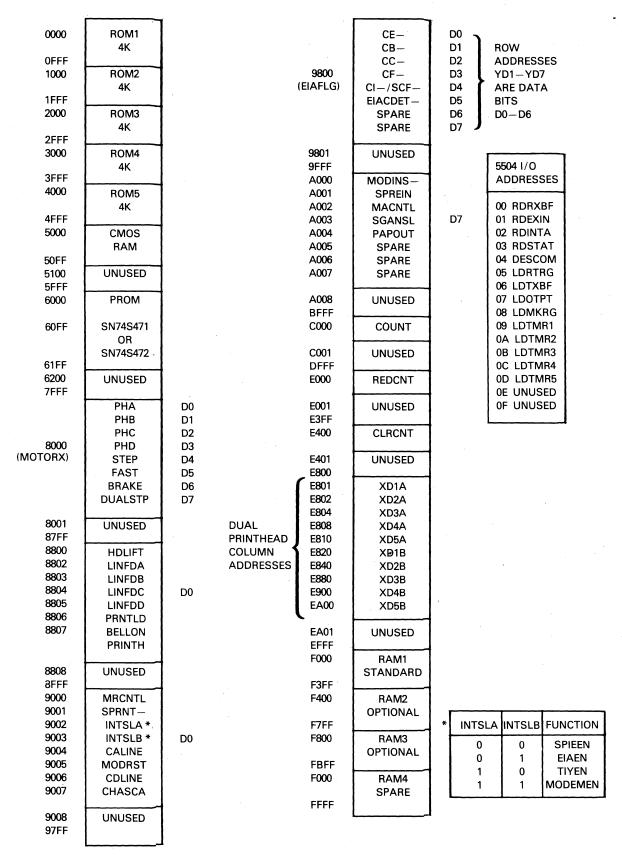

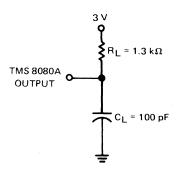

| 5.2.1   | 8080A Microprocessor                       | . 5-2 | 6.5.4   | Keyboard 6-28                        |

| 5.2.2   | TMS5504 Multifunction                      |       | 6.5.5   | Fan Assembly 6-28                    |

|         | I/O Controller                             | . 5-2 | 6.5.6   | Battery 6-30                         |

| 5.2.3   | Terminal Controller Memory                 |       | 6.5.7   | Main PWB 6-30                        |

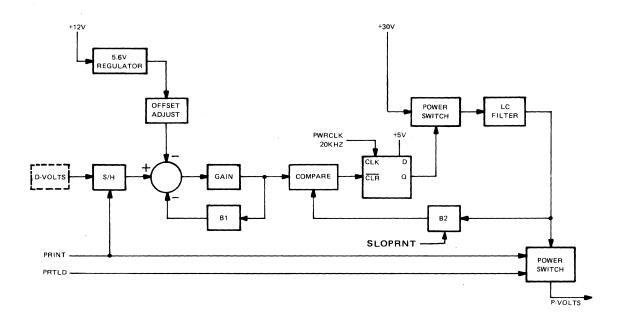

| 5.3     | Mechanism Drive Electronics                | . 5-4 | 6.5.8   | Power Supply PWB 6-30                |

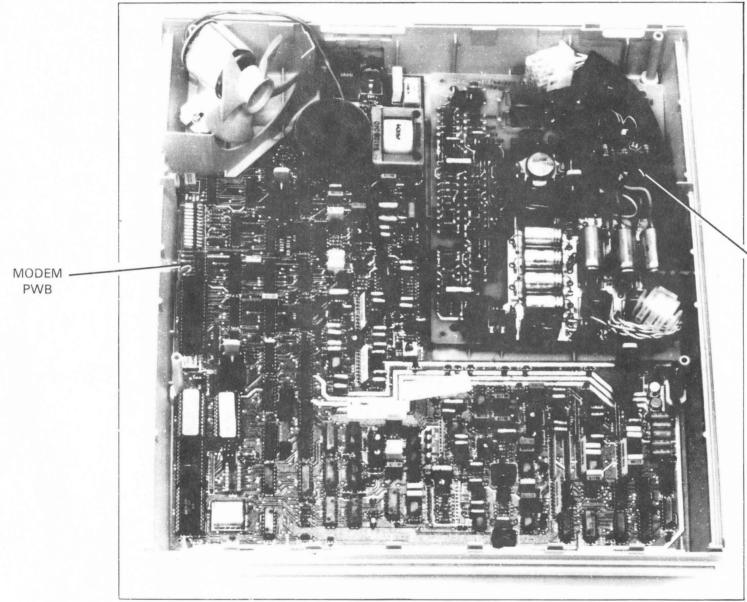

| 5.3.1   | Printhead Drive Motor                      |       | 6.5.9   | Modem PWB 6-30                       |

|         | Electronics                                |       | 6.6     | Terminal Adjustments 6-30            |

| 5.3.2   | Motion Control Electronics                 |       | 6.6.1   | Printhead Pressure Adjustment 6-33   |

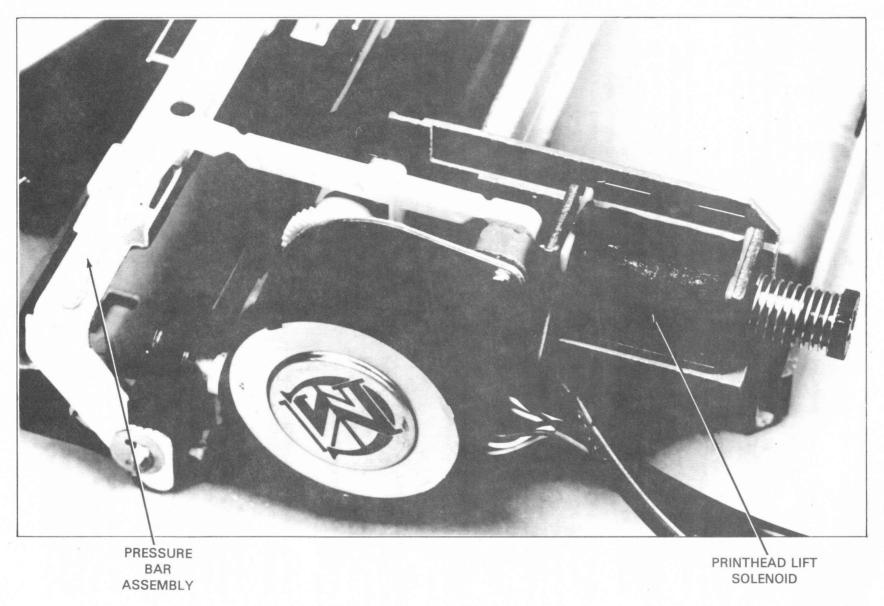

| 5.3.3   | Headlift Solenoid                          |       | 6.6.2   | Printhead Alignment 6-33             |

| 5.3.4   | Paper Advance                              |       | 6.6.3   | Print Image Contrast 6-33            |

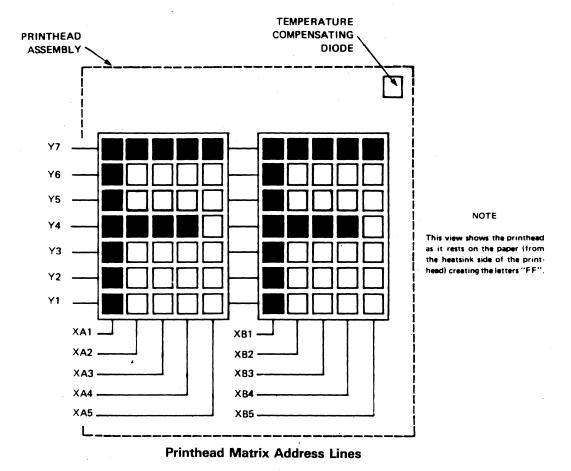

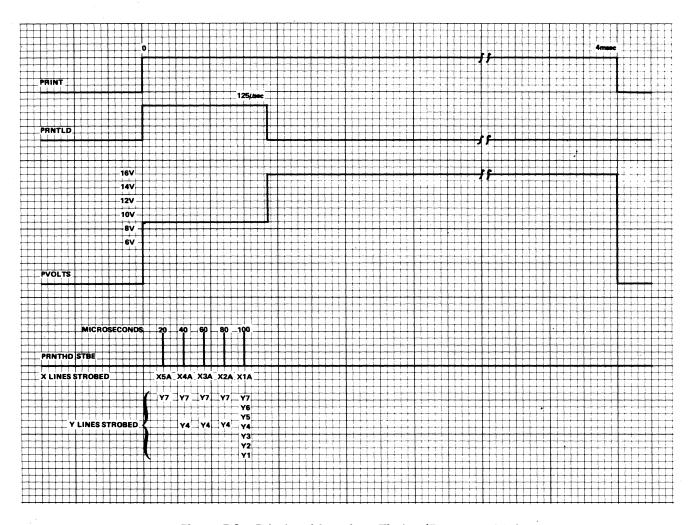

| 5.4     | Printhead System                           |       | 6.6.4   | Transmit Level Adjustment            |

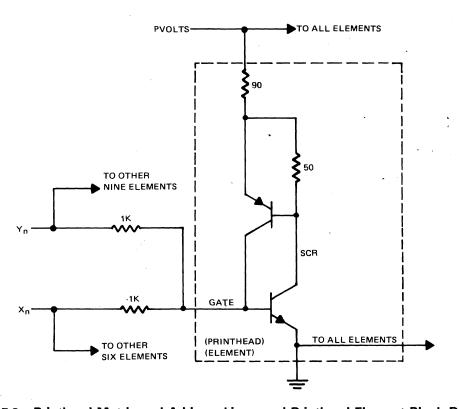

| 5.4.1   | Printhead                                  |       |         | (Models 785, 787) 6-33               |

| 5.4.2   | Printhead Drivers                          | 5-11  | 6.7     | Printhead Cleaning 6-33              |

| 5.4.3   | Temperature-Compensation                   |       | _       |                                      |

|         | Circuit                                    |       | 7       | Assembly Drawings                    |

| 5.4.4   | Print Voltage Circuit                      |       | _       |                                      |

| 5.5     | Keyboard                                   |       | 8       | Schematics                           |

| 5.5.1   | Keyboard Scan                              |       |         |                                      |

| 5.5.2   | Keyboard Interface                         |       |         |                                      |

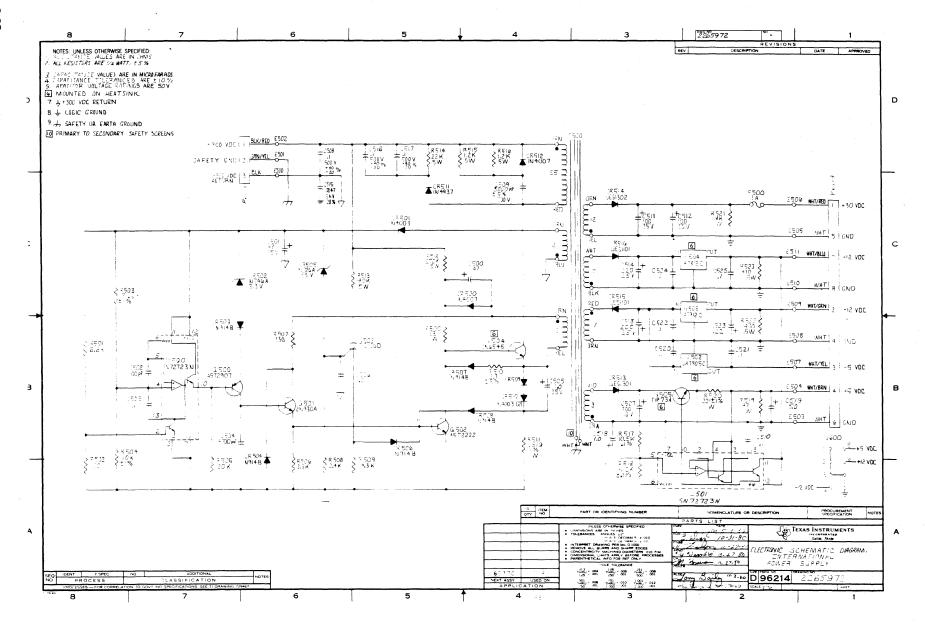

| 5.6     | Power Supply                               |       |         | Appendixes                           |

| 5.6.1   | Domestic Power Supply                      |       | _       |                                      |

| 5.6.2   | International Power Supply                 |       | A       | 8080A Microprocessor Data Manual     |

| 5.7     | Communications Interface                   |       | В       | 5504 Multifunction I/O Controller    |

| 5.7.1   | Current Loop Interface                     |       | •       | Data Manuals                         |

| 5.7.2   | EIA Interface                              |       | С       | Foreign Keyboard Layouts and Symbols |

| 5.7.3   | Acoustic Coupler/Modem                     |       | D       | Recommended Data Set Options         |

| 5.7.4   | Direct Connect/Modem                       |       | _       | and Cabling Information              |

| 5.8     | Firmware                                   | 5-29  | E       | Operator Reference Cards             |

# LIST OF ILLUSTRATIONS

| Figure | No. Title Pag                     | je Fiç      | gure No | D. Title                        | Page   |

|--------|-----------------------------------|-------------|---------|---------------------------------|--------|

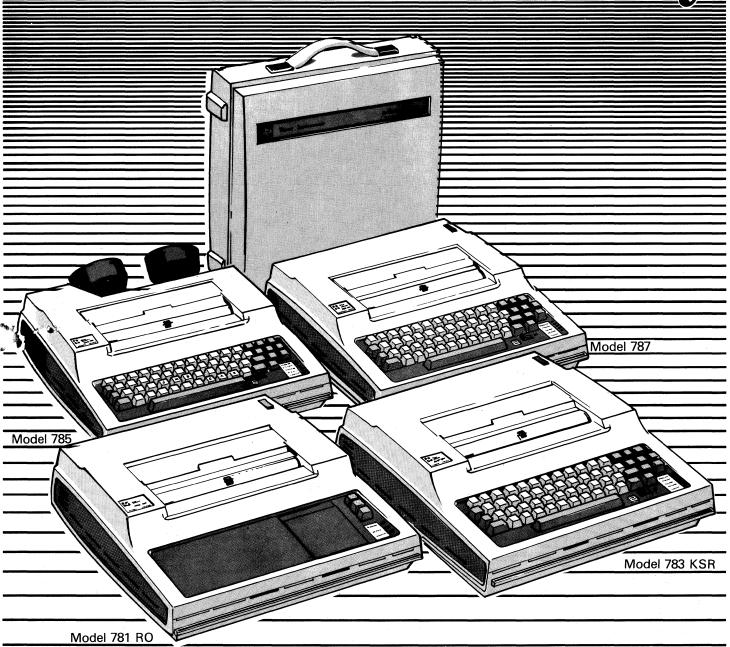

| 1-1    | Model 781 RO Printer 1-           | 2 5-7       | 7       | Printhead System                |        |

| 1-2    | Model 783 KSR Data Terminal 1-    | -2          |         | Block Diagram                   | 5-9    |

| 1-3    | Model 785 Portable Data           | 5-8         | 8       | Printhead Matrix and Address Li | nes,   |

|        | Terminal 1-                       | -2          |         | and Printhead Element Block     |        |

| 1-4    | Model 787 Portable Communications |             |         | Diagram                         | . 5-10 |

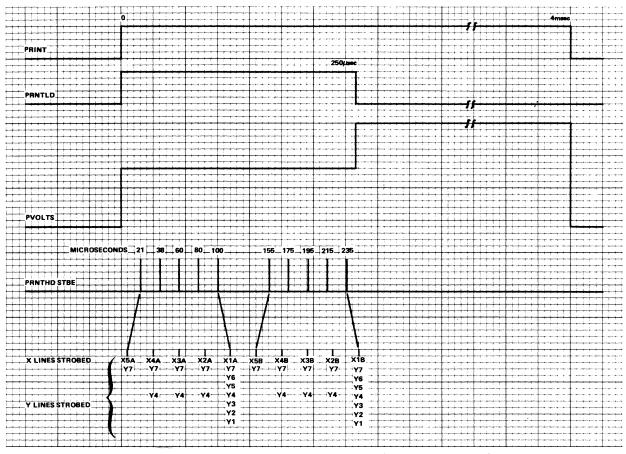

|        | Data Terminal 1-                  | 2 5-9       | 9       | Printhead Interface Timing      |        |

|        |                                   |             |         | (For Letter "F")                | . 5-12 |

| 2-1    | Communications Interfaces 2-      | 2 5-1       | 10      | Printhead Interface Timing      |        |

| 2-2    | Current Loop Configuration 2-     | 5           |         | (For Letters "FF")              | . 5-13 |

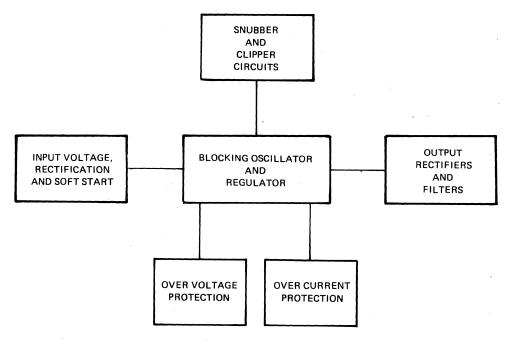

|        |                                   | <b>5</b> -1 | 11      | Domestic Power Supply Block     |        |

| 3-1    | Operator's Panel 3-               | 2           |         | Diagram                         | . 5-14 |

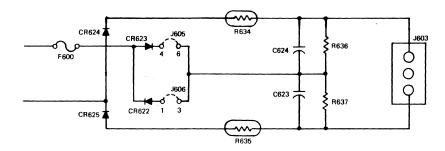

| 3-2    | Keyboard (Unshifted) 3-           | 3 5-1       | 12 '    | Voltage Doublers                | . 5-15 |

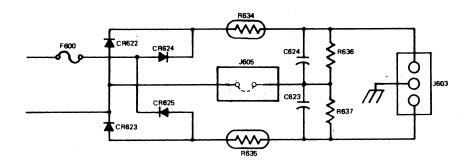

| 3-3    | Keyboard (Shifted) 3-             | 3 5-1       | 13      | Full-Wave Bridge                | . 5-16 |

| 3-4    | Keyboard (Upper Case) 3-          |             | 14      | nternational Power Supply       |        |

| 3-5    | Keyboard (Control) 3-             | 3           |         | Block Diagram                   | . 5-19 |

| 3-6    | LED Indicators (783, 785, 787) 3- | 5 5-1       | 15 (    | Communications Interface        | . 5-22 |

| 3-7    | Operator's Keypad (781) 3-        | 6 5-1       | 16      | 785 Modem Simplified            |        |

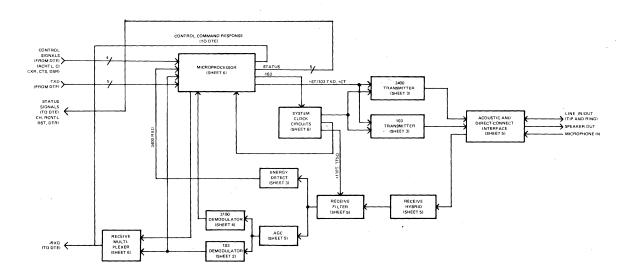

| 3-8    | LED Indicators (781) 3-           |             |         | Block Diagram                   | . 5-23 |

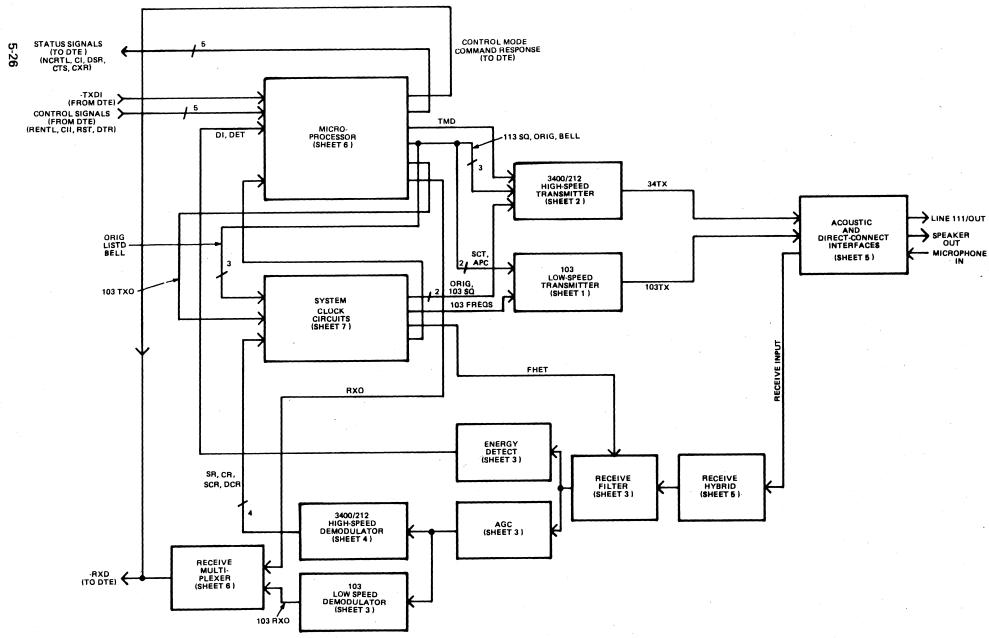

|        |                                   | 5-1         | 17      | 787 Modem Simplified            |        |

| 4-1    | Serial Data Timing Diagram 4-     | 3           |         | Block Diagram                   | . 5-26 |

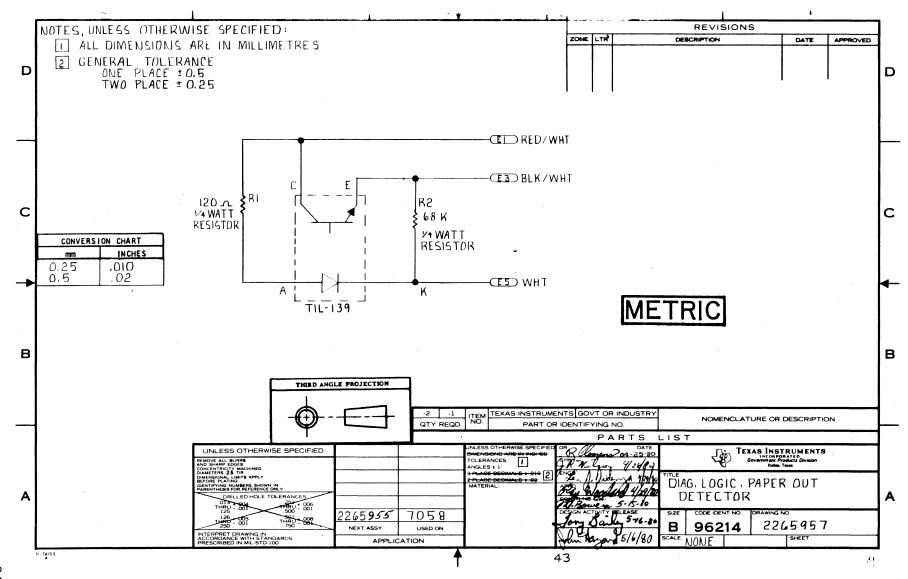

| 5-1    | 8080A Microprocessor Functional   | 6-1         | 1 1     | Barberpole Example              | 6-3    |

|        | Block Diagram 5-                  | 1 6-2       | 2 1     | RDLB Test Setup                 | 6-3    |

| 5-2    | Memory Organization 5-            | 3 6-3       | 3 /     | ALB Test Setup                  | 6-4    |

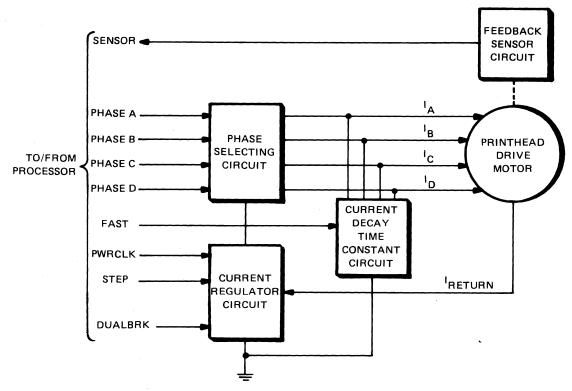

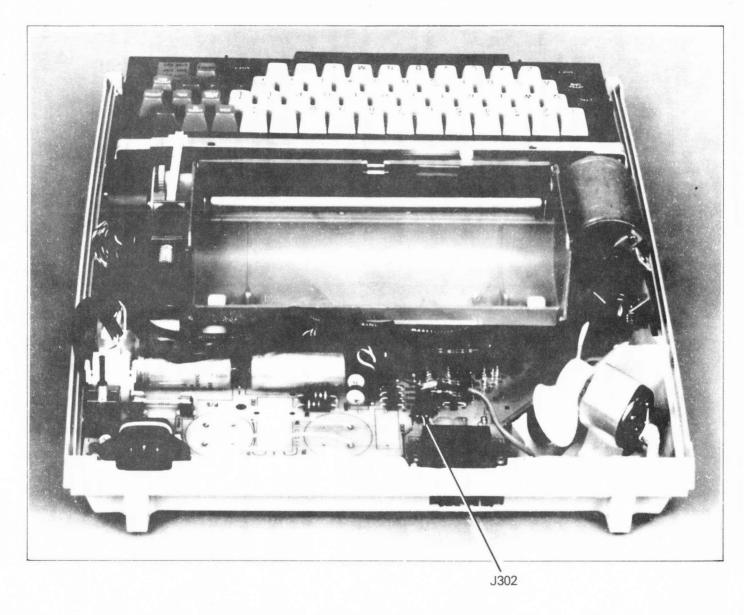

| 5-3    | Printhead Drive Electronics       | 6-4         | 1 1     | nternal Connector Locations     | . 6-25 |

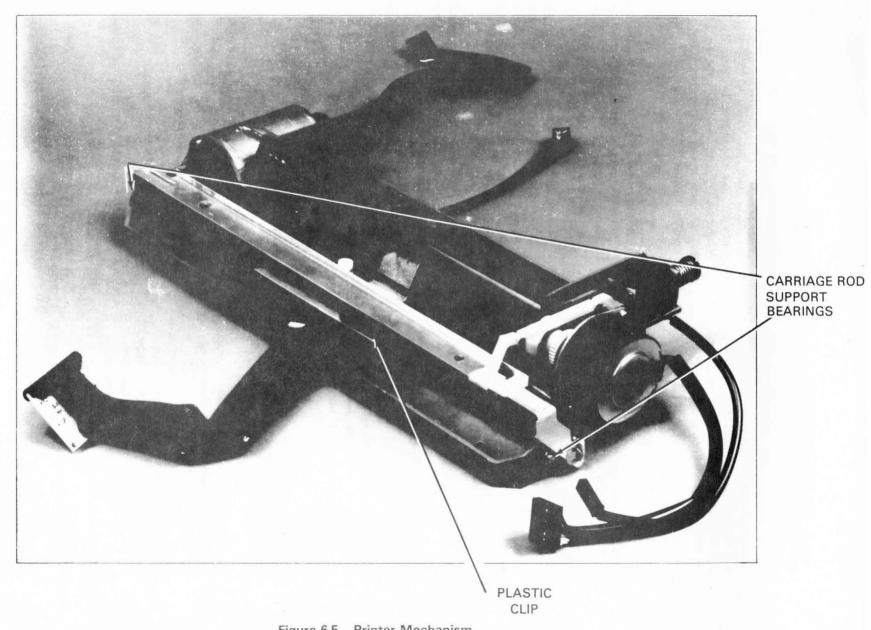

|        | Block Diagram 5-                  | 5 6-5       | 5 F     | Printer Mechanism               | . 6-27 |

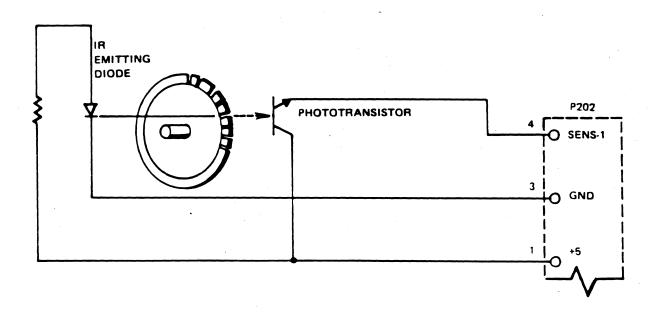

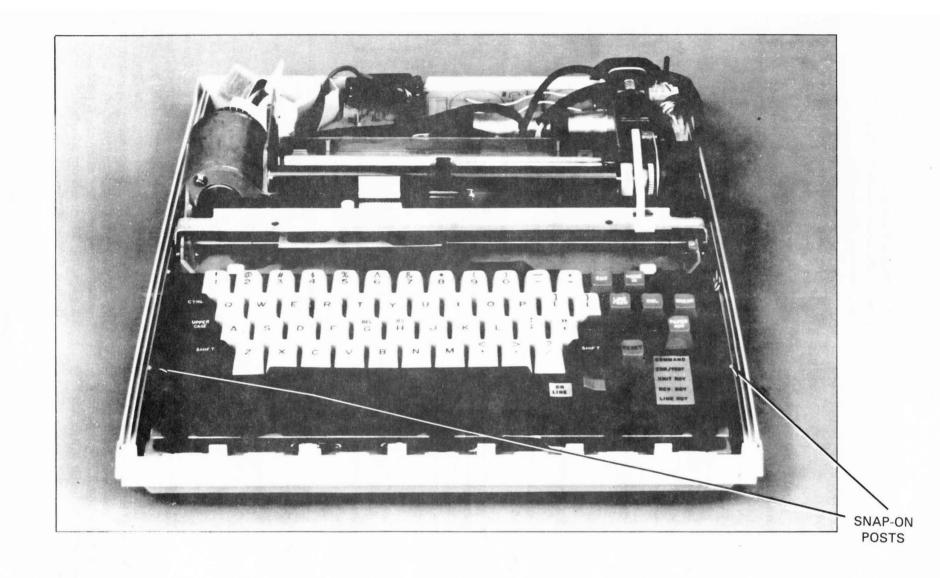

| 5-4    | Printhead Stepping Motor Feedback | 6-6         | 6 I     | Keyboard Removal                | . 6-29 |

|        | Sensor Light Path                 | 6-7         | 7 . 1   | nterboard Connector             |        |

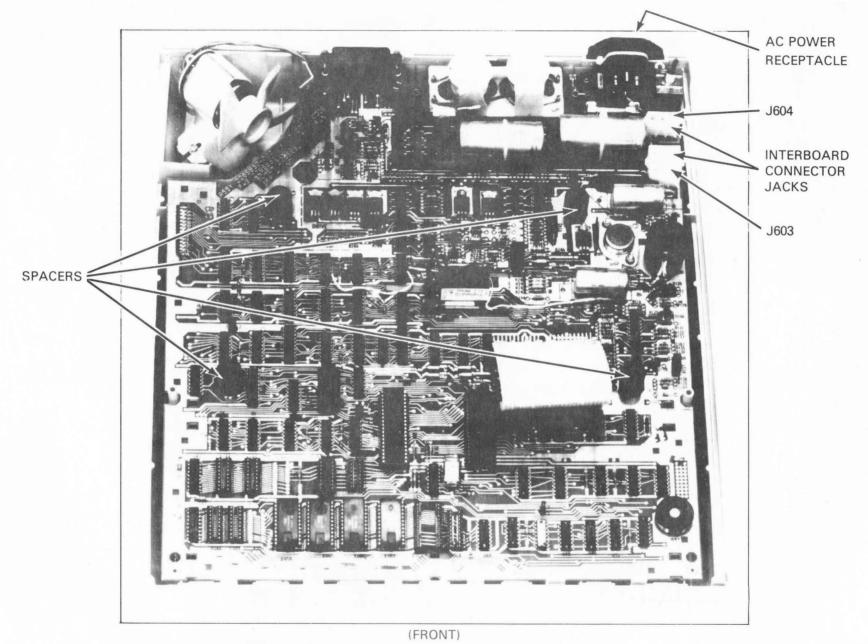

|        | Schematic 5-                      | 7           |         | Location                        | . 6-31 |

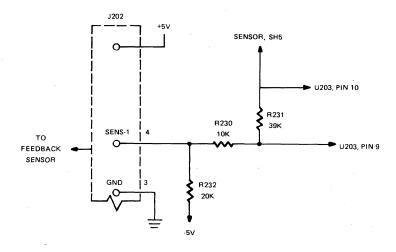

| 5-5    | Printhead Stepping Motor Feedback | 6-8         | 3 1     | Power Supply and Modem PWB      | . 6-32 |

|        | Sensor Motor Schematic 5-         | 7 6-9       | ) F     | Printhead Solenoid              | . 6-34 |

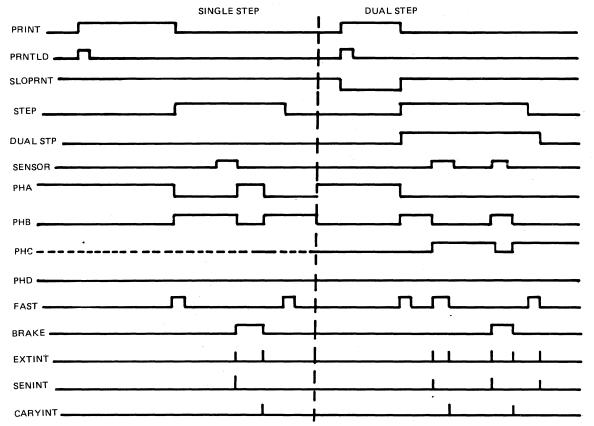

| 5-6    | Single-Step/Dual-Step Algorithm   | 6-1         | 10 F    | Print Contrast Adjustment       | . 6-35 |

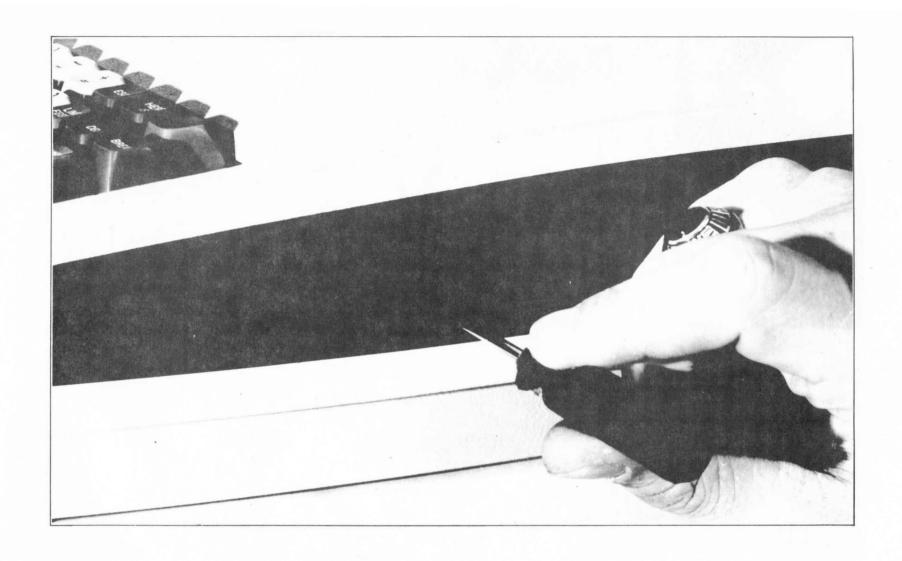

|        | Timing Diagram 5-                 | 7 6-1       | 11 F    | Printhead Cleaning              | . 6-36 |

NOTES: PERTAINING TO THE TONE DIAL OPTION INSTALATION PROCEDURE SEE PAGE E-5 IN BACK OF MANUAL.... E-5

# **LIST OF TABLES**

| Table | No. Title Page                 | Table N | No. Title               | Page     |

|-------|--------------------------------|---------|-------------------------|----------|

| 1-1   | Terminal Options 1-3           | 4-1     | Distortion Limits       |          |

|       |                                | 4-2     | EIA Signal Levels       | 4-2      |

| 2-1   | Interface Signals 2-3          | 4-3     | ASCII Code System       |          |

| 2-2   | Pin Assignments 2-4            |         | and Character Sets      | 4-2      |

|       |                                | 4-4     | EIA/CCITT/TTY Interface | <b>!</b> |

| 3-1   | ASCII/Hexadecimal              |         | Signals                 | 4-4      |

|       | Conversion Codes 3-6           | 4-5     | Current Loop Electrical |          |

| 3-2   | On-Off Configuration Codes 3-9 |         | Characteristics         | 4-5      |

| 3-3   | Multiple-Choice Configuration  |         |                         |          |

|       | Codes 3-10                     | 5-1     | Current Select Signal   |          |

| 3-4   | Program Commands 3-11          |         | Relationships           | 5-5      |

| 3-5   | Error Codes 3-12               |         | ·                       | •        |

| 3-6   | Audible Tone Signals 3-13      | 6-1     | Maintenance Tests       | 6-2      |

| 3-7   | Printed Status Reports 3-13    |         |                         |          |

| 3-8   | Transmitted Reports 3-14       |         |                         |          |

|       |                                |         |                         |          |

# Section 1

# **Equipment Description**

#### 1.1 INTRODUCTION

This section contains general descriptions, available options, physical dimensions, and specifications of the terminals in the 780 Series.

### 1.2 GENERAL DESCRIPTION

The 780 Series terminals are self-contained, compact, lightweight, programmable machines for use in a wide variety of telecommunications systems. The terminals can operate in both fixed location and portable applications. Communications data is input and output via a communications port, acoustic coupler or "direct-connect" jack, depending on the particular model. Each terminal is capable of communicating via an EIA RS-232-C interface or TTY current loop.

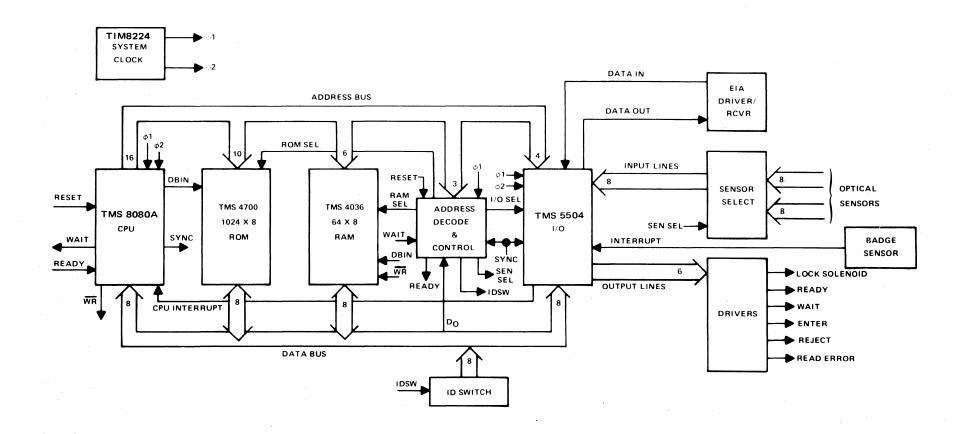

The terminal electronics consist primarily of an 8080A microprocessor, its associated memory, and interface circuitry to drive the printer mechanism and communications port.

The terminals utilize thermal printing and are capable of bidirectional printing at speeds up to 140 characters per second (cps) while handling communications data rates from 110 bits per second (bps) to 9600 bps.

Operating parameters such as communications mode, data transmission rate, parity selection, line

control, transmission control and terminal control are configurable directly from the operator interface by entering the proper code.

# 1.3 780 SERIES DATA TERMINALS

The 780 Series is comprised of the following terminals:

- Model 781 Receive-Only Printer,

- Model 783 Keyboard Send/Receive Data Terminal,

- Model 785 Portable Data Terminal, and

- Model 787 Portable Communications Data Terminal.

These terminals are described in more detail in the following paragraphs.

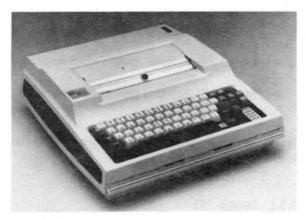

#### 1.3.1 Model 781

The Model 781 Receive-Only (RO) Printer (Figure 1-1) is intended for applications requiring a hard-copy, high-speed output device. Using a dual-matrix thermal printhead, the 781 RO provides virtually silent printing at up to 140 cps. Operating parameters are entered from a calculator-type keypad.

Figure 1-1. Model 781 RO Printer

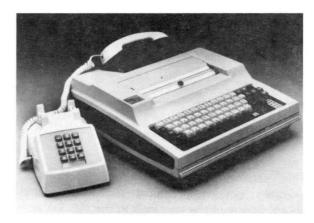

### 1.3.2 Model 783

The Model 783 Keyboard Send/Receive (KSR) Data Terminal shown in Figure 1-2 is highly suited for conversational, data/text entry, inquiry-response, and computer console applications. Operating parameters are configured by entering the desired code via the typewriter-like keyboard.

Figure 1-2. Model 783 KSR Data Terminal

# 1.3.3 Model 785

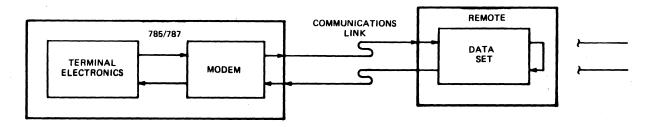

The Model 785 Portable Data Terminal (Figure 1-3) is similar to the Model 783 but includes an internal modem. The modem is a dual-speed, originate-only, full-duplex modem, with an acoustic coupler interface which permits communication over standard commercial telephone lines at communications rates of 110, 300, and 1200 bps. The modem provides communications compatibility with answering Racal-Vadic VA3400 Series and Bell 103/113-type data sets. This feature provides great flexibility, permitting use of

the terminal wherever a telephone and electrical outlet are available.

Figure 1-3. Model 785 Portable Data Terminal

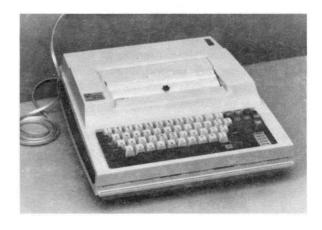

# 1.3.4 Model 787

The Model 787 Portable Communications Data Terminal (Figure 1-4) is similar to the Model 785 except that the internal modem is a dual-speed, answer/originate, full-duplex modem. The modem has a direct-connect interface which allows it to be plugged directly into a voice or data jack for communication over standard commercial telephone lines. The modem provides communications compatibility with all Racal-Vadic VA3400 series and Bell 103/113/212-type data sets. As an option, the 787 has an acoustic-coupler interface that provides greater flexibility.

Figure 1-4. Model 787 Portable Communications Data Terminal

# 1.4 OPTIONS

A variety of options provide versatility and flexibility for the 780 Series data terminals. These options are listed in Table 1-1 and identify the applicable terminal.

**Table 1-1. Terminal Options**

| Option                                | 781 | 783 | 785 | 787 |

|---------------------------------------|-----|-----|-----|-----|

| International Character Sets          | х   | х   | Х   | х   |

| Additional 1000-Character Buffer      | x   | X.  | N/A | N/A |

| 300-Foot Paper Adapter                | x   | х   |     | *   |

| Paper-Out Indicator                   | x   | x   | N/A | ×   |

| APL/Full ASCII Keyboard/Character Set |     | x   | x   | ×   |

| Katakana Keyboard/Character Set       | ×   | x   |     |     |

| Protected ABM                         | ×   | x   | x   | x   |

| Acoustic-Coupler Interface            |     |     | **  | X   |

| EIA or Current Loop Interface Cable   | **  | **  | **  | **  |

| Tone Dial Assist                      |     |     |     | ×   |

N/A Not applicable

\*\* Standard

<sup>\*</sup> Not compatible with acoustic-coupler interface

# 1.5 PHYSICAL DIMENSIONS

1.5.1 Size

Height: 139 mm (5.5 in)

Width: 391 mm (15.4 in)

Depth: 406 mm (16.0 in)

1.5.2 Weight

Model 781: 5.4 kg (12 lbs)

Model 783: 5.9 kg (13 lbs)

Model 785: 7.7 kg (17 lbs)

Model 787: 7.2 kg (16 lbs)

All weights include 110-foot paper roll.

# 1.6 ENVIRONMENTAL LIMITS

# 1.6.1 Non-Operating Environment

During shipping and storage the data terminals can withstand being subjected to the following:

In a shipping container:

Temperature:  $-30^{\circ}$  C to  $+70^{\circ}$  C ( $-22^{\circ}$  F to  $+158^{\circ}$  F).

Relative Humidity: 10% to 95% without condensation.

Shock: Drop from 1.22 meters (48") on each surface.

Vibration: Sinusoidal vibration of:

2 Gs-5 to 50 Hz 4 Gs-50 to 500 Hz.

Altitude: 15,000 meters (49,200 ft).

Cargo Bounce: Per MIL-STD-810B. One-inch double-orbital motion. 225 RPM, 30

minutes per side.

Without a shipping container:

Temperature:  $-30^{\circ}$  C to  $+70^{\circ}$  C ( $-22^{\circ}$ F to  $158^{\circ}$ F).

Relative Humidity: 10% to 95% without condensation.

Shock: a. Portable mode

40 Gs, ½ sinewave

11 ms maximum through each axis.

b. Bench handling per MIL-STD-810B, method 516.1, procedure V.

# 1.6.2 Operating Environment

The data terminals are capable of operating in the following conditions:

Ambient Temperature:

10°C to 40°C (50°F to 104°F).

Relative Humidity:

10% to 95% without condensation.

Altitude:

3,500 meters (11,500 ft).

Vibration:

Sinusoidal vibration of 0.5 Gs peak in the range of 10 Hz to 60 Hz.

Temperature Shock:

Operate in a 23°C (73°F), 50% relative humidity environment within 30

minutes after being stored for two hours at -30°C (-22°F), 50%

relative humidity.

### 1.7 SPECIFICATIONS

The following specifications apply to all terminals.

### 1.7.1 Printer

Method:

Nonimpact, electrically heated, 5×7 dual-character matrix thermal

printhead, prints on thermographic paper.

Character Set:

95 printable characters in normal mode with 33 ASCII or CCITT control

characters when configured.

Character Size:

2.66 mm  $\times$  2.0 mm (0.105 in  $\times$  0.080 in).

Line Length:

203.2 mm (8.0 in); 25.4 mm spacing; 10 characters per inch; 80

characters per line.

Vertical Line Spacing (center-to-

center):

4.24 mm (.1669 in); 6.0 lines per inch.

Printing Rate:

Up to 140 cps.

Paper:

Thermal (TI specification 972603).

Platen:

Friction feed.

# 1.7.2 Keyboard

Code:

ASCII or CCITT; 128 codes generated.

### 1.7.3 **Modem**

Compatibility: Racal-Vadic 3400 or Bell 103-type or 212\*-type data sets

Mode: Originate only (785)

Answer/Originate (787)

Modulation: Racal-Vadic 3400 and Bell 212-type

Differential Phase Shift Keying (DPSK)

Bell 103-type: Frequency Shift Keying (FSK)

Originate Mode

Transmit Carrier Frequencies: Racal-Vadic 3400: 2250 Hz

Bell 103-type: Mark = 1270 Hz

Space = 1070 Hz

Bell 212-type: 1200 Hz

Receive Carrier Frequencies: Racal-Vadic 3400: 1150 Hz

Bell 103-type: Mark = 2225 Hz

Space = 2025 Hz

Bell 212-type: 2400 Hz

Answer Mode

Transmit Carrier Frequencies: Racal-Vadic 3400: 1150 Hz

Bell 103-type: Mark = 2225 Hz

Space = 2025 Hz

Bell 212-Type: 2400 Hz

Receive Carrier Frequencies: Racal-Vadic 3400: 2250 Hz

Bell 103-type: Mark = 1270 Hz

Space = 1070 Hz

Bell 212-type: 1200 Hz

Transmit Level

Permissive Connection: -10 dBm, fixed for all methods

Programmable Connection: 0 to -12 dBm, per data jack

Optional Acoustic Coupler: Bell 103-type = -14 dBm

Bell 212-type = operation not recommended

Racal-Vadic 3400 = -17 dBm

Receiver Sensitivity

Direct Connect: All types = -45 dBm

Acoustic Coupler: Bell 103-type = +0 to -40 dBm depending upon quality of telephone

handset and communications line(s)

Bell 212-type = operation not recommended

Racal-Vadic 3400 = +0 to -32 dBm depending upon quality of

telephone handset and communications line(s)

<sup>\*</sup>Bell 212-type not available on 785.

# Section 2

# **Equipment Installation**

### 2.1 PRELIMINARY CHECKOUT

The 780 terminals are self-contained, requiring no auxiliary equipment for normal operation.

After unpacking, visually inspect the data terminal before applying power. Check for obvious shipping damage. Check that all keyboard keys operate freely. Before attempting to use the terminal, read the following cautions.

# **CAUTIONS**

DO NOT operate printer without paper for extended periods or damage may result to the printhead.

DO NOT operate the terminal outside the specified operating range of 10°C to 40°C (50°F to 104°F) or malfunctions may occur. If the terminal has been stored outside this range, allow it to sit for a minimum of 30 minutes before applying power.

# 2.2 POWER CONNECTION

The terminals are designed to operate from either domestic or foreign power distribution systems. The power supply is configured at the factory and is adjusted by means of jumper(s) on the main PWB. The terminal operates properly when the input voltage is within the following limits:

Nominal Voltage:

120 Vac

90 to 134 Vac

230 Vac

187 to 264 Vac

Input Frequency: 47 Hz to 450 Hz.

### **CAUTIONS**

Check the label on the rear of the terminal to determine the correct voltage required for your terminal. Ensure that the voltage at the wall outlet matches the terminal voltage rating listed on the label.

It is preferred that the terminal be plugged into a three-wire earth-grounded ac outlet. If an extension cord is required, it is preferred that it be of the three-wire type containing an earth-ground conductor.

# 2.3 COMMUNICATIONS INTERFACE

The terminals interface with numerous devices via at least one of three methods. All terminals have a communications interface connector (25-pin connector) located on the rear of the terminal that includes circuits for EIA and TTY (DC) current loop operation.

# **NOTE**

The communications interface connector is not a standard EIA port since the TTY current loop circuits are included in the connector.

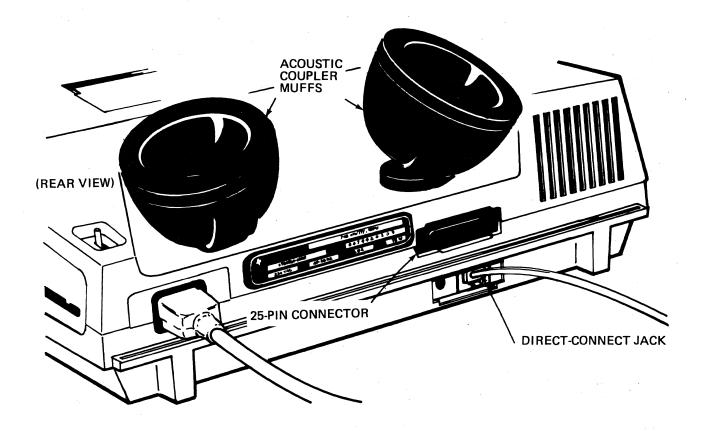

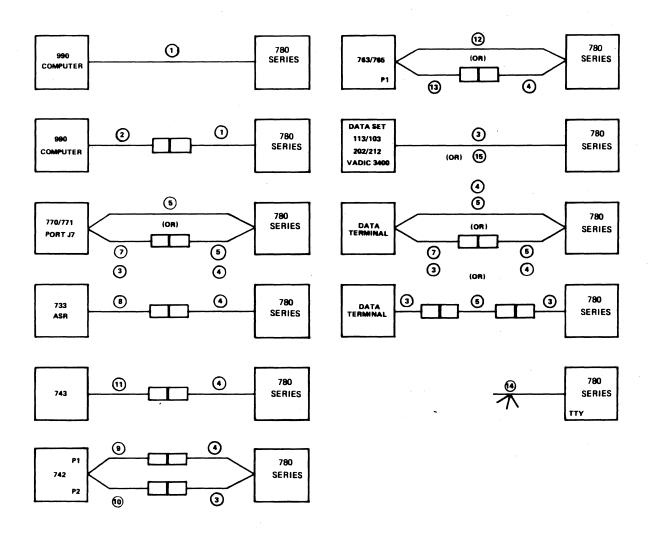

The 785 includes an acoustic-coupler interface located on the rear deck of the case. The 787 utilizes a direct-connect interface located below the 25-pin connector and, as an option, the 787 may also have an acoustic-coupler interface. The various communications interfaces are shown in Figure 2-1.

Figure 2-1. Communications Interfaces

A functional description of the interface signals present in the communications interface connector is presented in Table 2-1, and pin assignments are listed in Table 2-2.

Table 2-1. Interface Signals

**Protective Ground (AA)**—This lead is connected to the terminal frame and the earth-ground conductor of the power cord.

Signal Ground (AB)—This lead is tied to the dc ground of the terminal for all interface signals.

Transmitted Data (BA)—This lead conveys signals from the terminal data transmitted output to the data set transmitted circuitry. It is held to a MARKING condition unless data or BREAK signals are being transmitted.

Received Data (BB)—This lead conveys signals from the external data set receiver to the terminal data receiver input.

Request To Send (CA)—This line is used by the terminal to control the transmitter carrier of the data set. For full-duplex operation, this lead is held ON at all times that circuits CC (data set ready) and CD (data terminal ready) are ON. For half-duplex operation, this lead is held ON when the terminal is ONLINE and in the transmit mode.

Clear To Send (CB)—This line is switched on by the data set to indicate to the terminal that the data set is ready to transmit. The terminal will not attempt to transfer data across the interface when this line is off.

Data Set Ready (CC)—This signal line is controlled by the data set. The terminal will not attempt to receive or transmit data across the interface when this line is off.

Data Terminal Ready (CD)—This signal line is turned on by the terminal to indicate that it is ONLINE and ready to initiate or answer a data call. It is switched OFF momentarily during a terminal automatic disconnect sequence and is held OFF when the terminal is OFFLINE.

Ring Indicator (CE)—An ON condition on this circuit indicates that the data set is receiving a ringing signal from the communications line. The terminal monitors this circuit and uses the information presented to make a determination of whether it is in answer or originate mode for purposes of ABM autotrigger.

Received Line Signal Detector (CF)—This line is switched ON by the data set to indicate that it is receiving a valid carrier signal from the remote data set. The terminal will not accept data from the interface if this signal is OFF. This line will be regarded as ON when it is open (floating) to permit successful operation with data sets which do not provide circuit CF.

Data Signal Rate Selector (CH)—This signal is used by the terminal to select the transmit and receive data rate when used with Bell-type-212 data sets equipped with the originate speed select option. The terminal will hold circuit CH ON when configured for operation at speeds greater than or equal to 1200 bits per second (bps) or for 300/1200 auto-select, and will hold it OFF for all other data rates.

Secondary Request To Send (SCA)—This line is held ON by the terminal when it is ready to receive data and configured for half duplex with reverse channel operation (receive or idle mode). This signal will be switched OFF when the terminal enters the transmit mode. For this duplex mode, circuit SCA is the complement of circuit CA. This signal line will be controlled for other sequences of operation as described later in this manual.

Secondary Received Line Signal Detector (SCF)-This signal has a dual function, depending on the external data set. (1) It is held ON by 202 series data sets to indicate receipt of a valid reverse channel carrier from a remote data set. When the terminal is configured for half duplex with reverse channel operation, it will not transmit data until circuit SCF is ON and will treat any loss of SCF for 100-125 msec. or longer as a BREAK signal. (2) Bell 212 compatible data sets use this signal as a baud rate indicator, holding the signal ON for 1200 bps and OFF for 103 series operation. The terminal, when configured for 300/1200 auto-select, will adjust its data transmission rate in accordance to the status of circuit SCF. An open circuit SCF will be detected as an OFF condition. Detection of an ON condition will result in automatic selection of 1200 bps, and detection of an OFF condition will result in the automatic selection of 300 bps.

For more information concerning communications interconnections, refer to Appendix E.

Table 2-2. Pin Assignments

| Pin | RS-232-C<br>Circuit | Current<br>Loop | Function                                |

|-----|---------------------|-----------------|-----------------------------------------|

| 1   | AA                  |                 | Protective Ground (PG)                  |

| 2   | ВА                  |                 | Transmitted Data (XMT)                  |

| 3   | BB                  |                 | Received Data (RCV)                     |

| . 4 | CA                  |                 | Request to Send (RTS)                   |

| 5   | СВ                  |                 | Clear to Send (CTS)                     |

| 6   | CC                  |                 | Data Set Ready (DSR)                    |

| . 7 | AB                  |                 | Signal Ground (SG)                      |

| 8   | CF                  |                 | Received Line Signal Detector (DCD)     |

| 11  | SCA                 |                 | Secondary Request to Send               |

| 12  | SCF                 |                 | Secondary Received Line Signal Detector |

| 13  |                     | `X1             | TTY Transmitted Data (TTYXMTD)          |

| 14  |                     | X2              | TTY Transmitted Data Return (TTYXMTD/R) |

| 15  | DB                  |                 | Transmission Signal Element Timing      |

| 16  |                     | RL-1            | TTY Receive Data (TTYRCVD)              |

| 17  | DD                  |                 | Receiver Signal Element Timing          |

| 18  |                     | RL-2            | TTY Receive Data Return (TTYRCVD/R)     |

| 20  | CD                  | İ               | Data Terminal Ready (DTR)               |

| 22  | CE                  |                 | Ring Indicator (RI)                     |

| 23  | СН                  |                 | Data Signal Rate Selector               |

# 2.3.1 EIA Operation

All terminals interface with external devices through the 25-pin connector located at the rear of the terminal. The Asynch/Sync Cable (TI Part No. 2207634) consists of a 25-pin mating connector at the terminal end and 25-pin male connector on the modem end. The following steps provide a general guideline for setup when using Bell-type 103, 113, 202, 212, and Racal-Vadic 3400 series data sets:

- Connect the interface cable (TI Part No. 2207634-0001 supplied with the terminal) between the interface connector on the back of the terminal and the data set.

- 2. Ensure that the communications method and speed are compatible with the data set being used.

- 3. Ensure that the parity is set to conform to the requirements of the system.

- 4. Set the terminal to the ONLINE Mode.

The terminal is now ready for operation with the data set.

# 2.3.2 TTY (DC) Current Loop Operation

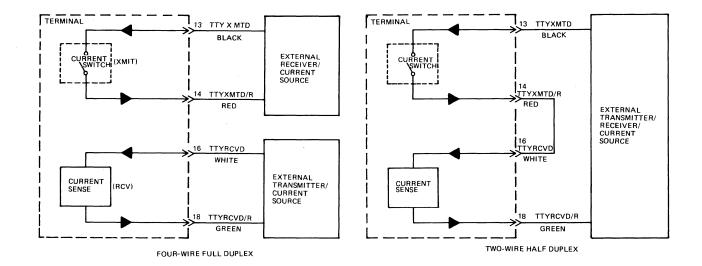

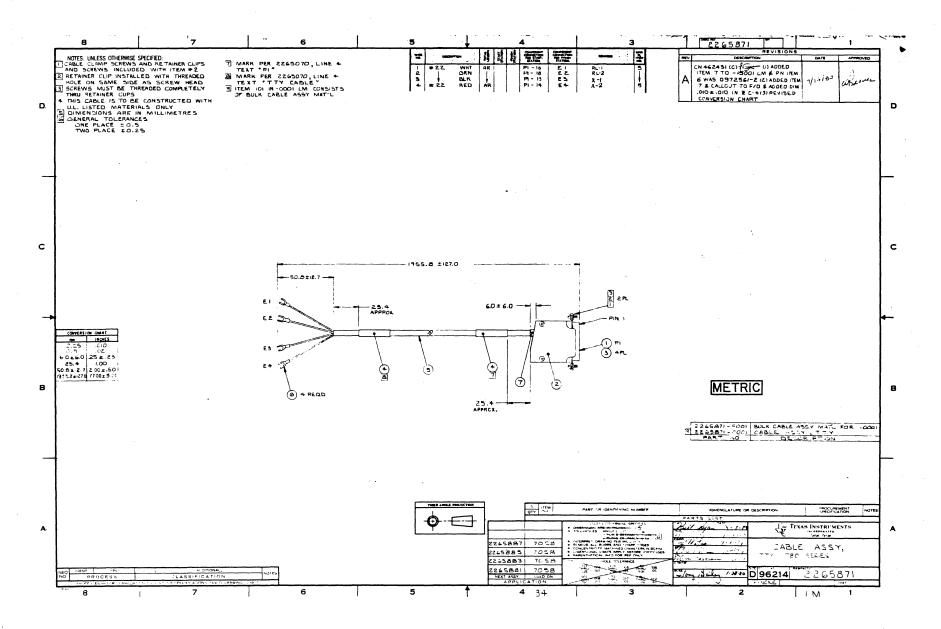

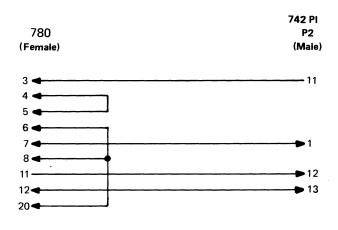

All terminals interface with external devices through the communications connector located at the rear of the terminal. The TTY Cable (TI Part No. 2265871-0001) consists of a 25-pin mating connector at the terminal end and four spade lugs at the other end. Figure 2-2 illustrates the four-wire (full-duplex) and two-wire (half-duplex) current loop configuration.

Figure 2-2. Current Loop Configuration

The following steps provide a general guideline for setup when using the current loop interface:

- Connect the current loop cable (TI Part No. 2265871-0001) between the interface connector on the back of the terminal and the external equipment.

- 2. Ensure that configuration *code* 16 (current loop) has been selected.

- Set the remaining configuration codes to comply with the requirements of the external equipment or system.

- 4. Set the terminal to the ONLINE Mode.

The terminal is now ready to communicate.

# 2.3.3 Internal Modem Operation

Models 785 and 787 are equipped with internal modems to provide communication over telephone lines. The modem in the 785 is a full-duplex, dual-speed, originate-only modem having an acoustic-coupler interface. The 787 has a full-duplex, dual-speed, answer/originate modem using a direct-connect interface.

# **2.3.3.1 Acoustic Coupler Interface Operation.** The following steps provide a general guideline for

setup when using the acoustic coupler.

- Switch the terminal power ON.

- Ensure that the proper configuration codes are enabled. In the majority of applications, the standard default parameters may be all that are required.

- 3. Set the terminal to ONLINE.

- Pick up the telephone handset and dial the appropriate number; a high-frequency signal (answer tone) is heard when the call is answered.

- 5. As soon as the answer tone is heard, firmly insert the telephone handset into the acoustic-coupler muffs so that the cord is to the left of the terminal. The terminal will in turn transmit a data tone to the remote modem or acoustic coupler.

- When the connection is completed, the XMIT RDY, RCV RDY, and LINE RDY indicators light and the terminal prints CONNECTED.

- Begin communications according to your system's procedures.

# **NOTES**

After prolonged operation the carbon particles in the telephone mouthpiece may settle, causing data errors. If this occurs, rap the handset several times against the palm of your hand.

Proper insertion of the handset in the muffs can make a significant difference in terminal operation. Ensure that the muffs fully encircle the earpiece and mouthpiece.

If the XMIT RDY and RCV RDY indicators begin flashing, communications have been lost and you must return to *Step* 4. This is indicative of the host modem not hearing us properly. If the message "connected" was printed, the terminal heard and responded to incoming carrier.

- When you are finished, terminate communications according to your system's procedures and set the terminal to LOCAL (the terminal prints DISCONNECTED).

- To hang up the telephone, remove the handset from the muffs by rolling it toward the front of the terminal and replace it in the handset cradle of the telephone.

- **2.3.3.2 Direct-Connect Interface Operation.** The following steps provide a general guideline for setup when using the direct-connect interface:

- 1. Switch the terminal ON.

- Ensure that the proper configuration codes are enabled. In the majority of applications, the standard default parameters may be all that are required.

- Insert the cable provided with the terminal into the receptacle on the rear of the terminal and into the data jack on the wall.

- 4. Start the call initiation procedure using the *Dial Function*.

- When the connection is completed, the XMIT RDY, RCV RDY and LINE RDY indicators light and the terminal prints CONNECTED.

- Begin communications according to your system's procedures.

### **NOTE**

If the XMIT RDY and RCV RDY indicators begin flashing, communications have been lost and you must return to *Step* 4.

- When you are finished, terminate communications according to your system's procedures.

- 8. Perform the call termination procedure (Command H). The terminal returns to LOCAL, prints DISCONNECTED, and after three seconds returns to the ONLINE Mode. A call can also be terminated by switching the terminal to LOCAL.

# **Section 3**

# **Operation**

### 3.1 OPERATING MODES

The 783, 785 and 787 terminals have three operating modes that are identifiable to the operator: LOCAL, ONLINE and COMMAND. The 781 terminal has two operating modes: LOCAL and ONLINE.

### **3.1.1 LOCAL**

The ONLINE/LOCAL switch on the keyboard is a momentary contact switch that switches the terminal between the ONLINE and LOCAL Modes of operation. The LOCAL Mode is indicated when the LED adjacent to the switch is extinguished. In the LOCAL Mode, the terminal cannot communicate with external devices. While in the LOCAL Mode, the terminal receives command data and print data from the keyboard, and the printer can print keyboard data or report data. The 781 must be in the LOCAL Mode to change special configuration parameters.

### **3.1.2 ONLINE**

In the ONLINE Mode, the terminal communicates with external devices through the communications interface. The keyboard and printer data is channeled through the communications interface. Command data or transmit data can be entered from the keyboard. The printer prints received line data or report data. Communications characteristics are determined by special configuration parameters entered from the keyboard when in the COMMAND Mode (783, 785 and 787). The ONLINE Mode is controlled by the ONLINE/LOCAL switch on the keyboard.

### 3.1.3 COMMAND

The COMMAND Mode allows the operator to change operating parameters, request reports, conduct special tests and initiate certain automatic functions. The terminal can be in either ONLINE or LOCAL Mode when the terminal is placed in the COMMAND Mode. In the 783, 785 and 787 the COMMAND Mode is entered by depressing the CMD key, while in the 781, the COMMAND Mode is entered when the CNFG or TEST key is depressed.

### 3.2 OPERATOR INTERFACE

The operator interface provides a way to communicate with the terminal and to other devices via the terminal. The 783, 785 and 787 are keyboard send-receive (KSR) terminals which use an operator's panel which is similar to a typewriter keyboard. The 781 is a receive-only (RO) terminal and uses a calculator-type keypad to input information.

# 3.2.1 KSR Operator's Panel

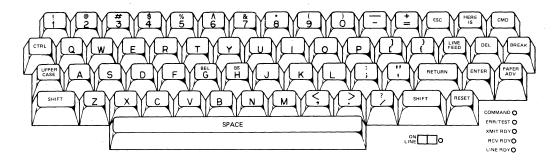

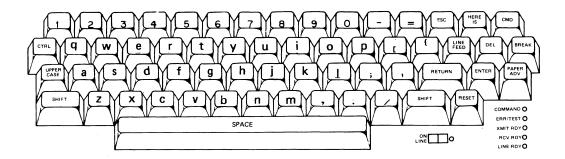

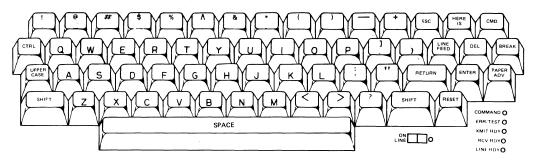

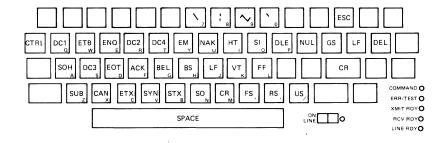

The KSR operator's panel is illustrated in Figure 3-1. The panel has 50 code-generating keys for generating all 128 ASCII codes. There are four keyboard mode control keys, six special function keys and one dual-position key for terminal control. The operator's panel also includes six light-emitting diode (LED) indicators for status reporting.

Figure 3-1. Operator's Panel

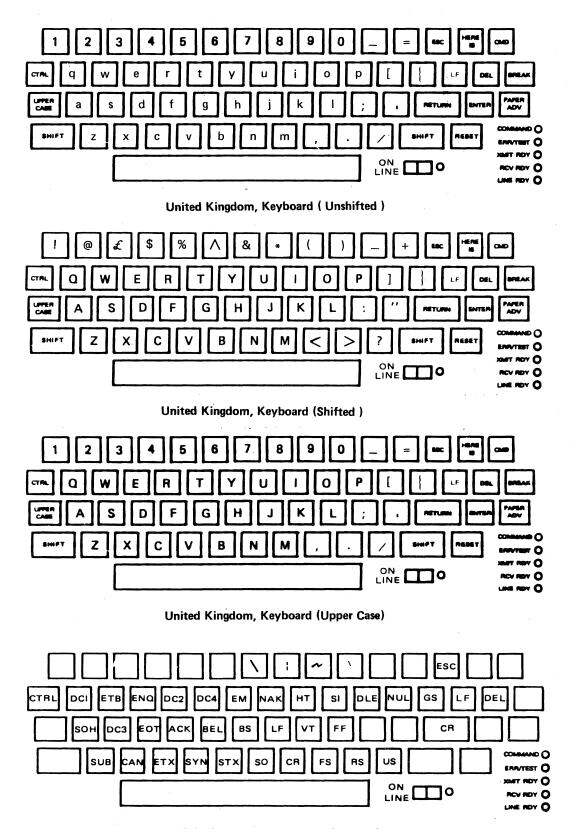

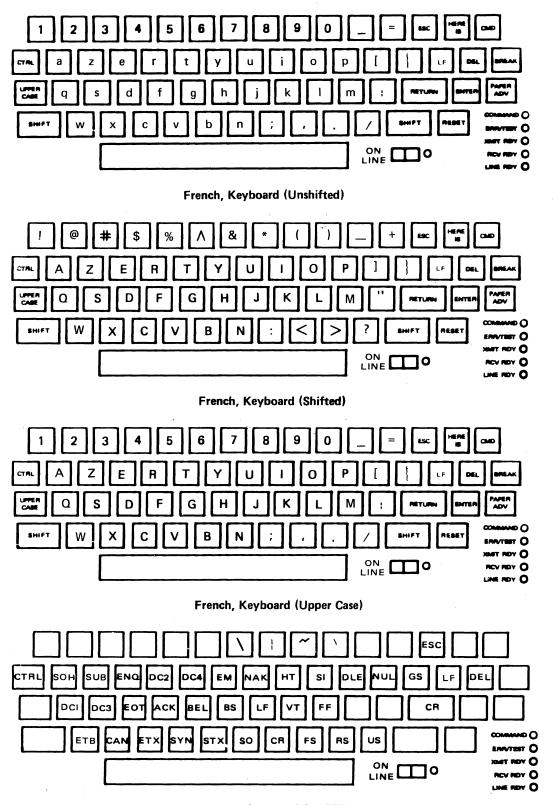

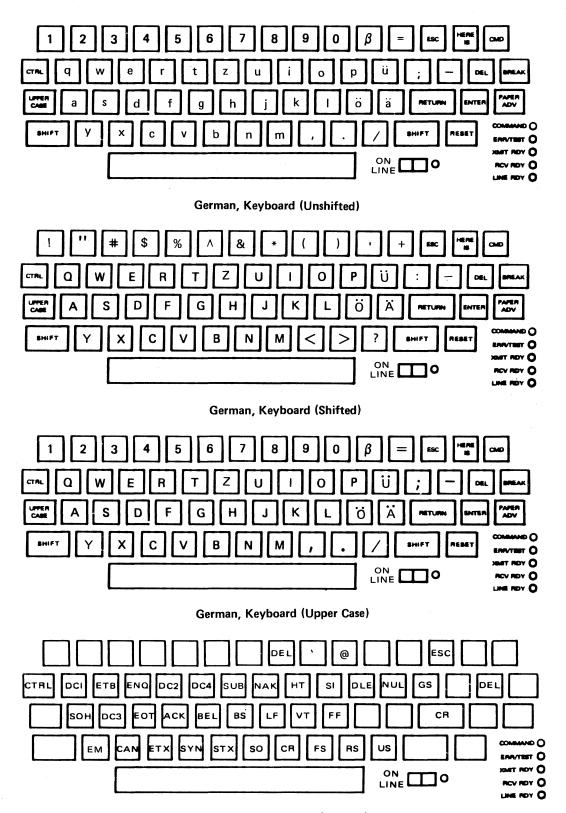

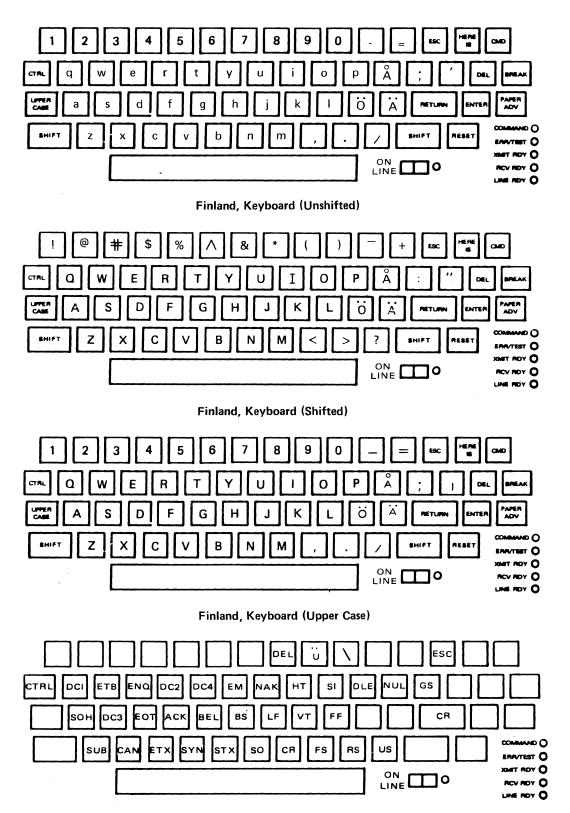

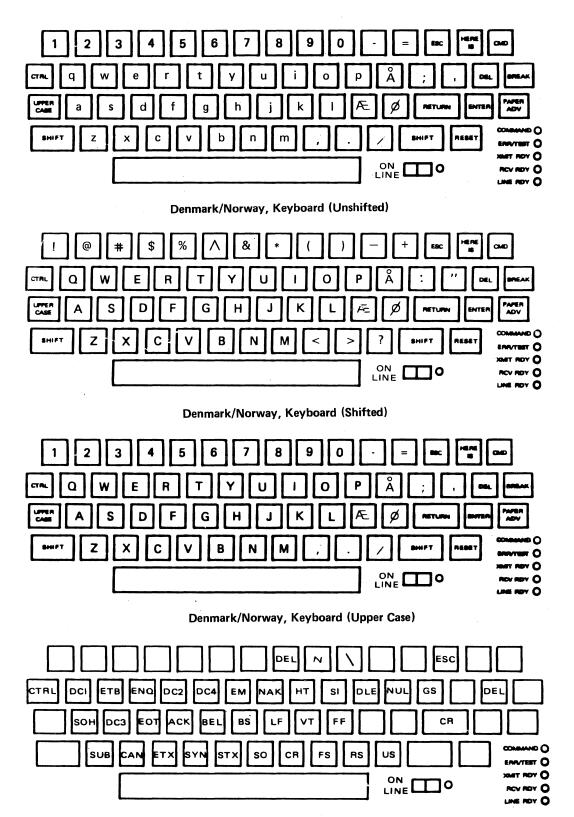

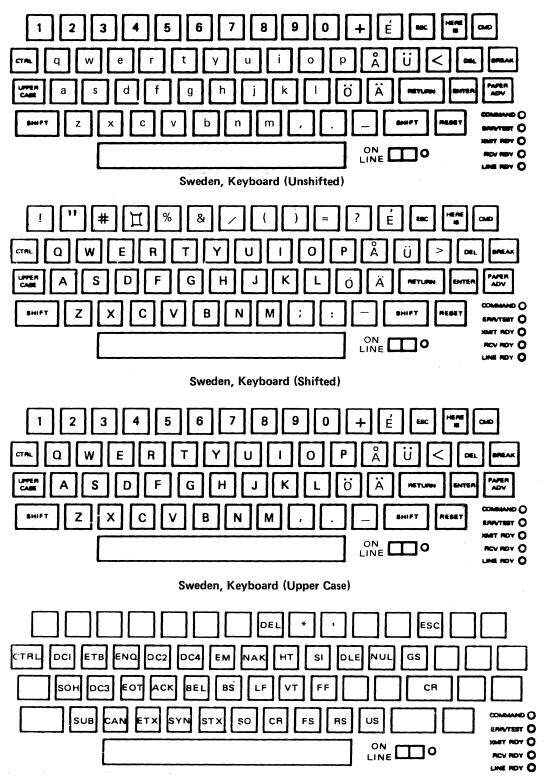

3.2.1.1 Keyboard Character Encoding. The code-generating keys include the alphabet, numerals, symbols, space, ESC, LINE FEED (except on Germany, Denmark/Norway and Sweden/Finland keyboards), DEL and RETURN. The characters generated in response to the depression of these keys are governed by the positions of the four mode control keys. These keys are SHIFT(2), UPPER CASE and CTRL which control the operating mode of the keyboard as described below:

- Unshifted—No mode control keys depressed; lowercase letters, symbols and numerals are encoded. Figure 3-2 illustrates the characters generated by each key in the unshifted mode.

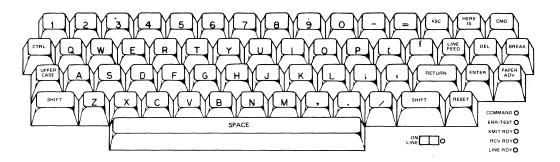

- Upper Case Only—UPPER CASE (alternate action) key depressed; all alphabetic characters a through z are encoded as ASCII upper case A through Z. The characters generated by each key when the UPPER CASE key is depressed are shown in Figure 3-3.

- Shifted—Either or both SHIFT keys depressed; uppercase letters and symbols are encoded. The characters generated by each key when depressing the SHIFT key are illustrated in Figure 3-4.

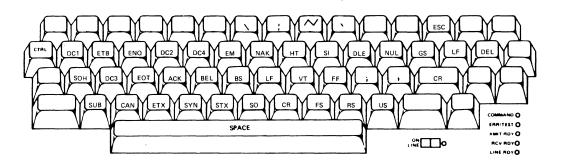

- Control—CTRL key depressed; ASCII control characters and the symbols \ \ \ \ \ \ are encoded. Figure 3-5 illustrates the control characters generated by each key.

When more than one mode control key is depressed, the following priority is maintained:

CTRL—Precedence over SHIFT and UPPER CASE,

SHIFT—Subordinate to CTRL; precedence over UPPER CASE.

UPPER CASE—Subordinate to CTRL and SHIFT.

Certain functions requiring the simultaneous depression of CTRL and SHIFT are described below:

CTRL/SHIFT/RESET—Clears the receive buffer.

CTRL/SHIFT/H—Generates a backspace.

The keys ESC, DEL, LINE FEED, RETURN and SPACE generate the same codes in all keyboard modes. All code-generating keys with the exception of ESC, DEL, and RETURN initiate automatic character repeat at 10 characters per second when switch depression exceeds 600 msec. Figures 3-2 through 3-5 illustrate the characters generated by the different keyboard modes. The Character Set Dot Matrix is located in Appendix C. The ASCII control characters are described further in paragraphs 3.5 and 4.1.3.

Figure 3-2. Keyboard (Unshifted)

Figure 3-3. Keyboard (Shifted)

Figure 3-4. Keyboard (Upper Case)

Figure 3-5. Keyboard (Control)

The terminal firmware recognizes foreign keyboards and their corresponding character sets. Each foreign character set is contained in an optional PROM. The foreign keyboards are illustrated in Appendix C.

**3.2.1.2 Controls.** Terminal control is facilitated by the use of one dual-position switch (ONLINE) and six unencoded special function keys (HERE IS, CMD, BREAK, ENTER, PAPER ADV, and RESET). The control keys function as described below:

ONLINE—Switches the terminal between ONLINE and LOCAL Modes of operation. A change from LOCAL to ONLINE results in Data Terminal Ready, DTR (EIA circuit CD) being switched ON, and line communications being enabled unless a nonoperational status exists. A change from ONLINE to LOCAL causes DTR to switch OFF, and line communications are disabled

HERE IS—Causes the following to happen:

ONLINE—Transmits the characters programmed in the ABM.

LOCAL—Prints the ABM message when the terminal is configured to local print ABM.

CONFIGure—Terminates the ABM or LTA programming sequence.

CMD—Causes the terminal to enter the COM-MAND Mode.

BREAK—Causes the following action depending on the communications mode:

Full Duplex—Depression of the BREAK key causes XMIT DATA (EIA circuit BA) to hold to a SPACING (ON)

condition for a minimum of 256 msec. If the depression exceeds 256 msec., the SPACING condition is maintained for the duration of the depression.

Half Duplex—In the transmit mode, the operation of the BREAK key is similar to full duplex. In the receive mode, the BREAK key has no function. However, if LTA recognition is configured, and DCD (EIA circuit CF) switches OFF before LTA is received, then the depression of the BREAK key initiates the transition to the transmit mode.

Half Duplex with Reverse Channel-When in the receive mode, depression of the BREAK key causes EIA circuit SCA (Secondary Request to Send) to be switched OFF for 256 msec. or the duration of the depression, whichever is longer. RCVD DATA (EIA circuit BB) is monitored for received data until an LTA is received or DCD switches OFF. The following transition is to either transmit or idle mode depending upon whether or not LTA recognition is configured and DCD switches OFF before an LTA is received. Depression of the BREAK key initiates transition to the transmit mode.

DC Current Loop—Depression of the BREAK key causes the transmit circuit to issue the BREAK condition for 256 msec. or for the duration of the key depression, whichever is longer.

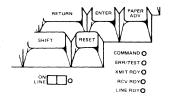

**3.2.1.3** Indicators. Six LED indicators are adjacent to the keyboard on the KSR operator's panel as shown in Figure 3-6. These indicators provide terminal status.

Figure 3-6. LED Indicators (783, 785, 787)

- ONLINE-This unlabeled indicator, adjacent to the ONLINE switch, is illuminated when DTR (EIA circuit CD) is ON and extinguished when DTR is OFF.

- COMMAND-This indicator, illuminated after the depression of the CMD key, indicates the terminal is in the COMMAND Mode. It remains illuminated until the COMMAND Mode is terminated.

Flashing of the COMMAND Mode indicator indicates that a request to enter the COMMAND Mode is pending. Flashing continues until the COMMAND Mode is entered.

ERR/TEST-This indicator has two functions. When flashing, the terminal has identified a reportable error or, when illuminated continuously, the terminal is in the TEST Mode. Depressing RESET extinguishes the indicator and prints the ERROR report. When both conditions exist

simultaneously, TEST has precedence over ERRor. Once TEST has been terminated with RESET, however, the ERRor condition is displayed until RESET is pressed.

- XMIT RDY-This indicator indicates the status of the terminal transmit capability as follows:

- ON—DTR, DSR, RTS, and CTS (EIA circuits CD, CC, CA and CB) and SCF (if required) are ON.

- FLASHING—DTR, DSR, and RTS (EIA circuits CD, CC, and CA) are ON but CTS (EIA circuit CB) or SCF (if required) is OFF.

- OFF-circuit DSR, DTR or RTS is OFF.

- RCV RDY-This indicator indicates the status of the terminal receive capability in conjunction with DCD (EIA circuit CF) as follows:

- ON—DTR, DSR, and DCD are ON in the receive mode.

- FLASHING—in the receive mode and DCD is OFF.

- OFF-not in the receive mode.

LINE RDY-This indicator indicates the status of DSR (EIA circuit CC) as follows:

ON-DTR and DSR are ON.

FLASHING—in the COMMAND Mode and DSR is ON.

OFF-DSR is OFF.

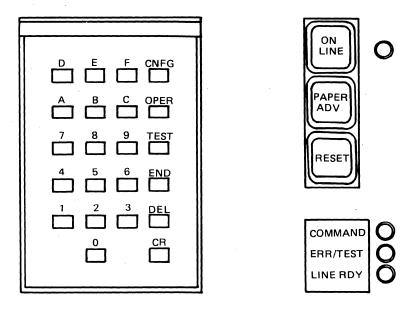

# 3.2.2 RO Operator's Panel

The RO operator's panel is shown in Figure 3-7. The panel includes the calculator-type keypad which has 16 code-generating keys (numerals 0

through 9 and letters A through F), six terminal control keys, and three operator control keys. The operator's panel also includes four LED indicators for reporting terminal status.

Figure 3-7. Operator's Keypad (781)

**3.2.2.1 Keypad Character Encoding.** The terminal uses the hexadecimal equivalent to generate all 128 ASCII characters. The ASCII characters are

encoded using a two-keystroke entry which represents the hexadecimal equivalent. Table 3-1 lists the ASCII/hexadecimal conversion codes.

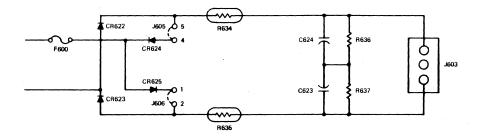

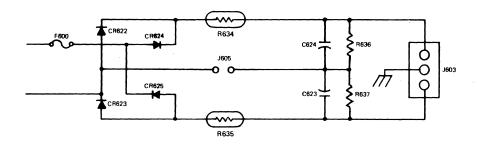

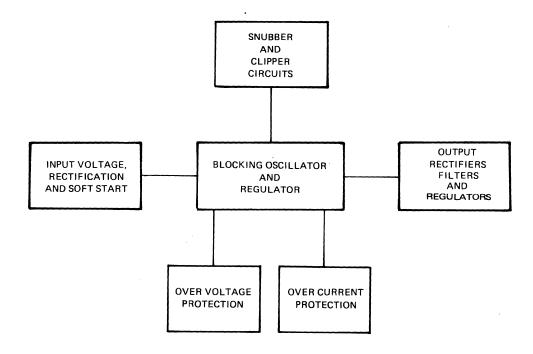

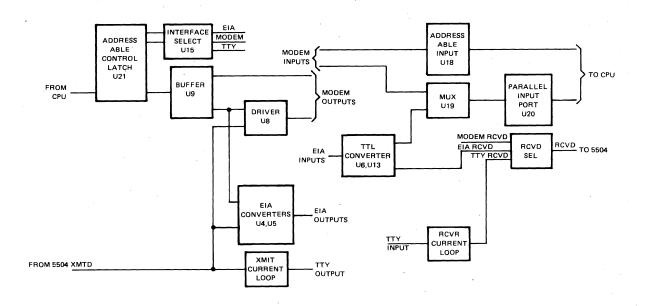

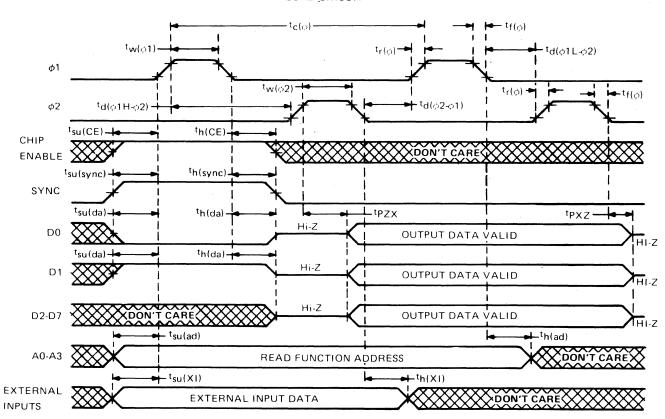

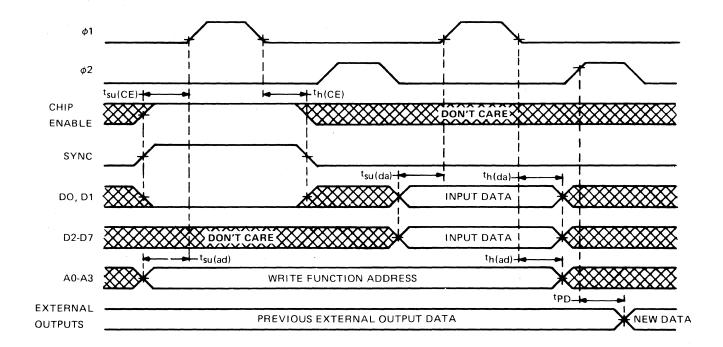

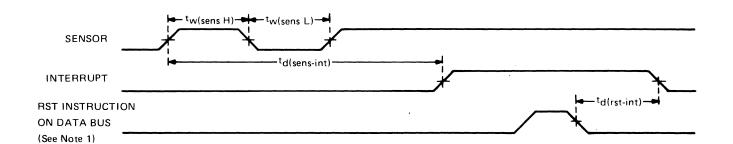

Table 3-1. ASCII/Hexadecimal Conversion Codes