| General Information                | 1 |

|------------------------------------|---|

| Data Transceivers/Multiplexers     | 2 |

| Address Buffers/Latches/Flip-Flops | 3 |

| <b>Clock-Distribution Circuits</b> | 4 |

| SDRAMs                             | 5 |

| Application Report                 | 6 |

| Mechanical Data                    | 7 |

## High-Speed Memory Interface Logic Data Book

## Address Drivers, Data Transceivers, Clock Drivers, and Synchronous DRAMs

#### INTRODUCTION

Texas Instruments (TI) Advanced System Logic group has a broad portfolio of devices designed for high-speed memory interfacing. Sections 2, 3, and 4–Data Transceivers/Multiplexers, Address Buffers/Latches/Flip-Flops, and Clock-Distribution Circuits–contain devices that have set the industry standards for fast propagation-delay speeds, bus hold, and low simultaneous-switching noise. Device families within this text include:

ALVC – One of the highest-performance 3.3-V bus-interface device families is ALVC. These specially designed 3.3-V products are processed in 0.6- $\mu$  CMOS technology, giving propagation of delays less than 3 ns, along with current drive of 24 mA and static power consumption of 40  $\mu$ A for bus-interface functions. The ALVC devices have bus-hold cells on inputs to eliminate the need for external pullup/pulldown resistors for floating inputs. The family also includes innovative functions with integrated series-damping resistors for memory interleaving, multiplexing, and interfacing to synchronous DRAMS.

SSTL – TI is the first to offer interface logic based on the new SSTL\_3 (stub series terminated logic) standard. With both an address driver and a clock driver that conform to this standard, TI continues to innovate logic for future generations of SDRAM.

LVT – The specially designed 3.3-V LVT family uses the latest 0.8- $\mu$  BiCMOS-process technology for bus-interface functions. LVT can provide up to 24 mA of drive, 4-ns propagation delays, and, in addition, consumes less than 100  $\mu$ A of standby current. The inputs have the bus-hold feature to eliminate the need for external pullup/pulldown resistors and I/Os that can tolerate up to 7 volts, which can allow them to act as 5-V/3.3-V translators.

ALB – The specially designed 3.3-V ALB family uses the latest in  $0.6-\mu$  technology for bus-interface functions. ALB provides 25 mA of drive at 3.3 V and boasts a maximum propagation delay of 2.2 ns, making it the fastest TI logic family to date. The inputs have clamping diodes to eliminate signal overshoot and undershoot.

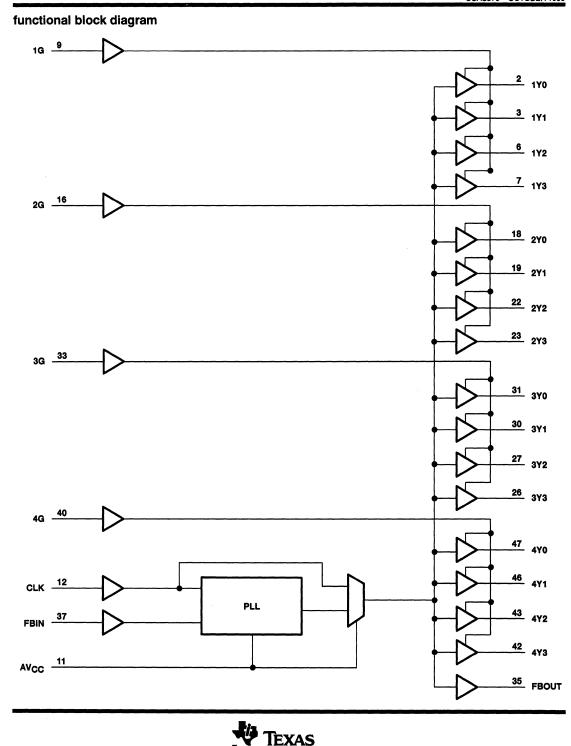

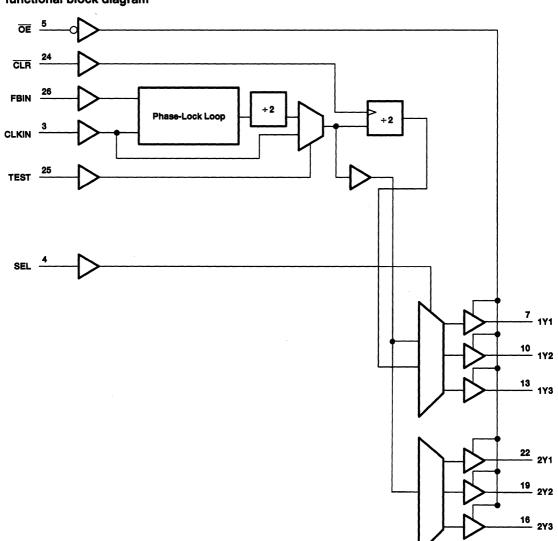

CDC – TI's CDCs provide accurate clock-generation circuitry fundamental to every digital system, producing timing signals that are used to synchronize system activity. To meet the stringent clock-signal timing requirements of today's systems, TI offers a series of low-propagation delay and skew, high-fan-out clock drivers designed to effectively drive high-performance clocking systems.

CBT – The CBT (crossbar technology) family is the industry's bus switch of choice. CBT enables a bus-interface device to function in one of two valuable roles. When the switch is closed, it is a very fast bus switch, effectively isolating buses. When the switch is open, it offers very little propagation delay. These devices can function as high-speed bus interfaces for computer-system components such as the central processing unit (CPU) and memory.

For more information on these or other TI products, please contact your local TI representative, authorized distributor, the TI technical support hotline at 972-644-5580, or visit the TI home page at http://www.ti.com.

For a complete listing of all TI logic products, please order the Logic Selection Guide (literature number SDYU001) by calling our literature response center at 1-800-477-8924.

۷

| Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 1 – General Information 1–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Alphanumeric Index       1-3         Glossary       1-5         Explanation of Function Tables       1-9         D Flip-Flop and Latch Signal Conventions       1-11         Thermal Information       1-12         Device Names and Package Designators       1-14         Section 2 – Data Transceivers/Multiplexers       2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Universal Bus Transceivers (UBT™)         2–3           SN74ALVCH16500         2–11           SN74ALVCH16501         2–19           SN74ALVCH16600         2–27           SN74ALVCH16601         2–35           SN74ALVCH162601         2–35           SN74ALVCH162601         2–43           SN54LVT16500, SN74LVT16500         2–53           SN54LVT16501, SN74LVT16501         2–61                                                                                                                                                                                                                                                                                                                                                                                                            |

| Multilevel Registered Transceivers         2-69           SN74ALVCH16524         2-77           SN74ALVCH16525         2-77           SN74ALVCH162525         2-85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Multiplexers         2–93           SN74ALVCH16260         2–101           SN74ALVCH162268         2–101           SN74ALVCH162268         2–109           SN74ALVCH16269         2–117           SN74ALVCH16270         2–133           SN74ALVCH16271         2–141           SN74ALVCH16272         2–145           SN74ALVCH16282         2–151           SN74ALVCH16282         2–155           SN74ALVCH16282         2–151           SN74ALVCH16282         2–155           SN74ALVCH16282         2–155           SN74ALVCH16282         2–155           SN74ALVCH16282         2–155           SN74ALVCH16282         2–155           SN74ALVCH16282         2–155           SN74ALVCH16282         2–157           SN74ALVCH162409         2–167           SN74ALVCH816233         2–175 |

| Section 3 – Address Buffers/Latches/Flip-Flops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8 Bit (1-to-4 fan-out)<br>SN74ALVCH16344                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9 Bit (1-to-4 fan-out)<br>SN74ALVCH16831                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10 Bit (1-to-2 fan-out)<br>SN74ALVCH16820                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## .

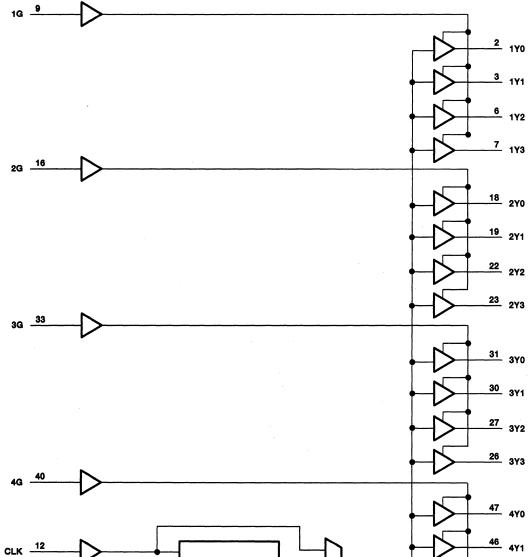

| Section 4 – Clock-Distribution Circuits          |  |

|--------------------------------------------------|--|

| CDC509                                           |  |

| CDC2509                                          |  |

| CDC516                                           |  |

| CDC2516                                          |  |

| CDC536                                           |  |

| CDC2536                                          |  |

| CDC582                                           |  |

| CDC2582                                          |  |

| CDC586                                           |  |

| CDC2586                                          |  |

| CDC587                                           |  |

| CDC2587                                          |  |

| Section 5 – SDRAMs                               |  |

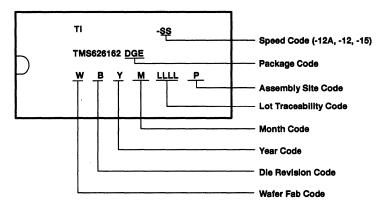

| TMS626162                                        |  |

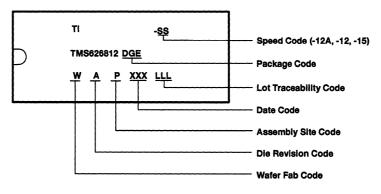

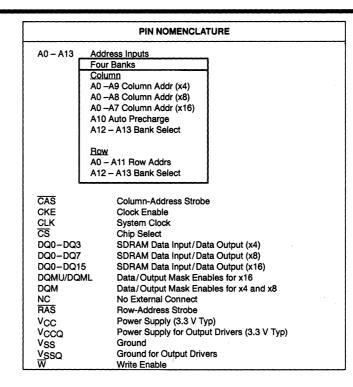

| TMS626812                                        |  |

| TMS664414, TMS664814, TMS664164                  |  |

| Section 6 – Application Report                   |  |

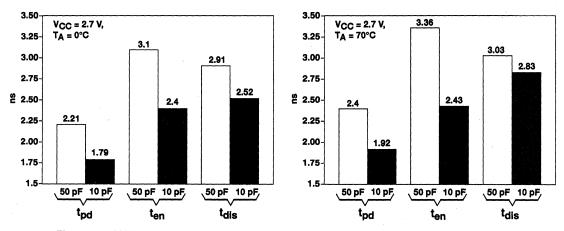

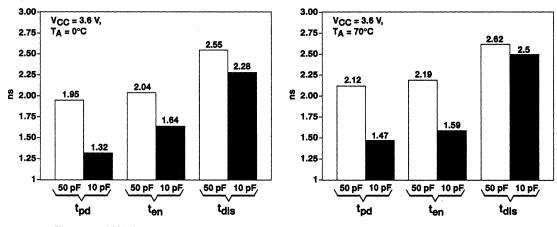

| Timing Differences of 10-pF Versus 50-pF Loading |  |

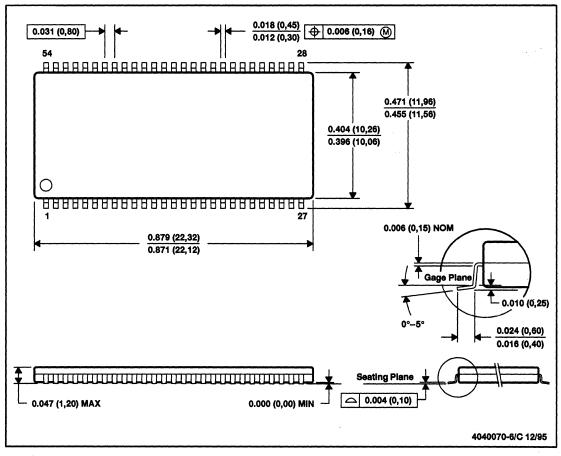

| Section 7 – Mechanical Data                      |  |

| Ordering Instructions                            |  |

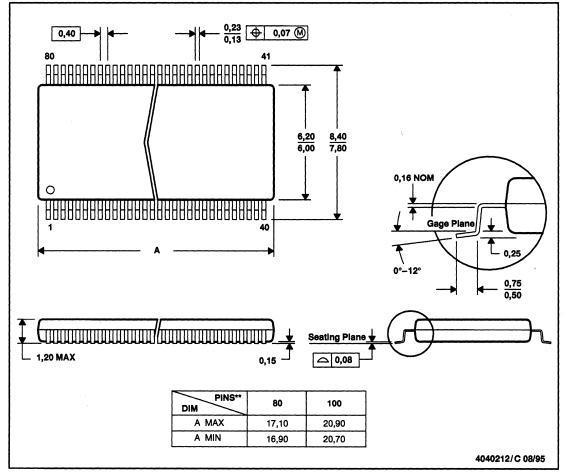

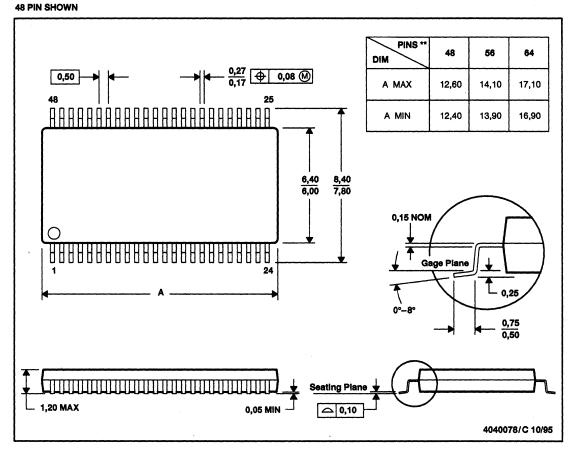

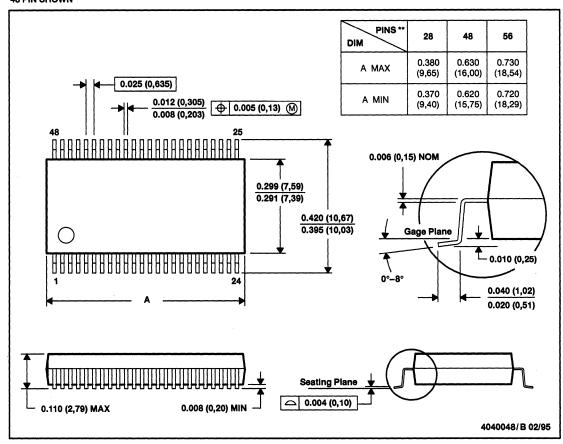

| DBB (R-PDSO-G**)                                 |  |

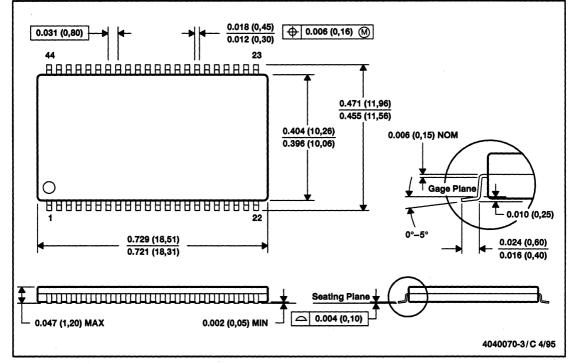

| DGE (R-PDSO-G50)                                 |  |

| DGG (R-PDSO-G**)                                 |  |

| DGV (R-PDSO-G**)                                 |  |

| DL (R-PDSO-G**)                                  |  |

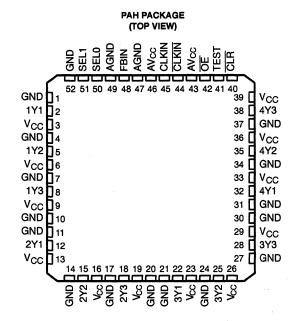

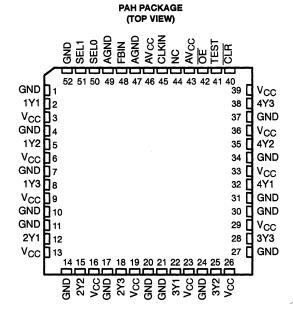

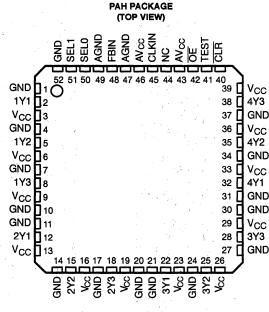

| PAH (S-PQFP-G52)                                 |  |

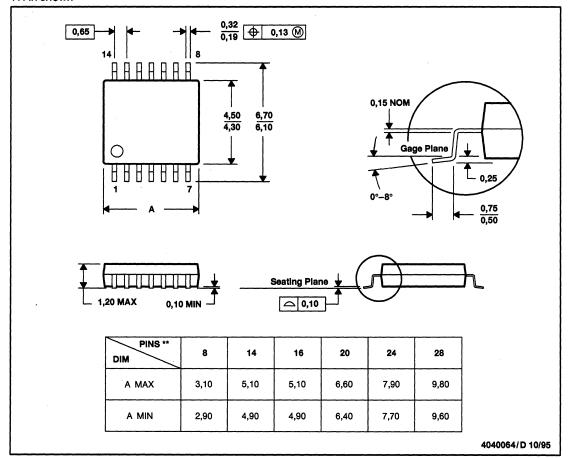

| PW (R-PDSO-G**)                                  |  |

ix

| General Information                | 1 |

|------------------------------------|---|

| Data Transceivers/Multiplexers     | 2 |

| Address Buffers/Latches/Flip-Flops | 3 |

| Clock-Distribution Circuits        | 4 |

| SDRAMS                             | 5 |

| Application Report                 | 6 |

| Mechanical Data                    | 7 |

## ALPHANUMERIC INDEX

| DEVICE PAGE          |

|----------------------|

| CDC509 4–3           |

| CDC516 4–15          |

| CDC536 4–31          |

| CDC582 4-49          |

| CDC586 4–69          |

| CDC587 4–89          |

| CDC2509 4–9          |

| CDC2516 4–23         |

| CDC2536 4-41         |

| CDC2582 4–59         |

| CDC2586 4–79         |

| CDC2587 4–97         |

| SN74ALB16244 3-57    |

| SN74ALVCH16244 3-63  |

| SN74ALVCH16260 2–93  |

| SN74ALVCH16269 2-117 |

| SN74ALVCH16270 2–133 |

| SN74ALVCH16271 2–141 |

| SN74ALVCH16272 2–145 |

| SN74ALVCH16282 2–151 |

| SN74ALVCH16334 3-49  |

| SN74ALVCH16344 3–3   |

| SN74ALVCH16373 3–105 |

| SN74ALVCH16374 3–121 |

| SN74ALVCH16409 2–159 |

| SN74ALVCH16500 2–3   |

| SN74ALVCH16501 2–11  |

| SN74ALVCH16524 2–69  |

| SN74ALVCH16525 2–77  |

| SN74ALVCH16600 2–19  |

| SN74ALVCH16601 2–27  |

| SN74ALVCH16721 3–217 |

| SN74ALVCH16820       |

| SN74ALVCH16821       |

| SN74ALVCH16823 3–161 |

| SN74ALVCH16825 3–151 |

| SN74ALVCH16827 3–197 |

| DEVICE                                                       | PAGE  |

|--------------------------------------------------------------|-------|

| SN74ALVCH16830                                               | 3–171 |

| SN74ALVCH16831                                               | 3–19  |

| SN74ALVCH16835                                               | 3–137 |

| SN74ALVCH16836                                               | 3–183 |

| SN74ALVCH16841                                               | 3–209 |

| SN74ALVCH16843                                               | 3–157 |

| SN74ALVCH16901                                               | 2–43  |

| SN74ALVCH162244                                              | 3–69  |

| SN74ALVCH162260                                              | 2–101 |

| SN74ALVCH162268                                              | 2–109 |

| SN74ALVCH162344                                              | 3–11  |

| SN74ALVCH162525                                              | 2–85  |

| SN74ALVCH162601                                              | 2–35  |

| SN74ALVCH162721                                              | 3–223 |

| SN74ALVCH162820                                              | 3-41  |

| SN74ALVCH162827                                              |       |

| SN74ALVCH162830/                                             |       |

| SN74ALVCH162831                                              |       |

| SN74ALVCHR162269                                             |       |

| SN74ALVCHR162409                                             |       |

| SN54ALVTH16244 SN74ALVTH16244                                |       |

| SN54ALVTH162244 SN74ALVTH162244                              |       |

| SN74CBT16232                                                 |       |

| SN74CBT16233                                                 |       |

| SN54LVT16500 SN74LVT16500                                    |       |

| SN54LVT16501 SN74LVT16501                                    |       |

| SN74LVT16835                                                 |       |

| SN54LVTH16244A SN74LVTH16244A                                |       |

| SN54LVTH16373 SN74LVTH16373                                  |       |

| SN54LVTH16374 SN74LVTH16374<br>SN54LVTH162244 SN74LVTH162244 |       |

| SN54LVTH162244 SN74LVTH162244<br>SN74SSTL16837               | 3-99  |

| TMS626162                                                    |       |

| TMS626102                                                    |       |

| TMS620612                                                    |       |

| TMS664414                                                    |       |

| TMS664814                                                    |       |

| (WJ004014                                                    | 0-93  |

## INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

## operating conditions and characteristics (in sequence by letter symbols)

C<sub>i</sub> Input capacitance

The internal capacitance at an input of the device

Cio Input/output capacitance

Input-to-output internal capacitance; transcapacitance

### Co Output capacitance

The internal capacitance at an output of the device

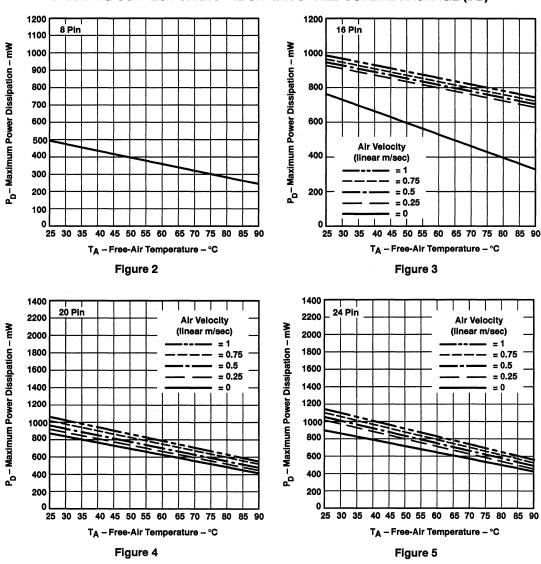

## C<sub>pd</sub> Power dissipation capacitance

Used to determine the no-load dynamic power dissipation per logic function (see individual circuit pages):  $P_D = C_{pd} V_{CC}^2 f + I_{CC} V_{CC}$

## fmax Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification

### I<sub>CC</sub> Supply current

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit

## △I<sub>CC</sub> Supply current change

The increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V or  $V_{CC}$

### ICEX Output high leakage current

The maximum leakage current into the collector of the pulldown output transistor when the output is high and the output forcing condition  $V_{O}$  = 5.5 V

## II(hold) Input hold current

Input current that holds the input at the previous state when the driving device goes to a high-impedance state

## IIH High-level input current

The current into\* an input when a high-level voltage is applied to that input

### IIL Low-level input current

The current into\* an input when a low-level voltage is applied to that input

## Input/output power-off leakage current

The current into a circuit mode when the device or a portion of the device affecting that circuit node is in the off state

#### IOH High-level output current

The current into\* an output with input conditions applied that, according to the product specification, establish a high level at the output

\*Current out of a terminal is given as a negative value.

#### t<sub>PHL</sub> Propagation delay time, high-to-low level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level

## t<sub>PHZ</sub> Disable time (of a 3-state output) from high level

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined high level to the high-impedance (off) state

#### tPLH Propagation delay time, low-to-high level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level

#### tpLZ Disable time (of a 3-state output) from low level

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined low level to the high-impedance (off) state

#### t<sub>PZH</sub> Enable time (of a 3-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from the high-impedance (off) state to the defined high leve

#### tpzL Enable time (of a 3-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from the high-impedance (off) state to the defined low level

## t<sub>sk(I)</sub> Input skew

The difference between any two propagation delay times that originate at different inputs and terminate at a single output. Input skew describes the ability of a device to manipulate (stretch, shrink, or chop) a clock signal. This is typically accomplished with a multiple-input gate wherein one of the inputs acts as a controlling signal to pass the clock through.  $t_{sk(l)}$  describes the ability of the gate to shape the pulse to the same duration regardless of the input used as the controlling input.

## t<sub>sk(I)</sub> Limit skew

The difference between 1) the greater of the maximum specified values of  $t_{PLH}$  and  $t_{PHL}$  and 2) the lesser of the minimum specified values of  $t_{PLH}$  and  $t_{PHL}$ . Limit skew is not directly observed on a device but rather is calculated from the data sheet limits for  $t_{PLH}$  and  $t_{PHL}$ .  $t_{sk(i)}$  quantifies for the designer how much variation in propagation delay time will be induced by operation over the entire ranges of supply voltage, temperature, output load, and other specified operating conditions. Specified as such,  $t_{sk(i)}$  also accounts for process variation. In fact, all other skew specifications [ $t_{sk(o)}$ ,  $t_{sk(i)}$ ,  $t_{sk(p)}$ , and  $t_{sk(pr)}$ ] are subsets of  $t_{sk(i)}$ ; they are never greater than  $t_{sk(i)}$ .

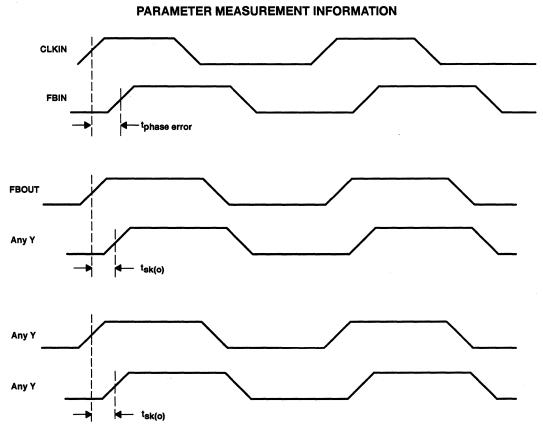

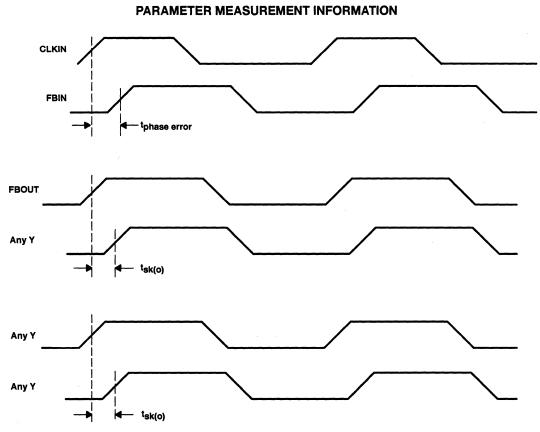

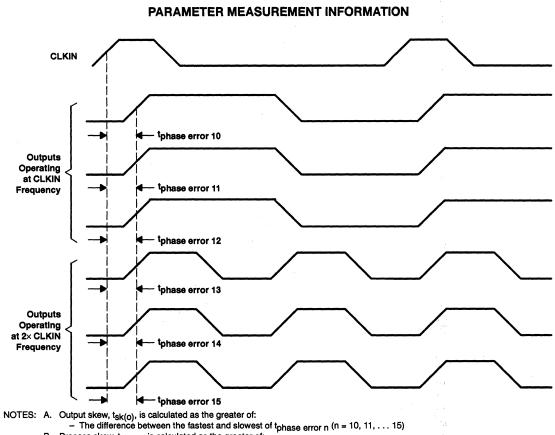

## t<sub>sk(o)</sub> Output Skew

The difference between any two propagation delay times when a single switching input or multiple inputs switching simultaneously cause multiple outputs to switch, as observed across all switching outputs. This parameter is used to describe the fanout capability of a clock driver and is of concern when making decisions on clock buffering and distribution networks.

## t<sub>sk(p)</sub> Puise Skew

The difference between propagation delay times  $t_{PHL}$  and  $t_{PLH}$  when a single switching input causes one or more outputs to switch.  $t_{sk(p)}$  quantifies the duty cycle characteristic of a clock driver. Certain applications require a fixed duty cycle for proper operation. As an example, the CLK2 input of an MC68020 processor operating at 40 MHz requires a duty cycle of 50  $\pm$  5%.  $t_{sk(p)}$  is a measure of a clock driver's ability to supply such a precisely controlled pulse.

## **EXPLANATION OF FUNCTION TABLES**

The following symbols are used in function tables on TI data sheets:

- H = high level (steady state)

- L = low level (steady state)

- ↑ = transition from low to high level

- = transition from high to low level

- ---- = value/level or resulting value/level is routed to indicated destination

- = value/level is re-entered

- X = irrelevant (any input, including transitions)

- Z = off (high-impedance) state of a 3-state output

- a...h = the level of steady-state inputs A through H respectively

- Q0 = level of Q before the indicated steady-state input conditions were established

- $\overline{Q}_0$  = complement of  $Q_0$  or level of  $\overline{Q}$  before the indicated steady-state input conditions were established

- $Q_n$  = level of Q before the most recent active transition indicated by  $\downarrow$  or  $\uparrow$

- \_\_\_\_ = one high-level pulse

- = one low-level pulse

- Toggle = each output changes to the complement of its previous level on each active transition indicated by  $\downarrow$  or  $\uparrow$

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

If, in the input columns, a row contains H, L, and/or X together with  $\uparrow$  and/or  $\downarrow$ , this means the output is valid whenever the input configuration is achieved but the transition(s) must occur following the achievement of the steady-state levels. If the output is shown as a level (H, L, Q<sub>0</sub>, or  $\overline{Q}_0$ ), it persists so long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. (If the output is shown as a pulse,  $\neg \neg$  or  $\neg \neg$ , the pulse follows the indicated input transition and persists for an interval dependent on the circuit.)

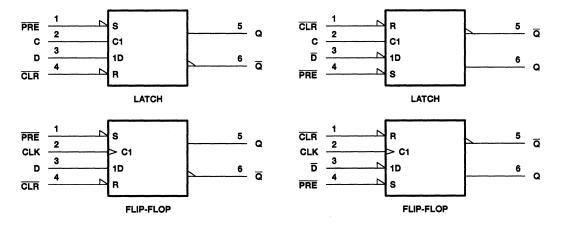

## D FLIP-FLOP AND LATCH SIGNAL CONVENTIONS

It is normal TI practice to name the outputs and other inputs of a D-type flip-flop or latch and to draw its logic symbol based on the assumption of true data (D) inputs. Outputs that produce data in phase with the data inputs are called Q and those producing complementary data are called  $\overline{Q}$ . An input that causes a Q output to go high or a  $\overline{Q}$  output to go low is called preset (PRE). An input that causes a  $\overline{Q}$  output to go high or a Q output to go low is called clear (CLR). Bars are used over these pin names (PRE and CLR) if they are active low.

The devices on several data sheets are second-source designs, and the pin name conventions used by the original manufacturers have been retained. That makes it necessary to designate the inputs and outputs of the inverting circuits  $\overline{D}$  and Q.

In some applications, it may be advantageous to redesignate the data input from D to  $\overline{D}$  or vice versa. In that case, all the other inputs and outputs should be renamed as shown below. Also shown are corresponding changes in the graphical symbols. Arbitrary pin numbers are shown.

The figures show that when Q and  $\overline{Q}$  exchange names, the preset and clear pins also exchange names. The polarity indicators ( $\square$ ) on PRE and CLR remain, as these inputs are still active low, but the presence or absence of the polarity indicator changes at D (or  $\overline{D}$ ), Q, and  $\overline{Q}$ . Pin 5 (Q or  $\overline{Q}$ ) is still in phase with the data input (D or  $\overline{D}$ ); their active levels change together.

| General Information                | 1 |

|------------------------------------|---|

| Data Transceivers/Multiplexers     | 2 |

| Address Buffers/Latches/Flip-Flops | 3 |

| Clock-Distribution Circuits        | 4 |

| SDRAMs                             | 5 |

| Application Report                 | 6 |

| Mechanical Data                    | 7 |

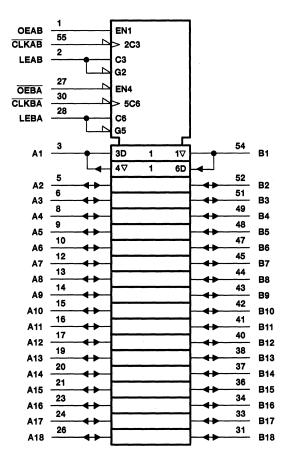

## SN74ALVCH16500 18-BIT UNIVERSAL BUS TRANSCEIVER WITH 3-STATE OUTPUTS

SCES023C - JULY 1995 - REVISED NOVEMBER 1996

|           | nber of the Texas Instruments<br><i>Jebus</i> ™ Family       | DGG OR DL<br>(TOP )  |                      |

|-----------|--------------------------------------------------------------|----------------------|----------------------|

|           | /C™ (Enhanced-Performance Implanted<br>OS) Submicron Process |                      | 56 GND               |

|           | 7™ (Universal Bus Transceiver)                               |                      | 54 B1                |

|           | nbines D-Type Latches and D-Type                             | GND 14               | 53 GND               |

|           | -Flops for Operation in Transparent,                         | A2 1 5               | 52 B2                |

| Late      | ched, or Clocked Mode                                        | A2 U3<br>A3 [] 6     | 51 B3                |

| • ESI     | D Protection Exceeds 2000 V Per                              |                      | 50 V <sub>CC</sub>   |

| MIL       | -STD-883, Method 3015; Exceeds                               |                      | 49 B4                |

|           | V Using Machine Model                                        | A5 0 9               | 49 B5                |

| (C =      | = 200 pF, R = 0)                                             |                      | 47 B6                |

| Late      | ch-Up Performance Exceeds 250 mA Per                         |                      |                      |

| JED       | DEC Standard JESD-17                                         | A7 0 12              | 45 B7                |

| Bus       | s Hold on Data Inputs Eliminates the                         | A8 1 13              | 44 B8                |

|           | ed for External Pullup/Pulldown                              | A9 11 14             | 43 B9                |

|           | sistors                                                      | A10 15               | 42 B10               |

| Pac       | kage Options Include Plastic 300-mil                         | A11 1 16             | 41 B11               |

|           | ink Small-Outline (DL) and Thin Shrink                       | A12 17               | 40 B12               |

|           | all-Outline (DGG) Packages                                   | GND 18               | 39 🛛 GND             |

|           |                                                              | A13 🚺 19             | 38 🛛 B13             |

| descripti | ion                                                          | A14 🚺 20             | 37 🚺 B14             |

|           |                                                              | A15 🛛 21             | 36 🛛 B15             |

|           | 18-bit universal bus transceiver is designed                 | V <sub>CC</sub> 🛛 22 | 35 🛛 V <sub>CC</sub> |

| tor 2.    | .3-V to 3.6-V V <sub>CC</sub> operation.                     | A16 23               | 34 B16               |

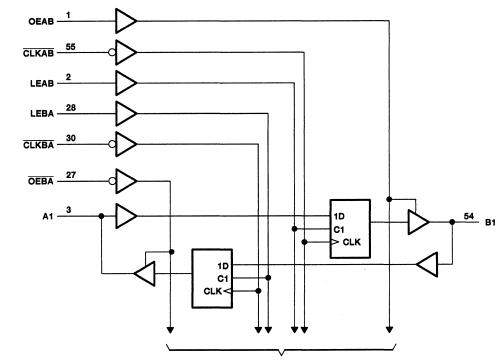

| Data      | flow in each direction is controlled by                      | A17 🚺 24             | 33 🛛 B17             |

|           | ut-enable (OEAB and OEBA), latch-enable                      | GND 🚺 25             | 32 🛛 GND             |

|           | B and LEBA), and clock (CLKAB and                            | A18 🚺 26             | 31 B18               |

|           | BA) inputs. For A-to-B data flow, the device                 | OEBA 🚺 27            | 30 CLKBA             |

| opera     | ates in the transparent mode when LEAB is                    | LEBA 🚺 28            | 29 GND               |

is low, the A-bus data is stored in the latch/flip-flop on the high-to-low transition of CLKAB. Output-enable OEAB is active high. When OEAB is high, the B-port outputs are active. When OEAB is low, the B-port outputs are in the high-impedance state.

Data flow for B to A is similar to that of A to B but uses OEBA, LEBA, and CLKBA. The output enables are complementary (OEAB is active high, and OEBA is active low).

To ensure the high-impedance state during power up or power down,  $\overline{\text{OEBA}}$  should be tied to  $V_{CC}$  through a pullup resistor and OEAB should be tied to GND through a pulldown resistor; the minimum value of the resistor is determined by the current-sinking/current-sourcing capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

The SN74ALVCH16500 is available in TI's shrink small-outline (DL) and thin shrink small-outline (DGG) packages, which provide twice the I/O pin count and functionality of standard small-outline packages in the same printed circuit board area.

The SN74ALVCH16500 is characterized for operation from -40°C to 85°C.

EPIC, UBT, and Widebus are trademarks of Texas Instruments Incorporated.

high. When LEAB is low, the A data is latched if CLKAB is held at a high or low logic level. If LEAB

PRODUCTION DATA information is current as of publication date. Products conform to specifications par the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1996, Texas Instruments Incorporated

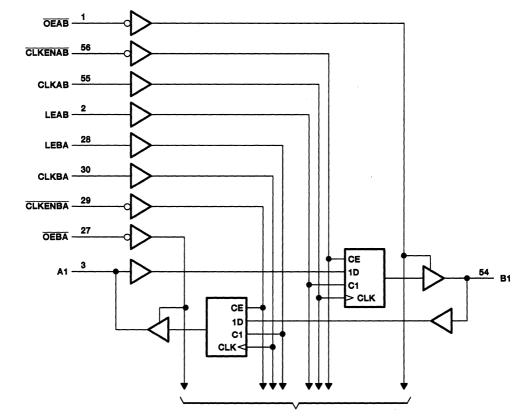

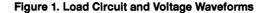

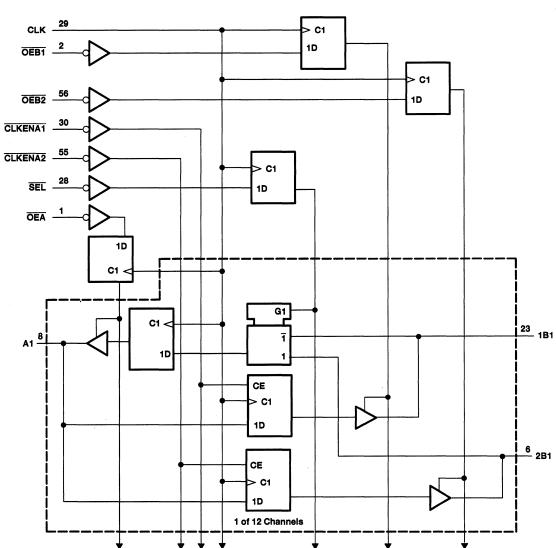

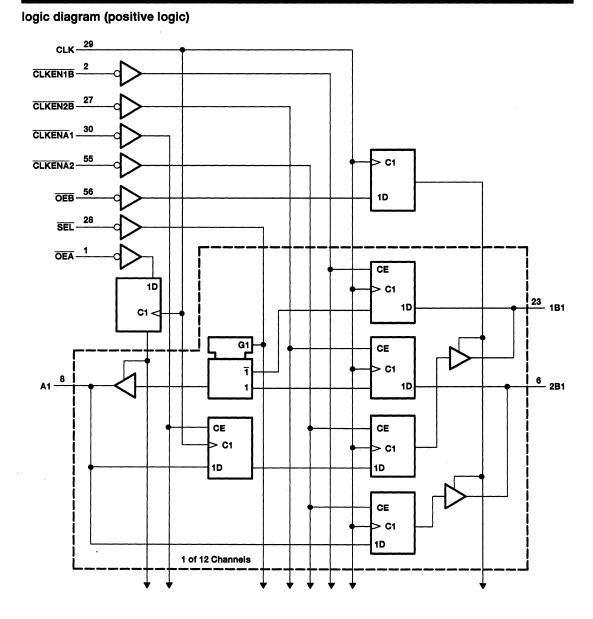

## SN74ALVCH16500 **18-BIT UNIVERSAL BUS TRANSCEIVER** WITH 3-STATE OUTPUTS SCES023C - JULY 1995 - REVISED NOVEMBER 1996

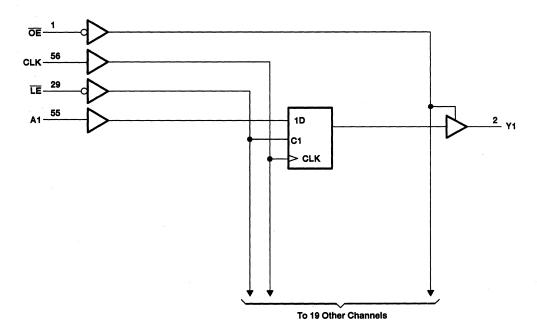

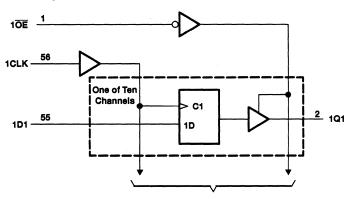

To 17 Other Channels

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub>                                                     | -0.5 V to 4.6 V                   |

|-------------------------------------------------------------------------------------------|-----------------------------------|

| Input voltage range, VI: Except I/O ports (see Note 1)                                    |                                   |

|                                                                                           |                                   |

| I/O ports (see Notes 1 and 2)                                                             |                                   |

| Output voltage range, V <sub>O</sub> (see Notes 1 and 2)                                  | –0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, IIK (VI < 0)                                                         | –50 mA                            |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{CC}$ )                            | ±50 mA                            |

| Continuous output current, $I_O (V_O = 0 \text{ to } V_{CC})$                             |                                   |

| Continuous current through each V <sub>CC</sub> or GND                                    |                                   |

| Maximum power dissipation at $T_A = 55^{\circ}C$ (in still air) (see Note 3): DGG package |                                   |

|                                                                                           | 1.4 W                             |

| Storage temperature range, T <sub>stg</sub>                                               |                                   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamo-current ratings are observed.

- This value is limited to 4.6 V maximum. 2.

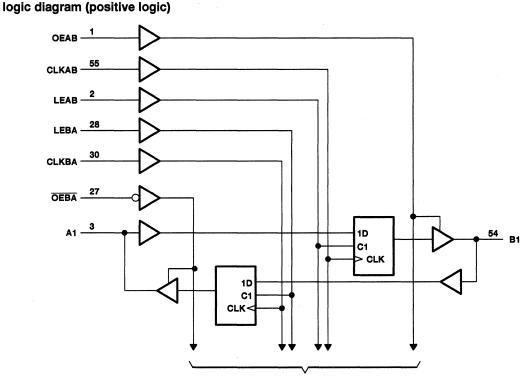

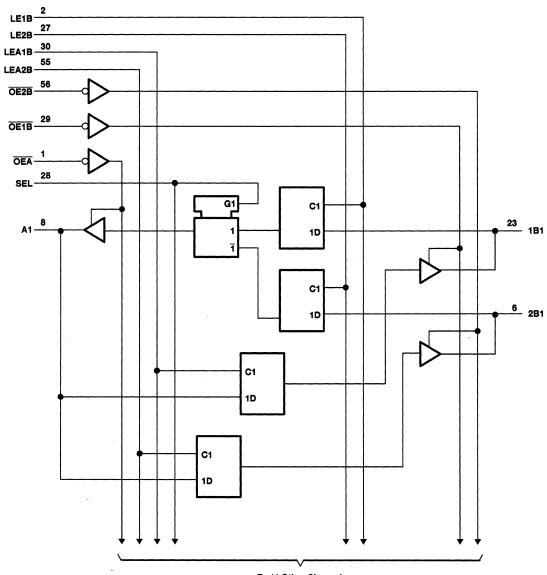

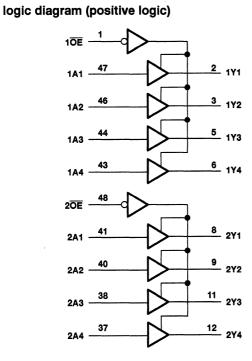

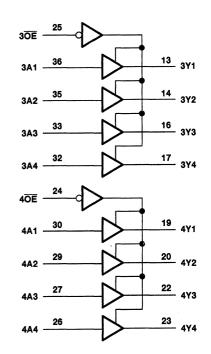

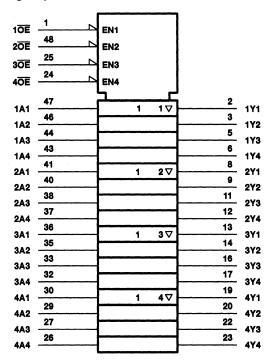

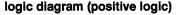

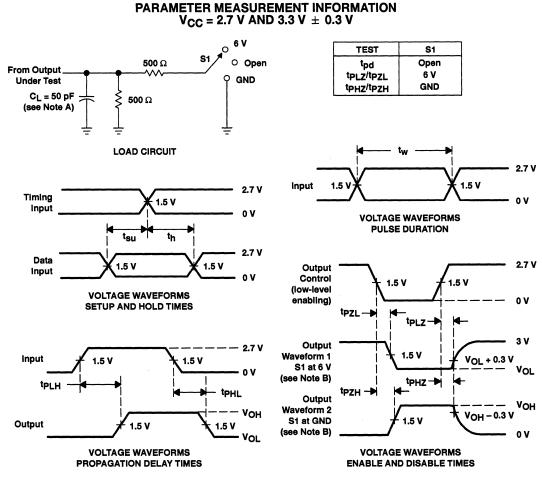

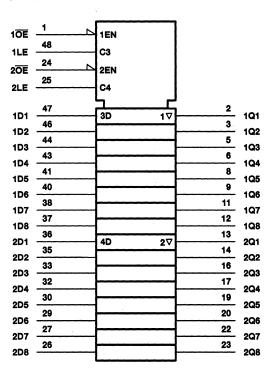

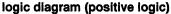

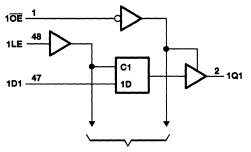

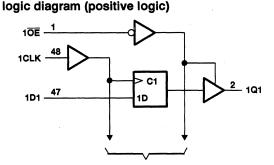

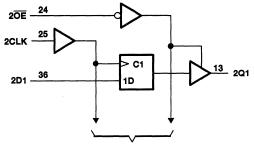

logic diagram (positive logic)

The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils. 3. For more information, refer to the Package Thermal Considerations application note in the ABT Advanced BiCMOS Technology Data Book.

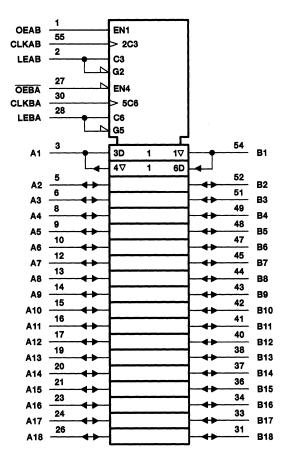

## SN74ALVCH16500 18-BIT UNIVERSAL BUS TRANSCEIVER WITH 3-STATE OUTPUTS SCES023C - JULY 1995 - REVISED NOVEMBER 1996

timing requirements over recommended operating free-air temperature range (unless otherwise noted)

|                 |                  |                                        |     | $\begin{array}{c c} 2.5 \ V \\ 0.2 \ V \\ \end{array}  \begin{array}{c c} V \\ V_{CC} = 2.7 \ V \\ \pm \ 0.3 \ V \\ \end{array}  \begin{array}{c c} V_{CC} = 3.3 \ V \\ \pm \ 0.3 \ V \\ \end{array}$ |     | V <sub>CC</sub> = 2.7 V |     | V <sub>CC</sub> = 3.3 V<br>± 0.3 V |     |

|-----------------|------------------|----------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------|-----|------------------------------------|-----|

|                 |                  |                                        | MIN | MAX                                                                                                                                                                                                   | MIN | MAX                     | MIN | MAX                                |     |

| fclock          | Clock frequency  |                                        | 0   | 150                                                                                                                                                                                                   | 0   | 150                     | 0   | 150                                | MHz |

|                 | D. has also that | LE high                                | 3.3 |                                                                                                                                                                                                       | 3.3 |                         | 3.3 |                                    |     |

| tw              | Pulse duration   | CLK high or low                        | 3.3 |                                                                                                                                                                                                       | 3.3 |                         | 3.3 |                                    | ns  |

|                 |                  | Data before $\overline{CLK}\downarrow$ | 1.7 |                                                                                                                                                                                                       | 1.4 |                         | 1.3 |                                    |     |

| t <sub>su</sub> | Setup time       | Data before LE↓, CLK high              | 1.1 |                                                                                                                                                                                                       | 1   |                         | 1   |                                    | ns  |

|                 |                  | Data before LE↓, CLK low               | 1.9 |                                                                                                                                                                                                       | 1.6 |                         | 1.4 |                                    | ,   |

| th              |                  | Data after CLK↓                        | 1.7 |                                                                                                                                                                                                       | 1.6 |                         | 1.3 |                                    |     |

|                 | Hold time        | Data after LE↓, CLK high               | · 2 |                                                                                                                                                                                                       | 1.8 |                         | 1.5 |                                    | ns  |

|                 |                  | Data after LE↓, CLK low                | 1.6 |                                                                                                                                                                                                       | 1.5 |                         | 1.2 |                                    |     |

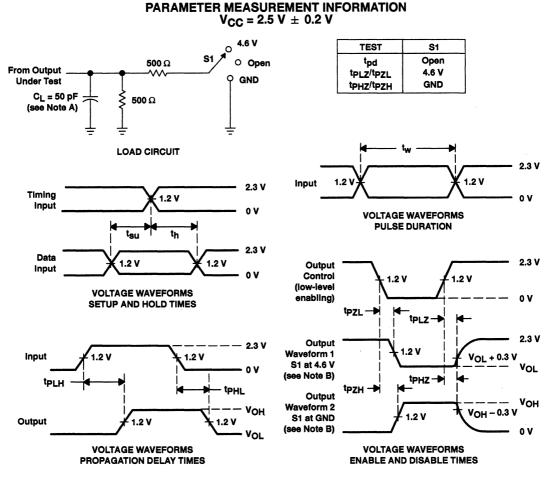

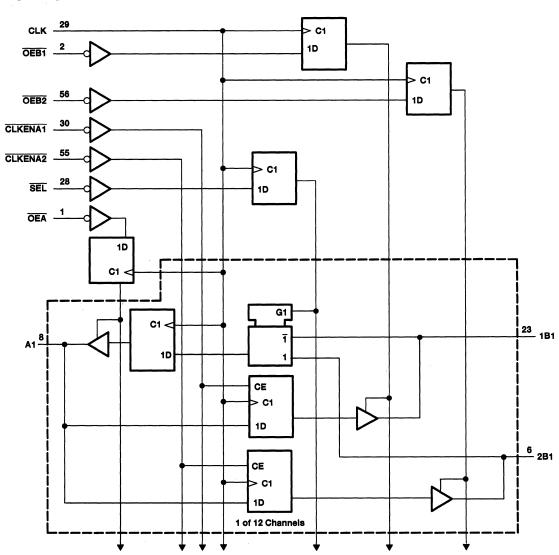

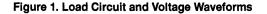

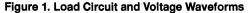

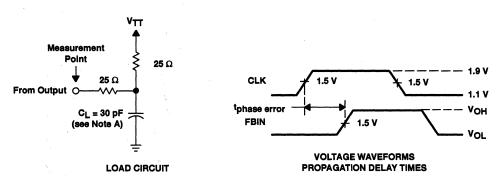

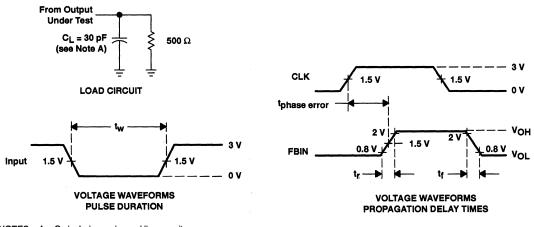

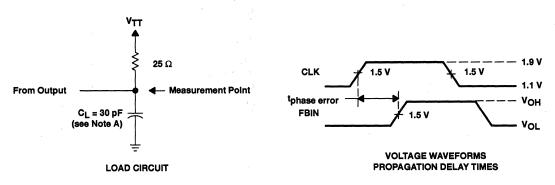

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted) (see Figures 1 and 2)

| PARAMETER        | FROM           | TO<br>(OUTPUT) | V <sub>CC</sub> = 2.5 V<br>± 0.2 V |     | V <sub>CC</sub> = 2.7 V |     | V <sub>CC</sub> = 3.3 V<br>± 0.3 V |     | UNIT |

|------------------|----------------|----------------|------------------------------------|-----|-------------------------|-----|------------------------------------|-----|------|

|                  | (INPUT)        | (001901)       | MIN                                | MAX | MIN                     | MAX | MIN                                | MAX |      |

| fmax             |                |                | 150                                |     | 150                     |     | 150                                |     | MHz  |

|                  | A or B         | B or A         | 1                                  | 5.7 |                         | 4.7 | 1                                  | 3.9 |      |

| <sup>t</sup> pd  | LEAB or LEBA   | A or B         | 1                                  | 6.5 |                         | 5.5 | 1                                  | 4.7 | ns   |

|                  | CLKAB or CLKBA | A or B         | 1                                  | 7.2 |                         | 6.6 | 1.1                                | 5.5 |      |

| t <sub>en</sub>  | OEAB           | B              | 1                                  | 6.2 |                         | 5.4 | 1                                  | 4.6 | ns   |

| tdis             | OEAB           | В              | 1.7                                | 6.3 |                         | 5.7 | 1.5                                | 5   | ns   |

| ten              | OEBA           | А              | 1                                  | 6.7 |                         | 6.2 | 1                                  | 5.2 | ns   |

| <sup>t</sup> dis | OEBA           | A              | 1                                  | 5.6 |                         | 4.6 | 1                                  | 4.3 | ns   |

## operating characteristics, T<sub>A</sub> = 25°C

|     | PARAMETER                     |                  | TEST CONDITIONS                    | V <sub>CC</sub> = 2.5 V<br>± 0.2 V | V <sub>CC</sub> = 3.3 V<br>± 0.3 V | UNIT |

|-----|-------------------------------|------------------|------------------------------------|------------------------------------|------------------------------------|------|

|     |                               |                  |                                    | TYP                                | TYP                                |      |

|     | Power dissipation capacitance | Outputs enabled  | C <sub>L</sub> = 50 pF, f = 10 MHz | 40                                 | 51                                 |      |

| Cpd | Power dissipation capacitance | Outputs disabled |                                    | 6                                  | 6                                  | pF   |

## SN74ALVCH16500 **18-BIT UNIVERSAL BUS TRANSCEI** WITH 3-STATE OUTPUTS

SCES023C - JULY 1995 - REVISED NOVEMBER 1996

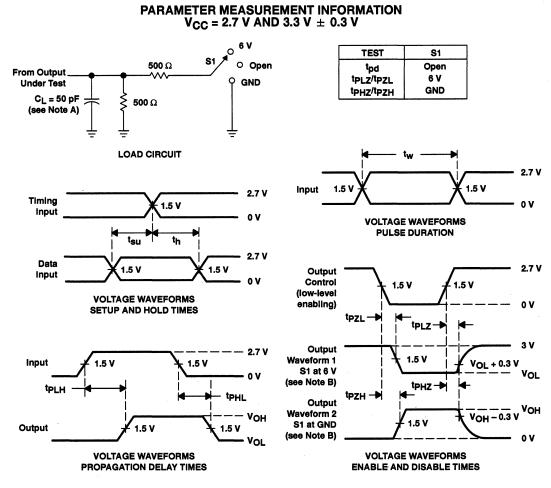

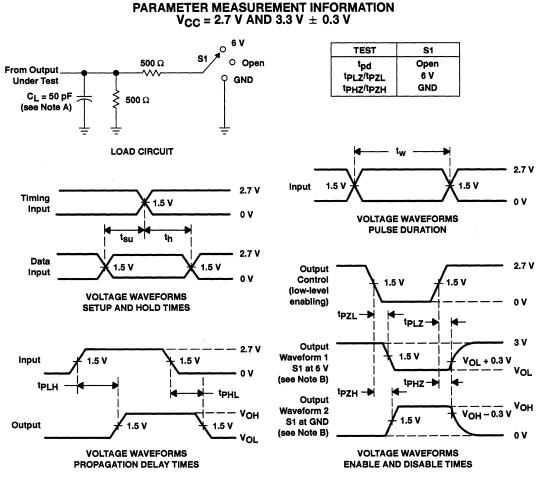

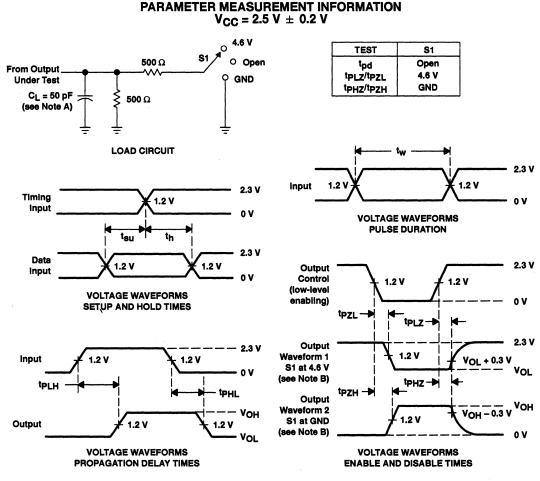

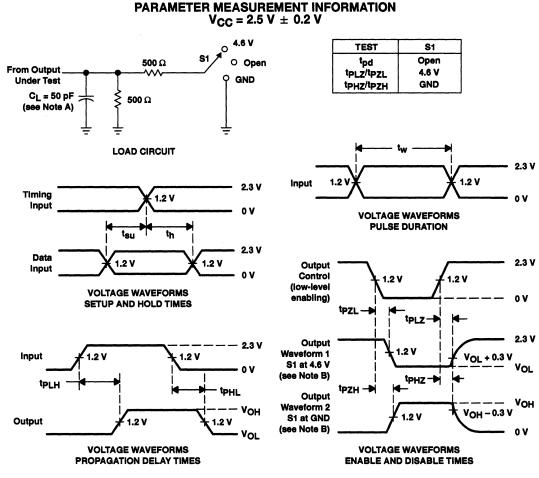

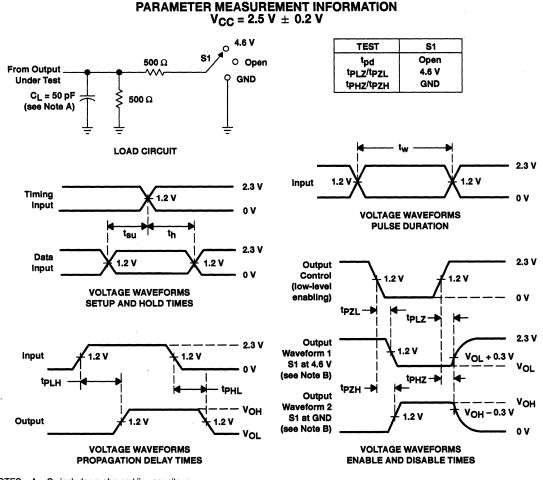

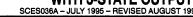

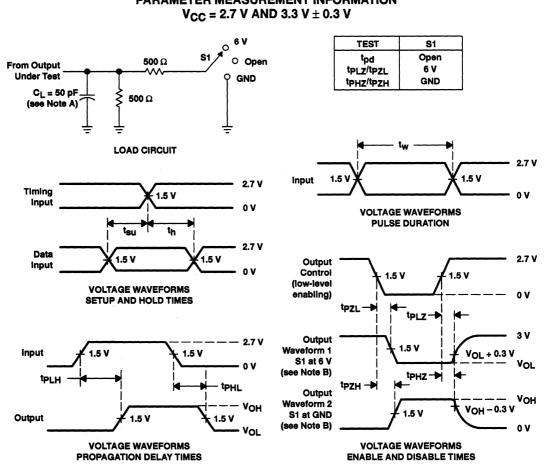

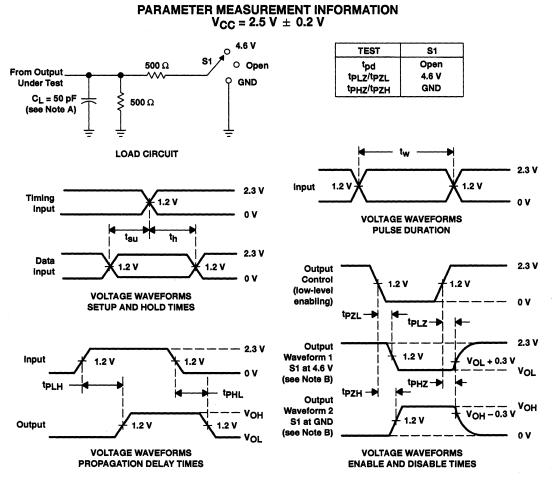

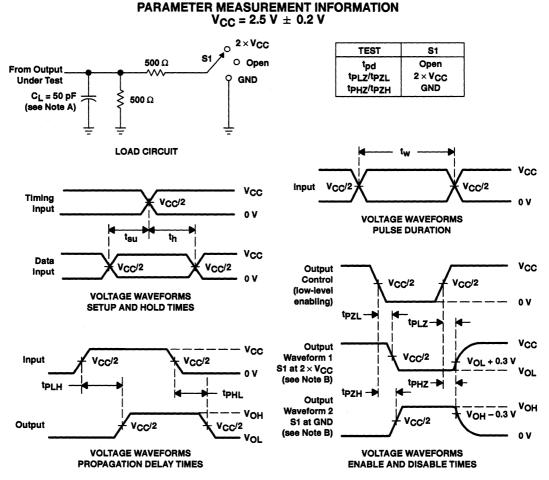

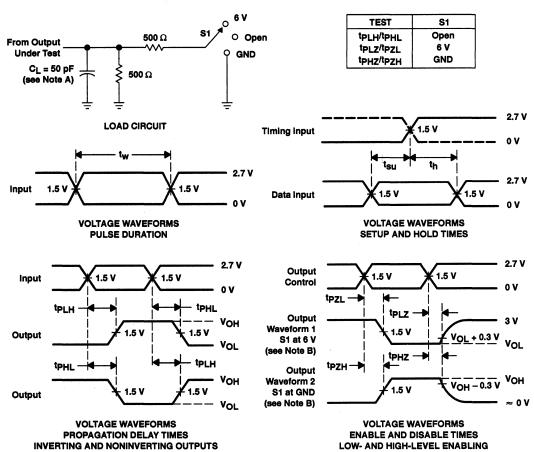

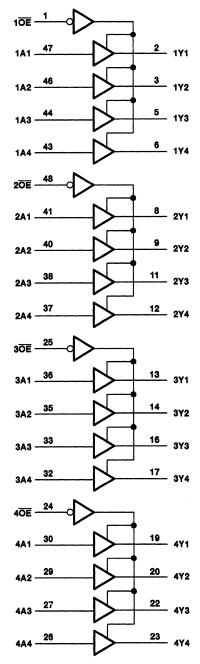

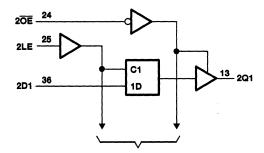

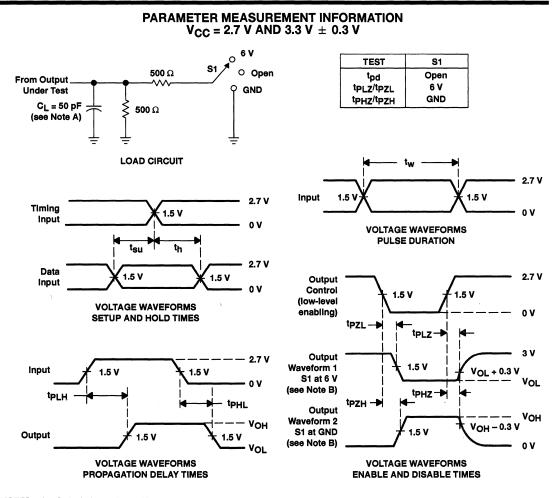

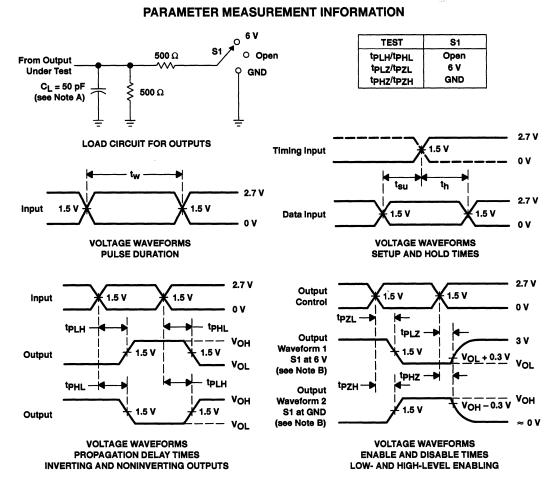

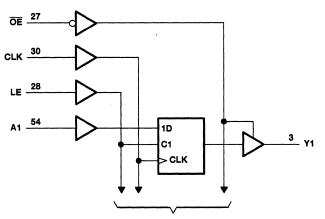

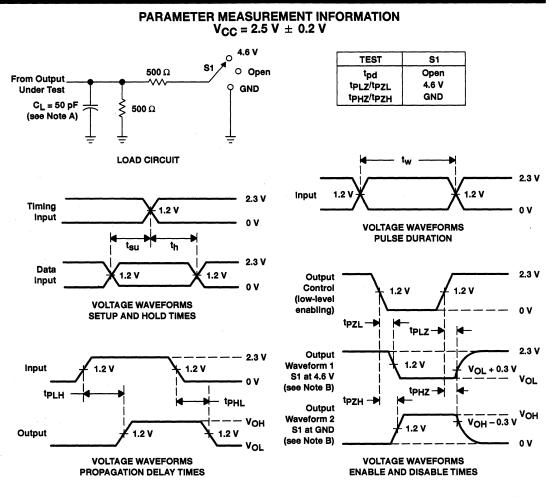

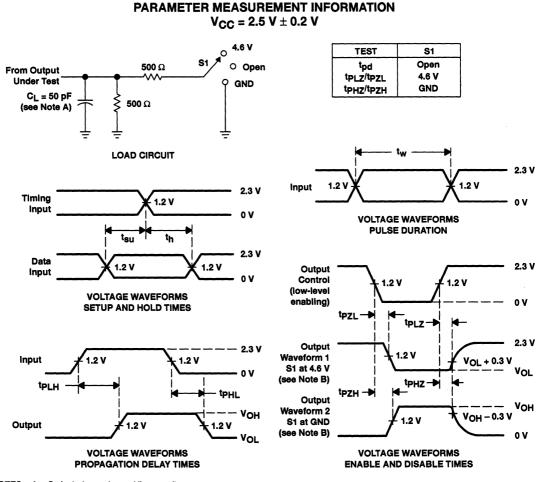

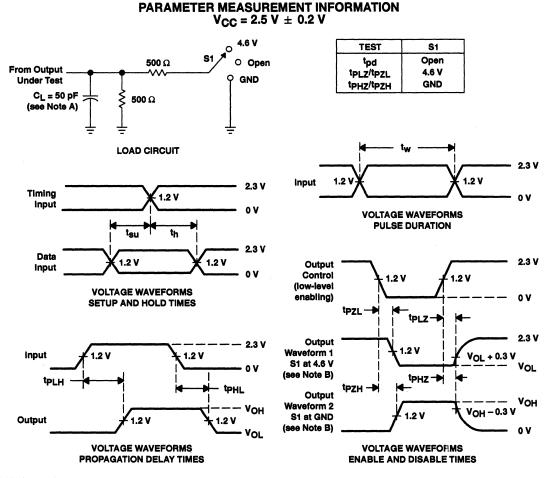

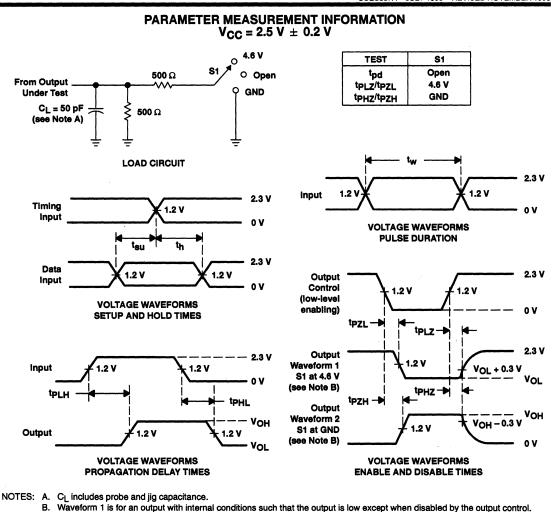

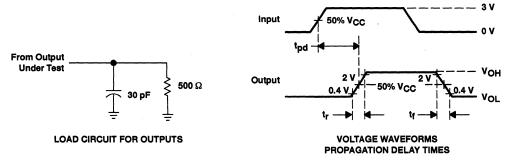

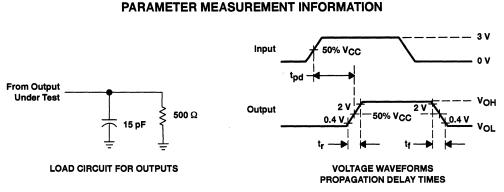

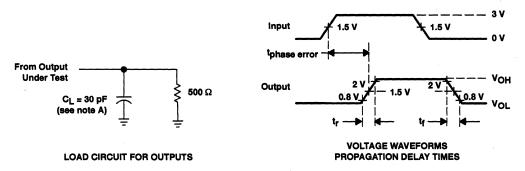

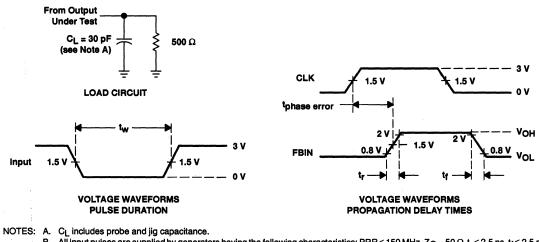

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , t<sub>r</sub>  $\leq$  2.5 ns, t<sub>f</sub>  $\leq$  2.5 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tpLz and tpHz are the same as tdis.

- F. tpzL and tpzH are the same as ten.

- G. tpLH and tpHL are the same as tod.

Figure 2. Load Circuit and Voltage Waveforms

## SN74ALVCH16501 **18-BIT UNIVERSAL BUS TRANS** WITH 3-STATE OUTPUTS

SCES024A - JULY 1995 - REVISED NOVEMBER 1996

| <ul> <li>Member of the Texas Instruments<br/>Widebus™ Family</li> </ul>                                   | DGG OR DL PACKAGE<br>(TOP VIEW)                                |  |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| <ul> <li>EPIC ™ (Enhanced-Performance Implanted<br/>CMOS) Submicron Process</li> </ul>                    |                                                                |  |

| <ul> <li>UBT™ (Universal Bus Transceiver)<br/>Combines D-Type Latches and D-Type</li> </ul>               | A1 🛛 3 54 🗍 B1                                                 |  |

| Flip-Flops for Operation in Transparent,<br>Latched, or Clocked Mode                                      | GND 4 53 GND<br>A2 5 52 B2                                     |  |

| <ul> <li>ESD Protection Exceeds 2000 V Per</li> </ul>                                                     | A3 [] 6 51 ] B3<br>V <sub>CC</sub> [] 7 50 ] V <sub>CC</sub> , |  |

| MIL-STD-883, Method 3015; Exceeds<br>200 V Using Machine Model                                            | A4 🛛 8 49 🗍 B4                                                 |  |

| (C = 200 pF, R = 0)                                                                                       | A5 9 48 B5<br>A6 10 47 B6                                      |  |

| <ul> <li>Latch-Up Performance Exceeds 250 mA<br/>Per JEDEC Standard JESD-17</li> </ul>                    | GND 11 46 GND<br>A7 12 45 B7                                   |  |

| <ul> <li>Bus Hold on Data Inputs Eliminates the<br/>Need for External Pullup/Pulldown</li> </ul>          | A8 🛛 13 44 🖸 B8                                                |  |

| Resistors                                                                                                 | A9 114 43 B9<br>A10 15 42 B10                                  |  |

| <ul> <li>Package Options Include Plastic 300-mil<br/>Shrink Small-Outline (DL) and Thin Shrink</li> </ul> | A11 0 16 41 0 B11<br>A12 0 17 40 0 B12                         |  |

| Small-Outline (DGG) Packages                                                                              | GND 🛛 18 39 🗍 GND                                              |  |

| description                                                                                               | A13 [] 19 38 [] B13<br>A14 [] 20 37 [] B14                     |  |

| This 18-bit universal bus transceiver is designed                                                         | A15 21 36 B15<br>V <sub>CC</sub> 22 35 V <sub>CC</sub>         |  |

| for 2.3-V to 3.6-V V <sub>CC</sub> operation.                                                             | A16 23 34 B16                                                  |  |

| Data flow in each direction is controlled by output-enable (OEAB and OEBA), latch-enable                  | A17 224 33 B17<br>GND 25 32 GND                                |  |

| (LEAB and LEBA), and clock (CLKAB and<br>CLKBA) inputs. For A-to-B data flow, the device                  | A18 [ 26 31 ] B18<br>OEBA [ 27 30 ] CLKBA                      |  |

is low, the A-bus data is stored in the latch/flip-flop on the low-to-high transition of CLKAB. When OEAB is high, the outputs are active. When OEAB is low, the outputs are in the high-impedance state.

LEBA 28

29 GND

To ensure the high-impedance state during power up or power down,  $\overline{OEBA}$  should be tied to V<sub>CC</sub> through a pullup resistor and OEAB should be tied to GND through a pulldown resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

Data flow for B to A is similar to that of A to B but uses OEBA, LEBA, and CLKBA. The output enables are complementary (OEAB is active high and OEBA is active low).

The SN74ALVCH16501 is available in TI's shrink small-outline (DL) and thin shrink small-outline (DGG) packages, which provide twice the I/O pin count and functionality of standard small-outline packages in the same printed circuit board area.

The SN74ALVCH16501 is characterized for operation from -40°C to 85°C.

EPIC, UBT, and Widebus are trademarks of Texas Instruments Incorporated.

operates in the transparent mode when LEAB is

high. When LEAB is low, the A data is latched if CLKAB is held at a high or low logic level. If LEAB

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1996, Texas Instruments Incorporated

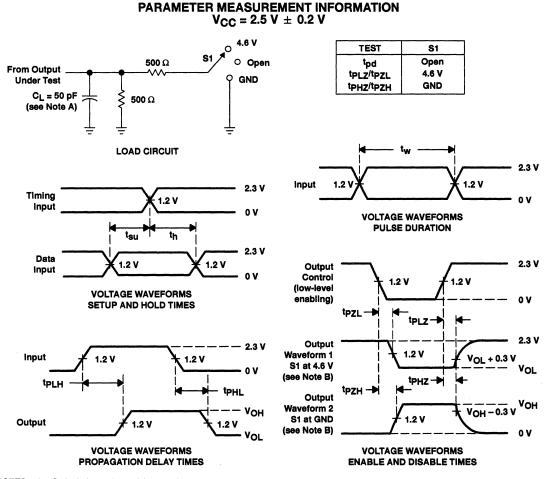

## SN74ALVCH16501 **18-BIT UNIVERSAL BUS TRANSCEIV** WITH 3-STATE OUTPUTS

SCES024A - JULY 1995 - REVISED NOVEMBER 1996

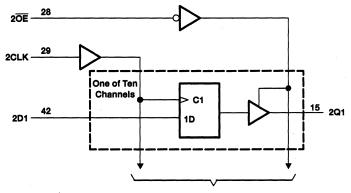

To 17 Other Channels

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub>                                                    | –0.5 V to 4.6 V                   |

|------------------------------------------------------------------------------------------|-----------------------------------|

| Input voltage range, VI: Except I/O ports (see Note 1)                                   |                                   |

| I/O ports (see Notes 1 and 2)                                                            | –0.5 V to V <sub>CC</sub> + 0.5 V |

| Output voltage range, VO (see Notes 1 and 2)                                             | –0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, IIK (VI < 0)                                                        |                                   |

| Output clamp current, $I_{OK}$ (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) | ±50 mA                            |

| Continuous output current, $I_O (V_O = 0 \text{ to } V_{CC})$                            | ±50 mA                            |

| Continuous current through each V <sub>CC</sub> or GND                                   | ±100 mA                           |

| Maximum power dissipation at $T_A = 55^{\circ}C$ (in still air) (see Note 3)             | DGG package 1 W                   |

|                                                                                          | DL package 1.4 W                  |

| Storage temperature range, T <sub>stg</sub>                                              |                                   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- 2. This value is limited to 4.6 V maximum.

- 3. The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils. For more information, refer to the Package Thermal Considerations application note in the ABT Advanced BiCMOS Technology Data Book.

## SN74ALVCH16501 18-BIT UNIVERSAL BUS TRANSCEIVER WITH 3-STATE OUTPUTS SCES024A – JULY 1995 – REVISED NOVEMBER 1996

## timing requirements over recommended operating free-air temperature range (unless otherwise noted)

|                 |                 |                                 | V <sub>CC</sub> = 2.5 V<br>± 0.2 V |     |     |     |     |     |     |  | UNIT |

|-----------------|-----------------|---------------------------------|------------------------------------|-----|-----|-----|-----|-----|-----|--|------|

|                 |                 |                                 | MIN                                | MAX | MIN | MAX | MIN | MAX |     |  |      |

| fclock          | Clock frequency |                                 | 0                                  | 150 | 0   | 150 | 0   | 150 | MHz |  |      |

| tw              | Pulse duration  | LE high                         | 3.3                                |     | 3.3 |     | 3.3 |     |     |  |      |

|                 | Pulse duration  | CLK high or low                 | 3.3                                |     | 3.3 |     | 3.3 |     | ns  |  |      |

|                 | Setup time      | Data before CLK↑                | 2.2                                |     | 2.1 |     | 1.7 |     |     |  |      |

| t <sub>su</sub> |                 | Data before LE↓, CLK high       | 1.9                                |     | 1.6 |     | 1.5 |     | ns  |  |      |

|                 |                 | Data before LE↓, CLK low        | 1.3                                |     | 1.1 |     | 1   |     |     |  |      |

|                 | Hold time       | Data after CLK↑                 | 0.6                                |     | 0.6 |     | 0.7 |     | ns  |  |      |

| th              |                 | Data after LE↓, CLK high or low | 1.4                                |     | 1.7 |     | 1.4 |     |     |  |      |

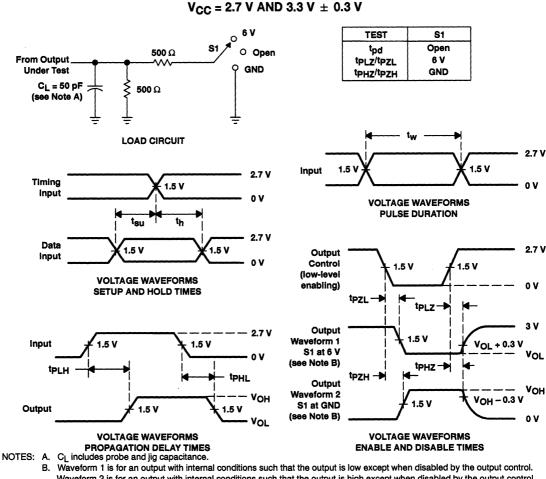

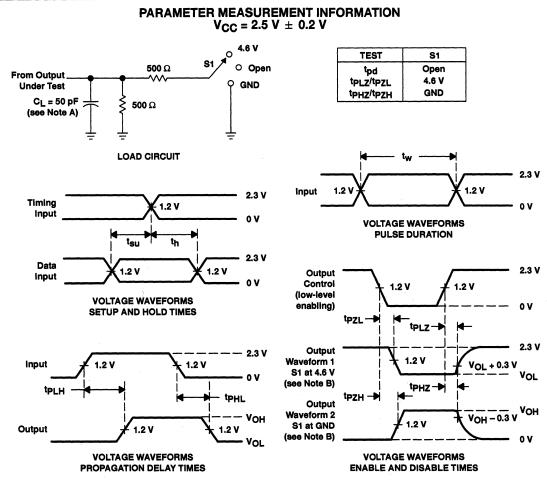

## switching characteristics over recommended operating free-air temperature range (unless otherwise noted) (see Figures 1 and 2)

| PARAMETER        |         | TO<br>(OUTPUT) |     | $V_{CC} = 2.5 V$<br>± 0.2 V |     | 2.7 V | V <sub>CC</sub> = 3.3 V<br>± 0.3 V |     | UNIT |

|------------------|---------|----------------|-----|-----------------------------|-----|-------|------------------------------------|-----|------|

|                  | (INFOT) | (001F01)       | MIN | MAX                         | MIN | MAX   | MIN                                | MAX |      |

| fmax             |         |                | 150 |                             | 150 |       | 150                                |     | MHz  |

|                  | A or B  | B or A         | 1.2 | 5.4                         |     | 4.5   | 1                                  | 3.9 |      |

| <sup>t</sup> pd  | LE      | A or B         | 1.6 | 6.3                         |     | 5.3   | 1.3                                | 4.6 | ns   |

|                  | CLK     | A or B         | 1.7 | 6.7                         |     | 5.6   | 1.4                                | 4.9 |      |

| ten              | OEAB    | В              | 1.1 | 6.3                         |     | 5.3   | 1                                  | 4.6 | ns   |

| <sup>t</sup> dis | OEAB    | В              | 2.2 | 6.4                         |     | 5.7   | 1.4                                | 5   | ns   |

| <sup>t</sup> en  | OEBA    | A              | 1.4 | 6.8                         |     | 6     | 1.1                                | 5   | ns   |

| <sup>t</sup> dis | OEBA    | A              | 2   | 5.5                         |     | 4.6   | 1.3                                | 4.2 | ns   |

## operating characteristics, T<sub>A</sub> = 25°C

| PARAMETER                                     |                               | TEST CONDITIONS  | V <sub>CC</sub> = 2.5 V<br>± 0.2 V | V <sub>CC</sub> = 3.3 V<br>± 0.3 V | UNIT |     |

|-----------------------------------------------|-------------------------------|------------------|------------------------------------|------------------------------------|------|-----|

|                                               |                               |                  | TYP                                | TYP                                |      |     |

|                                               | Power dissipation conseitance | Outputs enabled  |                                    | 44                                 | 54   | - 5 |

| C <sub>pd</sub> Power dissipation capacitance |                               | Outputs disabled | CL = 50 pF, f = 10 MHz             | 6                                  | 6    | pF  |

## SN74ALVCH16501 **18-BIT UNIVERSAL BUS TRANSCEIVER** WITH 3-STATE OUTPUTS SCES024A - JULY 1995 - REVISED NOVEMBER 1996

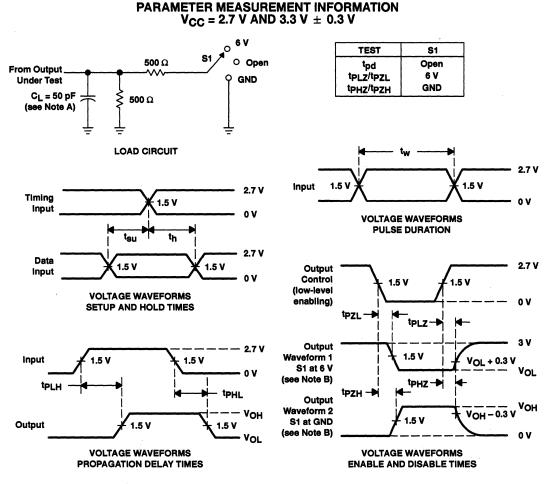

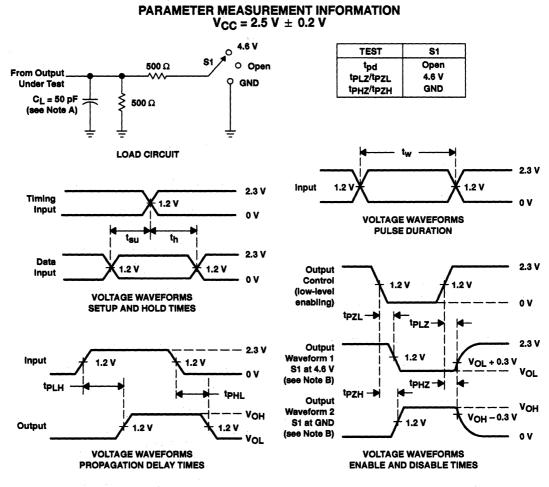

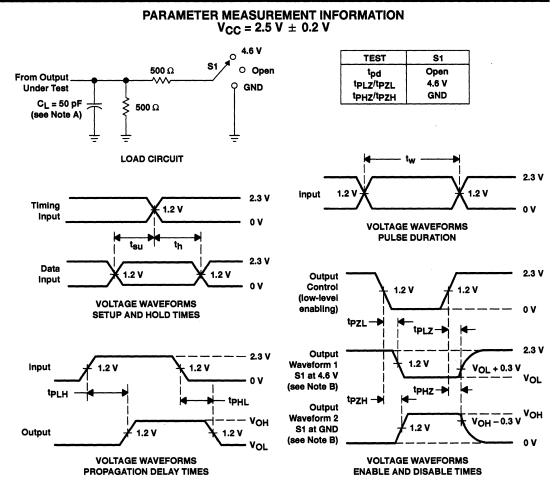

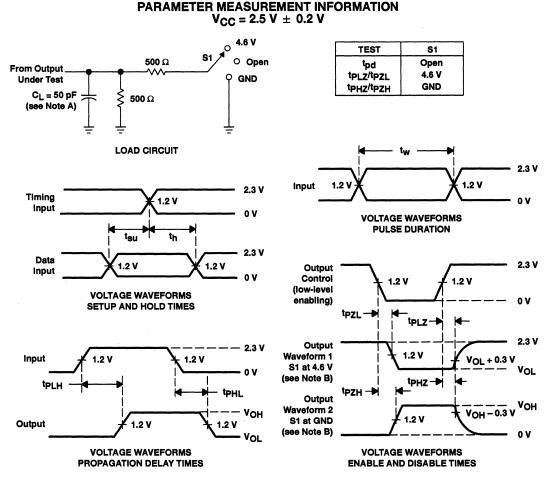

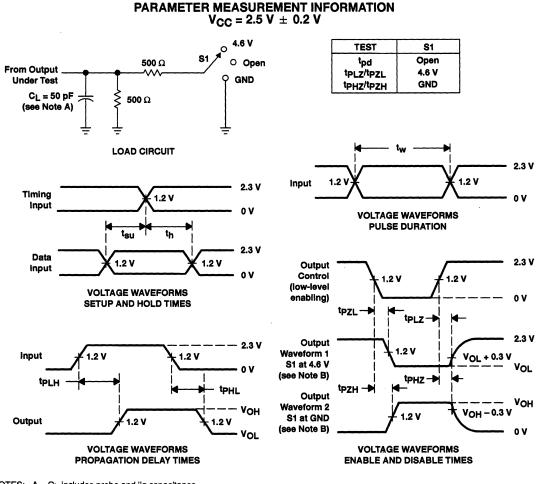

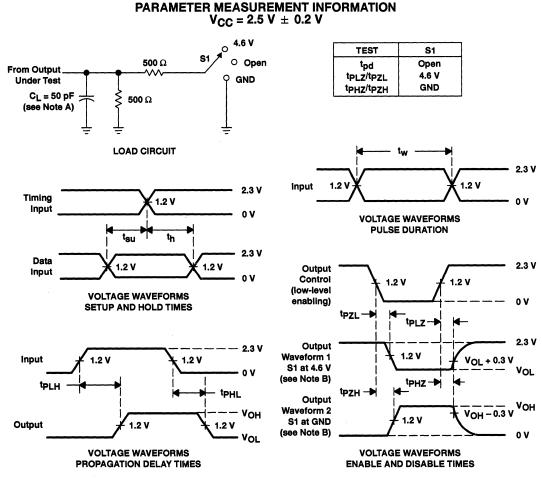

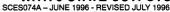

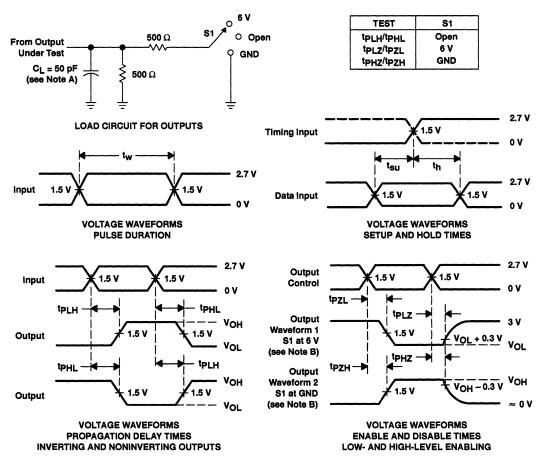

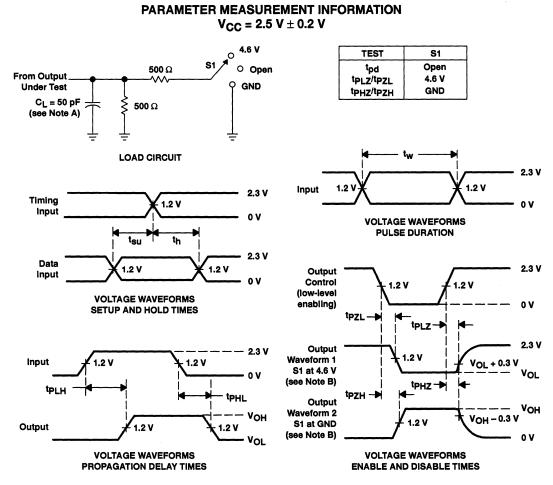

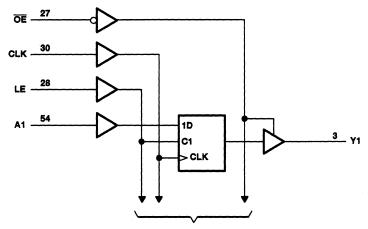

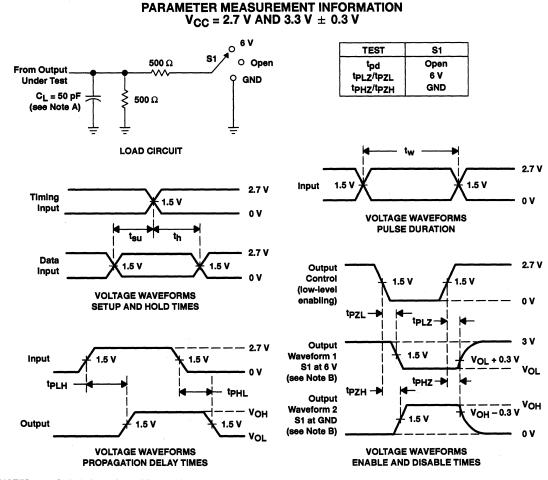

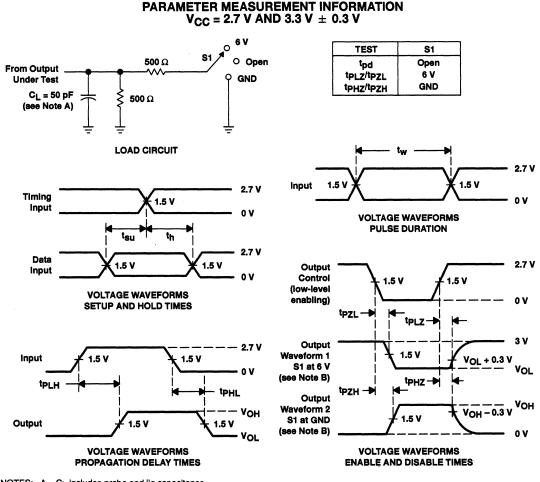

NOTES: A. CI includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , t<sub>r</sub>  $\leq$  2.5 ns, t<sub>f</sub>  $\leq$  2.5 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tpLz and tpHz are the same as tdis.

- F. tpzL and tpzH are the same as ten.

- G. tpLH and tpHL are the same as tpd.

Figure 2. Load Circuit and Voltage Waveforms

## SN74ALVCH16600 **18-BIT UNIVERSAL BUS TRANSCEIVER** WITH 3-STATE OUTPUTS SCES030A - JULY 1995 - REVISED NOVEMBER 1996

| <ul> <li>Member of the Texas Instruments<br/>Widebus™ Family</li> </ul>                                                                            | DGG OR DL PACKAGE<br>(TOP VIEW)                                  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| <ul> <li>EPIC ™ (Enhanced-Performance Implanted<br/>CMOS) Submicron Process</li> </ul>                                                             |                                                                  |  |

| <ul> <li>UBT™ (Universal Bus Transceiver)</li> <li>Combines D-Type Latches and D-Type</li> <li>Flip-Flops for Operation in Transparent,</li> </ul> | A1 3 54 B1<br>GND 4 53 GND<br>A2 5 52 B2                         |  |

| <ul> <li>Latched, Clocked, or Clock-Enabled Mode</li> <li>ESD Protection Exceeds 2000 V Per<br/>MIL-STD-883, Method 3015; Exceeds</li> </ul>       | A3 6 51 B3<br>V <sub>CC</sub> 7 50 V <sub>CC</sub><br>A4 8 49 B4 |  |

| 200 V Using Machine Model (C = 200 pF,<br>R = 0)                                                                                                   | A5 9 48 B5<br>A6 10 47 B6                                        |  |

| <ul> <li>Latch-Up Performance Exceeds 250 mA<br/>Per JEDEC Standard JESD-17</li> </ul>                                                             | GND [] 11 46 [] GND<br>A7 [] 12 45 [] B7                         |  |

| <ul> <li>Bus Hold on Data Inputs Eliminates the<br/>Need for External Pullup/Pulldown<br/>Resistors</li> </ul>                                     | A8 0 13 44 B8<br>A9 0 14 43 B9<br>A10 0 15 42 0 B10              |  |

| <ul> <li>Package Options Include Plastic 300-mil<br/>Shrink Small-Outline (DL) and Thin Shrink<br/>Small-Outline (DGG) Packages</li> </ul>         | A11 16 41 B11<br>A12 17 40 B12<br>GND 18 39 GND                  |  |

| description                                                                                                                                        | A13 19 38 B13<br>A14 20 37 B14<br>A15 21 36 B15                  |  |

| This 18-bit universal bus transceiver is designed for 2.3-V to 3.6-V $V_{CC}$ operation.                                                           | V <sub>CC</sub> [ 22 35] V <sub>CC</sub><br>A16 [ 23 34] B16     |  |

| The SN74ALVCH16600 combines D-type latches<br>and D-type flip-flops to allow data flow in<br>transparent, latched, and clocked modes.              | A17 24 33 B17<br>GND 25 32 GND<br>A18 26 31 B18                  |  |

| Data flow in each direction is controlled by output-enable (OEAB and OEBA), latch-enable                                                           | OEBA [] 27 30 ] CLKBA<br>LEBA [] 28 29 ] CLKENBA                 |  |

BA (<u>1</u>28 output-enable (OEAB and OEBA), latch-enable (LEAB and LEBA), and clock (CLKAB and CLKBA) inputs. The clock can be controlled by the clock-enable (CLKENAB and CLKENBA) inputs. For A-to-B

data flow, the device operates in the transparent mode when LEAB is high. When LEAB is low, the A data is latched if CLKAB is held at a high or low logic level. If LEAB is low, the A-bus data is stored in the latch/flip-flop on the high-to-low transition of CLKAB. Output enable OEAB is active low. When OEAB is low, the outputs are active. When OEAB is high, the outputs are in the high-impedance state.

Data flow for B to A is similar to that of A to B but uses OEBA, LEBA, CLKBA, and CLKENBA.

To ensure the high-impedance state during power up or power down,  $\overline{OE}$  should be tied to V<sub>CC</sub> through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

The SN74ALVCH16600 is available in TI's shrink small-outline (DL) and thin shrink small-outline (DGG) packages, which provide twice the I/O pin count and functionality of standard small-outline packages in the same printed circuit board area.

The SN74ALVCH16600 is characterized for operation from -40°C to 85°C.

EPIC, UBT, and Widebus are trademarks of Texas Instruments Incorporated.

PRODUCTION DATA Information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1996, Texas Instruments Incorporated

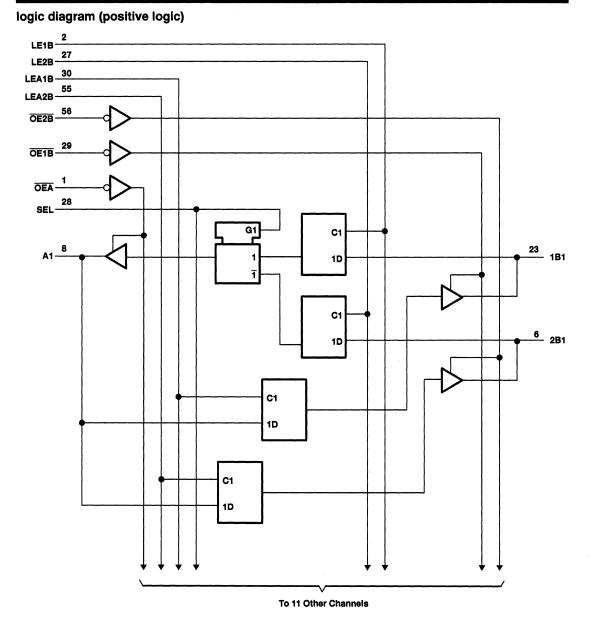

## SN74ALVCH16600 18-BIT UNIVERSAL BUS TRANSCEIVER WITH 3-STATE OUTPUTS SCES030A – JULY 1995 – REVISED NOVEMBER 1996

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub>                                                    | -0.5.V to 4.6.V                   |

|------------------------------------------------------------------------------------------|-----------------------------------|

|                                                                                          |                                   |

| Input voltage range, VI: Except I/O ports (see Note 1)                                   |                                   |

| I/O ports (see Notes 1 and 2)                                                            |                                   |

| Output voltage range, V <sub>O</sub> (see Notes 1 and 2)                                 | –0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, IIK (VI < 0)                                                        | –50 mA                            |

| Output clamp current, $I_{OK}$ (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) |                                   |

| Continuous output current, $I_O (V_O = 0 \text{ to } V_{CC})$                            |                                   |

| Continuous current through each V <sub>CC</sub> or GND                                   |                                   |

| Maximum power dissipation at T <sub>A</sub> = 55°C (in still air) (see Note 3): DGG pa   | ckage 1 W                         |

| DL pack                                                                                  | age 1.4 W                         |

| Storage temperature range, T <sub>stg</sub>                                              |                                   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- 2. This value is limited to 4.6 V maximum.

- 3. The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils. For more information, refer to the *Package Thermal Considerations* application note in the *ABT Advanced BiCMOS Technology Data Book*.

### recommended operating conditions (see Note 4)

|       |                                    |                                  | MIN | MAX | UNIT |

|-------|------------------------------------|----------------------------------|-----|-----|------|

| Vcc   | Supply voltage                     |                                  | 2.3 | 3.6 | v    |

| V     | High-level input voltage           | V <sub>CC</sub> = 2.3 V to 2.7 V | 1.7 |     | v    |

| VIH   |                                    | V <sub>CC</sub> = 2.7 V to 3.6 V | 2   |     | v    |

| V.,   | VIL Low-level input voltage        | V <sub>CC</sub> = 2.3 V to 2.7 V |     | 0.7 | v    |

| ۷IL   |                                    | V <sub>CC</sub> = 2.7 V to 3.6 V |     | 0.8 | v    |

| ٧I    | Input voltage                      |                                  | 0   | VCC | v    |

| Vo    | Output voltage                     |                                  | 0   | VCC | v    |

|       | High-level output current          | V <sub>CC</sub> = 2.3 V          |     | -12 |      |

| ЮН    |                                    | V <sub>CC</sub> = 2.7 V          |     | -12 | mA   |

|       |                                    | V <sub>CC</sub> = 3 V            |     | 24  |      |

|       |                                    | V <sub>CC</sub> = 2.3 V          |     | 12  |      |

| IOL   | Low-level output current           | V <sub>CC</sub> = 2.7 V          |     | 12  | mA   |

|       |                                    | V <sub>CC</sub> = 3 V            |     | 24  |      |

| ∆t/∆v | Input transition rise or fall rate |                                  | 0   | 10  | ns/V |

| TA    | Operating free-air temperature     |                                  | -40 | 85  | °C   |

NOTE 4: Unused control inputs must be held high or low to prevent them from floating.

## SN74ALVCH16600 18-BIT UNIVERSAL BUS TRANSCEIVER WITH 3-STATE OUTPUTS SCES030A – JULY 1995 – REVISED NOVEMBER 1996

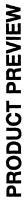

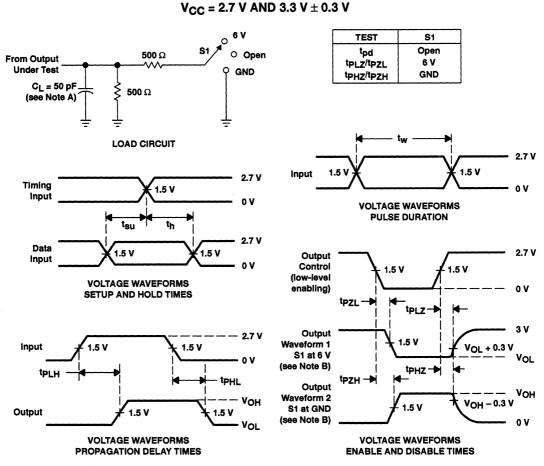

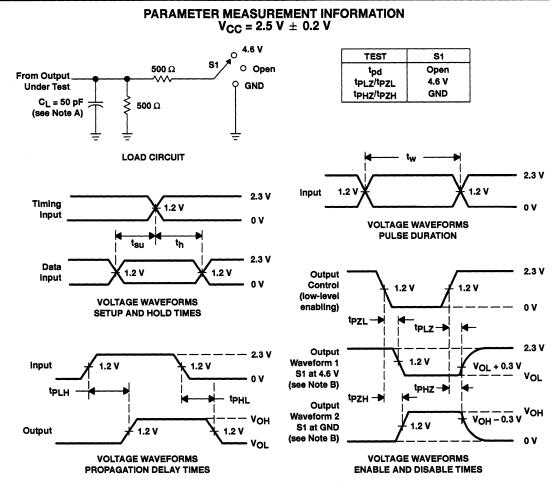

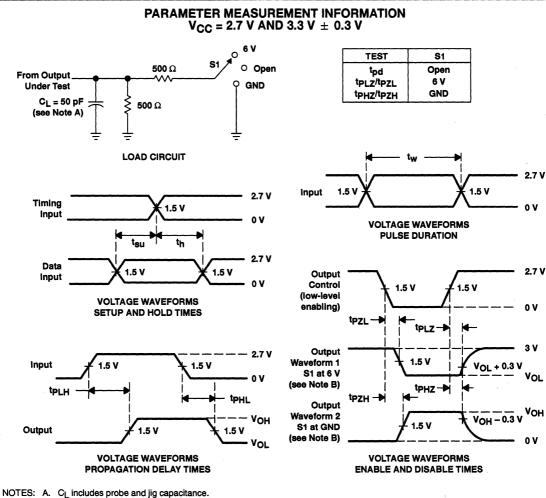

## switching characteristics over recommended operating free-air temperature range, $C_L = 50 \text{ pF}$ (unless otherwise noted) (see Figures 1 and 2)

| PARAMETER        | FROM TO<br>(INPUT) (OUTPUT) |        | V <sub>CC</sub> = 2.5 V<br>± 0.2 V |     | V <sub>CC</sub> = 2.7 V |     | V <sub>CC</sub> = 3.3 V<br>± 0.3 V |     | UNIT |

|------------------|-----------------------------|--------|------------------------------------|-----|-------------------------|-----|------------------------------------|-----|------|

|                  |                             | MIN    | MAX                                | MIN | MAX                     | MIN | MAX                                |     |      |

| fmax             |                             |        | 150                                |     | 150                     |     | 150                                |     | MHz  |

|                  | A or B                      | B or A | 1                                  | 5.7 |                         | 4.7 | 1                                  | 4   |      |

| <sup>t</sup> pd  | LEAB or LEBA                | A or B | 1                                  | 6.5 |                         | 5.5 | 1                                  | 4.8 | ns   |

|                  | CLKAB or CLKBA              | A or B | 1.4                                | 7.9 |                         | 6.8 | 1.3                                | 5.7 |      |

| ten              | OEAB or OEBA                | A or B | 1.1                                | 7.1 |                         | 6.3 | 1.1                                | 5.2 | ns   |

| <sup>t</sup> dis | OEAB or OEBA                | A or B | 1.7                                | 5.7 |                         | 4.7 | 1.2                                | 4.4 | ns   |

## operating characteristics, T<sub>A</sub> = 25°C

| PARAMETER                         |  | TEST CONDITIONS  | V <sub>CC</sub> = 2.5 V<br>± 0.2 V      | V <sub>CC</sub> = 3.3 V<br>± 0.3 V | UNIT |    |

|-----------------------------------|--|------------------|-----------------------------------------|------------------------------------|------|----|

|                                   |  |                  | TYP                                     | TYP                                |      |    |

|                                   |  | Outputs enabled  | C = = = = = = = = = = = = = = = = = = = | 43                                 | 56   | pF |

| Cpd Power dissipation capacitance |  | Outputs disabled | C <sub>L</sub> = 50 pF, f = 10 MHz      | 6                                  | 6    |    |

## SN74ALVCH16600 **18-BIT UNIVERSAL BUS TRANSCEIV** WITH 3-STATE OUTPUTS

SCES030A - JULY 1995 - REVISED NOVEMBER 1996

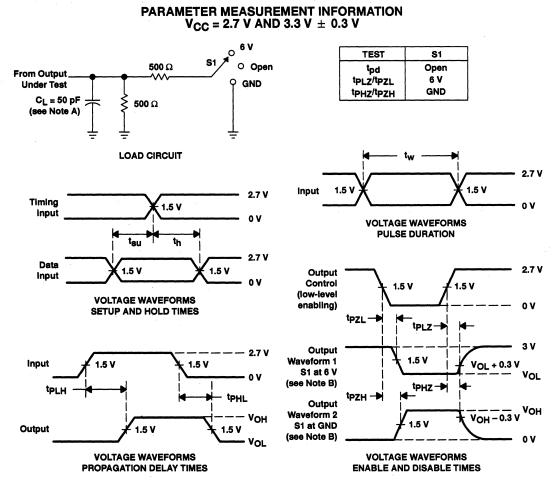

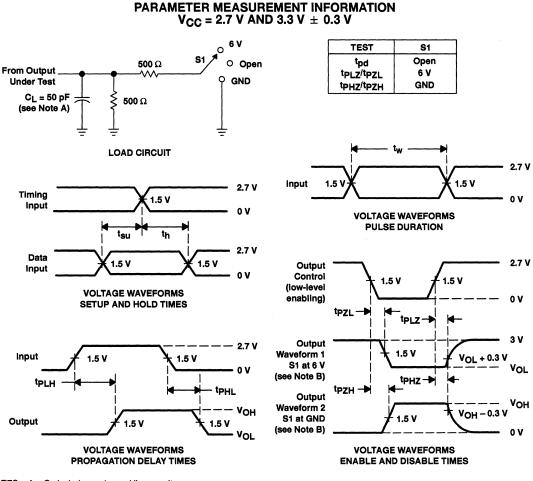

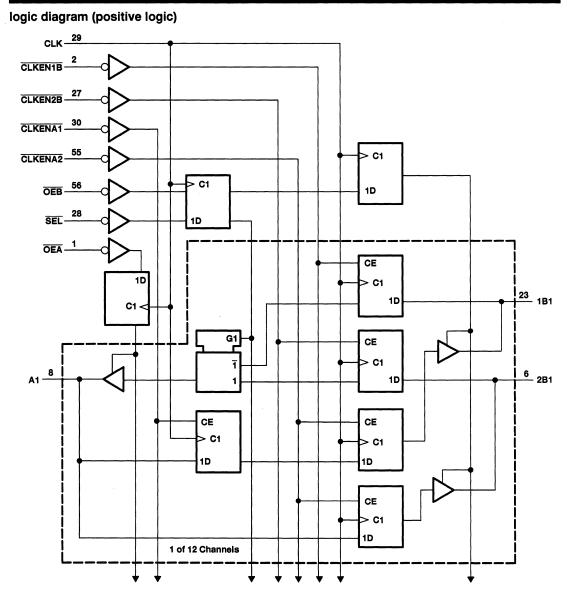

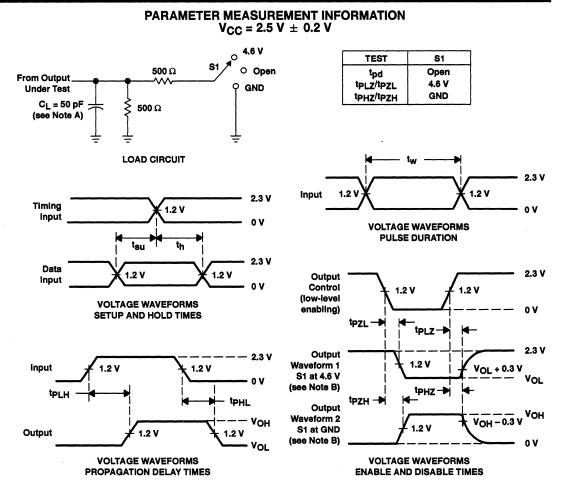

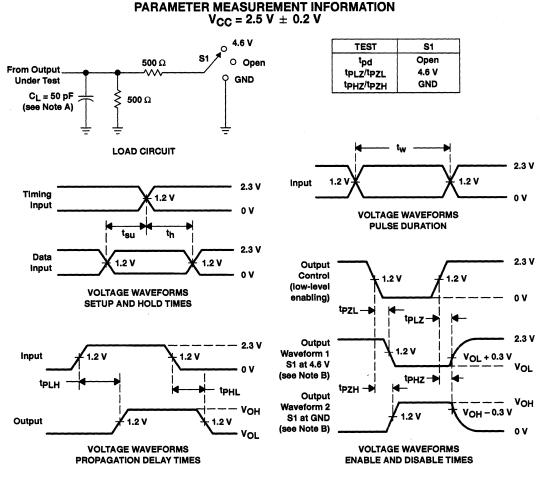

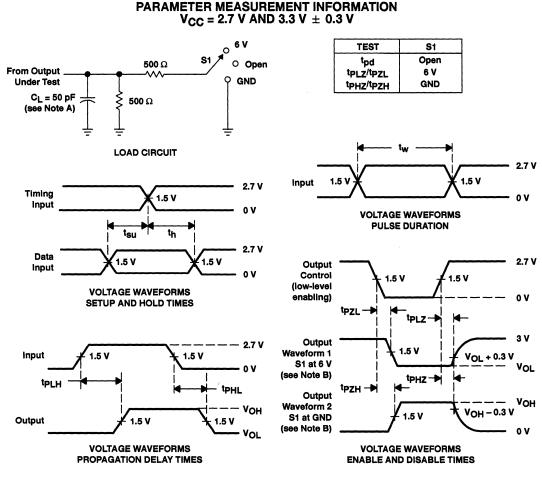

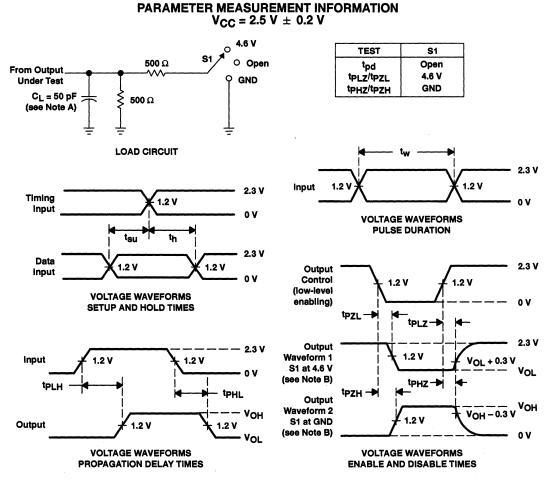

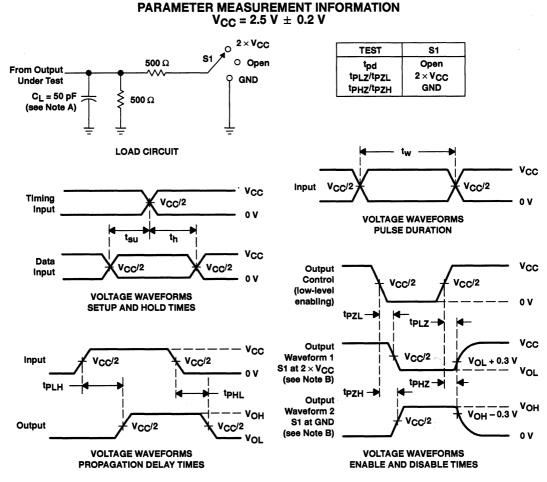

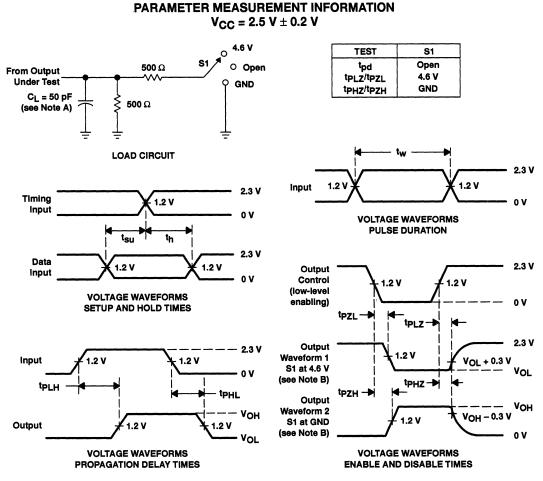

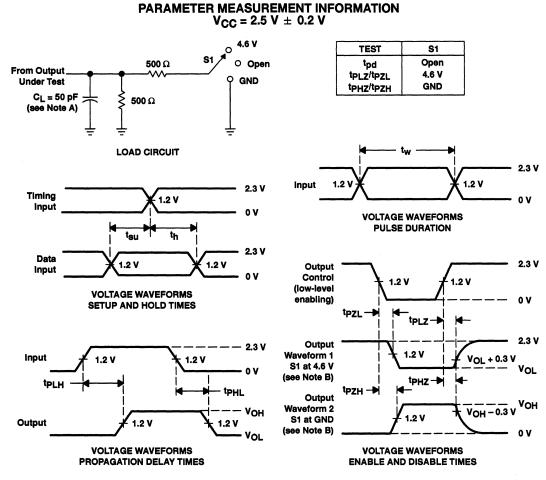

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , t<sub>f</sub>  $\leq$  2.5 ns, t<sub>f</sub>  $\leq$  2.5 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tpLz and tpHz are the same as tdis.

- F. tpzi and tpzH are the same as ten.

- G. tPLH and tPHL are the same as tod.

Figure 2. Load Circuit and Voltage Waveforms

## SN74ALVCH16601 **18-BIT UNIVERSAL BUS TRANSCEIVER** WITH 3-STATE OUTPUTS

SCES027A - JULY 1995 - REVISED NOVEMBER 1996

| ● Member of the Texas Instruments<br>Widebus™ Family                                                                                                                                 | DGG OR DL PACKAGE<br>(TOP VIEW)                                              |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|

| <ul> <li>UBT™ (Universal Bus Transceiver)<br/>Combines D-Type Latches and D-Type<br/>Flip-Flops for Operation in Transparent,<br/>Latched, Clocked, or Clock-Enabled Mode</li> </ul> | OEAB 1 56 CLKENAB<br>LEAB 2 55 CLKAB<br>A1 3 54 B1                           |  |

| <ul> <li>EPIC ™ (Enhanced-Performance Implanted<br/>CMOS) Submicron Process</li> </ul>                                                                                               | GND 4 53 GND<br>A2 5 52 B2<br>A3 6 51 B3                                     |  |

| <ul> <li>Bus Hold on Data Inputs Eliminates the<br/>Need for External Pullup/Pulldown<br/>Resistors</li> </ul>                                                                       | V <sub>CC</sub> [ 7 50 ] V <sub>CC</sub><br>A4 [ 8 49 ] B4<br>A5 [ 9 48 ] B5 |  |

| <ul> <li>ESD Protection Exceeds 2000 V Per<br/>MIL-STD-883, Method 3015; Exceeds</li> </ul>                                                                                          | A6 [ 10 47 ] B6<br>GND [ 11 46 ] GND                                         |  |

| 200 V Using Machine Model (C = 200 pF,<br>R = 0)<br>• Latch-Up Performance Exceeds 250 mA                                                                                            | A7 [] 12 45 [] B7<br>A8 [] 13 44 [] B8<br>A9 [] 14 43 [] B9                  |  |

| Per JEDEC Standard JESD-17     Package Options Include Plastic 300-mil                                                                                                               | A10 15 42 B10<br>A11 16 41 B11                                               |  |

| Shrink Small-Outline (DL) and Thin Shrink<br>Small-Outline (DGG) Packages                                                                                                            | A12 17 40 B12<br>GND 18 39 GND<br>A13 19 38 B13                              |  |

| description                                                                                                                                                                          | A14 0 20 37 0 B14<br>A15 0 21 36 0 B15                                       |  |

| This 18-bit universal bus transceiver is designed for 2.3-V to 3.6-V $V_{CC}$ operation.                                                                                             | V <sub>CC</sub> [] 22 35 [] V <sub>CC</sub><br>A16 [] 23 34 [] B16           |  |

| The SN74ALVCH16601 combines D-type latches and D-type flip-flops to allow data flow in                                                                                               | A17 [ 24 33 ] B17<br>GND [ 25 32 ] GND<br>A18 [ 26 31 ] B18                  |  |

| transparent, latched, and clocked modes.<br>Data flow in each direction is controlled by                                                                                             | OEBA [] 27 30 ]] CLKBA<br>LEBA [] 28 29 ]] CLKENBA                           |  |

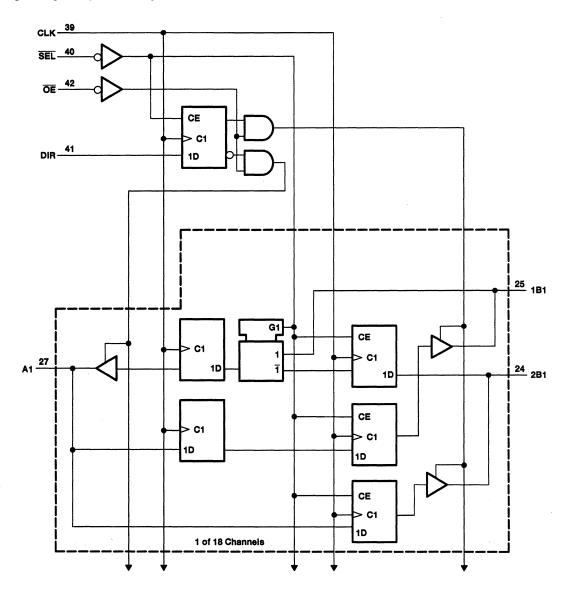

output-enable (OEAB and OEBA), latch-enable (LEAB and LEBA), and clock (CLKAB and

CLKBA) inputs. The clock can be controlled by the clock-enable (CLKENAB and CLKENBA) inputs. For A-to-B data flow, the device operates in the transparent mode when LEAB is high. When LEAB is low, the A data is latched if CLKAB is held at a high or low logic level. If LEAB is low, the A-bus data is stored in the latch/flip-flop on the low-to-high transition of CLKAB. Output enable OEAB is active low. When OEAB is low, the outputs are active. When OEAB is high, the outputs are in the high-impedance state.

Data flow for B to A is similar to that of A to B but uses OEBA, LEBA, CLKBA, and CLKENBA.

To ensure the high-impedance state during power up or power down,  $\overline{\text{OE}}$  should be tied to V<sub>CC</sub> through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

The SN74ALVCH16601 is available in TI's shrink small-outline (DL) and thin shrink small-outline (DGG) packages, which provide twice the I/O pin count and functionality of standard small-outline packages in the same printed circuit board area.

The SN74ALVCH16601 is characterized for operation from -40°C to 85°C.

EPIC, UBT, and Widebus are trademarks of Texas Instruments Incorporated.