# **High-Performance FIFO Memories** Standard and Specialty Memories From 1-Bit to 36-Bit Widths

Advanced System Logic Products

1996

| General Information                           |    |

|-----------------------------------------------|----|

| Telecom Single-Bit FIFOs                      | 2  |

| Reduced-Width FIFOs                           | 3  |

| 9-Bit Clocked/Strobed FIFOs                   | 4  |

| 8- and 9-Bit Asynchronous FIFOs               | 5  |

| 9-Bit Synchronous FIFOs                       | 6  |

| 18-Bit Clocked FIFOs                          | 7  |

| 18-Bit Strobed FIFOs                          | 8  |

| Multi-Q™ 18-Bit FIFO                          | 9  |

| 3.3-V Low-Powered 18-Bit FIFOs                | 10 |

| DSP 32- and 36-Bit Clocked FIFOs              | 11 |

| Internetworking 36-Bit Clocked FIFOs          | 12 |

| High-Bandwidth Computing 36-Bit Clocked FIFOs | 13 |

| Military FIFOs                                | 14 |

| Application Reports                           | 15 |

| Mechanical Data                               | 16 |

1. P

# *High-Performance FIFO Memories Data Book*

Standard and Specialty Memories From 1-Bit to 36-Bit Widths

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated

Printed in U.S.A. by Custom Printing Company Owensville, Missouri

#### INTRODUCTION

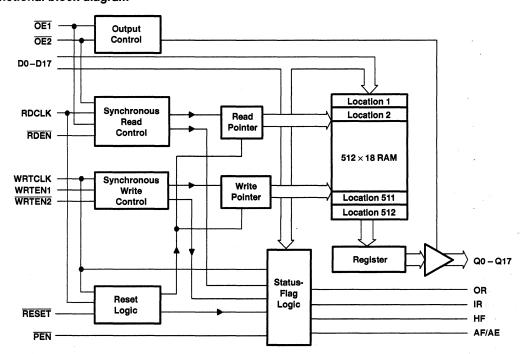

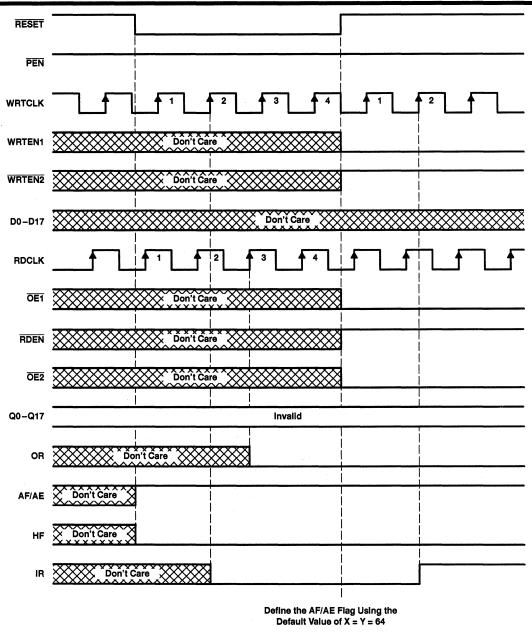

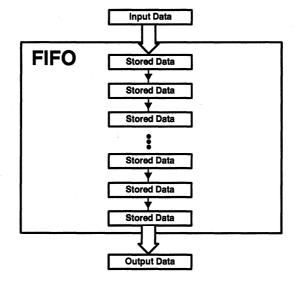

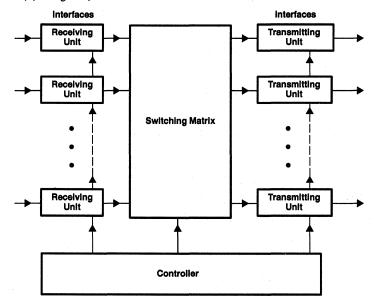

First-in, first-out (FIFO) memories from Texas Instruments (TI) are valuable data-path elements for eliminating bottlenecks and regulating flow. Data transfers in and out of a FIFO memory are independent of one another and allow the device to be the communication medium between two asynchronous systems. Empty and full status flags that prevent underflow and overflow conditions are standard with all devices, and many have programmable almost-full and almost-empty flags to optimize the control of a particular system.

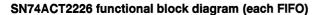

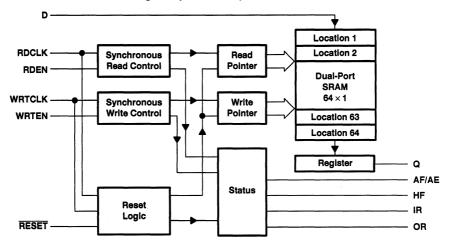

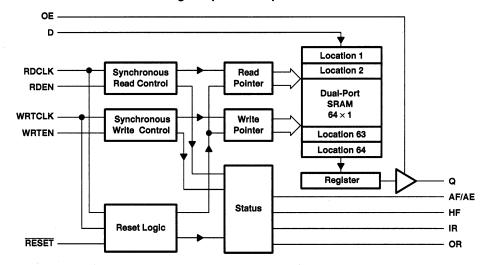

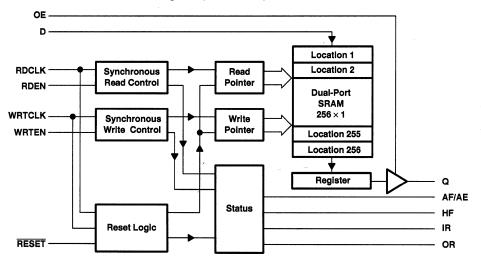

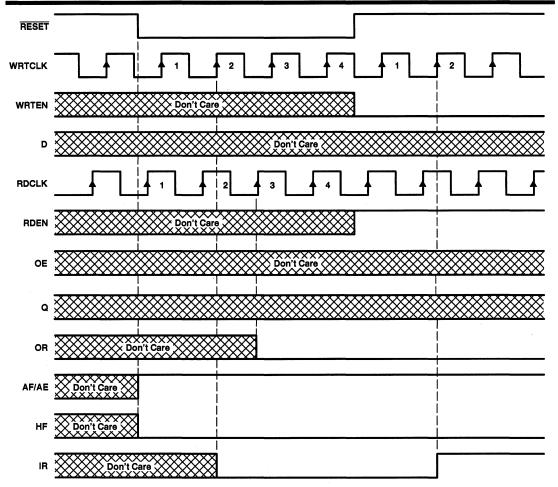

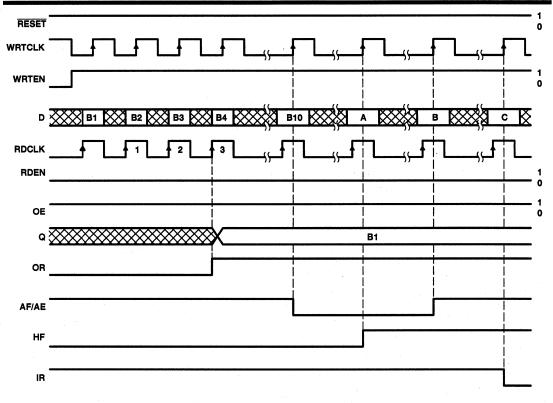

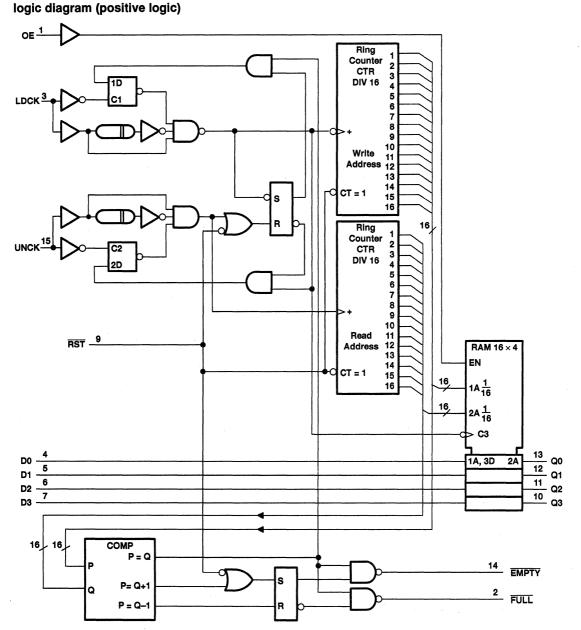

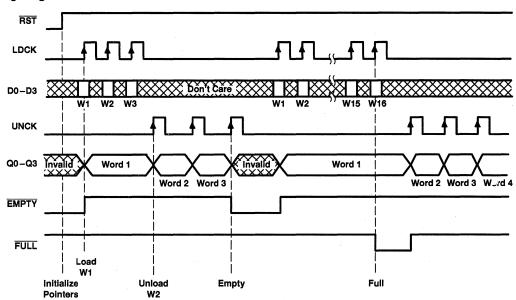

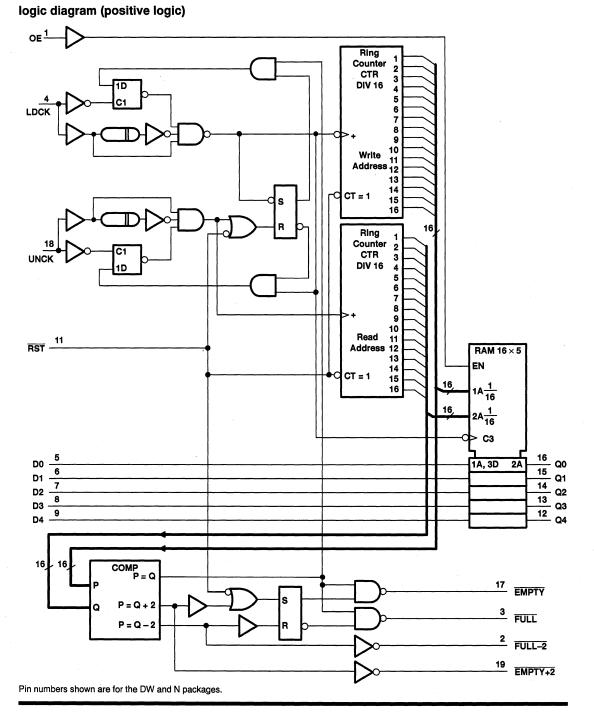

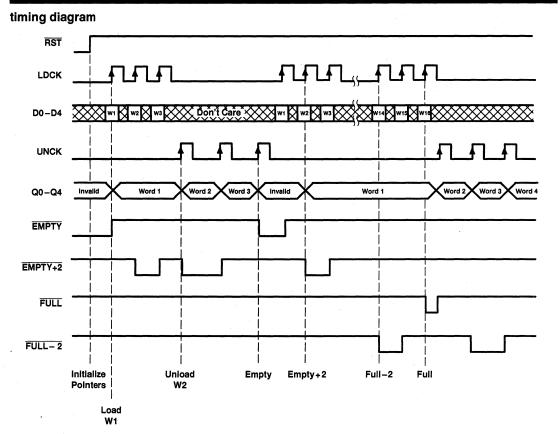

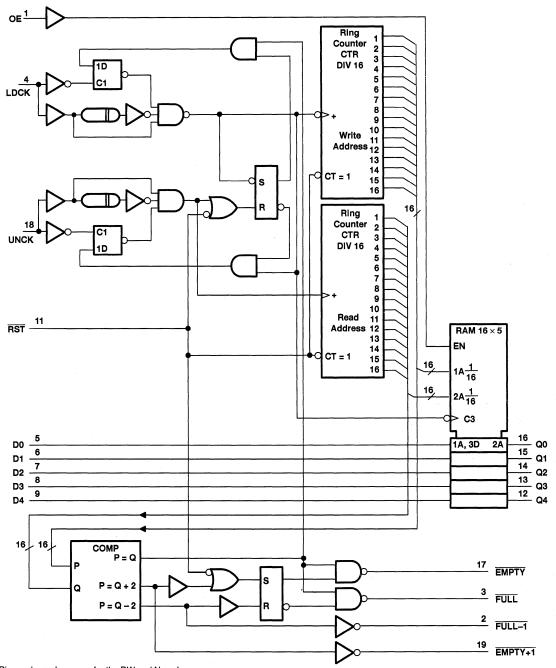

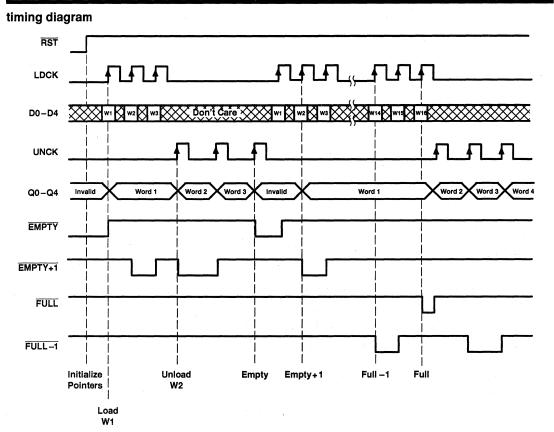

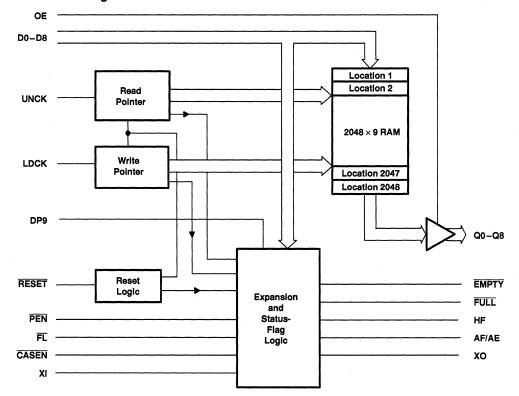

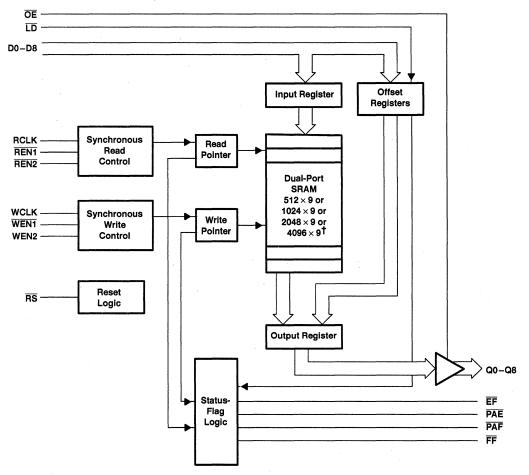

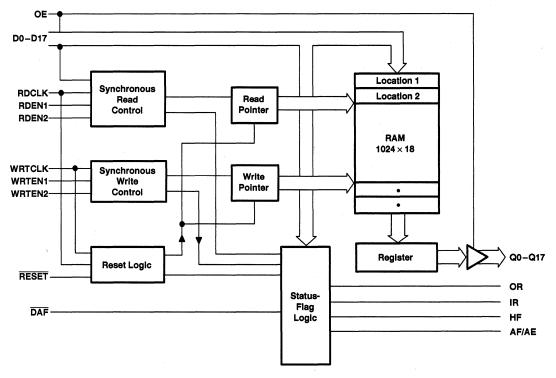

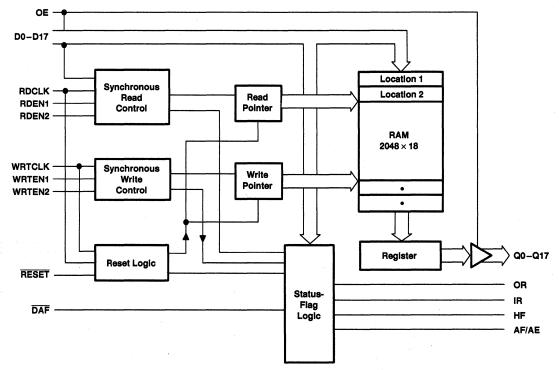

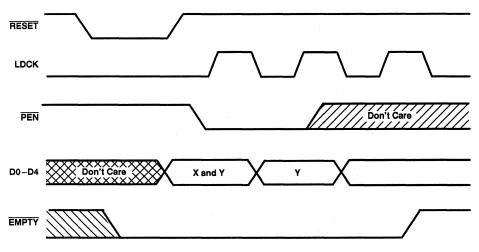

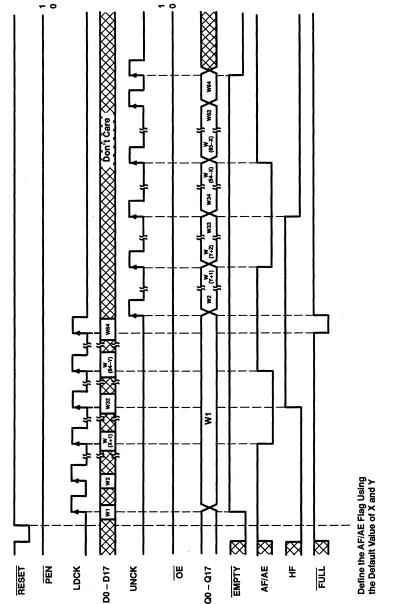

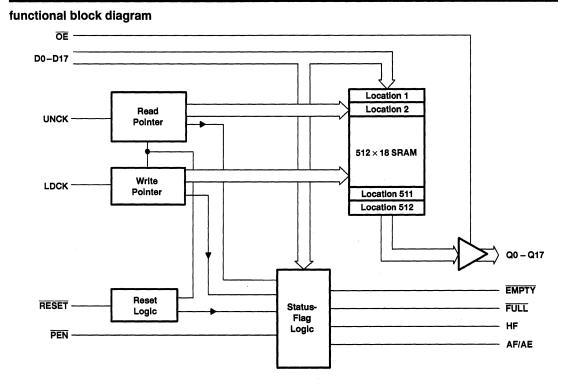

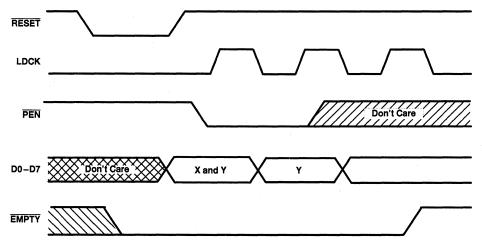

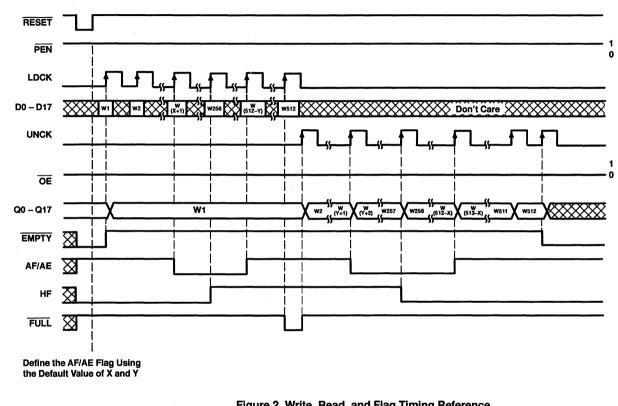

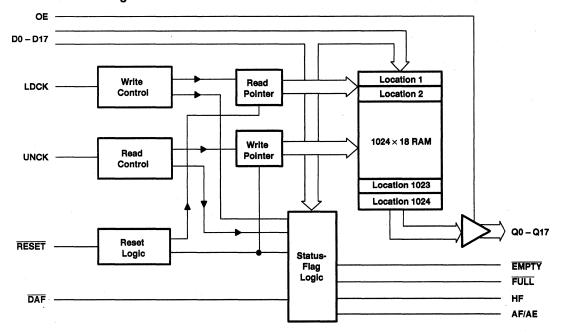

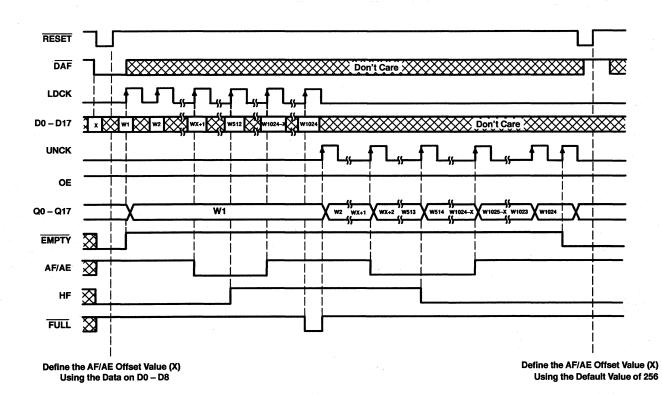

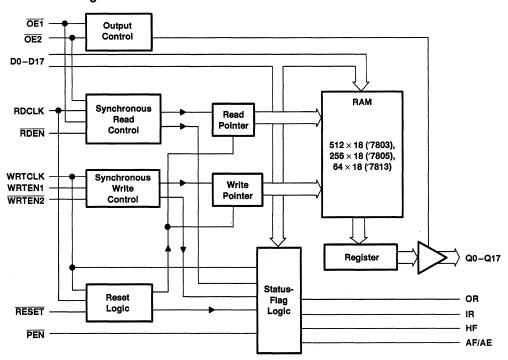

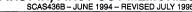

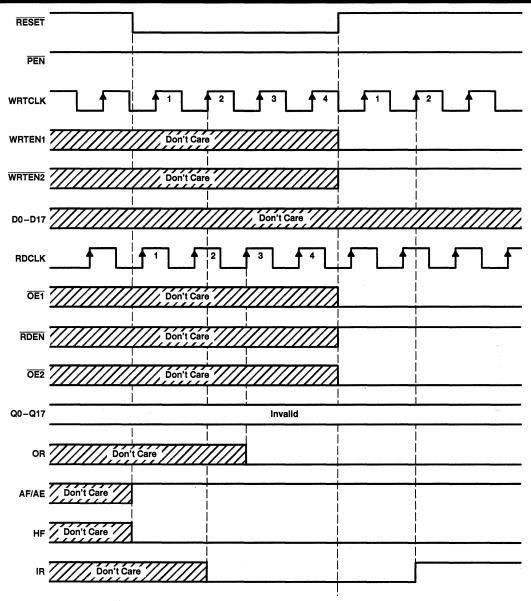

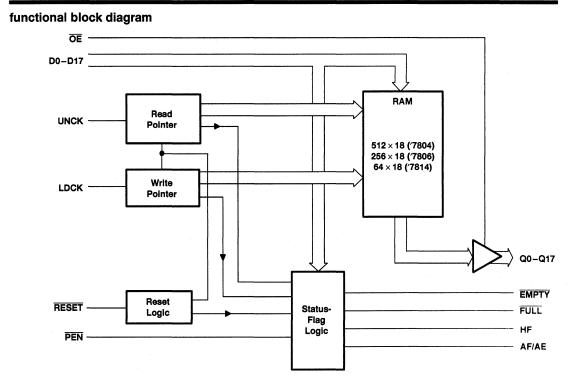

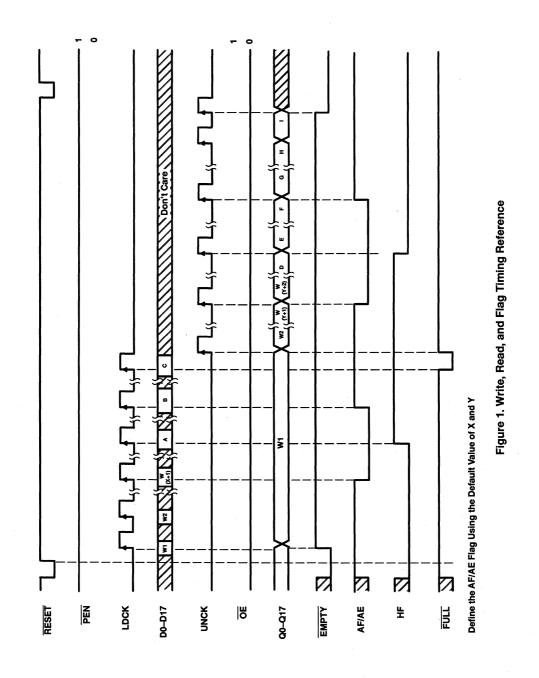

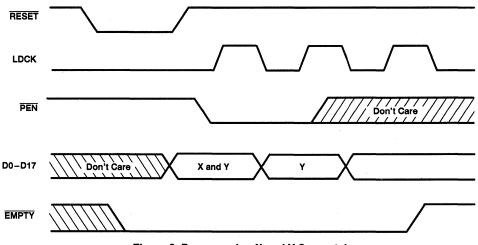

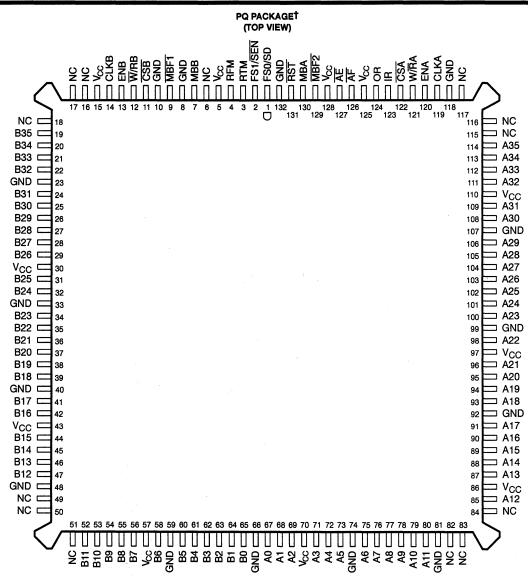

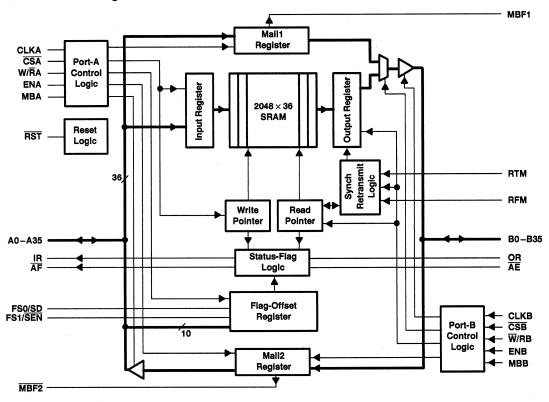

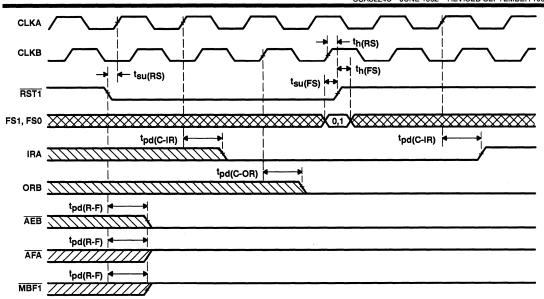

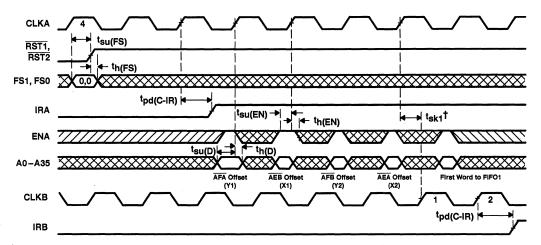

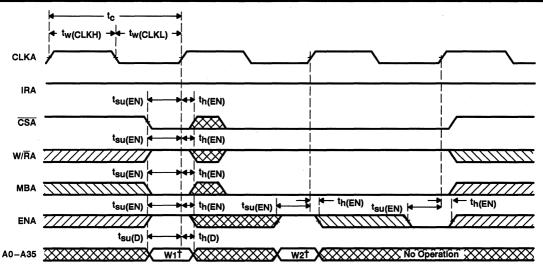

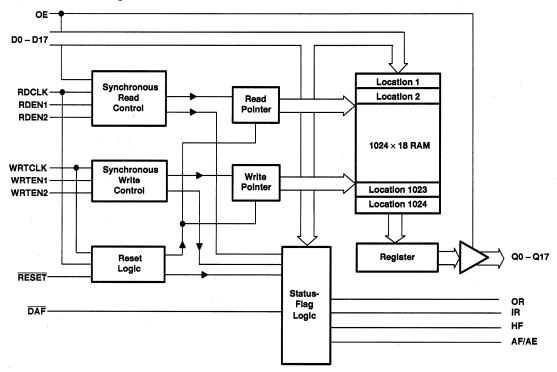

Each advanced FIFO is constructed with a dual-port SRAM, read and write addressincrementing logic, and flag circuitry. Rising-edge-triggered clocks are featured on all TI FIFOs, with self-timed reads and writes on memory that allow a large variance of usable pulse widths. TI's *strobed* style FIFO writes data to memory on each low-to-high transition of the load-clock (LDCK) input and reads data on each rising edge of the unload-clock (UNCK) input.

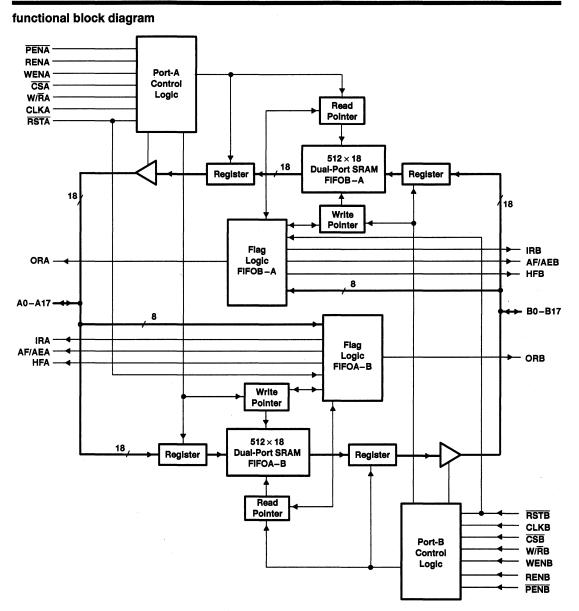

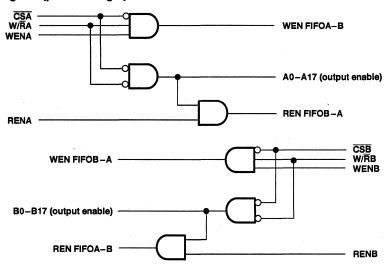

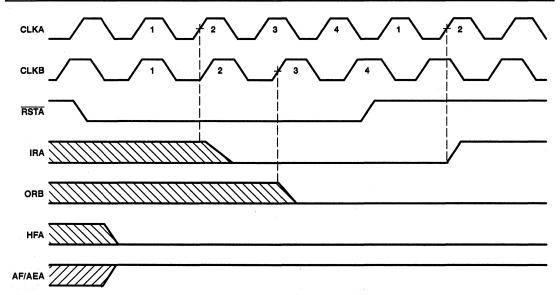

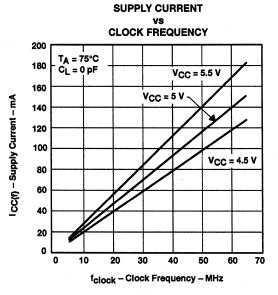

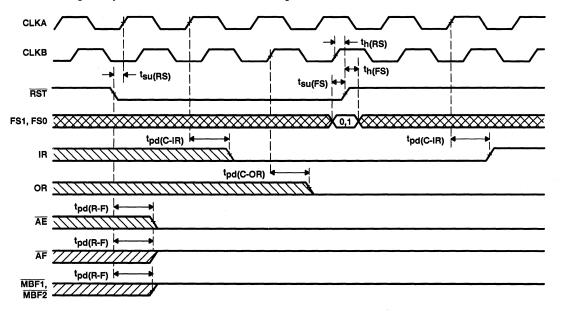

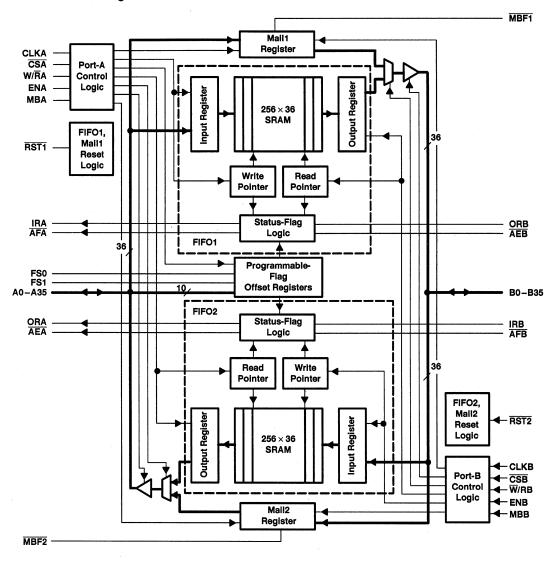

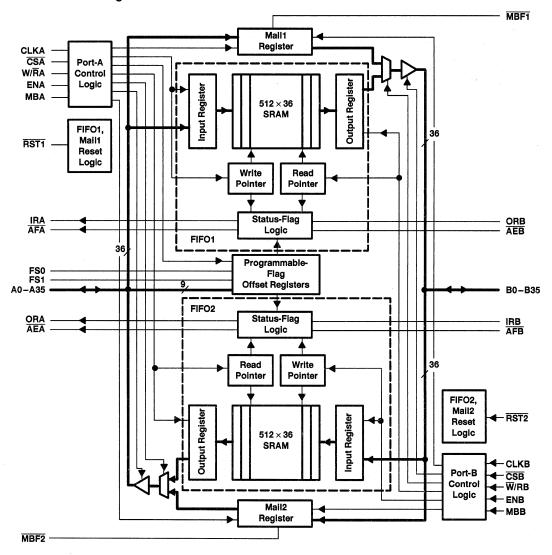

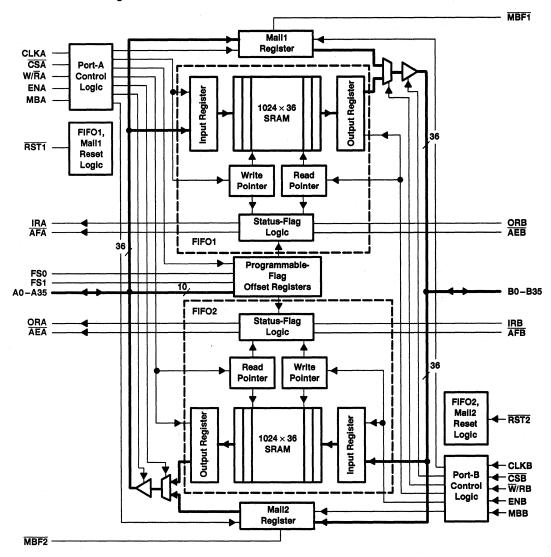

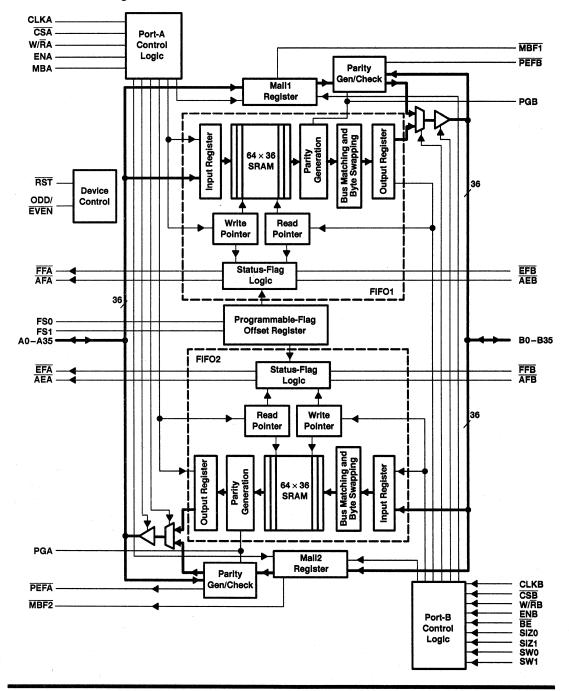

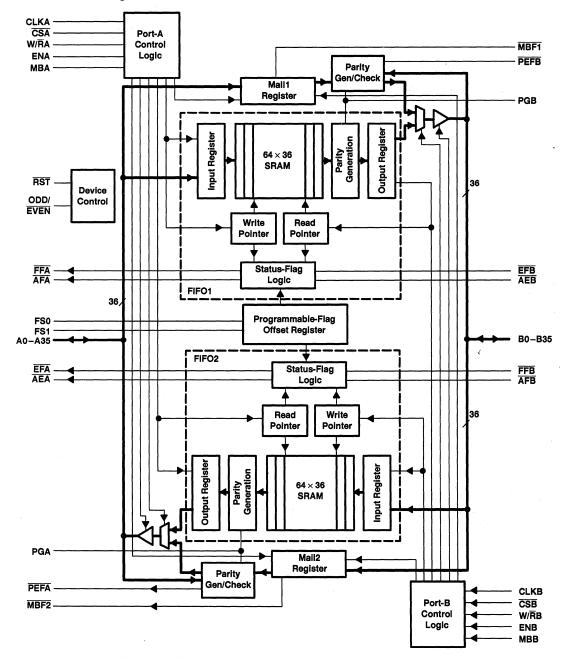

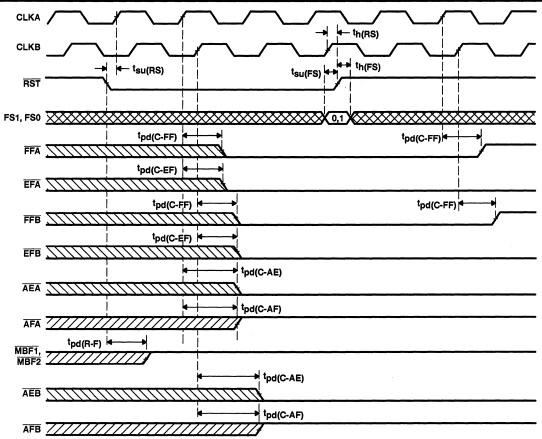

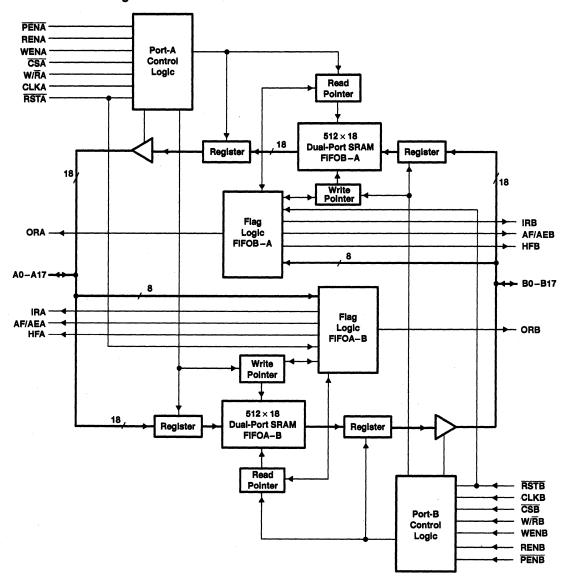

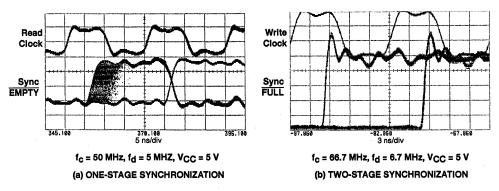

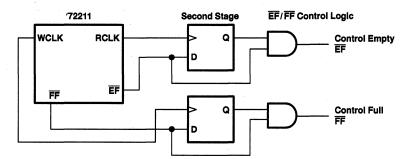

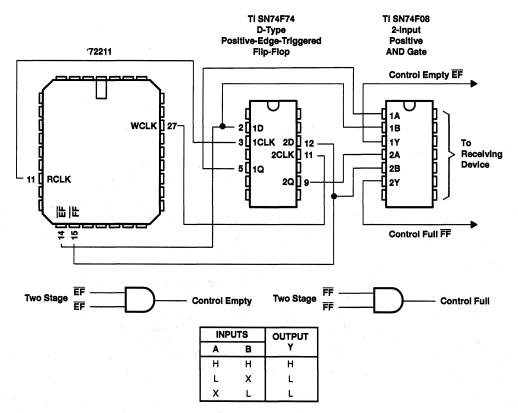

TI's *clocked* style FIFO also can receive asynchronous clocks for writing and reading data, but the clock inputs are designed to be continuous, with the rising edge affecting data transfers when separate enable signals are asserted. This characteristic allows a seamless interface between the device and other high-speed buses or microprocessors with similar control. The availability of the free-running clock also provides the means to synchronize the full and empty status flags as reliable control signals and reduce the amount of external support logic. Each TI clocked FIFO has the empty flag synchronized to the read clock and the full flag synchronized to the write clock with at least two flip-flop stages. Clocked FIFOs produced in advanced CMOS technology can support clock frequencies up to 67 MHz. The SN74ABT7819, produced in advanced BiCMOS technology, is capable of speeds up to 80 MHz. The SN74ABT7819 is also a bidirectional FIFO with two independent FIFO memories combined on one chip to buffer data in opposite directions.

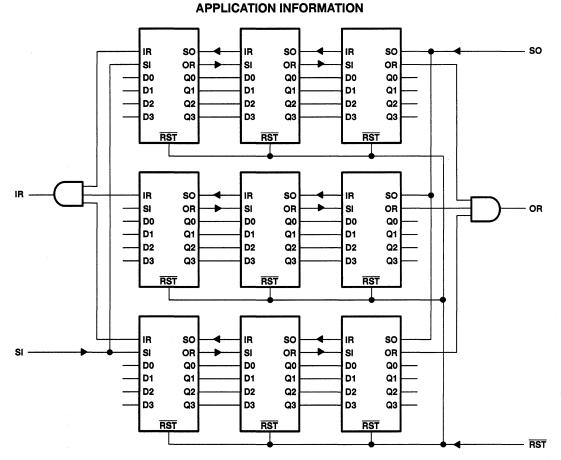

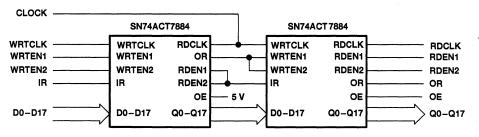

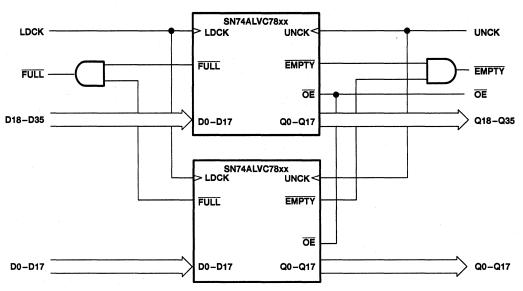

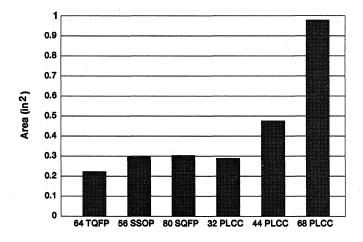

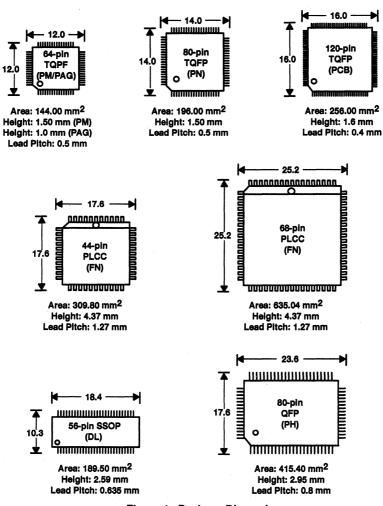

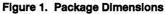

Memory organization of the FIFOs ranges in depth from 16 words to 16384 words and data bit widths of 1, 4, 5, 8, 9, 18, 32, and 36. The under and deeper FIFOs offer a high level of integration and board-space savings, where previously, multiple FIFOs had to be cascaded to achieve the desired architecture. To accommodate the need to reduce package area as data widths increase, many TI FIFO memories are offered in thin surface-mount packages. The SSOP and TQFP packages with 25-mil, 0.5-mm, and 0.4-mm lead pitch, respectively, can reduce the FIFO-dedicated board area by greater than 70% over PLCC packages.

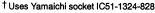

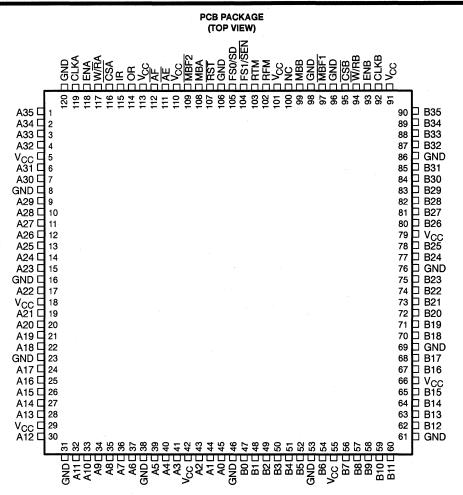

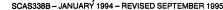

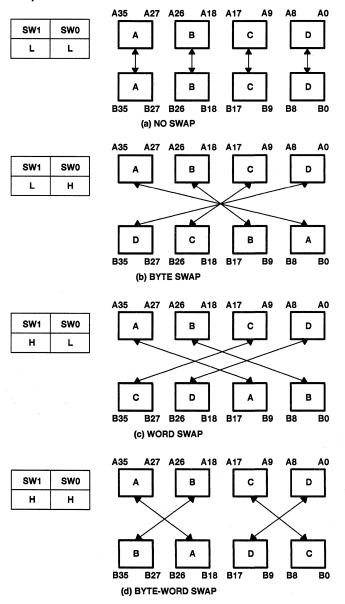

TI continues to offer leading-edge solutions to customers' needs in both packaging technology and device architecture. This is evidenced by the 120-pin TQFP with 16-mm  $\times$  16-mm area to house the 32- and 36-bit products. With features such as synchronous retransmit, mailbox-bypass registers, byte swapping, and bus-width matching, these devices provide a high level of integration in a compact area for applications such as interfacing a digital signal processor (DSP) to a host processor and matching systems with different memory organizations.

EPIC, EPIC-IIB, IMPACT, OEC, Widebus, and Multi-Q are trademarks of Texas Instruments Incorporated.

#### PRODUCT STAGE STATEMENTS

*Product stage statements* are used on Texas Instruments data sheets to indicate the development stage(s) of the product(s) specified in the data sheets.

If all products specified in a data sheet are at the same development stage, the appropriate statement from the following list is placed in the lower left corner of the first page of the data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

If not all products specified in a data sheet are at the PRODUCTION DATA stage, then the first statement below is placed in the lower left corner of the first page of the data sheet. Subsequent pages of the data sheet containing PRODUCT PREVIEW information or ADVANCE INFORMATION are then marked in the lower left-hand corner with the appropriate statement given below:

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

vi

| Contonio                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Section 1 – General Information 1                                                                                                                                                                                                                                                                                                                                                                                                                 | -1                 |

| Alphanumeric Index       1-         Product Overview       1-         Glossary       1-         Explanation of Function Tables       1-         D Flip-Flop and Latch Signal Conventions       1-         Thermal Information       1-                                                                                                                                                                                                            | 5<br>7<br>11<br>13 |

| Section 2 – Telecom Single-Bit FIFOs 2                                                                                                                                                                                                                                                                                                                                                                                                            | !-1                |

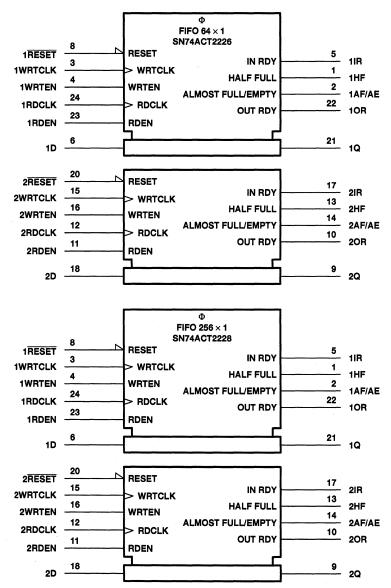

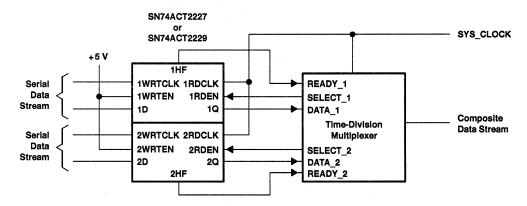

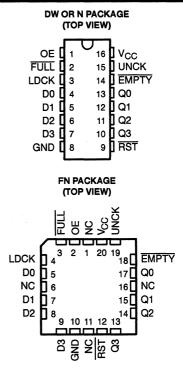

| SN74ACT2226, SN74ACT2228<br>Dual 64 × 1, Dual 256 × 1 Clocked First-In, First-Out Memories                                                                                                                                                                                                                                                                                                                                                        | -15                |

| Section 3 – Reduced-Width FIFOs                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>i-1</b>         |

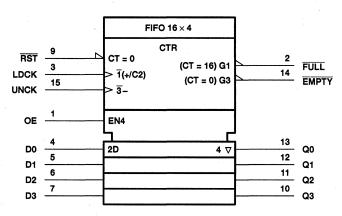

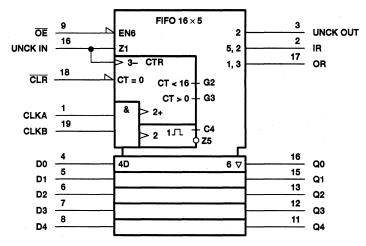

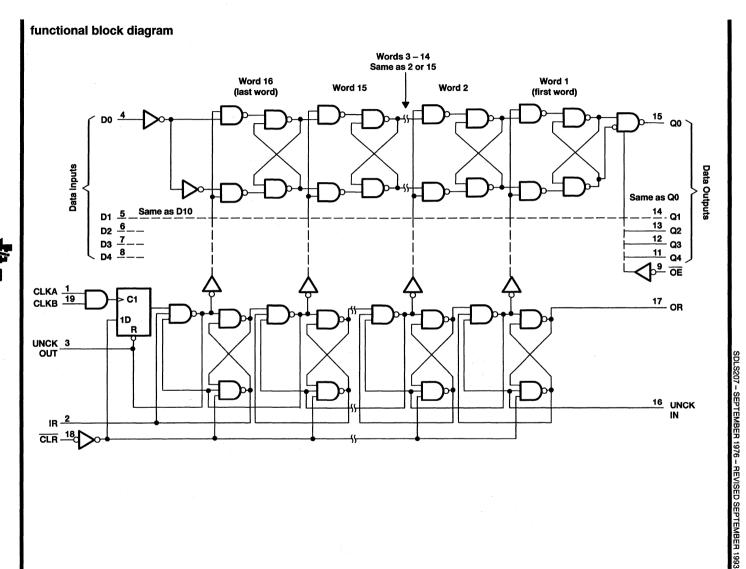

| SN74ALS232B       16 × 4 Asynchronous First-In, First-Out Memory       3-         SN74ALS234       64 × 4 Asynchronous First-In, First-Out Memory       3-         SN74ALS236       64 × 4 Asynchronous First-In, First-Out Memory       3-         SN74ALS236       16 × 5 Asynchronous First-In, First-Out Memory       3-         SN74S225       16 × 5 Asynchronous First-In, First-Out Memory       3-         SN74ALS229B       3-       3- | -11<br>-21         |

| 16 × 5 Asynchronous First-In, First-Out Memory 3-                                                                                                                                                                                                                                                                                                                                                                                                 | -41                |

| SN74ALS233B<br>16 × 5 Asynchronous First-In, First-Out Memory                                                                                                                                                                                                                                                                                                                                                                                     | -57                |

| Section 4 – 9-Bit Clocked/Strobed FIFOs                                                                                                                                                                                                                                                                                                                                                                                                           | -1                 |

| SN74ACT7807         2048 × 9 Clocked First-In, First-Out Memory         4-           SN74ACT7808         2048 × 9 Strobed First-In, First-Out Memory         4-                                                                                                                                                                                                                                                                                   | -19                |

| Section 5 – 8- and 9-Bit Asynchronous FIFOs 5                                                                                                                                                                                                                                                                                                                                                                                                     | -7                 |

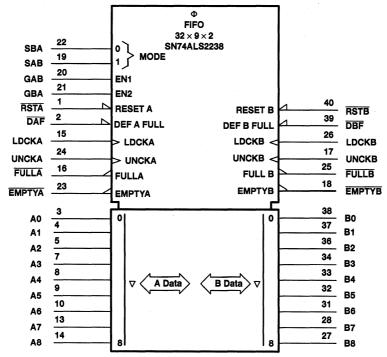

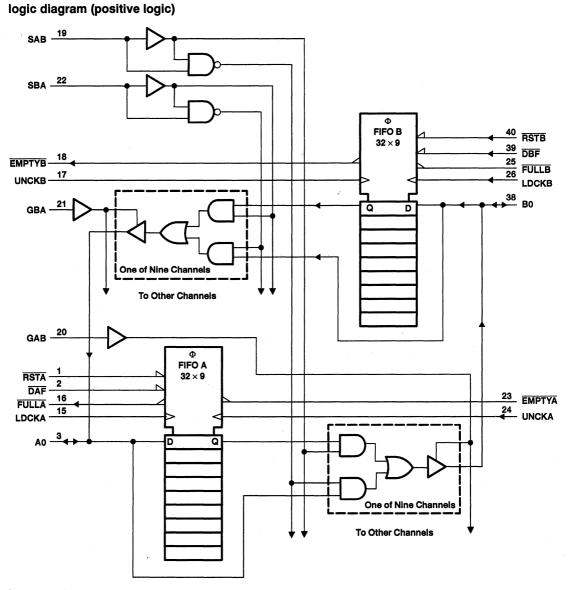

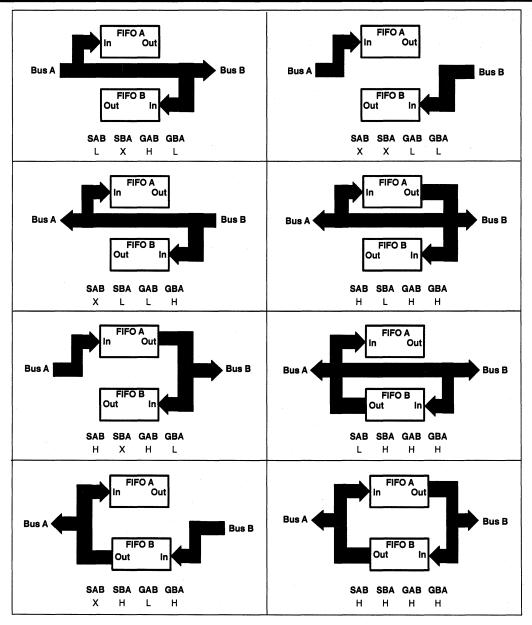

| SN74ALS2238<br>32 × 9 × 2 Asynchronous Bidirectional First-In, First-Out Memory                                                                                                                                                                                                                                                                                                                                                                   |                    |

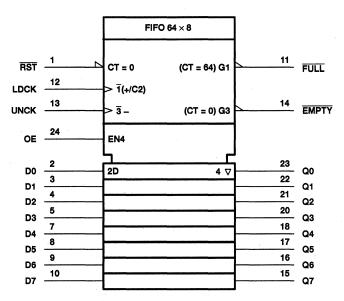

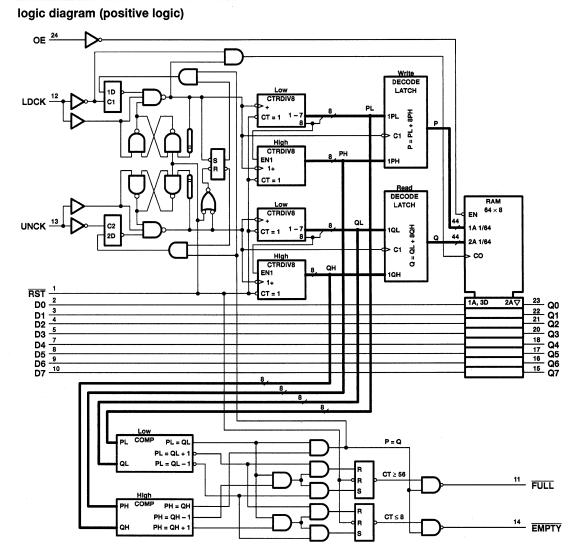

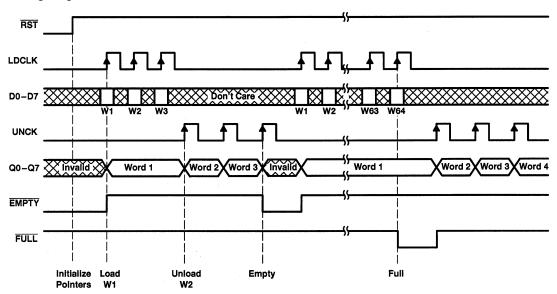

| 64 × 8 Asynchronous First-In, First-Out Memory                                                                                                                                                                                                                                                                                                                                                                                                    |                    |

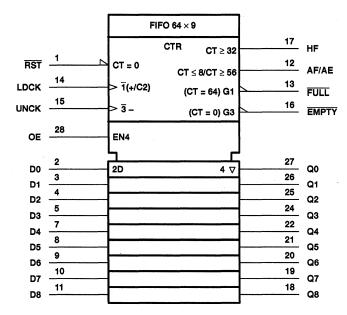

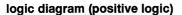

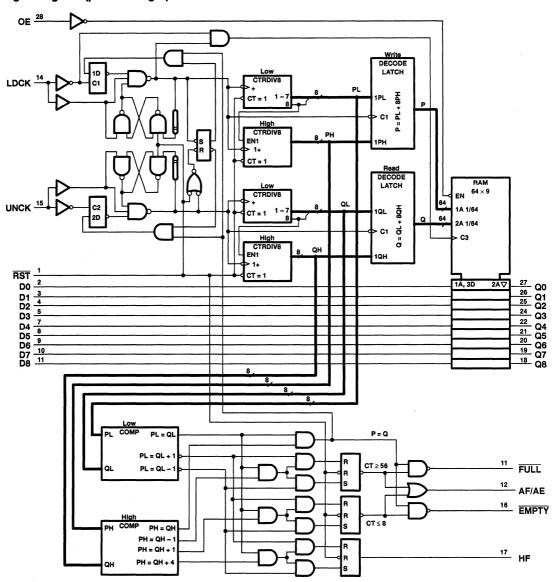

| 64 × 9 Asynchronous First-In, First-Out Memory                                                                                                                                                                                                                                                                                                                                                                                                    |                    |

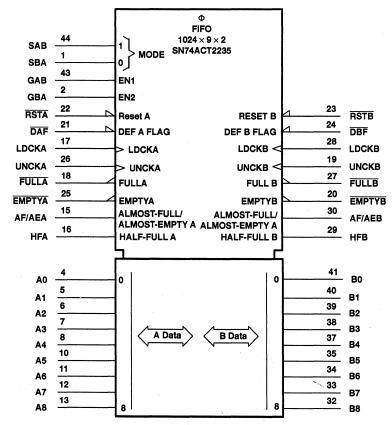

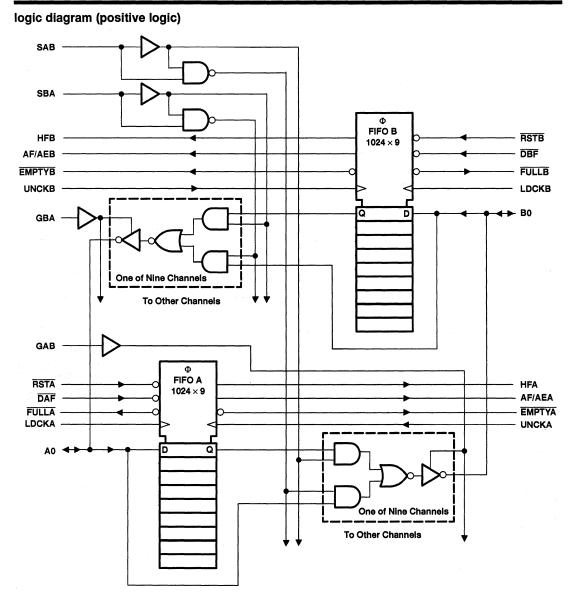

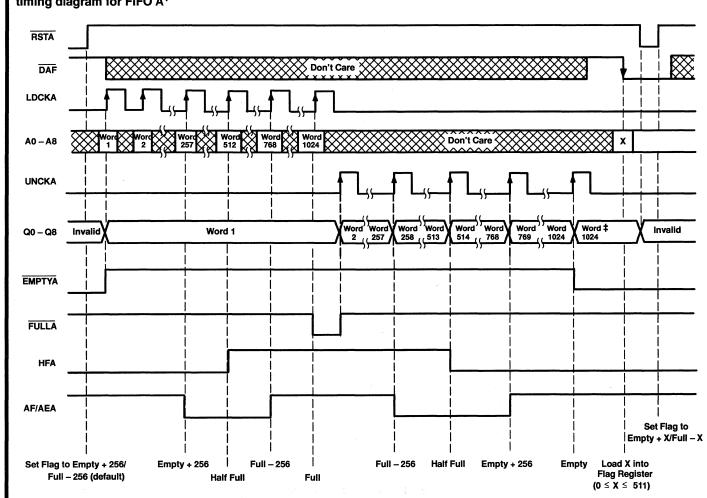

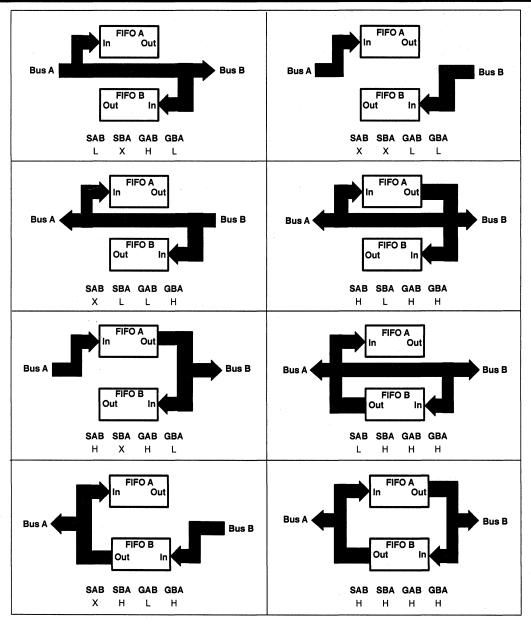

| SN74ACT2235<br>1024 × 9 × 2 Asynchronous Bidirectional First-In, First-Out Memory                                                                                                                                                                                                                                                                                                                                                                 | -49                |

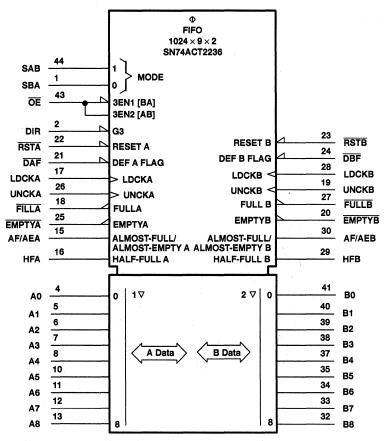

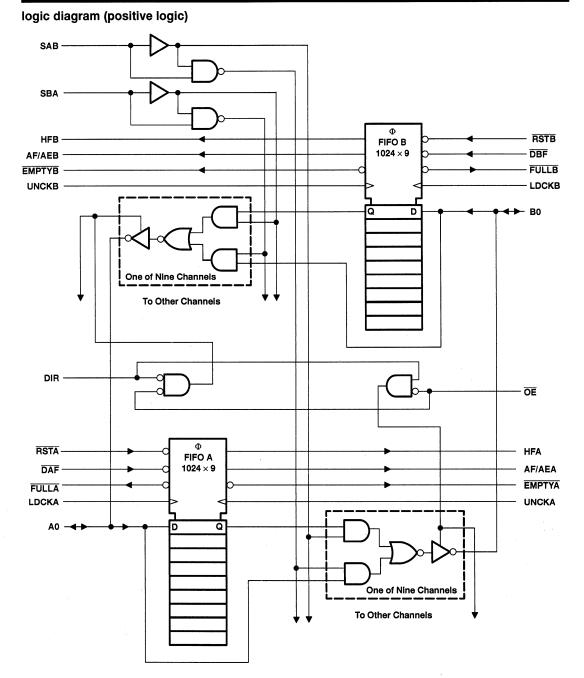

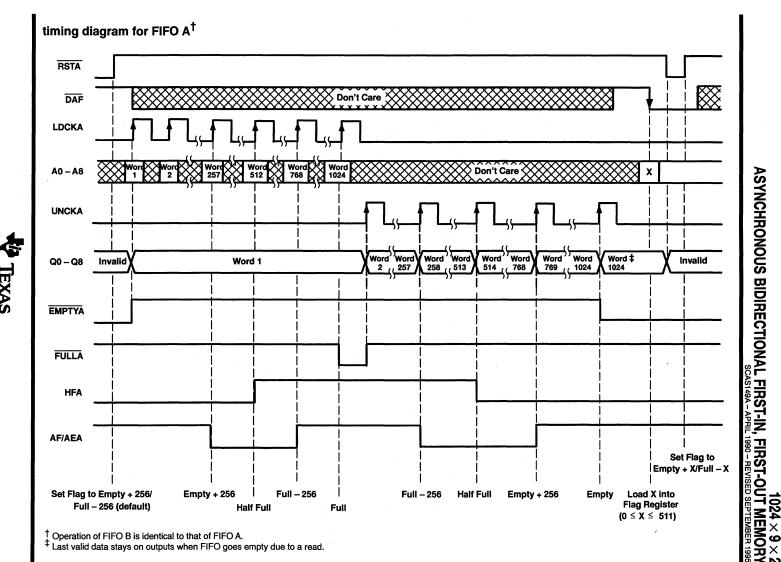

| 1024 × 9 × 2 Asynchronous Bidirectional First-In, First-Out Memory                                                                                                                                                                                                                                                                                                                                                                                |                    |

| Section 6 – 9-Bit Synchronous FIFOs                                                                                                                  | 6–1   |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

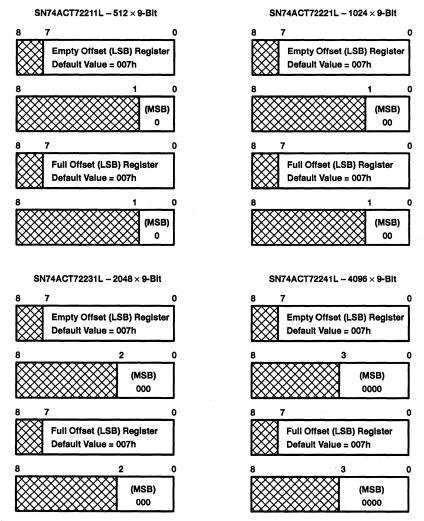

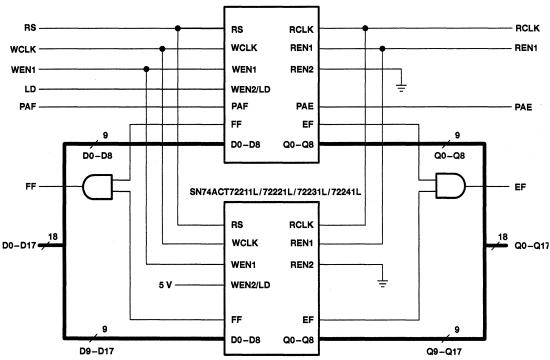

| SN74ACT72211L, SN74ACT72221L, SN74ACT72231L, SN74ACT72241L<br>512 × 9, 1024 × 9, 2048 × 9, and 4096 × 9 Synchronous First-In, First-Out Memories     | 6–3   |

| Section 7 – 18-Bit Clocked FIFOs                                                                                                                     | 7–1   |

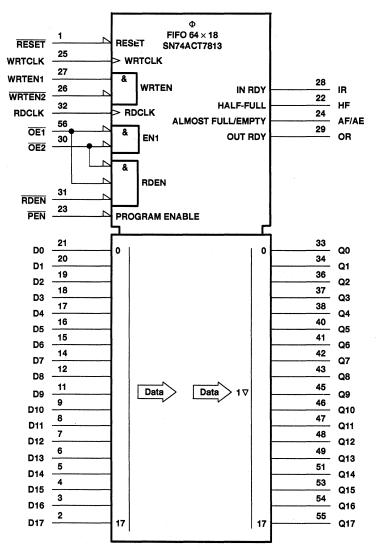

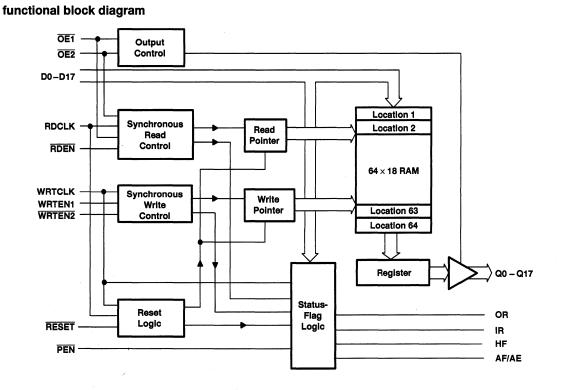

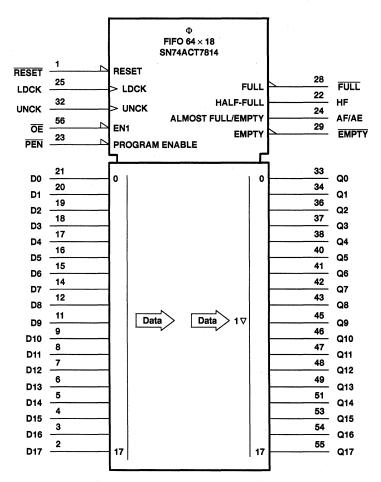

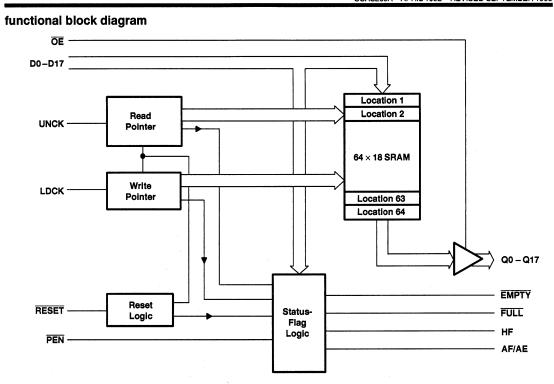

| SN74ACT7813<br>64 × 18 Clocked First-In, First-Out Memory                                                                                            | 7–3   |

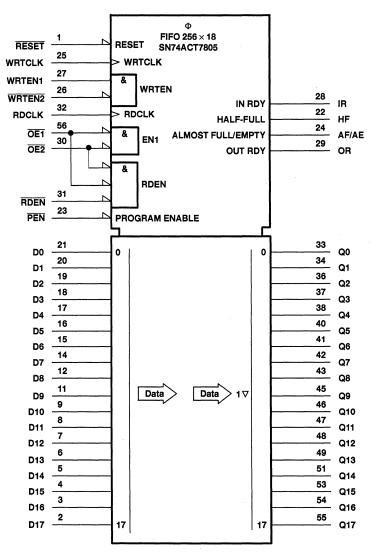

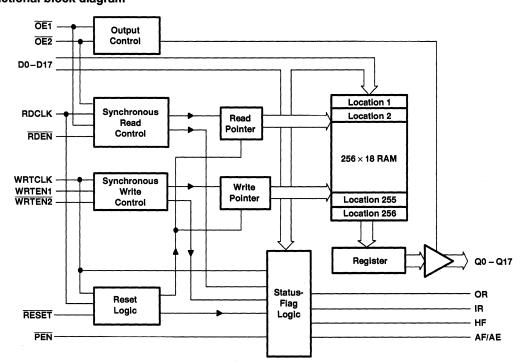

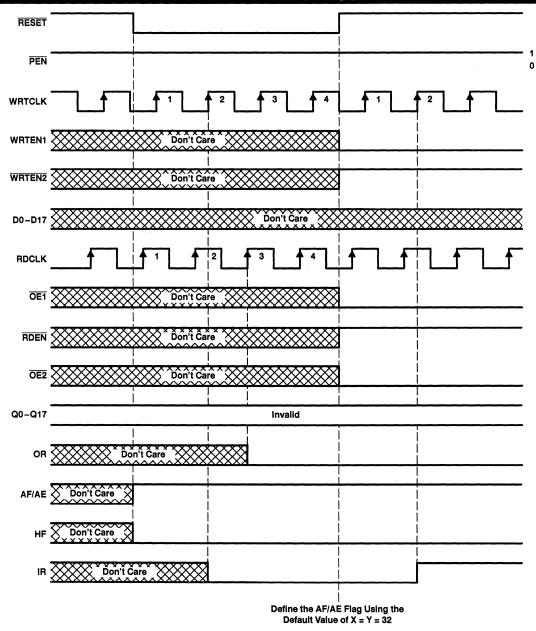

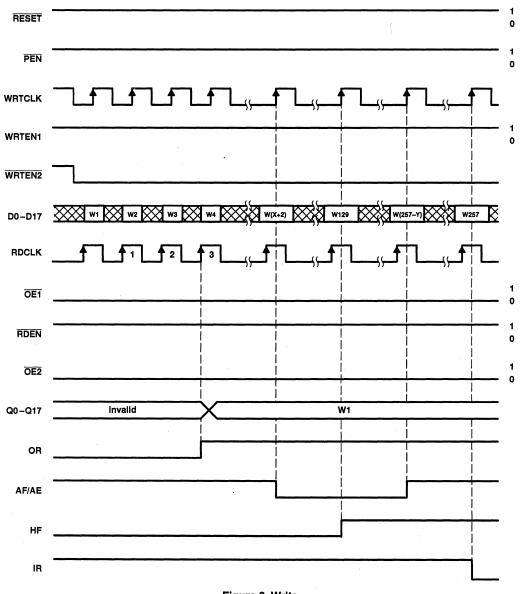

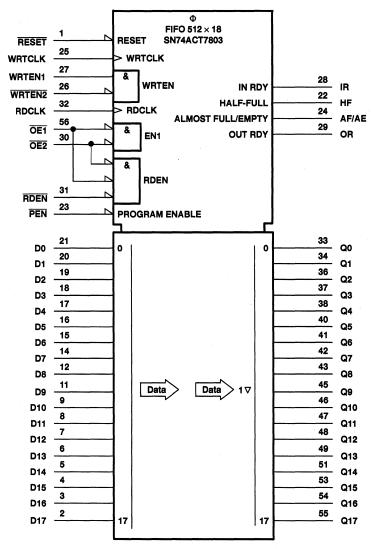

| SN74ACT7805<br>256 × 18 Clocked First-In, First-Out Memory<br>SN74ACT7803                                                                            | 7–17  |

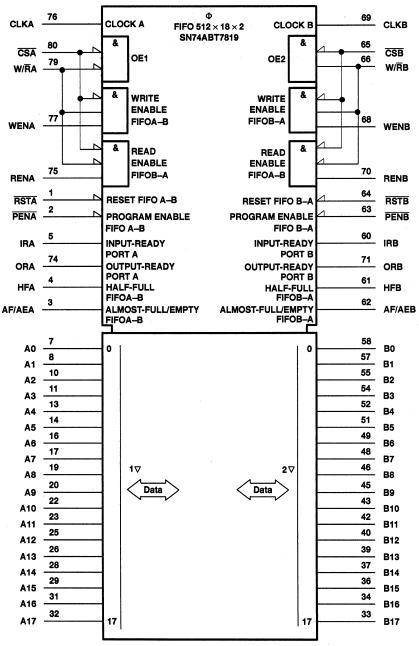

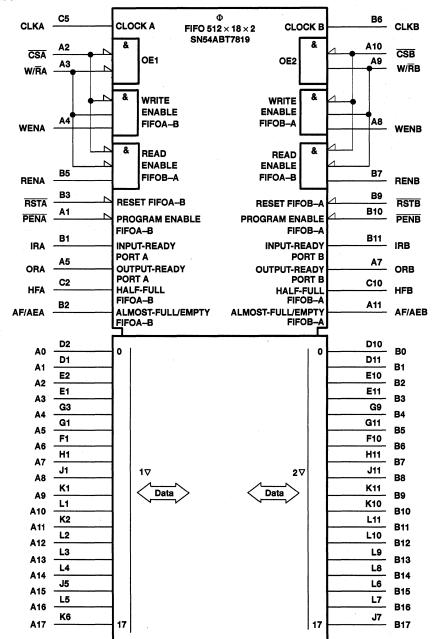

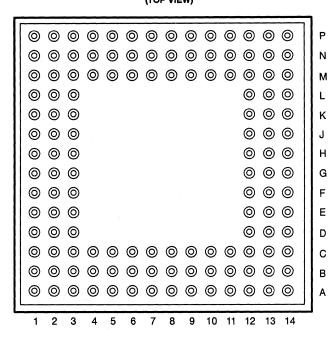

| 512 × 18 Clocked First-In, First-Out Memory<br>SN74ABT7819                                                                                           | 7–31  |

| 512 × 18 × 2 Clocked Bidirectional First-In, First-Out Memory<br>SN74ACT7811                                                                         | 7–45  |

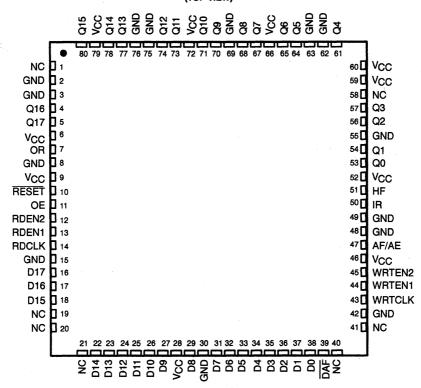

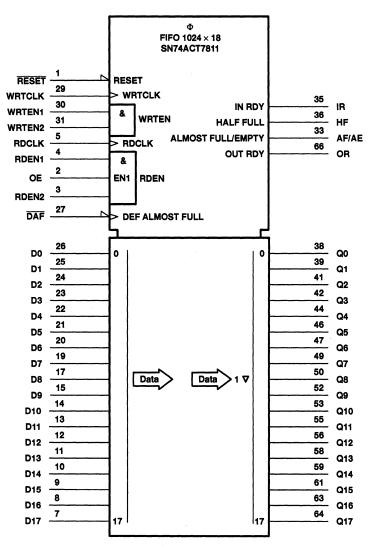

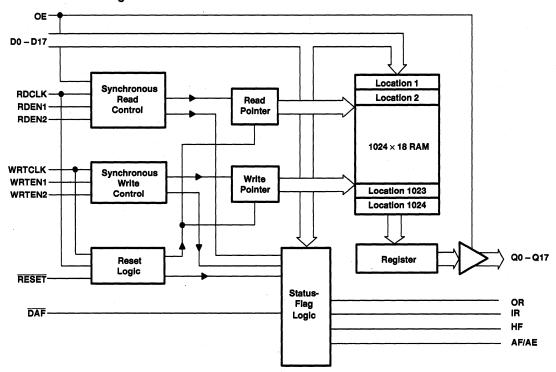

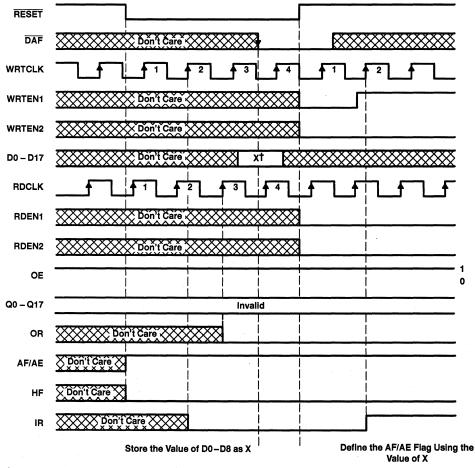

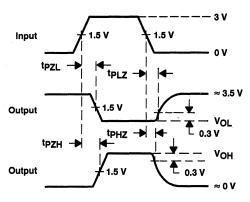

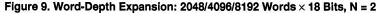

| 1024 × 18 Clocked First-In, First-Out Memory<br>SN74ACT7881                                                                                          | 7-65  |

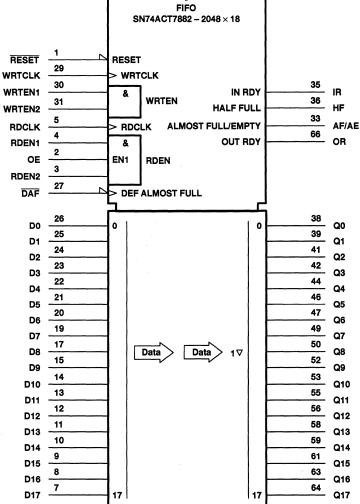

| 1024 × 18 Clocked First-In, First-Out Memory<br>SN74ACT7882                                                                                          | 7–81  |

| 2048 × 18 Clocked First-In, First-Out Memory<br>SN74ACT7884                                                                                          | 7–97  |

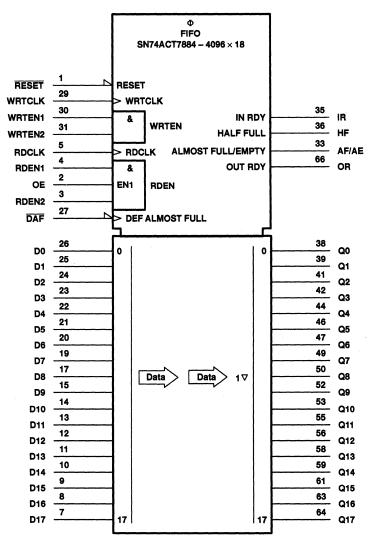

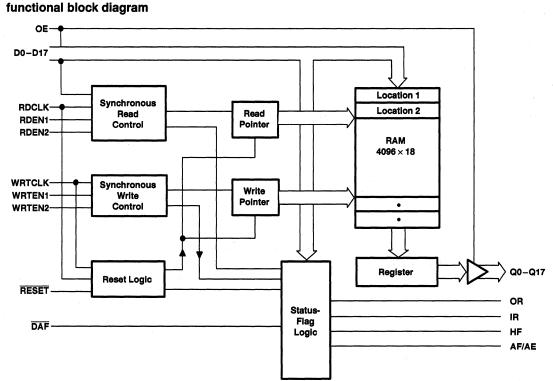

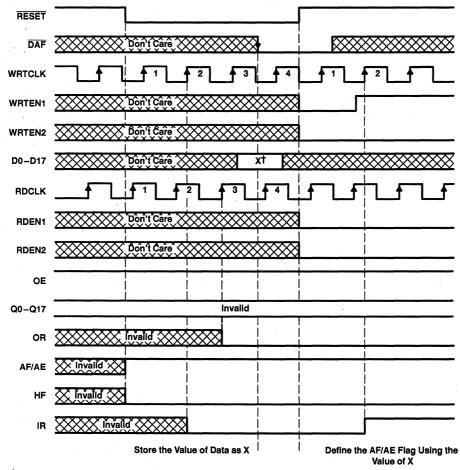

| 4096 × 18 Clocked First-In, First-Out Memory                                                                                                         | 7–113 |

| Section 8 – 18-Bit Strobed FIFOs                                                                                                                     | 8-1   |

| SN74ACT7814<br>64 × 18 Strobed First-In, First-Out Memory                                                                                            | 8–3   |

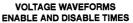

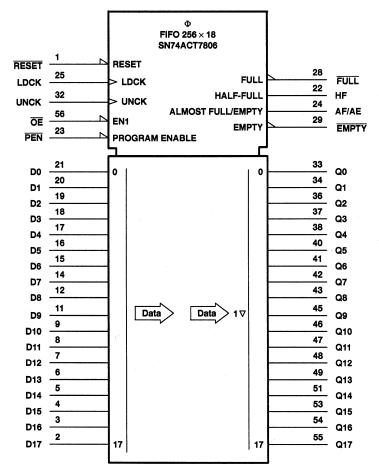

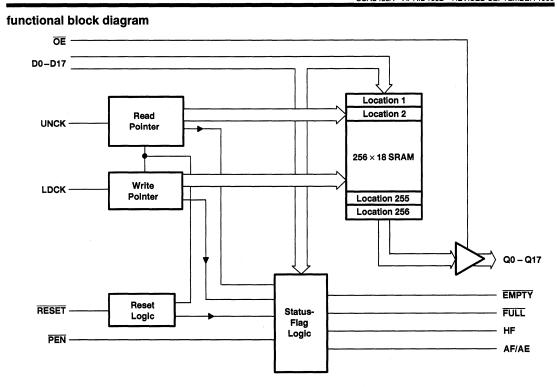

| SN74ACT7806<br>256 × 18 Strobed First-In, First-Out Memory                                                                                           |       |

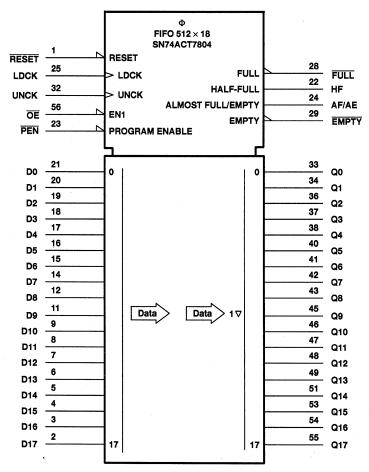

| SN74ACT7804<br>512 × 18 Strobed First-In, First-Out Memory                                                                                           |       |

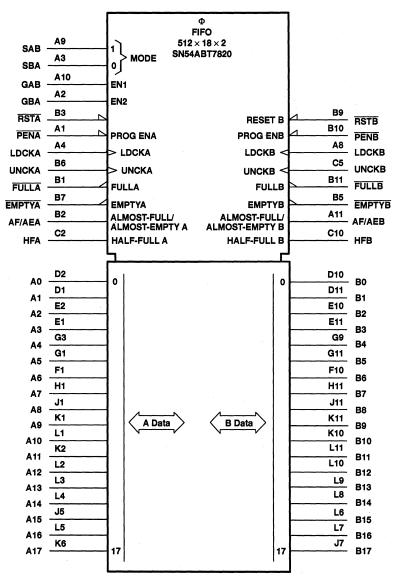

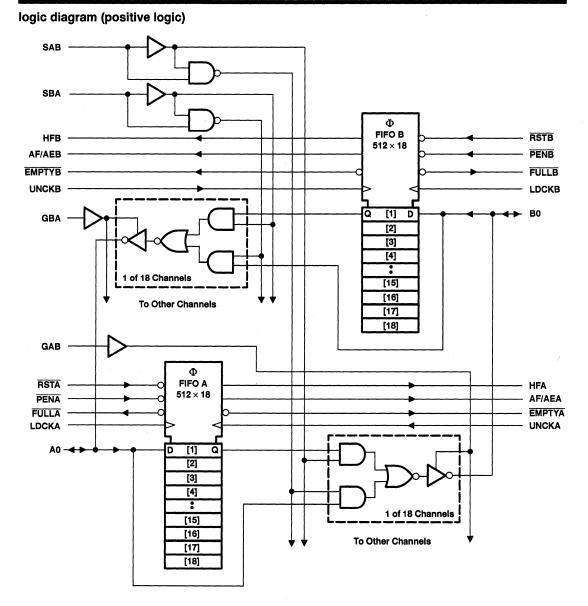

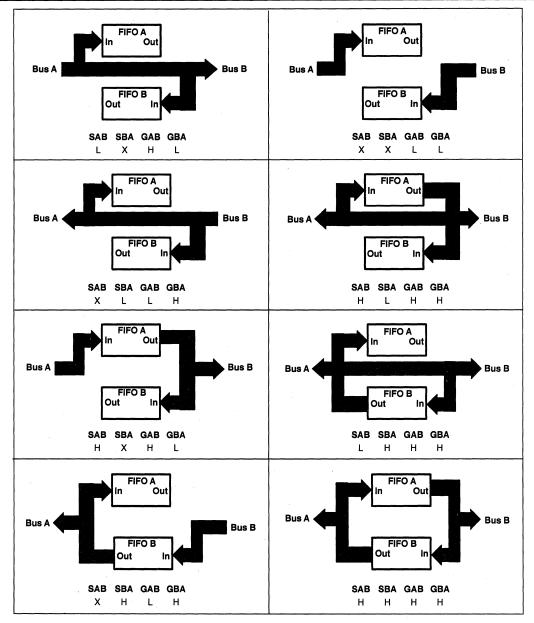

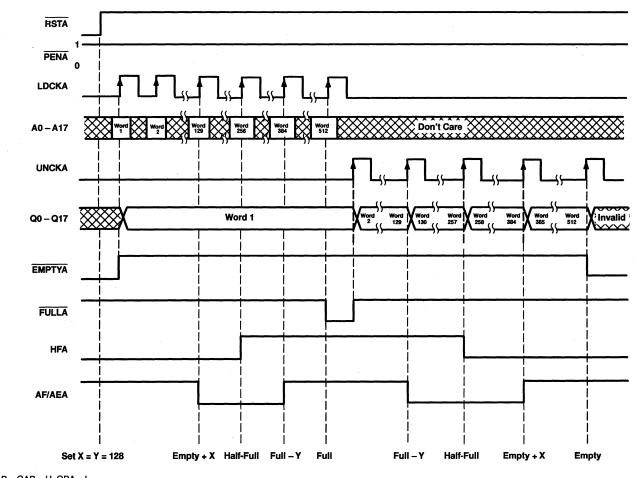

| SN74ABT7820<br>512 × 18 × 2 Strobed Bidirectional First-In, First-Out Memory                                                                         |       |

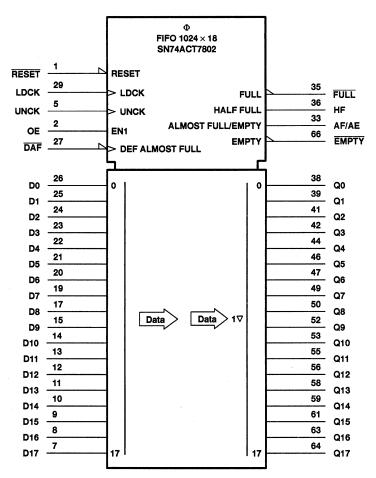

| SN74ACT7802<br>1024 × 18 Strobed First-In, First-Out Memory                                                                                          | 8-53  |

| Section 9 – Multi-Q™ 18-Bit FIFO                                                                                                                     | 9–1   |

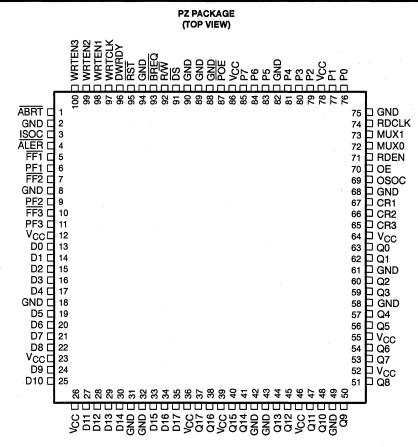

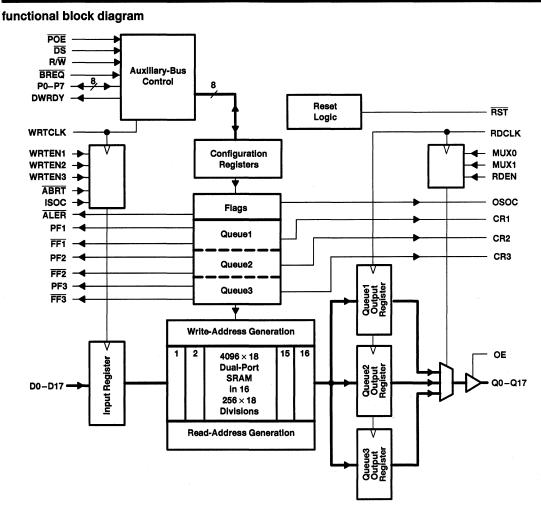

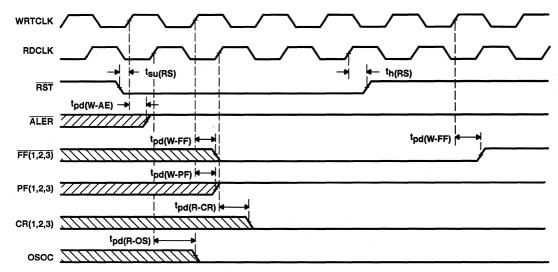

| SN74ACT53861<br>4096 × 18 Clocked Multiple-Queue (Multi-Q™) First-In, First-Out Memory<br>With Three Programmable-Depth Buffers and Cell-Based Flags | 9–3   |

| Section 10 – 3.3-V Low-Powered 18-Bit FIFOs                                                                                                          | 10-1  |

| SN74ALVC7803, SN74ALVC7805, SN74ALVC7813<br>512 × 18, 256 × 18, 64 × 18 Low-Powered Clocked First-In, First-Out Memories                             | 10-3  |

| SN74ALVC7804, SN74ALVC7806, SN74ALVC7814<br>512 × 18, 256 × 18, 64 × 18 Low-Powered First-In, First-Out Memories                                     | 10–17 |

| Section 11 – DSP 32- and 36-Bit Clocked FIFOs                                                                                                        | 11–1  |

| SN74ACT3631<br>512 × 36 Clocked First-In, First-Out Memory                                                                                           | 11-3  |

| SN74ACT3641<br>1024 × 36 Clocked First-In, First-Out Memory                                                                                          |       |

| SN74ACT3651<br>2048 × 36 Clocked First-In, First-Out Memory                                                                                          |       |

|                                                                                                                                                      |       |

| Section 11 – DSP 32- and 36-Bit Clocked FIFOs ( | (continued) | . 11–1 |

|-------------------------------------------------|-------------|--------|

|-------------------------------------------------|-------------|--------|

| SN74ACT3622                                                                    |        |

|--------------------------------------------------------------------------------|--------|

| 256 × 36 × 2 Clocked Bidirectional First-In, First-Out Memory                  | 11-81  |

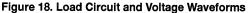

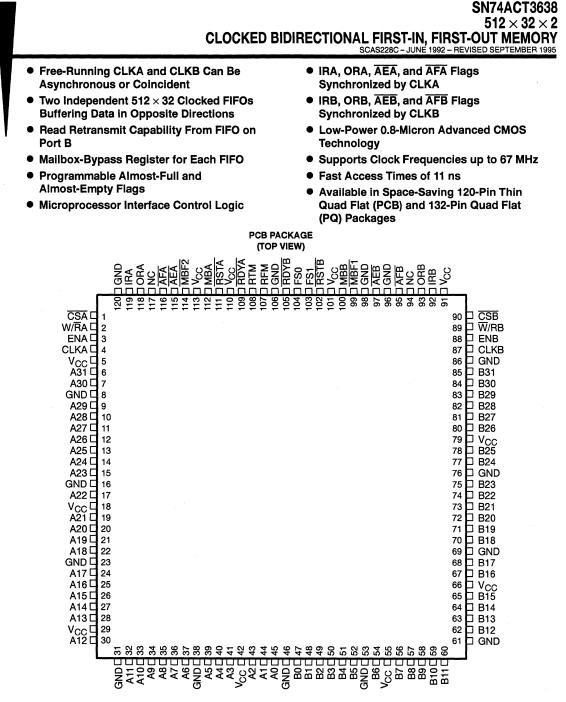

| SN74ACT3638                                                                    |        |

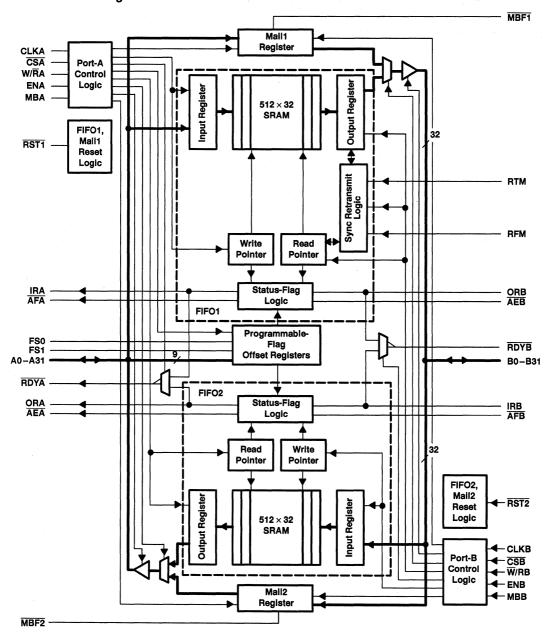

| 512 × 32 × 2 Clocked Bidirectional First-In, First-Out Memory                  | 11–107 |

| SN74ACT3632                                                                    |        |

| 512 × 36 × 2 Clocked Bidirectional First-In, First-Out Memory                  | 11–137 |

| SN74ACT3642                                                                    |        |

| 1024 × 36 × 2 Clocked Bidirectional First-In, First-Out Memory                 | 11–163 |

| Section 12 – Internetworking 36-Bit Clocked FIFOs                              | 12-1   |

| SN74ABT3613                                                                    |        |

| 64 × 36 Clocked First-In, First-Out Memory With Bus Matching and Byte Swapping | 12–3   |

| SN74ABT3614                                                                    |        |

| $64 \times 36 \times 2$ Clocked Bidirectional First-In, First-Out Memory       | 10.05  |

| With Bus Matching and Byte Swapping                                            | 12-35  |

| Section 13 – High-Bandwidth Computing 36-Bit Clocked FIFOs                     | 13–1   |

| SN74ABT3611                                                                    |        |

| 64 × 36 Clocked First-In, First-Out Memory                                     | 13–3   |

| SN74ABT3612                                                                    |        |

| 64 × 36 × 2 Clocked Bidirectional First-In, First-Out Memory                   | 13-29  |

| Section 14 – Military FIFOs                                                    | 14_1   |

|                                                                                |        |

| Introduction                                                                   | 14–3   |

| SN54ABT7819                                                                    |        |

| 512 × 18 × 2 Clocked Bidirectional First-In, First-Out Memory                  | 14-5   |

| SN54ABT7820                                                                    | 44.05  |

| 512 × 18 × 2 Strobed Bidirectional First-In, First-Out Memory                  | 14-25  |

| SN54ACT7811<br>1024 × 18 Clocked First-In, First-Out Memory                    | 14 20  |

| SN54ACT7881                                                                    | 14-09  |

| 1024 × 18 Clocked First-In, First-Out Memory                                   | 14-55  |

| SN54ABT3614                                                                    | 14-00  |

| 64 × 36 × 2 Clocked Bidirectional First-In, First-Out Memory                   |        |

| With Bus Matching and Byte Swapping                                            | 14-71  |

| SN54ACT3641                                                                    |        |

| 1024 × 36 Clocked First-In, First-Out Memory                                   | 14-113 |

| Section 15 – Application Reports                                               | 15–1   |

| FIFO Solutions for Increasing Clock Rates and Data Widths                      |        |

|                                                                                |        |

| FIFO Surface-Mount Package Information                                         |        |

|                                                                                |        |

| Metastability Performance of Clocked FIFOs                                     |        |

| Multiple-Queue First-In. First-Out Memory SN74ACT53861                         |        |

|                                                                                | 10-00  |

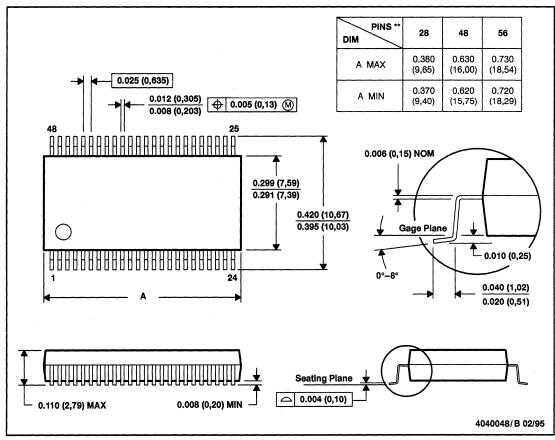

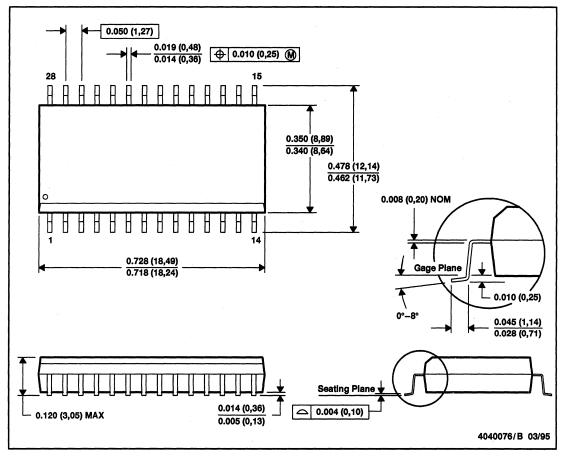

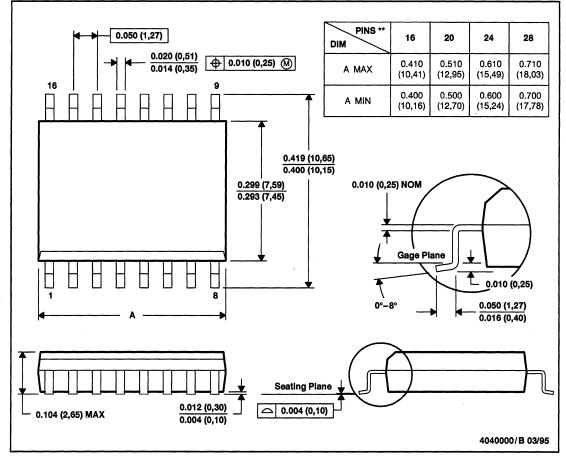

| Section 16 – Mechanical Data | 16–1  |

|------------------------------|-------|

| Ordering Instructions        | 16–3  |

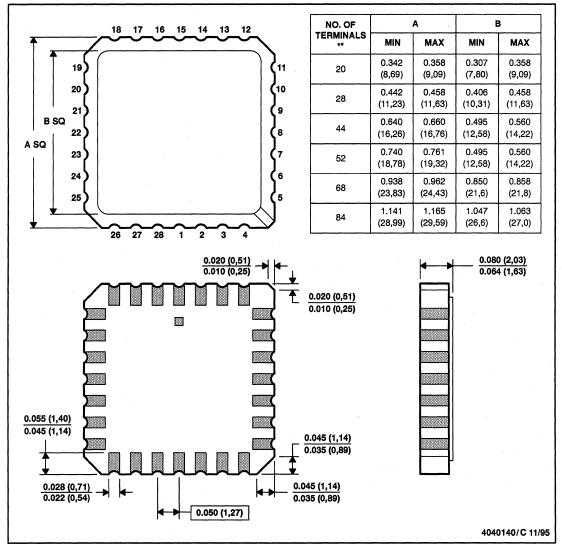

| DL (R-PDSO-G**)              |       |

| DV (R-PDSO-G28)              | 16-6  |

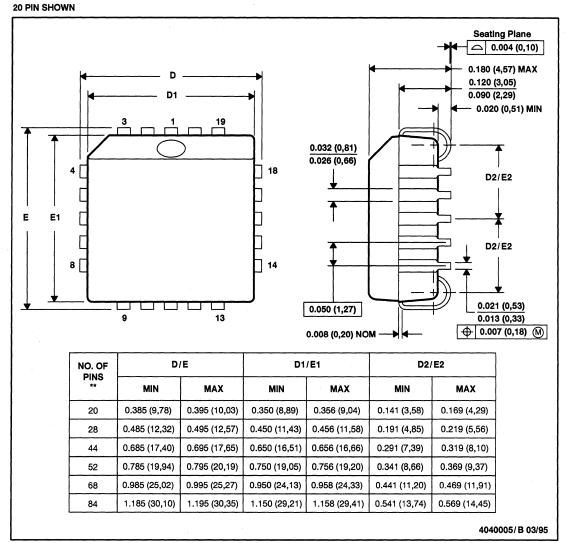

| DW (R-PDSO-G**)              | 16–7  |

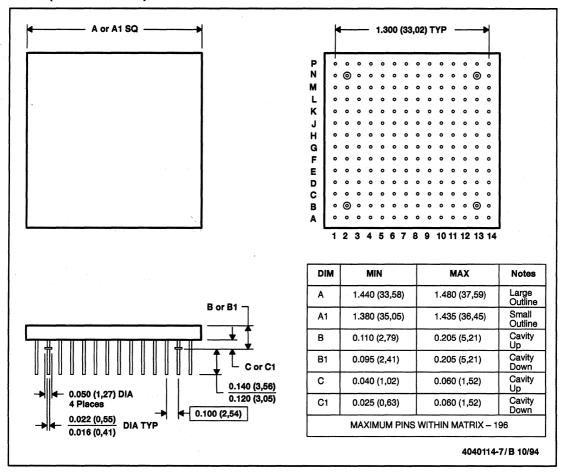

| FK (S-CQCC-N**)              | 16–8  |

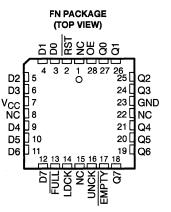

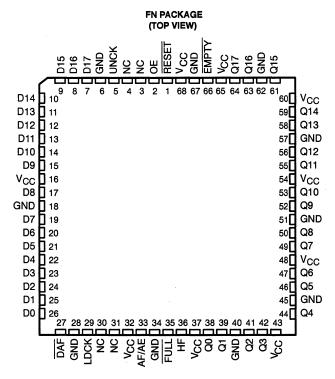

| FN (S-PQCC-J**)              |       |

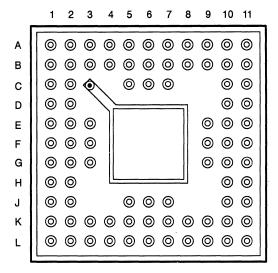

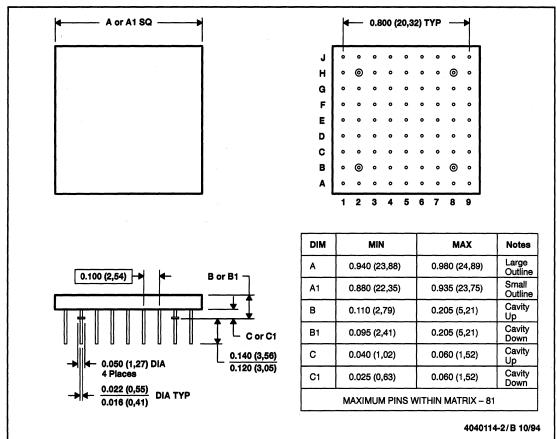

| GA-GB (S-CPGA-P9 × 9)        |       |

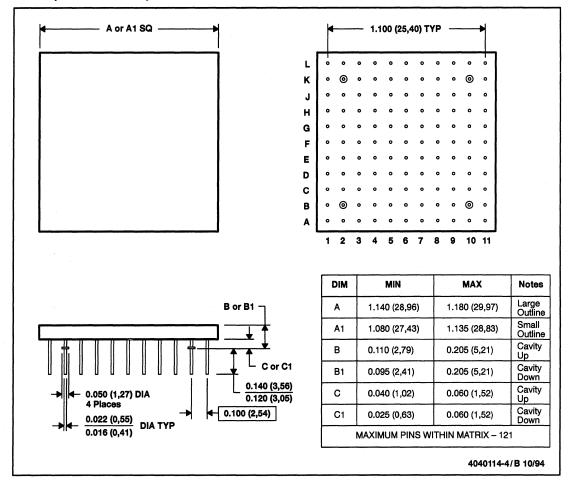

| GA-GB (S-CPGA-P11 × 11)      |       |

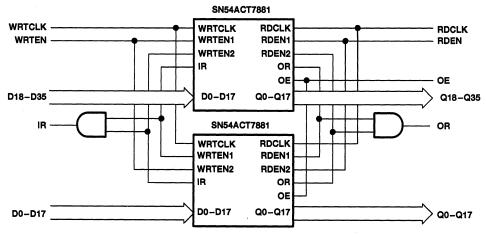

| GA-GB (S-CPGA-P14 × 14)      |       |

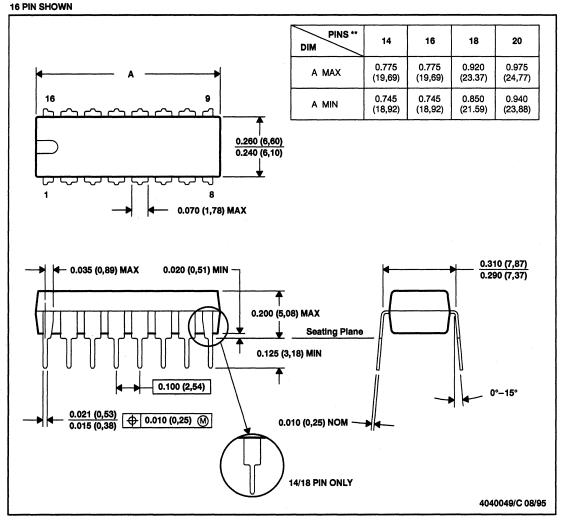

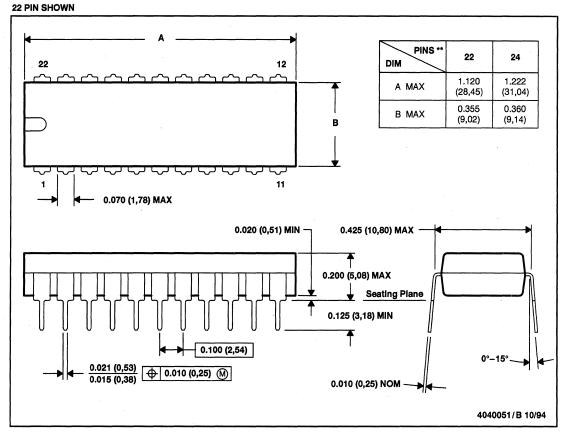

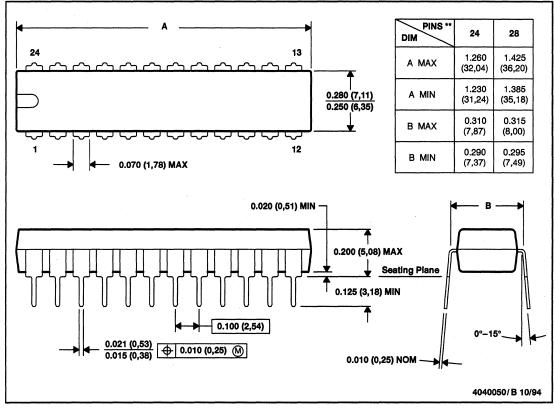

| N (R-PDIP-T**)               |       |

| N (R-PDIP-T**)               |       |

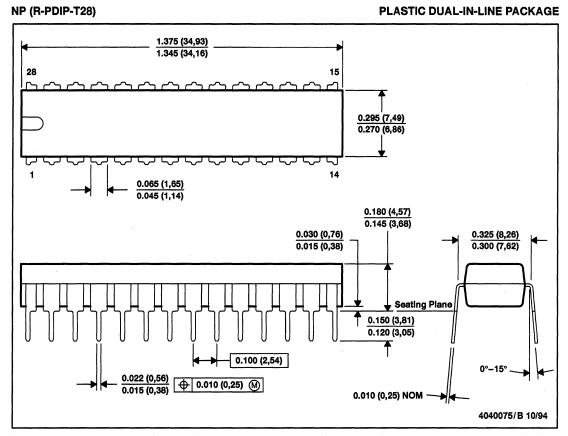

| NP (R-PDIP-T28)              |       |

| NT (R-PDIP-T**)              |       |

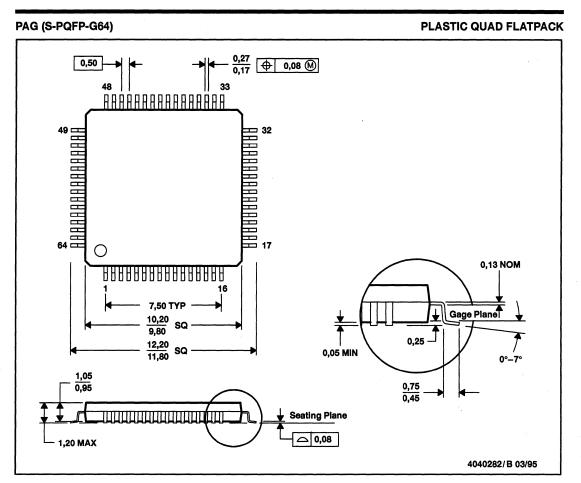

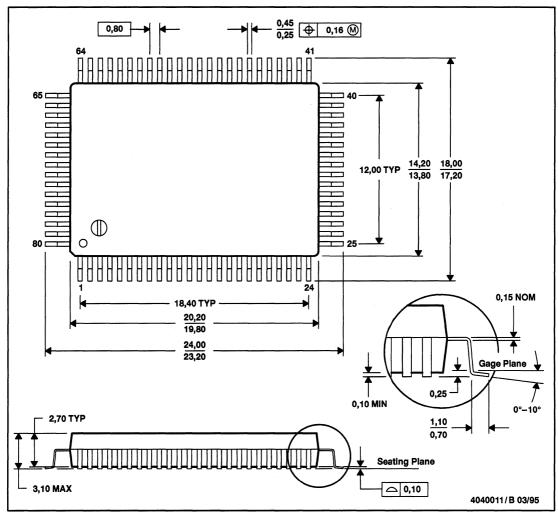

| PAG (S-PQFP-G64)             |       |

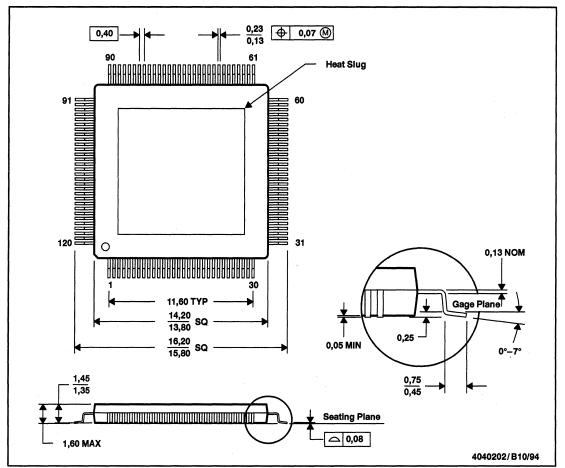

| PCB (S-PQFP-G120)            |       |

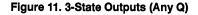

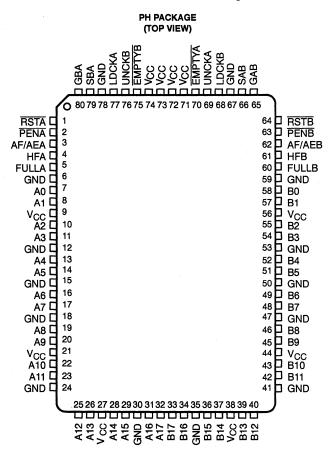

| PH (R-PQFP-G80)              |       |

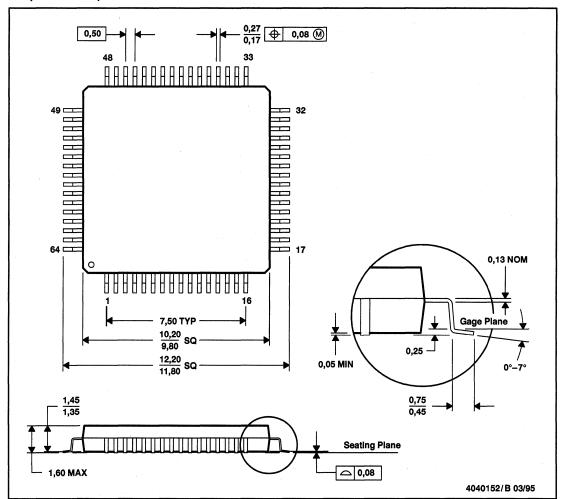

| PM (S-PQFP-G64)              | 16–20 |

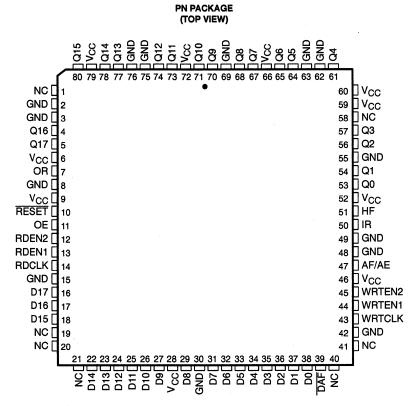

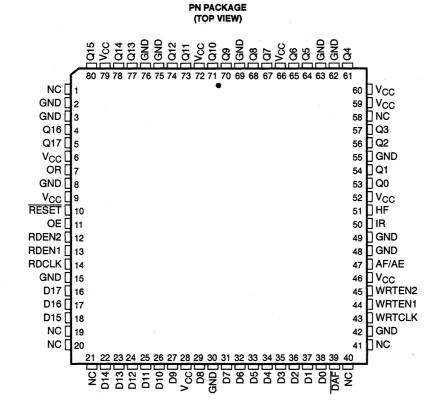

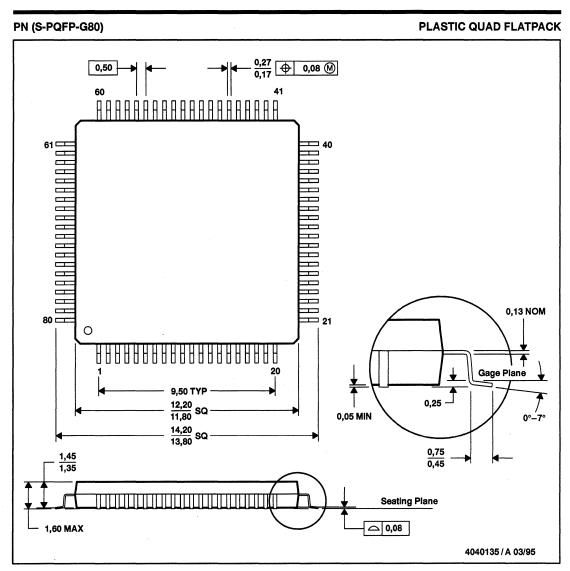

| PN (S-PQFP-G80)              |       |

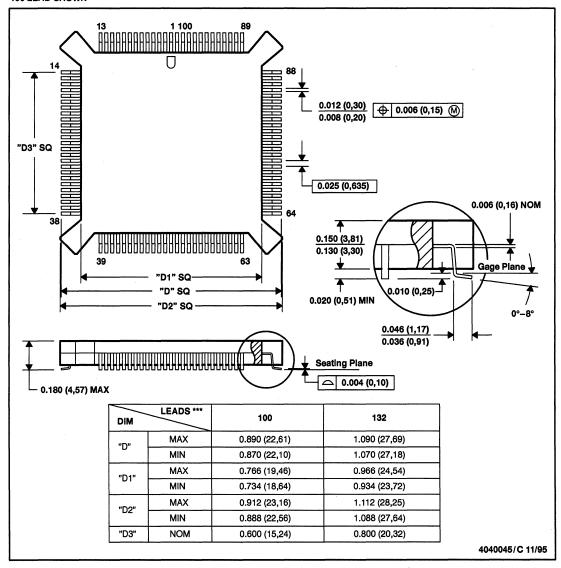

| PQ (S-PQFP-G***)             |       |

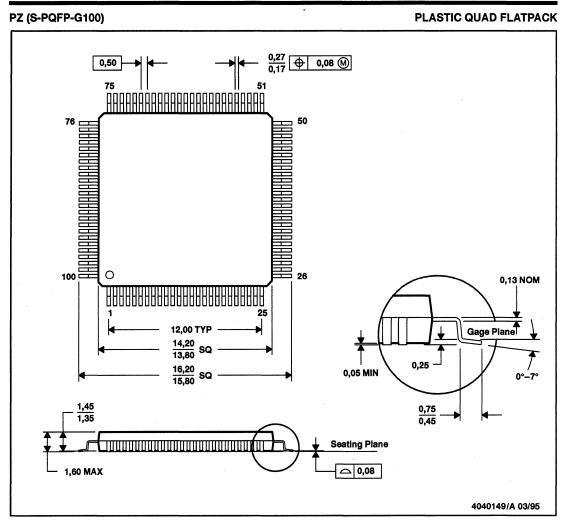

| PZ (S-PQFP-G100)             | 16–23 |

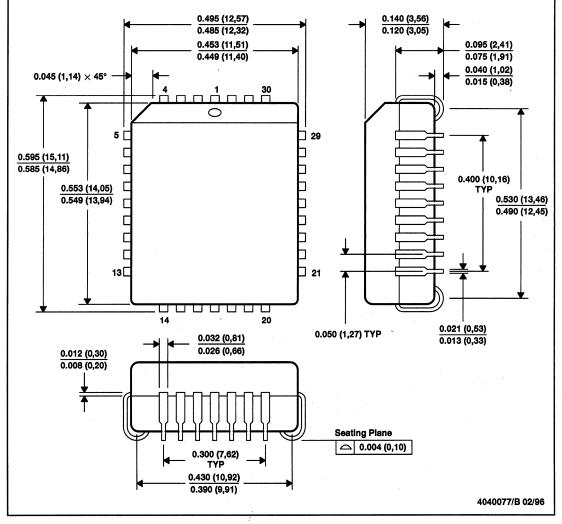

| RJ (R-PQCC-J32)              | 16–24 |

х

| General Information                           | 1  |

|-----------------------------------------------|----|

| Telecom Single-Bit FIFOs                      | 2  |

| Reduced-Width FIFOs                           | 3  |

| 9-Bit Clocked/Strobed FIFOs                   | 4  |

| 8- and 9-Bit Asynchronous FIFOs               | 5  |

| 9-Bit Synchronous FIFOs                       | 6  |

| 18-Bit Clocked FIFOs                          | 7  |

| 18-Bit Strobed FIFOs                          | 8  |

| Multi-Q™ 18-Bit FIFO                          | 9  |

| 3.3-V Low-Powered 18-Bit FIFOs                | 10 |

| DSP 32- and 36-Bit Clocked FIFOs              | 11 |

| Internetworking 36-Bit Clocked FIFOs          | 12 |

| High-Bandwidth Computing 36-Bit Clocked FIFOs | 13 |

| Military FIFOs                                | 14 |

| Application Reports                           | 15 |

| Mechanical Data                               | 16 |

# Contents

|                                          | Page |

|------------------------------------------|------|

| Alphanumeric Index                       |      |

| Product Overview                         |      |

| Glossary                                 |      |

| Explanation of Function Tables           | 1–11 |

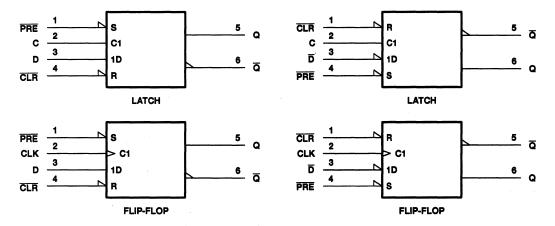

| D Flip-Flop and Latch Signal Conventions |      |

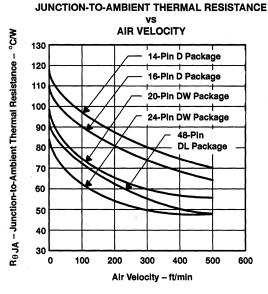

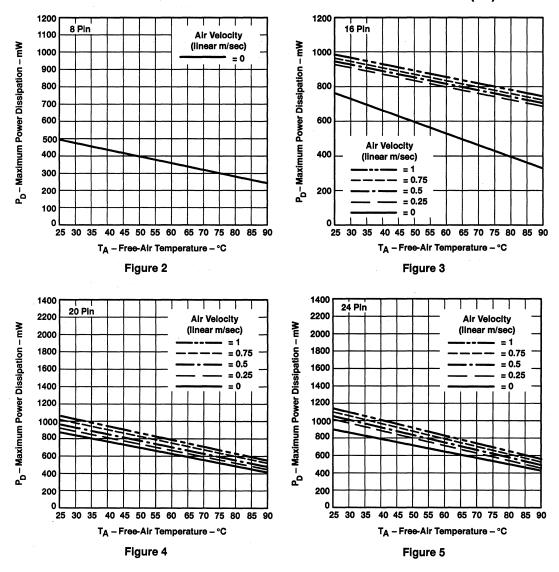

| Thermal Information                      |      |

# **ALPHANUMERIC INDEX**

| DEVICE        | PAGE   | DEVICE        | PAGE  |

|---------------|--------|---------------|-------|

| SN54ABT3614   | 14–71  | SN74ACT7803   |       |

| SN54ABT7819   | 14–5   | SN74ACT7804   |       |

| SN54ABT7820   | 14–25  | SN74ACT7805   |       |

| SN54ACT3641   | 14–113 | SN74ACT7806   | 8–15  |

| SN54ACT7811   | 14–39  | SN74ACT7807   | 4–3   |

| SN54ACT7881   | 14–55  | SN74ACT7808   | 4–19  |

| SN74ABT3611   | 13–3   | SN74ACT7811   |       |

| SN74ABT3612   | 13–29  | SN74ACT7813   |       |

| SN74ABT3613   | 12–3   | SN74ACT7814   | 8–3   |

| SN74ABT3614   | 12–35  | SN74ACT7881   |       |

| SN74ABT7819   |        | SN74ACT7882   |       |

| SN74ABT7820   | 8–39   | SN74ACT7884   |       |

| SN74ACT2226   | 2–3    | SN74ACT53861  |       |

| SN74ACT2227   | 2–15   | SN74ACT72211L | 6–3   |

| SN74ACT2228   | 2–3    | SN74ACT72221L | 6–3   |

| SN74ACT2229   | 2–15   | SN74ACT72231L | 6–3   |

| SN74ACT2235   | 5-49   | SN74ACT72241L | 6–3   |

| SN74ACT2236   | 5–61   | SN74ALS229B   |       |

| SN74ACT3622   | 11–81  | SN74ALS232B   | 3–3   |

| SN74ACT3631   | 11–3   | SN74ALS233B   | 3–49  |

| SN74ACT3632   | 11–137 | SN74ALS234    | 3–11  |

| SN74ACT3638   | 11–107 | SN74ALS235    |       |

| SN74ACT3641   | 11–29  | SN74ALS236    |       |

| SN74ACT3642   | 11–163 | SN74ALS2232A  | 5–13  |

| SN74ACT3651   | 11–55  | SN74ALS2233A  | 5–21  |

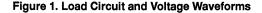

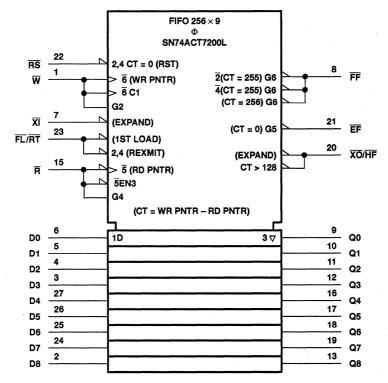

| SN74ACT7200L  | 5–29   | SN74ALS2238   | 5–3   |

| SN74ACT7201LA | 5–29   | SN74ALVC7803  | 10–3  |

| SN74ACT7202LA | 5–29   | SN74ALVC7804  | 10–17 |

| SN74ACT7203L  | 5–73   | SN74ALVC7805  | 10–3  |

| SN74ACT7204L  | 5–73   | SN74ALVC7806  | 10–17 |

| SN74ACT7205L  | 5–73   | SN74ALVC7813  | 10–3  |

| SN74ACT7206L  | 5–73   | SN74ALVC7814  | 10–17 |

| SN74ACT7802   | 8–53   | SN74S225      |       |

|               |        |               |       |

|               |        |               |       |

# **FIFO** Functionality

| DEVICE       | Depth (bits) | Width (bits) | Access Time (ns) | High Sink Capability<br>(IOL≥ 16 mA) | 3-State Outputs | Cascade for Memory<br>Depth | Bidirectional | Dual Independent FIFO | 5-V/3.3-V Counterparts | Flag Programming | Serial Flag Programming | Microprocessor<br>Interface-Control Logic | Mailbox Bypass | Parity Generate | Parity Check | Read Retransmit | Synchronous Read<br>Retransmit | Byte Swapping | Bus Matching | Programmable Depth | Multiple Queues |

|--------------|--------------|--------------|------------------|--------------------------------------|-----------------|-----------------------------|---------------|-----------------------|------------------------|------------------|-------------------------|-------------------------------------------|----------------|-----------------|--------------|-----------------|--------------------------------|---------------|--------------|--------------------|-----------------|

| SN74ACT2226  | 64           | 1            | 20               | ~                                    |                 | ~                           |               | ~                     |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT2227  | 64           | 1            | 9                | ~                                    | ~               | ~                           |               | •                     |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT2228  | 256          | 1            | 20               |                                      |                 | ~                           |               | ~                     |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT2229  | 256          | 1            | 9                | ~                                    | ~               | ~                           |               | ~                     |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALS232   | 16           | 4            | 23               | ~                                    | ~               |                             |               |                       |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALS234   | 64           | 4            | 17               | ~                                    | ~               | ~                           |               |                       |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALS236   | 64           | 4            | 17               | ~                                    | ~               | ~                           |               |                       |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALS229   | 16           | 5            | 30               | ~                                    | ~               |                             |               |                       |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALS233   | 16           | 5            | 30               | ~                                    | ~               |                             |               |                       |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74S225     | 16           | 5            | 75               | ~                                    | ~               | ~                           |               |                       |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALS235   | 64           | 5            | 17               | ~                                    | ~               | ~                           |               |                       |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALS2232  | 64           | 8            | 26               | ~                                    | 1               |                             |               |                       |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALS2238  | 32           | 9            | 33               | ~                                    | 1               |                             | ~             |                       |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              | ~                  |                 |

| SN74ALS2233  | 64           | 9            | 26               | ~                                    | ~               |                             |               |                       |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7200  | 256          | 9            | 15               |                                      | ~               | ~                           |               |                       |                        |                  |                         |                                           |                |                 |              | ~               |                                |               |              |                    |                 |

| SN74ACT72211 | 512          | 9            | 10               |                                      | ~               |                             |               |                       |                        | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7201  | 512          | 9            | 15               |                                      | ~               | ~                           |               |                       |                        |                  |                         | -                                         |                |                 |              | ~               |                                |               |              |                    |                 |

| SN74ACT72221 | 1K           | 9            | 10               |                                      | ~               |                             |               |                       |                        | >                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT2235  | 1K           | 9            | 25               | ~                                    | ~               |                             | ~             |                       |                        | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT2236  | 1K           | 9            | 25               | ~                                    | <b>V</b> .      |                             | ~             |                       |                        | >                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7202  | 1K           | 9            | 15               |                                      | >               | ~                           |               |                       |                        |                  |                         |                                           |                |                 |              | ~               |                                |               |              |                    |                 |

| SN74ACT7807  | 2К           | 9            | 12               | ~                                    | ~               | ~                           |               |                       |                        | >                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT72231 | 2K           | 9            | 10               |                                      | >               |                             |               |                       |                        | >                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7808  | 2K           | 9            | 15               | ~                                    | ~               | ~                           |               |                       |                        | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7203  | 2K           | 9            | 15               |                                      | >               | ~                           |               |                       |                        |                  |                         |                                           |                |                 |              | ~               |                                |               |              |                    |                 |

| SN74ACT72241 | 4K           | 9            | 10               |                                      | ~               |                             |               |                       |                        | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7204  | 4K           | 9            | 15               |                                      | ~               | ~                           |               |                       |                        |                  |                         |                                           |                |                 |              | ~               |                                |               |              |                    |                 |

| SN74ACT7205  | 8K           | 9            | 15               |                                      | ~               | ~                           |               |                       |                        |                  |                         |                                           |                |                 |              | ~               |                                |               |              |                    |                 |

| SN74ACT7206  | 16K          | 9            | 15               |                                      | >               | ~                           |               |                       |                        |                  |                         |                                           |                |                 |              | ~               |                                |               |              |                    |                 |

| SN74ACT7813  | 64           | 18           | 12               | ~                                    | ~               | ~                           | *             |                       | ~                      | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

TEXAS INSTRUMENTS POST OFFICE BOX 665303 DALLAS, TEXAS 75265 ቬ

**PRODUCT OVERVIEW**

## FIFO Functionality (Continued)

|                     | 1            |              | 1                | 1                                   |                 |                             | ·             | r                     |                        | r                | -                       |                                           |                |                 | r            |                 | <u> </u>                       | · · · · · · · | · · · · · ·  |                    |                 |

|---------------------|--------------|--------------|------------------|-------------------------------------|-----------------|-----------------------------|---------------|-----------------------|------------------------|------------------|-------------------------|-------------------------------------------|----------------|-----------------|--------------|-----------------|--------------------------------|---------------|--------------|--------------------|-----------------|

| DEVICE              | Depth (bits) | Width (bits) | Access Time (ns) | High Sink Capability<br>(IOL≥16 mA) | 3-State Outputs | Cascade for Memory<br>Depth | Bidirectional | Dual Independent FIFO | 5-V/3.3-V Counterparts | Flag Programming | Serial Flag Programming | Microprocessor<br>Interface-Control Logic | Mailbox Bypass | Parity Generate | Parity Check | Read Retransmit | Synchronous Read<br>Retransmit | Byte Swapping | Bus Matching | Programmable Depth | Multiple Queues |

| SN74ALVC7813        | 64           | 18           | 13               | ~                                   | <b>V</b> 1      | ~                           | *             |                       | ~                      | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7814         | 64           | 18           | 15               | •                                   | ~               |                             |               |                       | <b>v</b> .             | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALVC7814        | 64           | 18           | 18               | ~                                   |                 |                             |               |                       | 1                      | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7805         | 256          | 18           | 12               |                                     | ~               | ~                           | *             |                       | ~                      | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALVC7805        | 256          | 18           | 13               | . 1                                 | ~               | ~                           | *             |                       | ~                      | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7806         | 256          | 18           | 15               | ~                                   | <b>V</b> 1      |                             |               |                       | ~                      | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALVC7806        | 256          | 18           | 18               |                                     | >               |                             |               |                       | ~                      | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7803         | 512          | 18           | 12               | <                                   | >               | ~                           | *             |                       | ~                      | >                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ALVC7803        | 512          | 18           | 13               | <                                   | >               | ~                           | *             |                       | ~                      | >                |                         |                                           |                | 1               |              |                 |                                |               |              |                    |                 |

| SN74ACT7804         | 512          | 18           | 15               | ~                                   | ~               |                             |               |                       | ~                      | ~                |                         |                                           | -              |                 |              |                 |                                |               |              |                    |                 |

| SN74ALVC7804        | 512          | 18           | 18               | ~                                   | ~               |                             |               |                       | ~                      | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ABT7819         | 512          | 18           | 9                | ~                                   | ~               | ~                           | >             |                       |                        | ~                |                         | ~                                         |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ABT7820         | 512          | 18           | 12               | ~                                   | ~               |                             | ~             |                       |                        | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    | -               |

| SN74ACT7881         | 1K           | 18           | 11               | ~                                   | ~               | ~                           |               | :                     |                        | <b>v</b> 1       |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7811         | 1K           | 18           | 15               | ~                                   | >               | ~                           |               |                       |                        | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7802         | 1K           | 18           | 30               | ~                                   | >               |                             |               |                       |                        | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7882         | 2K           | 18           | 11               | ~                                   | >               | ~                           |               |                       |                        | >                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT7884         | 4K           | 18           | 11               | ~                                   | ~               | ~                           |               |                       |                        | ~                |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT53861        | 4K           | 18           | 11               | ~                                   | >               | V                           |               |                       | -                      | ~                |                         |                                           |                |                 |              |                 |                                |               |              | ~                  | <b>v</b>        |

| SN74ACT3638         | 512          | 32           | 11               |                                     | ~               | ~                           | ~             |                       |                        | ~                |                         | ~                                         | ~              |                 |              |                 | ~                              |               |              |                    |                 |

| SN74ABT3611         | 64           | 36           | 10               |                                     | ~               | ~                           |               |                       |                        | ~                |                         |                                           | ~              | ~               | ~            |                 |                                |               |              |                    |                 |

| SN74ABT3613         | 64           | 36           | 10               |                                     | <b>v</b> -      | ~                           |               |                       |                        | ~                |                         | ~                                         | ~              | ~               | ~            |                 |                                | ~             | ~            |                    |                 |

| SN74ABT3612         | 64           | 36           | 10               |                                     | ~               |                             | ~             |                       |                        | ~                |                         | ~                                         | ~              | ~               | ~            |                 |                                |               |              |                    |                 |

| SN74ABT3614         | 64           | 36           | 10               |                                     | ~               |                             | 2             |                       |                        | ~                |                         | ~                                         | >              | ~               | <b>v</b> .   |                 |                                | ~             | ~            |                    |                 |

| SN74ACT3622         | 256          | 36           | 11               |                                     | >               | ~                           | 2             |                       |                        | ~                |                         | ~                                         | 1              |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT3631         | 512          | 36           | 11               |                                     | ~               | ~                           |               |                       |                        | ~                | ~                       | 1                                         | ~              |                 |              |                 | ~                              |               |              |                    |                 |

| SN74ACT3632         | 512          | 36           | 11               |                                     | ~               | ~                           | >             |                       |                        | ~                |                         | ~                                         | ~              |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT3641         | 1K           | 36           | 11               |                                     | >               | V                           |               |                       |                        | ~                | ~                       | ~                                         | ~              |                 |              |                 | ~                              |               |              |                    |                 |

| SN74ACT3642         | 1K           | 36           | 11               |                                     | ~               | ~                           | ~             |                       |                        | ~                |                         | ~                                         | ~              |                 |              |                 |                                |               |              |                    |                 |

| SN74ACT3651         | 2K           | 36           | 11               |                                     | ~               | ~                           |               |                       |                        | ~                | ~                       | ~                                         | ~              |                 |              |                 | ~                              |               |              |                    |                 |

| * Didirectional con | C            |              | بندناء امراه     |                                     | -               |                             |               |                       |                        |                  |                         |                                           |                |                 |              |                 |                                |               |              |                    |                 |

\* Bidirectional configurable without additional logic

<del>Т</del>,

TEXAS INSTRUMENTS POST OFFICE BOX 685939\* DALIAS, TEXAS 78285

#### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

#### operating conditions and characteristics (in sequence by letter symbols)

C<sub>i</sub> Input capacitance

The internal capacitance at an input of the device

#### Co Output capacitance

The internal capacitance at an output of the device

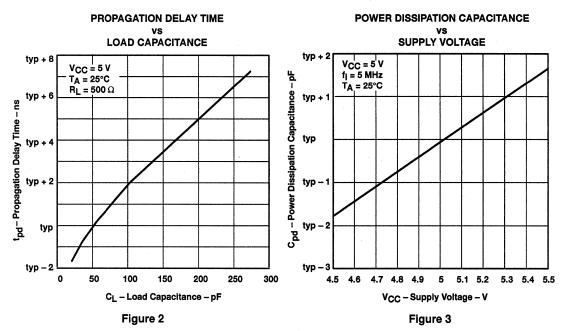

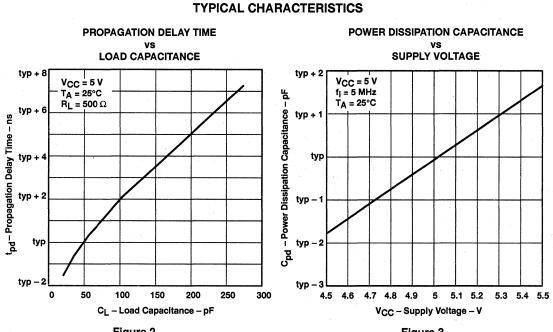

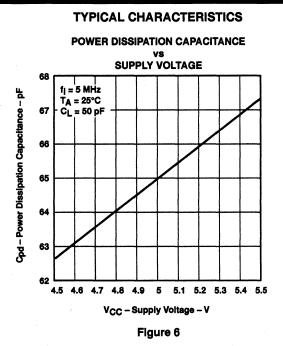

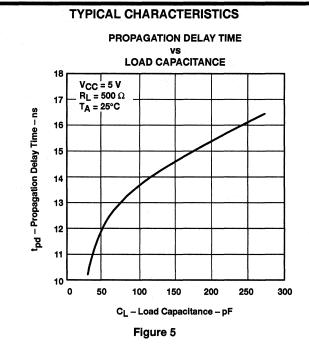

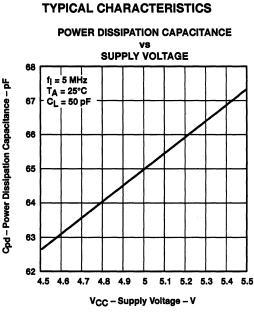

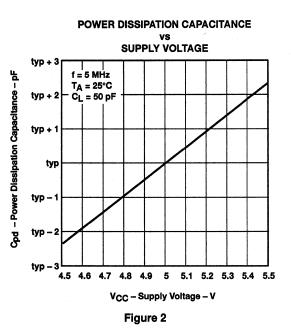

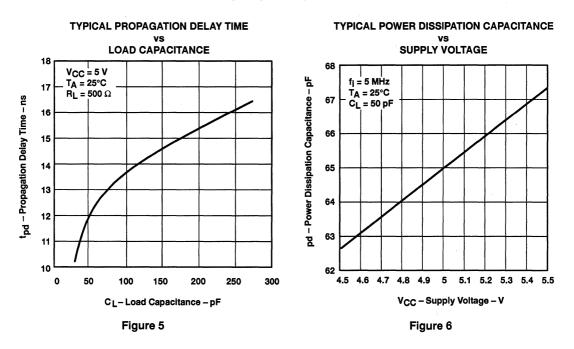

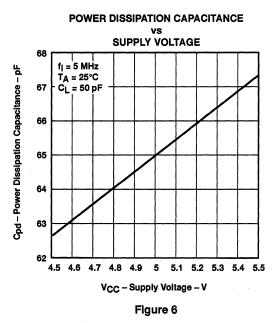

#### C<sub>pd</sub> Power dissipation capacitance

Used to determine the no-load dynamic power dissipation per logic function (see individual circuit pages):  $P_D = C_{pd} V_{CC}^2 f + I_{CC} V_{CC}$

#### fmax Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification

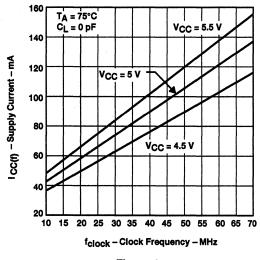

#### I<sub>CC</sub> Supply current

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit

#### △I<sub>CC</sub> Supply current change

The increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V or  $V_{CC}$

#### ICEX Output high leakage current

The maximum leakage current into the collector of the pulldown output transistor when the output is high and the output forcing condition  $V_0 = 5.5 \text{ V}$

#### II(hold) Input hold current

Input current that holds the input at the previous state when the driving device goes to a high-impedance state

#### I<sub>IH</sub> High-level input current

The current into\* an input when a high-level voltage is applied to that input

#### IIL Low-level input current

The current into\* an input when a low-level voltage is applied to that input

#### Input/output power-off leakage current

The maximum leakage current into/out of the input/output transistors when forcing the input/output to 4.5 V and V\_{CC} = 0 V

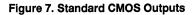

#### IOH High-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a high level at the output.

#### IOL Low-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a low level at the output. \*Current out of a terminal is given as a negative value.

# GLOSSARY SYMBOLS, TERMS, AND DEFINITIONS

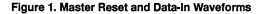

#### I<sub>OZ</sub> Off-state (high-impedance-state) output current (of a 3-state output)

The current flowing into\* an output having 3-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output

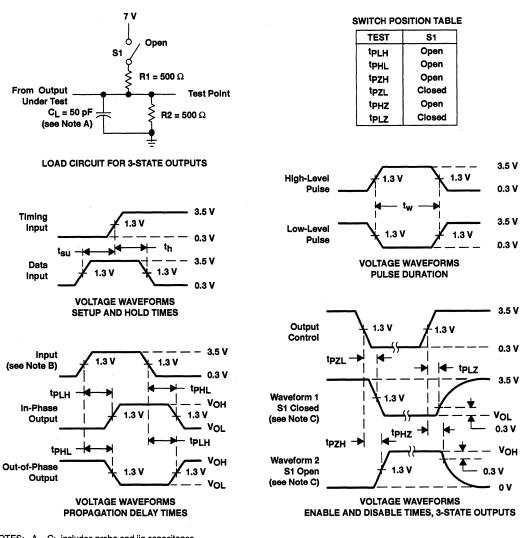

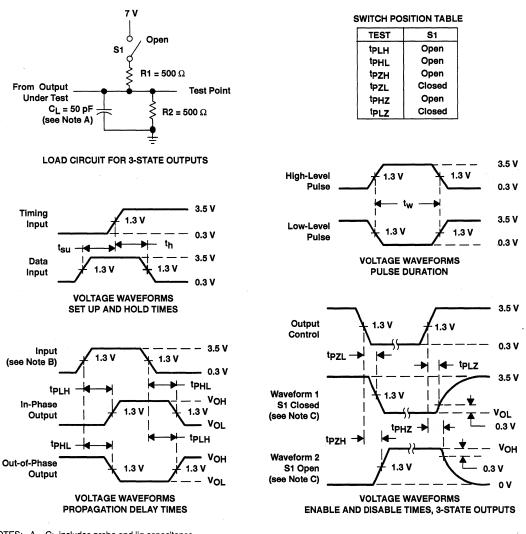

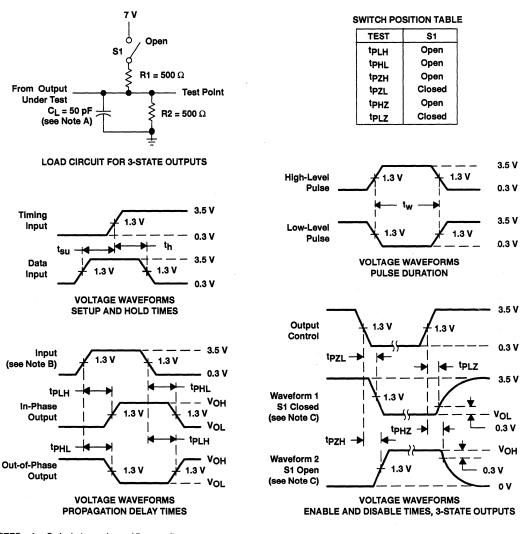

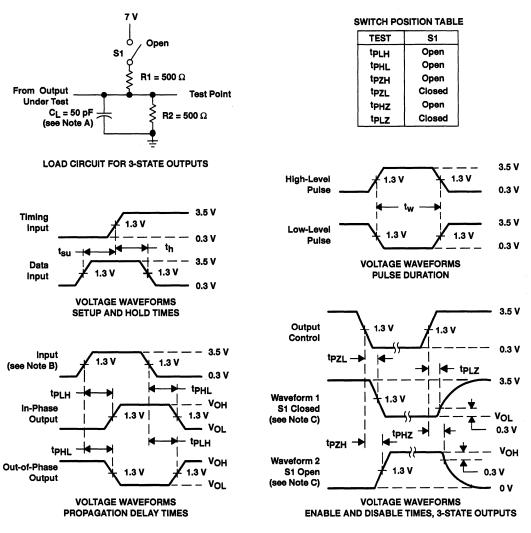

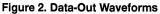

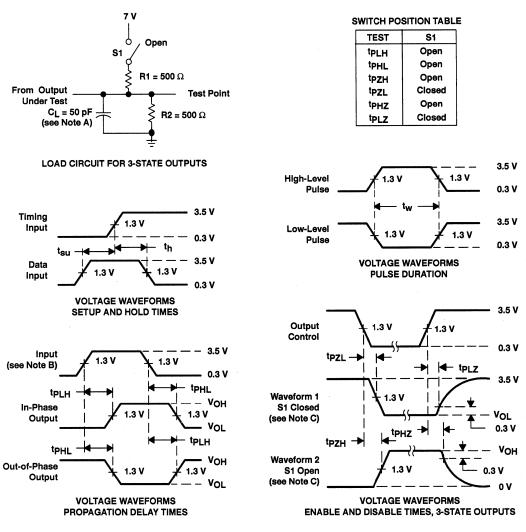

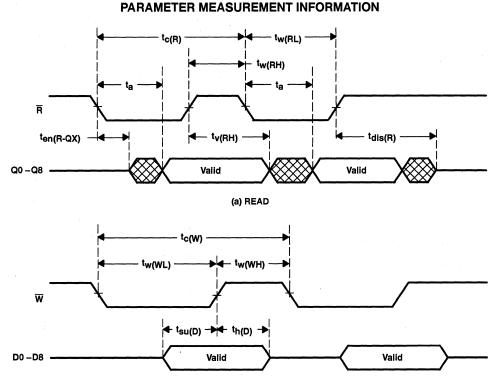

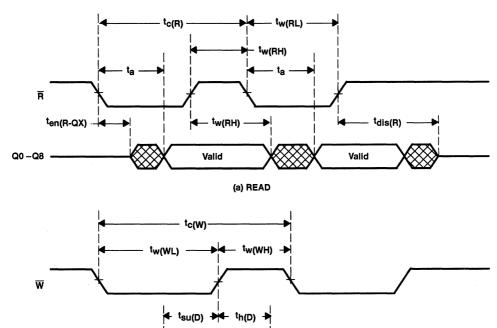

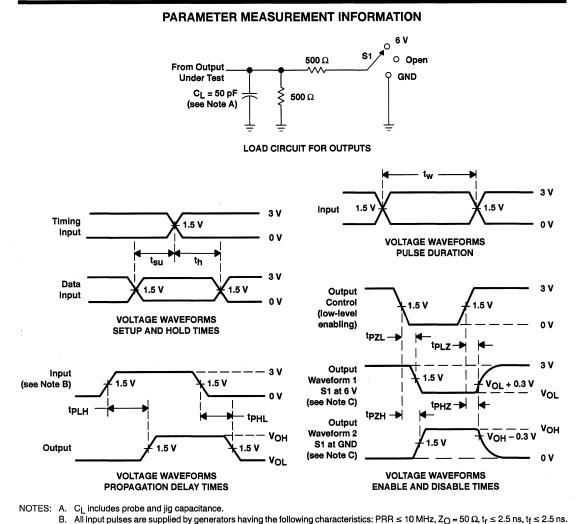

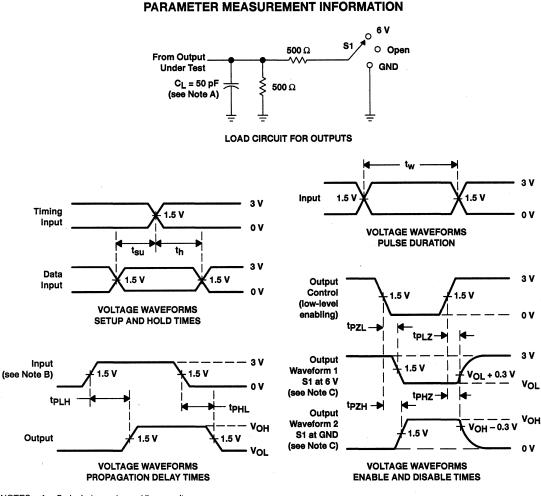

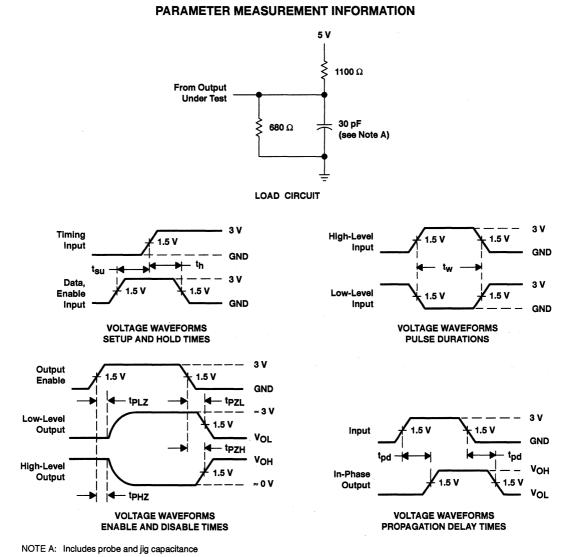

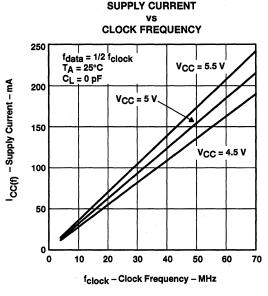

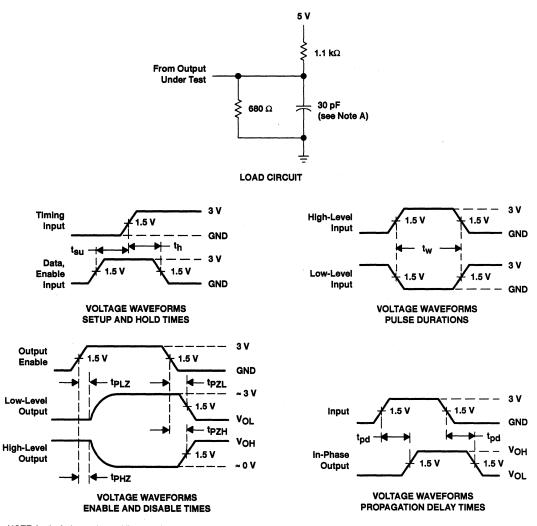

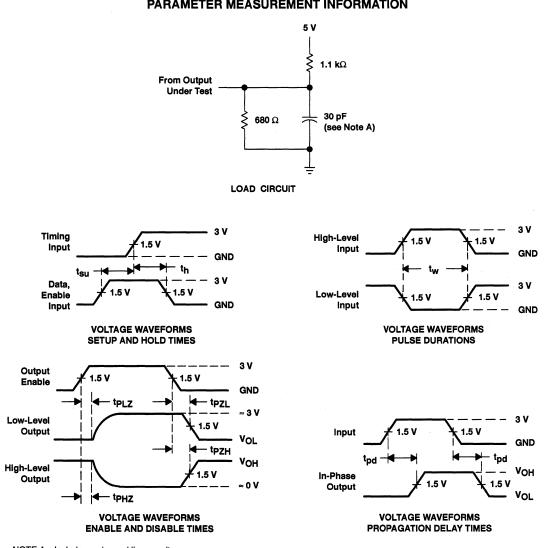

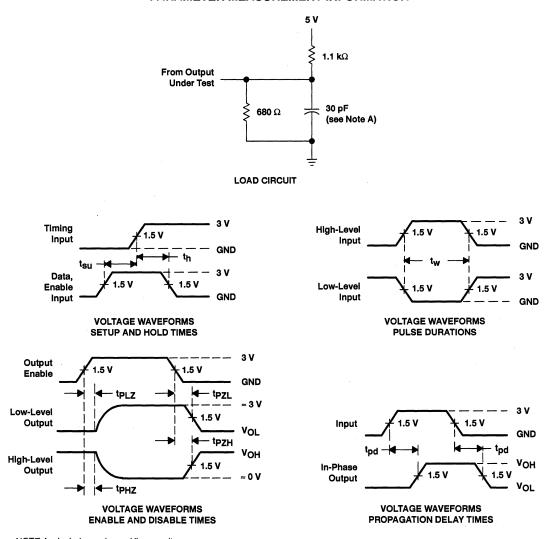

#### ta Access time

The time interval between the application of a specified input pulse and the availability of valid signals at an output

#### t<sub>c</sub> Clock cycle time

Clock cycle time is 1/fmax.

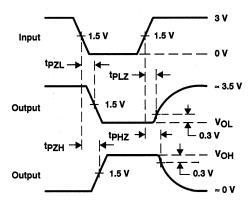

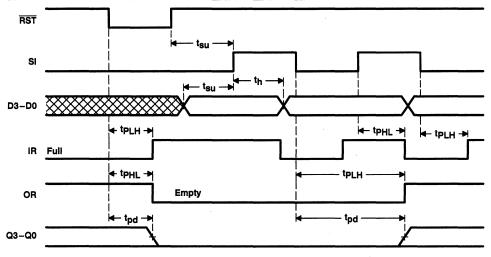

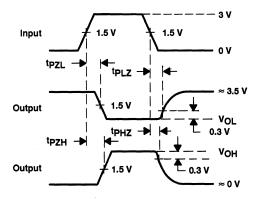

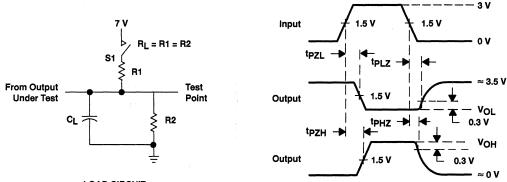

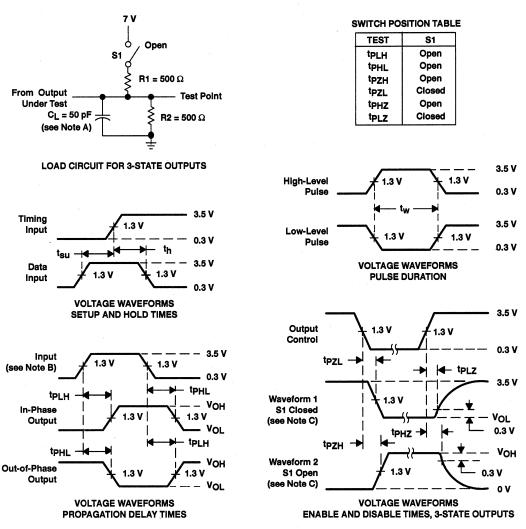

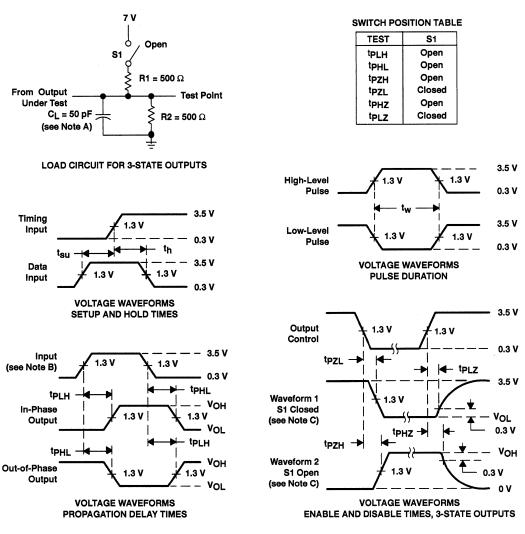

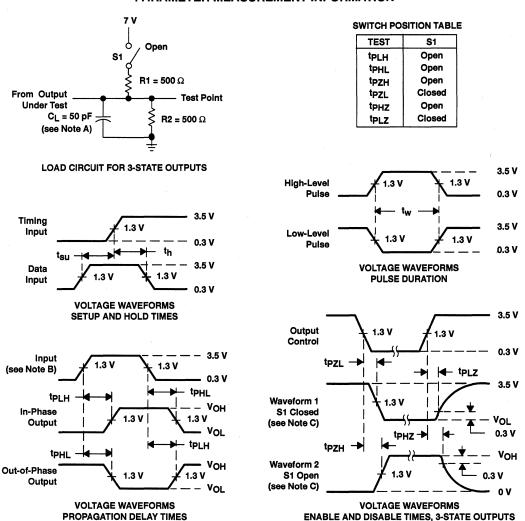

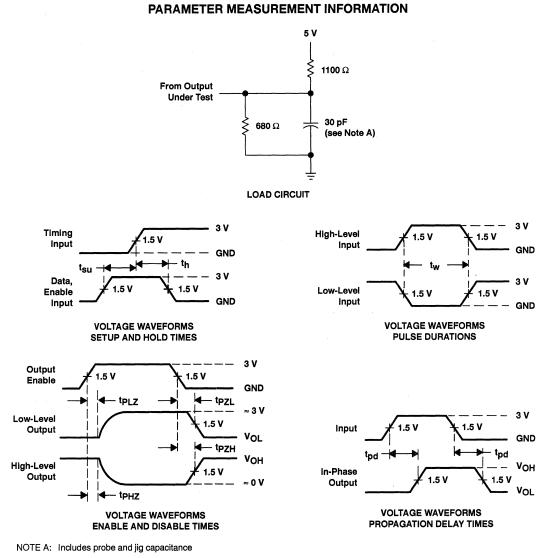

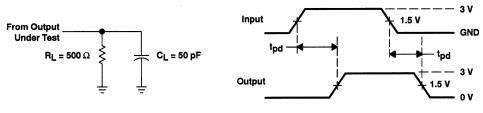

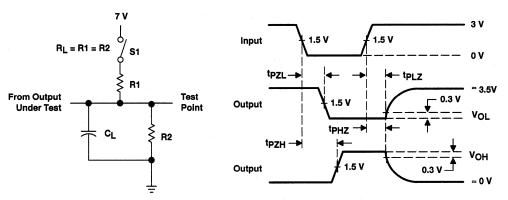

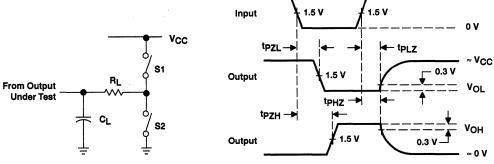

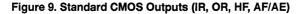

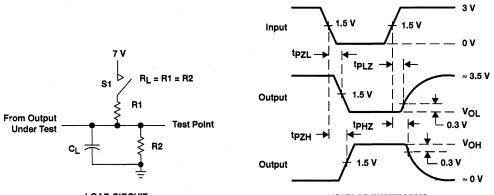

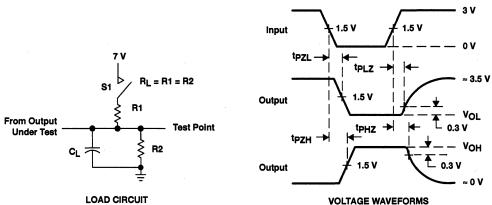

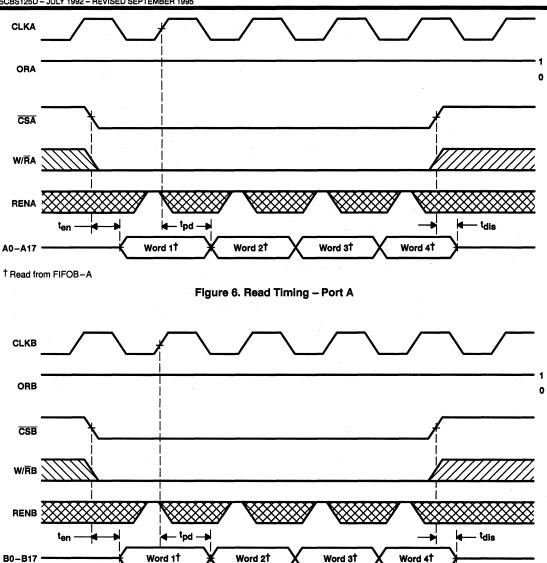

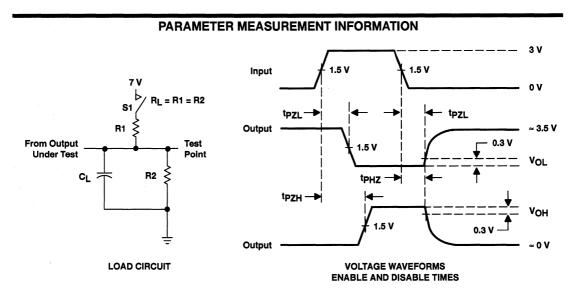

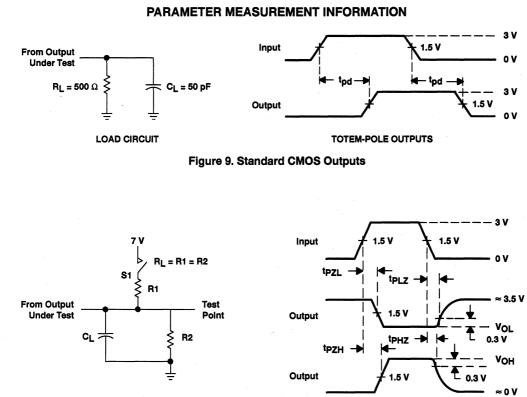

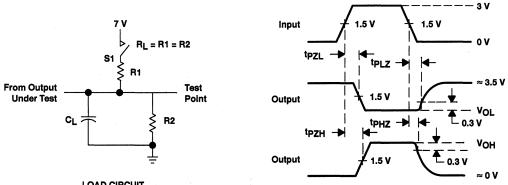

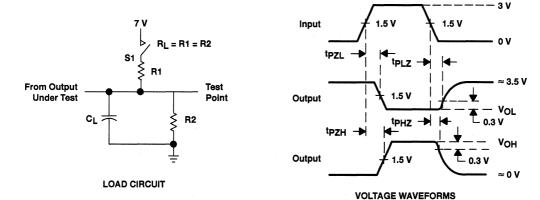

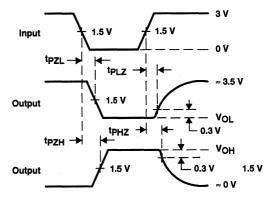

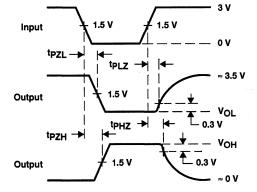

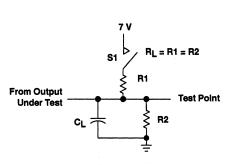

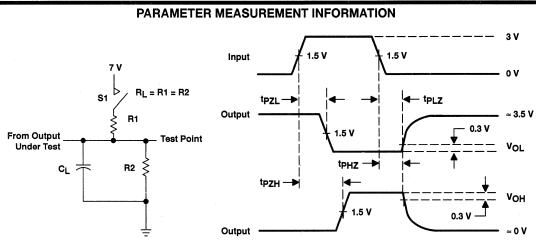

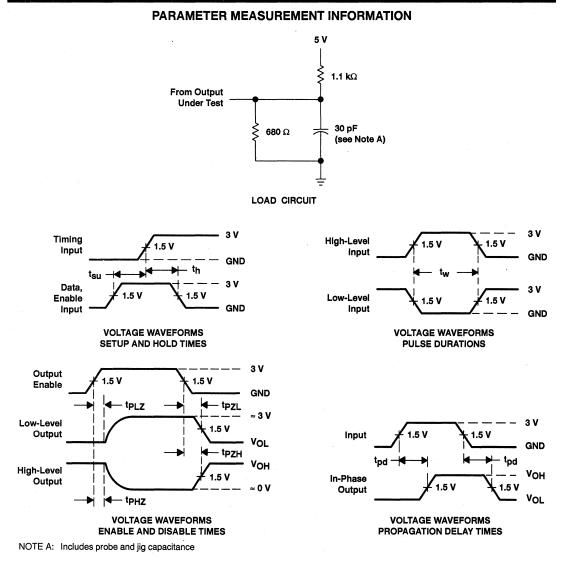

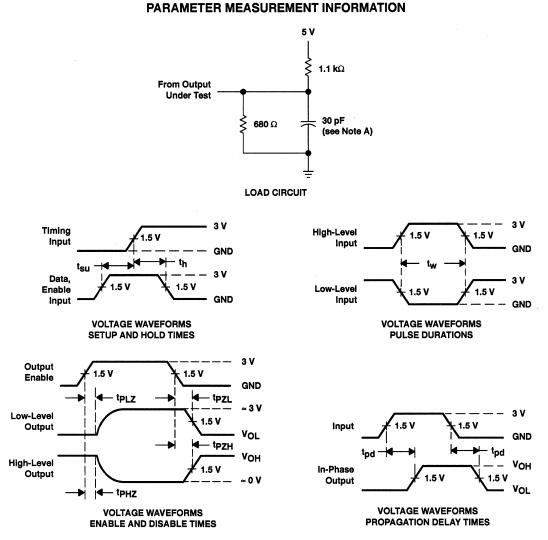

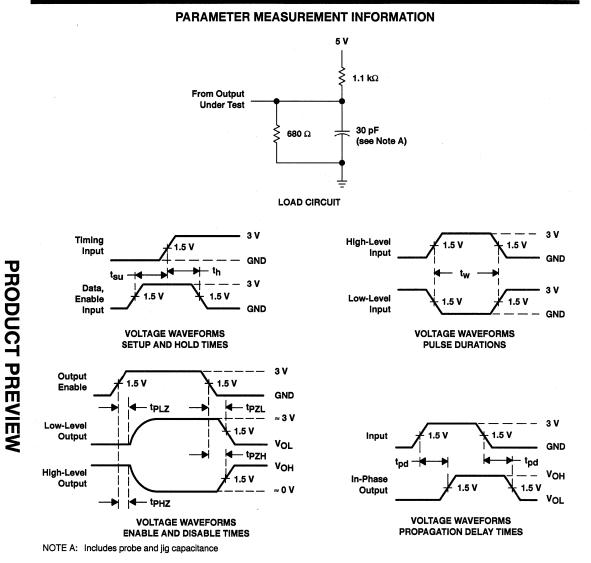

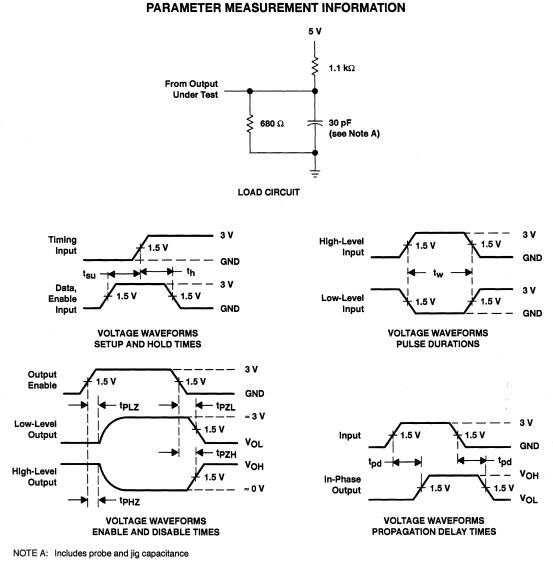

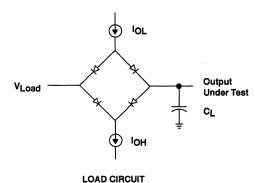

#### t<sub>dis</sub> Disable time (of a 3-state or open-collector output)

The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from either of the defined active levels (high or low) to a high-impedance (off) state

NOTE: For 3-state outputs,  $t_{dis} = t_{PHZ}$  or  $t_{PLZ}$ . Open-collector outputs will change only if they are low at the time of disabling, so  $t_{dis} = t_{PLH}$ .

#### ten Enable time (of a 3-state or open-collector output)

The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from a high-impedance (off) state to either of the defined active levels (high or low)

NOTE: In the case of memories, this is the access time from an enable input (e.g.,  $\overline{OE}$ ). For 3-state outputs, t<sub>en</sub> = t<sub>PZH</sub> or t<sub>PZL</sub>. Open-collector outputs will change only if they are responding to data that would cause the output to go low, so t<sub>en</sub> = t<sub>PHL</sub>.

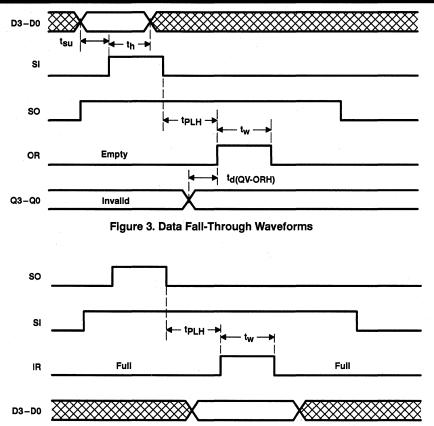

#### Hold time

th

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal

NOTES: 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is to be expected.

2. The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is to be expected.

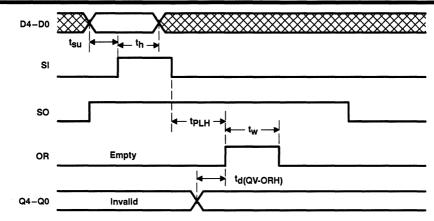

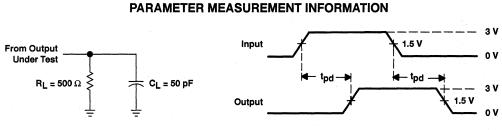

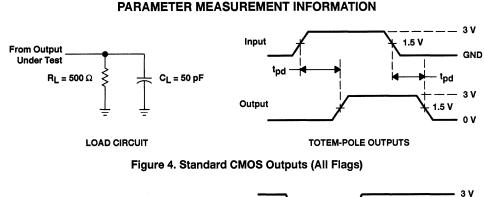

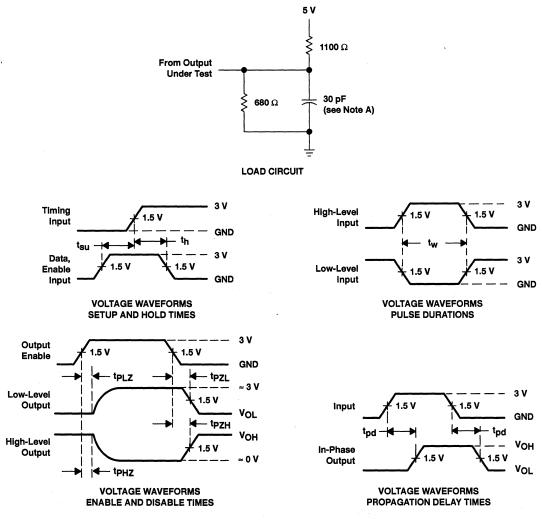

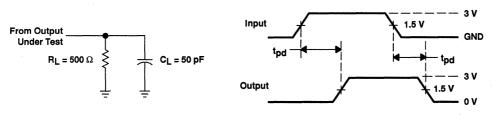

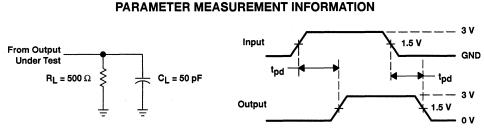

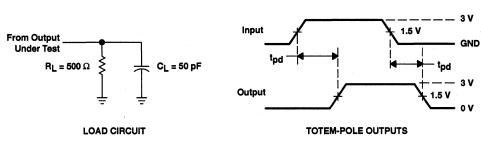

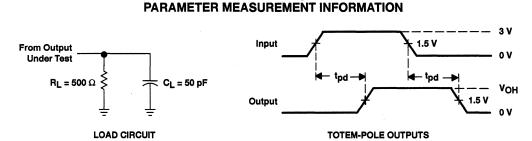

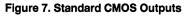

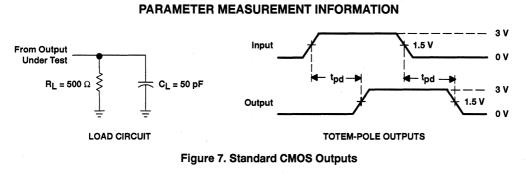

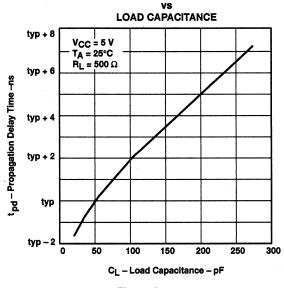

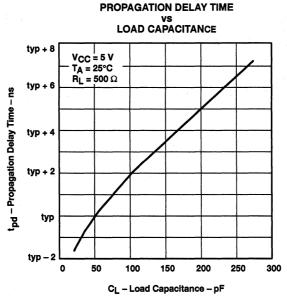

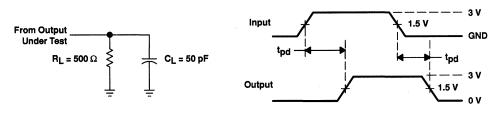

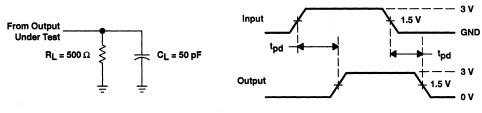

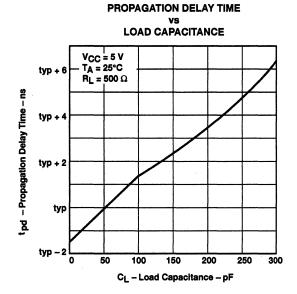

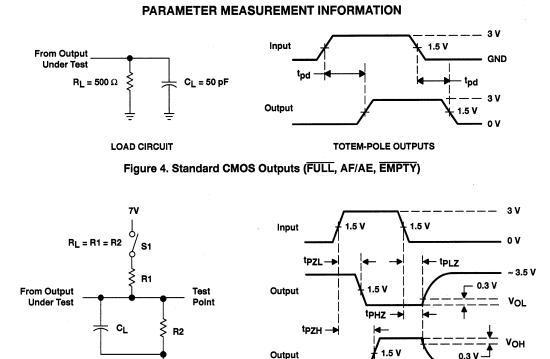

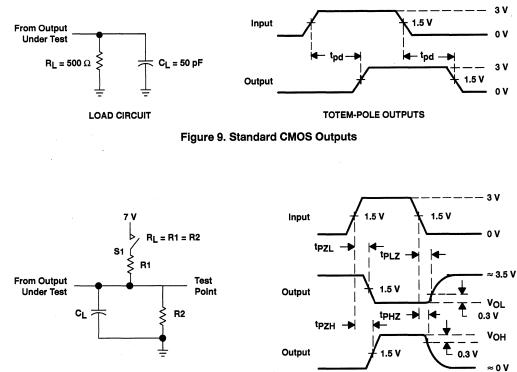

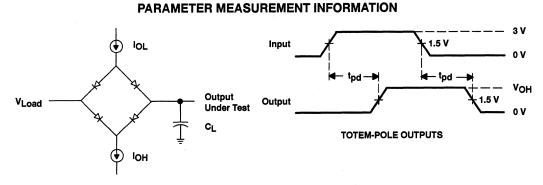

#### tpd Propagation delay time

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level ( $t_{pd}$  =  $t_{PHL}$  or  $t_{PLH}$ )

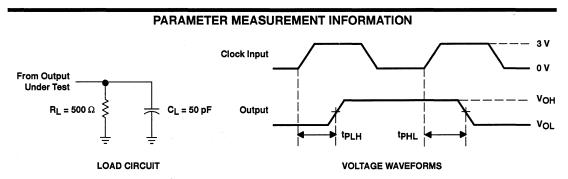

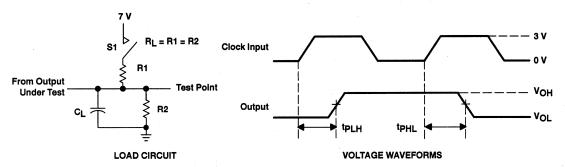

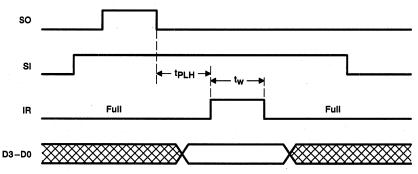

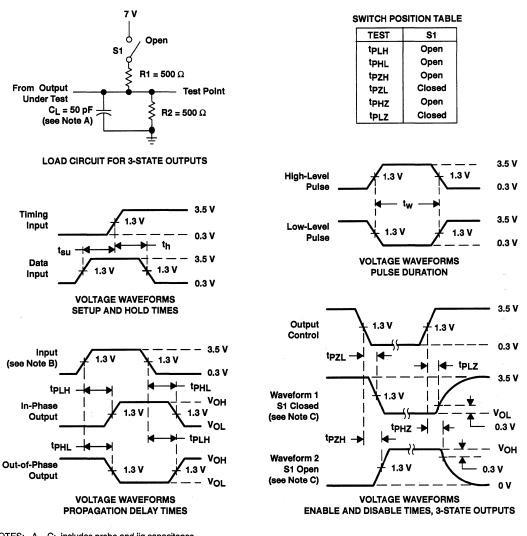

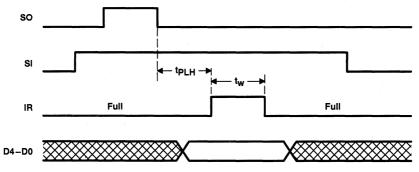

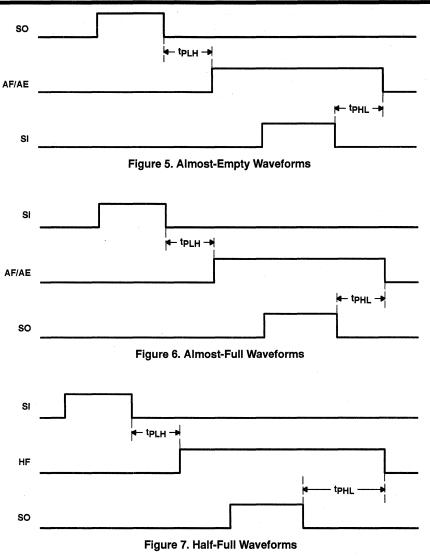

#### t<sub>PHL</sub> Propagation delay time, high-to-low level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level

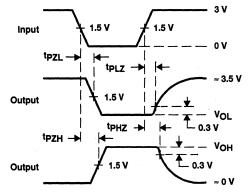

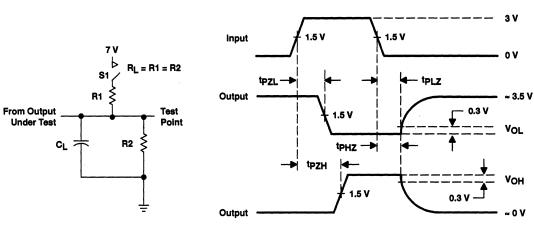

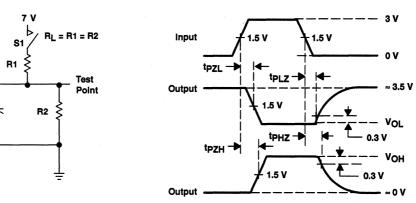

#### t<sub>PHZ</sub> Disable time (of a 3-state output) from high level

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined high level to the high-impedance (off) state

#### t<sub>PLH</sub> Propagation delay time, low-to-high level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level

\*Current out of a terminal is given as a negative value.

1-8

#### tpLZ Disable time (of a 3-state output) from low level

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined low level to the high-impedance (off) state

#### t<sub>PZH</sub> Enable time (of a 3-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from the high-impedance (off) state to the defined high level

#### tpzL Enable time (of a 3-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from the high-impedance (off) state to the defined low level

#### t<sub>su</sub> Setup time

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal

NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is to be expected.

2. The setup time may have a negative value, in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is to be expected.

#### tw Pulse duration (width)

The time interval between specified reference points on the leading and trailing edges of the pulse waveform

## VIH High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is to be expected.

#### VIL Low-level input voltage

An input voltage within the less positive (more negative) of the two ranges of values used to represent the binary variables

NOTE: A maximum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is to be expected.

### V<sub>OH</sub> High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a high level at the output

#### VOL Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a low level at the output

#### VIT+ Positive-going input threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage rises from a level below the negative-going threshold voltage,  $V_{IT-}$

#### VIT- Negative-going input threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage falls from a level above the positive-going threshold voltage,  $V_{IT+}$

# GLOSSARY SYMBOLS, TERMS, AND DEFINITIONS

#### definitions

#### asynchronous FIFO

Data writes are initiated by a low-level pulse on the write-enable input when the full flag is not asserted. Likewise, data reads are initiated by a low-level pulse on the read-enable input when the empty flag is not asserted. The empty and full flags are not synchronized to a particular clock and reflect the instantaneous comparison of the read and write pointers.

#### clocked FIFO

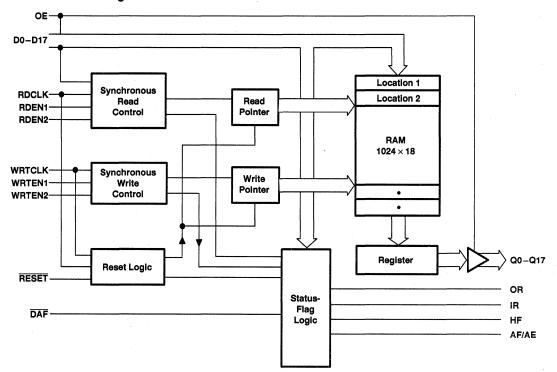

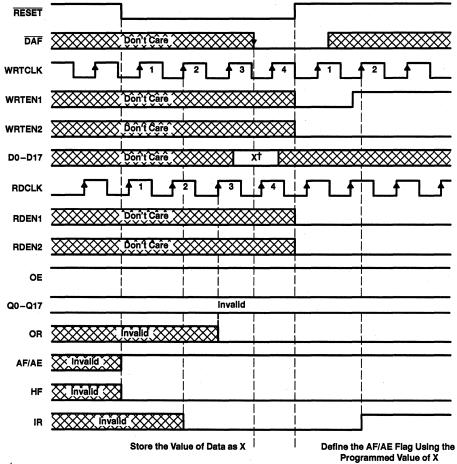

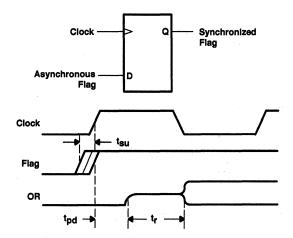

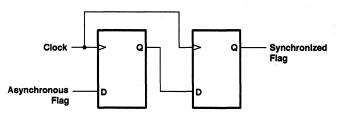

Data is written by a low-to-high transition of a write clock when write-enable inputs are asserted and the input-ready flag is not asserted. Likewise, data is read by a low-to-high transition of a read clock when read-enable inputs are asserted and the output-ready flag is asserted. The input-ready flag is multistaged synchronized to the write clock and the ouput-ready flag is multistaged synchronized to the read clock, improving metastability.

#### strobed FIFO

Data is written on a low-to-high transition on the load-clock input when the full flag is not asserted. Likewise, data is read on a low-to-high transition on the unload-clock input when the empty-flag is not asserted. The empty and full flags are not synchronized to a particular clock and reflect the instantaneous comparison of the read and write pointers.

#### synchronous FIFO

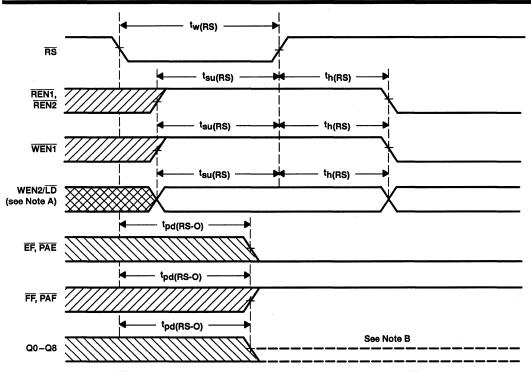

The term synchronous refers to a port-control method and does not imply that data writes and reads must be synchronous to one another. Data is written by a low-to-high transition of a write clock when write-enable inputs are asserted and the full flag is not asserted. Likewise, data is read by a low-to-high transition of a read clock when read-enable inputs are asserted and the empty flag is not asserted. The empty flag is single-staged synchronized to the read clock, and the full flag is single-staged synchronized to the write clock.

# **EXPLANATION OF FUNCTION TABLES**

The following symbols are used in function tables on TI data sheets:

- H = high level (steady state)

- L = low level (steady state)

- ↑ = transition from low to high level

- $\downarrow$  = transition from high to low level

- ---- = value/level or resulting value/level is routed to indicated destination

- = value/level is re-entered

- X = irrelevant (any input, including transitions)

- Z = off (high-impedance) state of a 3-state output

- a...h = the level of steady-state inputs A through H respectively

- Q<sub>0</sub> = level of Q before the indicated steady-state input conditions were established

- $\overline{Q}_0$  = complement of  $Q_0$  or level of  $\overline{Q}$  before the indicated steady-state input conditions were established

- $Q_n$  = level of Q before the most recent active transition indicated by  $\downarrow$  or  $\uparrow$

- \_\_\_\_ = one high-level pulse

- -\_\_\_ = one low-level pulse

- Toggle

- e = each output changes to the complement of its previous level on each active transition indicated by ↓ or ↑

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

If, in the input columns, a row contains H, L, and/or X together with  $\uparrow$  and/or  $\downarrow$ , this means the output is valid whenever the input configuration is achieved but the transition(s) must occur following the achievement of the steady-state levels. If the output is shown as a level (H, L, Q<sub>0</sub>, or  $\overline{Q}_0$ ), it persists so long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. (If the output is shown as a pulse,  $\_\_\_$  or  $\_\_\_$ , the pulse follows the indicated input transition and persists for an interval dependent on the circuit.)

Among the most complex function tables are those of the shift registers. These embody most of the symbols used in any of the function tables, plus more. Below is the function table of a 4-bit bidirectional universal shift register, e.g., type SN74194.

|        |      |         |          |      |       | INDE | -    |   |    |                 |                 |                 |                 |

|--------|------|---------|----------|------|-------|------|------|---|----|-----------------|-----------------|-----------------|-----------------|

|        | -    | OUTPUTS |          |      |       |      |      |   |    |                 |                 |                 |                 |

| 01 545 | MODE |         | SEI      | RIAL |       | PARA | LLEL |   | 0. | 0-              | 0.              | 0-              |                 |

| CLEAR  | S1   | S0      | CLOCK    | LEFT | RIGHT | Α    | В    | C | D  | QA              | QB              | QC              | QD              |

| L      | Х    | Х       | Х        | х    | х     | Х    | х    | х | х  | L               | L               | L               | L               |

| н      | х    | х       | L        | x    | х     | х    | х    | х | х  | Q <sub>A0</sub> | Q <sub>B0</sub> | Q <sub>C0</sub> | Q <sub>D0</sub> |

| н      | н    | н       | <b>↑</b> | x    | x     | а    | b    | с | d  | a               | b               | с               | d               |

| н      | L    | н       | <b>↑</b> | x    | н     | н    | н    | н | н  | н               | Q <sub>An</sub> | QBn             | QCn             |

| н      | L    | н       | Î        | x    | L     | L    | L    | L | L  | L               | Q <sub>An</sub> | QBn             | QCn             |

| н      | н    | L       | <b>↑</b> | н    | x     | х    | х    | х | х  | QBn             | QCn             | QDn             | н               |

| н      | н    | L       | <b>↑</b> | L    | х     | х    | х    | х | х  | QBn             | QCn             | QDn             | L               |

| н      | L    | L       | ×        | x    | х     | х    | х    | х | х  | Q <sub>A0</sub> | Q <sub>B0</sub> | Q <sub>C0</sub> | Q <sub>D0</sub> |

FUNCTION TABLE

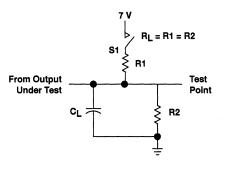

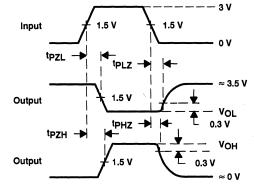

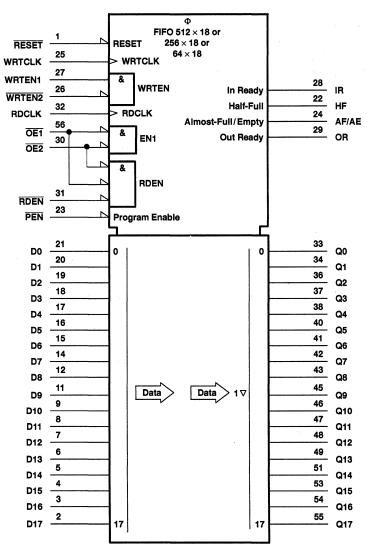

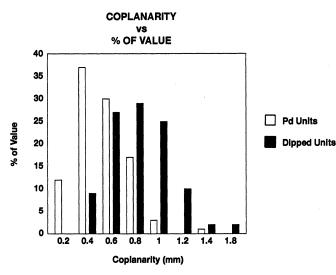

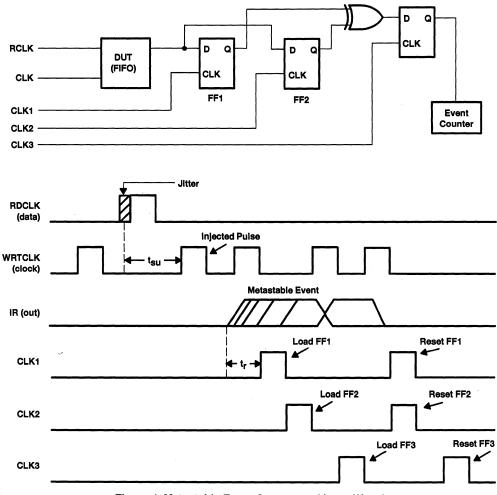

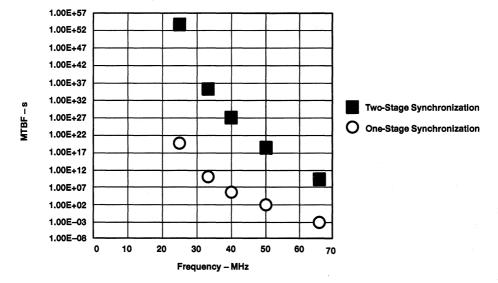

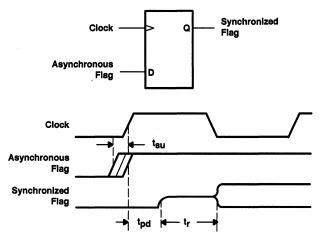

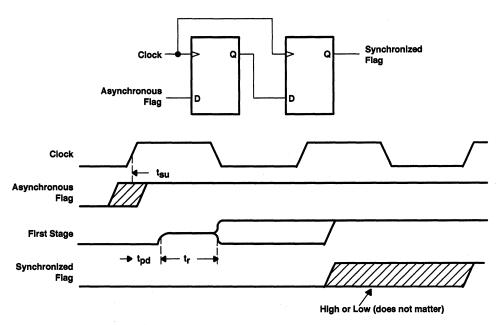

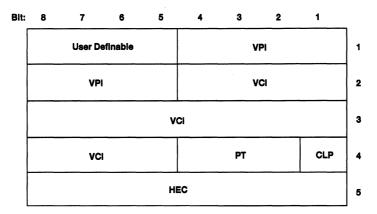

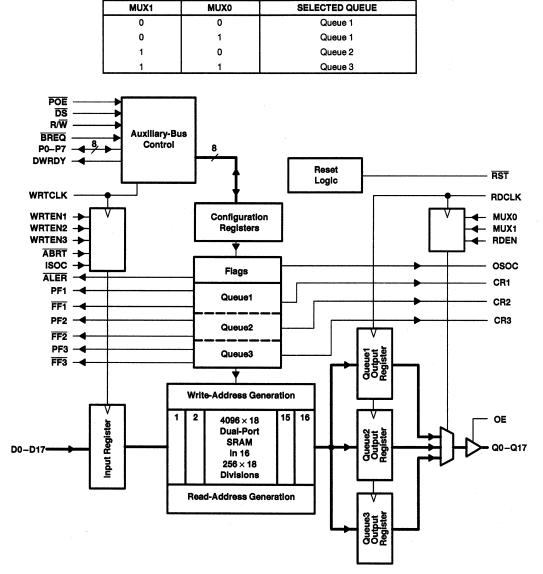

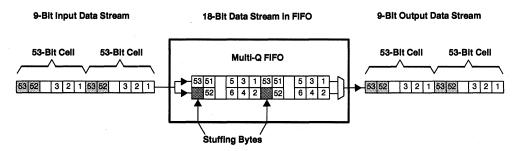

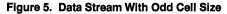

The first line of the table represents a synchronous clearing of the register and says that if clear is low, all four outputs will be reset low regardless of the other inputs. In the following lines, clear is inactive (high) and so has no effect.