# **PCIbus Solutions** Integrated Solutions for the PCIbus

Advanced System Logic Products

| General Information | · · · · · · · · · · · · · · · · · · · | 1 |

|---------------------|---------------------------------------|---|

| PCI1050             |                                       | 2 |

| PCI10XX             |                                       | 3 |

| PCI1130             | · · · ·                               | 4 |

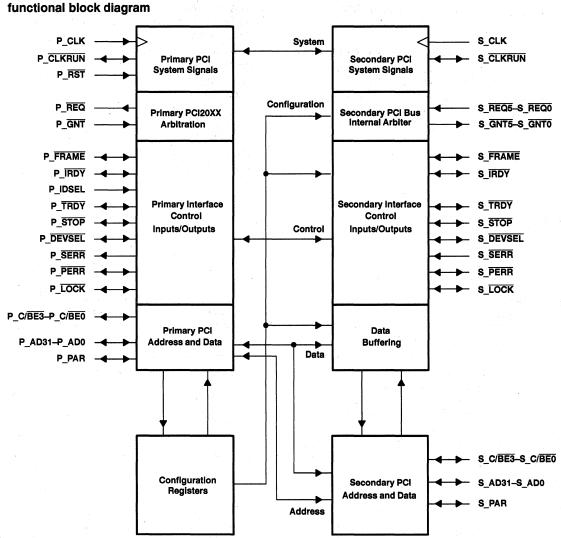

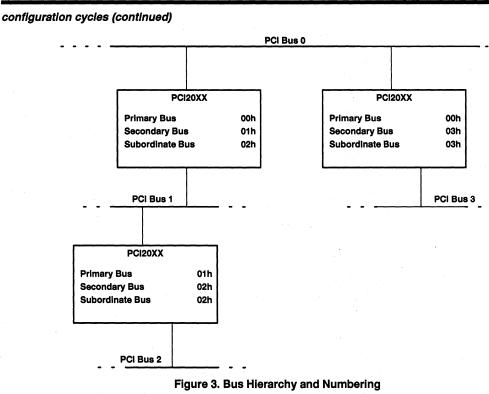

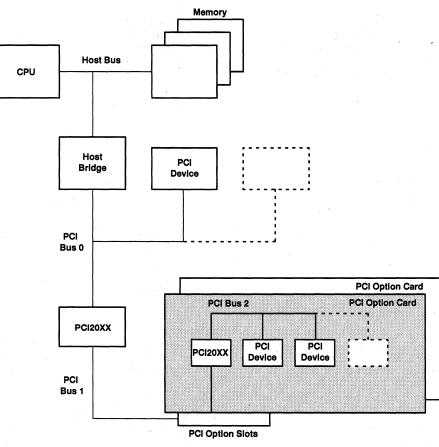

| PCI20XX             |                                       | 5 |

| Mechanical Data     |                                       | 6 |

•

# **PCIbus Solutions**

Integrated Solutions for the PClbus

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated

Printed in U.S.A. by Custom Printing Company Owensville, Missouri

### INTRODUCTION

The PCIbus solutions group develops connectivity and integration solutions for notebooks, desktops, and end equipment in emerging markets that require both design flexibility and superior performance.

A major highlight in this data book is the inclusion of the industry's first CardBus controller, the PCI1130. We also have included a product preview of the PCI10XX, an alternative solution that enables easy migration to CardBus, and a product preview of our first PCI-to-PCI bridge chip, the PCI20XX. Our book also features TI's first PCI-to-PCMCIA controller, the PCI1050, which employs earlier PC Card technologies. All four devices are based on a commonality of features requested by our customers.

Texas Instruments (TI) is active in many of the standards committees that are working to meet the computer industry's requirements for a total integrated solution. All of our PCIbus devices address the needs of existing and emerging technologies. Future products will continue to address dynamic requirements for design flexibility, power-management options, and integration of other available technologies.

More than ever, TI technologies are changing the way people throughout the world live, learn, and work. We believe you will find our first edition of the PCIbus data book resourceful and forward-looking. If you have any questions after reviewing this data book, please contact your local TI representative or call the Advanced System Logic hotline at (903) 868-5202.

ExCA and PC Card are trademarks of Personal Computer Memory Card International Association (PCMCIA). Intel and MPIIX are trademarks of Intel Corp. Lotus is a registered trademark of Lotus Development Corporation. Microsoft is a registered trademark of Microsoft Corporation.

### PRODUCT STAGE STATEMENTS

*Product stage statements* are used on Texas Instruments data sheets to indicate the development stage(s) of the product(s) specified in the data sheets.

If all products specified in a data sheet are at the same development stage, the appropriate statement from the following list is placed in the lower left corner of the first page of the data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

If not all products specified in a data sheet are at the PRODUCTION DATA stage, then the first statement below is placed in the lower left corner of the first page of the data sheet. Subsequent pages of the data sheet containing PRODUCT PREVIEW information or ADVANCE INFORMATION are then marked in the lower left-hand corner with the appropriate statement given below:

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

vi

| General Information | 1 |

|---------------------|---|

| PCI1050             | 2 |

| PCI10XX             | 3 |

| PCI1130             | 4 |

| PCI20XX             | 5 |

| Mechanical Data     | 6 |

# Contents

|                                | Page |

|--------------------------------|------|

| Glossary                       |      |

| Explanation of Function Tables |      |

| Related Publications           | 1–8  |

| Functional Index               | 1–9  |

### GLOSSARY SYMBOLS, TERMS, AND DEFINITIONS

### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

### operating conditions and characteristics (in sequence by letter symbols)

| C <sub>i</sub>   | Input capacitance                                                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | The internal capacitance at an input of the device                                                                                                                                                                    |

| Cio              | Input/output capacitance                                                                                                                                                                                              |

|                  | Input-to-output internal capacitance; transcapacitance                                                                                                                                                                |

| Co               | Output capacitance                                                                                                                                                                                                    |

|                  | The internal capacitance at an output of the device                                                                                                                                                                   |

| C <sub>pd</sub>  | Power dissipation capacitance                                                                                                                                                                                         |

|                  | Used to determine the no-load dynamic power dissipation per logic function (see individual circuit pages):<br>$P_D = C_{pd} V_{CC}^2 f + I_{CC} V_{CC}$                                                               |

| ∆lcc             | Supply current change                                                                                                                                                                                                 |

|                  | The increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V or $V_{CC}$                                                                                          |

| Ιн               | High-level input current                                                                                                                                                                                              |

|                  | The current into* an input when a high-level voltage is applied to that input                                                                                                                                         |

| l <sub>IL</sub>  | Low-level input current                                                                                                                                                                                               |

|                  | The current into* an input when a low-level voltage is applied to that input                                                                                                                                          |

| ЮН               | High-level output current                                                                                                                                                                                             |

|                  | The current into* an output with input conditions applied that, according to the product specification, establishes a high level at the output                                                                        |

| IOL              | Low-level output current                                                                                                                                                                                              |

|                  | The current into* an output with input conditions applied that, according to the product specification, establishes a low level at the output                                                                         |

| ta               | Access time                                                                                                                                                                                                           |

|                  | The time interval between the application of a specified input pulse and the availability of valid signals at an output                                                                                               |

| t <sub>c</sub>   | Clock cycle time                                                                                                                                                                                                      |

| · ·              | Clock cycle time is 1/f <sub>max</sub> .                                                                                                                                                                              |

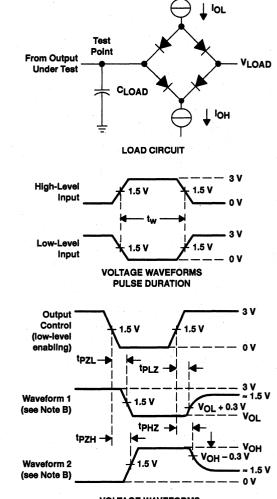

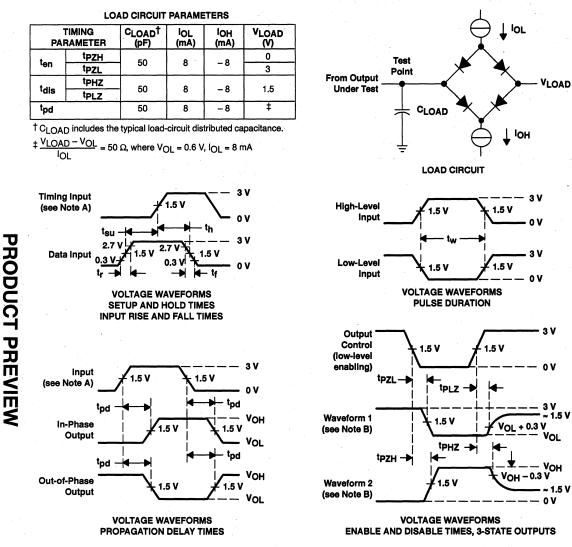

| <sup>t</sup> dis | Disable time (of a 3-state or open-collector output)                                                                                                                                                                  |

|                  | The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from either of the defined active levels (high or low) to a high-impedance (off) state |

|                  | NOTE: For 3-state outputs, $t_{dis} = t_{PHZ}$ or $t_{PLZ}$ . Open-collector outputs change only if they are low at the time of disabling, so $t_{dis} = t_{PLH}$ .                                                   |

\*Current out of a terminal is given as a negative value.

# GLOSSARY SYMBOLS, TERMS, AND DEFINITIONS

| t <sub>en</sub>    | Enable time (of a 3-s                            | state or open-collector out                                                                                                      | out)                                                                                                           |                                                                     |                                            |

|--------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------|

|                    |                                                  | between the specified referer<br>ing from a high-impedance (c                                                                    |                                                                                                                |                                                                     |                                            |

|                    | NOTE: For 3-state<br>responding                  | outputs, $t_{en} = t_{PZH}$ or $t_{PZ}$<br>to data that would cause the                                                          | L. Open-collector of output to go low, set                                                                     | outputs change on<br>o t <sub>en</sub> = t <sub>PHL</sub> .         | lly if they are                            |

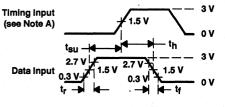

| th                 | Hold time                                        |                                                                                                                                  |                                                                                                                |                                                                     |                                            |

|                    | The time interval durin<br>occurs at another spe | ng which a signal is retained a cified input terminal                                                                            | at a specified input                                                                                           | terminal after an ac                                                | ctive transition                           |

|                    | system in w                                      | time is the actual time interval<br>hich the digital circuit operate<br>which correct operation of the                           | es. A minimum valu                                                                                             | ue is specified that i                                              |                                            |

|                    | interval (bet                                    | time may have a negative valu<br>ween the release of the signa<br>Il circuit is to be expected.                                  |                                                                                                                |                                                                     |                                            |

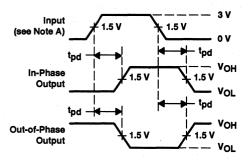

| t <sub>pd</sub>    | Propagation delay t                              | ime                                                                                                                              |                                                                                                                |                                                                     |                                            |

|                    | The time between the output changing from        | e specified reference points of one defined level (high or lo                                                                    | on the input and ou<br>w) to the other defi                                                                    | utput voltage wavel<br>ned level (t <sub>pd</sub> = t <sub>PH</sub> | iorms with the<br>IL or t <sub>PLH</sub> ) |

| t <sub>PHL</sub>   | Propagation delay t                              | ime, high-to-low level outp                                                                                                      | ut data da ser da                                                                                              |                                                                     |                                            |

|                    |                                                  | e specified reference points on the defined high level to the                                                                    |                                                                                                                | utput voltage wavel                                                 | forms with the                             |

| <sup>t</sup> PHZ   | Disable time (of a 3-                            | -state output) from high lev                                                                                                     | el                                                                                                             |                                                                     |                                            |

|                    |                                                  | veen the specified reference put changing from the defined                                                                       |                                                                                                                |                                                                     |                                            |

| t <sub>PLH</sub>   | Propagation delay t                              | ime, low-to-high level outp                                                                                                      | ut                                                                                                             |                                                                     |                                            |

|                    |                                                  | e specified reference points<br>the defined low level to the                                                                     |                                                                                                                | utput voltage wave                                                  | forms with the                             |

| tPLZ               | Disable time (of a 3-                            | -state output) from low leve                                                                                                     | el de la companya de |                                                                     |                                            |

|                    |                                                  | veen the specified reference put changing from the defined                                                                       |                                                                                                                |                                                                     |                                            |

| <sup>t</sup> PZH   | Enable time (of a 3-                             | state output) to high level                                                                                                      | •                                                                                                              |                                                                     |                                            |

|                    |                                                  | veen the specified reference p<br>anging from the high-impeda                                                                    |                                                                                                                |                                                                     |                                            |

| tPZL               | Enable time (of a 3-                             | state output) to low level                                                                                                       | •                                                                                                              |                                                                     |                                            |

|                    |                                                  | veen the specified reference p<br>anging from the high-impeda                                                                    |                                                                                                                |                                                                     | vaveforms with                             |

| <sup>t</sup> sk(o) | Output skew                                      |                                                                                                                                  |                                                                                                                |                                                                     |                                            |

|                    | switching simultaneous parameter is used to      | en any two propagation delay<br>usly cause multiple outputs to<br>describe the fanout capabil<br>uffering and distribution netwo | switch, as observe<br>ity of a clock drive                                                                     | d across all switchin                                               | ng output. This                            |

| t <sub>su</sub> | Setup time                                                                                                                                                                                                                                                                             |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal                                                                                                                             |

|                 | NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is to be expected. |

|                 | <ol><li>The setup time may have a negative value, in which case the minimum limit defines the<br/>longest interval (between the active transition and the application of the other signal) for which<br/>correct operation of the digital circuit is to be expected.</li></ol>         |

| t <sub>t</sub>  | Transition time                                                                                                                                                                                                                                                                        |

|                 | The time interval between tow specified levels, one near the beginning and one near the end of the same pulse edge                                                                                                                                                                     |

| tw              | Pulse duration (width)                                                                                                                                                                                                                                                                 |

|                 | The time interval between specified reference points on the leading and trailing edges of the pulse waveform                                                                                                                                                                           |

| VIH             | High-level input voltage                                                                                                                                                                                                                                                               |

|                 | An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables                                                                                                                                                           |

|                 | NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is to be expected.                                                                                                      |

| VIL             | Low-level input voltage                                                                                                                                                                                                                                                                |

|                 | An input voltage within the less positive (more negative) of the two ranges of values used to represent the binary variables                                                                                                                                                           |

|                 | NOTE: A maximum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is to be expected.                                                                                                        |

| VOH             | High-level output voltage                                                                                                                                                                                                                                                              |

|                 | The voltage at an output terminal with input conditions applied that, according to product specification, establishes a high level at the output                                                                                                                                       |

| VOL             | Low-level output voltage                                                                                                                                                                                                                                                               |

|                 | The voltage at an output terminal with input conditions applied that, according to product specification, establishes a low level at the output                                                                                                                                        |

|                 |                                                                                                                                                                                                                                                                                        |

|                 |                                                                                                                                                                                                                                                                                        |

## **EXPLANATION OF FUNCTION TABLES**

The following symbols are used in function tables on TI data sheets:

| $\boldsymbol{H} \in \boldsymbol{H}^{1,1}$ | =     | high level (steady state)                                                                                |

|-------------------------------------------|-------|----------------------------------------------------------------------------------------------------------|

| L                                         | = .   | low level (steady state)                                                                                 |

| 1                                         | =     | transition from low to high level                                                                        |

| $\downarrow$                              | • = • | transition from high to low level                                                                        |

|                                           | =     | value/level or resulting value/level is routed to indicated destination                                  |

|                                           | =     | value/level is re-entered                                                                                |

| X                                         | =     | irrelevant (any input, including transitions)                                                            |

| Z                                         | =     | off (high-impedance) state of a 3-state output                                                           |

| ah                                        | ÷     | the level of steady-state inputs A through H respectively                                                |

| Q <sub>0</sub>                            | =     | level of Q before the indicated steady-state input conditions were established                           |

| $\overline{Q}_0$                          | =     | complement of $\mathbf{Q}_0$ or level of $\overline{\mathbf{Q}}$ before the indicated steady-state input |

|                                           |       | conditions were established                                                                              |

| Q <sub>n</sub>                            | =     | level of Q before the most recent active transition indicated by $\downarrow$ or $\uparrow$              |

|                                           | =     | one high-level pulse                                                                                     |

|                                           | =     | one low-level pulse                                                                                      |

| Toggle                                    | =     | each output changes to the complement of its previous level on each active                               |

|                                           |       | transition indicated by $\downarrow$ or $\uparrow$                                                       |

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

If, in the input columns, a row contains H, L, and/or X together with  $\uparrow$  and/or  $\downarrow$ , this means the output is valid whenever the input configuration is achieved but the transition(s) must occur following the achievement of the steady-state levels. If the output is shown as a level (H, L, Q<sub>0</sub>, or  $\overline{Q}_0$ ), it persists so long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. (If the output is shown as a pulse,  $\_\_\_$  or  $\_\_\_$ , the pulse follows the indicated input transition and persists for an interval dependent on the circuit.)

Among the most complex function tables are those of the shift registers. These embody most of the symbols used in any of the function tables, plus more. Below is the function table of a 4-bit bidirectional universal shift register, e.g., type SN74194.

| INPUTS |      |    |           |      |       | OUTF | PUTS |              |     |                 |                 |                 |                 |

|--------|------|----|-----------|------|-------|------|------|--------------|-----|-----------------|-----------------|-----------------|-----------------|

| CLEAR  | MODE |    | CLOCK SEI |      | RIAL  |      | PARA | LLEL         |     | 0.              | 0-              | 0-              | 0               |

| OLEAN  | S1   | S0 | CLUCK     | LEFT | RIGHT | A    | В    | C            | D   | QA              | QB              | QC              | QD              |

| L      | X    | X  | х         | X    | х     | X    | х    | <b>X</b> * * | - X | L               | L               | L               | L               |

| H ,    | х    | х  | L         | х    | х     | X    | X    | X            | х   | Q <sub>A0</sub> | Q <sub>B0</sub> | Q <sub>C0</sub> | Q <sub>D0</sub> |

| н      | н    | н  | 1         | х    | х     | a    | b    | С            | d   | a               | b               | с               | d               |

| н      | Ľ    | H  | Î         | x    | н     | Ή.   | H    | H            | н   | н               | Q <sub>An</sub> | QBn             | QCn             |

| н      | L    | Н  | Î         | x    | L     | L    | L    | t Las.       | L   | L               | Q <sub>An</sub> | QBn             | QCn             |

| н      | н    | L  | Î         | н    | х     | X    | X    | Χ.           | х   | QBn             | QCn             | Q <sub>Dn</sub> | н               |

| н      | н    | L  | Î Î       | [ L  | X     | x    | X    | Х            | х   | QBn             | QCn             | Q <sub>Dn</sub> | L               |

| н      | L    | L  | х         | X    | x     | х    | х    | X            | Х   | Q <sub>A0</sub> | Q <sub>B0</sub> | Q <sub>C0</sub> | Q <sub>D0</sub> |

The first line of the table represents a synchronous clearing of the register and says that if clear is low, all four outputs will be reset low regardless of the other inputs. In the following lines, clear is inactive (high) and so has no effect.

The second line shows that so long as the clock input remains low (while clear is high), no other input has any effect and the outputs maintain the levels they assumed before the steady-state combination of clear high and clock low was established. Since on other lines of the table only the rising transition of the clock is shown to be active, the second line implicitly shows that no further change in the outputs will occur while the clock remains high or on the high-to-low transition of the clock.

The third line of the table represents synchronous parallel loading of the register and says that if S1 and S0 are both high then, without regard to the serial input, the data entered at A will be at output  $Q_A$ , data entered at B will be at  $Q_B$ , and so forth, following a low-to-high clock transition.

The fourth and fifth lines represent the loading of high- and low-level data, respectively, from the shift-right serial input and the shifting of previously entered data one bit; data previously at  $Q_A$  is now at  $Q_B$ , the previous levels of  $Q_B$  and  $Q_C$  are now at  $Q_C$  and  $Q_D$ , respectively, and the data previously at  $Q_D$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is low and S0 is high and the levels at inputs A through D have no effect.

The sixth and seventh lines represent the loading of high- and low-level data, respectively, from the shift-left serial input and the shifting of previously entered data one bit; data previously at  $Q_B$  is now at  $Q_A$ , the previous levels of  $Q_C$  and  $Q_D$  are now at  $Q_B$  and  $Q_C$ , respectively, and the data previously at  $Q_A$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is high and S0 is low and the levels at inputs A through D have no effect.

The last line shows that as long as both inputs are low, no other input has any effect and, as in the second line, the outputs maintain the levels they assumed before the steady-state combination of clear high and both mode inputs low was established.

The function table functional tests do not reflect all possible combinations or sequential modes.

### **Current Texas Instruments Advanced Logic Publications**

Listed below is the current collection of Texas Instruments logic technical documentation. The alphanumeric code is the literature number for each item listed. These documents can be ordered through a TI representative or authorized distributor by referencing the literature number.

| Document                                                                                                               | iterature Number |

|------------------------------------------------------------------------------------------------------------------------|------------------|

| Advanced BiCMOS Technology Data Book (1994)                                                                            | SCBD002B         |

| Advanced Bus-Interface SPICE I/O Models Data Book (1995)                                                               | SCBD004A         |

| Advanced CMOS Logic Data Book (1993)                                                                                   | SCAD001C         |

| Advanced Logic and Bus-Interface Logic Data Book (1991)                                                                | SCYD001          |

| ALS/AS Logic Data Book (1995)                                                                                          | SDAD001C         |

| BCT BiCMOS Bus-Interface Logic Data Book (1994)                                                                        | SCBD001B         |

| Boundary-Scan Logic, IEEE Std. 1149.1 (JTAG) 5-V and 3.3-V<br>Bus-Interface and Scan-Support Products Data Book (1994) | SCTD002          |

| CBT Bus Switches Crossbar Technology Data Book (1995)                                                                  | SCDD001          |

| CDC Clock-Distribution Circuits Data Book (1994)                                                                       | SCAD004          |

| F Logic Data Book (1994)                                                                                               | SDFD001B         |

| High-Performance FIFO Memories Data Book (1996)                                                                        | SCAD003C         |

| High-Performance FIFO Memories Designer's Handbook (1996)                                                              | SCAA012A         |

| High-Speed CMOS Logic Data Book (1989)                                                                                 | SCLD001C         |

| Low-Voltage Logic Data Book (1996)                                                                                     | SCBD003B         |

| TTL Logic Data Book (TTL, LS, S) (1988)                                                                                | SDLD001A         |

| Semiconductor Group Package Outlines Reference Guide                                                                   | SSYU001A         |

|                                                                                                                        |                  |

In addition to the books listed above, the following documents are available only in Europe.

| Document                                                | iterature Number |

|---------------------------------------------------------|------------------|

| Advanced BiCMOS Technology Data Book (1994)             | SCBDE08          |

| CBT Crossbar Technology Data Book (1995)                | SCDDE01          |

| CDC Data and Applications Manual (1995)                 | SCBTE07B         |

| Packaging Data Book (1995)                              | SCYDE04          |

| ASL SCOPE™ Products Data and Applications Manual (1994) | SCBDE09          |

# PCI-TO-PC CARD CONTROLLERS

# Signaling Environment

|                           | PCI1050                           | PCI10XX                             | PCI1130                           |

|---------------------------|-----------------------------------|-------------------------------------|-----------------------------------|

| FEATURES                  | PCI-TO-PC CARD<br>CONTROLLER UNIT | PCI-TO-PC CARD16<br>CONTROLLER UNIT | PCI-TO-CARDBUS<br>CONTROLLER UNIT |

| Core logic environment    | 5 V                               | 3.3 V                               | 3.3 V                             |

| PCI signaling environment | 3.3 V/5 V                         | 3.3 V/5 V                           | 3.3 V/5 V                         |

# **Standards Compliance/Compatibility**

|                                       | PCI1050                           | PCI10XX                             | PCI1130                            |  |

|---------------------------------------|-----------------------------------|-------------------------------------|------------------------------------|--|

| FEATURES                              | PCI-TO-PC CARD<br>CONTROLLER UNIT | PCI-TO-PC CARD16<br>CONTROLLER UNIT | PCI-TO-CARDBUS<br>CONTROLLER UNIT  |  |

| PCI specification compliance          | PCI specification 2.0             | PCI specification 2.1               | PCI specification 2.1              |  |

| PC Card™ standard compliance          | PCMCIA 2.1/JEIDA 4.1              | PC Card standard,<br>February 1995  | PC Card standard,<br>February 1995 |  |

| Intel™ 82365SL-DF register compatible | Yes                               | Yes                                 | Yes                                |  |

| ExCA™ register compatible             | Yes                               | Yes                                 | Yes                                |  |

# **Slots Support**

|                           | PCI1050                           | PCI10XX                             | PCI1130                                                 |  |

|---------------------------|-----------------------------------|-------------------------------------|---------------------------------------------------------|--|

| FEATURES                  | PCI-TO-PC CARD<br>CONTROLLER UNIT | PCI-TO-PC CARD16<br>CONTROLLER UNIT | PCI-TO-CARDBUS<br>CONTROLLER UNIT                       |  |

| Number of slots supported | 2                                 | 2                                   | 2                                                       |  |

| Slot voltages supported   | 3.3 V/5 V                         | 3.3 V/5 V                           | 3.3-V/5-V PC Card16 cards<br>and 3.3-V<br>CardBus cards |  |

| Hot insertion/removal     | Yes                               | Yes                                 | Yes                                                     |  |

# Interrupts

|              | PCI1050                           | PCI10XX                             | PCI1130                           |  |

|--------------|-----------------------------------|-------------------------------------|-----------------------------------|--|

| FEATURES     | PCI-TO-PC CARD<br>CONTROLLER UNIT | PCI-TO-PC CARD16<br>CONTROLLER UNIT | PCI-TO-CARDBUS<br>CONTROLLER UNIT |  |

| PCI style    | Yes                               | Yes                                 | Yes                               |  |

| ISA serial   | Yes                               | Yes                                 | Yes                               |  |

| ISA parallel | Yes                               | Yes                                 | Yes                               |  |

### DMA

|            | PCI1050                           | PCI10XX                             | PCI1130                           |

|------------|-----------------------------------|-------------------------------------|-----------------------------------|

| FEATURES   | PCI-TO-PC CARD<br>CONTROLLER UNIT | PCI-TO-PC CARD16<br>CONTROLLER UNIT | PCI-TO-CARDBUS<br>CONTROLLER UNIT |

| PCIWay DMA | No                                | Yes                                 | Yes                               |

| PC/PCI DMA | No                                | Yes                                 | Yes                               |

# PCI-TO-PC CARD CONTROLLERS

### **Other Features**

|                                            | PCI1050                           | PCI10XX                             | PCI1130                           |  |

|--------------------------------------------|-----------------------------------|-------------------------------------|-----------------------------------|--|

| FEATURES                                   | PCI-TO-PC CARD<br>CONTROLLER UNIT | PCI-TO-PC CARD16<br>CONTROLLER UNIT | PCI-TO-CARDBUS<br>CONTROLLER UNIT |  |

| Burst transfer support                     | No                                | Yes                                 | Yes                               |  |

| PCI clock run support                      | No                                | Yes                                 | Yes                               |  |

| Programmable windows for PC Card16 sockets | Five memory and two I/O           | Five memory and two I/O             | Five memory and two I/O           |  |

| Programmable windows for CardBus sockets   | Two memory and two I/O            | Two memory and two I/O              | Two memory and two I/O            |  |

| Zoom video support                         | No                                | Yes                                 | Yes                               |  |

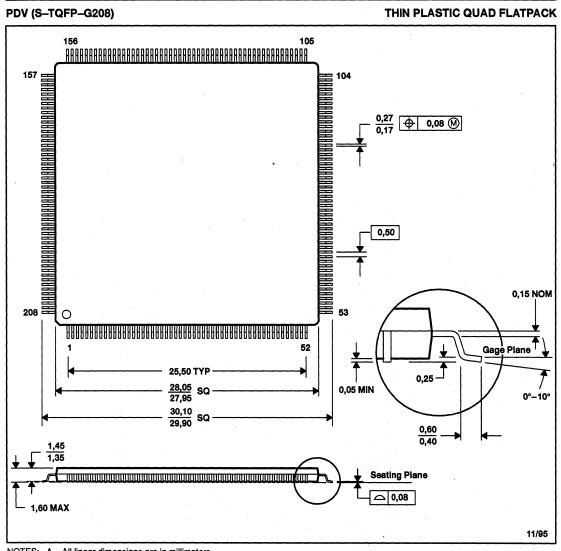

| Package type                               | 208-pin PQFP                      | 208-pin TQFP                        | 208-pin TQFP                      |  |

| General Information | 1 |

|---------------------|---|

| PCI1050             | 2 |

| PCI10XX             | 3 |

| PCI1130             | 4 |

| PCI20XX             | 5 |

| Mechanical Data     | 6 |

SCPS001F - OCTOBER 1994 - REVISED MARCH 1996

- Supports Two PC Card<sup>™</sup> Slots With Hot Insertion or Removal

- Supports Any Combination of 3.3-V and 5-V PC Cards™

- PCMCIA 2.1/JEIDA 4.1/ExCA™ Standard Compliant

- Intel<sup>™</sup> 82365SL-DF Register Compatible

- Programmable PCI/ISA Interrupt Routing

- Programmable Vpp and V<sub>CC</sub> Control for Each Slot

- Supports AT Attachment (ATA) Interface

- Device Selection for Cascading Done Through PCI Configuration

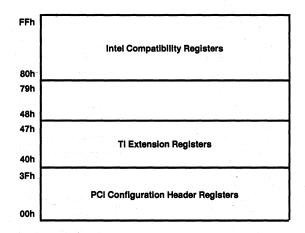

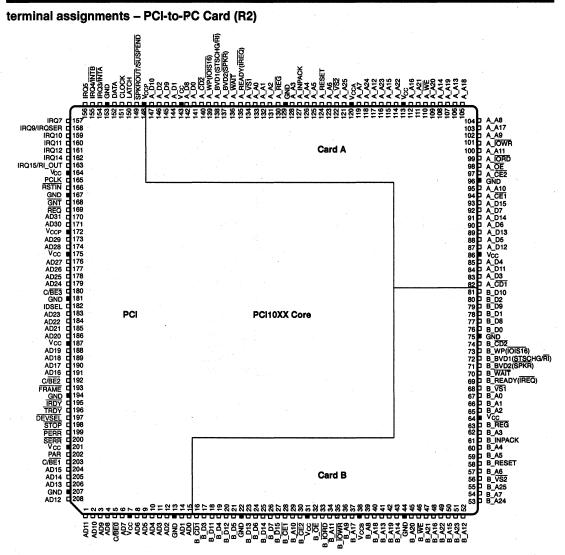

- Exchangeable Card (ExCA™)-Compatible Registers Mapped In the PCI Configuration Space and I/O Space

- Texas Instruments (TI) Extension Registers Mapped in the PCI Configuration Space

- Four-Deep, 32-Bit Write Buffers

- Low-Power Advanced Submicron CMOS Technology

- Packaged in 208-Pin Plastic Quad Flatpack (PPM)

### description

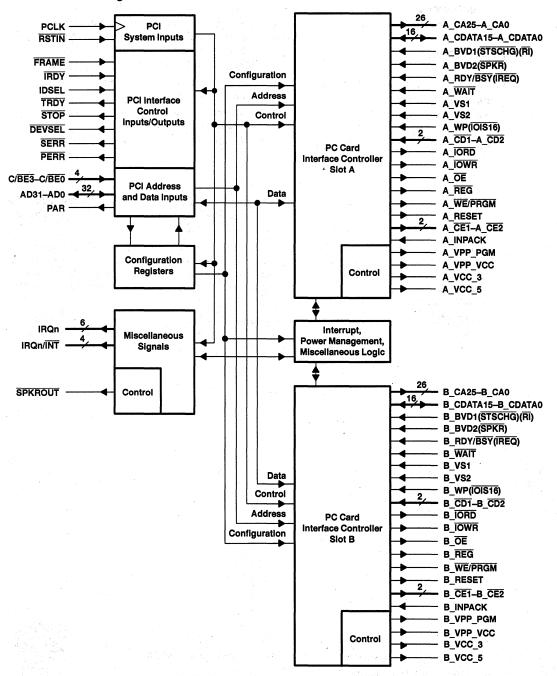

The TI PCI1050 is a high-performance card controller that interfaces two PC Card slots to the peripheral component interconnect (PCI) bus. The core logic and PCI interface are powered at 5 V while the card interfaces can be powered at the card  $V_{CC}$  to support any combination of 3.3-V and 5-V PC Cards.

All card signals are individually buffered to allow hot insertion and removal without external buffering. The PCI1050 is register compatible with the Intel 82365SL-DF ExCA controller and can be cascaded to support up to eight PC Card slots. The PCI1050 internal datapath logic allows the host to access 8-bit and 16-bit cards using full 32-bit PCI cycles for maximum performance. Independent four-deep by 32-bit write buffers allow fast posted writes to improve system bus utilization.

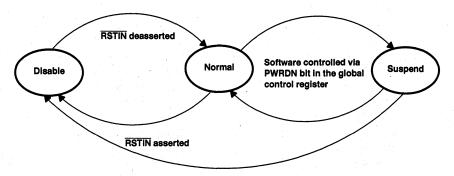

An advanced CMOS process is utilized to achieve low system-power consumption while operating at PCI clock rates up to 33 MHz. A power-down mode allows host software to reduce power consumption further while preserving internal register contents and allowing PC Cards to interrupt the host.

#### Table of Contents

|                                    |      | •••••••••                                   |      |

|------------------------------------|------|---------------------------------------------|------|

| Functional Block Diagram           | 2-4  | Electrical Characteristics                  | 2-54 |

| Terminal Assignments               |      | PCI Clock/Reset Timing Requirements         |      |

| Signal Name/Pin Number Sort Tables | 2-6  | PCI Timing Requirements                     |      |

| Terminal Functions                 |      | Parameter Measurement Information           |      |

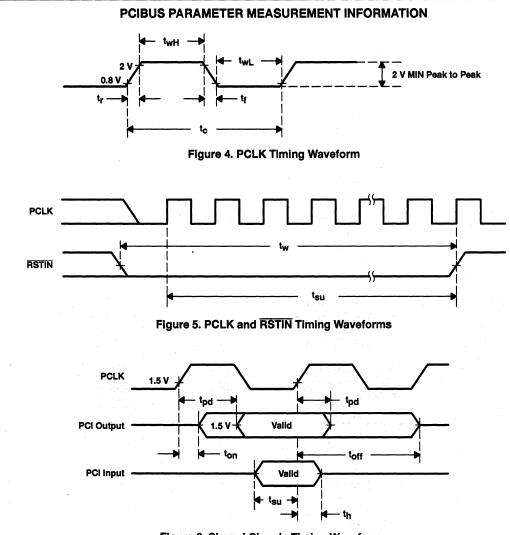

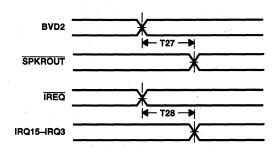

| Architecture                       | 2-13 | PCIbus Parameter Measurement Information    |      |

| Compatibility Registers            |      | PC Card Cycle Timing                        |      |

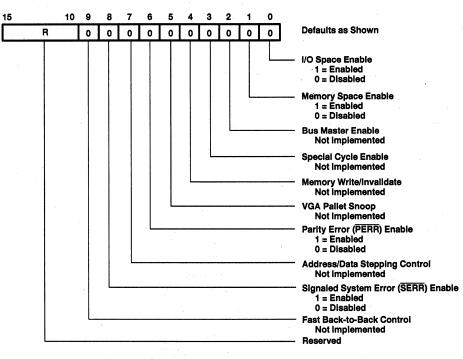

| PCI Configuration Headers          |      | Timing Requirements                         |      |

| TI Extension Registers             |      | Switching Characteristics                   |      |

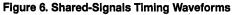

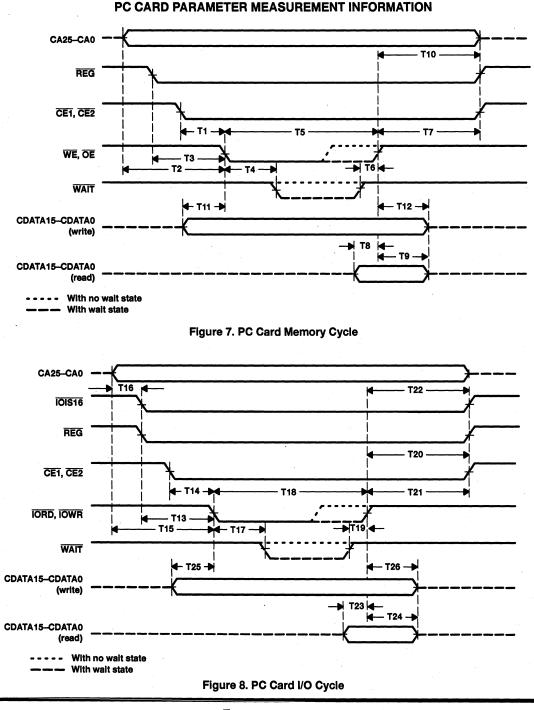

| Absolute Maximum Ratings           | 2-53 | PC Card Parameter Measurement Information . |      |

| Recommended Operating Conditions   | 2-53 |                                             |      |

|                                    |      |                                             |      |

Lotus is a registered trademark of Lotus Development Corporation Microsoft is a registered trademark of Microsoft Corporation.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1996, Texas Instruments Incorporated

SCPS001F - OCTOBER 1994 - REVISED MARCH 1996

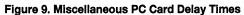

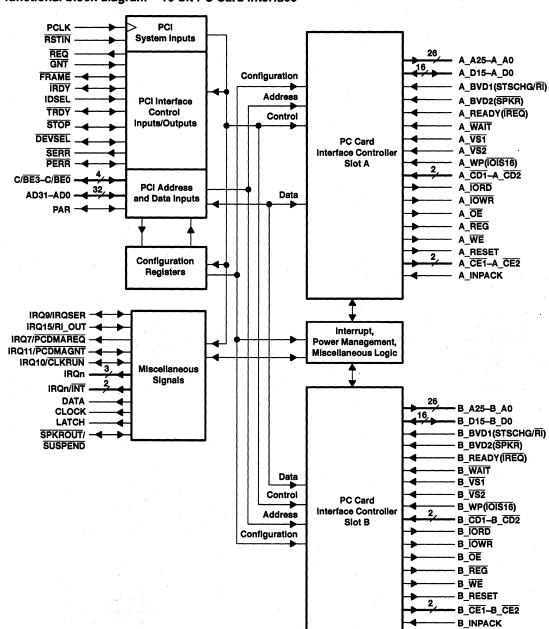

#### functional block diagram

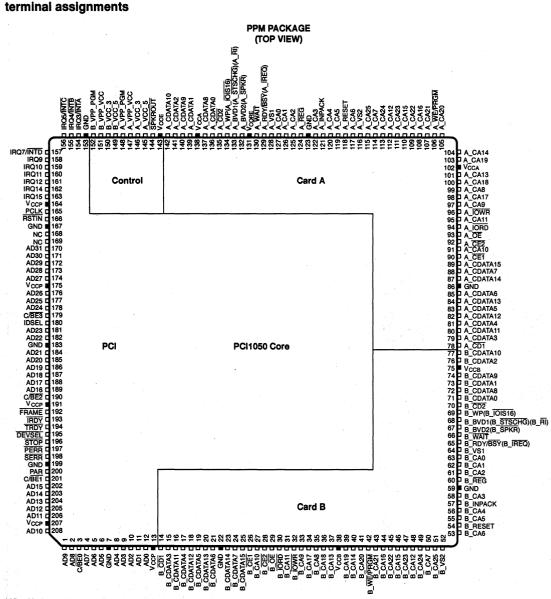

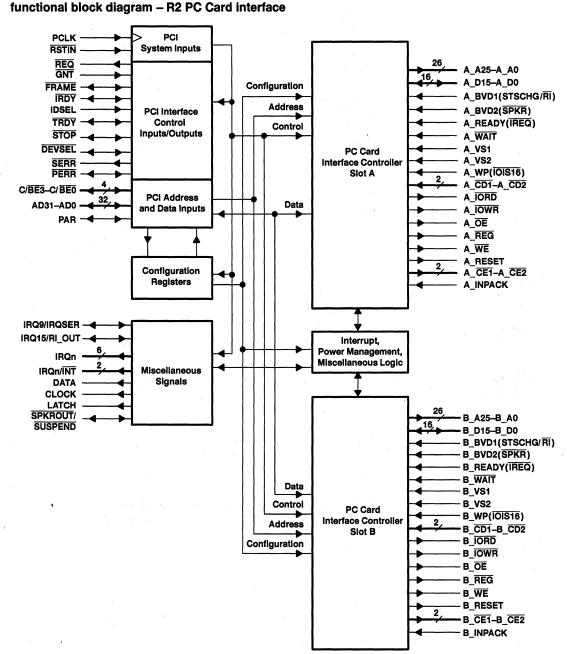

SCPS001F - OCTOBER 1994 - REVISED MARCH 1996

NC - No internal connection

SCPS001F - OCTOBER 1994 - REVISED MARCH 1996

| SIGNAL NAME            | NO. | SIGNAL NAME            | NO. | SIGNAL NAME       | NO. | SIGNAL NAME | NO. |

|------------------------|-----|------------------------|-----|-------------------|-----|-------------|-----|

| A BVD1(A STSCHG)(A RI) | 133 | A IOWR                 | 96  | B_CDATA10         | 77  | AD28        | 173 |

| A_BVD2(A_SPKR)         | 132 | AOE                    | 93  | B_CDATA11         | 16  | AD29        | 172 |

| A_CA0                  | 127 | A_RDY/BSY(A_IREQ)      | 129 | B_CDATA12         | 18  | AD30        | 171 |

| A_CA1                  | 126 | A_REG                  | 124 | B_CDATA13         | 20  | AD31        | 170 |

| A_CA2                  | 125 | ARESET                 | 118 | B_CDATA14         | 23  | C/BE0       | 3   |

| A CA3                  | 122 | A_VCC_3                | 146 | B CDATA15         | 25  | C/BE1       | 201 |

| A_CA4                  | 120 | A_VCC_5                | 145 | B_CE1             | 26  | C/BE2       | 190 |

| A_CA5                  | 119 | A_VPP_PGM              | 148 | B CE2             | 28  | C/BE3       | 179 |

| A_CA6                  | 117 | A_VPP_VCC              | 147 | B_VS1             | 64  | DEVSEL      | 195 |

| A_CA7                  | 114 |                        | 130 | B_VS2             | 52  | FRAME       | 192 |

| A_CA8                  | 99  | A_WE/PRGM              | 106 | B_INPACK          | 57  | GND         | 7   |

| A_CA9                  | 97  | A_WP(A_IOSI16)         | 134 | B IORD            | 30  | GND         | 22  |

| A_CA10                 | 91  | B_BVD1(B_STSCHG)(B_RI) | 68  | BIOWR             | 32  | GND         | 59  |

| A_CA11                 | 95  |                        | 67  | B OE              | 29  | GND         | 86  |

| A_CA12                 | 112 | B_BVD2(B_SPKR)         | 63  | B_RDY/BSY(B_IREQ) | 65  | GND         | 123 |

| A CA13                 | 101 | B_CA0                  | 62  | B_REG             | 60  | GND         | 153 |

| A_CA14                 | 104 | B_CA1                  | 61  | B_RESET           | 54  | GND         | 167 |

| A_CA15                 | 110 | B_CA2                  | 58  | B_VCC_3           | 150 | GND         | 183 |

| A_CA16                 | 108 | B_CA3                  | 56  | B_VCC_5           | 149 | GND         | 199 |

| A_CA17                 | 98  | B_CA4                  | 55  | B_VPP_PGM         | 152 | IDSEL       | 180 |

| A_CA18                 | 100 | B_CA5                  | 53  | B_VPP_VCC         | 152 | IRDY        | 193 |

| A_CA19                 | 100 | B_CA6                  | 50  | B WAIT            | 66  |             |     |

| A_CA20                 | 105 | B_CA7                  | 35  |                   |     | IRQ3/INTA   | 154 |

| A_CA20<br>A_CA21       |     | B_CA8                  |     | B_WE/PRGM         | 42  | IRQ4/INTB   | 155 |

|                        | 107 | B_CA9                  | 33  | B_WP(B_IOIS16)    | 69  | IRQ5/INTC   | 156 |

| A_CA22                 | 109 | B_CA10                 | 27  | AD0               | 12  | IRQ7/INTD   | 157 |

| A_CA23                 | 111 | B_CA11                 | 31  | AD1               | 11  | IRQ9        | 158 |

| A_CA24                 | 113 | B_CA12                 | 48  | AD2               | 10  | IRQ10       | 159 |

| A_CA25                 | 115 | B_CA13                 | 37  | AD3               | 9   | IRQ11       | 160 |

| A_CD1                  | 78  | B_CA14                 | 40  | AD4               | 8   | IRQ12       | 161 |

| A_CD2                  | 135 | B_CA15                 | 46  | AD5               | 6   | IRQ14       | 162 |

| A_CDATA0               | 136 | B_CA16                 | 44  | AD6               | 5   | IRQ15       | 163 |

| A_CDATA1               | 139 | B_CA17                 | 34  | AD7               | 4   | NC          | 168 |

| A_CDATA2               | 141 | B_CA18                 | 36  | AD8               | 2   | NC          | 169 |

| A_CDATA3               | 79  | B_CA19                 | 39  | AD9               | 1   | PAR         | 200 |

| A_CDATA4               | 81  | B_CA20                 | 41  | AD10              | 208 | PCLK        | 165 |

| A_CDATA5               | 83  | B_CA21                 | 43  | AD11              | 206 | RSTIN       | 166 |

| A_CDATA6               | 85  | B_CA22                 | 45  | AD12              | 205 | PERR        | 197 |

| A_CDATA7               | 88  | B_CA23                 | 47  | AD13              | 204 | SPKROUT     | 144 |

| A_CDATA8               | 137 | B_CA24                 | 49  | AD14              | 203 | STOP        | 196 |

| A_CDATA9               | 140 | B_CA25                 | 51  | AD15              | 202 | SERR        | 198 |

| A_CDATA10              | 142 | B_CD1                  | 14  | AD16              | 189 | TRDY        | 194 |

| A_CDATA11              | 80  | B_CD2                  | 70  | AD17              | 188 | VCCA        | 102 |

| A_CDATA12              | 82  | B_CDATA0               | 71  | AD18              | 187 | VCCA        | 138 |

| A_CDATA13              | 84  | B_CDATA1               | 73  | AD19              | 186 | VCCB        | 35  |

| A_CDATA14              | 87  | B_CDATA2               | 76  | AD20              | 185 | VCCB        | 75  |

| A_CDATA15              | 89  | B_CDATA3               | 15  | AD21              | 184 | VCCE        | 143 |

| A_CE1                  | 90  | B_CDATA4               | 17  | AD22              | 182 | VCCP        | 13  |

| A_CE2                  | 92  | B_CDATA5               | 19  | AD23              | 181 | VCCP        | 164 |

| A_VS1                  | 128 | B_CDATA6               | 21  | AD24              | 178 | VCCP        | 175 |

| A_VS2                  | 116 | B_CDATA7               | 24  | AD25              | 177 | VCCP        | 191 |

| A INPACK               | 121 | B_CDATA8               | 72  | AD26              | 176 | VCCP        | 207 |

| AIORD                  | .94 | B CDATA9               | 74  | AD27              | 174 | VCORE       | 131 |

Table 1. Signals Sorted by Signal Name

2-6

SCPS001F - OCTOBER 1994 - REVISED MARCH 1996

|          |                  |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |                        |     | /           |

|----------|------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|-----|-------------|

| NO.      | SIGNAL NAME      | NO.   | SIGNAL NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | NO. | SIGNAL NAME            | NO. | SIGNAL NAME |

| 1        | AD9              | 53    | B_CA6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 105 | A_CA20                 | 157 | IRQ7/INTD   |

| 2        | AD8              | 54    | B_RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 106 | A_WE/PRGM              | 158 | IRQ9        |

| 3        | C/BEO            | 55    | B_CA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107 | A_CA21                 | 159 | IRQ10       |

| 4        | AD7              | 56    | B_CA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 108 | A_CA16                 | 160 | IRQ11       |

| 5        | AD6              | 57    | B_INPACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 109 | A_CA22                 | 161 | IRQ12       |

| 6        | AD5              | 58    | B_CA3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 110 | A_CA15                 | 162 | IRQ14       |

| 7        | GND              | 59    | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 111 | A_CA23                 | 163 | IRQ15       |

| 8        | AD4              | 60    | B_REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 112 | A_CA12                 | 164 | VCCP        |

| 9        | AD3              | 61    | B_CA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 113 | A_CA24                 | 165 | PCLK        |

| 10       | AD2              | 62    | B_CA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 114 | A_CA7                  | 166 | RSTIN       |

| 11       | AD1              | 63    | B_CA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 115 | A_CA25                 | 167 | GND         |

| 12       | AD0              | 64    | B_VS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 116 | A_VS2                  | 168 | NC          |

| 13       | VCCP             | 65    | B_RDY/BSY(B_IREQ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 117 | A_CA6                  | 169 | NC          |

| 14       | B_CD1            | -66   | B_WAIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 118 | A_RESET                | 170 | AD31        |

| 15       | B_CDATA3         | 67    | B_BVD2(B_SPKR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 119 | A_CA5                  | 171 | AD30        |

| 16       | B_CDATA11        | 68    | B_BVD1(B_STSCHG)(B_RI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 120 | A_CA4                  | 172 | AD29        |

| 17       | B_CDATA4         | 69    | B_WP(B_IOIS16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 121 | A_INPACK               | 173 | AD28        |

| 18       | B_CDATA12        | 70    | B_CD2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 122 | A_CA3                  | 174 | AD27        |

| 19       | B_CDATA5         | 71    | B_CDATA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 123 | GND                    | 175 | VCCP        |

| 20       | B_CDATA13        | 72    | B_CDATA8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 124 | A_REG                  | 176 | AD26        |

| 21       | B_CDATA6         | 73    | B_CDATA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 125 | A_CA2                  | 177 | AD25        |