# **Data Acquisition Circuits**Data Conversion and DSP Analog Interface

Data Book

# Data Book

**Data Acquisition Circuits**Data Conversion and DSP Analog Interface

1995

1995

**Mixed-Signal Products**

| General Information                 | 1 |

|-------------------------------------|---|

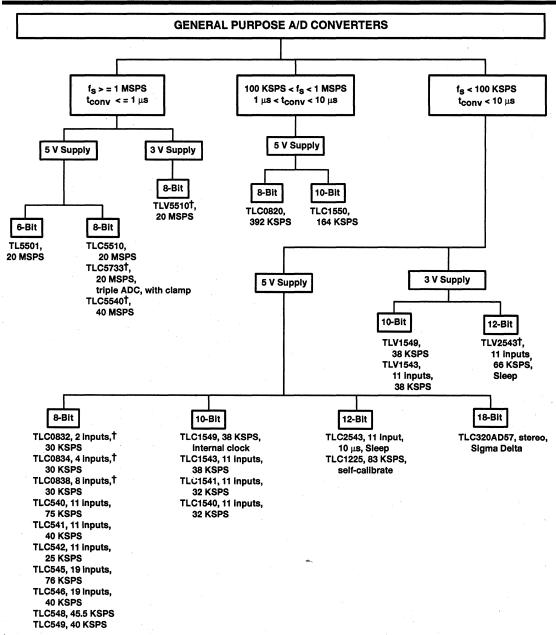

| General Purpose ADCs                | 2 |

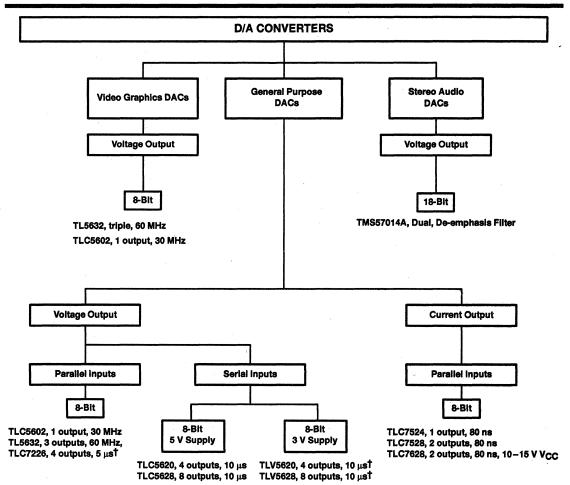

| General Purpose DACs                | 3 |

| DSP Analog Interface and Conversion | 4 |

| Special Functions                   | 5 |

| Video Interface Palettes            | 6 |

| Data Manuals                        | 7 |

| Application Reports                 | 8 |

| Mechanical Data                     | 9 |

| Appendix                            | А |

# Data Acquisition Circuits Data Book

Data Conversion and DSP Analog Interface

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1995, Texas Instruments Incorporated

Printed in U.S.A. by Custom Printing Company Owensville, Missouri

#### INTRODUCTION

Texas Instruments offers an extensive line of industry-standard integrated circuits designed to provide highly reliable circuits for peripheral support applications of microprocessor-based systems, DSP (digital signal processing) related analog interfaces, video interfaces, video and high-speed converters, digitizing requirements that demand ADC and DAC conversion, and general-purpose functions.

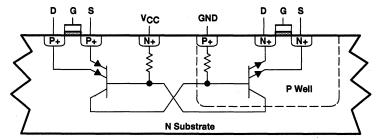

TI data acquisition system circuits represent technologies from traditional bipolar through LinCMOS<sup>TM</sup>, Advanced LinCMOS<sup>TM</sup>, and LinEPIC<sup>TM</sup> processes. The LinCMOS<sup>TM</sup> and Advanced LinCMOS<sup>TM</sup> technologies feature improvements in resolution, power consumption, and temperature stability. LinEPIC<sup>TM</sup> has both improved conversion speed and reduced power consumption.

This data book provides information on the following types of products:

- Dual-Slope Analog-to-Digital Converters (ADC)

- Successive-Approximation Semi-Flash, and Flash ADC Converters

- Current Multiplying and Video DAC Converters

- High-Speed Converters for Control Applications

- Color Palette Chips for Computer Graphics

- Analog Interface Circuits for DSP Interface

- Switched-Capacitor Filter ICs

- Other General-Purpose Functions

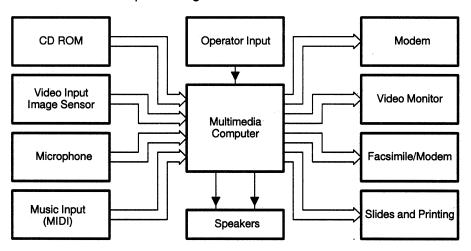

These products cover the requirements of PC and workstation multimedia applications such as audio, graphics, communication applications, modems and cellular phones, video capture and image processing, industrial control and disk-drive servo-loop control, automotive, f electronic instrumentation, consumer, digital audio and any DSP or microprocessor-based system. New surface-mount packages include both ceramic and plastic chip carriers, and the small-outline plastic packages that optimize board density with minimum impact on power-dissipation capability. The equipment with handlers and test equipment. In addition, specifications and programs are continuously updated. Quality and performance are monitored throughout all phases of manufacturing.

Included are those new products added to this volume as indicated by a dagger(†). The selection guide includes a functional description of each device by providing key parametric information and packaging options. Ordering information and mechanical data are in the last section of the book.

Complete technical data for all TI semiconductor products are available from your nearest TI Field Sales Office, local authorized TI distributor, or by writing directly to:

Texas Instruments Incorporated LITERATURE RESPONSE CENTER P.O. Box 809066 DALLAS, TEXAS 75380-9066

We sincerely believe the new 1995 Data Acquisition Circuits Data Book will be a significant addition to your technical literature from Texas Instruments.

vi

### **Contents**

| Section 1 - General Information             |      |

|---------------------------------------------|------|

| Analog-to-Digital Converter Selection Guide |      |

| Digital-to-Analog Converter Selection Guide | 1–5  |

| Cross-Reference Guide                       |      |

| Devices Discontinued Since 1992 Data Book   | 1–12 |

| Glossary                                    |      |

| Section 2 – Analog-to-Digital Converters 2–1                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICL7135C/TLC7135C<br>4 1/2-Digit Precision Analog-to-Digital Converters                                                                                   |

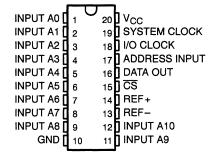

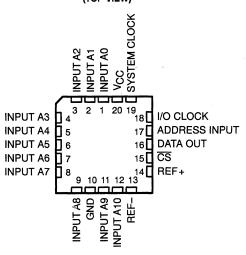

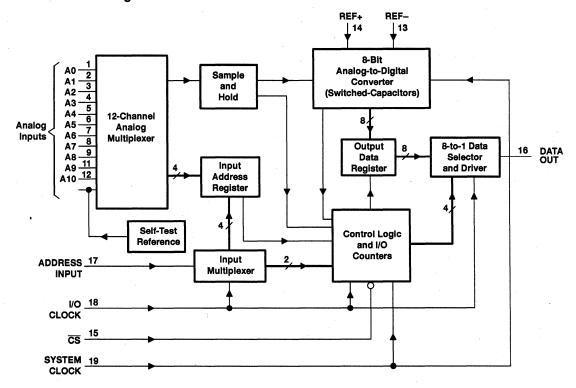

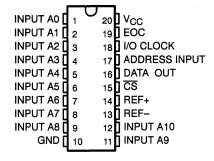

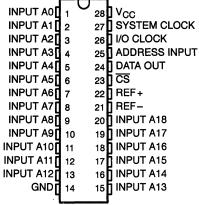

| TLC540I/TLC541I 8-Bit Analog-to-Digital Converters With Serial Control and 11 Inputs2-13                                                                  |

| TLC542C/TLC542I 8-Bit Analog-to-Digital Converters With Serial Control and 11 Inputs2-23                                                                  |

| TLC545C/TLC545I/TLC546C/TLC546I<br>8-Bit Analog-to-Digital Converters With Serial Control and 19 Inputs2-33                                               |

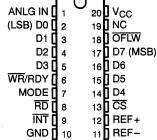

| TLC548C/TLC548I/TLC549C/TLC549I<br>8-Bit Analog-to-Digital Converters With Serial Control2-43                                                             |

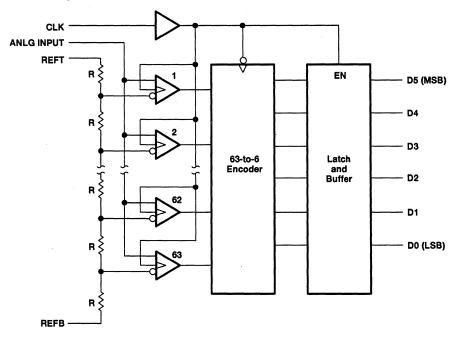

| TLC0820AC/TLC0820AI Advanced LinCMOS High-Speed 8-Bit Analog-to-Digital Converters Using Modified Flash Techniques                                        |

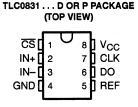

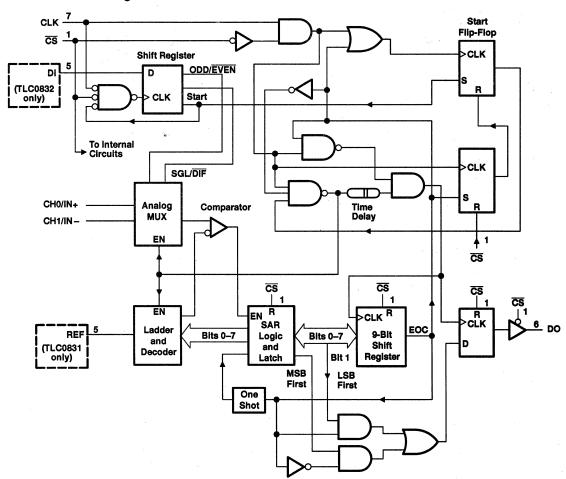

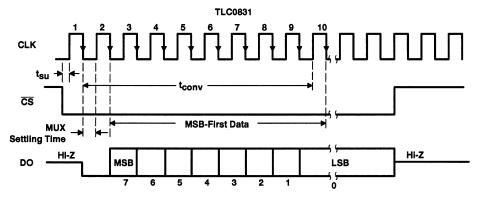

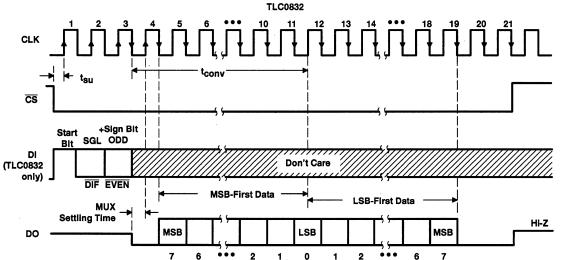

| TLC0831AC/TLC0831AI/TLC0831BC/TLC0831BI<br>TLC0832AC/TLC0832AI/TLC0832BC/TLC0832BI<br>8-Bit Analog-to-Digital Converters With Serial Control <sup>†</sup> |

| TLC0834AC/TLC0834AI/TLC0834BC/TLC0834BI<br>TLC0838AC/TLC0838AI/TLC0838BC/TLC0838BI<br>8-Bit Analog-to-Digital Converters With Serial Control <sup>†</sup> |

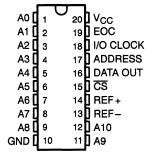

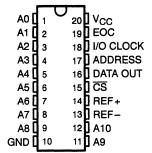

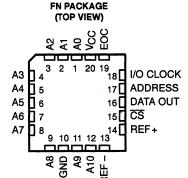

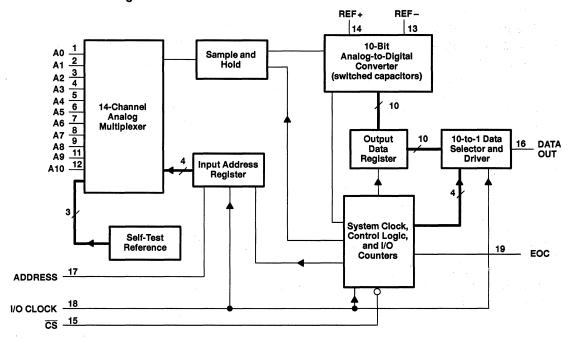

| TLC1540C/TLC1541C<br>10-Bit Analog-to-Digital Converters With Serial Control and 11 Inputs                                                                |

| TLC1542C/TLC1542I/TLC1542M/TLC1542Q/TLC1543C/TLC1543I/TLC1543Q 10-Bit Analog-to-Digital Converters With Serial Control and 11 Analog Inputs2-98           |

| TLC1549C/TLC1549I/TLC1549M<br>10-Bit Analog-to-Digital Converters With Serial Control2–118                                                                |

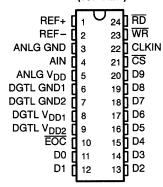

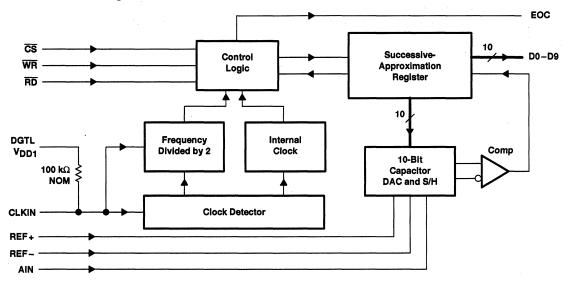

| TLC1550I/TLC1550M/TLC1551I<br>10-Bit Analog-to-Digital Converters With Parallel Outputs2–129                                                              |

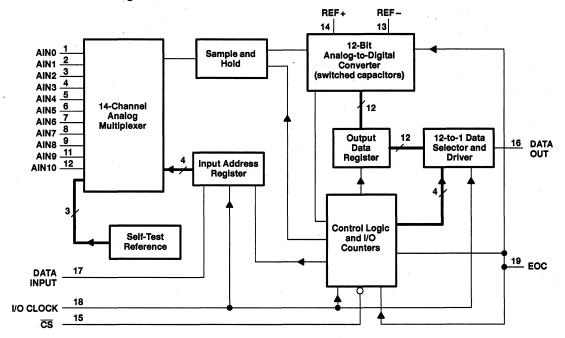

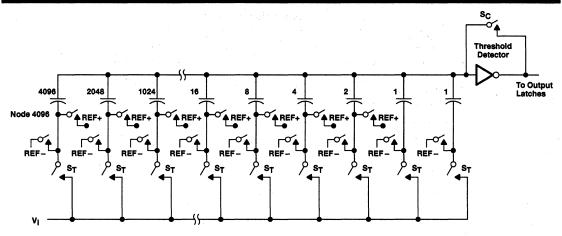

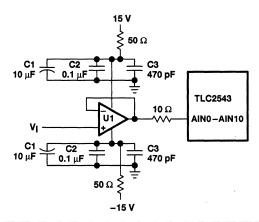

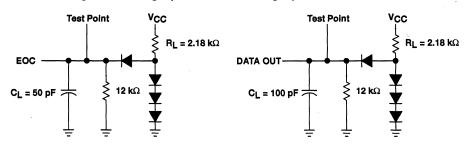

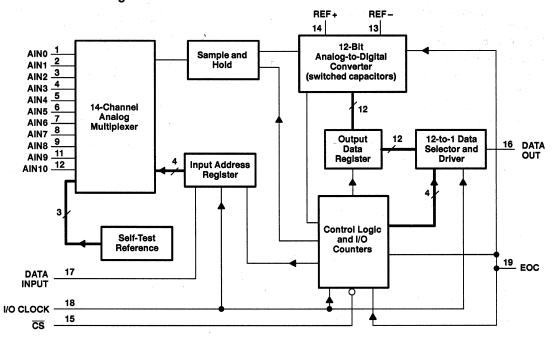

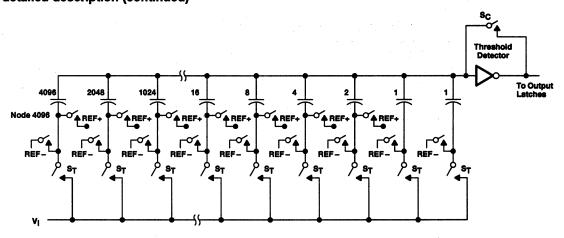

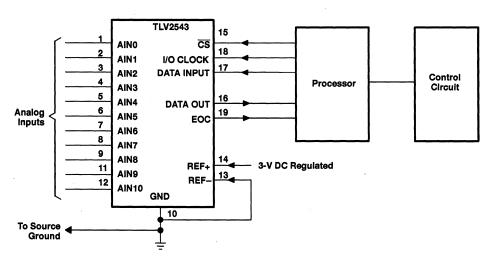

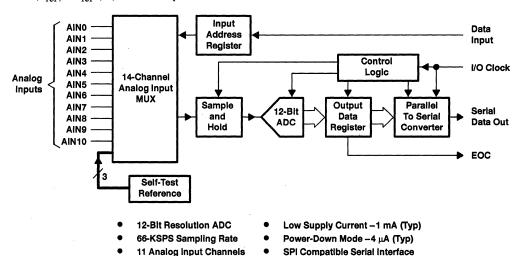

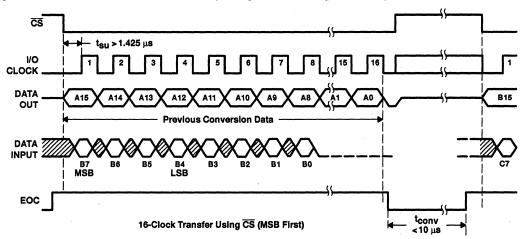

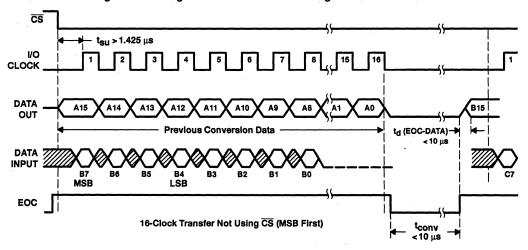

| TLC2543C/TLC2543I<br>12-Bit Analog-to-Digital Converters With Serial Control and 11 Analog Inputs2-13                                                     |

| TLC5510 8-Bit High-Speed Analog-to-Digital Converter2–15                                                                                                  |

| TLC5540 8-Bit High-Speed Analog-to-Digital Converter <sup>†</sup> 2–16                                                                                    |

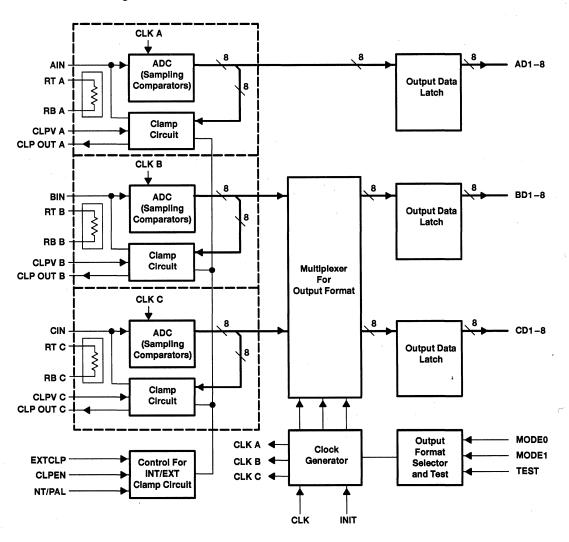

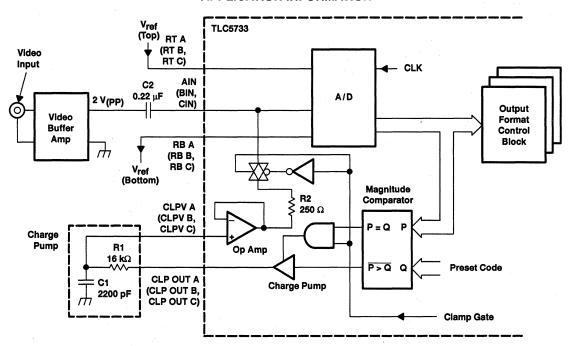

| TLC5733 20 MSPS 3-Channel Analog-to-Digital Converter With High-Precision Clamp                                                                           |

| TLV1543C/TLV1543M 3.3-V 10-Bit Analog-to-Digital Converters With Serial Control and 11 Analog Inputs 2-19                                                 |

| TLV1549C/TLV1549I/TLV1549M<br>10-Bit Analog-to-Digital Converters With Serial Control2–209                                                                |

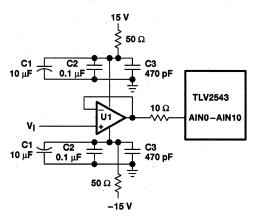

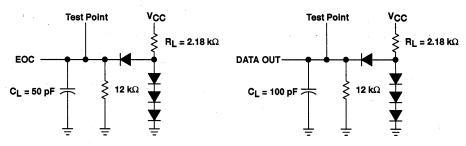

| TLV2543C/TLV2543I<br>12-Bit Analog-to-Digital Converters With Serial Control and 11 Analog Inputs2-223                                                    |

| TL5501 6-Bit Analog-to-Digital Converter                                                                                                                  |

| Section 3 – Digital-to-Analog Converters                                       | 3–1         |

|--------------------------------------------------------------------------------|-------------|

| TLC5602C/TLC5602M  Video 8-Bit Digital-to-Analog Converters                    | . 3–3       |

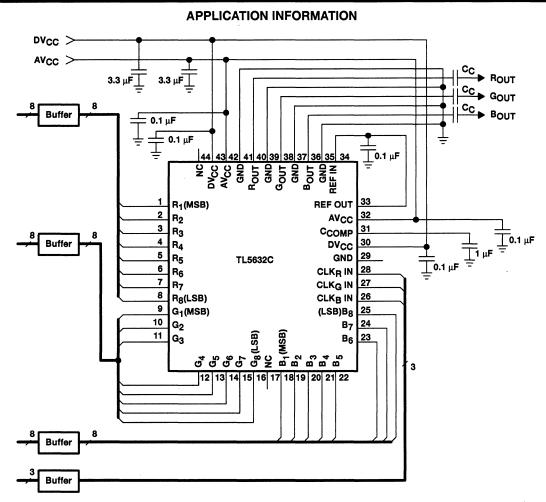

| TL5632C 8-Bit 3-Channel High-Speed Digital-to-Analog Converter                 | 3–11        |

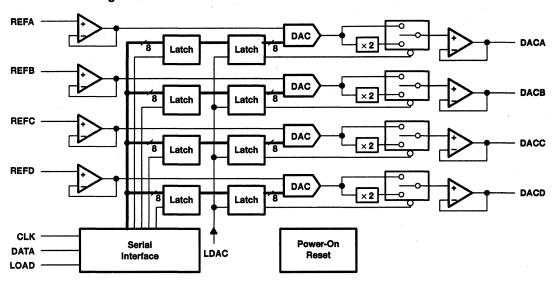

| TLC5620C/TLC5620I Quadruple 8-Bit Digital-to-Analog Converters                 | 3–19        |

| TLC5628C/TLC5628I Octal 8-Bit Digital-to-Analog Converters                     | 3–29        |

| TLC7226C/TLC7226I Quadruple 8-Bit Digital-to-Analog Converters†                | 3–39        |

| TLC7524C/TLC7524E/TLC7524I 8-Bit Multiplying Digital-to-Analog Converters      | 3–53        |

| TLC7528C/TLC7528E/TLC7528I Dual 8-Bit Multiplying Digital-to-Analog Converters | 3–63        |

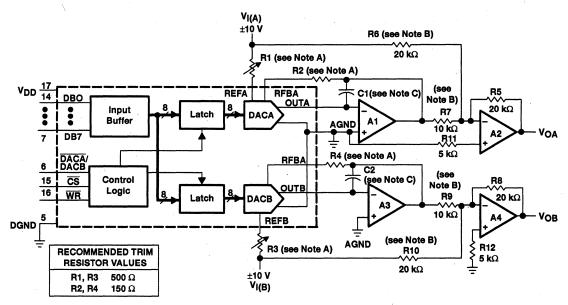

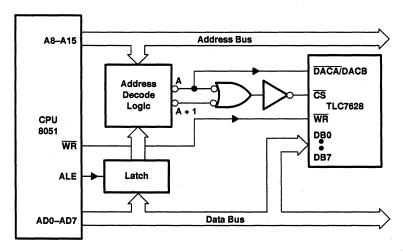

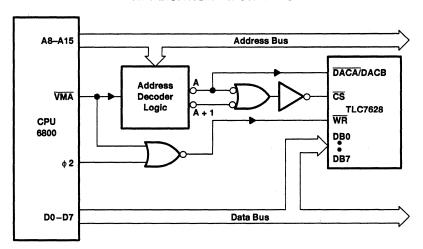

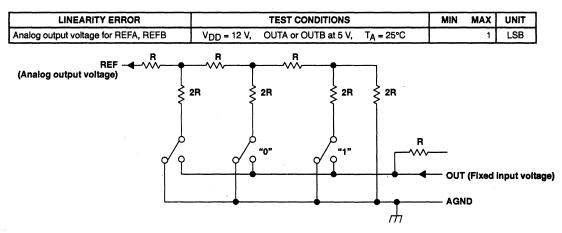

| TLC7628C/TLC7628E/TLC7628I Dual 8-Bit Multiplying Digital-to-Analog Converters | 3–77        |

| TLV5620C/TLV5620I Quadruple 8-Bit Digital-to-Analog Converters†                | 3–87        |

| TLV5628C/TLV5628I<br>Octal 8-Bit Digital-to-Analog Converters†                 | 3–95        |

| TMS57014A Dual Audio Digital-to-Analog Converter                               | -103        |

| AD7524M Advance LinCMOS 8-Bit Multiplying Digital-to-Analog Converter          | <b>⊢117</b> |

†Product Preview

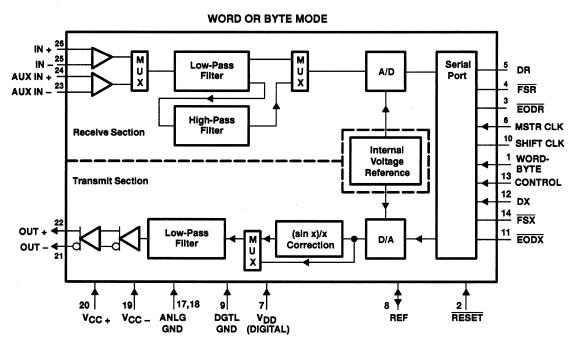

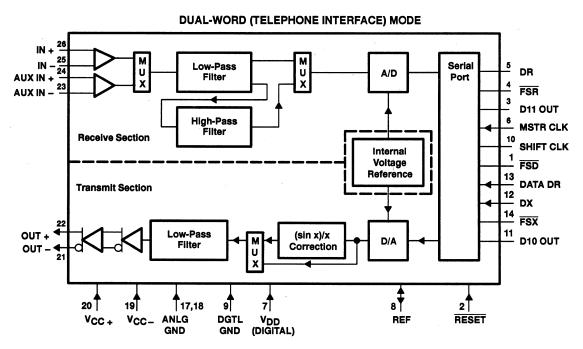

| Section 4 – Analog Interface Circuits and Codec                                                   | 4-1  |

|---------------------------------------------------------------------------------------------------|------|

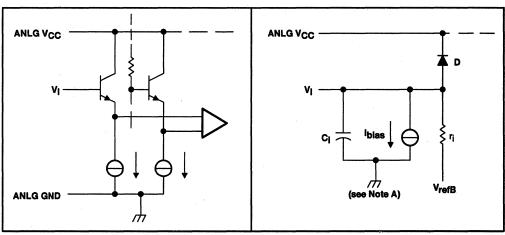

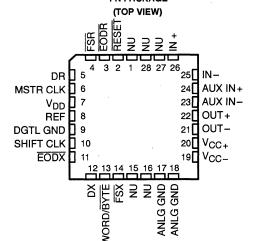

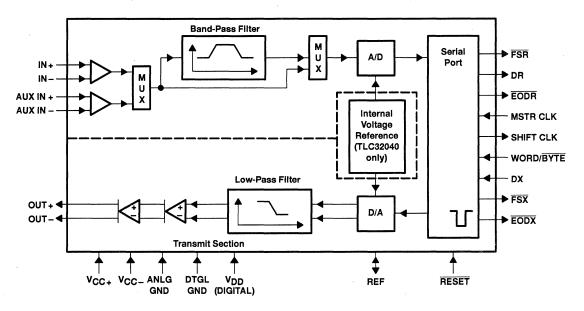

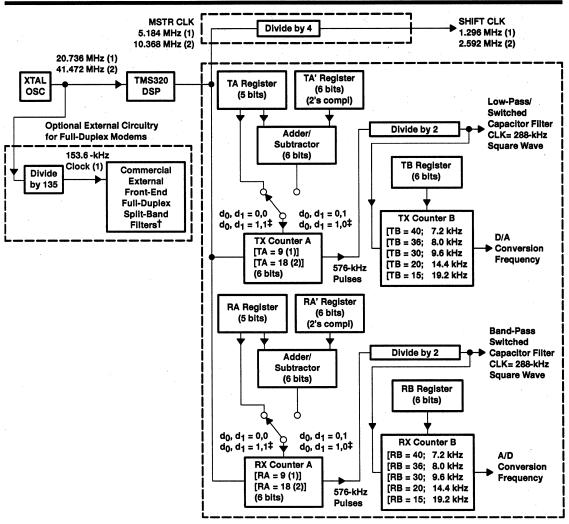

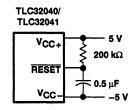

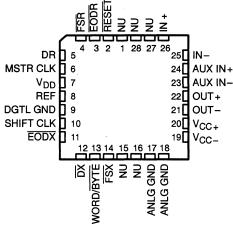

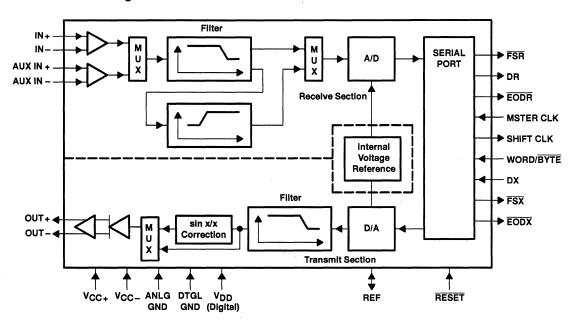

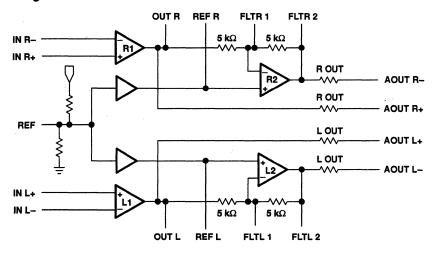

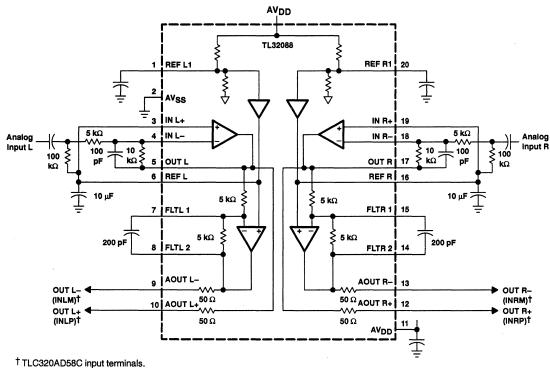

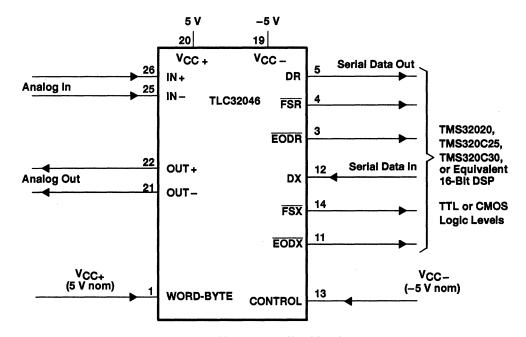

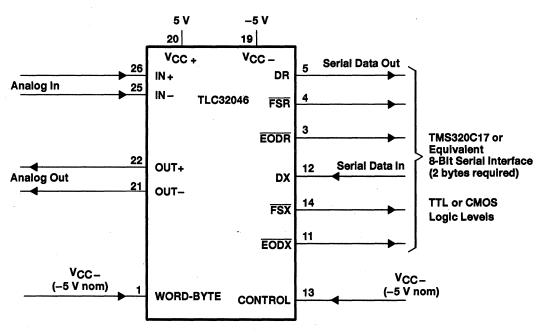

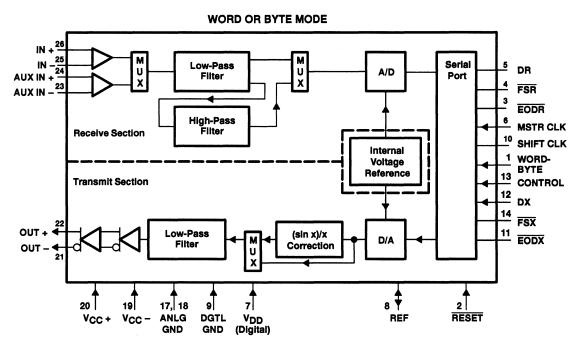

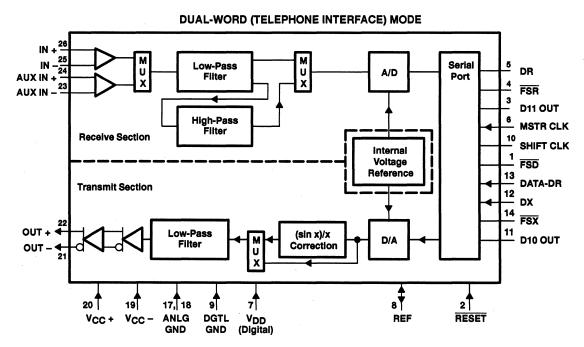

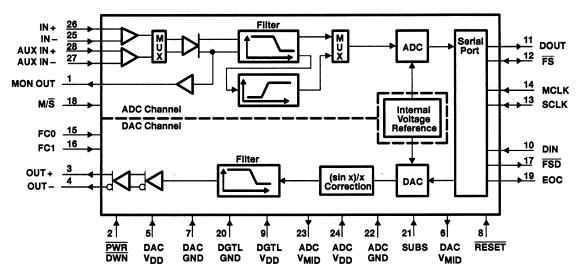

| TLC32040C/TLC32040I/TLC32041C/TLC32041I Analog Interface Circuits                                 | 4-3  |

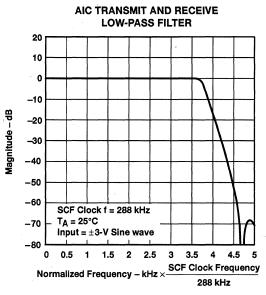

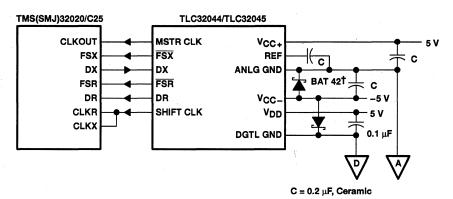

| TLC32044C/TLC32044E/TLC32044I/TLC32044M/TLC32045C/TLC32045I  Voice-Band Analog Interface Circuits | 4–35 |

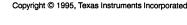

| TLC320AD56C Sigma-Delta Analog Interface Circuit†                                                 | 4-73 |

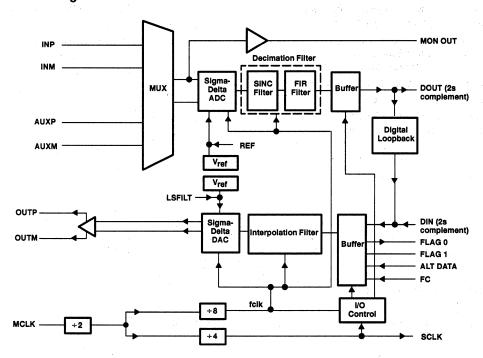

| TLC320AD65C 16-Bit Sigma-Delta Stereo Codec†                                                      | 4–75 |

| Section 5 – Related Special Products                                                      | 5–1  |

|-------------------------------------------------------------------------------------------|------|

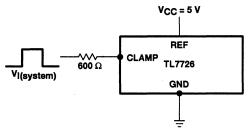

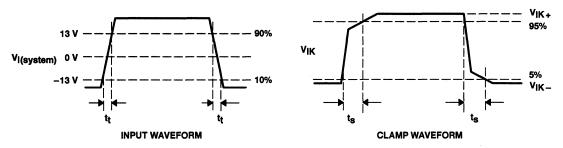

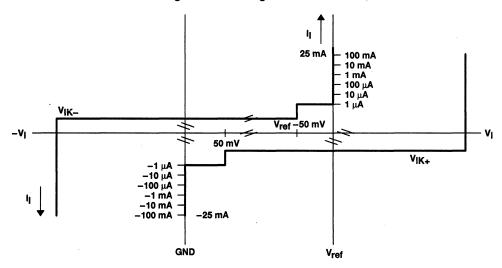

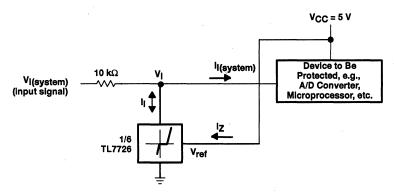

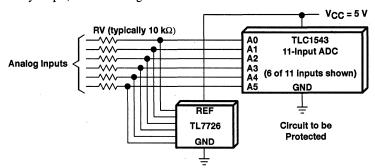

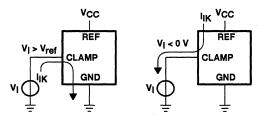

| TL7726C/TL7726I/TL7726Q Hex Clamping Circuits                                             | 5-3  |

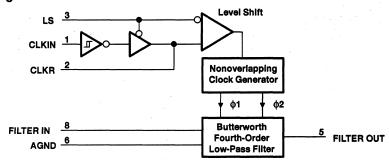

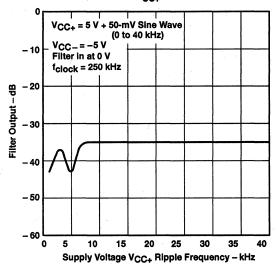

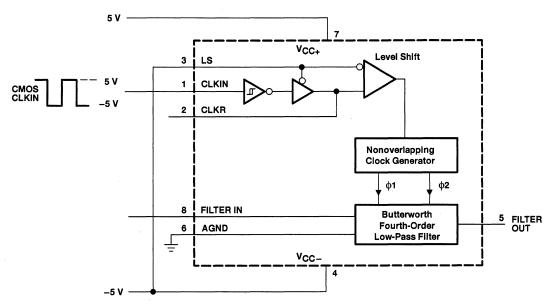

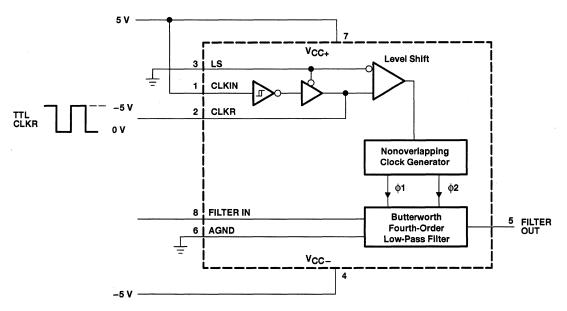

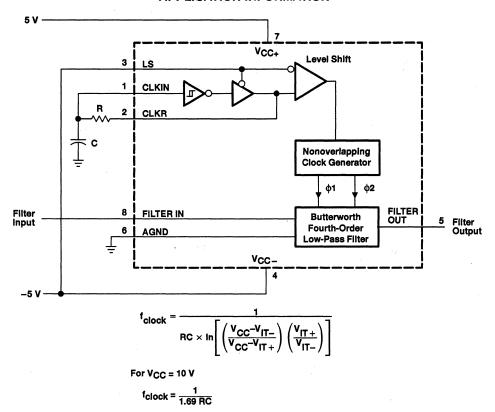

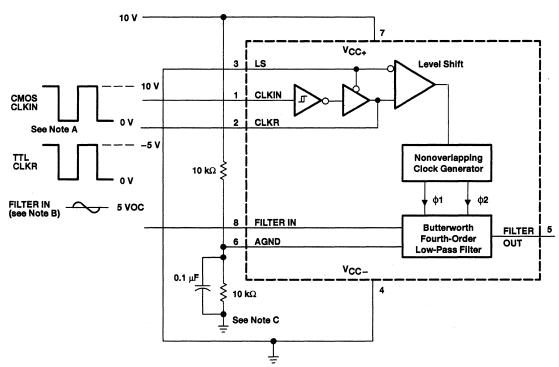

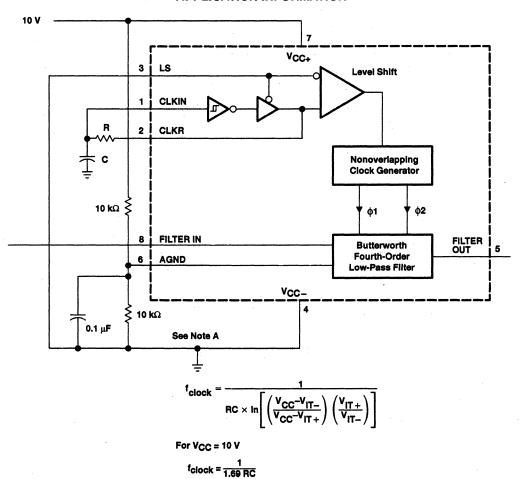

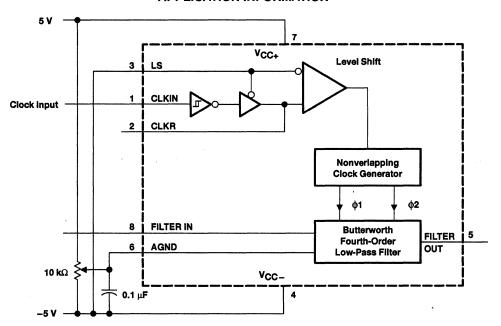

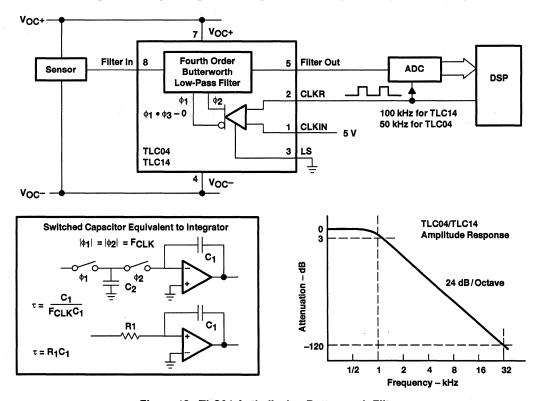

| TLC04/MF4A-50/TLC14/MF4A-100 Butterworth Fourth-Order Low-Pass Switched-Capacitor Filters | 5–7  |

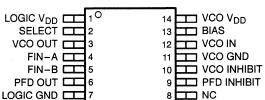

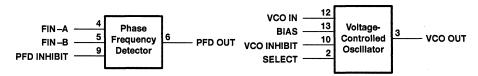

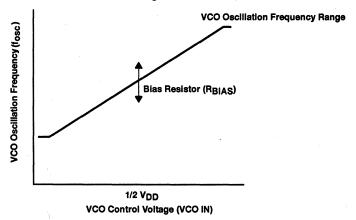

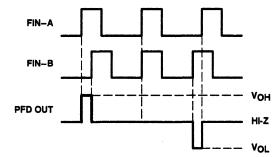

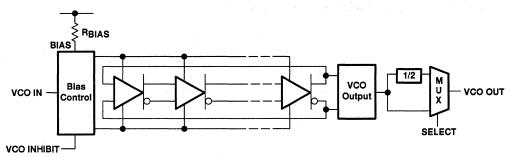

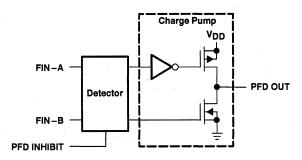

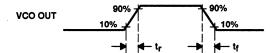

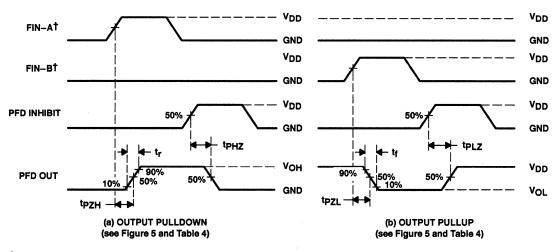

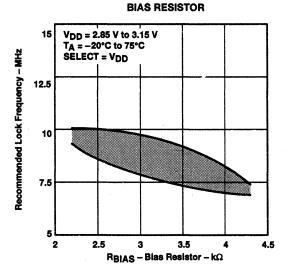

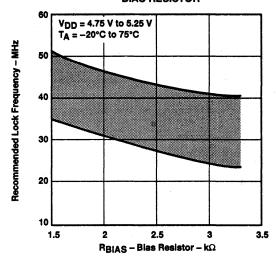

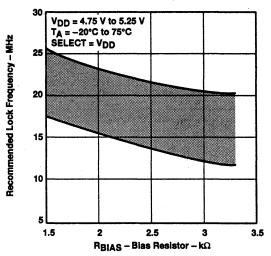

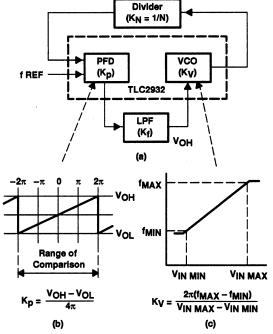

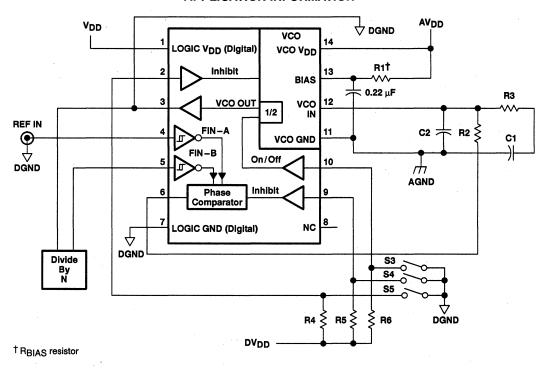

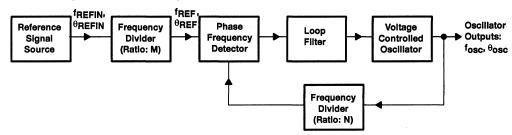

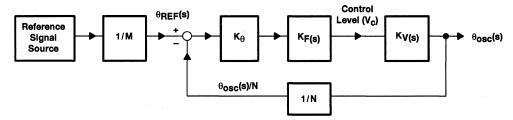

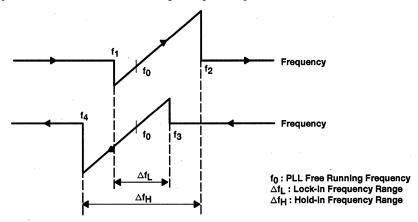

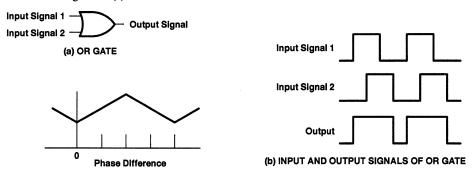

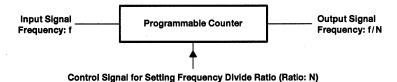

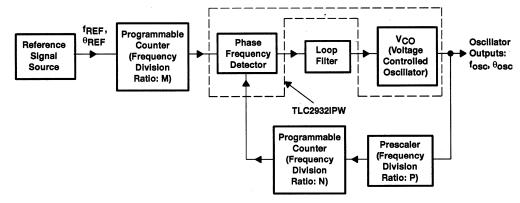

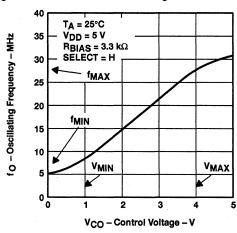

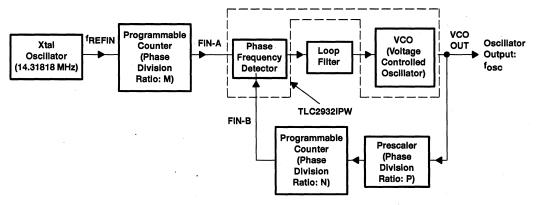

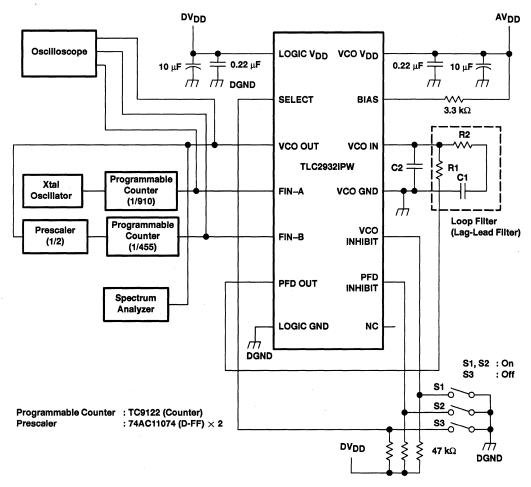

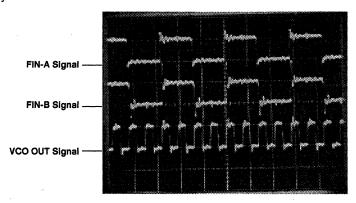

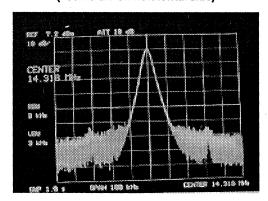

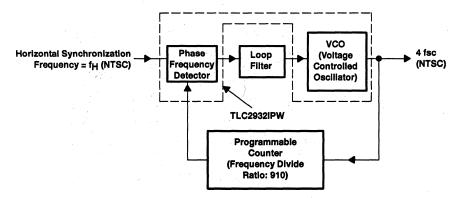

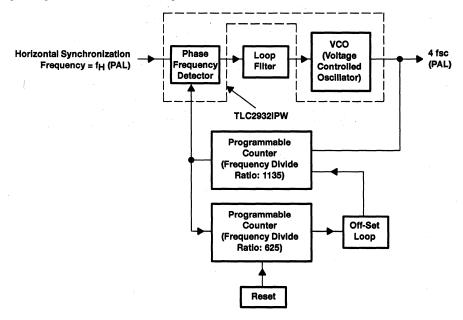

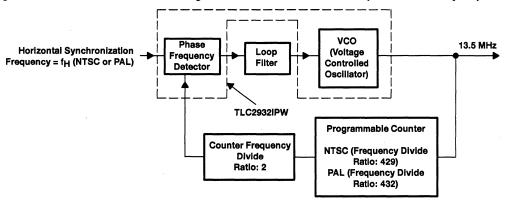

| TLC2932I High-Performance Phase-Locked Loop                                               | 5–19 |

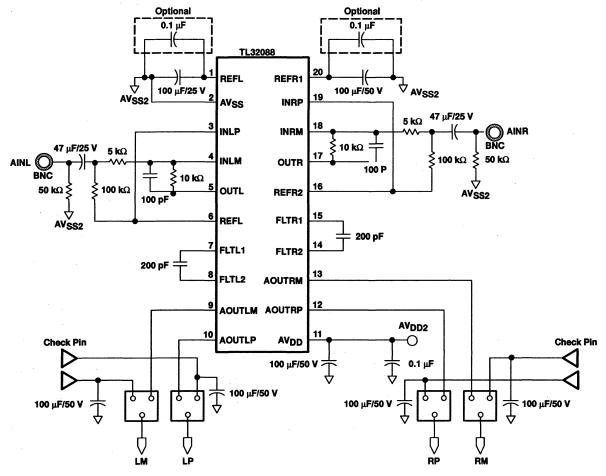

| TL32088 Differential Analog Buffer Amplifier†                                             | 5–41 |

†Product Preview

| Section 6 – Video Interface Palette Extracts            |

|---------------------------------------------------------|

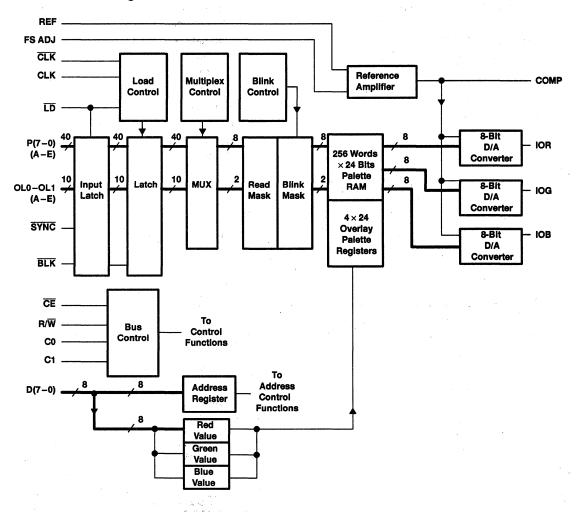

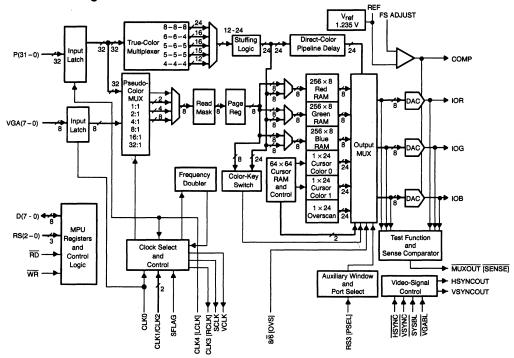

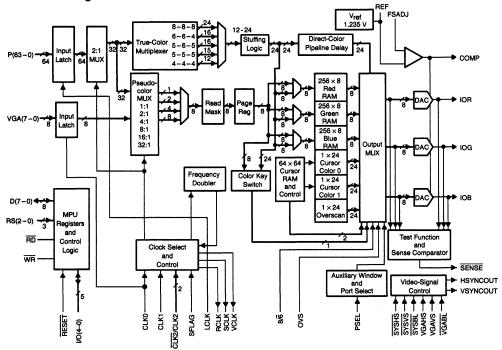

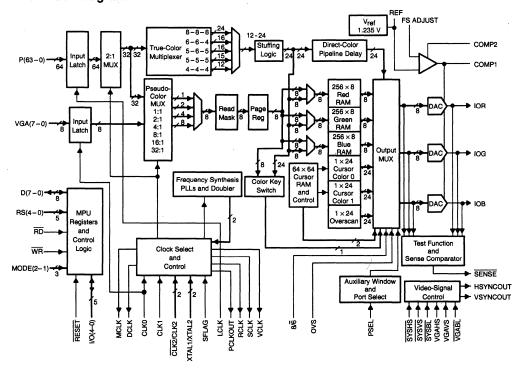

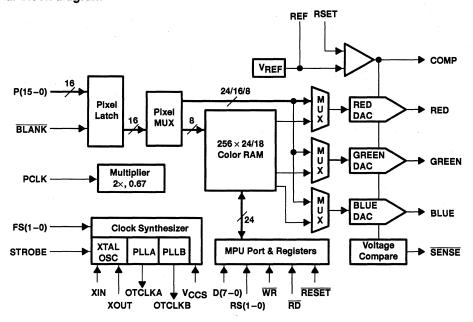

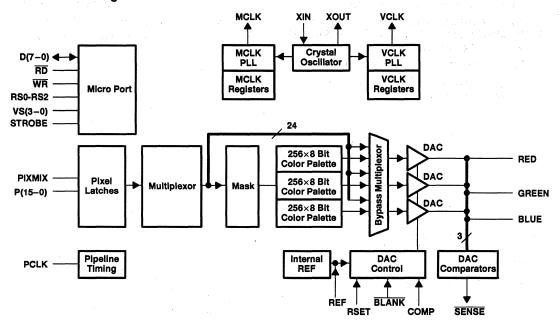

| TLC34058 256 × 24 Color Palette                         |

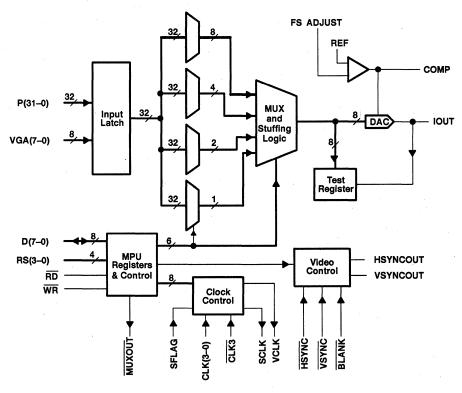

| TLC34074 Video Interface Digital-to-Analog Converter    |

| TLC34075A Video Interface Palette                       |

| TLC34076 Video Interface Palette                        |

| TLC34077 Video Interface Palette                        |

| TVP2002 Clock Driver                                    |

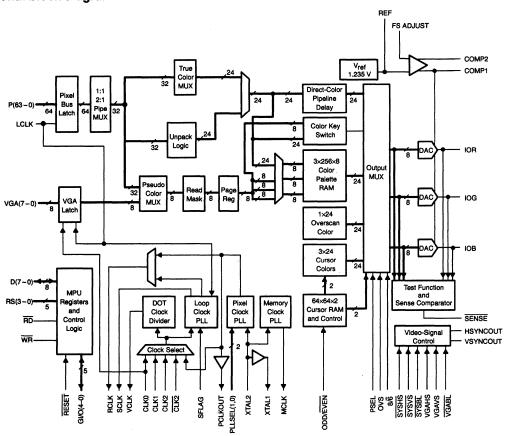

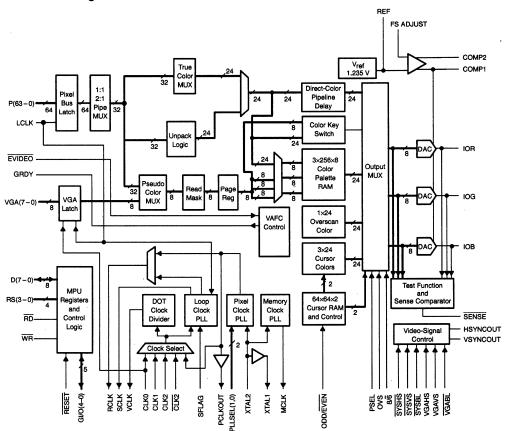

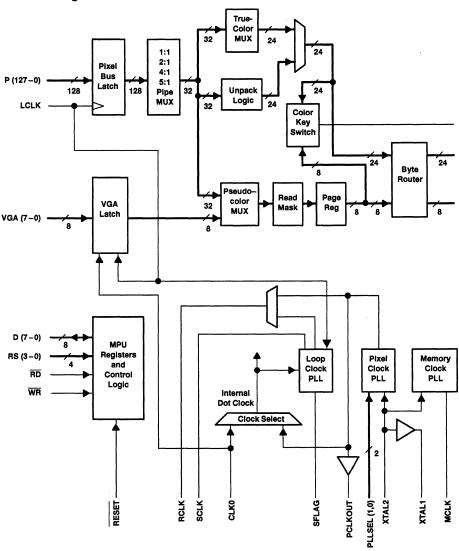

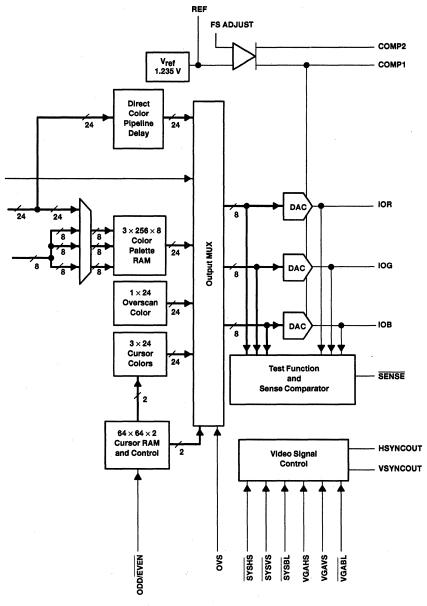

| TVP3010 Video Interface Palette                         |

| TVP3020 Video Interface Palette                         |

| TVP3025 Video Interface Palette                         |

| TVP3026 Video Interface Palette                         |

| TVP3027 Video Interface Palette <sup>†</sup>            |

| TVP3030 Video Interface Palette                         |

| TVP3409 Video Interface Palette True-Color CMOS RAMDAC† |

| TVP3703 Video Interface Palette True-Color CMOS RAMDAC† |

†Product Preview

| Section 7 – Data Manuals                                              | 7–1    |

|-----------------------------------------------------------------------|--------|

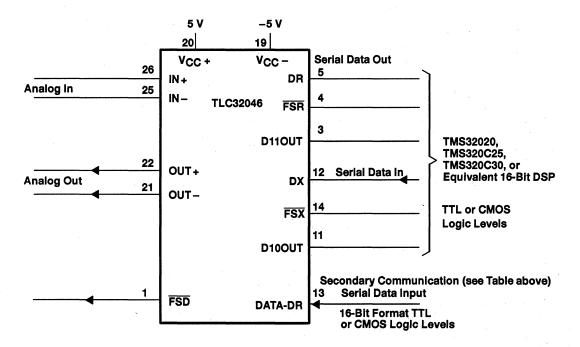

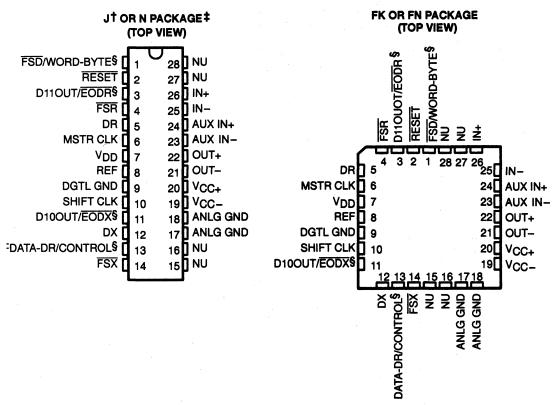

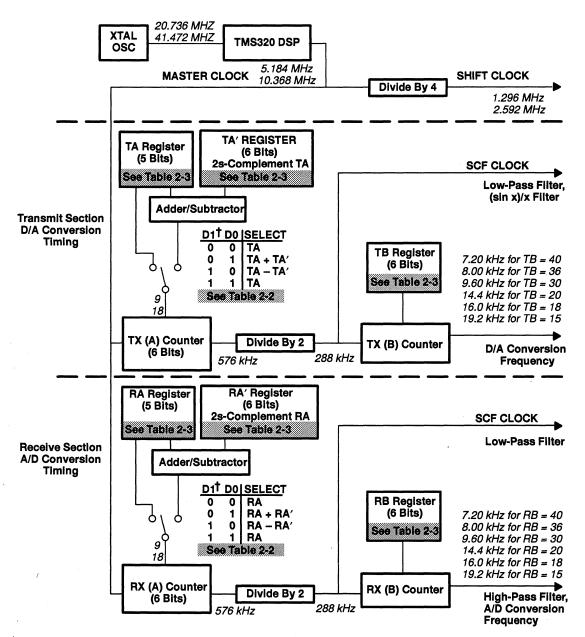

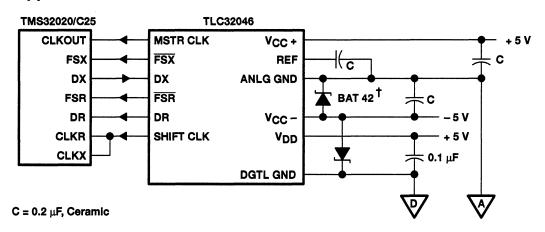

| TLC32046C, TLC32046I, TLC32046M<br>Wide-Band Analog Interface Circuit | 7–3    |

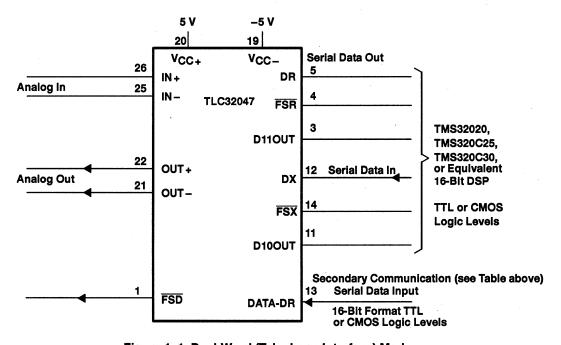

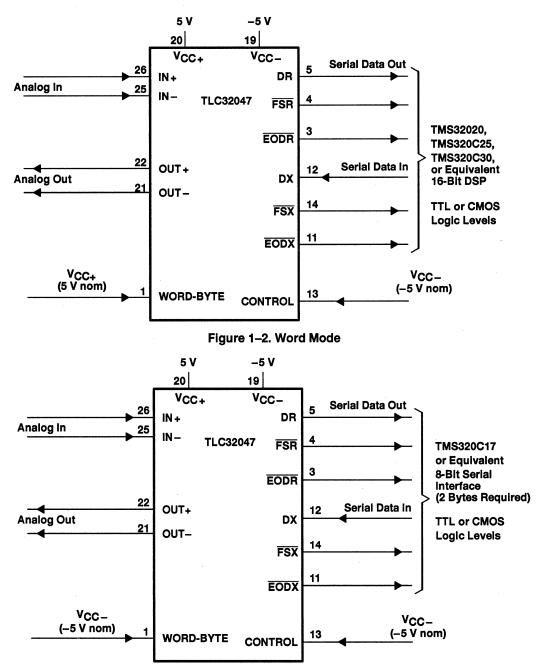

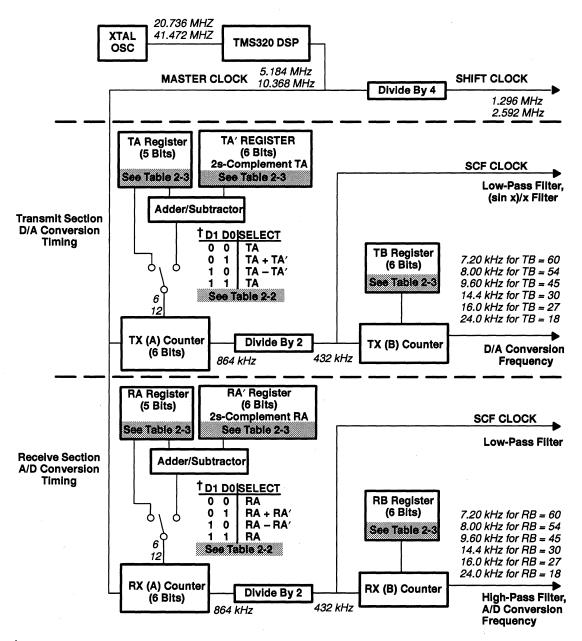

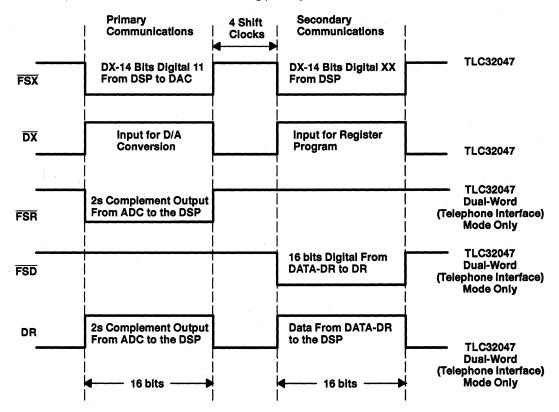

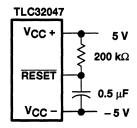

| TLC32047C, TLC32047I Wide-Band Analog Interface Circuit               | 7–59   |

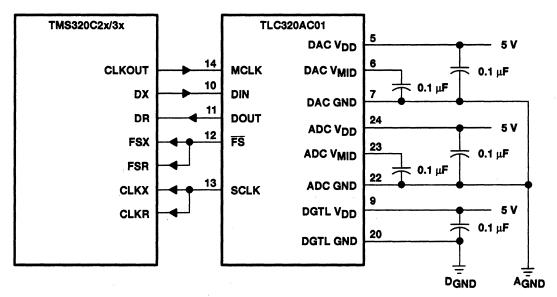

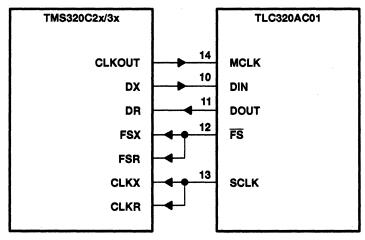

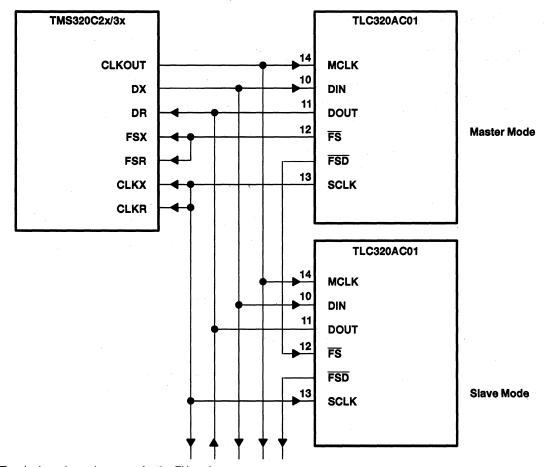

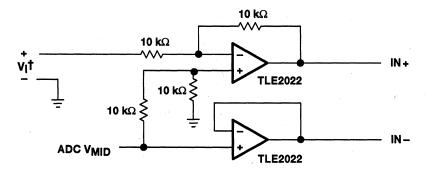

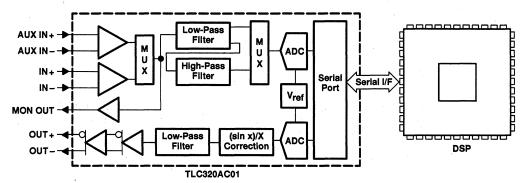

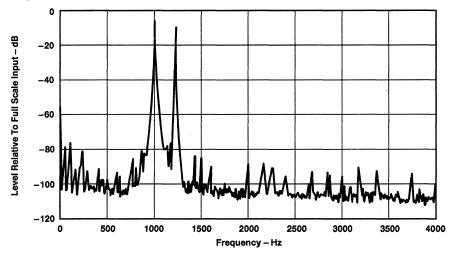

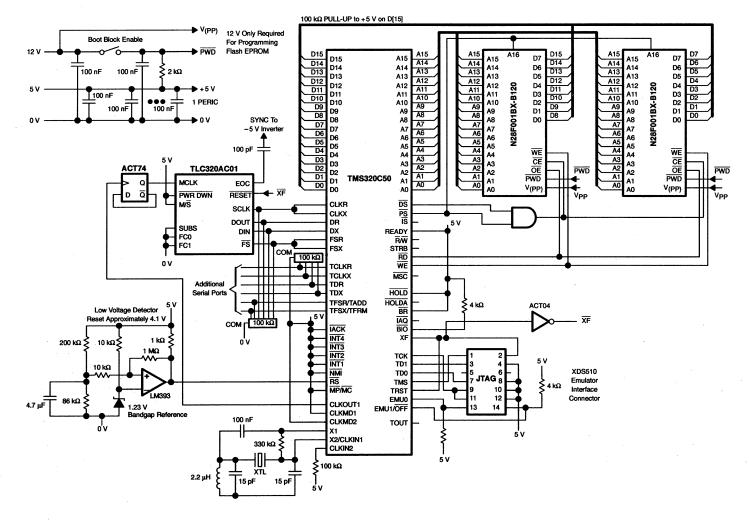

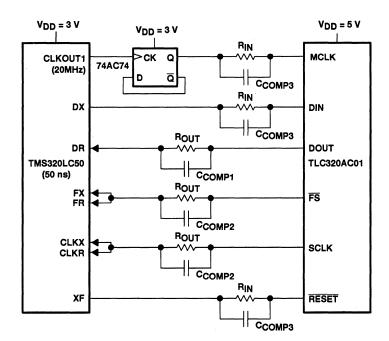

| TLC320AC01C Single-Supply Analog Interface Circuit                    | 7–117  |

| TLC320AC02C/TLC320AC02I Single-Supply Analog Interface Circuit        | 7– 191 |

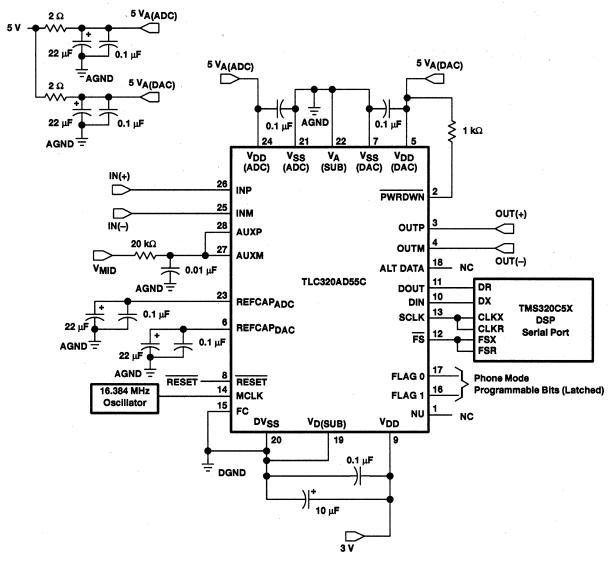

| TLC320AD55C Sigma-Delta Analog Interface Circuit                      | 7–265  |

| TLC320AD57C Sigma-Delta Stereo Analog-to-Digital Converter            | 7–303  |

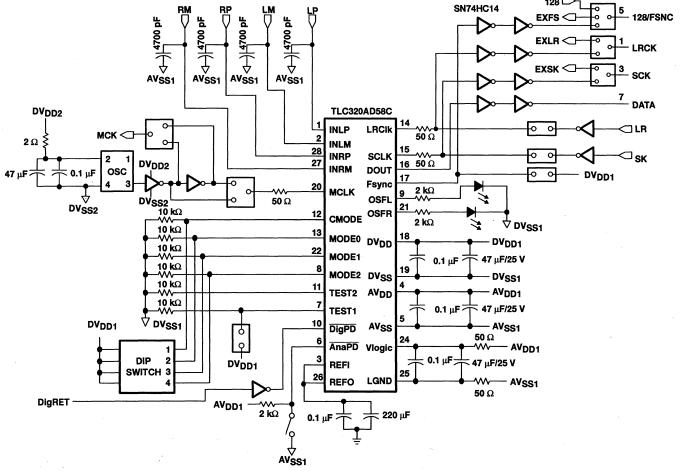

| TLC320AD58C Sigma-Delta Stereo Analog-to-Digital Converter            | 7–323  |

| Section 8 – Application Reports                                                                                 | 8–1   |

|-----------------------------------------------------------------------------------------------------------------|-------|

| TL7726 Hex Clamping Circuit                                                                                     | 8–3   |

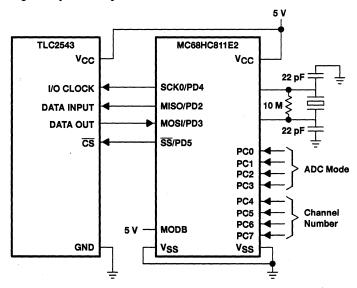

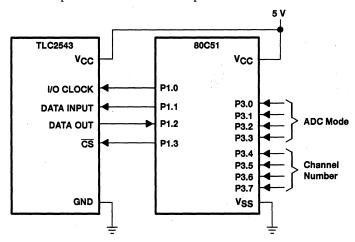

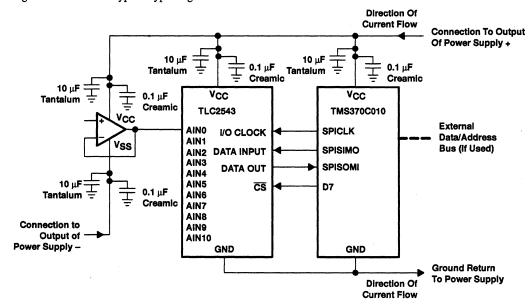

| Microcontroller Based Data Acquisition Using the TLC2543 12-Bit Serial-Out ADC                                  | 8–17  |

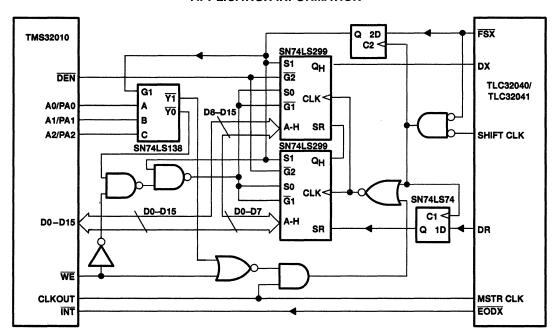

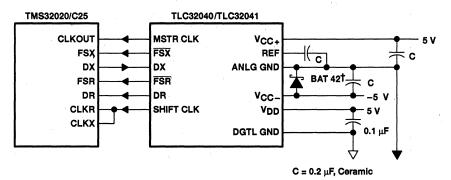

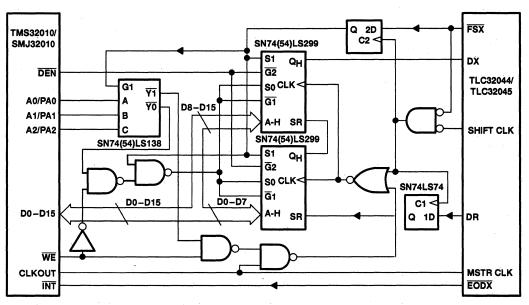

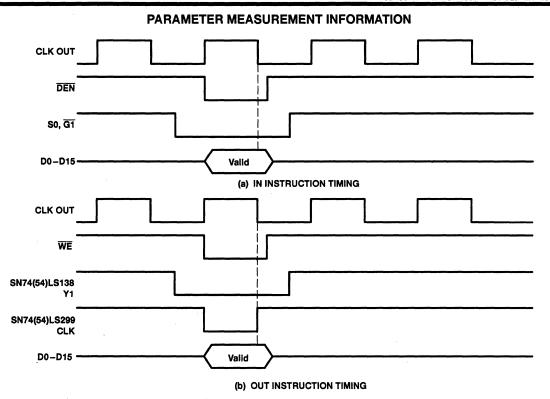

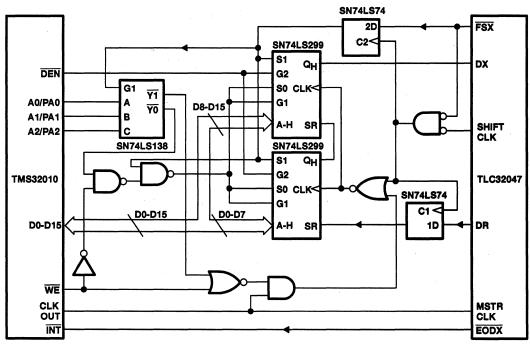

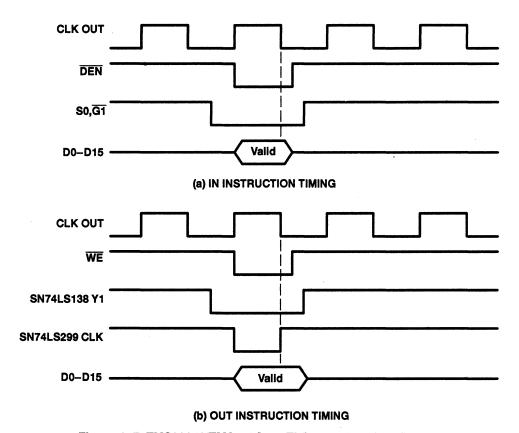

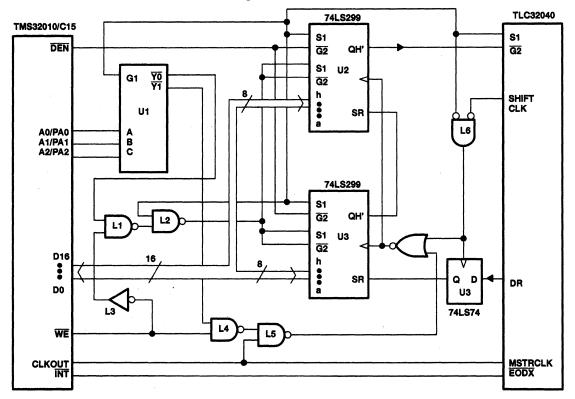

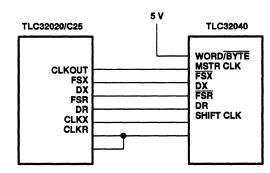

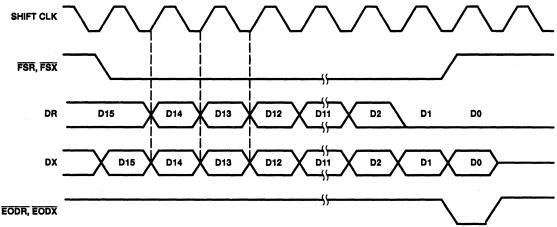

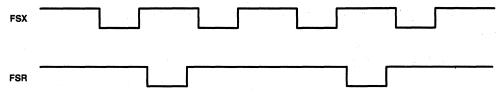

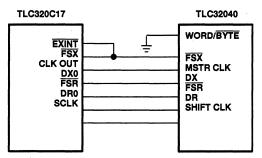

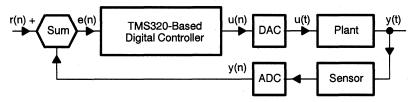

| Interfacing the TLC32040 Family to the TMS320 Family                                                            | 8–43  |

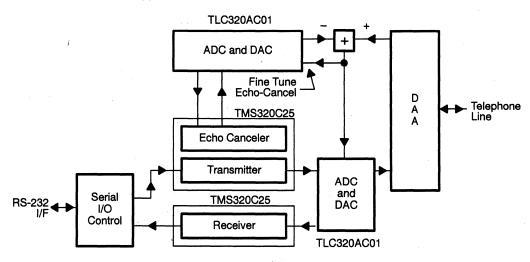

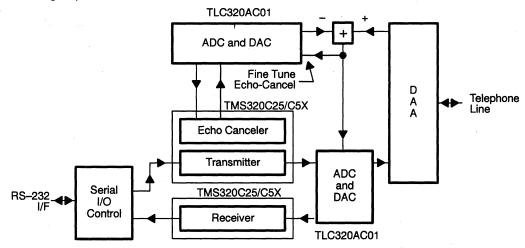

| Designing With the TLC320AC01 Analog Interface for DSPs                                                         | 8–93  |

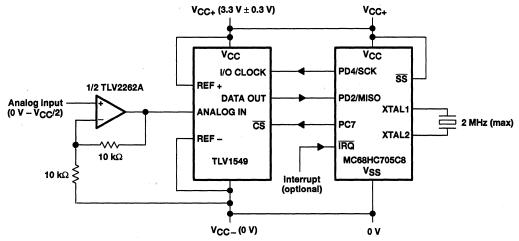

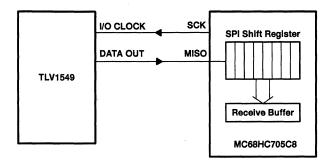

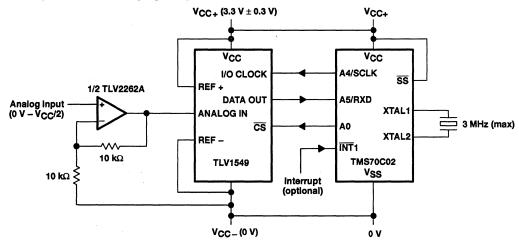

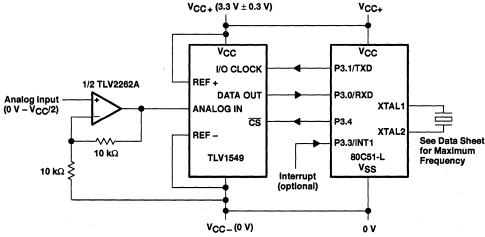

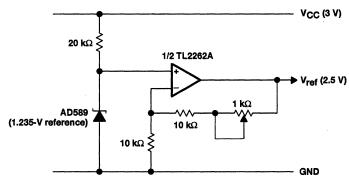

| Interfacing the TLV1549 10-Bit Serial-Out ADC to Popular 3.3-V Microcontrollers                                 |       |

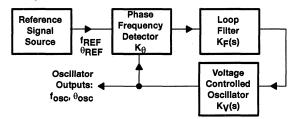

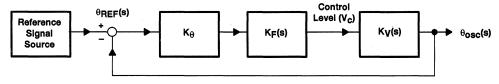

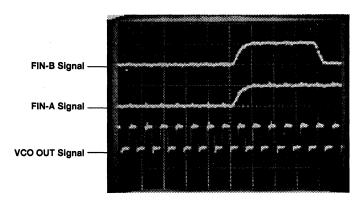

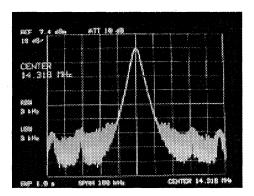

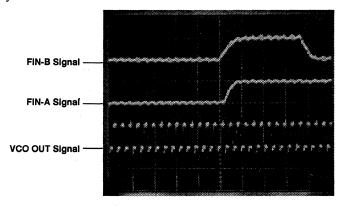

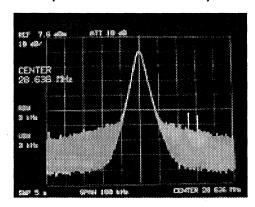

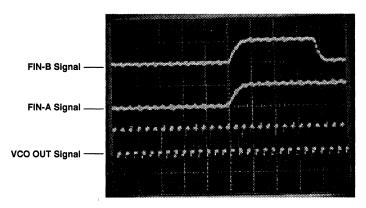

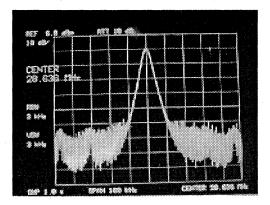

| TLC2932 Phase-Locked-Loop Building Block With Analog Voltage-Controlled Oscillator and Phase Frequency Detector | 8–137 |

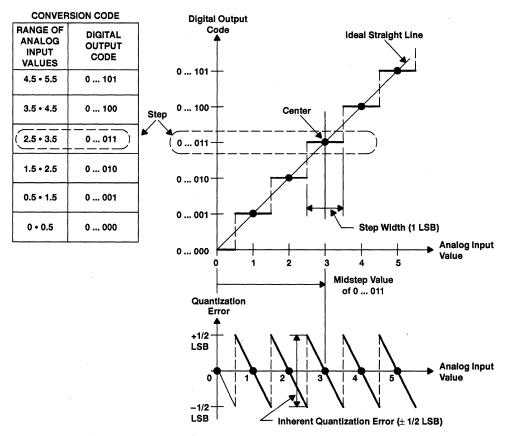

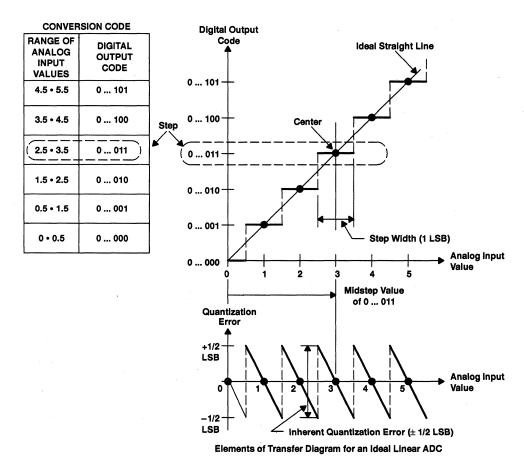

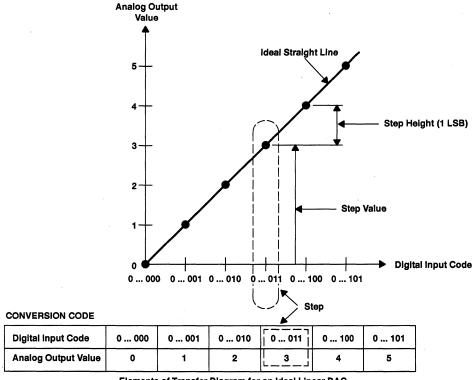

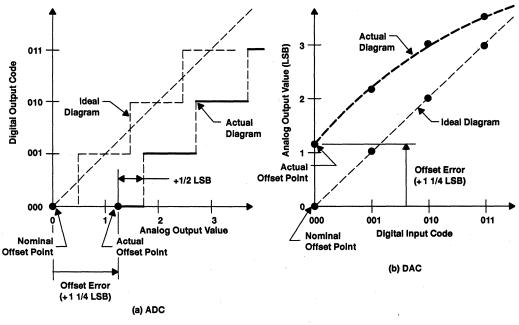

| Understanding Data Converters                                                                                   | 8–179 |

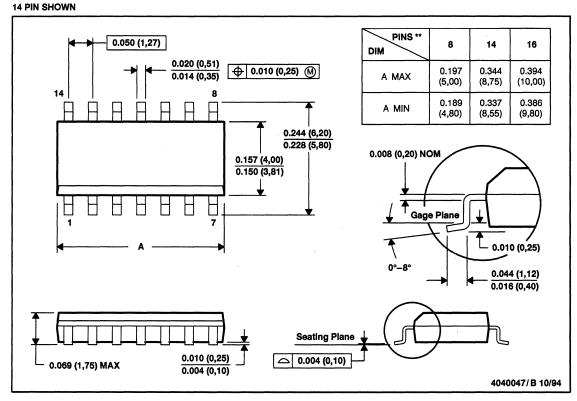

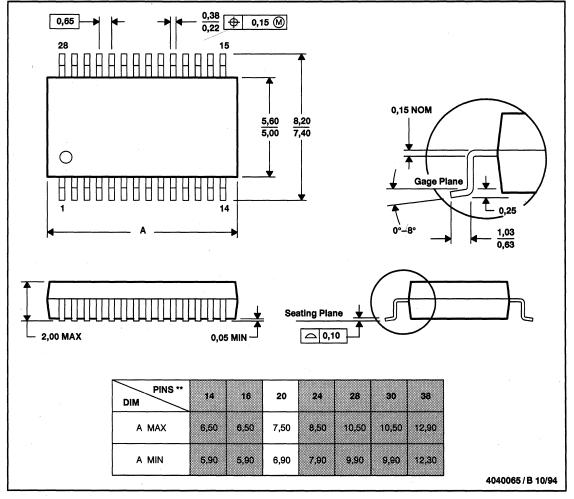

| Section 9 – Mechanical Data                                           | 9–1  |

|-----------------------------------------------------------------------|------|

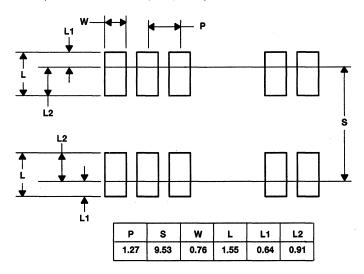

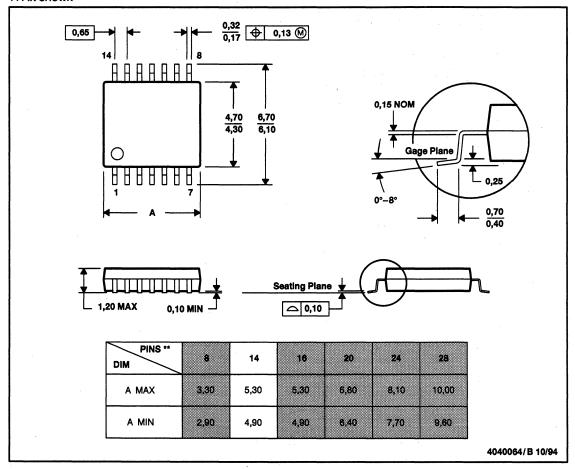

| D 8-, 14-, 16-Pin Plastic Small-Outline Package                       |      |

| DB 14-, 16-, 20-, 24-, 28-, 30-, 38-Pin Plastic Small-Outline Package | 9–4  |

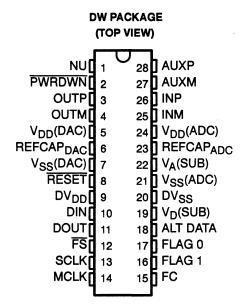

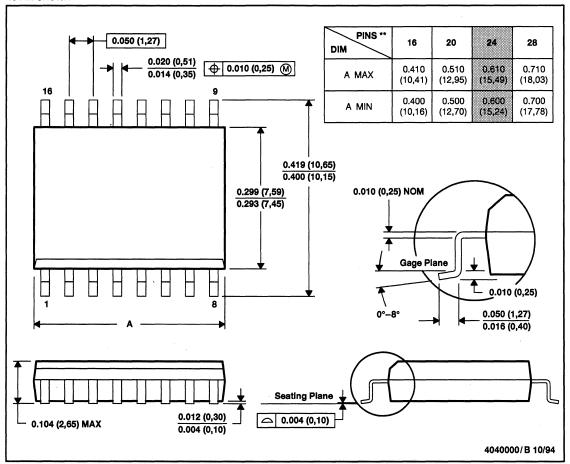

| DW 16-, 20-, 24-, 28-Pin Plastic Small-Outline Package                | 9–5  |

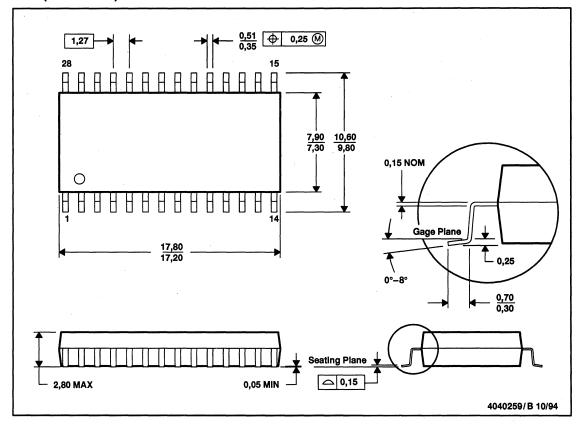

| DWB 28-Pin Plastic Small-Outline Package                              | 9–6  |

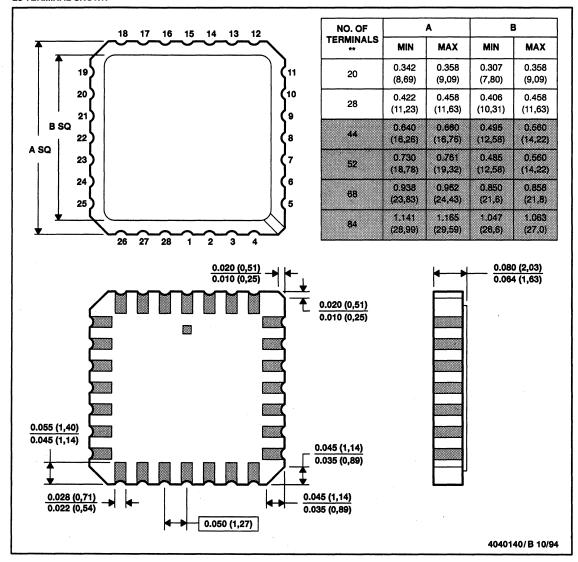

| FK 20-, 28-, 44-, 52-, 68-, 84-Pin Leadless Ceramic Chip Carrier      | 9–7  |

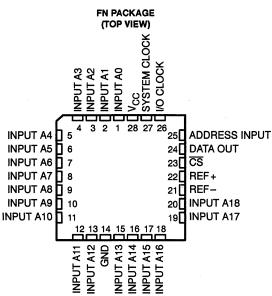

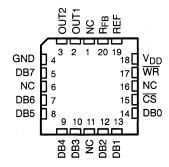

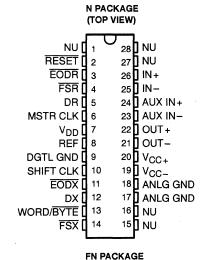

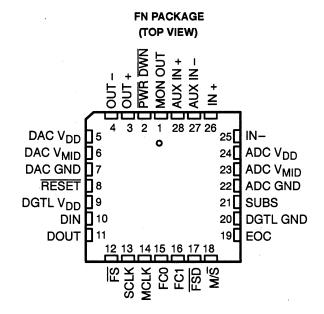

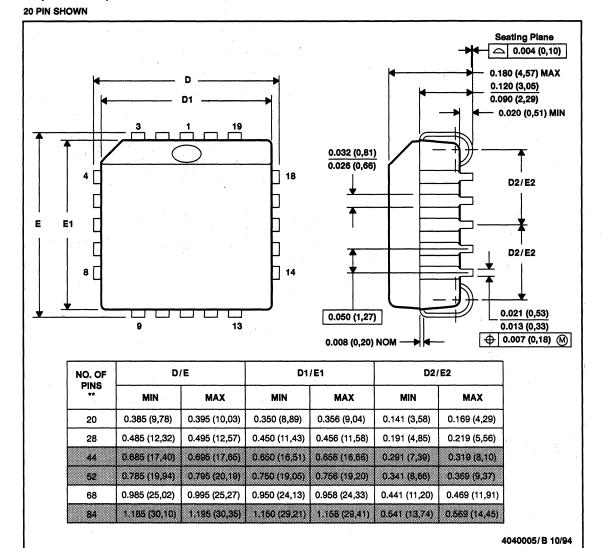

| FN 20-, 28-, 44-, 52-, 68-, 84-Pin Plastic J-Leaded Chip Carrier      | 9–8  |

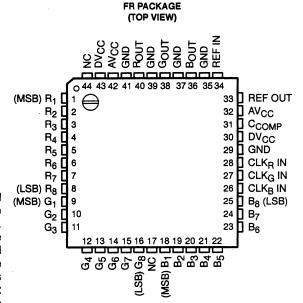

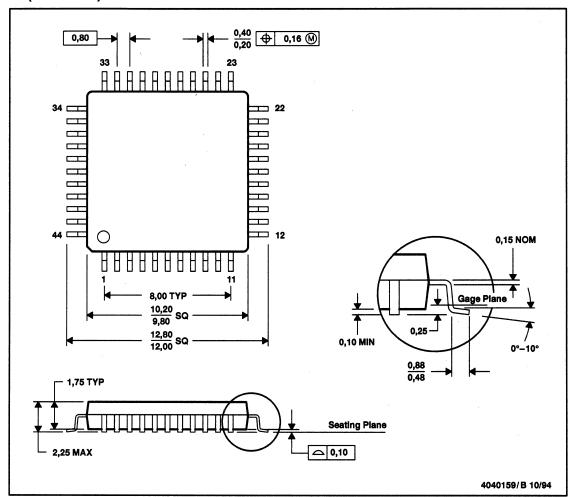

| FR 44-Pin Plastic Quad Flatpack                                       | 9–9  |

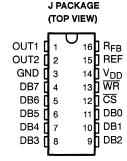

| J 14-, 16-, 18-, 20-, 22-Pin Ceramic Dual-In-Line Package             | 9–10 |

| JG 8-Pin Ceramic Dual-In-Line Package                                 | 9-11 |

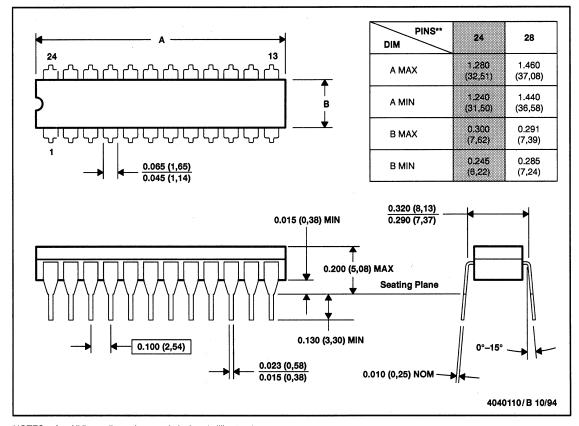

| JT 24-, 28-Pin Ceramic Dual-In-Line Package                           | 9–12 |

| JW 24-Pin Ceramic Dual-In-Line Package                                | 9–13 |

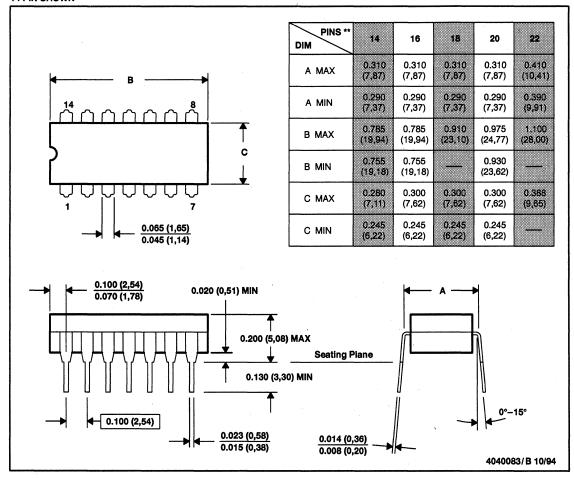

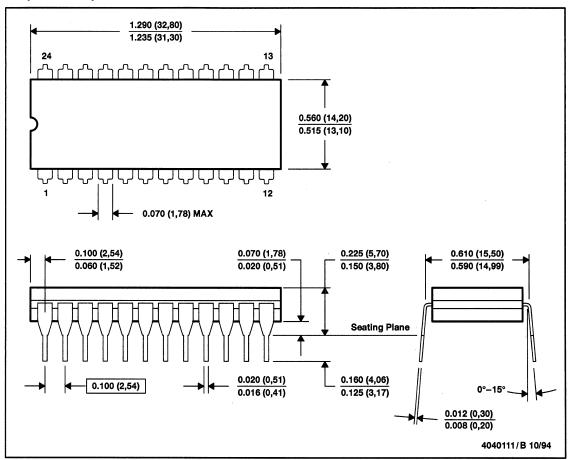

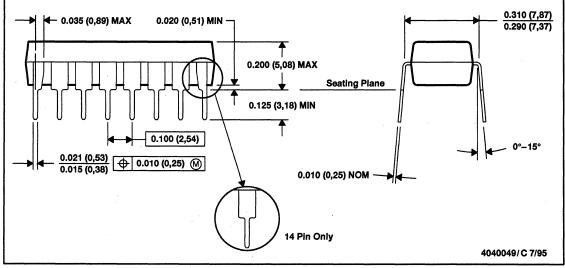

| N 14-, 16-, 18-, 20-Pin Plastic Dual-In-Line Package                  | 9–14 |

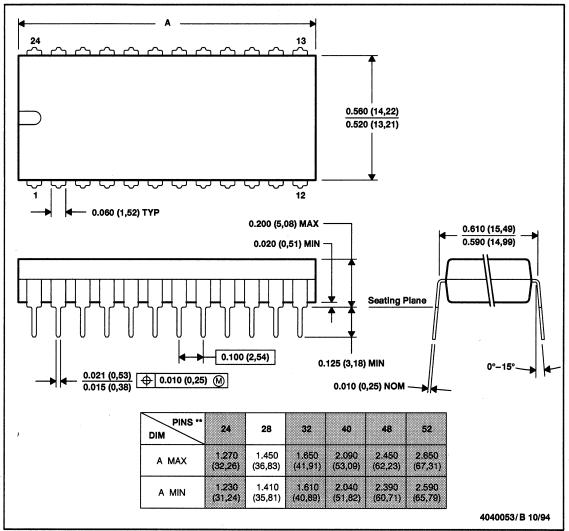

| N 24-, 28-, 32-, 40-, 48-, 52-Pin Plastic Dual-In-Line Package        | 9–15 |

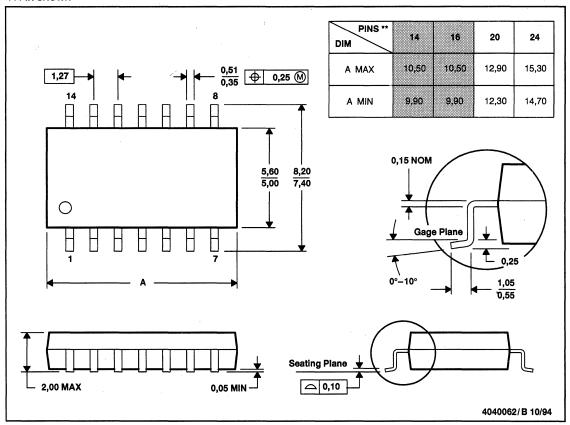

| NS 14-, 16-, 20-, 24-Pin Plastic Small-Outline Package                | 9–16 |

| NW 24-, 28-, 40-, 48-Pin Plastic Dual-In-Line Package                 | 9–17 |

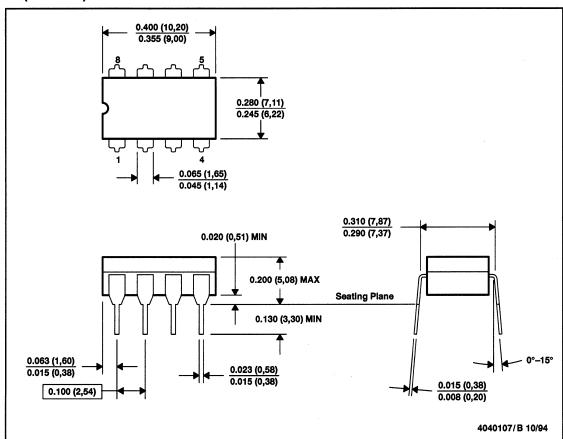

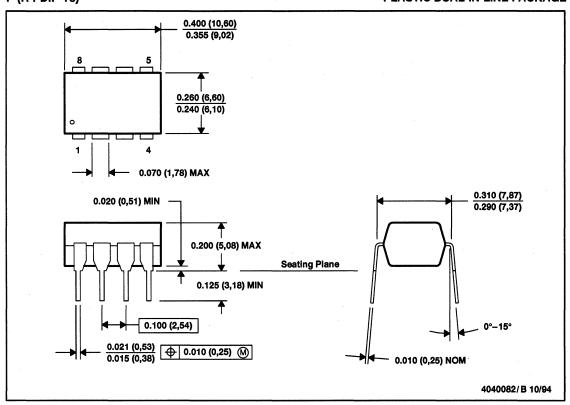

| P 8-Pin Plastic Dual-In-Line Package                                  | 9–18 |

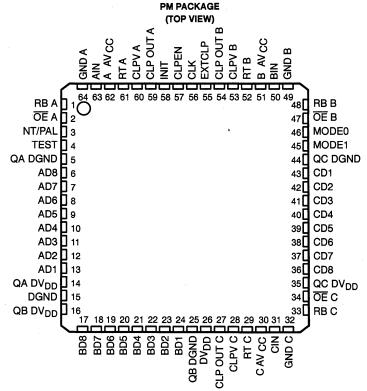

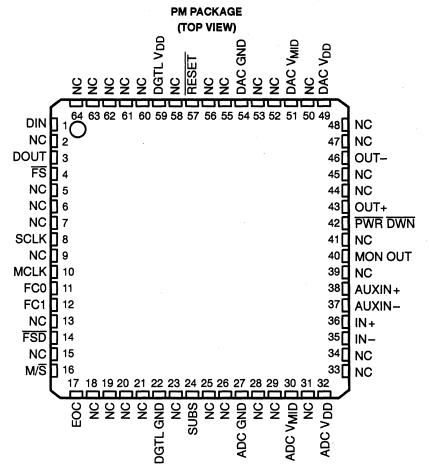

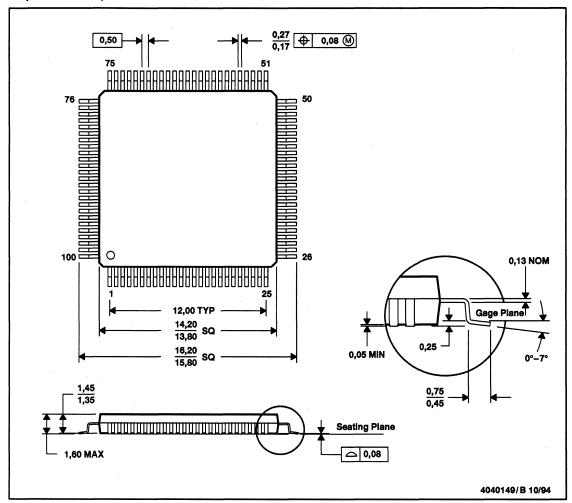

| PM 64-Pin Plastic Quad Flatpack                                       | 9–19 |

| PW 8-, 14-, 16-, 20-, 24-, 28-Pin Plastic Small-Outline Package       | 9–20 |

| PZ 100-Pin Plastic Quad Flatnack                                      |      |

| Section A – Appendix                          |  |  |  |

|-----------------------------------------------|--|--|--|

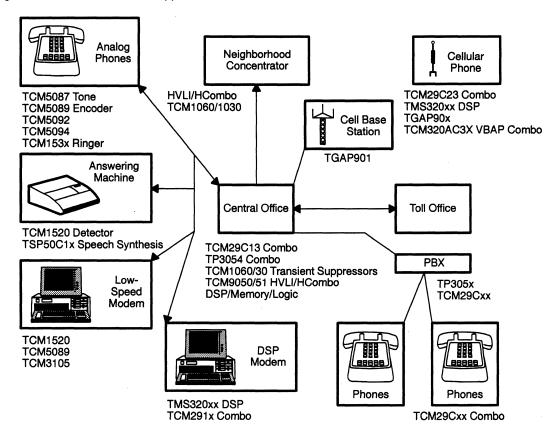

| Analog Interface Peripherals and Applications |  |  |  |

| General Information                 | 1 |

|-------------------------------------|---|

| General Purpose ADCs                | 2 |

| General Purpose DACs                | 3 |

| DSP Analog Interface and Conversion | 4 |

| Special Functions                   | 5 |

| Video Interface Palettes            | 6 |

| Data Manuals                        | 7 |

| Application Reports                 | 8 |

| Mechanical Data                     | 9 |

| Appendix                            | Δ |

|         |                       |     | N TIME (1.9)    | Z P                                    | S. A. A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | REFERENCE S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43. SK.) | N. S. | \$ &                                      | ۶     | CACKAGE THEY        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | STORM SURFACE |

|---------|-----------------------|-----|-----------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------|-------------------------------------------|-------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AESOLI, | 30,000                | SAN | ONLY ON THE     | ************************************** | TO MANUAL TO SERVICE STATE OF THE PARTY OF T | A AND | o Sa     | IJ R                                      | N. S. | O O O | A STAN              | A SECTION AND A |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16/18   | TLC320AD57            |     | 48,<br>44.1, 32 | 2                                      | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | х                                         | х                                         | 200   | DW                  | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Dual sigma-delta. SNR of 97 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | TLC2543               | 10  | 66              | 11                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | х                                         | х                                         | 12    | DW, FN,<br>N        | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Low cost, high resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12      | TLV2543‡              | 10  | 66              | 11                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | x                                         | x                                         | 8     | DW, FN,<br>N        | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3 V version TLC2543                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | TLC1225/1125          | 12  | 83              | 1                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ±5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | X        |                                           |                                           | 85    | N, FN               | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Uni or bipolar with self-calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | TLC1550/1551          | 6   | 164             | 1                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Х        | Х                                         |                                           | 40    | FN, NW              | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DSP front end with 3-state outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |