**CDC** Clock-Distribution Circuits A High-Performance Line of 5-V and 3.3-V Products

# Data Book

10

1994

Advanced System Logic

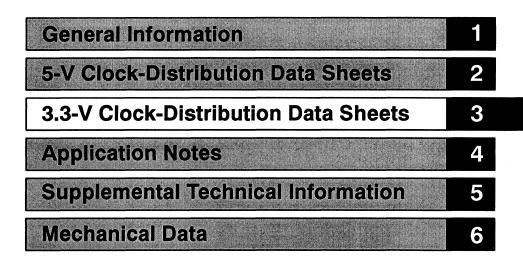

| General Information                  | 1 |

|--------------------------------------|---|

| 5-V Clock-Distribution Data Sheets   | 2 |

| 3.3-V Clock-Distribution Data Sheets | 3 |

| Application Notes                    | 4 |

| Supplemental Technical Information   | 5 |

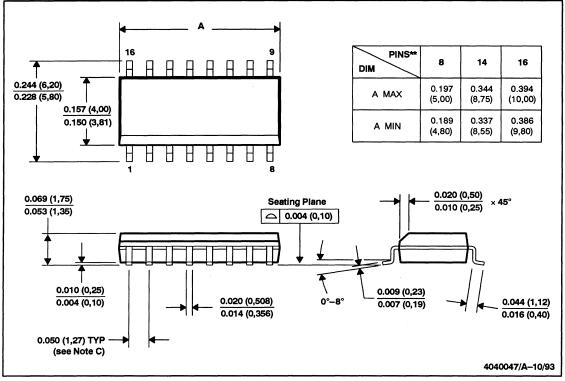

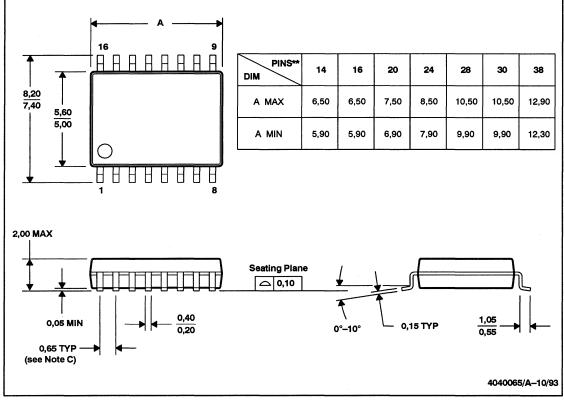

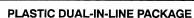

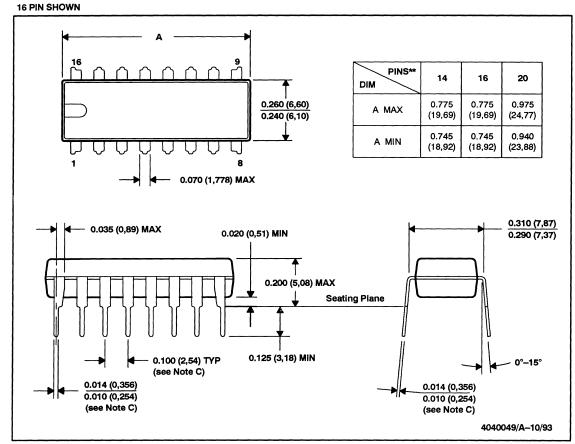

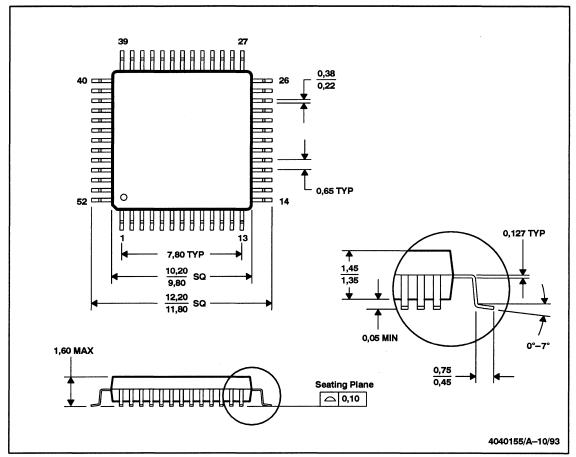

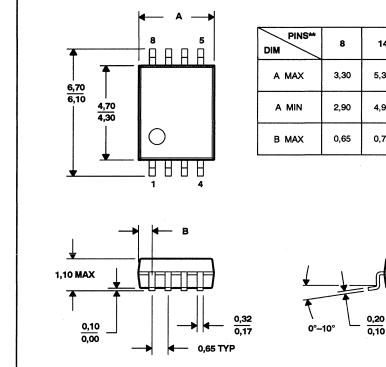

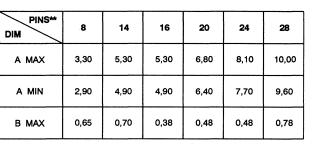

| Mechanical Data                      | 6 |

# CDC Clock-Distribution Circuits Data Book

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1994, Texas Instruments Incorporated

#### INTRODUCTION

Overall system performance is directly related to the quality of the clock distribution network. Virtually all high-performance digital designs subscribe to some form of clock distribution for proper system timing.

The 1994 CDC Clock-Distribution Circuits Data Book provides technical insight into the comprehensive line of clock-distribution circuits (CDC) or *clock drivers* developed by Texas Instruments. CDC products are offered in support of system-clocking layout and design and are targeted for applications in nearly all end equipments. The CDC line of products has been developed in a variety of Texas Instruments silicon processes ranging from Bipolar and CMOS to the latest Advanced BiCMOS technologies. Functionally, the CDC line serves to address a wide spectrum of design requirements with products developed to support 3.3-V and 5-V V<sub>CC</sub> applications. Texas Instruments is developing new buffer, flip-flop, and phase-locked loop (PLL)-based clock-distribution elements to meet today's higher-performance design requirements. With a large and varied portfolio of products already in production and in development, the designer is able to select the optimal clock driver based on a variety of clocking requirements such as:

- Low skew

- Minimal propagation delay

- TTL, CMOS, differential pseudo ECL (PECL) inputs and outputs

- 3.3-V or 5-V V<sub>CC</sub> applications

- Selectable true or complementary output configuration

- Output-enable control

- 1/2x, 1x, and 2x frequency multiplication

- Board-space constraints

The products in this book have been designed to meet the stringent requirements of today's advanced system architectures. Due to the increasing requirements to shrink board area, the products in this book are being developed in a variety of surface-mount packaging options such as shrink small-outline packaging (SSOP) and thin shrink small-outline packaging (TSSOP). Texas Instruments also supports the CDC line with an assortment of analytical modeling tools.

The latest high-speed microprocessors, buses, and memories are examples of critical-system components that are spurring a need for higher-performance clock distribution. Texas Instruments is working to provide optimal clock-driver solutions to meet these needs.

Complete technical data for any TI Advanced System Logic product is available from the nearest TI field sales office, local authorized TI distributor, or directly by calling the Advanced System Logic hotline at (214) 997-5202.

#### PRODUCT STAGE STATEMENTS

*Product stage statements* are used on Texas Instruments data sheets to indicate the development stage(s) of the product(s) specified in the data sheets.

If all products specified in a data sheet are at the same development stage, the appropriate statement from the following list is placed in the lower left corner of the first page of the data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

If not all products specified in a data sheet are at the PRODUCTION DATA stage, then the first statement below is placed in the lower left corner of the first page of the data sheet. Subsequent pages of the data sheet containing PRODUCT PREVIEW information or ADVANCE INFORMATION are then marked in the lower left-hand corner with the appropriate statement given below:

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

# Contents

|                     | Page |

|---------------------|------|

| Alphanumeric Index  | 1–3  |

| Glossary            | 1–5  |

| Thermal Information | 1–9  |

| Functional Index    | 1–11 |

| DEVICE                             | PAGE |

|------------------------------------|------|

| 5-V Clock-Distribution Data Sheets |      |

| CDC204, CDC204–7                   | 2-3  |

| CDC208, CDC208–7                   | 2–9  |

| CDC209, CDC209-7                   | 2-15 |

| CDC303                             | 2–23 |

| CDC304                             | 2–29 |

| CDC305                             | 2–35 |

| CDC328                             | 2-41 |

| CDC328A                            | 2–47 |

| CDC329A                            | 2-53 |

| CDC330                             | 259  |

| CDC337                             | 2–65 |

| CDC339                             | 2-71 |

| CDC340                             | 2-77 |

| CDC341                             | 283  |

| CDC391                             | 289  |

| CDC392                             | 295  |

| DEVICE                               | PAGE |  |

|--------------------------------------|------|--|

| 3.3-V Clock-Distribution Data Sheets |      |  |

| CDC111                               | 3–3  |  |

| CDC112                               | 3-9  |  |

| CDC203                               | 315  |  |

| CDC351                               | 3–19 |  |

| CDC536                               | 325  |  |

| CDC586                               | 3–35 |  |

| CDC2351                              | 3-45 |  |

| CDC2536                              | 3–51 |  |

| CDC2582                              | 361  |  |

| CDC2586                              | 3-71 |  |

. 1-4

### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

#### **OPERATING CONDITIONS AND CHARACTERISTICS (IN SEQUENCE BY LETTER SYMBOLS)**

| Ci                   | Input capacitance                                                                                                                                                                                                                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | The internal capacitance at an input of the device                                                                                                                                                                                                                                                    |

| Co                   | Output capacitance                                                                                                                                                                                                                                                                                    |

|                      | The internal capacitance at an output of the device                                                                                                                                                                                                                                                   |

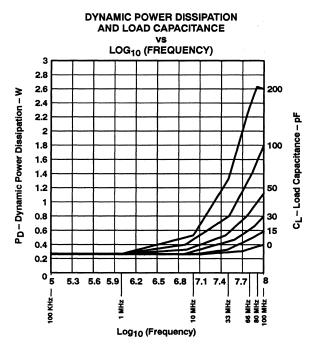

| C <sub>pd</sub>      | Power dissipation capacitance                                                                                                                                                                                                                                                                         |

|                      | Used to determine the no-load dynamic power dissipation per logic function (see individual circuit pages):<br>$P_D = C_{pd} V_{CC}^2 f + I_{CC} V_{CC}$ .                                                                                                                                             |

| f <sub>max</sub>     | Maximum clock frequency                                                                                                                                                                                                                                                                               |

|                      | The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification. |

| lcc                  | Supply current                                                                                                                                                                                                                                                                                        |

|                      | The current into* the $V_{CC}$ supply terminal of an integrated circuit                                                                                                                                                                                                                               |

| ∆lcc                 | Supply current change                                                                                                                                                                                                                                                                                 |

|                      | The increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V or $V_{CC}$                                                                                                                                                                          |

| ICEX                 | Output high leakage current                                                                                                                                                                                                                                                                           |

|                      | The maximum leakage current into the collector of the pulldown output transistor when the output is high and the output forcing condition $V_0 = 5.5 \text{ V}$ .                                                                                                                                     |

| I <sub>l(hold)</sub> | Input hold current                                                                                                                                                                                                                                                                                    |

|                      | Input current that holds the input at the previous state when the driving device goes to a high-impedance state                                                                                                                                                                                       |

| IIH                  | High-level input current                                                                                                                                                                                                                                                                              |

|                      | The current into* an input when a high-level voltage is applied to that input                                                                                                                                                                                                                         |

| կլ                   | Low-level input current                                                                                                                                                                                                                                                                               |

|                      | The current into* an input when a low-level voltage is applied to that input                                                                                                                                                                                                                          |

| l <sub>off</sub>     | Input/output power-off leakage current                                                                                                                                                                                                                                                                |

|                      | The maximum leakage current into/out of the input/output transistors when forcing the input/output to 4.5 V and V_{CC} = 0 V                                                                                                                                                                          |

| юн                   | High-level output current                                                                                                                                                                                                                                                                             |

|                      | The current into* an output with input conditions applied that, according to the product specification, will establish a high level at the output.                                                                                                                                                    |

| IOL                  | Low-level output current                                                                                                                                                                                                                                                                              |

|                      | The current into* an output with input conditions applied that, according to the product specification, will establish a low level at the output.                                                                                                                                                     |

\*Current out of a terminal is given as a negative value.

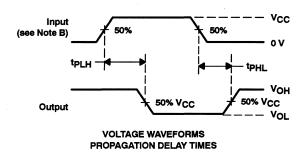

#### Off-state (high-impedance-state) output current (of a 3-state output) loz The current flowing into\* an output having 3-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output. Access time ta The time interval between the application of a specified input pulse and the availability of valid signals at an output Disable time (of a 3-state or open-collector output) t<sub>dis</sub> The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from either of the defined active levels (high or low) to a high-impedance (off) state. NOTE: For 3-state outputs, t<sub>dis</sub> = t<sub>PHZ</sub> or t<sub>PLZ</sub>. Open-collector outputs will change only if they are low at the time of disabling so t<sub>dis</sub> = t<sub>Pl H</sub>. ten Enable time (of a 3-state or open-collector output) The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from a high-impedance (off) state to either of the defined active levels (high or low). NOTE: In the case of memories, this is the access time from an enable input (e.g., OE). For 3-state outputs, ten = tp7H or tp7I. Open-collector outputs will change only if they are responding to data that would cause the output to go low so, for them $t_{en} = t_{PHI}$ . Hold time th The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal. NOTES: 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is to be expected. 2. The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is to be expected. Jitter tiitter Dispersion of a time parameter of the pulse waveforms in a pulse train with respect to a reference time. interval, or duration. Unless otherwise specified by a mathematical adjective, peak-to-peak jitter is assumed. tjitter(RMS) RMS Jitter The root mean square jitter, one sixth of the maximum peak-to-peak jitter Propagation delay time tpd The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level. (tod = tPHL or tPLH) Propagation delay time, high-to-low level output **t**PHL The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level Disable time (of a 3-state output) from high level t<sub>PHZ</sub> The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined high level to a high-impedance (off) state

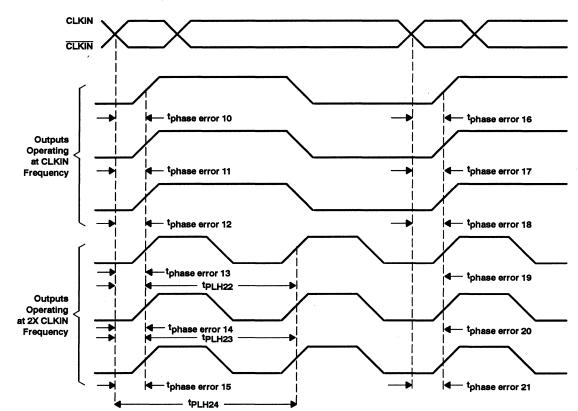

#### t<sub>PLH</sub> Propagation delay time, low-to-high level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level

#### t<sub>PLZ</sub> Disable time (of a 3-state output) from low level

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined low level to a high-impedance (off) state

#### t<sub>PZH</sub> Enable time (of a 3-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to the defined high level.

#### tpzL Enable time (of a 3-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to the defined low level.

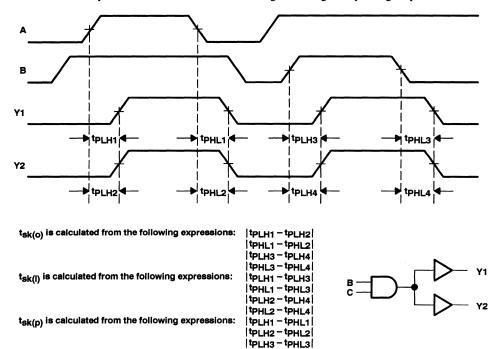

#### tsk(i) Input skew

The difference between any two propagation delay times that originate at different inputs and terminate at a single output. Input skew describes the ability of a device to manipulate (stretch, shrink, or chop) a clock signal. This is typically accomplished with a multiple-input gate wherein one of the inputs acts as a controlling signal to pass the clock through.  $t_{sk(l)}$  describes the ability of the gate to shape the pulse to the same duration regardless of the input used as the controlling input.

#### t<sub>sk(l)</sub> Limit skew

The difference between 1) the greater of the maximum specified values of  $t_{PLH}$  and  $t_{PHL}$  and 2) the lesser of the minimum specified values of  $t_{PLH}$  and  $t_{PHL}$ . Limit skew is not directly observed on a device but rather is calculated from the data sheet limits for  $t_{PLH}$  and  $t_{PHL}$ .  $t_{sk(l)}$  quantifies for the designer how much variation in propagation delay time will be induced by operation over the entire ranges of supply voltage, temperature, output load, and other specified operating conditions. Specified as such,  $t_{sk(i)}$  also accounts for process variation. In fact, all other skew specifications [ $t_{sk(o)}, t_{sk(i)}, t_{sk(p)}, and t_{sk(pr)}$ ] are subsets of  $t_{sk(i)}$ ; they will never be greater than  $t_{sk(i)}$ .

#### t<sub>sk(o)</sub> Output Skew

The difference between any two propagation delay times when a single switching input or multiple inputs switching simultaneously cause multiple outputs to switch, as observed across all switching outputs. This parameter is used to describe the fanout capability of a clock driver and is of concern when making decisions on clock buffering and distribution networks.

#### t<sub>sk(p)</sub> Pulse Skew

The difference between propagation delay times  $t_{PHL}$  and  $t_{PLH}$  when a single switching input causes one or more outputs to switch.  $t_{sk(p)}$  quantifies the duty cycle characteristic of a clock driver. Certain applications require a fixed duty cycle for proper operation. As an example, the CLK2 input of an MC68020 processor operating at 40 MHz requires a duty cycle of 50 ± 5%.  $t_{sk(p)}$  is a measure of a clock driver's ability to supply such a precisely controlled pulse.

#### t<sub>sk(pr)</sub> Process Skew

The difference between identically specified propagation delay times on any two like ICs operating under identical conditions.  $t_{sk(pr)}$  quantifies the skew induced by variations in the IC manufacturing process but not by variations in supply voltage, operating temperature, output loading, input edge rate, input frequency, etc. Process skew is commonly specified and production tested under fixed conditions (e.g.,  $V_{CC} = 5.25 \text{ V}$ ,  $T_A = 70^{\circ}$ C,  $C_L = 50 \text{ pF}$ , all inputs switching simultaneously).

#### t<sub>su</sub> Setup time

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

2. The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

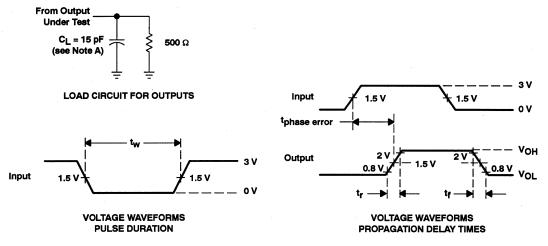

#### tw Pulse duration (width)

The time interval between specified reference points on the leading and trailing edges of the pulse waveform.

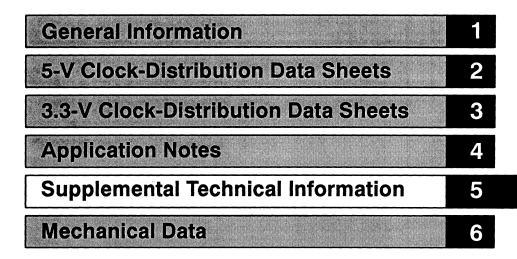

#### V<sub>IH</sub> High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is to be expected.

#### VIL Low-level input voltage

An input voltage within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A maximum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is to be expected.

#### V<sub>OH</sub> High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a high level at the output.

#### VOL Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a low level at the output.

#### V<sub>T+</sub> Positive-going threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage rises from a level below the negative-going threshold voltage,  $V_{T-}$ .

#### V<sub>T</sub>\_\_\_\_ Negative-going threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage falls from a level above the positive-going threshold voltage,  $V_{T+}$ .

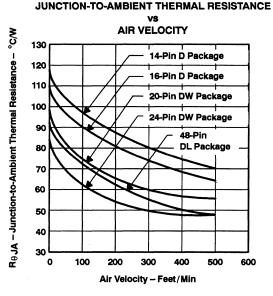

In digital system design, consideration must be given to thermal management of components. The small size of the small-outline package makes this even more critical. Figure 1 shows the thermal resistance of these packages for various rates of air flow.

The thermal resistances in Figure 1 can be used to approximate typical and maximum virtual junction temperatures for the ABT family. In general, the junction temperature for any device can be calculated using using the following equation.

$$T_J = R_{\Theta JA} \times P_T + T_A$$

where:

T<sub>J</sub> = virtual junction temperature

$R_{\theta,JA}$  = thermal resistance, junction to free air

$P_T$  = total power dissipation of the device

T<sub>A</sub> = free-air temperature

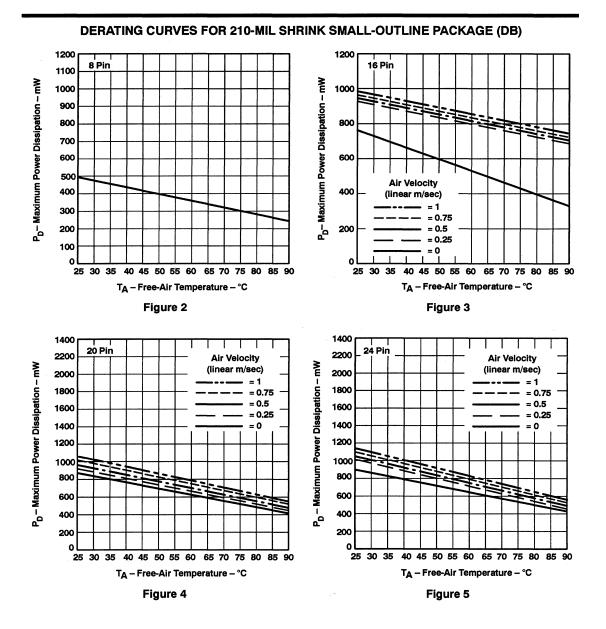

Figures 2 through 5 show power dissipation derating for the 8-, 16,-20-, and 24-pin DB packages.

#### **CLOCK-DISTRIBUTION CIRCUITS**

### 5-V Clock-Distribution Circuits (CDC)

| DESCRIPTION                                                                            | I/O LEVELS | TYPE  | TECHNOLOGY |    |     |     |  |

|----------------------------------------------------------------------------------------|------------|-------|------------|----|-----|-----|--|

| DESCRIPTION                                                                            |            |       | AS         | AC | ACT | ABT |  |

| Hex Inverter                                                                           | CMOS/CMOS  | '204  |            | ~  |     |     |  |

|                                                                                        | TTL/TTL    | '328  |            |    |     | ~   |  |

| 1-to-6 Exclusive OR                                                                    | TTL/TTL    | '328A |            |    |     | +   |  |

|                                                                                        | TTL/CMOS   | '329A |            |    |     | ~   |  |

|                                                                                        | TTL/TTL    | '391  |            |    |     | ~   |  |

| 1-to-6 Exclusive OR With OE                                                            | TTL/CMOS   | '392  |            |    |     | ~   |  |

| Dual 1-to-4 Buffer (2 inputs, 8 outputs)                                               | TTL/CMOS   | '208  |            |    | ~   |     |  |

|                                                                                        | CMOS/CMOS  | '209  |            | ~  |     |     |  |

| 1-to-8 Divide-by-2 Flip-Flop (6 inverting, 2 noninverting)                             | TTL/TTL    | '303  | ~          |    |     |     |  |

| 1-to-8 Divide-by-2 Flip-Flop (8 noninverting)                                          | TTL/TTL    | '304  | ~          |    |     |     |  |

| 1-to-8 Divide-by-2 Flip-Flop (4 inverting, 4 noninverting)                             | TTL/TTL    | '305  | ~          |    |     |     |  |

|                                                                                        | TTL/CMOS   | '337  |            |    |     | ~   |  |

| 1-to-8 Fanout (4 noninverting buffer, 4 divide-by-2 flip-flop)                         | TTL/TTL    | '339  |            |    |     | ~   |  |

| 1-to-8 NAND                                                                            | TTL/TTL    | '340  |            |    | 1   | ~   |  |

| 1-to-8 AND                                                                             | TTL/TTL    | '341  |            |    |     | ~   |  |

| 3-Way Fanout Buffer<br>(dual 1-to-3 noninverting buffer, 1-to-4 divide-by-2 flip-flop) | TTL/TTL    | '330  |            |    |     | ~   |  |

## 3.3-V Clock-Distribution Circuits (CDC)

| DESCRIPTION                                   | I/O LEVELS    | TYPE  | TECHNOLOGY |    |     |     |  |

|-----------------------------------------------|---------------|-------|------------|----|-----|-----|--|

|                                               | 1/0 LEVELS    | TYPE  | AS         | AC | ACT | ABT |  |

| Hex Inverter                                  | CMOS/CMOS     | '203  |            | ~  |     |     |  |

| 1-to-9 Differential LVPECL Buffer             | LVPECL/LVPECL | /111  |            |    |     | +   |  |

| 1-to-9 Differential LVPECL Buffer With TTL OE | LVPECL/LVPECL | '112  |            |    |     | +   |  |

| 1-to-10 Buffer With OE                        | TTL/TTL       | '351  |            |    |     | +   |  |

|                                               | TTL/TTL       | '2351 |            |    |     | +   |  |

|                                               | TTL/TTL       | ′536  |            |    |     | +   |  |

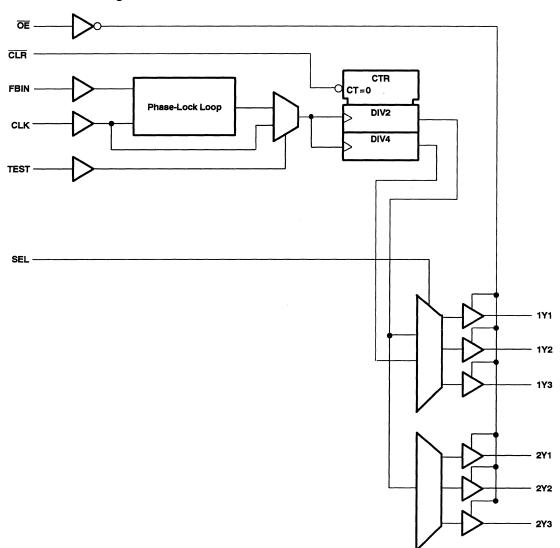

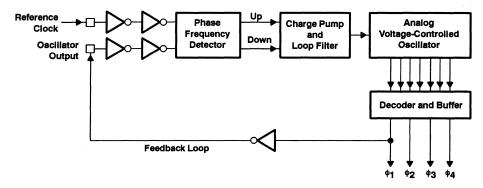

| 1-to-6 PLL Buffer                             | TTL/TTL       | '2536 |            |    |     | +   |  |

| 1-to-12 PLL Buffer                            | TTL/TTL       | ʻ586  |            |    |     | +   |  |

|                                               | TTL/TTL       | ′2586 |            |    |     | +   |  |

| 1-to-12 PLL Buffer                            | LVPECL/TTL    | '2582 |            |    |     | +   |  |

✔ Product available in technology indicated

+ New product planned in technology indicated

1–12

The following table lists military 5-V V<sub>CC</sub> clock-driver circuits currently targeted for market introduction. Customers interested in learning more about TI's plans for these devices should contact military Advanced System Logic marketing at (915) 561-7289.

| DEVICE     | PIN/PACKAGE       | DESCRIPTION                                            |

|------------|-------------------|--------------------------------------------------------|

| SN54CDC303 | 16/J, 16/W, 20/FK | Octal Divide-by-2 Circuit/Clock Driver                 |

| SN54CDC328 | 16/J, 16/W, 20/FK | 1-Line to 6-Line Clock Driver With Selectable Polarity |

SCAS098C - OCTOBER 1989 - REVISED MARCH 1994

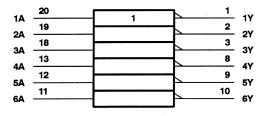

| CDC204 Replaces 74AC11204                                                                       | DW OR N PACKAGE<br>(TOP VIEW)                  |

|-------------------------------------------------------------------------------------------------|------------------------------------------------|

| <ul> <li>CDC204-7 Replaces 74AC11204-7</li> </ul>                                               | · · · · · · · · · · · · · · · · · · ·          |

| <ul> <li>Low-Skew Propagation Delay Specifications<br/>for Clock-Driver Applications</li> </ul> | 1Y 1 20 1A<br>2Y 2 19 2A                       |

| <ul> <li>CMOS-Compatible Inputs and Outputs</li> </ul>                                          | 3Y 🛛 3 18 🗍 3A                                 |

| • Flow-Through Architecture Optimizes                                                           | GND 🛛 4 17 🗍 NC                                |

| PCB Layout                                                                                      | GND <b>[]</b> 5 16 <b>[</b> ] V <sub>CC</sub>  |

| • Center-Pin V <sub>CC</sub> and GND Pin Configurations                                         | GND <b>[</b> ] 6 15 <b>[</b> ] V <sub>CC</sub> |

| Minimize High-Speed Switching Noise                                                             | GND [] 7 14 [] NC                              |

| <ul> <li>EPIC ™ (Enhanced-Performance Implanted</li> </ul>                                      | 4Y <b>U</b> 8 13 <b>U</b> 4A                   |

| CMOS) 1-µm Process                                                                              | 5Y 9 12 5A                                     |

| <ul> <li>500-mA Typical Latch-Up Immunity at 125°C</li> </ul>                                   | 6Y [ <u>10 11</u> ] 6A                         |

| <ul> <li>Package Options Include Plastic<br/>Small-Outline Package (DW) and Standard</li> </ul> | NC – No internal connection                    |

#### description

Plastic 300-mil DIPs (N)

The CDC204/204-7 contains six independent inverters. The device performs the Boolean function  $Y = \overline{A}$ . It is designed specifically for applications requiring low skew between switching outputs.

The CDC204/204-7 is characterized for operation from 25°C to 70°C.

| FUNCTION TABLE |   |  |  |  |

|----------------|---|--|--|--|

| INPUT OUTPUT   |   |  |  |  |

| A              | Y |  |  |  |

| н              | L |  |  |  |

| L.             | н |  |  |  |

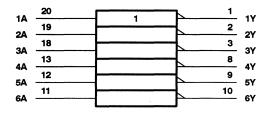

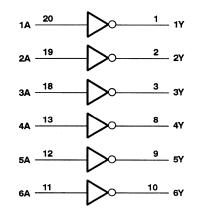

#### logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

### logic diagram (positive logic)

#### EPIC is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications par the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1994, Texas Instruments Incorporated

SCAS098C - OCTOBER 1989 - REVISED MARCH 1994

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub>                                                    |                                   |

|------------------------------------------------------------------------------------------|-----------------------------------|

| Input voltage range, VI (see Note 1)                                                     | –0.5 V to V <sub>CC</sub> + 0.5 V |

| Output voltage range, V <sub>O</sub> (see Note 1)                                        | –0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > V_{CC}$ )                            | ±20 mA                            |

| Output clamp current, $I_{OK}$ (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) | ±50 mA                            |

| Continuous output current, $I_O (V_O = 0 \text{ to } V_{CC})$                            | ±50 mA                            |

| Continuous current through V <sub>CC</sub> or GND                                        | ±150 mA                           |

| Storage temperature range                                                                |                                   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

#### recommended operating conditions

|        |                                                                                               |                          | MIN  | NOM | MAX  | UNIT |

|--------|-----------------------------------------------------------------------------------------------|--------------------------|------|-----|------|------|

| Vcc    | Supply voltage                                                                                |                          | 4.75 | 5   | 5.25 | V    |

| M., .  | High-level input voltage $\frac{V_{CC} = 4.75 \text{ V}}{V_{CC} = 5.25 \text{ V}} \qquad 3.3$ |                          |      | v   |      |      |

| VIН    |                                                                                               | V <sub>CC</sub> = 5.25 V | 3.7  |     |      | v    |

| M.,    |                                                                                               | V <sub>CC</sub> = 4.75 V |      |     | 1.4  |      |

| VIL    | Low-level input voltage                                                                       | V <sub>CC</sub> = 5.25 V |      |     | 1.6  | v    |

| VI     | Input voltage                                                                                 | ·                        | 0    |     | Vcc  | V    |

| 1      | High-level output current                                                                     | V <sub>CC</sub> = 4.75 V |      |     | -24  | mA   |

| IOH .  |                                                                                               | V <sub>CC</sub> = 5.25 V |      |     | -24  | mA   |

| 1      |                                                                                               | V <sub>CC</sub> = 4.75 V |      |     | 24   |      |

| IOL    | Low-level output current                                                                      | V <sub>CC</sub> = 5.25 V |      |     | 24   | mA   |

| ∆t/∆v  | Input transition rise or fall rate                                                            |                          | 0    |     | 10   | ns/V |

| fclock | Input clock frequency                                                                         |                          |      |     | 80   | MHz  |

| TA     | Operating free-air temperature                                                                |                          | 25   |     | 70   | °C   |

SCAS098C - OCTOBER 1989 - REVISED MARCH 1994

| DADAMETED                             | TEST CONDITIONS                                   | N.     | T/   | 4 = 25°C | ;    | CDC204 |      | CDC204-7 |      | UNIT |

|---------------------------------------|---------------------------------------------------|--------|------|----------|------|--------|------|----------|------|------|

| PARAMETER                             | TEST CONDITIONS                                   | Vcc    | MIN  | TYP      | MAX  | MIN    | MAX  | MIN      | MAX  | UNIT |

| · · · · · · · · · · · · · · · · · · · | 1                                                 | 4.75 V | 4.65 |          |      | 4.65   |      | 4.65     |      |      |

|                                       | lOH = - 50 μA                                     | 5.25 V | 5.15 |          |      | 5.15   |      | 5.15     |      |      |

| ∨он                                   | I <sub>ОН</sub> = – 24 mA                         | 4.75 V | 4.19 |          |      | 4.05   |      | 4.05     |      | v    |

|                                       |                                                   | 5.25 V | 4.68 |          |      | 4.55   |      | 4.55     |      |      |

|                                       | IOH = -75 mA <sup>†</sup>                         | 5.25 V |      |          |      | 3.6    |      | 3.6      |      |      |

| ,                                     | l <sub>OL</sub> = 50 μA                           | 4.75 V |      |          | 0.1  |        | 0.1  |          | 0.1  |      |

|                                       | 10L = 50 μA                                       | 5.25 V |      |          | 0.1  |        | 0.1  |          | 0.1  |      |

| VOL                                   |                                                   | 4.75 V |      |          | 0.36 |        | 0.44 |          | 0.44 | v    |

|                                       | I <sub>OL</sub> = 24 mA                           | 5.25 V |      |          | 0.36 |        | 0.44 |          | 0.44 |      |

|                                       | I <sub>OL</sub> = 75 mA <sup>†</sup>              | 5.25 V |      |          |      |        | 1.65 |          | 1.65 |      |

| lı lı                                 | VI = V <sub>CC</sub> or GND                       | 5.25 V |      |          | ±0.1 |        | ±1   |          | ±1   | μΑ   |

| ICC                                   | $V_{I} = V_{CC} \text{ or GND}, \qquad I_{O} = 0$ | 5.25 V |      |          | 4    |        | 40   |          | 40   | μΑ   |

| Ci                                    | VI = V <sub>CC</sub> or GND                       | 5 V    |      | 4        |      |        |      |          |      | pF   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

<sup>†</sup> Not more than one output should be tested at a time, and the duration of the test should not exceed 10 ms.

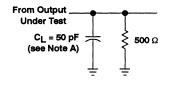

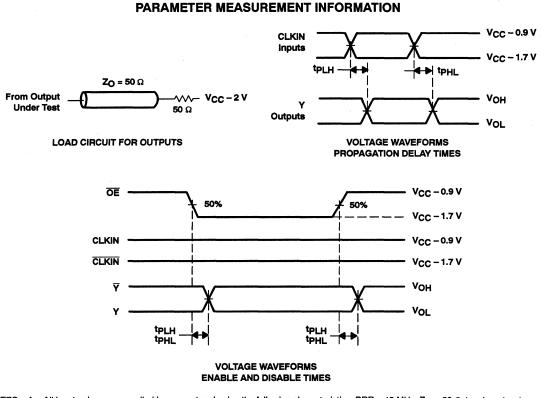

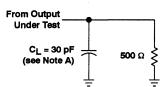

# switching characteristics over recommended operating free-air temperature range, $V_{CC}$ = 5 V $\pm$ 0.25 V (see Note 2 and Figures 1 and 2)

| DADAMETER          | FROM    | M TO CDC204 |     | 204 | CDC204-7 |     |      |

|--------------------|---------|-------------|-----|-----|----------|-----|------|

| PARAMETER          | (INPUT) | (OUTPUT)    | MIN | MAX | MIN      | MAX | UNIT |

| <sup>t</sup> PLH   |         | Y           | 3.7 | 5.7 | 3.7      | 5.7 | ns   |

| <sup>t</sup> PHL   | ~       |             | 3.7 | 5.7 | 3.7      | 5.7 |      |

| <sup>t</sup> sk(o) | A       | Y           |     | 1   |          | 0.7 | ns   |

NOTE 2: All specifications are valid only for all outputs switching simultaneously and in phase.

SCAS098C - OCTOBER 1989 - REVISED MARCH 1994

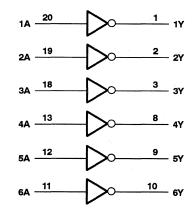

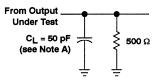

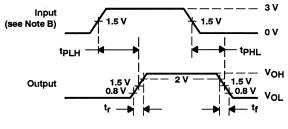

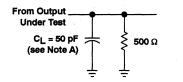

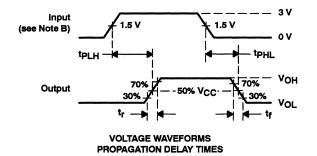

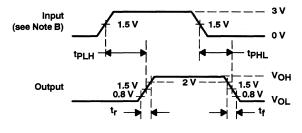

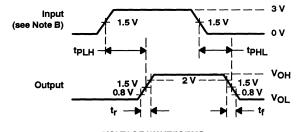

### PROPAGATION DELAY TIMES

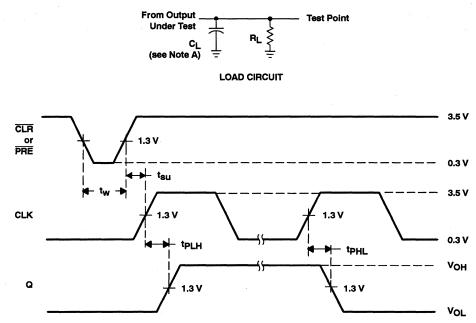

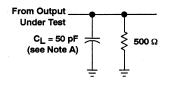

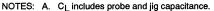

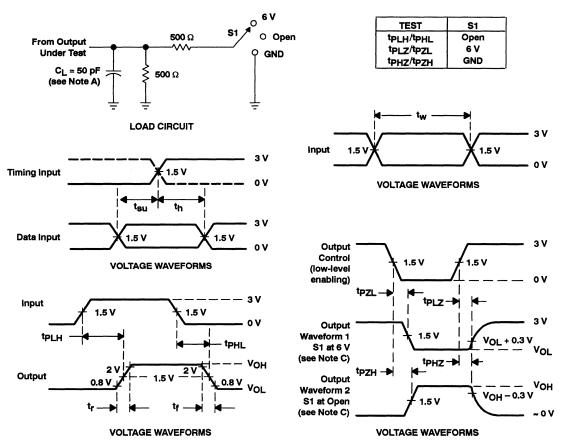

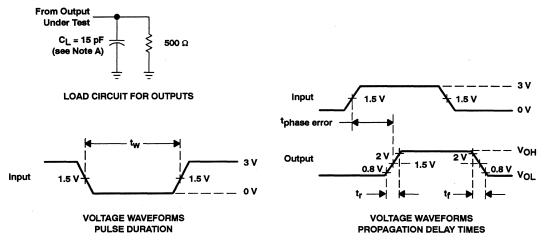

NOTES: A. CL includes probe and jig capacitance.

B. Input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z<sub>O</sub> = 50 Ω, t<sub>f</sub> = 3 ns, t<sub>f</sub> = 3 ns.

C. The outputs are measured one at a time with one input transition per measurement.

Figure 1. Load Circuit and Voltage Waveforms

SCAS098C - OCTOBER 1989 - REVISED MARCH 1994

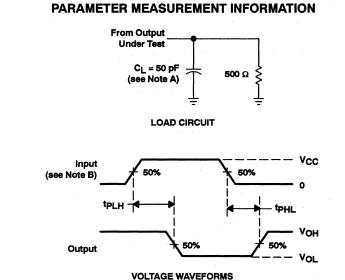

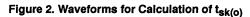

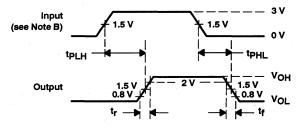

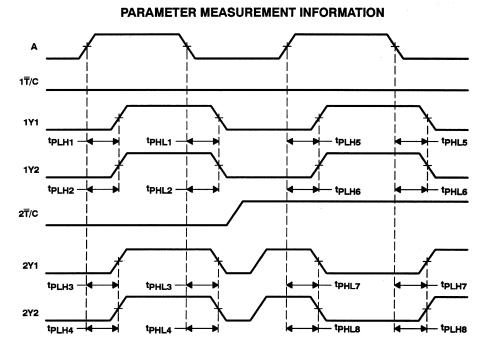

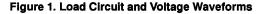

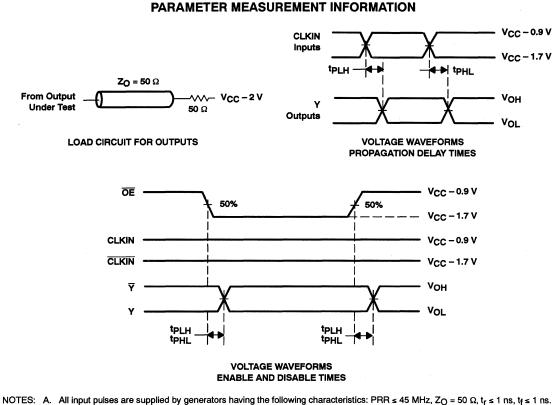

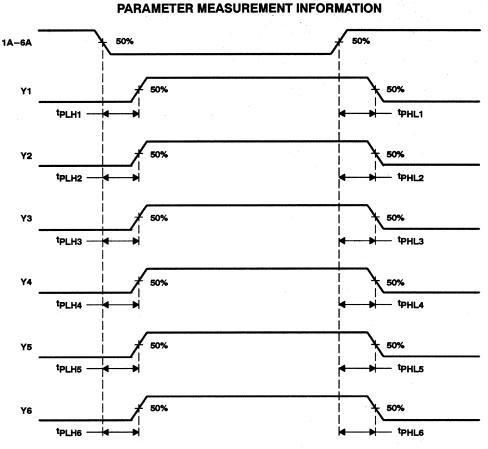

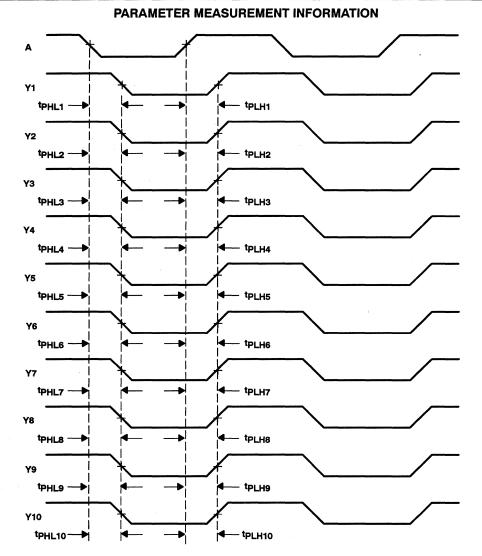

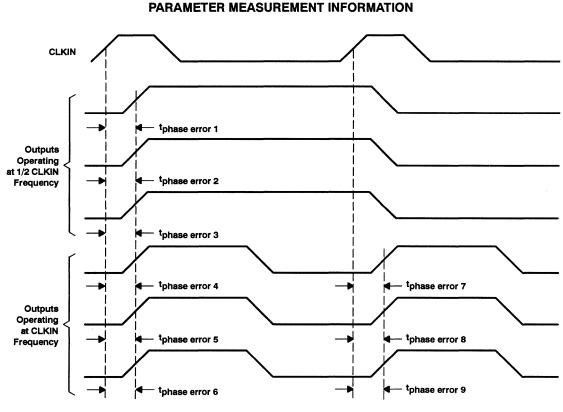

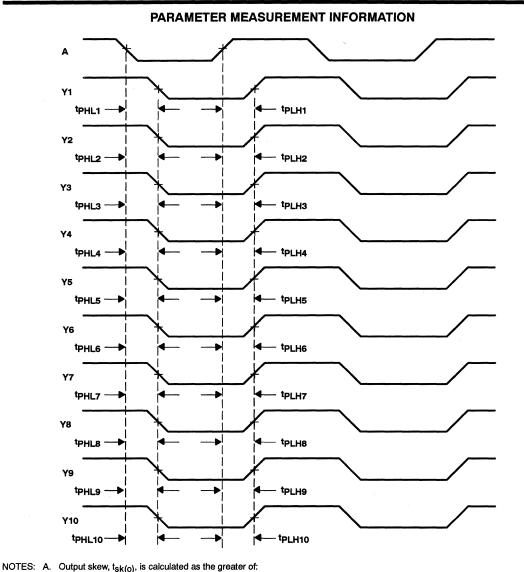

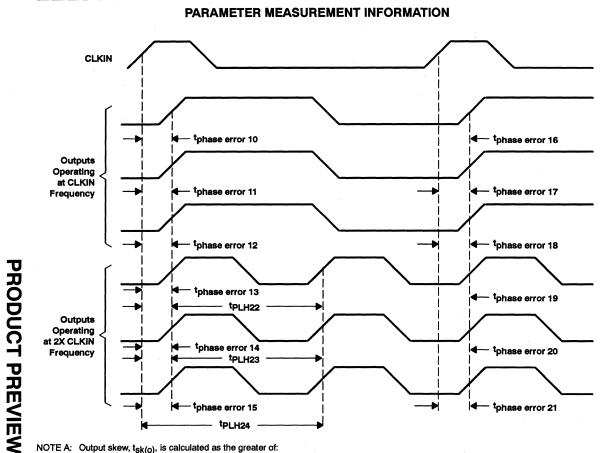

### PARAMETER MEASUREMENT INFORMATION

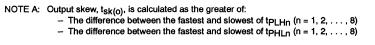

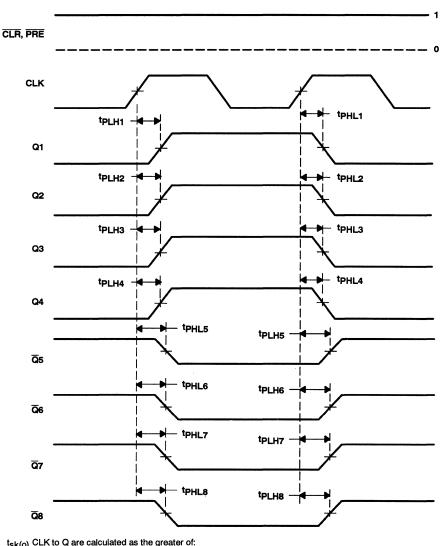

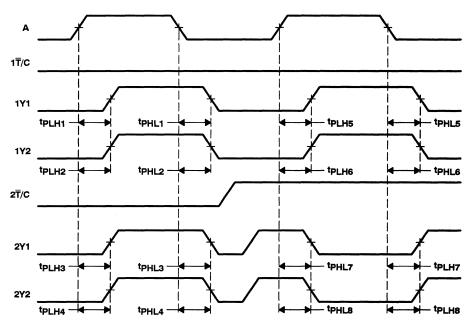

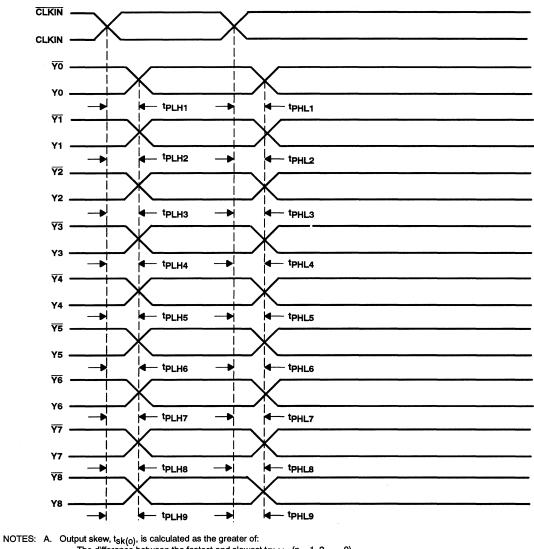

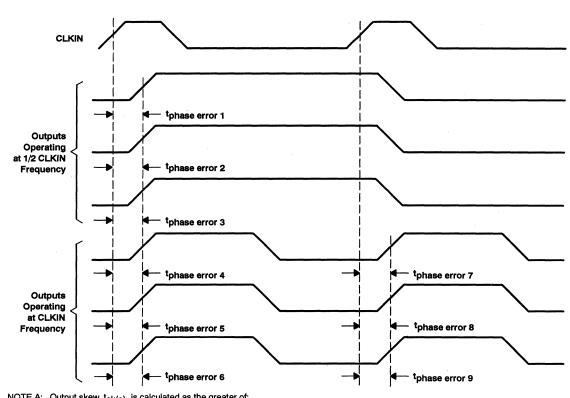

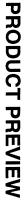

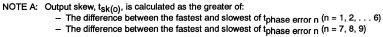

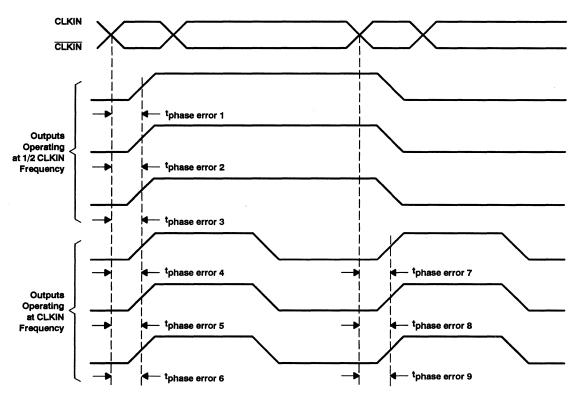

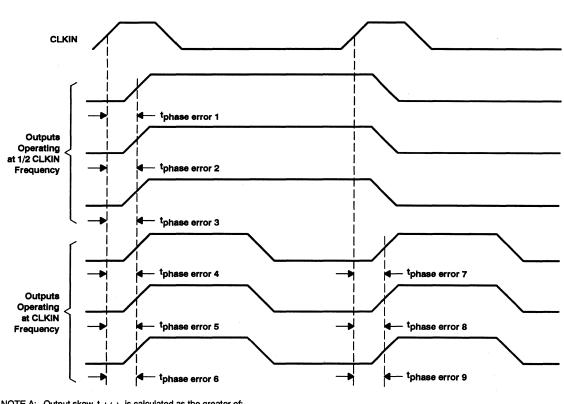

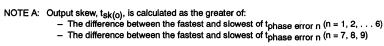

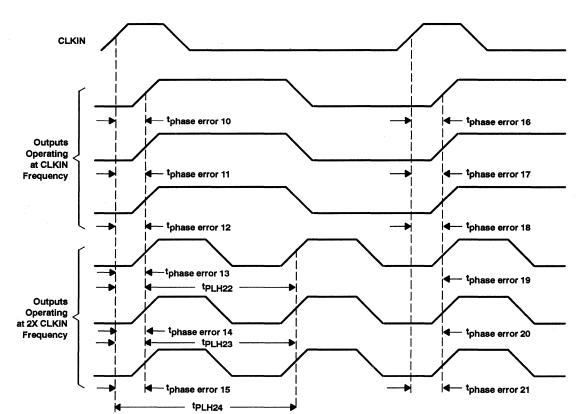

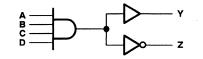

NOTE A: Output skew, t<sub>Sk(0)</sub>, is calculated as the greater of: - The difference between the fastest and slowest of tp<sub>HLn</sub> (n = 1, 2, ..., 6) - The difference between the fastest and slowest of tp<sub>Lhn</sub> (n = 1, 2, ..., 6)

Figure 2. Waveforms for Calculation of tsk(o)

.

2-8

CDC208, CDC208-7 **DUAL 1-LINE TO 4-LINE CLOCK DRIVERS** WITH 3-STATE OUTPUTS

SCAS109C - APRIL 1990 - REVISED MARCH 1994

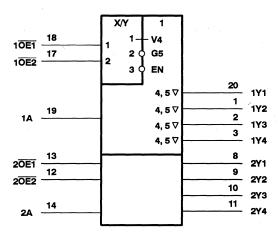

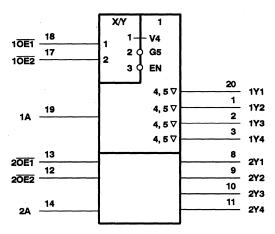

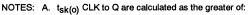

| <ul> <li>CDC208 Replaces 74ACT11208</li> <li>CDC208-7 Replaces 74ACT11208-7</li> </ul>          | DB, DW, OR N PACKAGE<br>(TOP VIEW)                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Low-Skew Propagation Delay Specifications<br/>for Clock-Driver Applications</li> </ul> | $\begin{array}{c c} 1Y2 \begin{bmatrix} 1 & 20 \\ 1Y3 \end{bmatrix} \begin{array}{c} 1Y2 \begin{bmatrix} 1 & 20 \\ 2 & 19 \end{bmatrix} \begin{array}{c} 1Y1 \\ 1Y3 \end{bmatrix} \begin{array}{c} 2 & 19 \end{bmatrix} \begin{array}{c} 1A \end{array}$ |

| <ul> <li>TTL-Compatible Inputs and</li></ul>                                                    | 1Y4 [] 3 18 ] 1 <del>0E1</del>                                                                                                                                                                                                                           |

| CMOS-Compatible Outputs                                                                         | GND [] 4 17 ] 1 <del>0E2</del>                                                                                                                                                                                                                           |

| <ul> <li>Flow-Through Architecture Optimizes</li></ul>                                          | GND <b>5</b> 16 V <sub>CC</sub>                                                                                                                                                                                                                          |

| PCB Layout                                                                                      | GND <b>6</b> 15 V <sub>CC</sub>                                                                                                                                                                                                                          |

| <ul> <li>Center-Pin V<sub>CC</sub> and GND Pin Configurations</li></ul>                         | GND 7 14 2A                                                                                                                                                                                                                                              |

| Minimize High-Speed Switching Nolse                                                             | 2Y1 8 13 20E1                                                                                                                                                                                                                                            |

| <ul> <li>EPIC <sup>™</sup> (Enhanced-Performance Implanted</li></ul>                            | 2Y2 9 12 2OE2                                                                                                                                                                                                                                            |

| CMOS) 1-μm Process                                                                              | 2Y3 10 11 2Y4                                                                                                                                                                                                                                            |

| • 500-mA Typical Latch-Up Immunity at 125°C                                                     |                                                                                                                                                                                                                                                          |

Package Options Include Plastic Small-Outline (DW) and Shrink Small-Outline (DB) Packages and Standard Plastic 300-mil DIPs (N)

#### description

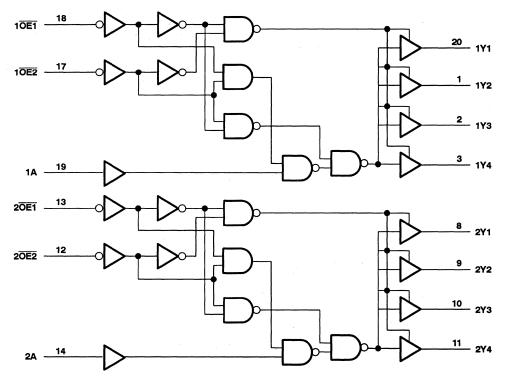

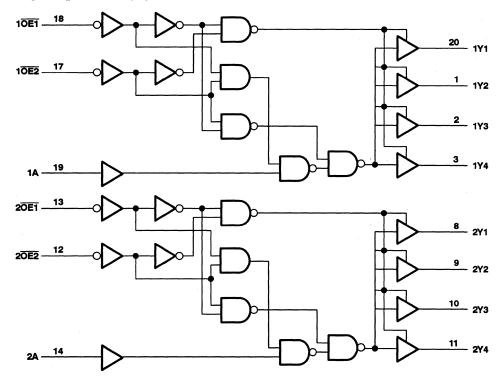

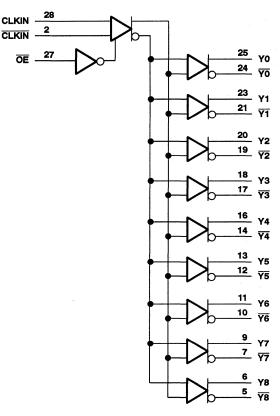

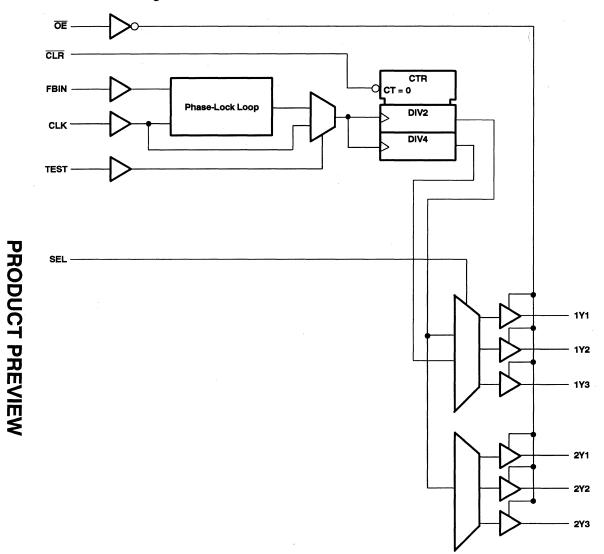

The CDC208/208-7 contains dual clock-driver circuits that fanout one input signal to four outputs with minimum skew for clock distribution (see Figure 2). The device also offers two output-enable ( $\overline{OE1}$  and  $\overline{OE2}$ ) inputs for each circuit that can force the outputs to be disabled to a high-impedance state or to a high- or low-logic level independent of the signal on the respective A input.

Skew parameters are specified for a reduced temperature and voltage range common to many applications.

The CDC208/208-7 is characterized for operation from -40°C to 85°C.

| FUNCTION TABLES |   |   |         |     |     |     |  |  |  |

|-----------------|---|---|---------|-----|-----|-----|--|--|--|

| INPUTS          |   |   | OUTPUTS |     |     |     |  |  |  |

| 10E1 10E2 1A    |   |   | 1Y1     | 1Y2 | 1Y3 | 1Y4 |  |  |  |

| L               | L | L | L       | L   | L   | L   |  |  |  |

| L               | L | н | н       | н   | н   | н   |  |  |  |

| L               | н | х | L       | L   | L   | L   |  |  |  |

| н               | L | х | н       | н   | н   | н   |  |  |  |

| н               | н | x | z       | z   | z   | z   |  |  |  |

\_\_\_\_\_

|      | INPUTS |    | OUTPUTS |     |     |     |  |  |

|------|--------|----|---------|-----|-----|-----|--|--|

| 20E1 | 20E2   | 2A | 2Y1     | 2Y2 | 2Y3 | 2Y4 |  |  |

| L    | L      | L  | L       | L   | L   | L   |  |  |

| L    | L      | н  | н       | н   | н   | н   |  |  |

| L    | н      | х  | L       | L   | L   | L   |  |  |

| н    | L      | х  | н       | н   | н   | н   |  |  |

| н    | н      | х  | z       | Z   | z   | z   |  |  |

EPIC is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication data. Products conform to specifications per the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1994, Texas Instruments Incorporated

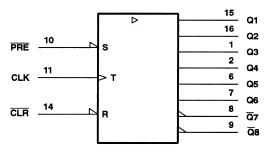

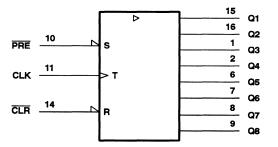

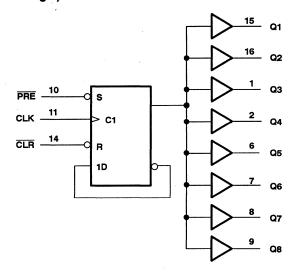

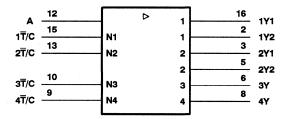

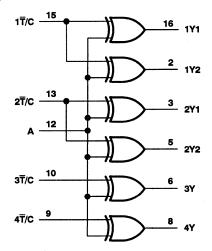

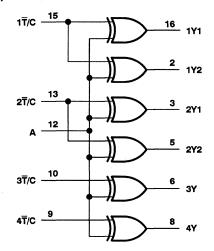

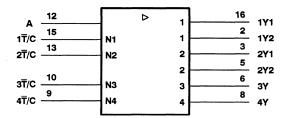

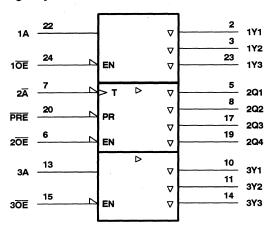

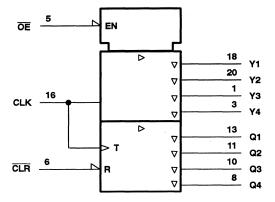

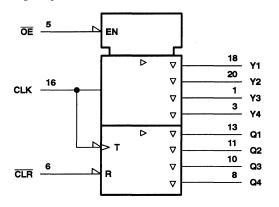

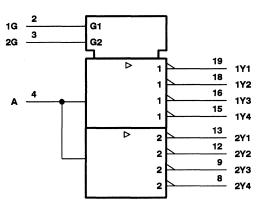

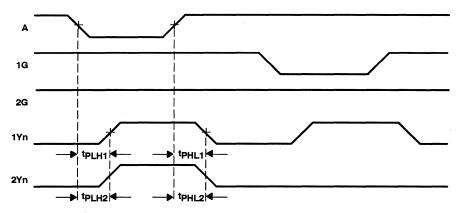

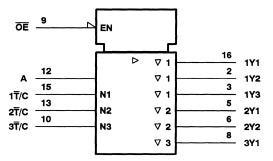

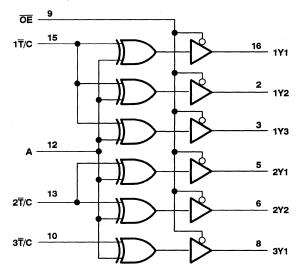

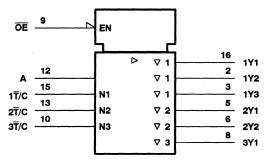

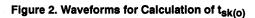

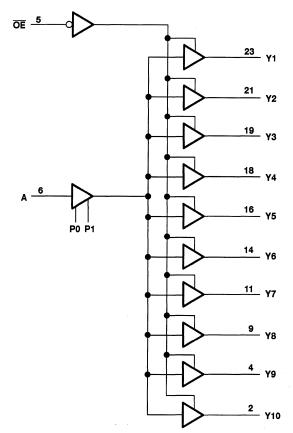

#### logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

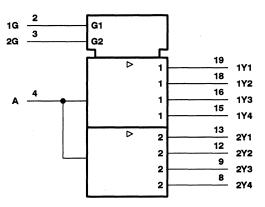

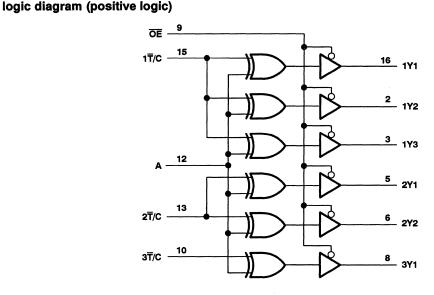

#### logic diagram (positive logic)

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub>                                                    |                                                        |

|------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Input voltage range, VI (see Note 1)                                                     | $\dots \dots -0.5 V$ to $V_{CC} + 0.5 V$               |

| Output voltage range, V <sub>O</sub> (see Note 1)                                        | $\dots \dots -0.5 \text{ V to V}_{CC} + 0.5 \text{ V}$ |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > V_{CC}$ )                            | ±20 mA                                                 |

| Output clamp current, $I_{OK}$ (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) | ±50 mA                                                 |

| Continuous output current, $I_O (V_O = 0 \text{ to } V_{CC})$                            | ±50 mA                                                 |

| Continuous current through V <sub>CC</sub> or GND                                        | ±200 mA                                                |

| Storage temperature range                                                                | –65°C to 150°C                                         |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

#### recommended operating conditions

|        |                                    | MIN | NOM | MAX | UNIT |

|--------|------------------------------------|-----|-----|-----|------|

| Vcc    | Supply voltage                     | 4.5 | 5   | 5.5 | V    |

| VIH    | High-level input voltage           | 2   |     |     | v    |

| VIL    | Low-level input voltage            |     |     | 0.8 | V    |

| VI     | Input voltage                      | 0   |     | Vcc | v    |

| юн     | High-level output current          |     |     | -24 | mA   |

| IOL    | Low-level output current           |     |     | 24  | mA   |

| ∆t/∆v  | Input transition rise or fall rate | 0   |     | 10  | ns/V |

| fclock | Input clock frequency              |     |     | 60  | MHz  |

| ТА     | Operating free-air temperature     | -40 |     | 85  | °C   |

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

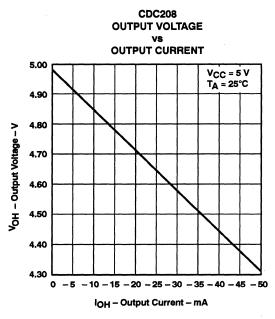

| DADAMETED | TEST CONDITIONS                                        |       | T,   | <b>α = 25°C</b> | ;    | CDC  | 208  | CDC208-7 |      | UNIT |

|-----------|--------------------------------------------------------|-------|------|-----------------|------|------|------|----------|------|------|

| PARAMETER | TEST CONDITIONS                                        | Vcc   | MIN  | TYP             | MAX  | MIN  | MAX  | MIN      | MAX  | UNIT |

|           | 1                                                      | 4.5 V | 4.4  |                 |      | 4.4  |      | 4.4      |      |      |

|           | lOH =50 μA                                             | 5.5 V | 5.4  |                 |      | 5.4  |      | 5.4      |      |      |

|           |                                                        | 4.5 V | 3.94 |                 |      | 3.8  |      | 3.8      |      | v    |

| ∨он       | I <sub>OH</sub> = -24 mA                               | 5.5 V | 4.94 |                 |      | 4.8  |      | 4.8      |      | v    |

|           | $I_{OH} = -50 \text{ mA}^{\dagger}$                    | 5.5 V |      |                 |      |      |      |          |      |      |

|           | $I_{OH} = -75 \text{ mA}^{\dagger}$                    | 5.5 V |      |                 |      | 3.85 |      | 3.85     |      |      |

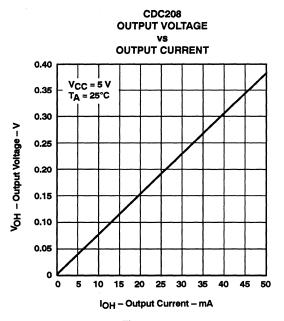

|           | 1                                                      | 4.5 V |      |                 | 0.1  |      | 0.1  |          | 0.1  | v    |

|           | l <sub>OL</sub> = 50 μA                                | 5.5 V |      |                 | 0.1  |      | 0.1  |          | 0.1  |      |

| 14-1      |                                                        | 4.5 V |      |                 | 0.36 |      | 0.44 |          | 0.44 |      |

| VOL       | I <sub>OL</sub> = 24 mA                                | 5.5 V |      |                 | 0.36 |      | 0.44 |          | 0.44 |      |

|           | $I_{OL} = 50 \text{ mA}^{\dagger}$                     | 5.5 V |      |                 |      |      |      |          |      |      |

|           | $I_{OL} = 75 \text{ mA}^{\dagger}$                     | 5.5 V |      |                 |      |      | 1.65 |          | 1.65 |      |

| ij        | VI = V <sub>CC</sub> or GND                            | 5.5 V |      |                 | ±0.1 |      | ±1   |          | ±1   | μA   |

| loz       | V <sub>O</sub> = V <sub>CC</sub> or GND                | 5.5 V |      |                 | ±0.5 |      | ±5   |          | ±5   | μA   |

| lcc       | $V_{I} = V_{CC} \text{ or GND}, \qquad I_{O} = 0$      | 5.5 V |      |                 | 8    |      | 80   |          | 80   | μA   |

| ∆ICC‡     | One input at 3.4 V,<br>Other inputs at $V_{CC}$ or GND |       |      |                 | 0.9  |      | 1    |          | 1    | mA   |

| Ci        | VI = V <sub>CC</sub> or GND                            | 5 V   |      | 4               |      |      |      |          |      | рF   |

| Co        | V <sub>O</sub> = V <sub>CC</sub> or GND                | 5 V   |      | 10              |      |      |      |          |      | pF   |

<sup>†</sup> Not more than one output should be tested at a time, and the duration of the test should not exceed 10 ms.

<sup>‡</sup> This is the increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V or V<sub>CC</sub>.

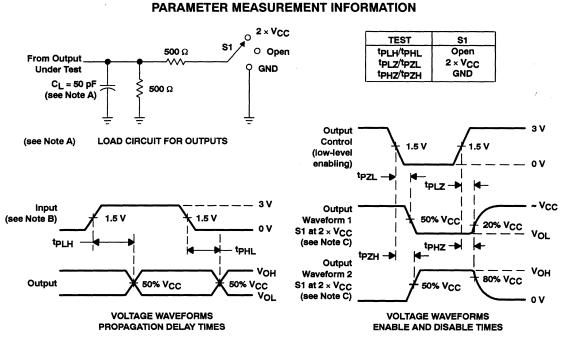

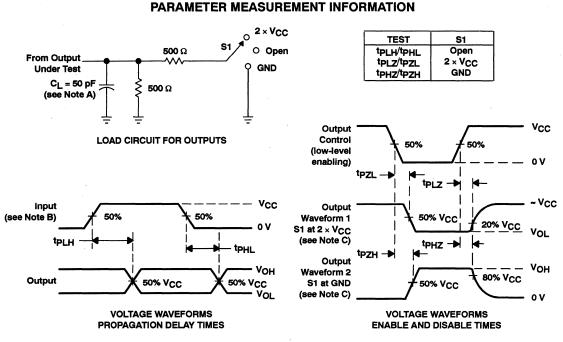

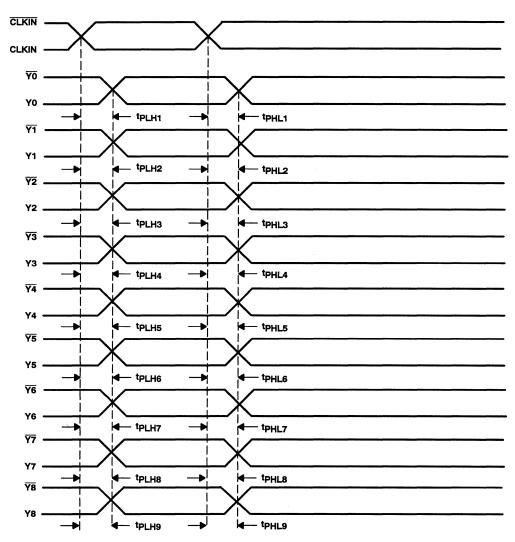

# switching characteristics over recommended operating free-air temperature range, $V_{CC}$ = 5 V ± 0.5 V (unless otherwise noted) (see Figure 1)

| PARAMETER        | FROM            | то       | Т   | T <sub>A</sub> = 25°C |      |     | CDC208 |     | CDC208-7 |      |

|------------------|-----------------|----------|-----|-----------------------|------|-----|--------|-----|----------|------|

| FARAMETER        | (INPUT)         | (OUTPUT) | MIN | TYP                   | MAX  | MIN | MAX    | MIN | MAX      | UNIT |

| <sup>t</sup> PLH | 1A and 2A       | Any Y    | 5.3 | 8.5                   | 10.9 | 5.3 | 11.7   | 5.3 | 11.7     | ns   |

| <sup>t</sup> PHL |                 |          | 3.6 | 7.7                   | 11   | 3.6 | 11.5   | 3.6 | 11.5     |      |

| <sup>t</sup> PLH | 10E1, 10E2, and | Anu V    | 4.7 | 8.5                   | 11.7 | 4.7 | 12.8   | 4.7 | 12.8     | ns   |

| <sup>t</sup> PHL | 20E1, 20E2      | Any Y    | 4.4 | 8.4                   | 11.3 | 4.4 | 12.4   | 4.4 | 12.4     |      |

| <sup>t</sup> PZH | 10E2 or 20E2    | Any Y    | 4.4 | 8.1                   | 11.3 | 4.4 | 12.4   | 4.4 | 12.4     |      |

| <sup>t</sup> PZL | 10E1 or 20E1    | Ally I   | 5   | 9.6                   | 13.3 | 5   | 14.9   | 5   | 14.9     | ns   |

| <sup>t</sup> PHZ | 10E2 or 20E2    | Any Y    | 4.2 | 7.4                   | 9.3  | 4.2 | 10.2   | 4.2 | 10.2     |      |

| <sup>t</sup> PLZ | 10E1 or 20E1    |          | 5.4 | 7.5                   | 9.2  | 5.4 | 9.9    | 5.4 | 9.9      | ns   |

### switching characteristics, V<sub>CC</sub> = 5 V $\pm$ 0.25 V, T<sub>A</sub> = 25°C to 70°C (see Note 2 and Figures 1 and 2)

| PARAMETER          | FROM      | то       | CDC | 208  | CDC2 | 08-7 | UNIT |

|--------------------|-----------|----------|-----|------|------|------|------|

| PARAMETER          | (INPUT)   | (OUTPUT) | MIN | MAX  | MIN  | MAX  | UNIT |

| <sup>t</sup> PLH   | 1A and 2A | Any Y    | 7.6 | 10.2 | 7.6  | 10.2 | ns   |

| <sup>t</sup> PHL   |           |          | 6.6 | 9.8  | 6.6  | 9.8  |      |

| <sup>t</sup> sk(o) | 1A and 2A | Any Y    |     | 1    |      | 0.7  | ns   |

NOTE 2: All specifications are valid only for all outputs switching simultaneously and in phase.

## CDC208, CDC208-7 DUAL 1-LINE TO 4-LINE CLOCK DRIVERS WITH 3-STATE OUTPUTS

SCAS109C - APRIL 1990 - REVISED MARCH 1994

#### operating characteristics, V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C

|          | PARAMETER                              | TEST CONDITIONS  | TYP                               | UNIT  |    |  |

|----------|----------------------------------------|------------------|-----------------------------------|-------|----|--|

| <u> </u> | Dewar disainstian consultance per bank | Outputs enabled  | C <sub>1</sub> = 50 pF, f = 1 MHz | 96 pF | -5 |  |

| Cpd      | Power dissipation capacitance per bank | Outputs disabled | CL = 50 pr, 1 = 1 MHZ             | 12    | рн |  |

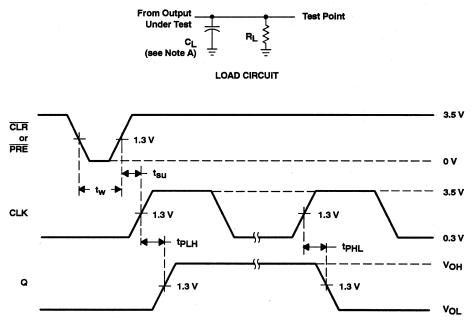

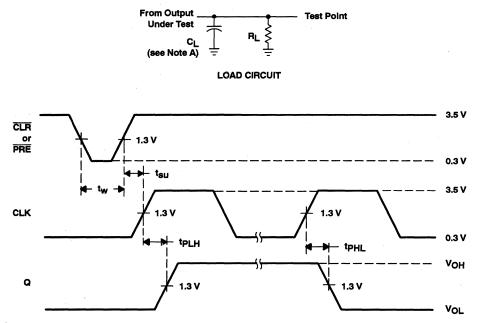

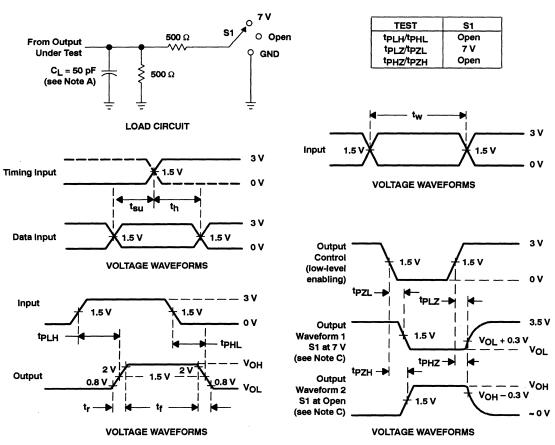

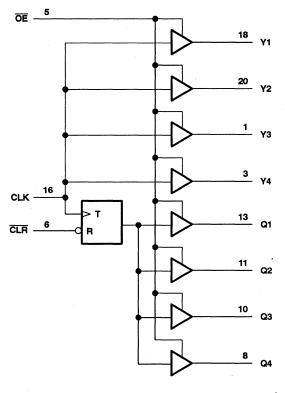

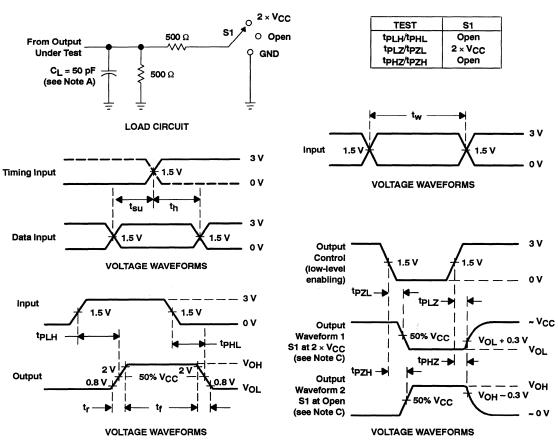

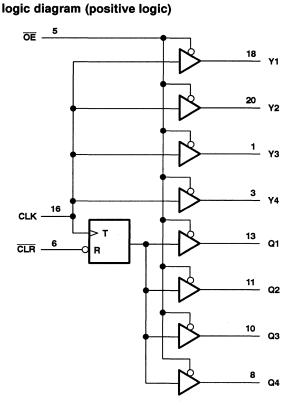

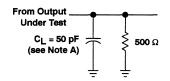

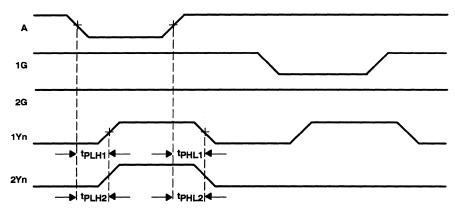

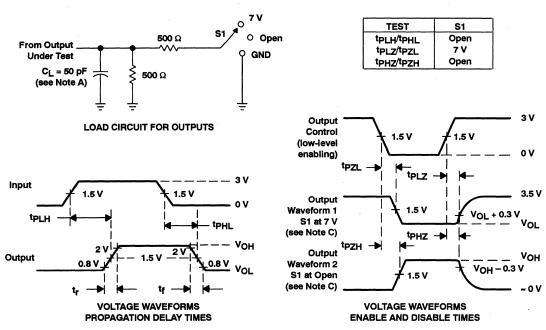

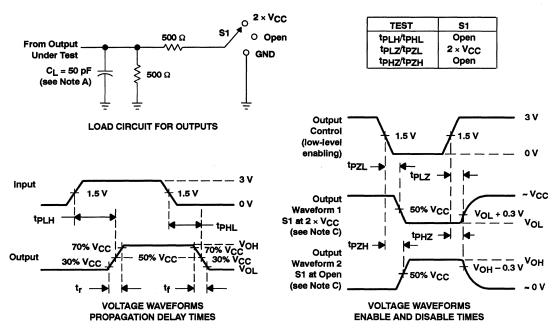

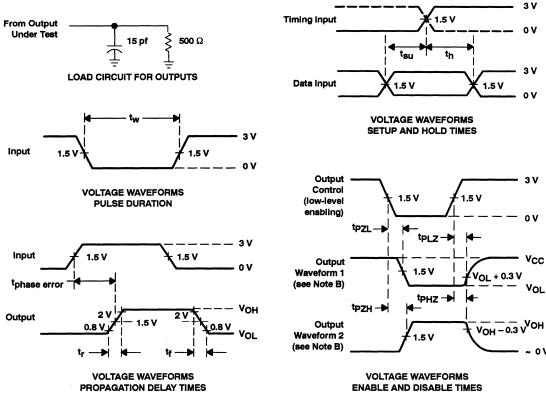

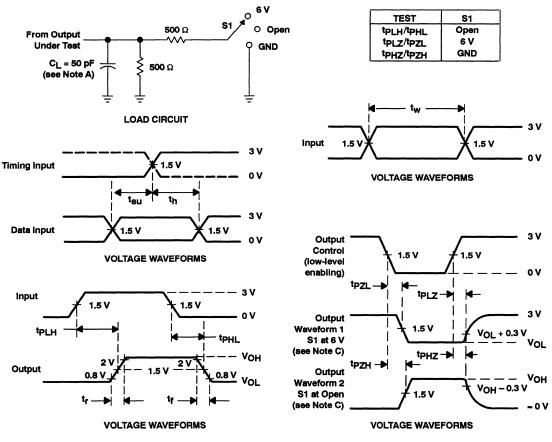

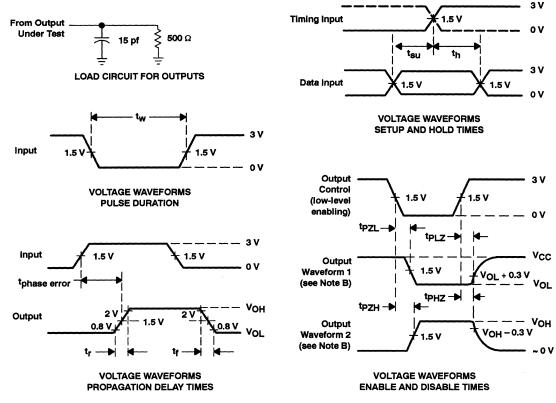

NOTES: A. CL includes probe and jig capacitance.

- B. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z<sub>O</sub> = 50 Ω, t<sub>f</sub> ≤ 3 ns, t<sub>f</sub> ≤ 3 ns. For testing pulse duration: t<sub>f</sub> = t<sub>f</sub> = 1 to 3 ns. Pulse polarity can be either high-to-low-to-high or low-to-high-to-low.

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

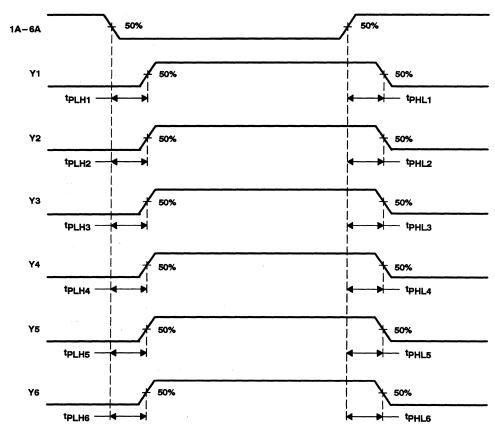

Figure 1. Load Circuit and Voltage Waveforms

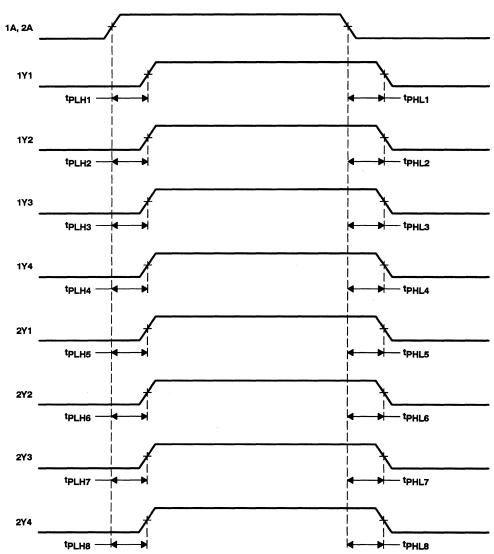

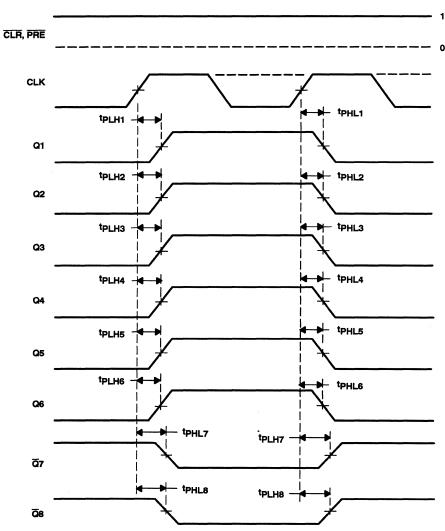

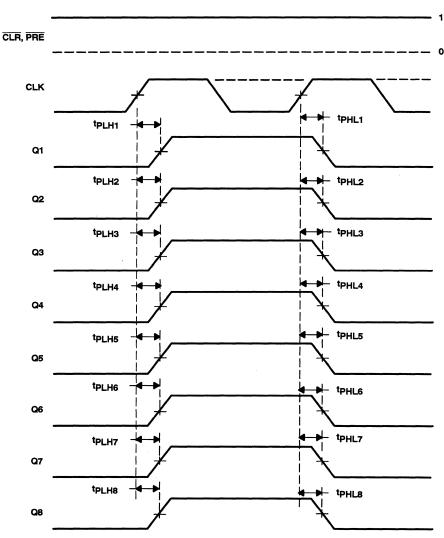

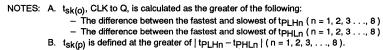

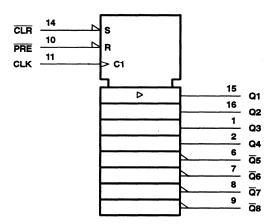

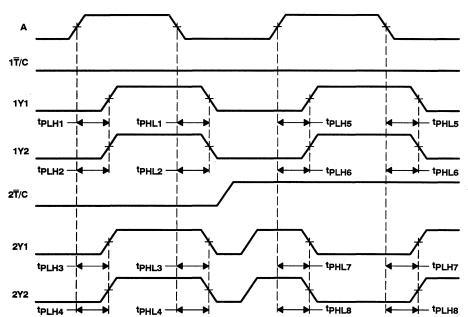

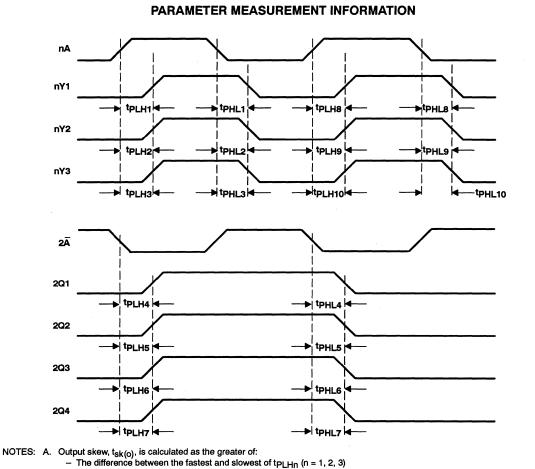

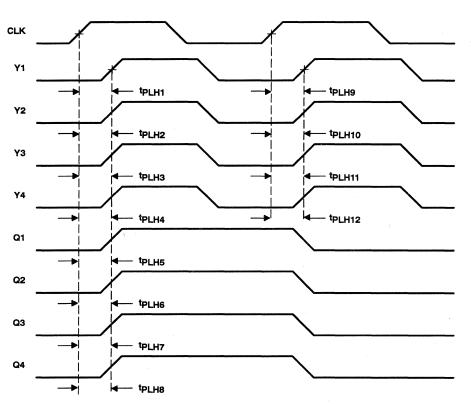

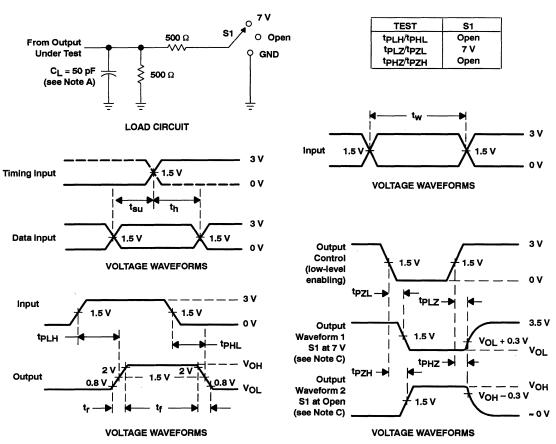

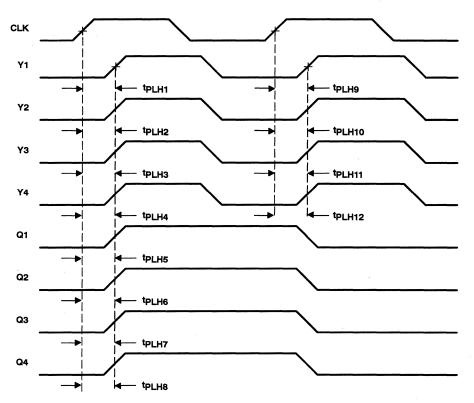

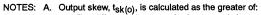

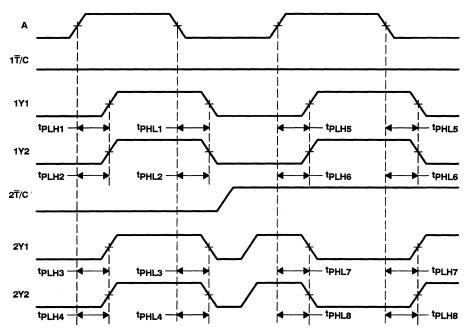

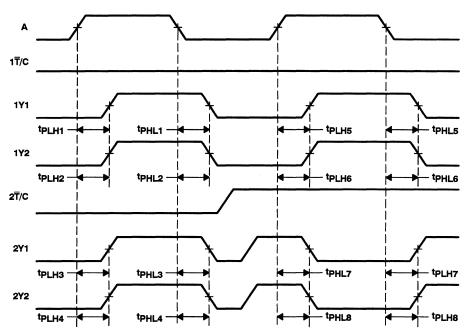

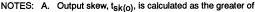

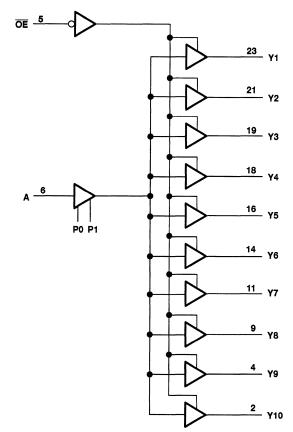

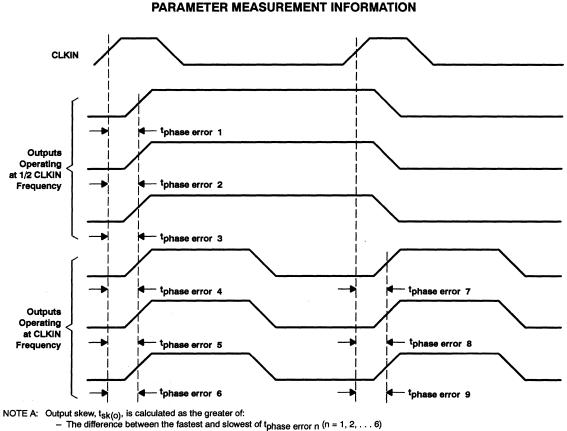

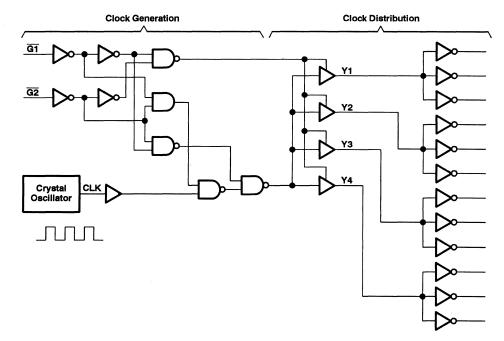

PARAMETER MEASUREMENT INFORMATION 1A, 2A 1Y1 tPHL1 <sup>t</sup>PLH1 1Y2 tPHL2 tPLH2 1Y3 <sup>t</sup>PLH3 <sup>t</sup>PHL3 1Y4 tPHL4 <sup>t</sup>PLH4 2Y1 tPHL5 <sup>t</sup>PLH5 2Y2 <sup>t</sup>PLH6 <sup>t</sup>PHL6 2Y3 <sup>t</sup>PLH7 <sup>t</sup>PHL7 2Y4 tPLH8 <sup>t</sup>PHL8 NOTE A: Output skew, t<sub>sk(0)</sub>, is calculated as the greater of: — The difference between the fastest and slowest of tp<sub>LHn</sub> (n = 1, 2, ..., 8) — The difference between the fastest and slowest of tp<sub>HLn</sub> (n = 1, 2, ..., 8)

### CDC209, CDC209-7 DUAL 1-LINE TO 4-LINE CLOCK DRIVERS WITH 3-STATE OUTPUTS

20 1 1Y1

19 1A

18 10E1

17 10E2

16 Vcc

15 VCC

13 20E1

12 20E2

11 1 2Y4

14**1**2A

DW OR N PACKAGE

(TOP VIEW)

1Y2

1Y3 2

1Y4 🛛 3

GND 4

GND 🛛 5

GND 6

GND 17

2Y1 8

2Y2 🛛 9

2Y3 1 10

SCAS108C - MARCH 1990 - REVISED MARCH 1994

- CDC209 Replaces 74AC11208

- CDC209-7 Replaces 74AC11208-7

- Low-Skew Propagation Delay Specifications for Clock-Driver Applications

- CMOS-Compatible Inputs and Outputs

- Flow-Through Architecture Optimizes PCB Layout

- Characterized for Operation at 5-V and 3.3-V  $V_{CC}$

- Center-Pin V<sub>CC</sub> and GND Pin Configurations Minimize High-Speed Switching Noise

- EPIC ™ (Enhanced-Performance Implanted CMOS) 1-μm Process

- 500-mA Typical Latch-Up Immunity at 125°C

- Package Options Include Plastic Small-Outline Package (DW) and Standard Plastic 300-mil DIPs (N)

#### description

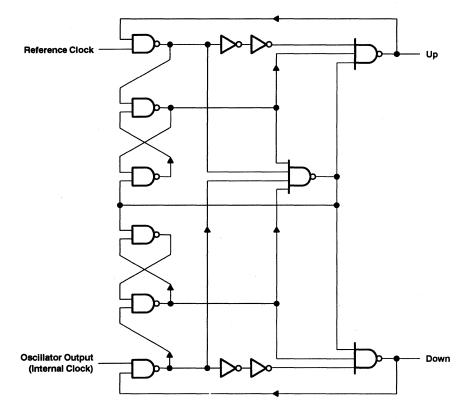

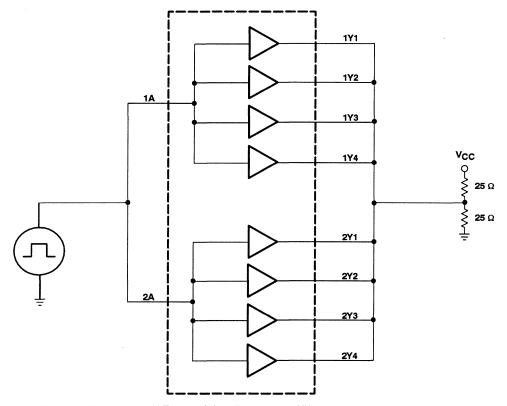

The CDC209/209-7 contains dual clock-driver circuits that fanout one input signal to four outputs with minimum skew for clock distribution (see Figure 2). The device also offers two output-enable ( $\overline{OE1}$  and  $\overline{OE2}$ ) inputs for each circuit that can force the outputs to be disabled to a high-impedance state or to a high- or low-logic level independent of the signal on the respective A input.

Skew parameters are specified for a reduced temperature and voltage range common to many applications.

The CDC209/209-7 is characterized for operation from -40°C to 85°C.

| FUNCTION TABLES |   |   |         |     |     |     |  |  |

|-----------------|---|---|---------|-----|-----|-----|--|--|

| INPUTS          |   |   | OUTPUTS |     |     |     |  |  |

| 10E1 10E2 1A    |   |   | 1Y1     | 1Y2 | 1Y3 | 1Y4 |  |  |

| L               | L | L | L       | L   | L   | L   |  |  |

| L               | L | н | н       | н   | н   | н   |  |  |

| L               | н | х | L       | L   | L   | L   |  |  |

| н               | L | х | н       | н   | н   | н   |  |  |

| н               | н | х | z       | z   | z   | z   |  |  |

FUNCTION TABLES

| INPUTS |      |    | OUTPUTS |     |     |     |  |

|--------|------|----|---------|-----|-----|-----|--|

| 20E1   | 20E2 | 2A | 2Y1     | 2Y2 | 2Y3 | 2Y4 |  |

| L      | L    | L  | L       | L   | L   | L   |  |

| L      | L    | н  | н       | н   | н   | н   |  |

| L      | н    | х  | L       | L   | L   | L   |  |

| н      | L    | х  | н       | н   | н   | н   |  |

| н      | н    | х  | z       | Z   | Z   | Z   |  |

EPIC is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to apacifications per the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1994, Texas Instruments Incorporated

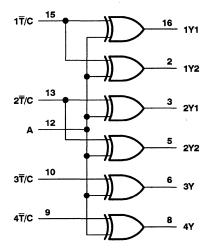

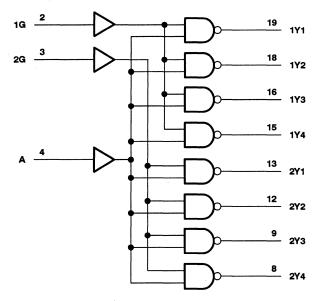

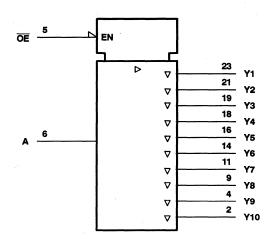

#### logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

#### logic diagram (positive logic)

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub>                                                           | –0.5 V to 7 V                     |

|-------------------------------------------------------------------------------------------------|-----------------------------------|

| Input voltage range, V <sub>1</sub> (see Note 1)                                                | -0.5 V to V <sub>CC</sub> + 0.5 V |

| Output voltage range, V <sub>O</sub> (see Note 1)                                               | -0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, IIK (VI < 0 or VI > VCC)                                                   | ±20 mA                            |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) |                                   |

| Continuous output current, I <sub>O</sub> (V <sub>O</sub> = 0 to V <sub>CC</sub> )              | ±50 mA                            |

| Continuous current through V <sub>CC</sub> or GND                                               | ±200 mA                           |

| Storage temperature range                                                                       | 65°C to 150°C                     |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

#### recommended operating conditions

|        |                                       |                         | MIN  | NOM | MAX  | UNIT          |

|--------|---------------------------------------|-------------------------|------|-----|------|---------------|

| Vcc    | Supply voltage                        |                         |      | 5   | 5.5  | v             |

| VIH    |                                       | V <sub>CC</sub> = 3 V   | 2.1  |     |      | v             |

|        | High-level input voltage              | V <sub>CC</sub> = 4.5 V | 3.15 |     |      |               |

|        | · · · · · · · · · · · · · · · · · · · | V <sub>CC</sub> = 5.5 V | 3.85 |     |      |               |

| VIL    |                                       | V <sub>CC</sub> = 3 V   |      |     | 0.9  | 0.9<br>1.35 V |

|        | Low-level input voltage               | V <sub>CC</sub> = 4.5 V |      |     | 1.35 |               |

|        |                                       | V <sub>CC</sub> = 5.5 V |      |     | 1.65 |               |

| VI     | Input voltage                         |                         |      |     | Vcc  | v             |

| Iон    |                                       | V <sub>CC</sub> = 3 V   |      |     | -4   | mA            |

|        | High-level output current             | V <sub>CC</sub> = 4.5 V |      |     | -24  |               |

|        |                                       | V <sub>CC</sub> = 5.5 V |      |     | -24  |               |

| IOL    |                                       | V <sub>CC</sub> = 3 V   |      |     | 12   |               |

|        | Low-level output current              | V <sub>CC</sub> = 4.5 V |      |     | 24   | mA            |

|        |                                       | V <sub>CC</sub> = 5.5 V |      |     | 24   |               |

| ∆t/∆v  | Input transition rise or fall rate    |                         | 0    |     | 10   | ns/V          |

| fclock | Input clock frequency                 |                         |      |     | 60   | MHz           |

| TA     | Operating free-air temperature        |                         | -40  |     | 85   | °C            |

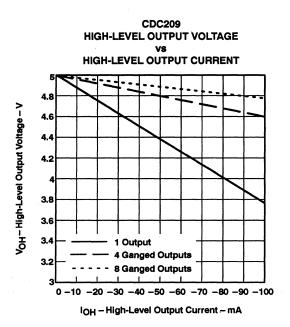

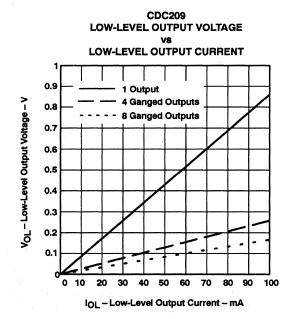

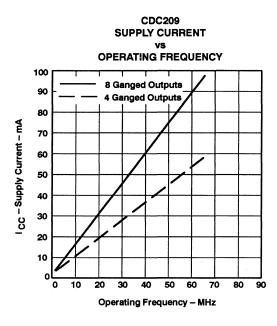

#### CDC209, CDC209-7 DUAL 1-LINE TO 4-LINE CLOCK DRIVERS WITH 3-STATE OUTPUTS SCAS108C - MARCH 1990 - REVISED MARCH 1994

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                                                                                                                |                                         |       | T,   | <b>α = 25°C</b> |      | CDC  | 209  | CDC2 | 09-7   |      |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------|------|-----------------|------|------|------|------|--------|------|

| PARAMETER                                                                                                      | TEST CONDITIONS                         | Vcc   | MIN  | TYP             | MAX  | MIN  | MAX  | MIN  | MAX    | UNIT |

| / 100 - 2010 - 2010 - 2010 - 2010 - 2010 - 2010 - 2010 - 2010 - 2010 - 2010 - 2010 - 2010 - 2010 - 2010 - 2010 | I <sub>OH</sub> = -50 μA                | 3 V   | 2.9  |                 |      | 2.9  |      | 2.9  |        |      |

|                                                                                                                |                                         | 4.5 V | 4.4  |                 |      | 4.4  |      | 4.4  |        |      |

|                                                                                                                |                                         | 5.5 V | 5.4  |                 |      | 5.4  |      | 5.4  |        |      |

| V <sub>OH</sub>                                                                                                | IOH = -4 mA                             | 3 V   | 2.58 |                 |      | 2.48 |      | 2.48 |        | v    |

|                                                                                                                | lou - 24 mA                             | 4.5 V | 3.94 |                 |      | 3.8  |      | 3.8  |        |      |

|                                                                                                                | I <sub>OH</sub> = -24 mA                | 5.5 V | 4.94 |                 |      | 4.8  |      | 4.8  |        |      |

|                                                                                                                | $I_{OH} = -75 \text{ mA}^{\dagger}$     | 5.5 V |      |                 |      | 3.85 |      | 3.85 |        |      |

|                                                                                                                | l <sub>OL</sub> = 50 μA                 | 3 V   |      |                 | 0.1  |      | 0.1  |      | 0.1    |      |

|                                                                                                                |                                         | 4.5 V |      |                 | 0.1  |      | 0.1  |      | 0.1    |      |

|                                                                                                                |                                         | 5.5 V |      |                 | 0.1  |      | 0.1  |      | 0.1    |      |

| Vol                                                                                                            | I <sub>OL</sub> = 12 mA                 | 3 V   |      |                 | 0.36 |      | 0.44 |      | 0.44 V | v    |

|                                                                                                                |                                         | 4.5 V |      |                 | 0.36 |      | 0.44 |      | 0.44   |      |

|                                                                                                                | I <sub>OL</sub> = 24 mA                 | 5.5 V |      |                 | 0.36 |      | 0.44 |      | 0.44   |      |

|                                                                                                                | I <sub>OL</sub> = 75 mA <sup>†</sup>    | 5.5 V |      |                 |      |      | 1.65 |      | 1.65   |      |

| i,                                                                                                             | VI = VCC or GND                         | 5.5 V |      |                 | ±0.1 |      | ±1   |      | ±1     | μA   |

| loz                                                                                                            | V <sub>O</sub> = V <sub>CC</sub> or GND | 5.5 V |      |                 | ±0.5 |      | ±5   |      | ±5     | μA   |

| lcc                                                                                                            | $V_I = V_{CC}$ or GND, $I_O = 0$        | 5.5 V |      |                 | 8    |      | 80   |      | 80     | μA   |

| Ci                                                                                                             | VI = V <sub>CC</sub> or GND             | 5 V   |      | 4               |      |      |      |      |        | рF   |

| Co                                                                                                             | V <sub>O</sub> = V <sub>CC</sub> or GND | 5 V   |      | 10              |      |      |      |      |        | pF   |

<sup>†</sup> Not more than one output should be tested at a time, and the duration of the test should not exceed 10 ms.

## switching characteristics over recommended operating free-air temperature range, $V_{CC}$ = 3.3 V $\pm$ 0.3 V (unless otherwise noted) (see Figure 1)

| PARAMETER        | FROM            | то       | Т   | T <sub>A</sub> = 25°C |      | CDC | 209  | CDC2 | 09-7 | UNIT |

|------------------|-----------------|----------|-----|-----------------------|------|-----|------|------|------|------|

| PARAMETER        | (INPUT)         | (OUTPUT) | MIN | TYP                   | MAX  | MIN | MAX  | MIN  | MAX  | UNIT |

| <sup>t</sup> PLH | 1A and 2A       | Any Y    | 4.8 | 11.1                  | 13.1 | 4.8 | 14.6 | 4.8  | 14.6 | ns   |

| <sup>t</sup> PHL |                 |          | 5.1 | 12.2                  | 14.3 | 5.1 | 15.6 | 5.1  | 15.6 |      |

| <sup>t</sup> PLH | 10E1, 10E2, and | Any Y    | 5.2 | 11.9                  | 14.2 | 5.2 | 15.8 | 5.2  | 15.8 | ns   |

| <sup>t</sup> PHL | 20E1, 20E2      | Any t    | 7.8 | 13.3                  | 15.7 | 7.8 | 17.4 | 7.8  | 17.4 |      |

| <sup>t</sup> PZH | 10E2 or 20E2    | Any Y    | 5.1 | 11.8                  | 14.2 | 5.1 | 15.7 | 5.1  | 15.7 |      |

| <sup>t</sup> PZL | 10E1 or 20E1    | Ally f   | 6.8 | 16.3                  | 19.5 | 6.8 | 22.8 | 6.8  | 22.8 | ns   |

| <sup>t</sup> PHZ | 10E2 or 20E2    | Anu V    | 3.4 | 6.9                   | 8.6  | 3.4 | 9.2  | 3.4  | 9.2  |      |

| <sup>t</sup> PLZ | 10E1 or 20E1    | Any Y    | 4.1 | 7.5                   | 9.4  | 4.1 | 10.2 | 4.1  | 10.2 | ns   |

## CDC209, CDC209-7 **DUAL 1-LINE TO 4-LINE CLOCK DRIVERS** WITH 3-STATE OUTPUTS

SCAS108C - MARCH 1990 - REVISED MARCH 1994

# switching characteristics over recommended operating free-air temperature range, $V_{CC}$ = 5 V $\pm$ 0.5 V (unless otherwise noted) (see Figure 1)

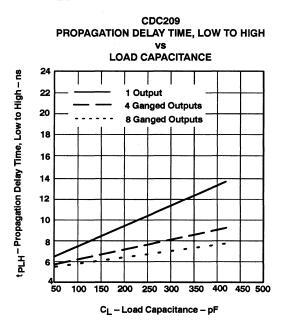

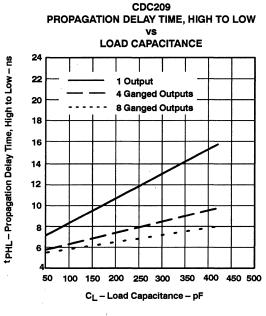

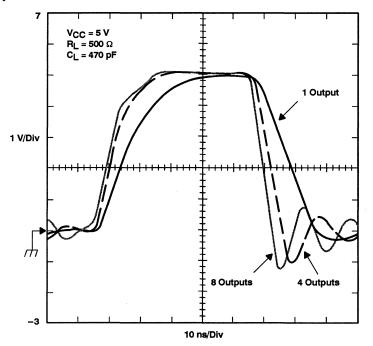

| DADAMETED        | FROM            | то              | Т,  | <b>α = 25°C</b> | ;    | CDC209 |      | CDC2 | 209-7 | UNIT |