### TMS370 Family

# Data Manual

# TMS370 Family

Data Manual

į,

1993

1993

8-Bit Microcontroller Family

#### IMPORTANT NOTICE

Texas Instruments Incorporated (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Please be aware that TI products are not intended for use in life-support appliances, devices, or systems. Use of TI product in such applications requires the written approval of the appropriate TI officer. Certain applications using semiconductor devices may involve potential risks of personal injury, property damage, or loss of life. In order to minimize these risks, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards. Inclusion of TI products in such applications is understood to be fully at the risk of the customer using TI devices or systems.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1993, Texas Instruments Incorporated

- **Chapter 16 Electrical Specifications and Timings.** Gives timing diagrams and electrical specifications for each of the device categories.

- **Chapter 17 Customer Information.** Describes mask-ROM prototyping, TMS370 physical characteristics, and parts ordering.

- Appendix A Differences Between a TMS370CxxxA Device and a TMS370Cxxx Device. Points out the differences between the TMS370CxxxA devices that are described in this manual and the TMS370Cxxx devices.

- Appendix B Peripheral File Memory Map. Gives reference tables for the TMS370 control bits and registers.

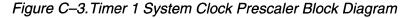

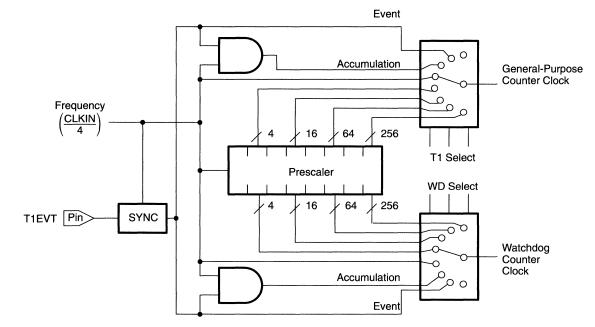

- Appendix C Block Diagrams. Gives reference block diagrams of the major circuits.

- Appendix D ASCII Character Set. Lists the ASCII character set that the TMS370 assembler recognizes.

- Appendix E Opcode/Instruction Cross-Reference. Gives an opcode-to-instruction cross-reference of all 73 mnemonics and 246 opcodes of the TMS370 instruction set.

- Appendix F Instruction/Opcode Cross-Reference and Bus Activity Table. Gives an instruction-to-opcode cross-reference of all 73 mnemonics and 246 opcodes of the TMS370 instruction set and provides a cycle-by-cycle bus activity table.

- Appendix G Device Pinouts. Provides pinouts for the individual device categories.

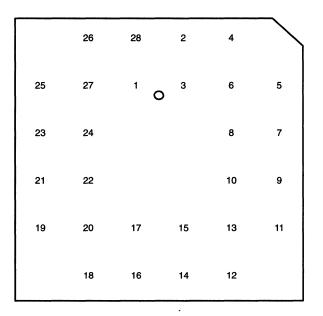

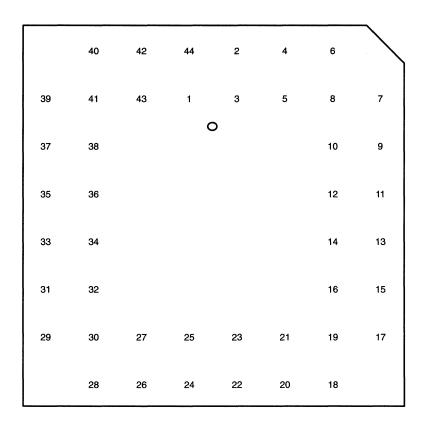

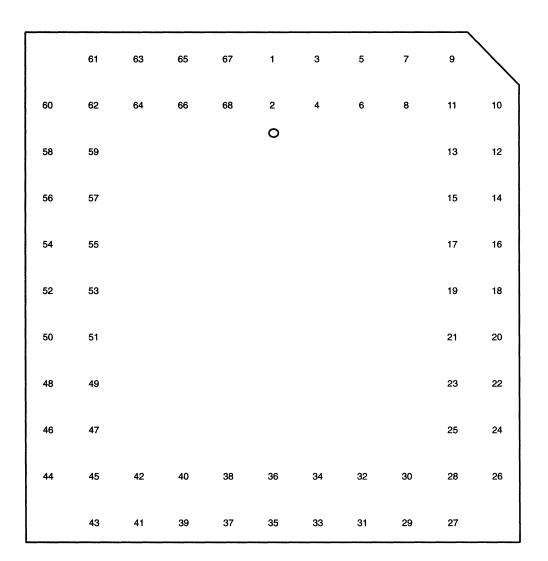

- Appendix H PLCC-to-PGA Pinouts. Shows the pinouts for the standard PLCC-to-PGA sockets that are commonly used in prototype and production applications. You can use these pinouts when you wirewrap your breadboard with a socket.

- Appendix I PACT.H. Gives PACT.H macros used with PACT example programs.

- **Appendix J** Glossary. Defines acronyms and key terms used in this book.

In syntax descriptions, the instruction, command, or directive is in a **bold typeface** font, and parameters are in an *italic typeface*. Portions of a syntax that are in **bold** should be entered as shown; portions of a syntax that are in *italics* describe the type of information that should be entered. Here is an example of a directive syntax:

MOV s,d

**MOV** is the instruction. This instruction has two parameters, indicated by *s* and *d*.

Braces ({and}) indicate a list. The symbol I (read as *or*) separates items within the list. Here's an example of a command that has a list:

TST {AIB}

This provides two choices: TST A or TST B.

Unless the list is enclosed in square brackets, you must choose one item from the list.

#### Information About Cautions and Warnings

This book may contain cautions and warnings.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

- *TMS370Cx5x 8-Bit Microcontrollers Data Sheet* (literature number SPNS010B) describes the features of the TMS370Cx5x devices and provides pinouts, electrical specifications, and timings for these microprocessors.

- Using the TMS370 A/D Converter Module Application Report (literature number SPNA005) provides examples of hardware interfaces and software routines for the TMS370 analog-to-digital converter module.

- Using the TMS370 SPI and SCI Modules Application Report (literature number SPNA006) provides examples of hardware interfaces and software routines for the TMS370 SPI and SCI modules.

- **Using the TMS370 Timer Modules Application Report** (literature number SPNA008) provides examples of hardware interfaces and software routines for the TMS370 timer 1 and timer 2 modules.

#### Trademarks

CROSSTALK is a trademark of Microstuf, Inc.

Kermit is a registered trademark of Columbia University.

MS-DOS is a registered trademark of Microsoft Corp.

PC-DOS is a trademark of International Business Machines Corp.

PROCOMM is a registered trademark of Datastorm Technologies Inc.

VAX and VMS are trademarks of Digital Equipment Corp.

XDS is a trademark of Texas Instruments Incorporated.

#### If You Need Assistance. . .

| If you want to                                                                  | Do this                                                                                                                                                                                                                      |  |  |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Request more information about<br>Texas Instruments<br>microcontroller products | Write to:<br>Texas Instruments Incorporated<br>Market Communications Manager, MS 736<br>P.O. Box 1443<br>Houston, Texas 77251–1443                                                                                           |  |  |

| Order Texas Instruments documentation                                           | Call the TI Literature Response Center: (800) 477–8924                                                                                                                                                                       |  |  |

| Ask questions about product<br>operation or report suspected<br>problems        | Call the Microcontroller Hotline:<br>(713) 274–2370<br>FAX: (713) 274–4203                                                                                                                                                   |  |  |

| Report mistakes in this document<br>or any other TI documentation               | Fill out and return the reader response card at<br>the end of this book, or send your comments to:<br>Texas Instruments Incorporated<br>Technical Publications Manager, MS 702<br>P.O. Box 1443<br>Houston, Texas 77251–1443 |  |  |

| 3 | CPU        | and Memo                                                    | ory Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -1                         |

|---|------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   |            |                                                             | as a register-to-register architecture. This chapter describes the CPU registers                                                                                                                                                                                                                                                                                                                                                                                   |                            |

|   | and n      | nemory org                                                  | ganization.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

|   | 3.1        | CPU/Reg                                                     | gister File Interaction                                                                                                                                                                                                                                                                                                                                                                                                                                            | -2                         |

|   | 3.2        | CPU Reg                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -4                         |

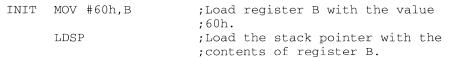

|   |            | 3.2.1                                                       | Stack Pointer (SP) 3-                                                                                                                                                                                                                                                                                                                                                                                                                                              | -4                         |

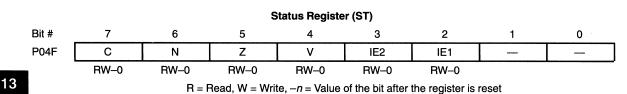

|   |            | 3.2.2                                                       | Status Register (ST) 3-                                                                                                                                                                                                                                                                                                                                                                                                                                            | -5                         |

|   |            | 3.2.3                                                       | Program Counter (PC) 3-                                                                                                                                                                                                                                                                                                                                                                                                                                            | -7                         |

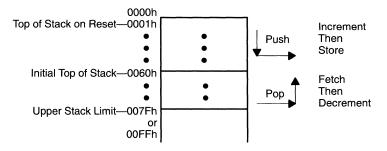

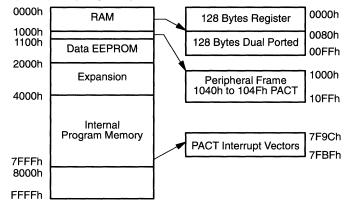

|   | 3.3        | Memory                                                      | Мар                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -8                         |

|   |            | 3.3.1                                                       | Register File                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -9                         |

|   |            | 3.3.2                                                       | Peripheral File                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                         |

|   |            | 3.3.3                                                       | Data EEPROM Modules 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                          |

|   |            | 3.3.4                                                       | Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                          |

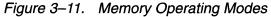

|   | 3.4        | Memory                                                      | Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                          |

|   |            | 3.4.1                                                       | Microcomputer Single-Chip Mode 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                          |

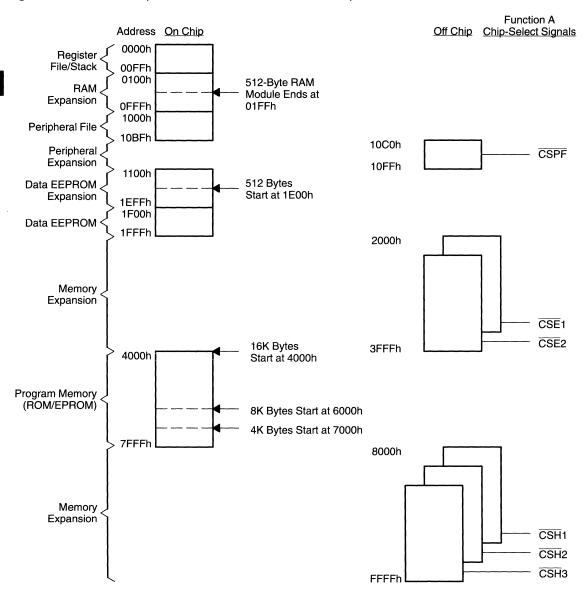

|   |            | 3.4.2                                                       | Microcomputer Mode With External Expansion (All Devices With Memory Expansion and Internal Program Memory)                                                                                                                                                                                                                                                                                                                                                         | 8                          |

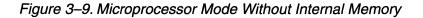

|   |            | 3.4.3                                                       | Microprocessor Mode Without Internal Memory (Memory Expansion Devices Only)                                                                                                                                                                                                                                                                                                                                                                                        | 22                         |

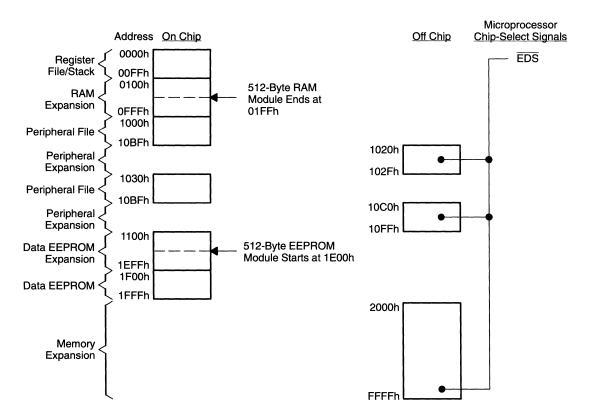

|   |            | 3.4.4                                                       | Microprocessor Mode With Internal Program Memory (Memory Expansion Devices Only)                                                                                                                                                                                                                                                                                                                                                                                   | 23                         |

|   |            | 3.4.5                                                       | Memory Mode Summary 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                         |

| 4 | Syste      | em and Di                                                   | gital I/O Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                            | -1                         |

|   | -          |                                                             | system and I/O configuration. Features and options are described, as well as                                                                                                                                                                                                                                                                                                                                                                                       |                            |

|   |            |                                                             | at control the configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |

|   | 4.1        | System C                                                    | 2-Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -2                         |

|   |            | 4.1.1                                                       | Privilege Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

|   |            | 4.1.2                                                       | Oscillator Fault                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

|   |            | 4.1.3                                                       | Automatic Wait States 4-                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |

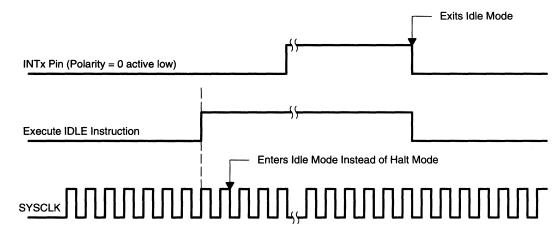

|   | 4.2        | Low-Pow                                                     | /er and Idle Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -6                         |

|   |            | 4.2.1                                                       | Standby Mode 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -7                         |

|   |            | 4.2.2                                                       | Halt Mode 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |

|   |            | 400                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

|   |            | 4.2.3                                                       | Using interrupts to Exit From the Hall Mode                                                                                                                                                                                                                                                                                                                                                                                                                        | -8                         |

|   |            | 4.2.3<br>4.2.4                                              | Using Interrupts to Exit From the Halt Mode                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

|   | 4.3        | 4.2.4                                                       | Oscillator Power Bit 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10                         |

|   | 4.3        | 4.2.4                                                       | Oscillator Power Bit                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10<br>11                   |

|   | 4.3        | 4.2.4<br>System 0                                           | Oscillator Power Bit       4-1         Control Registers       4-1         System Control and Configuration Register 0 (SCCR0)       4-1                                                                                                                                                                                                                                                                                                                           | 10<br>11<br>11             |

|   | 4.3        | 4.2.4<br>System (<br>4.3.1                                  | Oscillator Power Bit       4-1         Control Registers       4-1         System Control and Configuration Register 0 (SCCR0)       4-1         System Control and Configuration Register 1 (SCCR1)       4-1                                                                                                                                                                                                                                                     | 10<br>11<br>11<br>13       |

|   | 4.3<br>4.4 | 4.2.4<br>System (<br>4.3.1<br>4.3.2<br>4.3.3                | Oscillator Power Bit       4-1         Control Registers       4-1         System Control and Configuration Register 0 (SCCR0)       4-1                                                                                                                                                                                                                                                                                                                           | 10<br>11<br>11<br>13<br>14 |

|   |            | 4.2.4<br>System (<br>4.3.1<br>4.3.2<br>4.3.3                | Oscillator Power Bit       4-1         Control Registers       4-1         System Control and Configuration Register 0 (SCCR0)       4-1         System Control and Configuration Register 1 (SCCR1)       4-1         System Control and Configuration Register 2 (SCCR2)       4-1                                                                                                                                                                               | 10<br>11<br>13<br>14<br>16 |

|   |            | 4.2.4<br>System 0<br>4.3.1<br>4.3.2<br>4.3.3<br>Digital I/0 | Oscillator Power Bit       4-1         Control Registers       4-1         System Control and Configuration Register 0 (SCCR0)       4-1         System Control and Configuration Register 1 (SCCR1)       4-1         System Control and Configuration Register 2 (SCCR2)       4-1         System Control and Configuration Register 2 (SCCR2)       4-1         System Control and Configuration Register 2 (SCCR2)       4-1         O Configuration       4-1 | 10<br>11<br>13<br>14<br>16 |

|   | 7.6   | Interrupts  |                                                      | 7-16  |

|---|-------|-------------|------------------------------------------------------|-------|

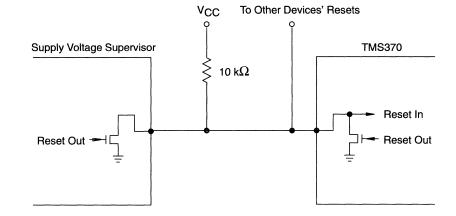

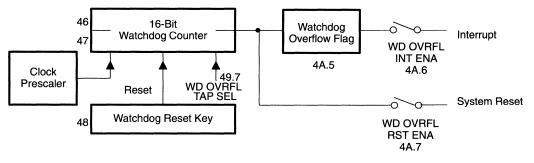

|   | 7.7   | Watchdog    | Timer                                                | 7-17  |

|   |       | 7.7.1       | Standard Watchdog Configuration (OTP/Reprogrammable  |       |

|   |       |             | EPROM Devices)                                       |       |

|   |       | 7.7.2       | Hard Watchdog Configuration (Mask-ROM Devices Only)  | 7-20  |

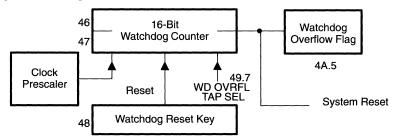

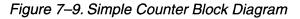

|   |       | 7.7.3       | Simple Counter Configuration (Mask-ROM Devices Only) | 7-22  |

|   |       | 7.7.4       | Summary of Watchdog Options                          | 7-23  |

|   | 7.8   | Low-Powe    | er Modes                                             | 7-24  |

|   |       | 7.8.1       | Halt Mode                                            | 7-24  |

|   |       | 7.8.2       | Standby Mode                                         | 7-24  |

|   | 7.9   | Timer 1 Co  | ontrol Registers                                     | 7-25  |

|   |       | 7.9.1       | Timer 1 Control Register 1 (T1CTL1)                  | 7-27  |

|   |       | 7.9.2       | Timer 1 Control Register 2 (T1CTL2)                  | 7-29  |

|   |       | 7.9.3       | Timer 1 Control Register 3 (T1CTL3)                  | 7-31  |

|   |       | 7.9.4       | Timer 1 Control Register 4 (T1CTL4)                  | 7-33  |

|   |       | 7.9.5       | Timer 1 Port Control Registers (T1PC1 and T1PC2)     | 7-35  |

|   |       | 7.9.6       | Timer 1 Interrupt Priority Control Register (T1PRI)  | 7-38  |

| - |       |             |                                                      |       |

| 8 |       |             |                                                      | . 8-1 |

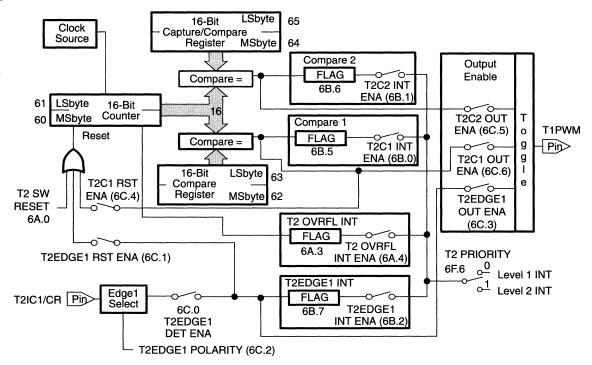

|   | Discu | sses the ar | chitecture and programming of the timer 2 module.    |       |

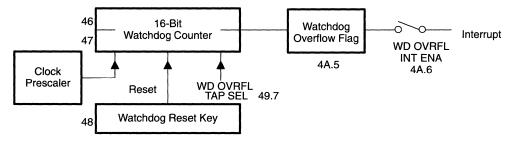

|   | 8.1   | Timer 2 Ov  | verview                                              | . 8-2 |

|   |       | 8.1.1       | Physical Description                                 | . 8-2 |

|   |       | 8.1.2       | Operating Modes                                      | . 8-3 |

|   |       | 8.1.3       | Control Registers                                    | . 8-4 |

|   | 8.2   | Timer 2 Co  | omponents                                            |       |

|   |       | 8.2.1       | 16-Bit Resettable Counter                            | . 8-5 |

|   |       | 8.2.2       | Compare Register                                     | . 8-5 |

|   |       | 8.2.3       | Capture Register (Dual Capture Mode Only)            | . 8-6 |

|   |       | 8.2.4       | Capture/Compare Register                             | . 8-7 |

|   | 8.3   | Operating   | Modes                                                | . 8-8 |

|   |       | 8.3.1       | Dual Compare Mode                                    | . 8-8 |

|   |       | 8.3.2       | Dual Capture Mode                                    | . 8-9 |

|   | 8.4   | Edge-Dete   | ection Circuitry                                     | 8-11  |

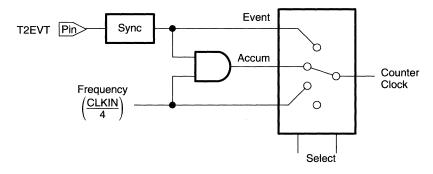

|   | 8.5   | Clock Sou   | Irces                                                | 8-12  |

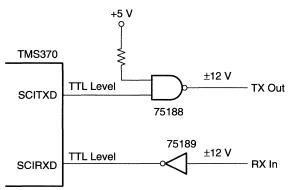

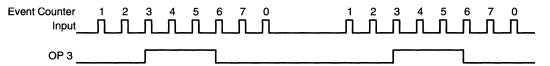

|   |       | 8.5.1       | Event Counter Mode                                   | 8-12  |

|   |       | 8.5.2       | Pulse Accumulator Mode                               | 8-13  |

|   | 8.6   | Interrupts  |                                                      | 8-13  |

|   | 8.7   | Low-Powe    | er Modes                                             | 8-14  |

|   | 8.8   | Timer 2 Co  | ontrol Registers                                     | 8-15  |

|   |       | 8.8.1       | Timer 2 Control Register 1 (T2CTL1)                  |       |

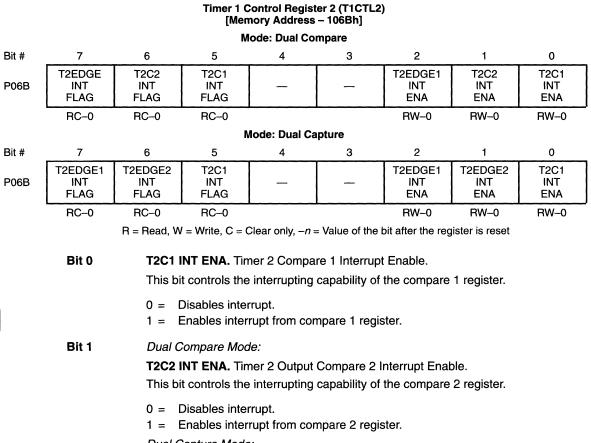

|   |       | 8.8.2       | Timer 2 Control Register 2 (T2CTL2)                  |       |

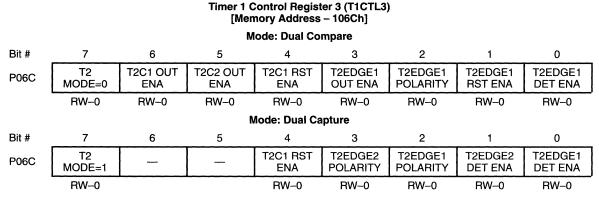

|   |       | 8.8.3       | Timer 2 Control Register 3 (T2CTL3)                  |       |

|   |       | 8.8.4       | Timer 2 Port Control Registers (T2PC1 and T2PC2)     |       |

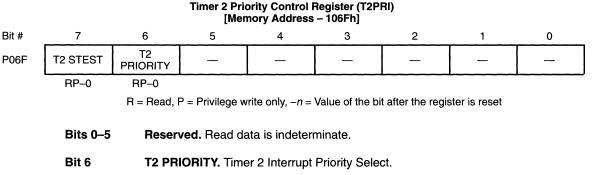

|   |       | 8.8.5       | Timer 2 Interrupt Priority Control Register (T2PRI)  |       |

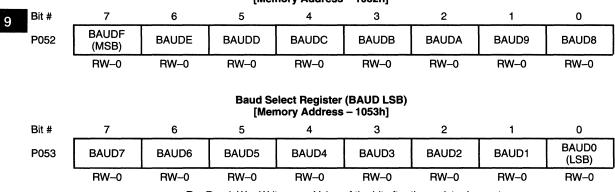

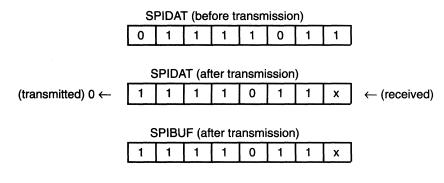

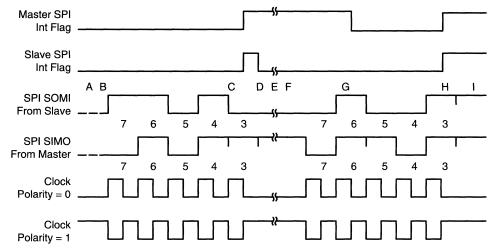

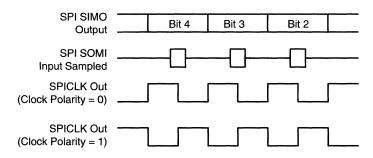

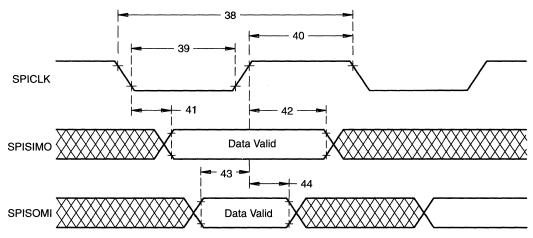

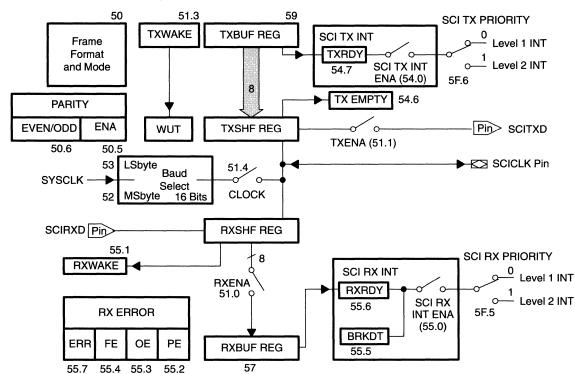

|                                                                                                                                                                       | 10.5<br>10.6<br>10.7<br>10.8<br>10.9 | Clock Sou<br>Initialization<br>SPI Exam | Inces       1         fon Upon Reset       1         iple       1         ol Registers       1         SPI Configuration Control Register (SPICCR)       1         SPI Operation Control Register (SPICTL)       1         Serial Input Buffer (SPIBUF)       1         Serial Data Register (SPIDAT)       1         SPI Port Control Registers (SPIPC1 and SPIPC2)       1         SPI Interrupt Priority Control Register (SPIPRI)       1 | 10-10<br>10-11<br>10-12<br>10-13<br>10-14<br>10-16<br>10-17<br>10-17<br>10-18 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

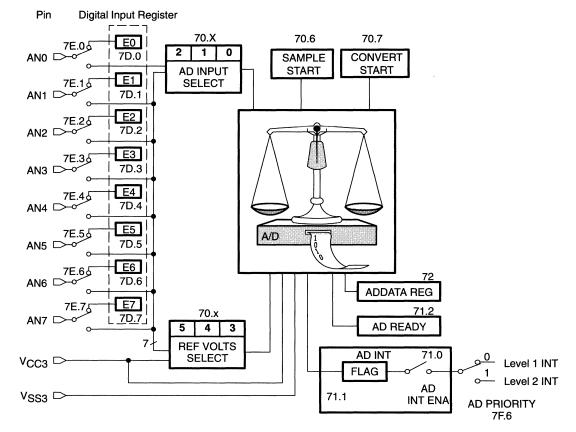

| 11                                                                                                                                                                    |                                      |                                         | al Converter Module                                                                                                                                                                                                                                                                                                                                                                                                                           | 11-1                                                                          |

|                                                                                                                                                                       |                                      |                                         | -Digital Converter (A/D) Overview                                                                                                                                                                                                                                                                                                                                                                                                             | 11 0                                                                          |

|                                                                                                                                                                       |                                      | 11.1.1                                  | Physical Description                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                               |

|                                                                                                                                                                       |                                      | 11.1.2                                  | Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |

|                                                                                                                                                                       | 11.2                                 |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                               |

|                                                                                                                                                                       |                                      | 11.2.1                                  | Input/Output Pins                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |

|                                                                                                                                                                       |                                      | 11.2.2                                  | Sampling Time                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                               |

|                                                                                                                                                                       |                                      | 11.2.3                                  | A/D Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                               |

|                                                                                                                                                                       |                                      | 11.2.4                                  | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11-5                                                                          |

|                                                                                                                                                                       |                                      | 11.2.5                                  | Programming Considerations                                                                                                                                                                                                                                                                                                                                                                                                                    | 11-6                                                                          |

|                                                                                                                                                                       | 11.3                                 | A/D Exam                                | ple Program                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11-7                                                                          |

|                                                                                                                                                                       | 11.4                                 | A/D Contr                               | ol Registers                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11-9                                                                          |

|                                                                                                                                                                       |                                      | 11.4.1                                  | Analog Control Register (ADCTL) 1                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |

|                                                                                                                                                                       |                                      | 11.4.2                                  | Analog Status and Interrupt Register (ADSTAT) 1                                                                                                                                                                                                                                                                                                                                                                                               |                                                                               |

|                                                                                                                                                                       |                                      | 11.4.3                                  | Analog Conversion Data Register (ADDATA) 1                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                               |

|                                                                                                                                                                       |                                      | 11.4.4                                  | Analog Port E Data Input Register (ADIN) 1                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                               |

|                                                                                                                                                                       |                                      | 11.4.5                                  | Analog Port E Input Enable Register (ADENA) 1                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                               |

|                                                                                                                                                                       |                                      | 11.4.6                                  | Analog Interrupt Priority Register (ADPRI) 1                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                               |

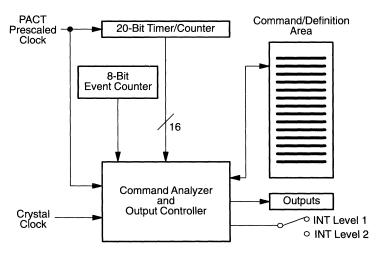

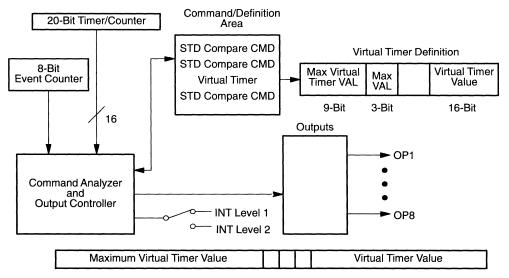

| 12                                                                                                                                                                    |                                      |                                         | Acquisition and Control Timer (PACT)                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                               |

| Discusses the architecture and programming of the programmable acquisition and<br>timer (PACT) module. Even if you have extensive experience with microcontroller tim |                                      |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                               |

|                                                                                                                                                                       | should                               |                                         | chapter to fully understand how to use the TMS370 PACT module.                                                                                                                                                                                                                                                                                                                                                                                |                                                                               |

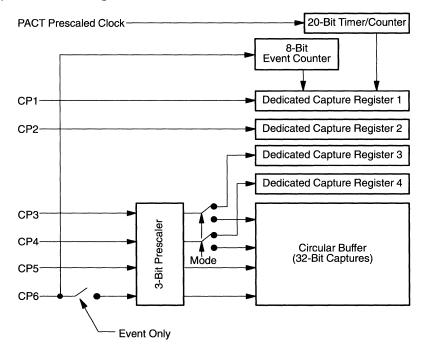

|                                                                                                                                                                       | 12.1                                 | PACT Ove                                | erview                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                               |

|                                                                                                                                                                       |                                      | 12.1.1                                  | Physical Description                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                               |

|                                                                                                                                                                       |                                      | 12.1.2                                  | Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |

|                                                                                                                                                                       | 12.2                                 | •                                       | eration                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |

|                                                                                                                                                                       |                                      | 12.2.1                                  | Hardware Pins                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                               |

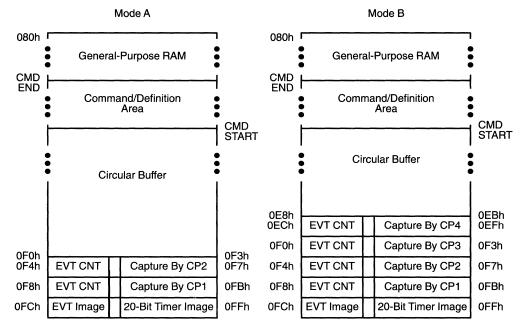

|                                                                                                                                                                       |                                      | 12.2.2                                  | Memory Organization                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                               |

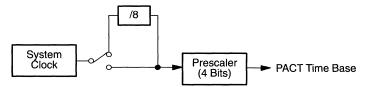

|                                                                                                                                                                       |                                      | 12.2.3                                  | Time Base                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                               |

|                                                                                                                                                                       |                                      | 12.2.4                                  | Command/Definition File Format                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                               |

|                                                                                                                                                                       |                                      | 12.2.5                                  | Available Time Slots                                                                                                                                                                                                                                                                                                                                                                                                                          | 12-7                                                                          |

| 13                         | Sumn                       | uage Instruction Set | -1                                                       |    |  |  |

|----------------------------|----------------------------|----------------------|----------------------------------------------------------|----|--|--|

|                            | 13.1 Instruction Operation |                      |                                                          |    |  |  |

|                            | 13.2                       |                      | efinitions                                               |    |  |  |

|                            | 13.3                       |                      | ng Modes                                                 |    |  |  |

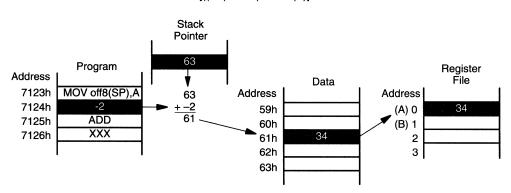

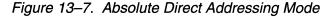

|                            |                            | 13.3.1               | General Addressing Modes 13-                             |    |  |  |

|                            |                            | 13.3.2               | Extended Addressing Modes 13-1                           |    |  |  |

|                            |                            | 13.3.3               | Additional Addressing Modes 13-1                         |    |  |  |

|                            |                            | 13.3.4               | Status Register                                          |    |  |  |

|                            | 13.4                       | Instructior          | n Set Overview                                           |    |  |  |

|                            | 13.5                       |                      | n Set Descriptions                                       |    |  |  |

| 1/                         | Docio                      | n Aide               |                                                          | .1 |  |  |

| 14                         | -                          |                      |                                                          |    |  |  |

|                            |                            | -                    | system development, contains sample TMS370 applications. |    |  |  |

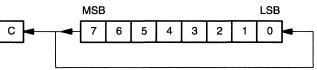

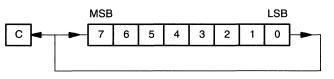

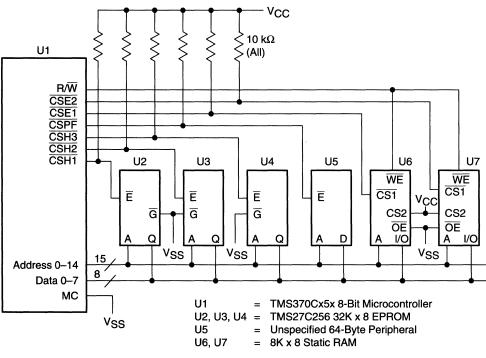

|                            | 14.1                       |                      | puter Interface Example 14                               |    |  |  |

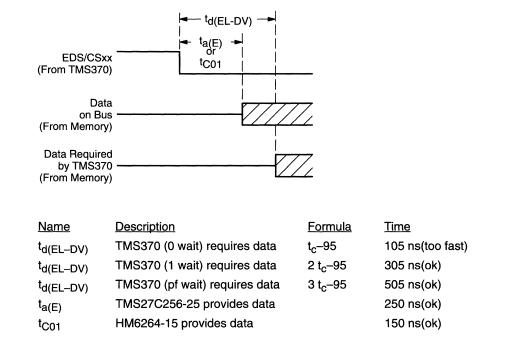

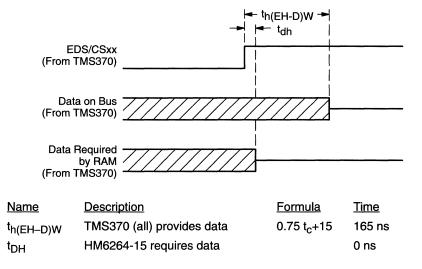

|                            |                            | 14.1.1               | Read Cycle Timing 14                                     |    |  |  |

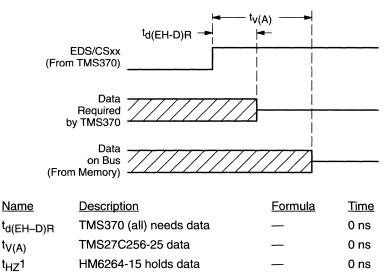

|                            |                            | 14.1.2               | Write Cycle Timing 14                                    |    |  |  |

|                            |                            | 14.1.3               | Design Options 14-1                                      |    |  |  |

|                            |                            | 14.1.4               | Bank Switching Examples 14-1                             |    |  |  |

|                            | 14.2                       | -                    | ning With the TMS370 Family 14-1                         |    |  |  |

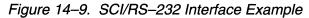

| 14.3 Serial Communications |                            |                      |                                                          |    |  |  |

|                            |                            | 14.3.1               | SPI Port Interfacing 14-1                                |    |  |  |

|                            |                            | 14.3.2               | SCI Port Interfacing 14-1                                |    |  |  |

|                            | 14.4                       | U U                  | -Digital Converter                                       |    |  |  |

|                            | 14.5                       |                      | dule                                                     |    |  |  |

|                            |                            | 14.5.1               | Time After Event Example 14-2                            |    |  |  |

|                            |                            | 14.5.2               | Double Event Compare Command Example    14-2             |    |  |  |

|                            |                            | 14.5.3               | PACT SCI Example 14-2                                    |    |  |  |

|                            | 14.6                       |                      | outines                                                  |    |  |  |

|                            |                            | 14.6.1               | T1PWM Pin Set-Up 14-3                                    |    |  |  |

|                            |                            | 14.6.2               | Clear RAM                                                |    |  |  |

|                            |                            | 14.6.3               | RAM Self Test 14-3                                       |    |  |  |

|                            |                            | 14.6.4               | ROM Checksum 14-3                                        |    |  |  |

|                            |                            | 14.6.5               | Binary-to-BCD Conversion 14-3                            |    |  |  |

|                            |                            | 14.6.6               | BCD-to-Binary Conversion 14-3                            |    |  |  |

|                            |                            | 14.6.7               | BCD String Addition 14-3                                 |    |  |  |

|                            |                            | 14.6.8               | Fast Parity    14-3                                      |    |  |  |

|                            |                            | 14.6.9               | Bubble Sort 14-3                                         |    |  |  |

|                            |                            | 14.6.10              | Table Search   14-3                                      |    |  |  |

|                            |                            | 14.6.11              | 16-by-16 (32-Bit) Multiplication 14-4                    |    |  |  |

|                            |                            | 14.6.12              | Keyboard Scan 14-4                                       |    |  |  |

|                            |                            | 14.6.13              | Divide 1 14-4                                            |    |  |  |

|                            |                            | 14.6.14              | Divide 2                                                 | 14 |  |  |

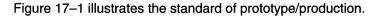

| 17 | Customer Information                                                                 |                                                  |                                                                        |    |  |  |

|----|--------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------|----|--|--|

|    | Describes mask-ROM prototyping, TMS370 physical characteristics, and parts ordering. |                                                  |                                                                        |    |  |  |

|    | 17.1                                                                                 | Mask-RO                                          | M Prototype and Production Flow 17-                                    | ·2 |  |  |

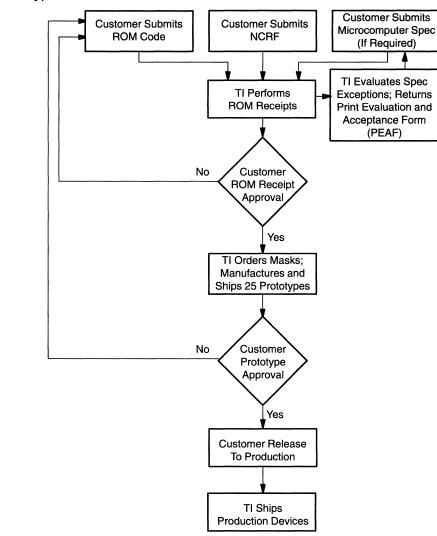

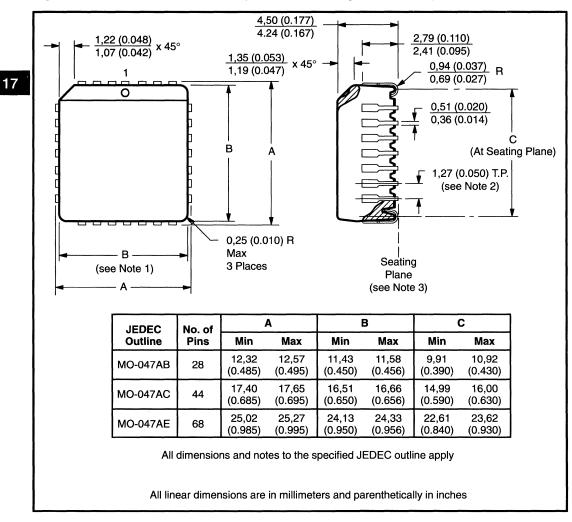

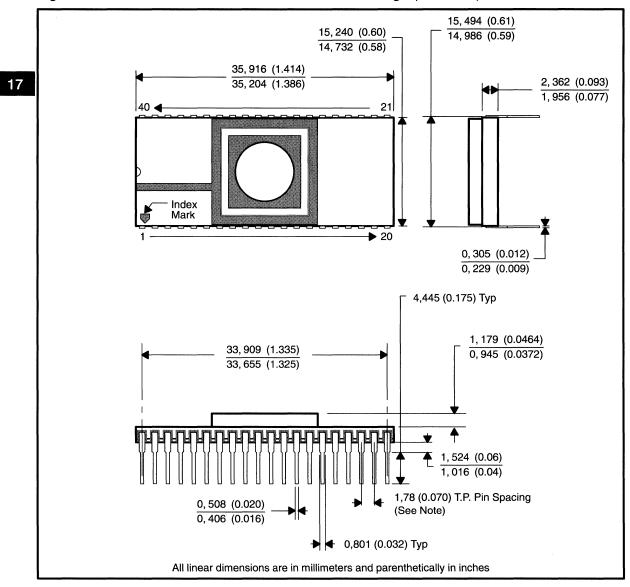

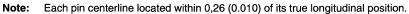

|    | 17.2                                                                                 | Mechanic                                         | al Package Information                                                 | •6 |  |  |

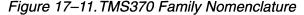

|    | 17.3                                                                                 | TMS370                                           | Family Numbering and Symbol Conventions                                | 5  |  |  |

|    |                                                                                      | 17.3.1                                           | Production Device Prefix Designators 17-1                              | 5  |  |  |

|    |                                                                                      | 17.3.2                                           | Support Device Prefix Designators 17-1                                 | 6  |  |  |

|    |                                                                                      | 17.3.3                                           | Device Numbering Conventions 17-1                                      | 6  |  |  |

|    |                                                                                      | 17.3.4                                           | Device Symbols                                                         | 7  |  |  |

|    | 17.4                                                                                 | Ordering                                         | Information for Development Support Tools                              | 9  |  |  |

|    |                                                                                      | 17.4.1                                           | TMS370 Macro Assembler, Linker, C Compiler, and Utilities 17-1         | 9  |  |  |

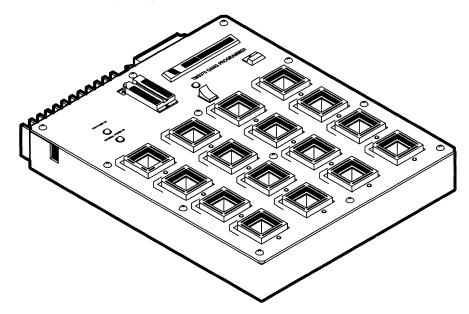

|    |                                                                                      | 17.4.2                                           | TMS370 Design Kit                                                      | 9  |  |  |

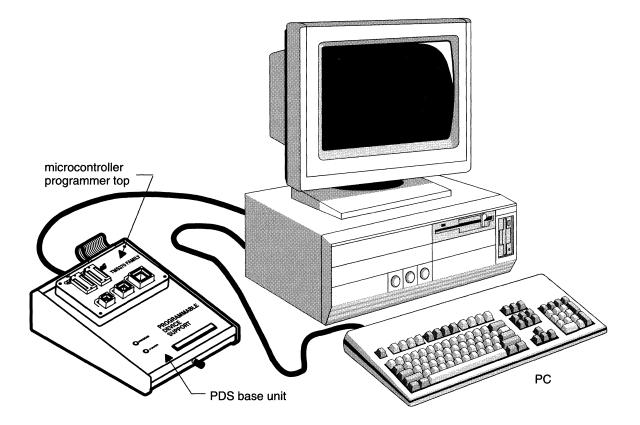

|    |                                                                                      | 17.4.3                                           | TMS370 Microcontroller Programmer 17-1                                 | 9  |  |  |

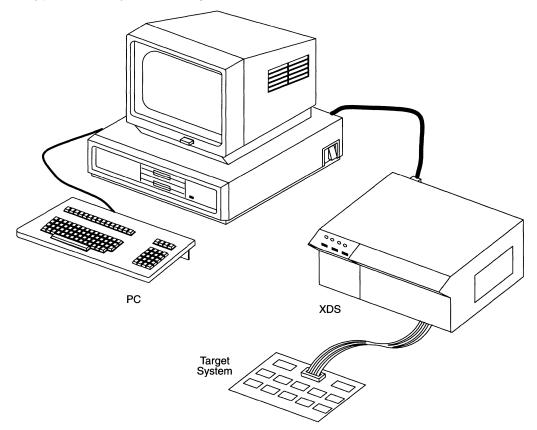

|    |                                                                                      | 17.4.4                                           | TMS370 XDS Systems                                                     | 20 |  |  |

|    |                                                                                      | 17.4.5                                           | TMS370 Compact Development Tool 17-2                                   | 20 |  |  |

|    |                                                                                      | 17.4.6                                           | XDS Upgrade (Available in Europe Only) 17-2                            |    |  |  |

|    |                                                                                      | 17.4.7                                           | XDS Target Connectors 17-2                                             | 20 |  |  |

|    |                                                                                      |                                                  |                                                                        |    |  |  |

| Α  | Differ                                                                               | ences Bet                                        | ween a TMS370CxxxA Device and a TMS370Cxxx Device A-                   | -1 |  |  |

|    |                                                                                      |                                                  | differences between the TMS370CxxxA devices that are described in this |    |  |  |

|    | manu                                                                                 | al and the                                       | TMS370Cxxx devices.                                                    |    |  |  |

|    | A.1                                                                                  | Watchdog                                         | g Options A-                                                           | ·2 |  |  |

|    | A.2                                                                                  | Timer 1 C                                        | Control Register 2 (T1CTL2) Bits A-                                    | .3 |  |  |

|    | A.3                                                                                  | System C                                         | Control and Configuration Register 2 (SCCR2) Bits A-                   | ·4 |  |  |

|    | A.4                                                                                  | V <sub>CC1</sub> and                             | I V <sub>CC2</sub> Pins A-                                             | .4 |  |  |

|    | A.5                                                                                  | Low-Pow                                          | er and Idle Modes A-                                                   | ·4 |  |  |

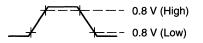

|    | A.6                                                                                  | Electrical                                       | Specifications A-                                                      | ·5 |  |  |

|    |                                                                                      | A.6.1                                            | Differences for TMS370Cx5x Devices A-                                  | -5 |  |  |

|    |                                                                                      | A.6.2                                            | Differences in SCI and SPI Specifications A-                           | ·6 |  |  |

|    | <b>A</b> .7                                                                          | Summary                                          | of Differences A·                                                      | ·7 |  |  |

| -  | Desite                                                                               |                                                  |                                                                        |    |  |  |

| В  |                                                                                      |                                                  | Метоту Мар В-                                                          | •1 |  |  |

|    |                                                                                      |                                                  | peripheral file and control bit information.                           |    |  |  |

|    | B.1                                                                                  | •                                                | Il File Frame 1: System Configuration Registers                        |    |  |  |

|    | B.2                                                                                  | •                                                | Il File Frame 2: Digital Port Control Registers B-                     |    |  |  |

|    | B.3                                                                                  | Periphera                                        | Il File Frame 3: SPI Control RegistersB                                | -4 |  |  |

|    | B.4                                                                                  | -                                                | Il File Frame 4: Timer 1 Control Registers B-                          |    |  |  |

|    | B.5                                                                                  | Periphera                                        | Il File Frame 4: PACT Control Registers B-                             | •6 |  |  |

|    | B.6                                                                                  | Periphera                                        | Il File Frame 5: SCI Control Registers B-                              | •7 |  |  |

|    | B.7                                                                                  | Periphera                                        | Il File Frame 6: Timer 2 Control Registers B-                          | -8 |  |  |

|    | B.8                                                                                  | Il File Frame 7: A/D Converter Control Registers | -9                                                                     |    |  |  |

# Figures

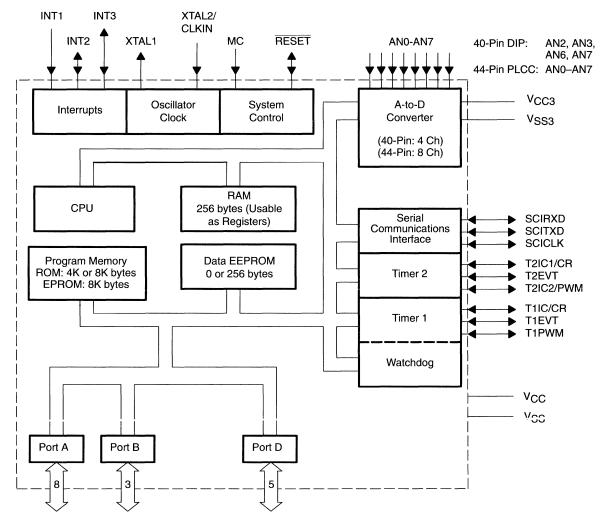

| 1–1  | TMS370Cx1x Block Diagram 1-11                                     |

|------|-------------------------------------------------------------------|

| 1–2  | TMS370Cx2x Block Diagram 1-12                                     |

| 1–3  | TMS370Cx3x Block Diagram 1-13                                     |

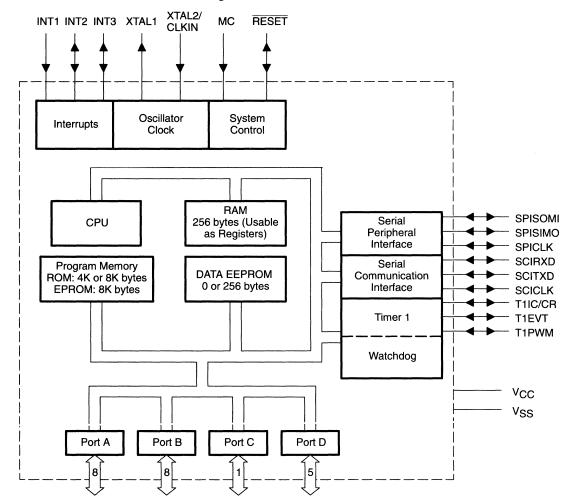

| 1–4  | TMS370Cx4x Block Diagram 1-14                                     |

| 1–5  | TMS370Cx5x Block Diagram 1-15                                     |

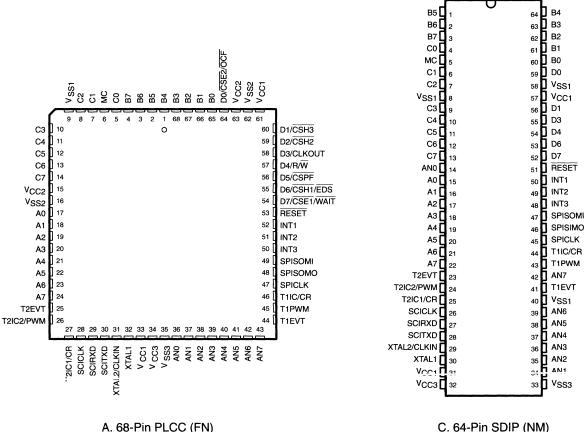

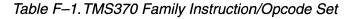

| 2–1  | Pinouts for TMS370Cx1x                                            |

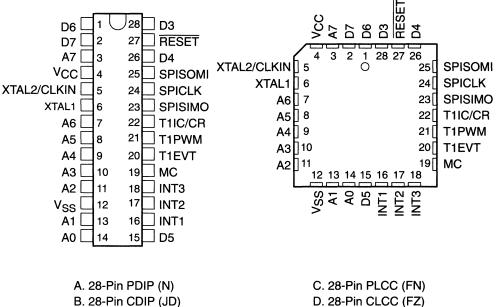

| 2–2  | Pinouts for TMS370Cx2x 2-4                                        |

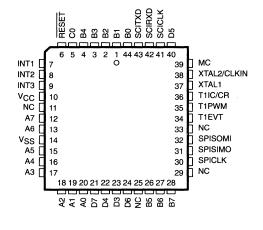

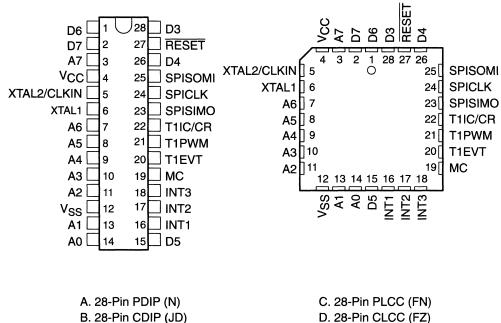

| 2–3  | Pinout for TMS370Cx3x                                             |

| 2–4  | Pinouts for TMS370Cx4x                                            |

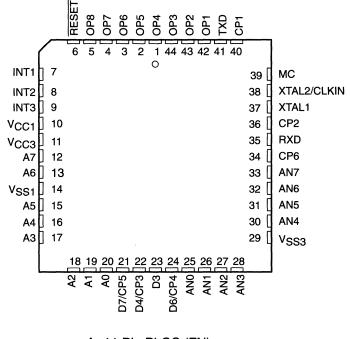

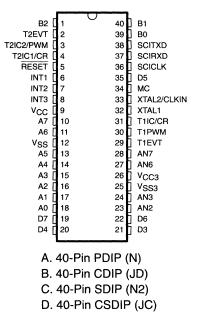

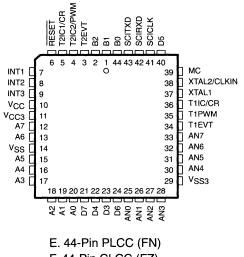

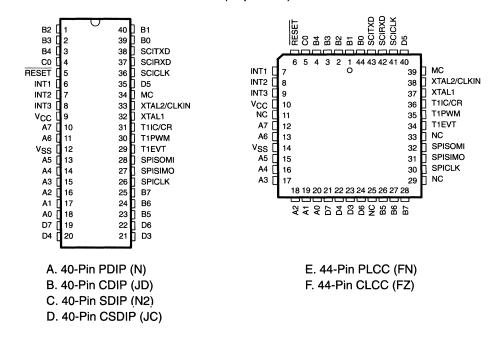

| 2–5  | Pinouts for TMS370Cx5x                                            |

| 3–1  | Programmer's Model 3-3                                            |

| 3–2  | Stack Example                                                     |

| 3–3  | Program Counter After Reset 3-7                                   |

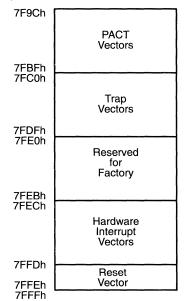

| 3–4  | TMS370 Memory Map 3-8                                             |

| 3–5  | Register File Addresses 3-9                                       |

| 3–6  | Microcomputer Single-Chip Mode                                    |

| 3–7  | Microcomputer Mode With Function A Expansion                      |

| 3–8  | Microcomputer Mode With Function B Expansion                      |

| 3–9  | Microprocessor Mode Without Internal Memory 3-22                  |

| 3–10 | Microprocessor Mode With Internal Program Memory 3-24             |

| 3–11 | Memory Operating Modes 3-26                                       |

| 4–1  | Correct Method to Enter Halt Mode 4-9                             |

| 4–2  | Improper Method to Enter Halt Mode 4-10                           |

| 4–3  | Peripheral File Frame 2: Digital Port Control Registers 4-17      |

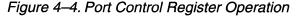

| 4–4  | Port Control Register Operation 4-18                              |

| 4–5  | System Interface Example 4-23                                     |

| 5–1  | Interrupt Control 5-3                                             |

| 5–2  | Peripheral File Frame 1: External Interrupt Control Registers 5-7 |

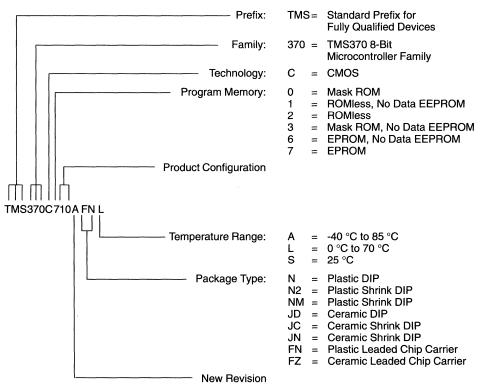

| 5–3  | Interrupt 1 Block Diagram 5-9                                     |

| 5–4  | Interrupts 2 and 3 Block Diagram 5-9                              |

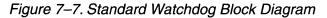

| 5–5  | Typical Reset Circuit                                             |

| 5–6  | Typical Reset Circuit Using a Supply Voltage Supervisor           |

| 6–1  | Write Protection Bits in an EEPROM Array 6-3                      |

| 6–2  | EEPROM Programming Example                                        |

| 6–3  | EPROM Programming Operation                                       |

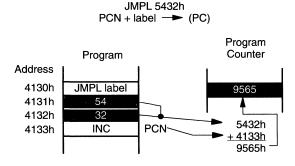

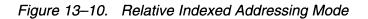

| 13–10 | Relative Indexed Addressing Mode                        | 13-14  |

|-------|---------------------------------------------------------|--------|

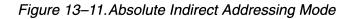

| 13–11 | Absolute Indirect Addressing Mode                       | 13-14  |

| 13–12 | Relative Indirect Addressing Mode                       | 13-15  |

| 13–13 | Absolute Offset Indirect Addressing Mode                | 13-15  |

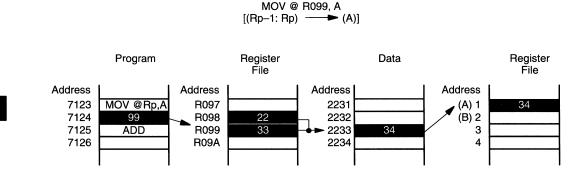

| 13–14 | Relative Offset Indirect Addressing Mode                | 13-16  |

| 13–15 | Status Register (ST)                                    |        |

| 14–1  | Microcomputer Interface Example                         | . 14-2 |