# MOS Memory Commercial and Military Specifications

## Data Book

### MOS Memory Data Book

Commercial and Military

Specifications

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Texas Instruments products are not intended for use in life-support appliances, devices, or systems. Use of a TI product in such applications without the written consent of the appropriate TI officer is prohibited.

Copyright © 1991, Texas Instruments Incorporated

|   | General Information                              | 11  |

|---|--------------------------------------------------|-----|

|   | Selection Guide                                  | 2   |

|   | Alternate Source Directory                       | 3   |

|   | Glossary/Timing Conventions/Data Sheet Structure | 4   |

| , | Dynamic RAMs                                     | 5   |

|   | Dynamic RAM Modules                              | 6   |

|   | EPROMs/OTPs/Flash EEPROMs                        | 7   |

|   | Application Specific Memories                    | 8   |

|   | Military Products                                | . 9 |

|   | Datapath VLSI Products                           | 10  |

|   | Logic Symbols                                    | 11% |

|   | Quality and Reliability                          | 12  |

|   | Electrostatic Discharge Guidelines               | 13  |

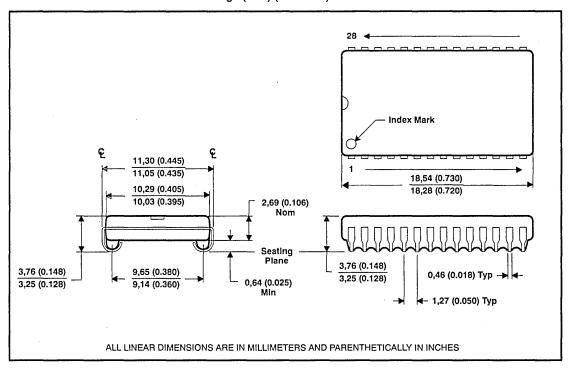

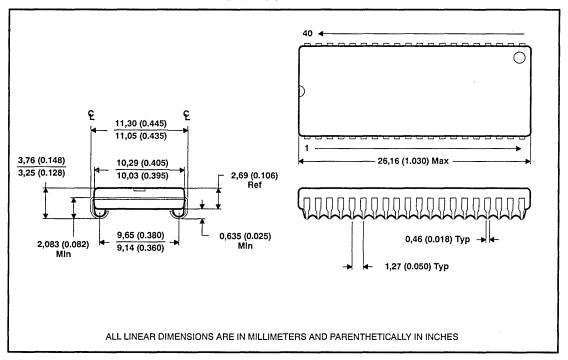

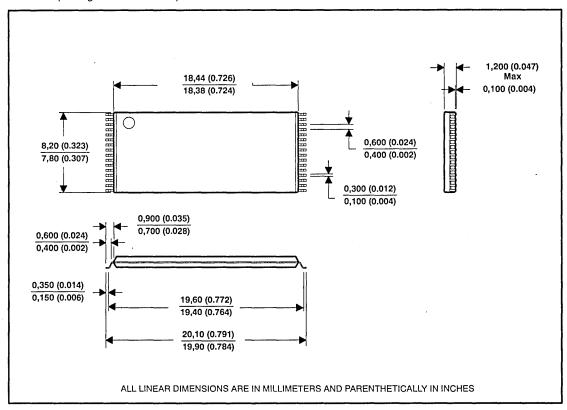

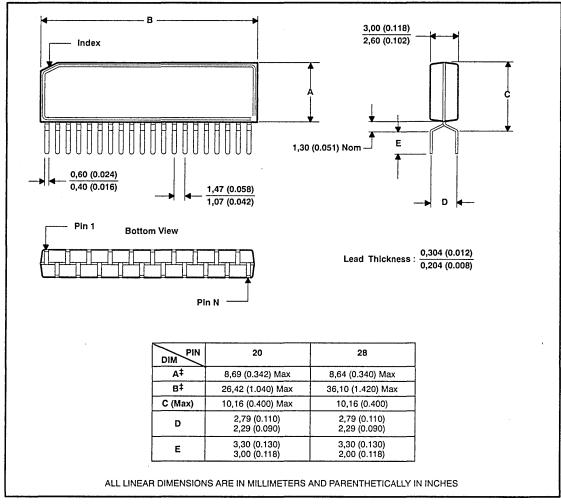

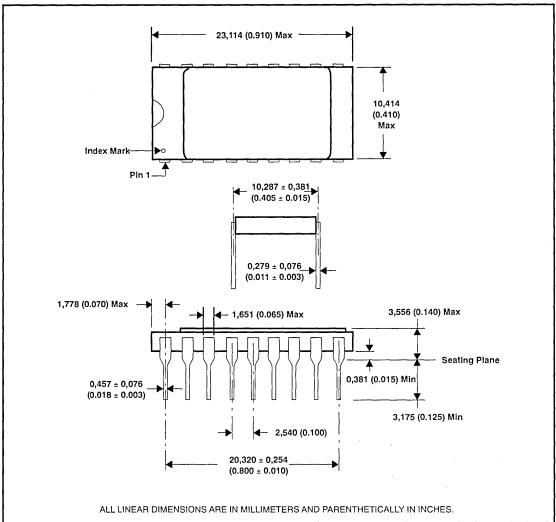

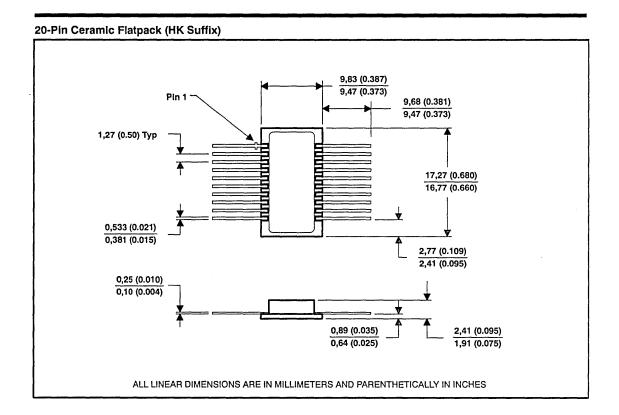

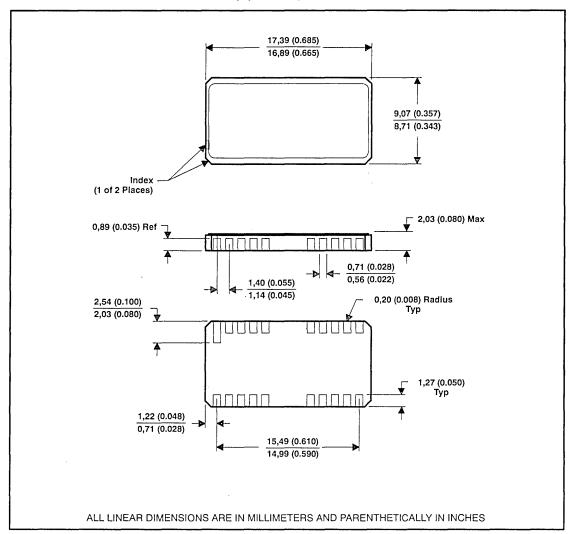

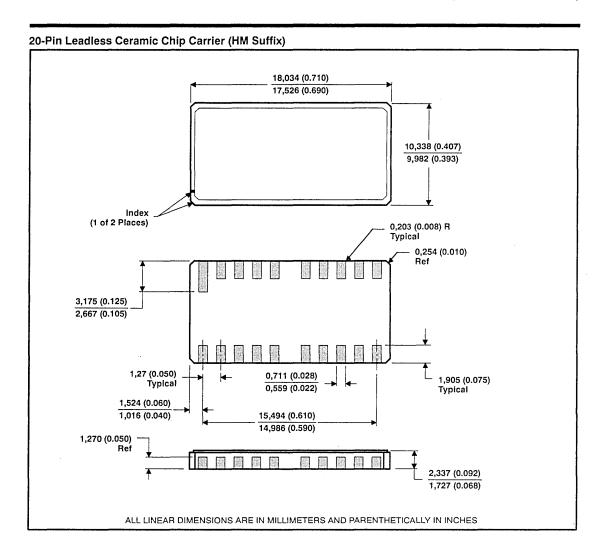

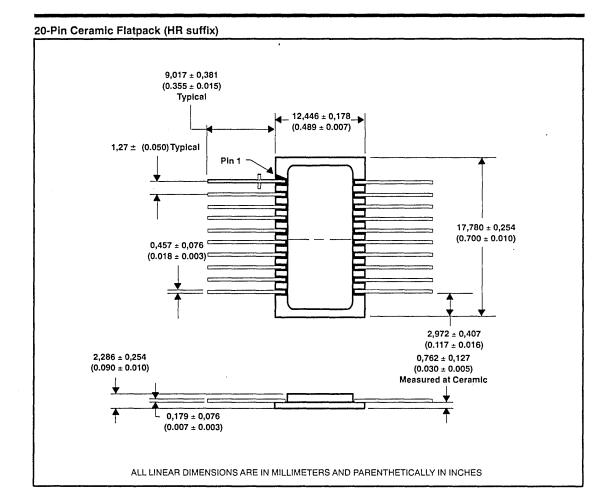

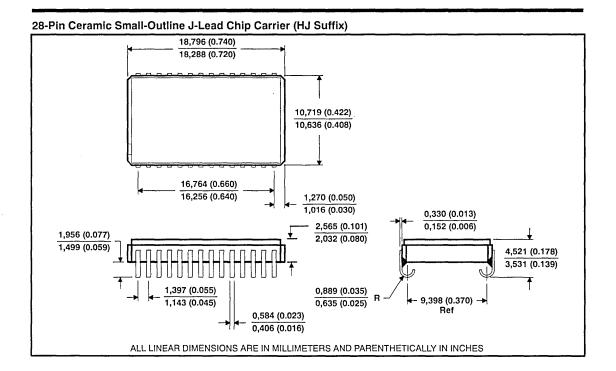

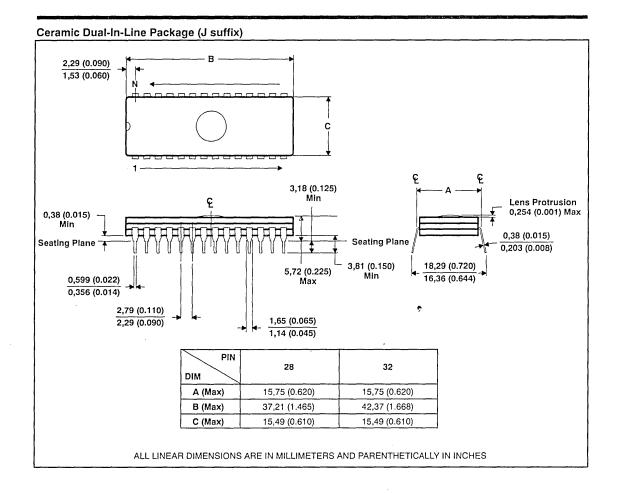

|   | Mechanical Data                                  | 14  |

| j  | General Information                              |

|----|--------------------------------------------------|

| 2  | Selection Guide                                  |

| 3  | Alternate Source Directory                       |

| 4  | Glossary/Timing Conventions/Data Sheet Structure |

| 5  | Dynamic RAMs                                     |

| 6  | Dynamic RAM Modules                              |

| 7  | EPROMs/OTPs/Flash EEPROMs                        |

| 8  | Application Specific Memories                    |

| 9  | Military Products                                |

| 10 | Datapath VLSI Products                           |

| 11 | Logic Symbols                                    |

| 12 | Quality and Reliability                          |

| 13 | Electrostatic Discharge Guidelines               |

| 14 | Mechanical Data                                  |

#### INTRODUCTION

The 1991 MOS Memory Data Book from Texas Instruments includes complete detailed specifications on the expanding MOS Memory product line including Dynamic Random-Access Memories (DRAMs), Single-In-Line Package DRAM Memory Modules (SIPs), Erasable Programmable Read-Only Memories (EPROMs), One-Time Programmable Read-Only Memories (OTP PROMs), Electrically Erasable Programmable Read-Only Memories (Flash EEPROMs), and Application Specific Memories (ASMs). Also included are military specifications for DRAMs, EPROMs, and ASMs, as well as specifications for the Datapath VLSI Memory Management products.

The data book is divided into 14 chapters. Below you will find a brief description of each chapter.

Chapter 1. General Information – Includes an alphanumeric index for quickly finding device numbers, a part number guide with ordering information, and an IC Line-up chart for a quick overview.

Chapter 2. Selection Guide – An easy-to-use reference guide that includes specific device information. Page numbers are also shown for easy access to the detailed specifications.

Chapter 3. Alternate Source Directory – Lists alternate vendor part numbering examples in addition to alternate sources for TI devices (based on published data).

Chapter 4. Glossary/Timing Conventions/Data Sheet Structure – Defines terms and standards used throughout the data book.

Chapters 5 - 10. Product specifications for over 100 devices can be found in these sections.

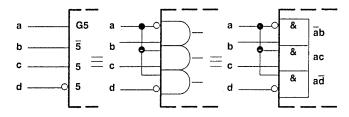

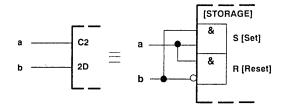

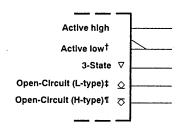

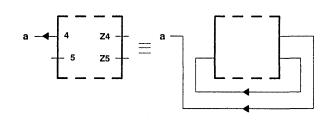

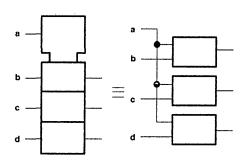

Chapter 11. Logic Symbols – Includes an explanation and examples of the IEEE standard.

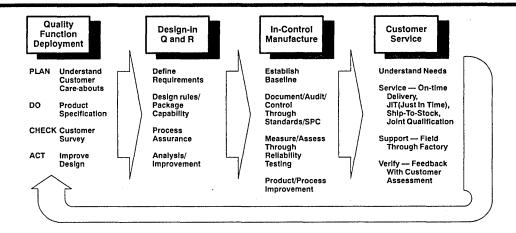

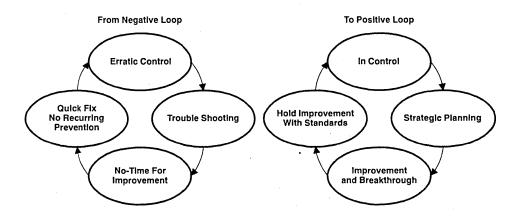

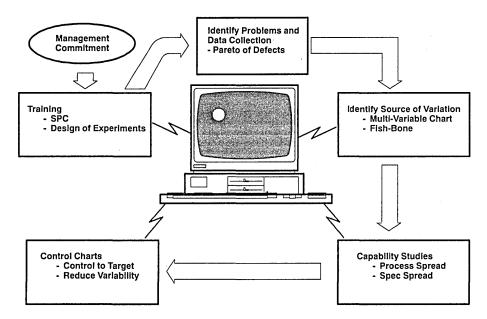

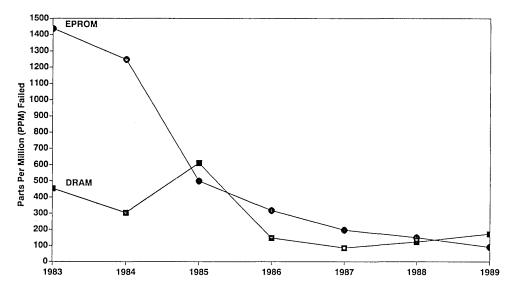

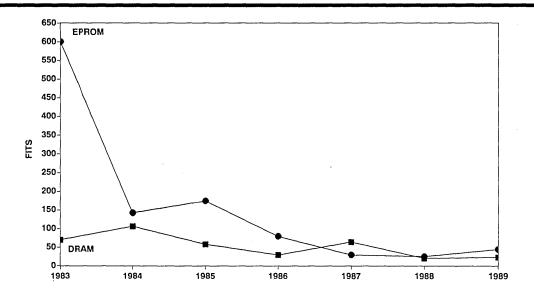

Chapter 12. Quality and Reliability – Details selected processes and the philosophies of Texas Instruments that are used to ensure high quality standards.

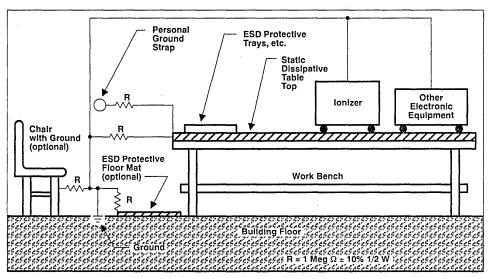

Chapter 13. Electrostatic Discharge Guidelines – Because all MOS Memory devices are ESD-sensitive, handling guidelines are included.

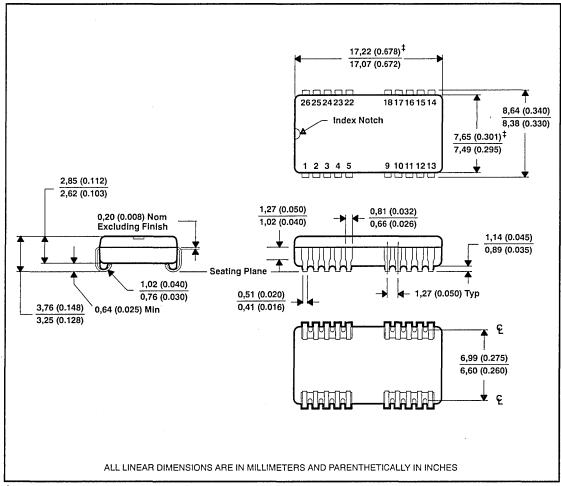

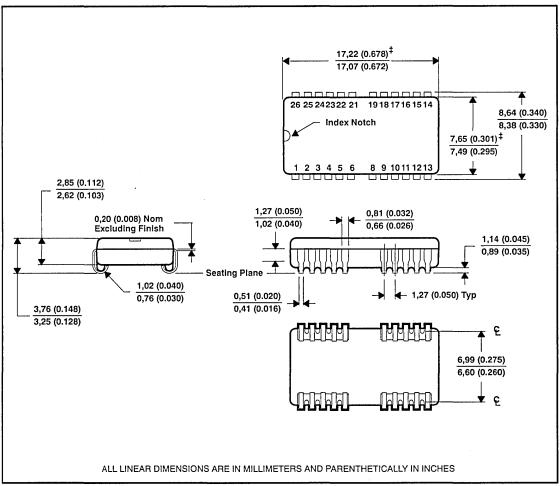

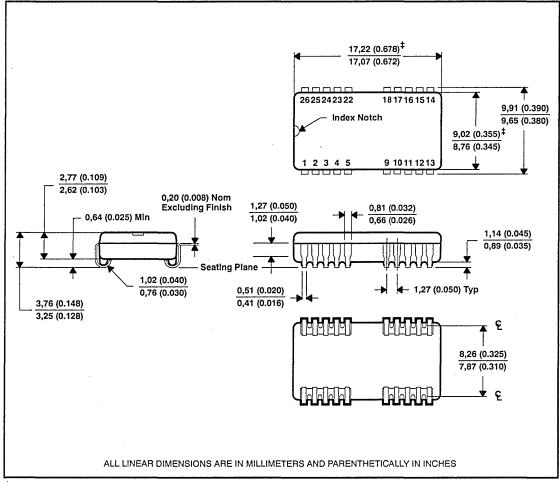

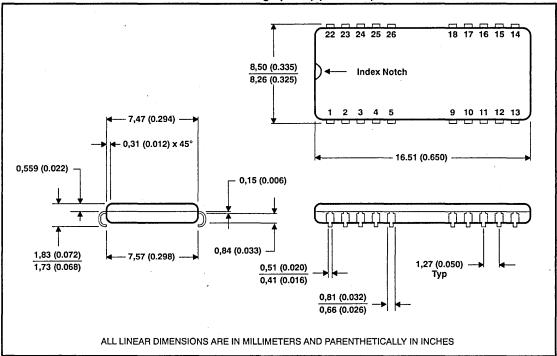

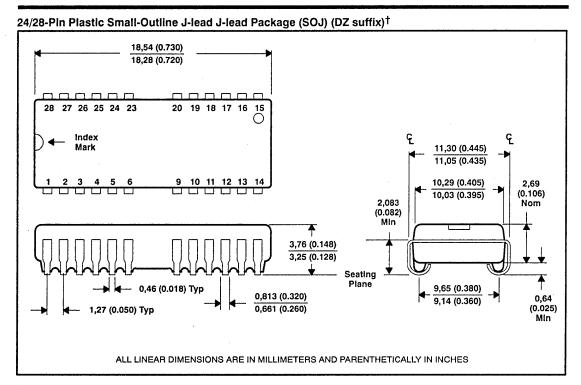

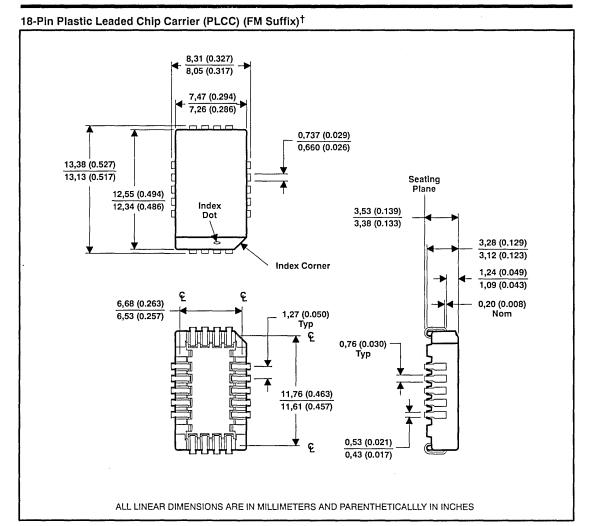

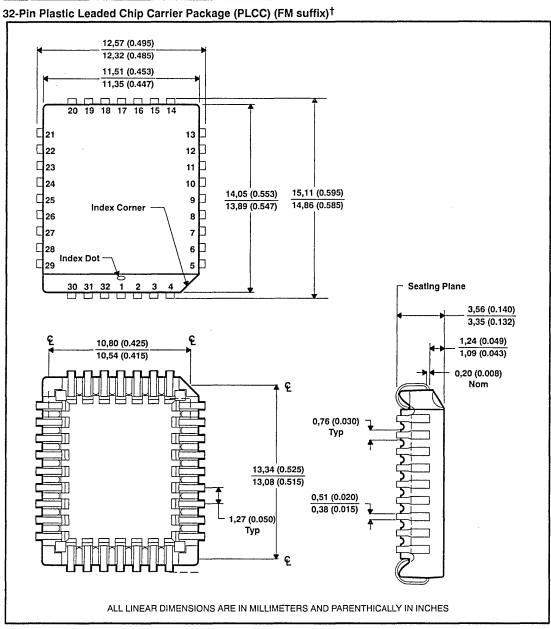

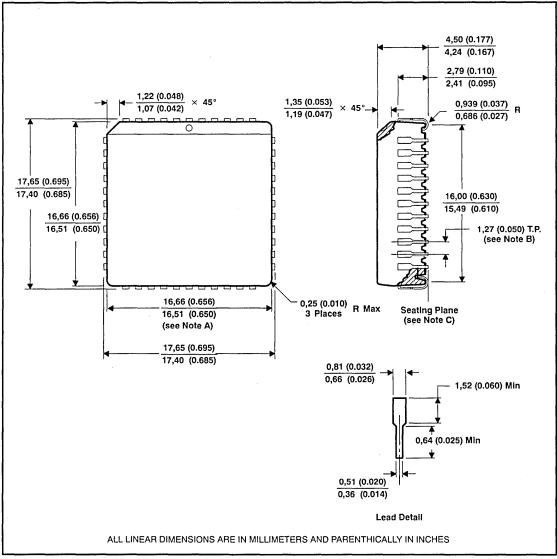

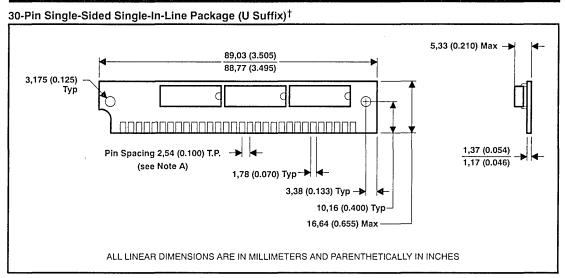

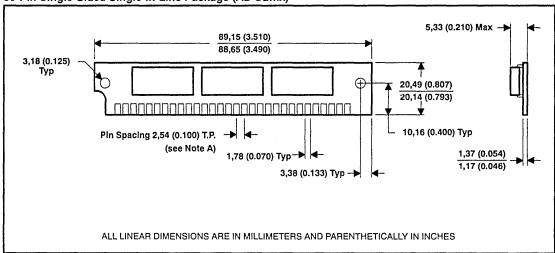

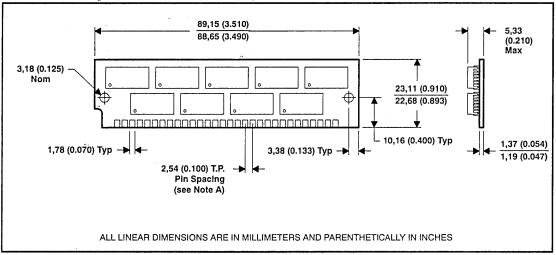

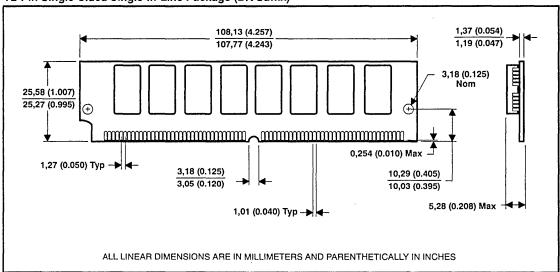

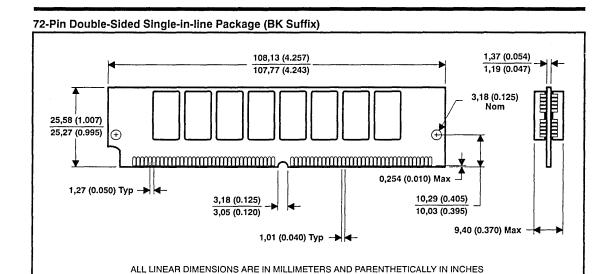

Chapter 14. Mechanical Data – Detailed package drawings and specifications are shown in this section.

Additional and/or updated information on these products is available from:

Texas Instruments Customer Response Center P.O. Box 809066 Dallas, Texas 75380-9066 1-800-232-3200

For ordering information or further assistance please contact your nearest Texas Instruments Sales Office or Distributor as listed in the back of this book.

### **Table of Contents**

| CHAPTER 1. GE                                                                                                  | NERAL INFORMAT                                                                                                                                        | ION                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ordering Inform<br>DRAM/VRA<br>DRAM Mod<br>EPROM/OT<br>MOS Memory I                                            | ation .M/FMEMule P PROM/Flash EEP C Line-up                                                                                                           | 1- 1- 1- 1- ROM 1- 1- 1- 1- 1- 1-                                                                                                                                                                                                                                                                                                                                                                                                            |

| CHAPTER 2. SE                                                                                                  | LECTION GUIDE                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DRAM Module<br>EPROM/FLASH<br>OTP PROM                                                                         | I EEPROM                                                                                                                                              | 2-<br>                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CHAPTER 3. AL                                                                                                  | TERNATE SOURCE                                                                                                                                        | DIRECTORY                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DRAM Module<br>EPROM/FLASH                                                                                     | EEPROM/OTP PRO                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CHAPTER 4. GL                                                                                                  | OSSARY/TIMING C                                                                                                                                       | ONVENTIONS/DATA SHEET STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                                              |

| Operating Cond<br>Timing Diagram                                                                               | itions and Characteris Conventions                                                                                                                    | ries                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CHAPTER 5. DY                                                                                                  | NAMIC RAMS                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TMS44C256<br>TMS4C1024<br>TMS4C1025<br>TMS4C1027<br>TMS48C128<br>TMS48C138<br>TMS44100<br>TMS44101<br>TMS44400 | 1 048 576-bit<br>1 048 576-bit<br>1 048 576-bit<br>1 048 576-bit<br>1 048 576-bit<br>1 048 576-bit<br>4 194 304-bit<br>4 194 304-bit<br>4 194 304-bit | (256K × 4) Enhanced Page Mode       5-         (1024K × 1) Enhanced Page Mode       5-2         (1024K × 1) Nibble Mode       5-2         (1024K × 1) Static Column Decode Mode       5-2         (128K × 8) Enhanced Page Mode       5-6         (128K × 8) Write-Per-Bit Operation       5-6         (4096K × 1) Enhanced Page Mode       5-8         (4096K × 1) Nibble Mode       5-10         (1024K × 4) Enhanced Page Mode       5-12 |

| TMS44410                                                                                                       | 4 194 304-bit                                                                                                                                         | (1024K × 4) Write-Per-Bit Operation 5-14                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | TMS416100     | 16 777 216-bit | (16 384K × 1) Enhanced Page Mode 5-165 |

|----|---------------|----------------|----------------------------------------|

|    | TMS416400     | 16 777 216-bit | (4096K × 4) Enhanced Page Mode 5-187   |

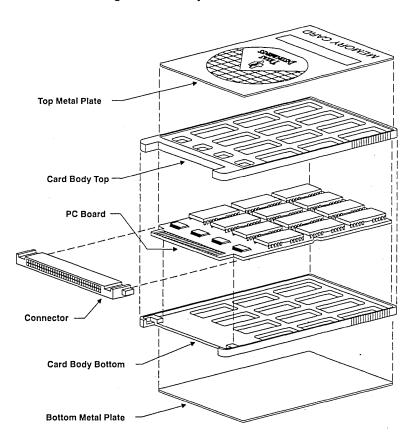

| C  | HAPTER 6. DYN | NAMIC RAM MOD  | DULES                                  |

|    | TM256GU9C     | 2 359 296-bit  | (256K × 9) Single-Sided 6-1            |

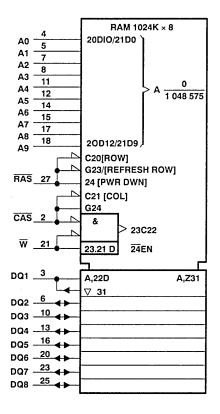

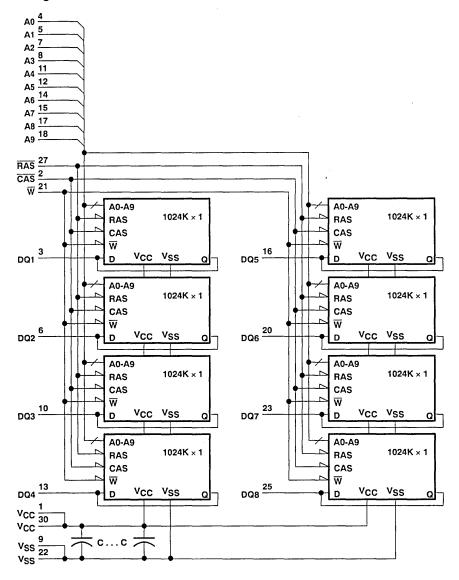

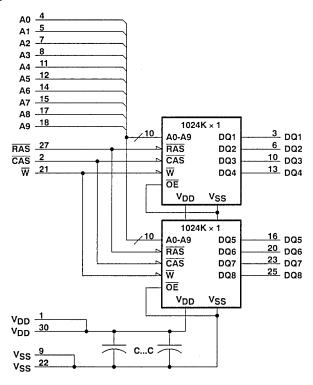

|    | TM024GAD8     | 8 388 608-bit  | (1024K × 8) Single-Sided 6-7           |

|    | TM124GU8A     | 8 388 608-bit  | (1024K × 8) Single-Sided               |

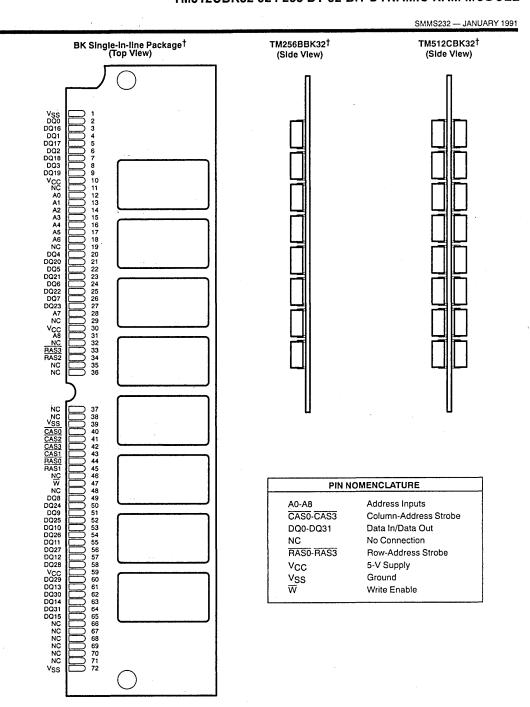

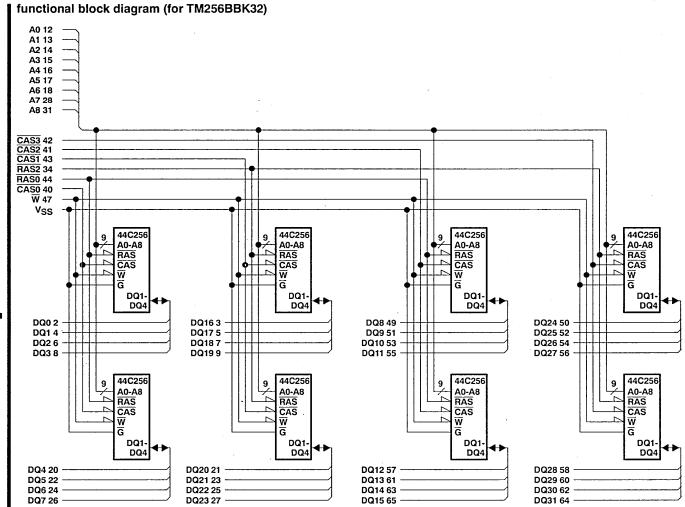

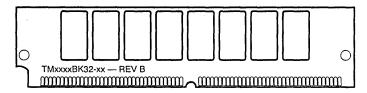

|    | TM256BBK32    | 8 388 608-bit  | (256K × 32) Single-Sided               |

|    | TM024EAD9     | 9 437 184-bit  | (1024K × 9) Single-Sided               |

|    | TM124EAD9B    | 9 437 184-bit  | (1024K × 9) Single-Sided               |

|    | TM124EAD9C    | 9 437 184-bit  | (1024K × 9) Single-Sided               |

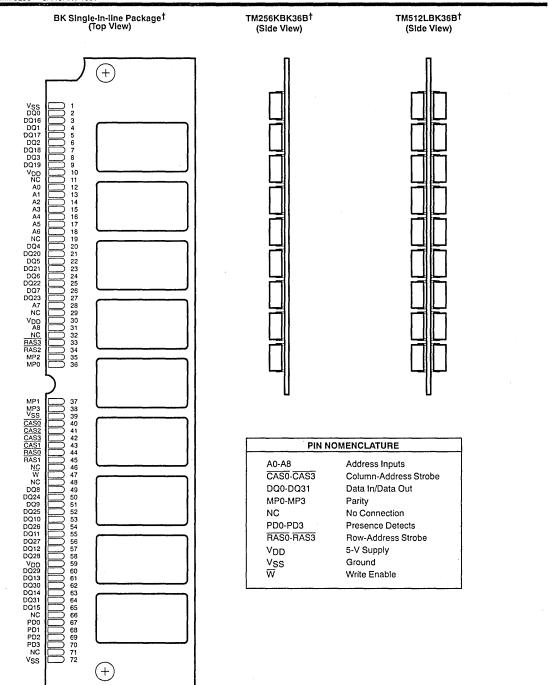

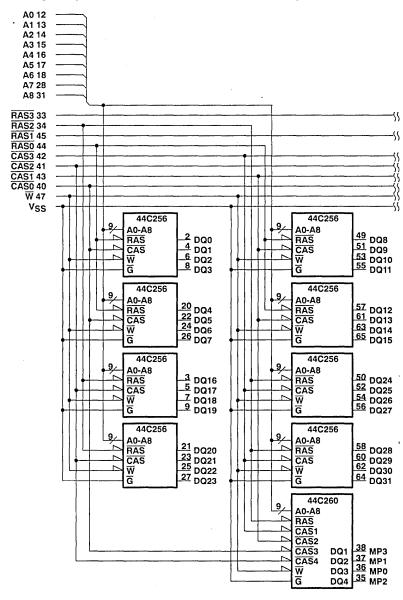

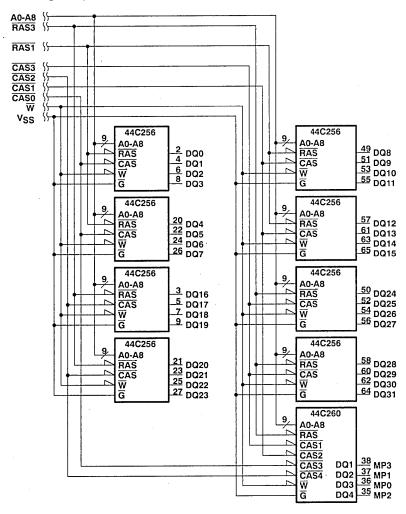

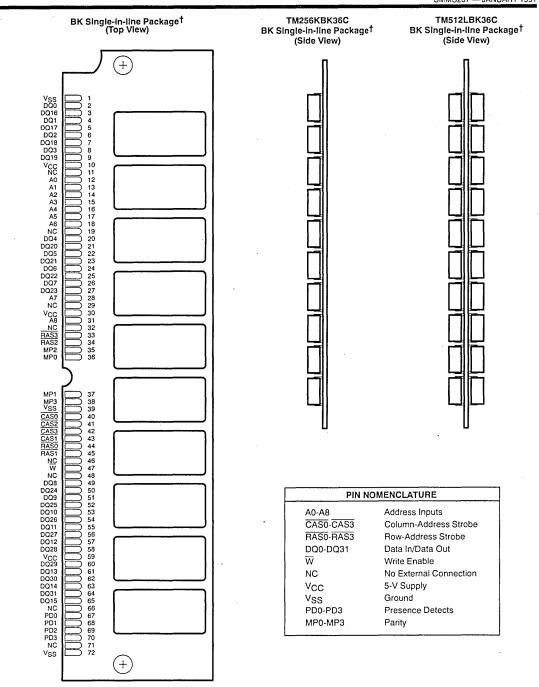

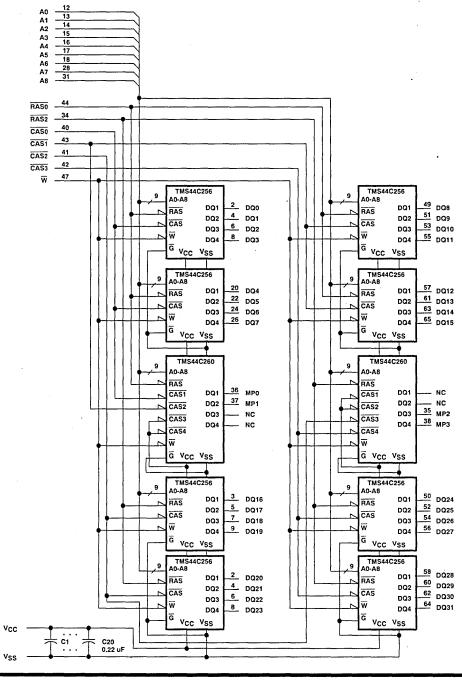

|    | TM256KBK36B   | 9 437 184-bit  | (256K × 36) Single-Sided               |

|    | TM256KBK36C   | 9 437 184-bit  | (256K × 36) Single-Sided               |

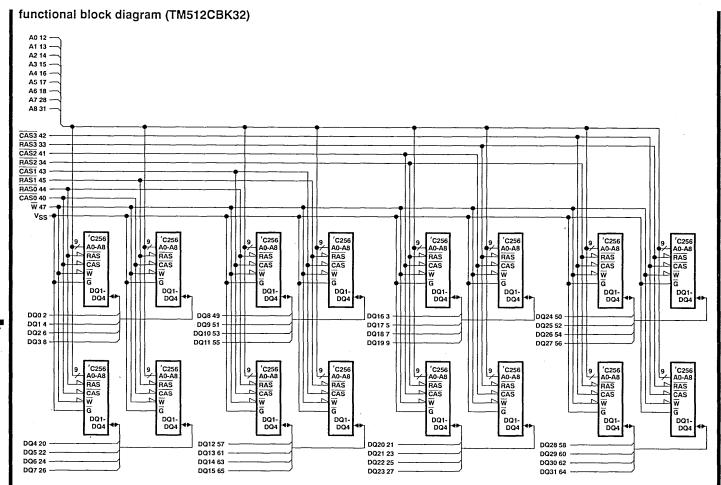

|    | TM512CBK32    | 16 777 216-bit | (512K × 32) Double-Sided               |

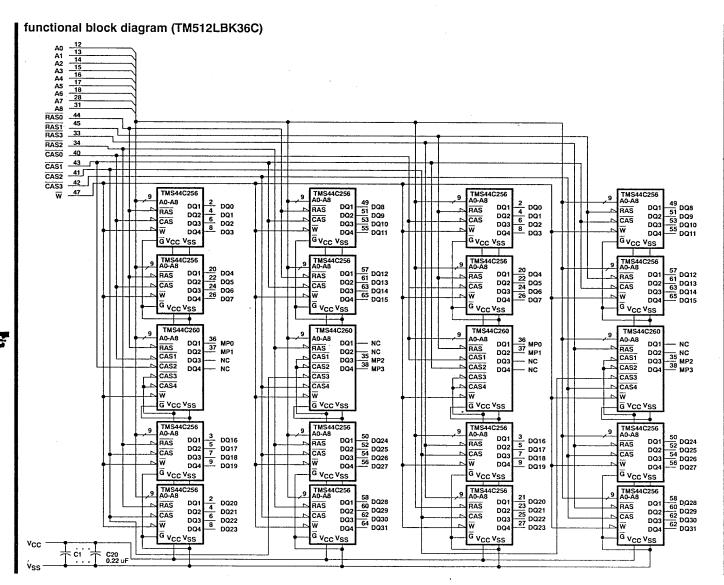

|    | TM512LBK36B   | 18 874 368-bit | (512K × 36) Double-Sided               |

|    | TM512LBK36C   | 18 874 368-bit | (512K × 36) Double-Sided               |

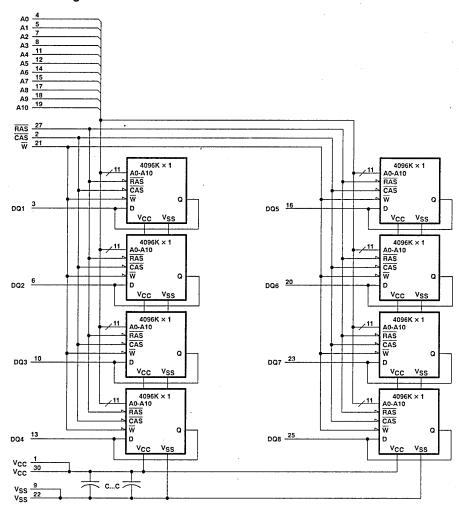

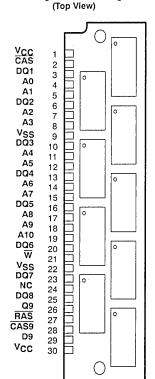

|    | TM4100GBD8    | 33 554 432-bit | (4096K × 8) Single-Sided               |

|    | TM124BBK32    | 33 554 432-bit | (1024K × 32) Single-Sided 6-73         |

|    | TM4100EBD9    | 37 748 736-bit | (4096K × 9) Single-Sided 6-81          |

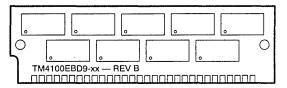

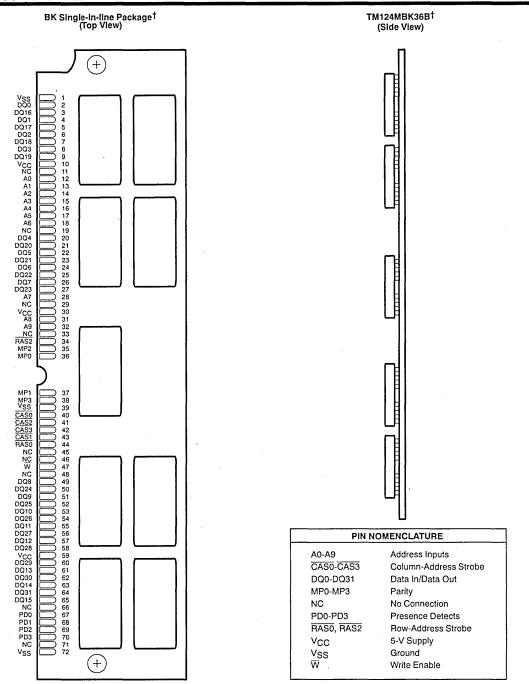

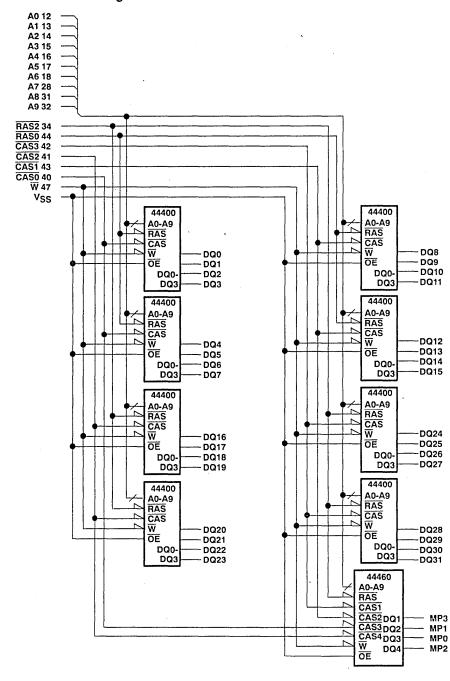

|    | TM124MBK36A   | 37 748 736-bit | (1024K × 36) Double-Sided 6-89         |

|    | TM124MBK36B   | 37 748 736-bit | (1024K × 36) Single-Sided 6-97         |

|    |               |                | 6-105                                  |

| _  | -             | •              |                                        |

| اب | HAPIER 7. EPF | ROM/OTP PROM/  | FLASH EEPROM                           |

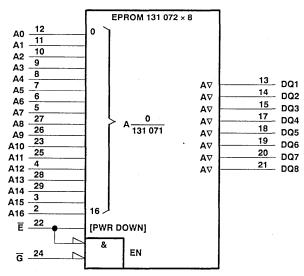

|    | TMS27C128     | 131 072-bit    | (16K × 8) CMOS EPROM 7-1               |

|    | TMS27PC128    | 131 072-bit    | (16K × 8) CMOS OTP PROM 7-1            |

|    | TMS27C256     | 262 144-bit    | (32K × 8) CMOS EPROM 7-15              |

|    | TMS27PC256    | 262 144-bit    | (32K × 8) CMOS OTP PROM 7-15           |

|    | TMS29F256     | 262 144-bit    | (32K × 8) 5-V Flash EEPROM 7-27        |

|    | TMS29F258     | 262 144-bit    | (32K × 8) 5-V Flash EEPROM 7-27        |

|    | TMS29F259     | 262 144-bit    | (32K × 8) 5-V Flash EEPROM 7-27        |

|    | TMS29F259 Pac | -              | 7-45                                   |

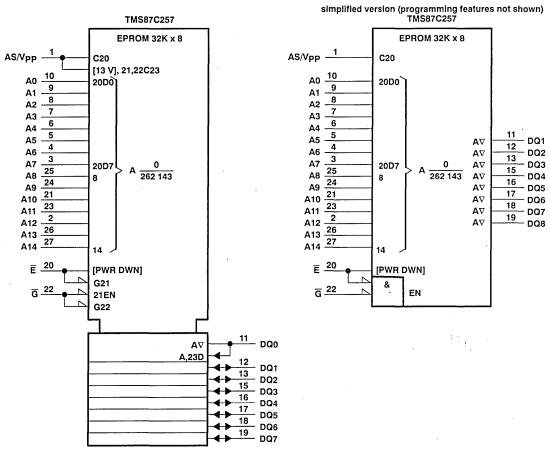

|    | TMS87C257     | 262 144-bit    | (32K × 8) CMOS Latched EPROM 7-47      |

|    | TMS27C510     | 524 288-bit    | (64K × 8) CMOS EPROM 7-57              |

|    | TMS27PC510    | 524 288-bit    | (64K × 8) CMOS OTP PROM 7-57           |

|    | TMS27C512     | 524 288-bit    | (64K × 8) CMOS EPROM 7-69              |

|    | TMS27PC512    | 524 288-bit    | (64K × 8) CMOS OTP PROM 7-69           |

|    | TMS29F512     | 524 288-bit    | (64K × 8) 5-V Flash EEPROM 7-81        |

|    | TMS29F512 Pac | -              |                                        |

|    | TMS27C010A    | 1 048 576-bit  | (128K × 8) CMOS EPROM 7-85             |

|    | TMS27PC010A   | 1 048 576-bit  | (128K × 8) CMOS OTP PROM 7-85          |

|    | TMS29F010     | 1 048 576-bit  | (128K × 8) 5-V Flash EEPROM            |

|    | TMS29F010 Pac |                | 7-117                                  |

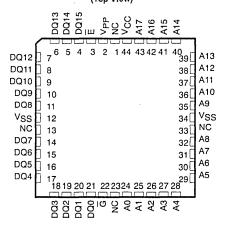

|    | TMS27C210A    | 1 048 576-bit  | (64K × 16) CMOS EPROM 7-119            |

| TMS27PC210A<br>TMS27C020<br>TMS27C040<br>TMS27PC040<br>TMS27C240<br>TMS27PC240                                    | 1 048 576-bit<br>2 097 152-bit<br>4 194 304-bit<br>4 194 304-bit<br>4 194 304-bit<br>4 194 304-bit                                                 | (64K × 16) CMOS OTP PROM       7-119         (256K × 8) CMOS EPROM       7-129         (512K × 8) CMOS EPROM       7-139         (512K × 8) CMOS EPROM       7-139         (256K × 16) CMOS EPROM       7-149         (256K × 16) CMOS OTP PROM       7-149                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 8. APP                                                                                                    | LICATION SPECIFIC                                                                                                                                  | MEMORIES                                                                                                                                                                                                                                                                                                                                                                                                       |

| TMS29F816<br>TMS44C250<br>TMS44C251<br>TMS44C260<br>TMS48C121<br>TMS4C1050<br>TMS4C1060<br>TMS4C1070<br>TMS4C4460 | 16 384-bit<br>1 048 576-bit<br>1 048 576-bit<br>1 048 576-bit<br>1 048 576-bit<br>1 048 576-bit<br>1 048 576-bit<br>1 048 576-bit<br>4 197 304-bit | (2K × 8) SCOPE™ Diary       8-1         (256K × 4) Multiport Video RAM       8-3         (256K × 4) Mulitport Video RAM       8-31         (256K × 4) Parity DRAM       8-73         (128K × 8) Multiport Video RAM       8-91         (256K × 4) Field Memory       8-125         (256K × 4) Field Memory       8-125         (256K × 4) Field Memory       8-141         (1024K × 4) Parity DRAM       8-155 |

| CHAPTER 9. MILI                                                                                                   | TARY PRODUCTS                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                |

| Military Introduction DYNAMIC RAMS                                                                                | on                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                |

| SMJ44C256<br>SMJ4C1024<br>SMJ44100<br>SMJ44400<br><i>EPROMS</i>                                                   | 1 048 576-bit<br>1 048 576-bit<br>4 197 304-bit<br>4 197 304-bit                                                                                   | (256K × 4) Enhanced Page Mode 9-3<br>(1024K × 1) Enhanced Page Mode 9-23<br>(4096K × 1) Enhanced Page Mode 9-41<br>(1024K × 4) Enhanced Page Mode 9-61                                                                                                                                                                                                                                                         |

| SMJ27C128<br>SMJ27C256<br>SMJ27C512<br>SMJ27C010<br>SMJ27C210                                                     | 131 072-bit<br>262 144-bit<br>524 288-bit<br>1 048 576-bit<br>1 048 576-bit                                                                        | (16K × 8) CMOS EPROM       9-81         (32K × 8) CMOS EPROM       9-91         (64K × 8) CMOS EPROM       9-101         (128K × 8) CMOS EPROM       9-113         (64K × 16) CMOS EPROM       9-115                                                                                                                                                                                                           |

| APPLICATION SF                                                                                                    | PECIFIC MEMORIES                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                |

| SMJ44C250<br>SMJ44C251<br>SMJ44C251A                                                                              | 1 048 576-bit<br>1 048 576-bit<br>1 048 576-bit                                                                                                    | (256K × 4) Multiport Video RAM       9-117         (256K × 4) Multiport Video RAM       9-147         (256K × 4) Multiport Video RAM       9-149                                                                                                                                                                                                                                                               |

| CHAPTER 10. DAT                                                                                                   | TAPATH VLSI PRODU                                                                                                                                  | JCTS                                                                                                                                                                                                                                                                                                                                                                                                           |

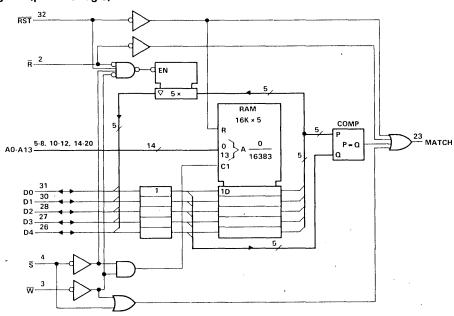

| CACHE ADDRES                                                                                                      | S COMPARATORS/D/                                                                                                                                   | ATA RAMS                                                                                                                                                                                                                                                                                                                                                                                                       |

| SN74ACT2140A<br>SN74ACT2150A<br>TMS2150A<br>SN74ACT2151<br>SN74ACT2153                                            | 4K × 18/8K × 18<br>512 × 8<br>512 × 8<br>1K × 11                                                                                                   | 10-1<br>10-3<br>10-5<br>10-7                                                                                                                                                                                                                                                                                                                                                                                   |

| 311/4A012133                                                                                                      | 11/ X /1                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                |

| SN74ACT2152A              | 2K × 8                                                     | . 10-9 |

|---------------------------|------------------------------------------------------------|--------|

| SN74ACT2154A              | 2K × 8                                                     | . 10-9 |

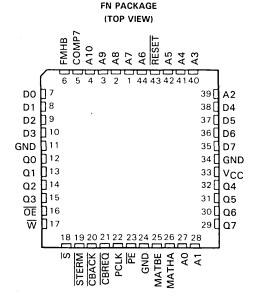

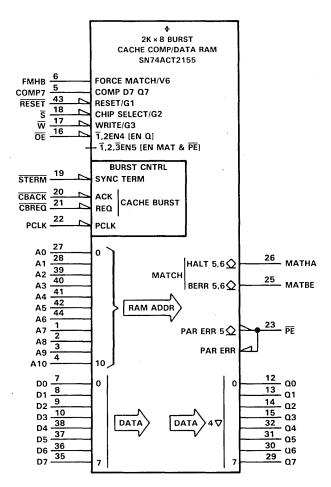

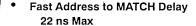

| SN74ACT2155               | 2K × 8                                                     | 10-11  |

| SN74ACT2156               | 16K × 4                                                    |        |

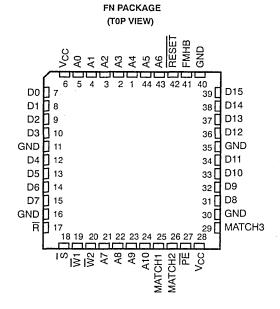

| SN74ACT2157               | 2K × 16                                                    |        |

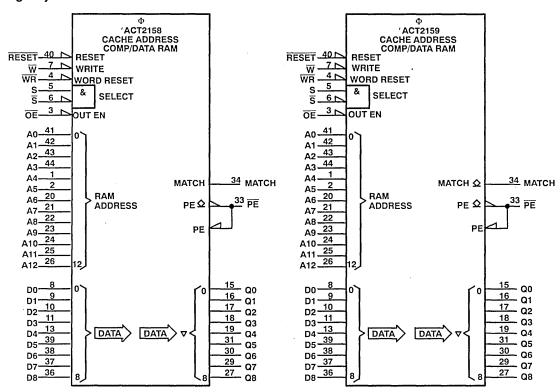

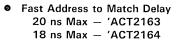

| SN74ACT2158               | 8K × 9                                                     |        |

| SN74ACT2159               | 8K × 9                                                     |        |

| SN74ACT2160               | 8K × 4                                                     |        |

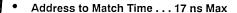

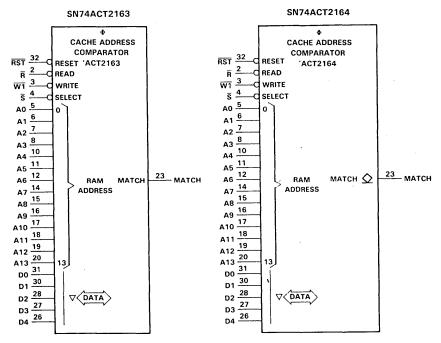

| SN74ACT2163               | 16K × 5                                                    |        |

| SN74ACT2164               | 16K × 5                                                    |        |

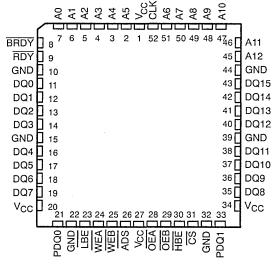

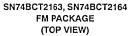

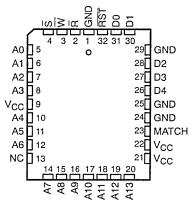

| SN74BCT2160               | 8K × 4                                                     |        |

| SN74BCT2141               | 8K × 18                                                    |        |

| SN74BCT2163               | 16K × 5                                                    |        |

| SN74BCT2164               | 16K×5                                                      |        |

| SN74BCT2166               | 16K × 5                                                    |        |

| SN74BCT2165               | 8K × 4                                                     | 10-29  |

| DYNAMIC MEMORY S          | UPPORT PRODUCTS                                            |        |

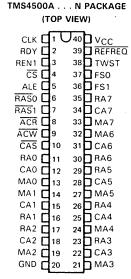

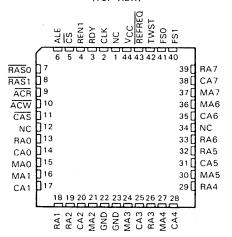

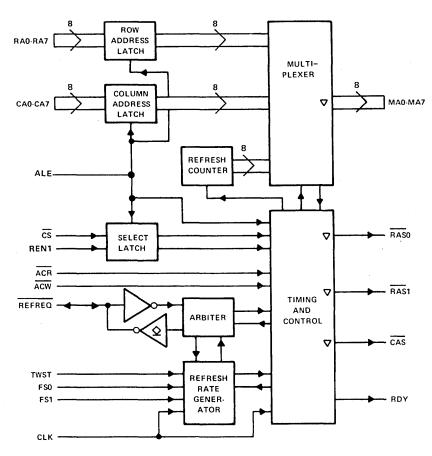

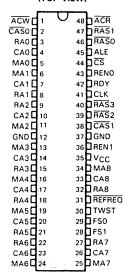

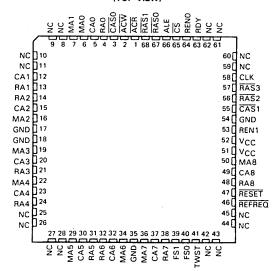

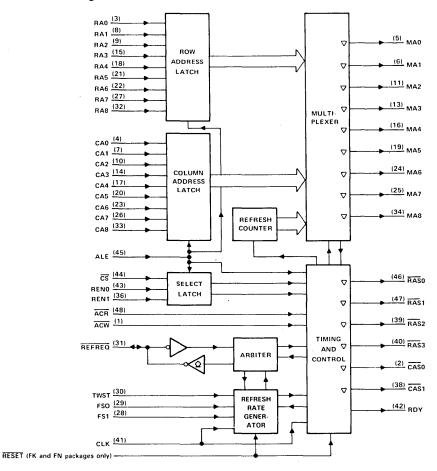

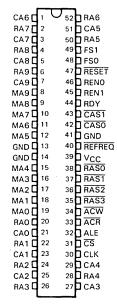

| TMS4500A                  | Dynamic RAM Controller                                     | 10-31  |

| THCT4502B                 | Dynamic RAM Controller                                     |        |

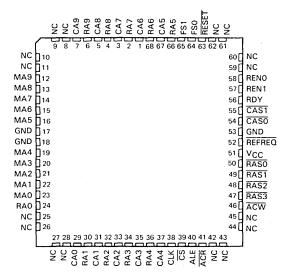

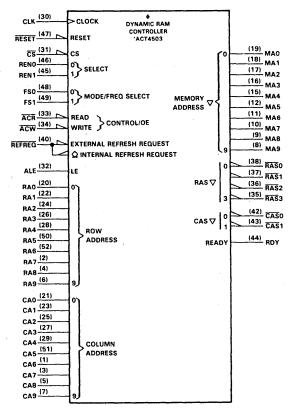

| SN74ACT4503               | Dynamic RAM Controller                                     |        |

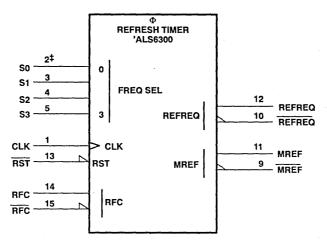

| SN74ALS6300               | Input-Selectable Refresh Timer                             |        |

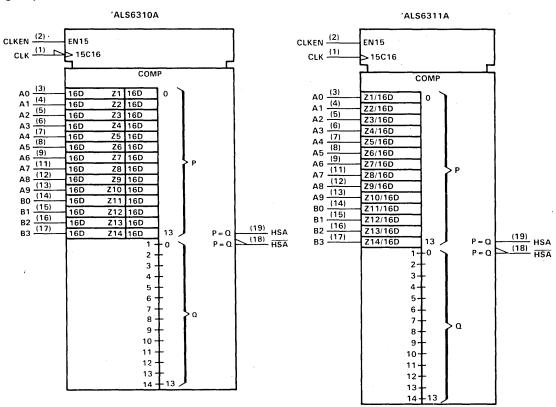

| SN74ALS6310A              | Static Column and Page Mode Access Detector                |        |

| SN74ALS6311A              | Static Column and Page Mode Access Detector                |        |

| SN74BCT2423A              | 16-bit Latched Multiplexer/Demultiplexer Bus Transceiver . |        |

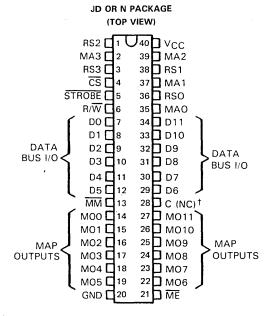

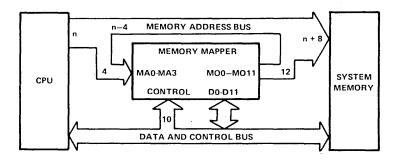

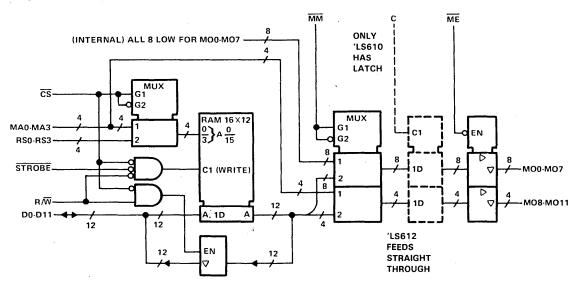

| SN74BCT2424A<br>SN74LS610 | 16-bit Latched Multiplexer/Demultiplexer Bus Transceiver . |        |

| SN74LS612                 | Memory Mapper  Memory Mapper                               |        |

|                           |                                                            | 10-40  |

|                           | ND CORRECTION (EDAC) PRODUCTS                              |        |

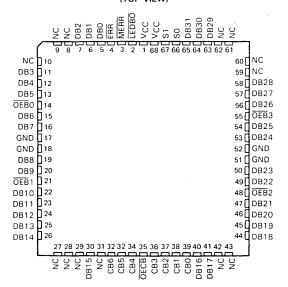

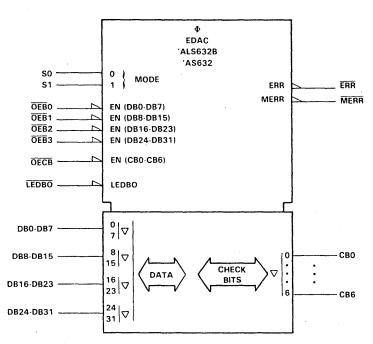

| SN74ALS632B               | 32-bit Parallel Circuit                                    |        |

| SN74AS632                 | 32-bit Parallel Circuit                                    |        |

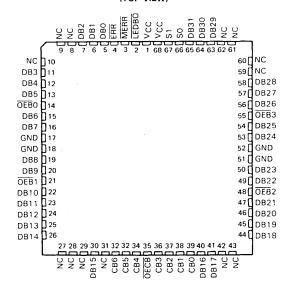

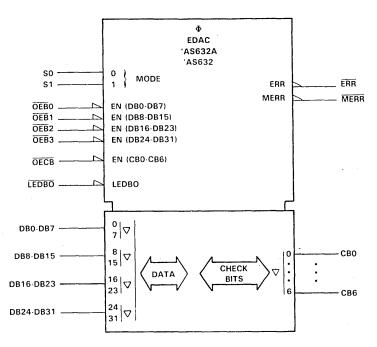

| SN74AS632A<br>SN74AS6364  | 32-bit Flow-Thru Circuit                                   |        |

| 3N74A30304                | 64-bit Flow-Tiffd Circuit                                  | 10-49  |

| CHAPTER 11. LOGIC S       | YMBOLS                                                     |        |

| Explanation of IEEE/IEC   | C Logic Symbols for Memories                               | . 11-1 |

| CHAPTER 12. QUALITY       | AND RELIABILITY                                            |        |

| MOS Memory Products       | Division Quality and Reliability Information               | . 12-1 |

| CHAPTER 13. ELECTR        | OSTATIC DISCHARGE GUIDELINES                               |        |

| Guidelines for Handling   | Electrostatic-Discharge Devices and Assemblies             | . 13-1 |

| CHAPTER 14. MECHAN        | IICAL DATA                                                 |        |

| MOS Memory Products       | — Commercial                                               | . 14-1 |

| MOS Memory Products       | - Military                                                 | 14-21  |

| General Information                              |

|--------------------------------------------------|

| Selection Guide 2                                |

| Alternate Source Directory 3                     |

| Glossary/Timing Conventions/Data Sheet Structure |

| Dynamic RAMs                                     |

| Dynamic RAM Modules 6                            |

| EPROMs/OTPs/Flash EEPROMs 7                      |

| Application Specific Memories 8                  |

| Military Products 9                              |

| Datapath VLSI Products                           |

| Logic Symbols                                    |

| Quality and Reliability 12                       |

| Electrostatic Discharge Guidelines               |

| Mechanical Data                                  |

| 1  | General Information                              |

|----|--------------------------------------------------|

| 2  | Selection Guide                                  |

| 8  | Alternate Source Directory                       |

| 4  | Glossary/Timing Conventions/Data Sheet Structure |

| 5  | Dynamic RAMs                                     |

| 6  | Dynamic RAM Modules                              |

| 7  | EPROMs/OTPs/Flash EEPROMs                        |

| 8  | Application Specific Memories                    |

| 9  | Military Products                                |

| 10 | Datapath VLSI Products                           |

| 11 | Logic Symbols                                    |

| 12 | Quality and Reliability                          |

| 18 | Electrostatic Discharge Guidelines               |

| 14 | Mechanical Data                                  |

| Alphanumeric Index                     |                                         |                   |

|----------------------------------------|-----------------------------------------|-------------------|

| SMJ27C010 9-113                        | SN74BCT216310-27                        | TMS27PC010A 7-85  |

| SMJ27C128 9-81                         | SN74BCT2163 10-27<br>SN74BCT2164 10-27  | TMS27PC010A 7-83  |

| SMJ27C210 9-115                        | SN74BCT2164 10-27<br>SN74BCT2165 10-29  | TMS27PC040 7-139  |

| SMJ27C256 9-91                         | SN74BCT2165 10-29<br>SN74BCT2166 10-27  | TMS27PC128 7-119  |

| SMJ27C512 9-101                        | SN74BCT2466 10-27<br>SN74BCT2423A 10-41 | TMS27PC210A 7-119 |

| SMJ441009-101                          | SN74BCT2424A 10-41                      | TMS27PC256 7-149  |

| SMJ44400                               | SN74LS610 10-41                         | TMS27PC510 7-15   |

| SMJ44C250 9-117                        | SN74LS612 10-43                         | TMS27PC510 7-69   |

| SMJ44C250 9-117<br>SMJ44C251 9-147     | THCT4502B 10-33                         | TMS29F010 7-95    |

| SMJ44C251 9-147<br>SMJ44C251A 9-149    | TM024EAD96-31                           | TMS29F070 7-95    |

| SMJ44C256 9-3                          | TM024GAD8 6-7                           | TMS29F258 7-27    |

| SMJ4C1024 9-23                         | TM124BBK32 6-7                          | TMS29F258 7-27    |

| SN74ACT2140A 10-1                      | TM124BBK32 6-73 TM124EAD9B 6-37         | TMS29F259 7-27    |

| SN74ACT2140A 10-1<br>SN74ACT2150A 10-3 |                                         | TMS29F816 8-1     |

|                                        | TM124EAD9C6-37                          |                   |

| SN74ACT2151 10-7                       | TM124GU8A6-13                           | TMS416100 5-165   |

| SN74ACT2152A 10-9                      | TM124MBK36A 6-89                        | TMS416400 5-187   |

| SN74ACT2153 10-7                       | TM124MBK36B 6-97                        | TMS44100 5-87     |

| SN74ACT2154A 10-9                      | TM256BBK32 6-21                         | TMS44101 5-107    |

| SN74ACT2155 10-11                      | TM256GU9C                               | TMS44400 5-125    |

| SN74ACT2156 10-13                      | TM256KBK36B 6-45                        | TMS44410 5-145    |

| SN74ACT2157 10-15                      | TM256KBK36C6-55                         | TMS44460 8-155    |

| SN74ACT2158 10-17                      | TM4100EBD96-81                          | TMS44C250 8-3     |

| SN74ACT2159 10-17                      | TM4100GBD8 6-65                         | TMS44C251 8-31    |

| SN74ACT2160 10-19                      | TM512CBK32 6-21                         | TMS44C256 5-1     |

| SN74ACT2163 10-21                      | TM512LBK36B6-45                         | TMS44C260 8-73    |

| SN74ACT2164 10-21                      | TM512LBK36C6-55                         | TMS4500A 10-31    |

| SN74ACT4503 10-35                      | TMS2150A 10-5                           | TMS48C121 8-91    |

| SN74ALS6300 10-37                      | TMS27C010A7-85                          | TMS48C128 5-63    |

| SN74ALS6310A 10-39                     | TMS27C020 7-129                         | TMS48C138 5-63    |

| SN74ALS6311A 10-39                     | TMS27C040 7-139                         | TMS4C1024 5-23    |

| SN74ALS632B 10-45                      | TMS27C128 7-1                           | TMS4C1025 5-23    |

| SN74AS6364 10-49                       | TMS27C210A7-119                         | TMS4C1027 5-23    |

| SN74AS632 10-45                        | TMS27C240 7-149                         | TMS4C1050 8-125   |

| SN74AS632A 10-47                       | TMS27C256 7-15                          | TMS4C1060 8-125   |

| SN74BCT2141 10-25                      | TMS27C510 7-57                          | TMS4C1070 8-141   |

| SN74BCT216010-23                       | TMS27C512 7-69                          | TMS87C257 7-47    |

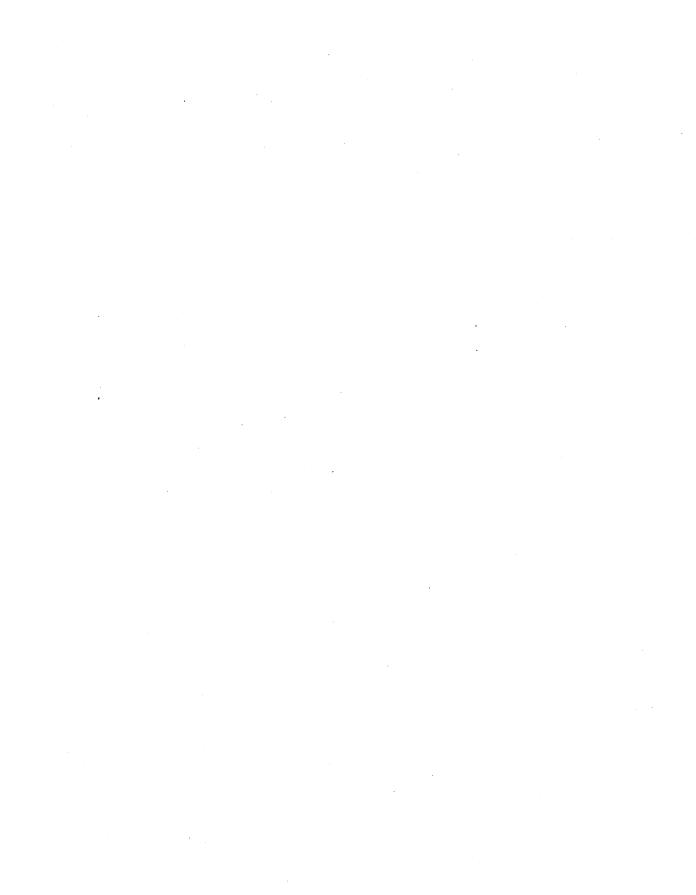

#### DRAM/VRAM/FMEM Ordering Information

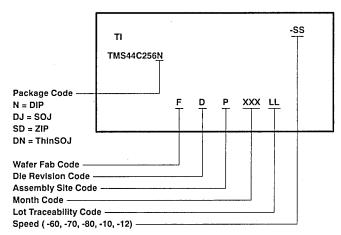

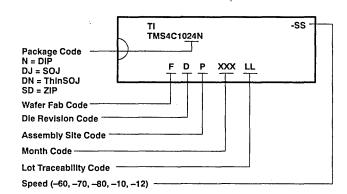

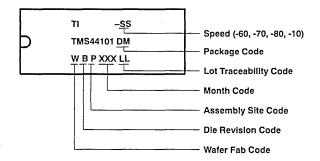

Factory orders for 1 Meg DRAMs, VRAMs, and FMEMs described in this book should include an eight-part type number as explained in the following example:

#### **DRAM Ordering Information**

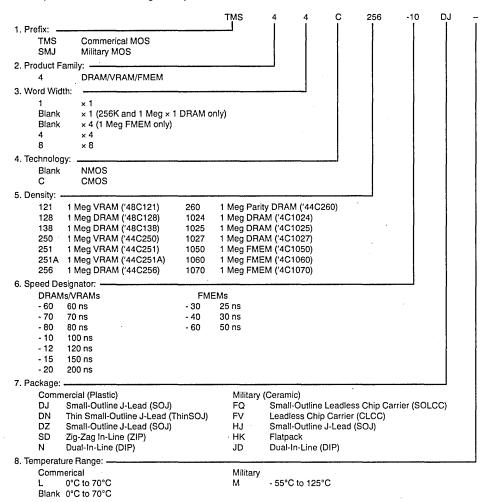

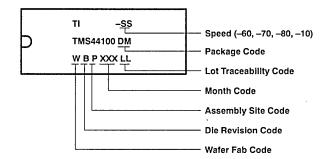

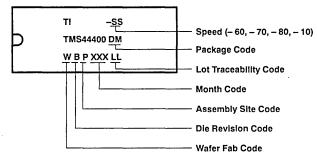

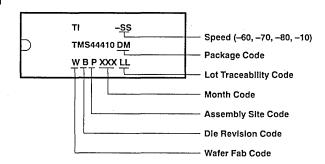

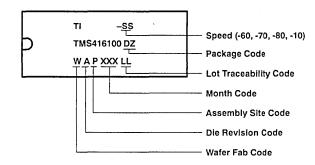

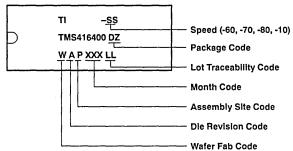

Factory orders for the 4 Meg and 16 Meg DRAMs described in this book should include an eight-part type number as explained in the following example:

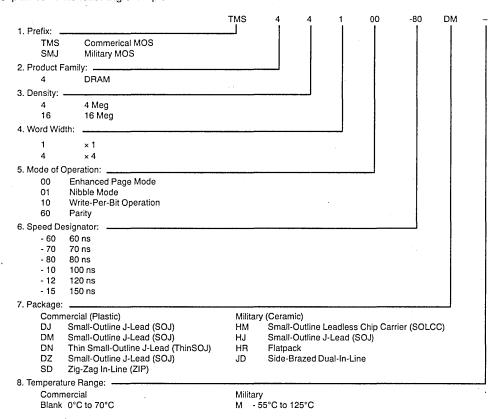

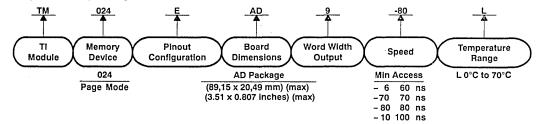

#### **Standard DRAM Module Ordering Information**

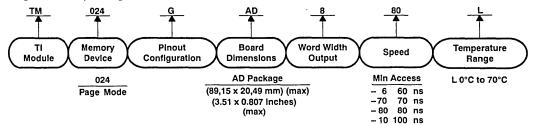

Factory orders for the standard DRAM Modules described in this book should include a seven-part type number as explained in the following example:

|              |                                                                | TM | 024 | E   | AD  | 9   | -10 - |

|--------------|----------------------------------------------------------------|----|-----|-----|-----|-----|-------|

|              |                                                                |    | - 1 | - [ | - [ | [   | 1 !   |

| TM           | Commerical TI MOS Module                                       |    | 1   | i   |     | i   |       |

| 2. Memory [  | Device:                                                        |    |     | i   | - 1 | ł   |       |

| 024<br>4100  | 1 Meg DRAM, Enhanced Page Mod<br>4 Meg DRAM, Enhanced Page Mod |    |     |     |     |     |       |

| 3. Pinout Co | onfiguration:                                                  |    |     |     | 1   |     |       |

| E            |                                                                |    |     |     | ł   | - 1 |       |

| G            |                                                                |    |     |     | -   |     |       |

| 4. Board Dir | nensions:                                                      |    |     |     |     | - 1 |       |

| AD           |                                                                |    |     |     |     |     | ] [   |

| BD           |                                                                |    |     |     |     | - { | 1 1   |

| 5. Word Wid  | Ith Output:                                                    |    |     |     |     |     |       |

| 8            | × 8                                                            |    |     |     |     |     | 1 1   |

| 9            | × 9                                                            |    |     |     |     |     |       |

| 6. Speed De  | esignator:                                                     |    |     |     |     |     |       |

| - 6          | 60 ns                                                          |    |     |     |     |     |       |

| - 70         | 70 ns                                                          |    |     |     |     |     |       |

|              | 80 ns                                                          |    |     |     |     |     |       |

| - 10         | 100 ns                                                         |    |     |     |     |     |       |

| 7. Temperat  | ure Range:                                                     |    |     |     |     |     |       |

| Blank        | 0°C to 70°C                                                    |    |     |     |     |     |       |

| L            | 0°C to 70°C (1 Meg only)                                       |    |     |     |     |     |       |

#### **Differentiated DRAM Module Ordering Information**

Factory orders for the mixed DRAM Modules described in this book should include an eight-part type number as explained in the following example:

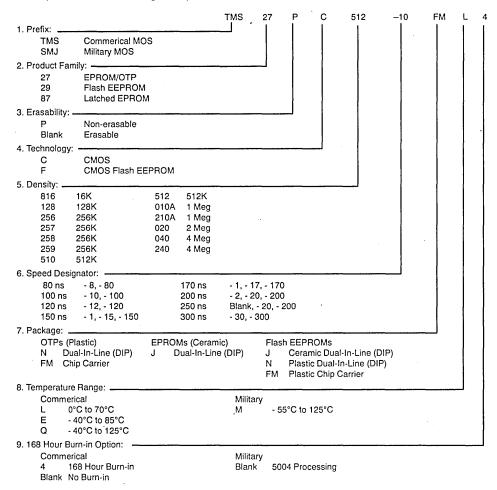

#### EPROM/OTP PROM/Flash EEPROM Ordering Information

Factory orders for EPROMs, OTPs, and Flash EEPROMs described in this book should include a nine-part type number as explained in the following example:

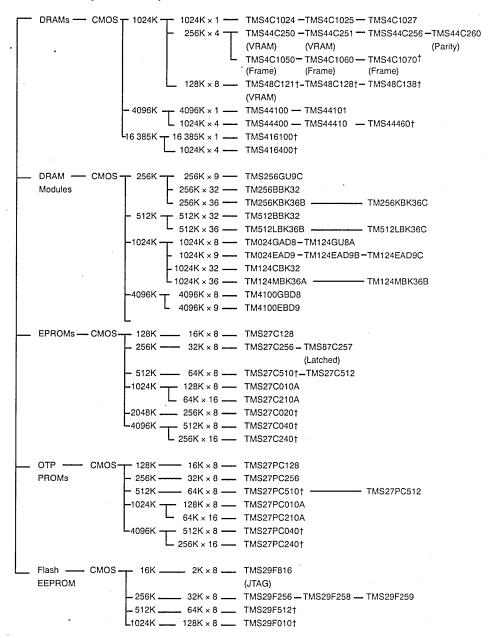

#### MOS Memory IC Line-up

<sup>†</sup> Product under development by TI

#### **MOS Memory Military IC Line-up**

```

DRAMS — CMOS — 1024K × 1 — SMJ4C1024

256K × 1 — SMJ44C256 — SMJ44C250† — SMJ44C251A† — SMJ44C251†

(VRAM) (VRAM) (VRAM)

4096K — 4096K × 1 — SMJ44100†

5MJ44400†

EPROMS — CMOS — 128K — 16K × 8 — SMJ27C128

256K — 32K × 8 — SMJ27C256

512K — 64K × 8 — SMJ27C512

1024K — 128K × 8 — SMJ27C010†

64K × 16 — SMJ27C210†

```

<sup>†</sup> Product under development by TI

| General Information                              | 1100 |

|--------------------------------------------------|------|

| Selection Guide                                  | 2    |

| Alternate Source Directory                       | 3    |

| Glossary/Timing Conventions/Data Sheet Structure | 4    |

| Dynamic RAMs                                     | . 5  |

| Dynamic RAM Modules                              | 6    |

| EPROMs/OTPs/Flash EEPROMs                        | 7    |

| Application Specific Memories                    | 8    |

| Military Products                                | 9    |

| Datapath VLSI Products                           | 10   |

| Logic Symbols                                    | 11   |

| Quality and Reliability                          | 12   |

| Electrostatic Discharge Guidelines               | 13   |

| Mechanical Data                                  | 14   |

| 1 General Information                              |

|----------------------------------------------------|

| 2 Selection Guide                                  |

| 3 Alternate Source Directory                       |

| 4 Glossary/Timing Conventions/Data Sheet Structure |

| 5 Dynamic RAMs                                     |

| 6 Dynamic RAM Modules                              |

| 7 EPROMs/OTPs/Flash EEPROMs                        |

| 8 Application Specific Memories                    |

| 9 Military Products                                |

| 10 Datapath VLSI Products                          |

| 11 Logic Symbols                                   |

| 12 Quality and Reliability                         |

| 13 Electrostatic Discharge Guidelines              |

| 14 Mechanical Data                                 |

#### DRAM

|         | Organization   | Device                                                                                                 | Max                          | Power         |                                 | Power<br>ipation |                            | _                    |                                                                   |       |

|---------|----------------|--------------------------------------------------------------------------------------------------------|------------------------------|---------------|---------------------------------|------------------|----------------------------|----------------------|-------------------------------------------------------------------|-------|

| Density | (Words × Bits) | Number                                                                                                 | Access<br>Time (ns)          | Supply<br>(V) | Active (mW)                     | Standby<br>(mW)  | Pins                       | Package <sup>†</sup> | Comments                                                          | Page  |

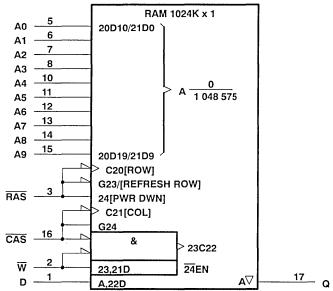

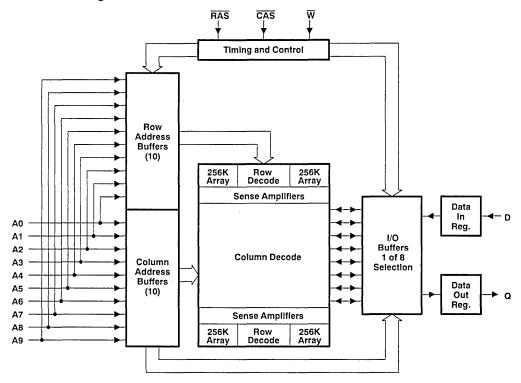

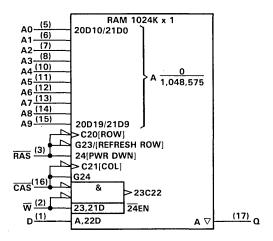

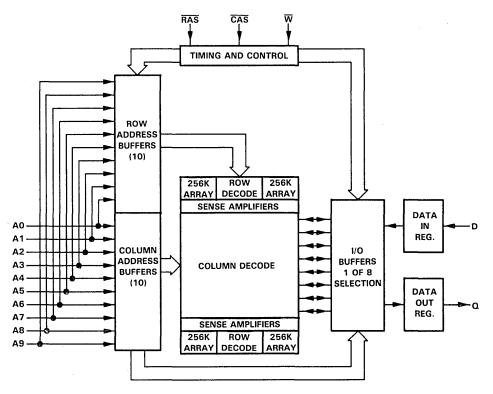

| 1024K   | 1024K × 1      | TMS4C1024-60 <sup>‡</sup><br>TMS4C1024-70 <sup>‡</sup><br>TMS4C1024-80<br>TMS4C1024-10<br>TMS4C1024-12 | 60<br>70<br>80<br>100<br>120 | 5 ± 10%       | 253<br>440<br>413<br>358<br>303 | 11               | 18,<br>20/26,<br>20/26, 20 | N,<br>DJ<br>DN, SD   | CMOS<br>Enhanced<br>Page Mode                                     | 5-23  |

|         |                | SMJ4C1024-10<br>SMJ4C1024-12<br>SMJ4C1024-15                                                           | 100<br>120<br>150            | 5 ± 10%       | 385<br>330<br>303               | 17               | 20/26,<br>20, 20           | HJ,<br>FQ, HK        | Military<br>CMOS<br>Enhanced<br>Page Mode                         | 9-23  |

|         |                | TMS4C1025-80<br>TMS4C1025-10<br>TMS4C1025-12                                                           | 80<br>100<br>120             | 5 ± 10%       | 413<br>358<br>303               | 11               | 18,<br>20/26,<br>20/26, 20 | N,<br>DJ<br>DN, SD   | CMOS<br>Nibble<br>Mode                                            | 5-23  |

|         |                | TMS4C1027-80<br>TMS4C1027-10<br>TMS4C1027-12                                                           | 80<br>100<br>120             | 5 ± 10%       | 413<br>358<br>303               | 11               | 18,<br>20/26,<br>20/26, 20 | N,<br>DJ<br>DN, SD   | CMOS<br>Static<br>Mode                                            | 5-23  |

|         | 256K × 4       | TMS44C256-60 <sup>‡</sup><br>TMS44C256-70 <sup>‡</sup><br>TMS44C256-80<br>TMS44C256-10<br>TMS44C256-12 | 60<br>70<br>80<br>100<br>120 | 5 ± 10%       | 523<br>440<br>413<br>358<br>303 | 11               | 20,<br>20/26,<br>20/26, 20 | N,<br>DJ<br>DN, SD   | CMOS<br>Enhanced<br>Page Mode                                     | 5-1   |

|         |                | SMJ44C256-10<br>SMJ44C256-12<br>SMJ44C256-15                                                           | 100<br>120<br>150            | 5 ± 10%       | 385<br>330<br>303               | 17               | 20,<br>20/26, 20           | JD,<br>HJ, FQ        | Military<br>CMOS<br>Enhanced<br>Page Mode                         | 9-3   |

| !       | 128K × 8       | TMS48C128-70<br>TMS48C128-80<br>TMS48C128-10                                                           | 70<br>80<br>100              | 5 ± 10%       | 468<br>440<br>385               | 11               | 24/26                      | DJ                   | CMOS<br>Enhanced<br>Page Mode                                     | 5-63  |

|         |                | TMS48C138-70<br>TMS48C138-80<br>TMS48C138-10                                                           | 70<br>80<br>100              | 5 ± 10%       | 468<br>440<br>385               | 11               | 24/26                      | DJ                   | CMOS<br>Enhanced<br>Page Mode<br>Write-per-<br>Bit Opera-<br>tion | 5-63  |

| 4096K   | 4096K × 1      | TMS44100-60<br>TMS44100-70<br>TMS44100-80<br>TMS44100-10                                               | 60<br>70<br>80<br>100        | 5 ± 10%       | 550<br>495<br>440<br>385        | 11               | 20/26,<br>20/26, 20        | DJ,<br>DM, SD        | CMOS<br>Enhanced<br>Page Mode                                     | 5-87  |

|         |                | SMJ44100-80 <sup>§</sup><br>SMJ44100-10 <sup>§</sup><br>SMJ44100-12 <sup>§</sup>                       | 80<br>100<br>120             | 5 ± 10%       | 468<br>440<br>385               | 22               | 18, 20,<br>20, 20          | JD, HM<br>HJ, HR     | Military<br>CMOS<br>Enhanced<br>Page Mode                         | 9-41  |

|         |                | TMS44101-60<br>TMS44101-70<br>TMS44101-80<br>TMS44101-10                                               | 60<br>70<br>80<br>100        | 5 ± 10%       | 523<br>468<br>413<br>358        | 11               | 20/26,<br>20/26, 20        | DJ,<br>DM, SD        | CMOS<br>Nibble<br>Mode                                            | 5-107 |

- - DJ

- DN

- DM

- Plaastic Dual In-Line Package (DIP)

Plastic Small-Outline J-Lead (SOJ)

Plastic Thin Small-Outline J-Lead (ThinSoJ)

Plastic Small-Outline J-Lead (SOJ)

Ceramic Small-Outline Leadless Chip Carrier (Military) (SOLCC)

Ceramic Small-Outline Leadless J-Lead (Military) (SOLCC) FQ

- HJ

- HΚ

- Plastic Small-Outline Leadless Chip Carrier (Military) (SOLCC) НМ

- HR

- Plastic Sinda-Odinine Leadiess Chip Carrier (wilitary) (SOEC Flatpack (Military) Ceramic Side-Brazed Dual In-Line Package (Military) (DIP) Plastic Zig-Zag In-Line Package (ZIP) JD

- Available only in DJ package

Advance Information for product under development by TI

#### **Selection Guide**

#### DRAM (Concluded)

| Density           | Organization<br>(Words × Bits) | Device                                                                                                           | Max<br>Access         | Power<br>Supply<br>(V) |                          | Power<br>ipation | Pins                | Package†         | Comments                                                          | Page  |

|-------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|--------------------------|------------------|---------------------|------------------|-------------------------------------------------------------------|-------|

|                   |                                | Number                                                                                                           | Time (ns)             |                        | Active<br>(mW)           | Standby<br>(mW)  | ]                   |                  |                                                                   |       |

| 4096K<br>(cont'd) | 1024K × 4                      | TMS44400-60<br>TMS44400-70<br>TMS44400-80<br>TMS44400-10                                                         | 60<br>70<br>80<br>100 | 5 ± 10%                | 550<br>495<br>440<br>385 | 11               | 20/26,<br>20/26, 20 | DJ,<br>DM, SD    | CMOS<br>Enhanced<br>Page Mode                                     | 5-125 |

|                   |                                | SMJ44400-80 <sup>‡</sup><br>SMJ44400-10 <sup>‡</sup><br>SMJ44400-12 <sup>‡</sup>                                 | 80<br>100<br>120      | 5 ± 10%                | 468<br>440<br>358        | 22               | 20, 20,<br>20, 20   | JD, HM<br>HJ, HR | Military<br>CMOS<br>Enhanced<br>Page Mode                         | 9-61  |

|                   |                                | TMS44410-60<br>TMS44410-70<br>TMS44410-80<br>TMS44410-10                                                         | 60<br>70<br>80<br>100 | 5 ± 10%                | 523<br>468<br>413<br>358 | 11               | 20/26,<br>20/26, 20 | DJ,<br>DM, SD    | CMOS<br>Enhanced<br>Page Mode<br>Write-per-<br>Bit Opera-<br>tion | 5-145 |

| 16 385K           | 16 385K × 1                    | TMS416100-60 <sup>‡</sup><br>TMS416100-70 <sup>‡</sup><br>TMS416100-80 <sup>‡</sup><br>TMS416100-10 <sup>‡</sup> | 60<br>70<br>80<br>100 | 5 ± 10%                | 495<br>440<br>385<br>330 | 11               | 24/28               | DZ               | CMOS<br>Enhanced<br>Page Mode                                     | 5-165 |

|                   | 4096K × 4                      | TMS416400-60 <sup>‡</sup><br>TMS416400-70 <sup>‡</sup><br>TMS416400-80 <sup>‡</sup><br>TMS416400-10 <sup>‡</sup> | 60<br>70<br>80<br>100 | 5 ± 10%                | 495<br>440<br>385<br>330 | 11               | 24/28               | DZ               | CMOS<br>Enhanced<br>Page Mode                                     | 5-187 |

DJ Plastic Small-Outline J-Lead (SOJ)

Plastic Small-Outline J-Lead (SOJ)

Plastic Small-Outline J-Lead (SOJ) DM

DΖ

НJ

Ceramic Small-Outline Leadless J-Lead (Military) (SOLCC)

Plastic Small-Outline Leadless Chip Carrier (Military) (SOLCC)

Flatpack (Military) НМ

HR

Ceramic Side-Brazed Dual In-Line Package (Military) (DIP)

Plastic Zig-Zag In-Line Package (ZIP) JD

Advance Information for product under development by TI

#### **DRAM Module**

| Density | Organization   | Device                                                              | Max<br>Access           | Power<br>Supply                         |                              | Power<br>Ipation         | Pins | Package                     | Page |

|---------|----------------|---------------------------------------------------------------------|-------------------------|-----------------------------------------|------------------------------|--------------------------|------|-----------------------------|------|

|         | (Words × Bits) | Number                                                              | Time (ns)               | (V)                                     | Active (mW)                  | Standby<br>(mW)          |      | ,                           |      |

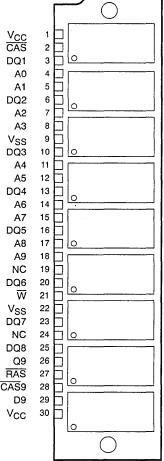

| 2304K   | 256K × 9       | TM256GU9C-6<br>TM256GU9C-70<br>TM256GU9C-80<br>TM256GU9C-10         | 60<br>70<br>80<br>100   | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 1496<br>1320<br>1238<br>1073 | 31<br>33<br>33<br>33     | 30   | Single-Sided,<br>Socketable | 6-1  |

| 8192K   | 1024K × 8      | TM024GAD8-6<br>TM024GAD8-70<br>TM024GAD8-80<br>TM024GAD8-10         | 60<br>70<br>80<br>100   | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 3990<br>3520<br>3300<br>2860 | 84<br>88<br>88<br>88     | 30   | Single-Sided,<br>Socketable | 6-7  |

| ,       |                | TM124GU8A-6<br>TM124GU8A-70<br>TM124GU8A-80<br>TM124GU8A-10         | 60<br>70<br>80<br>100   | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 998<br>935<br>825<br>715     | 21<br>22<br>22<br>22     | 30   | Single-Sided,<br>Socketable | 6-13 |

|         | 256K × 32      | TM256BBK32-6<br>TM256BBK32-70<br>TM256BBK32-80<br>TM256BBK32-10     | 60<br>70<br>80<br>100   | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 3990<br>3520<br>3300<br>2860 | 84<br>88<br>88<br>88     | 72   | Single-Sided,<br>Socketable | 6-21 |

| 9216K   | 1024K × 9      | TM024EAD9-6<br>TM024EAD9-70<br>TM024EAD9-80<br>TM024EAD9-10         | 60<br>70<br>80<br>100   | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 4489<br>3960<br>3713<br>3218 | 95<br>99<br>99<br>99     | 30   | Single-Sided,<br>Socketable | 6-31 |

|         |                | TM124EAD9B-6<br>TM124EAD9B-70<br>TM124EAD9B-80<br>TM124EAD9B-10     | . 60<br>70<br>80<br>100 | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 1496<br>1403<br>1238<br>1073 | 32<br>33<br>33<br>33     | 30   | Single-Sided,<br>Socketable | 6-37 |

|         |                | TM124EAD9C-6<br>TM124EAD9C-70<br>TM124EAD9C-80<br>TM124EAD9C-10     | 60<br>70<br>80<br>100   | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 1496<br>1403<br>1238<br>1073 | 32<br>33<br>33<br>33     | 30   | Single-Sided,<br>Socketable | 6-37 |

|         | 256K × 36      | TM256KBK36B-6<br>TM256KBK36B-70<br>TM256KBK36B-80<br>TM256KBK36B-10 | 60<br>70<br>80<br>100   | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 4489<br>3960<br>3713<br>3218 | 95<br>99<br>99<br>99     | 72   | Single-Sided,<br>Socketable | 6-45 |

|         |                | TM256KBK36C-6<br>TM256KBK36C-70<br>TM256KBK36C-80<br>TM256KBK36C-10 | 60<br>70<br>80<br>100   | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 4988<br>4400<br>4125<br>3575 | 105<br>110<br>110<br>110 | 72   | Single-Sided,<br>Socketable | 6-55 |

| 16 384K | 512K × 32      | TM512CBK32-6<br>TM512CBK32-70<br>TM512CBK32-80<br>TM512CBK32-10     | 60<br>70<br>80<br>100   | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 4074<br>3608<br>3388<br>2948 | 168<br>176<br>176<br>176 | 72   | Double-Sided,<br>Socketable | 6-21 |

| 18 432K | 512K × 36      | TM512LBK36B-6<br>TM512LBK36B-70<br>TM512LBK36B-80<br>TM512LBK36B-10 | 60<br>70<br>80<br>100   | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 4583<br>4059<br>3812<br>3317 | 189<br>198<br>198<br>198 | 72   | Double-Sided,<br>Socketable | 6-45 |

|         |                | TM512LBK36C-6<br>TM512LBK36C-70<br>TM512LBK36C-80<br>TM512LBK36C-10 | 60<br>70<br>80<br>100   | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 5093<br>4510<br>4235<br>3685 | 210<br>220<br>220<br>220 | 72   | Double-Sided,<br>Socketable | 6-55 |

#### **Selection Guide**

#### **DRAM Module (Concluded)**

| Danaite | Organization   | Device                                                                                 | Max<br>Access         | Power                                   |                              | Power pation         | Pins  | Package                     | Page  |

|---------|----------------|----------------------------------------------------------------------------------------|-----------------------|-----------------------------------------|------------------------------|----------------------|-------|-----------------------------|-------|

| Density | (Words × Bits) | Number                                                                                 | Time (ns)             | Supply<br>(V)                           | Active<br>(mW)               | Standby<br>(mW)      | FIIIS | Package                     | · ugo |

| 32 768K | 4096K × 8      | TM4100GBD8-6<br>TM4100GBD8-70<br>TM4100GBD8-80<br>TM4100GBD8-10                        | 60<br>70<br>80<br>100 | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 3990<br>3740<br>3300<br>2860 | 84<br>88<br>88<br>88 | 30    | Single-Sided,<br>Socketable | 6-65  |

|         | 1024K× 32      | TM124BBK32-6<br>TM124BBK32-70<br>TM124BBK32-80<br>TM124BBK32-10                        | 60<br>70<br>80<br>100 | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 3990<br>3740<br>3300<br>2860 | 84<br>88<br>88<br>88 | 72    | Single-Sided,<br>Socketable | 6-73  |

| 36 864K | 4096K × 9      | TM4100EBD9-6<br>TM4100EBD9-70<br>TM4100EBD9-80<br>TM4100EBD9-10                        | 60<br>70<br>80<br>100 | 5 ± 5%<br>5 ± 10%<br>5 ± 10%<br>5 ± 10% | 4489<br>4208<br>3713<br>3218 | 95<br>99<br>99<br>99 | 30    | Single-Sided,<br>Socketable | 6-81  |

|         | 1024K × 36     | TM124MBK36A-6†<br>TM124MBK36A-7†<br>TM124MBK36A-8†                                     | 60<br>70<br>80        | 5 ± 5%<br>5 ± 5%<br>5 ± 5%              | 5985<br>5250<br>4725         | 126<br>126<br>126    | 72    | Double-Sided,<br>Socketable | 6-89  |

|         |                | TM124MBK36B-6 <sup>†</sup><br>TM124MBK36B-7 <sup>†</sup><br>TM124MBK36B-8 <sup>†</sup> | 60<br>70<br>80        | 5 ± 5%<br>5 ± 5%<br>5 ± 5%              | 4489<br>4016<br>3544         | 95<br>95<br>95       | 72    | Single-Sided,<br>Socketable | 6-97  |

<sup>†</sup> Advance Information for product under development by TI

#### EPROM/Flash EEPROM

|         | Organization                   | Device                                                                                                                                                                       | Max                                                                | Power                                                                                                 |                                                                    | Power<br>ipation        |               |                      |                                                                |      |

|---------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------|---------------|----------------------|----------------------------------------------------------------|------|

| Density | Organization<br>(Words × Bits) | Number                                                                                                                                                                       | Access<br>Time (ns)                                                | Supply<br>(V)                                                                                         | Active<br>(mW)                                                     | Standby<br>CMOS<br>(mW) | Pins          | Package <sup>†</sup> | Comments                                                       | Page |

| 128K    | 16K × 8                        | TMS27C128-100<br>TMS27C128-120<br>TMS27C128-12<br>TMS27C12-1<br>TMS27C128-15<br>TMS27C128-2<br>TMS27C128-2<br>TMS27C128-20<br>TMS27C128-25                                   | 100<br>120<br>120<br>150<br>150<br>200<br>200<br>250<br>250        | 5 ± 5%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%            | 158<br>158<br>165<br>158<br>165<br>158<br>165<br>158<br>165        | 1.4                     | 28            | J                    | CMOS                                                           | 7-1  |

|         |                                | SMJ27C128-12<br>SMJ27C128-15<br>SMJ27C128-17<br>SMJ27C128-20<br>SMJ27C128-25<br>SMJ27C128-30                                                                                 | 120<br>150<br>170<br>200<br>250<br>300                             | 5 ± 10%                                                                                               | 220                                                                | 1.7                     | 28            | J                    | Military<br>CMOS                                               | 9-81 |

| 256K    | 32K × 8                        | TMS27C256-120<br>TMS27C256-12<br>TMS27C256-150<br>TMS27C256-15<br>TMS27C256-15<br>TMS27C256-17<br>TMS27C256-2<br>TMS27C256-2<br>TMS27C256-20<br>TMS27C256-20<br>TMS27C256-25 | 120<br>120<br>150<br>150<br>170<br>170<br>200<br>200<br>250<br>250 | 5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10% | 158<br>165<br>158<br>165<br>158<br>165<br>158<br>165<br>158<br>165 | 1.4                     | 28            | J                    | CMOS                                                           | 7-15 |

|         |                                | SMJ27C256-15<br>SMJ27C256-17<br>SMJ27C256-20<br>SMJ27C256-25<br>SMJ27C256-30                                                                                                 | 150<br>170<br>200<br>250<br>300                                    | 5 ± 10%                                                                                               | 220                                                                | 1.7                     | 28            | J                    | Military<br>CMOS                                               | 9-91 |

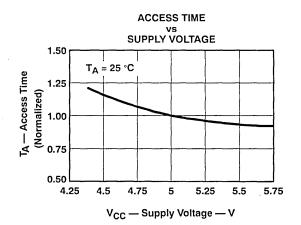

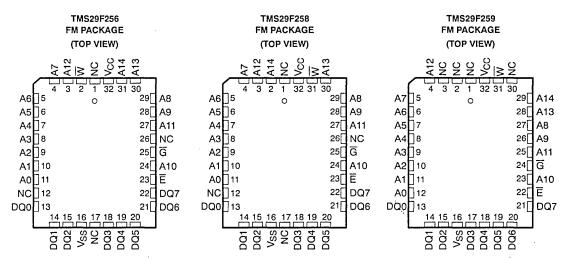

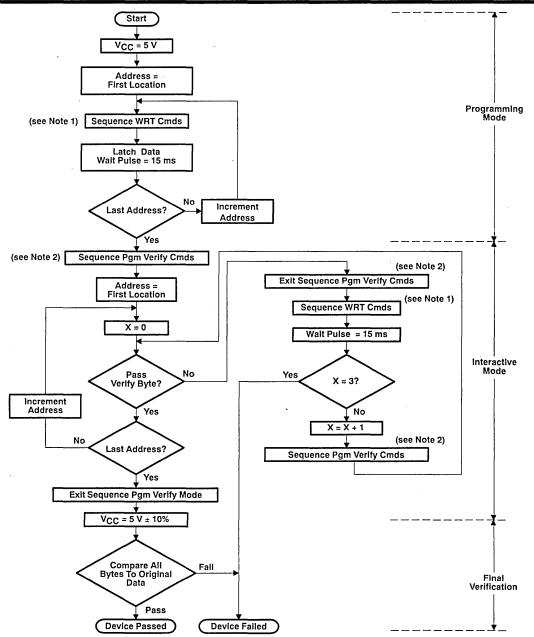

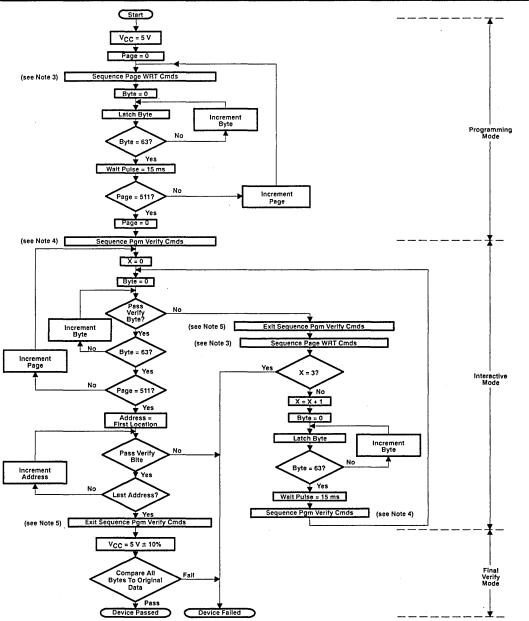

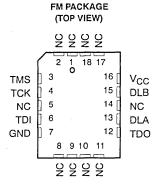

|         | ,                              | TMS29F256-170<br>TMS29F256-200<br>TMS29F256-20<br>TMS29F256-250<br>TMS29F256-255<br>TMS29F256-300<br>TMS29F256-300                                                           | 170<br>200<br>200<br>250<br>250<br>250<br>300                      | 5 ± 5%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%                                 | 83                                                                 | 17                      | 28, 28,<br>32 | J, N,<br>FM          | CMOS 5-V<br>Flash<br>EEPROM;<br>EPROM<br>Pinout                | 7-27 |

|         |                                | TMS29F258-170<br>TMS29F258-200<br>TMS29F258-20<br>TMS29F258-250<br>TMS29F258-255<br>TMS29F258-300<br>TMS29F258-300                                                           | 170<br>200<br>200<br>250<br>250<br>300<br>300                      | 5 ± 5%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%                                 | 83                                                                 | 17                      | 28, 28,<br>32 | J, N,<br>FM          | CMOS 5-V<br>Flash<br>EEPROM;<br>EEPROM<br>Pinout               | 7-27 |

|         |                                | TMS29F259-170<br>TMS29F259-200<br>TMS29F259-20<br>TMS29F259-250<br>TMS29F259-25<br>TMS29F259-300<br>TMS29F259-300                                                            | 170<br>200<br>200<br>250<br>250<br>300<br>300                      | 5 ± 5%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%                                 | 83                                                                 | 17                      | 28, 28,<br>32 | J, N,<br>FM          | CMOS 5-V<br>Flash<br>EEPROM;<br>12-V Flash<br>Memory<br>Pinout | 7-27 |

<sup>†</sup> J Ceramic Dual In-Line Package (DIP)

N Plastic Dual In-Line Package (DIP)

FM Plastic Chip Carrier

#### **Selection Guide**

#### EPROM/Flash EEPROM

|                  | Organization        | Device                                                                                                                                                                                                        | Max                                                                | Power                                                                                                 |                                                                    | Power<br>Ipation        |               |                      | +                                               |       |

|------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------|---------------|----------------------|-------------------------------------------------|-------|

| Density          | (Words × Bits)      | Number                                                                                                                                                                                                        | Access<br>Time (ns)                                                | Supply<br>(V)                                                                                         | Active<br>(mW)                                                     | Standby<br>CMOS<br>(mW) | Pins          | Package <sup>†</sup> | Comments                                        | Page  |

| 256K<br>(cont'd) | 32K × 8<br>(cont'd) | TMS87C257-150<br>TMS87C257-1<br>TMS87C257-2<br>TMS87C257                                                                                                                                                      | 150<br>170<br>200<br>250                                           | 5 ± 5%                                                                                                | 158                                                                | 1.4                     | 28            | J                    | CMOS<br>Latched<br>EPROM                        | 7-47  |

| 512K             | 64K × 8             | TMS27C510-120‡ TMS27C510-12‡ TMS27C510-150‡ TMS27C510-150‡ TMS27C510-170‡ TMS27C510-170‡ TMS27C510-200‡ TMS27C510-200‡ TMS27C510-250‡ TMS27C510-255‡                                                          | 120<br>120<br>150<br>150<br>170<br>170<br>200<br>200<br>250<br>250 | 5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10% | 158<br>165<br>158<br>165<br>158<br>165<br>158<br>165<br>158<br>165 | 1.4                     | 32            | J                    | CMOS;<br>1 Meg<br>EPROM<br>Compatible<br>Pinout | 7-57  |

|                  |                     | TMS27C512-100 TMS27C512-10 TMS27C512-10 TMS27C512-12 TMS27C510-150 TMS27C510-150 TMS27C512-2 TMS27C512-2 TMS27C512-20 TMS27C512-25                                                                            | 100<br>100<br>120<br>120<br>150<br>150<br>200<br>200<br>250<br>250 | 5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10% | 158<br>165<br>158<br>165<br>158<br>165<br>158<br>165<br>158<br>165 | 1.4                     | 28            | J                    | CMOS                                            | 7-69  |

|                  |                     | SMJ27C512-20<br>SMJ27C512-25<br>SMJ27C512-30                                                                                                                                                                  | 200<br>250<br>300                                                  | 5 ± 10%                                                                                               | 263                                                                | 1.8                     | 28            | J                    | Military<br>CMOS                                | 9-101 |

|                  |                     | TMS29F512-100 <sup>‡</sup><br>TMS29F512-120 <sup>‡</sup><br>TMS29F512-12 <sup>‡</sup><br>TMS29F512-15 <sup>‡</sup><br>TMS29F512-15 <sup>‡</sup><br>TMS29F512-200 <sup>‡</sup>                                 | 100<br>120<br>120<br>150<br>150<br>200<br>200                      | 5 ± 5%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%                                 | 79<br>79<br>83<br>79<br>83<br>79<br>83                             | 5.5                     | 32, 32,<br>32 | J, N,<br>FM          | CMOS 5-V<br>Flash<br>EEPROM                     | 7-81  |

| 1024K            | 128K × 8            | TMS27C010A-100<br>TMS27C010A-120<br>TMS27C010A-12<br>TMS27C010A-15<br>TMS27C010A-15<br>TMS27C010A-200<br>TMS27C010A-20                                                                                        | 100<br>120<br>120<br>150<br>150<br>200<br>200                      | 5 ± 5%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%                                 | 158<br>158<br>165<br>158<br>165<br>158<br>165                      | 0.55                    | 32            | J                    | CMOS                                            | 7-85  |

|                  |                     | SMJ27C010-17<br>SMJ27C010-20<br>SMJ27C010-25                                                                                                                                                                  | 170<br>200<br>250                                                  | 5 ± 10%                                                                                               | 220                                                                | 1.5                     | 32            | J                    | Military<br>CMOS                                | 9-113 |

|                  |                     | TMS29F010-100 <sup>‡</sup><br>TMS29F010-120 <sup>‡</sup><br>TMS29F010-12 <sup>‡</sup><br>TMS29F010-150 <sup>‡</sup><br>TMS29F010-150 <sup>‡</sup><br>TMS29F010-200 <sup>‡</sup><br>TMS29F010-200 <sup>‡</sup> | 100<br>120<br>120<br>150<br>150<br>200<br>200                      | 5 ± 5%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%                                 | 79<br>79<br>83<br>79<br>83<br>79<br>83                             | 5.5                     | 32, 32,<br>32 | J, N,<br>FM          | CMOS 5-V<br>Flash<br>EEPROM                     | 7-95  |

<sup>†</sup> J Ceramic Dual In-Line Package (DIP)

<sup>‡</sup> Advance Information for product under development by TI

N Plastic Dual In-Line Package (DIP)

FM Plastic Leaded Chip Carrier

#### EPROM/Flash EEPROM (Concluded)

|                   | Organization   | Device                                                                                                                                                                                                                                 | Max                                                         | Power                                                                                      |                                                             | Power<br>Ipation        |      |          |                  |       |

|-------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------|------|----------|------------------|-------|

| Density           | (Words × Bits) | Number                                                                                                                                                                                                                                 | Access<br>Time (ns)                                         | Supply<br>(V)                                                                              | Active<br>(mW)                                              | Standby<br>CMOS<br>(mW) | Pins | Package† | Comments         | Page  |

| 1024K<br>(cont'd) | 64K×16         | TMS27C210A-120‡<br>TMS27C210A-12‡<br>TMS27C210A-150‡<br>TMS27C210A-150‡<br>TMS27C210A-200‡<br>TMS27C210A-200‡<br>TMS27C210A-250‡<br>TMS27C210A-250‡                                                                                    | 120<br>120<br>150<br>150<br>200<br>200<br>250<br>250        | 5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%           | 158<br>165<br>158<br>165<br>158<br>165<br>158<br>165        | 0.55                    | 40   | J        | CMOS             | 7-119 |

|                   |                | SMJ27C210A-17<br>SMJ27C210A-20<br>SMJ27C210A-25                                                                                                                                                                                        | 170<br>200<br>250                                           | 5 ± 10%                                                                                    | 220                                                         | 1.5                     | 32   | J.       | Military<br>CMOS | 9-115 |

| 2048K             | 256K × 8       | TMS27C020-100‡ TMS27C020-120‡ TMS27C020-125‡ TMS27C020-150‡ TMS27C020-150‡ TMS27C020-200‡ TMS27C020-200‡ TMS27C020-250‡ TMS27C020-250‡                                                                                                 | 100<br>120<br>120<br>150<br>150<br>200<br>200<br>250<br>250 | 5 ± 5%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10% | 158<br>158<br>165<br>158<br>165<br>158<br>165<br>158<br>165 | 0.55                    | 32   | J        | CMOS             | 7-129 |

| 4096K             | 512K x 8       | TMS27C040-8 <sup>‡</sup><br>TMS27C040-80 <sup>‡</sup><br>TMS27C040-100 <sup>‡</sup><br>TMS27C040-10 <sup>‡</sup><br>TMS27C040-120 <sup>‡</sup><br>TMS27C040-120 <sup>‡</sup><br>TMS27C040-15 <sup>‡</sup><br>TMS27C040-15 <sup>‡</sup> | 80<br>80<br>100<br>100<br>120<br>120<br>150                 | 5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%           | 263<br>275<br>263<br>275<br>263<br>275<br>263<br>275        | 0.55                    | 32   | J        | CMOS             | 7-139 |

|                   | 256K × 16      | TMS27C240-8‡<br>TMS27C240-80‡<br>TMS27C240-100‡<br>TMS27C240-100‡<br>TMS27C240-120‡<br>TMS27C240-120‡<br>TMS27C240-150‡<br>TMS27C240-150‡                                                                                              | 80<br>80<br>100<br>100<br>120<br>120<br>150                 | 5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%<br>5 ± 5%<br>5 ± 10%           | 263<br>275<br>263<br>275<br>263<br>275<br>263<br>275        | 0.55                    | 40   | J        | CMOS             | 7-149 |

<sup>†</sup> J Ceramic Dual In-Line Package (DIP) ‡ Advance Information for product under development by TI

One-Time Programmable (OTP) PROM

|                   | Organization<br>(Words × Bits) | Device                                                                                                                                               | Max                                                                | Power                                                                                                                                                                                                   |                                                                    | Power<br>ipation        |        |                      |                                           |       |