# SN74ACT8800 Family

32-Bit CMOS Processor Building Blocks

1989

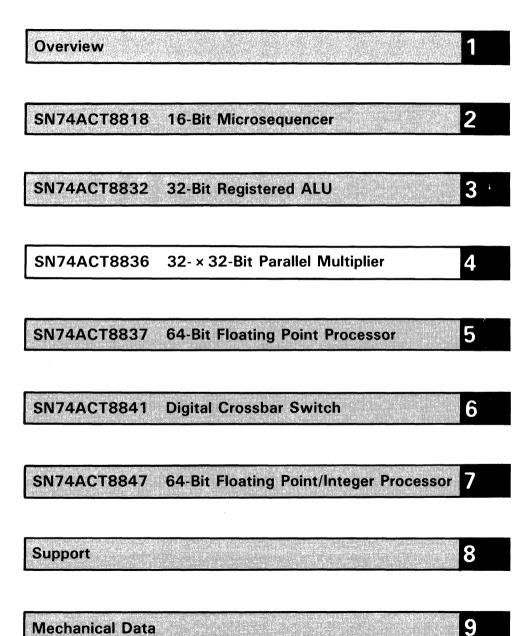

| Overview    |                       | 1 |

|-------------|-----------------------|---|

| SN74ACT8818 | 16-Bit Microsequencer | 2 |

| SN74ACT8832 | 32-Bit Registered ALU | 3 |

| SN74ACT8836 | 32- × 32-Bit Parallel Multiplier | 4          |

|-------------|----------------------------------|------------|

| 1           | •                                | <b>U</b> 1 |

| SN74ACT8837 64-Bit Floating Point Processor | 5 |

|---------------------------------------------|---|

|---------------------------------------------|---|

| SN74ACT8841 | Digital Crossbar Switch | 6 |

|-------------|-------------------------|---|

|             |                         |   |

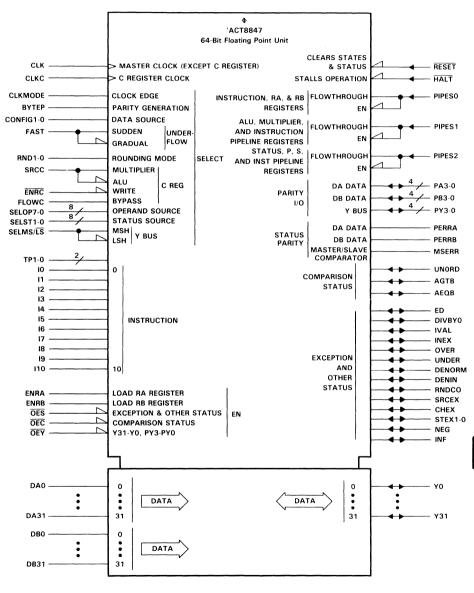

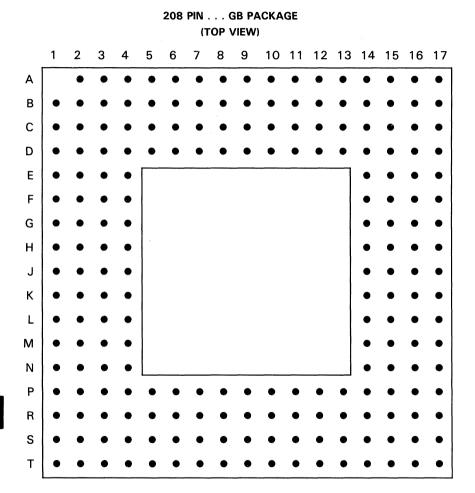

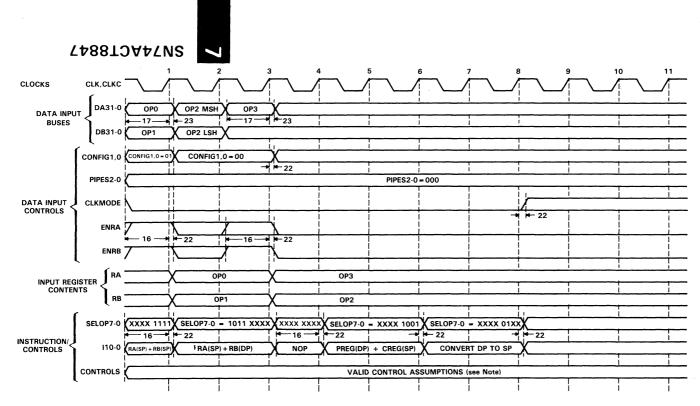

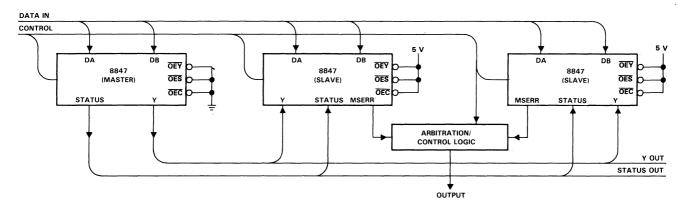

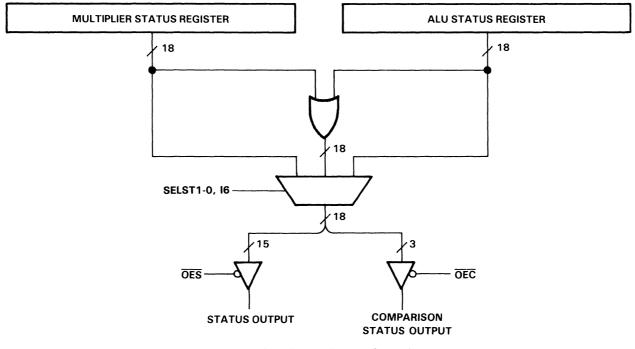

SN74ACT8847 64-Bit Floating Point/Integer Processor 7

Support

Mechanical Data

# SN74ACT8800 Family 32-Bit CMOS Processor Building Blocks

Data Manual

### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1988, Texas Instruments Incorporated First edition: March 1988 First revision: June 1988 Second revision: June 1989

## INTRODUCTION

In this manual, Texas Instruments presents technical information on the TI SN74ACT8800 family of 32-bit processor "building block" circuits. The SN74ACT8800 family is composed of single-chip VLSI processor functions, all of which are designed for high-complexity processing applications.

This manual includes specifications and operational information on the following highperformance advanced-CMOS devices:

- SN74ACT8818 16-bit microsequencer

- SN74ACT8832 32-bit registered ALU

- SN74ACT8836 32- × 32-bit parallel multiplier

- SN74ACT8837 64-bit floating point processor

- SN74ACT8841 Digital crossbar switch

- SN74ACT8847 64-bit floating point/integer processor

These high-speed devices operate at or above 20 MHz, while providing the low power consumption of TI's advanced one-micron EPIC<sup>™</sup> CMOS technology. The EPIC<sup>™</sup> CMOS process combines twin-well structures for increased density with one-micron gate lengths for increased speed.

The *SN74ACT8800 Family* Data Manual contains design and specification data for all five devices previously listed and includes additional programming and operational information for the '8818, '8832, and '8837/'8847. Two application notes, ''Chebyshev Routines for the SN74ACT8847'' and ''High-speed Vector Math and 3D Graphics Using the SN74ACT8837/8847 Floating Point Unit'' are also included.

Introductory sections of the manual include an overview of the '8800 family and a summary of the software tools and design support TI offers for the chip-set. The general information section includes an explanation of the function tables, parameter measurement information, and typical characteristics related to the products listed in this volume.

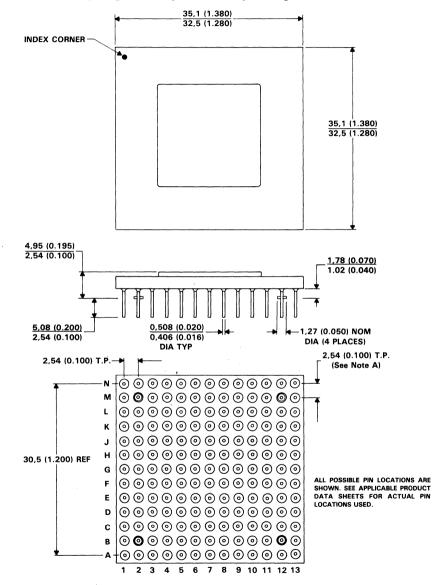

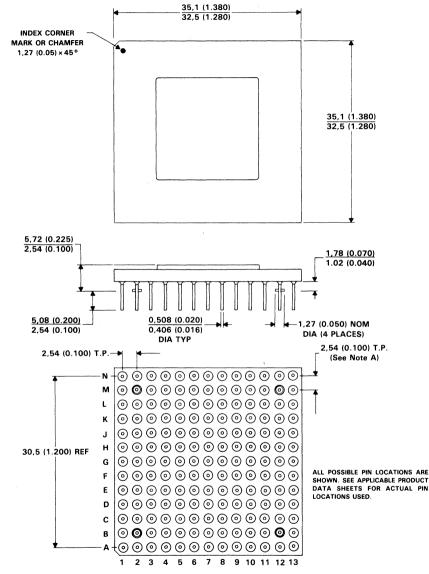

Package dimensions are given in the Mechanical Data section of the book in metric measurement (and parenthetically in inches).

Complete technical data for any Texas Instruments semicondutor product is available from your nearest TI field sales office, local authorized TI distributor, or by calling Texas Instruments at 1-800-232-3200.

EPIC is a trademark of Texas Instruments Incorporated.

vi

1

SN74ACT8818 16-Bit Microsequencer 2

SN74ACT8832 32-Bit Registered ALU 3

SN74ACT8836 32- × 32-Bit Parallel Multiplier 4

SN74ACT8837 64-Bit Floating Point Processor

SN74ACT8841 Digital Crossbar Switch

SN74ACT8847 64-Bit Floating Point/Integer Processor 7

Support

8

5

6

**Mechanical Data**

1-2

## Introduction

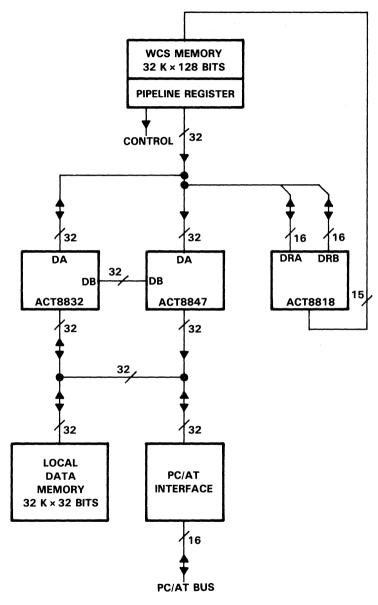

Texas Instruments SN74ACT8800 family of 32-bit processor building blocks has been developed to allow the easy, custom design of functionally sophisticated, high-performance processor systems. The '8800 family is composed of single-chip, VLSI devices, each of which represents an element of a CPU.

Geared for computationally intensive applications, SN74ACT8800 devices include highperformance ALUs, multipliers, microsequencers, and floating point processors.

The '8800 chip set provides the performance, functionality, and flexibility to fill the most demanding processing needs and is structured to reduce system design cost and effort. Most of these high-speed processor functions operate at 20 MHz and above, and, at the same time, provide the power savings of TI's advanced, 1  $\mu$ m EPIC<sup>TM</sup> CMOS technology.

The family's building block approach allows the easy, ''pick-and-choose'' creation of customized processor systems, while the devices' high level of integration provides cost-effectiveness.

Designed especially for high-complexity processing, the devices in the '8800 family offer a range of functional options. Device features include three-port architecture, double-precision accuracy, optional pipelined operation, and built-in fault tolerance.

Array, digital signal, image, and graphics processing can be optimized with '8800 devices. Other applications are found in supermini and fault-tolerant computers, and I/O and network controllers.

In addition to the high-performance, CMOS processor functions featured in this data manual, the family includes several high-speed, low-power bipolar support chips. To reduce power dissipation and ensure reliability, these bipolar devices use TI's proprietary Schottky Transistor Logic (STL) internal circuitry.

At present, TI's '8800 32-bit processor building block family comprises the following functions:

- SN74ACT8818 16-bit microsequencer

- SN74ACT8832 32-bit registered ALU

- SN74ACT8836 32- × 32-bit parallel multiplier

- SN74ACT8837 64-bit floating point processor

- SN74ACT8841 digital crossbar switch

- SN74ACT8847 64-bit floating point and integer processor

- Bipolar Support Chips

- SN74AS8838 32-bit barrel shifter

- SN74AS8839 32-bit shuffle/exchange network

- SN74AS8840 16 × 4 crossbar switch

## 20 MIPS and Low CMOS Power Consumption

With instruction cycle times of 50 ns or less and the low power consumption of EPIC<sup>™</sup> CMOS, the '8800 chip set offers an unrivaled speed/power combination. Unlike traditional microprocessors, which require multiple cycles to perform an operation, the 'ACT8800 processors typically can complete instructions in a single cycle.

The 'ACT8832 registered ALU and 'ACT8818 microsequencer together create a powerful 20-MHz CPU. Because instructions can be performed in a single cycle, the 8832/8818 combination is capable of executing over 20 million instructions per second (MIPS).

For math-intensive applications, the 'ACT8836 fixed-point multiplier/accumulator (MAC), 'ACT8837 64-bit floating point processor, and 'ACT8847 64-bit floating point and integer processor offer unprecedented computational power.

The exceptional performance of the 'ACT8800 family is made possible by TI's EPIC<sup>™</sup> CMOS technology. The EPIC<sup>™</sup> CMOS process combines twin-well structures for increased density with one-micron gate lengths for increased speed.

## **Customized Solution**

The '8800 family is designed with a variety of architectural and functional options to provide maximum design flexibility. These device features allow the creation of ''customized'' solutions with the '8800 chipset.

A **building block approach** to processing allows designers to match specialized hardware to their specific design needs. The '8818/8832 combination forms the basis of the system, a high-speed CPU. For applications requiring high-speed integer multiplication, the 'ACT8836 can be added. To provide the high precision and large dynamic range of floating point numbers, the 'ACT8837 or 'ACT8847 can be employed.

Overview

To ensure speed and flexibility, each component of the '8800 family has **three data ports**. Each data port accommodates 32 bits of data, plus four parity bits. This architecture eliminates many of the I/O bottlenecks associated with traditional single-I/O microprocessors.

The three-port architecture and functional partitioning of the '8800 chip-set opens the door to a variety of **parallel processing** applications. Placing the math and shifting functions in parallel with the ALU permits concurrent processing of data. Additional processors can be added when performance needs dictate.

The 'ACT8800 building block processors are microprogrammable, so that their instruction sets can be tailored to a specific application. This **high degree of programmability** offers greater speed and flexibility than a typical microprocessor and ensures the most efficient use of hardware.

A **separate control bus** eliminates the need for multiplexing instructions and data, further reducing processing bottlenecks. The microcode bus width is determined by the designer and the application.

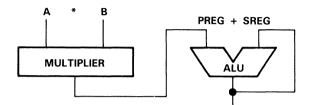

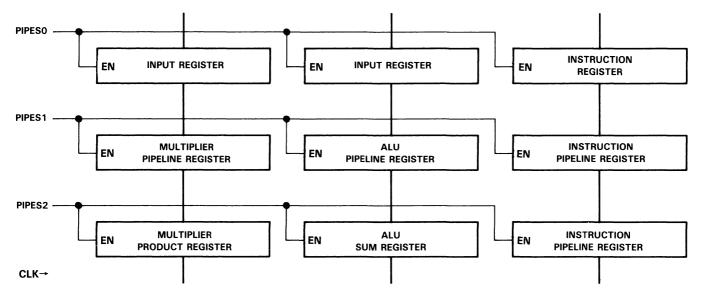

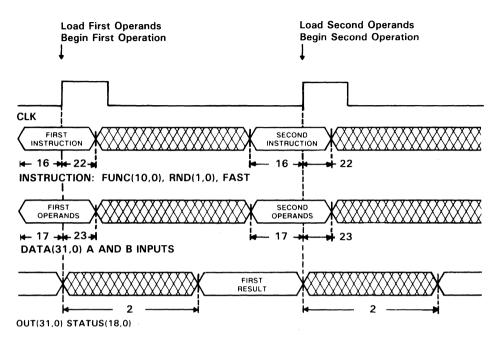

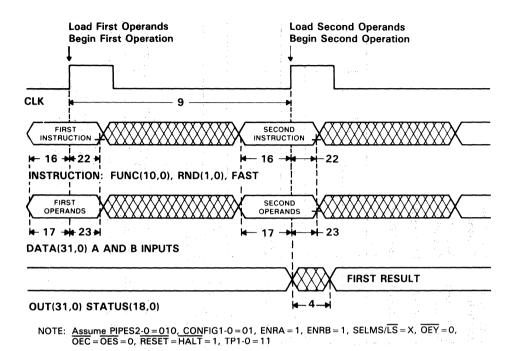

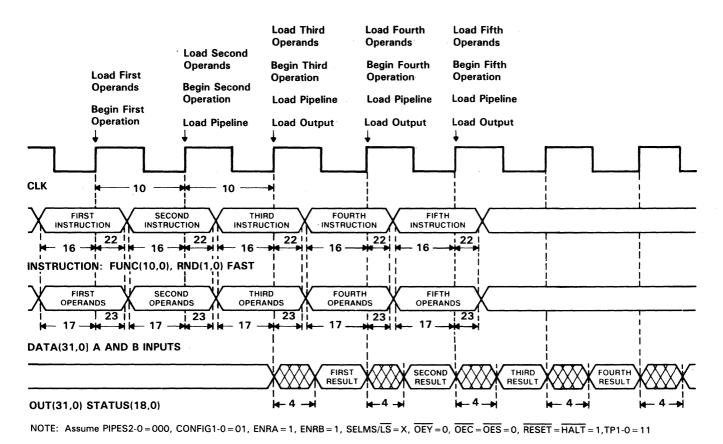

Another source of design flexibility is provided by the **pipelined**/flowthrough operation option. Pipelining can dramatically reduce the time required to perform iterative, or sequential, calculations. On the other hand, random or nonsequential algorithms require fast flowthrough operations. The '8800 chip set allows the designer to select the mode (fully pipelined, partially pipelined, or nonpipelined) most suited to each design.

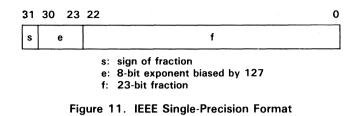

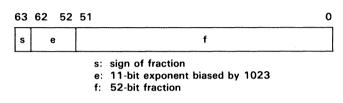

## **Scientific Accuracy**

The '8800 family is designed to support applications which require **double-precision accuracy**. Many scientific applications, such as those in the areas of high-end graphics, digital signal processing, and array processing, require such accuracy to maintain data integrity. In general-purpose computing applications, floating point processors must often support double-precision data formats to maintain compatibility with existing software.

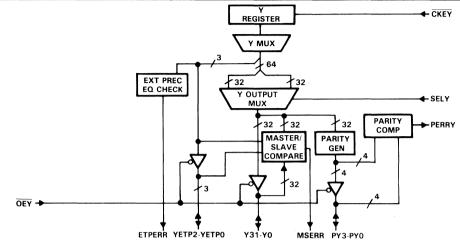

To ensure data integrity, '8800 devices (excluding the barrel shifter and microsequencer) support **parity checking and generation**, as well as **master/slave error detection**. Byte parity checking is performed on the input ports, and a parity generator and a master/slave comparator are provided at the output. **Fault tolerance** is built into the processors, ensuring correct device operation without extra logic or costly software.

## The SN74ACT8800 Building Block Processor System

Some of the high-performance '8800 devices are described in the following paragraphs.

## SN74ACT8818 16-Bit Microsequencer

In a high-performance microcoded system, a fast microcode controller is required to control the flow of instructions. The SN74ACT8818 is a high-speed, versatile 16-bit microsequencer capable of addressing 64K words of microcode memory. The 'ACT8818 can address the next instruction fast enough to support a 50-ns system cycle time.

The 'ACT8818 65-word-deep by 16-bit-wide stack is useful for storing subroutine return addresses, top of loop addresses, and loop counts. Addresses can be sourced from eight different sources: the three I/O ports, the two register counters, the microprogram counter, the stack, and the 16-way branch.

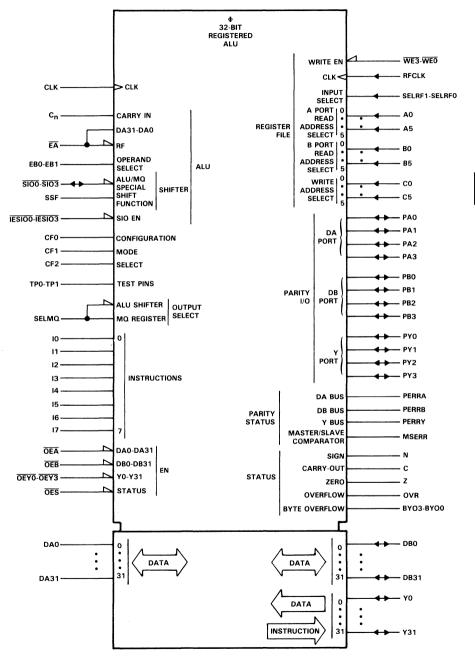

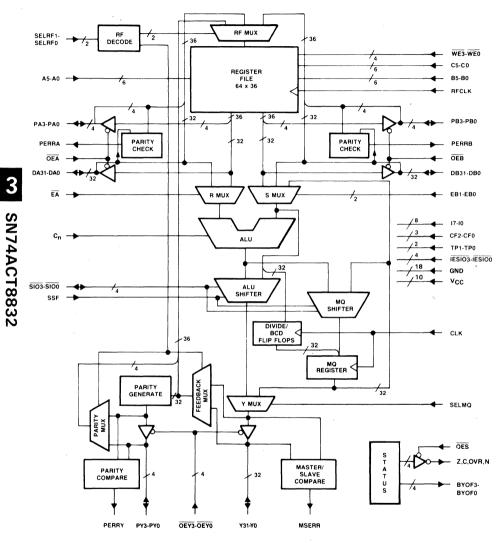

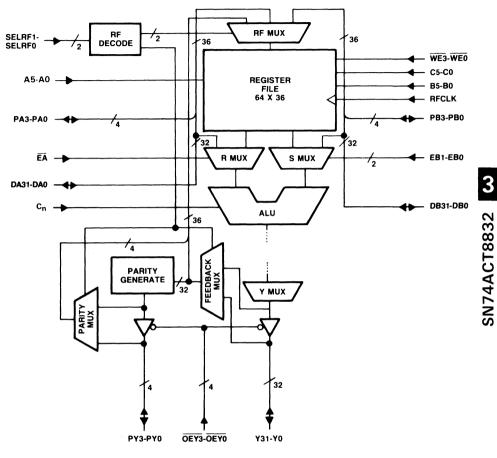

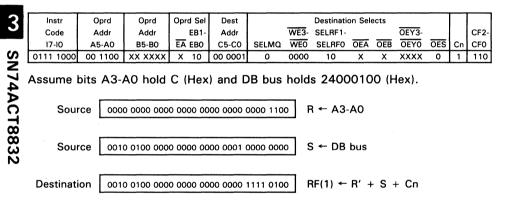

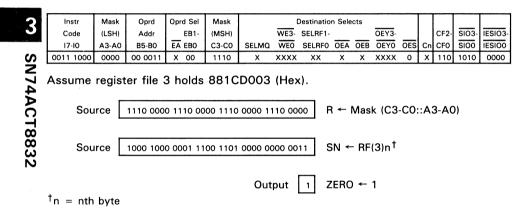

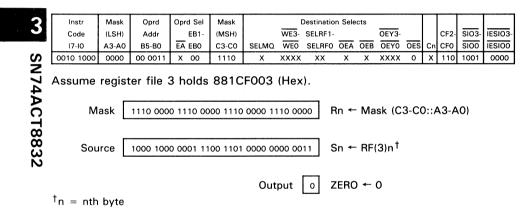

## SN74ACT8832 Registered ALU

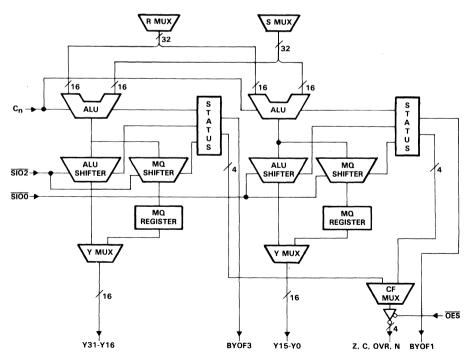

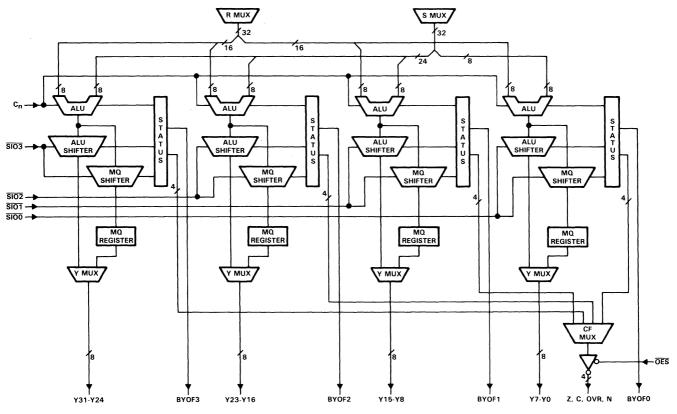

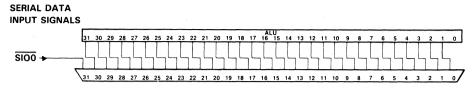

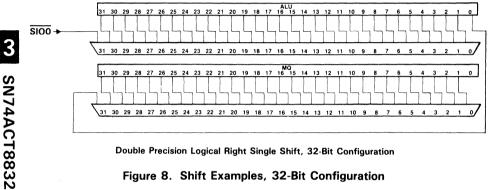

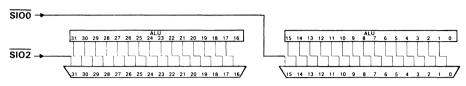

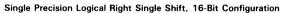

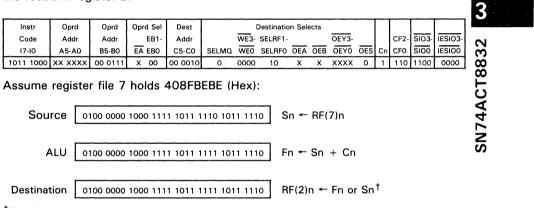

The SN74ACT8832 is a 32-bit registered ALU that operates at approximately 20 MHz. Because instructions can be performed in a single cycle, the 'ACT8832 is capable of executing 20 million microinstructions per second. An on-board 64-word register file is 36-bits-wide to permit the storage of parity bits. The 3-operand register file increases performance by enabling the creation of an instruction and the storage of the previous result in a single cycle. To facilitate data transfer, operands stored in the register file can be accessed externally, while the ALU is executing. To support the parallel processing of data, the 'ACT8832 can be configured to operate as four 8-bit ALUs, two 16-bit ALUs, or a single 32-bit ALU. The 'ACT8832 incorporates 32-bit shifters for double-precision shift operations.

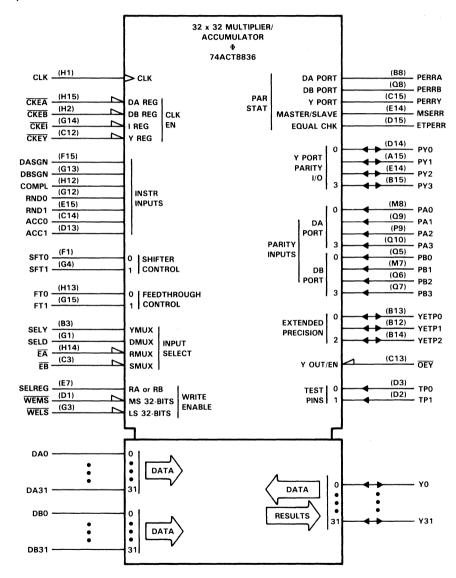

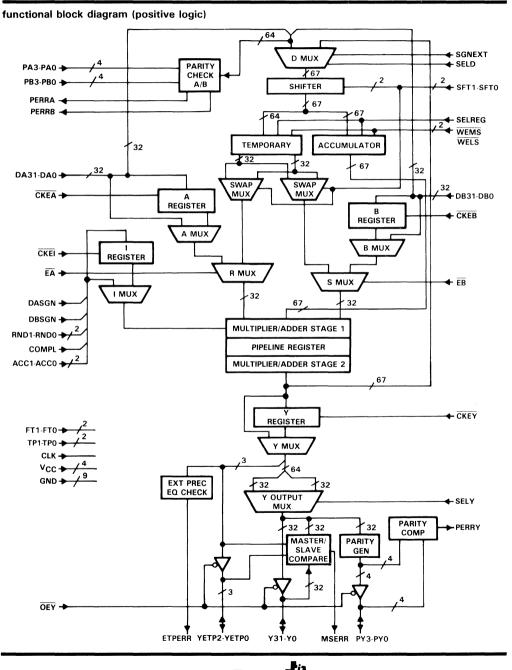

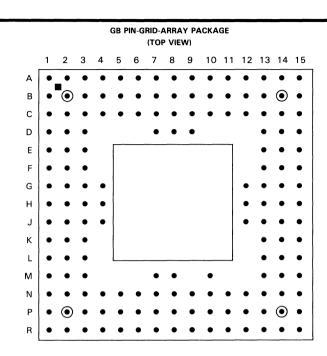

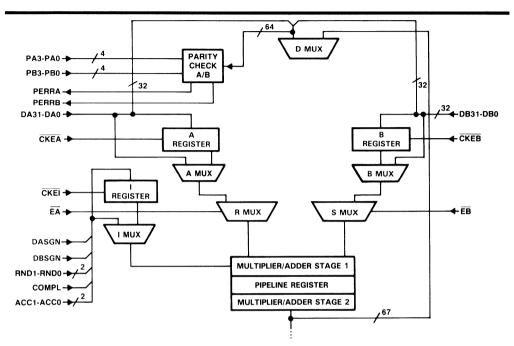

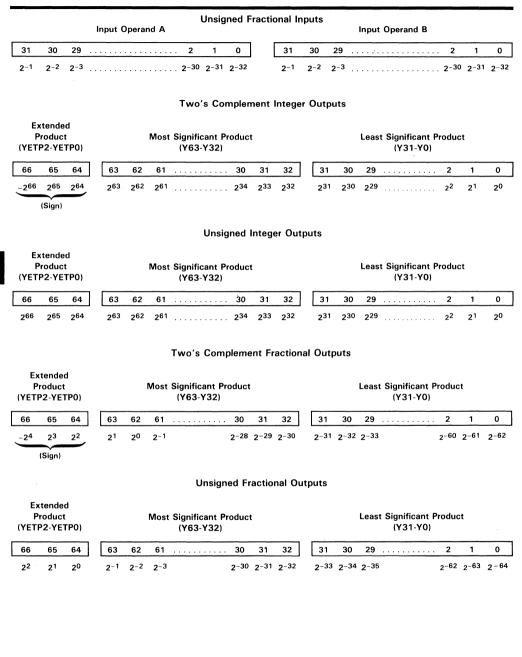

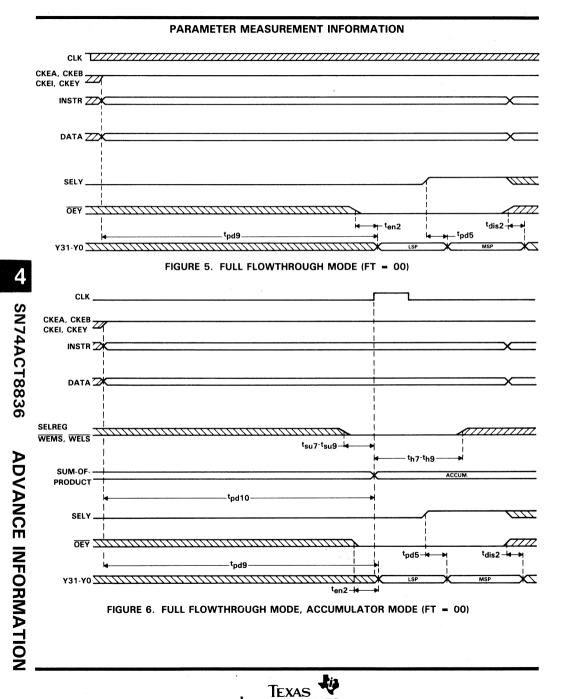

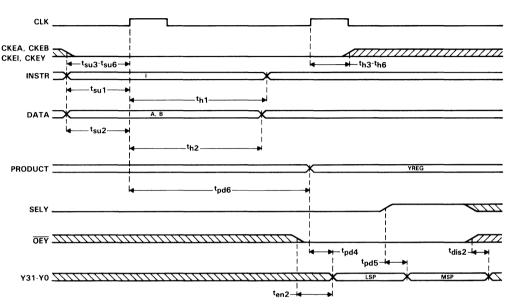

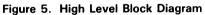

## SN74ACT8836 32- × 32-Bit Integer MAC

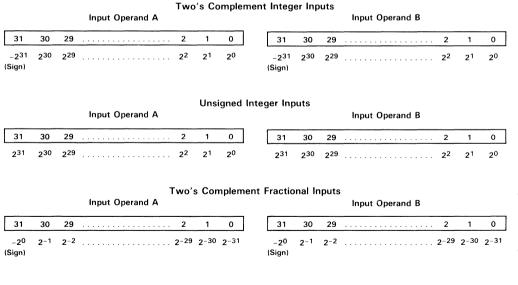

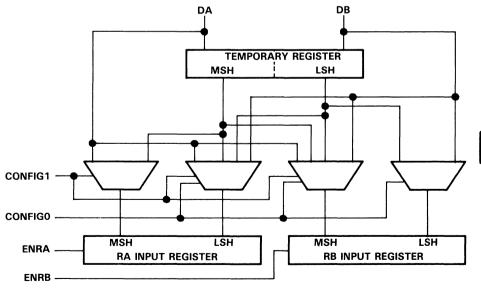

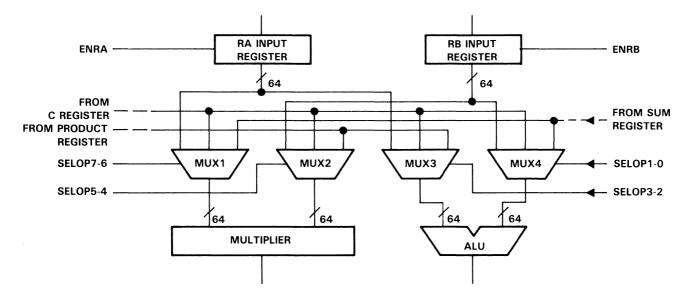

The SN74ACT8836 is a 32-bit integer multiplier/accumulator (MAC) that accepts two 32-bit inputs and computes a 64-bit product. The device can also operate as a 64-bit by 64-bit multiplier. An onboard adder is provided to add or subtract the product or the complement of the product from the accumulator.

When pipelined internally, the 1- $\mu$ m CMOS parallel MAC performs a full 32-  $\times$  32-bit multiply/accumulate in a single 36-ns clock cycle. In flowthrough mode (without any pipelining), the 'ACT8836 takes 60 ns to multiply two 32-bit numbers. The 'ACT8836 performs a 64-  $\times$  64-bit multiply/accumulate, outputting a 64-bit result, in 225 ns.

The 'ACT8836 can handle a wide variety of data types, including two's complement, signed, and mixed. Division is supported via the Newton-Raphson algorithm.

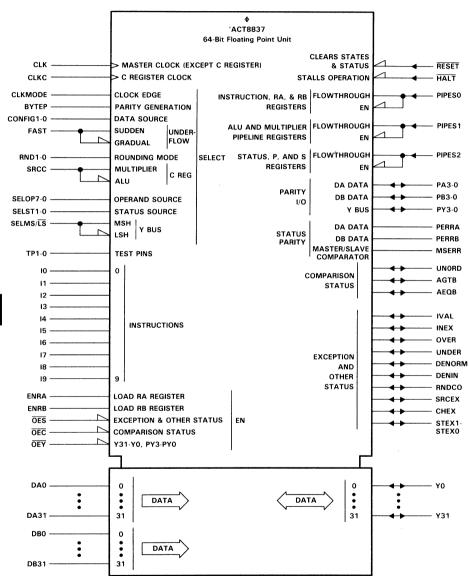

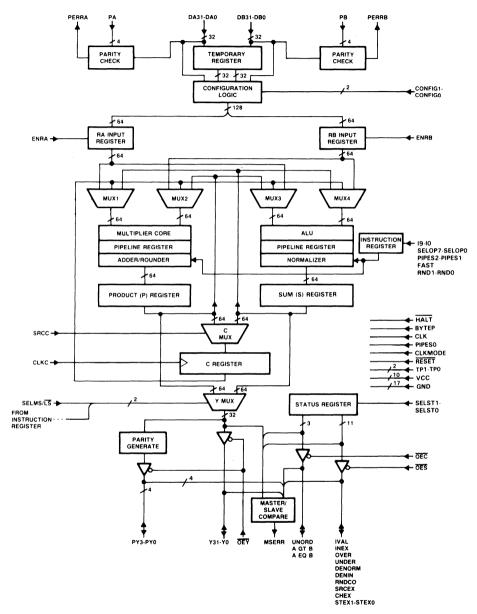

## SN74ACT8837 64-Bit Floating Point Unit

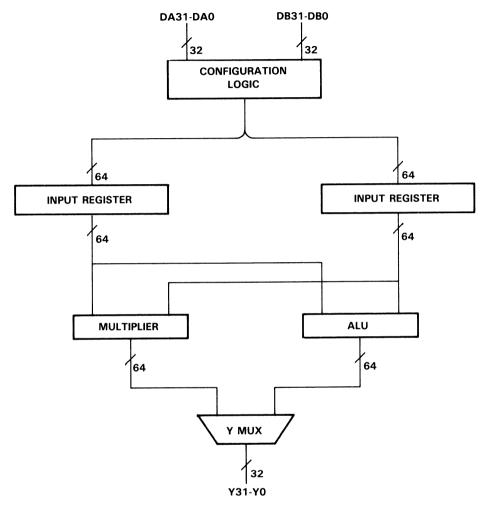

The SN74ACT8837 is a high-speed floating point processor. This single-chip device performs 32- or 64-bit floating point operations.

1

More than just a coprocessor, the 'ACT8837 integrates on one chip a double-precision floating point ALU and multiplier. Integrating these functions on a single chip reduces data routing problems and processing overhead. In addition, three data ports and a 64-bit internal bus architecture allow for single-cycle operations.

The 'ACT8837 can be pipelined for iterative calculations or can operate with input registers disabled for low latency.

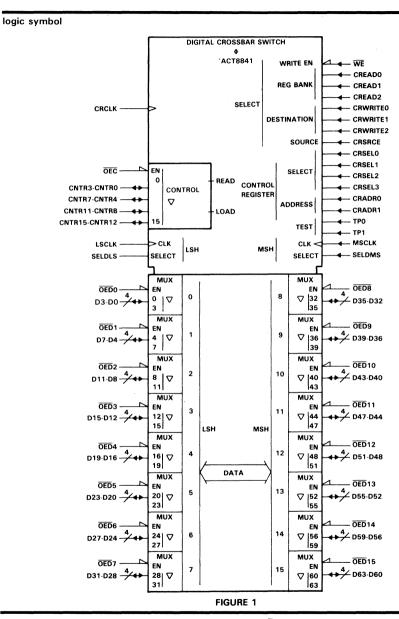

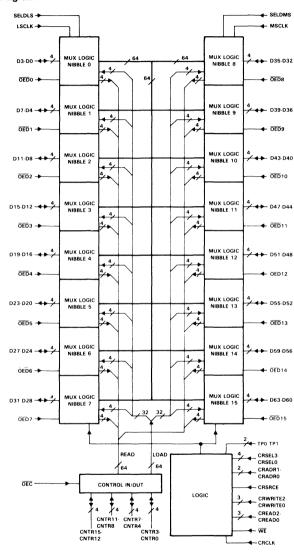

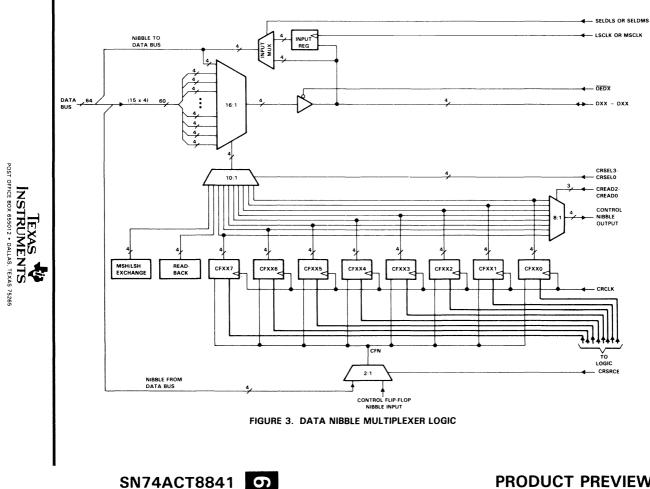

## SN74ACT8841 Digital Crossbar Switch

The SN74ACT8841 is a single-chip digital crossbar switch. The high-performance device, cost-effectively eliminates bottlenecks to speed data through complex bus architecture.

The 'ACT8841 is ideal for multiprocessor applications, where memory bottlenecks tend to occur. The device has 64 bidirectional I/O ports that can be configured as 16 4-bit ports, 8 8-bit ports, or 4 16-bit ports. Each bidirectional port can be connected in any conceivable combination. Any single input port can be broadcast to any combination of output ports. The total time for data transfer is 20 ns.

The control sources for ten separate switching configurations are on-chip, including eight banks of programmable control flip-flops and two hard-wired control circuits.

The EPIC<sup>™</sup> CMOS SN74ACT8841 and its predecessor, SN74AS8840, are based on the same architecture, differing in power consumption, number of control registers, and pin-out. Microcode written for the 'AS8840 can be run on the 'ACT8841.

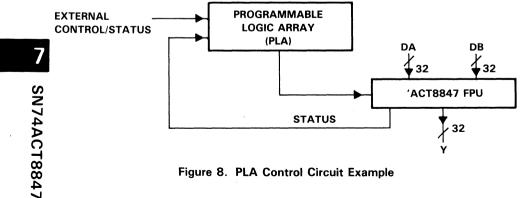

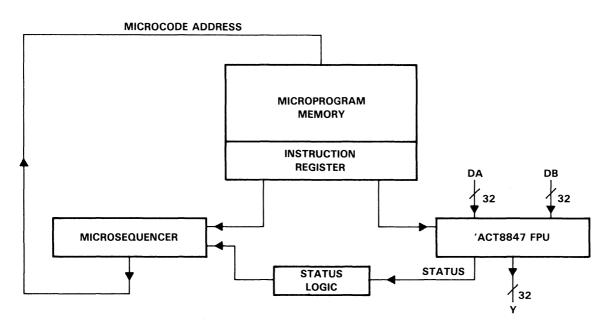

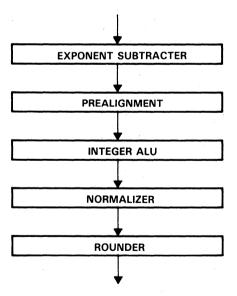

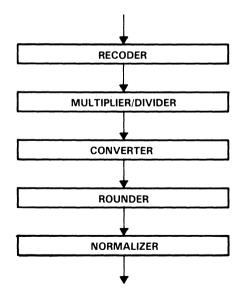

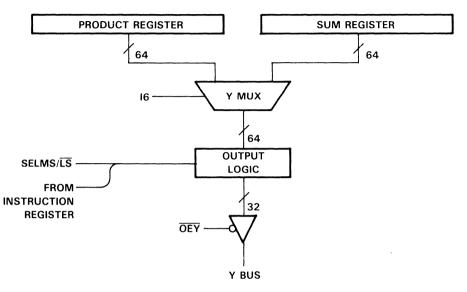

## SN74ACT8847 64-Bit Floating Point Unit

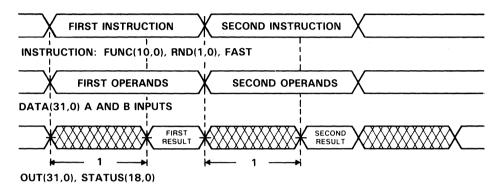

The SN74ACT8847 is a high-speed 64-bit floating point processor. The device is fully compatible with IEEE standard 754-1985 for addition, subtraction, multiplication, division, square root, and comparison. Division and square root operations are implemented via hardwired control.

The SN74ACT8847 FPU also performs integer arithmetic, logical operations, and logical shifts. Registers are provided at the inputs, outputs, and inside the ALU and multiplier to support multilevel pipelining. These registers can be bypassed for nonpipelined operations.

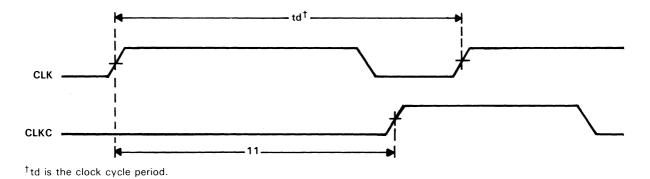

When fully pipelined, the 'ACT8847 can perform a double-precision floating point or 32-bit integer operation in under 40 ns. When in flowthrough mode, the 'ACT8847 takes less than 100 ns to perform an operation.

### **Bipolar Support Chips**

Overview

1

The SN74AS8838 high-speed, 32-bit barrel shifter can shift up to 32 bits in a single instruction cycle of under 25 ns. Five basic shifts can be programmed: circular left, circular right, logical left, logical right, and arithmetic right. The 'AS8838 offloads the responsibility for shifting operations from the ALU, which increases shifter functionality and system throughput.

The SN74AS8839 is a 32-bit shuffle/exchange network. The high-speed device can perform data permutations on one 32-bit, two 16-bit, four 8-bit, or eight 4-bit data words in a single instruction cycle of under 25 ns. The shuffle/exchange network is designed primarily for use in digital signal processing applications.

SN74ACT8818 16-Bit Microsequencer

SN74ACT8832 32-Bit Registered ALU 3

SN74ACT8836 32-×32-Bit Parallel Multiplier 4

SN74ACT8837 64-Bit Floating Point Processor 5

SN74ACT8841 Digital Crossbar Switch 6

SN74ACT8847 64-Bit Floating Point/Integer Processor 7

Support

8

9

2

Mechanical Data

# SN74ACT8818 16-Bit Microsequencer

- Addresses Up to 64K Locations of Microprogram Memory

- CLK-to-Y = **30 ns**  $(t_{pd})$

- Low-Power EPIC<sup>™</sup> CMOS

- Addresses Selected from Eight Different Sources

- Performs Multiway Branching, Conditional Subroutine Calls, and Nested Loops

- Large 65-Word by 16-bit Stack

- Cascadable

Because they're microprogrammable, the ACT8800 building block processors provide greater speed and flexibility than does a typical microprocessor. In such a high-performance microcoded system, a fast microsequencer is required to control the flow of microinstructions.

The SN74ACT8818 is a high-speed, versatile 16-bit microsequencer capable of addressing 64K words of microcode memory. The 'ACT8818 can address the next instruction fast enough to support a 50-ns system cycle time.

The 'ACT8818 65-word-deep by 16-bit-wide stack is useful for storing subroutine return addresses, top-of-loop addresses, and loop counts. For added flexibility, addresses can be selected from eight different sources: the three I/O ports, the two register/counters, the microprogram counter, the stack, and the 16-way branch input.

EPIC is a trademark of Texas Instruments Incorporated.

## Contents

|                                                                                                                                                                                    | Page                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Introduction                                                                                                                                                                       | 2-11 2                                                            |

| Understanding the 'ACT8818 Microsequencer<br>Microprogramming the 'ACT8818<br>Design Support<br>Systems Expertise<br>'ACT8818 Pin Grid Allocation<br>'ACT8818 Specification Tables | 2-11<br>2-12<br>2-12<br>2-12<br>2-13<br>2-14<br>2-21<br>4<br>2-21 |

| Architecture                                                                                                                                                                       | 2-25                                                              |

| Y Output Multiplexer                                                                                                                                                               | 0<br>2-28<br>2-28<br>2-28<br>2-29<br>2-29                         |

| Stack Pointer<br>Read Pointer<br>Stack Warning/Read Error Pin<br>Interrupt Return Register                                                                                         | 2-29<br>2-29<br>2-29<br>2-30                                      |

| Microprogramming the 'ACT8818                                                                                                                                                      | 2-31                                                              |

| Address Selection          Stack Controls          Register Controls                                                                                                               | 2-32<br>2-32<br>2-33                                              |

| Continue/Repeat Instructions         Branch Instructions         Conditional Branch Instructions         Loop Instructions                                                         | 2-34<br>2-34<br>2-35<br>2-35                                      |

| Subroutine Calls                                                                                                                                                                   | 2-37<br>2-38<br>2-39                                              |

| Clear Pointers                                                                                                                                                                     | 2-39<br>2-39<br>2-39                                              |

2-5

## **Contents (Continued)**

| 2 <sub>sa</sub> | ample Microinstructions for the 'ACT8818 | 2-40 |

|-----------------|------------------------------------------|------|

| SN74AC          | Continue                                 | 2-40 |

| 17.             | Continue and Pop                         | 2-40 |

| 4 A             | Continue and Push                        | 2-40 |

| ó               | Branch (Example 1)                       | 2-42 |

| <b>T</b> 8      | Branch (Example 2)                       | 2-42 |

| 8               | Sixteen-Way Branch                       | 2-42 |

| 18              | Conditional Branch                       | 2-44 |

| •••             | Three-Way Branch                         | 2-44 |

|                 | Thirty-Two-Way Branch                    | 2-44 |

|                 | Repeat                                   | 2-46 |

|                 | Repeat on Stack                          | 2-46 |

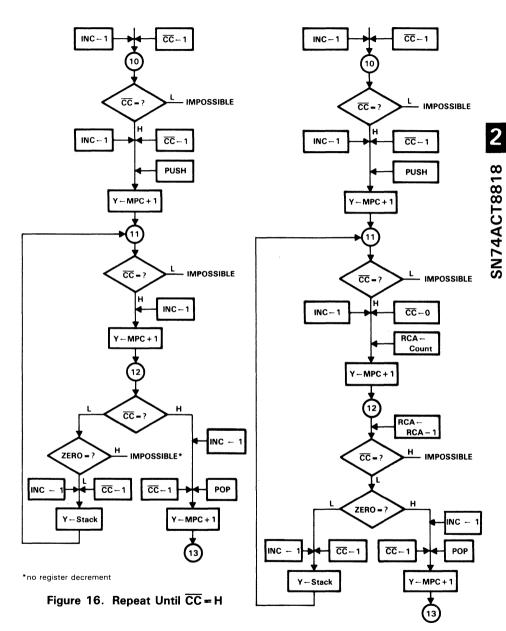

|                 | Repeat Until CC = H                      | 2-48 |

|                 | Loop Until Zero                          | 2-48 |

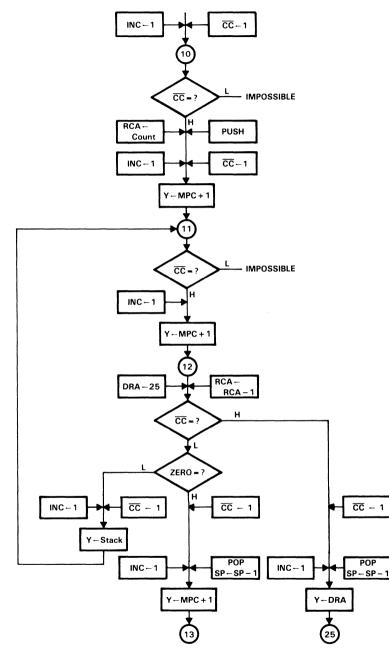

|                 | Conditional Loop Until Zero              | 2-50 |

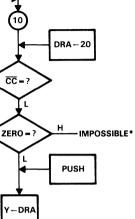

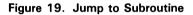

|                 | Jump to Subroutine                       | 2-52 |

|                 | Conditional Jump to Subroutine           | 2-52 |

|                 | Two-Way Jump to Subroutine               | 2-52 |

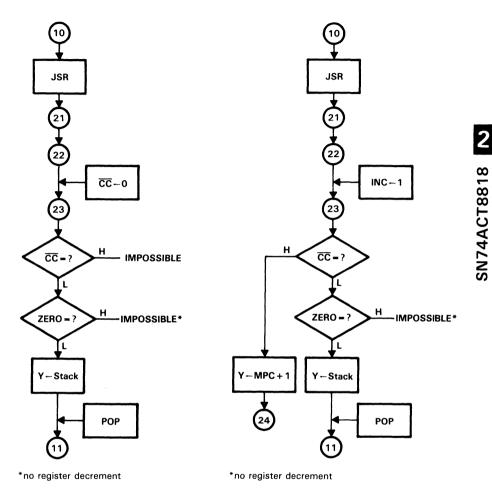

|                 | Return from Subroutine                   | 2-54 |

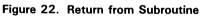

|                 | Conditional Return from Subroutine       | 2-54 |

|                 | Clear Pointers                           | 2-54 |

|                 | Reset                                    | 2-54 |

# List of Illustrations

| Figure | Title                                   | Page |           |

|--------|-----------------------------------------|------|-----------|

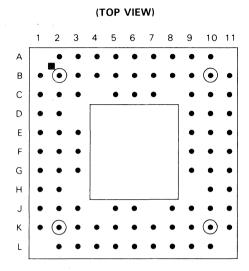

| 1      | 'ACT8818 GC Package                     | 2-14 | 2         |

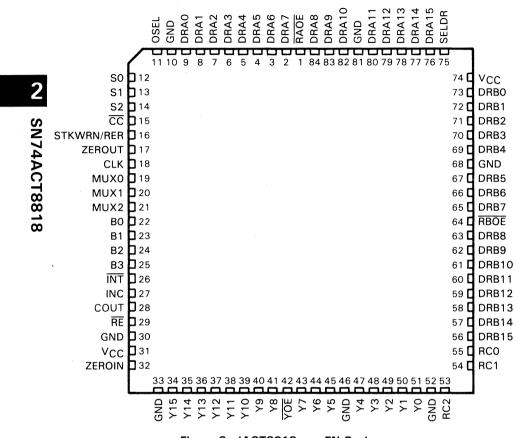

| 2      | 'ACT8818 FN Package                     | 2-16 | 4         |

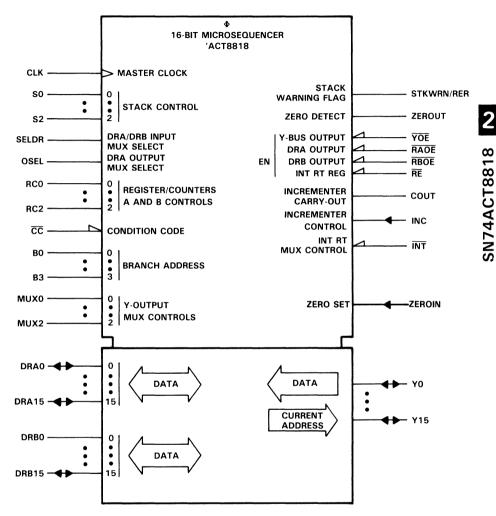

| 3      | ACT8818 Logic Symbol                    | 2-17 | ω         |

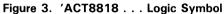

| 4      | ACT8818 Functional Block Diagram        | 2-27 | <b>~~</b> |

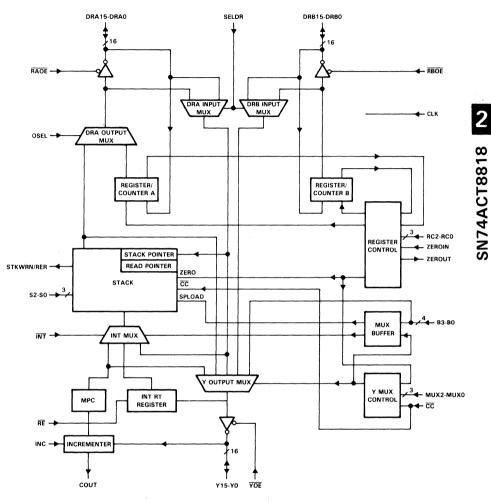

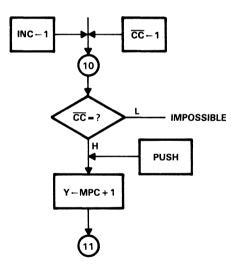

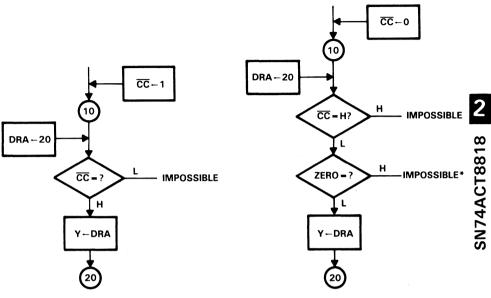

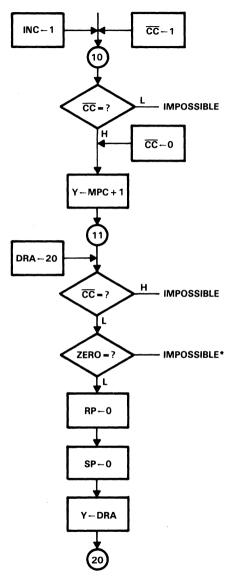

| 5      | Continue                                | 2-41 | 88        |

| 6      | Continue and Pop                        | 2-41 | Ë         |

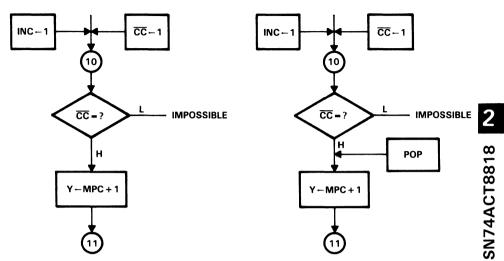

| 7.     | Continue and Push                       | 2-41 | 4ACT      |

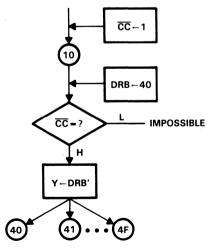

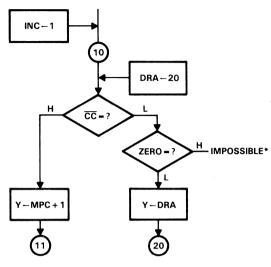

| 8      | Branch Example 1                        | 2-43 | 4         |

| 9      | Branch Example 2                        | 2-43 | SN7       |

| 10     | Sixteen-Way Branch                      | 2-43 | S         |

| 11     | Conditional Branch                      | 2-45 |           |

| 12     | Three-Way Branch                        | 2-45 |           |

| 13     | Thirty-Two Way Branch                   | 2-45 |           |

| 14     | Repeat                                  | 2-46 |           |

| 15     | Repeat on Stack                         | 2-47 |           |

| 16     | Repeat Until CC = H                     | 2-49 |           |

| 17     | Loop Until Zero                         | 2-49 |           |

| 18     | Conditional Loop Until Zero (Example 2) | 2-51 |           |

| 19     | Jump to Subroutine                      | 2-53 |           |

| 20     | Conditional Jump to Subroutine          | 2-53 |           |

| 21     | Two-Way Jump to Subroutine              | 2-53 |           |

| 22     | Return from Subroutine                  | 2-55 |           |

| 23     | Conditional Return from Subroutine      | 2-55 |           |

| 24     | Clear Pointers                          | 2-56 |           |

**2** SN74ACT8818

## List of Tables

| Table | Title                                        | Page          |

|-------|----------------------------------------------|---------------|

| 1     | 'ACT8818 Pin Grid Allocation                 | 2-15          |

| 2     | ACT8818 Pin Functional Description           | 2-18          |

| 3     | Response to Control Inputs                   | 2-26          |

| 4     | Y Output Controls (MUX2-MUX0)                | 2-32 💭        |

| 5     | Stack Controls (S2-S0)                       | 2-33 8        |

| 6     | Register Controls (RC2-RC0)                  | 2-33 🛏        |

| 7     | Decrement and Branch on Nonzero Encodings    | 2-36 <b>O</b> |

| 8     | Call Encodings without Register Decrements   | 2-37 🗗        |

| 9     | Call Encodings with Register Decrements      | 2-38          |

| 10    | Return Encodings without Register Decrements | 2-38 <b>5</b> |

| 11    | Return Encodings with Register Decrements    | 2-39          |

## Introduction

The SN74ACT8818 microsequencer is a low-power, high-performance microsequencer implemented in TI's EPIC<sup>™</sup> Advanced CMOS technology. The 16-bit device addresses up to 64K locations of microprogram memory and is compatible with the SN74AS890 2

The 'ACT8818 performs a range of sequencing operations in support of TI's family of building block devices and special-purpose processors such as the SN74ACT8847 Floating Point Unit (FPU).

## Understanding the 'ACT8818 Microsequencer

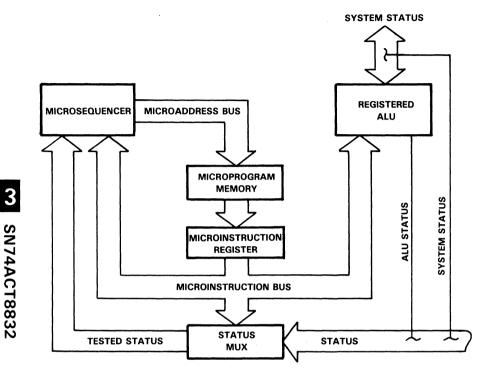

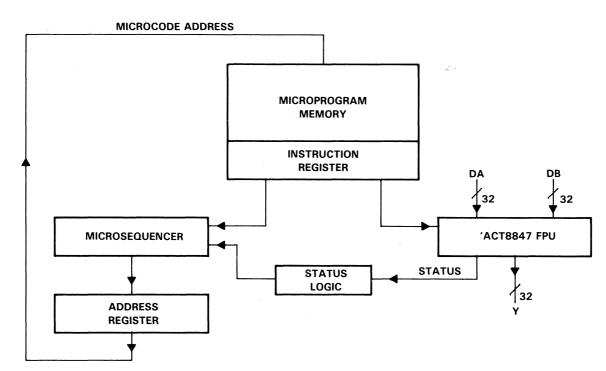

The 'ACT8818 microsequencer is designed to control execution of microcode in a microprogrammed system. Basic architecture of such a system usually incorporates at least the microsequencer, one or more processing elements such as the 'ACT8847 FPU or the SN74ACT8832 Registered ALU, microprogram memory, microinstruction register, and status logic to monitor system states and provide status inputs to the microsequencer.

The 'ACT8818 combines flexibility and high speed in a microsequencer that performs multiway branching, conditional subroutine calls, nested loops, and a variety of other microprogrammable operations. The 'ACT8818 can also be cascaded for providing additional register/counters or addressing capability for more complex microcoded control functions.

In this microsequencer, several sources are available for microprogram address selection. The primary source is the 16-bit microprogram counter (MPC), although branch addresses may be input on the two 16-bit address buses, DRA and DRB. An address input on the DRA bus can be pushed on the stack for later selection. Register/counters RCA and RCB can store either branch addresses or loop counts as needed, either for branch operations or for looping on the stack.

The selection of address source can be based on external status from the device being controlled, so that three-way or multiway branching is supported. Once selected, the address which is output on the Y bus passes to the microprogram memory, and the microinstruction from the selected location is clocked into the pipeline register at the beginning of the next cycle.

It is also possible to interrupt the 'ACT8818 by placing the Y output bus in a highimpedance state and forcing an interrupt vector on the Y bus. External logic is required to place the bus in high impedance and load the interrupt vector. The first microinstruction of the interrupt handler subroutine can push the address from the Interrupt Return register on the stack so that proper linkage is preserved for the return from subroutine.

## Microprogramming the 'ACT8818

Microinstructions for the 'ACT8818 select the specific operations performed by the Y output multiplexer, the register/counters RCA and RCB, the stack, and the bidirectional DRA and DRB buses. Each set of inputs is represented as a separate field in the microinstructions, which control not only the microsequencer but also the ALU or other devices in the system.

The 3-port architecture of the 'ACT8818 facilitates both branch addressing and register/counter operations. Both register/counters can be used to hold either loop counts or branch addresses loaded from the DRA and DRB buses. Register/counter operations are selected by control inputs RC2-RC0.

Similarly, the 65-word by 16-bit stack can save addresses from the DRA bus, the microprogram counter (MPC), or the Interrupt Return register, depending on the settings of stack controls S2-S0 and related control inputs. Flexible instructions such as Branch DRA else Branch to Stack else Continue can be coded to take advantage of the conditional branching capability of the 'ACT8818.

Multiway branching (16- or 32-way) uses the B3-B0 inputs to set up a 16-way branch address on DRA or DRB by concatenating B3-B0 with the upper 12 bits of the DRA or DRB bus. The resulting branch addresses DRA' (DRA15-DRA4::B3-B0) and DRB' (DRB15-DRB4::B3-B0) are selected by the Y output multiplexer controls MUX2-MUX0. A Branch DRB' else Branch DRA' instruction can select up to 32 branch addresses, as determined by the settings of B3-B0.

## **Design Support**

TI's '8818 16-bit microsequencer is supported by a variety of tools developed to aid in design evaluation and verification. These tools will streamline all stages of the design process, from assessing the operation and performance of the '8818 to evaluating a total system application. The tools include a functional model, behavioral model, and microcode development software and hardware. Section 8 of this manual provides specific information on the design tools supporting TI's SN74ACT8800 Family.

# SN74ACT8818

## **Systems Expertise**

Texas Instruments VLSI Logic applications group is available to help designers analyze TI's high-performance VLSI products, such as the '8818 16-bit microsequencer. The group works directly with designers to provide ready answers to device-related questions and also prepares a variety of applications documentation.

The group may be reached in Dallas, at (214) 997-3970.

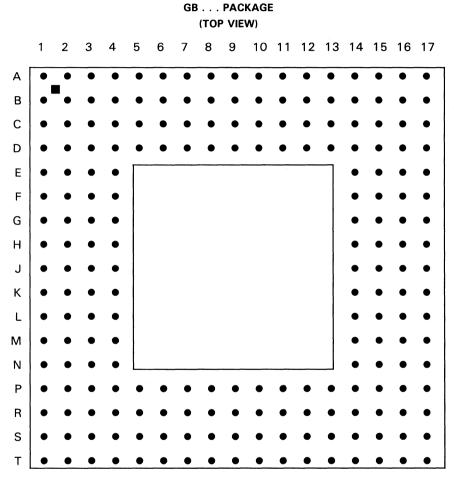

## 'ACT8818 Pin Grid Allocation

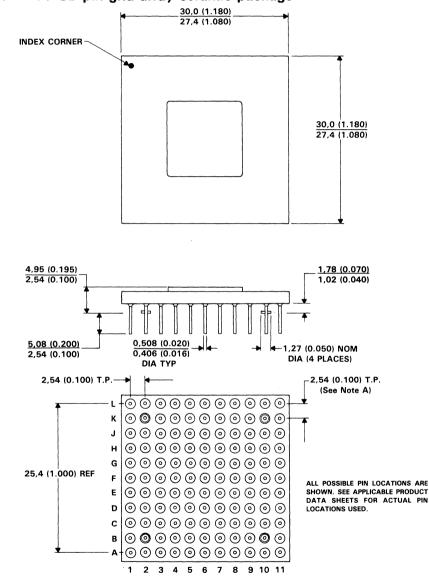

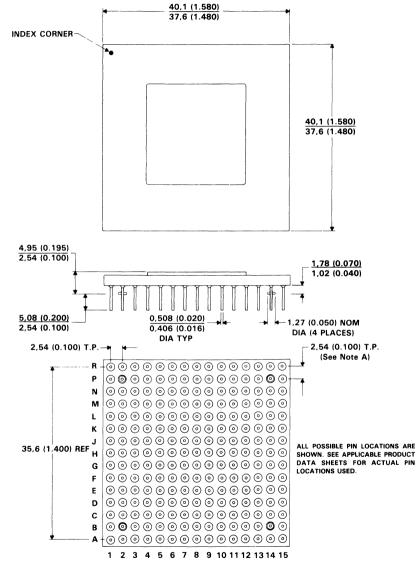

Figure 1. 'ACT8818 . . . . GC Package

**2** SN74ACT8818

|     | PIN    | PIN |                   | PIN PIN |           | PIN      |            |  |

|-----|--------|-----|-------------------|---------|-----------|----------|------------|--|

| NO. | NAME   | NO. | NO. NAME NO. NAMI |         | NAME      | NO. NAME |            |  |

| A2  | RC2    | C2  | RC0               | F3      | RBOE      | J10      | S1         |  |

| A3  | Y1     | C3  | GND               | F9      | BO        | J11      | STKWRN/RER |  |

| A4  | Y3     | C5  | GND               | F10     | B1        | К1       | DRBO       |  |

| A5  | Y5     | C6  | Y7                | F11     | MUX2      | К2       | SELDR      |  |

| A6  | Y6     | C7  | Y10               | G1      | DRB6      | кз       | DRA14      |  |

| A7  | Y8     | C9  | GND               | G2      | DRB5      | К4       | DRA12      |  |

| A8  | Y11    | C10 | V <sub>CC</sub>   | G3      | GND       | К5       | DRA10      |  |

| A9  | Y13    | C11 | RE                | G9      | CLK       | К6       | DRA7       |  |

| A10 | NC     | D1  | DRB12             | G10     | MUXO      | К7       | DRA5       |  |

| B1  | DRB15  | D2  | DRB13             | G11     | MUX1      | К8       | DRA3       |  |

| B2  | RC1    | D9  | GND               | H1      | DRB4      | К9       | DRAO       |  |

| В3  | YO     | D10 | COUT              | H2      | DRB3      | К10      | SO         |  |

| B4  | Y2     | D11 | INC               | H10     | <u>CC</u> | К11      | S2         |  |

| B5  | Y4     | E1  | DRB9              | H11     | ZEROUT    | L2       | DRA15      |  |

| B6  | YOE    | E2  | DRB10             | J1      | DRB2      | L3       | DRA13      |  |

| B7  | Y9     | E3  | DRB11             | J2      | DRB1      | L4       | DRA11      |  |

| B8  | Y12    | E9  | INT               | J3      | Vcc       | L5       | DRA9       |  |

| В9  | Y14    | E10 | B3                | J5      | GND       | L6       | DRA8       |  |

| B10 | Y15    | E11 | B2                | B2 J6 F |           | L7       | DRA6       |  |

| B11 | ZEROIN | F1  | DRB7              | J8      | DRA1      | L8       | DRA4       |  |

| C1  | DRB14  | F2  | DRB8              | 19      | GND       | L9       | DRA2       |  |

|     |        |     |                   |         | ACT 0     | L10      | OSEL       |  |

Table 1. 'ACT8818 Pin Grid Allocation

#### (TOP VIEW)

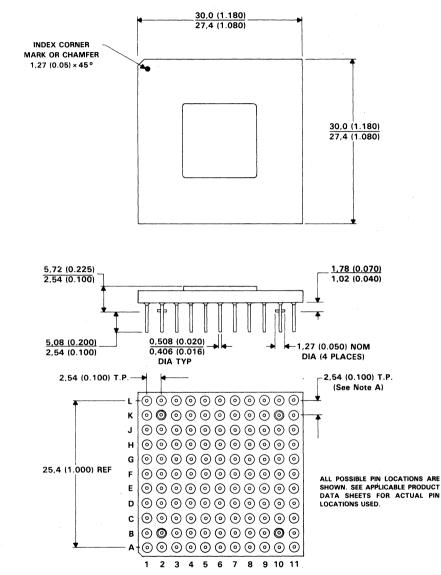

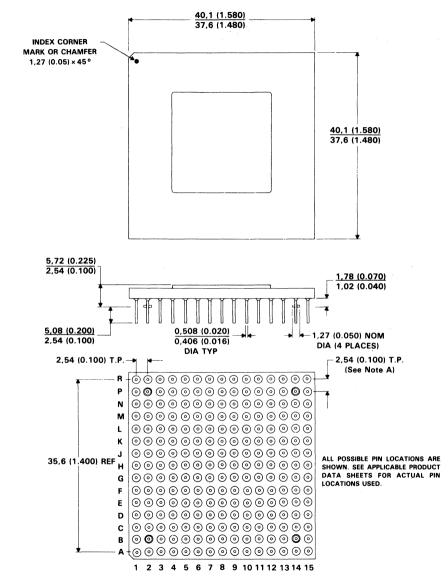

Figure 2. 'ACT8818 . . . FN Package

| PIN   | GC  | FN  | I/O | DESCRIPTION                                                                                       |

|-------|-----|-----|-----|---------------------------------------------------------------------------------------------------|

| NAME  | NO. | NO. |     |                                                                                                   |

| BO    | F9  | 22  |     |                                                                                                   |

| B1    | F10 | 23  | I   | Input bits for branch addressing (see Table 3)                                                    |

| B2    | E11 | 24  |     |                                                                                                   |

| B3    | E10 | 25  |     |                                                                                                   |

| CLK   | G9  | 18  |     | System clock                                                                                      |

| соит  | D10 | 28  | 0   | Incrementer carry-out. Goes high when an attempt is made to increment microprogram counter beyond |

|       |     |     |     | addressable micromemory.                                                                          |

|       | H10 | 15  | 1   | Condition code                                                                                    |

| DRAO  | К9  | 9   |     |                                                                                                   |

| DRA1  | J8  | 8   |     |                                                                                                   |

| DRA2  | L9  | 7   |     |                                                                                                   |

| DRA3  | К8  | 6   |     |                                                                                                   |

| DRA4  | L8  | 5   |     |                                                                                                   |

| DRA5  | К7  | 4   |     |                                                                                                   |

| DRA6  | L7  | 3   |     |                                                                                                   |

| DRA7  | К6  | 2   | I/O | Bidirectional DRA data port. Outputs data from                                                    |

| DRA8  | L6  | 84  |     | stack or register/counter A (RAOE = 0) or inputs                                                  |

| DRA9  | L5  | 83  |     | external data ( $\overline{RAOE} = 1$ ).                                                          |

| DRA10 | К5  | 82  |     |                                                                                                   |

| DRA11 | L4  | 80  |     |                                                                                                   |

| DRA12 | К4  | 79  |     |                                                                                                   |

| DRA13 | L3  | 78  |     |                                                                                                   |

| DRA14 | КЗ  | 77  |     |                                                                                                   |

| DRA15 | L2  | 76  |     |                                                                                                   |

| DRBO  | К1  | 73  |     |                                                                                                   |

| DRB1  | J2  | 72  |     |                                                                                                   |

| DRB2  | J1  | 71  |     |                                                                                                   |

| DRB3  | H2  | 70  |     | Bidirectional DRB data port. Outputs data from                                                    |

| DRB4  | H1  | 69  | 1/0 | register/counter B                                                                                |

| DRB5  | G2  | 67  |     | $(\overline{\text{RBOE}} = 0)$ or inputs external data                                            |

| DRB6  | G1  | 66  |     |                                                                                                   |

| DRB7  | F1  | 65  |     |                                                                                                   |

| DRB8  | F2  | 63  |     |                                                                                                   |

| DRB10 | E2  | 61  |     |                                                                                                   |

Table 2. 'ACT8818 Pin Functional Description

| PIN     | GC  | FN  | 1/0 | DESCRIPTION                                                          |

|---------|-----|-----|-----|----------------------------------------------------------------------|

| NAME    | NO. | NO. | "0  | DESCRIPTION                                                          |

| DRB11   | E3  | 60  |     |                                                                      |

| DRB12   | D1  | 59  |     | Bidirectional DRB data port. Outputs data from                       |

| DRB13   | D2  | 58  | 1/0 | register/counter B ( $\overline{RBOE} = 0$ ) or inputs external data |

| DRB14   | C1  | 57  |     | $(\overline{RBOE} = 1).$                                             |

| DRB15   | B1  | 56  |     |                                                                      |

| GND     | C3  | 10  |     |                                                                      |

| GND     | C5  | 30  |     |                                                                      |

| GND     | C9  | 33  |     |                                                                      |

| GND     | D9  | 46  |     | Ground pins. All pins must be used.                                  |

| GND     | G3  | 52  |     |                                                                      |

| GND     | J5  | 68  |     |                                                                      |

| GND     | J9  | 81  |     |                                                                      |

| INC     | D11 | 27  | 1   | Incrementer control pin                                              |

| INT     | E9  | 26  | 1   | Selects INT RT register to stack, active low (see                    |

|         | 69  | 20  | 1   | Table 3)                                                             |

| MUXO    | G10 | 19  |     |                                                                      |

| MUX1    | G11 | 20  | 1   | MUX control for Y output bus (see Table 4)                           |

| MUX2    | F11 | 21  |     |                                                                      |

| OSEL    | L10 | 11  |     | DRA output MUX select. Low selects RCA, high                         |

| USEL    | LIU |     | 1   | selects stack.                                                       |

| RAOE    | J6  | 1   | 1   | DRA output enable, active low                                        |

| RBOE    | F3  | 64  | I   | DRB output enable, active low                                        |

| RCO     | C2  | 55  |     |                                                                      |

| RC1     | B2  | 54  | 1   | Controls for register/counters A and B                               |

| RC2     | A2  | 53  |     |                                                                      |

|         |     |     |     | INT RT register enable, active low. A high input holds               |

| RE      | C11 | 29  | 1   | INT RT register while a low input passes Y to INT RT                 |

|         |     |     |     | register (see Table 3).                                              |

| S0      | K10 | 12  |     |                                                                      |

| S1      | J10 | 13  | T   | Stack controls                                                       |

| S2      | K11 | 14  |     |                                                                      |

| SELDR   | К2  | 75  | 1   | Selects data source to DRA bus and DRB bus (See                      |

| SELUR   | ĸΖ  | 75  | 1   | Table 3)                                                             |

| STKWRN/ | J11 | 16  | 0   | Stack warning signal flag                                            |

| RER     | 511 | 10  |     | Stack warning signal flag                                            |

| Vcc     | C10 | 31  |     |                                                                      |

| Vcc     | J3  | 74  |     | Supply voltage (5 V)                                                 |

|         |     |     |     |                                                                      |

# SN74ACT8818 **N**

| PIN<br>NAME | GC<br>NO. | FN<br>NO. | I/O | DESCRIPTION                                 |  |  |

|-------------|-----------|-----------|-----|---------------------------------------------|--|--|

| YO          | B3        | 51        |     |                                             |  |  |

| Y1          | A3        | 50        |     |                                             |  |  |

| Y2          | B4        | 49        |     |                                             |  |  |

| Y3          | A4        | 48        |     |                                             |  |  |

| Y4          | B5        | 47        |     |                                             |  |  |

| Y5          | A5        | 45        |     |                                             |  |  |

| Y6          | A6        | 44        |     |                                             |  |  |

| Y7          | C6        | 43        | I/O | Bidirectional Y data port                   |  |  |

| Y8          | A7        | 41        |     |                                             |  |  |

| Y9          | B7        | 40        |     |                                             |  |  |

| Y10         | C7        | 39        |     |                                             |  |  |

| Y11         | A8        | 38        |     |                                             |  |  |

| Y12         | B8        | 37        |     |                                             |  |  |

| Y13         | A9        | 36        |     |                                             |  |  |

| Y14         | В9        | 35        |     |                                             |  |  |

| Y15         | B10       | 34        |     |                                             |  |  |

| YOE         | B6        | 42        | ŀ   | Y output enable, active low                 |  |  |

| ZEROIN      | B11       | 32        | 1   | Forces internal zero detect high            |  |  |

| ZEROUT      | H11       | 17        | 0   | Outputs register/counter zero detect signal |  |  |

Table 2. 'ACT8818 Pin Functional Description (Concluded)

# SN74ACT8818

### 'ACT8818 Specification Tables

# absolute maximum ratings over operating free air temperature range (unless otherwise noted) $^{\dagger}$

| Supply voltage, V <sub>CC</sub>                                                                      |

|------------------------------------------------------------------------------------------------------|

| Input clamp current, I <sub>IK</sub> (VI < 0 or VI > V <sub>CC</sub> ) $\dots \dots \dots \pm 20$ mA |

| Output clamp current, IOK (VO<0 or VO>VCC $\dots \dots \pm 50$ mA                                    |

| Continuous output current, IO (VO = 0 to VCC) $\dots \dots \pm 50$ mA                                |

| Continuous current through V <sub>CC</sub> or GND pins ± 100 mA                                      |

| Operating free-air temperature range 0 °C to 70 °C                                                   |

| Storage temperature range                                                                            |

<sup>†</sup>Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

|       | PARAMETER                          | MIN | NOM | MAX | UNIT |

|-------|------------------------------------|-----|-----|-----|------|

| Vcc   | Supply voltage                     | 4.5 | 5   | 5.5 | V    |

| VIH   | High-level input voltage           | 2   |     | Vcc | V    |

| VIL   | Low-level input voltage            | 0   |     | 0.8 | V    |

| ЮН    | High-level output current          |     |     | - 8 | mA   |

| IOL   | Low-level output current           |     |     | 8   | mA   |

| VI    | Input voltage                      | 0   |     | Vcc | V    |

| Vo    | Output voltage                     | 0   |     | Vcc | V    |

| dt/dv | Input transition rise or fall rate | 0   |     | 15  | ns/V |

| TA    | Operating free-air temperature     | 0   |     | 70  | °C   |

#### recommended operating conditions

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|           |                                                             |       | TA = 25°C |     |       |      |     |      |      |

|-----------|-------------------------------------------------------------|-------|-----------|-----|-------|------|-----|------|------|

| PARAMETER | TEST CONDITIONS                                             | vcc   | MIN       | ТҮР | MAX   | MIN  | ТҮР | MAX  | UNIT |

|           |                                                             | 4.5 V | 4.48      |     |       |      |     |      |      |

|           | I <sub>OH</sub> = -20 μA                                    | 5.5 V | 5.46      | -   |       |      |     |      |      |

| ∨он       |                                                             | 4.5 V | 4.15      |     |       | 3.76 |     |      | V    |

|           | $I_{OH} = -8 \text{ mA}$                                    | 5.5 V | 4.97      |     |       | 4.76 |     |      |      |

|           | $I_{OL} = 20 \ \mu A$                                       | 4.5 V |           |     | 0.014 |      |     |      | v    |

|           |                                                             | 5.5 V |           |     | 0.014 |      |     |      |      |

| VOL       | I <sub>OL</sub> = 8 mA                                      | 4.5 V |           |     | 0.15  |      |     | 0.45 |      |

|           |                                                             | 5.5 V |           |     | 0.13  |      |     | 0.45 |      |

| Ξį.       | $V_{I} = V_{CC} \text{ or } 0$                              | 5.5 V |           |     |       |      |     | ± 1  | μA   |

| lcc       | $V_{I} = V_{CC} \text{ or } 0$                              | 5.5 V |           |     | 98    |      |     | 200  | μA   |

| Ci        | $V_{I} = V_{CC} \text{ or } 0$                              | 5 V   |           | 3   |       |      |     |      | рF   |

| ∆lcc†     | One input at 3.4 V, other<br>inputs at 0 or V <sub>CC</sub> | 5.5 V |           |     |       |      |     | 1    | mA   |

<sup>†</sup>This is the increase in supply current for each input that is at one of the specified TTL voltage levels rather  $\cdot$  than 0 V or V<sub>CC</sub>.

**N** SN74ACT8818

#### 2-22

| PARAMETER       | FROM<br>(INPUT) | TO<br>(OUTPUT) |        |     |     |        |      | UNIT |

|-----------------|-----------------|----------------|--------|-----|-----|--------|------|------|

|                 | (INPUT)         | γ              | ZEROUT | DRA | DRB | STKWRN | COUT |      |

|                 | CC              | 23             |        |     |     |        |      |      |

|                 | CLK             | 27             |        | 24  | 16  | 25     |      |      |

|                 | CLK             | 30†            | 23†    |     |     |        |      |      |

|                 | DRA15-DRA0      | 23             |        |     |     |        |      |      |

|                 | DRB15-DRB0      | 22             |        |     |     |        |      |      |

|                 | MUX2-MUX0       | 22             |        |     |     |        |      |      |

| <sup>t</sup> pd | RC2-RC0         | 26             | 18     |     |     |        |      |      |

|                 | S2-S0           | 25             |        | 19  |     |        |      |      |

|                 | B3-B0           | 19             |        |     |     |        |      | ns   |

|                 | OSEL            | 25             |        | 20  |     |        |      |      |

|                 | ZEROIN          | 25             |        |     |     |        |      | 1    |

|                 | SELDR           | 23             |        |     |     |        |      |      |

|                 | INC             |                |        |     |     |        | 20   |      |

|                 | Y               |                |        |     |     |        | 16   |      |

|                 | YOE             | 16             |        |     |     |        |      |      |

| <sup>t</sup> en | RAOE            |                |        | 18  |     |        |      | ns   |

|                 | RBOE            |                |        |     | 17  |        |      |      |

|                 | YOE             | 14             |        |     |     |        |      |      |

| tdis            | RAOE            |                |        | 13  |     |        |      | ns   |

| :               | RBOE            |                |        |     | 14  |        |      |      |

<sup>†</sup>Decrementing register/counter A or B and sensing a zero.

SN74ACT8818

#### setup and hold times

| PARAMETER       | FROM (INPUT) | TO (OUTPUT)        | MIN | MAX | UNIT |

|-----------------|--------------|--------------------|-----|-----|------|

|                 | CC           | Stack              | 15  |     |      |

| t i i           |              | Stack              | 9   |     |      |

|                 | DRA15-DRA0   | RCA                | 6   |     |      |

|                 |              | INT RT             | 9   |     |      |

|                 | DRB15-DRB0   | RCB                | 7   |     |      |

|                 |              | INT RT             | 11  |     | 1    |

|                 | INC          | MPC                | 7   |     | 1    |

|                 | INT          | Stack              | 7   |     | 1    |

|                 |              | Stack              | 15  |     | 1    |

|                 | RC2-RC0      | RCA, RCB           | 6   |     | - ns |

|                 |              | INT RT             | 16  |     |      |

|                 | S2-S0        | Stack              | 13  |     |      |

| <sup>t</sup> su | 52-50        | INT RT             | 13  |     |      |

|                 | OSEL         | Stack              | 12  |     |      |

|                 | USEL         | INT RT             | 13  |     |      |

|                 | D2 D0        | Stack              | 8   |     | 1    |

|                 | B3-B0        | INT RT             | 14  |     | 1    |

|                 | SELDR        | Stack              | 10  |     | 1    |

|                 | SELDR        | INT RT             | 10  |     |      |

|                 | 750010       | Stack              | 14  |     | 1    |

|                 | ZEROIN       | INT RT             | 13  |     |      |

|                 | Y            | MPC                | 6   | -   | 1    |

|                 | RE           | INT RT (CLK)       | 7   |     | 1    |

| 1               | MUX2-MUX0    | INT RT             | 12  |     | 1    |

| t <sub>h</sub>  | Any<br>Input | Any<br>Destination | 0   |     | ns   |

# clock requirements

|                 | PARAMETER                  | MIN | MAX | UNIT |

|-----------------|----------------------------|-----|-----|------|

| tw1             | Pulse duration, clock low  | 7   |     | ns   |

| <sup>t</sup> w2 | Pulse duration, clock high | 9   |     | ns   |

| t <sub>c</sub>  | Clock cycle time           | 33  |     | ns   |

2

#### Architecture

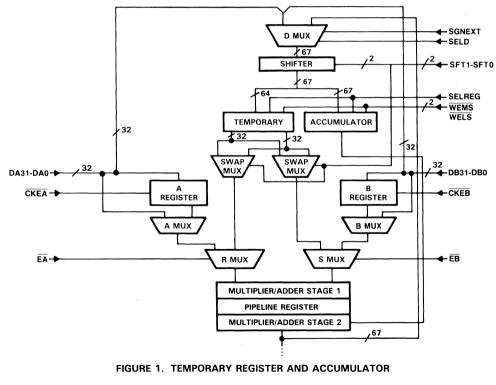

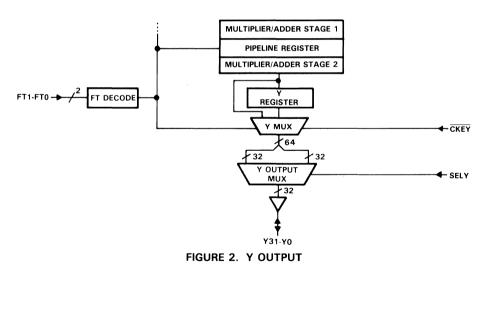

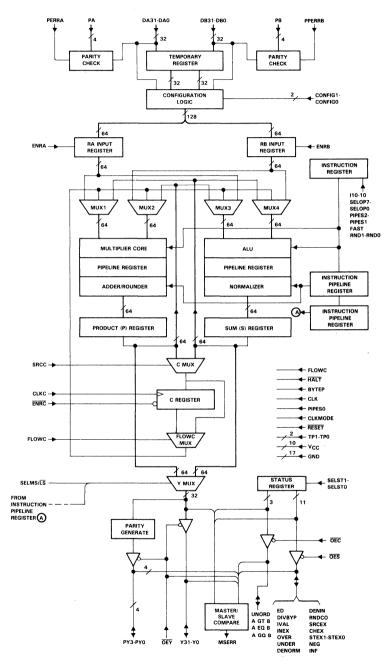

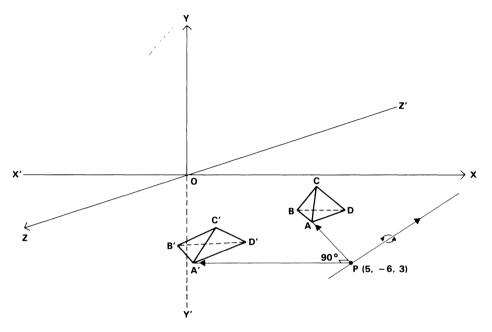

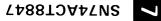

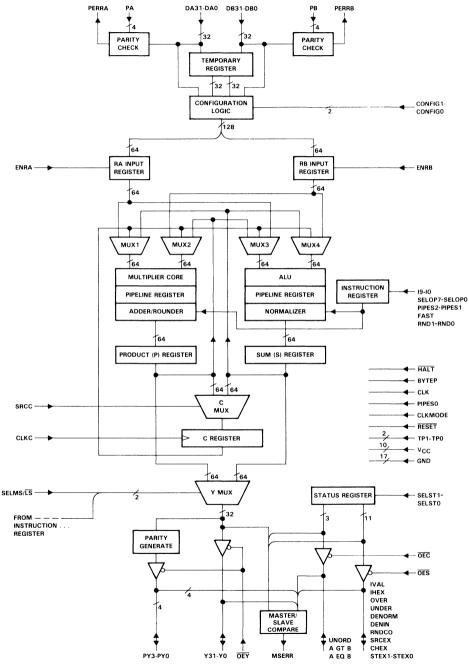

The 'ACT8818 microsequencer is designed with a 3-port architecture similar to the bipolar SN74AS890 microsequencer. Figure 4 shows the architecture of the 'ACT8818. The device consists of the following principal functional groups:

- 1. A 16-bit microprogram counter (MPC) consisting of a register and incrementer which generates the next sequential microprogram address

- 2. Two register/counters (RCA and RCB) for counting loops and iterations, storing branch addresses, or driving external devices

- 3. A 65-word by 16-bit LIFO stack which allows subroutine calls and interrupts at the microprogram level and is expandable and readable by external hardware

- 4. An interrupt return register and Y output enable for interrupt processing at the microinstruction level

- 5. A Y output multiplexer by which the next address can be selected from MPC, RCA, RCB, external buses DRA and DRB, or the stack.

'ACT8818 control signals are summarized in Table 3. Those signals, which typically originate from the instruction register, are Y output multiplexer controls, MUX2-MUX0. These select the source of the next address; stack operation controls, S2-S0; register/counter operation controls, RC2-RC0; OSEL, which allows the stack to be read for diagnostics; input MUX select, SELDR; DRA and DRB output enables, RAOE and RBOE; and INT, used during the first cycle of interrupt service routines to push the address in the interrupt return register address onto the stack.

Control and data signals that commonly originate from the microinstruction and from other hardware sources include INC, which determines whether to increment the MPC; DRA and DRB, used to load or read loop counters and/or next addresses; and  $\overline{CC}$ , the condition code input. The address being loaded into the MPC is not incremented if INC is low, allowing wait states and repeat until flag instructions to be implemented. If INC originates from status, repeat until flag instructions are possible.

The condition code input  $\overline{CC}$  typically originates from ALU status to permit test and branch instructions. However, it must also be asserted under microprogram control to implement other instructions such as continue or loop. Therefore,  $\overline{CC}$  will generally be controlled by the output of a status multiplexer. In this case, whether  $\overline{CC}$  is to be forced high, forced low or taken from ALU status will be determined by a status MUX select field in the microinstruction.

| SIGNAL          | LOGIC LE                                                                                | EVEL                                                                         |

|-----------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| NAME            | HIGH                                                                                    | LOW                                                                          |

| BO†             | Load stack pointer from 7 least significant bits of DRA                                 | No effect                                                                    |

| B1 <sup>†</sup> | Selects DRA contents as stack input (takes priority over INT)                           | No effect                                                                    |

| CC              | Condition code input. May be<br>microcoded or selected from<br>external status results. | Condition code input. For branch operations, low active.                     |

| INC             | Increment address from Y bus and load into MPC                                          | Pass address from Y bus to MPC unincremented.                                |

| ĪNT‡            | Selects MPC as input to stack                                                           | Selects interrupt return register as<br>input to stack                       |

| OSEL            | Selects stack as output from DRA output MUX                                             | Selects RCA as output from DRA output MUX                                    |

| MUX2-MUX0       | See Table 4                                                                             | See Table 4                                                                  |

| RAOE            | DRA output disabled (high-Z)                                                            | DRA output enabled                                                           |

| RBOE            | DRB output disabled (high-Z)                                                            | DRB output enabled                                                           |

| RC2-RC0         | See Table 6                                                                             | See Table 6                                                                  |

| RE              | Hold interrupt return register contents                                                 | Load address on Y bus to interrupt return register                           |

| S2-S0           | See Table 5                                                                             | See Table 5                                                                  |

| SELDR           | Selects DRA/DRB external data as inputs to DRA/DRB buses                                | Selects RCA (OSEL low) or stack<br>(OSEL high) to DRA bus, RCB to<br>DRB bus |

| YOE             | Y output disabled (high-Z)                                                              | Y output enabled                                                             |

| ZEROIN          | Sets ZEROUT to a high externally to set up conditional branch                           | No effect                                                                    |

#### Table 3. Response to Control Inputs

$^{\dagger}$ No control effect when DRA' or DRB' selected (MUX2-MUX0) = HLH) because B3-B0 are address inputs.  $^{\ddagger}$ When B1 is low or B1 is not in control mode.

Control signals which may also originate from hardware are B3-B0, which can be used as a 4-bit status input to support 16- and 32-way branches, and  $\overline{\text{YOE}}$ , which allows interrupt hardware to force an interrupt vector on the microaddress bus.

2 SN74ACT8818

Figure 4. 'ACT8818 Functional Block Diagram

Status from the 'ACT8818 is provided by ZEROUT, which is set at the beginning of a cycle in which either of the register/counters will decrement to zero, and STKWRN/RER, set at the beginning of the cycle in which the bottom of stack is read or in which the next to last location is written. In the latter case, STKWRN/RER remains high until the stack pointer is decremented from 64 to 63.

# Y Output Multiplexer

Address selection is controlled by the Y output multiplexer and the  $\overline{RAOE}$  and  $\overline{RBOE}$  enables. Addresses can be selected from eight sources:

- 1. The microprogram counter register, used for repeat (INC off) and continue (INC on) instructions

- 2. The stack, which supports subroutine calls and returns as well as iterative loops and returns from interrupts

- 3. The DRA and DRB ports, which provide two additional paths from external hardware by which microprogram addresses can be generated

- 4. Register counters RCA and RCB, which can be used for additional address storage

- 5. B3-B0, whose contents can replace the four least significant bits of the DRA and DRB buses to support 16-way and 32-way branches

- 6. An external input onto the bidirectional Y port to support external interrupts.

Use of controls MUX2-MUX0 is explained further in the later section on microprogramming the 'ACT8818.

#### Microprogram Counter

Based on system status and the current instruction, the microsequencer outputs the next execution address in the microprogram. Usually the incrementer adds one to the address on the Y bus to compute next address plus one. Next address plus one is stored in the microprogram register at the beginning of the subsequent instruction cycle. During the next instruction, this 'continue' address will be ready at the Y output MUX for possible selection as the source of the subsequent instruction. The incrementer thus looks two addresses ahead of the address in the instruction register to set up a continue (increment by one) or repeat (no increment) address.

Selecting INC from status is a convenient means of implementing instructions that must repeat until some condition is satisfied; for example, Shift ALU Until MSB = 1, or Decrement ALU Until Zero. The MPC is also the standard path to the stack. The next address is pushed onto the stack during a subroutine call, so that the subroutine will return to the instruction following that from which it was called.

#### Register/Counters

Addresses or loop counts may be loaded directly into register/counters RCA and RCB through the direct data ports DRA15-DRA0 and DRB15-DRB0. The values stored in these registers may either be held, decremented, or read. Independent control of both the registers during a single cycle is supported with the exception of a simultaneous decrement of both registers.

SN74ACT8818

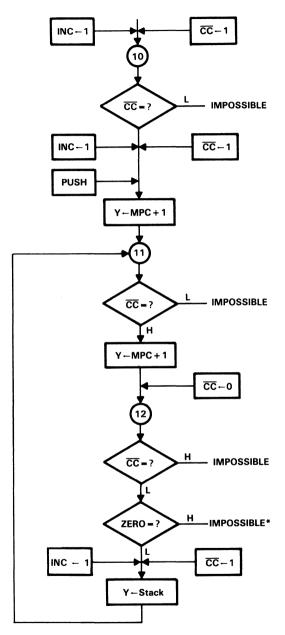

#### Stack

The positive edge clocked 16-bit address stack allows multiple levels of nested calls or interrupts and can be used to support branching and looping. Seven stack operations are possible:

- 1. Reset, which pulls all Y outputs low and clears the stack pointer and read pointer

- 2. Clear, which sets the stack pointer and read pointer to zero

- 3. Pop, which causes the stack pointer to be decremented

- 4. Push, which puts the contents of the MPC, interrupt return register, or DRA bus onto the stack and increments the stack pointer

- 5. Read, which makes the address indicated by the read pointer available at the DRA port

- 6. Hold, which causes the address of the stack and read pointers to remain unchanged

- 7. Load stack pointer, which inputs the seven least significant bits of DRA to the stack pointer.

#### Stack Pointer

The stack pointer (SP) operates as an up/down counter; it increments whenever a push occurs and decrements whenever a pop occurs. Although push and pop are two event operations (store then increment SP, or decrement SP then read), the 'ACT8818 performs both events within a single cycle.

#### **Read Pointer**

The read pointer (RP) is provided as a tool for debugging microcoded systems. It permits a nondestructive, sequential read of the stack contents from the DRA port. This capability provides the user with a method of backtracking through the address sequence to determine the cause of overflow without affecting program flow, the status of the stack pointer, or the internal data of the stack.

#### Stack Warning/Read Error Pin

A high signal on the STKWRN/RER pin indicates a potential stack overflow or underflow condition. STKWRN/RER becomes active under two conditions. If 62 of the 65 stack locations (0-64) are full (the stack pointer is at 62) and a push occurs, the STKWRN/RER pin outputs a high signal to warn that the stack is approaching its capacity and will be full after two more pushes.

The STKWRN/RER signal will remain high if hold, push or pop instructions occur, until the stack pointer is decremented to 62. If a push instruction is attempted when the stack is full, the new address will be ignored and the old address in stack location 64 will be retained.

The STKWRN/RER pin will go high when the stack pointer is less than or equal to one and a pop or read from stack is coded on the S2-S0 pins. The pin will go high after reading the next to the bottom stack address (1). When the S2-S0 pins are set to pop or read the last address (0) or to pop or read an empty stack, the STKWRN/RER pin will go high. The pin depends only on the setting of the S2-S0 pins and the stack pointer, not on the clock.

#### Interrupt Return Register

Unlike the MPC register, which normally gets next address plus one, the interrupt return register simply gets next address. This permits interrupts to be serviced with zero latency, since the interrupt vector replaces the pending address.

The interrupting hardware disables the Y output and forces the vector onto the microaddress bus. This event must be synchronized with the system clock. The first address of the service routine must program  $\overline{\text{INT}}$  low and perform a push to put the contents of the interrupt return register on the stack.

# Microprogramming the 'ACT8818

Microprogramming is unlike programming monolithic processors for several reasons. First, the width of the microinstuction word is only partially constrained by the basic signals required to control the sequencer. Since the main advantage of a microprogrammed processor is speed, many operations are often supported by or carried out in special purpose hardware. Lookup tables, extra registers, address generators, elastic memories, and data acquisition circuits may also be controlled by the microinstruction.

The number of slices in a bit-slice ALU is user-defined, which makes the microinstruction width even more application dependent. Types of instructions resulting from manipulation of the sequencer controls are discussed below. Examples of some commonly used instructions can be found in the later section of microinstructions and flow diagrams. The following abbreviations are used in the tables in this section:

#### Address Selection

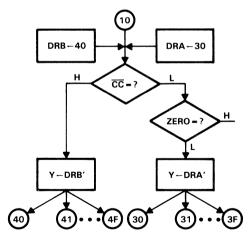

Y-output multiplexer controls MUX2-MUX0 select one of eight 3-source branches as shown in Table 4. The states of  $\overline{CC}$  and ZERO determine which of the three sources is selected as the next address. ZERO is set at the beginning of any cycle in which a register/counter will decrement to zero. This applies to both internal ZERO and external ZEROUT signals.

|       |       |                   | •                   |         |  |  |  |

|-------|-------|-------------------|---------------------|---------|--|--|--|

| MUX2- |       | Y OUTPUT SOURCE   |                     |         |  |  |  |

| MUX2- | RESET | CC                | $\overline{CC} = H$ |         |  |  |  |

| WUNU  |       | ZERO = L          | ZERO = H            | CC = H  |  |  |  |

| XXX   | Yes   | All Low           | All Low             | All Low |  |  |  |

| LLL   | No    | STK               | MPC                 | DRA     |  |  |  |

| LLH   | No    | STK               | MPC                 | DRB     |  |  |  |

| LHL   | No    | STK               | DRA                 | MPC     |  |  |  |

| LHH   | No    | STK               | DRB                 | MPC     |  |  |  |

| HLL   | No    | DRA               | MPC                 | DRB     |  |  |  |

| HLH   | No    | DRA' <sup>†</sup> | MPC                 | DRB'‡   |  |  |  |

| HHL   | No    | DRA               | STK                 | MPC     |  |  |  |

| ннн   | No    | DRB               | ѕтк                 | MPC     |  |  |  |

Table 4. Output Controls (MUX2-MUX0)

<sup>†</sup>DRA15-DRA4::B3-B0 <sup>‡</sup>DRB15-DRB4::B3-B0

By programming  $\overline{CC}$  high or low without decrementing registers, only one outcome is possible; thus, unconditional branches or continues can be implemented by forcing the condition code. Alternatively,  $\overline{CC}$  can be selected from status, in which case Branch A on Condition Code Else Branch B instructions are possible, where A and B are the address sources determined by MUX2-MUX0.

Decrement and Branch on Nonzero instructions, creating loops that repeat until a terminal count is reached, can be implemented by programming  $\overline{CC}$  low and decrementing a register/counter. If  $\overline{CC}$  is selected from status and registers are decremented, more complex instructions such as Exit on Condition Code or End or Loop are possible.

When MUX2-MUX0 = HLH, the B3-B0 inputs can replace the four least significant bits of DRA or DRB to create 16-Way branches or, when  $\overline{CC}$  is based on status, to create 32-way branches.

#### **Stack Controls**

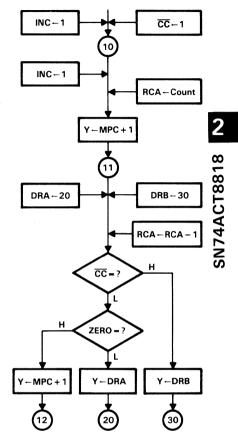

As in the case of the MUX controls, each stack-control coding is a three-way choice based on  $\overline{CC}$  and ZERO (see Table 5). This allows push, pop, or hold stack operations to occur in parallel with the aforementioned branches. A subroutine call is accomplished by combining a branch and push, while returns result from coding a branch to stack with a pop.

|       |      | S           | STACK OPERATION     |             |  |  |  |

|-------|------|-------------|---------------------|-------------|--|--|--|

| S2-S0 | OSEL | <u>55</u>   | $\overline{CC} = H$ |             |  |  |  |

|       |      | ZERO = L    | ZERO = H            | UU = H      |  |  |  |

| LLL   | Х    | Reset/Clear | Reset/Clear         | Reset/Clear |  |  |  |

| LLH   | х    | Clear SP/RP | Hold                | Hold        |  |  |  |

| LHL   | х    | Hold        | Рор                 | Рор         |  |  |  |

| LHH   | х    | Рор         | Hold                | Hold        |  |  |  |

| HLL   | Х    | Hold        | Push                | Push        |  |  |  |

| HLH   | Х    | Push        | Hold                | Hold        |  |  |  |

| HHL   | Х    | Push        | Hold                | Push        |  |  |  |

| ннн   | н    | Read        | Read                | Read        |  |  |  |

| ннн   | Ł    | Hold        | Hold                | Hold        |  |  |  |

| Table 5. Stack Controls (S | S2-S0) |

|----------------------------|--------|

|----------------------------|--------|

rmits

2

SN74ACT8818

Combining stack and MUX controls with status results and register decrements permits even greater complexity. For example: Return on Condition Code or End of Loop; Call A on Condition Code Else Branch to B; Decrement and Return on Nonzero; Call 16-Way.

Diagnostic stack dumps are possible using Read (S2-S0 = HHH) when OSEL is set high.

#### **Register Controls**

Unlike stack and MUX controls, register control is not dependent upon  $\overline{CC}$  and ZERO. Registers can be independently loaded, decremented, or held using register control inputs RC2-RC0 (see Table 6). All combinations are supported with the exception of simultaneous register decrements. The register control inputs can be set to store branch addresses and loop counts or to decrement loop counts, facilitating the complex branching instructions described above.

| RC2-RC0 | REGISTER OP | OPERATIONS |  |  |

|---------|-------------|------------|--|--|

| h02-h00 | REG A       | REG B      |  |  |

| LLL     | Hold        | Hold       |  |  |

| LLH     | Decrement   | Hold       |  |  |

| LHL     | Load        | Hold       |  |  |

| LHH     | Decrement   | Load       |  |  |

| HLL     | Load        | Load       |  |  |

| HLH     | Hold        | Decrement  |  |  |

| HHL     | Hold        | Load       |  |  |

| ннн     | Load        | Decrement  |  |  |

Table 6. Register Controls (RC2-RC0)

The contents of RCA are accessible to the DRA port when OSEL is low and the output bus is enabled by  $\overrightarrow{\text{RAOE}}$  being low. Data from RCB is available when DRB is enabled by  $\overrightarrow{\text{RBOE}}$  being low.

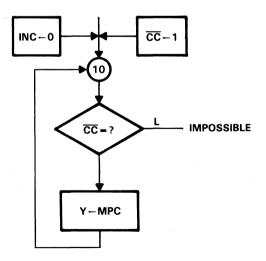

#### **Continue/Repeat Instructions**

The most commonly used instruction is a continue, implemented by selecting MPC at the Y output MUX and setting INC high. If MPC is selected and INC is off, the current instruction will simply be repeated.

A repeat instruction can be implemented in two ways. A programmed repeat (INC forced low) may be useful in generating wait states, for example, wait for interrupt. A conditional repeat (INC originates from status) may be useful in implementing Do While operations. Several bit patterns in the MUX control field of the microinstruction will place MPC on the microaddress bus.

2

#### **Branch Instructions**

A branch or jump to a given microaddress can also be coded several ways. RCA, DRA, RCB, DRB, and STK are possible sources for branch addresses (see Table 4). Branches to register or stack are useful whenever the branch address could be stored to reduce overhead.

The simplest branches are to DRA and DRB, since they require only one cycle and the branch address is supplied in the microinstruction. Use of registers or stack requires an initial load cycle (which may be combined with a preceding instruction), but may be more practical when an entry point is referenced over and over throughout the microprogram, for example, in error-handling routines. Branches to stack or register also enhance sequencing techniques in which a branch address is dynamically computed or multiple branches to a common entry point are used, but the entry point varies according to the system state. In this case, the state change might require reloading the stack or register.

In order to force a branch to DRA or DRB,  $\overline{CC}$  must be programmed high or low. A branch to stack is only possible when  $\overline{CC}$  is forced low (see Table 4).

When  $\overline{CC}$  is low, the ZERO flag is tested, and if a register decrements to zero the branch will be transformed into a Decrement and Branch on Nonzero instruction. Therefore, registers should not be decremented during branch instructions using  $\overline{CC} = 0$  unless it is certain the register will not reach terminal count. Call (Branch and Push MPC) instructions and Return (Branch to Stack and Pop) instructions are discussed in later sections.

2

#### **Conditional Branch Instructions**

Perhaps the most useful of all branches is the conditional branch. The 'ACT8818 permits three modes of conditional branching: Branch on Condition Code; Branch 16-Way from DRA or DRB; and Branch on Condition Code 16-Way from DRA Else Branch 16-Way from DRB. This increases the versatility of the system and the speed of processing status tests because both single-bit and 4-bit status are allowed.

Testing single bit status is preferred when the status can be set up and selected through a status MUX prior to the conditional branch. Four-bit status allows the 'ACT8818 to process instructions based on Boolean status expressions, such as Branch if Overflow and Not Carry if Zero or if Negative. It also permits true n-way branches, such as If Negative then Branch to X, Else if Overflow, and Not Carry then Branch to Y. The tradeoff is speed versus program size. Since multiway branching occurs relatively infrequently in most programs, users will enjoy increased speed at a negligible cost. Call (Branch and Push MPC) instructions and Return (Branch to Stack and Pop) instructions are discussed in later sections.

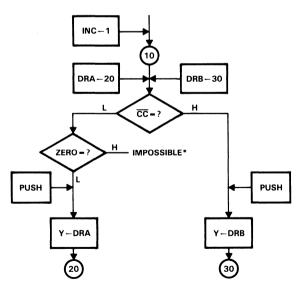

#### Loop Instructions