# TMS380 Adapter Chipset User's Guide

# Local Area Network Products

# TMS380 Adapter Chipset User's Guide

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes in the devices or the device specifications identified in this publication without notice. TI advises its customers to obtain the latest version of device specifications to verify, before placing orders, that the information being relied upon by the customer is current.

TI warrants that the software content of the TMS38020 device is a faithful reproduction of the software developed by TI and IBM for this chipset.<sup>†</sup> This is the only warranty with regard to the software and all other warranties, whether express or implied and including any implied warranties of merchantability and fitness for a particular purpose, are disclaimed. TI reserves the right to offer the TMS38020 or a derivative product with different software contained in the chip. TI has no responsibility to upgrade or replace products previously sold if different versions of the product and software are offered. TI shall not be liable for incidental or consequential damages arising from the software or its use or modification.

In the absence of written agreement to the contrary, TI assumes no liability for TI applications assistance, customer's product design, or infringement of patents or copyrights of third parties by or arising from use of semiconductor devices described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor devices might be or are used.

iAPX 86 is a registered trademark of the Intel Corporation.

IBM, IBM PC, PC/XT, PC AT are registered trademarks of International Business Machines Corporation.

#### Copyright © 1986, Texas Instruments Incorporated

#### MANUAL REVISION HISTORY TMS380 ADAPTER CHIPSET USER'S GUIDE

| Document Release            | Date           | Software Release |

|-----------------------------|----------------|------------------|

| Original Issue User's Guide | September 1985 | RC0114           |

| Manual Update A             | October 1985   | RC0114           |

| Manual Update B             | January 1986   | RC011B           |

| Manual Update C             | February 1986  | RC011B           |

| Revision D User's Guide     | July 1986      | RC011B           |

The Adapter software release number may be found in the first location of the code (mapped at LAN Adapter bus address >COOO). This corresponds to the first word of the PH ROM or the first word of external EPROM, if used.

Adapter software release RC011B has been fully tested by IBM and TI and is compatible with IEEE 802.5 and the IBM Token-Ring Network Architecture Reference, part number 6165877, February 1986.

<sup>&</sup>lt;sup>†</sup>Copyright © 1986 by Texas Instruments Incorporated and International Business Machines, all rights reserved.

# Contents

| Section                                                                                                                      |                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.6.1<br>1.6.2<br>1.6.3<br>1.6.4<br>1.7<br>1.8<br>1.9<br>1.10<br>1.11<br>1.12 | IEEE 802 LAN Standards<br>The Token Ring LAN: IEEE 802.5<br>LAN Adapter Architectures<br>Overview of the TMS380<br>The System Interface<br>The Communications Processor<br>The Protocol Handler<br>The Ring Interface<br>Network Reliability<br>LAN Management Services<br>Performance Features<br>Transmitting and Receiving a Frame | 1-1<br>1-2<br>1-3<br>1-3<br>1-6<br>1-7<br>1-8<br>1-8<br>1-8<br>1-8<br>1-9<br>1-10<br>1-10<br>1-11<br>1-13<br>1-14 |

| 2.1<br>2.2<br>2.2.1                                                                                                          | Introduction         PC Family LAN Adapter Card: I/O Mapped Design Example         Theory of Operation         PC Family LAN Adapter Card: Memory-Mapped Example         PC Family LAN Adapter Card: Memory-Mapped Example         Theory of Operation                                                                                | 2-1<br>2-5<br>2-5<br>2-9<br>2-9<br>2-9<br>2-12<br>2-12<br>2-12<br>2-14<br>2-14                                    |

| 3.1<br>3.1.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.2<br>3.2.3<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3                                    | Introduction<br>Scope<br>Conventions<br>Network Management Considerations<br>Ring Error Monitor<br>Network Manager<br>Ring Parameter Server<br>Physical Signaling<br>Differential Manchester Code<br>Ring Clocking<br>Elastic Buffer                                                                                                  | 3-1<br>3-1<br>3-4<br>3-5<br>3-5<br>3-5<br>3-5<br>3-5<br>3-6<br>3-7<br>3-7                                         |

## Section

ii

### Page

| 3.4.2  | Frame Format                                  | 3-8  |

|--------|-----------------------------------------------|------|

| 3.4.3  | Starting Delimiter                            | 3-9  |

| 3.4.4  | Physical Control Fields - PCF                 |      |

| 3.4.5  | Source and Destination Address Fields         | 3-10 |

| 3.4.6  | Information Field                             | 3-10 |

| 3.4.7  | Frame Check Sequence                          | 3-10 |

| 3.4.8  | Ending Delimiter Field                        | 3-11 |

| 3.4.9  | Frame Status Field - FS                       | 3-11 |

| 3.5    | Ring Addressing                               | 3-12 |

| 3.5.1  | Address Types                                 | 3-12 |

| 3.5.2  | Source Routing                                |      |

| 3.6    | Medium Access Control                         | 3-16 |

| 3.6.1  | Concept                                       | 3-16 |

| 3.6.2  | MAC Frame Format                              | 3-17 |

| 3.6.3  | MAC Frame FC                                  |      |

| 3.6.4  | MAC Frame Source Address                      | 3-18 |

| 3.6.5  | MAC Frame Major Vectors                       | 3-18 |

| 3.6.6  | MAC Frames Processed by the Adapter           | 3-20 |

| 3.6.7  | MAC Frame Receive and Transmit Processing     | 3-23 |

| 3.6.8  | Response MAC Frames                           | 3-26 |

| 3.7    | Monitor Functions                             | 3-28 |

| 3.7.1  | Active Monitor Functions                      | 3-28 |

| 3.7.2  | Stand-by Monitor Functions                    | 3-30 |

| 3.8    | MAC Processes                                 | 3-31 |

| 3.8.1  | Notes on Reading the MAC Frame Tables         | 3-32 |

| 3.8.2  | Monitor Contention Process                    | 3-33 |

| 3.8.3  | Ring Purge Process                            | 3-37 |

| 3.8.4  | Ring Poll Process                             | 3-38 |

| 3.8.5  | Beacon Process                                | 3-40 |

| 3.8.6  | Hardware Error Process                        | 3-44 |

| 3.8.7  | Ring Insertion Process                        | 3-44 |

| 3.8.8  | Transmit Forward Process                      | 3-51 |

| 3.9    | Miscellaneous MAC Frames                      | 3-53 |

| 3.9.1  | Remove Ring Station MAC Frame                 | 3-53 |

| 3.9.2  | Network Management MAC Frames                 | 3-53 |

| 3.10   | Token Transmit and Priority Control           |      |

| 3.10.1 | The Model Access Control Field                | 3-55 |

| 3.10.2 | Token Capture                                 |      |

| 3.10.3 | Priority Reservation Modification             | 3-57 |

| 3.10.4 | Token Priority Control Protocol               |      |

| 3.11   | Soft Error Counting and Reporting             |      |

| 3.11.1 | Soft Error Counters                           | 3-77 |

| 3.11.2 | Attached Product Counters                     |      |

| 3.11.3 | Isolating versus Non-Isolating Error Counters | 3-78 |

| 3.11.4 | Isolating Error Counters                      | 3-78 |

|        |                                               |      |

| Section                                                                                                                                                                                                                                                                                            | · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.11.5<br>3.12<br>3.12.1<br>3.12.2<br>3.12.3                                                                                                                                                                                                                                                       | Non-isolating Error Counters         Token Ring Recovery         Hard Error Recovery         Soft Error Recovery         Hard Error Recovery         Hard Error Recovery         Hard Error Recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-81<br>3-83                                                                                                                                                                                                                                                      |

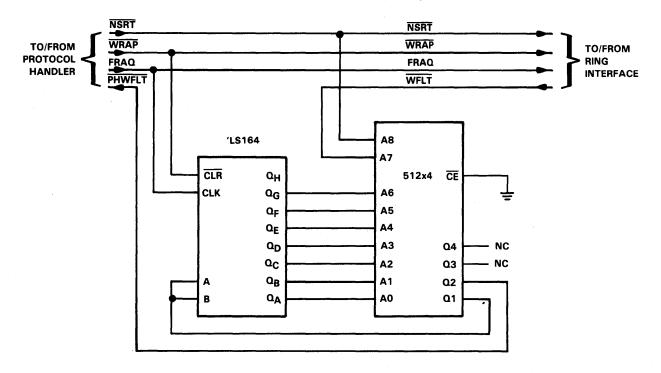

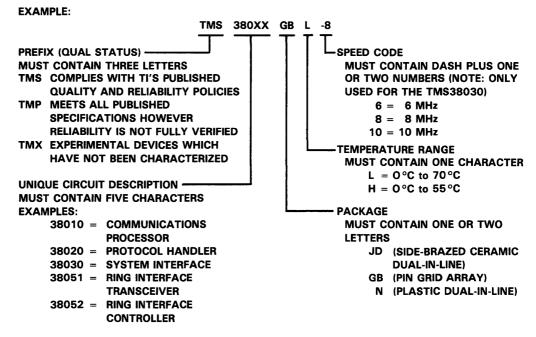

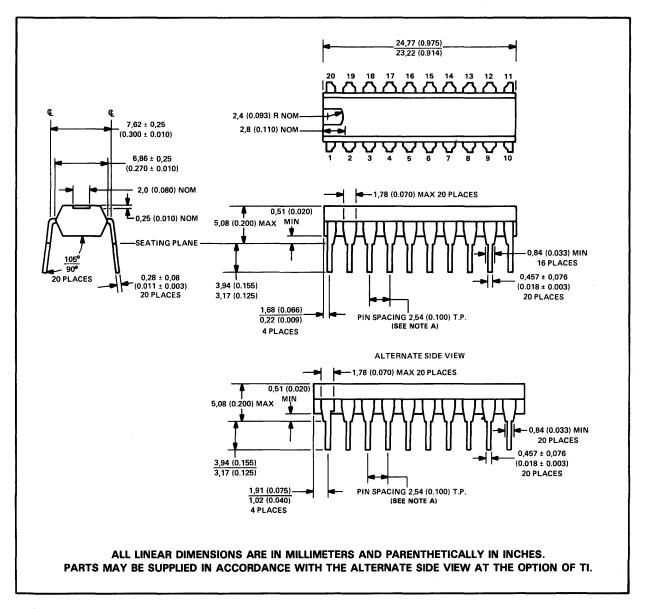

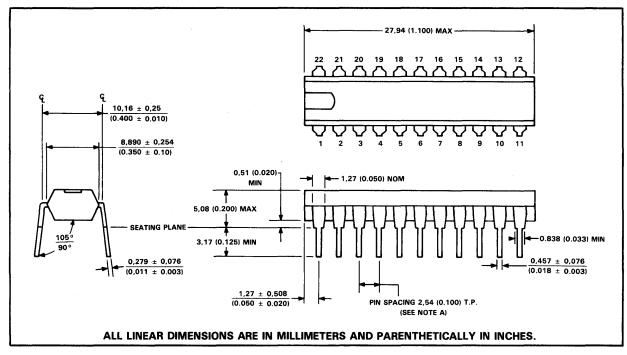

| $\begin{array}{c} 4\\ 4.1\\ 4.1.1\\ 4.1.2\\ 4.1.3\\ 4.1.5\\ 4.2.1\\ 4.3.1\\ 4.3.2\\ 4.3.1\\ 4.3.2\\ 4.3.3\\ 4.3.5\\ 4.4.1\\ 4.4.2\\ 4.4.3\\ 4.4.5\\ 4.4.5\\ 4.4.5\\ 4.4.5\\ 4.4.5\\ 4.5.1\\ 4.5.5\\ 4.5.5\\ 4.5.6\\ 4.5.7\\ 4.5.8\\ 4.5.6\\ 4.5.7\\ 4.5.8\\ 4.5.9\\ 4.5.10\\ 4.5.11\\ \end{array}$ | Adapter Design         Introduction         Scope         Conventions         Hardware Interface Overview         Software Interface         Adapter Data Flow         Adapter Interconnect         LAN Adapter Bus Memory Expansion         System Hardware Interface         Hardware Interface Modes         Direct I/O Interface         Direct Memory Access Interface         Adapter Interrupt Interface         Adapter Hardware Reset         System Software Interface         Summary of System Buffer Requirements         Register Descriptions         Bring-up Diagnostics Verification         Adapter Commands         Ring Interface         TMS38051 and TMS38052 Components         Ring Interface         TMS38052 Protocol Handler to Ring Interface Signals         Ring Interface Interconnect Schematic         Watchdog Timer         Burned-In Address         TMS38020 Protocol Handler to Ring Interface Signals         Ring Interface Transmitter         Ring Interface Phase Locked Loop         Energy Detect         Wrap Mode         Ring Interface Phantom Drive | $\begin{array}{c} 4-1\\ 4-3\\ 4-6\\ 4-11\\ 4-9\\ 4-9\\ 4-19\\ 4-20\\ 4-36\\ 4-65\\ 4-65\\ 4-65\\ 4-65\\ 4-65\\ 4-65\\ 4-65\\ 4-71\\ 4-72\\ 4-76\\ 4-71\\ 4-72\\ 4-76\\ 4-116\\ 4-116\\ 4-1120\\ 4-120\\ 4-121\\ 4-122\\ 4-127\\ 4-127\\ 4-127\\ 4-127\end{array}$ |

| A<br>A.1<br>A.2<br>A.3<br>A.4                                                                                                                                                                                                                                                                      | Data SheetsTMS38010 Communications Processor Data SheetTMS38020 Protocol Handler Data SheetTMS38030 System Interface Data SheetTMS38051/TMS38052 Ring Interface Components Data Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A-23<br>A-53                                                                                                                                                                                                                                                      |

| B<br>B.1<br>B.2<br>B.3<br>B.4                                                                                                                                                                                                                                                                      | General<br>MAC Frame Summary<br>Burned-In Addressing Technique<br>Ordering Information, Package, Thermal and Mechanical Data<br>Glossary of Terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | B-8<br>B-16                                                                                                                                                                                                                                                       |

#### iii

# Illustrations

| Figure |                                                             | Page |

|--------|-------------------------------------------------------------|------|

| 1-1    | TMS380 LAN Adapter Chipset                                  | 1-1  |

| 1-2    | The OSI Reference Model                                     | 1-2  |

| 1-3    | IEEE 802 LAN Standards                                      | 1-3  |

| 1-4    | The Star-Wired Ring Topology                                | 1-4  |

| 1-5    | Token Ring Wiring Concentrator                              | 1-4  |

| 1-6    | Free Token Format and Frame Format                          | 1-5  |

| 1-7    | Token-Passing Example                                       | 1-5  |

| 1-8    | LAN Controller-Based Adapter Card Architecture              | 1-6  |

| 1-9    | Integrated Adapter Architecture                             | 1-7  |

| 1-10   | Adapter Self-Test                                           | 1-9  |

| 1-11   | Adapter Data Flow                                           | 1-11 |

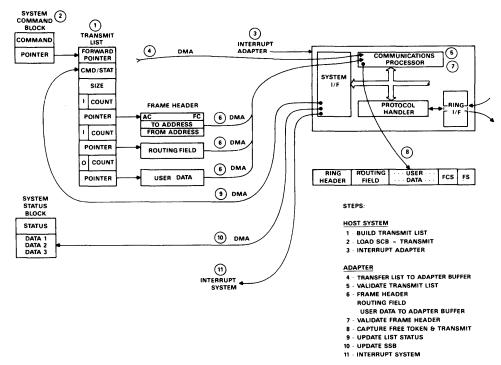

| 1-12   | Transmitting a Frame                                        | 1-13 |

| 2-1    | I/O Mapped Design Block Diagram                             | 2-2  |

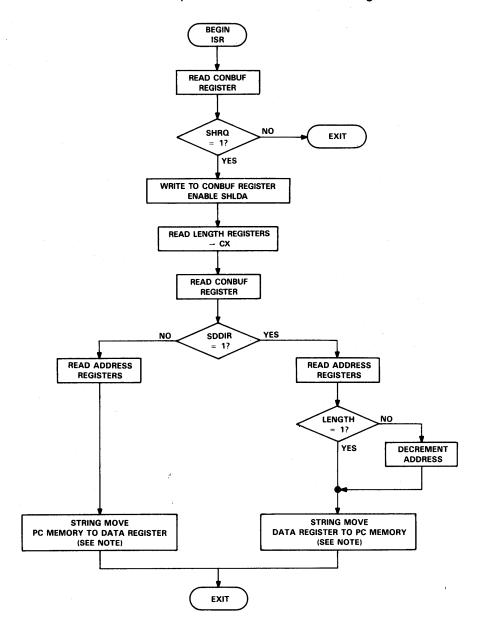

| 2-2    | Interrupt Service Routine Flowchart - I/O Mapped Example    | 2-4  |

| 2-3    |                                                             | 2-6  |

| 2-4    |                                                             | 2-8  |

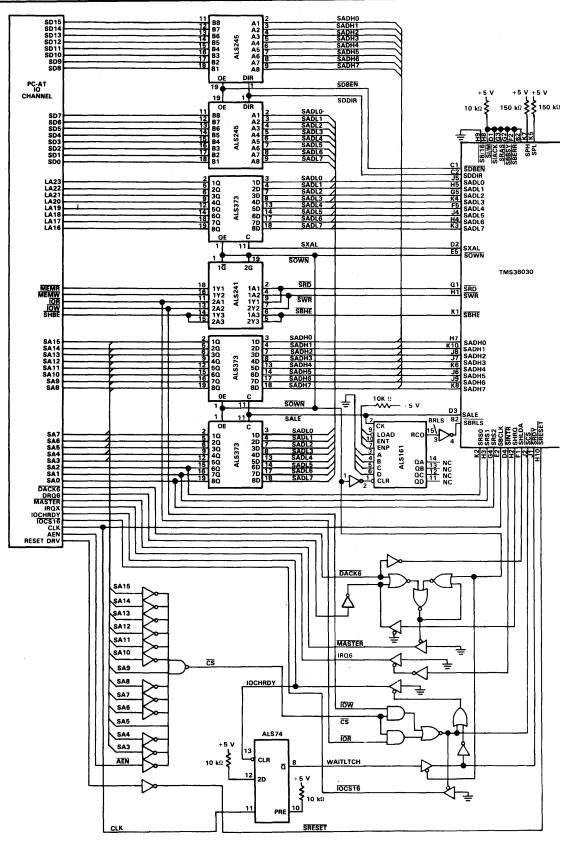

| 2-5    | TMS380 Interface to IBM PC AT System Bus                    | 2-11 |

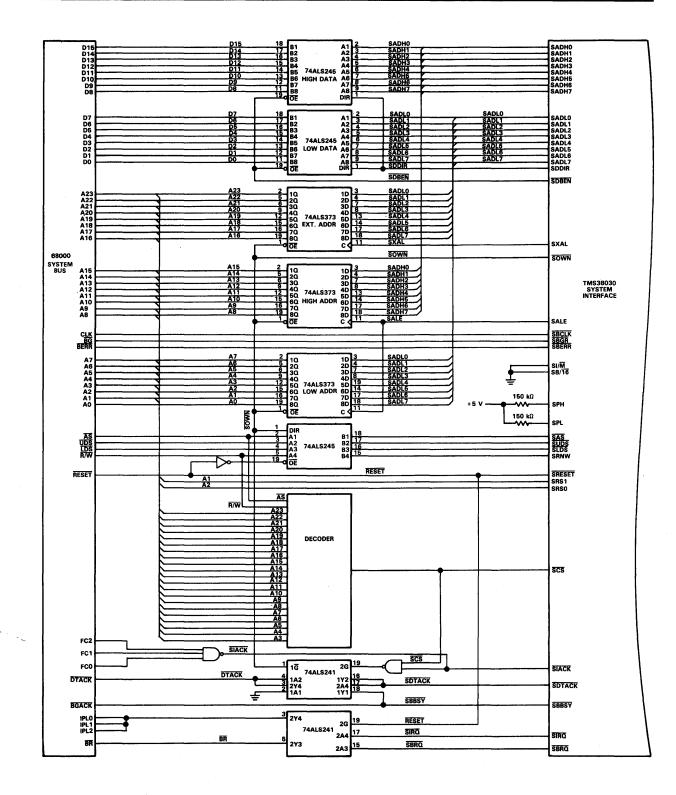

| 2-6    | TMS380 Interface to a 68000-Style Bus                       | 2-13 |

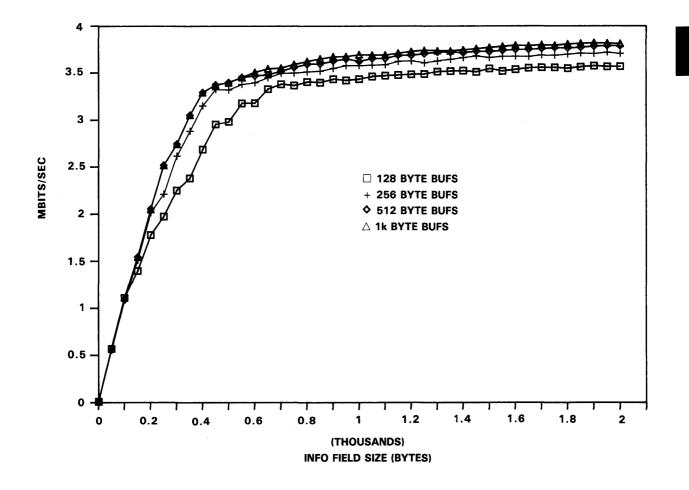

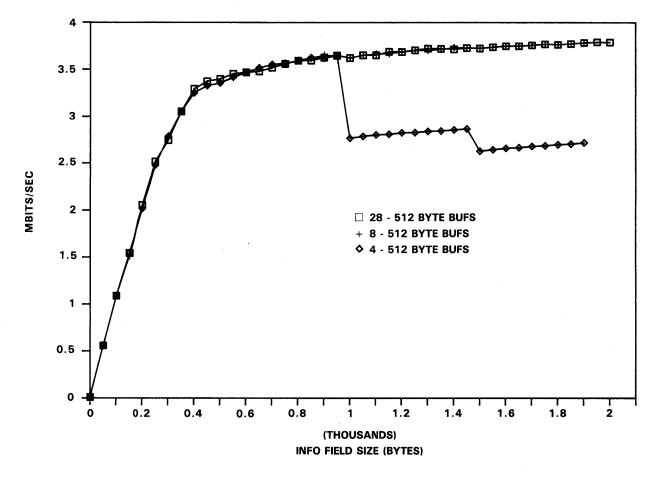

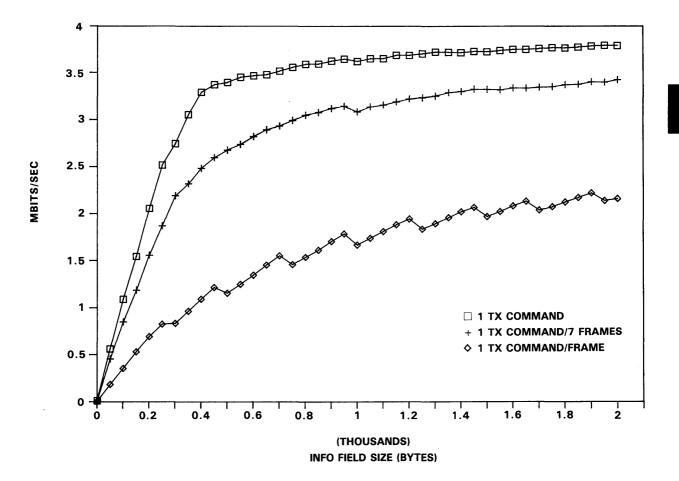

| 2-7    | Transmit Throughput - PC AT Adapter:                        | 2-15 |

|        | Internal Buffer Size Comparison                             |      |

| 2-8    | Transmit Throughput - PC AT Adapter:                        | 2-16 |

|        | Internal Buffer Count Comparison                            |      |

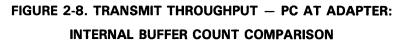

| 2-9    | External Hardware Counter for Limiting Effective Burst Size |      |

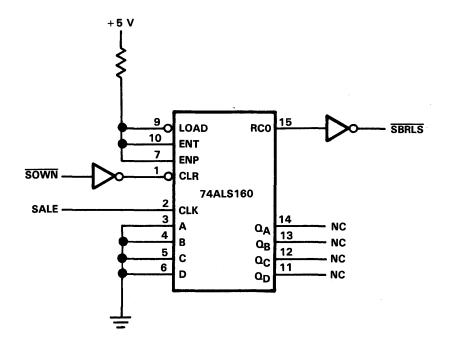

| 2-10   | Transmit Throughput - PC AT Adapter:                        | 2-18 |

|        | DMA Mode Comparison - 512 Byte Buffers                      |      |

| 2-11   | Transmit Throughput - PC AT Adapter:                        | 2-19 |

|        | TX Command Comparison - 512 Byte Buffers                    |      |

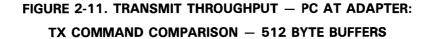

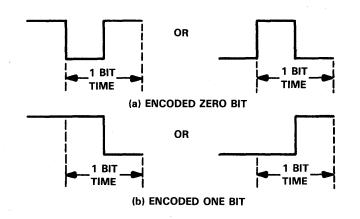

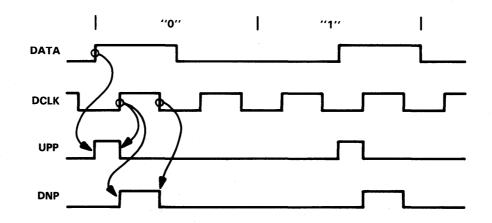

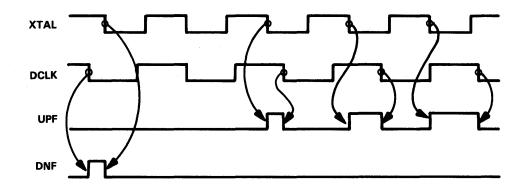

| 3-1    | Differential Manchester Code                                | 3-6  |

| 3-2    | Code Violations                                             |      |

| 3-3    |                                                             |      |

| 3-4    | Starting Delimiter Bit Assignments                          |      |

| 3-5    |                                                             |      |

| 3-6    |                                                             | 3-10 |

| 3-7    | Ending Delimiter Bit Assignments                            |      |

| 3-8    | FS Bit Assignments                                          |      |

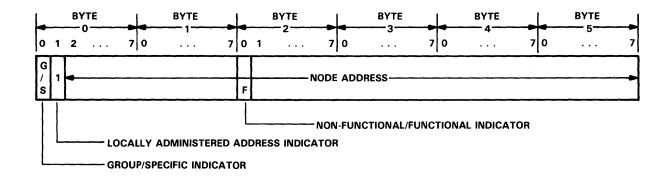

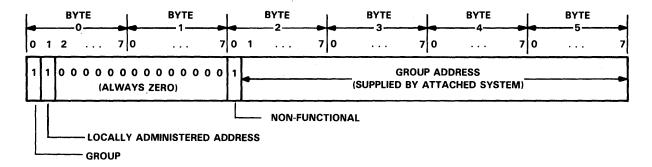

| 3-9    | Destination Address Format                                  |      |

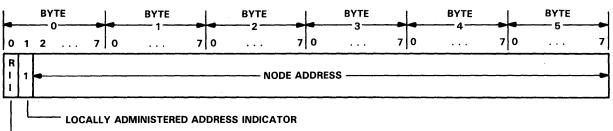

| 3-10   | Source Address Format                                       |      |

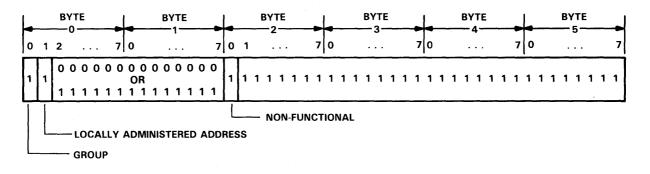

| 3-11   | Broadcast Group Address                                     |      |

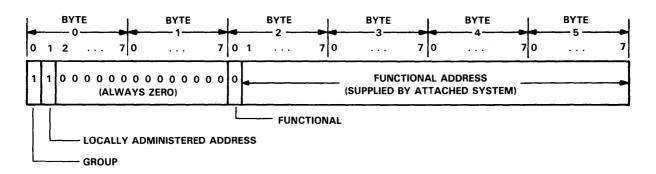

| 3-12   | Functional Group Address                                    | 3-13 |

| 3-13   | Group Address                                               |      |

| 3-14   | Ring Station Address Format                                 |      |

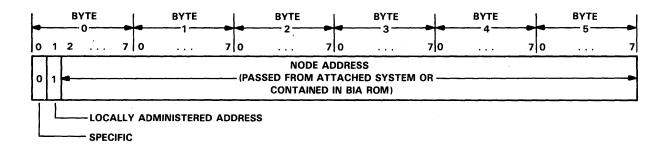

| 3-15   | Routing Information Field Format                            |      |

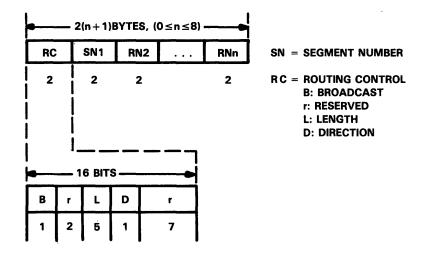

| 3-16   | General MAC Frame Format                                    |      |

| 3-17   | Response Code Subvector                                     |      |

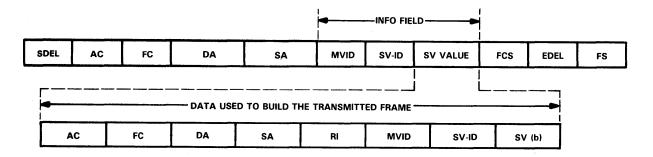

| 3-18   | Transmit Forward MAC Frame                                  |      |

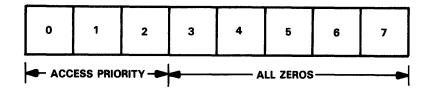

| 3-19   | Model AC                                                    |      |

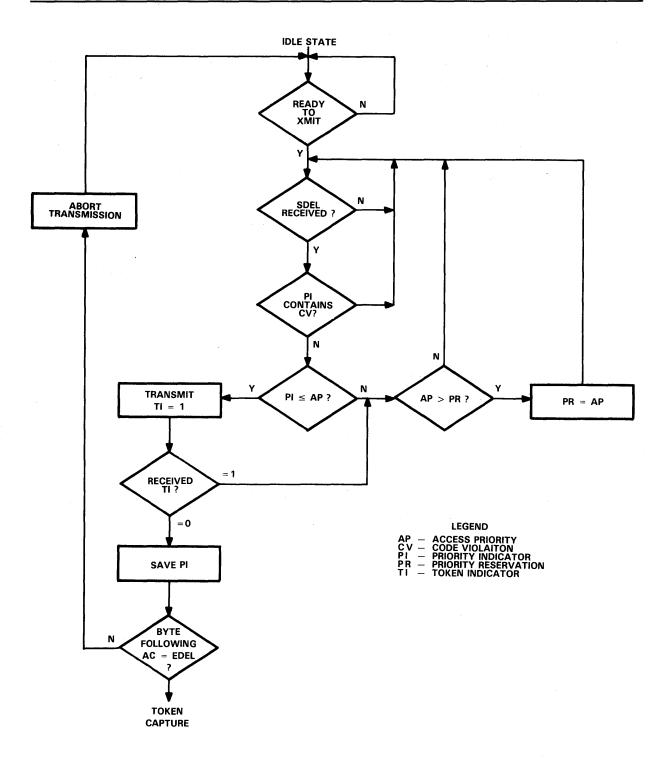

| 3-20   | Token Capture Flowchart                                     | 3-56 |

iv

# Figure

## Page

۷

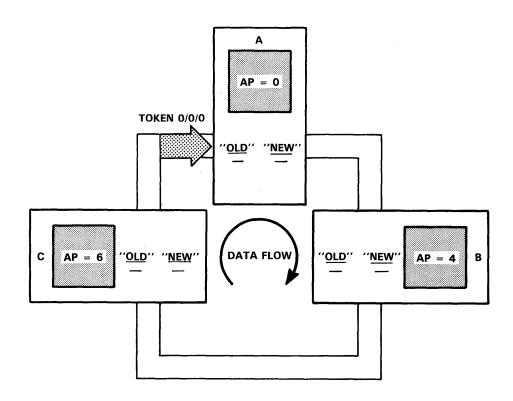

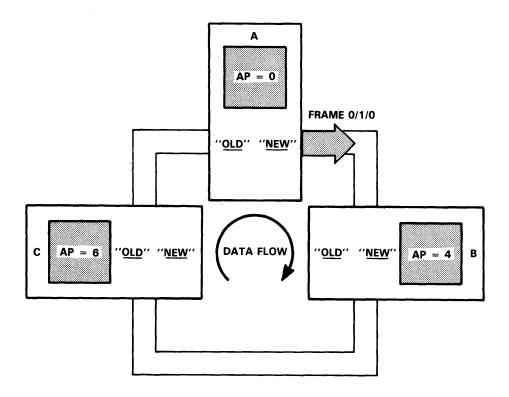

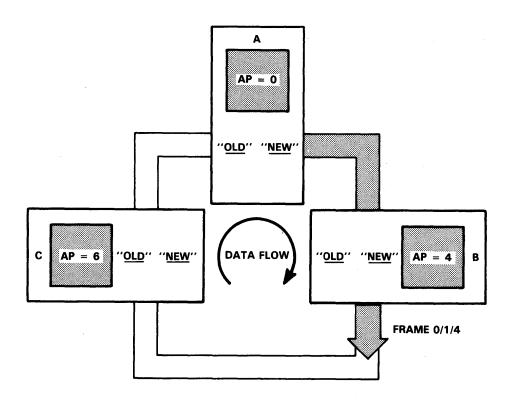

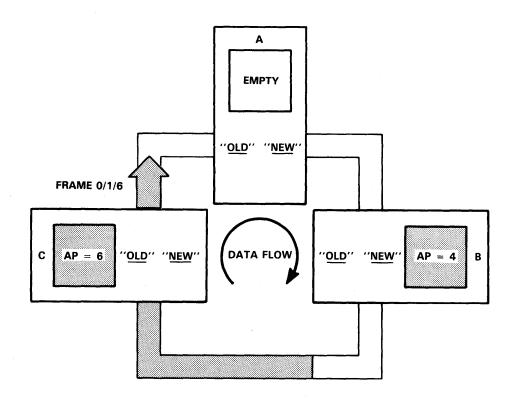

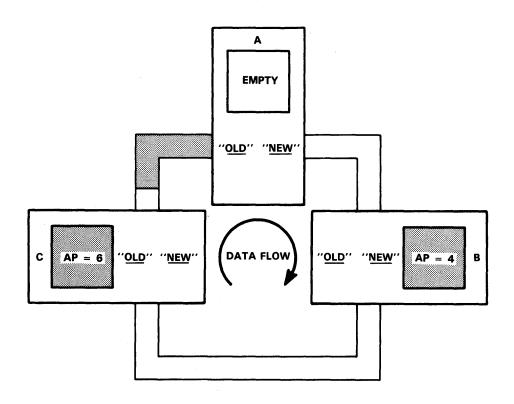

| 3-21       | Token Is at Point Shown                                   |      |

|------------|-----------------------------------------------------------|------|

| 3-22       | Station A Captures Token and Begins Transmission of Frame | 3-62 |

| 3-23       | Station B Repeats Frame and Changes PR to 4               | 3-63 |

| 3-24       | Station C Repeats Frame and Changes PR to 6               |      |

| 3-25       | Station A Strips Frame from the Ring                      |      |

| 3-26       | Station A Releases a New Token                            |      |

| 3-27       | Station B Repeats Token and Changes PR to 4               |      |

| 3-28       | Station C Captures Token and Begins Transmission of Frame |      |

| 3-29       | Frame Circulates with No Modification                     |      |

| 3-30       | Station C Begins Stripping the Frame from the Ring        | 2 70 |

| 3-30       |                                                           |      |

|            | Station C Issues a New Token of Same Priority             |      |

| 3-32       | Station A Performs a REPLACE and Transmits the Token      |      |

| 3-33       | Station B Captures Token and Transmits Frame              |      |

| 3-34       | Station B Strips Its Frame from the Ring                  |      |

| 3-35       | Station B Issues a New Token at the Original Priority     |      |

| 3-36       | Station A POPS Its Stacks and Issues Priority-Free Token  |      |

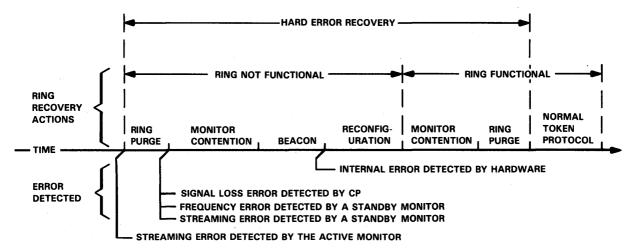

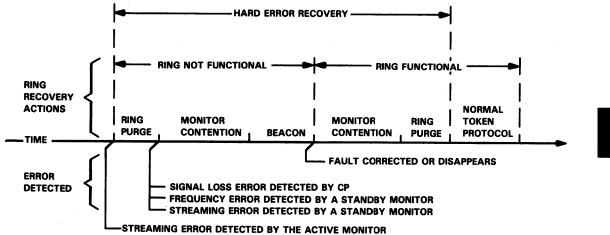

| 3-37       | Solid Hard Error Recovery Time Line                       |      |

| 3-38       | Intermittent Hard Error Recovery Time Line                | 3-83 |

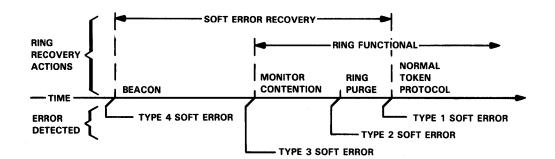

| 3-39       | Soft Error Recovery Time Line                             | 3-86 |

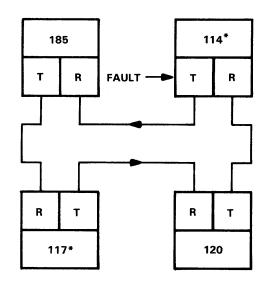

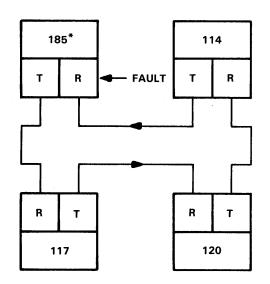

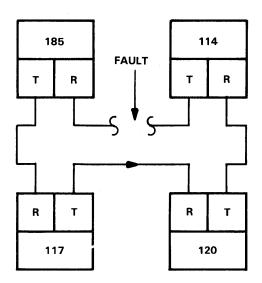

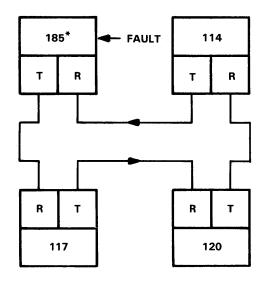

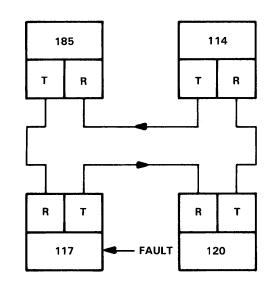

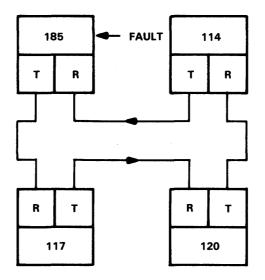

| 3-40       | Transmitter Fault in Adapter 114                          | 3-87 |

| 3-41       | Receiver Fault in Adapter 185                             |      |

| 3-42       | Broken Ring Fault                                         |      |

| 3-43       | Transmitter Streaming Fault in Adapter 185                |      |

| 3-44       | Adapter 117 Detects a Streaming Error                     |      |

| 3-45       | Adapter 185 Streaming Claim Token Frames                  |      |

| 4-1        | Star-Wired Local Area Network                             |      |

| 4-2        | Adapter Registers                                         |      |

| 4-3        | System Command Block and System Status Block              |      |

| 4-4        | Adapter Command Set                                       |      |

| 4-5        | Adapter Chipset Interconnect Diagram                      |      |

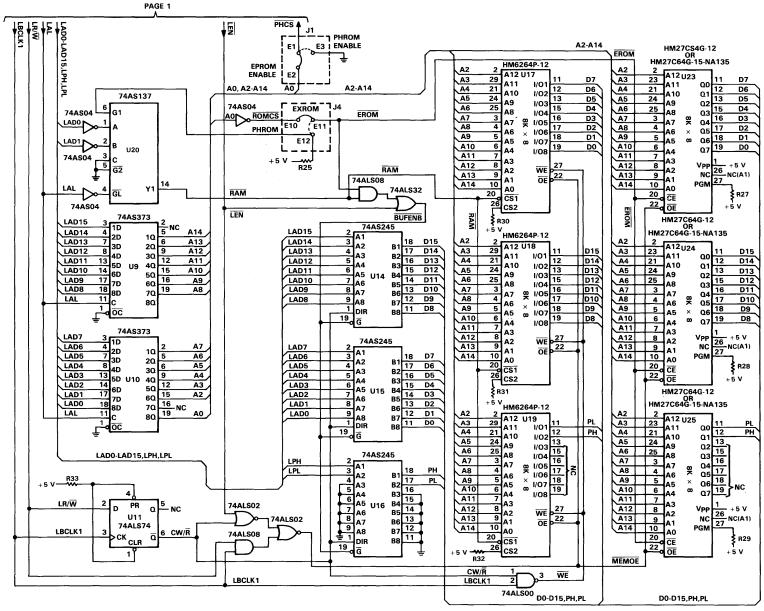

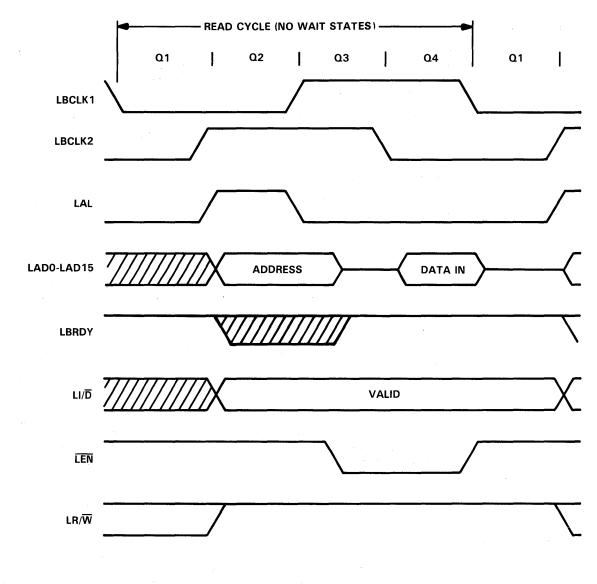

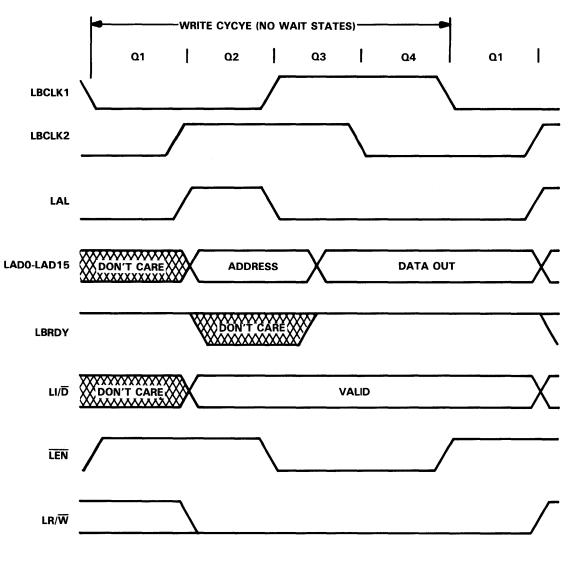

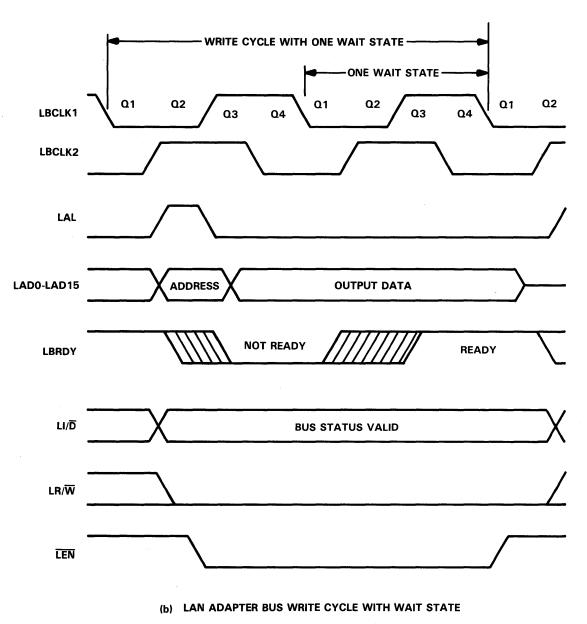

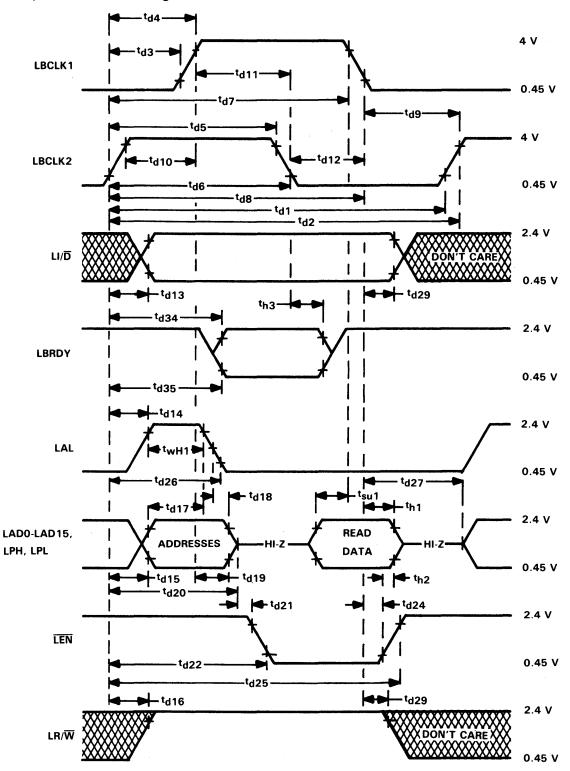

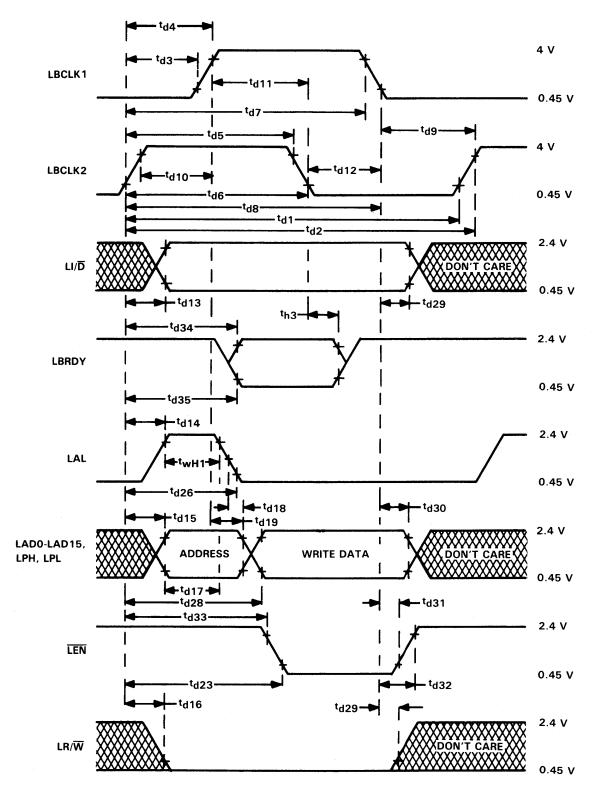

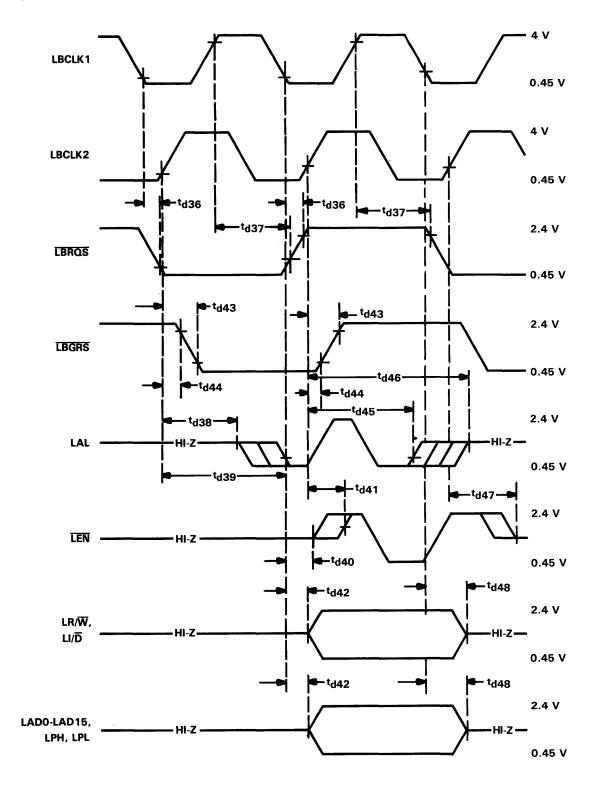

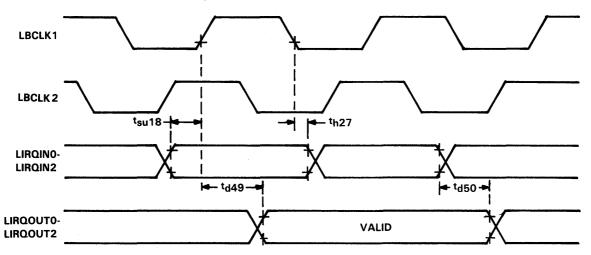

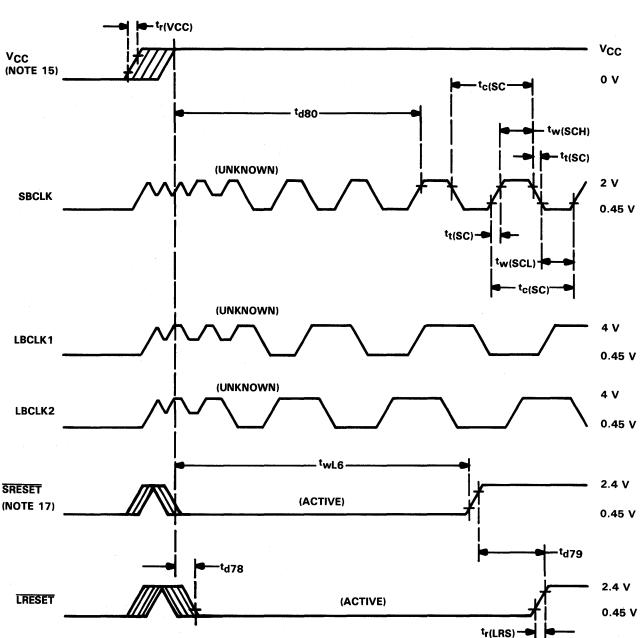

| 4-5        | Basic Timing for LAN Adapter Bus Transfers                |      |

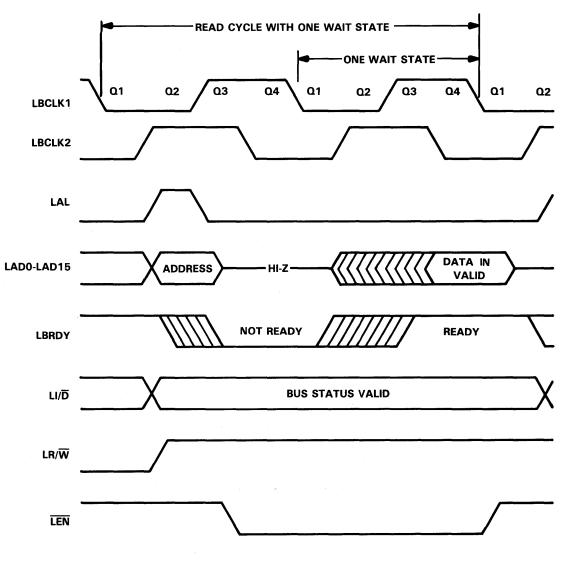

| 4-0        | LAN Adapter Bus Transfers with One Wait State             |      |

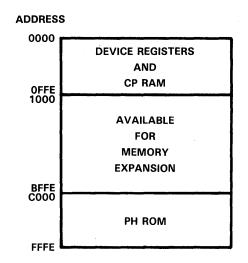

| 4-7        | LAN Adapter Bus Memory Map                                |      |

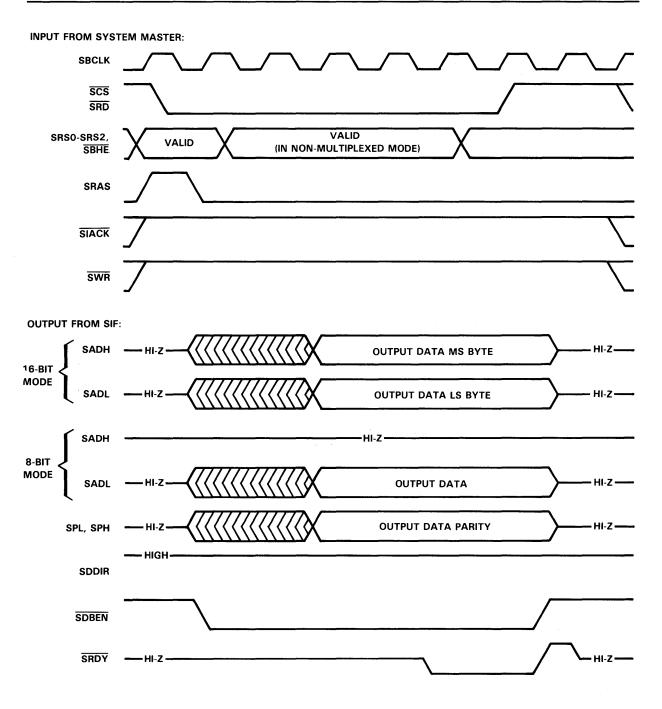

| 4-0<br>4-9 |                                                           |      |

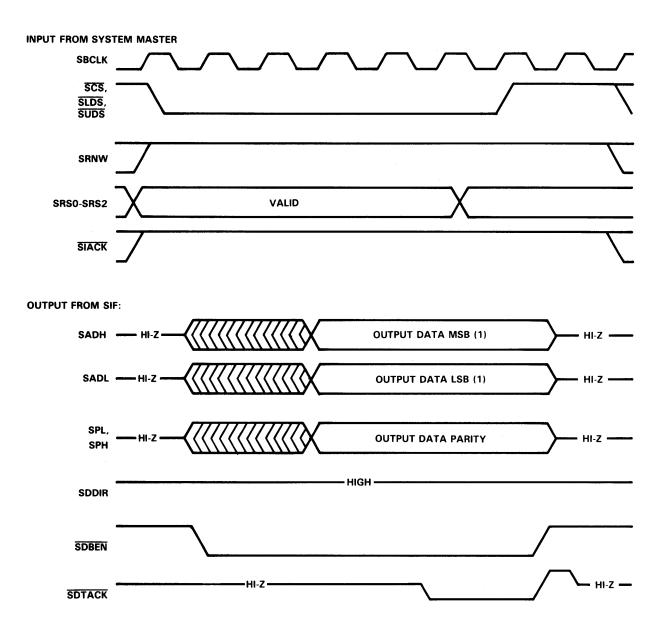

| 4-9        | 808X DIO Read Cycle                                       |      |

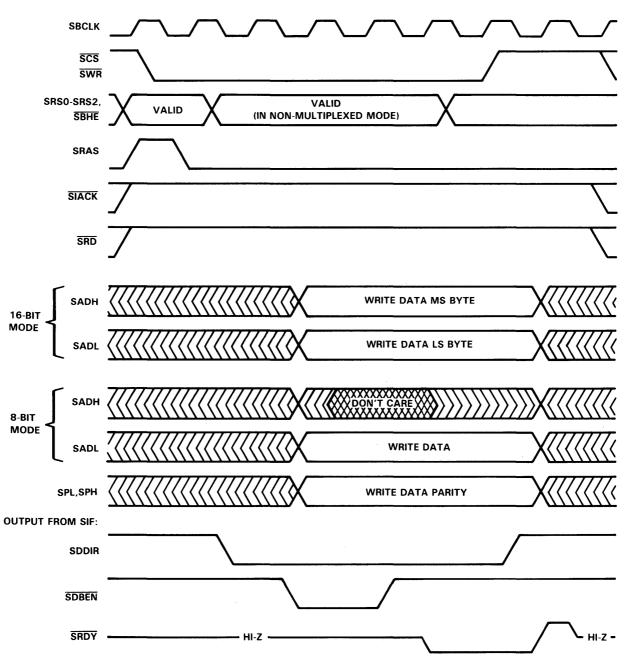

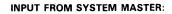

| -          | 808X DIO Write Cycle                                      |      |

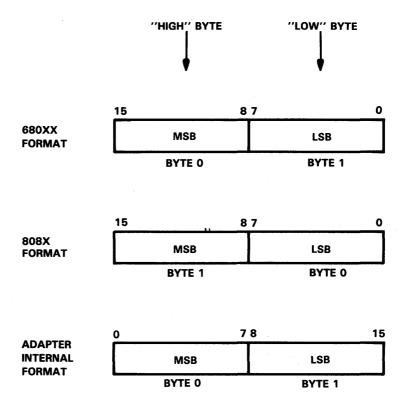

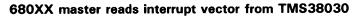

| 4-11       | 680XX Mode DIO Read Cycle Timing                          |      |

| 4-12       | 680XX Mode DIO Write Cycle Timing                         |      |

| 4-13       | Bit- and Byte-Numbering Conventions                       |      |

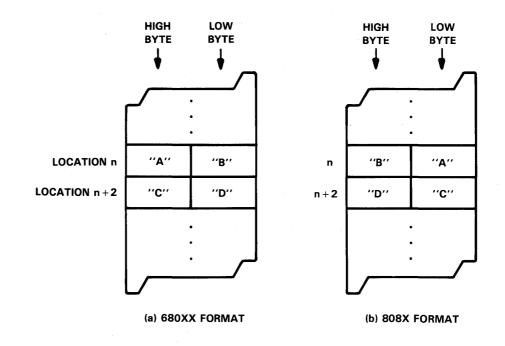

| 4-14       | Formats for Storing Character String "ABCD" in Memory     |      |

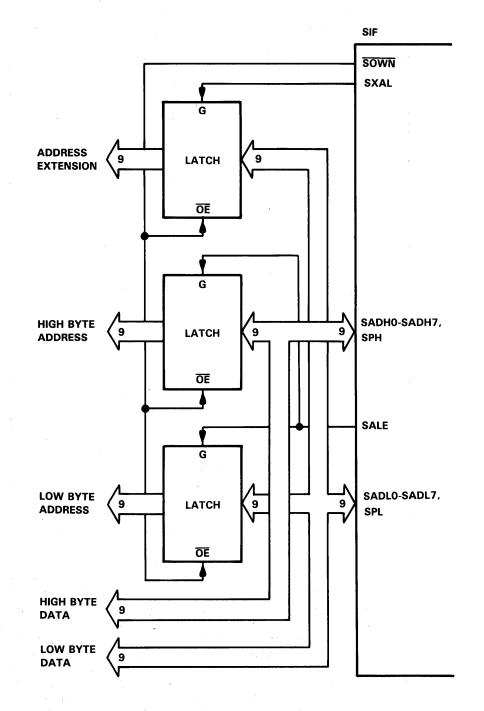

| 4-15       | External TTL Latches Demultiplex Address/Data Bus         |      |

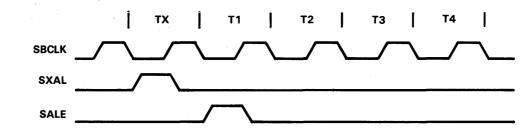

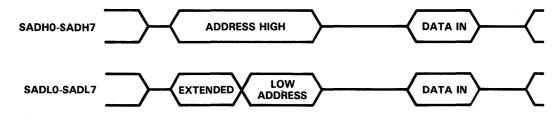

| 4-16       | Address Multiplexing for 8- and 16-Bit Modes              |      |

| 4-17       | Comparison of Address Bit Formats                         | 4-45 |

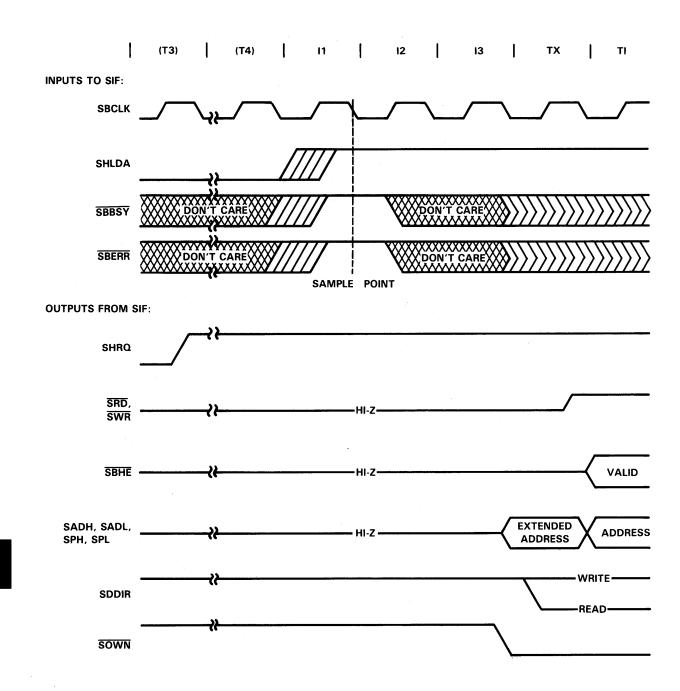

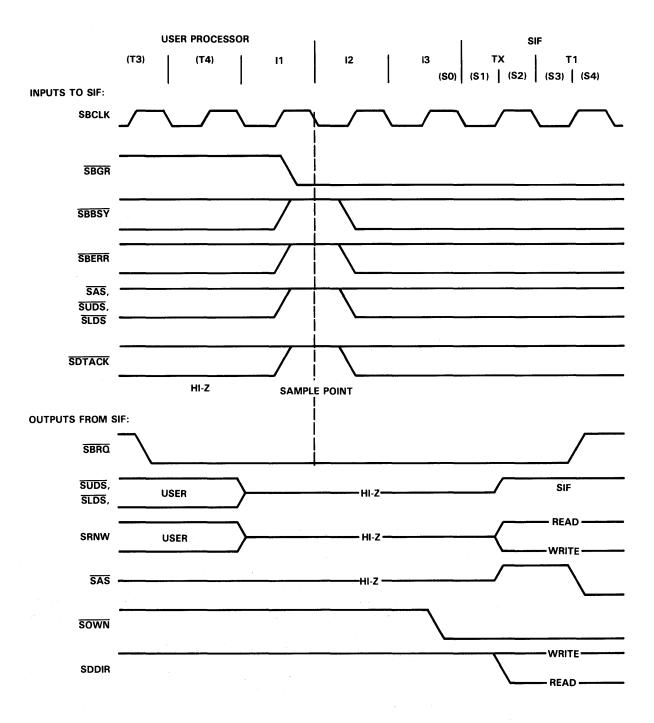

| 4-18       | Adapter Acquires System Bus - 808X Mode                   |      |

| 4-19       | Adapter Returns System Bus - 808X Mode                    |      |

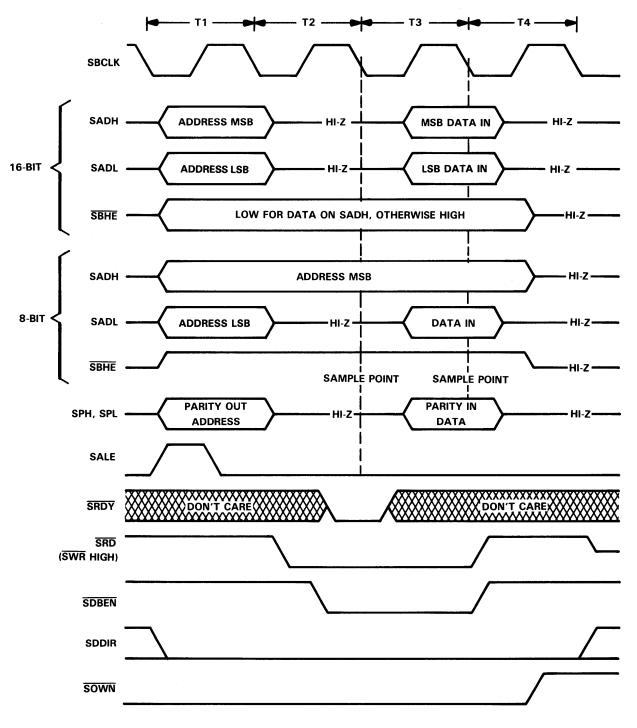

| 4-20       | 808X DMA Read Cycle Timing                                |      |

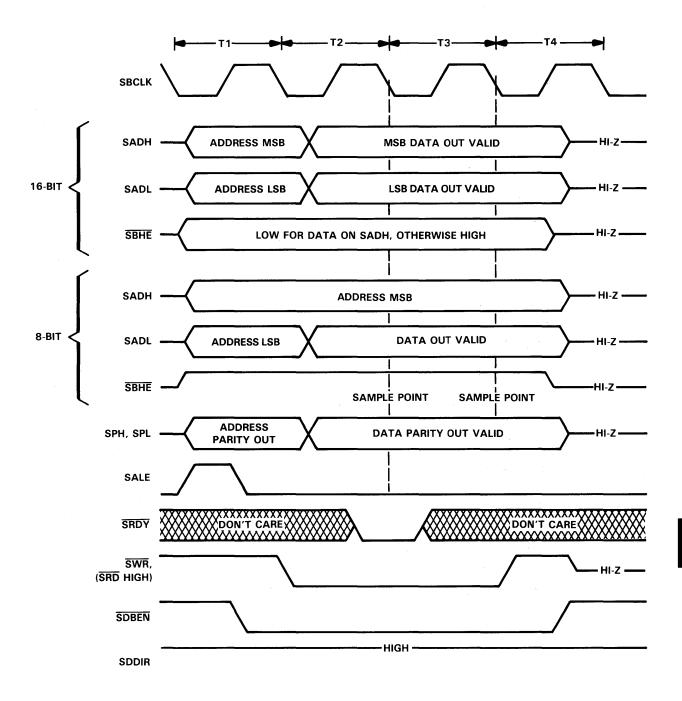

| 4-21       | 808X DMA Write Cycle Timing                               |      |

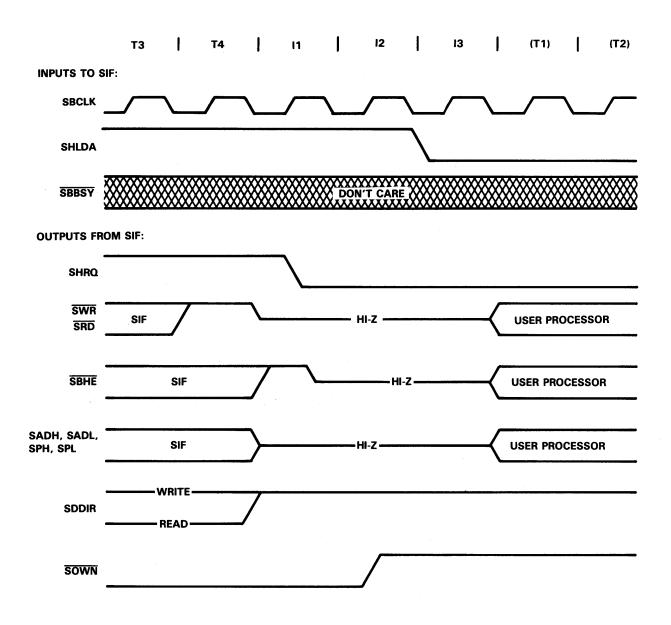

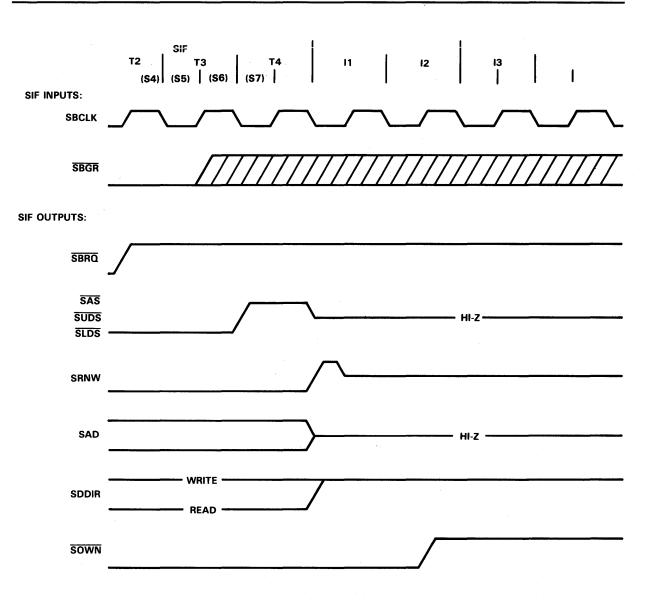

| 4-22       | Adapter Acquires System Bus – 680XX Mode                  |      |

| 4-23       | Adapter Returns System Bus – 680XX Mode                   | 4-58 |

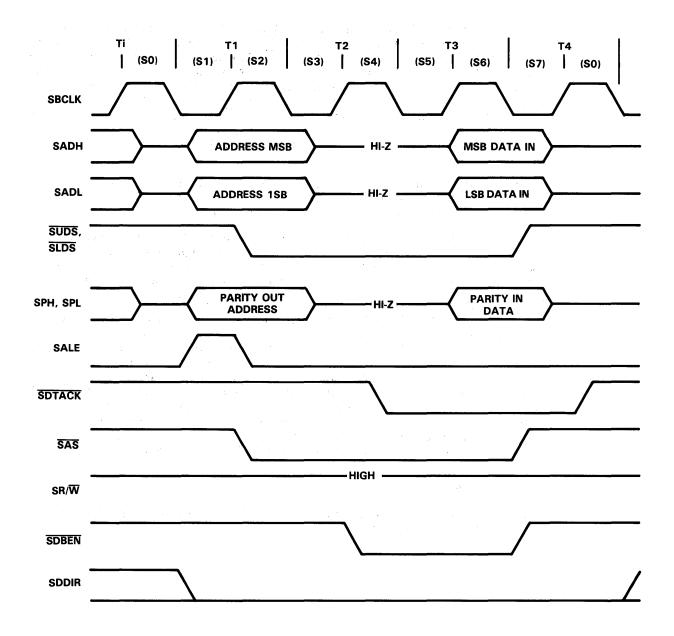

| 4-24       | 680XX Mode DMA Read Timing                                | 4-60 |

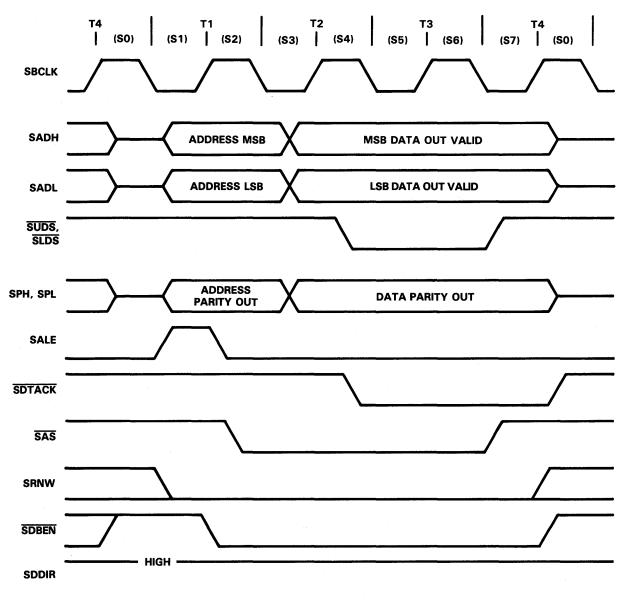

| 4-25       | 680XX Mode DMA Write Timing                               | 4-61 |

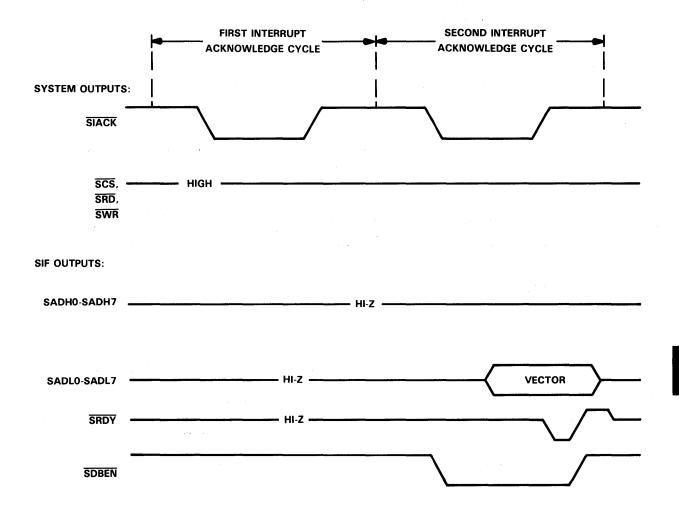

| 4-26       | Interrupt Acknowledge Timing for 808X Mode                |      |

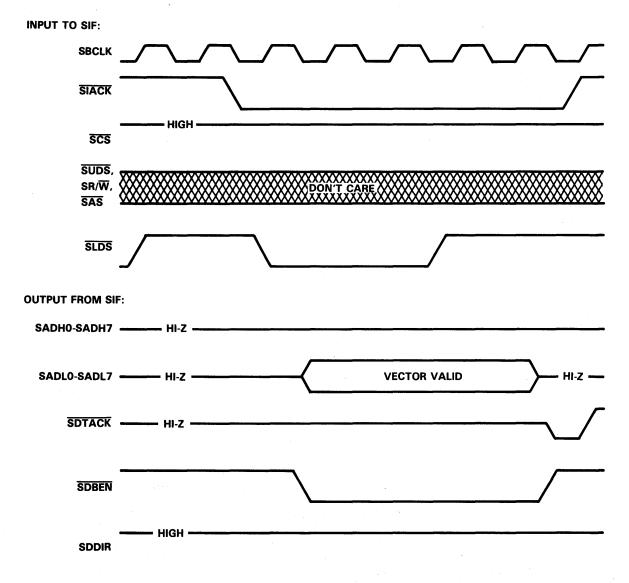

| 4-27       | Interrupt Acknowledge Timing for 680XX Mode               |      |

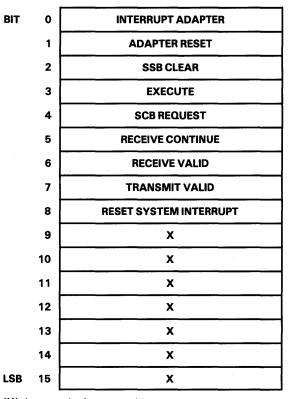

| 4-28       | Interrupt Register Write Bit Assignments                  |      |

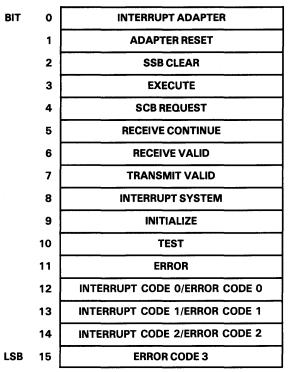

| 4-29       | Interrupt Register Read Bit Assignments                   |      |

| 4-30       | Parameter Initialization Block                            |      |

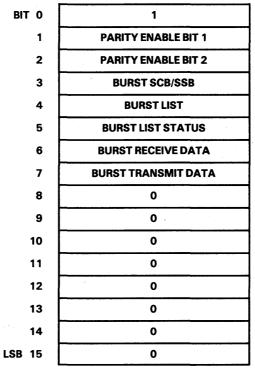

| 4-31       | Initialization Options Bit Assignments                    |      |

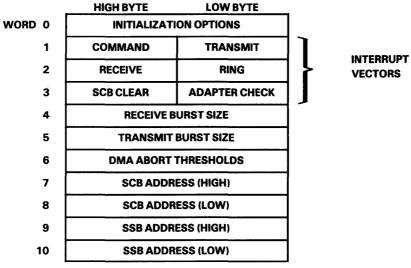

| 4-32       | System Command Block Format                               |      |

|            | ,                                                         |      |

# Figure

| 4-33         |                                       | 4-78  |

|--------------|---------------------------------------|-------|

| 4-34         |                                       | 4-79  |

| 4-35         | · · · · · · · · · · · · · · · · · · · | 4-79  |

| 4-36         |                                       | 4-80  |

| 4-37         |                                       | 4-81  |

| 4-38         |                                       | 4-82  |

| 4-39         |                                       | 4-82  |

| 4-40         |                                       | 4-85  |

| 4-41         |                                       | 4-86  |

| 4-42         |                                       | 4-89  |

| 4-43         |                                       | 4-92  |

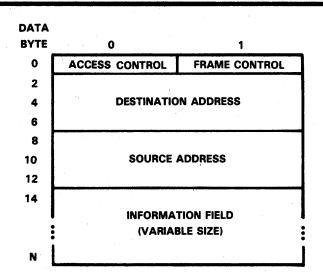

| 4-44         | Attached System Frame Logical Format  | 4-93  |

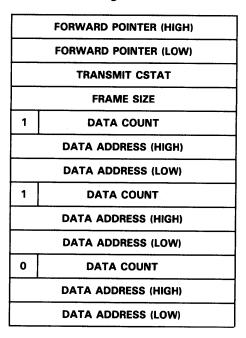

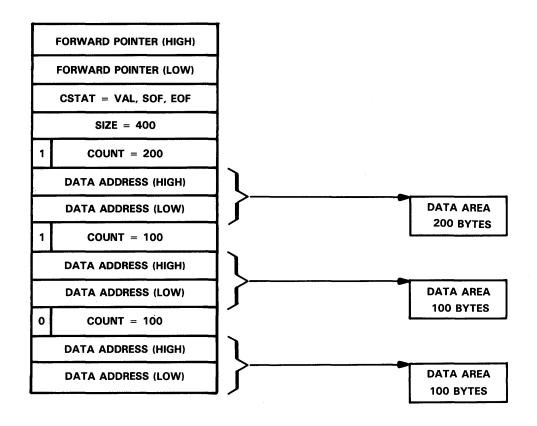

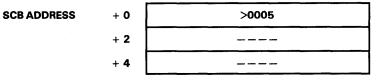

| 4-45         | Transmit SCB                          | 4-94  |

| 4-46         | Transmit Parameter List               | 4-95  |

| 4-47         | Transmit SSB                          | 4-98  |

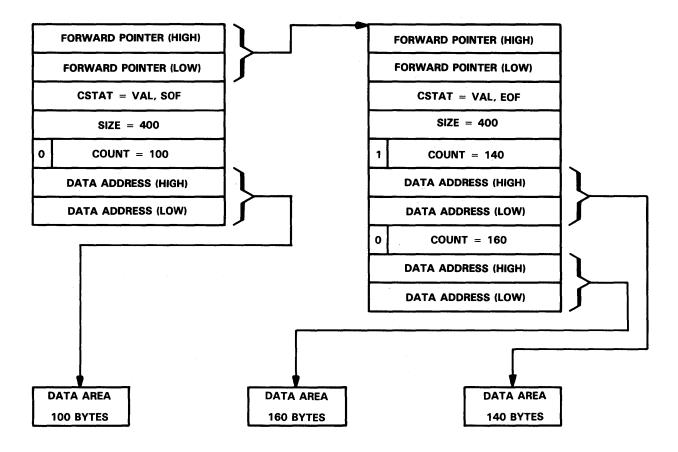

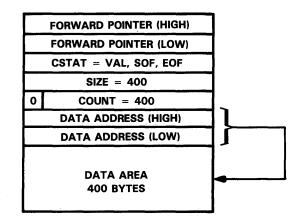

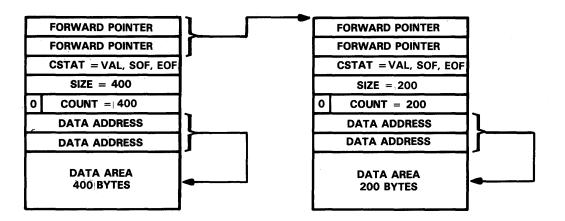

| 4-48         | Transmit List Format: Example 1       | 4-101 |

| 4-49         | Transmit List Format: Example 2       | 4-102 |

| 4-50         | Transmit List Format: Example 3       |       |

| 4-51         |                                       | 4-103 |

| 4-52         |                                       | 4-103 |

| 4-53         |                                       | 4-104 |

| 4-54         | Receive Parameter List                |       |

| 4-55         | Receive Command SSB                   |       |

| 4-56         |                                       | 4-110 |

| 4-57         |                                       | 4-110 |

| 4-58         |                                       | 4-110 |

| 4-59         |                                       | 4-111 |

| 4-59         |                                       | 4-111 |

| 4-61         |                                       | 4-111 |

| 4-62         | Read Error Log Command SCB            |       |

| 4-02         |                                       | 4-112 |

| 4-03         | Read Error Log Command SSB            |       |

| 4-04<br>4-65 |                                       | 4-114 |

| 4-65         |                                       |       |

|              | Read Adapter System Buffer Space      | 4-114 |

| 4-67<br>4-68 |                                       | 4-115 |

|              |                                       |       |

| 4-69         |                                       | 4-118 |

| 4-70         |                                       | 4-122 |

| 4-71         |                                       | 4-123 |

| 4-72         |                                       | 4-124 |

| 4-73         |                                       | 4-124 |

| 4-74         |                                       | 4-125 |

| 4-75         |                                       | 4-126 |

| 4-76         |                                       | 4-128 |

| B-1          |                                       | B-8   |

| B-2          |                                       | B-9   |

|              |                                       |       |

# Tables

| Table        |                                                    | Page |

|--------------|----------------------------------------------------|------|

| 3-1          | Network Management Functional Addresses            |      |

| 3-2          | MAC Frame Class Designators                        |      |

| 3-3          | Source and Destination Class Applications          |      |

| 3-4          | Major Vector Commands                              |      |

| 3-5<br>3-6   | Subvector Types                                    |      |

| 3-0<br>3-7   | Response Code Subvector Code Values                |      |

| 3-7          | MAC Protocol Processes                             |      |

| 3-9          | Monitor Contention Process - Applicable MAC Frames |      |

| 3-10         | Events Triggering Monitor Contention               |      |

| 3-11         | Ring Purge Process - Applicable MAC Frames         |      |

| 3-12         | Ring Poll Process - Applicable MAC Frames          |      |

| 3-13         | Beacon Process - Applicable MAC Frames             |      |

| 3-14         | Insertion Process - Applicable MAC Frames          |      |

| 3-15         | Transmit Forward Process - Applicable MAC Frames   |      |

| 3-16         | Remove Ring Station MAC Frame                      |      |

| 3-17         | Network Management Request MAC Frames              |      |

| 3-18         | Network Management Response MAC Frames             |      |

| 3-19         | Priority Control Stimuli                           | 3-60 |

| 3-20         | Report Error MAC Frame                             | 3-77 |

| 3-21         | Isolating Error Counters                           | 3-79 |

| 3-22         | Non-Isolating Error Counters                       |      |

| 4-1          | Adapter Bus Status Codes                           |      |

| 4-2          | Memory Performance Requirements                    |      |

| 4-3          | Hardware Interface Option Select                   |      |

| 4-4          | SIF Register Selection                             |      |

| 4-5          | Interface Pin Functions - 808X Mode                |      |

| 4-6          | 808X 16-Bit Address Map                            |      |

| 4-7          | 808X 8-Bit Address Map                             |      |

| 4-8          | 808X DIO Read Data Bus Controls                    |      |

| 4-9          | 808X DIO Write Data Bus Controls                   |      |

| 4-10         | Interface Pin Functions - 680XX Mode               |      |

| 4-11<br>4-12 | 680XX 16-Bit Address Map                           |      |

| 4-12         | 680XX DIO Read Data Bus Controls                   |      |

| 4-13         | System DMA Cycle Description - 808X                |      |

| 4-14         | System DMA Cycle Description - 680XX               |      |

| 4-16         | 808X DMA Interface Pin Functions                   |      |

| 4-17         | 680XX DMA Interface Pin Functions                  |      |

| 4-18         | Adapter Interrupt Pin Descriptions                 |      |

| 4-19         | Interrupt Register Write Bit Functions             |      |

| 4-20         | Interrupt Register Read Bit Functions              |      |

| 4-21         | Bring-up Diagnostic Error Codes                    |      |

| 4-22         | Initialization Options Field Bit Functions         |      |

| 4-23         | Adapter Initialization Errors                      |      |

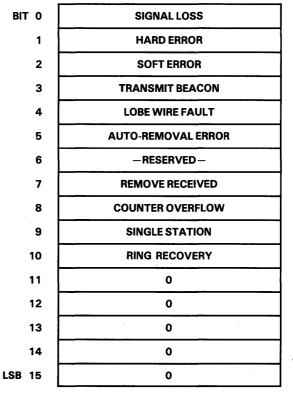

| 4-24         | Ring Status Field Bit Functions                    |      |

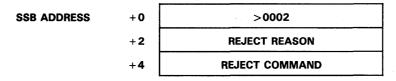

| 4-25         | Reject Reason Field Bit Functions                  | 4-81 |

| 4-26         | Adapter Check Bit Definitions                      | 4-83 |

| 4-27         | Adapter Command Summary                            | 4-84 |

| 4-28         | Open Parameter Functions                           |      |

| 4-29         | Open Status Bit Definitions                        |      |

| 4-30         | Open Phases and Open Error Codes                   |      |

| 4-31         | Open Error Codes                                   |      |

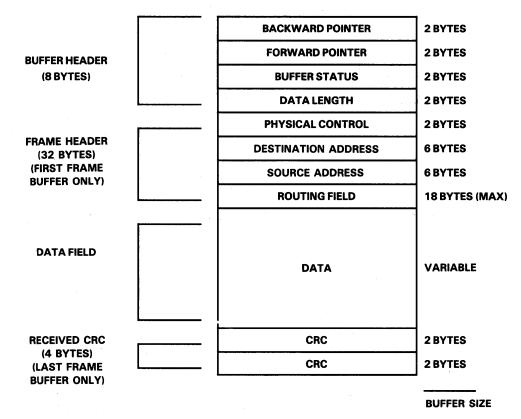

| 4-32         | Attached System Frame Fields                       |      |

| 4-33         | Transmit Parameter List Fields                     | 4-96 |

-

| Table |                                                         | Page  |

|-------|---------------------------------------------------------|-------|

| 4-34  | Transmit Complete Field Bit Definitions                 | 4-99  |

| 4-35  | Receive Parameter List Field Definitions                | 4-106 |

| 4-36  | Receive Complete Field Bit Definitions                  | 4-108 |

| 4-37  | Close Completion Field Bit Definitions                  |       |

| 4-38  | Set Group Address Completion Field Bit Definitions      |       |

| 4-39  | Set Functional Address Completion Field Bit Definitions | 4-112 |

| 4-40  | Read Error Log Counters                                 | 4-113 |

| 4-41  | Read Error Log Completion Field Bit Definitions         | 4-114 |

| 4-42  | Adapter Internal Pointers                               | 4-115 |

| 4-43  | Read Adapter Buffer Completion Field Bit Definitions    | 4-116 |

| 4-44  | Ring Interface Component List                           |       |

| 4-45  | Protocol Handler to Ring Interface Signals              | 4-121 |

| B-1   | MAC Frame Major Vectors                                 | B-1   |

| B-2   | MAC Frame Subvectors                                    | B-5   |

| B-3   | Burned-In Address Contents                              | B-11  |

# Introduction

Appendix B - General

.

# 1. Introduction

#### 1.1 Overview

The Texas Instruments TMS380 LAN adapter chipset was developed jointly with IBM and provides computer, peripheral, and telecommunication equipment manufacturers with a verified chipset for connecting to the IBM token ring local area network (LAN).

The TMS380 chipset uses a token-passing access technology compatible with the IEEE 802.5 standard. The chipset provides a 4-megabit per second data expressway using twisted-pair wire or fiber-optic media. The integrated LAN adapter architecture of the TMS380 ensures connectivity to the IBM token ring network by providing all the functions needed to connect an attaching product's host system bus to the physical media. High reliability of the network is provided via dedicated error checker circuits, on-chip diagnostic and error-monitoring software, and other network-management features.

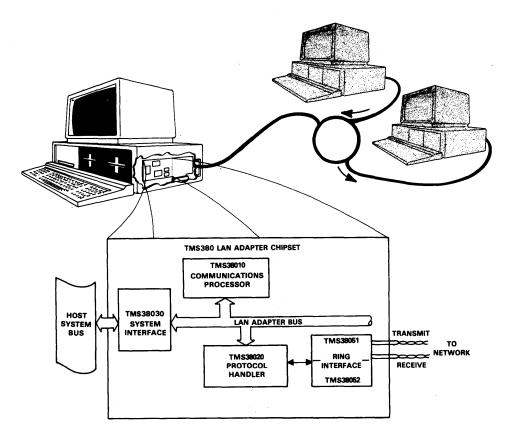

FIGURE 1-1. TMS380 LAN ADAPTER CHIPSET

The integrated architecture of the TMS380 chipset combines a high-speed DMA hostsystem bus interface, a 16-bit CPU with on-chip buffer RAM, a protocol handler with on-chip ROM for software, and a pair of chips for interfacing to the physical media. This approach eliminates incompatibilities that could arise with different LAN adapter cards, thus ensuring standardized LAN connectivity and multi-vendor interoperability on the IBM token ring network. The 16K bytes of on-chip software supports highly reliable token ring operation, extensive LAN management services, and thorough self-test diagnostics. The TMS380 chipset meets the critical requirements of LAN connections for 16- and 32-bit desktop workstations by supplying a high performance LAN adapter with reduced chip count, low power dissipation, and minimal use of circuit card area. The TMS380 LAN adapter chipset has been rigorously verified by Texas Instruments and IBM to provide a compatible foundation for OEMs and end users to build long-term LAN solutions with confidence.

The TMS380 chipset is fully supported with development tools, applications information, documentation, and courses through Texas Instruments' Regional Technology Centers.

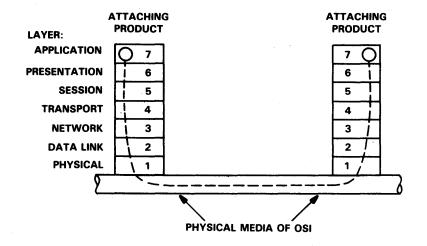

#### **1.2 The OSI Reference Model**

The Open Systems Interconnection (OSI) model is a conceptual network structure defined by the International Organization for Standardization. The purpose of the OSI model is to promote the development of worldwide data-communications standardization.

Networks are partitioned into a series of layers to reduce their design complexity. These layers are hierarchical with each layer built upon its predecessor, thus shielding each layer from the details of how the services from the other layers are implemented. The OSI model is partitioned into seven layers. The bottom four layers of the model define the network and how it functions, and the top three layers define how the network is used. The seven-layer OSI model is shown below.

FIGURE 1-2. THE OSI REFERENCE MODEL

The illustration shows the relationship of the seven layers to one another and the path taken by communication between two attaching products.

The functions of the layers are described here in order, starting with the lowest.

- The Physical layer defines the mechanical and electrical connection.

- The Data Link layer defines the way data is formatted for transmission and how access to the network is controlled. This layer has been separated by the IEEE 802 standards committee into two sublayers: the Medium Access Control (MAC) sublayer and the Logical Link Control (LLC) sublayer. (The MAC sublayer is discussed in more detail in the next section.)

- The Network layer defines the routing and switching of data between networks.

- The Transport layer ensures that data is sent to and arrives at the destination correctly.

- The **Session** layer defines the end user's interface into the network and establishes and manages communication dialogs.

- The **Presentation** layer maps applications data structures to and from the session layer.

- The **Application** layer provides network-based services to an end user's application programs.

#### 1.3 IEEE 802 LAN Standards

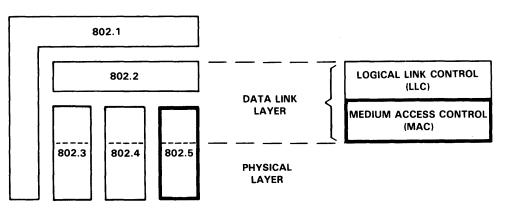

The Institute of Electrical and Electronics Engineers (IEEE) 802 committee has developed a set of local area network standards and protocols for the Physical and Data Link layers of the OSI model.

The Data Link layer has been divided by the IEEE 802 committee into two sublayers: the Medium Access Control (MAC) sublayer and the Logical Link Control (LLC) sublayer. To meet a variety of end-user requirements, the committee has defined three MAC technologies with associated physical media. The MAC technologies defined by IEEE 802 committee include:

- IEEE Standard 802.3, a bus topology using a Carrier Sense Multiple Access/Collision Detect (CSMA/CD) access method

- IEEE Standard 802.4, a bus topology using a token-passing access method

- IEEE Standard 802.5, a star-wired ring topology using a token-passing access method

In addition to the published standards listed above, the IEEE 802 committee has defined a Logical Link Control standard (802.2) and an internetworking and network management standard (802.1).

FIGURE 1-3. IEEE 802 LAN STANDARDS

#### 1.4 The Token Ring LAN: IEEE 802.5

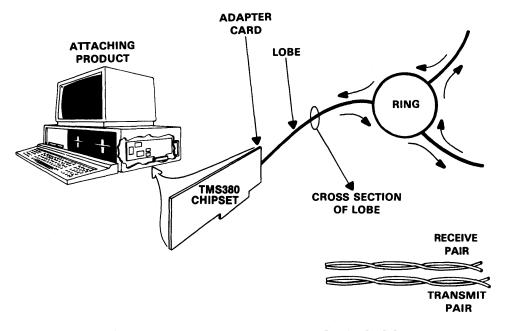

The IEEE 802.5 standard defines the MAC and physical sublayers for a star-wired topology. The TMS380 chipset, jointly developed by Texas Instruments and IBM, enables vendors to build LAN adapter cards that conform to the IEEE 802.5 standard.

The IEEE 802.5 standard defines a star-wired ring topology with a token-passing access method. A star-wired ring operates logically as a ring but physically resembles a star. This topology combines the point-to-point signaling advantages of a ring with the maintenance and reliability advantages of a centrally wired star.

An adapter card, based on the TMS380 chipset, is used to attach products to the network. The adapter card enables connection to the network through twisted wire-pairs, referred to as a **lobe**.

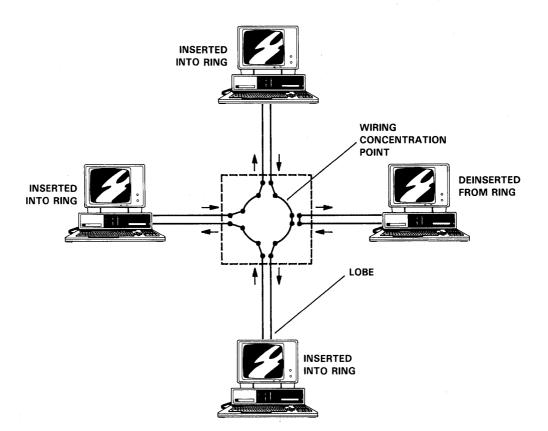

FIGURE 1-4. THE STAR-WIRED RING TOPOLOGY

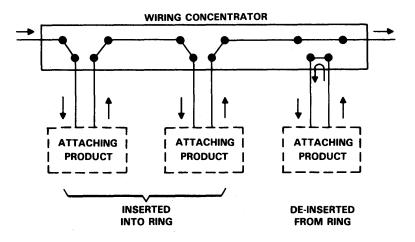

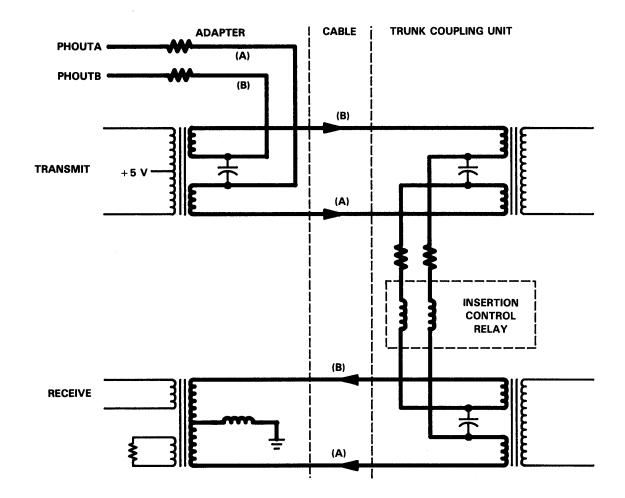

The lobe connects to the ring through a wiring concentrator as shown in the illustration on the next page. In its basic form, a wiring concentrator consists of bypass relays that are normally closed, but which are switched on when an attaching product is inserted into the ring or switched off when an attaching product is de-inserted from the ring.

Each adapter card provides the insertion control to drive the relay for inserting into the ring. Products not powered on or lobes that have been damaged and cannot provide the insertion signal to the wiring concentrator are not inserted in the ring. This central concentration of the cable permits the star-wired ring LAN to be easily reconfigured, expanded, and diagnosed for problems.

FIGURE 1-5. TOKEN RING WIRING CONCENTRATOR

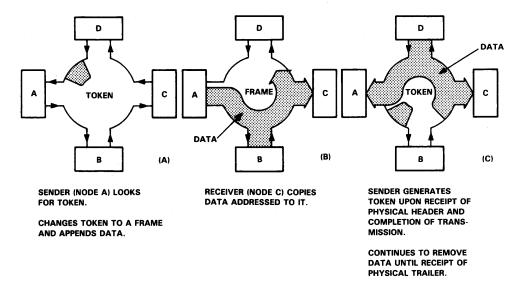

Once a product is physically inserted into the ring, logical access to the ring is controlled with a token-passing protocol. A **token** is an access-granting message that circulates from node to node. Only one node can have control of the token at a time, thereby preventing data **collisions** (two or more nodes attempting to transmit at the same time).

A single token, 24 bits in length, circulates around the ring when no data is being transmitted. A node that needs to transmit data waits for a token, captures the token, and marks it "busy." The node then transmits a frame containing data onto the ring.

The destination node copies the data and acknowledges the receipt of the frame by setting the address-recognized and frame-copied bits in the frame. The node that originated the frame removes, or "strips," the frame when it circulates back. After the frame is stripped from the ring, the node releases a token. Thus, there is only one token on the ring at a time, and possession of this token gives the node exclusive use of the ring.

This deterministic approach insures orderly, collision-free access to the ring and loadingindependent response times. Token-passing access also allows priority levels to be assigned to tokens, thus providing support for time-critical and synchronous traffic. The format of a token and a frame are shown below.

#### TOKEN FORMAT:

| STARTING  | ACCESS  | ENDING    |

|-----------|---------|-----------|

| DELIMITER | CONTROL | DELIMITER |

| 1 BYTE    | 1 BYTE  | 1 BYTE    |

#### FRAME FORMAT:

| STARTING<br>DELIMITER<br>1 BYTE | ACCESS<br>CONTROL<br>1 BYTE | FRAME<br>CONTROL<br>1 BYTE | DESTINATION<br>ADDRESS<br>6 BYTES | SOURCE<br>ADDRESS<br>6 BYTES | INFORMATION<br>FIELD | FRAME<br>CHECK<br>SEQUENCE<br>4 BYTES | ENDING<br>DELIMITER<br>1 BYTE | FRAME<br>STATUS<br>1 BYTE |

|---------------------------------|-----------------------------|----------------------------|-----------------------------------|------------------------------|----------------------|---------------------------------------|-------------------------------|---------------------------|

|---------------------------------|-----------------------------|----------------------------|-----------------------------------|------------------------------|----------------------|---------------------------------------|-------------------------------|---------------------------|

| FIGURE 1-6. FREE | TOKEN | FORMAT | AND | FRAME FORMAT | Г |

|------------------|-------|--------|-----|--------------|---|

|------------------|-------|--------|-----|--------------|---|

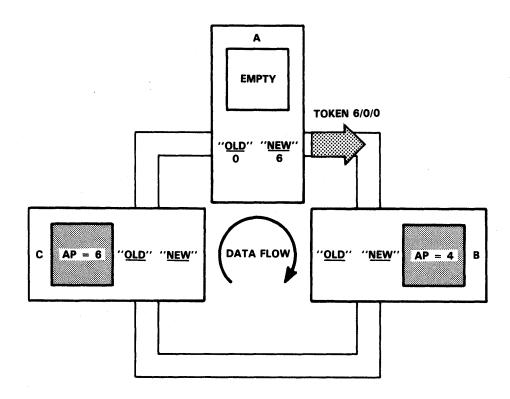

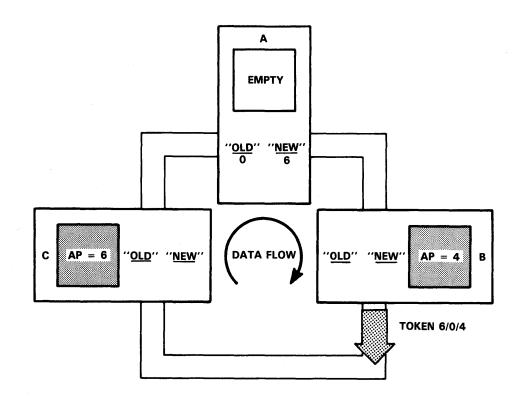

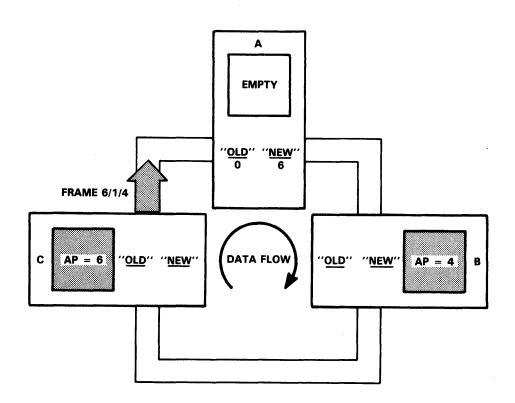

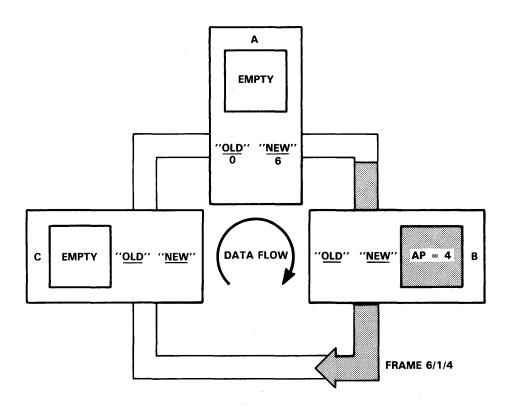

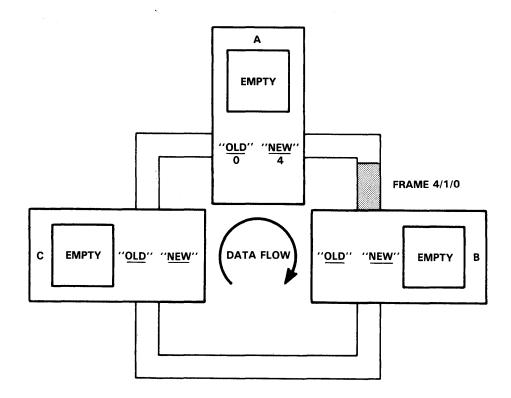

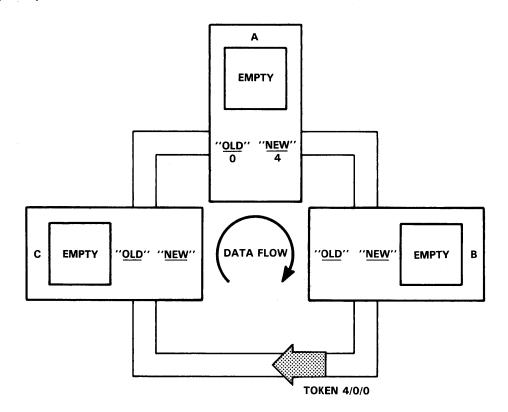

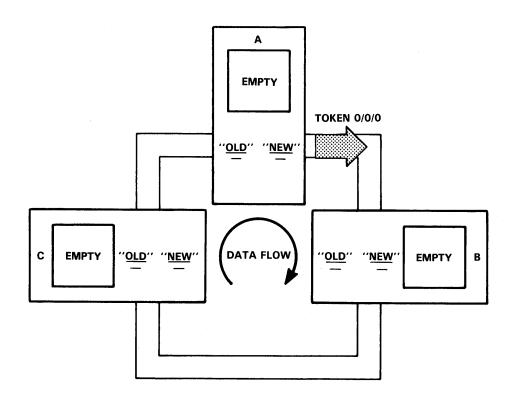

A token-passing example is shown below.

#### FIGURE 1-7. TOKEN-PASSING EXAMPLE

#### **1.5 LAN Adapter Architectures**

As LANs evolved from the laboratory to the marketplace, designers recognized the importance of minimizing a LAN's overhead burden on the host system. To achieve this goal, autonomous adapter architectures were designed by adding a dedicated central processing unit (CPU), memory, and support circuits to the LAN attachment card.

Autonomous adapter architectures, as opposed to controller-based architectures with no CPU on the adapter card, are the dominant LAN design approach used today. However, because early LSI chips were targeted at LAN controller-based architectures, card designers were forced to use more chips and expend extra design effort to build an adapter card. Typical adapter cards designed around LAN controllers require a general-purpose microprocessor, RAM for buffering data, ROM for the protocol software and diagnostics, interface circuits for connecting to the media, an interface for connecting to the host system bus, and various glue circuits, as illustrated below.

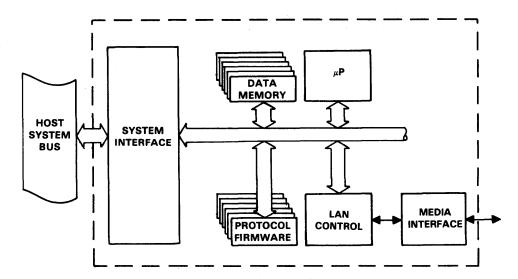

FIGURE 1-8. LAN CONTROLLER-BASED ADAPTER CARD ARCHITECTURE

The LAN controller-based approach to adapter card design suffers from high part count, high power dissipation, and wasteful use of printed circuit board area. More important, a fundamental drawback of the controller-based approach is that different adapter card designs, even those using the same LAN controller chip, do not necessarily work together on the same network. This places the burden of verifying compatibility with each card manufacturer, and eventually on the end user.

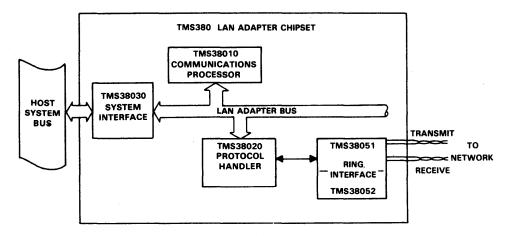

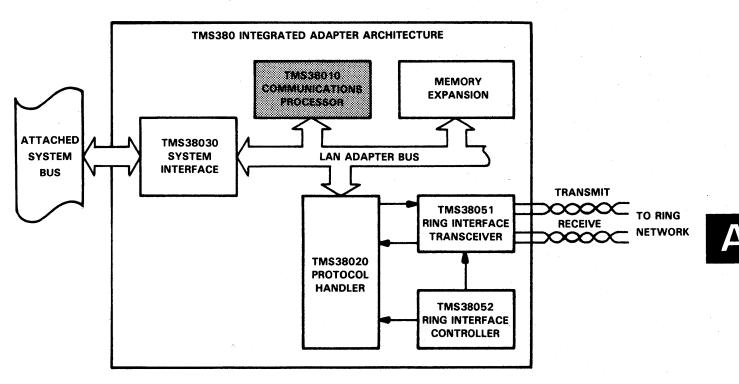

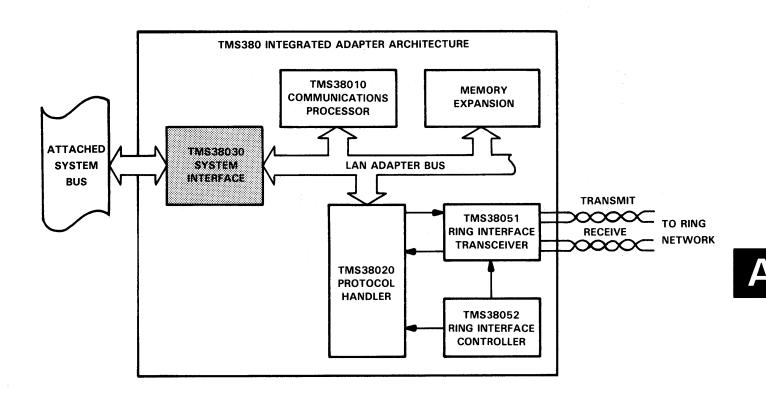

Host-independent operation of the LAN and the requirement for verified silicon standards mandated an ''integrated LAN adapter architecture'' for the TMS380. Through the use of advanced VLSI NMOS and bipolar processes, Texas Instruments reduced the essential building blocks needed on a LAN adapter card into the five-piece chipset shown below.

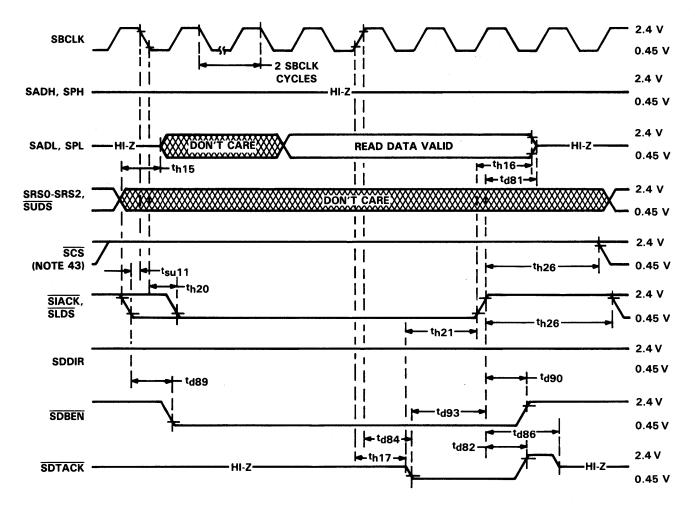

FIGURE 1-9. INTEGRATED ADAPTER ARCHITECTURE

The integrated architecture of the TMS380 chipset provides LAN designers with a total LAN adapter solution, from a flexible direct memory access (DMA) interface for the host system bus to the circuits providing the physical attachment to the LAN. The result is high-performance, low-cost LAN adapter cards with low power dissipation.

#### 1.6 Overview of the TMS380

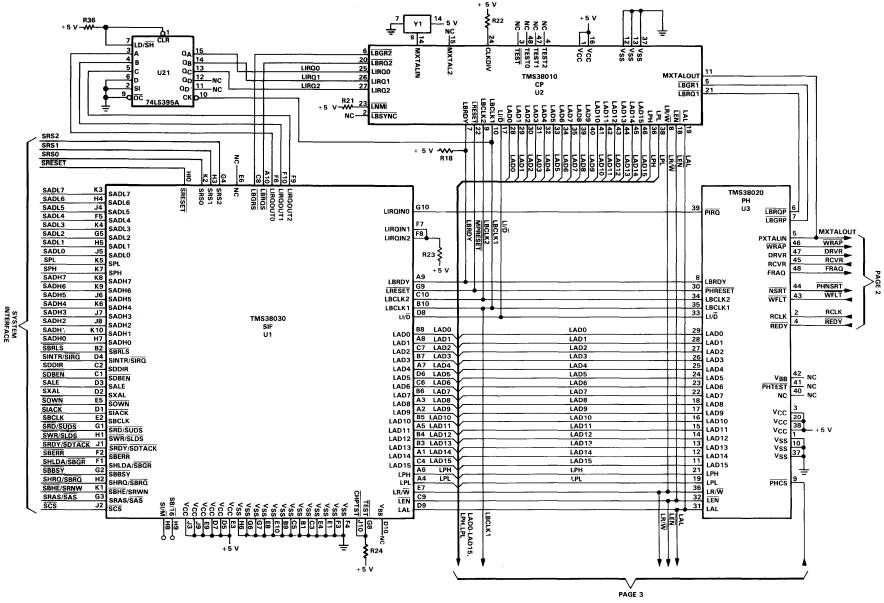

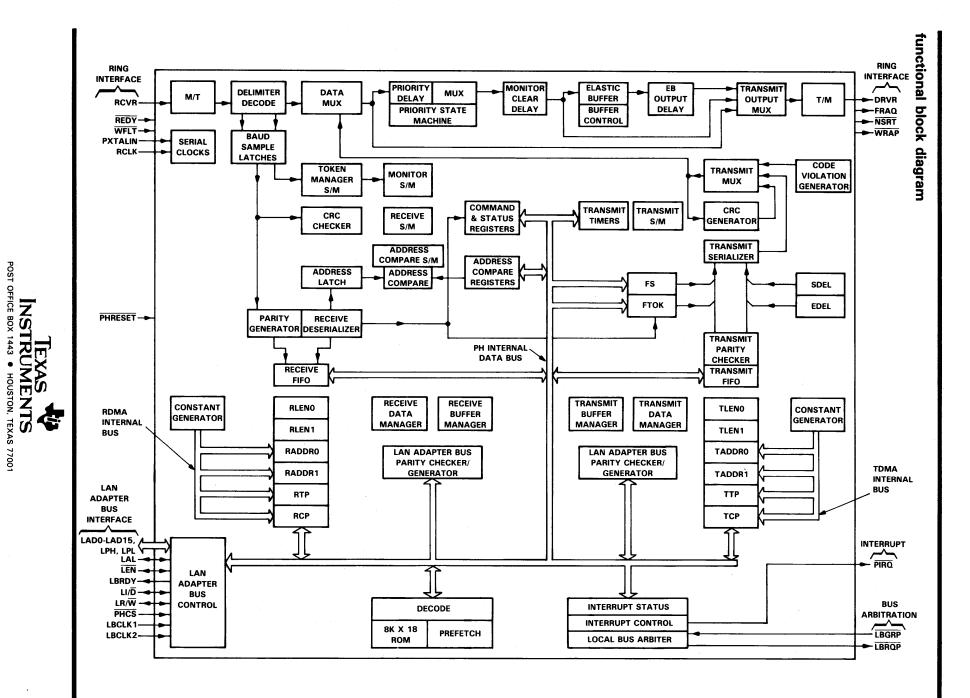

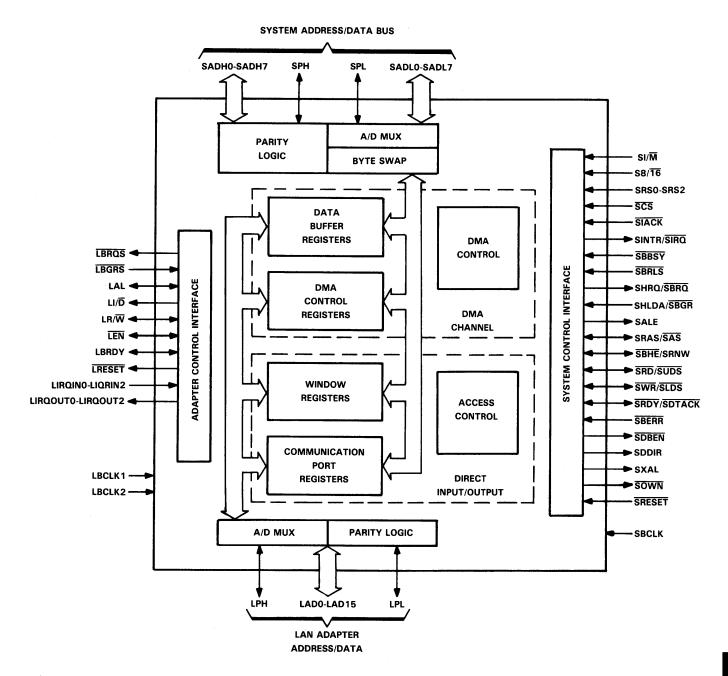

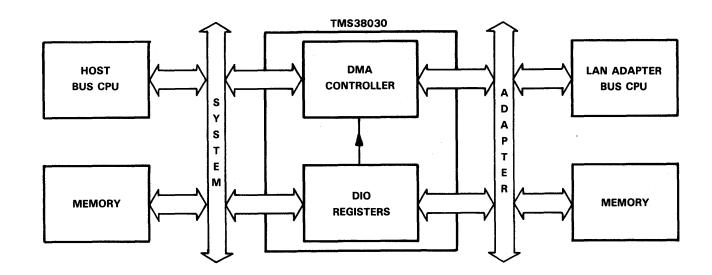

The TMS380 architecture integrates the functions of a LAN adapter into a five-chip set. The components of the chipset are the TMS38030 System Interface chip, the TMS38010 Communications Processor chip, the TMS38020 Protocol Handler chip, and the TMS38051 and TMS38052 Ring Interface chip pair.

#### 1.6.1 The System Interface

The TMS38030 System Interface (SIF) chip provides up to 40 megabits per second of data to the host system via DMA bus master transfers. The host system bus interface is selectable for two types of memory organization and control signals:

- 8-, 16-, and 32-bit members of the iAPX86 and Series 32000 microprocesor families

- 16- and 32-bit members of the 68000 microprocesor family

The System Interface is controlled through command blocks with a high-level command structure; for example, commands include TRANSMIT, RECEIVE, and READ ERROR LOG. (Additional details on SIF commands are provided with the examples in "Transmitting and Receiving a Frame.") The System Interface has a 24-bit address reach into the host system and a "scatter write-gather read" DMA feature that allows discontiguous memory blocks to be transferred and received via linked lists. Programmable burst transfers or cycle-steal operation and optional parity protection allow system designers to customize the TMS38030 to their particular bus.

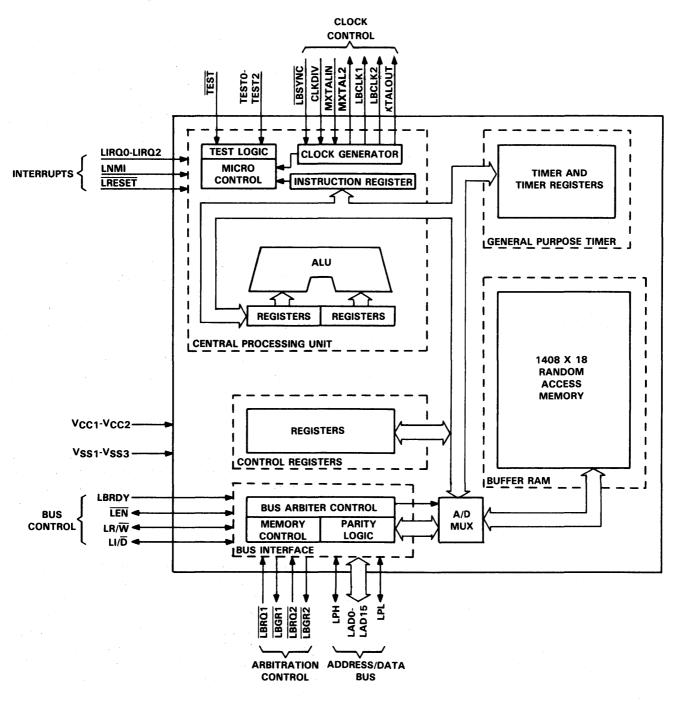

#### **1.6.2 The Communications Processor**

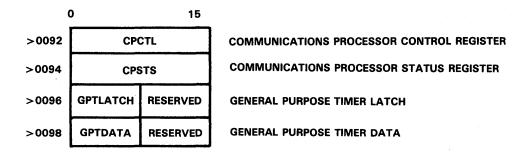

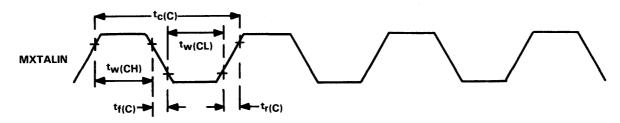

The TMS38010 Communications Processor (CP) contains dedicated 16-bit CPU with 2.75K bytes of on-chip RAM. The Communications Processor executes the adapter software contained within the TMS38020. The on-chip RAM buffers the frames being transmitted and received. This high-performance CPU provides single-cycle arbitration of the 3 MHz LAN adapter bus for maximum adapter throughput. Up to 42K of expansion memory can be added to the LAN adapter bus. All on-chip RAM and expansion memory is parity protected.

#### **1.6.3 The Protocol Handler**

The TMS38020 Protocol Handler (PH) performs hardware-based protocol functions for a 4-megabit per second token ring LAN compatible with the IEEE 802.5 standard. An on-chip ROM contains 16K bytes of adapter software executed by the Communications Processor. This software supports reliable ring operation, LAN management services, and thorough diagnostic coverage of the adapter chipset.

The Protocol Handler implements differential Manchester encoding and decoding and frame-address recognition (group, specific, and functional). The Protocol Handler also contains state machines that capture tokens, transmit and receive frames, manage the adapter chipset buffer RAM, and provide token-priority controls.

Four DMA channels, two for transmit and two for receive, ensure high-speed frame transfer between the ring and the adapter's buffer RAM. Integrity of transmitted and received data is assured by cyclic redundancy checks (CRC), detection of differential Manchester code violations, and parity on internal data paths. All data paths and registers are parity-protected to assure functional integrity.

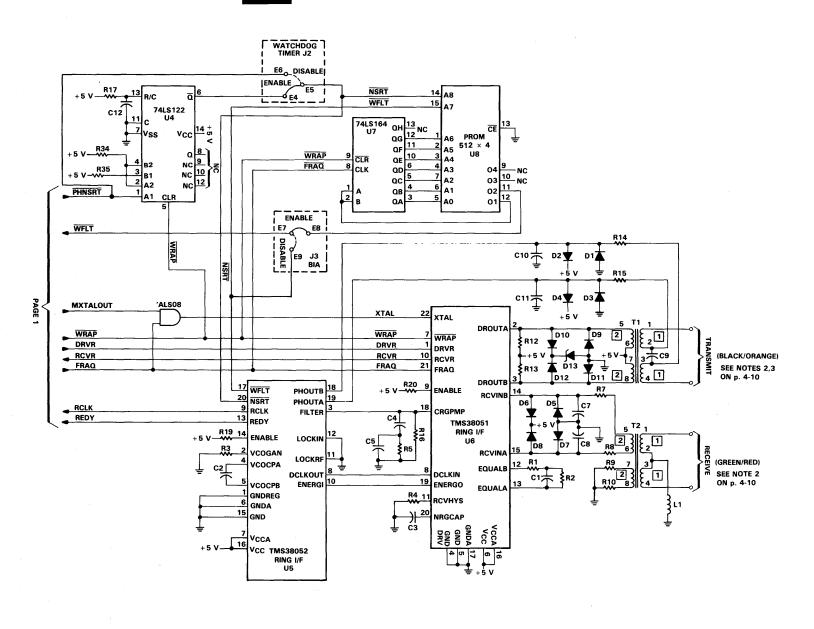

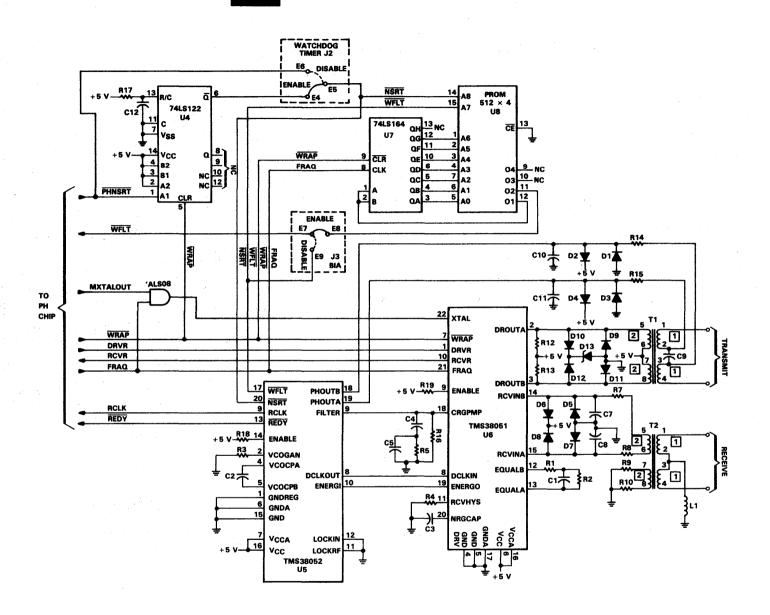

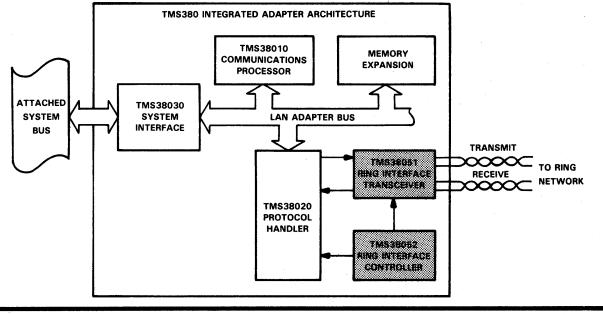

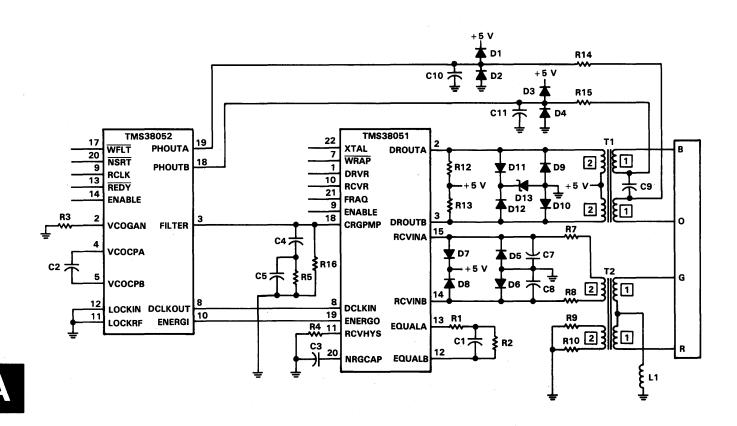

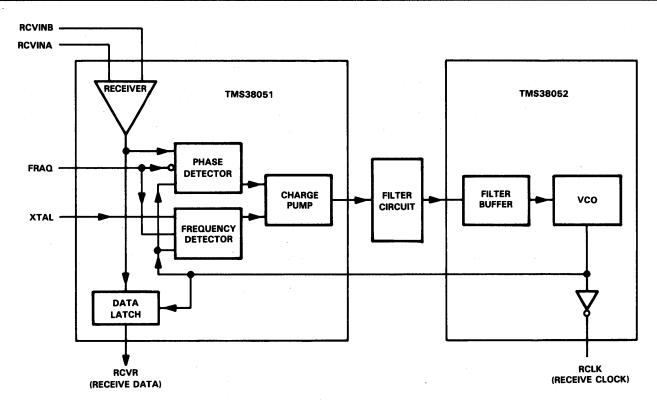

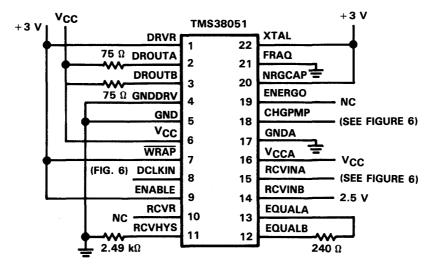

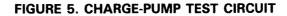

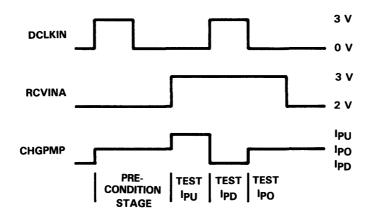

#### **1.6.4 The Ring Interface**

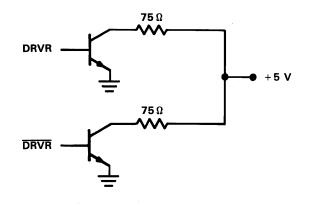

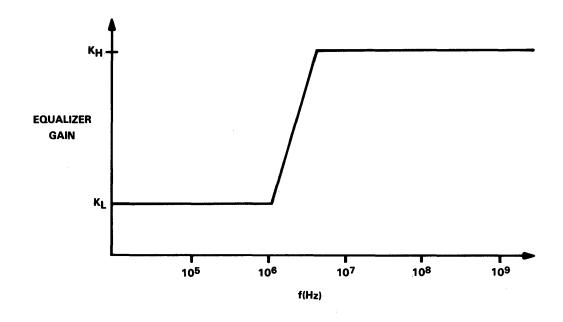

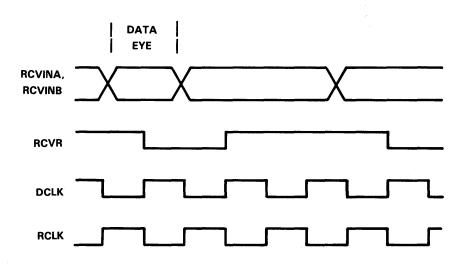

The TMS38051 and TMS38052, collectively the Ring Interface, are the Ring Interface Transceiver and Ring Interface Controller. These chips contain the digital and analog circuitry to connect the adapter chipset to a 4-megabit per second token ring LAN through separate receive and transmit channels.

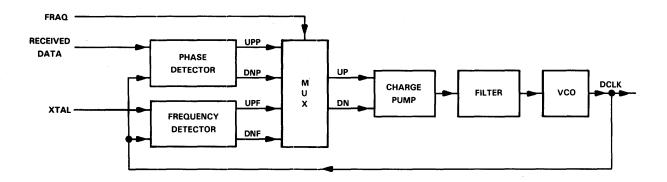

The Ring Interface provides the clock for the ring when in active monitor mode and contains a phase lock loop for clock recovery, data detection, and phase alignment. The Ring Interface also provides the phantom drive signal to a wiring concentrator, a loop-back path for diagnostic testing, and error detection of wire faults.

#### **1.7 Network Reliability**

Day-to-day LAN operation requires a high degree of reliability. The TMS380 chipset meets this requirement with self-test diagnostics that exercise each adapter card before permitting the card to insert into the ring, and by ensuring that all adapters on the network work together to isolate and recover from problems automatically.

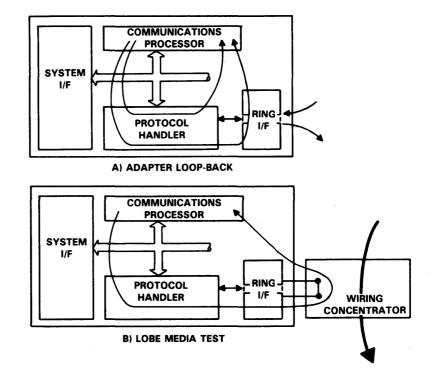

The TMS380 adapter chipset has designed-in hardware and software features to insure a reliable LAN. Prior to inserting into the LAN, the TMS380 adapter chipset performs a self-test by running diagnostics and a lobe media test. The software to perform these tests is contained within the Protocol Handler's ROM.

The diagnostic software, in conjunction with parity protection, address path checkers, and loop-back testing, verifies operation of the adapter chipset. The lobe media test checks the CRC circuitry and tests the entire lobe from the adapter to the wiring concentrator. This ensures that a faulty adapter card or an attaching product with a bad lobe will not be allowed to insert into the LAN and disrupt its operation. The illustration below shows how the attaching product performs self-testing of its adapter prior to insertion onto the LAN.

FIGURE 1-10. ADAPTER SELF-TEST

If the adapter chipset detects an error after inserting into the LAN, the adapter chipset immediately de-inserts, allowing the LAN to continue reliable operation. The adapter chipset that detects the error reruns the self-test diagnostics, re-inserts if the test passes, or stays de-inserted and signals the host system if the error condition persists.

The TMS380 adapter chipset also has the capability to allow the LAN to recover from soft errors and hard errors with minimal disruption to service. Soft errors, such as corrupted or lost tokens, are automatically handled by the adapter chipsets on the LAN. The adapter chipset that detects the error logs the condition and the LAN automatically recovers. The error condition and location is then reported to the host system and a network manager. Hard errors, such as a wire fault on the lobe or a bad receiver/transmitter on the adapter card, are also automatically isolated and resolved by the adapters on the LAN. These isolation and recovery processes are performed by the adapter chipset independent of the host system.

#### **1.8 LAN Management Services**

The TMS380 adapter chipset contains a wealth of LAN management services to build and manage reliable networks. These services are embedded in the chipset and operate independently of the attaching product.

The availability of a standard set of services enables vendors to build network management products that will operate with products independently developed by other manufacturers. Because these services are embedded in the adapter chipset, end users can confidently expand the network as requirements grow, without affecting the installed products.

The TMS380 LAN management services are provided by MAC frames that are exchanged between adapters on the ring. MAC frames are special frames that are used to control the operation of the ring; they do not transfer data.

The IEEE 802.5 standard defines six MAC frames that are used for basic ring operation. In addition to these six basic MAC frames, the TMS380 also contains MAC frames that are used with specified functional addresses on the LAN. There are over 20 MAC frames used to collect error reports automatically generated by adapter chipsets, monitor and modify the configuration of the LAN, and assign operating parameters to attached products.

The MAC frames processed by the TMS380 adapter chipset are listed below.

Response Beacon Ring Purge Standby Monitor Present Lobe Media Test Change Parameters Request Station Adress Request Station Attachment Request Initialization Report Station State Report Station Attachment Report SUA Change Report Monitor Error Claim Token Active Monitor Present Duplicate Address Test Transmit Forward Remove Ring Station Initialize Ring Station Request Station State Report Transmit Forward Report Station Address Report New Monitor Report Ring Poll Failure Report Error

#### **1.9 Performance Features**

LAN performance, as measured in user response time, is dependent on three factors: the physical data transfer rate and delays caused by the access protocols, the movement of data from the physical medium to the host system, and the efficiency of the host-based protocol software. The TMS380 adapter chipset provides features in all three of these areas.

The token-passing access protocol, operating at a 4-megabit per second data rate, results in a high-speed LAN that remains efficient and stable even during periods of high demand. The deterministic nature of a token-passing ring, whereby each node transmits only when it has the token, eliminates the performance uncertainties of collision-based LANs. The TMS380 chipset maximizes efficient use of the 4-megabit per second data rate by minimizing the delay a node imposes on the circulating token or frame. The TMS380 imposes a mere 2.5 bit time delay per node.

The adapter presents a full-duplex interface to the host system with separate receive and transmit channels between the adapter and the LAN. The adapter hardware has been designed to handle reception of back-to-back frames on the LAN and to allow simultaneous reception and tansmission of data at the full ring data rate.

The adapter chipset has separate receive and transmit lines to the LAN, two separate pairs of DMA channels in the TMS38020 Protocol Handler for both receive and transmit, and a 48-megabit per second LAN adapter bus with single-cycle arbitration for internal adapter transfers. A 40-megabit per second DMA controller connects the LAN adapter bus to the host system bus.

Host system protocol efficiency is improved with the TMS380 LAN adapter chipset. The chipset offers the designer configurable options such as cycle-steal programmableburst mode operation, a linked-list interface controlled by high-level commands, polled or interrupt operation, and list-suspension capability to allow the host system to interrogate portions of an incoming frame. The adapter chipset can also "scatter writegather read" to and from discontiguous memory locations in the host during DMA transfers. Up to three high-level commands (such as TRANSMIT, RECEIVE, and READ ERROR LOG) can be queued simultaneously on the adapter chipset at any time.

The flow of data between host system, the LAN adapter chipset, and the ring is shown below.

FIGURE 1-11. ADAPTER DATA FLOW

#### 1.10 Transmitting and Receiving a Frame

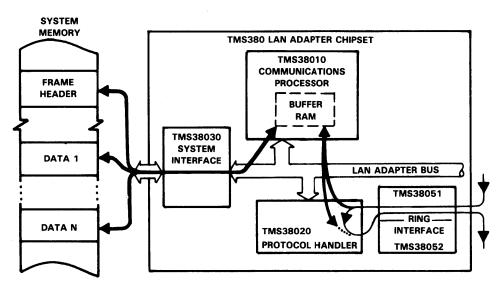

The TMS380 chipset presents a linked-list interface to the host system bus that is controlled by high-level commands.

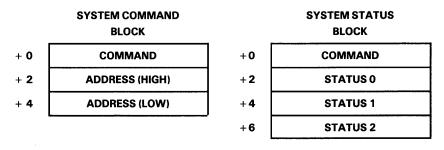

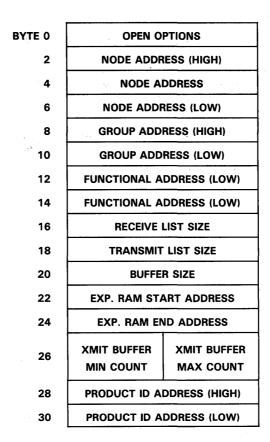

During adapter chipset initialization, a host system configures the adapter interface. The adapter chipset can be initialized to match specific host system bus requirements. Examples of the initialization parameters include: interrupt conditions and frequency, buffer sizes and allocation of these buffers to either transmit or receive channels, expansion memory, and the setting of addresses. Command and status information is passed between the adapter and host system via two control blocks:

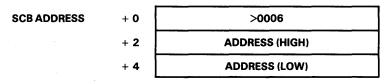

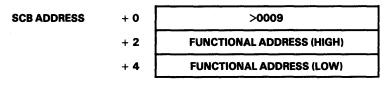

- System Command Block (SCB)

- System Status Block (SSB)

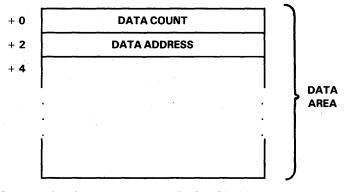

To transmit a frame, the host system first interrupts the adapter chipset. The adapter then DMA reads the System Command Block. The SCB contains the transmit command and the starting address of the transmit list that resides in host system memory. The adapter chipset then transfers the transmit list from the host system to the adapter's buffer RAM using DMA. Next, the adapter transfers the entire frame to the adapter RAM, and the adapter chipset captures a token and transmits the frame onto the LAN. The frame will circulate to the destination address, which copies the data and returns the frame to circulate on the LAN. When the frame returns to the originating adapter chipset, it is stripped and a token is released. The System Status Block is updated by the adapter and transferred to the host system.

This procedure is illustrated on the following page.

FIGURE 1-12. TRANSMITTING A FRAME

A frame is received in a manner similar to the way it is transmitted. An SCB is issued to the adapter pointing to the receive list in host system memory. Upon reception of a frame, the adapter will transfer the receive list from the host system to the adapter RAM and then transfer the received data to the appropriate location in host system memory. The SSB is then updated.

#### 1.11 Package Type and Power Dissipation

The package type and power dissipation of the five chips are shown below.

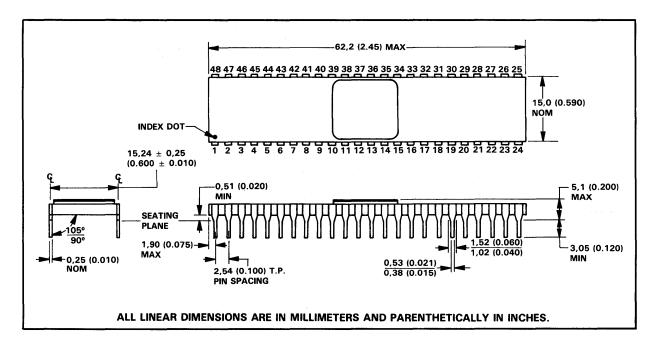

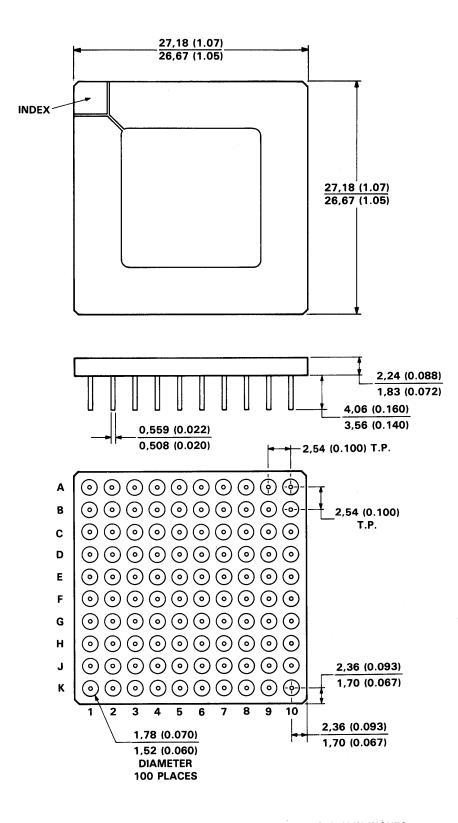

| DEVICE                              | PACKAGE TYPE | POWER DISSIPATION |

|-------------------------------------|--------------|-------------------|

| TMS38010 Communications Processor   | 48-pin DIP   | 750 mW            |

| TMS38020 Protocol Handler           | 48-pin DIP   | 550 mW            |

| TMS38030 System Interface           | 100-pin PGA  | 950 mW            |

| TMS38051 Ring Interface Transceiver | 22-pin DIP   | 350 mW            |

| TMS38052 Ring Interface Controller  | 20-pin DIP   | 250 mW            |

#### 1.12 TMS380 User's Guide Organization

This User's Guide provides information about the TMS380 LAN adapter chipset for hardware and software engineers, network planners and architects. The hardware engineer will find the Application Examples in section 2, portions of Adapter Design in section 4, and the Data Sheets in Appendix A particularly useful. Software engineers should focus on Communications Services in section 3, portions of Adapter Design in section 4, and the Appendices. The network planner and architects should review portions of the entire User's Guide.

- Section 2. Application Examples: This section contains examples of adapter card designs using the TMS380 adapter chipset. Design examples include an adapter card for IBM PC family (8 bit), a PC AT card, and 680XX-family interface example.

- Section 3. Communications Services: This section describes the architecture, operation and services provided by the TMS380 adapter chipset as it relates to the Physical and Medium Access Control (MAC) layers, network management and security services, and error reporting.

- Section 4. Adapter Design: This section describes the hardware and software interface as viewed from the host system, the ring interface, and the LAN adapter bus.

- Section 5. Appendices: Appendix A contains data sheets on all the chips. Appendix B.1 contains a summary of the Medium Access Control (MAC) frames. Appendix B.2 illustrates a technique for implementing a 'burned in' address. Appendix B.3 contains ordering information and package mechanical data, followed by a Glossary of Terms in Appendix B.4.

Introduction

**Application Examples**

Adapter Communications Services

3

2

Adapter Design 4

Appendix A - Data Sheets

Appendix B - General

B

i

# 2. APPLICATION EXAMPLES

#### 2.1 Introduction

This section provides application examples that demonstrate how the TMS380 LAN Adapter chipset attaches to different host system buses with various data movement methods. The TMS380 Adapter chipset attaches to a host system bus through the TMS38030 System Interface chip (SIF). The TMS38030 provides the designer with a high performance, user configurable interface that minimizes logic between the TMS380 Adapter chipset and the host system bus.

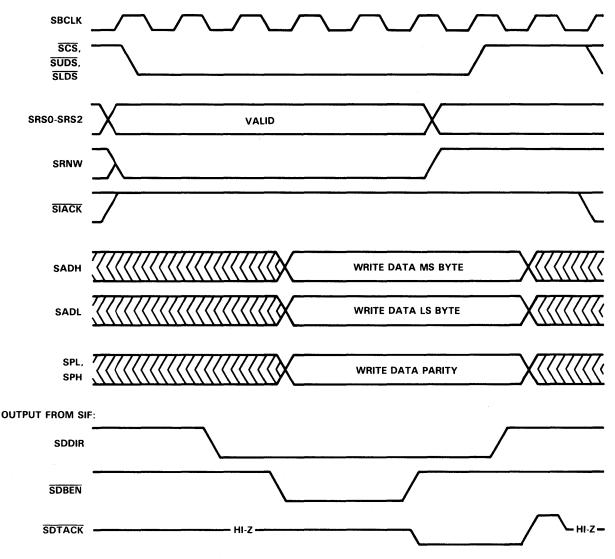

This section includes four application examples that show the TMS380 interface to both iAPX-86 and 68000-style buses. In both interfaces, the TMS38030 automatically comprehends the different memory orientations and reduces byte swapping overhead on the attaching product. These examples describe data movement methods including input/output register moves under host processor control, a shared memory interface, and direct memory access whereby the TMS380 is a powerful DMA controller that provides up to a 40 megabit-per-second data transfer rate to the attaching product. Additional details on the TMS38030, the hardware interface, and the software interface can be found in Section 4, Adapter Design, and in the TMS38030 data sheet.

The four application examples are:

- 2.2. An interface to the 8-bit PC bus that uses data moves through the I/O space of the PC.

- 2.3. An interface to the 8-bit PC bus that uses string moves through a memory mapped register.

- 2.4. An interface to the 16-bit PC AT bus that uses DMA data moves from the TMS38030.

- 2.5. An interface to a 16-bit 68000-style microprocessor that uses DMA data moves from the TMS38030.

#### 2.2 PC Family LAN Adapter Card: I/O Mapped Design Example

This example describes a TMS380-based LAN adapter card that interfaces to the 8-bit expansion slot of the IBM PC family and compatibles. This example demonstrates an interface design that allows a PC-executed software loop to transfer data to and from the LAN adapter card via the PC's I/O address space. The average data rate across this interface is 496k bits-per-second for the PC and PC/XT and 1.184 megabits-per-second for the PC AT.

#### 2.2.1 Theory of Operation

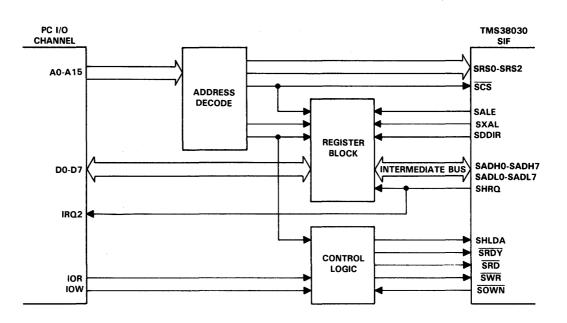

Since the TMS38030 System Interface (SIF) requires control of the host system bus for data transfers (DMA operation), this application uses an external register block containing data and address registers, address decode, and control logic to connect the PC I/O channel to the TMS38030. This block diagram is shown in Figure 2-1.

#### **APPLICATION EXAMPLES**

#### FIGURE 2-1. I/O MAPPED DESIGN BLOCK DIAGRAM

Data transfer between the PC and the LAN adapter card is a two-step process. The first step involves the transfer of a data byte to an external data register. During a data transfer from the Adapter to the PC, the TMS38030 writes data to this external register. During a data transfer from the PC to the Adapter, the PC writes data to the external register.

The second step involves reading the external data register by either the PC or the Adapter, depending on the direction of the transfer.

This two-step approach allows the PC to control its system bus while the TMS38030 controls an intermediate bus connected to the register block.

#### 2.2.1.1 Register Block

The register block provides five external registers accessible to the PC: a data register (DATABUF), a status register (STATBUF), and three registers for holding the 24-bit direct memory access (DMA) address as output by the TMS38030; the extended address byte (HADRBUF), the address middle byte (MADRBUF), and the address low byte (LADRBUF).

The data register (DATABUF) is the external holding register used for PC-to-Adapter and Adapter-to-PC data transfers. This register may be read or written by either the TMS38030 or the PC.

The Status Register (STATBUF), when read by the PC, provides the logic state of the TMS38030's SDDIR (data direction), SHRQ (hold request), and SINTR (interrupt request) output pins. SDDIR is used by the PC to determine the direction of the data transfer. SHRQ is used by the PC to determine when a data transfer is completed.

The Address Registers are latched with DMA address information during DMA operations by the TMS38030's SXAL (extended address latch) and SALE (address latch enable) signals. These registers allow the PC to acquire the starting address for the data transfer to or from the PC memory space. Since TMS38030 DMA operations are always to sequential system memory locations, these registers need only to be read once by the PC for every DMA event initiated.

#### 2.2.1.2 Address Decode Block

The decode block in Figure 2-1 decodes the I/O address from the PC I/O channel and determines whether an external register is addressed or whether an internal TMS38030 DIO register is addressed. If a register within the register block is addressed, the appropriate enable signal is activated. The output of the address decode block is also presented to the control logic block, as shown in Figure 2-1.

#### 2.2.1.3 Control Logic Block

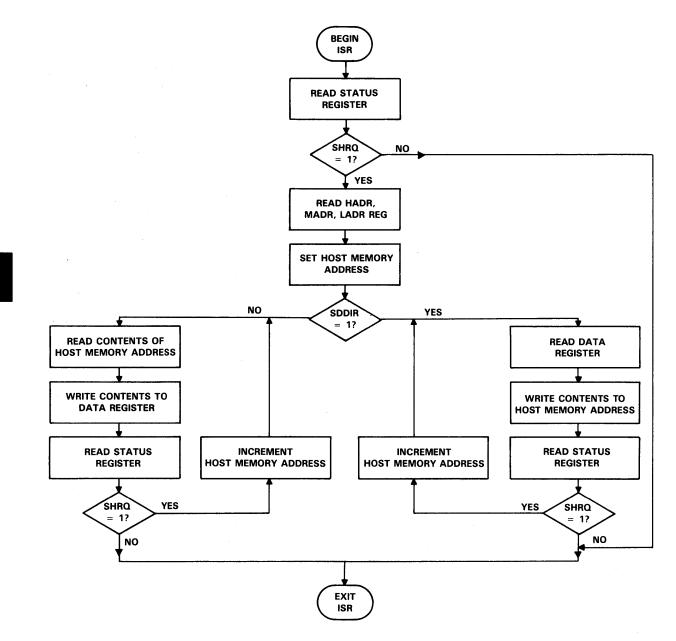

When the TMS38030 begins a DMA transfer, the TMS38030 first takes signal SHRQ (hold request) active. This signal is fed into the PC's IRQ2 (interrupt request) input. This causes the PC to be interrupted, and execution of an interrupt service routine begins. A flow chart of the interrupt service routine is shown in Figure 2-2.

#### **APPLICATION EXAMPLES**

FIGURE 2-2. INTERRUPT SERVICE ROUTINE FLOWCHART - I/O MAPPED EXAMPLE

The PC first reads the contents of STATBUF to determine the direction of transfer and the status of the SHRQ signal. If SHRQ is not high, the interrupt service routine is terminated. By reading STATBUF when SHRQ is active, the PC causes the control logic to assert SHLDA (hold acknowledge) and deassert SRDY (ready). The TMS38030 will take control of the intermediate bus and latch the 24-bit DMA address into the three address registers. However, since SRDY is deasserted, the TMS38030 will remain in a wait state until the PC completes a read or write operation on an external register.

At this point, the PC reads the three address registers and initializes the software loop with the starting address of the transfer.

The direction of the transfer is determined by the state of the SDDIR signal read from STATBUF. If SDDIR is zero, a DMA read operation (PC-to-Adapter) is denoted. If SDDIR is one, a DMA write operation (Adapter-to-PC) is denoted.

After determining the direction of transfer, the PC either moves the data byte from DATABUF to system memory (DMA write) or moves the next byte from system memory to DATABUF (DMA read).

The PC must examine SHRQ in STATBUF following each transfer to determine if the data transfer is complete. If SHRQ is found to be inactive, the data transfer is complete and the interrupt service routine is terminated; otherwise, the address pointer, which points to the next location to be read or written, is incremented and the software loop continues.

The SRDY signal to the TMS38030 is used to control the TMS38030's access to the intermediate bus. In this way the TMS38030 is 'throttled': data flow to and from the TMS38030 is controlled by the PC's software loop within the Interrupt Service Routine. For DIO access to the internal registers of the TMS38030, the control logic block (shown in Figure 2-1) is responsible for control of SRDY as well as the TMS38030's SHLDA and SRD (read enable) and SWR (write enable) signals.

#### 2.3 PC Family LAN Adapter Card: Memory-Mapped Example

This example of a TMS380-based LAN adapter card for the IBM PC family is similar in design approach to the example in Section 2.2. However, this example features a register mapped into the memory map of the PC allowing the string move instruction of the PC CPU to be used in lieu of the input/output instructions. The efficiency gained in using the string move instruction within the interrupt service routine allows the average data rate through the PC I/O channel to be increased to 2.8 megabits-per-second for the PC and PC/XT and 6 megabits-per-second for the PC AT.

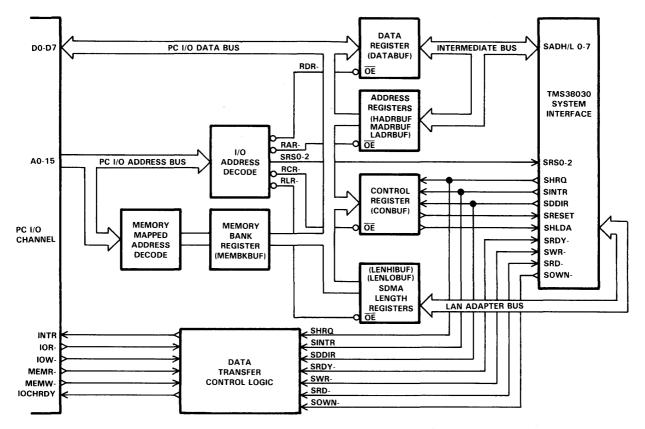

#### 2.3.1 Theory of Operation

To use the string move instruction of the PC CPU, it is necessary to know the length of the string to be moved. In this example, the string length is equal to the length of the direct memory access (DMA) as requested by the TMS38030. Information regarding the length of a DMA transfer is not available from the host bus side of the TMS38030 System Interface but is available on the LAN Adapter bus. Thus, additional hardware can provide the PC CPU the length of a DMA transfer (when the TMS38030 takes SHRQ active-high).

#### **APPLICATION EXAMPLES**

#### 2.3.1.1 DMA Length Register

The length of DMA transfers is provided to the host bus by mapping the TMS38030's SDMALEN (System DMA Length) register, on the LAN Adapter bus, to a read-only register accessible to the PC CPU. This register is shown in the block diagram in Figure 2-3.

FIGURE 2-3. MEMORY MAPPED DESIGN BLOCK DIAGRAM

When the TMS38030 is initialized for a DMA transfer by the TMS38010 Communications Processor, the SDMALEN register will be loaded with the length of the transfer. This action, the TMS38010 writing to the SDMALEN register, will result in the read-only host bus register also being loaded. Thus, the PC CPU may read the length of the transfer for use by the string move instruction.

#### 2.3.1.2 Memory Mapped Data Register

Like the I/O mapped example provided in Section 2.2, data transfer between the PC and the LAN adapter card is a two-step process. The first step involves the transfer of a data byte to an external data register. During a data transfer from the Adapter to the PC, the TMS38030 writes data to this external register. During a data transfer from the PC to the Adapter, the PC writes data to the external register.

The second step involves reading the external data register by either the PC or the Adapter, depending on the direction of the transfer.

This data register is mapped into the memory map of the PC so that a string move instruction may be used. This differs from the I/O mapped design example which described the data register residing in the I/O map of the PC. Using a string move instruction in lieu of input and output instructions reduces the number of bus cycles required to move a block of data thus increasing the overall bus throughput. This memory-mapped register is shown in Figure 2-3.

#### 2.3.1.3 Other I/O Mapped Registers

The register block mapped into the I/O space of the PC contains eight 8-bit registers including the read-only DMA length registers (LENLOWBUF and LENHIBUF) as previously described. The additional registers include a status/control register (CONBUF/STATBUF), an I/O mapped equivalent to the memory mapped data register (DATABUF), and three registers for holding the 24-bit direct memory access (DMA) address as output by the TMS38030: the extended address byte (HADRBUF), the address middle byte (MADRB'UF), and the address low byte (LADRBUF).

The I/O mapped data register (DATABUF) provides the equivalent of the memory mapped data register mapped into the I/O space of the PC. DATABUF would only be used if memory space was not available for the memory mapped data register. In this event, data transfer would use the I/O instructions of the 8088 as shown in Section 2.2.

The control/status register (CONBUF/STATBUF), when read by the PC, provides the logic state of the TMS38030's SDDIR (data direction), SHRQ (hold request), and SINTR (interrupt request) output pins. SDDIR is used by the PC to determine the direction of the data transfer.

The control/status register (CONBUF/STATBUF) is written by the PC to control the state of SHLDA (hold acknowledge) to the TMS38030. This allows the PC to initiate TMS38030 data transfer to and from the data registers (both I/O and memory mapped). The CONBUF/STATBUF register may also be used to control other functions of the Adapter card like enabling interrupts, controlling address decode circuitry or providing a software reset. The implementation of these functions is not discussed in this example.

#### 2.3.1.4 Address Decode

Address decoding (both I/O and memory) must be done to select the appropriate I/O mapped register or the memory mapped data register. Because the memory mapped data register is accessed using the string move instruction, this register must respond to the number of addresses corresponding to the length of the string. The length of the string corresponds to the length of the DMA operation as contained in the read-only DMA length register. Thus, the memory mapped data register actually occupies more memory locations in the PC than its physical size.

For simplicity, the address decode for the memory mapped data register may be designed to map the data register within an 8K byte boundary in the PC's memory address space. Thus, string moves up through 8K bytes may be used, however, the actual length of string moves can be much smaller.

Care must be exercised to assure that the memory mapped data register occupies a unique 8K byte window in the PC's memory map to avoid PC I/O channel bus conflicts.

#### 2.3.1.5 Interrupt Service Routine

When the TMS38030 begins a DMA transfer, the TMS38030 first takes SHRQ (hold request) active. This signal is fed into one of the PC's IRQ (interrupt request) signals. This causes the PC to be interrupted, and execution of an interrupt service routine is started. A flowchart of this interrupt service routine is shown in Figure 2-4.

NOTE: The string move instruction automatically increments the source and destination addresses for each byte until the CX register is decremented to zero.

## FIGURE 2-4. INTERRUPT SERVICE ROUTINE FLOWCHART – MEMORY MAPPED EXAMPLE

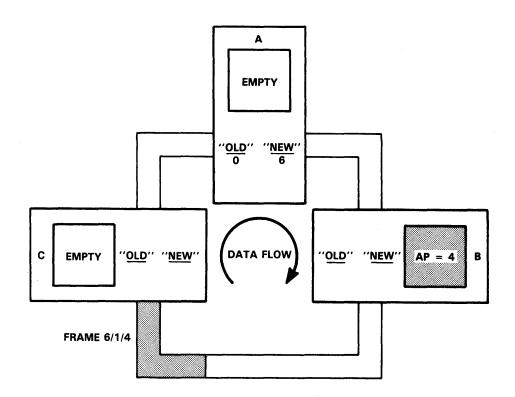

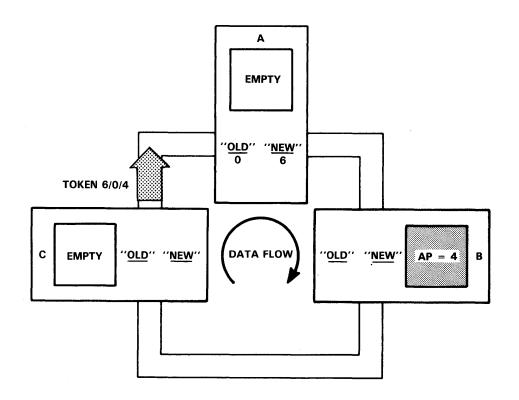

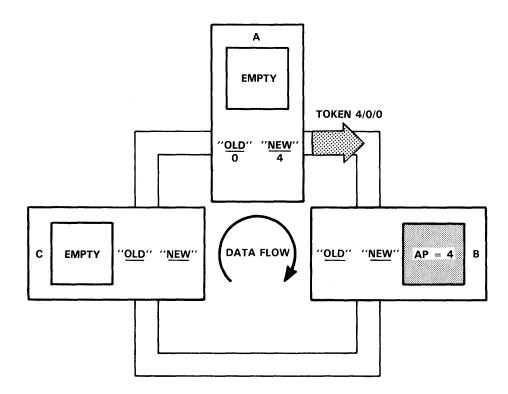

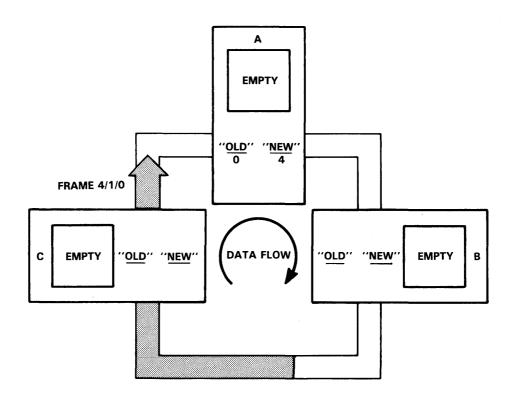

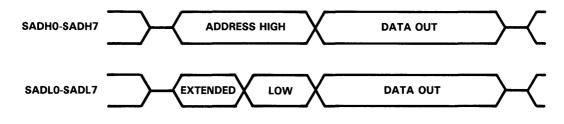

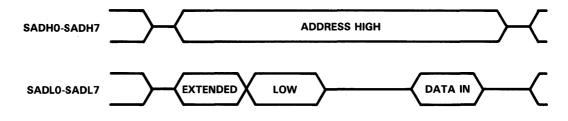

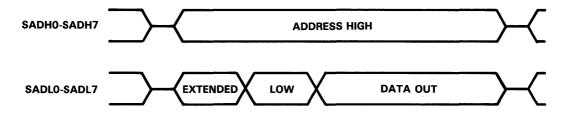

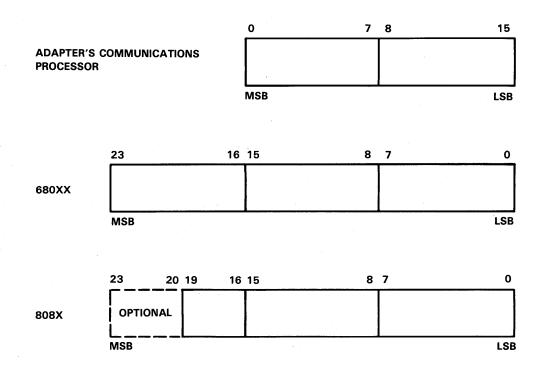

## 2.4 PC AT LAN Adapter Card Example