The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED

Semiconductor Group

# Bipolar Microcomputer Components Data Book

for Design Engineers

**JANUARY 1977**

# TI worldwide sales offices

#### ALABAMA

P.O. Box 2237, 304 Wynn Drive Huntsville, Alabama 35804 205-837-7530

#### ARIZONA

4820 N. Black Canyon Hwy Suite 202 Phoenix, Arizona 85017 602:248:8028

## CALIFORNIA

831 S. Douglass St. El Segundo, California 90245 213-973-2571

Balboa Towers Bidg., Suite 805 5252 Balboa Avenue San Diego, California 92117 714-279-2622

1505 East 17th St., Suite 201 Santa Ana, California 92701 714-835-9031

776 Palomar Avenue Sunnyvale, California 94086 408-732-1840

#### COLORADO

9725 E. Hampden St., Suite 301 Denver, Colorado 80231 303-751-1780

CONNECTICUT

35 Worth Avenue Hamden, Connecticut 06518 203-281-0074

#### ARGENTINA

Texas Instruments Argentina S.A.I C.F

C C Box 2296 Correo Central Buenos Aires, Argentina 748-1141

#### ASIA

Texas Instruments Asia Limited

5F Aoyama Tower Bidg 24-15 Minami Aoyama Chome Minato ku, Tokyo 107, Japan 402-6171

11A-15 Chatham Road First Floor, Kowloon Hong Kong 3-670061

Texas Instruments Singapore (PTE) Ltd 27 Katlang Place Singapore 1, Rep. of Singapore 258-1122

Texas Instruments Taiwan Limited P O. Box 3999 Taipei, Chung Ho, Taiwan 921 623

Texas Instruments Malaysia SDN. BHD. Number 1 Lorong Enggang 33 Kuala Lampur 15-07, Malaysia 647 911

#### AUSTRALIA

Texas Instruments Australia Ltd

Suite 205, 118 Great North Road Five Dock N.S.W. 2046 Australia 831-2555

Box 63, Post Office 171-175 Philip Highway Elizabeth 5112 South Australia 255-2066 FLORIDA

601 W. Oakland Park Blvd. Fort Lauderdale, Florida 33311 305-566-3294

2221 Lee Road, Suite 108 Winter Park, Florida 32789 305-644-3535

GEORGIA

Route 1, Creekwood Pass Dallas, Georgia 30132 404-445-4908

ILLINOIS

1701 Lake Avenue, Suite 300 Glenview, Illinois 60025 312-729-5710

#### INDIANA

3705 Rupp Drive Arch Bidg. Fort Wayne, Indiana 46805 219-484-0606

2346 S. Lynhurst Dr., Suite 101 Indianapolis, Indiana 46241 317-248-8555

#### MASSACHUSETTS

504 Totten Pond Road Waltham, Mass. 02154 617-890-7400

MICHIGAN Central Park Plaza 26211 Central Park Blvd., Suite 215 Southfield, Michigan 48076 313 353.0830

#### BRAZIL

Texas Instrumentos Electronicos do Brasil Ltda.

Riia Joao Annes, 153-Lapa Caixa Postal 30 103, CEP 01.000 Sao Pauto, SP, Brasil 260-2956

#### CANADA

Texas Instruments Incorporated

935 Montee De Liesse St. Laurent H4T 1R2 Quebec, Canada 514-341-3232

5F Caesar Avenue Ottawa 12 Ontario, Canada 613-825-3716

280 Centre Str. East Richmond Hill (Toronto) Ontario, Canada 716-856-4453

#### DENMARK

Texas Instruments Denmark

46D, Marielundvej 2730 Herlev, Denmark (01) 91 74 00

#### FINLAND

Texas Instruments Finland OY

Fredrikinkatu 75, A7 Helsinki 10, Finland 44 71 71 MINNESOTA

A.I.C. Bidg., Suite 202 7615 Metro Bivd. Edina, Minn. 55435 612:835:2900

NEW JERSEY

1245 Westfield Ave. Clark, New Jersey 07066 201-574-9800

NEW MEXICO

1101 Cardenas Drive, N.E., Room 215 Albuquerque, New Mexico 87110 505-265-8491

NEW YORK

144 Metro Pk. Rochester, New York 14623 716-461-1800

6700 Old Collamer Rd. East Syracuse, New York 13057 315:463:9291

P.O. Box 618, 112 Nanticoke Ave. Endicott, New York 13760 607-785-9987

167 Main Street Fishkill, New York 12524 914-896-6793

2 Huntington Quadrangle, Suite 2N04 Huntington Station, New York 11746 516:293:2560

NORTH CAROLINA

3631 Westfield High Point, N.C. 27260 919 869-3651

#### FRANCE

Texas Instruments France

Boite Postale 5 06 Villeneuve-Loubet, France 31 03 64

La Boursidiere, Bloc A R.N. 186, 92350 Le Plessis Robinson 630.23.43

30-31 Quai Rambaud 69 Lyon, France 42 78 50

#### GERMANY

Texas Instruments Deutschland GmbH

Haggerty Str. 1 8050 Freising, Germany 08161/80-1

Frankfurter Ring 243 8000 Munich 40, Germany 089/325011-15

Lazarettstrasse, 19 4300 Essen, Germany 02141/20916

Krugerstrasse 24 1000 Berlin 49, Germany 0311/74 44 041

Akazienstrasse 22-26 6230 Frankfurt-Griesheim Germany 0611/39 90 61

Steimbker Hof 8A 3000 Hannover, Germany 0511/55 60 41

Krefelderstrasse 11-15 7000 Stuttgart 50, Germany 0711/54 70 01

#### оню

28790 Chagrin Blvd., Suite 120 Cleveland, Ohio 44122 216-464-2990

Hawley Bldg., Suite 101 4140 Linden Avenue Dayton, Ohio 45432 513-253-3121

OREGON

10700 S.W. Beaverton Hwy., Suite 111 Beaverton, Oregon 97005 503-643-1182

PENNSYLVANIA

275 Cominerce Drive Fort Washington, Pa. 19034 215-643-6450

TEXAS

Headquarters -- Gen. Offices Dallas, Texas 75222 214-238-2011

MS366 P.O. Box 5012 Dallas, Texas 75222 214-238-6805

3939 Ann Arbor Houston, Texas 77042 713-785-6906

VIRGINIA

8512 Trabue Road Richmond, Virginia 23235 804-320-3830

WASHINGTON

700 112th N.E., Suite 101 Bellevue, Washington 98004 206-455-3480

WASHINGTON, D.C.

1500 Wilson Blvd., Suite 1100 Arlington, Virginia 22209 703-525-0336

ITALY Texas Instruments Italia SpA

> Via Della Grustizia 9 20125 Milan, Italy 02-688 31 41

> Via L. Mancinella 65 00199 Roma, Italy 06:83 77 45

> Via Montebello 27 10124 Torino, Italy 011-83 22 76

MEXICO

Texas Instruments de Mexico S.A.

Poniente 116 ≠489 Col. Industrial Vallejo Mexico City, D.F., Mexico 567-92-00

NETHERLANDS

Texas Instruments Holland N.V.

Entrepot Gebouw-Kamer 225 P.O. Box 7603

Schiphol-Centrum 020-17 36 36

NORWAY Texas Instruments Norway A/S Sentrumskontorene Brugaten 1 Oslo 1, Norway 33 18 80

SWEDEN

Texas Instruments Sweden AB

S-104 40 Stockholm 14

Skeppargatan 26 67 98 35

UNITED KINGDOM

Texas Instruments Limited

Manton Lane Bedford, England 0234-67466

# Bipolar Microcomputer Components Data Book

# for Design Engineers

**First Edition**

Printed in U.S.A.

LCC-4270

# **IMPORTANT NOTICES**

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

Copyright © 1977 Texas Instruments Incorporated

# BIPOLAR MICROCOMPUTER COMPONENTS DATA BOOK

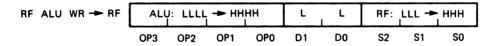

This data book describes a series of high complexity bipolar digital building blocks designed specifically for implementing high performance computer or controller systems. The series offers a system designer the maximum flexibility for achieving cost-effective hardware designs from dedicated, highly specialized unique systems with tailored instructions to general-purpose computers capable of emulating existing machine instructions, or programs, without loss of software investment.

In addition to a choice between the high-performance Schottky<sup>†</sup> TTL 4-bit slice processor element, the unique performance flexibility of an I<sup>2</sup>L 4-bit slice processor element, or a 16-bit computer central processing unit (CPU), the system designer can pick from a full family of Schottky TTL memories (RAMs, PROMs and ROMs), and state-of-the-art support functions needed to meet all control and interface requirements.

The SN54S/74S481, with a clock cycle time of 100 ns, is the industry's highest complexity Schottky TTL processor element, and the only bipolar micro/macroprogrammable element featuring automatically sequenced iterative multiply and divide and cyclical-redundancy algorithms.

The SBP0400A and the SBP0401A, integrated injection logic ( $I^2L$ ) bit slices with complete TTL/MOS compatibility, can operate at a constant speed-power product over a wide range of supply current therein offering an unmatched level of performance flexibility.

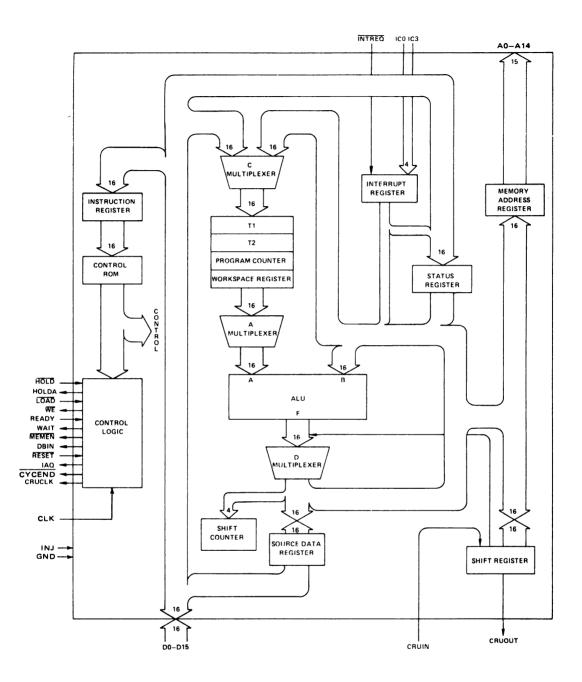

The SBP9900 microprocessor, a ruggedized monolithic parallel 16-bit (I<sup>2</sup>L) central processing unit (CPU), combines an advanced memory-to-memory architecture, a powerful minicomputer instruction set, user-programmable speed/power performance with the simplicity of a single power supply and static logic with a single phase clock to thrust its capabilities beyond those of existing microprocessors.

The family of high-performance Schottky TTL memories offers a wide variety of organizations providing efficient solutions for virtually any size microcontrol or program memory.

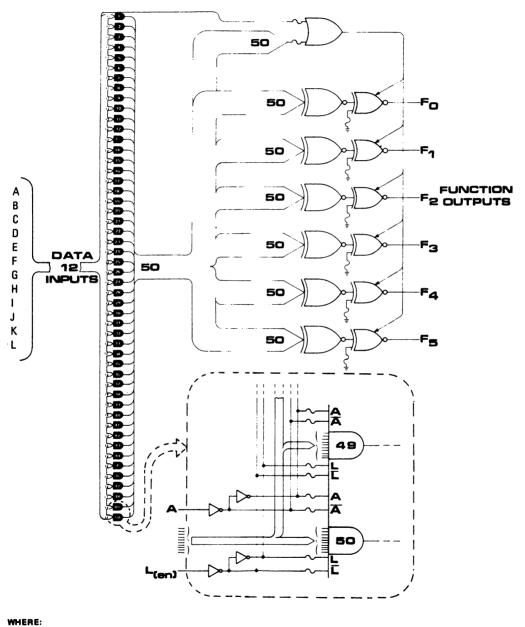

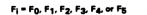

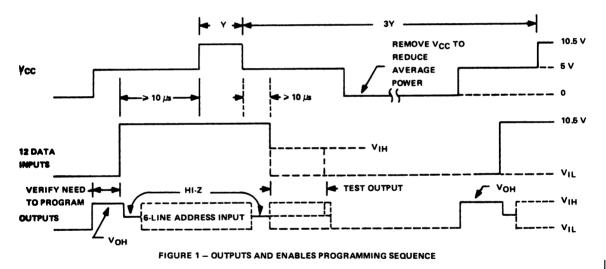

System control is simplified to a very low package count with the expandable SN54S/74S482 4-bit slice controller performing next-address generation functions coupled with system status decoding performed by the industry's most versatile field-programmable logic arrays, the SN54S/74S330/'S331.

A number of advanced high-complexity I/O and interface circuits have been added to the series. Most of these I/O and interface functions as well as a number of the other processor support functions are offered in space saving 20-pin packages which reduce package count and enhance system density.

Although this volume offers design and specification data only for bipolar computer components, complete technical data for any TI semiconductor/component product are available from your nearest TI field sales office, local authorized TI distributor, or by writing direct to: Marketing and Information Services, Texas Instruments Incorporated, P. O. Box 5012, MS 308, Dallas, Texas 75222.

We sincerely hope you will find the Bipolar Microcomputer Components Data Book a meaningful addition to your technical library.

<sup>†</sup>Integrated Schottky-Barrier diodeclamped transistor is patented by Texas Instruments. U. S. Patent Number 3,463,975.

TEXAS INSTRUMENTS

NOTICE

Some products described in this document are in the developmental stage, and Texas Instruments reserves the right to change these specifications in any manner, without notice.

v

# NUMERICAL INDEX

| TYPE NU    | JMBERS     | SECTION | PAGE | TYPE N     | UMBERS     | SECTION | PAGE |

|------------|------------|---------|------|------------|------------|---------|------|

| SBP0400A   |            | 2       | 1    | SN54S299   | SN74S299   | 5       | 9    |

| SBP0401A   |            | 2       | 1    | SN54LS300A | SN74LS300A | 4       | 19   |

| SBP9900    |            | 3       | 1    | SN54S300A  | SN74S300A  | 4       | 19   |

| SN5488A    | SN7488A    | 4       | 7    | SN54S301   | SN74S301   | t       |      |

| SN54186    | SN74186    | t       |      | SN54LS302  | SN74LS302  | 4       | 19   |

| SN54187    | SN74187    | 4       | 7    | SN54LS314  | SN74LS314  | 4       | 25   |

| SN54S188   | SN74S188   | 4       | 1    |            | SN74S314A  | 4       | 25   |

| SN54S189   | SN74S189   | 4       | 15   | SN54S314   | SN74S314   | 4       | 25   |

| SN54LS200A | SN74LS200A | 4       | 19   | SN54LS315  | SN74LS315  | 4       | 25   |

| SN54S200A  | SN74S200A  | 4       | 19   | SN54S330   | SN74S330   | 5       | 13   |

| SN54S201   | SN74S201   | t       |      | SN54S331   | SN74S331   | 5       | 13   |

| SN54LS202  | SN74LS202  | 4       | 19   | SN54S370   | SN74S370   | 4       | 7    |

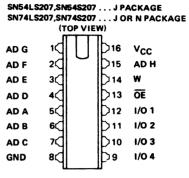

| SN54LS207  | SN74LS207  | 4       | 31   | SN54S371   | SN74S371   | 4       | 7    |

| SN54S207   | SN74S207   | 4       | 31   | SN54S373   | SN74S373   | 5       | 26   |

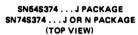

| SN54LS208  | SN74LS208  | 4       | 31   | SN54S374   | SN74S374   | 5       | 26   |

| SN54S208   | SN74S208   | 4       | 31   | SN54S387   | SN74S387   | 4       | 1    |

| SN54LS214  | SN74LS214  | 4       | 25   | SN54S400   | SN74S400   | 4       | 37   |

|            | SN74S214A  | 4       | 25   | SN54S401   | SN74S401   | 4       | 37   |

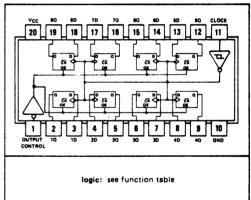

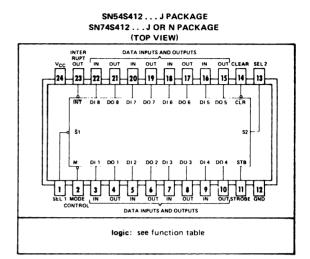

| SN54S214   | SN74S214   | 4       | 25   | SN54S412   | SN74S412   | 5       | 30   |

| SN54LS215  | SN74LS215  | 4       | 25   |            | SN74S428   | 5       | 35   |

| SN54S225   | SN74S225   | 4       | 39   |            | SN74S438   | 5       | 35   |

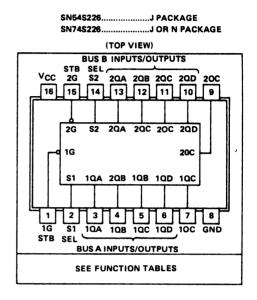

| SN54S226   | SN74S226   | 5       | 1    | SN54S470   | SN74S470   | 4       | 1    |

| SN54S240   | SN74S240   | 5       | 5    | SN54S471   | SN74S471   | 4       | 1    |

| SN54S241   | SN74S241   | 5       | 5    | SN54S472   | SN74S472   | 4       | 1    |

| SN54S270   | SN74S270   | 4       | 7    | SN54S473   | SN74S473   | 4       | 1    |

| SN54S271   | SN74S271   | 4       | 7    | SN54S474   | SN74S474   | 4       | 1    |

| SN54S287   | SN74S287   | 4       | 1    | SN54S475   | SN74S475   | 4       | 1    |

| SN54S288   | SN74S288   | 4       | 1    | SN54S481   | SN74S481   | 1       | 1    |

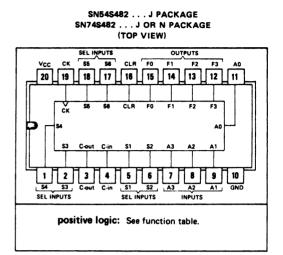

| SN54S289   | SN74S289   | 4       | 15   | SN54S482   | SN74S482   | 5       | 41   |

<sup>†</sup>Not recommended for new designs. For data sheets, see *The Semiconductor Memory Data Book for Design Engineers*. For new designs, refer to section 4 of this manual for TI's advanced Schottky PROM and RAM families.

# GLOSSARY TTL TERMS AND DEFINITIONS

# INTRODUCTION

This glossary consists of two parts: (1) general concepts for digital circuits including types of bipolar memories, and (2) operating conditions and characteristics (including letter symbols). The terms, symbols, abbreviations, and definitions used with memory integrated circuits have not, as yet, been standardized. All are currently under consideration by the EIA/JEDEC (Electronic Industries Association) and the IEC (International Electrotechnical Commission). The following are as consistent with the past and future work of these organizations as is possible to anticipate at this time.

# PART I - GENERAL CONCEPTS INCLUDING TYPES OF BIPOLAR MEMORIES

#### **Chip-Enable Input**

A control input that when active permits operation of the integrated circuit for input, internal transfer, manipulation, refreshing, and/or output of data and when inactive causes the integrated circuit to be in a reduced-power standby mode.

NOTE: See "chip-select input".

#### **Chip-Select Input**

A gating input that when inactive prevents input or output of data to or from an integrated circuit. NOTE: See "chip-enable input".

#### Dynamic (Read/Write) Memory

A read/write memory in which the cells require the repetitive application of control signals in order to retain stored data.

- NOTES: 1. The words "read/write" may be omitted from the term when no misunderstanding will result.

- 2. Such repetitive application of the control signals is normally called a refresh operation.

- 3. A dynamic memory may use static addressing or sensing circuits.

- 4. This definition applies whether the control signals are generated inside or outside the integrated circuit.

# First-In First-Out (FIFO) Memory

A memory from which data bytes or words can be read in the same order, but not necessarily at the same rate, as that of the data entry.

#### **Gate Equivalent Circuit**

A basic unit-of-measure of relative digital-circuit complexity. The number of gate equivalent circuits is that number of individual logic gates that would have to be interconnected to perform the same function.

#### Large-Scale Integration, LSI

A concept whereby a complete major subsystem or system function is fabricated as a single microcircuit. In this context a major subsystem or system, whether digital or linear, is considered to be one that contains 100 or more equivalent gates or circuitry of similar complexity.

#### Mask-Programmed Read-Only Memory

A read-only memory in which the data content of each cell is determined during manufacture by the use of a mask, the data content thereafter being unalterable.

#### Medium-Scale Integration, MSI

A concept whereby a complete subsystem or system function is fabricated as a single microcircuit. The subsystem or system is smaller than for LSI, but whether digital or linear, is considered to be one that contains 12 or more equivalent gates or circuitry of similar complexity.

#### Memory Cell

The smallest subdivision of a memory into which a unit of data has been or can be entered, in which it is or can be stored, and from which it can be retrieved.

#### **Memory Integrated Circuit**

An integrated circuit consisting of memory cells and usually including associated circuits such as those for address selection, amplifiers, etc.

#### **Output-Enable Input**

A gating input that when active permits the integrated circuit to output data and when inactive causes the integrated circuit output(s) to be at a high impedance (off).

#### Programmable Read-Only Memory (PROM)

A read-only memory that after being manufactured can have the data content of each memory cell altered once only.

#### Random-Access Memory (RAM)

A memory that permits access to any of its address locations in any desired sequence with similar access time for each location.

NOTE: The term RAM, as commonly used, denotes a read/write memory.

#### Read-Only Memory (ROM)

A memory in which the contents are not intended to be altered during normal operation. NOTE: Unless otherwise qualified, the term "read-only memory" implies that the content is unalterable and defined by construction.

## **Read/Write Memory**

A memory in which each cell may be selected by applying appropriate electronic input signals and the stored data may be either (a) sensed at appropriate output terminals, or (b) changed in response to other similar electronic input signals.

#### Small-Scale Integration, SSI

Integrated circuits of less complexity than medium-scale integration (MSI).

#### Very-Large-Scale Integration, VLSI

A concept whereby a complete system function is fabricated as a single microcircuit. In this context, a system, whether digital or linear, is considered to be one that contains 1000 or more gates or circuitry of similar complexity.

# **Volatile Memory**

A memory the data content of which is lost when power is removed.

#### PART II – OPERATING CONDITIONS AND CHARACTERISTICS (INCLUDING LETTER SYMBOLS)

The symbols for quantities involving time use upper and lower case letters according to the following historically evolved principles:

- a. Time itself, is always represented by a lower case t.

- b. Subscripts are lower case when one or more letters represent single words, e.g., d for delay, su for setup, rd for read, wr for write.

- c. Multiple subscripts are upper case when each letter stands for a different word, e.g., SR for sense recovery and PLH for propagation delay from low to high.

#### Access Time (of a memory)

The time between the application of a specified input pulse during a read cycle and the availability of valid data signals at an output.

Example symbology:

| ta(ad)             | Access time from address     |

|--------------------|------------------------------|

| t <sub>a</sub> (E) | Access time from chip enable |

| t <sub>a(S)</sub>  | Access time from chip select |

#### **Clock Frequency**

#### Maximum clock frequency, fmax

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transistions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

### Current

# High-level input current, IIH

The current into\* an input when a high-level voltage is applied to that input.

#### High-level output current, IOH

The current into\* an output with input conditions applied that according to the product specification will establish a high level at the output.

#### Low-level input current, IIL

The current into\* an input when a low-level voltage is applied to that input.

#### Low-level output current, IOL

The current into\* an output with input conditions applied that according to the product specification will establish a low level at the output.

# Off-state output current, IO(off)

The current flowing into<sup>\*</sup> an output with input conditions applied that according to the product specification will cause the output switching element to be in the off state.

Note: This parameter is usually specified for open-collector outputs intended to drive devices other than logic circuits.

\*Current out of a terminal is given as a negative value.

#### Off-state (high-impedance-state) output current (of a three-state output), IOZ

The current into\* an output having three-state capability with input conditions applied that according to the product specification will establish the high-impedance state at the output.

#### Short-circuit output current, IOS

The current into<sup>\*</sup> an output when that output is short-circuited to ground (or other specified potential) with input conditions applied to establish the output logic level farthest from ground potential (or other specified potential).

#### Supply current, ICC

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit.

#### Cycle Time

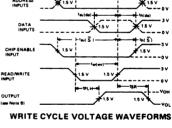

#### Read cycle time, t<sub>c(rd)</sub> (see note)

The time interval between the start and end of a read cycle.

#### Read-write cycle time, tc(rd,wr) (see note)

The time interval between the start of a cycle in which the memory is read and new data are entered, and the end of that cycle.

#### Write cycle time, t<sub>c(wr)</sub> (see note)

The time interval between the start and end of a write cycle.

NOTE: The read, read-write, or write cycle time is the actual interval between two impulses and may be insufficient for the completion of operations within the memory. A minimum value is specified that is the shortest time in which the memory will perform its read and/or write function correctly.

# **Hold Time**

# Hold time, th

The interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

- NOTES: 1. The hold time is the actual time between two events and may be insufficient to accomplish the intended result. A minimum value is specified that is the shortest interval for which correct operation of the logic element is guaranteed.

- 2. The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of data and the active transition) for which correct operation of the logic element is guaranteed.

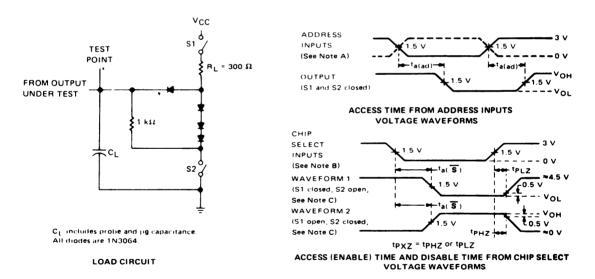

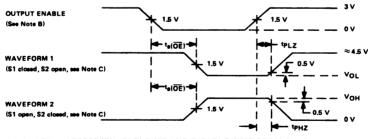

#### **Output Enable and Disable Time**

Output enable time (of a three-state output) to high level, tpZH (or low level, tpZL)

The propagation delay time between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined high (or low) level.

Output enable time (of a three-state output) to high or low level, tpZX

The propagation delay time between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to either of the defined active levels (high or low).

#### Output disable time (of a three-state output) from high level, tpHZ (or low level, tpLZ)

The propagation delay time between the specified reference points on the input and output voltage waveforms with the three-state output changing from the defined high (or low) level to a high-impedance (off) state.

\*Current out of a terminal is given as a negative value.

# GLOSSARY TTL TERMS AND DEFINITIONS

#### Output disable time (of a three-state output) from high or low level, tpxz

The propagation delay time between the specified reference points on the input and output voltage waveforms with the three-state output changing from either of the defined active levels (high or low) to a high-impedance (off) state.

#### **Propagation Time**

#### Propagation delay time, tpp

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level.

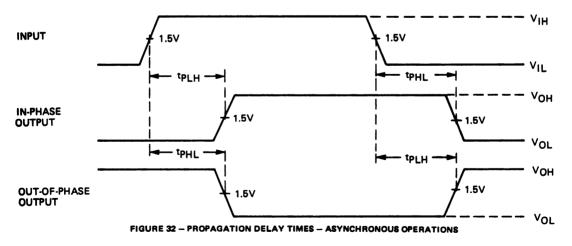

#### Propagation delay time, low-to-high-level output, tpLH

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level.

#### Propagation delay time, high-to-low-level output, tPHL

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level.

# **Pulse Width**

# Pulse width, tw

The time interval between specified reference points on the leading and trailing edges of the pulse waveform.

Example symbology:

| <sup>t</sup> w(cir) | Clear pulse width |

|---------------------|-------------------|

| tw(wr)              | Write pulse width |

# **Recovery Time**

#### Sense Recovery time, tSR

The time interval needed to switch a memory from a write mode to a read mode and to obtain valid data signals at the output.

#### **Release Time**

#### Release time, trelease

The time interval between the release from a specified input terminal of data intended to be recognized and the occurrence of an active transition at another specified input terminal.

Note: When specified, the interval designated "release time" falls within the setup interval and constitutes, in effect, a negative hold time.

#### Setup Time

#### Setup time, t<sub>su</sub>

The time interval between the application of a signal that is maintained at a specified input terminal and a consecutive active transition at another specified input terminal.

- NOTES: 1. The setup time is the actual time between two events and may be insufficient to accomplish the setup. A minimum value is specified that is the shortest interval for which correct operation of the logic element is guaranteed.

- 2. The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the logic element is guaranteed.

# **Transition Time**

Transition time, low-to-high-level, tTLH

The time between a specified low-level voltage and a specified high-level voltage on a waveform that is changing from the defined low level to the defined high level.

#### Transition time, high-to-low-level, tTHL

The time between a specified high-level voltage and a specified low-level voltage on a waveform that is changing from the defined high level to the defined low level.

#### Voltage

#### High-level input voltage, VIH

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least positive value of high-level input voltage for which operation of the logic element within specification limits is guaranteed.

#### High-level output voltage, VOH

The voltage at an output terminal with input conditions applied that according to the product specification will establish a high level at the output.

#### Input clamp voltage, VIK

An input voltage in a region of relatively low differential resistance that serves to limit the input voltage swing.

#### Low-level input voltage, VIL

An input voltage level within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A maximum is specified that is the most positive value of low-level input voltage for which operation of the logic element within specification limits is guaranteed.

#### Low-level output voltage, VOL

The voltage at an output terminal with input conditions applied that according to the product specification will establish a low level at the output.

#### Negative-going threshold voltage, VT\_

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage falls from a level above the positive-going threshold voltage,  $V_{T+}$ .

#### Off-state output voltage, VO(off)

The voltage at an output terminal with input conditions applied that according to the product specification will cause the output switching element to be in the off state.

Note: This characteristic is usually specified only for outputs not having internal pull-up elements.

## On-state output voltage, VO(on)

The voltage at an output terminal with input conditions applied that according to the product specification will cause the output switching element to be in the on state.

Note: This characteristic is usually specified only for outputs not having internal pull-up elements.

#### Positive-going threshold voltage, VT+

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage rises from a level below the negative-going threshold voltage,  $V_{T-}$ .

The following symbols are used in function tables on TI data sheets:

| н                  | = | high level (steady state)                                                                                                      |

|--------------------|---|--------------------------------------------------------------------------------------------------------------------------------|

|                    |   | inginiteven (steady state)                                                                                                     |

| L                  | = | low level (steady state)                                                                                                       |

| 1                  | = | transition from low to high level                                                                                              |

| Ļ                  | = | transition from high to low level                                                                                              |

| <b>→</b>           | = | value/level or resulting value/level is routed to indicated destination                                                        |

| $\hat{\mathbf{r}}$ | = | value/level is re-entered                                                                                                      |

| x                  | = | irrelevant (any input, including transitions)                                                                                  |

| ah                 | = | the level of steady-state inputs at inputs A through H respectively                                                            |

| Q <sub>0</sub>     | = | level of ${\bf Q}$ before the indicated steady-state input conditions were established                                         |

| ₫0                 | = | complement of Q0 or level of $\overline{\mathbf{Q}}$ before the indicated steady-state input conditions were established       |

| Qn                 | = | level of Q before the most recent active transition indicated by $\downarrow$ or $\uparrow$                                    |

|                    | = | one high-level pulse                                                                                                           |

| IJ                 | = | one low-level pulse                                                                                                            |

| TOGGLE             | - | each output changes to the complement of its previous level on each active transition indicated by $\downarrow$ or $\uparrow.$ |

|                    |   |                                                                                                                                |

The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group

**NOVEMBER 1976**

TEXAS INSTRUMENTS

Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patents or rights of others that may result from its use. No license is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

> Copyright © 1976 Texas Instruments Incorporated

# TABLE OF CONTENTS

| 1. | INT  | RODUCTION                                                                                                |     |     |     |          |

|----|------|----------------------------------------------------------------------------------------------------------|-----|-----|-----|----------|

|    | 1.1  | Architectural Features .                                                                                 |     |     |     | 1        |

|    | 1.2  | Operational Features                                                                                     |     |     |     | 1        |

|    | 1.3  | Mechanical Features .                                                                                    |     |     |     | 1        |

| 2. | DET  | TAILED FUNCTIONAL DESCRIPTIONS                                                                           |     |     |     |          |

|    | 2.1  | Micro-Decoding Logic Array                                                                               |     |     |     | 4        |

|    | 2.2  | Relative Position Control (POS) .                                                                        |     |     |     | 4        |

|    | 2.3  | Clock                                                                                                    |     |     |     | 5        |

|    | 2.4  | Latched Data Input Ports .                                                                               |     |     |     | 5        |

|    | 2.5  | A and B Operand Sources                                                                                  |     |     |     | 6        |

|    | 2.6  | Arithmetic/Logic Unit (ALU)                                                                              |     |     |     | 8        |

|    | 2.7  | ALU Magnitude and Carry Functions .                                                                      |     |     |     | 9        |

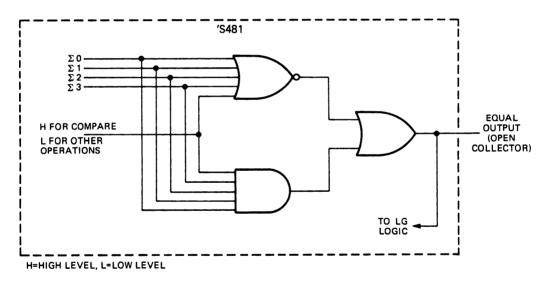

|    |      | 2.7.1 Equal (EQ, See Figure 5)                                                                           |     |     |     | 9        |

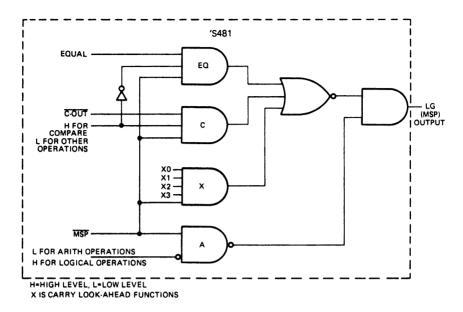

|    |      | 2.7.2 Logically-Greater Than (LG, See Figure 6)                                                          |     |     |     | 9        |

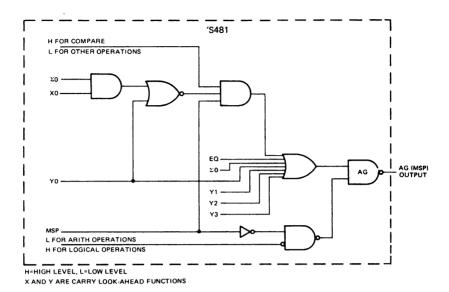

|    |      | 2.7.3 Arithmetically-Greater-Than (AG, See Figure 7)                                                     |     |     |     | 10       |

|    | 2.8  | Operand Overflow                                                                                         |     |     |     | 11       |

|    | 2.9  | •                                                                                                        |     |     |     | 12       |

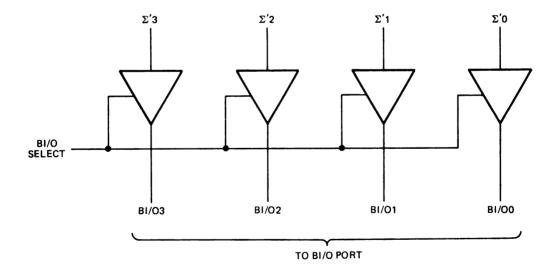

|    |      | B-Input/Output Control                                                                                   |     |     |     | 13       |

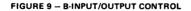

|    |      | Working Register                                                                                         |     |     |     | 14       |

|    |      | ? Working Register Multiplexer (WR MUX) .                                                                |     |     |     | 14       |

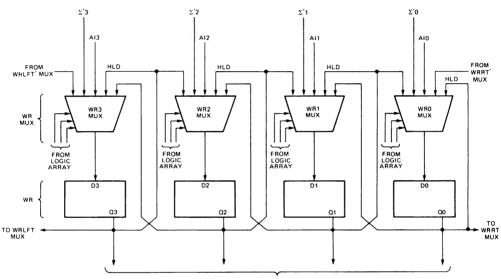

|    |      | B Extended Working Register                                                                              |     |     |     | 15<br>15 |

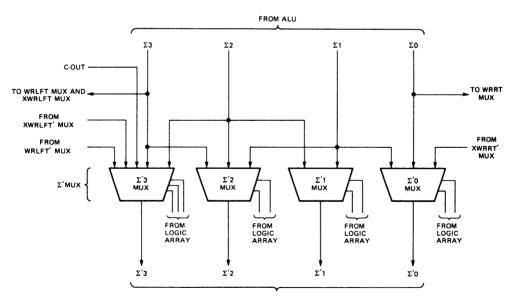

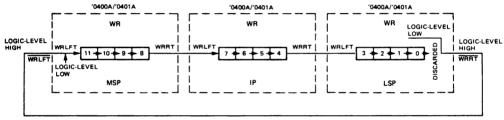

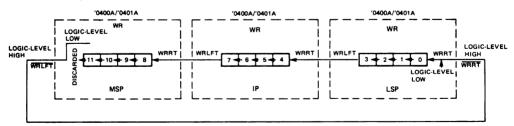

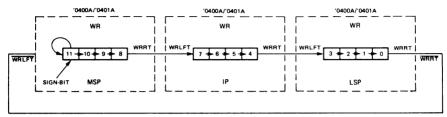

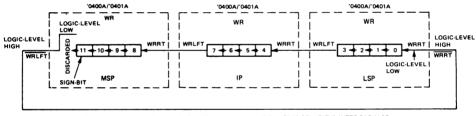

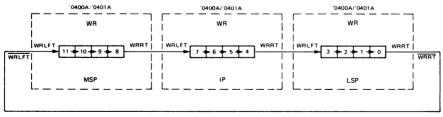

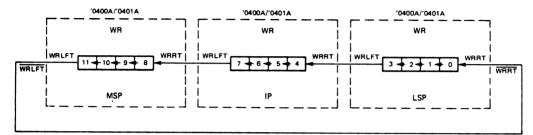

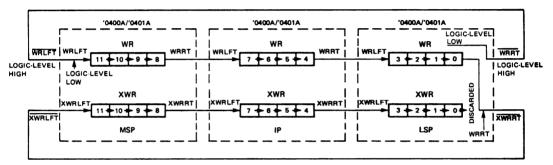

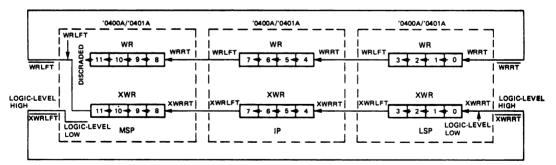

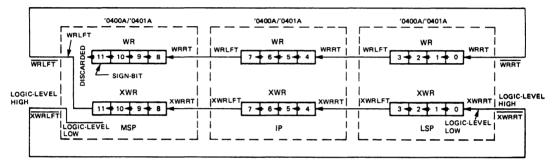

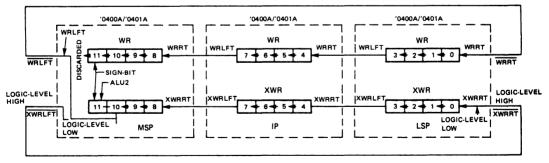

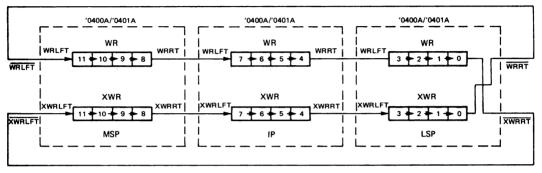

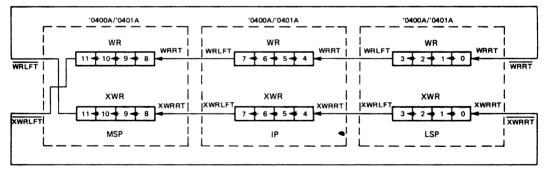

|    | 2.14 | Extended Working Register Multiplexer (XWR MUX)<br>2.14.1 Σ-Bus, WR, XWR MSB Shift Transfer Multiplexers |     |     |     | 15       |

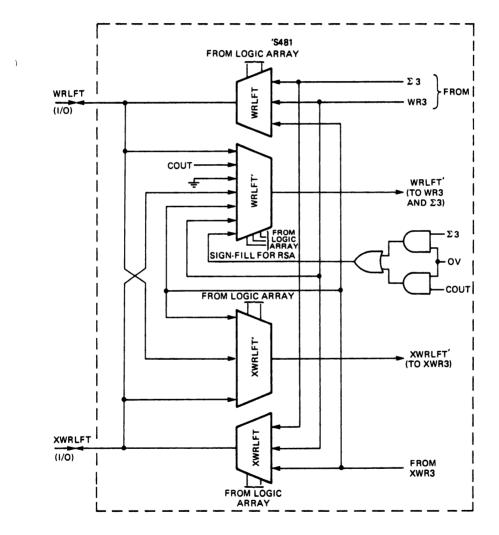

|    |      | 2.14.1 2-bus, wh, XWH MSB Shift Transfer Multiplexers<br>2.14.2 WRLFT, XWRLFT Multiplexers .             |     |     |     | 16       |

|    |      | 2.14.2 WRLFT', XWRLFT' Multiplexers                                                                      |     |     |     | 16       |

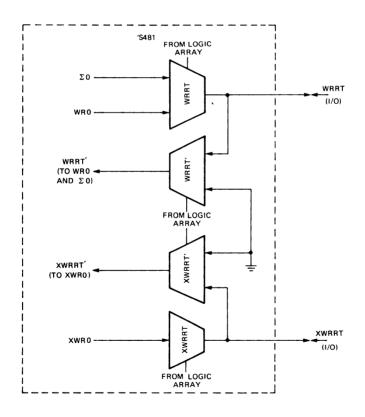

|    |      | 2.14.4 WR, XWR LSB Shift Transfer Multiplexers .                                                         |     |     |     | 16       |

|    |      | 2.14.5 WRRT Multiplexer, XWRRT Buffer .                                                                  |     |     |     | 17       |

|    |      | 2.14.6 WRRT', XWRRT' Multiplexers .                                                                      |     |     |     | 17       |

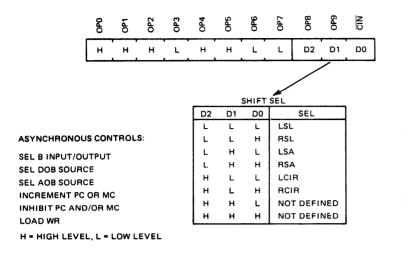

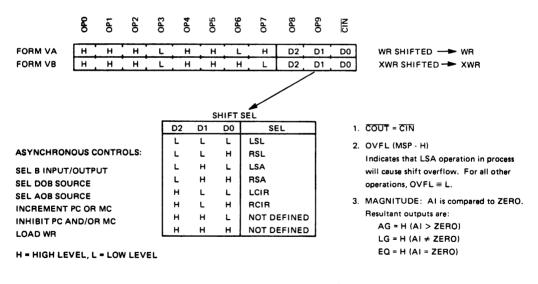

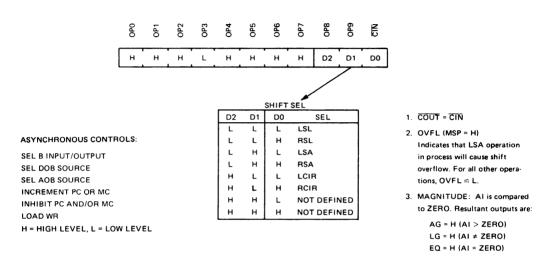

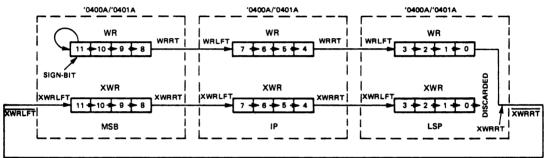

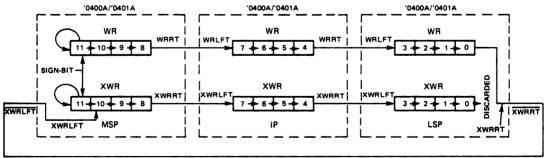

|    | 2 15 | 5 Shift Functions                                                                                        |     |     |     | 20       |

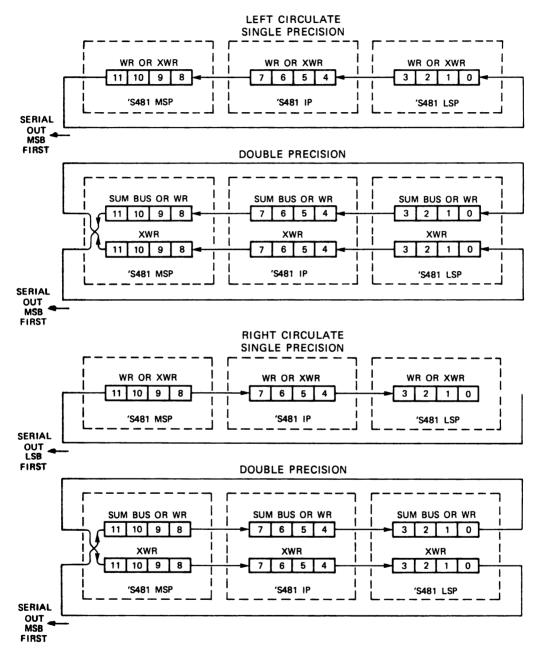

|    | 2.15 | 2.15.1 Circulate (Shift) Functions (Microprogrammable)                                                   |     |     |     | 20       |

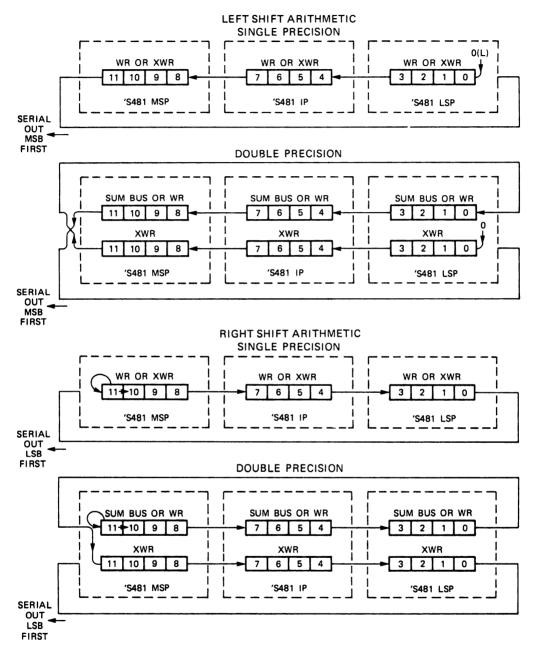

|    |      | 2.15.2 Arithmetic Shift Functions (Microprogrammable)                                                    |     |     |     | 20       |

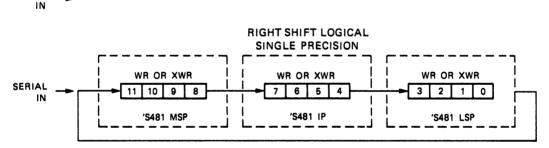

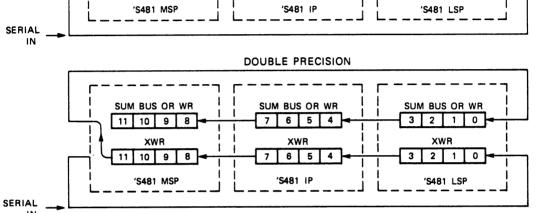

|    |      | 2.15.3 Logical Shift Functions (Microprogrammable)                                                       |     |     |     | 22       |

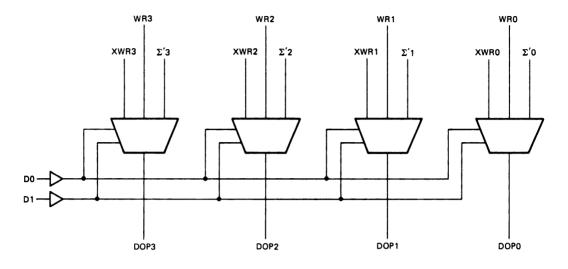

|    | 2.16 | Data-Out Port Multiplexer (DO MUX) .                                                                     |     |     |     | 22       |

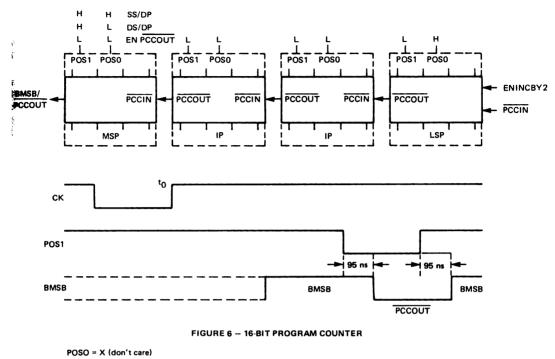

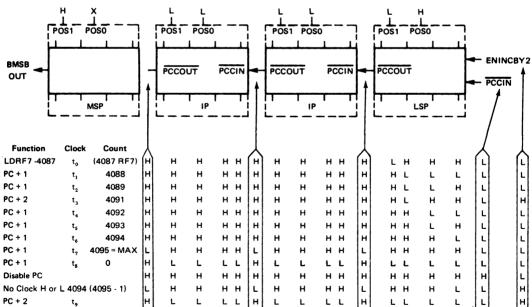

|    |      | Memory and Program Counters                                                                              |     |     |     | 22       |

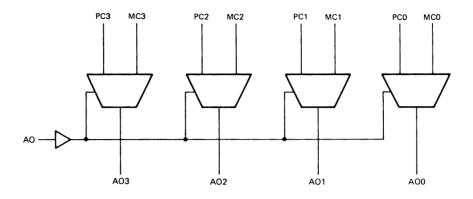

|    |      | Address-Out Port Multiplexer (AO MUX) .                                                                  |     |     |     | 26       |

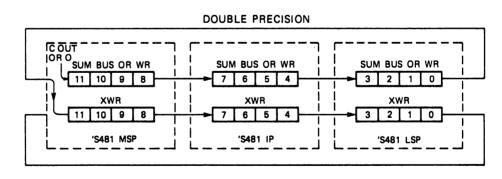

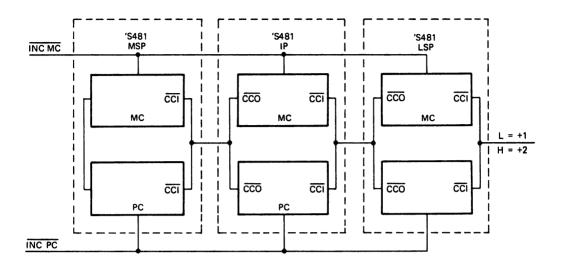

|    |      | Expanding the Word Length .                                                                              |     |     |     | 27       |

| 3. | OPE  | ERATIONAL DESCRIPTIONS                                                                                   |     |     |     |          |

|    | 3.1  | Micro/Macro-Operations                                                                                   |     |     |     | 27       |

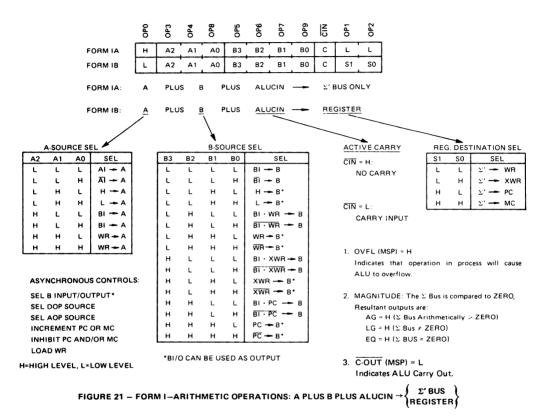

|    | 3.2  | Operation Form I – Add/Subtract → Register                                                               |     |     |     | <br>30   |

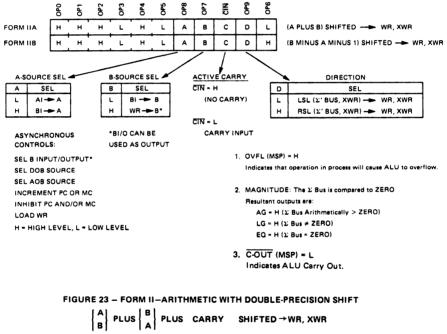

|    | 3.3  | Operation Form II – Add/Subtract with Double-Precision Shift                                             |     |     |     | <br>32   |

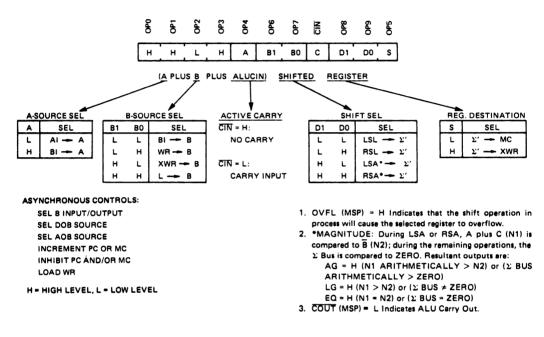

|    | 3.4  | Operation Form III – Add with Single-Precision Shift                                                     |     |     |     | <br>32   |

|    | 3.5  | Operation Form IV – AI Shifted $\rightarrow \Sigma'$ Bus                                                 |     |     |     | <br>33   |

|    | 3.6  | Operation Form V — Single-Length Shift                                                                   |     |     |     | <br>34   |

|    | 3.7  | Operation Form VI – Double-Precision Shifts                                                              |     |     |     |          |

|    | 3.8  | Operation Form VII – Compare (A:B or B:A)                                                                |     | • • | •   | <br>35   |

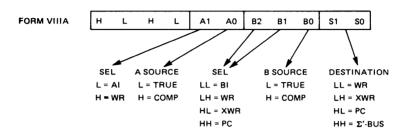

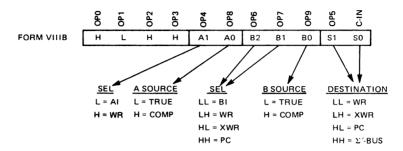

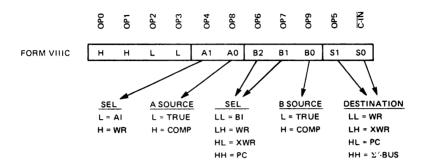

|    | 3.9  | Operation Form VIII – Logical Functions                                                                  | • • | • • | • • |          |

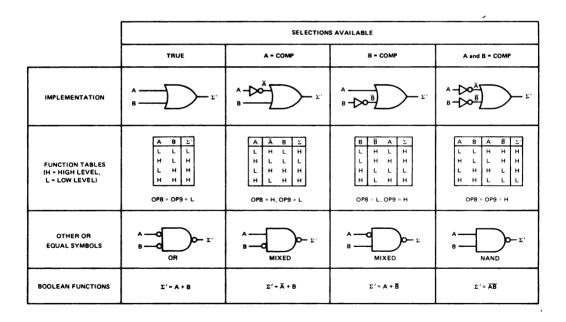

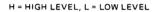

|    |      | 3.9.1 NOR/AND Logical Operations                                                                         |     | • • |     | <br>37   |

# **TABLE OF CONTENTS (Continued)**

|    | 3.9.2       | OR/NAND Logical Operations                             | 38 |

|----|-------------|--------------------------------------------------------|----|

|    | 3.9.3       | Exclusive-OR/Exclusive-NOR Logical Operations          | 39 |

|    | 3.10 Operat | tion Form IX                                           | 40 |

|    | 3.11 Operat | tion Form X – Cyclic Redundancy Character Accumulation | 40 |

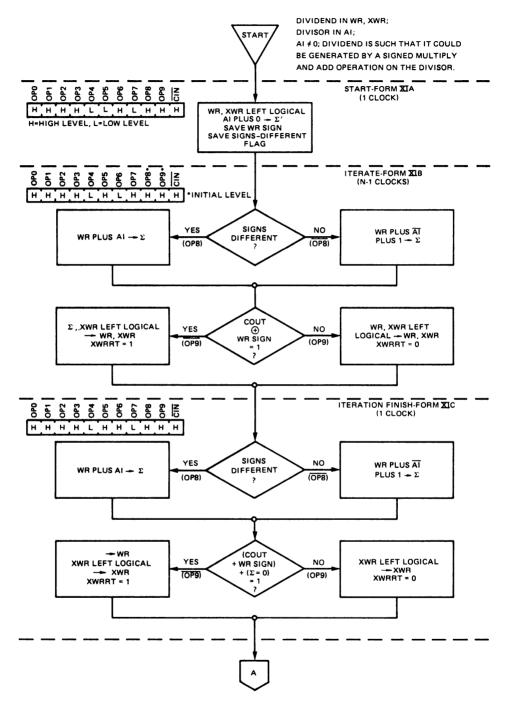

|    | 3.12 Operat | tion Form XI – Signed Integer Divide .                 | 41 |

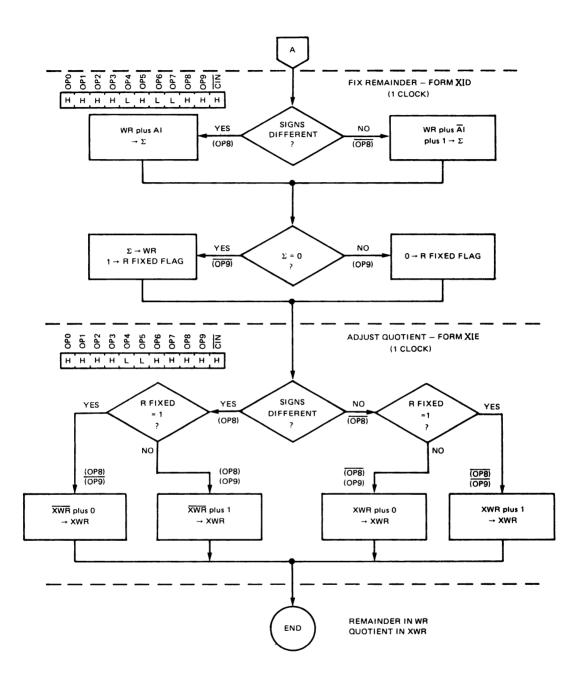

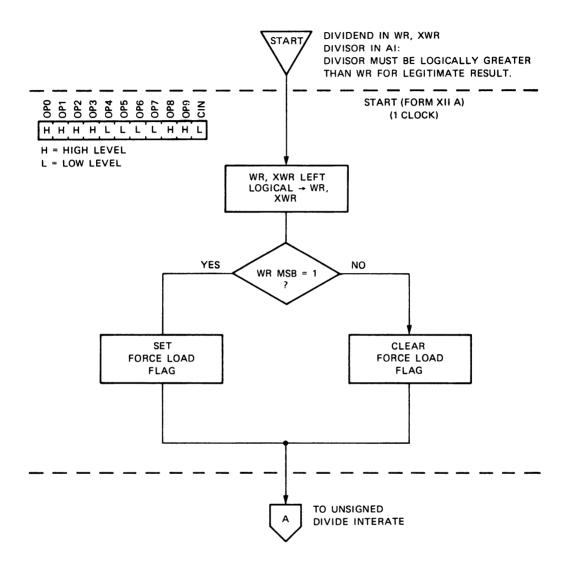

|    | 3.13 Operat | tion Form XII – Unsigned Divide                        | 41 |

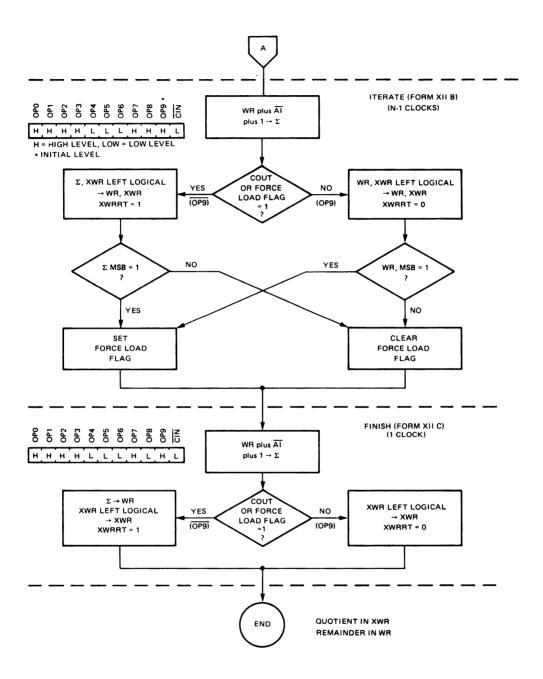

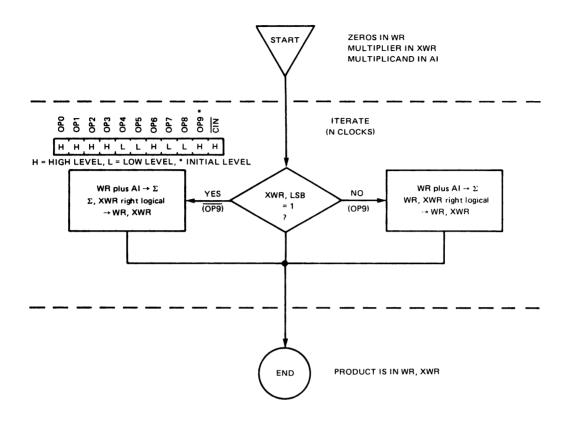

|    | 3.14 Operat | tion Form XIII – Unsigned Multiply                     | 41 |

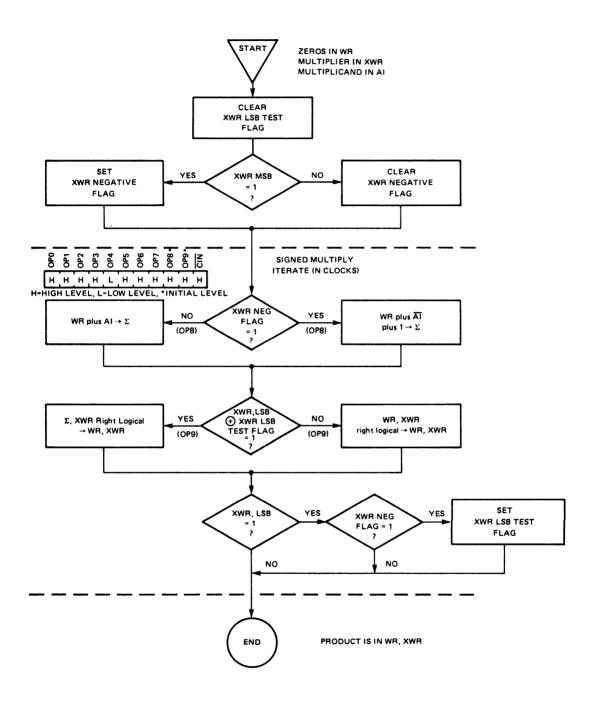

|    | 3.15 Operat | tion Form XIV – Signed Integer Multiply                | 46 |

| 4. | SPECIFIC    | ATIONS .                                               | 48 |

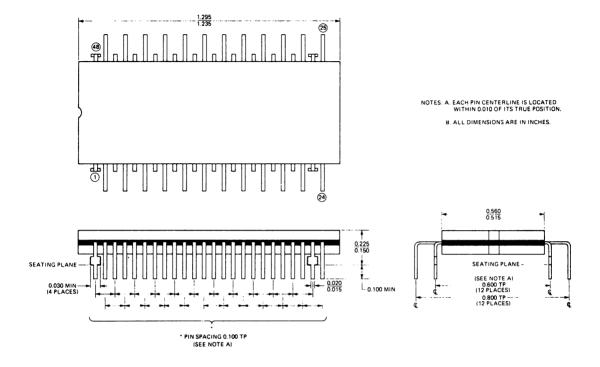

| 5. | MECHANI     | ICAL DATA                                              | 50 |

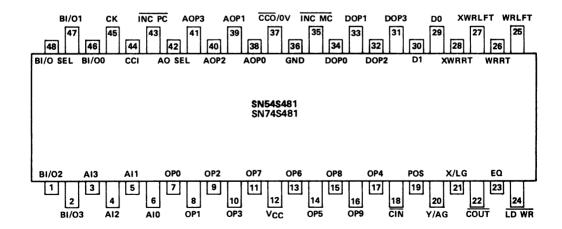

| 6. | PIN ASSIG   | GNMENTS                                                | 50 |

# LIST OF ILLUSTRATIONS

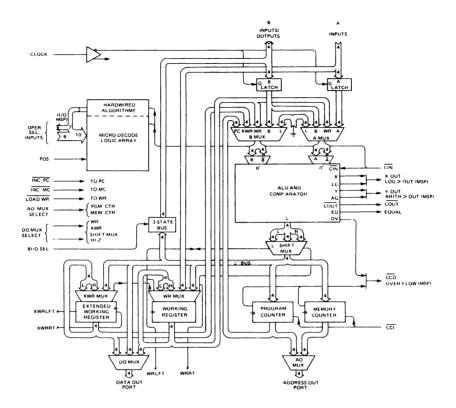

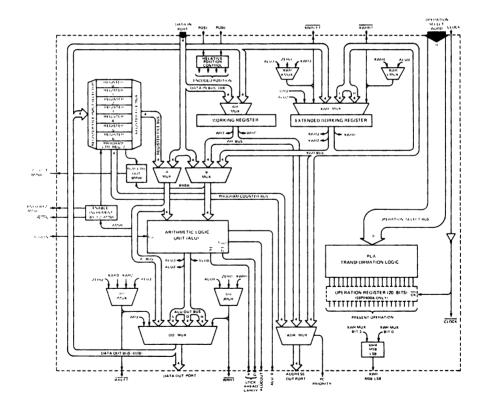

| Figure 1  | Functional Block Diagram                                                                                                            | . 3  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2  | Clock Cycle                                                                                                                         | . 5  |

| Figure 3  | Input Latches Setup/Hold Times                                                                                                      | . 6  |

| Figure 4  | ALU Operand Sources                                                                                                                 | . 7  |

| Figure 5  | Equal Output                                                                                                                        | . 9  |

| Figure 6  | MSP Logically-Greater-Than (LG) Output                                                                                              | . 10 |

| Figure 7  | MSP Arithmetically-Greater-Than (AG) Output                                                                                         | . 11 |

| Figure 8  | Sum Bus Multiplexer .                                                                                                               | . 12 |

| Figure 9  | B-Input/Output Control                                                                                                              | . 13 |

| Figure 10 | Working Register (WR) and WR Multiplexer                                                                                            | . 14 |

| Figure 11 | Extended Working Register (XWR) and XWR Multiplexer                                                                                 | . 15 |

| Figure 12 | Sum-Bus, WR, XWR MSB Shift Transfer Multiplexers                                                                                    | . 17 |

| Figure 13 | Sum-Bus, WR, XWR LSB Shift Transfer Multiplexers                                                                                    | . 19 |

| Figure 14 | Circulate Functions                                                                                                                 | . 21 |

| Figure 15 | Arithmetic Shift Functions                                                                                                          | . 23 |

| Figure 16 | Logical Shift Functions                                                                                                             | . 24 |

| Figure 17 | Data-Out Port Multiplexer (DO MUX)                                                                                                  | . 25 |

| Figure 18 | Program and Memory Counter Functions                                                                                                | . 26 |

| Figure 19 | Address-Out Port Multiplexer (AO MUX)                                                                                               | . 27 |

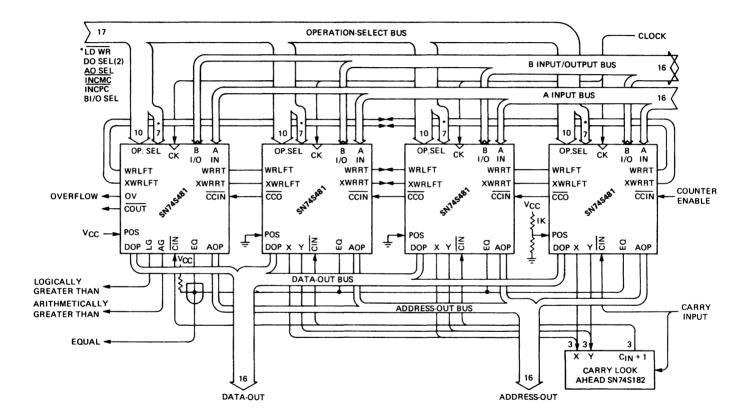

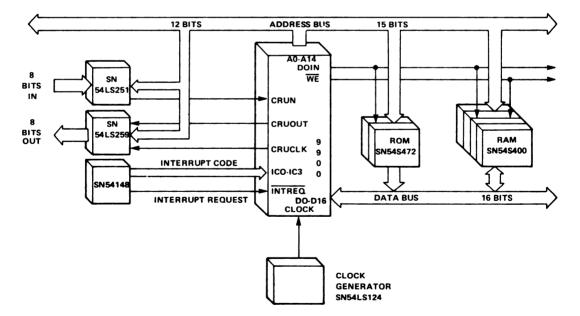

| Figure 20 | Typical 16-Bit Processor                                                                                                            | . 28 |

| Figure 21 | Form I – Arithmetic Operations: A Plus B Plus ALUCIN $\rightarrow \begin{cases} \Sigma' \text{ Bus} \\ \text{Register} \end{cases}$ | . 30 |

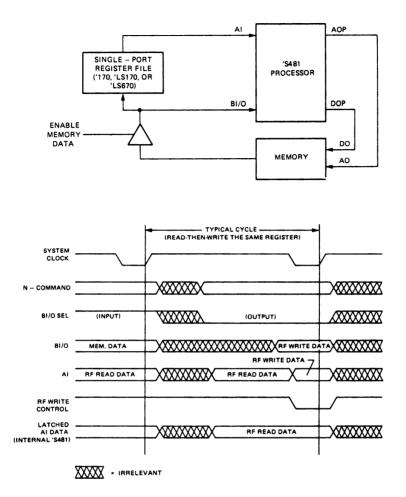

| Figure 22 | 'S481 Operation with Single Port Register File                                                                                      | . 31 |

| Figure 23 | Form II – Arithmetic with Double-Precision Shift                                                                                    | . 32 |

| Figure 24 | Form III – Arithmetic With Single-Precision Shift                                                                                   | . 33 |

| Figure 25 | Form IV – AI Shifted $\rightarrow \Sigma'$ Bus                                                                                      | . 34 |

| Figure 26 | Form V: {WR<br>XWR} Shifted → {WR<br>XWR}                                                                                           | . 34 |

| Figure 27 | Form VI – Double Precision Shifts: (WR, XWR)Shifted →(WR, XWR)                                                                      | . 35 |

# LIST OF ILLUSTRATIONS (Continued)

| Figure 28 | Form VII – Compare: $egin{pmatrix} A &: B \ B &: A \end{pmatrix}$                                              |  |  |     | . 36 |

|-----------|----------------------------------------------------------------------------------------------------------------|--|--|-----|------|

| Figure 29 | Form VIII – Logical Operations: $A \begin{cases} NOR \\ OR \\ X \cdot OR \end{cases} B \rightarrow Register$ . |  |  |     | . 36 |

|           | Form VIIIA – NOR/AND Logical Operations                                                                        |  |  |     | . 37 |

| Figure 31 | Form VIIIB – OR/NAND Logical Operations                                                                        |  |  |     | . 38 |

| Figure 32 | Form VIIIC – EXCLUSIVE-OR/EXCLUSIVE-NOR Operations                                                             |  |  |     | . 39 |

| Figure 33 | Form IX – No Operation: Zero $\Rightarrow \Sigma'$ Bus                                                         |  |  |     | . 40 |

| Figure 34 | Cyclic Redundancy Character Accumulation                                                                       |  |  |     | . 40 |

| Figure 35 | Form XI – Signed Integer Divide                                                                                |  |  |     | 2,43 |

| Figure 36 | Form XII – Unsigned Divide                                                                                     |  |  | . 4 | 4,45 |

| Figure 37 | Form XIII – Unsigned Multiply .                                                                                |  |  |     | . 46 |

| Figure 38 | Form XIV - Signed Integer Multiply                                                                             |  |  |     | . 47 |

# LIST OF TABLES

| Table 1  | Functional Descriptions                        |      |    |    |     |     |  |  |   |  |   |   |   |   |   |   | 2,  | ,3 |

|----------|------------------------------------------------|------|----|----|-----|-----|--|--|---|--|---|---|---|---|---|---|-----|----|

| Table 2  | MSP OP8 and OP9 Iterative Function Summary     |      |    |    |     |     |  |  |   |  |   |   |   |   |   |   |     | 4  |

| Table 3  | Position Control Functions                     |      |    |    |     |     |  |  |   |  |   |   |   |   |   |   |     | 4  |

| Table 4  | Dual-Function Logic I/O Pins                   |      |    |    |     |     |  |  |   |  |   |   |   |   |   |   |     | 5  |

| Table 5  | 'S481 ALU and Logic Functions                  |      |    | •  |     |     |  |  |   |  |   |   |   |   |   |   |     | 8  |

| Table 6  | Extended ALU Functions of 'S481                |      |    |    |     |     |  |  |   |  |   |   |   |   |   |   |     | 8  |

| Table 7  | MSP Logically-Greater-Than (LG) Output         |      |    |    |     |     |  |  |   |  |   |   |   |   |   |   | . 1 | 0  |

| Table 8  | ALU Carry and MSP Arithmetically-Greater-Than  | n (A | G) | 0  | utp | uts |  |  |   |  |   |   |   |   |   |   | . 1 | 1  |

| Table 9  | MSP Overflow (OV) Output                       |      | •  |    |     |     |  |  |   |  |   |   | • |   | • | • | . 1 | 2  |

| Table 10 | B-Input/Output Control                         | •    |    |    |     |     |  |  |   |  |   |   |   |   |   |   | . 1 | 3  |

| Table 11 | Working Register Bit Transfers to WRLFT/WRRT   | Г    |    |    |     |     |  |  |   |  |   |   |   |   |   |   | . 1 | 8  |

| Table 12 | Sum-Bus Bit Transfers to WRLFT/WRRT            |      | •  | •  |     |     |  |  |   |  |   |   |   |   | • |   | . 1 | 8  |

| Table 13 | Extended Working Register Bit Transfers to XWR | lLF  | Т/ | X٧ | /RF | ۲F  |  |  |   |  | • | • |   |   |   |   | . 1 | 8  |

| Table 14 | Sum-Bus Bit Transfers to WRLFT (MSP)           |      |    |    |     |     |  |  | • |  | • |   |   |   |   |   | . 1 | 9  |

| Table 15 | Microprogrammable Shift Functions              |      | •  |    |     |     |  |  |   |  |   |   | • |   |   | • | . 2 | 0  |

| Table 16 | Data-Out Port Control .                        | •    | •  |    | •   |     |  |  |   |  |   |   |   |   |   | • | . 2 | 5  |

| Table 17 | Address-Out Port Control                       |      |    | •  | •   |     |  |  |   |  |   | • |   | • |   |   | . 2 | 6  |

| Table 18 | Operation Form Summary                         |      |    |    |     |     |  |  | • |  | • |   | • |   |   | • | . 2 | 9  |

| Table 19 | Recommended Operating Conditions               | •    |    | •  |     |     |  |  |   |  |   |   |   | • | • | • | . 4 | 8  |

| Table 20 | Electrical Characteristics                     |      |    |    |     |     |  |  |   |  | • |   |   | • | • |   | . 4 | 9  |

| Table 21 | Switching Characteristics                      |      | •  | •  |     |     |  |  |   |  |   |   |   |   |   |   | . 4 | 9  |

|          |                                                |      |    |    |     |     |  |  |   |  |   |   |   |   |   |   |     |    |

# 1. INTRODUCTION

#### 1.1 ARCHITECTURAL FEATURES

The SN54S481, SN74S481 are Schottky TTL 4-bit expandable parallel binary micro/macroprogrammable processor element building blocks designed specifically for implementing high-performance digital computers/controllers. The 'S481, with its ability to efficiently emulate existing systems, can be used to upgrade hardware performance with full compatibility to protect the software investments.

Designed with full parallel dual input/output ports, the memory-to-memory architecture of the 'S481 provides a new dimension in interrupt processing or program context switching flexibilities. Its static bipolar logic performs each microinstruction within a single 100 ns clock cycle.

Primary among the 'S481 architectural features are:

- Microprogrammable, bit-slice design is expandable in 4-bit multiples

- Full parallel dual input/output ports for use in advanced memory-to-memory architecture

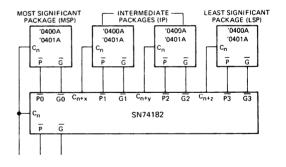

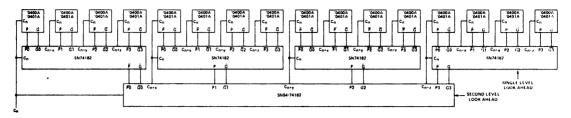

- Full-function ALU with carry look-ahead, magnitude, and overflow decision capabilities

- Double-length accumulator with full shifting capability and sign-bit handling

- Dual memory address generators on-chip.

#### 1.2 OPERATIONAL FEATURES

The functional capabilities, characterized by the 24,780 unique operations of the 'S481, coupled with its macroprogrammable multiply and divide algorithms, make the 'S481 particularly attractive for implementing advanced high performance computers and controllers.

In addition to the full parallel data bus structure, the 'S481 architecture also features asynchronous access to data routing and counter updating controls which, when combined with the most versatile instruction set available (see operational description) maximizes flexibility, efficiency, and performance. Simultaneous compound operations in the form of an ALU function with shift, plus destination selection with address/iteration updating, plus address and present data to memory can be accomplished in a single microcycle. Some other operational features are:

- Simultaneous one-clock compound operations with status can reduce microcycles and improve throughput

- Pre-programmed multiply, divide, and CRG algorithms

- Performs 16-bit by 16-bit double-precision divide in less than 3 microseconds

- Double length accumulator with full bidirectional single/double precision arithmetic/logical/circulate shift capabilities include sign protection

- Full-micro-operational control is provided for programming: address updating, data and address source selection, and direct transfer of data to working register or working memory

- Relative position control defines bit-slice rank and sign handling in N-bit applications.

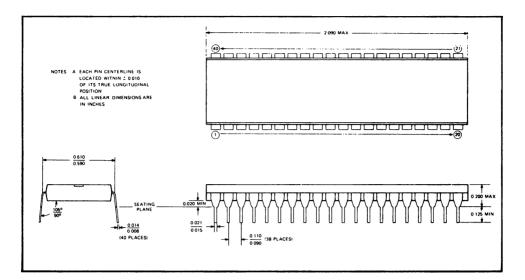

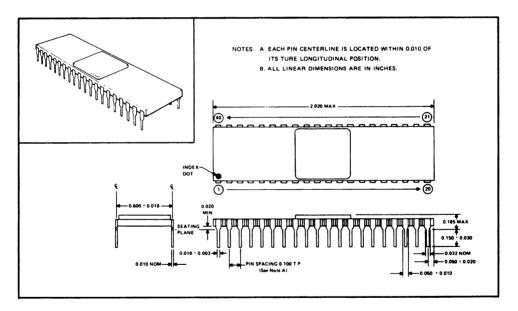

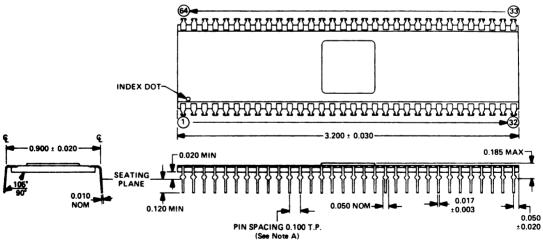

#### 1.3 MECHANICAL FEATURES

The 'S481 is supplied in a high-density 48-pin package with the qud pin rows formed on 600- and 800-mil centers. Within each of the four rows pin spacing is 100-mils, center-to-center. See mechanical data for detailed dimensions.

#### DESIGN GOAL

This document provides tentative information on a product in the developmental stage. Toxas Instruments reserves the right to change or discontinue this product without notice.

| PIN NUMBER                                  | PIN NAME                                                 | PIN FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                   | INPUT, OUTPUT, OR<br>INPUT/OUTPUT |

|---------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 46, 47<br>1, 2                              | BI/O0, BI/O1<br>BI/O2, BI/O3                             | 4-bit parallel data input port to the B latch, or 4-bit parallel data<br>output for the ン-bus when not being used as an input.                                                                                                                                                                                                                                                                                                                                 | Inputs/Outputs                    |

| 6, 5<br>4, 3                                | AI0, AI1<br>AI2, AI3                                     | 4-bit parallel data input port to the A latch and WR.                                                                                                                                                                                                                                                                                                                                                                                                          | Inputs                            |

| 7, 8<br>9, 10<br>17, 14<br>13, 11<br>15, 16 | OP0, OP1<br>OP2, OP3<br>OP4, OP5<br>OP6, OP7<br>OP8, OP9 | OP0 through OP9 serve as a 10-bit parallel operation-select input to<br>the micro-decode logic array. In the most-significant position, OP8<br>and OP9 additionally serve as open-collector outputs during multi-<br>ply and divide algorithms. In the least-significant position, OP9<br>serves as an open-collector output during the CRC algorithm.                                                                                                         | Inputs                            |

| 12                                          | Vcc                                                      | Single 5-volt power-supply terminal.                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply Voltage Pin                |

| 18                                          | CIN                                                      | Receives low-active ripple carry input data.                                                                                                                                                                                                                                                                                                                                                                                                                   | Input                             |

| 19                                          | POS                                                      | Directs internal and input/output end-conditions required to define<br>the relative position of each bit-slice when N-SN74S481's are<br>cascaded to implement Nx4-bit word lengths. When biased at 2.4<br>volts, the package operates as the least-significant (LSP) slice; when<br>grounded, it functions as an intermediate (IP) slice; and when high, 5<br>volts, it functions as the most-significant (MSP) slice.                                         | Input                             |

| 20                                          | Y/AG                                                     | In least-significant and intermediate positions outputs arithmetic<br>carry generate (Y) for use with look-ahead. In most-significant<br>position outputs true arithmetically-greater-than signal.                                                                                                                                                                                                                                                             | Output                            |

| 21                                          | X/LG                                                     | In least-significant and intermediate positions outputs arithmetic<br>carry propagate (X) for use with look-ahead. In most-significant<br>position outputs true logically-greater-than signal.                                                                                                                                                                                                                                                                 | Output                            |

| 22                                          | COUT                                                     | Outputs low-active ripple carry data.                                                                                                                                                                                                                                                                                                                                                                                                                          | Output                            |

| 23                                          | EQ                                                       | Outputs true (active-high) equality of $\Sigma'$ bus equals zero for each 4-bit slice. The open-collector output permits wire-AND to achieve Nx4-bit equality output.                                                                                                                                                                                                                                                                                          | Open-Collector-Output             |

| 24                                          | LDWR                                                     | When low, data applied at the AI port coincident with the 1 clock transition is loaded into the WR.                                                                                                                                                                                                                                                                                                                                                            | Input                             |

| 26<br>25                                    | WRRT,<br>WRLFT                                           | Working register and ∑-bus shift interconnectivity pins. WRRT<br>receives left-shift and outputs right-shift (true) data. WRLFT<br>receives right-shift and outputs left-shift (true) data. Shift can be<br>single-precision, double-precision, signed or unsigned.                                                                                                                                                                                            | Bidirectional I/O                 |

| 28<br>27                                    | XWRRT,<br>XWRLFT                                         | Extended working register shift interconnectivity pins. XWRRT<br>receives left-shift and outputs right-shift (true) data. XWRLFT<br>receives right-shift and outputs left-shift (true) data. Shift can be<br>single-precision, double-precision, signed or unsigned.                                                                                                                                                                                           | Bidirectional I/O                 |

| 29<br>30                                    | D0<br>D1                                                 | Selects one of three DOP sources (WR, XWR, or $\Sigma$ -bus) or places the DOP outputs in a high-impedance state.                                                                                                                                                                                                                                                                                                                                              | Inputs                            |

| 34<br>33<br>32<br>31                        | DOP0<br>DOP1<br>DOP2<br>DOP3                             | 4-bit parallel, data-out port. DOPO is LSB.                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-state outputs                   |

| 35                                          | INCMC                                                    | When low, enables the MC to increment as directed by CCI on the next f clock transition. When high, inhibits MC to hold mode. As CCO is common to MC and PC, the MC should be inhibited when PC is enabled.                                                                                                                                                                                                                                                    | Input                             |

| 36                                          | GND                                                      | Common or ground terminal for the supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |

| 37                                          | CCO/OV                                                   | In least-significant and intermediate positions a low-level output<br>indicates that either the PC or MC is at maximum count. As CCO is<br>common for both PC and MC ambiguous carry can be avoided if one<br>or both counters is/are disabled by the INCPC and/or INCMC<br>inputs. In the most-significant position, a high-level output,<br>depending on the operation selected, indicates that the WR, XWR,<br>or ALU will overflow (OV) on the next clock. | Output                            |

#### TABLE 1 FUNCTIONAL DESCRIPTIONS

| PIN NUMBER       | PIN NAME                 | PIN FUNCTION                                                                                                                                                                                                                                                                               | INPUT, OUTPUT, OR<br>INPUT/OUTPUT |

|------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 38, 39<br>40, 41 | AOP0, AOP1<br>AOP2, AOP3 | 4-bit parallel address-out port.                                                                                                                                                                                                                                                           | Outputs                           |

| 42               | A0                       | Selects one of two AOP sources (PC or MC).                                                                                                                                                                                                                                                 | Input                             |

| 43               | INCPC                    | When low, enables the PC to increment as directed by $\overline{CCI}$ on the next 1 clock transition. When high, inhibits PC to hold mode. As $\overline{CCO}$ is common to PC and MC, the PC should be inhibited when MC is enabled.                                                      | Input                             |

| 44               | CCI                      | In least-significant position, a low input directs enabled PC or<br>enabled MC to increment by one on next 1 clock transition. In the<br>LSP, a high directs enabled PC or enabled MC to increment by 2. In<br>other positions, a low is a carry input and a high inhibits the<br>counter. | Input                             |

| 45               | СК                       | When high, enables the transparency of A and B input latches. When<br>low, latches A and B input data. Clocks synchronous registers and<br>counters on the positive transition.                                                                                                            | Input                             |

| 48               | BI/O SEL                 | When low, enables BI/O to output ∑-bus data. When high, the BI/O output drivers are placed in a high-impedance state permitting BI/O to be used as data inputs.                                                                                                                            | Input                             |

#### TABLE 1 (Continued)

# 2. DETAILED FUNCTIONAL DESCRIPTIONS

### 2.1 MICRO-DECODING LOGIC ARRAY

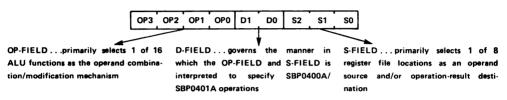

The micro-decoding logic array is a dedicated 11 input PLA decoding 73 product terms to generate 24 control lines needed to implement the 14 operation forms. The eleven inputs consist of the ten operation select lines (OP0 through OP9) and the ALU carry input. The carry input, utilized as an additional operation select line during operation forms not performing arithmetic functions, maximizes system pin efficiency and functional density.

In an expanded word-length system (two or more 'S481's), operation select inputs 8 (OP8) and 9 (OP9) assume an input/output capability in the most-significant or least-significant package as a result of the position control and the type of operation being performed. During microprogrammable operation forms I through IX, OP8 and OP9 function simply as another input; but, during the macroprogrammable operations of forms X through XIV one or both become an output during iterations. Table 2 summarizes by operation form the control (output) package and the operation lines which are used as an output.

| 00 5004   |                   | CONTROL | OPERATION | SELECT I/O |

|-----------|-------------------|---------|-----------|------------|

| OP. FORM  | ALGORITHM         | PACKAGE | OP8       | OP9        |

| l thru IX | All               | None    | INPUT     | INPUT      |

| x         | CRC ACCUMULATION  | LSP     | INPUT     | OUTPUT     |

| XI        | SIGNED DIVIDE     | MSP     | OUTPUT    | OUTPUT     |

| XII       | UNSIGNED DIVIDE   | MSP     | INPUT     | OUTPUT     |

| XIII      | UNSIGNED MULTIPLY | MSP     | INPUT     | OUTPUT     |

| xıv       | SIGNED MULTIPLY   | MSP     | OUTPUT    | OUTPUT     |

TABLE 2 MSP OP8 and OP9 ITERATIVE FUNCTION SUMMARY

If the macroinstructions are to be used in an expanded word length, OP8 and OP9 select lines of the MSP and the OP9 line of the LSP should be driven from either a 3-state output (which can be placed in high-impedance state) or an open-collector output (which can be wire-OR'ed with the OP select I/O lines). During an iterative function for which the OP line is designated as an open-collector output, the OP line driver should be placed in a high-impedance or off state permitting the output function to drive similar OP lines in the remaining packages.

The output state of OP8 or OP9 is a function of on-chip status decoder as enumerated in the flow diagrams illustrating the five algorithms.

## 2.2 RELATIVE POSITION CONTROL (POS)

The single line position control, with the ability of decoding one of three input logic states, provides each 'S481 in an expanded word length system with the capability of identifying its relative position. The relative positions, with the corresponding input logic levels are enumerated in Table 3.

TABLE 3 POSITION CONTROL FUNCTIONS

| MOST-SIGNIFICANT POSITION (MSP)  |

|----------------------------------|

| LEAST-SIGNIFICANT POSITION (LSP) |

| INTERMEDIATE POSITION (IP)       |

|                                  |

This relative position identification dictates how each 'S481 in the system handles the multi-purpose I/O accommodations and ALU sign and magnitude functions. See Table 4. Shift/Circulate interconnectivity bit transfers are explained in detail under shift/circulate transfer multiplexers.

| DUAL-FUNCTION LOGIC I/U PINS |                |           |     |  |

|------------------------------|----------------|-----------|-----|--|

| PIN                          | MSP            | IP        | LSP |  |

| X/LG                         | LG (OUT)       | ×         | x   |  |

| Y/LG                         | AG (OUT)       | Y         | Y   |  |

| <u>cco</u> /ov               | OVERFLOW (OUT) | CCO (OUT) |     |  |

TABLE 4 DUAL-FUNCTION LOGIC 1/O PINS

X AND Y ARE CARRY LOOK-AHEAD FUNCTIONS

### 2.3 CLOCK

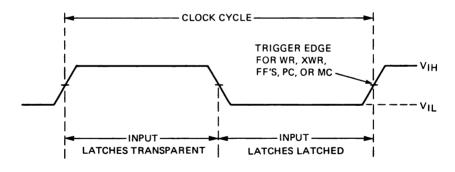

The clock synchronizes the entry or change of data in the 'S481 registers and counters, and it controls the status of the A and B input latches. A typical clock cycle is illustrated in Figure 2. The low-to-high transition of the clock input is the clocking edge for any combination of either the working register, extended working register, flag flip-flops, and the program counter or the memory counter activated by the resident operation. During the low-level portion of the clock input, both input latches are latched ensuring data stability at the positive clock transition. After the clock has gone to a high level, the input latches are placed in a transparent mode to accept the next set of input data.

#### FIGURE 2 - CLOCK CYCLE

#### 2.4 LATCHED DATA INPUT PORTS

The SN54S/74S481 features dual input ports combined with data flow paths which are designed specifically to reduce the number of system clock cycles needed to enter operands and/or data. Both the A and B input ports are latched, eliminating the need for external registers, to simplify interfacing directly with system data bus paths.

The A input port data is made available to both the input latch and the working register which allows A data to be loaded into the working register directly.

The B port is configured to serve as an input/output data path providing the capability to:

- a. Input data to the B latch

- b. Output sum-bus data.

This I/O port is designed specifically to simplify implementation of data transfers to the external working memory.

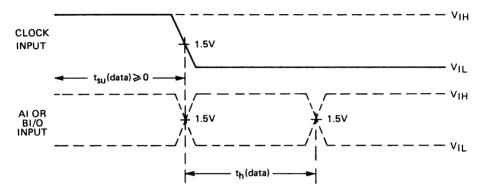

Both the A and B latches are transparent when the 'S481 clock input is high. Data applied at the A and B inputs should be stable anytime prior to or at least coincident with the falling edge of the clock input (see Figure 3). After the clock falling edge, the data inputs should be held steady for  $t_{hold(data)}$  or longer to facilitate the on-chip clock buffers to latch the data.

FIGURE 3 - INPUT LATCHES SETUP/HOLD TIMES

The A input port latch data is routed to the A input multiplexers, and the B input port latch data is sourced to both the A and B input multiplexers.

#### 2.5 A AND B OPERAND SOURCES

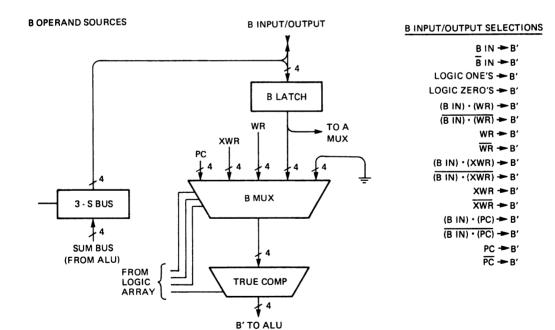

The A and B input multiplexers source the ALU A' and B' ports through true/complement conditional inverter circuits. Data routing for each, illustrated and listed in Figure 4, provides the ALU with access to the true or complement of:

#### ALU A' PORT

- 1. A input latch

- 2. B input latch

- 3. Working Register

- 4. Low logic level inputs

- (force zeros)

### ALU B' PORT

- 1. B input latch

- 2. Sum bus

- 3. Working register

- 4. Extended working register

- 5. Program counter

- 6. Low logic level inputs

- (force zeros)

The A and B multiplexers and true complement circuits, under control of the resident operation code, are selectable at the microprogram level. The number of A or B multiplexer sources available depend upon the specific operation being performed by the 'S481. Operation form descriptions contain detailed microprogramming.

The A and B input multiplexers, with selectable true and complement operand sources, maximizes the processing power of the 'S481 by minimizing the active components needed to achieve both the simple but highly flexible data routing tasks and full ALU capabilities.

A INPUT SELECTIONS  $A \text{ IN} \Rightarrow A'$   $\overline{A} \text{ IN} \Rightarrow A'$   $LOGIC ONE'S \Rightarrow A'$   $LOGIC ZERO'S \Rightarrow A'$   $B \text{ IN} \Rightarrow A'$   $\overline{B} \text{ IN} \Rightarrow A'$   $WR \Rightarrow A'$   $\overline{WR} \Rightarrow A'$

FIGURE 4 - ALU OPERAND SOURCES

#### 2.6 ARITHMETIC/LOGIC UNIT (ALU)

The 4-bit, parallel, binary arithmetic/logic unit provides the arithmetic/Boolean operand combination/modification mechanism including magnitude and overflow status. The ALU performs, as directed by the resident operation form, one of four basic functions which, when combined with the operand selections at the A and B multiplexers, extends the arithmetic/logic capabilities to that of a full 16-function ALU.

When compared to other bit-slice processor elements, unique to the 'S481 arithmetic architecture are the parallel input ports and fully microprogrammable symmetry for all ALU functions within the selections of the A and B input multiplexers.

Logical and arithmetic operation forms for the 'S481 are shown in Table 5. The full functional power of the 'S481 can be visualized only if it is understood that although both ALU's have parallel A and B input ports, the 'S481 architecture not only provides access to multiple sources but has the capability to route true or complement of any source to the A and B ALU port. This means that for a subtract operation, the subtrahend may be either an A or B input. In addition to maximizing data routing capabilities of the 'S481 at minimum logic/gate levels, this architecture permits fully symmetrical operations to be performed on the A or B sources within the selections offered by these 'S481 arithmetic/logical operation forms.

| DATA   | INPUT | TWO'S COMPLEMENT INTEGER ARITHMETIC OP'S |                         | LOGIC | AL OP'S (FO<br>CTN = H OR |        |

|--------|-------|------------------------------------------|-------------------------|-------|---------------------------|--------|

| A PORT | BPORT | CIN = L                                  | CIN - H                 | OR    | NOR                       | EX-NOR |

| ZEROS  | ZEROS | 1                                        | 0                       | ZEROS | ONES                      | ONES   |

| ZEROS  | ONES  | 0                                        | MINUS 1                 | ONES  | ZEROS                     | ZEROS  |

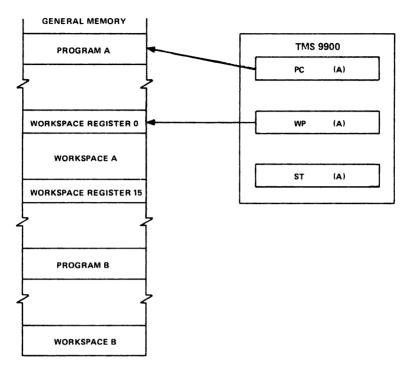

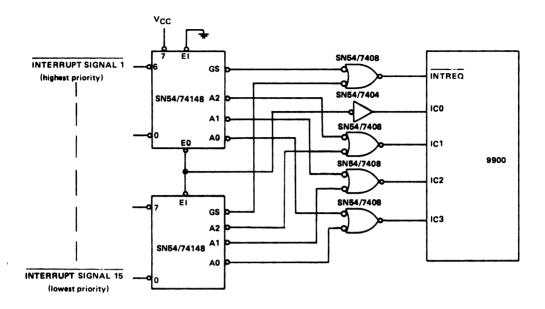

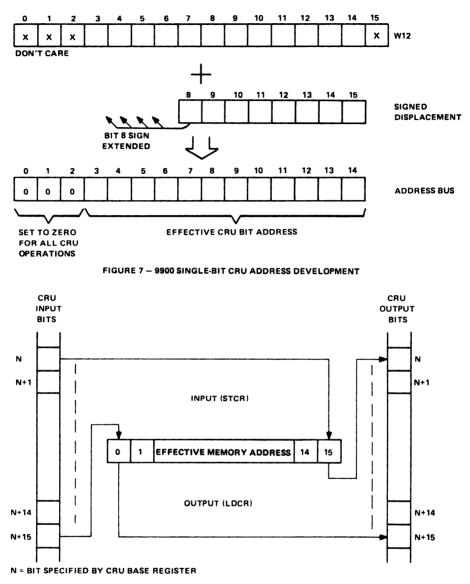

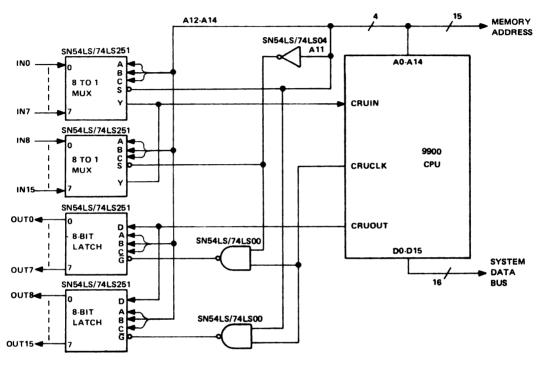

| ONES   | ZEROS | 0                                        | MINUS 1                 | ONES  | ZEROS                     | ZEROS  |