The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group

# TMS 9901 PROGRAMMABLE SYSTEMS INTERFACE

**JULY 1978**

# TEXAS INSTRUMENTS

#### IMPORTANT NOTICES

,

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

TI cannot assume any resposibility for any circuits shown or represent that they are free from patent infringement.

Copyright © 1978 Texas Instruments Incorporated

# TABLE OF CONTENTS

|             | 1.1         | Description of the second s |    |

|-------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1           |             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1  |

| 1           | 1.2         | Key Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1  |

| 1           | 1.3         | Application Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1  |

| 2.          | ARC         | HITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|             | 2.1         | CRU Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| _           | 2.2         | Interrupt Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|             | 2.3         | Input/Output Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| _           | 2.4         | Programmable Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -  |

| 2           | 2.6         | Power-Up Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 2           | 2.7         | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11 |

| 3. <i>I</i> | APP         | LICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| Э           | 3.1         | Hardware Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12 |

| Э           | 3.2         | Software Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13 |

| Э           | 3.3         | Interval Timer Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15 |

| 4. 1        | TMC         | 9901 ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|             |             | Absolute Maximum Ratings Over Operating Free Air                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|             | <b>T.</b> I | Temperature Range (Unless Otherwise Noted)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19 |

|             | 4.2         | Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|             | 4.3         | Electrical Characteristics Over Full Range of Recommended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10 |

| -           | 1.0         | Operating Conditions (Unless Otherwise Noted)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19 |

| 2           | 4.4         | Timing Requirements Over Full Range of Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19 |

|             | 4.5         | Switching Characteristics Over Full Range of Recommended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10 |

|             | 1.0         | Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20 |

| 5. N        | мес         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

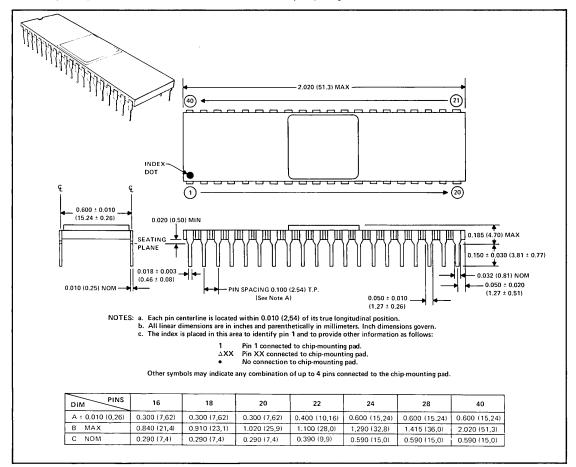

|             |             | TMS 9901 — 40 Pin Ceramic Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

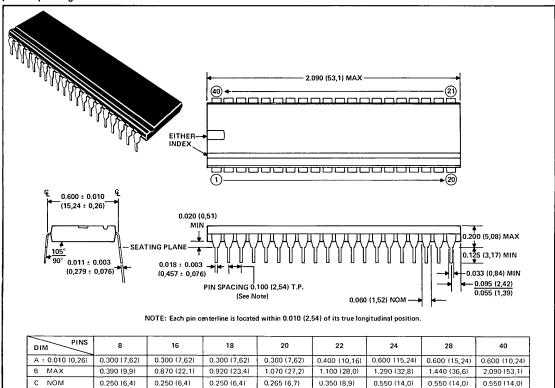

|             |             | TMS 9901 — 40 Pin Plastic Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|             |             | LIST OF ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| Figure      | 91          | Typical TMS 9901 Programmable System Interface (PSI) Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2  |

| Figure      |             | TMS 9901 PSI Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| Figure      |             | TMS 9901 PSI Interrupt Control Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

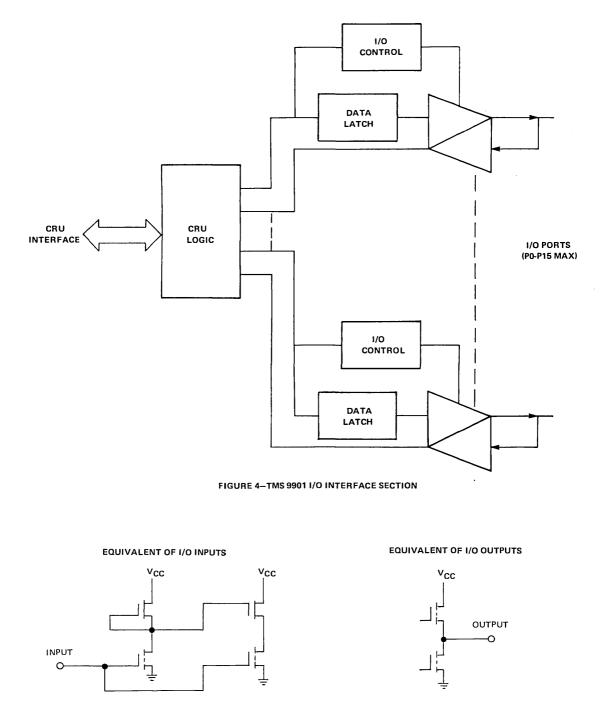

| Figure      |             | TMS 9901 I/O Interface Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| Figure      |             | Input and Output Equivalents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

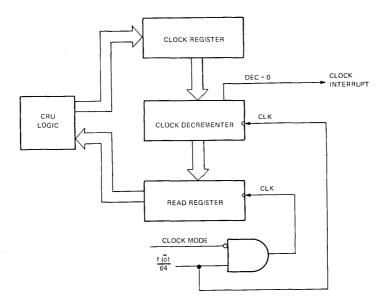

| Figure      | e 6         | TMS 9901 Interval Timer Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9  |

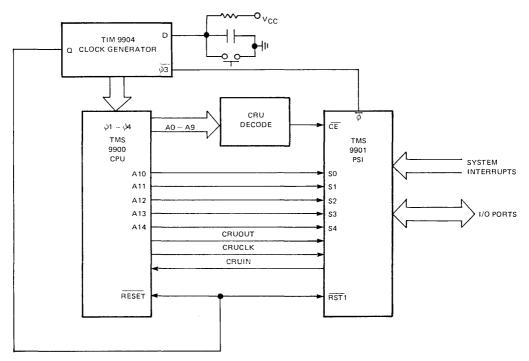

| Figure      | 97          | TMS 9900/TMS 9901 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12 |

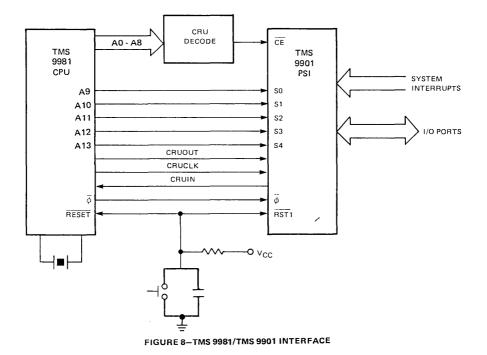

| Figure 8  | TMS 9981/TMS 9901 Interface                      | 13 |

|-----------|--------------------------------------------------|----|

| Figure 9  | TMS 9900 Sample Software To Control The TMS 9901 | 14 |

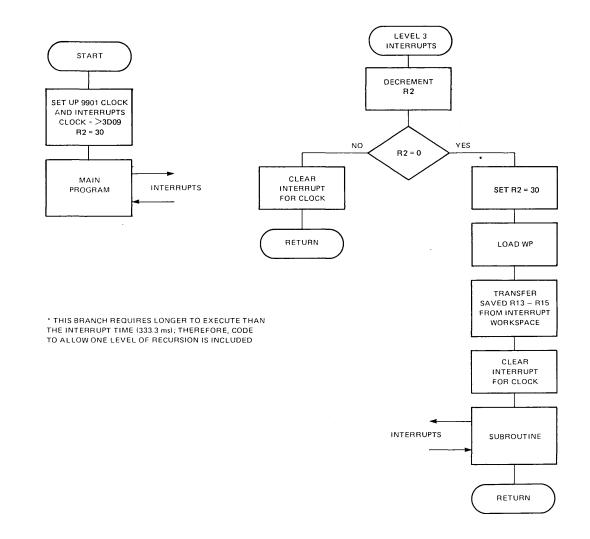

| Figure 10 | TMS 9901 Interval Timer Application Flowchart    | 16 |

| Figure 11 | Interval Timer                                   | 17 |

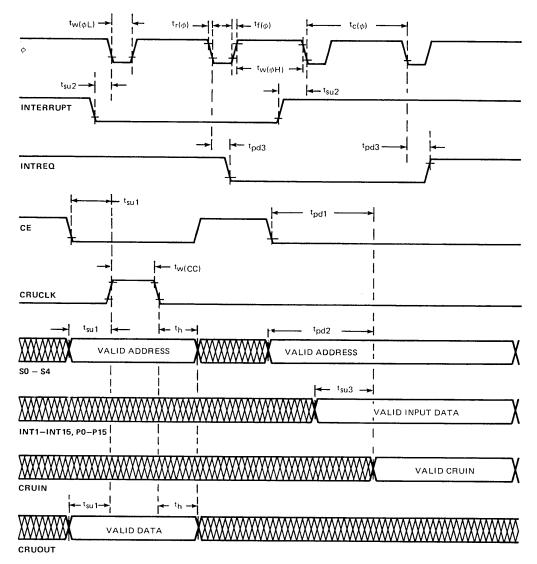

| Figure 12 | Switching Characteristics                        | 20 |

# LIST OF TABLES

| Table 1 | CRU Bit Assignments                        | 4  |

|---------|--------------------------------------------|----|

| Table 2 | Interrupt Code Generation                  | 4  |

| Table 3 | TMS 9980A or TMS 9981 Interrupt Level Data | 7  |

| Table 4 | TMS 9901 Pin Assignments and Functions     | 11 |

#### 1. INTRODUCTION

#### 1.1 DESCRIPTION

The TMS 9901 Programmable Systems Interface (PSI) is a multifunctional component designed to provide low cost interrupt and I/O ports and an interval timer for TMS 9900-family microprocessor systems. The TMS 9901 is fabricated using N-channel silicon-gate MOS technology. The TMS 9901 is TTL-compatible on all inputs and outputs, including the power supply (+5 V) and single-phase clock.

#### 1.2 KEY FEATURES

- Low Cost

- 9900-Family Peripheral

- Performs Interrupt and I/O Interface functions:

- Six Dedicated Interrupt Lines

- Seven Dedicated I/O Lines

- Nine Programmable Lines as I/O or Interrupt

- Up to 15 Interrupt Lines

- Up to 22 Input Lines

- Up to 16 Output Lines

- Easily Cascaded for Expansion

- Interval or Event Timer

- Single 5 V Power Supply

- All Inputs and Outputs TTL-Compatible

- Standard 40-Pin Plastic or Ceramic Package

- N-Channel Silicon-Gate MOS Technology.

#### 1.3 APPLICATION OVERVIEW

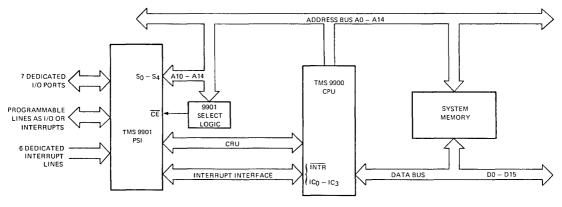

The following example of a typical application may help introduce the user to the TMS 9901 PSI. Figure 1 is a block diagram of a typical application. Each of the ideas presented below is described in more detail in later sections of this manual.

The TMS 9901 PSI interfaces to the CPU through the Communications Register Unit (CRU) and the interrupt control lines as shown in Figure 1. The TMS 9901 occupies 32 bits of CRU input and output space. The five least significant bits of address bus are connected to the S lines of the PSI to address one of the 32 CRU bits of the TMS 9901. The most significant bits of the address bus are decoded on CRU cycles to select the PSI by taking its chip enable (CE) line active (LOW).

Interrupt inputs to the TMS 9901 PSI are synchronized with  $\overline{\phi}$ , inverted, and then ANDed with the appropriate mask bit. Once every  $\overline{\phi}$  clock time, the prioritizer looks at the 15 interrupt input AND gates and generates the interrupt control code. The interrupt control code and the interrupt request line constitute the interrupt interface to the CPU.

After reset all I/O ports are programmed as inputs. By writing to any I/O port, that port will be programmed as an output port until another reset occurs, either software or hardware. Data at the input pins is buffered on to the TMS 9901. Data to the output ports is latched and then buffered off-chip by the PSI's MOS-to-TTL buffers.

The interval timer on the TMS 9901 is accessed by writing a ONE to select bit zero (control bit), which puts the PSI CRU interface in the clock mode. Once in the clock mode the 14-bit clock contents can be read or written. Writing to the clock register will reinitialize the clock and cause it to start decrementing,. When the clock counts to zero, it will cause an interrupt and reload to its initial value. Reading the clock contents permits the user to see the decrementer contents at that point in time just before entering the clock mode. The clock read register is not updated when the PSI is in the clock mode.

FIGURE 1- TYPICAL TMS 9901 PROGRAMMABLE SYSTEM INTERFACE (PSI) APPLICATION

# 2. ARCHITECTURE

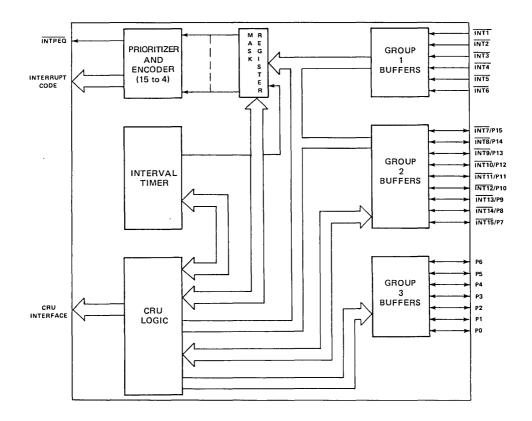

The architecture of the TMS 9901 Programmable Systems Interface (PSI) is designed to provide the user maximum flexibility when designating system I/O ports and interrupts. The TMS 9901 can be divided into four subsystems: CRU interface, interrupt interface, input/output interface, and interval timer. Figure 2 is a general block diagram of the TMS 9901 internal architecture. Each of the subsystems of the PSI is discussed in detail in subsequent paragraphs.

#### 2.1 CRU Interface

The CPU communicates with the TMS 9901 PSI via the CRU. The TMS 9901 occupies 32 bits in CRU read space and 32 bits in CRU write space. Table 1 shows the mapping for CRU bit addresses to TMS 9901 functions.

The CRU interface consists of five address select lines (S0-S4), chip enable ( $\overline{CE}$ ), and the three CRU lines (CRUIN, CRUOUT, CRUCLK). The select lines (S0-S4) are connected to the five least significant bits of the address bus; for a TMS 9900 system S0-S4 are connected to A10-A14, respectively. Chip enable ( $\overline{CE}$ ) is generated by decoding the most significant bits of the address bus on CRU cycles; for a 9900 based system address bits 0-9 would be decoded. When  $\overline{CE}$  goes active (LOW), the five select lines point to the CRU bit being accessed. When  $\overline{CE}$  is inactive (HIGH), the PSI's CRU interface is disabled.

#### NOTE

When  $\overline{CE}$  is inactive (HIGH) the 9901 sets its CRUIN pin to high impedance and disables CRUCLK from coming on chip. This means that CRUIN can be used as an OR tied bus. When  $\overline{CE}$  is high the 9901 will still see the select lines, but no command action is taken.

In the case of a write operation, the TMS 9901 strobes data off the CRUOUT line with CRUCLK. For a read operation, the data is sent to the CPU on the CRUIN line.

Several TMS 9901 devices may be cascaded to expand I/O and interrupt handling capability simply by connecting all CRU and address select lines in parallel and providing each device with a unique chip enable signal: the chip enable  $(\overline{CE})$  is generated by decoding the high-order address bits (A0-A9) on CRU cycles.

For those unfamiliar with the CRU concept, the following is a discussion of how to build a CRU interface. The CRU is a bit addressable (4096 bits), synchronous, serial interface over which a single instruction can transfer between one and 16 bits serially. Each one of the 4096 bits of the CRU space has a unique address and can be read and written to. During multi-bit CRU transfers, the CRU address is incremented at the beginning of each CRU cycle to point to the next consecutive CRU bit.

| CRU Bit | $S_0 S_1 S_2 S_3 S_4$ | CRU Read Data               | CRU Write Data             |

|---------|-----------------------|-----------------------------|----------------------------|

| 0       | 0 0 0 0               | CONTROL BIT(1)              | CONTROL BIT <sup>(1)</sup> |

| 1       | 0 0 0 0 1             | INT1/CLK1(2)                | Mask 1/CLK1(3)             |

| 2       | 0 0 0 1 0             | INT2/CLK2                   | Mask 2/CLK2                |

| 3       | 0 0 0 1 1             | INT3/CLK3                   | Mask 3/CLK3                |

| 4       | 0 0 1 0 0             | INT4/CLK4                   | Mask 4/CLK4                |

| 5       | 0 0 1 0 1             | INT5/CLK5                   | Mask 5/CLK5                |

| 6       | 0 0 1 1 0             | INT6/CLK6                   | Mask 6/CLK6                |

| 7       | 0 0 1 1 1             | INT7/CLK7                   | Mask 7/CLK7                |

| 8       | 0 1 0 0 0             | INT8/CLK8                   | Mask 8/CLK8                |

| 9       | 0 1 0 0 1             | INT9/CLK9                   | Mask 9/CLK9                |

| 10      | 0 1 0 1 0             | INT10/CLK10                 | Mask 10/CLK10              |

| 11      | 0 1 0 1 1             | INT11/CLK11                 | Mask 11/CLK11              |

| 12      | 0 1 1 0 0             | INT12/CLK12                 | Mask 12/CLK12              |

| 13      | 0 1 1 0 1             | INT13/CLK13                 | Mask 13/CLK13              |

| 14      | 0 1 1 1 0             | INT14/CLK14                 | Mask 14/CLK14              |

| 15      | 0 1 1 1 1             | INT15/INTREQ <sup>(7)</sup> | Mask 15/RST2(4)            |

| 16      | 10000                 | PO Input <sup>(5)</sup>     | PO Output(6)               |

| 17      | 1 0 0 0 1             | P1 Input                    | P1 Output                  |

| 18      | 1 0 0 1 0             | P2 Input                    | P2 Output                  |

| 19      | 1 0 0 1 1             | P3 Input                    | P3 Output                  |

| 20      | 1 0 1 0 0             | P4 Input                    | P4 Output                  |

| 21      | 10101                 | P5 Input                    | P5 Output                  |

| 22      | 10110                 | P6 Input                    | P6 Output                  |

| 23      | 1 0 1 1 1             | P7 Input                    | P7 Output                  |

| 24      | 1 1 0 0 0             | P8 Input                    | P8 Output                  |

| 25      | 1 1 0 0 1             | P9 Input                    | P9 Output                  |

| 26      | 1 1 0 1 0             | P10 Input                   | P10 Output                 |

| 27      | 1 1 0 1 1             | P11 Input                   | P11 Output                 |

| 28      | 1 1 1 0 0             | P12 Input                   | P12 Output                 |

| 29      | 1 1 1 0 1             | P13 Input                   | P13 Output                 |

| 30      | 1 1 1 1 0             | P14 Input                   | P14 Output                 |

| 31      | 1 1 1 1 1             | P15 Input                   | P15 Output                 |

TABLE 1 CRU SELECT BIT ASSIGNMENTS

NOTES:

(1)

(2)

0 = Interrupt Mode 1 = Clock Mode Data present on INT Input pin (or clock value) will be read regardless of mask value. While in the Interrupt Mode (Control Bit = 0) writing a "1" into mask will enable interrupt; a "0" will disable. Writing a zero to bit 15 while in the clock mode (Control Bit = 1) executes a software reset of the I/O pins. (3)

(4)

Data present on the pin will be read. Output data can be read without affecting the data. (5)

Writing data to the port will program the port to the output mode and output the data. INTREQ is the inverted status of the INTREQ pin. (6)

(7)

When a 99XX CPU executes a CRU Instruction, the processor uses the contents of workspace register 12 as a base address. (Refer to the 9900 Microprocessor Data Manual for a complete discussion on how CRU addresses are derived.) The CRU address is brought out on the 15-bit address bus; this means that the least significant bit of R12 is not brought out of the CPU. During CRU cycles, the memory control lines (MEMEN, WE, and DBIN) are all inactive; MEMEN being inactive (HIGH) indicates the address is not a memory address and therefore is a CRU address or external instruction code. Also, when MEMEN is inactive (HIGH) and a valid address is present, address bits A0-A2 must all be zero to constitute a valid CRU address; if address bits A0-A2 are other than all zeros, they are indicating an external instruction code. In summary, address bits A3-A14 contain the CRU address to be decoded, address bits A0-A2 must be zero and MEMEN must be inactive (HIGH) to indicate a CRU cycle.

#### 2.2 Interrupt Interface

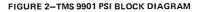

A block diagram of the interrupt control section is shown in Figure 3. The interrupt inputs (six dedicated,  $\overline{INT1}$ - $\overline{INT6}$ , and nine programmable) are sampled on the falling edge of  $\overline{\phi}$  and latched onto the chip for one  $\overline{\phi}$  time by the SYNC LATCH, each  $\overline{\phi}$  time. The output of the sync latch is inverted (interrupts are LOW active) and ANDed with its respective mask bit (MASK = 1, INTERRUPT ENABLED). On the rising edge of  $\overline{\phi}$ , the prioritizer and encoder senses the masked interrupts and produces a four-bit encoding of the highest priority interrupt present (see Tables 2 and 3). The four-bit prioritized code and INTREQ are latched off-chip with a sync latch on the falling edge of the next  $\overline{\phi}$ , which ensures proper synchronization to the processor.

Once an interrupt goes active (LOW), it should stay active until the appropriate interrupt service routine explicitly turns off the interrupt. If an interrupt is allowed to go inactive before the interrupt service routine is entered, an erroneous interrupt code could be sent to the processor. A total of five clock cycles occur between the time the CPU samples the INTREQ line and the time it samples the ICO-IC3 lines. For example, if an interrupt is active and the CPU recognizes that an interrupt is pending, but before the CPU can sample the interrupt control lines the interrupt goes inactive, the interrupt control lines will contain an incorrect code.

The interrupt mask bits on the TMS 9901 PSI are individually set or reset under software control. Any unused interrupt line should have its associated mask disabled to avoid false interrupts: To do this, the control bit (CRU bit zero), is first set to a zero for interrupt mode operation. Writing to TMS 9901 CRU bits 1-15 will enable or disable interrupts 1-15, respectively. Writing a one to an interrupt mask will *enable* that interrupt; writing a zero will *disable* that interrupt. Upon application of RST1 (power-up reset), all mask bits are reset (LOW), the interrupt code is forced to all zeros, and INTREQ is held HIGH. Reading TMS 9901 CRU bits 1-15 indicates the status of the respective interrupt inputs; thus, the designer can employ the unused (disabled) interrupt input lines as data inputs (true data in).

#### 2.3 Input/Output Interface

A block diagram of the TMS 9901 I/O interface is shown in Figure 4. Up to 16 individually controlled, I/O ports are available (seven dedicated, P0-P6, and nine programmable) and, as discussed above, the unused dedicated interrupt lines also can be used as input lines (true data in). Thus the 9901 can be configured to have more than 16 inputs. RST1 (power-up reset) will program all I/O ports to input mode. Writing data to a port will automatically switch that port to the output mode. Once programmed as an output, a port will remain in output mode until RST1 or RST2 (command bit) is executed. An output port can be read and indicates the present state of the pin. A pin programmed to the output mode *cannot* be used as an input pin: *Applying an input current to an output pin may cause damage to the TMS 9901*. The TMS 9901 outputs are latched and buffered off-chip, and inputs are buffered onto the chip. The output buffers are MOS-to-TTL buffers and can drive two standard TTL loads.

FIGURE 3- TMS 9901 PSI INTERRUPT CONTROL SECTION BLOCK DIAGRAM

ი

| INTERRUPT/STATE | PRIORITY    | ICO | <sup>1</sup> C1 | IC2 | IC3 | INTREQ |

|-----------------|-------------|-----|-----------------|-----|-----|--------|

| RST 1           | -           | 0   | 0               | 0   | 0   | 1      |

| INT 1           | 1 (HIGHEST) | 0   | 0               | 0   | 1   | 0      |

| INT 2           | 2           | 0   | 0               | 1   | 0   | 0      |

| INT 3/CLOCK     | 3           | 0   | 0               | 1   | 1   | 0      |

| INT 4           | 4           | 0   | 1               | 0   | 0   | 0      |

| INT 5           | 5           | 0   | 1               | 0   | 1   | 0      |

| INT 6           | 6           | 0   | 1               | 1   | 0   | 0      |

| INT 7           | 7           | 0   | 1               | 1   | 1   | 0      |

| INT 8           | 8           | 1   | 0               | 0   | 0   | 0      |

| INT 9           | 9           | 1   | 0               | 0   | 1   | 0      |

| INT 10          | 10          | 1   | 0               | 1   | 0   | 0      |

| INT 11          | 11          | 1   | 0               | 1   | 1   | · 0    |

| INT 12          | 12          | 1   | 1               | 0   | 0   | 0      |

| INT 13          | 13          | 1   | 1               | 0   | 1   | 0      |

| INT 14          | 14          | 1   | 1               | 1   | 0   | 0      |

| INT 15          | 15 (LOWEST) | 1   | 1               | 1   | 1   | 0      |

| NO INTERRUPT    | -           | 1   | 1               | 1   | 1   | 1      |

TABLE 2 INTERRUPT CODE GENERATION

TABLE 3 TMS 9980A OR TMS 9981 INTERRUPT LEVEL DATA

| INTERRUPT<br>CODE<br>(IC0–IC2) | FUNCTION | VECTOR LOCATION<br>(MEMORY ADDRESS<br>IN HEX) | DEVICE ASSIGNMENT | INTERRUPT MASK VALUES<br>TO ENABLE<br>(ST12 THROUGH ST15) |  |

|--------------------------------|----------|-----------------------------------------------|-------------------|-----------------------------------------------------------|--|

| 1 1 0                          | Level 4  | 0 0 1 0                                       | External Device   | 4 Through F                                               |  |

| 101                            | Level 3  | 0 0 0 C                                       | External Device   | 3 Through F                                               |  |

| 1 0 0                          | Level 2  | 0 0 0 8                                       | External Device   | 2 Through F                                               |  |

| 0 1 1                          | Level 1  | 0 0 0 4                                       | External Device   | 1 Through F                                               |  |

| 0 0 1                          | Reset    | 0 0 0 0                                       | Reset Stimulus    | Don't Care                                                |  |

| 0 1 0                          | Load     | 3 F F C                                       | Load Stimulus     | Don't Care                                                |  |

| 000                            | Reset    | 0 0 0 0                                       | Reset Stimulus    | Don't Care                                                |  |

| 1 1 1                          | No-Op    |                                               |                   |                                                           |  |

FIGURE 5 - INPUT AND OUTPUT EQUIVALENTS

#### 2.4 Programmable Ports

A total of nine pins ( $\overline{INT7}/P15$ - $\overline{INT15}/P7$ ) on the TMS 9901 are user-programmable as either I/O ports or interrupts. These pins will assume all characteristics of the type pin they are programmed to be (as described in Sections 2.2 and 2.3). Any pin which is not being used for interrupt should have the appropriate interrupt mask disabled (mask = 0) to avoid erroneous interrupts to the CPU. To program one of the pins as an interrupt, its interrupt mask simply is enabled and the line may be used as if it were one of the dedicated interrupt lines. To program a pin as an I/O port, disable the interrupt mask and use that pin as if it were one of the dedicated I/O ports.

#### 2.5 Interval Timer

Figure 6 is a block diagram of the TMS 9901 interval timer section. The clock consists of a 14-bit counter that decrements at a rate of  $f(\overline{\phi})/64$  (at 3 MHz this results in a maximum interval of 349 milliseconds with a resolution of 21.3 microseconds). The clock can be used as either an interval timer or an event timer. To access the clock, select bit zero (control bit) must be set to a one. The clock is enabled to cause interrupts by writing a nonzero value to it and is then disabled from interrupting by writing zero to it or by a RST1. The clock starts operating at no more than two  $\phi$  times after it is loaded. When the clock decrementer is running, it will decrement down to zero and issue a level-3 interrupt. The decrementer, when it becomes zero, will also be reloaded from the clock register and decrementing will start again. (The zero state is counted as any other decrementer state.) The decrementer always runs, but it will not issue interrupts unless enabled; of course, the contents of the unenabled clock read register are meaningless.

FIGURE 6-TMS 9901 INTERVAL TIMER SECTION

The clock is accessed by writing a one into the control bit (TMS 9901 CRU bit zero) to force CRU bits 1-15 to clock mode. Writing a nonzero value into the clock register then enables the clock and sets its time period. When the clock is enabled, it interrupts on level 3 and external level-3 interrupts are disabled. The mask for level 3 in the PSI must be set to a one so that the processor will see the clock interrupt. When the clock interrupt is active, the clock mask (mask bit 3) must be written into with either a one or zero to clear the interrupt; writing a zero also disables further interrupts.

If a new clock value is required, a new 14-bit clock start value can be programmed by executing a CRU write operation to the clock register. During programming, the decrementer is restarted with the current start value after each start value bit is written. A timer restart is easily implemented by writing a single bit to any of the clock bits. The clock is disabled by  $\overrightarrow{\text{RST1}}$  (power up reset) or by writing a zero value into the clock register;  $\overrightarrow{\text{RST2}}$  does not affect the clock.

The clock read register is updated every time the decrementer decrements when the TMS 9901 is not in clock mode. There are two methods to leave the clock mode : first, a zero is written to the control bit; or second, a TMS 9901 select bit greater than 15 is accessed. Note that when  $\overline{CE}$  is inactive(HIGH), the PSI is not disabled from seeing the select lines. As the CPU is addressing memory, A10-A14 could very easily have a value of 15 or greater — A10-A14 are connected to the select lines; therefore, the TMS 9901 interval timer section can "think" it is out of clock mode and update the clock read register. Very simply, this means that a value cannot be locked into the clock read register by writing a one to CRU select bit zero (the control bit). The 9901 must be out of clock mode for at least one timer period to ensure that the contents of the clock read register has been updated. This means that to read the most recent contents of the decrementer, just before reading, the TMS 9901 *must* not be in the clock mode. The only sure way to manipulate clock mode is to use the control bit (select bit zero). When clock mode is reentered to access the clock read register, updating of the read register will cease. This is done so that the contents of the clock read register, updating of the read register will cease.

#### 2.6 Power-Up Considerations

During hardware reset, RST1 must be active (LOW) for a minimum of two clock cycles to force the TMS 9901 into a known state. RST1 will disable all interrupts, disable the clock, program all I/O ports to the input mode, and force ICO-IC3 to all zeros with INTREQ held HIGH. The system software must enable the appropriate interrupts, program the clock, and configure the I/O ports as required. After initial power-up the TMS 9901 is accessed only as needed to service the clock, enable (disable) interrupts, or read (write) data to the I/O ports. The I/O ports can be reconfigured by use of the RST2 software reset command bit.

# 2.7 Pin Descriptions

Table 4 defines the TMS 9901 pin assignments and describes the function of each pin.

TABLE 4

TMS 9901 PIN ASSIGNMENTS AND FUNCTIONS

| SIGNATURE              | PIN      | I/O        | DESCRIPTION                                                                                                                                 |                      |               |                 |                       |

|------------------------|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|-----------------|-----------------------|

|                        |          |            |                                                                                                                                             | <del></del>          |               |                 |                       |

| INTREO                 | 11       | OUT        |                                                                                                                                             | RST1                 | 1             | 40              | Vcc                   |

|                        |          |            | INTREQ indicates that an enabled interrupt<br>has been received. INTREQ will stay active                                                    | CRUOUT               | 2             | 39              | so                    |

|                        |          |            | until all enabled interrupt inputs are re-                                                                                                  | CRUCLK               | 3             | 38              | PO                    |

|                        |          |            | moved.                                                                                                                                      | CRUIN                | 4             | 37              | P1                    |

| ICO (MSB)              | 15       | оυт        |                                                                                                                                             | · CE                 | 5 [           | 36              | S1                    |

| IC1                    | 14       | OUT        |                                                                                                                                             | INT6                 | 6 [           | 35              | S2                    |

| IC2                    | 13       | OUT        |                                                                                                                                             | INT5                 | 7 [           | 34              | INT7/P15              |

| IC3 (LSB)              | 12       | OUT        |                                                                                                                                             | INT4                 | 8 []          | 33              | INT8/P14              |

| CE                     | 5        | IN         | Chip Enable. When active (low) data may be                                                                                                  | INT3                 | 9 🛛           | 32              | INT9/P13              |

|                        |          |            | transferred through the CRU interface to                                                                                                    | ,                    | 10            | 31              | INT10/P12             |

|                        |          |            | the CPU, CE has no effect on the interrupt                                                                                                  | INTREO               | a             | 30              | INT11/P11             |

|                        |          |            | control section.                                                                                                                            | 103                  | 리             | 29              | INT12/P10<br>INT13/P9 |

| S0                     | 39       | IN         | Address select lines. The data bit being                                                                                                    | IC2                  | 리             | 20              | INT 14/P8             |

| S1                     | 36       | IN         | accessed by the CRU interface is specified                                                                                                  | 100                  |               | 26              | P2                    |

| S2                     | 35       | IN         | by the 5-bit code appearing on S0-S4.                                                                                                       | V <sub>SS</sub>      | 귀             | 25              | S3                    |

| S3                     | 25       | IN         |                                                                                                                                             |                      |               | 24              |                       |

| S4                     | 24       | IN         |                                                                                                                                             | INT2                 | ~             | 23              |                       |

| CRUIN                  | 4        | OUT        | · · · ·                                                                                                                                     | P6                   | -             | 22              | P3                    |

| •                      |          | 1          | S0-S4 is transmitted to the CPU by CRUIN.                                                                                                   | P5                   | 20            | 21              | P4                    |

|                        |          |            | When CE is not active CRUIN is in a high-                                                                                                   |                      | u             |                 |                       |

|                        |          |            | impedance state.                                                                                                                            |                      |               |                 |                       |

| CRUOUT                 | 2        | IN         | CRU data out (from CPU). When CE is activ<br>CRUCLK and written into the command bit spe                                                    |                      | the CRUO      | UT input wil    | I be sampled during   |

| CRUCLK                 | 3        | IN         | CRU Clock (from CPU). CRUCLK specifies that                                                                                                 | valid data is preser | t on the CR   | UOUT line.      |                       |

| RST1                   | 1        | IN         | Power Up Reset. When active (low) RST1 res<br>INTERQ = 1, disables the clock, and prograr<br>allow implementation with an RC circuit as sho | ns all 1/0 ports to  |               |                 |                       |

| Vcc                    | 40       |            | Supply Voltage. +5 V nominal.                                                                                                               |                      |               |                 |                       |

| V <sub>SS</sub>        | 16       |            | Ground Reference                                                                                                                            |                      |               |                 |                       |

| $\overline{\phi}$      | 10       | IN         | System clock (\$\vec{\alpha}\$3 in TMS 9900 system, CKOUT                                                                                   | in TMS 9980 syste    | m).           |                 |                       |

| INT1                   | 17       | IN         | ר - ,                                                                                                                                       |                      |               |                 |                       |

| INT2                   | 18       | IN         | Group 1, interrupt inputs.                                                                                                                  |                      |               |                 |                       |

| INT3                   | 9        | IN         | When active (Low) the signal is ANDed with it                                                                                               | s corresponding      |               |                 |                       |

| INT4                   | 8        | IN         | mask bit and if enabled sent to the interrupt co                                                                                            |                      |               |                 |                       |

| INT5                   | 7        | IN         | INT1 has highest priority.                                                                                                                  |                      |               |                 |                       |

| INT6                   | 6        | IN         |                                                                                                                                             |                      |               |                 |                       |

| INT7/ P15              | 34       | 1/0        |                                                                                                                                             |                      |               |                 |                       |

| INT8/ P14              | 33       | 1/0        |                                                                                                                                             |                      |               |                 |                       |

| INT9/ P13<br>INT10/P12 | 32<br>31 | 1/0<br>1/0 |                                                                                                                                             |                      |               |                 |                       |

| INT11/P11              | 30       | 1/0        | Group 2, programmable interrupt (active low)                                                                                                | or I/O pins (true lo | gic). Each p  | in is individua | ally programmable as  |

| INT12/P10              | 29       | 1/0        | an interrupt, an input port, or an output port.                                                                                             |                      |               |                 |                       |

| INT13/P9               | 28       | 1/0        |                                                                                                                                             |                      |               |                 |                       |

| INT14/P8               | 27       | 1/0        |                                                                                                                                             |                      |               |                 |                       |

| INT15/P7               | 23       | 1/0        | J                                                                                                                                           |                      |               |                 |                       |

| PO                     | 38       | 1/0        | ĥ                                                                                                                                           |                      |               |                 |                       |

| P1                     | 37       | 1/0        |                                                                                                                                             |                      |               |                 |                       |

| P2                     | 26       | 1/0        |                                                                                                                                             |                      |               |                 |                       |

| P3                     | 22       | 1/0        | Group 3, I/O ports (true logic). Each pin is indiv                                                                                          | idually programma    | ble as an inp | out port or an  | output port.          |

| P4                     | 21       | I/O        |                                                                                                                                             |                      |               |                 |                       |

| P5                     | 20       | 1/0        |                                                                                                                                             |                      |               |                 |                       |

| P6                     | 19       | 1/0        | μ                                                                                                                                           |                      |               |                 |                       |

|                        |          |            | •                                                                                                                                           |                      |               |                 |                       |

#### 3. APPLICATIONS

#### 3.1 Hardware Interface

Figure 7 illustrates the use of a TMS 9901 PSI in a TMS 9900 system. The TIM 9904 clock generator/driver syncs the RESET for both the TMS 9901 and the CPU. The RC circuit on the TIM 9904 provides the power-up and pushbutton RESET input to the clock chip. Address lines A0-A9 are decoded on CRU cycles to select the TMS 9901. Address lines A10-A14 are sent directly to PSI select lines S0-S4, respectively, to select which TMS 9901 CRU bit is to be accessed.

Figure 8 illustrates the use of a TMS 9901 with a TMS 9981 CPU. No TIM 9904 is needed with the TMS 9981, so the reset circuitry is connected directly to the system reset line. The clock  $(\overline{\phi})$  then comes from the TMS 9981. All other circuitry is identical to the TMS 9900 system.

FIGURE 7-TMS 9900/TMS 9901 INTERFACE

#### 3.2 Software Interface

Figure 9 lists the TMS 9900 code needed to control the TMS 9901 PSI. The code initializes the PSI to an eight-bit input port, an eight-bit output port, and enables interrupt levels 1-6. The six dedicated interrupt pins are all used for interrupts; their mask bits are set ON. The nine programmable pins are all used as I/O ports; mask bits 7-15 remain reset. P0-P7 are programmed as an eight-bit output port, and P8-P15 are programmed as an eight-bit input port.

Some code is added to read the contents of the clock read-register. The SBZ instruction takes the TMS 9901 out of clock mode long enough for the clock read register to be updated with the most recent decrementer value. When clock mode is reentered, the decrementer will cease updating the clock read-register so that the contents of the register will not be changing during a read operation.

The second section of code is typical code found in a clock interrupt service routine. All interrupts initially are disabled by the routine. These functions are not necessary, but are usually done to ensure system integrity. The interrupt mask should be restored as soon as the sensitive processing is complete. The interrupt is counted in the variable COUNT and is then cleared by writing a one to mask bit 3. If a zero is written to mask bit 3 to clear the interrupt, clock interrupt will be disabled from that point onward, but the clock will continue to run.

#### ASSUMPTION:

- System uses clock at maximum interval (349 msec @ 3MHz)

- Interrupts 1-6 are used

- Eight bits are used as an output port , P0 P7

- Eight bits are used as an input port , P8 P15

- RST1 (power-up reset) has been applied

- The most significant byte of R1 contains data to be output.

|        | LI                                    | R12, PSIBAS                           | Set up CRU base to point to 9901                                                                                                                                                      |

|--------|---------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | LDCR                                  | @CLKSET, 0                            | 16-bit transfer, set clock to max interval                                                                                                                                            |

|        | LDCR                                  | @INTSET, 7                            | Enter interrupt mode and enable interrupts $1-6$                                                                                                                                      |

|        | LI                                    | R12, PSIBAS+32                        | Set CRU base to I/O ports — output                                                                                                                                                    |

|        | LDCR                                  | R1, 8                                 | Output byte from R1, program ports 0 — 7 as output                                                                                                                                    |

|        | LI                                    | R12, PSIBAS+48                        | Set CRU base to I/O ports — input                                                                                                                                                     |

|        | STCR                                  | R2, 8                                 | Store a byte from input port into MSBT of R2                                                                                                                                          |

|        | LI                                    | R 12, PSIBAS                          | Set CRU base to 9901                                                                                                                                                                  |

|        | SBZ                                   | 0                                     | Leave clock mode so decremented contents can be latched                                                                                                                               |