The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group

# TMS 9900 Microprocessor Data Manual

**MAY 1976**

Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patents or rights of others that may result from its use. No license is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

Copyright © 1976 Texas Instruments Incorporated

# TABLE OF CONTENTS

| 1. | INT        | RODUCI     | ΓΙΟΝ          |            |        |        |      |       |      |      |     |   | · |   |   |     |   |   |   |   |   |   |   |     |     |    |   |    |

|----|------------|------------|---------------|------------|--------|--------|------|-------|------|------|-----|---|---|---|---|-----|---|---|---|---|---|---|---|-----|-----|----|---|----|

|    | 1.1        |            | on            |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 3  |

|    | 1.2        | -          | ures          |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 3  |

|    | 1.2        | itey i cut |               |            | •••    | • •    | ·    | •     | • •  | ·    | ·   | • | • | • | • | • • | • | · | • | • | • | · | · | •   | ·   | •  | • | Ŭ  |

| 2. | AR         | CHITECT    | URE           |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   |    |

|    | 2.1        | Registers  | and Memo      | ry         |        |        |      |       |      |      |     |   |   | • |   |     |   |   |   |   |   |   |   |     |     |    |   | 3  |

|    | 2.2        |            | s             |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 6  |

|    | 2.3        | Input/Ou   | tput          |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   | - |   |   |   |   |     |     |    |   | 7  |

|    | 2.4        |            | CRU Oper      |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 8  |

|    | 2.5        | -          | Bit CRU O     |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 8  |

|    | 2.6        | •          | Instruction   |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 10 |

|    | 2.7        | Load Fur   |               | · · ·      |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     | •   | •  | • | 11 |

|    | 2.7        |            |               |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     | •   | •  | • | 13 |

|    | 2.0<br>2.9 |            | 0 Pin Desc    |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   |    |

|    | 2.9        | -          |               |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 15 |

|    |            |            | Memory .      |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 15 |

|    |            |            | Hold          |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 15 |

|    |            | 2.9.3      | CRU           | • • •      | •••    | • •    | ·    | •     | • •  | ·    | •   | ٠ | · | · | • | • • | • | ٠ | · | ٠ | · | · | · | ٠.  | •   | •  | · | 18 |

| 3. | TNA        |            | ISTRUCT       |            | т      |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   |    |

| з. | 3.1        |            |               |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 18 |

|    | 3.1        |            | n<br>ng Modes |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 18 |

|    | J.Z        |            | ų.            |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   |    |

|    |            |            | Workspace     |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 18 |

|    |            |            | Workspace     | -          |        |        |      | -     | -    |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 18 |

|    |            |            | Workspace     |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 18 |

|    |            |            | Symbolic (I   |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 20 |

|    |            |            | Indexed Ad    |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 20 |

|    |            | 3.2.6      | Immediate     | Addressin  | g.     |        | •    |       |      |      |     |   |   |   | • |     | • |   |   |   |   |   |   |     |     |    | • | 20 |

|    |            |            | Program Co    |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 20 |

|    |            | 3.2.8      | CRU Relati    | ve Addres  | ssing  |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 20 |

|    | 3.3        |            | d Definitio   |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 21 |

|    | 3.4        | Status Re  |               |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 21 |

|    | 3.5        | Instructio | 0             |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 22 |

|    | 0.0        |            | Dual Opera    |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 22 |

|    |            |            | Dual Opera    |            |        |        |      |       |      |      |     | • |   |   |   |     |   |   |   |   |   |   |   | per | anc | 1. | • | 22 |

|    |            | 0.0.2      |               | kspace Re  |        |        |      |       |      |      |     | - |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 23 |

|    |            | 252        |               |            | •      |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   |    |

|    | ,          |            | Extended C    | •          |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 24 |

|    |            |            | Single Oper   |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 24 |

|    |            |            | CRU Multip    |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 25 |

|    |            |            | CRU Single    |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 25 |

|    |            |            | Jump Instru   |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 25 |

|    |            |            | Shift Instru  |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 26 |

|    |            | 3.5.9      | Immediate     | Register I | nstru  | ction  | ıs.  |       |      | •    |     | • | • | • | • |     | • |   |   | - |   | • | • | •   | •   |    | • | 26 |

|    |            | 3.5.10     | Internal Re   | gister Loa | ıd Im  | medi   | ate  | Instr | ucti | ions |     |   |   |   |   |     |   |   |   |   |   | • |   |     |     |    |   | 27 |

|    |            | 3.5.11     | Internal Re   | gister Sto | re Ins | struct | ions | з.    |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 27 |

|    |            |            | Return Wor    |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 27 |

|    |            | 3.5.13     | External In   | structions |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 27 |

|    | 3.6        |            | 0 Instructio  |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 28 |

|    |            |            |               |            |        |        |      |       |      |      | _ · |   |   |   |   | _   |   |   |   |   |   |   |   |     |     |    |   |    |

| 4. |            |            | LECTRIC       |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   |    |

|    | 4.1        |            | Maximum       |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 29 |

|    | 4.2        |            | ended Oper    | •          |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 30 |

|    | 4.3        |            | Characteri    |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 30 |

|    | 4.4        |            | equirement    |            |        |        |      |       |      |      |     |   |   |   |   |     |   |   |   |   | • | • | • | •   | •   | •  |   | 31 |

|    | 4.5        | Switching  | g Characteri  | istics .   |        |        |      | •     |      |      |     |   |   |   |   |     |   |   |   |   |   |   |   |     |     |    |   | 31 |

1

# TABLE OF CONTENTS (Continued)

| 5. | TMS | 9900 PRO    | то  | TΥ | PII | NG | S'  | YS | TE | EM |   |  |   |   |   |  |   |  |  |  |   |   |    |   |   |  |    |

|----|-----|-------------|-----|----|-----|----|-----|----|----|----|---|--|---|---|---|--|---|--|--|--|---|---|----|---|---|--|----|

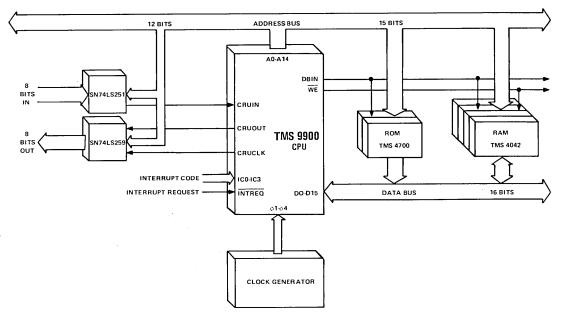

|    | 5.1 | Hardware .  |     |    |     |    |     |    |    |    |   |  |   |   |   |  |   |  |  |  |   |   |    |   |   |  | 32 |

|    |     | System Cons |     |    |     |    |     |    |    |    |   |  |   |   |   |  |   |  |  |  |   |   |    |   |   |  |    |

|    | 5.3 | Software .  | •   |    |     |    | •   |    |    |    |   |  |   |   |   |  |   |  |  |  |   |   |    |   |   |  | 33 |

|    | 5.4 | Options     | •   |    |     |    |     | •  |    |    |   |  |   |   |   |  |   |  |  |  |   |   |    | • | • |  | 33 |

| 6. | TMS | 9900 SUPI   | POF | ۲  | CI  | RC | ะบเ | TS | 5  |    | • |  | • |   | • |  |   |  |  |  | • |   | ·. |   |   |  | 34 |

| 7. | SYS | TEM DESIG   | GΝ  | EX | A   | ŴР | LE  | S  | •  |    | • |  | • | • |   |  | • |  |  |  | • | • |    |   |   |  | 34 |

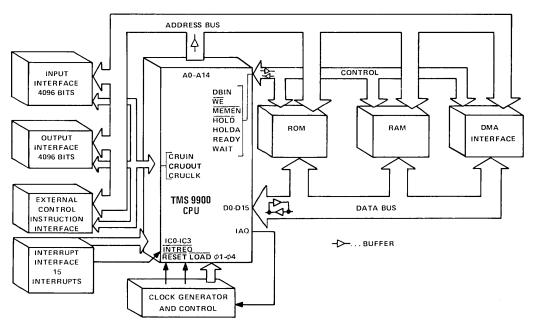

| 8. | MEC | HANICAL     | DA  | ТА | ٩   |    |     |    |    |    |   |  |   |   |   |  |   |  |  |  |   |   |    |   |   |  | 36 |

# LIST OF ILLUSTRATIONS

| Figure 1  | Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5  |

| Figure 3  | TMS 9900 Interrupt Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8  |

| Figure 4  | TMS 9900 Single-Bit CRU Address Development     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     .     . <td>9</td> | 9  |

| Figure 5  | TMS 9900 LDCR/STCR Data Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9  |

| Figure 6  | TMS 9900 16-Bit Input/Output Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10 |

| Figure 7  | External Instruction Decode Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 |

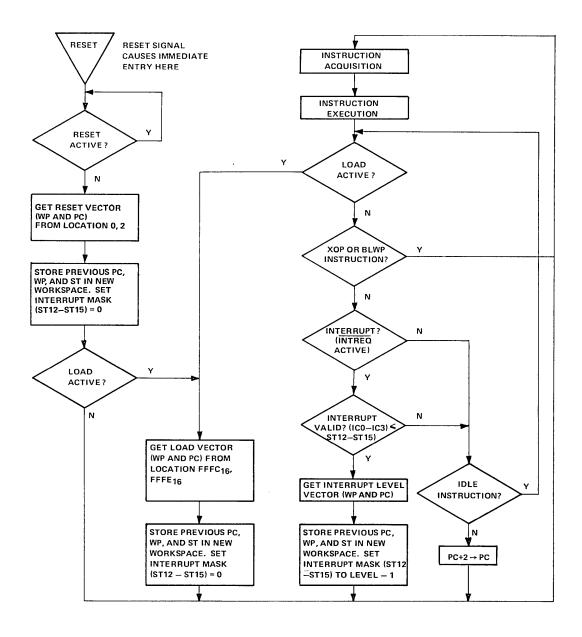

| Figure 8  | TMS 9900 CPU Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12 |

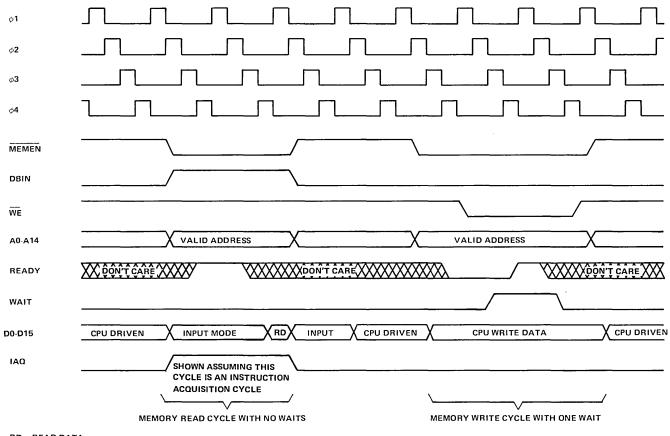

| Figure 9  | TMS 9900 Memory Bus Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16 |

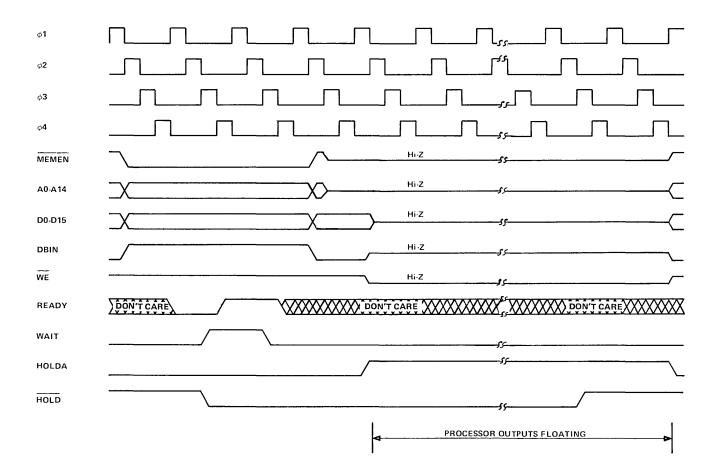

| Figure 10 | TMS 9900 Hold Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17 |

| Figure 11 | TMS 9900 CRU Interface Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19 |

| Figure 12 | Clock Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31 |

| Figure 13 | Signal Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32 |

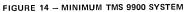

| Figure 14 | Minimum TMS 9900 System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35 |

| Figure 15 | Maximum TMS 9900 System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35 |

# LIST OF TABLES

| Table 1 | Interrupt Level Data                   |  |  |  |  |  |  |  |  |  |  |  | 7  |

|---------|----------------------------------------|--|--|--|--|--|--|--|--|--|--|--|----|

| Table 2 | TMS 9900 Pin Assignments and Functions |  |  |  |  |  |  |  |  |  |  |  | 13 |

| Table 3 | Instruction Execution Times            |  |  |  |  |  |  |  |  |  |  |  | 28 |

.

# 1. INTRODUCTION

#### 1.1 DESCRIPTION

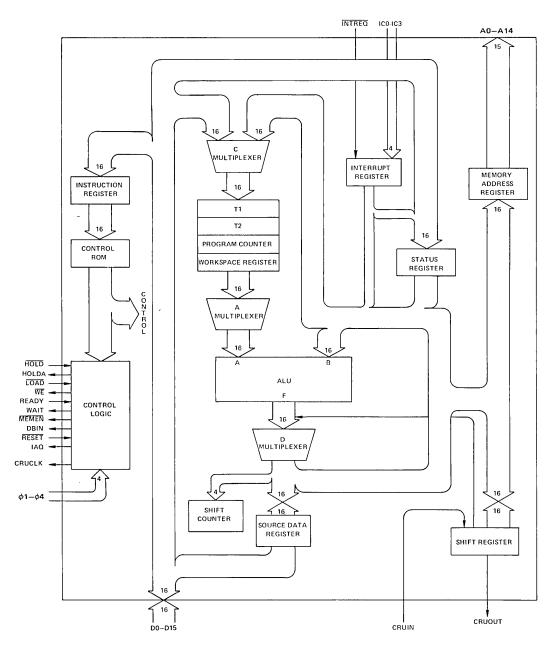

The TMS 9900 microprocessor is a single-chip 16-bit central processing unit (CPU) produced using N-channel silicon-gate MOS technology (see Figure 1). The instruction set of the TMS 9900 includes the capabilities offered by full minicomputers. The unique memory-to-memory architecture features multiple register files, resident in memory, which allow faster response to interrupts and increased programming flexibility. The separate bus structure simplifies the system design effort. Texas Instruments provides a compatible set of MOS and TTL memory and logic function circuits to be used with a TMS 9900 system. The system is fully supported by software and a complete prototyping system.

#### 1.2 KEY FEATURES

- 16-Bit Instruction Word

- Full Minicomputer Instruction Set Capability Including Multiply and Divide

- Up to 65,536 Bytes of Memory

- 3-MHz Speed

- Advanced Memory-to-Memory Architecture

- Separate Memory, I/O, and Interrupt-Bus Structures

- 16 General Registers

- 16 Prioritized Interrupts

- Programmed and DMA I/O Capability

- N-Channel Silicon-Gate Technology

# 2. ARCHITECTURE

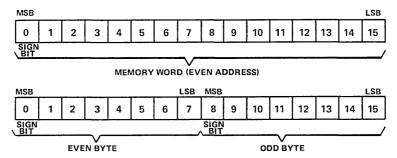

The memory word of the TMS 9900 is 16 bits long. Each word is also defined as 2 bytes of 8 bits. The instruction set of the TMS 9900 allows both word and byte operands. Thus, all memory locations are on even address boundaries and byte instructions can address either the even or odd byte. The memory space is 65,536 bytes or 32,768 words. The word and byte formats are shown below.

#### 2.1 REGISTERS AND MEMORY

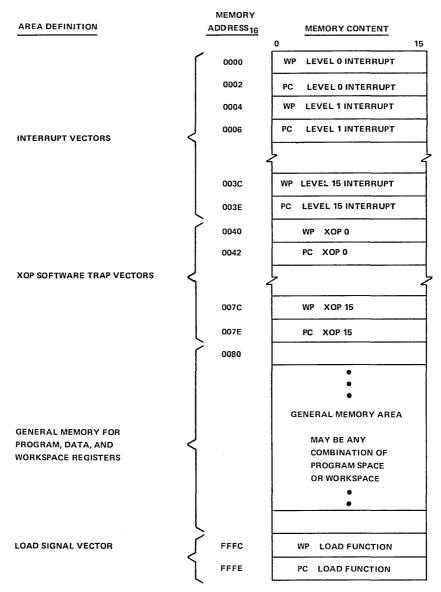

The TMS 9900 employs an advanced memory-to-memory architecture. Blocks of memory designated as workspace replace internal-hardware registers with program-data registers. The TMS 9900 memory map is shown in Figure 2. The first 32 words are used for interrupt trap vectors. The next contiguous block of 32 memory words is used by the extended operation (XOP) instruction for trap vectors. The last two memory words, FFFC<sub>16</sub> and FFFE<sub>16</sub>, are used for the trap vector of the LOAD signal. The remaining memory is then available for programs, data, and workspace registers. If desired, any of the special areas may also be used as general memory.

FIGURE 1 - ARCHITECTURE

FIGURE 2 - MEMORY MAP

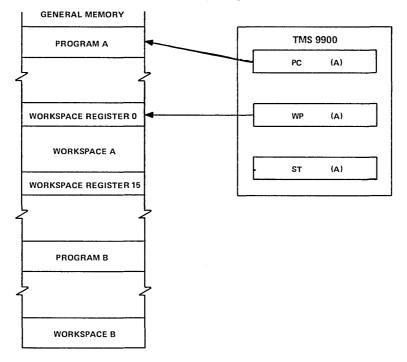

Three internal registers are accessible to the user. The program counter (PC) contains the address of the instruction following the current instruction being executed. This address is referenced by the processor to fetch the next instruction from memory and is then automatically incremented. The status register (ST) contains the present state of the processor and will be further defined in Section 3.4. The workspace pointer (WP) contains the address of the first word in the currently active set of workspace registers.

A workspace-register file occupies 16 contiguous memory words in the general memory area (see Figure 2). Each workspace register may hold data or addresses and function as operand registers, accumulators, address registers, or

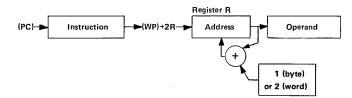

index registers. During instruction execution, the processor addresses any register in the workspace by adding the register number to the contents of the workspace pointer and initiating a memory request for the word. The relationship between the workspace pointer and its corresponding workspace is shown below.

The workspace concept is particularly valuable during operations that require a context switch, which is a change from one program environment to another (as in the case of an interrupt) or to a subroutine. Such an operation, using a conventional multi-register arrangement, requires that at least part of the contents of the register file be stored and reloaded. A memory cycle is required to store or fetch each word. By exchanging the program counter, status register, and workspace pointer, the TMS 9900 accomplishes a complete context switch with only three store cycles and three fetch cycles. After the switch the workspace pointer contains the starting address of a new 16-word workspace in memory for use in the new routine. A corresponding time saving occurs when the original context is restored. Instructions in the TMS 9900 that result in a context switch include:

- 1. Branch and Load Workspace Pointer (BLWP)

- 2. Return from Subroutine (RTWP)

- 3. Extended Operation (XOP).

Device interrupts, RESET, and LOAD also cause a context switch by forcing the processor to trap to a service subroutine.

# 2.2 INTERRUPTS

The TMS 9900 employs 16 interrupt levels with the highest priority level 0 and lowest level 15. Level 0 is reserved for the  $\overrightarrow{\text{RESET}}$  function and all other levels may be used for external devices. The external levels may also be shared by several device interrupts, depending upon system requirements.

The TMS 9900 continuously compares the interrupt code (IC0 through IC3) with the interrupt mask contained in status-register bits 12 through 15. When the level of the pending interrupt is less than or equal to the enabling mask level (higher or equal priority interrupt), the processor recognizes the interrupt and initiates a context switch following

completion of the currently executing instruction. The processor fetches the new context WP and PC from the interrupt vector locations. Then, the previous context WP, PC, and ST are stored in workspace registers 13, 14, and 15, respectively, of the new workspace. The TMS 9900 then forces the interrupt mask to a value that is one less than the level of the interrupt being serviced, except for level-zero interrupt, which loads zero into the mask. This allows only interrupts of higher priority to interrupt a service routine. The processor also inhibits interrupts until the first instruction of the service routine has been executed to preserve program linkage should a higher priority interrupt occur. All interrupt requests should remain active until recognized by the processor in the device-service routine. The individual service routines must reset the interrupt requests before the routine is complete.

If a higher priority interrupt occurs, a second context switch occurs to service the higher priority interrupt. When that routine is complete, a return instruction (RTWP) restores the first service routine parameters to the processor to complete processing of the lower-priority interrupt. All interrupt subroutines should terminate with the return instruction to restore original program parameters. The interrupt-vector locations, device assignment, enabling-mask value, and the interrupt code are shown in Table 1.

|                      | Vector Location            |                   | Interrupt Mask Values To                         | Interrupt             |

|----------------------|----------------------------|-------------------|--------------------------------------------------|-----------------------|

| Interrupt Level      | (Memory Address<br>In Hex) | Device Assignment | Enable Respective Interrupts<br>(ST12 thru ST15) | Codes<br>ICO thru IC3 |

| (Highest priority) 0 | 00                         | Reset             | 0 through F*                                     | 0000                  |

| . 1                  | 04                         | External device   | 1 through F                                      | 0001                  |

| 2                    | 08                         |                   | 2 through F                                      | 0010                  |

| 3                    | 0C                         |                   | 3 through F                                      | 0011                  |

| 4                    | 10                         |                   | 4 through F                                      | 0100                  |

| 5                    | 14                         |                   | 5 through F                                      | 0101                  |

| 6                    | 18                         |                   | 6 through F                                      | 0110                  |

| 7                    | 1C                         |                   | 7 through F                                      | 0111                  |

| 8                    | 20                         |                   | 8 through F                                      | 1000                  |

| 9                    | 24                         |                   | 9 through F                                      | 1001                  |

| 10                   | 28                         |                   | A through F                                      | 1010                  |

| 11                   | 2C                         |                   | B through F                                      | 1011                  |

| 12                   | 30                         |                   | C through F                                      | 1100                  |

| 13                   | 34                         |                   | D through F                                      | 1101                  |

| 14                   | 38                         | ↓ ↓               | E and F                                          | 1110                  |

| (Lowest priority) 15 | 3C                         | External device   | Fonly                                            | 1111                  |

TABLE 1 INTERRUPT LEVEL DATA

\*Level 0 can not be disabled.

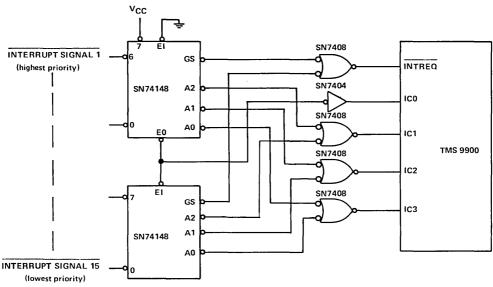

The TMS 9900 interrupt interface utilizes standard TTL components as shown in Figure 3. Note that for eight or less external interrupts a single SN74148 is required and for one external interrupt INTREQ is used as the interrupt signal with a hard-wired code IC0 through IC3.

# 2.3 INPUT/OUTPUT

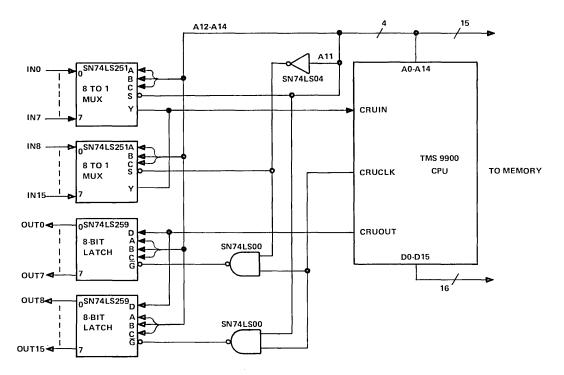

The TMS 9900 utilizes a versatile direct command-driven I/O interface designated as the communications-register unit (CRU). The CRU provides up to 4096 directly addressable input bits and 4096 directly addressable output bits. Both input and output bits can be addressed individually or in fields of from 1 to 16 bits. The TMS 9900 employs three dedicated I/O pins (CRUIN, CRUOUT, and CRUCLK) and 12 bits (A3 through A14) of the address bus to interface with the CRU system. The processor instructions that drive the CRU interface can set, reset, or test any bit in the CRU array or move between memory and CRU data fields.

FIGURE 3 - TMS 9900 INTERRUPT INTERFACE

# 2.4 SINGLE-BIT CRU OPERATIONS

The TMS 9900 performs three single-bit CRU functions: test bit (TB), set bit to one (SBO), and set bit to zero (SBZ). To identify the bit to be operated upon, the TMS 9900 develops a CRU-bit address and places it on the address bus, A3 to A14.

For the two output operations (SBO and SBZ), the processor also generates a CRUCLK pulse, indicating an output operation to the CRU device, and places bit 7 of the instruction word on the CRUOUT line to accomplish the specified operation (bit 7 is a one for SBO and a zero for SBZ). A test-bit instruction transfers the addressed CRU bit from the CRUIN input line to bit 2 of the status register (EQUAL).

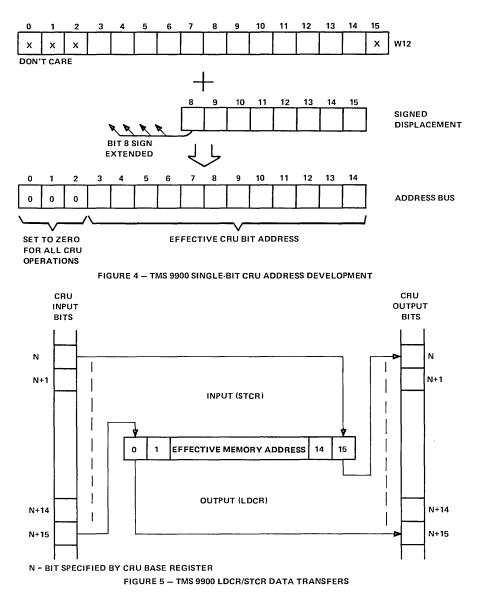

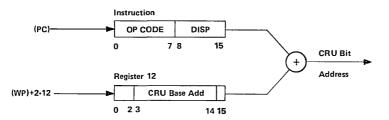

The TMS 9900 develops a CRU-bit address for the single-bit operations from the CRU-base address contained in workspace register 12 and the signed displacement count contained in bits 8 through 15 of the instruction. The displacement allows two's complement addressing from base minus 128 bits through base plus 127 bits. The base address from W12 is added to the signed displacement specified in the instruction and the result is loaded onto the address bus. Figure 4 illustrates the development of a single-bit CRU address.

# 2.5 MULTIPLE-BIT CRU OPERATIONS

The TMS 9900 performs two multiple-bit CRU operations: store communications register (STCR) and load communications register (LDCR). Both operations perform a data transfer from the CRU-to-memory or from memory-to-CRU as illustrated in Figure 5. Although the figure illustrates a full 16-bit transfer operation, any number of bits from 1 through 16 may be involved. The LDCR instruction fetches a word from memory and right-shifts it to serially transfer it to CRU output bits. If the LDCR involves eight or fewer bits, those bits come from the right-justified field within the addressed byte of the memory word. If the LDCR involves nine or more bits, those bits come from the right-justified field within the whole memory word. When transferred to the CRU interface, each successive bit receives an address that is sequentially greater than the address for the previous bit. This addressing mechanism results in an order reversal of the bits; that is, bit 15 of the memory word (or bit 7) becomes the lowest addressed bit in the CRU and bit 0 becomes the highest addressed bit in the CRU field.

An STCR instruction transfers data from the CRU to memory. If the operation involves a byte or less transfer, the transferred data will be stored right-justified in the memory byte with leading bits set to zero. If the operation involves from nine to 16 bits, the transferred data is stored right-justified in the memory word with leading bits set to zero.

When the input from the CRU device is complete, the first bit from the CRU is the least-significant-bit position in the memory word or byte.

Figure 6 illustrates how to implement a 16-bit input and a 16-bit output register in the CRU interface. CRU addresses are decoded as needed to implement up to 256 such 16-bit interface registers. In system application, however, only the exact number of interface bits needed to interface specific peripheral devices are implemented. It is not necessary to have a 16-bit interface register to interface an 8-bit device.

FIGURE 6 - TMS 9900 16-BIT INPUT/OUTPUT INTERFACE

# 2.6 EXTERNAL INSTRUCTIONS

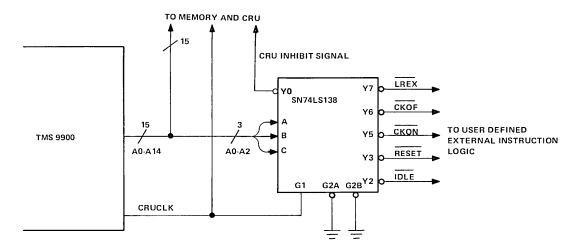

The TMS 9900 has five external instructions that allow user-defined external functions to be initiated under program control. These instructions are CKON, CKOF, RSET, IDLE, and LREX. These mnemonics, except for IDLE, relate to functions implemented in the 990 minicomputer and do not restrict use of the instructions to initiate various user-defined functions. IDLE also causes the TMS 9900 to enter the idle state and remain until an interrupt, RESET, or LOAD occurs. When any of these five instructions are executed by the TMS 9900, a unique 3-bit code appears on the most-significant 3 bits of the address bus (A0 through A2) along with a CRUCLK pulse. When the TMS 9900 is in an idle state, the 3-bit code and CRUCLK pulses occur repeatedly until the idle state is terminated. The codes are:

| EXTERNAL INSTRUCTION | A0  | A1 | A2       |

|----------------------|-----|----|----------|

| LREX                 | н   | н  | н        |

| CKOF                 | н   | н  | L        |

| CKON                 | н   | L  | н        |

| RSET                 | ( L | н  | н        |

| IDLE                 | L   | н  | <u>L</u> |

Figure 7 illustrates typical external decode logic to implement these instructions. Note that a signal is generated to inhibit CRU decodes during external instructions.

FIGURE 7 - EXTERNAL INSTRUCTION DECODE LOGIC

#### 2.7 LOAD FUNCTION

The LOAD signal allows cold-start ROM loaders and front panels to be implemented for the TMS 9900. When active, LOAD causes the TMS 9900 to initiate an interrupt sequence immediately following the instruction being executed. Memory location FFFC is used to obtain the vector (WP and PC). The old PC, WP and ST are loaded into the new workspace and the interrupt mask is set to 0000. Then, program execution resumes using the new PC and WP.

FIGURE 8 - TMS 9900 CPU FLOW CHART

# 2.8 TMS 9900 PIN DESCRIPTION

Table 2 defines the TMS 9900 pin assignments and describes the function of each pin.

# TABLE 2 TMS 9900 PIN ASSIGNMENTS AND FUNCTIONS

| SIGNATURE       | PIN      | 1/0 | DESCRIPTION                                           |                 | 714         | S 9900 PIN ASSIGNN | ENTO                     |                 |

|-----------------|----------|-----|-------------------------------------------------------|-----------------|-------------|--------------------|--------------------------|-----------------|

| SIGNATORE       | PIN      | 1/0 |                                                       |                 | 1000        | 5 5500 FIN A551GNN |                          |                 |

|                 |          |     | ADDRESS BUS                                           | VBB             | 1 🛱         | 0                  | IT -                     | HOLD            |

| A0 (MSB)        | 24       | OUT | A0 through A14 comprise the address bus.              | vcc             | 2           |                    | <b>T</b>                 | MEMEN           |

| A1              | 23       | OUT | This 3-state bus provides the memory-                 | WAIT            | 3 🏹         |                    | <b>T</b>                 | READY           |

| A2              | 22       | OUT | address vector to the external-memory                 | LOAD            | 4 67        |                    | <b>F</b> <sup>1 61</sup> |                 |

| A3              | 21       | OUT | system when MEMEN is active and I/O-bit               | HOLDA           | 5 🛱         |                    | 111                      | CRUCLK          |

| A4              | 20       | OUT | addresses and external-instruction addresses          | RESET           | ۴ <u>۲</u>  |                    | <b>1</b> 59              | Vcc             |

| A5              | 19       | OUT | to the I/O system when MEMEN is inactive.             | IAQ             | 752         |                    |                          | NC              |

| A6              | 18       | OUT | The address bus assumes the high-impedance            | φ1              | ° 17        |                    | <b>F</b> <sup>157</sup>  | NC<br>D15       |

| A7              | 17       |     | state when HOLDA is active.                           | φ2              | ° 17        |                    |                          |                 |

| A8              | 16       |     |                                                       | A14             |             |                    |                          | D14             |

| A9              | 15       | OUT |                                                       | A13             | 11 57       |                    |                          | D13             |

| A10             | 14       |     |                                                       | A12             | 12          |                    |                          | D12<br>D11      |

| A11             | 13       |     |                                                       | A11             |             |                    | 177                      | D10             |

| A12             | 12       |     |                                                       | A10             |             |                    |                          | D10<br>D9       |

| A13             | 11       | OUT |                                                       | A9              |             |                    | T -                      |                 |

| A14 (LSB)       | 10       | Ουτ |                                                       | A8              |             |                    | 49                       | D8<br>D7        |

|                 |          |     | DATA DUC                                              | A7              |             |                    |                          | D6              |

| D0 (M0D)        |          | 1/0 | DATA BUS<br>D0 through D15 comprise the bidirectional | A6<br>A5        |             |                    | H 46                     | D5              |

| D0 (MSB)<br>D1  | 41<br>42 | 1/0 | 3-state data bus. This bus transfers memory           | A5<br>A4        |             |                    | 45                       | D3<br>D4        |

| D1<br>D2        | 42       | 1/0 | data to (when writing) and from (when                 |                 |             |                    | 44                       | D4<br>D3        |

| D2<br>D3        | 43       | 1/0 | reading) the external-memory system when              |                 |             |                    |                          | D3<br>D2        |

| D3<br>D4        | 44       | 1/0 | MEMEN is active. The data bus assumes the             | A2<br>A1        | 22 5        |                    |                          | D2<br>D1        |

| D4<br>D5        | 45       | 1/0 | high-impedance state when HOLDA is                    |                 | 24          |                    | H 41                     | DO              |

| D5<br>D6        | 40       | 1/0 | active.                                               |                 |             |                    |                          | V <sub>SS</sub> |

| D8<br>D7        | 48       | 1/0 | active.                                               | V <sub>SS</sub> | 26          |                    | 39                       | NC              |

| D8              | 49       | 1/0 |                                                       | V <sub>DD</sub> |             |                    | 38                       | NC              |

| D9              | 50       | 1/0 |                                                       |                 | 28          |                    | 37                       | NC              |

| D10             | 51       | 1/0 |                                                       | DBIN            | - L         | ĺ                  | 36                       | ICO             |

| D10             | 52       | 1/0 |                                                       | CRUOUT          |             |                    | 35                       | IC1             |

| D12             | 53       | 1/0 |                                                       | CRUIN           |             |                    | 34                       | IC2             |

| D12             | 54       | 1/0 |                                                       | INTREO          |             |                    |                          | 103             |

| D14             | 55       | 1/0 |                                                       | in the c        | 01 ° E      | <u> </u>           | 1                        | 100             |

| D15 (LSB)       | 56       | 1/0 |                                                       |                 |             |                    |                          |                 |

| 010 (200)       |          | "   |                                                       | 10 No 14        |             |                    |                          |                 |

|                 |          |     | POWER SUPPLIES                                        | NC - No in      | ternal col  | inection           |                          |                 |

| VBB             | 1        |     | Supply voltage (-5 V NOM)                             |                 |             |                    |                          |                 |

| Vcc             | 2,59     |     | Supply voltage (5 V NOM), Pins 2 and 59 n             | nust be con     | nected in   | parallel.          |                          |                 |

| V <sub>DD</sub> | 27       |     | Supply voltage (12 V NOM)                             |                 |             |                    |                          |                 |

| V <sub>SS</sub> | 26,40    |     | Ground reference. Pins 26 and 40 must be o            | connected in    | n parallel. |                    |                          |                 |

|                 |          |     |                                                       |                 |             |                    |                          |                 |

|                 |          |     | CLOCKS                                                |                 |             |                    |                          |                 |

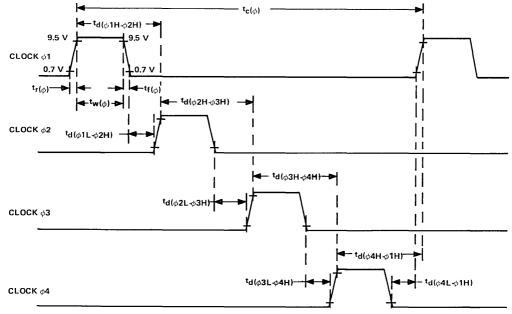

| φ1              | 8        | IN  | Phase-1 clock                                         |                 |             |                    |                          |                 |

| φ2              | 9        | IN  | Phase-2 clock                                         |                 |             |                    |                          |                 |

| φ3              | 28       | IN  | Phase-3 clock                                         |                 |             |                    |                          |                 |

| φ4              | 25       | IN  | Phase-4 clock                                         |                 |             |                    |                          |                 |

|                 | •        | •   | 1                                                     |                 |             |                    |                          |                 |

# TABLE 2 (CONTINUED)

| SIGNATURE                            | PIN                  | 1/0                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------|----------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBIN                                 | 29                   | OUT                  | <b>BUS CONTROL</b><br>Data bus in. When active (high), DBIN indicates that the TMS 9900 ha <u>s disable</u> d its output buffers to<br>allow the memory to place memory-read data on the data bus during MEMEN. DBIN remains low in<br>all other cases except when HOLDA is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MEMEN                                | 63                   | оит                  | Memory enable. When active (low), MEMEN indicates that the address bus contains a memory address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WE                                   | 61                   | Ουτ                  | Write enable. When active (low), WE indicates that memory-write data is available from the TMS 9900 to be written into memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CRUCLK                               | 60                   | оит                  | CRU clock. When active (high), CRUCLK indicates that external interface logic should sample the output data on CRUOUT or should decode external instructions on A0 through A2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CRUIN                                | 31                   | IN                   | CRU data in. CRUIN, normally driven by 3-state or open-collector devices, receives input data from external interface logic. When the processor executes a STCR or TB instruction, it samples CRUIN for the level of the CRU input bit specified by the address bus (A3 through A14).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CRUOUT                               | 30                   | OUT                  | CRU data out. Serial I/O data appears on the CRUOUT line when an LDCR, SBZ, or SBO instruction is executed. The data on CRUOUT should be sampled by external I/O interface logic when CRUCLK goes active (high).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| INTREQ                               | 32                   | IN                   | INTERRUPT CONTROL<br>Interrupt request. When active (low), INTREQ indicates that an external interrupt is requested. If<br>INTREQ is active, the processor loads the data on the interrupt-code-input lines ICO through IC3 into<br>the internal interrupt-code-storage register. The code is compared to the interrupt mask bits of the<br>status register. If equal or higher priority than the enabled interrupt level (interrupt code equal or less<br>than status register bits 12 through 15) the TMS 9900 interrupt sequence is initiated. If the<br>comparison fails, the processor ignores the request. INTREQ should remain active and the processor<br>will continue to sample ICO through IC3 until the program enables a sufficiently low priority to accept<br>the request interrupt. |

| IC0 (MSB)<br>IC1<br>IC2<br>IC3 (LSB) | 36<br>35<br>34<br>33 | IN<br>IN<br>IN<br>IN | Interrupt codes. ICO is the MSB of the interrupt code, which is sampled when INTREQ is active. When ICO through IC3 are LLLH, the highest external-priority interrupt is being requested and when HHHH, the lowest-priority interrupt is being requested.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| HOLD                                 | 64                   | IN                   | $\label{eq:memory} \begin{array}{c} \textbf{MEMORY CONTROL} \\ \textbf{Hold. When active (low), $\overline{HOLD}$ indicates to the processor that an external controller (e.g., DMA device) desires to utilize the address and data buses to transfer data to or from memory. The TMS 9900 enters the hold state following a hold signal when it has completed its present memory cycle.* The processor then places the address and data buses in the high-impedance state (along with $\overline{WE}$, $\overline{MEMEN}$, and $DBIN$) and responds with a hold-acknowledge signal (HOLDA). When $\overline{HOLD}$ is removed, the processor returns to normal operation. \\ \end{array}$                                                                                                          |

| HOLDA                                | 5                    | OUT                  | Hold acknowledge. When active (high), HOLDA indicates that the processor is in the hold state and the address and data buses and memory control outputs (WE, MEMEN, and DBIN) are in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| READY                                | 62                   | IN                   | Ready. When active (high), READY indicates that memory will be ready to read or write during the next clock cycle. When not-ready is indicated during a memory operation, the TMS 9900 enters a wait state and suspends internal operation until the memory systems indicate ready.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| WAIT                                 | 3                    | оит                  | Wait. When active (high), WAIT indicates that the TMS 9900 has entered a wait state because of a not-ready condition from memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

• If the cycle following the present memory cycle is also a memory cycle, it, too, is completed before the TMS9900 enters the hold state. The maximum number of consecutive memory cycles is two.

.

## TABLE 2 (CONCLUDED)

| SIGNATURE | PIN | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ΙΑΩ       | 7   | OUT | TIMING AND CONTROL<br>Instruction acquisition. IAQ is active (high) during any memory cycle when the TMS 9900 is acquiring an<br>instruction. IAQ can be used to detect illegal op codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LOAD      | 4   | IN  | Load. When active (low), $\overline{\text{LOAD}}$ causes the TMS 9900 to execute a nonmaskable interrupt with memory address FFFC <sub>16</sub> containing the trap vector (WP and PC). The load sequence begins after the instruction being executed is completed. $\overline{\text{LOAD}}$ will also terminate an idle state. If $\overline{\text{LOAD}}$ is active during the time RESET is released, then the $\overline{\text{LOAD}}$ will occur after the RESET function is completed. $\overline{\text{LOAD}}$ should remain active for one instruction period. IAQ can be used to determine instruction boundaries. This signal can be used to implement cold-start ROM loaders. Additionally, front-panel routines can be implemented using CRU bits as front-panel-interface signals and software-control routines to control the panel operations. |

| RESET     | 6   | IN  | Reset. When active (low), RESET causes the processor to be reset and inhibits WE and CRUCLK. When RESET is released, the TMS 9900 then initiates a level-zero interrupt sequence that acquires WP and PC from locations 0000 and 0002, sets all status register bits to zero, and starts execution. RESET will also terminate an idle state. RESET must be held active for a minimum of three clock cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# 2.9 TIMING

#### 2.9.1 MEMORY

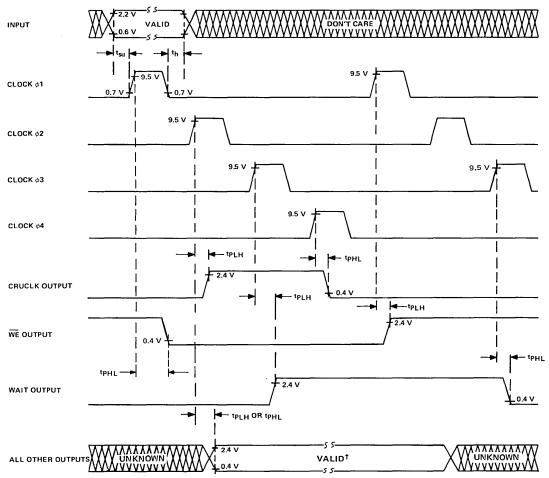

A basic memory read and write cycle is shown in Figure 9. The read cycle is shown with no wait states and the write cycle is shown with one wait state.

MEMEN goes active (low) during each memory cycle. At the same time that MEMEN is active, the memory address appears on the address bus bits A0 through A14. If the cycle is a memory-read cycle, DBIN will go active (high) at the same time MEMEN and A0 through A14 become valid. The memory-write signal WE will remain inactive (high) during a read cycle. If the read cycle is also an instruction acquisition cycle, IAQ will go active (high) during the cycle.

The READY signal, which allows extended memory cycles, is shown high during  $\phi 1$  of the second clock cycle of the read operation. This indicates to the TMS 9900 that memory-read data will be valid during  $\phi 1$  of the next clock cycle. If READY is low during  $\phi 1$ , then the TMS 9900 enters a wait state suspending internal operation until a READY is sensed during a subsequent  $\phi 1$ . The memory read data is then sampled by the TMS 9900 during the next  $\phi 1$ , which completes the memory-read cycle.

At the end of the read cycle, MEMEN and DBIN go inactive (high and low, respectively). The address bus may also change at this time, however, the data bus remains in the input mode for one clock cycle after the read cycle.

A write cycle is similar to the read cycle with the exception that  $\overline{WE}$  goes active (low) as shown and valid write data appears on the data bus at the same time the address appears. The write cycle is shown as an example of a one-wait-state memory cycle. READY is low during  $\phi$ 1 resulting in the WAIT signal shown.

#### 2.9.2 HOLD

Other interfaces may utilize the TMS 9900 memory bus by using the hold operation (illustrated in Figure 10) of the TMS 9900. When HOLD is active (low), the TMS 9900 enters the hold state at the next available non-memory cycle. Considering that there can be a maximum of two consecutive memory cycles, the maximum delay between HOLD going active to HOLDA going active (high) could be  $t_{c}(\phi)$  (for setup) + (4+W)  $t_{c}(\phi)$  (delay for HOLDA), where W is the number of wait states per memory cycle and  $t_{c}(\phi)$  is the clock cycle time. When the TMS 9900 has entered the hold state, HOLDA goes active (high) and A0 through A15, D0 through D15 DBIN, MEMEN, and WE go into a high-impedance state to allow other devices to use the memory buses. When HOLD goes an extra clock cycle (after the removal of the HOLD signal) to reassert the CRU address providing the normal setup times for the CRU bit transfer that was interrupted.

RD = READ DATA

FIGURE 9 - TMS 9900 MEMORY BUS TIMING

16

576

FIGURE 10 - TMS 9900 HOLD TIMING

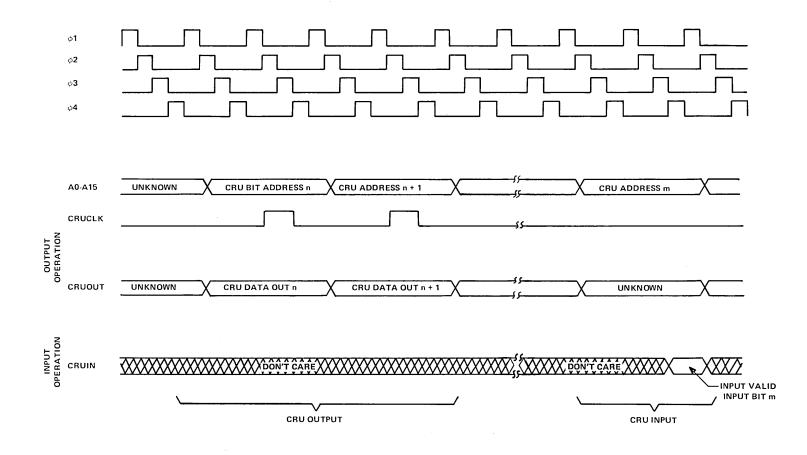

#### 2.9.3 CRU

CRU interface timing is shown in Figure 11. The timing for transferring two bits out and one bit in is shown. These transfers would occur during the execution of a CRU instruction. The other cycles of the instruction execution are not illustrated. To output a CRU bit, the CRU-bit address is placed on the address bus A0 through A14 and the actual bit data on CRUOUT. During the second clock cycle a CRU pulse is supplied by CRUCLK. This process is repeated until the number of bits specified by the instruction are completed.

The CRU input operation is similar in that the bit address appears on A0 through A14. During the subsequent cycle the TMS 9900 accepts the bit input data as shown. No CRUCLK pulses occur during a CRU input operation.

# 3. TMS 9900 INSTRUCTION SET

# 3.1 DEFINITION

Each TMS 9900 instruction performs one of the following operations:

- Arithmetic, logical, comparison, or manipulation operations on data

- Loading or storage of internal registers (program counter, workspace pointer, or status)

- Data transfer between memory and external devices via the CRU

- Control functions.

# 3.2 ADDRESSING MODES

TMS 9900 instructions contain a variety of available modes for addressing random-memory data (e.g., program parameters and flags), or formatted memory data (character strings, data lists, etc.). The following figures graphically describe the derivation of the effective address for each addressing mode. The applicability of addressing modes to particular instructions is described in Section 3.5 along with the description of the operations performed by the instruction. The symbols following the names of the addressing modes [R, \*R, @ LABEL, or @ TABLE (R)] are the general forms used by TMS 9900 assemblers to select the addressing mode for register R.

# 3.2.1 WORKSPACE REGISTER ADDRESSING R

Workspace Register R contains the operand.

#### 3.2.2 WORKSPACE REGISTER INDIRECT ADDRESSING \*R

Workspace Register R contains the address of the operand.

# 3.2.3 WORKSPACE REGISTER INDIRECT AUTO INCREMENT ADDRESSING \*R+

Workspace Register R contains the address of the operand. After acquiring the operand, the contents of workspace register R are incremented.

FIGURE 11 - TMS 9900 CRU INTERFACE TIMING

19

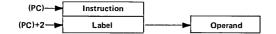

#### 3.2.4 SYMBOLIC (DIRECT) ADDRESSING @ LABEL

The word following the instruction contains the address of the operand.

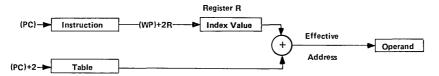

# 3.2.5 INDEXED ADDRESSING @ TABLE (R)

The word following the instruction contains the base address. Workspace register R contains the index value. The sum of the base address and the index value results in the effective address of the operand.

# 3.2.6 IMMEDIATE ADDRESSING

The word following the instruction contains the operand.

(PC) Instruction (PC)+2 Operand

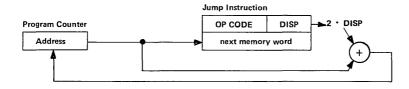

## 3.2.7 PROGRAM COUNTER RELATIVE ADDRESSING

The 8-bit signed displacement in the right byte (bits 8 through 15) of the instruction is multiplied by 2 and added to the updated contents of the program counter. The result is placed in the PC.

# 3.2.8 CRU RELATIVE ADDRESSING

The 8-bit signed displacement in the right byte of the instruction is added to the CRU base address (bits 3 through 14 of the workspace register 12). The result is the CRU address of the selected CRU bit.

# 3.3 TERMS AND DEFINITIONS

The following terms are used in describing the instructions of the TMS 9900:

| TERM   | DEFINITION                                   |

|--------|----------------------------------------------|

| В      | Byte indicator (1=byte, 0 = word)            |

| с      | Bit count                                    |

| D      | Destination address register                 |

| DA     | Destination address                          |

| IOP    | Immediate operand                            |

| LSB(n) | Least significant (right most) bit of (n)    |

| MSB(n) | Most significant (left most) bit of (n)      |

| N      | Don't care                                   |

| PC     | Program counter                              |

| Result | Result of operation performed by instruction |

| S      | Source address register                      |

| SA     | Source address                               |

| ST     | Status register                              |

| STn    | Bit n of status register                     |

| тр     | Destination address modifier                 |

| тs     | Source address modifier                      |

| w      | Workspace register                           |

| WRn    | Workspace register n                         |

| (n)    | Contents of n                                |

| a→b    | a is transferred to b                        |

| [n]    | Absolute value of n                          |

| +      | Arithmetic addition                          |

| -      | Arithmetic subtraction                       |

| AND    | Logical AND                                  |

| OR     | Logical OR                                   |

| ÷      | Logical exclusive OR                         |

| n      | Logical complement of n                      |

# 3.4 STATUS REGISTER

The status register contains the interrupt mask level and information pertaining to the instruction operation.

| 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7 | 8   | 9    | 10   | 11 | 12    | 13      | 14      | 15    |

|-----|-----|-----|-----|-----|-----|-----|---|-----|------|------|----|-------|---------|---------|-------|

| STO | ST1 | ST2 | ST3 | ST4 | ST5 | ST6 |   | not | used | (=0) |    | ST 12 | ST13    | ST14    | ST 15 |

| L>  | A>  | =   | с   | ο   | Р   | х   |   |     |      |      |    | I     | nterrup | ot Mask |       |

| віт | NAME       | INSTRUCTION | CONDITION TO SET BIT TO 1                               |

|-----|------------|-------------|---------------------------------------------------------|

| ST0 | LOGICAL    | C,CB        | If MSB(SA) = 1 and MSB(DA) = 0, or if MSB(SA) = MSB(DA) |

|     | GREATER    |             | and MSB of $(DA) - (SA) = 1$                            |

|     | THAN       | СІ          | If MSB(W) = 1 and MSB of IOP = 0, or if MSB(W) = MSB of |

|     |            | 1           | IOP and MSB of IOP $-$ (W) = 1                          |

|     |            | ABS         | If (SA) $\neq 0$                                        |

|     |            | All Others  | If result $\neq$ 0                                      |

| ST1 | ARITHMETIC | C,CB        | If MSB(SA) = 0 and MSB(DA) = 1, or if MSB(SA) = MSB(DA) |

|     | GREATER    |             | and $MSB(DA) - (SA) = 1$                                |

|     | THAN       | СІ          | If MSB(W) = 0 and MSB of IOP = 1, or if MSB(W) = MSB of |

|     |            |             | IOP and MSB of IOP $-$ (W) = 1                          |

|     |            | ABS         | If MSB(SA) = 0 and (SA) $\neq$ 0                        |

|     |            | All Others  | If MSB of result = 0 and result $\neq$ 0                |

- Continued

| віт       | NAME      | INSTRUCTION          | CONDITION TO SET BIT TO 1                                      |

|-----------|-----------|----------------------|----------------------------------------------------------------|

| ST2       | EQUAL     | C, CB                | If (SA) = (DA)                                                 |

|           |           | C1                   | If $(W) = IOP$                                                 |

|           |           | coc                  | If (SA) and $(\overline{DA}) = 0$                              |

|           |           | czc                  | If (SA) and (DA) = 0                                           |

|           |           | тв                   | If CRUIN = 1                                                   |

|           |           | ABS                  | If (SA) = 0                                                    |

|           |           | All others           | lf result = 0                                                  |

| ST3       | CARRY     | A, AB, ABS, AI, DEC, |                                                                |

|           |           | DECT, INC, INCT,     | If CARRY OUT = 1                                               |

|           |           | NEG, S, SB           |                                                                |

| _         |           | SLA, SRA, SRC, SRL   | If last bit shifted out = 1                                    |

| ST4       | OVERFLOW  | A, AB                | If MSB(SA) = MSB(DA) and MSB of result $\neq$ MSB(DA)          |

|           |           | AI                   | If MSB(W) = MSB of IOP and MSB of result $\neq$ MSB(W)         |

|           |           | S, SB                | If MSB(SA) $\neq$ MSB(DA) and MSB of result $\neq$ MSB(DA)     |

|           |           | DEC, DECT            | If MSB(SA) = 1 and MSB of result = $0$                         |

|           |           | INC, INCT            | If MSB(SA) = 0 and MSB of result = 1                           |

|           |           | SLA                  | If MSB changes during shift                                    |

|           |           | DIV                  | If $MSB(SA) = 0$ and $MSB(DA) = 1$ , or if $MSB(SA) = MSB(DA)$ |