# TMS34010 Assembly Language Tools

# User's Guide

İP

1987

**Graphics Products**

# TMS34010 Assembly Language Tools User's Guide

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1987, Texas Instruments Incorporated

## Contents

| Sect                                                                                                                                                        | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5                                                                                                                 | Introduction         Software Development Tools Overview         Getting Started         Manual Organization         Related Documentation         Style and Symbol Conventions                                                                                                                                                                                                                                                                                                              | 1-4<br>1-5<br>1-6                                                                                                   |

| <b>2</b><br>2.1<br>2.2<br>2.3                                                                                                                               | Software Installation<br>Installation for IBM/TI PCs with PC/MS-DOS                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-4                                                                                                                 |

| <b>3</b><br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.3<br>3.3.1<br>3.3.2<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2                         | Introduction to Common Object File Format         Sections         How the Assembler Handles Sections         Uninitialized Sections         Initialized Sections         Named Sections         Section Program Counters         An Example That Uses Sections Directives         How the Linker Handles Sections         Default Allocation         Placing Sections in the Memory Map         Relocation         Symbols in a COFF File         External Symbols         The Symbol Table | 3-3<br>3-4<br>3-5<br>3-6<br>3-9<br>3-9<br>3-12<br>3-15<br>3-16<br>3-17<br>3-17                                      |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.2<br>4.4.3<br>4.4.4<br>4.5.1<br>4.5.5<br>4.5.5<br>4.5.5<br>4.5.5<br>4.5.6<br>4.5.7 | Assembler Description         Assembler Development Flow         Invoking the Assembler         Specifying Alternate Directories for Assembler Input         -i Assembler Option         Environment Variable (A—DIR)         Source Statement Format         Label Field         Mnemonic Field         Operand List         Constants         Decimal Integers         Decimal Integers         Hexadecimal Integers         XY Constants         Character Constants                      | 4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-7<br>4-7<br>4-7<br>4-7<br>4-8<br>4-8<br>4-8<br>4-8<br>4-9<br>4-9<br>4-9<br>4-9 |

| 4.6<br>4.7 |                                      | 4-11<br>4-11 |

|------------|--------------------------------------|--------------|

| 4.7        |                                      | 4-11         |

| 4.8.1      |                                      | 4-12         |

| 4.8.2      | 1                                    | 4-13         |

| 4.8.3      | Wall Defined Expressions             | 4-14         |

| 4.8.4      | ·····                                | 4-14         |

| 4.8.5      |                                      | 4-14         |

| 4.8.5      |                                      | 4-14         |

|            |                                      | 4-10         |

| 4.10       | Cross-Reference Listings             | 4-18         |

| 5          |                                      | 5-1          |

| 5.1        | Directives Summary                   | 5-2          |

| 5.2        |                                      | 5-4          |

| 5.3        | Directives that Initialize Constants | 5-6          |

| 5.4        |                                      | 5-9          |

| 5.5        |                                      | 5-11         |

| 5.6        | Conditional Assembly Directives      | 5-12         |

| 5.7        |                                      | 5-13         |

| 5.8        |                                      | 5-14         |

| 6          | Instruction Set                      | 6-1          |

| 6.1        |                                      | 6-2          |

| 6.2        |                                      | 6-5          |

| 6.3        |                                      | 6-22         |

| 6.4        |                                      | 6-24         |

| 6.5        |                                      | 6-26         |

| 6.6        |                                      | 6-20         |

| 6.7        |                                      | 6-30         |

|            |                                      |              |

| 6.8        |                                      | 6-32         |

| 6.9        | XY Instructions                      | 6-33         |

| 7          | Macro Language                       | 7-1          |

| 7.1        | Macro Directives Summary             | 7-2          |

| 7.2        | Macro Libraries                      | 7-3          |

| 7.3        | Defining Macros                      | 7-4          |

| 7.4        | Macro Parameters                     | 7-6          |

| 7.5        | Conditional Blocks                   | 7-7          |

| 7.6        |                                      | 7-8          |

| 7.7        | •                                    | 7-9          |

| 8          | Archiver Description                 | 8-1          |

| 8.1        |                                      | 8-2          |

| 8.2        |                                      | 8-3          |

| 8.3        |                                      | 8-3<br>8-4   |

| 0.0        |                                      | 0-4          |

| 9      | Linker Description                                      |     |     |     |   |   | 9-1  |

|--------|---------------------------------------------------------|-----|-----|-----|---|---|------|

| 9.1    | Linker Development Flow                                 |     |     |     |   |   | 9-2  |

| 9.2    | Invoking the Linker                                     |     |     |     |   |   | 9-3  |

| 9.3    | Linker Options                                          |     |     |     |   |   | 9-4  |

| 9.3.1  | Relocation Capability (-a and -r Options)               |     |     |     |   |   | 9-4  |

| 9.3.2  | C Language Options (-c and -cr Options)                 |     |     |     |   |   | 9-6  |

| 9.3.3  | Define an Entry Point (-e symbol Option)                |     |     |     |   |   | 9-6  |

| 9.3.4  | Set Default Fill Value (-f cc Option)                   |     |     |     |   |   | 9-6  |

| 9.3.5  | Make All Global Symbols Static (-h Option)              |     |     |     |   |   | 9-7  |

| 9.3.6  | Alter the Library Search Algorithm (-idir Option/C_DIR) |     |     |     |   |   | 9-7  |

| 9.3.7  | Create a Map File (-m filename Option)                  |     |     |     |   |   | 9-9  |

| 9.3.8  | Name an Output Module (-o filename Option)              |     |     |     |   |   | 9-9  |

| 9.3.9  | Specify a Quiet Run (-q Option)                         |     |     |     |   |   | 9-9  |

| 9.3.10 |                                                         |     |     |     |   |   | 9-10 |

| 9.3.11 |                                                         |     |     |     |   |   | 9-10 |

| 9.4    | Linker Command Files                                    |     |     |     |   |   | 9-11 |

|        | Object Libraries                                        |     |     |     |   |   | 9-13 |

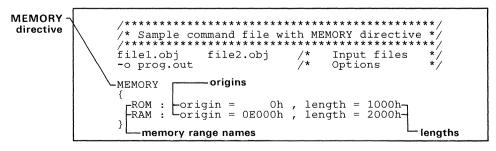

|        | The MEMORY Directive                                    |     |     |     |   |   | 9-14 |

| 9.6.1  | Default Memory Model                                    |     |     |     |   |   | 9-14 |

| 9.6.2  | MEMORY Directive Syntax                                 |     |     |     |   |   | 9-14 |

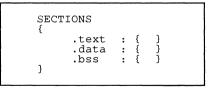

|        | The SECTIONS Directive                                  |     |     |     |   |   | 9-16 |

| 9.7.1  | Default Sections Configuration                          |     |     |     |   |   | 9-16 |

| 9.7.2  | SECTIONS Directive Syntax                               |     |     |     |   |   | 9-16 |

| 9.7.3  | Specifying Input Sections                               |     |     |     |   |   | 9-18 |

| 9.7.4  | Specifying the Address of Output Sections (Allocation)  |     |     |     |   |   | 9-20 |

| 9.7.5  | Grouping Output Sections Together                       |     |     |     |   | ÷ | 9-22 |

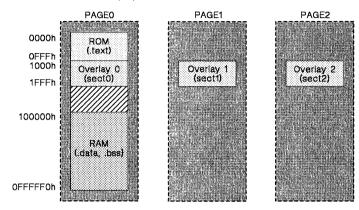

| 9.8    | Overlay Pages                                           |     |     |     |   |   | 9-23 |

| 9.8.1  | Using the MEMORY Directive to Define Overlay Pages .    |     |     |     |   |   | 9-23 |

| 9.8.2  | Using Overlay Pages with the SECTIONS Directive         |     |     |     |   |   | 9-24 |

| 9.8.3  | Syntax of Page Definitions                              |     |     |     |   |   | 9-25 |

| 9.9    | Default Allocation                                      |     |     |     |   |   | 9-27 |

| 9.9.1  | Allocation Algorithm                                    |     |     |     |   |   | 9-27 |

| 9.9.2  | General Rules for Output Sections                       |     |     |     |   |   | 9-27 |

|        | Special Section Types (DSECT, COPY, and NOLOAD)         |     |     |     |   |   | 9-29 |

|        | Assigning Symbols at Link Time                          |     |     |     |   |   | 9-30 |

| 9.11.1 |                                                         | • • |     | • • | • |   | 9-30 |

| 9.11.2 |                                                         | • • | ••• | ••• | · | • | 9-30 |

| 9.11.3 |                                                         |     |     |     |   |   | 9-31 |

| 9.11.4 | 0 1 1 1 1 1 1                                           |     | • • | ••• |   | · | 9-32 |

|        | Creating and Filling Holes                              |     |     | • • | · |   | 9-33 |

| 9.12.1 |                                                         | • • | • • | • • | • | • | 9-33 |

| 9.12.2 |                                                         |     |     |     |   |   | 9-33 |

| 9.12.3 |                                                         |     |     |     |   |   | 9-35 |

| 9.12.4 |                                                         |     |     |     |   |   | 9-36 |

|        | Partial Linking                                         |     |     |     |   |   | 9-37 |

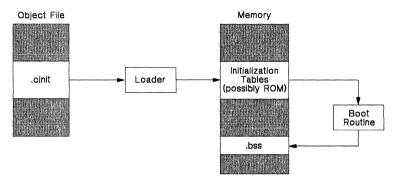

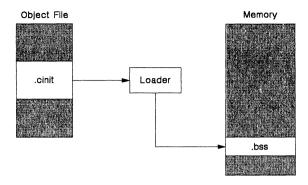

|        | Linking C Code                                          |     |     |     |   |   | 9-38 |

| 9.14.1 |                                                         |     |     |     |   |   | 9-38 |

| 9.14.2 |                                                         | • • | • • | • • | • | • | 9-38 |

| 9.14.3 |                                                         | • • | • • | • • | · | • | 9-38 |

| 9.14.4 |                                                         | • • | • • | • • | · | • | 9-40 |

|        |                                                         |     |     |     |   |   | 9-41 |

|        |                                                         |     |     |     |   |   |      |

| 10                         | Object Format Converter Description                                                                                                    | 10-1                            |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 10.1                       | Object Format Converter Development Flow                                                                                               | 10-2                            |

| 10.2                       | Invoking the Object Format Converter                                                                                                   | 10-3                            |

| 10.3                       | Object Format Converter Examples                                                                                                       | 10-4                            |

| 11                         | Simulator Description                                                                                                                  | 11-1                            |

| 11.1                       | Simulator Development Flow                                                                                                             | 11-2                            |

| 11.2                       | Invoking the Simulator                                                                                                                 | 11-3                            |

| 11.3                       | Hardware and System Requirements                                                                                                       | 11-4                            |

| 11.4                       | Screen Displays                                                                                                                        | 11-5                            |

| 11.4.1                     | Machine-State Display                                                                                                                  | 11-5                            |

| 11.4.2                     | 2 Displaying Graphics and Status Information Simultaneously                                                                            | 11-9                            |

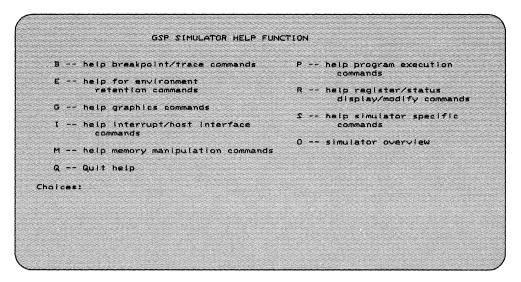

| 11.4.3                     | 3 Using the HELP Function                                                                                                              | 11-9                            |

| 11.5                       | Entering Commands                                                                                                                      | 11-11                           |

| 11.5.1                     | Command Parameters                                                                                                                     | 11-12                           |

| 11.5.2                     | 2 Command Buffers                                                                                                                      | 11-13                           |

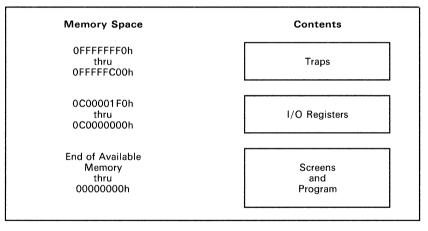

| 11.5.3                     | 3 Loading and Running Code                                                                                                             | 11-15                           |

| 11.5.4                     | 4 Line Assembler                                                                                                                       | 11-16                           |

| 11.5.5                     |                                                                                                                                        | 11-16                           |

| 11.6                       | System Simulation                                                                                                                      | 11-17                           |

| 11.6.1                     | Local Memory Simulation                                                                                                                | 11-17                           |

| 11.6.2                     | 2 Interrupts Simulation                                                                                                                | 11-17                           |

| 11.6.3                     | 3 Host Interface Simulation                                                                                                            | 11-17                           |

| 11.6.4                     |                                                                                                                                        | 11-19                           |

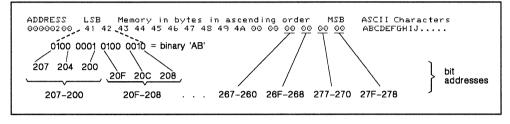

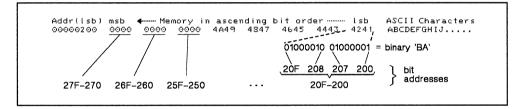

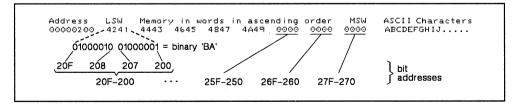

| 11.6.5                     | 5 DB, DM, and DW Display Comparison                                                                                                    | 11-20                           |

| 11.6.6                     |                                                                                                                                        | 11-21                           |

| 11.7                       | Demonstration Program                                                                                                                  | 11-22                           |

| 11.8                       | Simulator Commands                                                                                                                     | 11-24                           |

| A<br>B<br>C<br>D<br>E<br>F | Common Object File Format<br>Symbolic Debugging Directives<br>Assembler Error Messages<br>Linker Error Messages<br>ASCII Character Set | A-1<br>B-1<br>C-1<br>D-1<br>E-1 |

| F                          | Glossary                                                                                                                               | F-1                             |

E F ASCII Cha Glossary

## Illustrations

# Figure

| 1-1<br>3-1<br>3-2 | TMS34010 Assembly Language Development Flow<br>Partitioning Memory into Logical Blocks<br>Using Sections Directives | 1-2<br>3-3<br>3-7 |

|-------------------|---------------------------------------------------------------------------------------------------------------------|-------------------|

| 3-3               | Object Code Generated by Figure 3-2                                                                                 | 3-8               |

| 3-4               | Default Allocation of the Object Code from Figure 3-2                                                               | 3-10              |

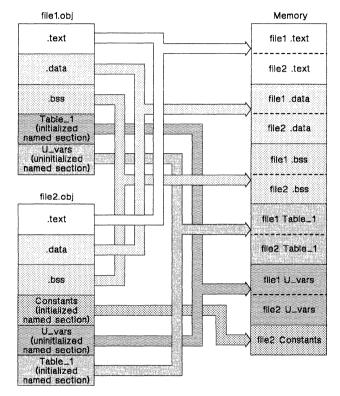

| 3-5               | Combining Input Sections from Two Files (Default Allocation)                                                        |                   |

| 3-6               | MEMORY and SECTIONS Directives for Figure 3-7 and Figure 3-8                                                        | 3-12              |

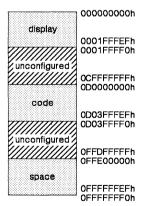

| 3-7               | Memory Map Defined in Figure 3-6                                                                                    | 3-13              |

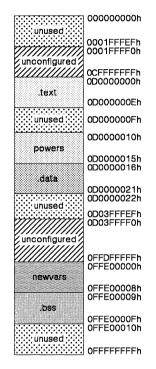

| 3-8               | Placing the Code from Figure 3-4 into the Memory Map Defined by Figure 3-6                                          | 3-14              |

| 3-9               | An Example of Code that Generates Relocation Entries                                                                | 3-15              |

| 4-1               | Assembler Development Flow                                                                                          | 4-2               |

| 4-2               | Sample Assembler Listing                                                                                            | 4-17              |

| 4-3               | Cross-Reference Listing Format                                                                                      | 4-18              |

| 5-1               | Sections Directives Example                                                                                         | 5-5               |

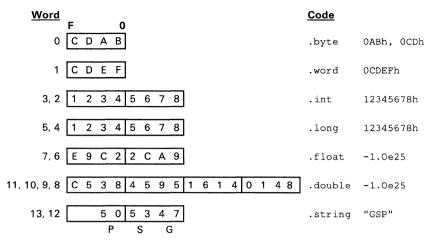

| 5-2               | Examples of Initialization Directives                                                                               | 5-7               |

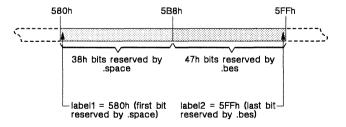

| 5-3               | An Example of the .space and .bes Directive                                                                         | 5-7               |

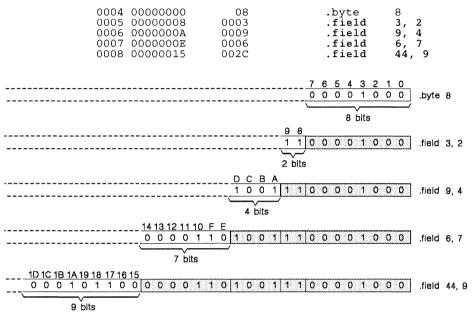

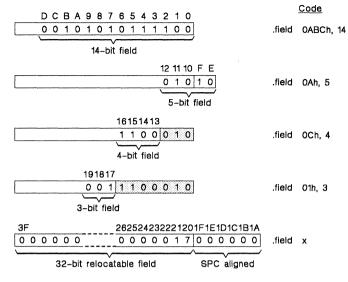

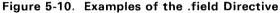

| 5-4               | An Example of the field Directive                                                                                   | 5-8               |

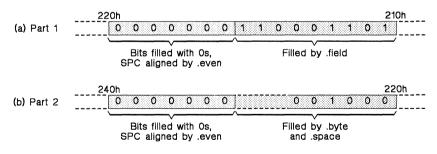

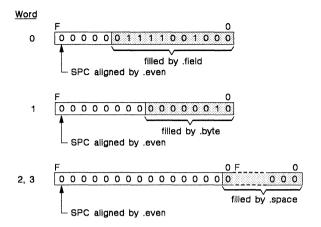

| 5-5               | An Example of the even Directive                                                                                    | 5-9               |

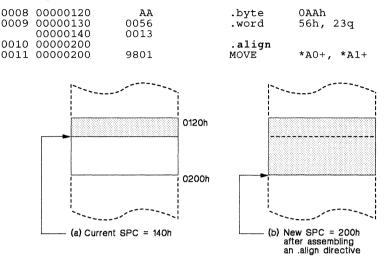

| 5-6               | An Example of the align Directive                                                                                   | 5-10              |

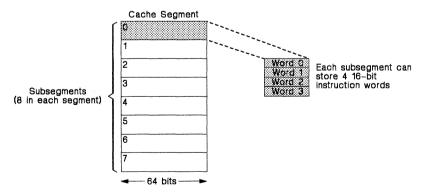

| 5-7               | Cache Segment Organization                                                                                          | 5-10              |

| 5-8               | An Example of Conditional Assembly                                                                                  | 5-12              |

| 5-9               | An Example of the .even Directive                                                                                   | 5-24              |

| 5-10              | Examples of the field Directive                                                                                     | 5-26              |

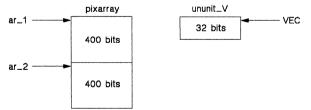

| 5-11              | An Example of the usect Directive                                                                                   | 5-46              |

| 7-1               | An Example of a Macro Definition, Call, and Expansion                                                               | 7-5               |

| 7-2               | An Example of Using Parameter Values                                                                                | 7-6               |

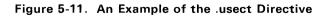

| 7-3               | An Example of a Conditional Block                                                                                   | 7-7               |

| 7-4               | An Example of a Repeatable Block                                                                                    | 7-8               |

| 7-5               | An Example of Unique Labels                                                                                         | 7-9               |

| 8-1               | Archiver Development Flow                                                                                           | 8-2               |

| 9-1               | Linker Development Flow                                                                                             | 9-2               |

| 9-2               | An Example of a Linker Command File                                                                                 | 9-11              |

| 9-3               | An Example of a Command File with Linker Directives                                                                 | 9-12              |

| 9-4               | An Example of the MEMORY Directive                                                                                  | 9-14              |

| 9-5               | Memory Map Defined in Figure 9-4                                                                                    | 9-15              |

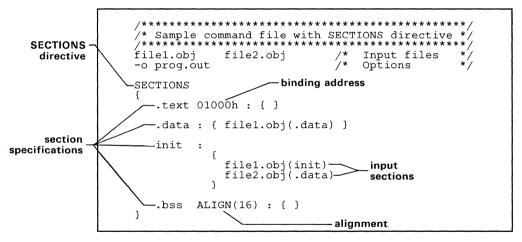

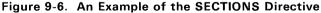

| 9-6               | An Example of the SECTIONS Directive                                                                                | 9-16              |

| 9-7               | Section Allocation Defined by Figure 9-6                                                                            | 9-18              |

| 9-8               | The Most Common Method of Specifying Section Contents                                                               | 9-18              |

| 9-9               | An Example of Overlay Pages                                                                                         | 9-23              |

| 9-10              | Overlay Pages Defined by Figure 9-9                                                                                 | 9-24              |

| 9-11              | SECTIONS Directive Definition for Figure 9-9                                                                        | 9-24              |

| 9-12              | ROM Model of Autoinitialization                                                                                     | 9-39              |

| 9-13              | RAM Model of Autoinitialization                                                                                     | 9-40              |

| 9-14              | Linker Command File, demo.cmd                                                                                       | 9-42              |

| 9-15              |                                                                                                                     | 9-43              |

| 10-1              | Object Format Converter Development Flow                                                                            | 10-2              |

| 11-1              | Simulator Development Flow                                                                                          | 11-2              |

| 11-2              | Initial Simulator Display                                                                                           | 11-3              |

| 11-3  | Simulator Display Format                                    | 11-5  |

|-------|-------------------------------------------------------------|-------|

| 11-4  | Simulator Help Menu                                         | 11-10 |

| 11-5  | Dedicated and Available TMS34010 Memory Spaces              | 11-15 |

| 11-6  | DB, DM, and DW Displays                                     | 11-20 |

| 11-7  | Display of Existing Breakpoints                             | 11-31 |

| 11-8  | Modify Breakpoints Menu                                     | 11-33 |

| 11-9  | Display Bytes Format                                        | 11-50 |

| 11-10 | Display Bytes Format - Over 10 Lines                        | 11-51 |

| 11-11 | Cache Contents Display                                      | 11-53 |

| 11-12 | Memory Display                                              | 11-54 |

| 11-13 | A- and B-File Registers Display                             | 11-55 |

| 11-14 | I/O Registers Display                                       | 11-56 |

| 11-15 | Display Word Format                                         | 11-57 |

|       | Find Word Display                                           | 11-61 |

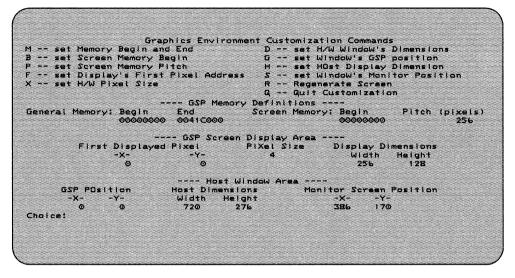

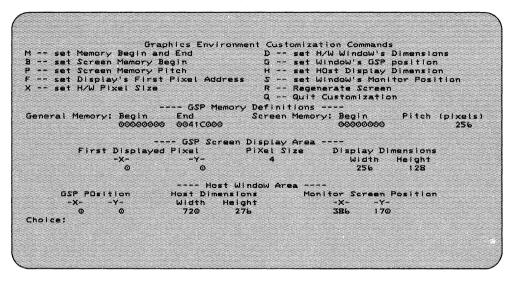

| 11-17 | Graphics Customization Menu                                 | 11-62 |

|       | Simulator Help Utility Menu                                 | 11-66 |

| 11-19 | Interrupt Displays                                          | 11-67 |

| 11-20 | Display Interrupt Options                                   | 11-69 |

| 11-21 | I/O Registers Display                                       | 11-73 |

| 11-22 | Graphics Environment Menu                                   | 11-80 |

|       | Modify Memory Display                                       | 11-82 |

| 11-24 | Modify Special Traps Display                                | 11-85 |

|       | gspinput.000 Example File                                   | 11-11 |

|       | Display of Existing Traces                                  | 11-11 |

| 11-27 | Trace Options Display                                       | 11-12 |

| 11-28 | Trace on Address Display                                    | 11-12 |

| 11-29 | Trace on Address Pattern Display                            | 11-12 |

| 11-30 | Trace on Data Display                                       | 11-12 |

| 11-31 | Trace on Pattern Display                                    | 11-12 |

|       | Trace on Range Display                                      | 11-12 |

| 11-33 | Reverse-Assembly Display                                    | 11-12 |

| 11-34 | Reverse-Assembly from a Starting Location Display           | 11-12 |

|       | Reverse-Assembly within a Range of Addresses Display        | 11-12 |

| 11-36 | Evaluate Data Display                                       | 11-13 |

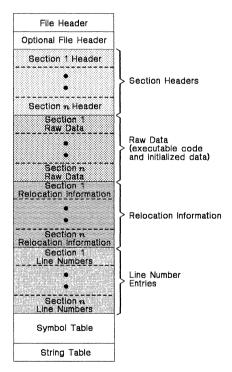

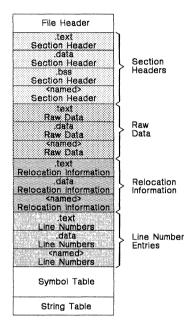

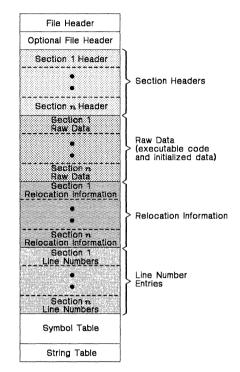

| A-1   | COFF File Structure                                         | A-2   |

| A-2   | Sample COFF Object File                                     |       |

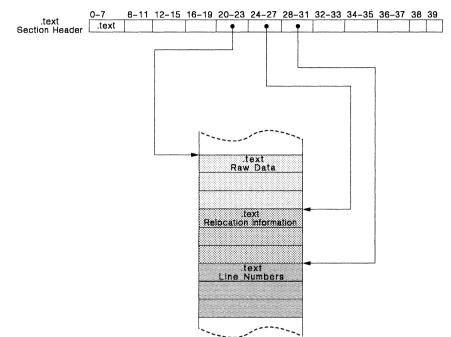

| A-3   | An Example of Section Header Pointers for the .text Section | A-7   |

| A-4   | Line Number Blocks                                          |       |

| A-5   | Line Number Entries Example                                 | A-11  |

| A-6   | Symbol Table Contents                                       | A-12  |

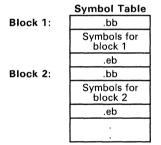

| A-7   | Symbols for Blocks                                          | A-14  |

| A-8   | Symbols for Functions                                       | A-14  |

| A-9   | Sample String Table                                         | A-15  |

# Tables

### Table

| 4-1          | Operators                                                                                      | 4-13        |

|--------------|------------------------------------------------------------------------------------------------|-------------|

| 4-1          | Expressions with Absolute and Relocatable Symbols                                              | 4-14        |

| 4-2<br>4-3   | Expressions with Absolute and Relocatable Symbols                                              | 4-14        |

| 4-3<br>5-1   | Symbol Attributes<br>Directives Summary                                                        | 4-10<br>5-2 |

|              |                                                                                                | 5-2<br>6-23 |

| 6-1          | Summary of Arithmetic, Logical, and Compare Instructions                                       |             |

| 6-2          | Summary of Move Instructions                                                                   | 6-24        |

| 6-3          | Summary of Operand Formats for the MOVE Instruction                                            | 6-25        |

| 6-4          | Summary of Operand Formats for the MOVB Instruction                                            | 6-25        |

| 6-5          | Summary of Graphics Instructions                                                               | 6-26        |

| 6-6          | Summary of Operand Formats for the PIXT Instruction                                            | 6-27        |

| 6-7          | Summary of Array Types for the PIXBLT Instruction                                              | 6-27        |

| 6-8          | Immediate Operands Used by Graphics Instructions                                               | 6-28        |

| 6-9          | Summary of Program Control and Context Switching Instructions                                  | 6-29        |

| 6-10         | Summary of Jump Instructions                                                                   | 6-30        |

| 6-11         | Condition Codes                                                                                | 6-31        |

| 6-12         | Summary of Shift Instructions                                                                  | 6-32        |

| 6-13         | Summary of XY Instructions                                                                     | 6-33        |

| 9-1          | Linker Options Summary                                                                         | 9-4         |

| 9-2          | Operators in Assignment Expressions                                                            | 9-32        |

| 11-1         | HIF ASCII Record Format                                                                        | 11-18       |

| 11-2         | TI-PC Color Mapping                                                                            | 11-19       |

| 11-3         | Addresses of Routines in the Demonstration Program                                             | 11-23       |

| 11-3         | Simulator Command Summary                                                                      | 11-23       |

| 11-4         |                                                                                                | 11-24       |

|              | I/O Registers and Offsets                                                                      |             |

| 11-6         | Pixel Processing Options                                                                       | 11-92       |

| A-1          | File Header Contents                                                                           | A-4         |

| A-2          | File Header Flags (Bytes 18 and 19)                                                            | A-4         |

| A-3          | Optional File Header Contents Section Header Contents                                          | A-5         |

| A-4          | Section Header Contents                                                                        | A-6         |

| A-5          | Section Header Flags (Bytes 36 and 37)<br>Relocation Entry Contents                            | A-6         |

| A-6          | Relocation Entry Contents                                                                      | A-8         |

| A-7          | Relocation Types (Bytes 8 and 9)                                                               | A-9         |

| A-8          | Line Number Entry Format                                                                       | A-10        |

| A-9          | Symbol Table Entry Contents                                                                    | A-13        |

| A-10         | Special Symbols in the Symbol Table                                                            | A-13        |

| A-11         | Symbol Storage Classes                                                                         |             |

| A-12         | Special Symbols and Their Storage Classes                                                      | A-16        |

| A-13         | Symbol Values and Storage Classes                                                              | A-17        |

| A-14         | Section Numbers                                                                                | A-18        |

| A-15         | Basic Types                                                                                    |             |

| A-16         | Derived Types                                                                                  | A-19        |

| A-17         | Auxiliary Symbol Table Entries Format                                                          | Δ-20        |

| A-18         | Filename Format for Auxiliary Table Entries                                                    |             |

| A-19         | Section Format for Auxiliary Table Entries                                                     |             |

| A-13<br>A-20 | Tag Name Format for Auxiliary Table Entries                                                    | A 21        |

| A-20<br>A-21 | End of Structure Format for Auxiliary Table Entries                                            | A 21        |

| A-21<br>A-22 | Eurotion Format for Auxiliary Table Entries                                                    | A-21        |

| A-22<br>A-23 | Function Format for Auxiliary Table Entries           Array Format for Auxiliary Table Entries | A-22        |

|              |                                                                                                |             |

| A-24         | End of Blocks and Functions Format for Auxiliary Table Entries                                 | A-22        |

A-25 Beginning of Blocks and Functions Format for Auxiliary Table Entries ... A-23 A-26 Structure, Union, and Enumeration Names Format for Auxiliary Table Entries A-23

Section 1

Introduction

The TMS34010 Graphics System Processor (**GSP**) is an advanced 32-bit microprocessor optimized for graphics systems. The GSP is a member of the TMS340 family of computer graphics products from Texas Instruments. The TMS34010 is well supported by a full set of hardware and software development tools, including a C compiler, a full-speed emulator, a software simulator, and an IBM/TI-PC development board. This document discusses the software development tools that are included with the TMS34010 assembly language tools package:

- Assembler

- Archiver

- Linker

- Object format converter

- Simulator<sup>1</sup>

These tools can be installed on the following systems:

- PCs:

- IBM-PC with PC-DOS - TI-PC with MS-DOS

- VAX:

- VMS

- DEC Ultrix

- Unix System V

The TMS34010 assembly language tools create and use object files that are in common object file format, or COFF. COFF makes modular programming easier because it encourages you to think in terms of *blocks* of code and data. Object files contain separate blocks (called **sections**) of code and data that you can load into different memory spaces. You will be able to program the TMS34010 more efficiently if you have a basic understanding of COFF; Section 3, Introduction to Common Object File Format, discusses this object format in detail.

Topics covered in this introductory section include:

| Sec | tion                                | Page |

|-----|-------------------------------------|------|

| 1.1 | Software Development Tools Overview | 1-2  |

| 1.2 | Getting Started                     | 1-4  |

| 1.3 | Manual Organization                 | 1-5  |

| 1.4 | Related Documentation               | 1-6  |

|     | Style and Symbol Conventions        |      |

<sup>&</sup>lt;sup>1</sup> The simulator is available in a PC version only.

#### **1.1 Software Development Tools Overview**

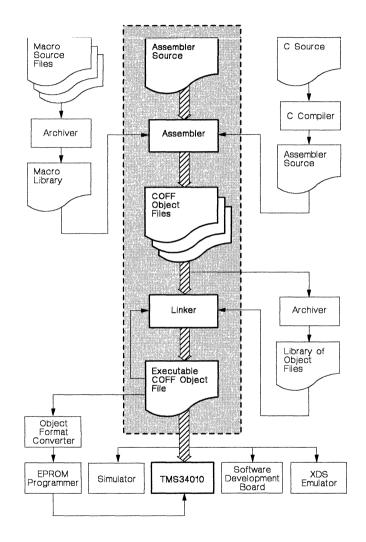

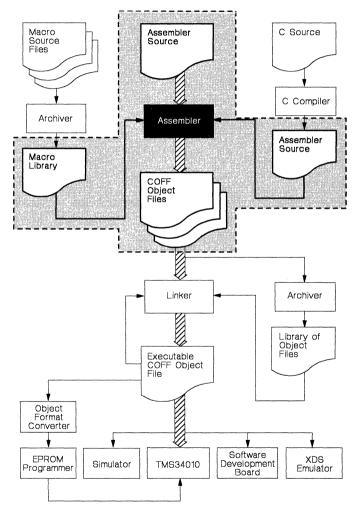

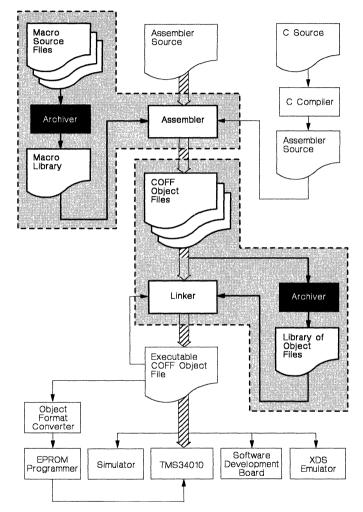

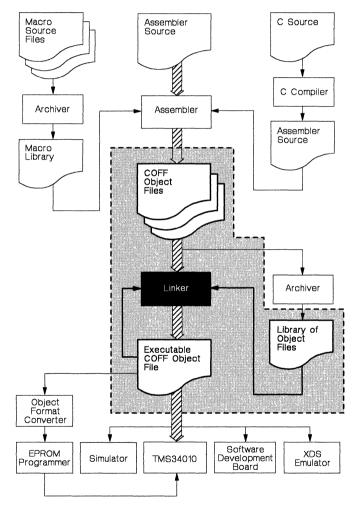

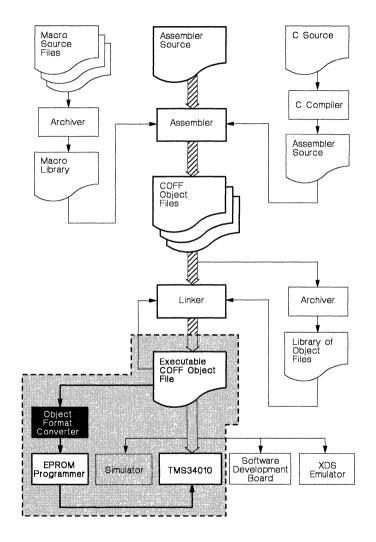

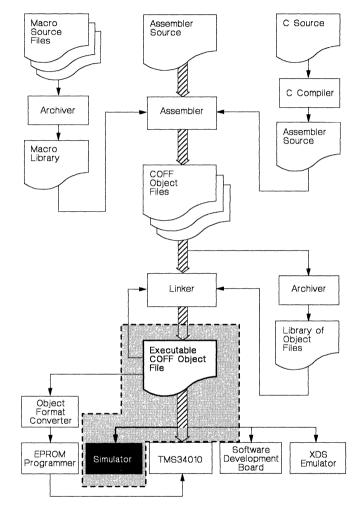

Figure 1-1 shows the TMS34010 assembly language development flow. The center section of the illustration highlights the most common path; the other portions are optional.

Figure 1-1. TMS34010 Assembly Language Development Flow

- The C compiler translates C source code into TMS34010 assembly language source code. The C compiler is not shipped as part of the assembly language tools package.

- The **assembler** translates assembly language source files into machine language object files. Source files can contain TMS34010 assembly language instructions, assembler directives, and macro directives. You can use assembler directives to control various aspects of the assembly process, such as the source listing format, data alignment, and section content.

- The **archiver** allows you to collect a group of files into a single archive file. For example, you can collect several macros together into a macro library. The assembler will search through the library and use the members that are called as macros by the source file. You can also use the archiver to collect a group of object files into an object library. The linker will include the members in the library that resolve external references during the link.

- The **linker** combines object files into a single executable object module. As it creates the executable module, it performs relocation and resolves external references. The linker accepts relocatable COFF object files (created by the assembler) as input. It can also accept archive library members and output modules created by a previous linker run. Linker directives allow you to combine object file sections, bind sections or symbols to specific addresses or within specific portions of memory, and define or redefine global symbols.

- The main purpose of this development process is to produce a module that can be executed in a system that contains a **TMS34010**. You can use one of several debugging tools to refine and correct your code before executing it in a TMS34010 system. These tools share similar debugger interfaces. (Note that only *linked* files can be executed.)

- The simulator simulates TMS34010 functions in a configurable graphics environment. The simulator allows you to design, implement, and evaluate both graphics and nongraphics software systems. The simulator command set displays and maintains graphics and machine status information and controls execution of the software system under development.

- The software development board (SDB) is a highperformance graphics card that can be used with a TI or an IBM PC. The SDB is not shipped as part of the TMS34010 assembly language package.

- The **XDS**/22 emulator is a realtime, in-circuit emulator. It is not shipped as part of the TMS34010 assembly language package.

- Most EPROM programmers do not accept COFF object files as input. The object format converter converts a COFF object file into Intel hex, Tektronix hex, or TI-tagged object format. The converted file can be downloaded to an EPROM programmer.

#### 1.2 Getting Started

The tools you will probably use most often are the assembler and the linker. This section provides a quick walkthrough so that you can get started without reading the whole user's guide. These examples show the most common methods for invoking the assembler and linker.

First, create two short source files to use for the walkthrough; call them tilel.asm and file2.asm.

| file1.asm |               |                    |         | file2         | .asm        |

|-----------|---------------|--------------------|---------|---------------|-------------|

| COLOR0    | .file<br>.set | "Set_Colors"<br>B8 |         | .file<br>EINT | "Set_Parms" |

|           | MOVI          | OFFFFh,COLORO      | CONTROL | .set          | 0C00000B0h  |

| COLOR1    | .set          | B9                 |         | MOVI          | 4A4h,A1     |

|           | MOVI          | 3333h,COLOR1       | ]       | MOVE          | A1,@CONTROL |

|           |               |                    | INTENB  | .set          | 0C0000110h  |

|           |               |                    |         | MOVI          | 0C00h,A1    |

|           |               |                    |         | MOVE          | A1,@INTENB  |

2) Assemble file1.asm; enter:

gspa filel

The **gspa** command invokes the assembler. file1.asm is the input source file. (If the input file extension is .asm, you don't have to specify the extension; the assembler uses .asm as the default.) This example creates an object file called file1.obj. The assembler always creates an object file. You can specify a name for the object file, but if you don't, the assembler will use the input filename appended to the .obj extension.

Now assemble file2.asm; enter:

gspa file2 -1

This time, the assembler creates an object file called file2.obj. The -I (lowercase "L") option tells the assembler to create a listing file; the listing file for this example is called file2.lst.

Link file1.obj and file2.obj; enter:

gsplnk filel file2 -o prog.out

The **gspink** command invokes the linker. file1.obj and file2.obj are the input object files. (If the input file extension is .obj, you don't have to specify the extension; the linker uses .obj as the default.) The linker combines file1.obj and file2.obj to create an executable object module called prog.out (the -o option supplies the name of the output module).

You can find more information about invoking the tools in the following sections:

| Section |                                      | Page |

|---------|--------------------------------------|------|

| 4.1     | Invoking the Assembler               |      |

| 8.1     | Archiver Development Flow            |      |

| 9.1     | Invoking the Linker                  |      |

| 10.1    | Invoking the Object Format Converter |      |

|         | Invoking the Simulator               |      |

#### **1.3 Manual Organization**

#### Section 1 Introduction

Provides an overview of the assembly language tools and the assembly language development process, gives quick examples for invoking the tools, lists related documentation, and explains the style and symbol conventions used throughout this document.

Section 2 Software Installation Contains instructions for installing the assembly language tools on PC and VAX systems.

#### Section 3 Introduction to Common Object File Format

Discusses the basic COFF concept of **sections** and how they can help you use the assembler and linker more efficiently. (Common object file format, or COFF, is the object file format that the TMS34010 assembly language tools use.) *Read Section 3 before using the assembler and linker.*

#### Section 4 Assembler Description

Tells you how to invoke the assembler and discusses source statement format, valid constants and expressions, and assembler output.

#### Section 5 Assembler Directives

Divided into two parts: the first part describes the directives according to function, the second part is a reference that presents the directives in alphabetical order.

- Section 6 Instruction Set Summary Summarizes the TMS34010 instruction set alphabetically.

- Section 7 Macro Language Describes macro directives and creating macros.

#### Section 8 Archiver Description

Contains instructions for invoking the archiver, creating new archive libraries, and modifying existing libraries.

#### Section 9 Linker Description

Tells you how to invoke the linker, provides details of linker operation, discusses linker directives, and presents a detailed linking example.

Section 10 Object Format Converter Description Tells you how to invoke the object format converter so that you can convert a COFF object file into an Intel or Tektronix hex object format.

Section 11 Simulator Description Contains instructions for invoking the simulator and loading the tutorial program, explains the various fields on the simulator screen, and contains a complete alphabetical reference of simulator commands.

- Appendix A Common Object File Format Contains specific information about the internal format of COFF object files.

- Appendix B Symbolic Debugging Directives

- Appendix C Assembler Error Messages

- Appendix D Linker Error Messages

- Appendix E ASCII Character Set

- Appendix F Glossary

#### **1.4 Related Documentation**

The following TMS34010 documents are also available.

- The TMS34010 User's Guide (literature number SPVU001) discusses hardware aspects of the TMS34010, such as pin functions, architecture, stack operation, and interfaces, and contains the TMS34010 instruction set. (If you received this User's Guide with the TMS34010 assembly language tools package, you should also have received a copy of the IMS34010 User's Guide).

- The *TMS34010 Data Sheet* (literature number SPVS002) contains the recommended operating conditions, electrical specifications, and timing characteristics of the TMS34010.

- The TMS34010 C Compiler User's Guide (literature number SPVU005) tells you how to use the TMS34010 C compiler. This C compiler accepts standard Kernighan and Ritchie C source code and produces TMS34010 assembly language source code. We suggest that you use The C Programming Language (written by Brian W. Kernighan and Dennis M. Ritchie, published by Prentice-Hall) as a companion to the TMS34010 C Compiler User's Guide.

- The TMS34010 Software Development Board User's Guide (literature number SPVU002) describes using the TMS34010 software development board (a high-performance, PC-based graphics card) for testing and developing TMS34010-based graphics systems.

- The *TMS34010 Software Development Board Schematics* (literature number SPVU003) is a companion to the *TMS34010 Software Development Board User's Guide*.

- The TMS34010 Font Library User's Guide (literature number SPVU007) describes a set of fonts that are available for use in a TMS34010-based graphics system.

#### **1.5 Style and Symbol Conventions**

In this document, program listings, program examples, interactive displays, filenames, and symbol names are shown in a special font. Examples use a bold version of the special font for emphasis. Here is a sample program listing:

| 0011 | 00000210 | 0001 | .field | 1, 2 |

|------|----------|------|--------|------|

| 0012 | 00000212 | 0003 | .field | 3, 4 |

| 0013 | 00000215 | 0006 | .field | 6, 3 |

| 0014 | 00000220 |      | .even  |      |

In syntax descriptions, the instruction, command, or directive is in a **bold face** font and parameters are in *italics*. Portions of a syntax that are in **bold face** should be entered as shown; portions of a syntax that are in *italics* describe the type of information that should be entered. Here is an example of an instruction syntax:

#### CVXYL Rs, Rd

**CVXYL** is the instruction. This instructions has two parameters, indicated by *Rs* and *Rd Rs* and *Rd* are abbreviations for *source register* and *destination register*; when you use CVXYL, these parameters must be real register names (such as A0, B1, etc.).

• Square brackets ( [ and ] ) indicate an optional parameter. Here's an example of a directive that has an optional parameter:

.field value [, size in bits]

The .field directive has two parameters. The first parameter, *value*, is required. The second parameter, *size in bits*, is optional. As this syntax shows, if you use the optional second parameter, you must precede it with a comma.

Square brackets are also used as part of the pathname specification for VMS pathnames; in this case, the brackets are actually part of the pathname (they aren't optional).

• Some parameters must be enclosed in double quotes. For example, consider the .sect directive:

.sect "section name"

This directive has one parameter, *section name*. When you use .sect, this parameter must be an actual section name, and it must be enclosed in double quotes.

Braces ( { and } ) indicate a list. The | symbol (read as or) separates items within a list. Here's the syntax of a simulator command that shows an example of a list:

**MM** address { 16-bit-value | 32-bit-value | assembler-statement }

The **MM** command has two parameters. The first parameter must be an *address*; the second parameter can be a *16-bit value*, a *32-bit value*, or an *assembler statement*.

• Some directives can have a varying number of parameters. For example, the .byte directive can have up to 100 parameters. The syntax for this directive is:

.byte value<sub>1</sub> [, ... , value<sub>n</sub>]

This syntax shows that .byte must have at least one value parameter, but you have the option of supplying additional value parameters, separated by commas.

w

# **Software Installation**

This section contains step-by-step instructions for installing and executing the assembler, archiver, linker, object format converter, and simulator<sup>2</sup>. This software can be installed on four operating systems:

#### IBM and TI PCs

- PC-DOS<sup>3</sup> (IBM PC)

- MS-DOS<sup>4</sup> (TI PC)

#### Digital Equipment Corporation VAX-115

- VMS operating system

- DEC Ultrix operating system

- Unix System V operating system

You will find installation instructions for these systems in the following sections:

#### Section

| 000 |                                      | aye   |

|-----|--------------------------------------|-------|

| 2.1 | PC Installations                     | . 2-2 |

| 2.2 | VAX/VMS Installation                 | . 2-4 |

|     | VAX/ULTRIX and System V Installation |       |

Section 1.5 (page 1-7) describes style and symbol conventions that are used in this section.

Dauro

<sup>&</sup>lt;sup>2</sup> The simulator is available in a PC version only.

<sup>&</sup>lt;sup>3</sup> PC-DOS is a trademark of International Business Machines.

<sup>&</sup>lt;sup>4</sup> MS is a trademark of Microsoft Corporation.

<sup>&</sup>lt;sup>5</sup> VAX-11 and VMS are trademarks of Digital Equipment Corporation.

#### 2.1 Installation for IBM/TI PCs with PC/MS-DOS

The TMS34010 software package is shipped on several double-sided, double-density diskettes. Note that two versions of the simulator are shipped (one is for the IBM-PC and one is for the TI-PC). Use the simulator that is appropriate for your system; refer to the release notes for more information.

The tools execute in batch mode on PC-DOS (IBM PC) and MS-DOS (TI PC) systems. At least 512K bytes of memory space must be available in your system.

These instructions are for both hard-disk, single-drive, and and dual-drive systems. On a dual-drive system, the MS/PC-DOS system diskette should be in drive B. The instructions use these symbols for drive names:

- A: Floppy disk drive for hard-disk and single-drive systems *or* source drive for dual-drive systems.

- B: Destination or system disk drive for dual-drive systems.

- C: Winchester (hard disk) for hard disk systems. (E: on TI PCs.)

- 1) Make backups of the product diskettes. First format a blank diskette. Insert a blank (destination) diskette in drive A. Enter:

FORMAT A: CR

When MS/PC-DOS prompts: FORMAT ANOTHER (Y/N)?, respond with N. Now copy the disks.

• On hard-disk or single-drive systems, enter:

DISKCOPY A: A: CR

Follow the system prompts, removing and inserting the product and blank diskettes as directed. When MS/PC-DOS prompts: COPY ANOTHER (Y/N)?, respond with N.

• On **dual-drive** systems, place a product diskette in drive A: and a blank, formatted diskette in drive B. Enter:

COPY A:\*.\* B:\*.\* CR

- 2) Create a directory to contain the TMS34010 software.

- On hard-disk or single-drive systems, enter:

MD E:\GSPTOOLS CR

• On dual-drive systems, enter:

MD B:\GSPTOOLS CR

- Copy the TMS34010 tools onto the hard disk or the system disk. (Remember, you have two copies of the simulator disk – copy only one.)

- On hard disk or single-drive systems, enter:

COPY A:\\*.\* E:\GSPTOOLS\\*.\* CR

• On dual-drive systems, enter:

COPY A:\\*.\* B:\GSPTOOLS\\*.\* CR

#### 2.2 Installation for VAX/VMS

The TMS34010 software tape was created with the VMS BACKUP utility at 1600 BPI. These tools were developed on version 4.4 of VMS. If you are using an earlier version of VMS, you must relink the object files; refer to the release notes for relinking instructions.

- 1) Mount the tape on your tape drive.

- Execute the following commands. Note that you must create a destination directory for the tools; in this example, DEST:directory represents that directory. Replace TAPE: with the name of the tape drive you are using.

| allocate           | TAPE:<br>TAPE: |                |

|--------------------|----------------|----------------|

| mount/for/den=1600 |                |                |

| backup             | TAPE:GSP.bck   | DEST:directory |

| \$<br>dismount     | TAPE:          |                |

| \$<br>dealloc      | TAPE:          |                |

3) The product tape contains a file called setup.com. This file sets up VMS symbols that allow you to execute the tools in the same manner as other VMS commands. Execute the file as follows:

\$ @setup DEST:directory

This sets up symbols that you can use to call the various tools. As the file is executed, it will display the defined symbols on the screen.

#### 2.3 Installation for VAX/ULTRIX and VAX/System V

This tape was made at 1600 BPI using the TAR utility. Follow these instructions to install the software:

- 1) Mount the tape on your tape drive.

- 2) Make sure that the directory that you'll store the tools in is the current directory.

- 3) Enter the TAR command for your system; for example,

TAR x

This copies the entire tape into the directory.

# **Introduction to Common Object File Format**

The assembler and linker create object files that are in a format called *common* object file format, or **COFF**.

COFF makes modular programming easier because it encourages you to think in terms of *blocks* of code and data when you write an assembly language program. These blocks are known as **sections**. Both the assembler and the linker provide directives that allow you to create and manipulate sections.

This chapter provides an overview of COFF sections and includes the following topics:

| Sec | tion                               | Page |

|-----|------------------------------------|------|

| 3.1 | stion<br>Sections                  |      |

| 3.2 | How the Assembler Handles Sections |      |

| 3.3 | How the Linker Handles Sections    | 3-9  |

| 3.4 | Relocation                         |      |

| 3.5 | Loading a Program                  |      |

|     | Symbols in a COFF File             |      |

Appendix A details COFF object file structure; for example, it describes the fields in a file header and the structure of a symbol table entry. Appendix A is mainly useful for those of you who are interested in the internal format of object files.

#### 3.1 Sections

The smallest relocatable unit of an object file is called a **section**. A section is a relocatable block of code or data which will (ultimately) occupy contiguous space in the TMS34010 memory map. Each section of an object file is separate and distinct from the other sections. COFF object files always contain three default sections:

- The .text section usually contains executable code.

- The .data section usually contains initialized data.

- The .bss section usually reserves space for uninitialized variables.

In addition, the assembler and linker allow you to create, name, and link **named** sections that are used similarly to the .data, .text, and .bss sections.

It is important to note that there are two basic types of sections:

- Initialized sections contain data or code. The .text and .data sections are initialized; named sections created with the .sect assembler directive are also initialized.

- **Uninitialized sections** reserve space in the memory map for uninitialized data. The .bss section is uninitialized; named sections created with the .usect assembler directive are also uninitialized.

The assembler provides several directives that allow you to associate various portions of code and data with the appropriate sections. The assembler builds these sections during the assembly process, creating an object file that is organized similarly to the object file shown in Figure 3-1.

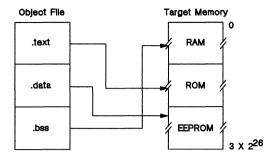

One of the linker's functions is to relocate sections into the target memory map (this is called **allocation**). Since most systems contain several different types of memory, using sections can help you to use target memory more efficiently. All sections are independently relocatable; you can place different sections into various blocks of target memory. For example, you can define a section that contains an initialization routine, and then allocate the routine into a portion of the memory map that contains EPROM.

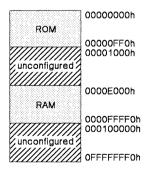

Figure 3-1 shows the relationship between sections in an object file and a hypothetical target memory.

Figure 3-1. Partitioning Memory into Logical Blocks

#### 3.2 How the Assembler Handles Sections

The assembler's main function in regard to sections is to identify the portions of an assembly language program that belong in a particular section. The assembler has six directives that support this function:

- The .bss and .usect directives reserve defined amounts of space in memory (usually RAM). This reserved space is used for storing variables.

- The .text directive identifies the source statements that follow it as executable code. The statements following a .text directive are assembled into the .text section.

- The .data directive identifies the source statements that follow it as initializable data. The statements following a .data directive are assembled into the .data section.

- The .sect directive defines named sections that are used like the .text and .data sections. The statements following a .sect directive are assembled into the named section.

The .bss and .usect directives create *uninitialized sections*; the .text, .data, and .sect directives create *initialized sections*.

#### Note:

If you don't use any of the sections directives, the assembler assembles everything into the .text section.

#### 3.2.1 Uninitialized Sections

Uninitialized sections reserve space in memory; they are usually allocated into RAM. These sections have no actual contents in the object file; they simply reserve memory. A program can use this space at run time for creating and storing variables.

Uninitialized data areas are built by using the .bss and .usect assembler directives. The .bss directive reserves space in the .bss section. The .usect directive reserves space in a specific uninitialized named section. Each time you invoke the .bss directive, the assembler reserves more space in the .bss section. Each time you invoke the .usect directive, the assembler reserves more space in the specified named section.

The syntaxes for these directives are:

.bss symbol, size in bits

symbol .usect "section name", size in bits

- The *symbol* points to the first bit reserved by this invocation of the .bss or .usect directive. The *symbol* corresponds to the name of the variable that you're reserving space for. It can be referenced by any other section and can also be declared as a global symbol (with the .global assembler directive).

- The *size* is an absolute expression. The .bss directive reserves *size* bits in the .bss section; the .usect directive reserves *size* bits in section *name*.

- The *section name* parameter tells the assembler which named section to reserve space in. (For more information about named sections, see Section 3.2.3.)

The .text, .data, and .sect directives tell the assembler to stop assembling into the current section and begin assembling into the indicated section. The .bss and .usect directives, however, **do not** end the current section and begin a new one; they simply "escape" from the current section temporarily. The .bss and .usect directives can appear anywhere in an initialized section without affecting the contents of the initialized section.

#### 3.2.2 Initialized Sections

Initialized sections contain executable code or initialized data. The contents of these sections are stored in the object file and placed in memory when the program is loaded. Each initialized section is separately relocatable and may reference symbols that are defined in other sections. The linker automatically resolves these section-relative references.

Three directives tell the assembler to place code or data into a section. The syntaxes for these directives are:

.text

.data

.sect "section name"

When the assembler encounters one of these directives, it stops assembling into the current section (acting as an implied "end current section" command). It then assembles subsequent code into the respective section until it encounters another .text, .data, or .sect directive.

Sections are built up through an iterative process. For example, when the assembler *first* encounters a .data directive, the .data section is empty. The statements following this first .data directive are assembled into the .data section (until the assembler encounters a .text or .sect directive). If the assembler encounters subsequent .data directives, it *adds* the statements following these .data directives to the statements that are already in the .data section. This creates a single .data section that can be allocated contiguously into memory.

#### 3.2.3 Named Sections

Named sections are sections that **you** create. You can use them like the default .text, .data, and .bss sections, but they are assembled separately from the default sections.

For example, repeated use of the .text directive builds up a single .text section in the object file. When linked, this .text section is allocated into memory as a single unit. Suppose there is a portion of executable code (perhaps an initialization routine) that you don't want allocated with .text. If you assemble this segment of code into a named section, it will be assembled separately from .text, and you will be able to allocate it into memory separately from .text. (Note that you can also assemble initialized data that is separate from the .data section, and you can reserve space for variables that is separate from the .bss section.)

Two directives let you create named sections:

- The .usect directive creates sections that are used like the .bss section. These sections reserve space in RAM for variables.

- The .sect directive create sections that are used like the default .text and .data sections.

The syntaxes for these directives are:

symbol .usect "section name", size

.sect "section name"

The *section name* parameter is the name of the section. Section names are significant to 8 characters. You can create up to 32,767 separate named sections.

Each time you invoke one of these directives with a new name, you create a new named section. Each time you invoke one of these directives with a name that is already used, the assembler assembles the additional code or data (or reserves space) into the section with that name. You cannot use the same names with different directives. That is, you cannot create a section with the .usect directive and then try to use the same section with .sect.

#### 3.2.4 Section Program Counters

The assembler maintains a separate program counter for each section. These program counters are known as section program counters, or **SPCs**.

An SPC represents the current address within a section of code or data. Initially, the assembler sets each SPC to 0. As the assembler fills a section with code or data, it increments the appropriate SPC. If you *resume* assembling into a section, the assembler remembers the appropriate SPC's previous value and continues incrementing the SPC at that point.

The assembler treats each section as if it begins at address 0; the linker relocates each section according to its final location in the memory map.

#### 3.2.5 An Example That Uses Sections Directives

Figure 3-2 shows how you can build COFF sections incrementally, using the sections directives to swap back and forth between the different sections. You can use sections directives:

- To begin assembling into a section for the first time, or

- To continue assembling into a section that already contains code. In this case, the assembler simply appends the new code to the code that is already in the section.

The format of this example is a listing file. By using a listing file, this example shows how the SPCs are modified during assembly. A line in a listing file has four fields:

- 1) The first field contains the source code line counter.

- 2) The second field contains the section program counter.

- 3) The third field contains the object code.

- 4) The fourth field contains the original source statement.

| 0001<br>0002<br>0003                    |                           | ** Asse                                    | mble an i             | **************************************                           |   |  |  |  |  |

|-----------------------------------------|---------------------------|--------------------------------------------|-----------------------|------------------------------------------------------------------|---|--|--|--|--|

| 0004 0000000<br>0005 0000000<br>0000020 | 00000020                  | pixvals:                                   | .data<br>.long        | 64, 32, 16                                                       |   |  |  |  |  |

| 00000040                                | 00000010<br>0005          | pbuf_sz:                                   | .set                  | 5 ; (produces no object code)                                    |   |  |  |  |  |

| 0007                                    |                           | * * * * * * * *                            | * * * * * * * * *     | ******                                                           |   |  |  |  |  |

| 0009                                    |                           | ** Rese<br>******                          | rve space<br>******   | e in .bss for two variables **<br>************                   |   |  |  |  |  |

| 0011 0000000<br>0012 00000020<br>0013   |                           |                                            | .bss<br>.bss          | var1, 32, 1<br>pix_buf, pbuf_sz * 16, 1                          |   |  |  |  |  |

| 0013                                    |                           | ******                                     | * * * * * * * * *     | ******                                                           |   |  |  |  |  |

| 0015<br>0016                            |                           | * *<br>* * * * * * * *                     | S<br>*******          | **<br>***********************************                        |   |  |  |  |  |

| 0017 00000060<br>00000080<br>000000A0   | 22222222                  | colors:                                    | .long                 | 011111111h, 022222222h, 033333333                                | h |  |  |  |  |

| 0018                                    | 555555555                 | ******                                     | *******               | ******                                                           |   |  |  |  |  |

| 0019                                    |                           | ** Assemble code into the .text section ** |                       |                                                                  |   |  |  |  |  |

| 0020                                    |                           | ******                                     |                       | ***********                                                      |   |  |  |  |  |

| 0021 0000000<br>0022 0000000<br>0000010 | 09E0<br>00000020+         | init_a:                                    | .text<br>MOVI         | pix_buf, AO                                                      |   |  |  |  |  |

| 0023 00000030                           | 07A2<br>00000060"         |                                            | MOVE                  | @colors, A2,1                                                    |   |  |  |  |  |

| 0024 00000060<br>0025 00000070          | 2602<br>05A3              |                                            | SLL<br>MOVE           | l6, A2<br>@pixvals, A3                                           |   |  |  |  |  |

| 0026 000000A0<br>0027 000000B0          | 00000000"<br>EE43<br>09C4 |                                            | MOVY<br>MOVI          | A2, A3<br>pbuf_sz, A4                                            |   |  |  |  |  |

| 00000000                                | 0005                      |                                            |                       | *****                                                            |   |  |  |  |  |

| 0028                                    |                           |                                            |                       |                                                                  |   |  |  |  |  |

| 0029<br>0030<br>0031                    |                           | ASSC.                                      |                       | <pre>ther initialized table into  ** section called powers</pre> |   |  |  |  |  |

| 0032 00000000                           |                           |                                            | .sect                 | "powers"                                                         |   |  |  |  |  |

| 0033 0000000<br>0000020<br>00000040     | 00000005                  | powers:                                    | .long                 | 6, 5, 4                                                          |   |  |  |  |  |

| 0034                                    | 0000004                   | *******                                    | *******               | *****                                                            |   |  |  |  |  |

| 0035                                    |                           |                                            |                       | nitialized named section to **                                   |   |  |  |  |  |

| 0036<br>0037                            |                           | * *<br>* * * * * * * *                     | reserve m<br>******** | nore space for variables **<br>***********                       |   |  |  |  |  |

| 0038 0000000<br>0039 00000010           |                           | var2:<br>inbuf:                            | .usect<br>.usect      | "newvars", 1 * 16, 1<br>"newvars", 8 * 16, 1                     |   |  |  |  |  |

| 0040                                    |                           | ******                                     | *******               | *****                                                            |   |  |  |  |  |

| 0042<br>0043                            |                           | * *<br>* * * * * * * * *                   |                       | e more code into .text **                                        |   |  |  |  |  |

| 0044 000000D0                           |                           |                                            | .text                 |                                                                  |   |  |  |  |  |

| 0045 000000D0<br>0046 000000E0          | 9260<br>3C44              | aloop:                                     | MOVE<br>DSJS          | A3, *A0+, 1<br>A4, aloop                                         |   |  |  |  |  |

|                                         |                           |                                            |                       |                                                                  |   |  |  |  |  |

Figure 3-2. Using Sections Directives

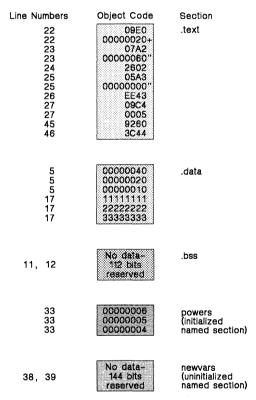

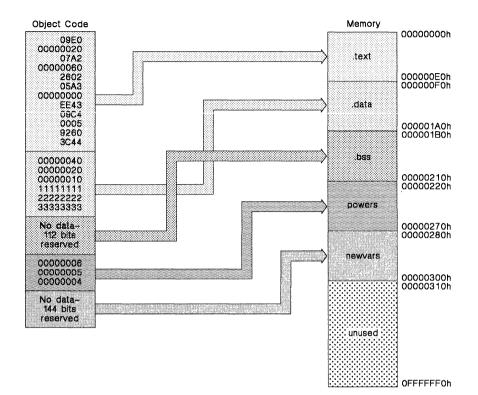

As Figure 3-3 shows, the file in Figure 3-2 creates five sections:

- .text contains 240 bits of object code.

- .data contains 192 bits of object code.

- .bss reserves 112 bits in memory.

- powers is a named section created with the .sect directive; it contains 96 bits of initialized data.

- **newvars** is a named section created with the .usect directive; it reserves 144 bits in memory.

In Figure 3-3, note that the first column shows the source statements in Figure 3-2 that generate the object code in column 2.

Figure 3-3. Object Code Generated by Figure 3-2