### The Connection Machine System

·

CM.5

## VU Programmer's Handbook

CMOST Version 7.2

ýš - 6 - 6 - 7 - 7 - 7 - 7

## Thinking Machines Corporation

Č

| Alternation       Alternation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Interface Registers       Interface Registers         Interface Registers       0x500         Interface Registers       0x500         Interface Registers       0x400         Interface Registers       0x400         Interface Registers       0x400         Interface Registers       0x400         Interface Registers       0x10         InterfaceRegisters       0x10         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| NI Virtual Memory Area<br>(user or supervisor)<br>In the offset<br>(user or supervisor)<br>In the offset<br>(user or supervisor)<br>(user or send first<br>(user or send firs |  |

| Node Virtual Memory Map<br>(with or without VUs installed)       hex address       hex address       Acreation on the stack begions       OS Kernel     0xF800 0000       OS Kernel     0xF800 0000       OS Kernel     0xF800 0000       UU Heap and<br>Stack Regions     0x4000 0000       VU Heap and<br>Stack Regions     0x2000 0000       VU Heap and<br>Stack Regions     0x2000 0000       Orden heap     0x2000 0000       User area     0x2000 0000       User area     0x2000 0000       User area     0x2000 0000       User variables     0x2000 0000       User area     0x2000 0000       User area     0x2000 0000       Dr     0     0       In Interface Send Ifr     Interface Send Ifr       In I I I I     Interface Send Ifr       In I I I I I     Interface Send Ifr       Interface Send Ifr     I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Image: Second state and space     Image: Second state and space       6 5 4 3     0       1     Cause/clast_internal_fault       SBC COM     ni_cause/clast_me_error       ni_cause/clast_me_error     ni_cau |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66: DR L/<br>and to be reaction to be |

### The Connection Machine System

## VU Programmer's Handbook

CMOST Version 7.2, August 1993

**Thinking Machines Corporation**

#### First printing, August 1993

The information in this document is subject to change without notice and should not be construed as a commitment by Thinking Machines Corporation. Thinking Machines reserves the right to make changes to any product described herein.

Although the information in this document has been reviewed and is believed to be reliable, Thinking Machines Corporation assumes no liability for errors in this document. Thinking Machines does not assume any liability arising from the application or use of any information or product described herein.

Connection Machine<sup>®</sup> is a registered trademark of Thinking Machines Corporation. CM, CM-2, CM-200, CM-5, CM-5 Scale 3, and DataVault are trademarks of Thinking Machines Corporation. CMOST, CMAX, and Prism are trademarks of Thinking Machines Corporation. C\*<sup>®</sup> is a registered trademark of Thinking Machines Corporation. Paris, \*Lisp, and CM Fortran are trademarks of Thinking Machines Corporation. CMMD, CMSSL, and CMX11 are trademarks of Thinking Machines Corporation. Thinking Machines<sup>®</sup> is a registered trademark of Thinking Machines Corporation. SPARC and SPARCstation are trademarks of SPARC International, Inc. UNIX is a registered trademark of UNIX System Laboratories, Inc.

Copyright © 1993 by Thinking Machines Corporation. All rights reserved.

Thinking Machines Corporation 245 First Street Cambridge, Massachusetts 02142-1264 (617) 234-1000

## Contents

|                   | anual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ix<br>ciii                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Chapter 1         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                       |

| 1.1               | Programming the CM-5 Vector Units (VUs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                       |

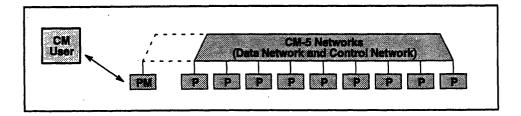

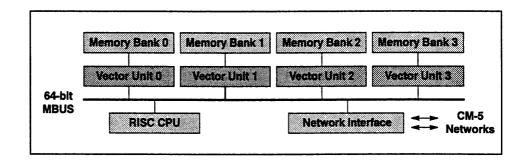

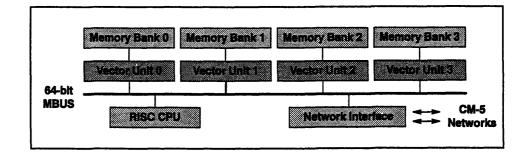

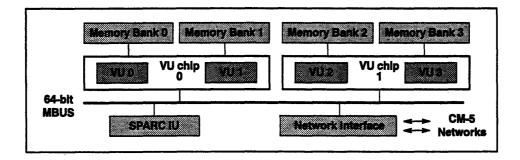

| 1.2               | The CM-5 Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                       |

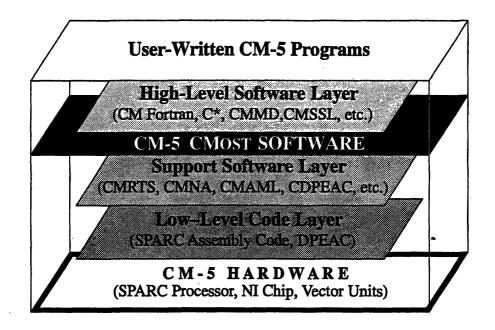

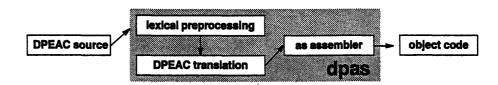

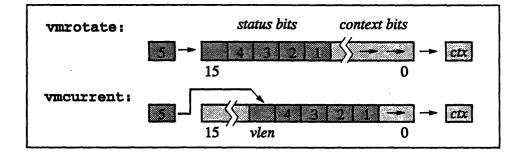

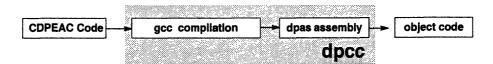

| 1.3               | The DPEAC and CDPEAC Instruction Sets         1.3.1       The CM-5 Assembly Code Level         1.3.2       DPEAC — Vector Unit Assembly Code         1.3.3       CDPEAC — DPEAC Written in C                                                                                                                                                                                                                                                                                                                                                 | 4<br>4<br>5<br>6                                        |

| 1.4               | Using DPEAC and CDPEAC<br>1.4.1 The DPEAC Header File<br>1.4.2 The CDPEAC Header File                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7<br>7<br>7                                             |

| 1.5               | Using This Handbook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                                                       |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                         |

| Chapter 2         | The CM-5 Vector Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9                                                       |

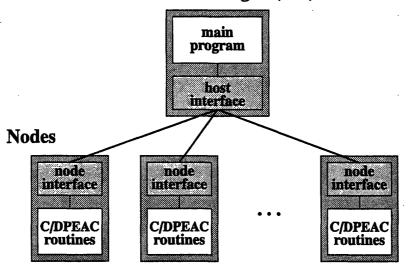

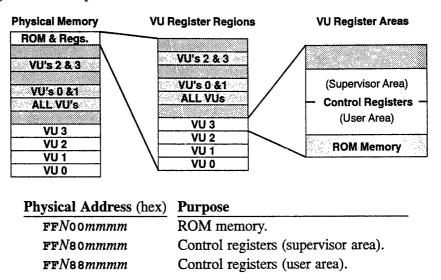

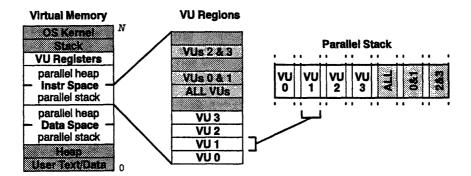

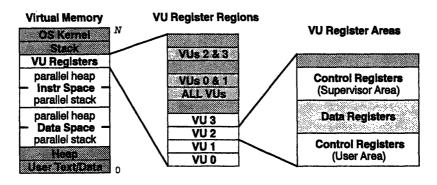

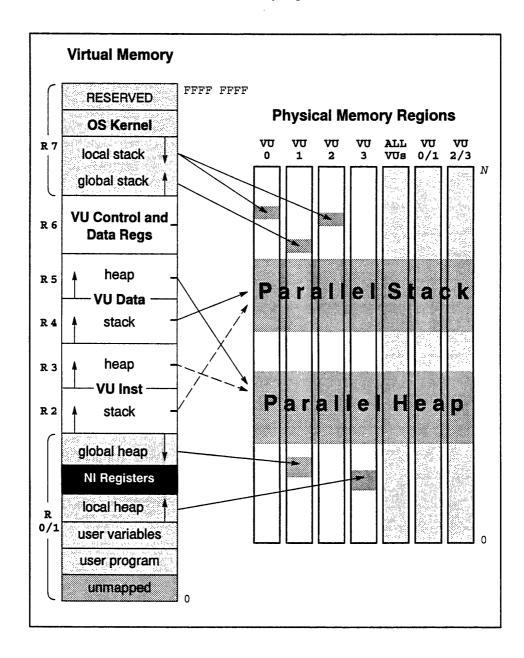

| -                 | CM-5 Vector Unit Accelerators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9<br>9<br>10<br>10                                      |

| 2.1               | CM-5 Vector Unit Accelerators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9<br>10                                                 |

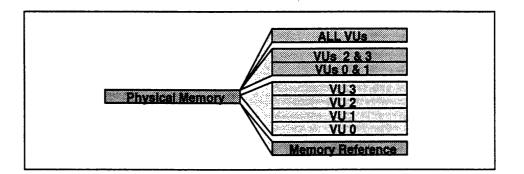

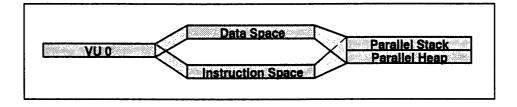

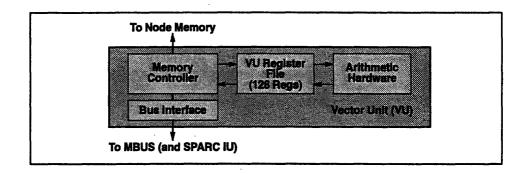

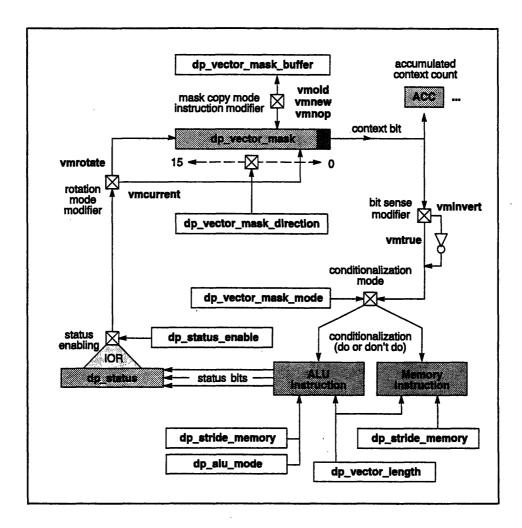

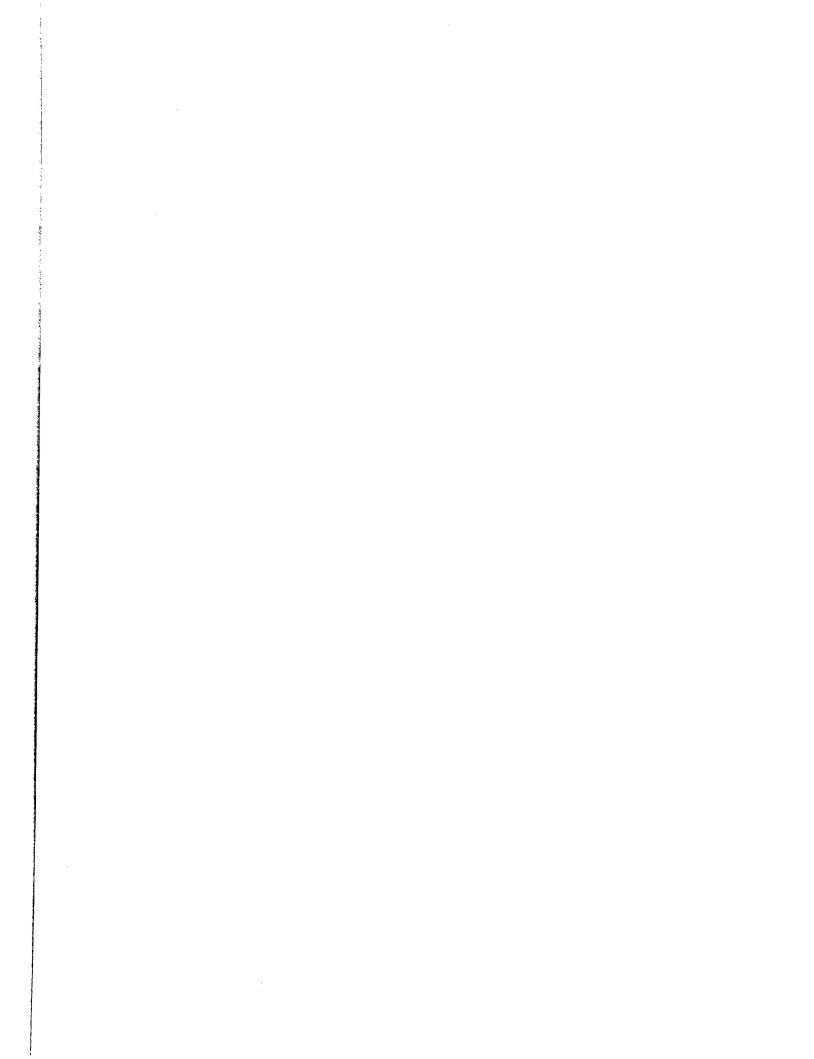

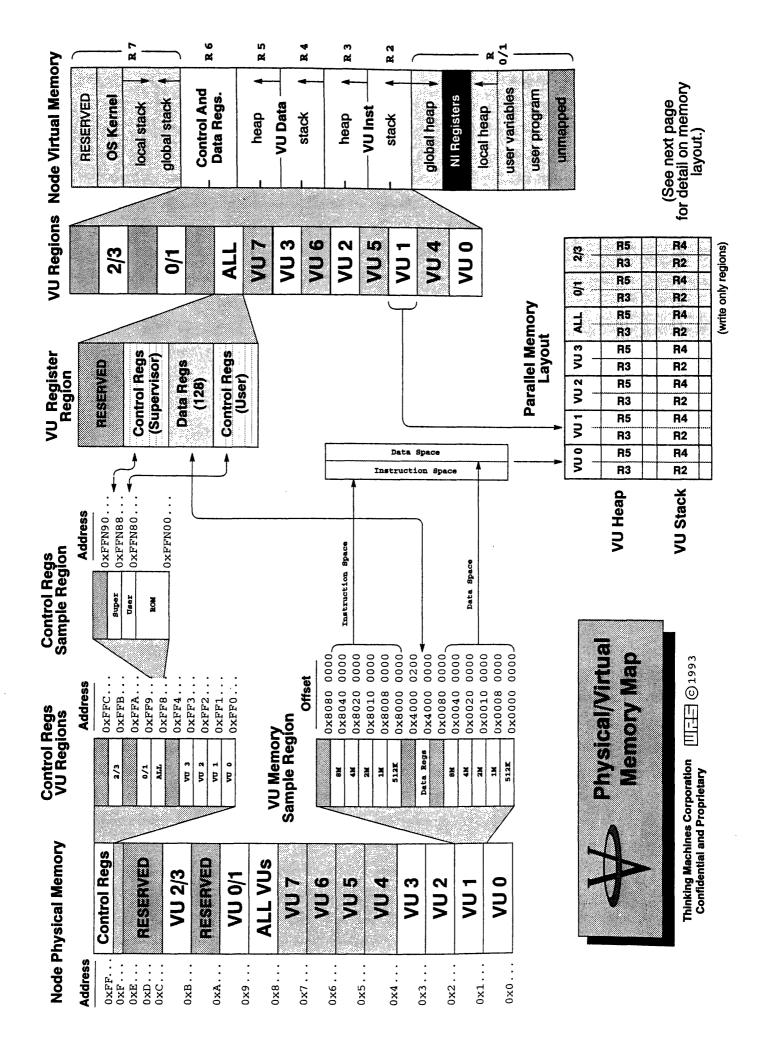

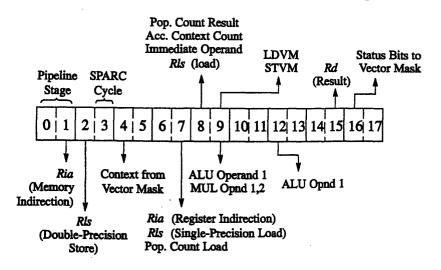

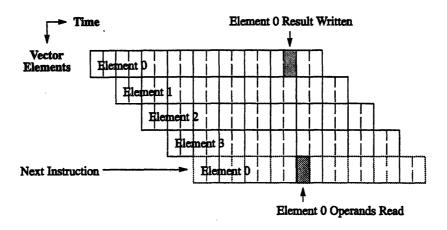

| 2.1               | CM-5 Vector Unit Accelerators         2.1.1 Vector Unit Hardware         2.1.2 VU Virtual Memory Layout         VU Registers         2.2.1 VU Data Registers         2.2.2 VU Control Registers         2.2.2 VU Control Registers         2.3.1 Vector Mask and Conditionalization         2.3.2 ALU Status and Contextualization         2.3.3 Status Register Flags                                                                                                                                                                       | 9<br>10<br>10<br>12<br>12                               |

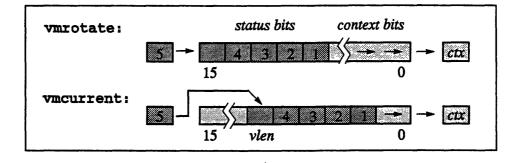

| 2.1<br>2.2<br>2.3 | <ul> <li>CM-5 Vector Unit Accelerators .</li> <li>2.1.1 Vector Unit Hardware .</li> <li>2.1.2 VU Virtual Memory Layout .</li> <li>VU Registers .</li> <li>2.2.1 VU Data Registers .</li> <li>2.2.2 VU Control Registers .</li> <li>Effects of VU Control Registers .</li> <li>2.3.1 Vector Mask and Conditionalization .</li> <li>2.3.2 ALU Status and Contextualization .</li> <li>2.3.3 Status Register Flags .</li> <li>2.3.4 The Vector Mask Buffer .</li> <li>Other VU Features .</li> <li>2.4.1 Accumulated Context Count .</li> </ul> | 9<br>10<br>10<br>12<br>12<br>13<br>14<br>15<br>15<br>16 |

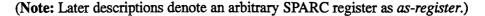

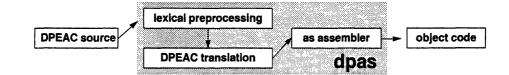

| 3.1 DPEAC Code       19         3.1.1 Chain Loading       20         3.1.2 DPEAC Accessor Instructions       20         3.2 DPEAC Syntax       21         3.2.1 General Syntax       21         3.2.2 SPARC CPU Registers       22         3.2.3 Vector Unit Data Registers       23         3.2.4 Vector Unit Control Registers       24         3.2.5 VU Register and Memory Stride Markers       24         Xu Memory Stride Markers       24         Xu Memory Stride Markers       24         Xu Memory Stride Markers       25         3.2.6 VU Selection in DPEAC Statements       25         3.2.7 VU Selection in DPEAC Accessor Instructions       26         3.3 DPEAC Instructions       27         3.3.1 Scalar and Vector Instructions       27         3.3.2 Register Operands       27         3.3.3 Data Types       28 | Chapter 3 | The DPEAC Instruction Set     | <b>19</b> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------|-----------|

| 3.1.1Chain Loading203.1.2DPEAC Accessor Instructions203.2DPEAC Syntax213.2.1General Syntax213.2.2SPARC CPU Registers223.2.3Vector Unit Data Registers233.2.4Vector Unit Control Registers243.2.5VU Register and Memory Stride Markers24VU Memory Stride Markers24VU Memory Stride Markers253.2.6VU Selection in DPEAC Statements253.2.7VU Selection in DPEAC Accessor Instructions263.3DPEAC Instructions273.3.1Scalar and Vector Instructions273.3.3Data Types28                                                                                                                                                                                                                                                                                                                                                                        | -         |                               |           |

| 3.1.2 DPEAC Accessor Instructions203.2 DPEAC Syntax213.2.1 General Syntax213.2.2 SPARC CPU Registers223.2.3 Vector Unit Data Registers233.2.4 Vector Unit Control Registers243.2.5 VU Register and Memory Stride Markers24VU Memory Stride Markers24VU Memory Stride Markers253.2.6 VU Selection in DPEAC Statements253.2.7 VU Selection in DPEAC Accessor Instructions263.3 DPEAC Instructions273.3.1 Scalar and Vector Instructions273.3.2 Register Operands273.3.3 Data Types28                                                                                                                                                                                                                                                                                                                                                       | 5.1       |                               |           |

| 3.2 DPEAC Syntax213.2.1 General Syntax213.2.2 SPARC CPU Registers223.2.3 Vector Unit Data Registers233.2.4 Vector Unit Control Registers243.2.5 VU Register and Memory Stride Markers24VU Memory Stride Markers24VU Memory Stride Markers253.2.6 VU Selection in DPEAC Statements253.2.7 VU Selection in DPEAC Accessor Instructions263.3 DPEAC Instructions273.3.1 Scalar and Vector Instructions273.3.2 Register Operands273.3.3 Data Types28                                                                                                                                                                                                                                                                                                                                                                                          |           | -                             |           |

| 3.2.1General Syntax213.2.2SPARC CPU Registers223.2.3Vector Unit Data Registers233.2.4Vector Unit Control Registers243.2.5VU Register and Memory Stride Markers24Register Stride Markers24VU Memory Stride Markers253.2.6VU Selection in DPEAC Statements253.2.7VU Selection in DPEAC Accessor Instructions263.3DPEAC Instructions273.3.1Scalar and Vector Instructions273.3.2Register Operands273.3.3Data Types28                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                               |           |

| 3.2.2SPARC CPU Registers223.2.3Vector Unit Data Registers233.2.4Vector Unit Control Registers243.2.5VU Register and Memory Stride Markers24Register Stride Markers24VU Memory Stride Markers253.2.6VU Selection in DPEAC Statements253.2.7VU Selection in DPEAC Accessor Instructions263.3DPEAC Instructions273.3.1Scalar and Vector Instructions273.3.2Register Operands273.3.3Data Types28                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.2       |                               |           |

| 3.2.3Vector Unit Data Registers233.2.4Vector Unit Control Registers243.2.5VU Register and Memory Stride Markers24Register Stride Markers24VU Memory Stride Markers253.2.6VU Selection in DPEAC Statements253.2.7VU Selection in DPEAC Accessor Instructions263.3DPEAC Instructions273.3.1Scalar and Vector Instructions273.3.2Register Operands273.3.3Data Types28                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | -                             |           |

| 3.2.4Vector Unit Control Registers243.2.5VU Register and Memory Stride Markers24Register Stride Markers24VU Memory Stride Markers253.2.6VU Selection in DPEAC Statements253.2.7VU Selection in DPEAC Accessor Instructions263.3DPEAC Instructions273.3.1Scalar and Vector Instructions273.3.2Register Operands273.3.3Data Types28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | -                             |           |

| 3.2.5VU Register and Memory Stride Markers24Register Stride Markers24VU Memory Stride Markers253.2.6VU Selection in DPEAC Statements253.2.7VU Selection in DPEAC Accessor Instructions263.3DPEAC Instructions273.3.1Scalar and Vector Instructions273.3.2Register Operands273.3.3Data Types28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •         |                               |           |

| Register Stride Markers24VU Memory Stride Markers253.2.6VU Selection in DPEAC Statements253.2.7VU Selection in DPEAC Accessor Instructions263.3DPEAC Instructions273.3.1Scalar and Vector Instructions273.3.2Register Operands273.3.3Data Types28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                               |           |

| VU Memory Stride Markers253.2.6VU Selection in DPEAC Statements253.2.7VU Selection in DPEAC Accessor Instructions263.3DPEAC Instructions273.3.1Scalar and Vector Instructions273.3.2Register Operands273.3.3Data Types28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           | - ·                           |           |

| 3.2.6VU Selection in DPEAC Statements253.2.7VU Selection in DPEAC Accessor Instructions263.3DPEAC Instructions273.3.1Scalar and Vector Instructions273.3.2Register Operands273.3.3Data Types28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                               | -         |

| 3.2.7VU Selection in DPEAC Accessor Instructions263.3DPEAC Instructions273.3.1Scalar and Vector Instructions273.3.2Register Operands273.3.3Data Types28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | -                             |           |

| 3.3 DPEAC Instructions       27         3.3.1 Scalar and Vector Instructions       27         3.3.2 Register Operands       27         3.3.3 Data Types       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                               |           |

| 3.3.1       Scalar and Vector Instructions       27         3.3.2       Register Operands       27         3.3.3       Data Types       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                               |           |

| 3.3.2 Register Operands       27         3.3.3 Data Types       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.3       |                               |           |

| 3.3.3 Data Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                               |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                               |           |

| 3.3.4 Arithmetic Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | 3.3.4 Arithmetic Instructions |           |

| 3.3.5 Memory Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                               |           |

| 3.3.6 Modifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | •                             |           |

| 3.4 DPEAC Statement Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34        |                               |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                               |           |

| 3.5 The Short Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                               |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                               |           |

| 3.7 Register Stride (Long) Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.7       | Register Stride (Long) Format |           |

| 3.8 Memory Stride (Long) Format 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.8       | Memory Stride (Long) Format   |           |

| 3.9 Mode Set (Long) Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.9       | -                             | 37        |

| 3.9.1 Mode Set Format Variants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                               | 38        |

| Vector Length Variant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                               | 38        |

| rS1 Stride Variant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                               |           |

| Register Stride Indirection Variant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | -                             |           |

| Memory Stride Indirection Variant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | ·                             | 40        |

| Population Count Variant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           | -                             |           |

| Special Modifier Variant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                               |           |

| Scalar Instruction Variant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                               | . –       |

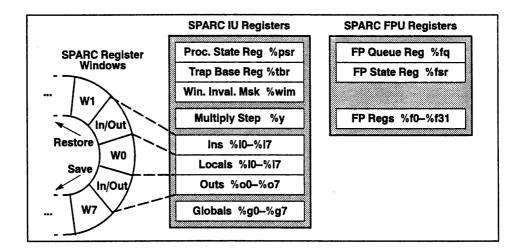

| 3.9.2 Vector Length Modifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |                               |           |

| 3.9.3 Register Stride Indirection423.9.4 Memory Indirection43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | -                             |           |

| 3.9.5 Mode Set Format Modifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                               |           |

#### CMost Version 7.2, August 1993 Copyright © 1993 Thinking Machines Corporation

iv

| Chapter 4 | DPEAC   | Instruction Set Reference                           | 45 |

|-----------|---------|-----------------------------------------------------|----|

| 4.1       | DPEAC A | Arithmetic Instructions                             | 45 |

|           | 4.1.1   | Monadic (One-Source) Arithmetic Instructions        | 45 |

|           | 4.1.2   | Dyadic (Two-Source) Instructions                    | 46 |

|           | 4.1.3   | Arithmetic Comparisons                              | 47 |

|           | 4.1.4   | Compare (Dyadic with rD constant)                   | 48 |

|           | 4.1.5   | Dyadic Mult-Op Operators                            | 48 |

|           | 4.1.6   | Convert Operation (Dyadic with rS2 constant)        | 49 |

|           | 4.1.7   | True Triadic (Three-Source) Operators               | 50 |

|           | 4.1.8   | No-Op Operator                                      | 51 |

| 4.2       | DPEAC N | Memory Instructions                                 | 51 |

|           | 4.2.1   | No-Op Operator                                      | 51 |

| 4.3       | DPEAC I | nstruction Modifiers                                | 52 |

|           | 4.3.1   | Modifiers That Can Be Used in All (or Most) Formats | 52 |

|           | 4.3.2   | Conditionalization Modifiers                        | 53 |

|           | 4.3.3   | Special Modifiers (Mode Set Format Only)            | 54 |

| 4.4       | DPEAC A | Accessor Instructions                               | 56 |

|           | 4.4.1   | VU Register Accessor Instructions                   | 56 |

|           | 4.4.2   | VU Trap Instructions                                | 57 |

|           | 4.4.3   | Vector Mask Instructions                            | 58 |

|           | 4.4.4   | SPARC Accessor Instructions                         | 58 |

|           |         |                                                     |    |

| Chapter 5 | The CD  | PEAC Instruction Set                                | 61 |

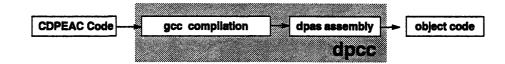

| 5.1       | CDPFAC  | Code                                                | 62 |

| 5.1       | 5.1.1   | VU Instructions                                     | 62 |

|           | 5.1.2   | VU Accessor Instructions                            | 63 |

|           | 5.1.2   | VU Special Instructions                             | 63 |

|           | 5.1.4   | The Join Macro                                      | 63 |

|           |         | Instruction Suffixes                                |    |

|           |         | Argument Macros                                     | 65 |

| 5.2       |         | Syntax                                              | 65 |

|           | 5.2.1   | -                                                   | 65 |

|           | 5.2.2   | Vector Unit Data Registers                          | 66 |

|           | 5.2.3   | Vector Unit Control Registers                       | 66 |

|           | 5.2.4   | Register Offset Macro                               | 67 |

|           | 5.2.5   | VU Register Stride Macros                           | 67 |

|           | 5.2.6   | VU Memory Striding                                  | 68 |

|           | 5.2.7   | VU Selection in CDPEAC Statements                   | 68 |

|           | 5.2.8   | VU Selection in CDPEAC Accessor Instructions        | 69 |

| 5.3       | CDPEAC Instructions                                | 70             |

|-----------|----------------------------------------------------|----------------|

|           | 5.3.1 Scalar and Vector Instructions               | 70             |

|           | 5.3.2 Register Arguments                           | 70             |

|           | 5.3.3 Data Type Argument                           | 71             |

|           | 5.3.4 Arithmetic Instructions                      | 71             |

|           | 5.3.5 Memory Instructions                          | 72             |

|           | 5.3.6 Modifiers                                    | 73             |

| 5.4       | CDPEAC Statement Formats                           | 74             |

| 5.5       | The Short Format                                   | 75             |

| 5.6       | Immediate (Long) Format                            | 77             |

| 5.7       | Register Stride (Long) Format                      | 78             |

| 5.8       | Memory Stride (Long) Format                        | 79             |

| 5.9       | Mode Set (Long) Format                             | 80             |

|           | 5.9.1 Mode Set Format Variants                     | 81             |

|           | Vector Length Variant                              | 81             |

|           | rS1 Stride Variant                                 | 82             |

|           | Register Stride Indirection Variant                | 82             |

|           | Memory Stride Indirection Variant                  | 83             |

|           | Population Count Variant                           | 83             |

|           | Special Modifier Variant                           | 84             |

|           | Scalar Instruction Variant                         | 84             |

|           | 5.9.2 Vector Length Instruction Suffixes           | 85             |

|           | 5.9.3 Register Stride Indirection                  | 86             |

|           | 5.9.4 Memory Indirection                           | 86             |

|           | 5.9.5 Mode Set Format Modifier                     | 87             |

|           |                                                    |                |

| Chapter 6 | CDPEAC Instruction Set Reference                   | 89             |

| 6.1       | The CDPEAC Join Macro                              | 89             |

| 6.2       | CDPEAC Type Abbreviations                          | <b>89</b>      |

| 6.3       | CDPEAC Argument Macros                             | 90             |

| 6.4       | Instruction Suffixes                               | <b>9</b> 0     |

| 6.5       | CDPEAC Arithmetic Instructions                     | 91             |

|           | 6.5.1 Monadic (One-Source) Arithmetic Instructions | 91             |

|           | 6.5.2 Dyadic (Two-Source) Instructions             | 92             |

|           | 6.5.3 Arithmetic Comparisons                       | 93             |

|           | 6.5.4 Compare (Dyadic with rD constant)            | <b>93</b>      |

|           | 6.5.5 Dyadic Mult-Op Operators                     | <del>9</del> 4 |

|           | 6.5.6 Convert Operation (Dyadic with Rs2 Constant) | 95             |

vi

|                                        | 6.5.7 True Triadic (Three-Source) Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | 6.5.8 No-Op Operator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.6                                    | CDPEAC Memory Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.7                                    | CDPEAC Statement Modifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                        | 6.7.1 Modifiers That Can Be Used in All (or Most) Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                        | 6.7.2 Conditionalization Modifiers 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        | 6.7.3 Special Modifiers (Mode Set Format Only) 100                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.8                                    | CDPEAC Accessor Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                        | 6.8.1 VU Register Accessor Instructions 102                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.9                                    | CDPEAC Special Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chapter 7                              | Using DPEAC/CDPEAC in Programs 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7.1                                    | Example: An Arithmetic Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.2                                    | Low-Level Program Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.2                                    | Low-Level Program Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.2                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.2                                    | 7.2.1 Program Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.2                                    | 7.2.1 Program Files       107         Source File Naming Conventions       107                                                                                                                                                                                                                                                                                                                                                                                                                           |

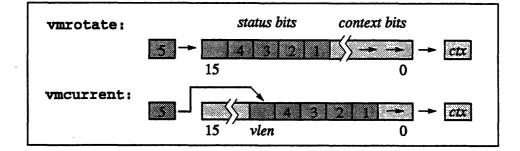

|                                        | 7.2.1 Program Files       107         Source File Naming Conventions       107         7.2.2 Host/Node Interface Naming Conventions       108                                                                                                                                                                                                                                                                                                                                                            |

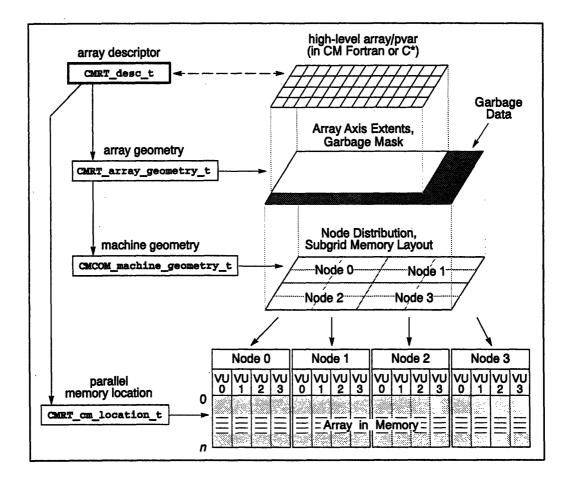

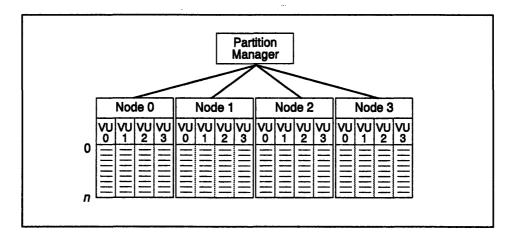

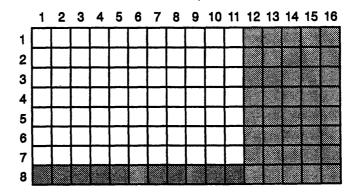

| 7.3                                    | 7.2.1 Program Files       107         Source File Naming Conventions       107         7.2.2 Host/Node Interface Naming Conventions       108         Passing Arrays into DPEAC and CDPEAC Routines       109                                                                                                                                                                                                                                                                                            |

| 7.3<br>7.4                             | 7.2.1 Program Files       107         Source File Naming Conventions       107         7.2.2 Host/Node Interface Naming Conventions       108         Passing Arrays into DPEAC and CDPEAC Routines       109         Sample Program Source Files       110                                                                                                                                                                                                                                              |

| 7.3<br>7.4<br>7.5                      | 7.2.1       Program Files       107         Source File Naming Conventions       107         7.2.2       Host/Node Interface Naming Conventions       108         Passing Arrays into DPEAC and CDPEAC Routines       109         Sample Program Source Files       110         The Main CM Fortran Program (main.fcm)       110                                                                                                                                                                         |