# REFERENCE

# MANUAL

T-5101

INTERACTIVE

DISPLAY

TERMINAL

Systematics General Corporation

National Scientific Laboratories Division

## TABLE OF CONTENTS

| Paragraph                                                                                                                                            | Page                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Section I - Specification                                                                                                                            |                                                                     |

| IntroductionT-5101 Specification                                                                                                                     | 1-1<br>1-3                                                          |

| Section II - Programming                                                                                                                             |                                                                     |

| Microcontroller Programming                                                                                                                          | 2-1<br>2-12<br>2-23<br>2-24<br>2-25<br>2-25<br>2-25<br>2-26<br>2-27 |

| Section III - Theory of Operation                                                                                                                    |                                                                     |

| Introduction                                                                                                                                         | 3-3<br>3-5<br>3-5<br>3-6<br>3-12<br>3-12<br>3-14<br>3-18<br>3-18    |

| Section IV - Monitor Description                                                                                                                     |                                                                     |

| Monitor Electrical Specifications Data Display Specifications Environmental Specifications Human Factors Specifications Controls Theory of Operation | 4-1<br>4-2<br>4-3<br>4-3<br>4-3<br>4-6                              |

| Section V - Maintenance and Failure Analysis                                                                                                         |                                                                     |

| Care of the T-5101                                                                                                                                   | 5-22                                                                |

## TABLE OF CONTENTS (cont)

| <u>Paragraph</u>                              | <u>Page</u> |

|-----------------------------------------------|-------------|

| Section VI - Scheduled Maintenance            |             |

| Scheduled Maintenance                         | 6-1<br>6-7  |

| Section VII - Schematic Drawings and Diagrams | 7-1         |

| Section VIII - Renewal Parts Information      | 8-1         |

# LIST OF TABLES

| <u>Table</u>                                                                |                                                     | Page                                                 |

|-----------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11 | T-5101 Functional Units                             | 2-14<br>2-16<br>2-17<br>2-18<br>2-19<br>2-21<br>2-24 |

| 3-1<br>3-2<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8                               | Keyboard Operation Binary Codes                     | 3-11<br>3-13<br>3-17<br>3-20<br>3-22                 |

| 4-1<br>4-2                                                                  | Input Data SpecificationsCRT Display Specifications | 4-1<br>4-2                                           |

| 5-1<br>5-2<br>5-3<br>5-4                                                    | Baud Rate Selections                                | 5-21                                                 |

## LIST OF FIGURES

| Figure       |                                                                | Page         |

|--------------|----------------------------------------------------------------|--------------|

| 1-1          | T-5101 Interactive Display Terminal                            | 1-2          |

| 2-1          | T-5101 Data Flow Block Diagram                                 | 2-1          |

| 2-2          | T-5101 Asynchronous Receiver/Transmitter                       | 2-3          |

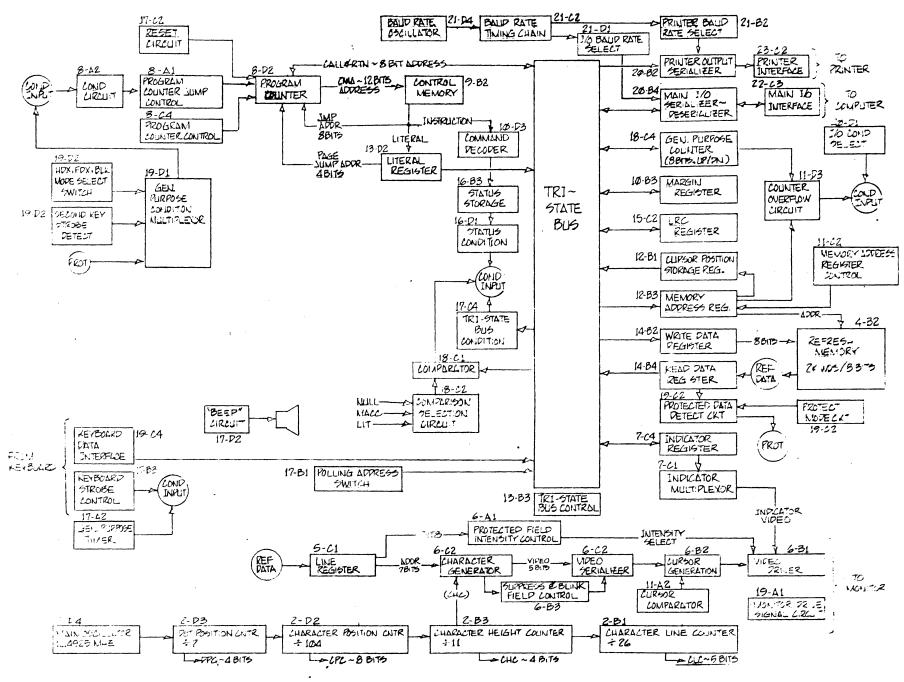

| 3-1          | T-5101 Functional Block Diagram                                | 3-2          |

| 3-2<br>3-3   | Character FormatKeyboard                                       | 3-4<br>3-7   |

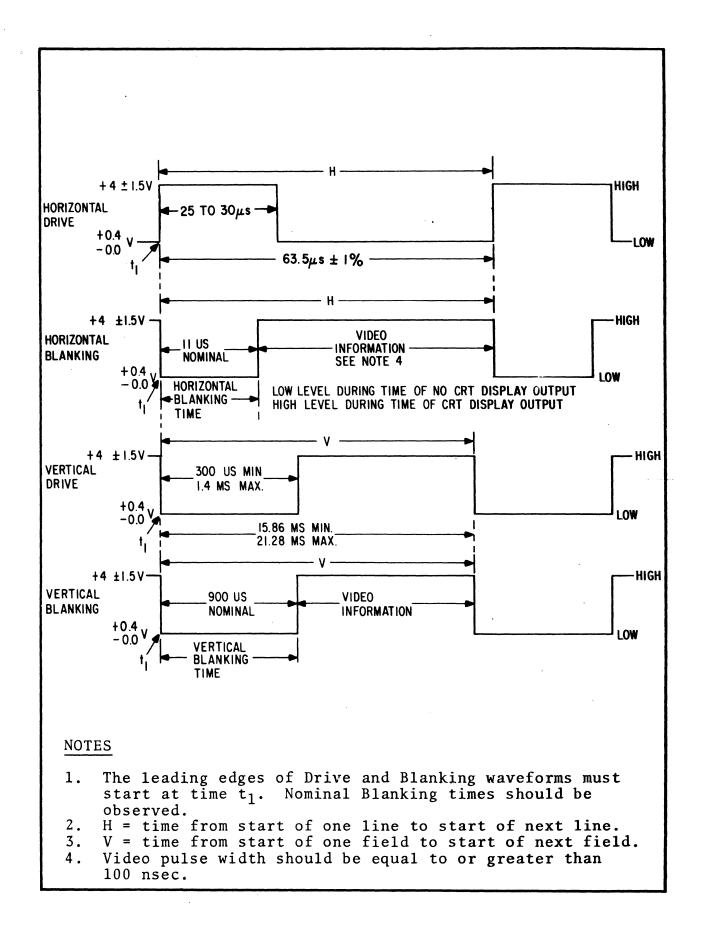

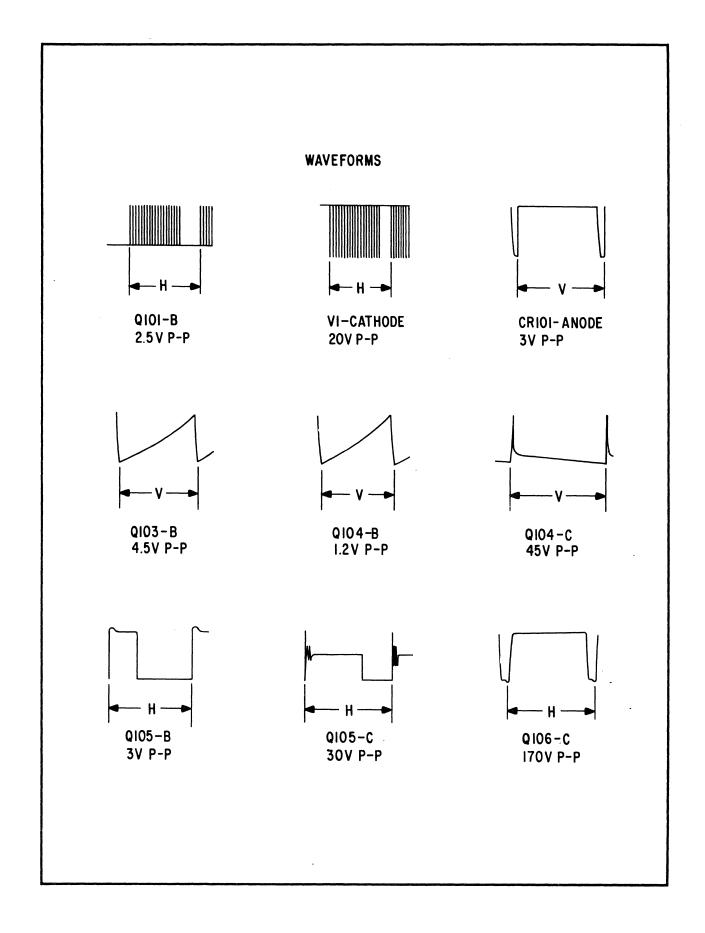

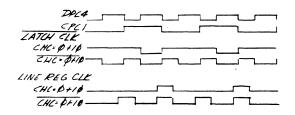

| 4-1          | Synchronization and Blanking Generator Waveforms               | 4-5          |

| 5-1          | External Controls                                              | 5-2          |

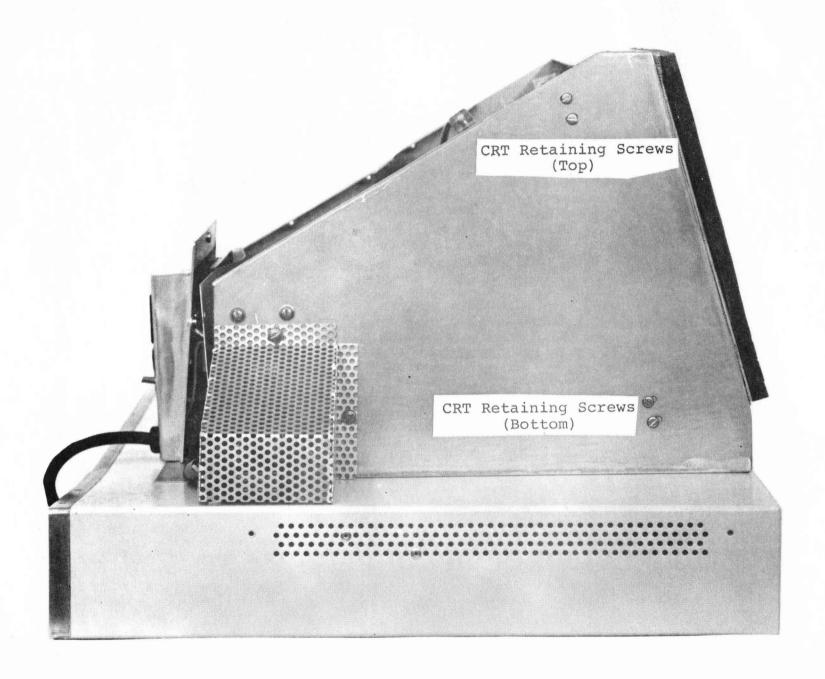

| 5-2          | Video Shield Retaining Screws                                  | 5-4          |

| 5-3          | Rear Cover Retraining Screws                                   | 5-5          |

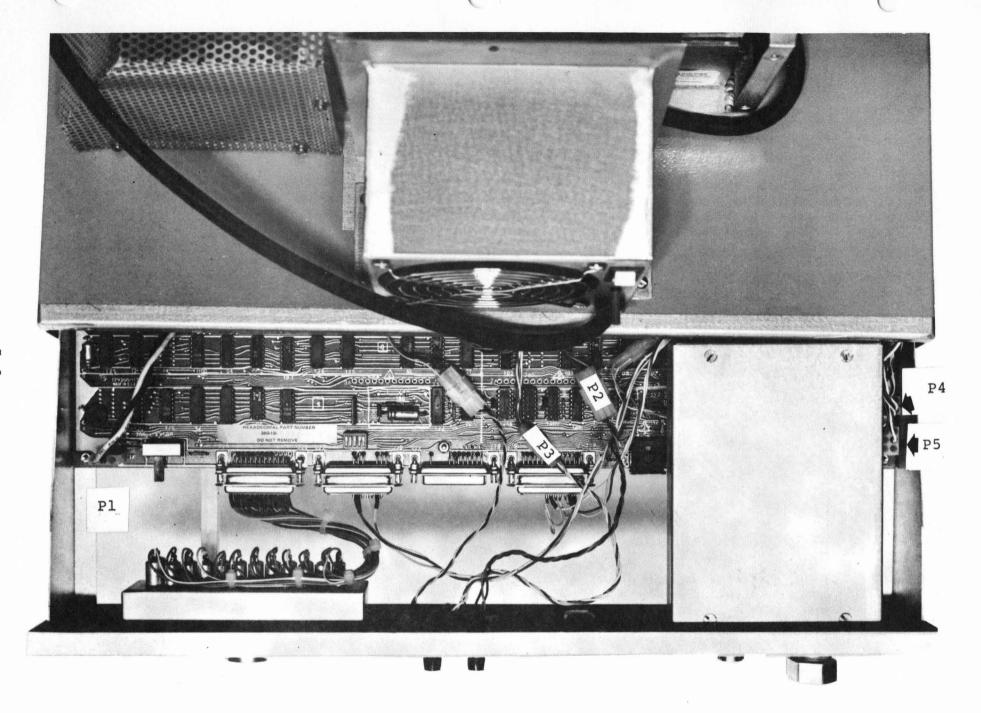

| 5-4          | Logic Assembly Interconnections                                | 5-6          |

| 5-5          | Logic Power Supply Shields                                     | 5-8          |

| 5-6          | Logic Power Supply                                             | 5-9          |

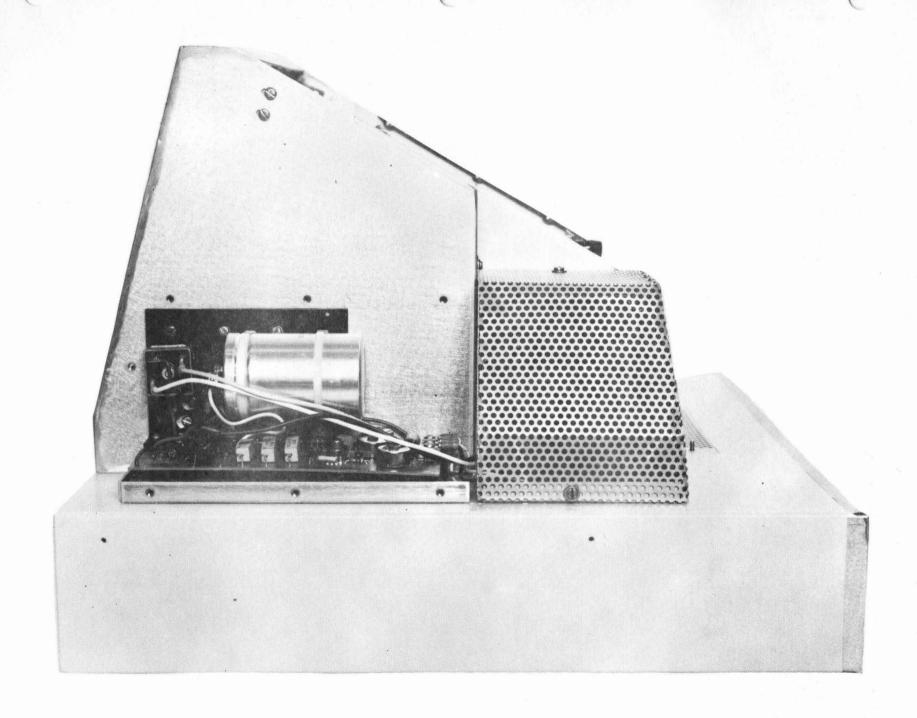

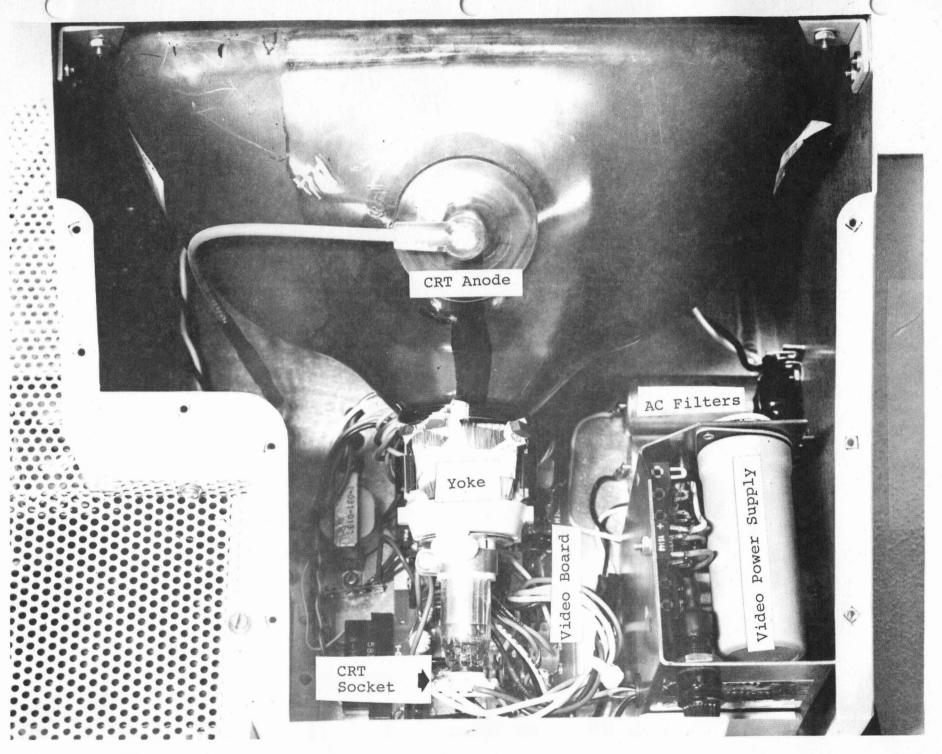

| 5-7          | Video Enclosure                                                | 5-10         |

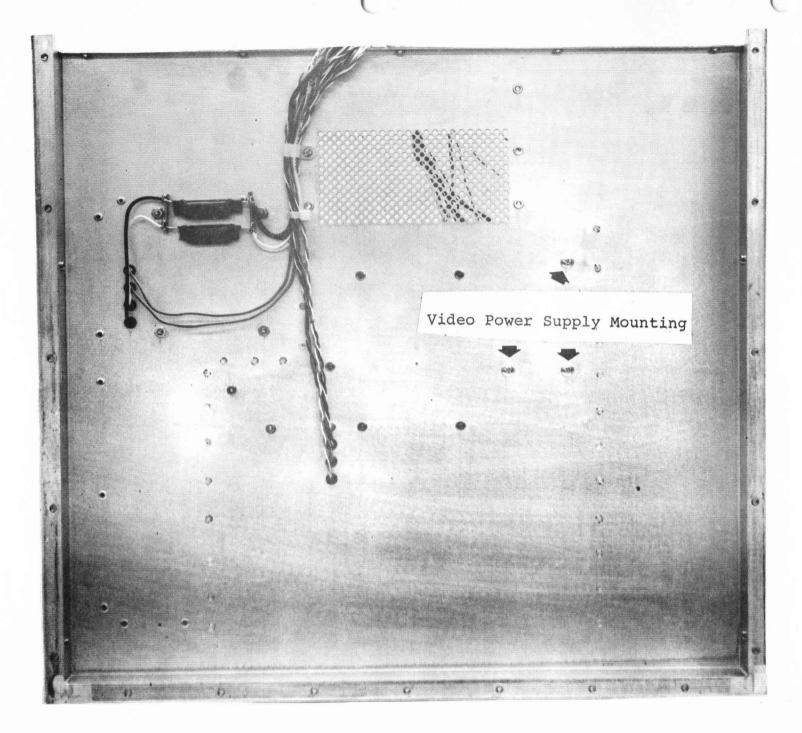

| 5-8          | Chassis Cabling                                                |              |

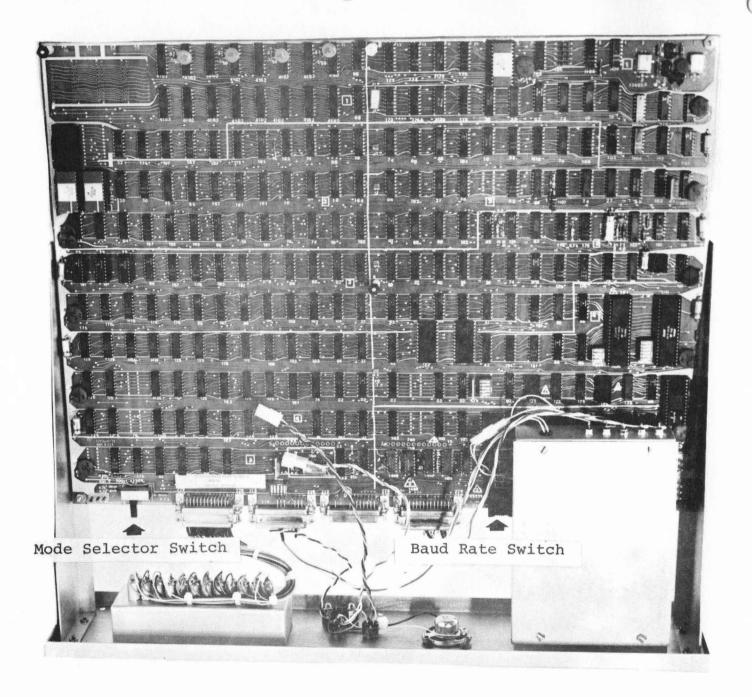

| 5-9          | Internal Controls                                              | 5-14         |

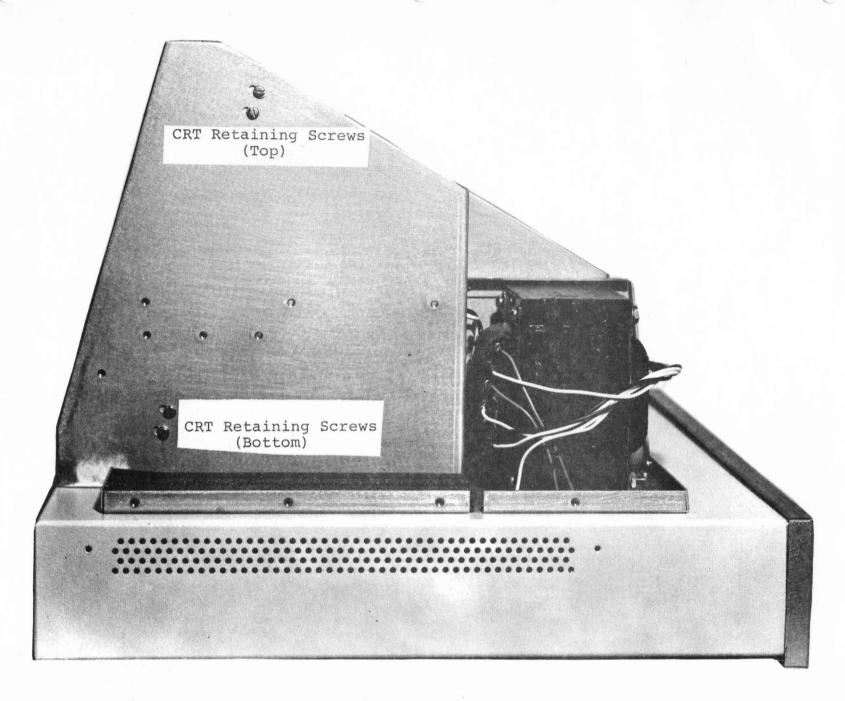

| 5-10         | CRT Mounting (Right Side)                                      | 5-15         |

| 5-11         | CRT Mounting (Left Side)                                       | 5-16         |

| 5-12         | Voltage Waveforms for Display                                  | 5-12         |

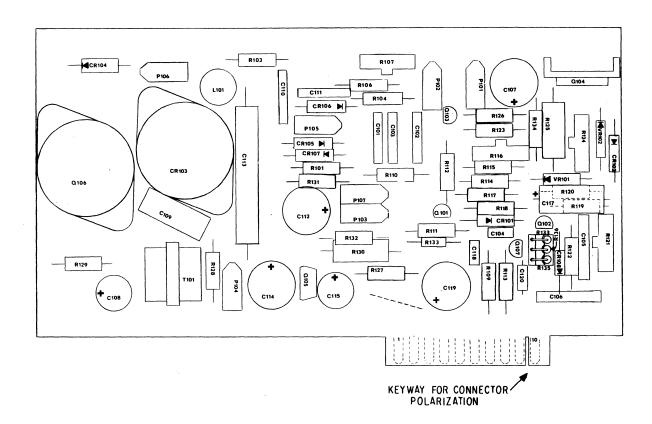

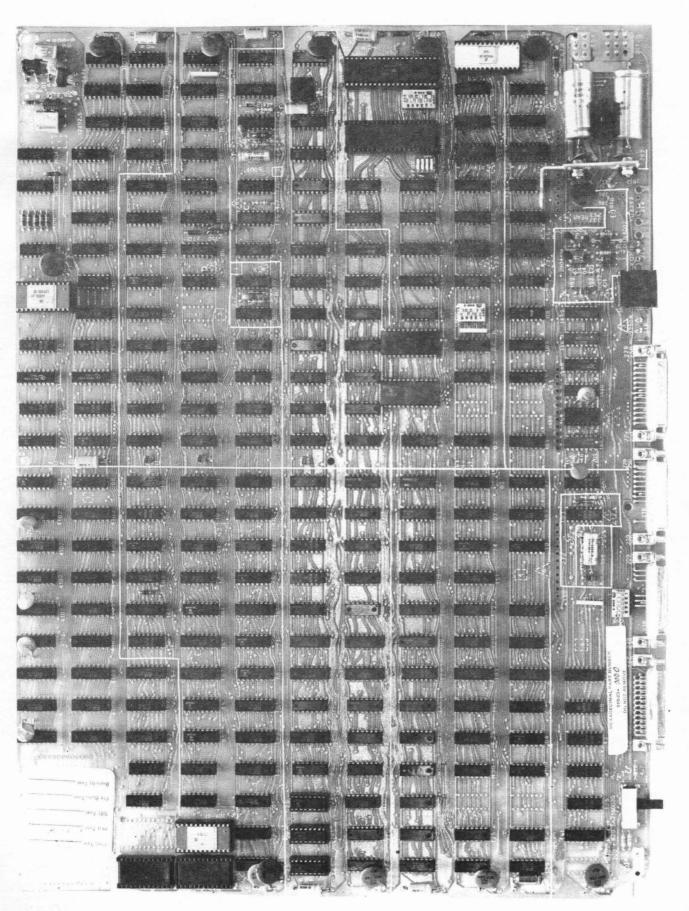

| 5-13<br>5-14 | Video Circuit Board Component Location Main Logic Board Layout | 5-24<br>5-30 |

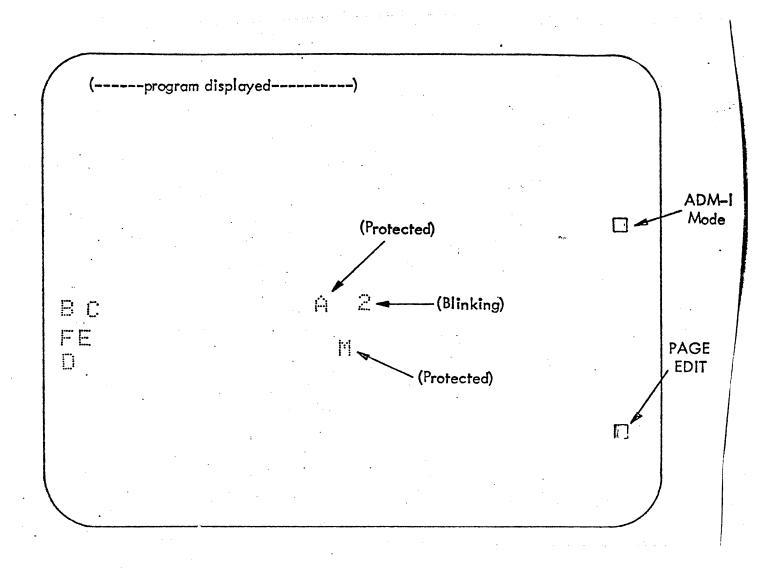

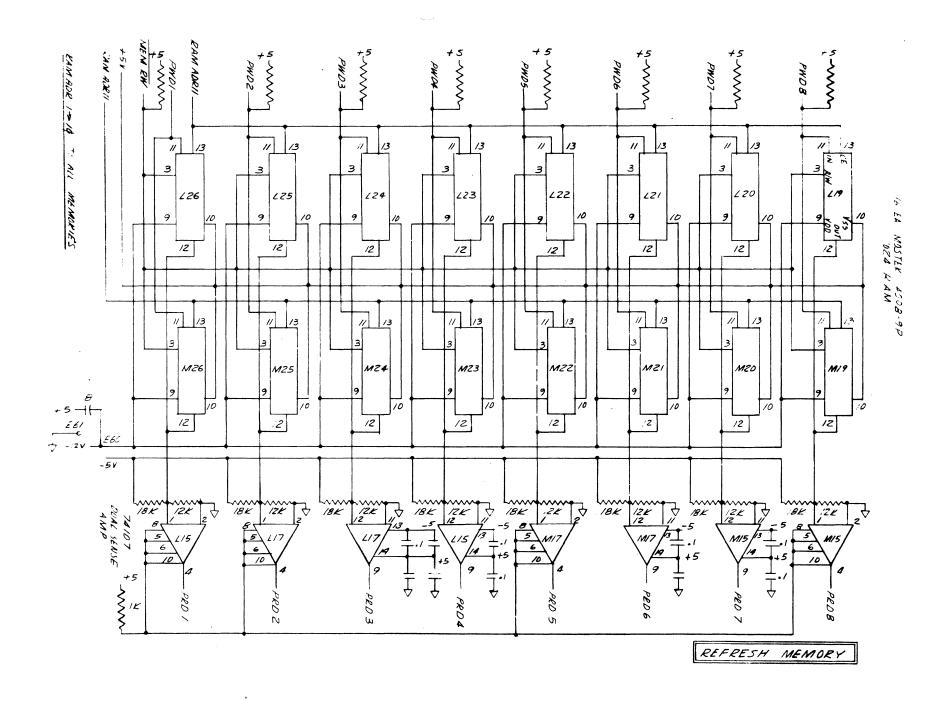

| 6-1          | Program Display                                                | 6-6          |

| 7-1 th       |                                                                |              |

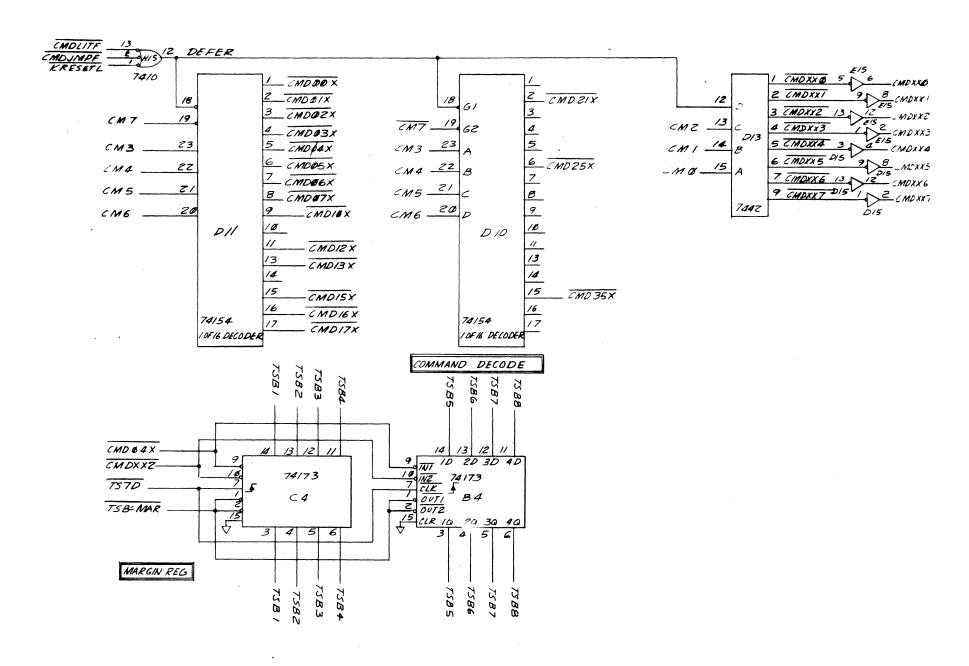

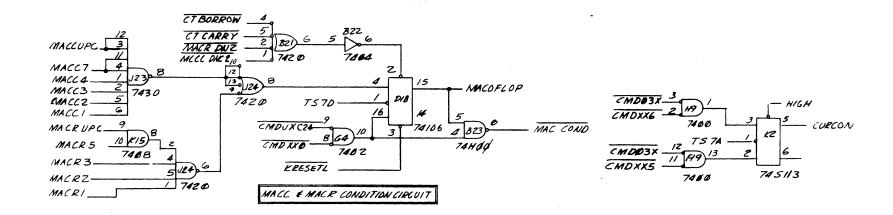

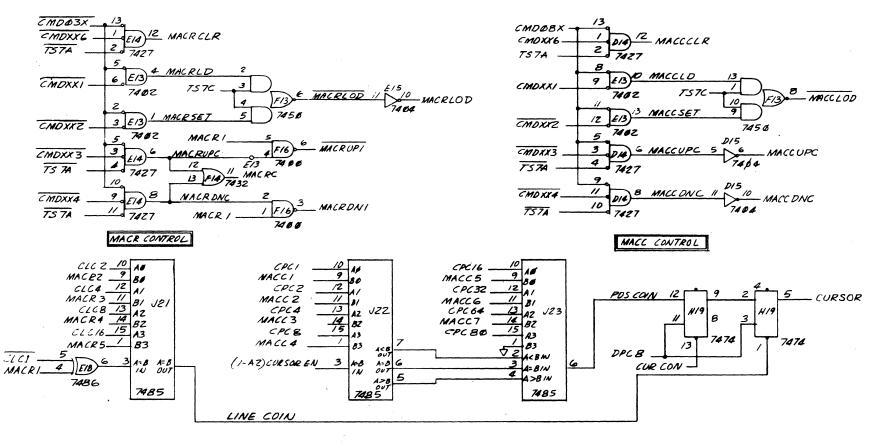

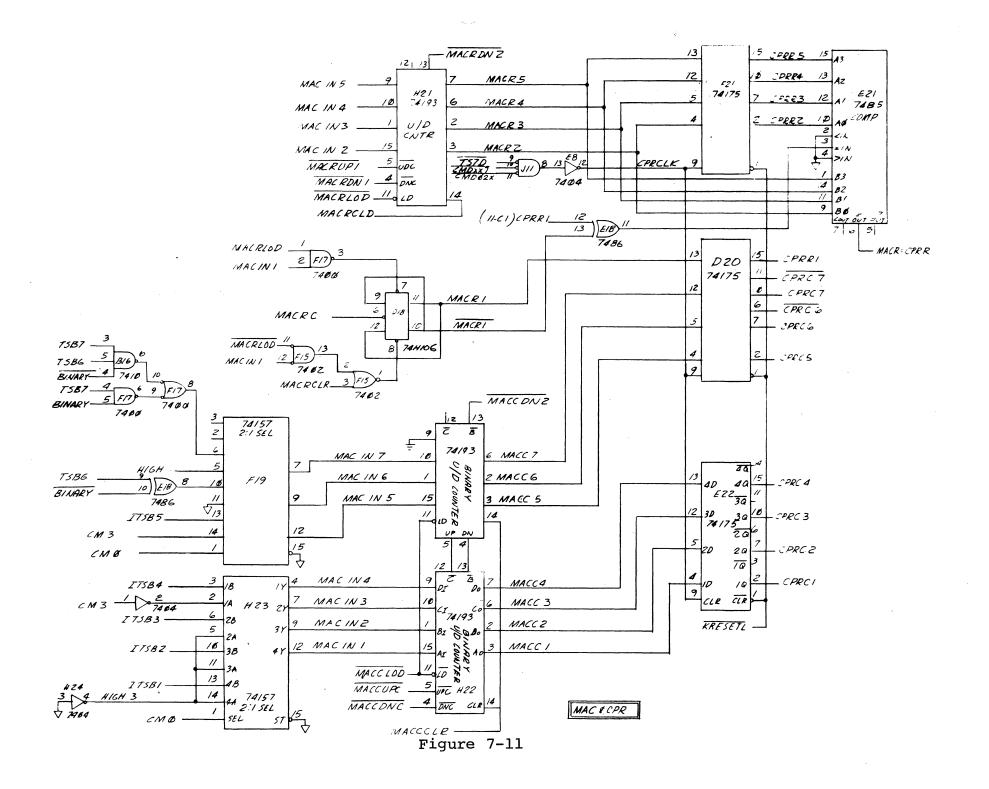

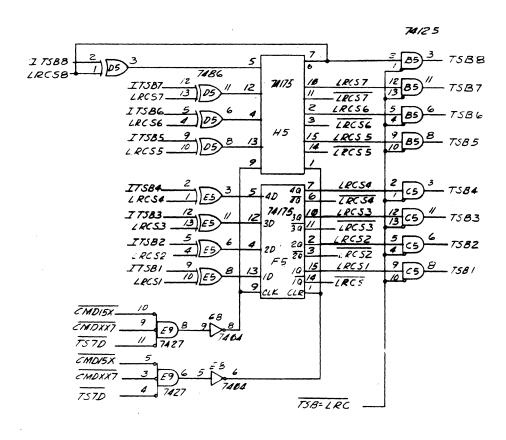

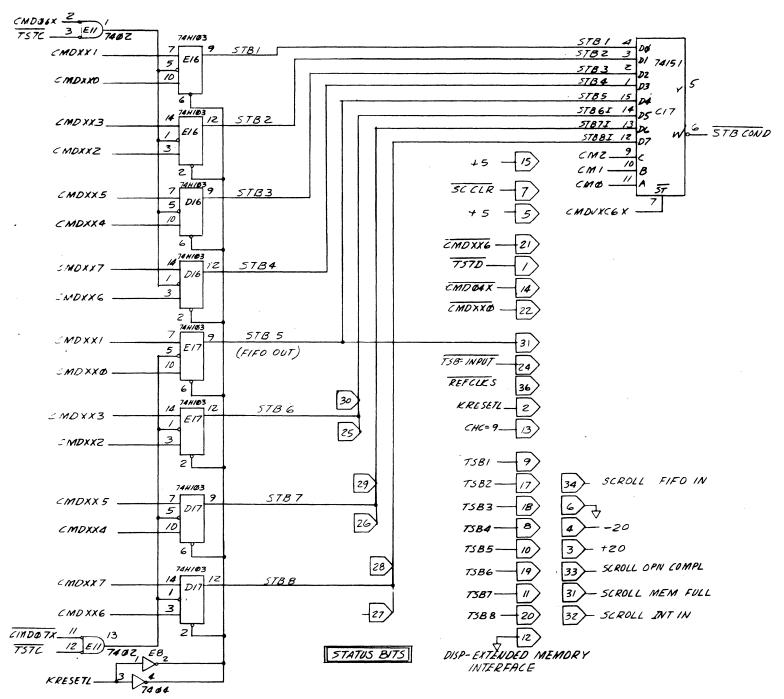

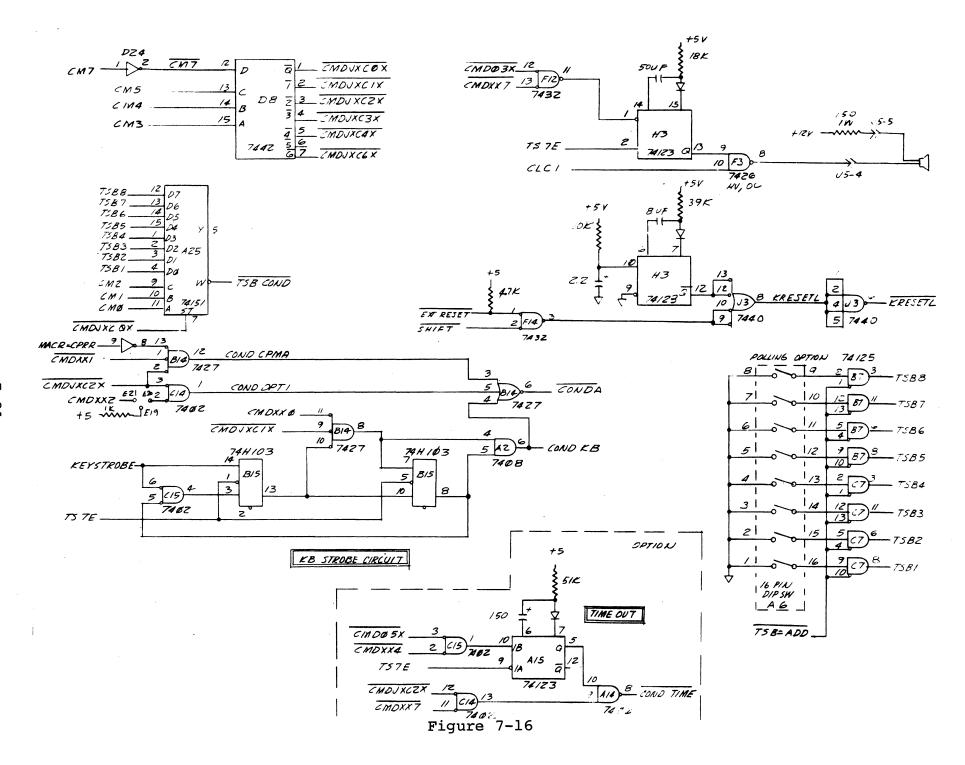

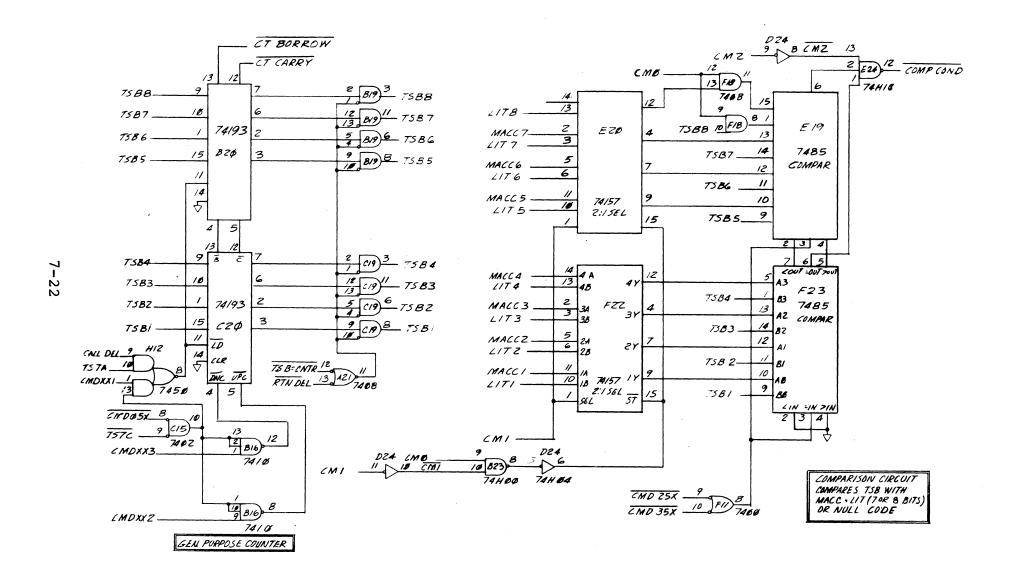

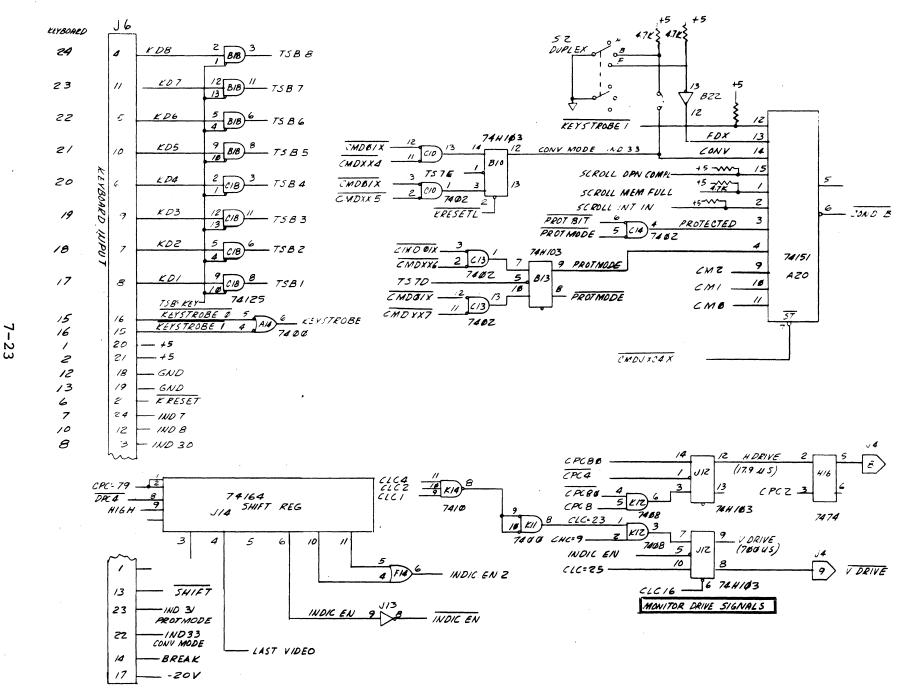

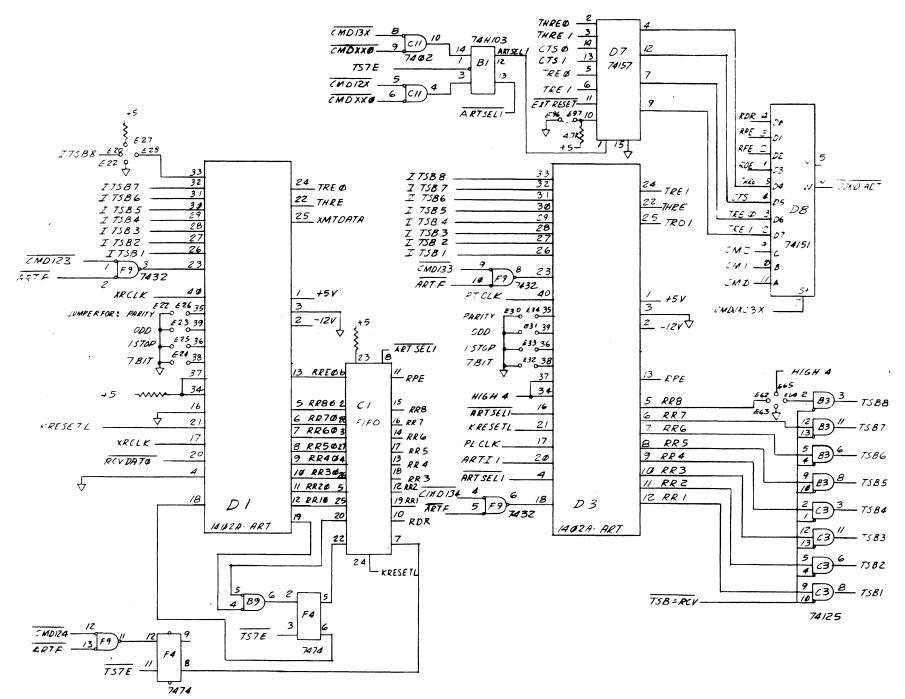

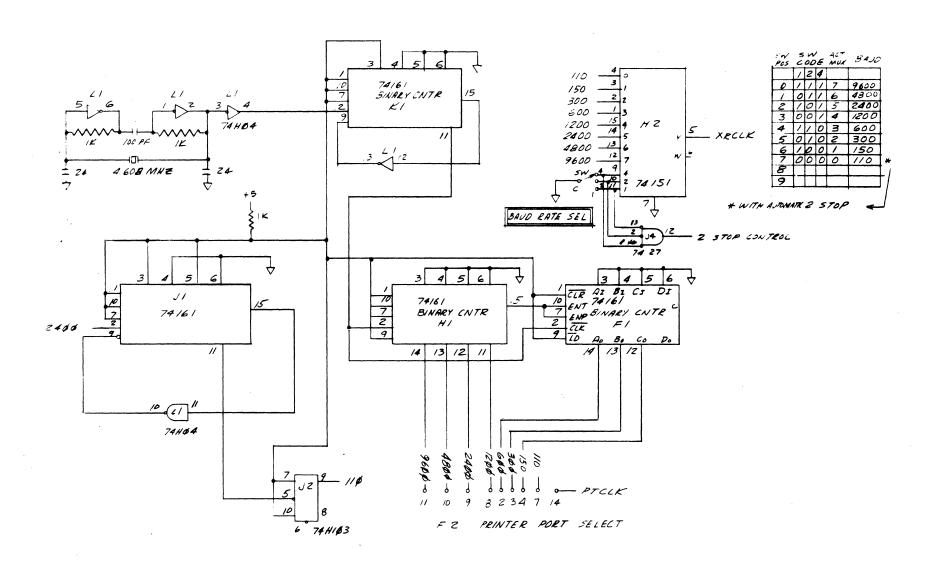

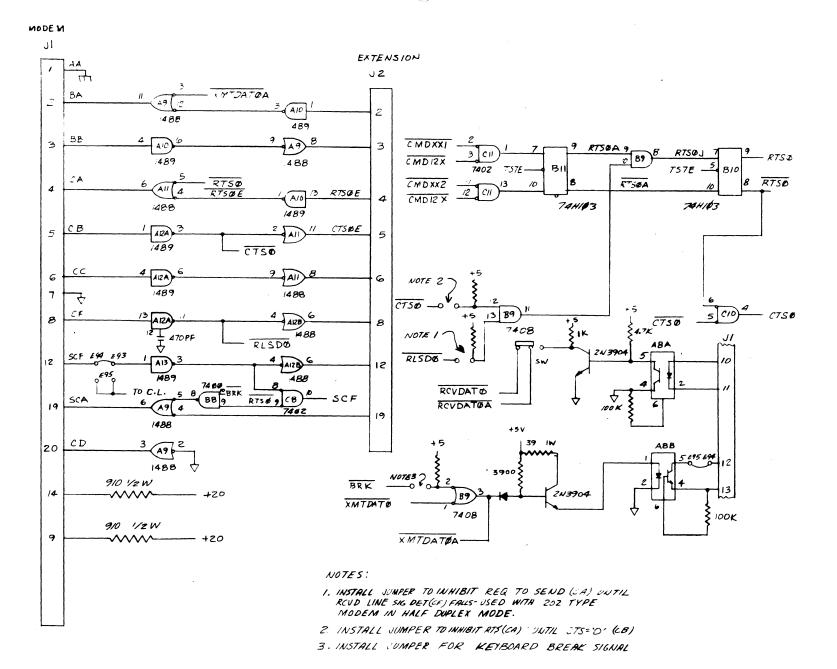

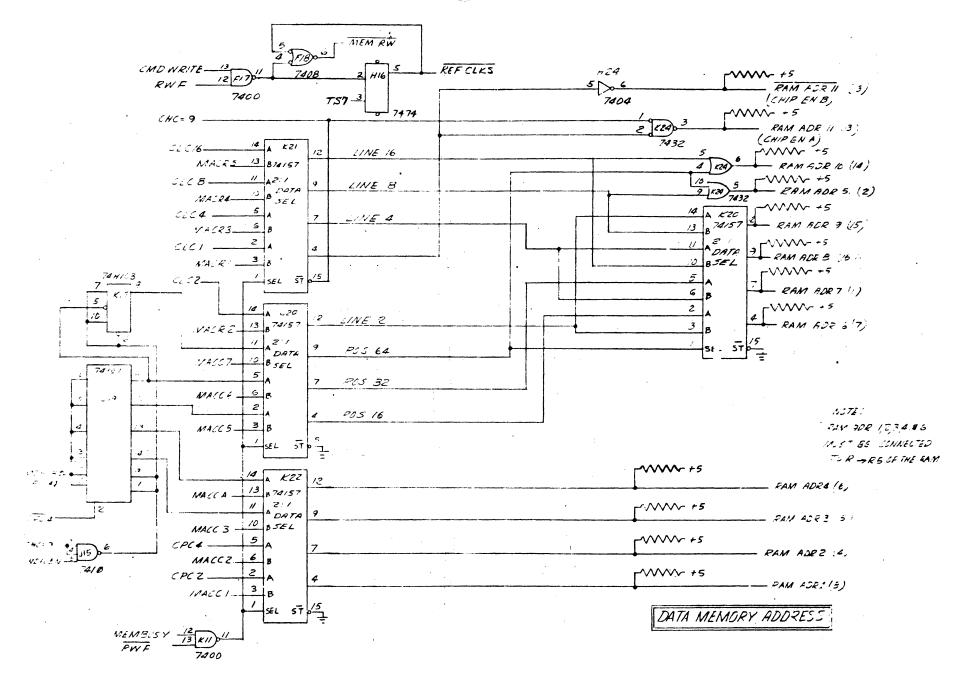

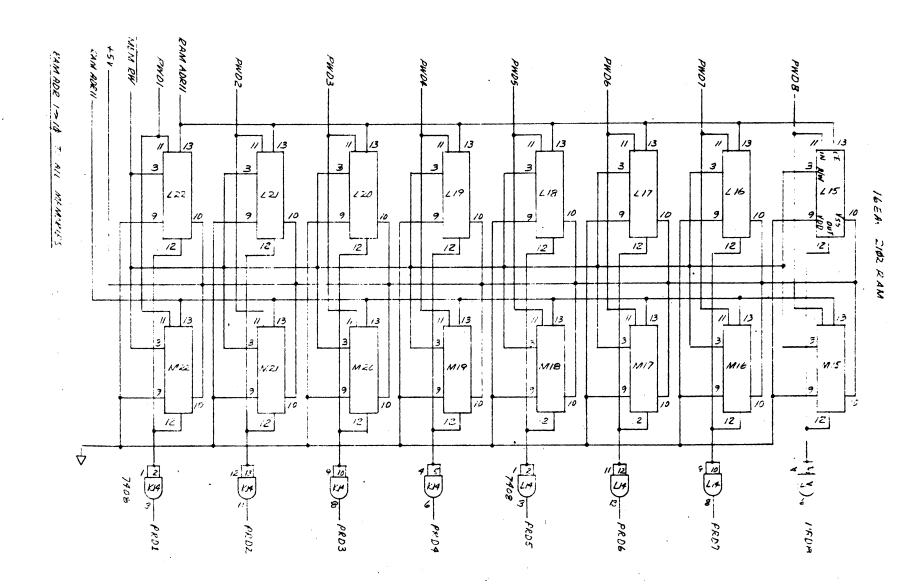

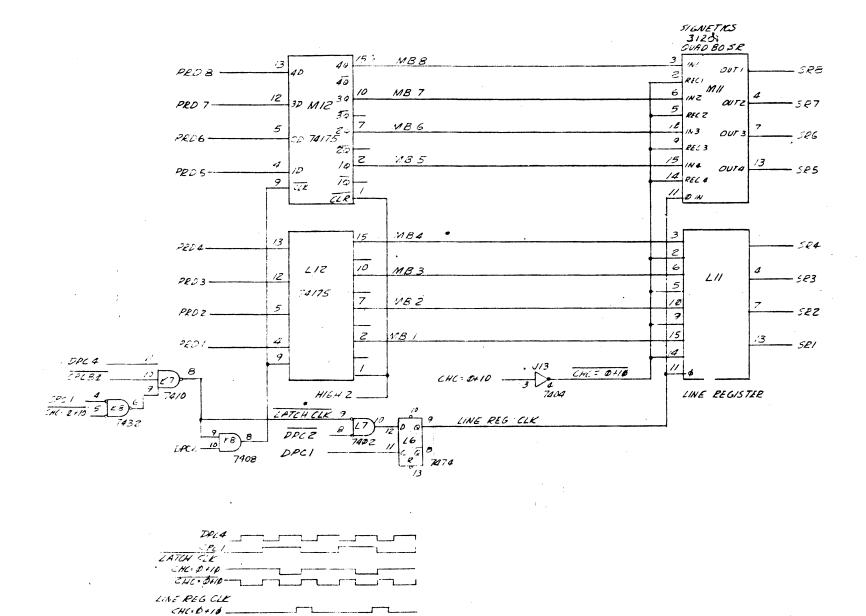

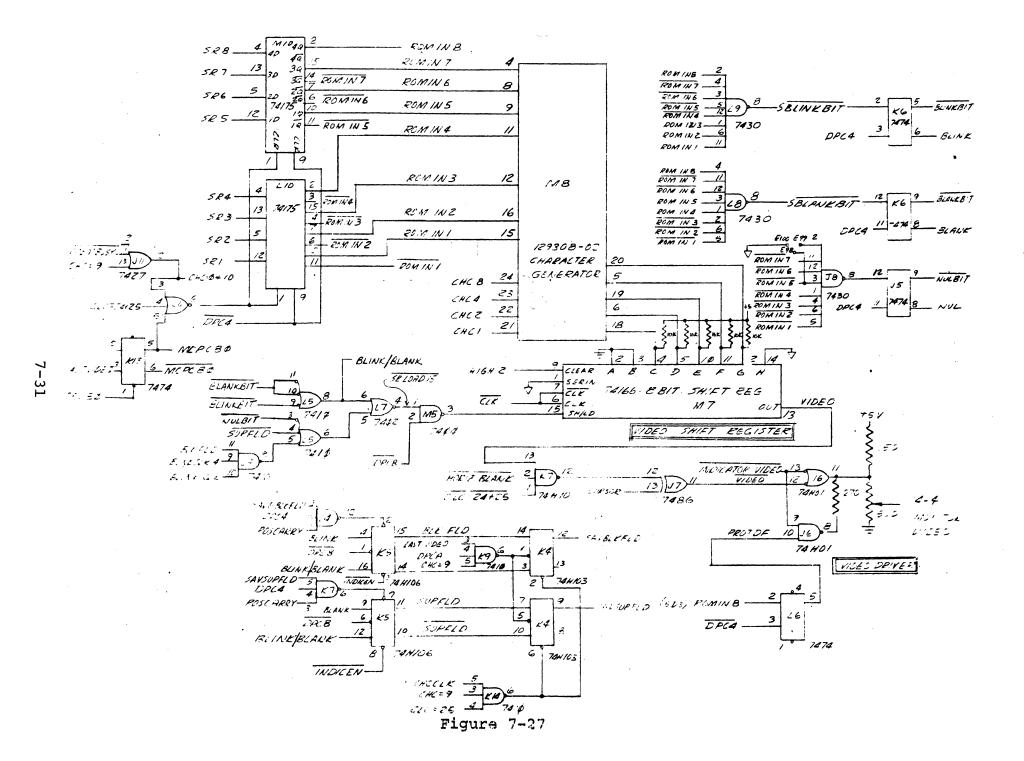

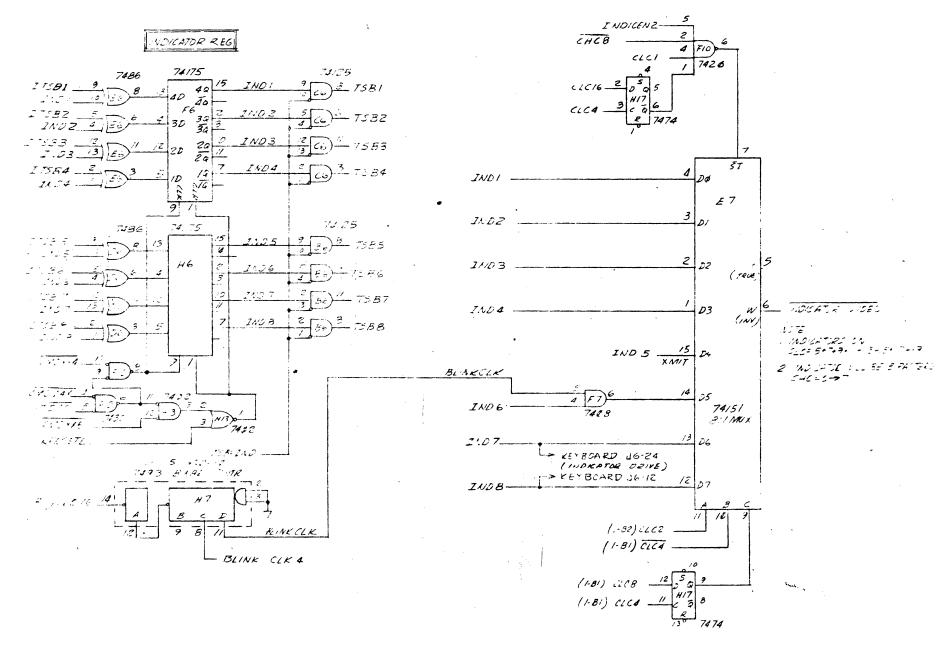

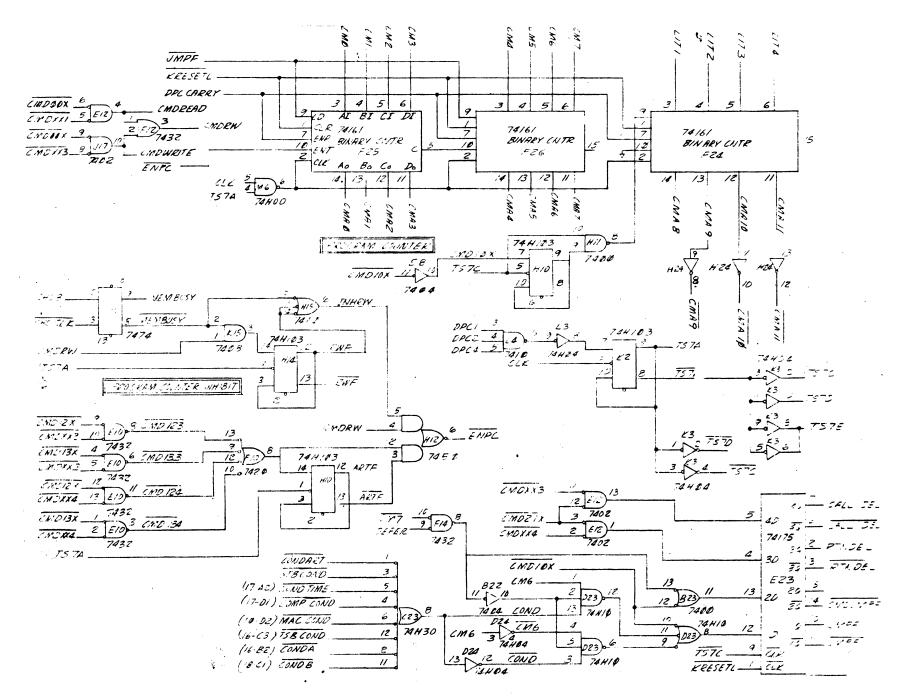

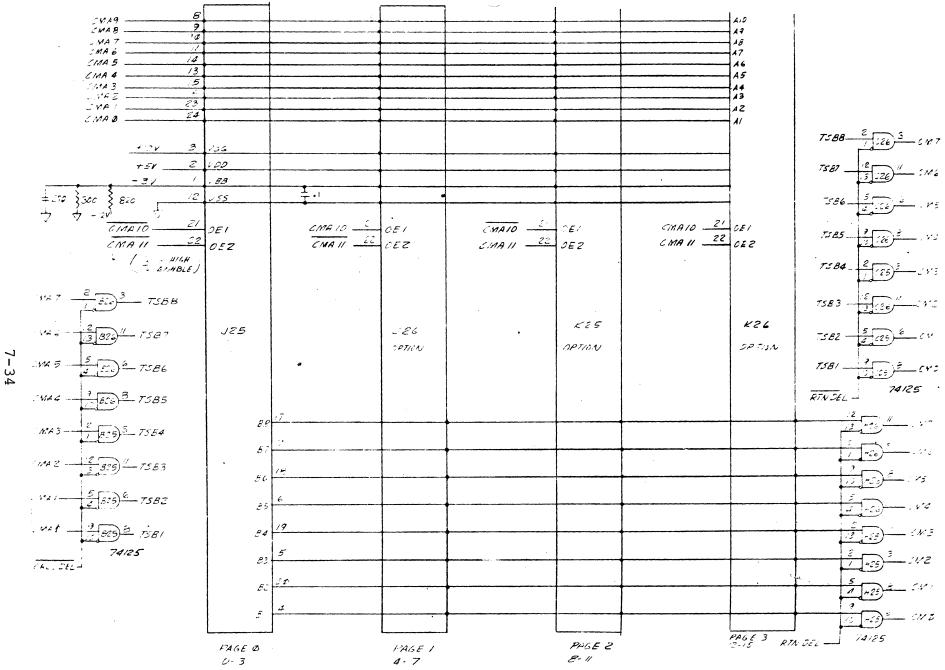

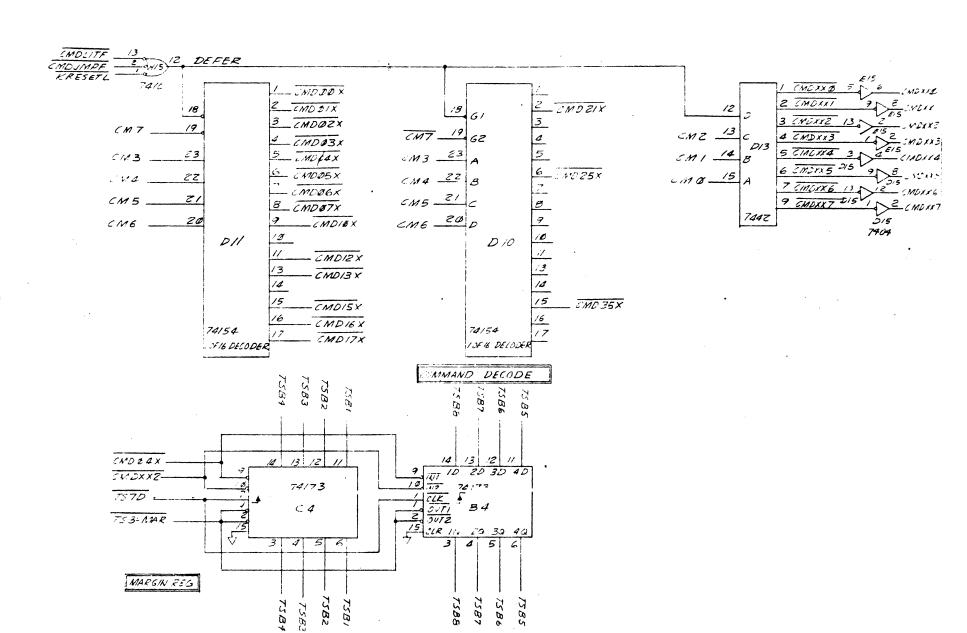

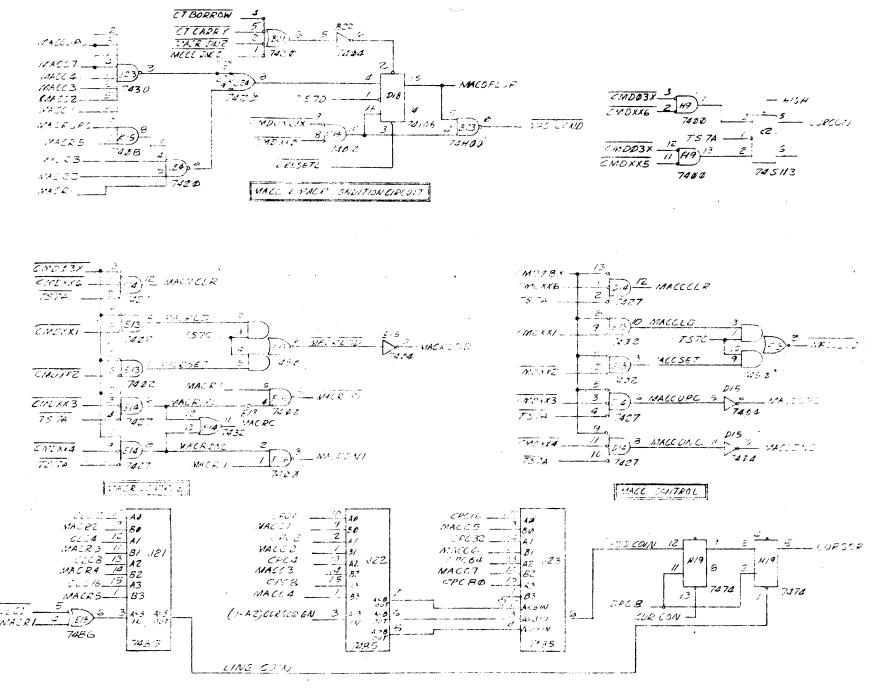

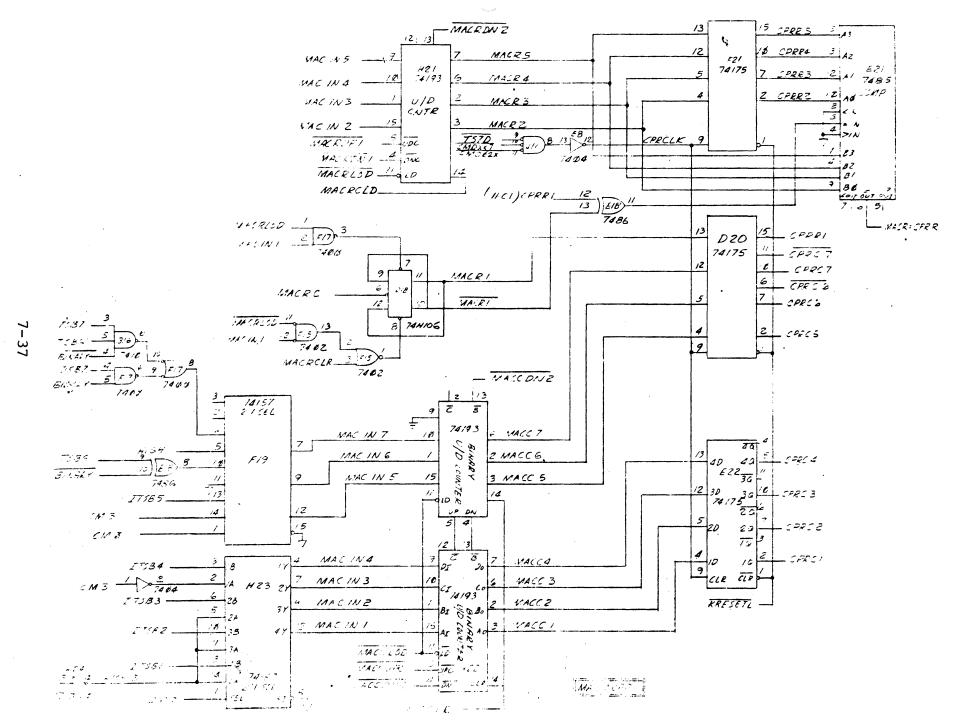

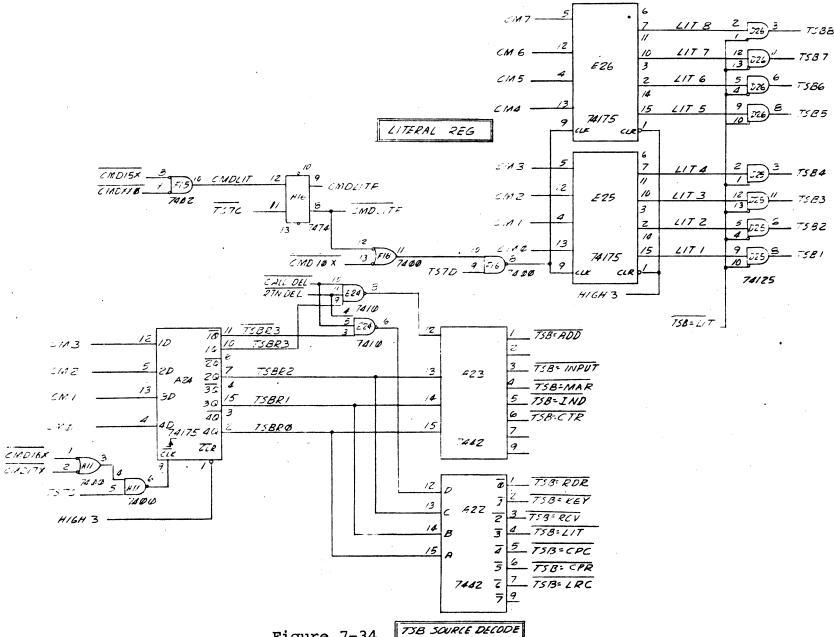

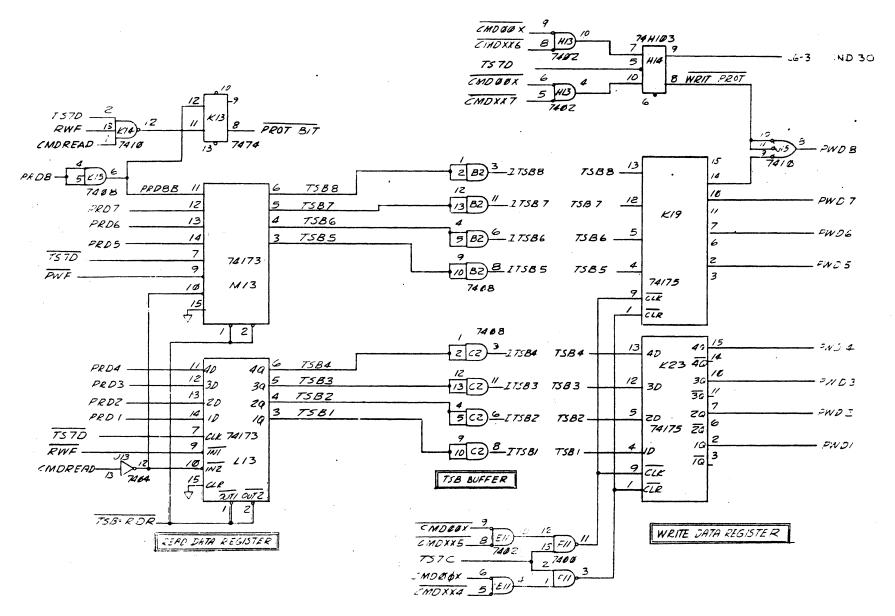

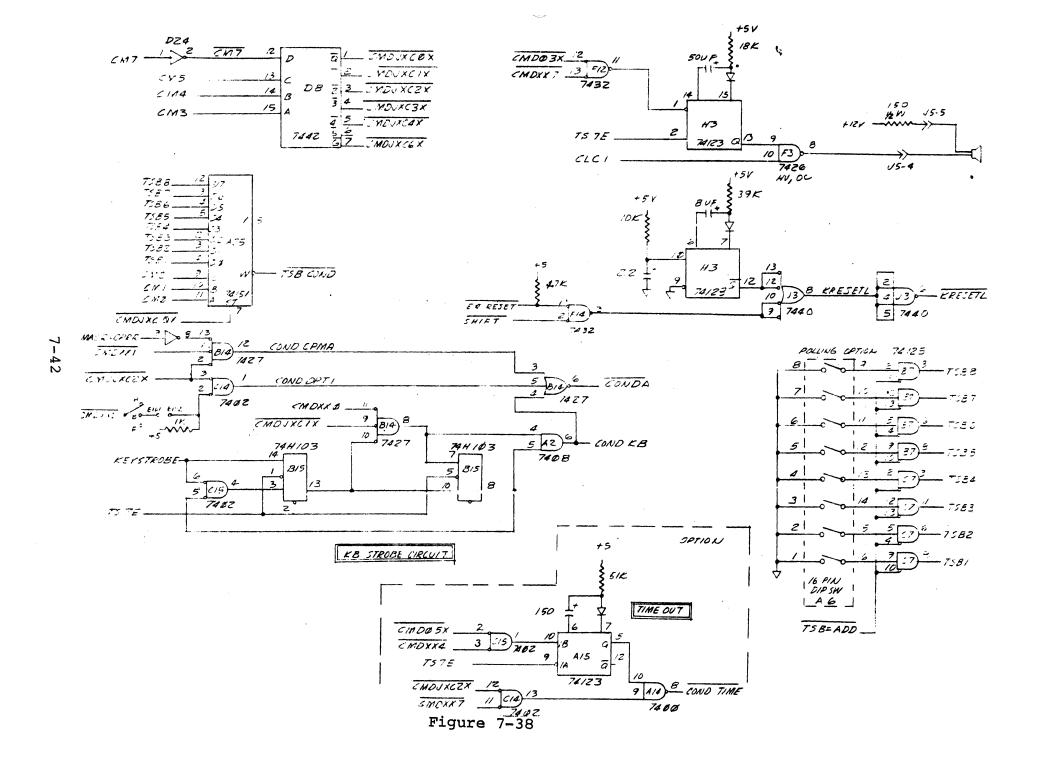

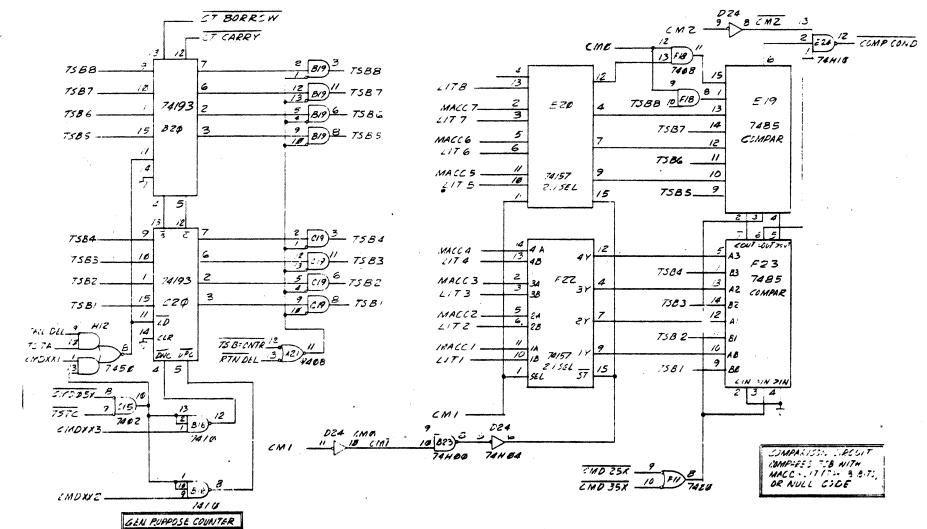

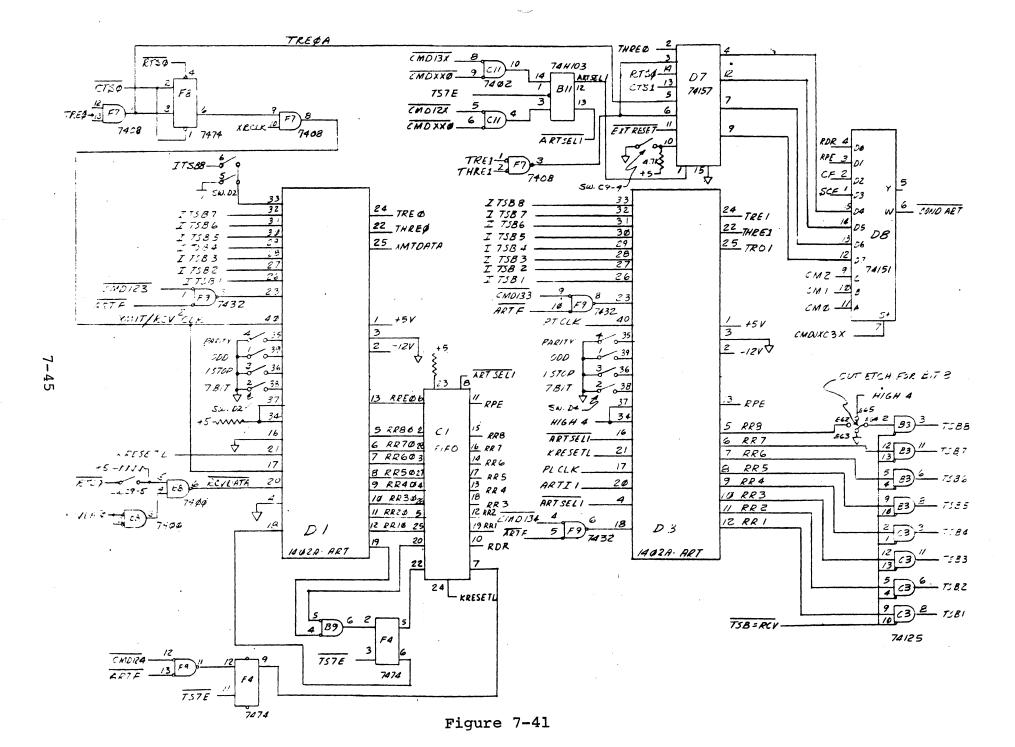

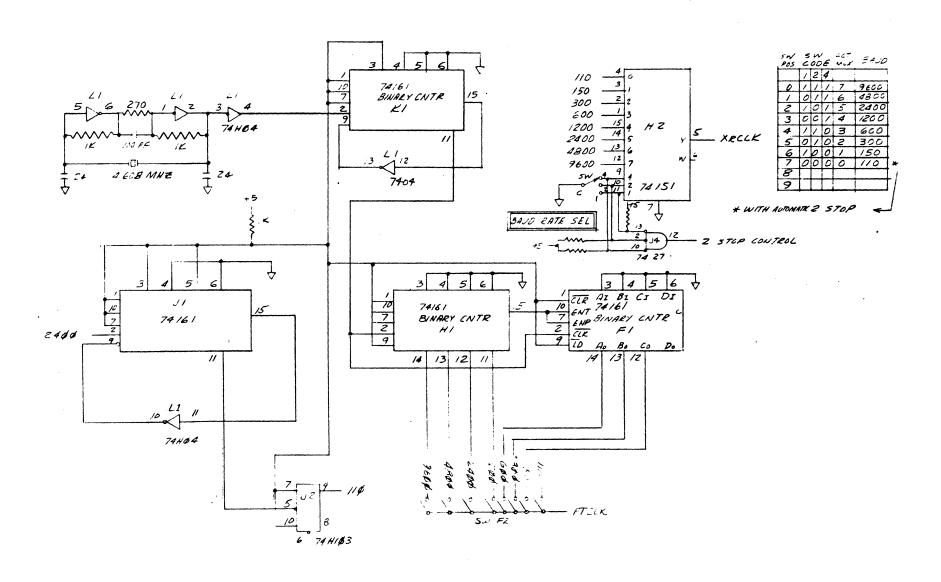

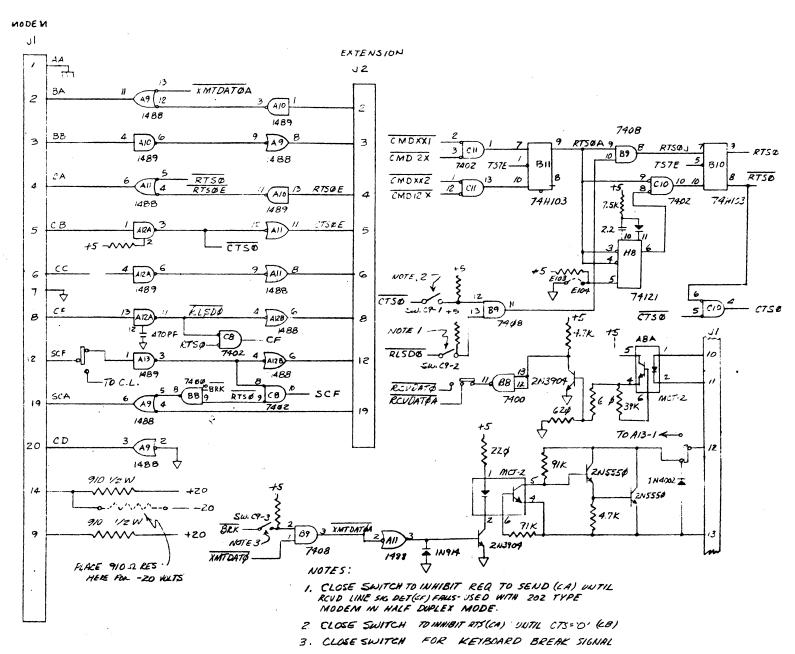

| 7-21         | Schematics -7 Configuration                                    | 7–3          |

| 7-22 t       |                                                                |              |

| 7-44         | Schematics -13 Configuration                                   | 7–27         |

| 7-45 t       |                                                                |              |

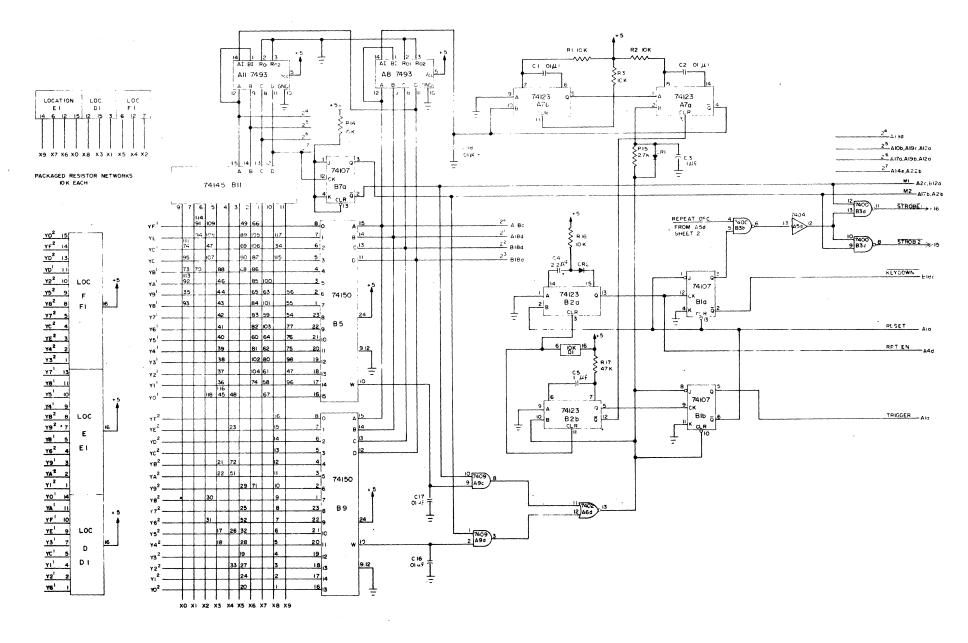

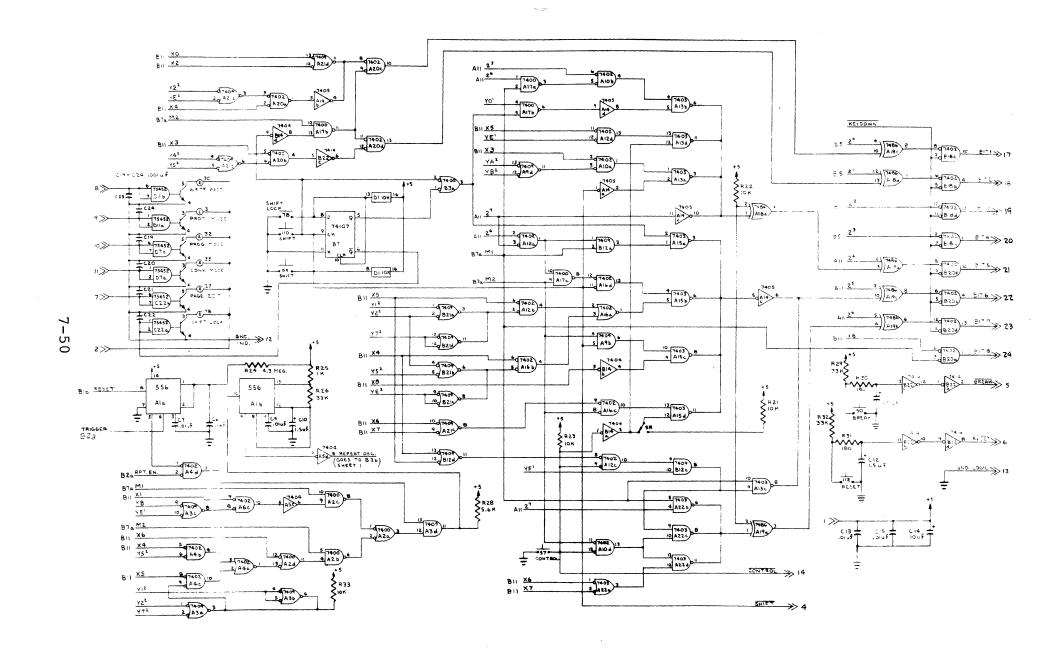

| 7-46         | Keyboard Schematic                                             | 7-49         |

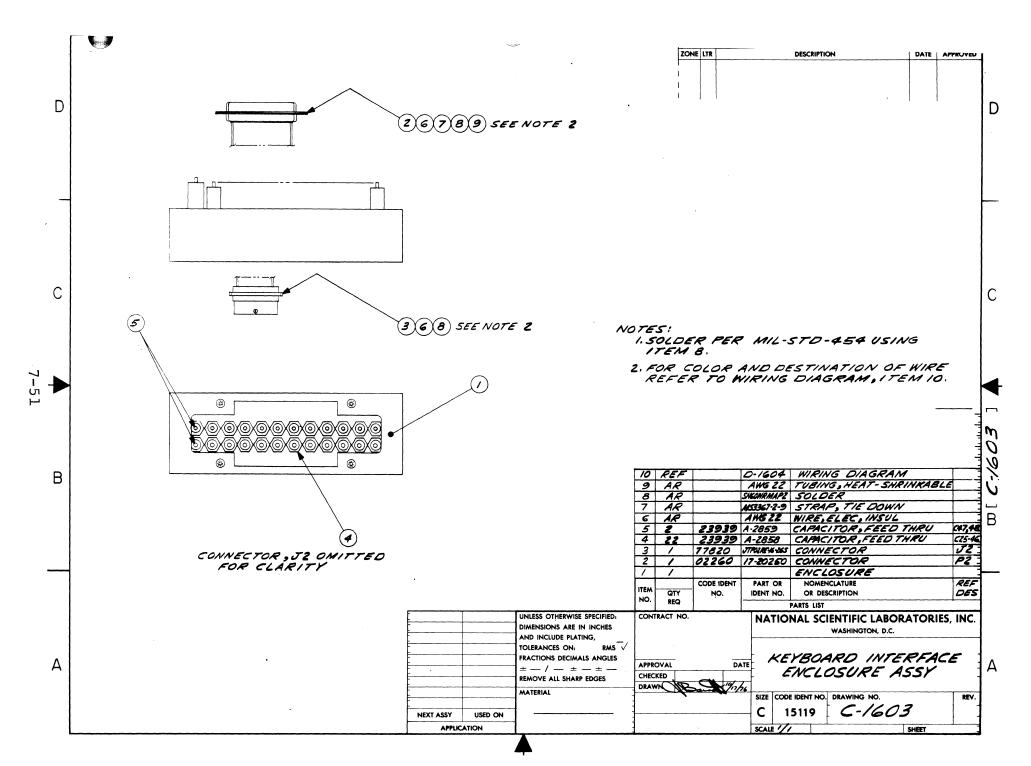

| 7-47         | Keyboard Interface Assembly                                    | 7-51         |

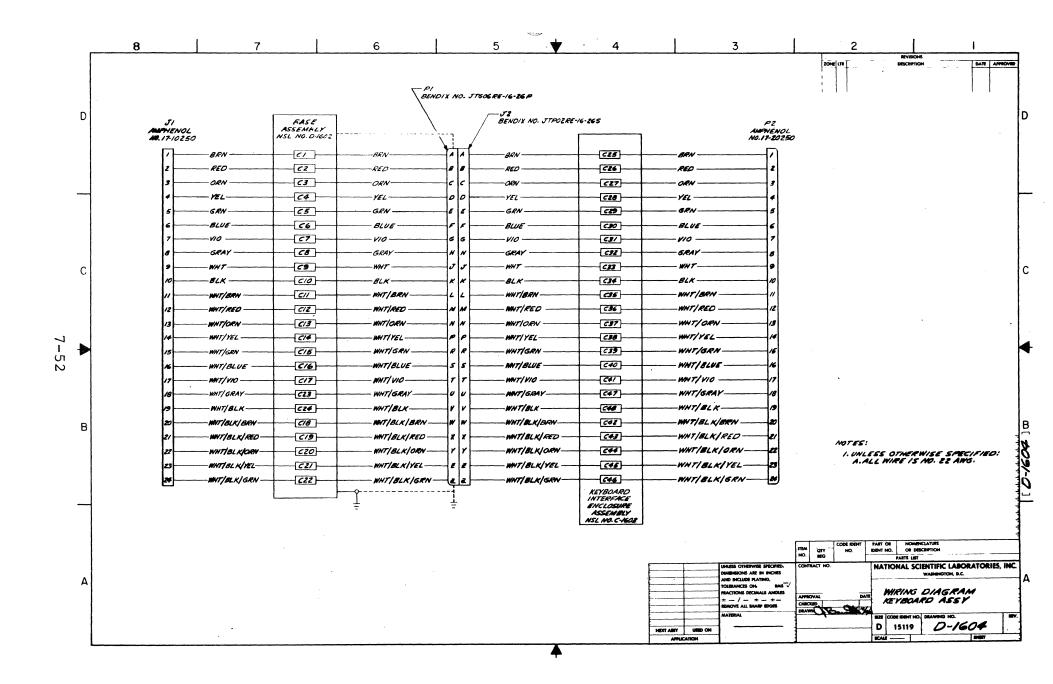

| 7-48         | Wiring Diagram                                                 | 7-52         |

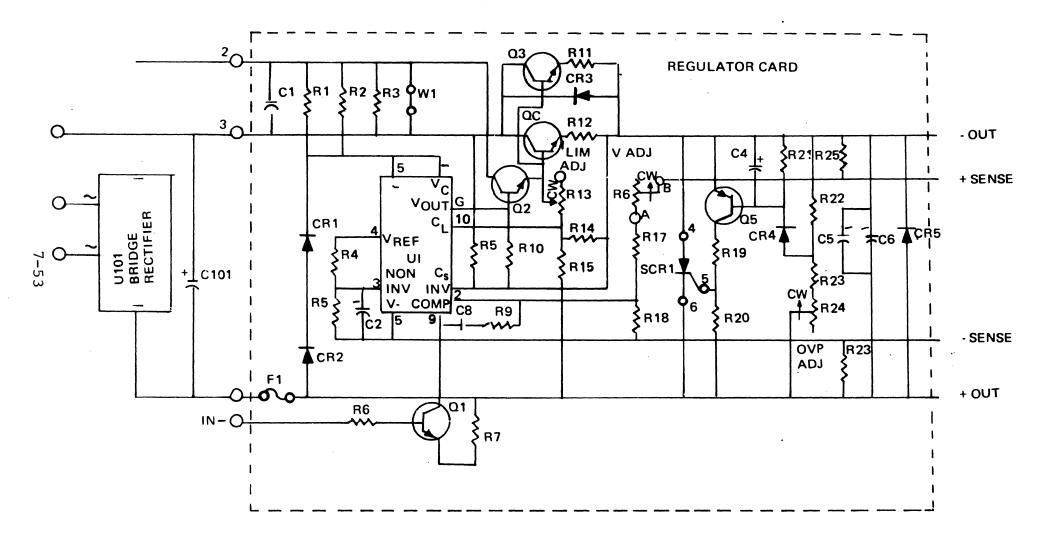

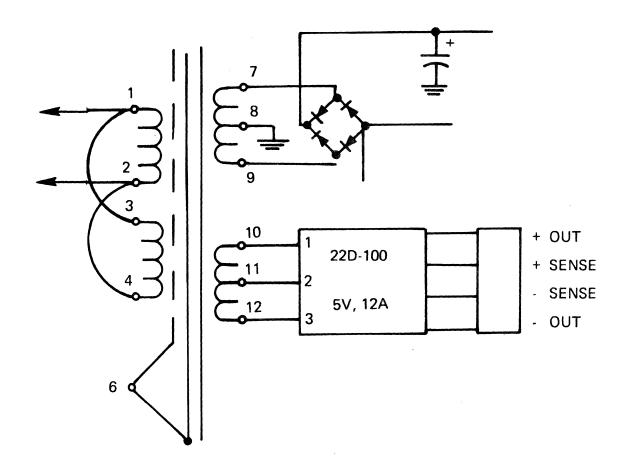

| 7-49         | Logic Power Supply                                             | 7-53         |

| 7-50         | Wiring Pkll12                                                  | 7-54         |

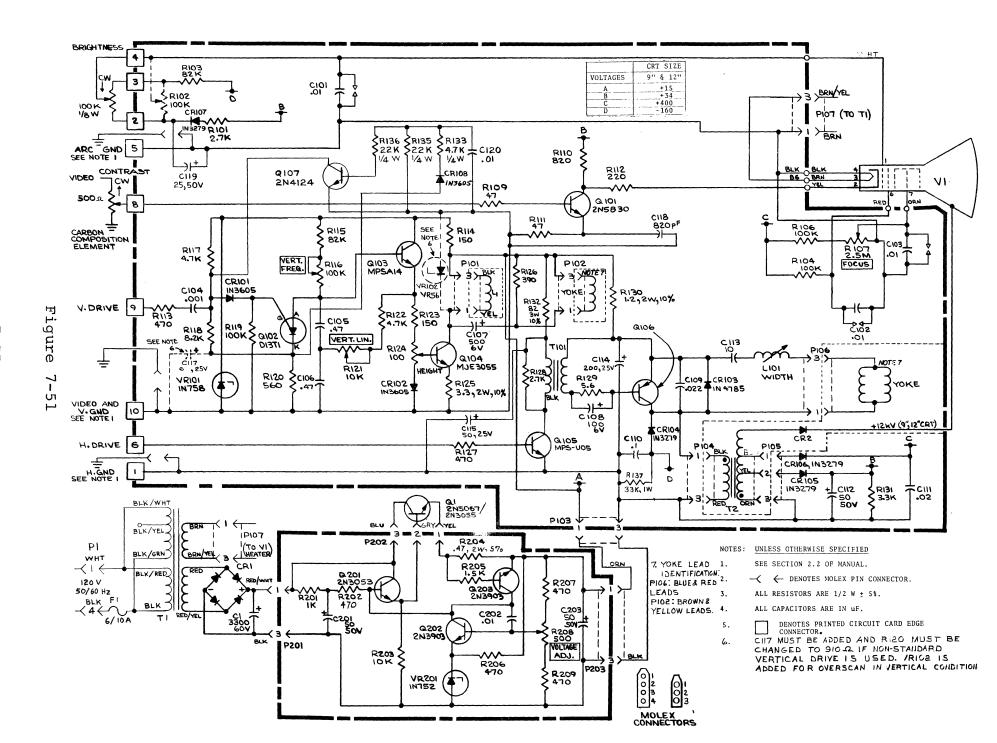

| 7-51         | Video Schematic                                                | 7-55         |

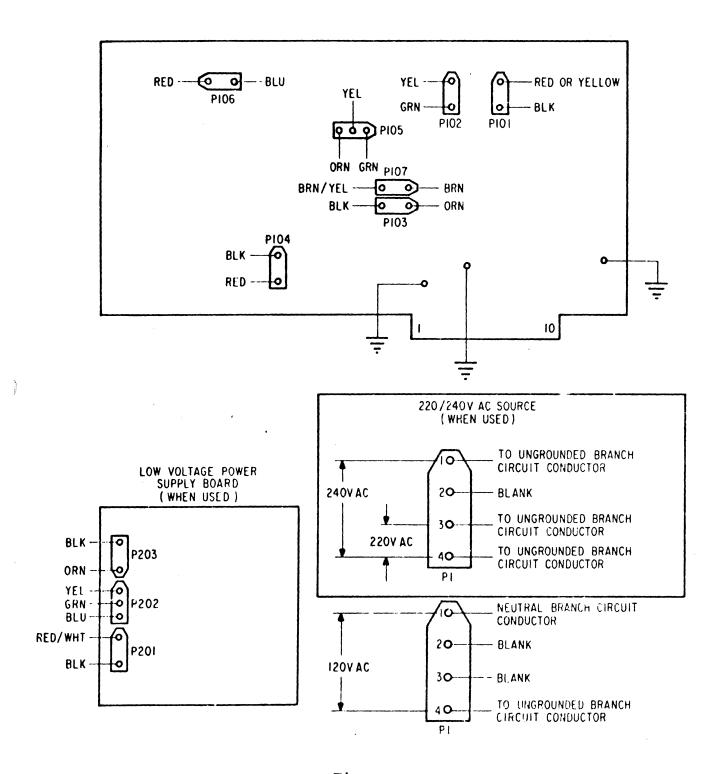

| 7-52         | Video Wiring                                                   | 7-56         |

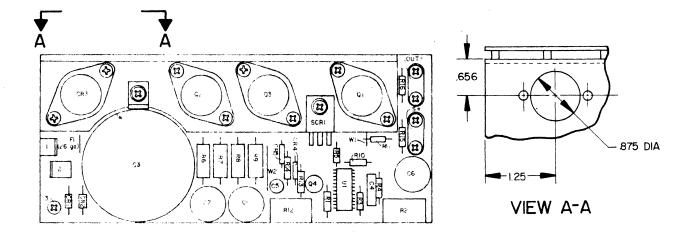

| 7-53         | Power Supply Layout                                            | 7-57         |

#### SECTION I

#### T-5101 Specification

#### INTRODUCTION

The purpose of this manual is to provide operation and maintenance information for the T-5101 Interactive Display Terminal.

The scope of the material provided is sufficient in all aspects of operation and maintenance of the equipment.

The T-5101 consists of cable-interconnected assemblies. This unit is in turn connected to a computer by an additional interface cable.

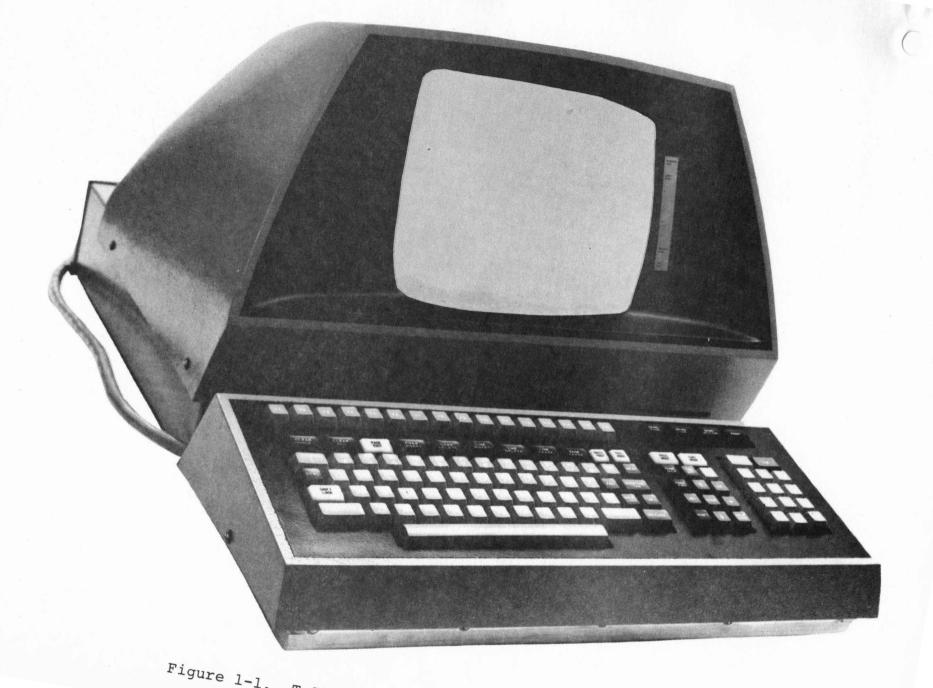

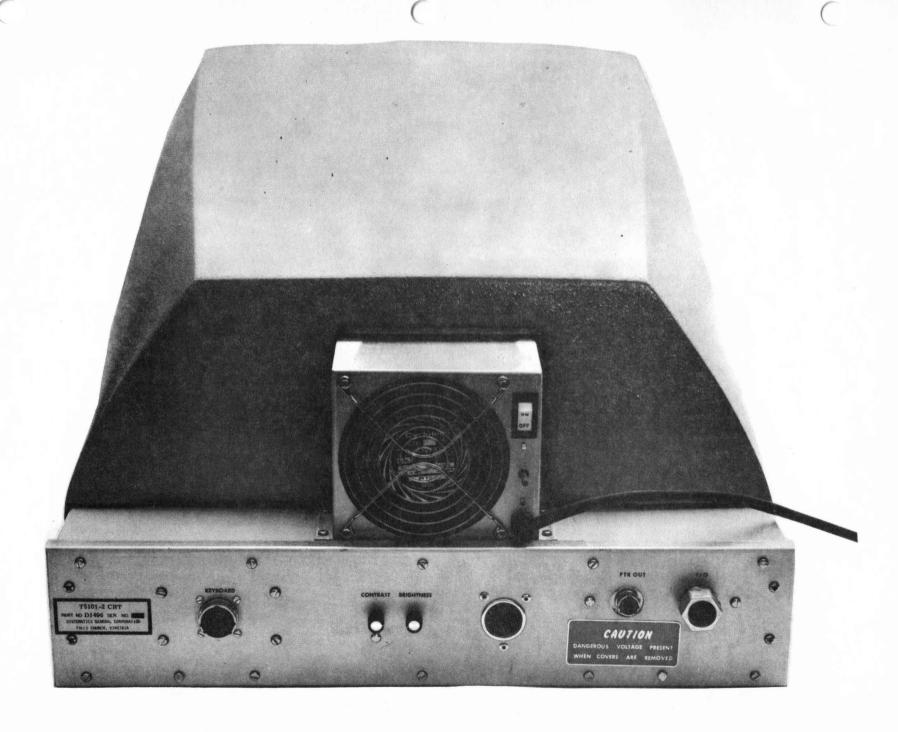

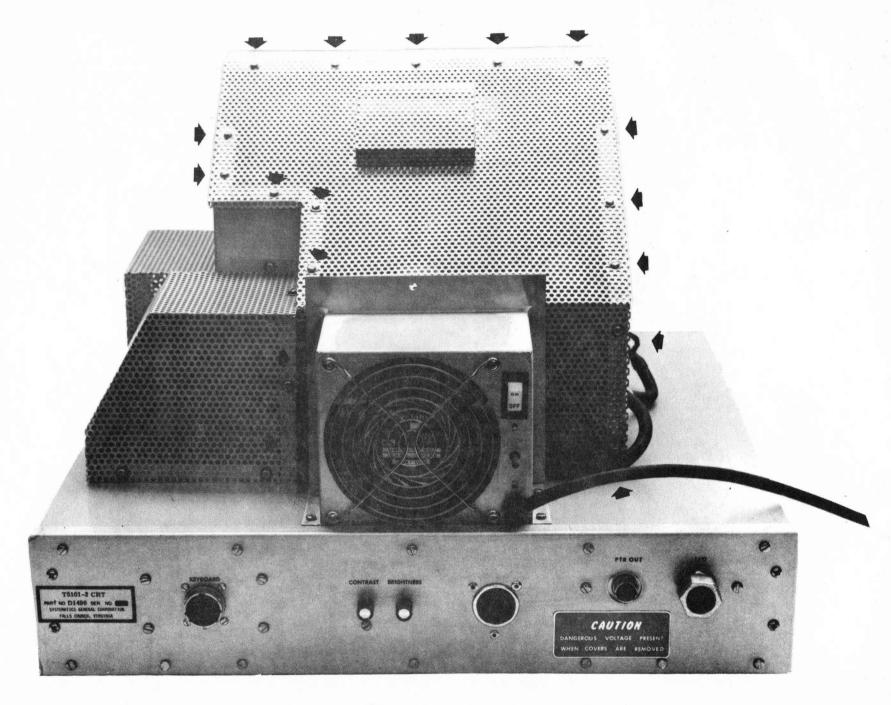

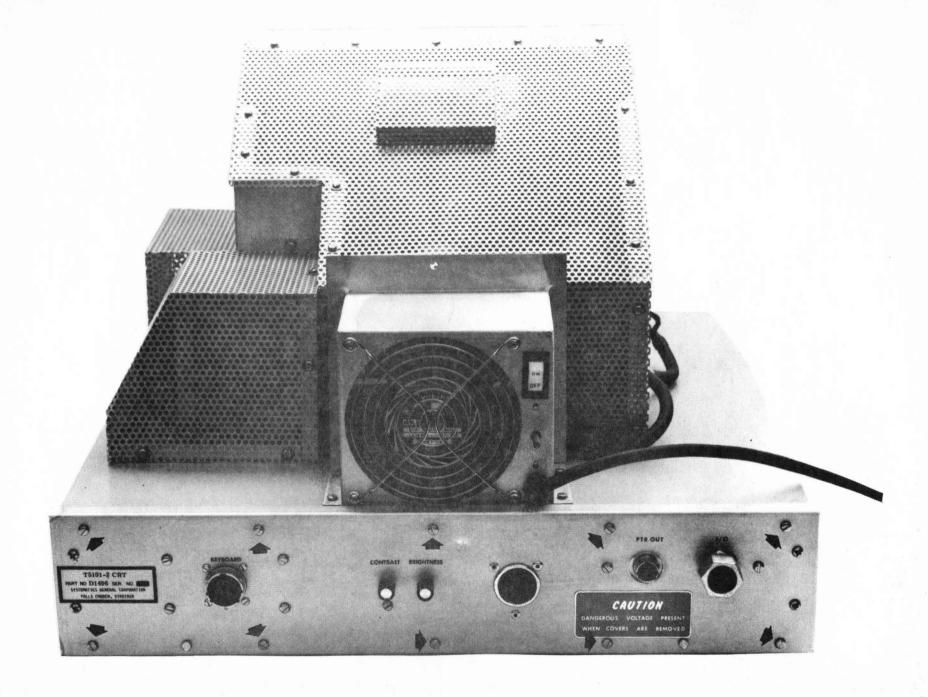

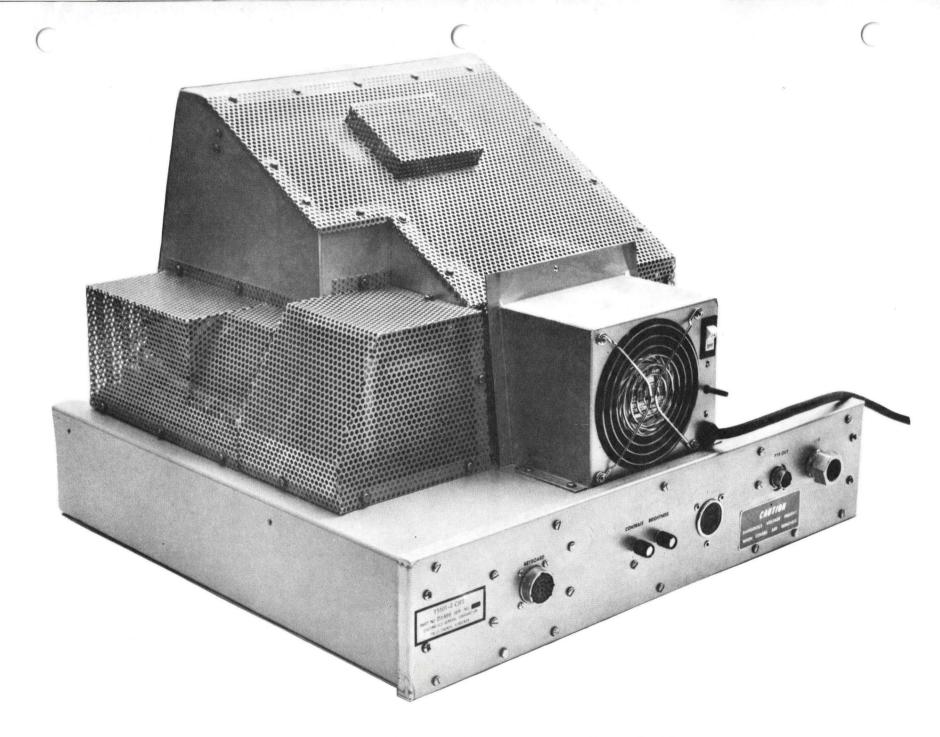

The T-5101 Interface Display Terminal is shown in Figure 1-1.

Figure 1-1. T-5101 Interactive Display Terminal

#### T-5101 SPECIFICATIONS

#### Display

80 Character Lines 24

Character Positions 1920

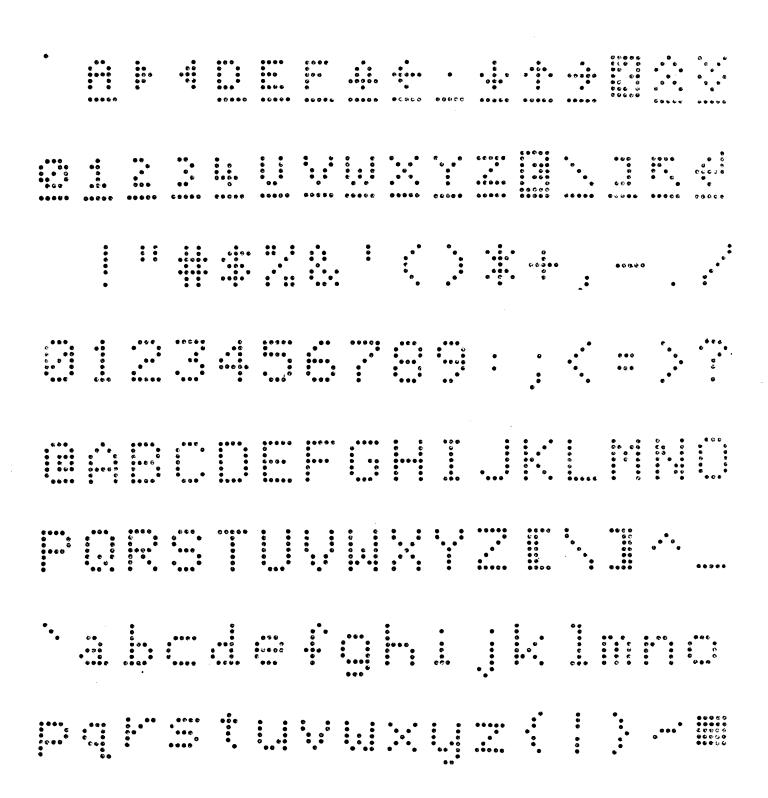

Character Set 96 ASCII (Upper Case)

Screen Phosphor White (P4)

Face Plate Etched

Refresh Rate 60 Pages/Second

Protected Fields Reduced Intensity

Status Displays 8

Control Characters Display 31

Blinking Field Rate 4 per second

Security Fields Display Suppressed

Page Roll Up

#### Cursor

Format Reverse Video Block

Controls Forespace, Backspace

Upline, Downline, New Line, Return, Home, Tab

Backtab, Position Addressing, Position

Reading

#### Data Transmission

Code Asynchronous ASCII

10 unit code

Parity Even

#### Data Transmission

Interface RS-232-C

Rates 110, 150, 300, 600, 1200,

2400, 4800, 9600 Baud

Duplex Full and Half

Modes Conversational

Block

Line, Page or Message (all or foreground)

#### Keyboard

Construction Separate

Character and Control Keys 68

Cursor and Format Keys 14

Numeric Keys Pad 14

Function Keys 16

Transmission Send Control

Keys Page, Line, Message

Interlocking Two Key rollover

Key Operation 2 ounce

Lighted Mode Keys Shift Lock, Write Protect

Program, Conversation,

Page Edit

#### Memory

Storage Capacity 1920 Characters

Security Locations Display Suppressed

Control Character Storage Direct from Keyboard

or Computer

#### Memory

Protected Fields

Character Protect Bit

#### Data Editing

Keyboard Editing

Character

Type over, Insert, Delete

Line

Insert, Delete, Erase to

End of line

Page

Clear all or foreground to Nulls or Spaces, Erase to End of Page (Replace All or Foreground with

Nulls or Spaces)

Protected Fields

Reduced Intensity

Computer Controlled Editing All of Above with Receipt

All of Above with Receipt of ESC Sequences

#### Tempest

Complies With NACSEM 5100, As Modified By AFNAG-9A

#### Physical Characteristics

Dimensions

Display

14.12"H x 20.5"W x 18"L

Keyboard

$4"H \times 20.5"W \times 9"L$

Weight

55 lbs.

A-C Power Requirement

115 Volt, 60 Hz

Environment

$5-50^{\circ}$ C;  $41-122^{\circ}$  F

5-95% Relative Humidity without Condensation

#### SECTION II

#### MICROCONTROLLER PROGRAMMING

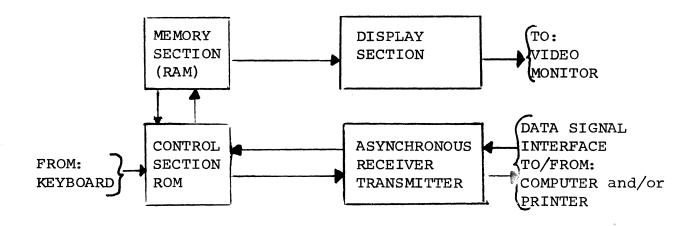

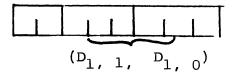

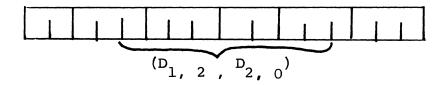

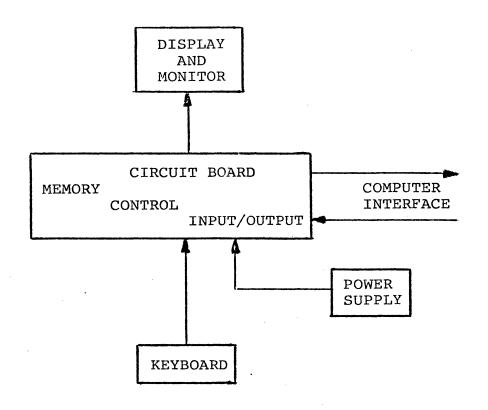

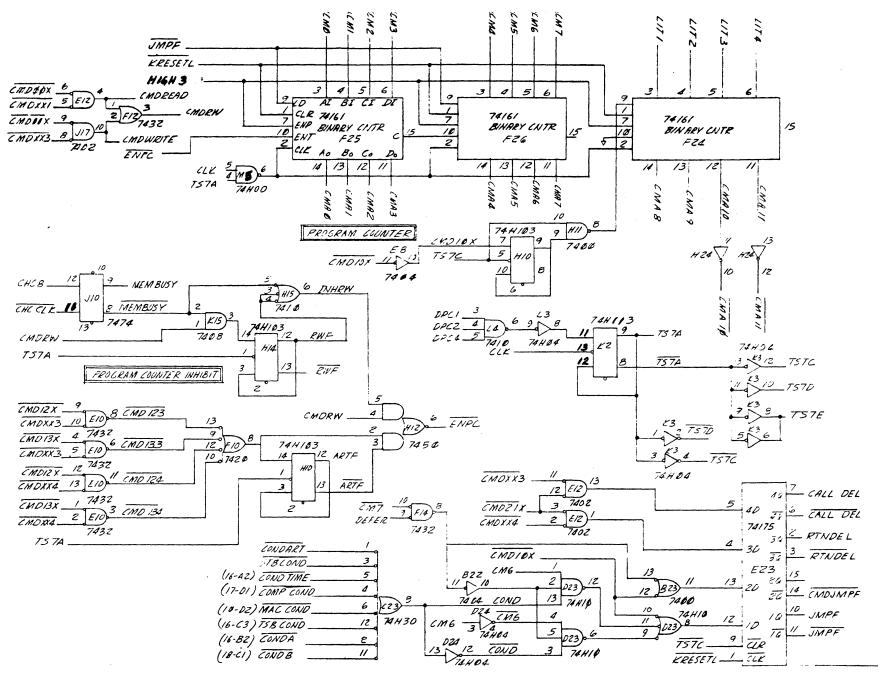

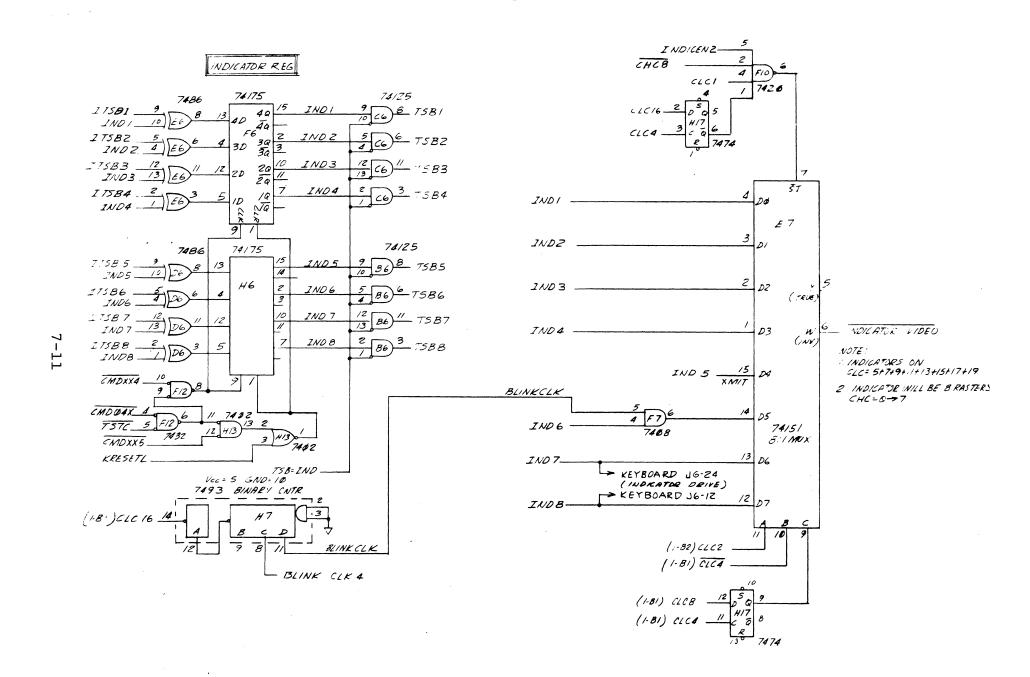

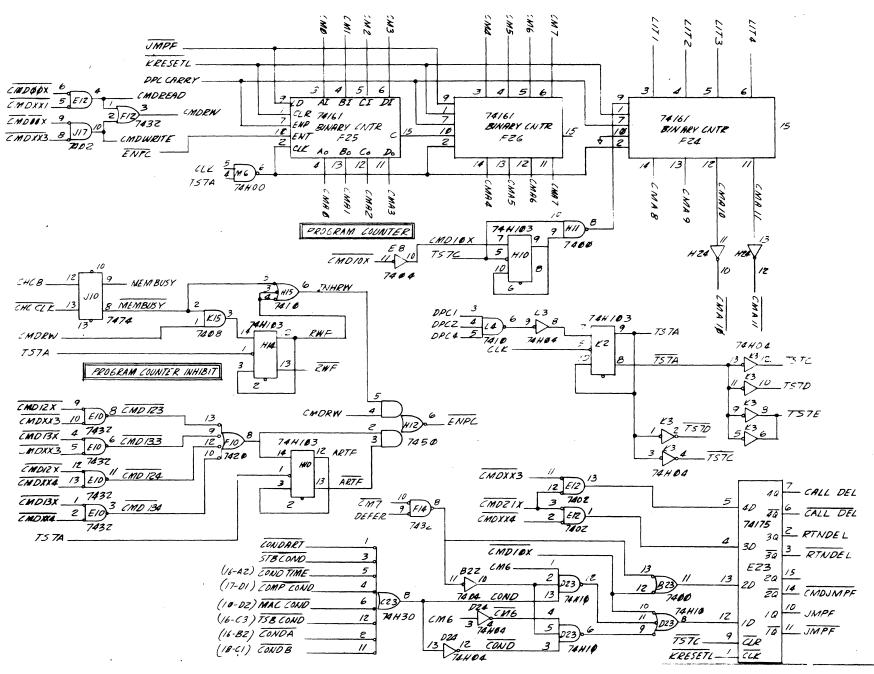

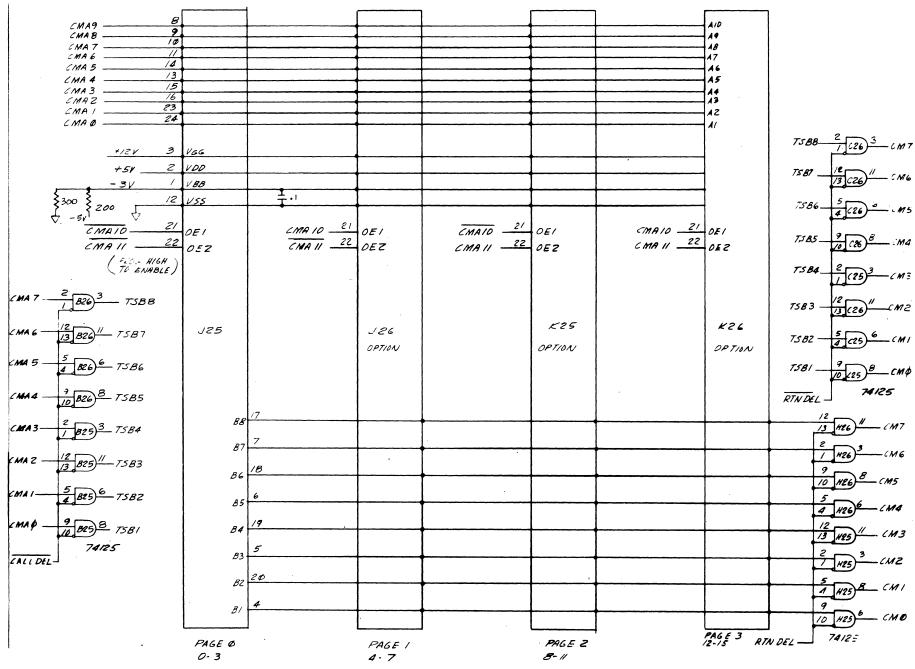

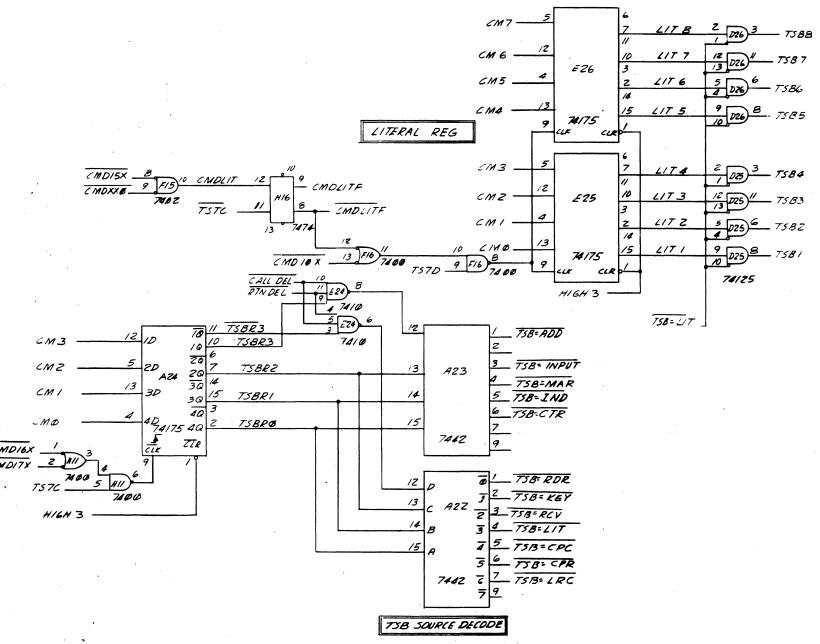

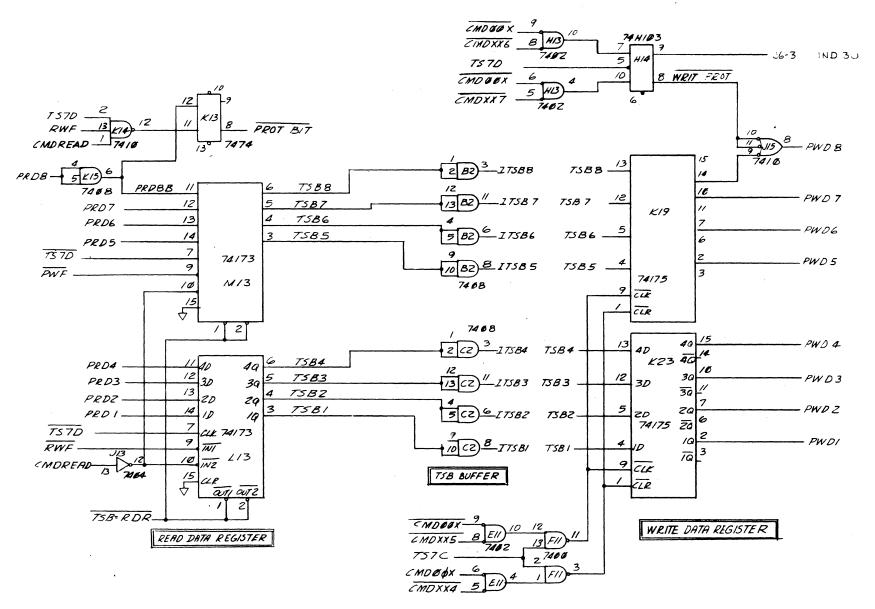

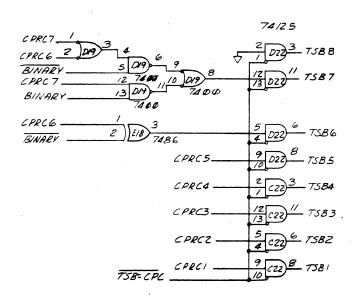

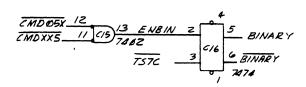

The organization of data transmission and control for the T-5101 interactive data display terminal is given in the data flow block diagram, Figure 2-1 below. A detailed description of control and programming for the microcontroller follows. Specific details of the terminal logic and control devices are contained in schematic drawing 129361, sheets 7-1 through 7-22, contained in Section 7.

Figure 2-1. T-5101 Main Circuit Board

Data Flow Block Diagram

T-5101 Data organization is based on random access memory time sharing between control section and display section, with the display section given highest priority for the refresh function and the control section given secondary priority. The display function utilize random access memory 27% of the time leaving 73% for the control functions. This sharing organization provides the T-5101 with greater reliability of terminal operations since fewer components are required.

Data information and control commands are transferred internally between the various logic sections and components over a tri-state (memory, control, timing) bus.

Keystroke signals enter the main logic board as 8 bit parallel data codes, along with strobe signals. However, data received from an interfacing computer is received as ASCII seven bit serial data. The logic board has a serial-parallel converter to translate serial ASCII codes to parallel codes as well as a FIFO buffer to allow time for operations which are longer than inter character intervals in fast transmission rate environments.

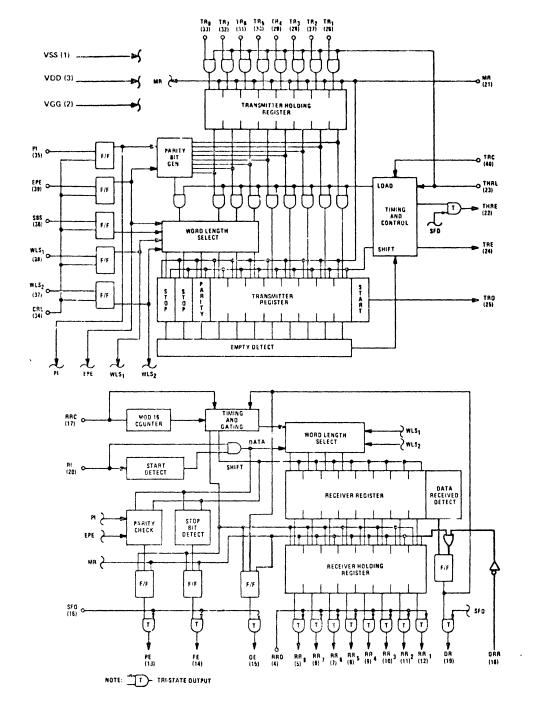

The transmitter/receiver is an LSI/UART chip which (1) accepts serial ASCII 10 or 11 unit codes (word structure option is strappable) from an RS-232-C standard interface or 20 ma current loop optional interface and (2) transmits an equivalent 8 bit parallel code as a data word to the control section. Furthermore, the universal asynchronous transmitter/receiver (UART) also decodes 8 bit words received from the T-5101 control section and transmits serial ASC II over the data signal interface. See Figure 2-2 for additional details of the UART.

Information transfer is controlled in the T-5101 by the microcontrol logic commanded by codes stored in a preprogrammed ROM. The standard T-5101 terminal functions are contained in four pages (256-8 bit words/pages) of microcode, with printer extension option requiring an additional page, and terminal polling option needing two pages.

The display memory section consists of 16 random access memory (RAM) chips, providing storage capacity of 2048 8-bit words. This memory provides useful character storage of 1920 characters, 24 lines of 80 characters each. The memory section also contains conversion logic necessary to monitor display cursor position.

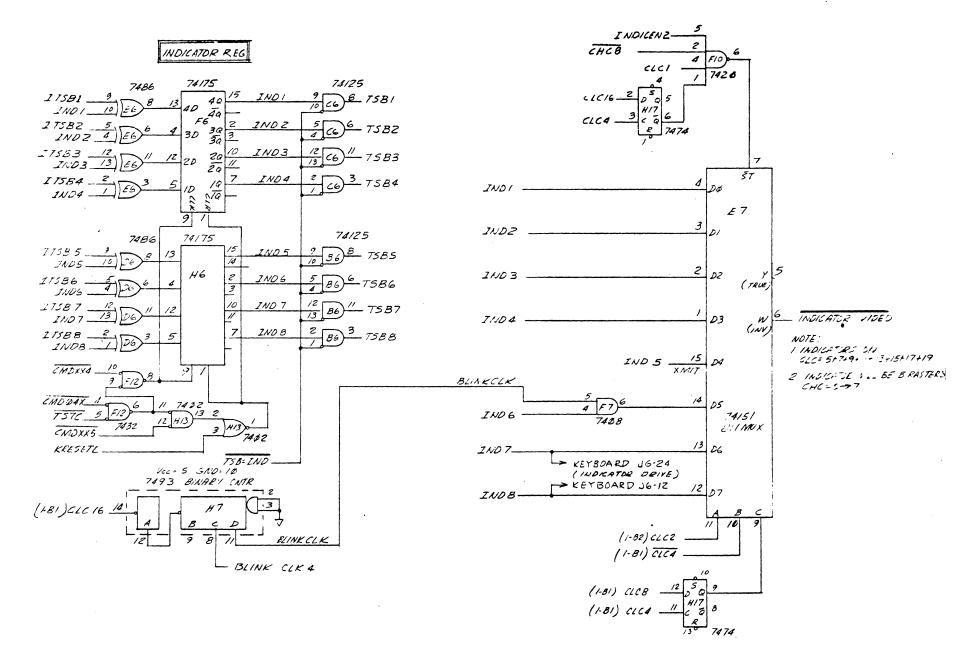

The display section consists of four main subsections, i.e.,

(1) Character Generator, (2) Row Refresh Logic, (3) Cursor Display

Logic, and (4) Timing Control. In addition to the above functions,

display section also provides control for reduced luminance

(protected fields) and 8-status indicator displays.

Actual registers used in the T-5101 micro controller code are summarized and listed in Table 2-2.

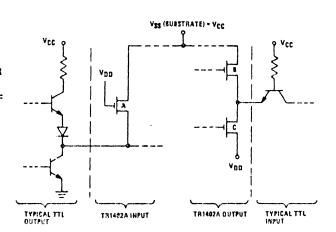

#### INPUT STRUCTURE

MOS DEVICE "A" ACTS AS AN INTERNAL PULL-UP RESISTOR TO  $V_{SS} = V_{CC}$  WHICH BIASES OFF THE CASCODE DEVICE OF THE TTL OUTPUT IN THE HIGH-LEVEL OUTPUT STATE. IN THE LOW-LEVEL OUTPUT STATE THE TTL OUTPUT DEVICE SINKS THE CURRENT SUPPLIED BY DEVICE "A".

#### **OUTPUT STRUCTURE**

DEVICES "B" & "C" COMPRISE A PUSH-PULL OUTPUT BUFFER. IN THE LOW-LEVEL STATE, OUTPUT TRANSISTOR "C" IS "ON" AND CASCODE DEVICE "B" IS OFF. IN THE HIGH-LEVEL STATE, THE OPPOSITE IS TRUE. IN THE DISCON NECTED STATE, BOTH "B" AND "C" ARE TURNED OFF CAUSING THE OUTPUT NODE TO FLOAT.

Figure 2-2. T-5101 Asynchronous Receiver/Transmitter (UART)

| PIN<br><u>NUMBER</u> | NAME                               | SYMBOL                             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | V <sub>SS</sub> POWER SUPPLY       | $v_{ss}$                           | +5 volts Supply                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2                    | V <sub>GG</sub> POWER SUPPLY       | $v_{ m GG}$                        | -12 volts Supply                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3                    | V <sub>DD</sub> POWER SUPPLY       | $v_{DD}$                           | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4                    | RECEIVER<br>REGISTER<br>DISCONNECT | RRD                                | A high-level input voltage.<br>V <sub>IH</sub> applied to this line<br>disconnects the RECEIVER<br>HOLDING REGISTER outputs from<br>the RR <sub>8</sub> -RR <sub>1</sub> data outputs<br>(pins 5-12).                                                                                                                                                                                                                                                     |

| 5-12                 | RECEIVER HOLDING REGISTER DATA     | RR <sub>8</sub><br>RR <sub>1</sub> | The contents of the RECEIVER HOLDING REGISTER appear on these lines in parallel if a low-level input voltage, V <sub>IL</sub> , is applied to RRD. Program control selection of a word length less than eight (8) bits will cause the most significant bits of the character to be forced to a low-level output voltage, V <sub>OL</sub> . The character will be right justified. RR <sub>1</sub> (pin 12) is the least significant bit of the character. |

| 13                   | PARITY ERROR                       | PE                                 | The status of the parity verification circuit appears on this line, if a low-level input voltage, V <sub>IL</sub> , is applied to the STATUS FLAGS DISCONNECT (pin 16) control line. Wired OR capability is provided on this line allowing PE lines from other arrays to be OR tied. A high level output voltage, V <sub>OH</sub> , on this line (under the conditions above)                                                                             |

Figure 2-2. T-5101 Asynchronous Receiver/Transmitter (UART) (Continued)

| PIN<br>NUMBER | NAME             | SYMBOL | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                  |        | indicates a PARITY ERROR in the received parity bit as programmed by the EVEN PARITY ENABLE control line (pin 39). The status is updated each time a character is transferred from the RECEIVER REGISTER to the RECEIVER HOLDING REGISTER.                                                                                                                                                                                                                                                   |

| 14            | FRAMING<br>ERROR | FE     | The status of the STOP bit detection circuit appears on this line if a low-level input voltage, V <sub>IL</sub> , is applied to the STATUS FLAG DISCONNECT (pin 16) control line. Wired OR capability is provided on this line allowing FE lines from other arrays to be OR tied. A high-level output voltage, V <sub>OH</sub> , indicates that the received character has no valid STOP bit, i.e., the bit following the parity bit is not a high-level input voltage, V <sub>IH</sub> .    |

| 15            | OVERRUN<br>ERROR | OE     | The status of the DATA RECEIVED circuit appears on this line of a low-level input voltage, V <sub>IL</sub> , is applied to the STATUS FLAG DISCONNECT (pin 16) control line. Wired OR capability is provided on this line allowing OE lines from other arrays to be OR-tied. A high level output voltage, V <sub>OH</sub> , indicates that the previously received character was not read (DR line not reset) before the present character was transferred to the RECEIVER HOLDING REGISTER. |

Figure 2-2. T-5101 Asynchronous Receiver/Transmitter (UART) (Continued)

| PIN<br>NUMBER | <u>NAME</u>                        | SYMBOL | _FUNCTION                                                                                                                                                                                                                                                |

|---------------|------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16            | STATUS FLAGS<br>DISCONNECT         | SFD    | A high-level input voltage, V <sub>IH</sub> , applied to this pin disconnects the PE, FE, OE, DR and THRE circuit outputs.                                                                                                                               |

| 17            | RECEIVER REGIS-<br>TER CLOCK       | RRC    | This clock is sixteen (16) times faster than the desired receiver shift rate.                                                                                                                                                                            |

| 18            | DATA RECEIVED<br>RESET             | DRR    | A low-level input voltage, $V_{\rm IL}$ , applied to this line resets the DR line.                                                                                                                                                                       |

| 19            | DATA RECEIVED                      | DR     | A high level output voltage, V <sub>OH</sub> , indicates that an entire character has been received and transferred to the RECEIVER HOLDING REGISTER.                                                                                                    |

| 20            | RECEIVER INPUT                     | RI     | Serial input data received on this line enters the RECEIVER REGISTER at a point determined by the character length, parity, and the number of stop bits.  A high-level input voltage, V <sub>IH</sub> , must be present when data is not being received. |

| 21            | MASTER RESET                       | MR     | This line is strobed to a high-level input voltage, V <sub>IH</sub> , to clear the logic after power turn-on. It resets all registers and sets the serial output line to a high-level output voltage, V <sub>OH</sub> .                                  |

| 22            | TRANSMITTER HOLDING REGISTER EMPTY | THRE   | A high-level output Voltage, V <sub>OH</sub> , on this line indicates the TRANSMITTER HOLDING REGISTER has transferred its contents to the TRANSMITTER REGISTER and may be loaded with a new character.                                                  |

Figure 2-2. T-5101 Asynchronous Receiver/Transmitter (UART) (Continued)

| PIN<br>NUMBER | NAME                              | SYMBOL | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|-----------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23            | TRANSMITTER HOLDING REGISTER LOAD | THRL   | A low-level input voltage, $V_{\rm IL}$ , applied to this line enters a character into the TRANSMITTER HOLDING REGISTER. A transition from a low-level input voltage. $V_{\rm IL}$ , to a high level input voltage. $V_{\rm IH}$ , transfers the character into the TRANSMITTER REGISTER if it is not in the process of transmitting a character. If a character is being transmitted, the transfer is delayed until its transmission is completed. Upon completion, the new character is transferred simultaneously with the initiation of the serial transmission of the new character. |

| 24            | TRANSMITTER REGISTER EMPTY        | TRE    | A high-level output voltage. V <sub>OH</sub> . on this line indicates that the TRANSMITTER REGISTER has completed serial transmission of a full character including STOP bit(s). It remains at this level until the start of transmission of the next character.                                                                                                                                                                                                                                                                                                                          |

| 25            | TRANSMITTER REGISTER OUTPUT       | TRO    | The contents of the TRANSMITTER REGISTER (START bit DATA bits, PARITY bit, and STOP bit), are serially shifted out on this line. This line will remain at a high level output voltage, V <sub>OH</sub> , when no data is being transmitted. A start of transmission is defined as the transition from a high-level output voltage, V <sub>OL</sub> , of the start bit.                                                                                                                                                                                                                    |

Figure 2-2. T-5101 Asynchronous Receiver/Transmitter (UART) (Continued)

| PIN<br>NUMBER | NAME                             | SYMBOL                               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|----------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26-33         | TRANSMITTER REGISTER DATA INPUTS | TR <sub>1</sub> -<br>TR <sub>8</sub> | Parallel 8-bit characters are input on these lines into the TRANSMITTER HOLDING REGISTER with THRL Strobe. If a character of less than 8 bits has been selected (by WLS1 and WLS2), the least significant bits only are accepted. The character is right justified into the least significant bit. A high-level input voltage, VIH, will cause a high-level output voltage, VOH, to be transmitted.                                                                                     |

| 34            | CONTROL<br>REGISTER<br>LOAD      | CRL                                  | A high-level input voltage, V <sub>IH</sub> , on the line loads the CONTROL REGISTER with the control bits (WLS <sub>1</sub> , WLS <sub>2</sub> , EPE, PI, SBS). This line may be strobed or hard wired to a high-level input voltage, V <sub>IH</sub> .                                                                                                                                                                                                                                |

| 35            | PARITY<br>INHIBIT                | PI                                   | A high-level input voltage, V <sub>IH</sub> , on this line inhibits the parity generation and verification circuits. The STOP bit(s) will immediately follow the last data bit on transmission if parity is uninhibited. A low-level input voltage, V <sub>IL</sub> , enables the parity generation and verification circuits. PI will, when a high-level input voltage, V <sub>IH</sub> , is applied, also clamp the PE line (pin 13) to a low-level output voltage, V <sub>OL</sub> . |

| 36            | STOP BIT(S) SELECT               | SBS                                  | This line selects the number of STOP bits generated after the PARITY bit during transmission. A high-level input voltage, V <sub>IH</sub> , on this line selects two STOP bits, and a low-level input voltage, V <sub>IL</sub> , selects a single STOP bit.                                                                                                                                                                                                                             |

Figure 2-2. T-5101 Asynchronous Receiver/Transmitter (UART) (Continued)

| PIN<br><u>NUMBER</u> | <u>NAME</u>                   | SYMBOL                                  |                                                   | FUNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FION                                                                                                              |

|----------------------|-------------------------------|-----------------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 37-38                | WORD<br>LENGTH<br>SELECT      | $\substack{\text{WLS}_2\\\text{WLS}_1}$ | charac                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | es select the gth to be 5, 6,                                                                                     |

|                      |                               |                                         | WLS <sub>2</sub>                                  | WLS <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | WORD LENGTH                                                                                                       |

|                      |                               |                                         | $\mathtt{A}^{\mathtt{I} \mathtt{\Gamma}}$         | $\mathtt{v}_\mathtt{IL}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5 bits                                                                                                            |

|                      |                               |                                         | $v_{\mathtt{IL}}$                                 | $v_{\mathtt{IH}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6 bits                                                                                                            |

|                      |                               |                                         | $v_{\mathtt{IH}}$                                 | $v_{\mathtt{IL}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7 bits                                                                                                            |

|                      |                               |                                         | $v_{\mathtt{IH}}$                                 | $v_{\mathtt{IH}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8 bits                                                                                                            |

| 39                   | EVEN<br>PARITY<br>ENABLE      | EPE                                     | or odd<br>the tra<br>the re-<br>voltage<br>PARITY | PARITY ansmitted ceiver.  e, V <sub>IH</sub> , and a defect the contract of the contract | ects either even to be generated by er and checked by A high-level input selects even low-level input selects odd |

| 40                   | TRANSMITTER<br>REGISTER CLOCK | TRC                                     | faster                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | sixteen (16) times<br>ne desired trans-<br>rate.                                                                  |

Figure 2-2. T-5101 Asynchronous Receiver/Transmitter (UART) (Continued)

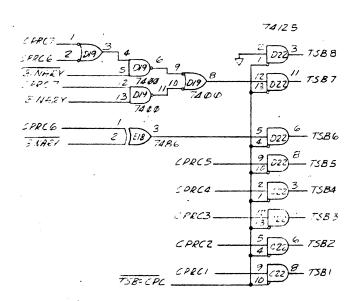

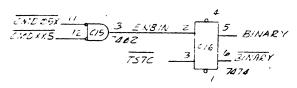

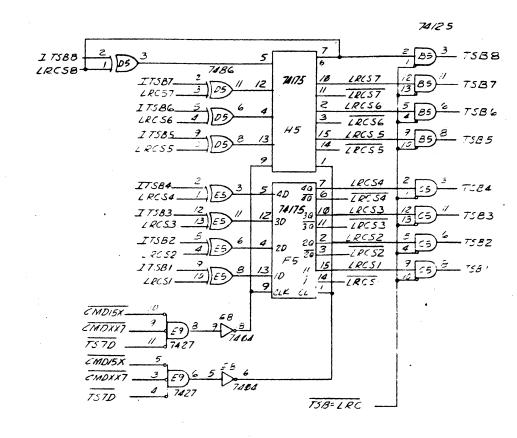

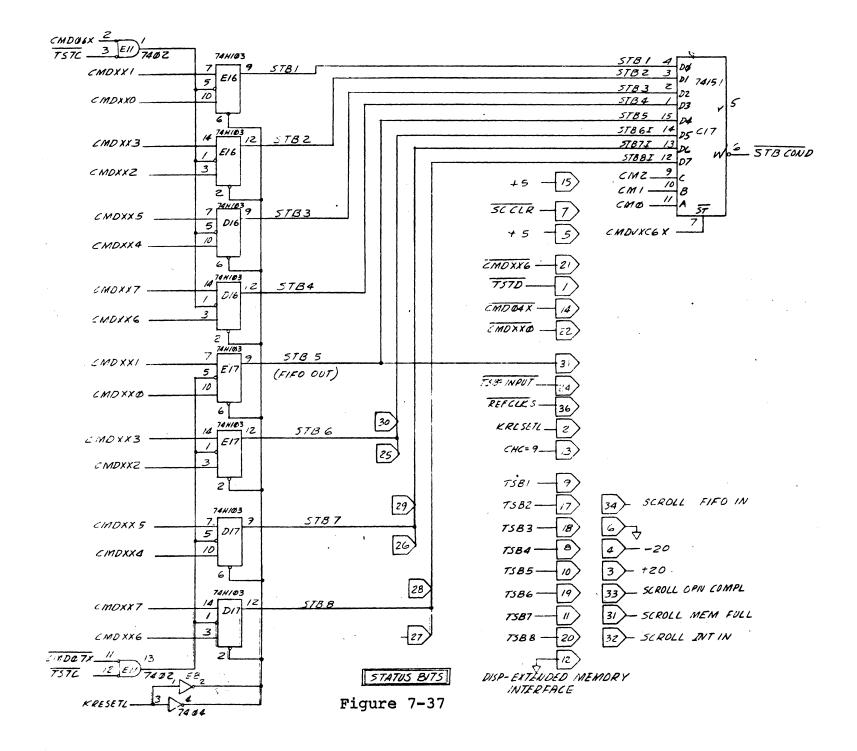

Information is transferred between functional units by way of the tristate bus, TSB, under microprogram control. This information transfer consists of eight-bit characters transmitted in parallel between the following units.

TABLE 2-1. T-5101 FUNCTIONAL UNITS

| Unit     |         |                                                                               |

|----------|---------|-------------------------------------------------------------------------------|

| Mnemonic |         | Unit                                                                          |

| RCV      | From    | External Serial Source via UART Receiver                                      |

| KEY      | From    | Keyboard                                                                      |

| CPR      | From    | Cursor position row register                                                  |

| CPC      | From    | Cursor position character register                                            |

| LIT      | From/To | Eight bit literal register                                                    |

| RDR      | From    | Random access page buffer via the Read<br>Data Register                       |

| WDR      | ТО      | Random access page buffer via the Write<br>Data Register                      |

| LRC      | From/To | Modulo 2 adder and accumulator (7 bits)                                       |

| ADD      | From    | Switch (8 bits) internal, manually set                                        |

| MACR     | From/To | Random access page buffer row counter (address register high order five bits) |

| INPUT    |         | Utility Register*                                                             |

| OUTPUT   |         | Utility Register*                                                             |

| CMD      |         | Utility Register*                                                             |

| MAR      | From/To | Margin Register                                                               |

| IND      | From/To | Indicator Register                                                            |

| CNTR     | From/To | Counter Register                                                              |

<sup>\*</sup> Unused in Standard T-5101

TABLE 2-2. TABLE OF REGISTER USAGE

| Register<br>Symbol | Register<br>Name                             | Description                                                                                             |

|--------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------|

| WDR                | Write Data Register                          | Eight bit character register contains characters to be written into the R.A.M. from tri state bus.      |

| RDR                | Read Data Register                           | Eight Bit register to con-<br>tain characters read from<br>the R.A.M. for transfer to<br>tri state bus. |

| MACC               | Memory Address Counter<br>Character          | Contains low order 7 bits of the R.A.M. address accessible to the tri state bus (column).               |

| MACR               | Memory Address Counter<br>Row                | Contains high order 5 bits of the R.A.M. address accessible to the tri state bus (row).                 |

| ARTO               | Communications Interface<br>UART             |                                                                                                         |

| ART1               | Auxiliary Interface UART (printer, etc.)     |                                                                                                         |

| LIT                | Literal (8 bit) Register                     | Used to transfer constants from ROM to tri state bus.                                                   |

| CPR                | Cursor Row Position<br>Register              |                                                                                                         |

| CPC                | Cursor Character Position<br>Register        | ·                                                                                                       |

| KEY                | Keyboard Register                            |                                                                                                         |

| LRC                | Longitudinal Transmissions<br>Check Register | For modulo 2 sum check of transmission characters.                                                      |

| RCV                | Receiver                                     | Receiver character register                                                                             |

TABLE 2-2. TABLE OF REGISTER USAGE (Continued)

| Register<br>Symbol | Register<br>Name   | Description                                                                                                                          |

|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| ADD                |                    | Switches set manually inside cabinet                                                                                                 |

| MAR                | Margin Register    | Eight bit utility register used for temporary holding of dynamic data.                                                               |

| CNTR               | Counter Register   | Eight bit utility register used for holding program counter during subroutine calls, and for incremented or decremented comparisons. |

| IND                | Indicator Register | Eight bit register controls<br>lighted indicators at right<br>hand side of screen.<br>l = lighted                                    |

| CMD                | Command Register   | Not used in standard MMDC.                                                                                                           |

| OUTPUT             | Output Register    | Not used in standard MMDC.                                                                                                           |

| INPUT              | Input Register     | Not used in standard MMDC.                                                                                                           |

#### INSTRUCTION SET FOR T-5101 MICRO CONTROLLER

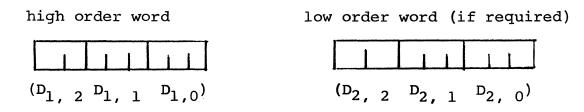

Instructions may be partitioned into two classes, those which occupy two eight bit bytes and those which occupy one eight bit byte. These can be represented as six or three octal digits, respectively, where the high order bit in each word is assumed to be zero. The implied ninth bit is, of course, not actually present in the eight bit hardware.

Where  $D_{i,j}$  is the j<sup>th</sup> octal digit for the i<sup>th</sup> 8 bit word.

Subfields of instructions will be indicated by only the high order and low order octal digits in parentheses, for example: Only high order word:

or both high and low order words:

Examples of terminal control functions written in the T-5101 mnemonic instruction set are given at the conclusion of this section.

TABLE 2-3. T-5101 INSTRUCTION SET

| T   |            |     |            |     |               |

|-----|------------|-----|------------|-----|---------------|

| 001 | READ       | 072 | CLR STB6   | 220 | JFC OFLO      |

| 003 | WRITE      | 073 | SET STB6   | 221 | JFC MAC=CPR   |

| 004 | CLR WDR    | 074 | CLR STB7   | 222 | JFC OPT1      |

| 005 | LOA WDR    | 075 | SET STB7   |     |               |

| 006 | SET WPROT  | 076 | CLR STB8   | 230 | JFC RDR       |

| 007 | CLR WPROT  | 077 | SET STB8   | 231 | JFC RPE       |

| 016 | SET PROTM  | 100 | JMP        | 232 | JFC RFE       |

| 017 | CLR PROTM  | 120 | SEL ARTO   | 234 | JFC THRE      |

| 020 | CLR MACC   | 121 | SET RTSO   | 235 | JFC CTS       |

| 021 | LOA MACC   | 122 | CLR RTSO   | 236 | JFC TRE       |

| 022 | SET MACC   | 123 | LOA ARTO   | 237 | JFC NORS/OPT2 |

| 023 | INC MACC   | 124 | CLR ARTO   | 240 | JFC PROTM     |

| 024 | DEC MACC   | 130 | SEL ART1   | 241 | JFC PROT      |

| 027 | LOA CPR    | 131 | SET RTS1   | 242 | JFC INTIN     |

| 030 | CLR MACR   | 132 | CLR RTS1   | 243 | JFC FULL      |

| 031 | LOA MACR   | 133 | LOA ART1   | 243 | JFC KEYST2    |

| 032 | SET MACR   | 134 | CLR ART1   | 244 | JFC OPNC      |

| 033 | INC MACR   | 150 | LOA LIT    | 244 | JFC RESET     |

| 034 | DEC MACR   | 156 | CLR LRC    | 245 | JFC CONV      |

| 035 | INH CUR    | 157 | CLK LRC    | 246 | JFC FDX       |

| 036 | ENA CUR    | 160 | TSB=RDR    | 247 |               |

| 037 | SET BEEP   | 161 | TSB=KEY    |     |               |

| 040 | LOA OUTPUT | 162 | TSB=RCV    | 250 | JFC MACC      |

| 042 | LOA MAR    | 163 | TSB=LIT    | 251 | JFC NULL      |

| 044 | LOA IND    | 164 | TSB=CPC    | 252 | JFC LIT7      |

| 045 | CLR IND    | 165 | TSB=CPR    | 253 | JFC LIT8      |

| 046 | LOA CMD    | 166 | TSB=LRC    | 260 | JFC STB1      |

| 051 | LOA CNTR   |     |            | 261 | JFC STB2      |

| 052 | INC CNTR   | 170 | TSB=ADD    | 262 | JFC STB3      |

| 053 | DEC CNTR   | 172 | TSB=INPUT  | 263 | JFC STB4      |

| 054 | SET TIME   | 173 | TSB=MAR    | 264 | JFC STB5      |

| 055 | SET BIN    | 174 | TSB=IND    | 265 | JFC STB6      |

| 056 | CLR RTSEN  | 175 | TSB=CNTR   | 266 | JFC STB7      |

| 057 | SET RTSEN  | 200 | JFC TSB1   | 267 | JFC STB8      |

| 060 | CLR STB1   | 201 | JFC TSB2   | 300 | JTC TSB1      |

| 061 | SET STB1   | 202 | JFC TSB3   | 301 | JTC TSB2      |

| 062 | CLR STB2   | 203 | JFC TSB4   | 302 | JTC TSB3      |

| 063 | SET STB2   | 204 | JFC TSB5   | 303 | JTC TSB4      |

| 064 | CLR STB3   | 205 | JFC TSB6   | 304 | JTC TSB5      |

| 065 | SET STB3   | 206 | JFC TSB7   | 305 | JTC TSB6      |

| 066 | CLR STB4   | 207 | JFC TSB8   | 306 | JTC TSB7      |

| 067 | SET STB4   | 210 | JFC KEYSTR | 307 | JTC TSB8      |

| 070 | CLR STB5   | 213 | JFC CALL   | 310 | JTC KEYSTR    |

| 071 | SET STB5   | 214 | JFC RTN    | 313 | JTC CALL      |

| L   |            | . " |            |     |               |

TABLE 2-3. T-5101 INSTRUCTION SET (Continued)

TABLE 2-4. RANDOM ACCESS MEMORY CONTROL

| Mnemonic  | (D <sub>1,2</sub> D <sub>1,0</sub> ) | Description                                                                                                                                                        |

|-----------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ      | 001                                  | Transfers the contents of the RAM location indicated by the contents of MACR, MACC into the RDR                                                                    |

| WRITE     | 003                                  | Transfers the contents of the WDR into the RAM location indicated by the contents of MACR, MACC                                                                    |

| LOA WDR   | 005                                  | Replaces the contents of the WDR with the contents currently on the TSB                                                                                            |

| CLR WDR   | 004                                  | Clears the WDR                                                                                                                                                     |

| TSB=RDR   | 160                                  | Sets the contents on the TSB equal to the contents of the RDR                                                                                                      |

| SET WPROT | 006                                  | Sets the write protect bit on all words subsequently written into the RAM                                                                                          |

| CLR WPROT | 007                                  | Clears the write protect bit on all words subsequently written into the RAM                                                                                        |

| SET PROTM | 016                                  | Set the PROTM. This status bit is used as a global condition by the program to disable the overwriting of any characters in the RAM for which the WPROT bit is set |

| CLR PROTM | 017                                  | Clear the PROTM. This global condition enables the overwriting of write protected characters                                                                       |

TABLE 2-5. RAM ADDRESS CONTROL

| Mnemonic | (D <sub>1,2</sub> D <sub>1,0</sub> ) | Description                                                                                                                                                             |

|----------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLR MACC | 020                                  | Set character counter to left<br>margin                                                                                                                                 |

| CLR MACR | 030                                  | Set row counter to top row                                                                                                                                              |

| LOA MACC | 021                                  | Set character counter to value on tri state bus                                                                                                                         |

| LOA MACR | 031                                  | Set row counter to value on<br>tri state bus                                                                                                                            |

| LOA CPR  | 027                                  | Sets contents of CPC and CPR equal to current contents of MACC and MACR, respectively                                                                                   |

| SET MACC | 022                                  | Set character counter to right margin                                                                                                                                   |

| SET MACR | 032                                  | Set row counter to bottom row                                                                                                                                           |

| INC MACC | 023                                  | * Move character counter right one position                                                                                                                             |

| INC MACR | 033                                  | * Move row counter down one line                                                                                                                                        |

| DEC MACC | 024                                  | * Move character counter left one position                                                                                                                              |

| DEC MACR | 034                                  | * Move row counter up one line                                                                                                                                          |

| SET BIN  | 055                                  | This instruction, if followed immediately by LOA MACC or LOA MACR, will load the binary value of the (TSB) rather than the interpreted character value normally loaded. |

<sup>\*</sup> These operations will set OFLO if they cause character address to run off either margin or if they cause row address to run off top or bottom of page.

TABLE 2-6. ROM INSTRUCTION EXECUTION SEQUENCE CONTROL

| Mnemonic | (D <sub>1,2</sub> D <sub>2,0</sub> ) | Description                                                                                                                                                                                                                                                              |

|----------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| THEMOTIC | (51,2 52,0)                          |                                                                                                                                                                                                                                                                          |

| ЈМР      | 10P LLL                              | Causes next instructions to be<br>taken from the location indicated<br>by LLL on page P                                                                                                                                                                                  |

| JTC      | 3CC LLL                              | Causes next instructions to be taken from the location indicated by LLL on the local page if the condition indicated by CC is true. Instructions are taken in normal sequence otherwise. (See table of conditions for values of CC.) (See note below for CALL and RTN.)  |

| JFC      | 2CC LLL                              | Causes next instructions to be taken from the location indicated by LLL on the local page if the condition indicated by CC is false. Instructions are taken in normal sequence otherwise. (See table of conditions for values of CC.) (See Note below for CALL and RTN.) |

| · ·      |                                      | o subroutines on the same page<br>e CALL and RTN conditions as                                                                                                                                                                                                           |

| JFC CALL | 213                                  | Causes contents of the program counter to be transferred to CNTR prior to transfer of control                                                                                                                                                                            |

| JFC RTN  | 214                                  | Causes contents of CNTR to replace contents of program counter. LLL is ignored. CNTR must be incremented prior to this operation                                                                                                                                         |

TABLE 2-7. TABLE OF CONDITIONS

| Mnemonic | Condition<br>Identifier | Description                                   |

|----------|-------------------------|-----------------------------------------------|

| TSBl     | 00                      | Tri State Bus Bit l                           |

| 2        | 01                      | Tri State Bus Bit 2                           |

| 3        | 02                      | Tri State Bus Bit 3                           |

| 4        | 03                      | Tri State Bus Bit 4                           |

| 5        | 04                      | Tri State Bus Bit 5                           |

| 6        | 05                      | Tri State Bus Bit 6                           |

| 7        | 06                      | Tri State Bus Bit 7                           |

| 8        | 07                      | Tri State Bus Bit 8                           |

| KEYSTER  | 10                      | Keyboard strobe                               |

| OFLO     | 20                      | MACC/MACR overflow or underflow               |

| MAC=CPR  | 21                      | Set if MACR equals CPR                        |

| OPTl     | 22                      | Wire straps on main logic board               |

| PROTM    | 40                      | Set if in character protection mode           |

| PROT     | 41                      | Character protect bit in RAM and protect mode |

| CONV     | 45                      | Conversation mode                             |

| CALL     | 13                      | Subprogram call                               |

| RTN      | 14                      | Subprogram return                             |

| RDR      | 30                      | RCV Data ready                                |

| RPE      | 31                      | RCVR parity error                             |

| RFE      | . 32                    | RCVR framing error                            |

TABLE 2-7. TABLE OF CONDITIONS (Continued)

| Mnemonic   | Condition<br>Identifier | Description                                      |

|------------|-------------------------|--------------------------------------------------|

| ROE        | 33                      | RCVR overflow                                    |

| THRE       | 34                      | Transmitter holding register<br>ready            |

| CTS        | 35                      | Clear to sent (asynchronous transmission)        |

| TRE        | 36                      | Transmitter register empty                       |

| RESET/OPT2 | 37                      | Reset by OPT 2 (Strap)                           |

| INTIN      | 42                      | Extended memory option                           |

| KEYST2     | 47                      | Send Key Strobe Line (operation keys)            |

| RESET      | 44                      | Reset key (also used with extended memory)       |

| FDX        | 46                      | Full duplex                                      |

| MACC       | 50                      | (TSB) equals (MACC)                              |

| NULL       | 51                      | (TSB) equals (NULL)                              |

| LIT7       | 52                      | (TSB) equals (LIT) seven bits only (1 through 7) |

| LIT8       | 53                      | (TSB) equals (LIT) eight bits                    |

| STBl       | 60                      | Status BIT 1                                     |

| 2          | 61                      | Status BIT 2                                     |

| 3          | 62                      | Status BIT 3                                     |

| 4          | 63                      | Status BIT 4                                     |

| 5          | 64                      | Status BIT 5                                     |

TABLE 2-7. TABLE OF CONDITIONS (Continued)

| Mnemonic | Condition<br>Identifier | Description  |

|----------|-------------------------|--------------|

| 6        | 65                      | Status BIT 6 |

| 7        | 66                      | Status BIT 7 |

| 8        | 67                      | Status BIT 8 |

TABLE 2-8. TABLE OF CONDITION SIGNIFICANCE

| Condition<br>Mnemonic | Use or Action Resulting                               |

|-----------------------|-------------------------------------------------------|

| WPROT                 | Write Protect bit copies into RAM each Write          |

| PROTM                 | Write Protect mode                                    |

| STBl                  | Status Bits set by microprogram for global<br>control |

| 2                     | Status Bits set by microprogram for global control    |

| 3                     | Status Bits set by microprogram for global control    |

| 4                     | Status Bits set by microprogram for global control    |

| 5                     | Status Bits set by microprogram for global control    |

| 6                     | Status Bits set by microprogram for global control    |

| 7                     | Status Bits set by microprogram for global control    |

| 8                     | Status Bits set by microprogram for global control    |

TABLE 2-8. TABLE OF CONDITION SIGNIFICANCE (Continued)

| Condition<br>Mnemonic | Use of Action Resulting                                                   |

|-----------------------|---------------------------------------------------------------------------|

| RTSO                  | Request to sent (Main ART)                                                |

| RTS1                  | Request to send (Auxiliary ART)                                           |

| TSBl                  | Tri State Bus Bits                                                        |

| 2                     | Tri State Bus Bits                                                        |

| 3                     | Tri State Bus Bits                                                        |

| 4.                    | Tri State Bus Bits                                                        |

| 5                     | Tri State Bus Bits                                                        |

| 6                     | Tri State Bus Bits                                                        |