STANDARD MICROSYSTEMS CORPORATION Data CATALOG

1979

| INDEX           | PAGE |

|-----------------|------|

| PART NUMBER     | 3    |

| FUNCTIONAL      | 4-7  |

| CROSS REFERENCE | 8-9  |

FACILITIES/CUSTOM CAPABILITIES ..... 10-14 QUALITY ASSURANCE ..... 15-16

DATA COMMUNICATION PRODUCTS ..... 17-76

PRINTER ..... 109-122

CRT DISPLAY ..... 77-108

SECT

SECTION VI

SECTION VII

SECTION IX

MICROPROCESSOR PERIPHERAL ..... 165-187

BAUD RATE GENERATOR ..... 123-150

KEYBOARD ENCODER ..... 151-164

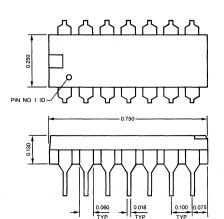

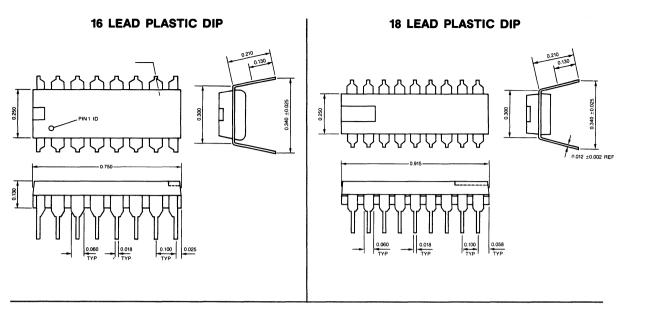

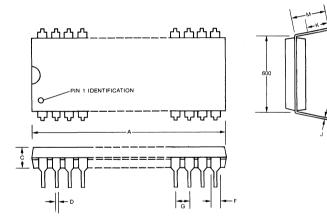

PACKAGE DATA ..... 188-189 REPRESENTATIVES AND DISTRIBUTORS ..... 190-191

TERMS OF SALE ..... INSIDE BACK

#### ORDERING INFORMATION

## PART NUMBER INDEX

SECTION I

| PART NUMBER | PAGE    | PART NUMBER  | PAGE    |

|-------------|---------|--------------|---------|

| COM 1553A   | 18-19   | COM 5036     | 128-129 |

| COM 1671    | 20-35   | COM 5036T    | 128-129 |

| FDC 1771    | _       | CRT 5037     | 78-85   |

| FDC 1791    | —       | COM 5046     | 130-131 |

| COM 1863    | 36      | COM 5046T    | 130-131 |

| COM 2017    | 37-44   | CRT 5057     | 78-85   |

| COM 2017H   | 37-44   | FDC 7003     | 178-179 |

| KR 2376XX   | 152-155 | CRT 7004A    | 104-108 |

| COM 2502    | 37-44   | CRT 7004B    | 104-108 |

| COM 2502H   | 37-44   | CRT 7004C    | 104-108 |

| COM 2601    | 45-52   | CRT 8002A    | 94-103  |

| COM 2651    | 53-54   | CRT 8002B    | 94-103  |

| FDC 3400    | 170-177 | CRT 8002C    | 94-103  |

| CCC 3500    | 180-187 | COM 8004     | 67      |

| KR 3600XX   | 156-163 | COM 8017     | 68-75   |

| CG 4103     | 110-113 | COM 8018     | 36      |

| ROM 4732    | 166-169 | COM 8046     | 136-137 |

| SR 5015XX   | 114-117 | COM 8046T    | 136-137 |

| SR 5015-80  | 114-117 | COM 8116     | 138-139 |

| SR 5015-81  | 114-117 | COM 8116T    | 138-139 |

| SR 5015-133 | 114-117 | COM 8126     | 140-141 |

| COM 5016    | 124-125 | COM 8126T    | 140-141 |

| COM 5016T   | 124-125 | COM 8136     | 142-143 |

| SR 5017     | 118-121 | COM 8136T    | 142-143 |

| SR 5018     | 118-121 | COM 8146     | 144-145 |

| COM 5025    | 55-66   | COM 8146T    | 144-145 |

| COM 5026    | 126-127 | COM 8251A    | 76      |

| COM 5026T   | 126-127 | COM 8502     | 68-75   |

| CRT 5027    | 78-85   | CRT 96364A/B | 86-93   |

3

## **FUNCTIONAL INDEX**

## **Data Communication Products**

| Part<br>Number           | Name                                | Description                                                                                                                                                   | Max<br>Baud Rate               | Power<br>Supplies | Package | Page  |

|--------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------|---------|-------|

| COM 1553A <sup>(1)</sup> | MIL-STD-<br>1553A UART              | MIL-STD 1553 (Manchester) Interface<br>Controller                                                                                                             | 1 MB                           | +5                | 40 DIP  | 18-19 |

| COM 1671                 | ASTRO                               | Asynchronous/Synchronous<br>Transmitter/Receiver, Full Duplex 5-8<br>data bit, 1X or 32X clock                                                                | 1 MB                           | +5, -5, +12       | 40 DIP  | 20-35 |

| COM 1863 <sup>(1)</sup>  | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 1½, 2 stop bit, enhanced distortion<br>margin                                | 40 KB                          | +5                | 40 DIP  | 36    |

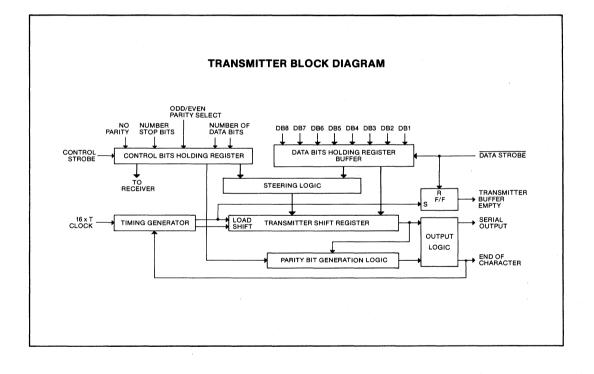

| COM 2017                 | UART                                | Universal Asynchronous Receiver<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 1½, 2 stop bit                                                                | 25 KB                          | +5, -12           | 40 DIP  | 37-44 |

| COM 2017H                | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 1½, 2 stop bit                                                               | 40 KB                          | +5, -12           | 40 DIP  | 37-44 |

| COM 2502                 | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 2 stop bit                                                                   | 25 KB                          | +5, -12           | 40 DIP  | 37-44 |

| COM 2502H                | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 2 stop bit                                                                   | 40 KB                          | +5, -12           | 40 DIP  | 37-44 |

| COM 2601                 | USRT                                | Universal Synchronous Receiver/<br>Transmitter, STR, BSC, Bi-sync<br>compatible                                                                               | 250 KB                         | +5, -12           | 40 DIP  | 45-52 |

| COM 2651 <sup>(1)</sup>  | USART/PCI                           | Universal Synchronous/Asynchronous<br>Receiver/Transmitter, Full Duplex; 5-8<br>Data bits; 1, 1½, 2 stop bit, 1X, 16X,<br>64X clock                           | 1 <b>M</b> B                   | +5                | 28 DIP  | 53-54 |

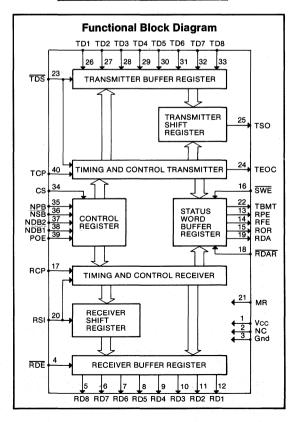

| COM 5025                 | Multi-Protocol<br>USRT              | SDLC, HDLC, ADCCP, Bi-sync, DDCMP<br>compatible, automatic bit stuffing/<br>stripping, frame detection/generation,<br>CRC generation/checking, sync detection | 1.5 MB                         | +5, +12           | 40 DIP  | 55-66 |

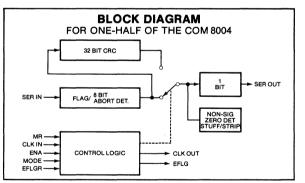

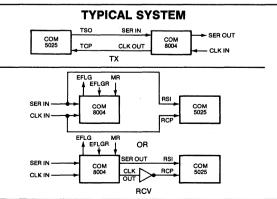

| COM 8004 <sup>(1)</sup>  | 32 Bit CRC<br>Generator/<br>Checker | Companion device to COM 5025<br>for 32 bit CRC                                                                                                                | 2.0 MB                         | +5                | 20 DIP  | 67    |

| COM 8017                 | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 1 <sup>1</sup> / <sub>2</sub> , 2 stop bit                                   | 40 KB                          | +5                | 40 DIP  | 68-75 |

| COM 8018 <sup>(1)</sup>  | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 1½, 2 stop bit, enhanced distortion<br>margin                                | 40 KB                          | +5                | 40 DIP  | 36    |

| COM 8251A <sup>(1)</sup> | USART/PCI                           | Universal Synchronous/Asynchronous<br>Receiver/Transmitter, Full Duplex, 5-8<br>data bit, 1, 1½, 2 stop bit                                                   | 64 KB (sync)<br>9.6 KB (async) | +5                | 28 DIP  | 76    |

| COM 8502                 | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 2 stop bit                                                                   | 40 KB                          | +5                | 40 DIP  | 68-75 |

(1)For future release

#### **VTAC<sup>®</sup> TIMING CONTROLLERS**

| Part #                     | Description                                                    | Features                            | Display<br>Format   | Max<br>Clock | Power<br>Supplies | Package | Page  |

|----------------------------|----------------------------------------------------------------|-------------------------------------|---------------------|--------------|-------------------|---------|-------|

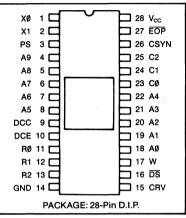

| CRT 5027                   | provides all of the                                            |                                     |                     |              |                   |         |       |

| CRT 5037                   | timing and control<br>for interlaced and<br>non-interlaced CRT | balanced beam interlace             | programmable        | 4 MHz        | +5, +12           | 40 DIP  | 78-85 |

| CRT 5057 <sup>(1)</sup>    | display                                                        | line-lock                           |                     |              |                   |         |       |

| CRT 96364/B <sup>(1)</sup> | complete CRT<br>processor                                      | on-chip cursor and<br>write control | 64 column<br>16 row | 1.6 MHz      | +5                | 28 DIP  | 86-93 |

(1)For future release

#### **VDAC<sup>™</sup> DISPLAY** CONTROLLERS

| Part #                     | Description                                                                                   | Display                            | Attributes                        | Max<br>Clock | Power<br>Supply | Package | Page   |

|----------------------------|-----------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------|--------------|-----------------|---------|--------|

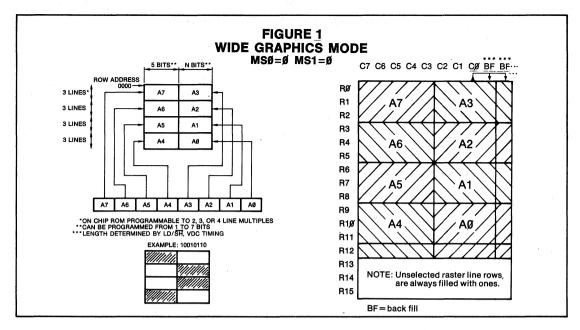

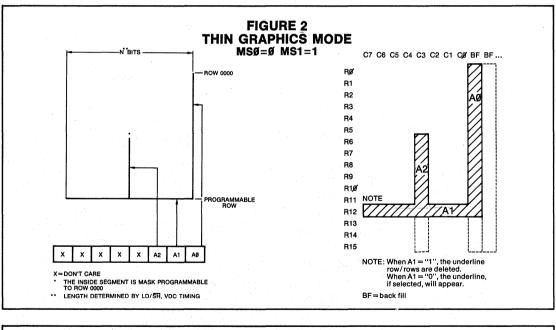

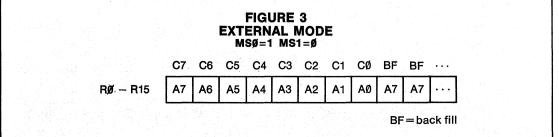

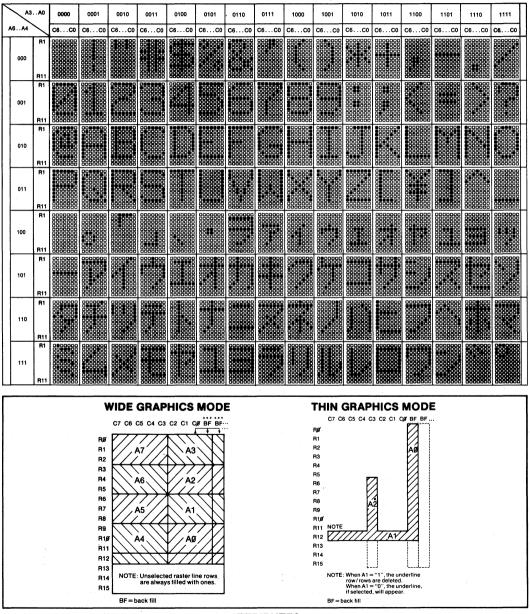

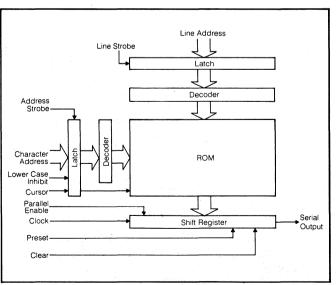

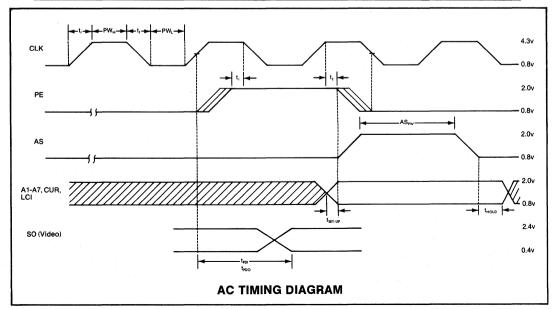

| CRT 8002A <sup>(2,3)</sup> | display and attri-                                                                            | 7x11 dot matrix,<br>wide graphics, | blank                             | 20 MHz       |                 |         |        |

| CRT 8002B <sup>(2,3)</sup> | Consists of 7x11x128                                                                          | thin graphics.<br>on-chip cursor   | blink<br>underline<br>strike-thru | 15 MHz       | +5              | 28 DIP  | 94-103 |

| CRT 8002C <sup>(2,3)</sup> | character generator,<br>video shift register,<br>latches, graphics and<br>attributes circuits |                                    |                                   | 10 MHz       |                 |         |        |

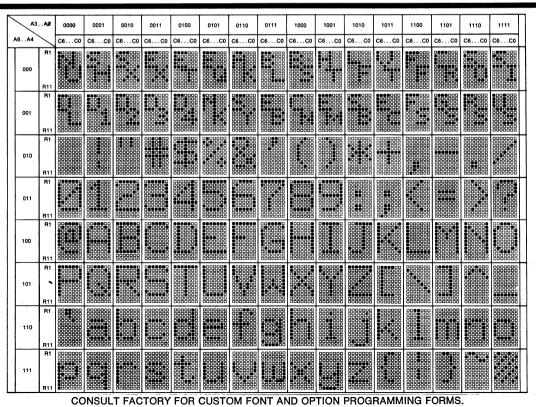

(2)Also available as CRT 8002A,B,C—001 Katakana CRT 8002A,B,C—003 5X7 dot matrix

<sup>(3)</sup>May be custom mask programmed

#### CHARACTER GENERATORS

| Part #                   | Description                   | Max<br>Frequency | Power Supply | Package | Page    |

|--------------------------|-------------------------------|------------------|--------------|---------|---------|

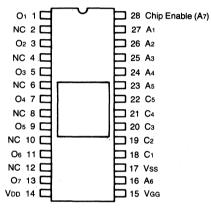

| CRT 7004A <sup>(3)</sup> | 7x11x128 character generator, | 20 MHz           |              |         |         |

| CRT 7004B <sup>(3)</sup> | latches, video shift register | 15 MHz           | +5 ·         | 24 DIP  | 104-108 |

| CRT 7004C <sup>(3)</sup> |                               | 10 MHz           |              |         |         |

<sup>(3)</sup>May be custom mask programmed

#### CHARACTER GENERATOR

| Part Number            | Description | Scan   | <b>Max Access Time</b> | <b>Power Supplies</b>        | Package | Page    |

|------------------------|-------------|--------|------------------------|------------------------------|---------|---------|

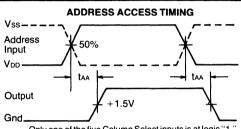

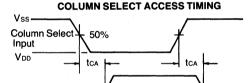

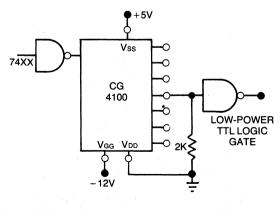

| CG 4103 <sup>(3)</sup> | 5x7x64      | Column | 1.2 µsec               | $+5, -12 \text{ or } \pm 12$ | 28 DIP  | 110-113 |

<sup>(3)</sup>May be custom mask programmed

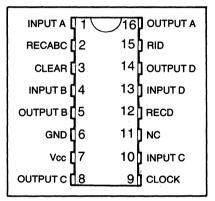

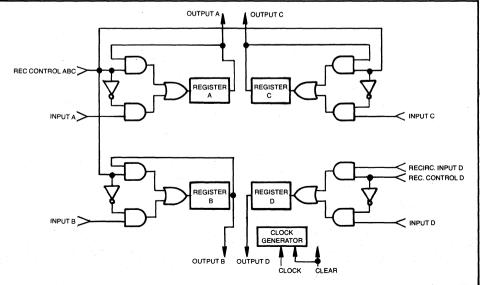

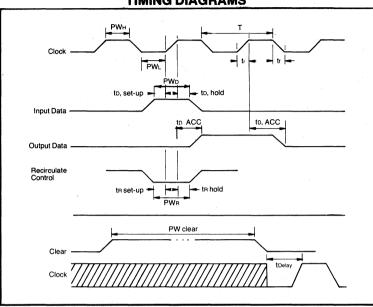

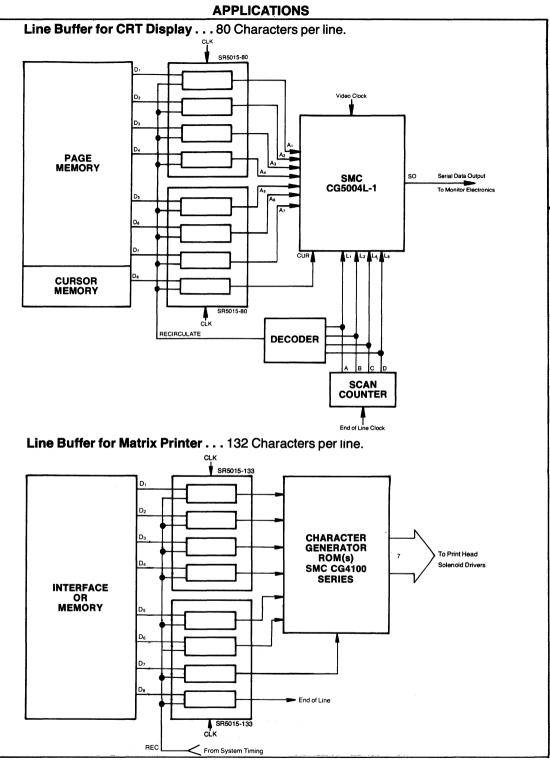

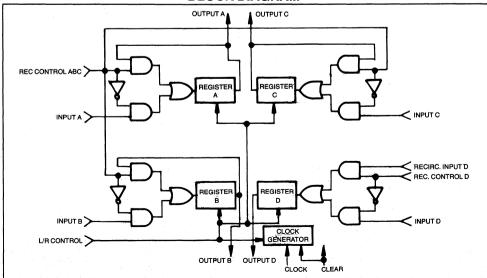

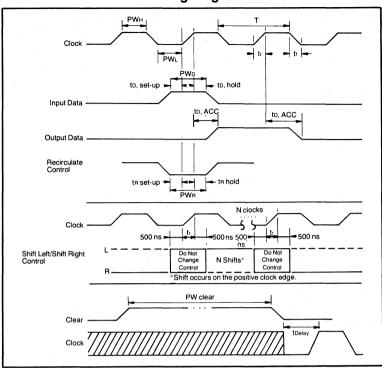

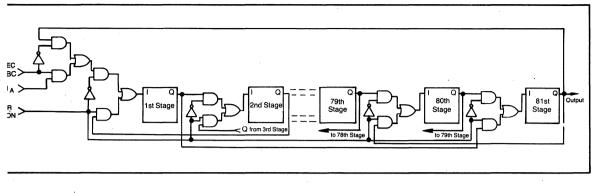

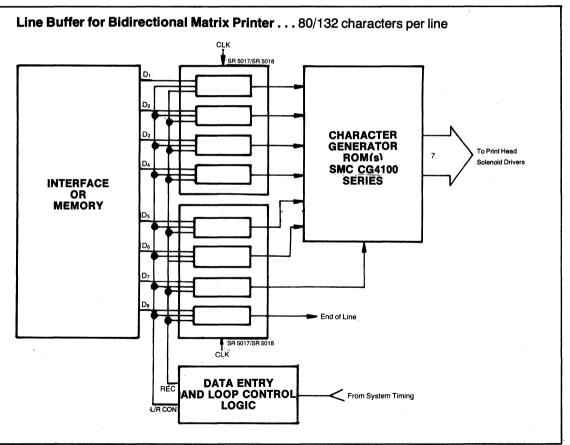

#### SHIFT REGISTER

| Part Number | Description                                            | Feature                                | Max<br>Clock Freq. | Power<br>Supply. | Package | Page    |

|-------------|--------------------------------------------------------|----------------------------------------|--------------------|------------------|---------|---------|

| SR 5015-XX  | Quad Static Shift Register<br>Mask Programmable Length | Load, Recirculate,<br>Shift Controls,  |                    |                  |         | · · · · |

| SR 5015-80  | Quad 80 Bit Static                                     |                                        |                    |                  |         | 2       |

| SR 5015-81  | Quad 81 Bit Static                                     |                                        | 1 MHz              | +5               | 16 DIP  | 114-117 |

| SR 5015-133 | Quad 133 Bit Static                                    |                                        |                    |                  |         | 10 A    |

| SR 5017     | Quad 81 Bit                                            | Shift Left/Shift<br>Right, Recirculate | 1 MHz              | +5               | 16 DIP  | 118-121 |

| SR 5018     | Quad 133 Bit                                           | Controls, Asynch-<br>ronous clear      |                    | , 0              | 10 011  |         |

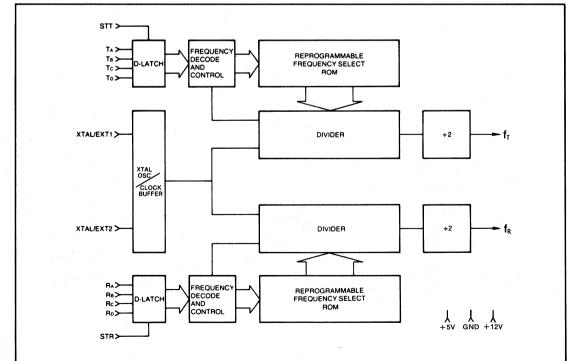

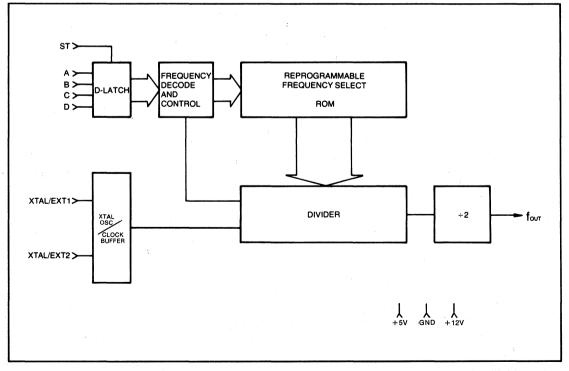

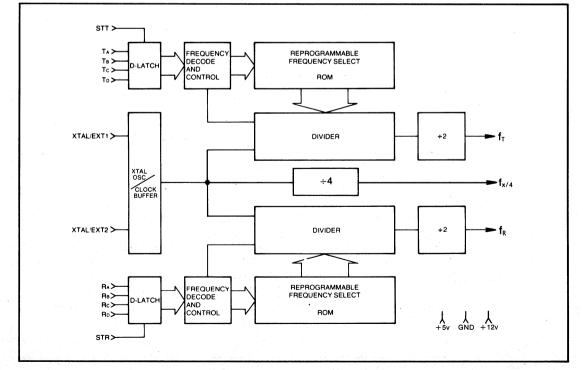

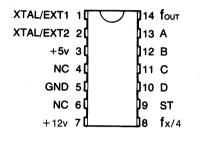

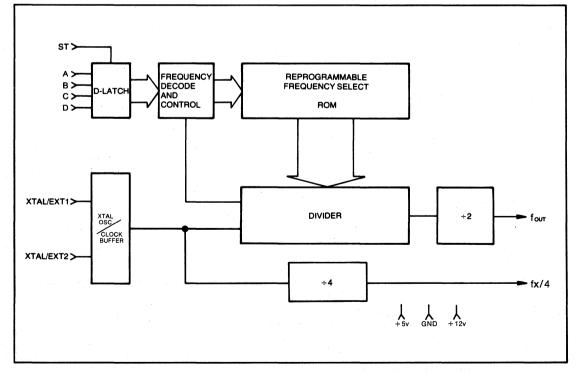

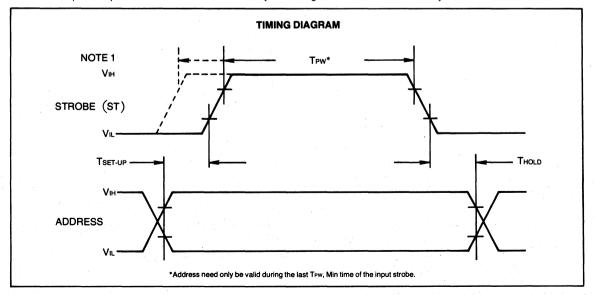

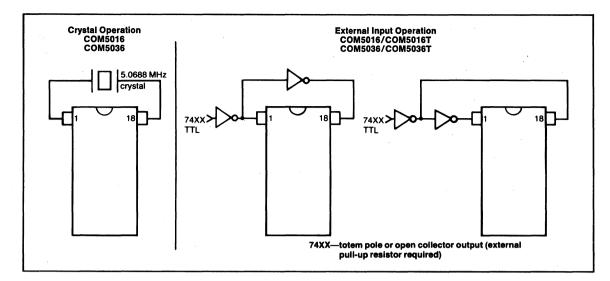

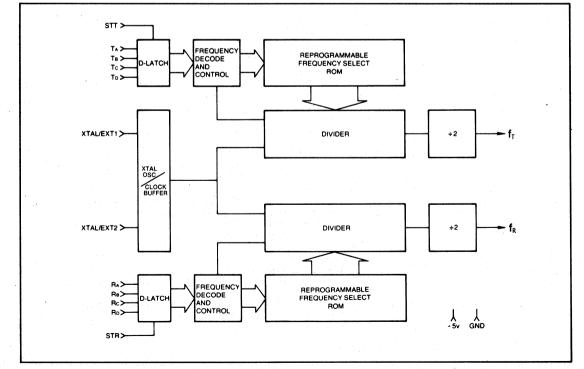

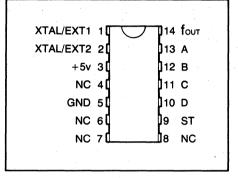

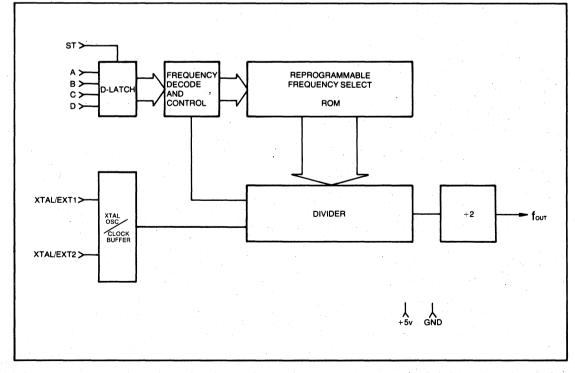

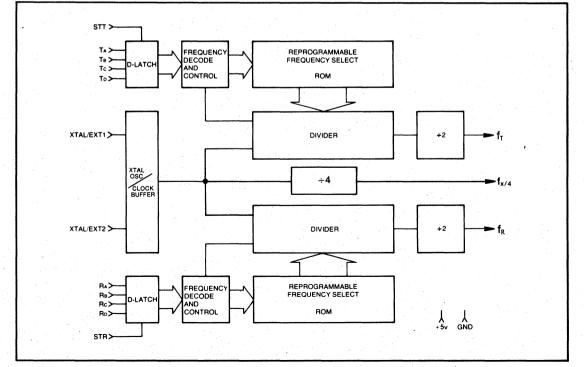

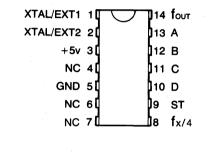

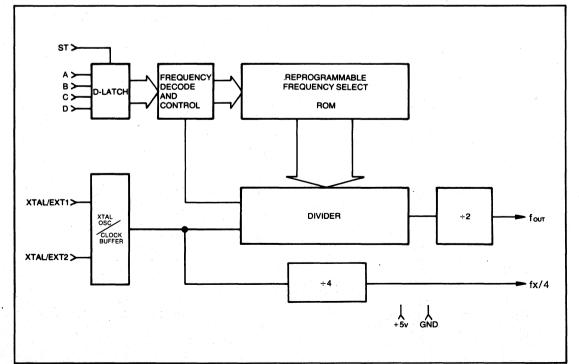

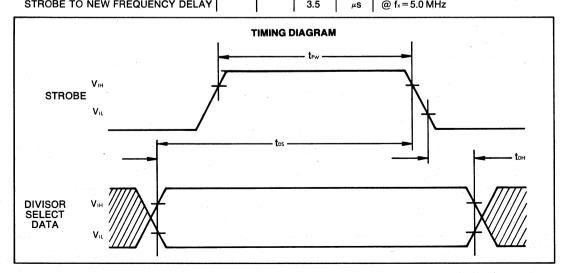

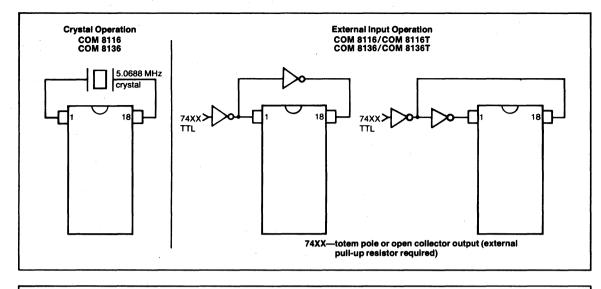

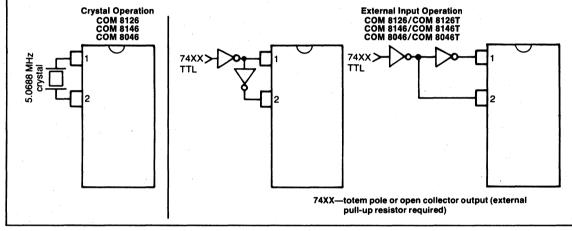

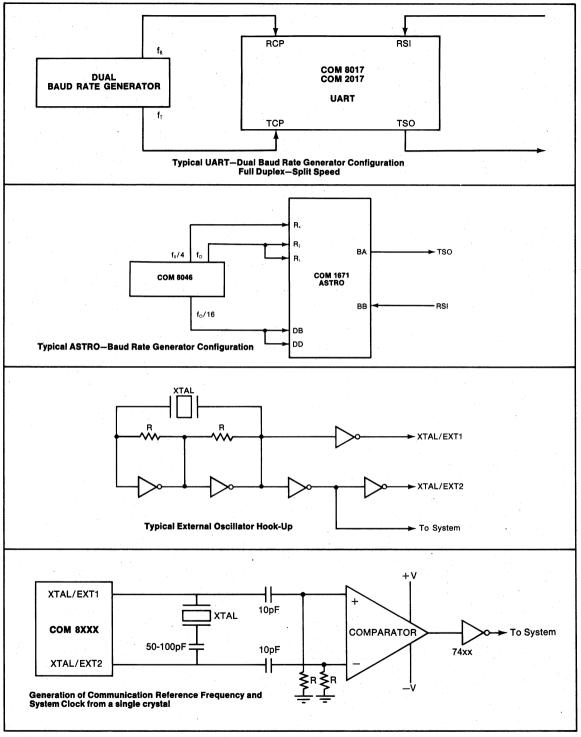

All Baud Rate Generators are programmable dividers capable of providing 16 output frequencies' for UARTs or USARTs from either an on-chip crystal oscillator or an external frequency input. "T" versions utilize an external frequency input only. Dual Baud Rate Generators provide two output frequencies simultaneously for full duplex communication.

Baud Rate Generators providing all standard baud rates from various popular crystal frequencies are available. In addition the baud rate generator may be custom mask programmed for other divisors.

#### \*except as noted

| Part #    | Description                | Features                                                               | Power<br>Supplies | Package | Page    |

|-----------|----------------------------|------------------------------------------------------------------------|-------------------|---------|---------|

| COM 5016  | Dual Baud Rate Generator   | On-chip oscillator or external frequency input                         | +5, +12           | 18 DIP  | 124-125 |

| COM 5016T | Dual Baud Rate Generator   | External frequency input                                               | +5, +12           | 18 DIP  | 124-125 |

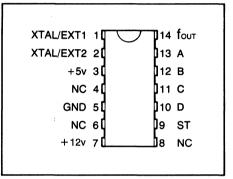

| COM 5026  | Single Baud Rate Generator | On-chip oscillator or external frequency input                         | +5, +12           | 14 DIP  | 126-127 |

| COM 5026T | Single Baud Rate Generator | External frequency input                                               | +5, +12           | 14 DIP  | 126-127 |

| COM 5036  | Dual Baud Rate Generator   | COM 5016 with additional output of input frequency ÷ 4                 | +5, +12           | 18 DIP  | 128-129 |

| COM 5036T | Dual Baud Rate Generator   | COM 5016T with additional output of input frequency ÷ 4                | +5, +12           | 18 DIP  | 128-129 |

| COM 5046  | Single Baud Rate Generator | COM 5026 with additional output of input frequency ÷ 4                 | +5, +12           | 14 DIP  | 130-131 |

| COM 5046T | Single Baud Rate Generator | COM 5026T with additional<br>output of input frequency ÷ 4             | +5, +12           | 14 DIP  | 130-131 |

| COM 8046  | Single Baud Rate Generator | 32 baud rates; 1X, 16X, 32X<br>clock outputs; single +5 volt<br>supply | +5                | 16 DIP  | 136-137 |

| COM 8046T | Single Baud Rate Generator | COM 8046 with external frequency input only                            | +5                | 16 DIF  | 136-137 |

| COM 8116  | Dual Baud Rate Generator   | Single +5 volt version of<br>COM 5016                                  | +5                | 18 DIP  | 138-139 |

| COM 8116T | Dual Baud Rate Generator   | Single +5 volt version of<br>COM 5016T                                 | +5                | 18 DIP  | 138-139 |

| COM 8126  | Single Baud Rate Generator | Single +5 volt version of COM 5026                                     | +5                | 14 DIP  | 140-141 |

| COM 8126T | Single Baud Rate Generator | Single +5 volt version of<br>COM 5026T                                 | +5                | 14 DIP  | 140-141 |

| COM 8136  | Dual Baud Rate Generator   | Single +5 volt version of<br>COM 5036                                  | +5                | 18 DIP  | 142-143 |

| COM 8136T | Dual Baud Rate Generator   | Single +5 volt version of<br>COM 5036T                                 | +5                | 18 DIP  | 142-143 |

| COM 8146  | Single Baud Rate Generator | Single +5 volt version of COM 5046                                     | +5                | 14 DIP  | 144-145 |

| COM 8146T | Single Baud Rate Generator | Single +5 volt version of<br>COM 5046T                                 | +5                | 14 DIP  | 144-145 |

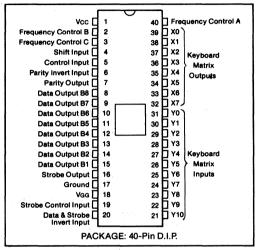

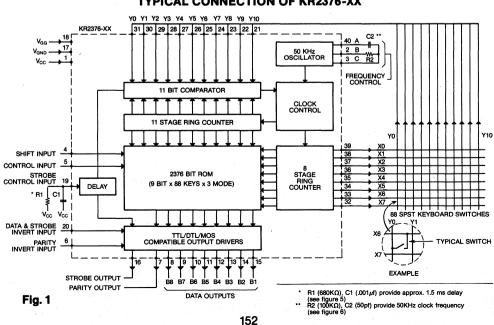

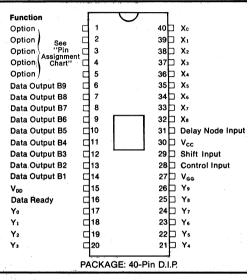

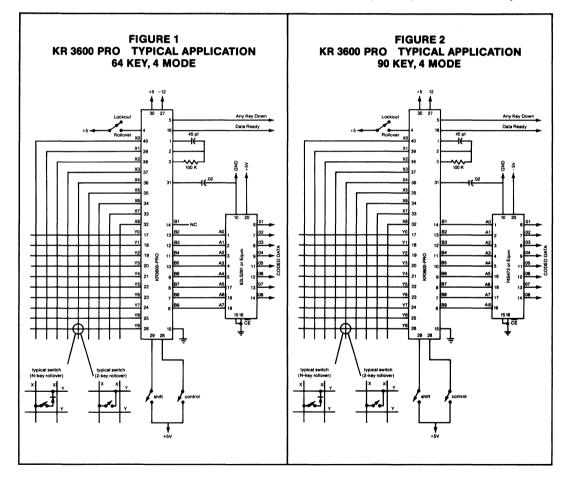

### Keyboard Encoder

| Part #                    | No. of Keys | Modes | Features                   | Sta<br>Suffix       | ndard Fonts<br>Description          | Power<br>Supplies | Package | Page    |

|---------------------------|-------------|-------|----------------------------|---------------------|-------------------------------------|-------------------|---------|---------|

| KR-2376 XX <sup>(3)</sup> | 88          | 3     | 2 Key Rollover             | -ST                 | ASCII                               | +5, -12           | 40 DIP  | 152-155 |

| KR-3600 XX <sup>(3)</sup> | 90          | 4     | 2 Key or<br>N Key Rollover | -ST<br>-STD<br>-PRO | ASCII<br>ASCII<br>Binary Sequential | +5, -12           | 40 DIP  | 156-163 |

<sup>(3)</sup>May be custom mask programmed

## **Microprocessor Peripheral**

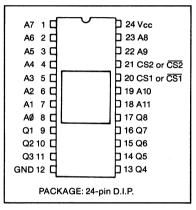

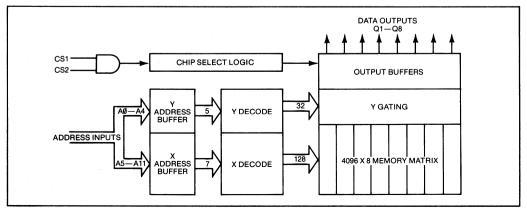

#### ROM

| Part Number             | Description                           | Access Time | Power Supply | Package | Page    |

|-------------------------|---------------------------------------|-------------|--------------|---------|---------|

| ROM 4732 <sup>(3)</sup> | 32K ROM; 32,768 bits organized 4096x8 | 450 nsec    | +5           | 24 DIP  | 166-169 |

<sup>3)</sup>May be custom mask programmed

#### FLOPPY DISK

| Part<br>Number          | Description                                                                         | Sector<br>Format | Density | IBM<br>Compatible | Write<br>Pre-com-<br>pensation | Power<br>Supplies | Package | Page    |

|-------------------------|-------------------------------------------------------------------------------------|------------------|---------|-------------------|--------------------------------|-------------------|---------|---------|

| FDC 1771 <sup>(1)</sup> | Controller/Formatter                                                                | Soft             | Single  | Yes               | No                             | +5                | 40 DIP  |         |

| FDC 1791 <sup>(1)</sup> | Floppy Disk<br>Controller/Formatter                                                 | Soft             | Double  | Yes               | External                       | +5                | 40 DIP  |         |

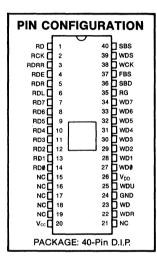

| FDC 3400                | Floppy Disk Data Handler<br>provides serial/parallel inter-<br>face, sync detection | Hard             | N.A.    | N.A.              | No                             | +5, -12           | 40 DIP  | 170-177 |

| FDC 7003 <sup>(1)</sup> | Floppy Disc<br>Controller/Formatter                                                 | Soft             | Double  | Yes               | Internal                       | +5                | 40 DIP  | 178-179 |

#### CASSETTE/CARTRIDGE

| Part Number | Description                     | Max<br>Data Rate | Features                                 | Power<br>Supply | Package | Page    |

|-------------|---------------------------------|------------------|------------------------------------------|-----------------|---------|---------|

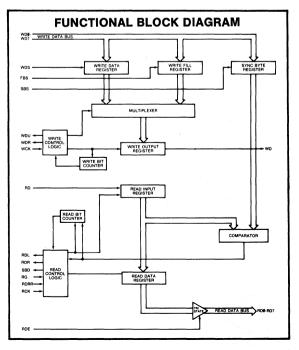

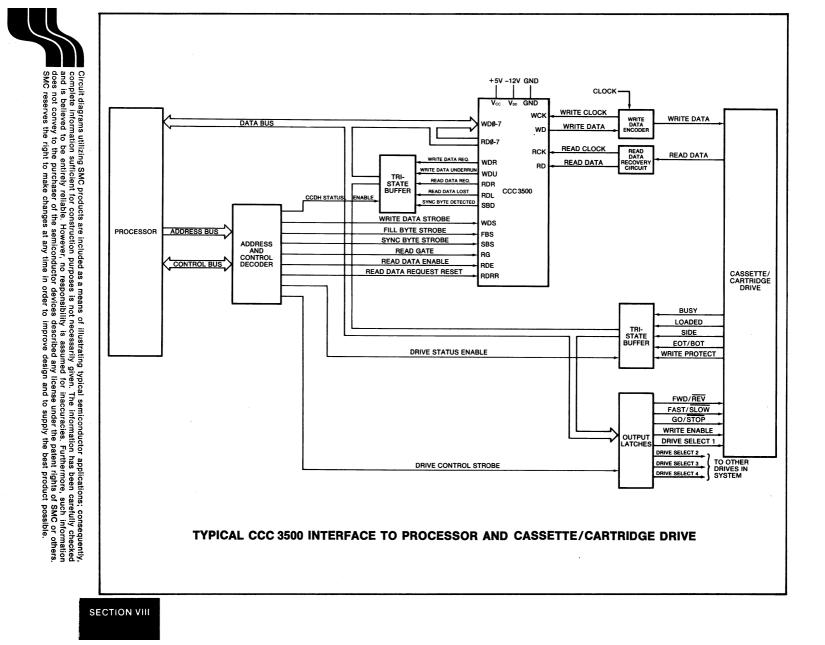

| CCC 3500    | Cassette/Cartridge Data Handler | 250K bps         | Sync byte detection,<br>Read While Write | +5, -12         | 40 DIP  | 180-187 |

For future release

## **SMC CROSS REFERENCE GUIDE**

| Description           | SMC<br>Part #              | AMI        | E.A.                      | Fairchild  | G.I.        | Harris             | Intel | Inter |

|-----------------------|----------------------------|------------|---------------------------|------------|-------------|--------------------|-------|-------|

| UART (1½ SB)**        | COM 2017                   | S1883      | _                         | <u> </u>   | AY 5-1013A  |                    | _     | _     |

| UART (1, 2 SB)**      | COM 2502                   | S1863      | -                         | _          | AY 5-1013   |                    |       | -     |

| UART (N-Channel)**    | COM 8017                   | S6850*     | ·                         | _          | AY 3-1015   | HM6402             | _     | IM64C |

| UART (N-Channel)**    | COM 8502                   |            | _                         | _          | AY 3-1015   | HM6403*            | 8251* | IM640 |

| UART (CMOS)**         | COM 6402                   | · <u> </u> | _                         | _          | _           | HM6402             |       | IM64C |

| USR/T                 | COM 2601                   | S2350*     |                           |            |             |                    | _     |       |

| ASTRO                 | COM 1671                   |            | ·                         | _          |             |                    | 8251* |       |

| Multi-Protocol        | COM 5025                   |            |                           | ·          | . —         | .—                 |       |       |

| Dual Baud Rate Gen.   | COM 5016/36<br>COM 8116/36 | —          | · · · ·                   | _          | <b></b>     |                    |       |       |

| Single Baud Rate Gen. | COM 5026/46<br>COM 8126/46 | . <b>—</b> | _                         | F4702*     | _           | HD4702*<br>HD6405* |       |       |

| 88 Key KB Encoder     | KR 2376                    |            | -                         | _          | AY 5-2376   | _                  |       |       |

| 90 Key KB Encoder     | KR 3600                    | —          | EA2007*<br>2030*<br>2007* | -          | AY 5-3600   | _                  | _     |       |

| Character Generator   | CRT 7004                   | S8564*     |                           | · <b>-</b> | <b>—</b>    | -                  |       | _     |

| Character Generator   | CRT 8002                   |            |                           | -          |             | _                  |       | _     |

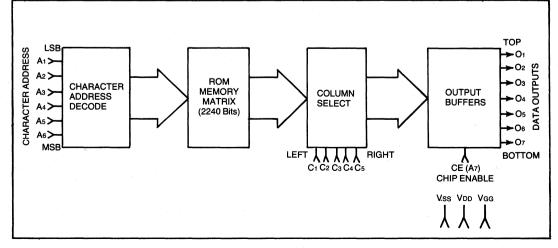

| Character Generator   | CG 4100                    | S8499      |                           |            | RO 5-2240S* | _                  | _     | _     |

| Shift Register        | SR 5015                    | S2182/3/5  | -                         |            | _           |                    |       |       |

| Shift Register        | SR 5017                    | _          | -                         |            |             |                    | _     | -     |

| CRT Controller        | CRT 5027                   | _          | _                         |            |             |                    | 8275* |       |

| ROM                   | ROM 4732                   | S68322     | 8332                      |            | RO 3-9332   | _                  | 2332  |       |

\*Functional Equivalent

SECTION I

|                    |         | ·····                | <b>F</b> | r            |         |           | 1                            |          |                      |         |

|--------------------|---------|----------------------|----------|--------------|---------|-----------|------------------------------|----------|----------------------|---------|

| MOS<br>chnology    | Mostek  | Motorola             | National | NEC          | Plessy  | Signetics | Solid<br>State<br>Scientific | Synertec | т.і.                 | W.D.    |

|                    | -       | _                    | MM5303*  | HPD369*      | _       | _         | -                            | -        | TMS6011              | TR1602  |

| · ·                | -       | _                    | _        |              | _       | 2536      | _                            | _        | _                    | TR1402  |

| _                  | -       | MC6850*              | _        |              | _       | _         | -                            |          | ·                    | TR1863  |

|                    | -       | _                    |          | _            | -       | _         | -                            | _        | -                    | TR1983* |

| <u> </u>           | _       | _                    | _        |              | _       |           | SCP1854                      | _        | _                    | _       |

|                    | _       | -                    | _        |              | _       | _         |                              |          | -                    | _       |

| ` ·                |         | _                    | INS1671  | _            | _       | 2651*     |                              |          |                      | UC1671  |

|                    |         | <u> </u>             |          | HPD379*      |         | 2652      |                              | _        |                      | SD1933* |

| ·                  |         | _                    |          | _            |         |           |                              |          |                      | BR1941L |

|                    | _       | 'MC14411*            | MM5307*  | _            | _       |           |                              |          | _                    |         |

|                    | _       | . —                  | —        | _            |         | _         | —                            | _        | _                    | -       |

| CS1009*            | _       | _                    | MM5740*  | HPD364*      | MP3802* | _         | _                            | -        | TMS5001              | _       |

|                    |         | MCM66700*<br>MC6570* | DM8678*  | _            | _       | 2609*     | <b>—</b> .                   |          | _                    | _       |

|                    |         |                      |          |              |         |           | —                            | _        | _                    | _       |

| CS1004*<br>CS2027* | MK2002  | MC1132*              | M5240    | _            | _       |           |                              | -        | TMS4103              |         |

| -                  | MK1002* |                      | 5054*    |              | _       | 2532*     | -                            | _        | TMS3113*<br>TMS3114* | _       |

| -                  | —       | - 1.<br>             |          |              | ·. —    |           |                              | _        | _                    | · .     |

|                    |         | MC6845*              | DP8350*  |              | _       |           | -                            | 6545*    | TMS9927              |         |

|                    |         | _                    |          | $\mu$ PD2332 | · -     | 2632      |                              | SY2332   | TMS4732              |         |

|                    |         | MC6845*<br>—         |          | —<br>μpd2332 |         | <br>2632  | -                            |          |                      |         |

\*\*Most UART's are interchangeable; consult the factory for detailed information on interchangeability.

9

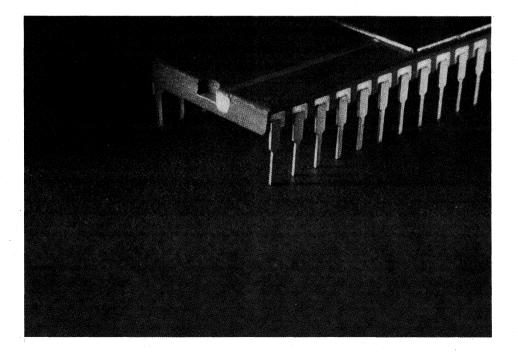

## Innovation in microelectronic technology is the key to growth at Standard Microsystems.

Since its inception, Standard Microsystems has been a leader in creating new technology for metal oxide semiconductor large scale integrated (MOS/LSI) circuits.

For example, while the first MOS/LSI processes were P-channel, it was recognized very early that an N-channel process would greatly improve switching speeds and circuit density. However, the fundamental problem of parasitic currents needed to be solved. The research and development staff at Standard Microsystems recognized this problem and directed its energy toward the development of its now-famous COPLAMOS<sup>®</sup> technology. COPLAMOS<sup>®</sup> defines a self-aligned, field-doped, locally oxidized structure which produces high-speed, high-density N-channel IC's.

In addition, on-chip generation of substrate bias, also pioneered by Standard Microsystems, when added to the COPLAMOS® technology, results in the ability to design dense, high-speed, low-power N-channel MOS integrated circuits through the use of one external power supply voltage.

Again recognizing a need and utilizing its staff of qualified process experts, Standard Microsystems developed the CLASP® process. The need was for fast turnaround, easily programmable semi-custom LSI technology. The development was CLASP,® a process that utilizes ion implantation to define either an active or passive device which allows for the presence of a logical 1 or 0 in the matrix of a memory or logic array. This step is accomplished after all wafer manufacturing steps are performed including metalization and final passiviation layer formation. Thus, the wafer can be tested and stored until customer needs dictate the application, a huge saving in turnaround time and inventory costs.

These innovations in both process and circuit technology have received widespread industry recognition. In fact, many of the world's most prominent semiconductor companies have been granted patent and patent/technology licenses covering various aspects of these technologies. The companies include Texas Instruments, IBM, General Motors, ITT and Western Electric.

# Our engineering staff follows the principle that "necessity is the mother of invention."

This philosophy led Standard Microsystems Corporation to COPLAMOS,<sup>®</sup> CLASP<sup>®</sup> and other innovative developments. It also brings companies to us to solve tough problems that other suppliers can't.

But it's a philosophy that involves more than just developing the next generation of MOS/LSI devices.

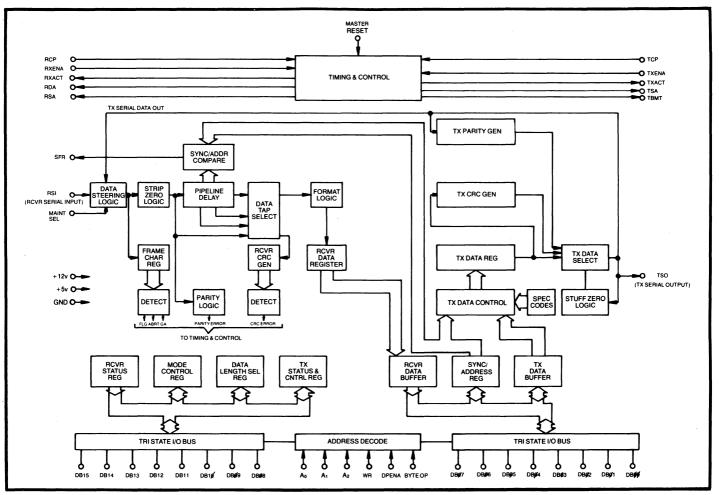

Such exploration, for example, helped Standard Microsystems recognize the need for communication controllers to handle the latest data communication protocols. As a result, Standard Microsystems was the first to introduce a one-chip LSI controller for HDLC protocols — the COM 5025.

The COM 5025 is so versatile it can actually provide the receiver/ transmitter functions for all the standard bit and byte oriented synchronous protocols, including SDLC, HDLC, ADCCP, bi-sync and DDCMP.

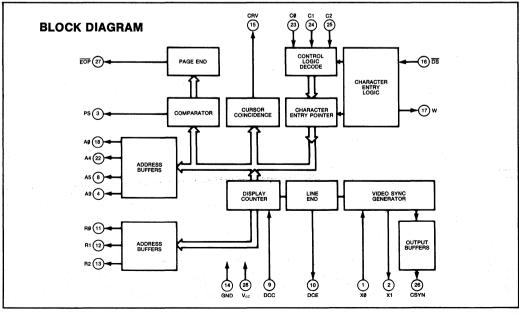

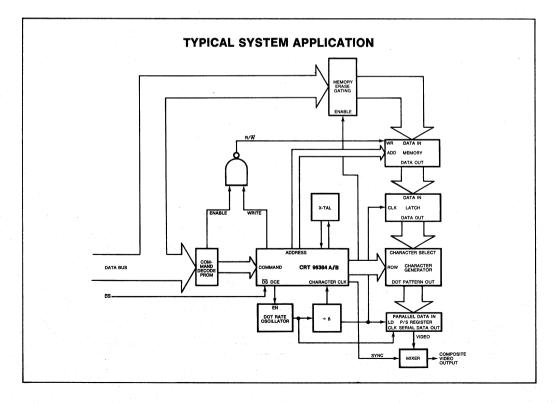

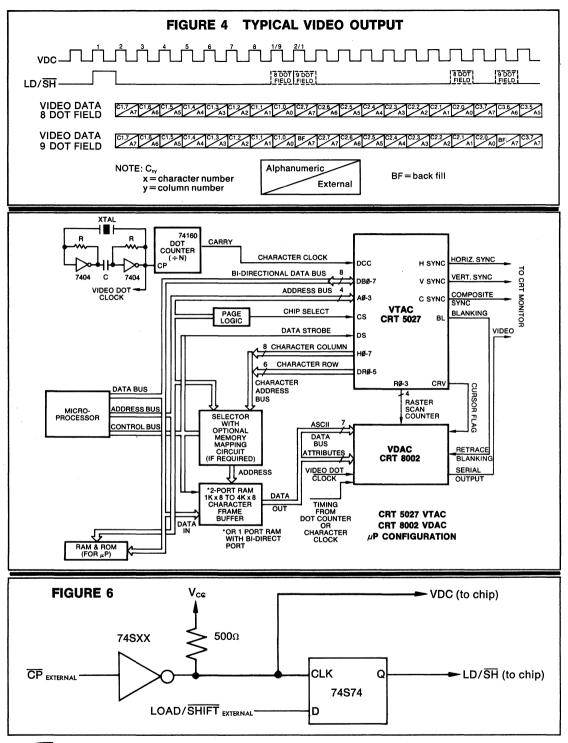

In another area, CRT display systems have traditionally required a great deal of support circuitry for the complex timing, refresh and control functions.

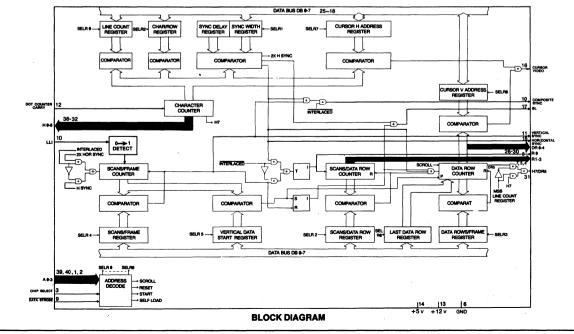

This need led the engineers at Standard Microsystems to develop the CRT 5027 Video Timer and Controller (VTAC®) that provides all these functions on a single chip. This left the display, graphics and attributes control spread over another 20 or 30 SSI, MSI and LSI devices. Standard Microsystems combined all these functions in the CRT 8002 Video Display Attributes Controller VDAC™). The COPLAMOS® process was used to achieve a 20 MHz video shift register, and CLASP® was used for fast turnaround of character font changes through its last stage programmability.

So from 60 to 80 integrated circuits, Standard Microsystems reduced display and timing to 2 devices, drastically reducing the cost and size of today's CRT terminal.

Achievements like these help keep Standard Microsystems custom and standard products in the forefront of technology with increased speeds and densities, and a lower cost per function.

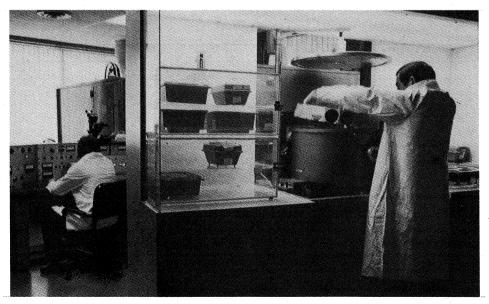

## Improvements in processing and manufacturing keep pace with advances in semiconductors.

With the phenomenal growth of the electronics industry, innovation is, of course, highly desirable. But if the products are to perform as designed, they also have to be reliable.

That's why at Standard Microsystems we take every means to insure the utmost quality and dependability. Consequently, "state-of-the-art" applies not only to our products, but to the way we manufacture them.

In wafer fabrication, the latest equipment and techniques are employed. In addition to conventional processing equipment, we use ion implantation technology extensively. We also use plasma reactors for much of our etching and stripping operations to maintain tight tolerances on process parameters.

To make plastic packaging immune to moisture, we use a process that deposits a protective (passivating) layer of silicon nitride on the device surface.

Standard Microsystems processes include high and low voltage P-channel metal gate, N-channel silicon gate (COPLAMOS<sup>®</sup>), high-speed N-channel silicon gate with depletion mode devices, and CLASP.<sup>®</sup> In general, these processes have been engineered so that they are also compatible with most industry standard processes.

One obvious advantage our total capability gives customers, is that they can bring us their project at any stage in the development process. For instance, they may already have gone through system definition. Or they may have gone all the way to prototype masks, and only want production runs.

It makes no difference to Standard Microsystems. We can enter the process at any level.

Our full service capability lets us make full use of the technologies we develop. We can produce any quantity of semiconductors customers may require. And we can offer them one of the fastest turnaround times in the industry.

## SMC microcircuits are built under the industry's most carefully controlled conditions.

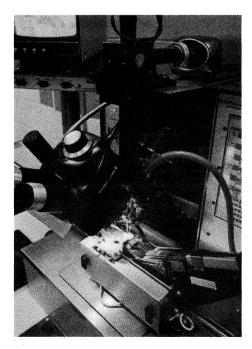

Standard Microsystems uses the latest equipment and techniques for assembly — just as it does for processing. Automatic wire-bonding which we introduced recently to expand Standard Microsystems' capacity is a typical example.

However, nothing is left to chance. To make sure every IC performs the way it should, each product is subjected to 37 quality control checks during assembly. Every run that comes out of wafer fabrication is analyzed to insure that all of its DC electrical characteristics are within specifications. Standard Microsystems' computerized analysis techniques, in fact, are second to none in the industry.

Tightly-controlled QC measures include die and pre-seal inspection and wire-pull, among others. Assembled parts are further subjected to vigorous mechanical tests including centrifuge, temperature cycling, and hermeticity testing.

Naturally, to perform all these tests properly requires adequate personnel. That's why 35% of all Standard Microsystems production technicians are assigned to the Quality Control Department.

Many tests are computer-controlled. In addition, we use dedicated equipment designed to simulate the customers' systems requirements.

Thanks to the dedication of Standard Microsystems' highly-motivated technical staff and well-trained production personnel, Standard Microsystems has one of the highest product yields in the industry.

## SMC can supply standard microcircuits or custom-design them to your requirements.

The product mix at Standard Microsystems is approximately half custom products and half standard products.

This makes Standard Microsystems the ideal company to talk with if you're undecided which direction to take.

As a matter of fact, a combination of custom and standard may actually be best for you.

Since our processes are industry compatible, we can enter a program at any level: 1. Complete system design and definition; 2. Artwork generation; 3. Wafer processing.

If you need quick turnaround on mask-programmable options, we can also combine COPLAMOS® technology with CLASP® (which stands for COPLAMOS® Last Stage Programmable), to provide the solution.

As for standard products, Standard Microsystems makes one of the widest lines of standard MOS/LSI circuits for data communications and computer peripherals in the industry.

Standard Microsystems custom circuits have found their way into such industrial, computer, and aerospace applications as computer peripherals, modems, telecommunications, data communications, home entertainment, word processing, pay TV, and many other consumer and industrial uses. In fact, Standard Microsystems has created over 100 different custom designs for the above applications.

Standard or custom LSI? Bring your requirements to Standard Microsystems. We'll give you an unbiased recommendation as to which is the best route for you to take.

### **Quality Assurance**

It is well understood at Standard Microsystems that for an integrated circuit to be attractive to a system designer, it must provide not only state-of-the-art circuit function, but do so with a high degree of reliability.

The manufacture of reliable quality product is no accident. Although testing is necessary to flag problems as soon as possible, it is an old adage that quality cannot be tested into a product, but must be designed in and builtin. The design of a reliable product is assured by adher-

The design of a reliable product is assured by adherence to tested and proven design rules. Before any change in design rules or processing steps is accepted for production, sample runs are exhaustively evaluated for both basic reliability and consistent manufacturability. The manufacturing flow is closely monitored by quality assurance to insure not only that all potential failures are identified and rejected, but that proper standards are met for the processing itself. Clean room standards, calibrations and work methods are all monitored.

In addition, test and field failures are analyzed in conjuction with design and process engineering to monitor and correct any possible flaws in either design or manufacture.

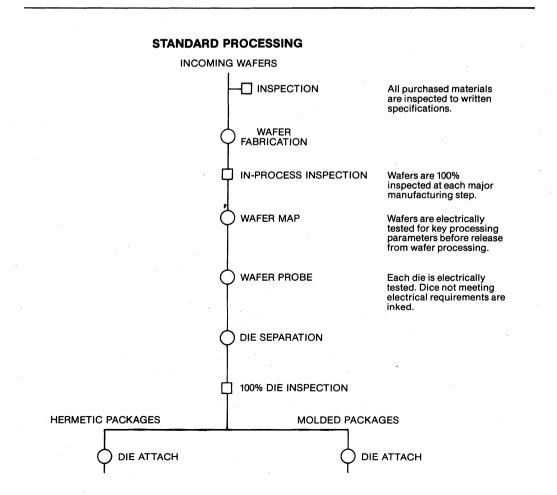

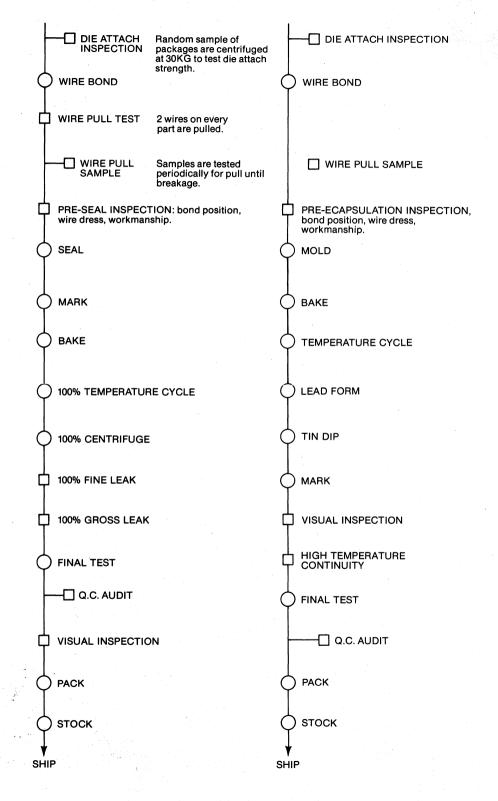

Product flow and screening for standard devices is shown on the following flow charts. In addition, MIL-STD-883 level B screening may be done on request.

SECTION I

## Data Communication Products

| Part<br>Wumber           | Name                                | Description                                                                                                                                                   | Max<br>Baud Rate               | Power<br>Supplies | Package | Page  |             |

|--------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------|---------|-------|-------------|

| COM 1553A <sup>(1)</sup> | MIL-STD-<br>1553A UART              | MIL-STD 1553 (Manchester) Interface<br>Controller                                                                                                             | 1 MB                           | + 6               | 40 DIP  | 18-19 |             |

| COM 1671                 | ASTRO                               | Asynchronous/Synchronous<br>Transmitter/Receiver, Full Duplex 5-8<br>data bit, 1X or 32X clock                                                                | 1 MB                           | +5, -5, +12       | 40 DIP  | 20-35 | SECTION III |

| COM 1863 <sup>(1)</sup>  | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 1½, 2 stop bit, enhanced distortion<br>margin                                | 40 KB                          | +5                | 40 DIP  | 36    | S           |

| COM 2017                 | UART                                | Universal Asynchronous Receiver<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 1½, 2 stop bit                                                                | 25 KB                          | +5, -12           | 40 DIP  | 37-44 |             |

| COM 2017H                | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 1½, 2 stop bit                                                               | 40 KB                          | +5, -12           | 40 DIP  | 37-44 |             |

| COM 2502                 | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 2 stop bit                                                                   | 25 KB                          | +5, -12           | 40 DIP  | 37-44 |             |

| COM 2502H                | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 2 stop bit                                                                   | 40 KB                          | +5, -12           | 40 DIP  | 37-44 |             |

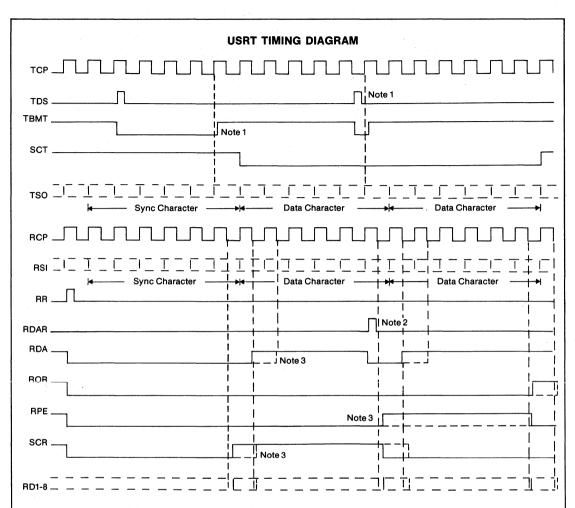

| 00 <b>M 26</b> 01        | USRT                                | Universal Synchronous Receiver/<br>Transmitter, STR, BSC, Bi-sync<br>compatible                                                                               | 250 KB                         | +5, -12           | 40 DIP  | 45-52 |             |

| 20 <b>M 2651</b> (1)     | USART/PCI                           | Universal Synchronous/Asynchronous<br>Receiver/Transmitter, Full Duplex; 5-8<br>Data bits; 1, 1½, 2 stop bit, 1X, 16X,<br>64X clock                           | 1 MB                           | +5                | 28 DIP  | 53-64 | -           |

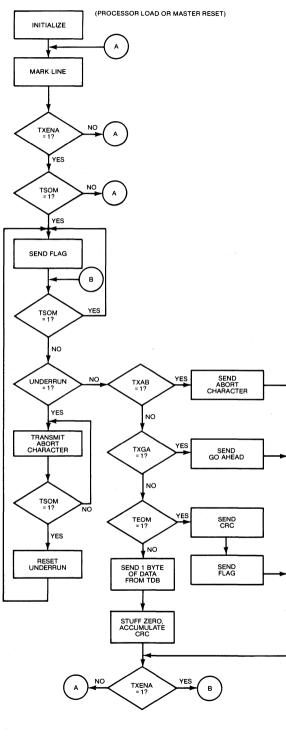

| OM 5025                  | Multi-Protocol<br>USRT              | SDLC, HDLC, ADCCP, Bi-sync, DDCMP<br>compatible, automatic bit stuffing/<br>stripping, frame detection/generation,<br>CRC generation/checking, sync detection | 1.5 MB                         | +5, +12           | 40 DIP  | 55-66 |             |

| 30M 8004(1)              | 32 Bit CRC<br>Generator/<br>Checker | Companion device to COM 5025<br>for 32 bit CRC                                                                                                                | 2.0 MB                         | + 5               | 20 DIP  | 67    |             |

| OM 8017                  | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 1½, 2 stop bit                                                               | 40 KB                          | +5                | 40 DIP  | 68-75 |             |

| OM 8018(1)               | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 1%, 2 stop bit, enhanced distortion<br>margin                                | 40 KB                          | +5                | 40 DIP  | 36    |             |

| OM 8251A(1               | USART/PCI                           | Universal Synchronous/Asynchronous<br>Receiver/Transmitter, Full Duplex, 5-8<br>data bit, 1, 1½, 2 stop bit                                                   | 64 KB (sync)<br>9.6 KB (async) | +6                | 28 DIP  | 76    |             |

| 2008 MOX                 | UART                                | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex 5-8 data bit,<br>1, 2 stop bit                                                                   | 40 KB                          | +5                | 40 DIP  | 68-75 |             |

)For future release

COM 1553A\* μPC FAMILY

### MIL-STD-1553A "UART"

#### FEATURES

- Support of MIL-STD-1553A

- Operates as a: Remote Terminal Responding Bus Controller Initiating

- □ Performs Parallel to Serial Conversion when Transmitting

- □ Performs Serial to Parallel Conversion when Receiving

- Compatible with HD-15530 Manchester Encoder/ Decoder

- □ All Inputs and Outputs are TTL Compatible

- □ Single +5 Volt Supply

- COPLAMOS® N Channel MOS Technology

- □ Available in PC Board Form from Grumman Aerospace Corporation

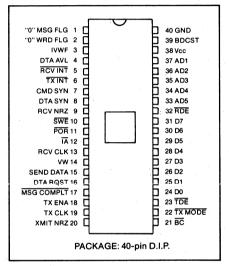

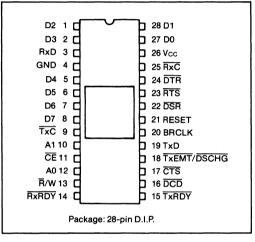

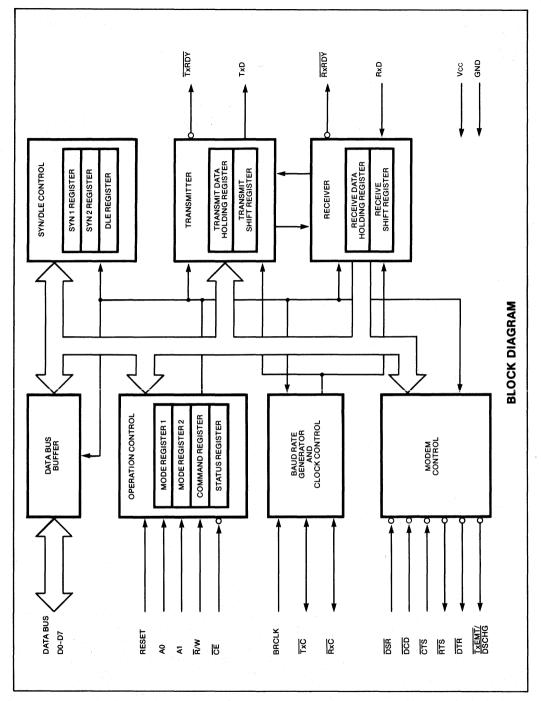

#### PIN CONFIGURATION

#### **GENERAL DESCRIPTION**

SMC's COM 1553A is a special purpose N Channel MOS/LSI-UART designed to provide a compatible user interface in support of MIL STD 1553A. The COM 1553A meets the requirements of MIL-STD-883 Method 5004.1 Level B. It operates at a 1 MHz clock rate over the full military temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C, with a single  $+5^{\circ}$  DC power supply.

The COM 1553A performs the following functions in response to a 16 bit Command Word. It provides address detection for the first five bits of the serial data input. If all 1's appear in the address field, a broadcast signal is generated. The sixth bit is decoded as mode: transmit or receive. The next five bits are decoded for zero message flag and special flags in the subaddress/mode field. The last five bits (word-count field) are decoded determining the number of words to be received or transmitted.

When receiving data sync the COM 1553A performs a serial to parallel conversion, buffers the 16 bit message word, and formats it into two parallel (8 bit) bytes for presentation to the I/O bus under processor or hard wired logic control.

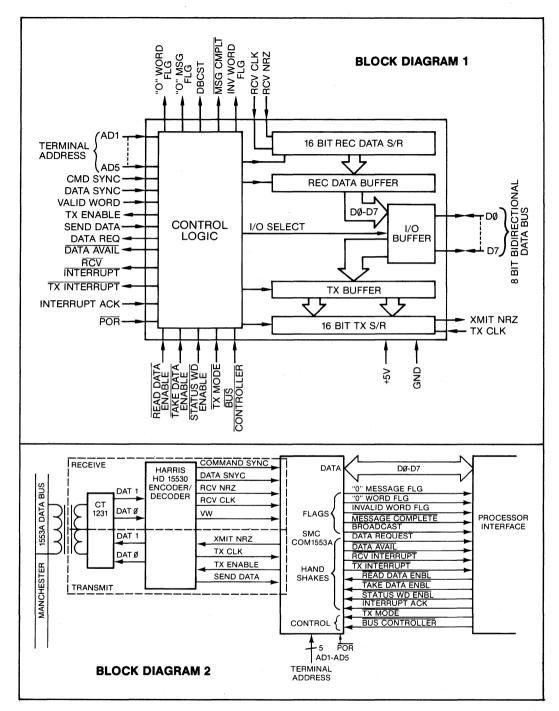

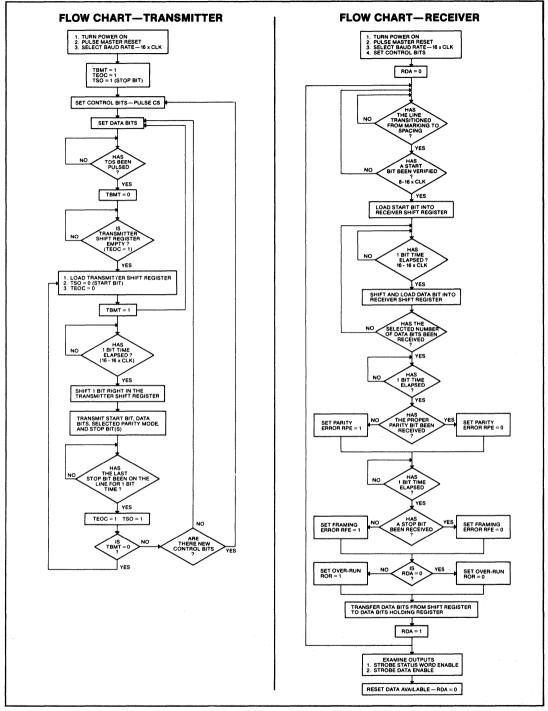

In the transmit mode the COM 1553A takes two parallel 8 bit data words from the I/O bus and serially transmits the resultant 16 bit word to the Harris HD 15530. This is done under the control of Send Data. To facilitate data transfer the COM 1553A provides all necessary buffering and storage for transmitted and received data. It also provides all necessary hand shaking, control flags and interrupts to a processor or hard wired logic terminal. See block diagram 1.

The COM 1553A can be set up as either: a terminal or a bus controller interface.

The COM 1553A is compatible with Harris' HD-15530 CMOS Manchester Encoder-Decoder chip and interfaces directly with it. A 3 device kit consisting of: SMC's COM 1553A, Harris' HD-15530 and Circuit Technology's CT1231 forms a complete system interface for the message structure of MIL-STD-1553A. See block diagram 2.

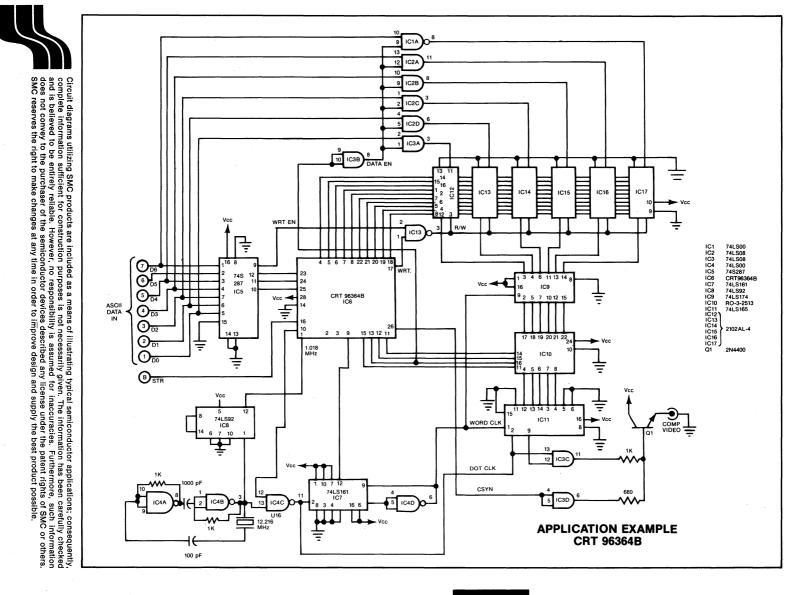

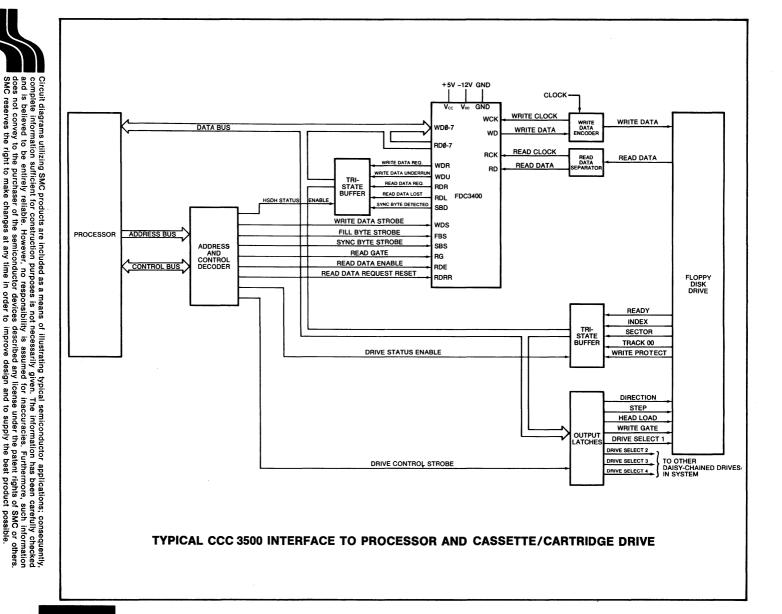

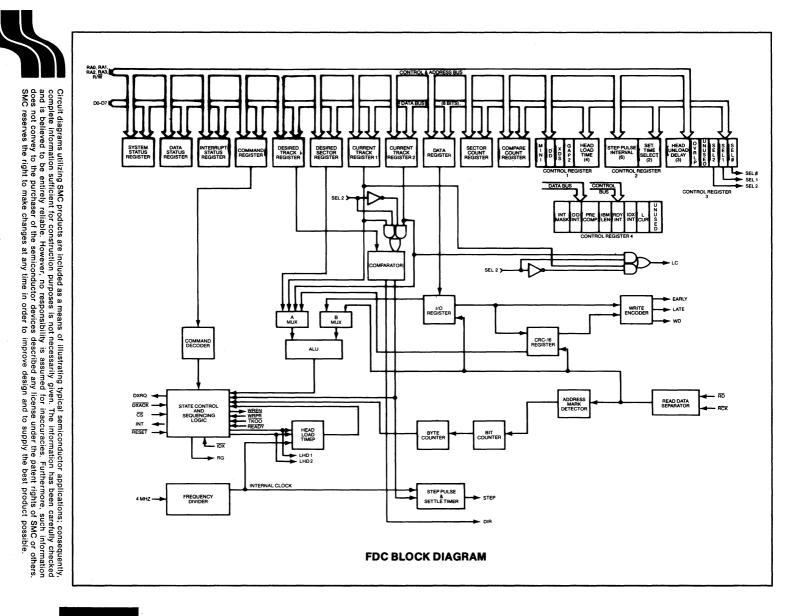

Circuit diagrams utilizing SMC products are included as a means of illustrating-typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of SMC or others. SMC reserves the right to make changes at any time in order to improve design and to supply the best product possible.

4

### Asynchronous/Synchronous Transmitter-Receiver

### ASTRO

#### FEATURES

□ SYNCHRONOUS AND ASYNCHRONOUS **Full Duplex Operations** □ SYNCHRONOUS MODE Selectable 5-8 Bit Characters Two Successive SYN Characters Sets Synchronization Programmable SYN and DLE Character Strippina Programmable SYN and DLE-SYN Fill ASYNCHRONOUS MODE Selectable 5-8 Bit Characters Line Break Detection and Generation 1-, 1<sup>1</sup>/<sub>2</sub>-, or 2-Stop Bit Selection Start Bit Verification Automatic Serial Echo Mode □ BAUD RATE—DC TO 1M BAUD □ 8 SELECTABLE CLOCK RATES Accepts 1X Clock and Up To 4 Different 32X Baud Rate Clock Inputs Up to 47% Distortion Allowance With 32X Clock □ SYSTEM COMPATIBILITY Double Buffering of Data 8-Bit Bi-Directional Bus For Data, Status, and Control Words All Inputs and Outputs TTL Compatible Up To 32 ASTROS Can Be Addressed On Bus **On-Line Diagnostic Capability** □ ERROR DETECTION Parity, Overrun and Framing

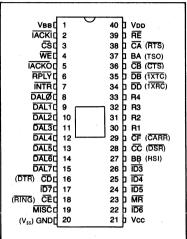

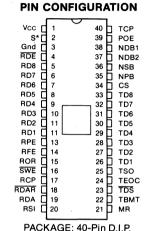

#### **PIN CONFIGURATION**

- □ COPLAMOS<sup>®</sup> n-Channel Silicon Gate Technology

- Pin for Pin replacement for Western Digital UC1671 and National INS 1671

- Baud Rate Clocks Generated by COM5036 @ 1X and COM5016-6 @ 32X

#### **APPLICATIONS**

Synchronous Communications Asynchronous Communications Serial/Parallel Communications

#### **General Description**

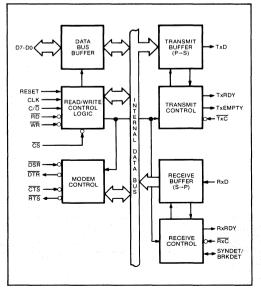

The COM1671 (ASTRO) is a MOS/LSI device which performs the functions of interfacing a serial data communication channel to a parallel digital system. The device is capable of full duplex communications (receiving and transmitting) with synchronous or asynchronous systems. The ASTRO is designed to operate on a multiplexed bus with other bus-oriented devices. Its operation is programmed by a processor or controller via the bus and all parallel data transfers with these machines are accomplished over the bus lines.

The ASTRO contains several "handshaking" signals to insure easy interfacing with modems or other peripheral devices such as display terminals. In addition, a programmable diagnostic mode allows the selection of an internal looping feature which allows the device to be internally connected for processor testing.

The COM1671 provides the system communication designer with a software responsive device capable of handling complex communication formats in a variety of system applications.

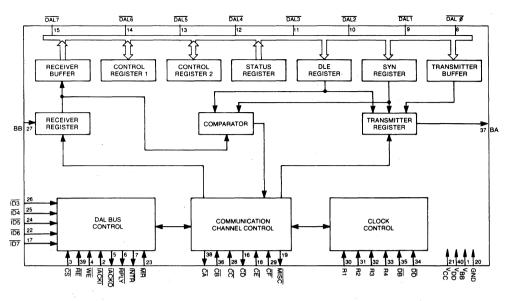

#### Organization

**Data Access Lines** — The DAL bus is an 8-bit bi-directional port over which all address, data, control, and status transfers occur. In addition to transferring data and control words the DAL bus also transfers information related to addressing of the device, reading and writing requests, and interrupting information.

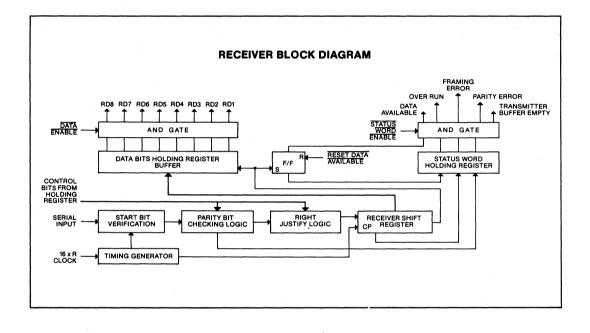

**Receiver Buffer** — This 8-bit parallel register presents assembled received characters to the DAL bus when requested through a Read operation.

**Receiver Register** — This 8-bit shift register inputs the received data at a clock rate determined by Control Register 2. The incoming data is assembled to the selected character length and then transferred to the Receiver Buffer with logic zeroes filling out any unused high-order bit positions.

**Syn Register** — This 8-bit register is loaded from the DAL bus by a Write operation and holds the synchronization code used for receiver character synchronization. It serves as a fill character when no new data is available in the Transmitter Buffer during transmission. This register cannot be read onto the DAL bus. It must be loaded with logic zeroes in all unused high-order bits.

**Comparator** — The 8-bit comparator is used in the Synchronous mode to compare the assembled contents of the Receiver Register and the SYN register or the DLE register. A match between the registers sets up stripping of the received character, when programmed, by preventing the data from being loaded into the Receiver Buffer. A bit in the Status Register is set when stripping is effected. The comparator output also enables character synchronization of the Receiver on two successive matches with the SYN register.

**DLE Register** — This 8-bit register is loaded from the DAL bus by a Write operation and holds the DLE character used in the Transparent mode of operation in which an idle transmit period is filled with the combination DLE-SYN pair of characters rather than a single SYN character. In addition the ASTRO may be programmed to force a single DLE character prior to any data character transmission while in the transmitter transparent mode.

Status Register — This 8-bit register holds information on communication errors, interface data register status, match character conditions, and communication equipment status. This register may be read onto the DAL bus by a Read operation.

**Control Registers** — There are two 8-bit Control Registers which hold device programming signals such as mode selection, clock selection, interface signal control, and data format. Each of the Control Registers can be loaded from the DAL bus by a Write operation or read onto the DAL bus by a Read operation. The registers are cleared by a Master Reset.

**Transmitter Buffer** — This 8-bit parallel register holds data transferred from the DAL bus by a Write operation. This data is transferred to the Transmitter Register when the transmitter section is enabled and the Transmitter Register is ready to send new data.

**Transmitter Register** — This 8-bit shift register is loaded from the Transmitter Buffer, SYN register, or DLE register. The purpose of this register is to serialize data and present it to the serial data output.

#### **Astro Operation**

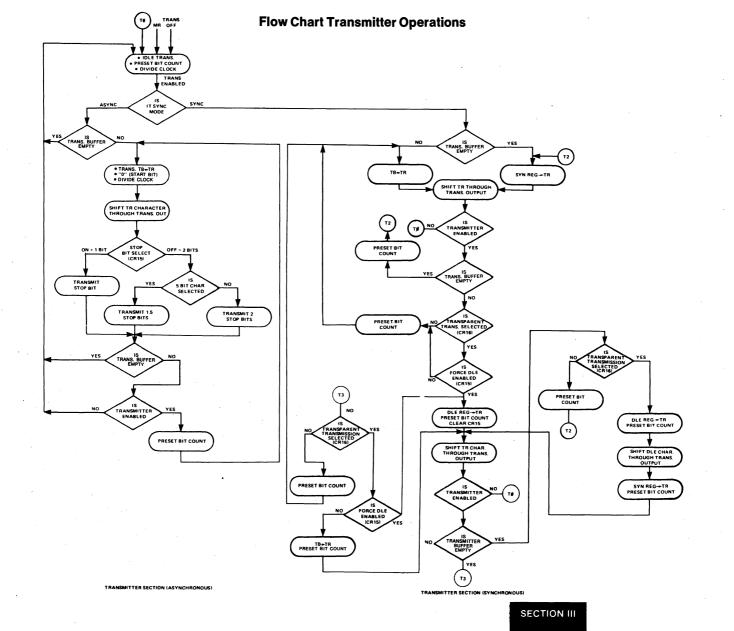

#### **Asynchronous Mode**

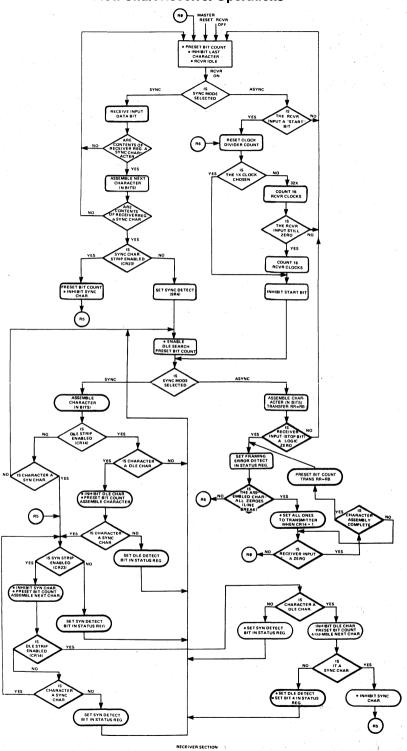

Framing of asynchronous characters is provided by a Start bit (logic 0) at the beginning of a character and a Stop bit(s) (logic 1) at the end of a character. Reception of a character is initiated on recognition of the first Start bit by a positive transition of the receiver clock, after a preceding Stop bit(s). The Start and Stop bits are stripped off while assembling the serial input into a parallel character.

The character assembly is completed by the reception of the Stop bit(s) after reception of the last character bit (including the parity bit, if selected). If the Stop bit(s) is a logic 1, the character is determined to have correct framing and the ASTRO is prepared to receive the next character. If the Stop bit(s) is a logic 0, the Framing Error Status flag is set and the Receiver assumes this bit to be the Start bit of the next character. Character assembly continues from this point if the input is still a logic 0 when sampled at the theoretical center of the assumed Start bit. As long as the Receiver input is spacing, all zero characters are assembled and error flags and data received interrupts are generated so that line breaks can be determined. After a character of all zeroes is assembled along with a zero in the Stop bit(s) location, the first sampled logic one is determined as a Stop bit and this resets the Receiver circuit to a Ready state for assembly of the next character.

In the Asynchronous mode the character transmission occurs when information contained in the Transmitter Buffer is transferred to the Transmitter Register. Transmission is initiated by the insertion of a Start bit, followed by the serial output of the character (including the parity bit, if selected), then the insertion of a 1, 1.5, or 2 bit length Stop condition. If the Transmitter Buffer is full, the next character transmission starts after the transmission of the Stop bit(s) of the present character in the Transmitter Register. Otherwise, the Mark (logic 1) condition is continually transmitted until the Transmitter Buffer is loaded.

#### Synchronous Mode

Framing of characters is carried out by a special Synchronization Character Code (SYN) transmitted at the beginning of a block of characters. The Receiver, when enabled, searches for two contiguous characters matching the bit pattern contained in the SYN register. During the time the Receiver is searching, data is not transferred to the Receiver Buffer, status bits are not updated, and the Receiver interrupt is not activated. After the detection of the first SYN character, the Receiver assembles subsequent bits into characters whose length is determined by the contents of Control Register 2. If, after the first SYN character detection, a second SYN character is present, the Receiver enters the Synchronization mode until the Receiver Enable Bit is turned off. If a second successive SYN character is not found, the Receiver reverts back to the Search mode.

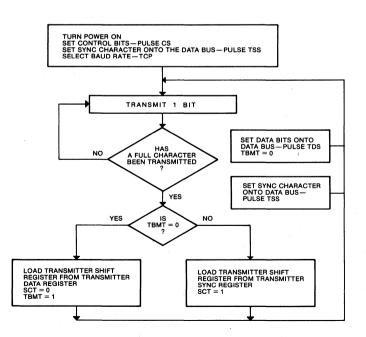

In the Synchronous mode a continuous stream of characters are transmitted once the Transmitter is enabled. If the Transmitter Buffer is not loaded at the time the Transmitter Register has completed transmission of a character, this idle time will be filled by a transmission of the character contained in the SYN register in the Non-transparent mode, or the characters contained in the DLE and SYN registers respectively while in the Transparent mode of operation.

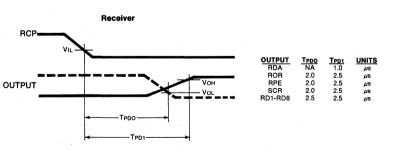

#### Astro Operation Receiver

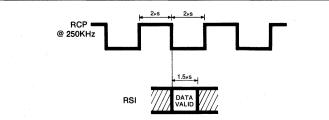

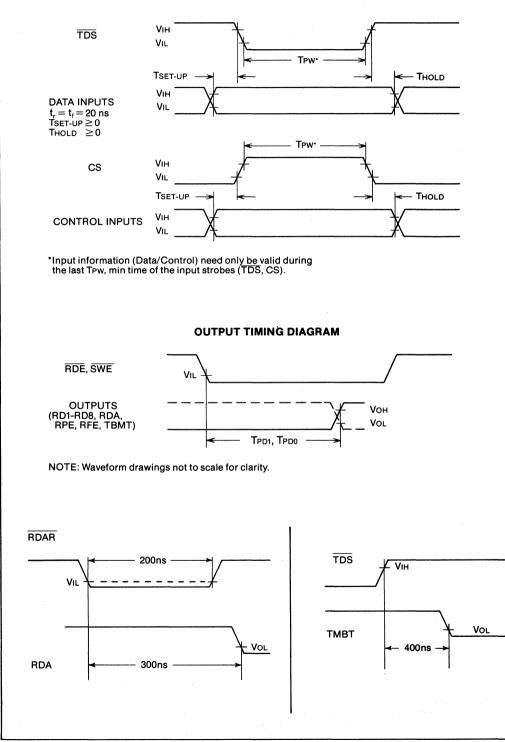

The Receiver Data input is clocked into the Receiver Register by a 1X Receiver Clock from a modem Data Set, or by a local 32X bit rate clock selected from one of four externally supplied clock inputs. When using the 1X clock, the Receiver Data is sampled on the positive transition of the clock in both the Asynchronous and Synchronous modes. When using a 32X clock in the Asynchronous mode, the Receiver Sampling Clock is phased to the Mark-To-Space transition of the Received Data Start bit and defines, through clock counts, the center of each received Data bit with +0%, -3% at the positive transition 16 clock periods later.

In the Synchronous mode the Sampling Clock is phased to all Mark-To-Space transitions of the Received Data inputs when using a 32X clock. Each transition of the data causes an incremental correction of the Sampling Check by 1/32nd of a bit period. The Sampling clock can be immediately phased to every Mark-To-Space Data transition by setting Bit 4 of Control Register 1 to a logic one, while the Receiver is disabled.

When the complete character has been shifted into the Receiver Register it is transferred to the Receiver Buffer; the unused, higher order bits are filled with logic zero's. At this time the Receiver Status bits (Framing Error/Sync Detect, Parity Error/DLE Detect, Overrun Error, and Data Received) are updated in the Status Register and the Data Received interrupt is activated. Parity Error is set, if encountered while the Receiver parity check is enabled in the Control Registers. Overrun Error is set if the Data Received status bit is not cleared through a Read operation by an external device when a new character is transferred to the Receiver Buffer. This error flag indicates that a character has been lost; new data is lost while the old data and its status flags are saved.

The characters assembled in the Receiver Register that match the content of the SYN or the DLE register are not loaded into the Receiver Buffer, and the DR interrupt is not generated, if Bit 3 of Control Register 2 (CR23) or Bit 4 of Control Register 1 (CR14) are set respectively, and SYN Detect and DLE Detect are set with the next non SYN or non DLE character. When both CR23 and CR14 are set (Transparent mode), the DLE-SYN combination is stripped. The SYN comparison occurs only with the character received after the DLE character. If two successive DLE characters are received only the first DLE character is stripped. No parity check is made while in this mode.

#### Transmitter

Information is transferred to the Transmitter Buffer by a Write operation. Information can be loaded into this register at any time, even when the Transmitter is not enabled. Transmission of data occurs only when the Request to Send bit is set to a logic 1 in Control Register 1 and the Clear To Send input is logic 0. Information is normally transferred from the Transmitter Buffer to the Transmitter Register when the latter has completed transmission of a character. However, information in the DLE register may be transferred prior to the information contained in the Transmitter Buffer if the Force DLE signal condition is enabled (Bits 5 and 6 of Control Register 1 set to a logic 1). The control bit CR15 must be set prior to loading of a new character in the Transmitter Register output passes through a flip-flop which delays the output by one clock period. When using the 1X clock generated by the Modem Data Set, the output data changes state on the negative clock transition and the delay is one bit period. When using a local 32X clock the the transmitter section selects one of the four selected rate inputs and divides the clock down to the baud rate. This clock is phased to the Transmitter Buffer Empty Flag such that transmission of characters occurs within two clock times of the loading of the Transmitter Register is empty.

When the Transmitter is enabled, a Transmitter interrupt is generated each time the Transmitter Buffer is empty. If the Transmitter Buffer is empty, when the Transmitter Register is ready for a new character, the Transmitter enters an idle state. During this idle time a logic 1 will be presented to the Transmitted Data output in the Asynchronous mode or the contents of the SYN register will be presented in the Synchronous Non-transparent mode (CR16=0). In the Synchronous Transmit Transparent mode (CR16=1), the idle state will be filled by DLE-SYN character transmission in that order. When entering the Transparent mode DLE must precede the contents of the Transmitter Buffer. This is accomplished by setting of Bit 5 of Control Register 1.

If the transmitter section is disabled by a reset of the Request to Send, any partially transmitted character is completed before the transmitter section of the ASTRO is disabled. As soon as the Clear To Send goes high the transmitted data output will go high.

When the Transmitter parity is enabled, the selected Odd or Even parity bit is inserted into the last data bit of the character in place of the last bit of the Transmitter Register. This limits transfer of character information to a maximum of seven bits plus parity or eight bits without parity. Parity cannot be enabled in the Synchronous Transparency mode.

#### Input/Output Operations

All Data, Control, and Status words are transferred over the Data Access Lines (DAL 0-7). Additional input lines provide controls for addressing a particular ASTRO, and regulating all input and output operations. Other lines provide interrupt capability to indicate to a Controller that an input operation is requested by the ASTRO. All input/output terminology below is referenced to the Controller so that a Read or input takes data from the ASTRO and places it on the DAL bus, while a Write or Output places data from the DAL bus into the ASTRO.

A Read or Write operation is initiated by the placement of an eight-bit address on the DAL bus by the Controller. When the Chip Select signal goes to a logic 0 state, the ASTRO compares Bits 7-3 of the DAL bus with its hard-wired ID code (Pins 17, 22, 24, 25, and 26) and becomes selected on a Match condition. The ASTRO then sets its RPLY line low to acknowledge its readiness to transfer data. Bit 0 must be a logic 0 in Read or Write operation. A setup time must exist between CS and the RE or WE signals to allow chip selection prior to read/write operations.

Bits 2-0 of the address are used to select ASTRO registers to read from as follows:

| Bits 2-0 | Selected Register  |

|----------|--------------------|

| 000      | Control Register 1 |

| 010      | Control Register 2 |

| 100      | Status Register    |

| 110      | Receiver Buffer    |

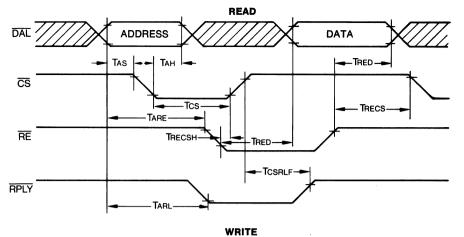

Read

When the Read Enable (RE) line is set to a logic 0 condition by the Controller the ASTRO gates the contents of the addressed register onto the DAL bus. The Read operation terminates, and the device becomes unselected, when both the Chip Select and Read Enable return to a logic 1 condition. Reading of the Receiver Buffer clears the Data Received Status bit. The data is removed from the DAL bus when the RE signal returns to the logic high state.

Write Bits 2-0 of the address are used to select ASTRO registers to be written into as follows: Bits 2-0 Selected Register

| 3its 2-0 | Selected Register    |

|----------|----------------------|

| 000      | Control Register 1   |

| 010      | Control Register 2   |

| 100      | SYN and DLE Register |

| 110      | Transmitter Buffer   |

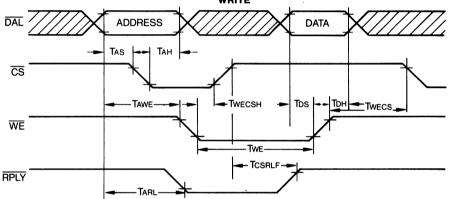

When the Write Enable (WE) line is set to a logic 0 condition by the Controller the ASTRO gates the data from the DAL bus into the addressed register. If data is written into the Transmitter Buffer, the TBMT Status bit is cleared to a logic zero.

The 100 address loads both the SYN and DLE registers. After writing into the SYN register the device is conditioned to write into the DLE if followed by another Write pulse with the 100 address. Any intervening Read or Write operation with other addresses or other ASTROs resets this condition such that the next 100 will address the SYN register.

#### Interrupts

The following conditions generate interrupts:

#### Data Received (DR)

Indicates transfer of a new character to the Receiver Buffer while the Receiver is enabled.

#### Transmitter Buffer Empty (TBMT)

Indicates that the Transmitter Buffer is empty while the Transmitter is enabled. The first interrupt occurs when the Transmitter becomes enabled if there is an empty Transmitter Buffer, or after the character is transferred to the Transmitter Register making the Transmitter Buffer empty.

**Carrier On**

Indicates Carrier Detector input goes low and the Data Terminal Ready (DTR) bit (CR10) is high. Carrier Off

Indicates Carrier Detector input goes high and the Data Terminal Ready (DTR) bit (CR10) is high. Data Set Ready On

Indicates the Data Set Ready input goes low and the Data Terminal Ready (DTR) bit (CR10) is high. Data Set Ready Off

Indicates the Data Set Ready input goes high and the Data Terminal Ready (DTR) bit (CR10) is high. Ring On

Indicates the Ring Indicator input goes low and the Data Terminal Ready (DTR) bit (CR10) is low. Each time an interrupt condition exists the INTR output from the ASTRO is made a logic low. The following interrupt procedure is then carried out even if the interrupt condition is removed.

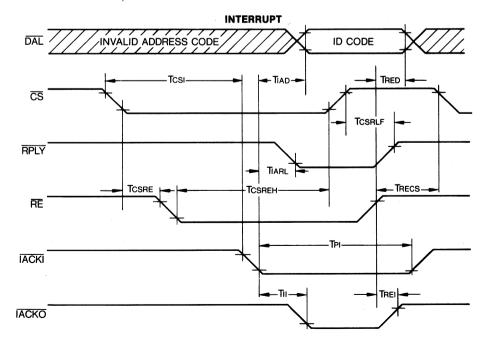

<u>The Controller acknowledges the Interrupt request by setting the Chip Select (CS) and the Interrupt</u> Acknowledge Input (IACKI) to the ASTRO to a low state. On this transition all non-interrupting devices receiving the IACKI signal set their Interrupt Acknowledge Output (IACKO) low, enabling lower priority daisy-chained devices to respond to the interrupt request. The highest priority device that is interrupting will then set its RPLY line low. This device will place its ID code on Bit Positions 7-3 of the DAL bus when a low RE signal is received. The data is removed from the DAL bus when the Read Enable (RE) signal returns to the logic one state. To reset the Interrupt condition (INTR) Chip Select (CS) and IACKI must be received by the ASTRO.

#### **Description of Pin Functions**

| Pin No.                    | Symbol                                                                   | Pin Name                                               | I/O                   | Function                                                                                                                                                                                                      |

|----------------------------|--------------------------------------------------------------------------|--------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>21<br>40<br>20        | V <sub>BB</sub><br>V <sub>CC</sub><br>V <sub>DD</sub><br>V <sub>SS</sub> | POWER SUPPLY<br>POWER SUPPLY<br>POWER SUPPLY<br>GROUND | PS<br>PS<br>PS<br>GND | <ul> <li>5 Volts</li> <li>+ 5 Volts</li> <li>+ 12 Volts</li> <li>Ground</li> </ul>                                                                                                                            |

| 23                         | MR                                                                       | MASTER RESET                                           | 1                     | The Control and Status Registers and other controls are cleared when this input is low.                                                                                                                       |

| 8-<br>15                   | DAL0-<br>DAL7                                                            | DATA ACCESS LINES                                      | 1/0                   | Eight-bit bi-directional bus used for transfer of data, control status, and address information.                                                                                                              |

| 17<br>22<br>24<br>25<br>26 | ID7<br>ID6<br>ID5<br>ID4<br>ID3                                          | SELECT CODE                                            | <br> <br> <br>        | Five input pins which when hard-wired assign the<br>device a unique identification code used to select<br>the device when addressing and used as an<br>identification when responding to interrupts.          |

| 3                          | ĊŚ                                                                       | CHIP SELECT                                            | I                     | The low logic transition of $\overline{\text{CS}}$ identifies a valid address on the DAL bus during Read and Write operations.                                                                                |

| 39                         | RE                                                                       | READ ENABLE                                            | I                     | This input, when low, gates the contents of the<br>addressed register from a selected ASTRO onto<br>the DAL bus.                                                                                              |

| 4                          | WE                                                                       | WRITE ENABLE                                           | <b>I</b> .            | This input, when low, gates the contents of the DAL<br>bus into the addressed register of a selected<br>ASTRO.                                                                                                |

| , <b>7</b>                 | INTR                                                                     | INTERRUPT                                              | 0                     | This open drain output, to facilitate WIRE-ORing,<br>goes low when any interrupt conditions<br>occur.                                                                                                         |

| 2                          | IACKI                                                                    | INTERRUPT<br>ACKNOWLEDGE IN                            | I                     | When the Controller (determining the interrupting<br>ASTRO) makes this input low, the ASTRO places<br>its ID code on the DAL bus and sets reply low if it is<br>interrupting, otherwise it makes IACKO a low. |

| 5                          | IACKO                                                                    | INTERRUPT<br>ACKNOWLEDGE OUT                           | 0                     | This output goes low in response to a low $\overline{IACKI}$ if the ASTRO is not the interrupting device.                                                                                                     |

| 6                          | RPLY                                                                     | REPLY                                                  | 0                     | This open drain output, to facilitate WIRE-ORing,<br>goes low when the ASTRO is responding to being<br>selected by an address on the DAL bus or in<br>affirming that it is the interrupting source.           |

### **Description of Pin Functions**

| Pin No.              | Symbol               | Pin Name               | I/O        | Function                                                                                                                                                                                                                                                                            |

|----------------------|----------------------|------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30<br>31<br>32<br>33 | R1<br>R2<br>R3<br>R4 | CLOCK RATES            |            | These four inputs accept four different local 32X<br>data rate Transmit and Receive clocks. The input on<br>R4 may be divided down into a 32X clock from a<br>32X, 64X, 128X, or 256X clock input. The clock used<br>in the ASTRO is selected by bits 0-2 of Control<br>Register 2. |

| 37                   | BA                   | TRANSMITTED DATA       | 0          | This output is the transmitted serial data from the ASTRO. This output is held in a Marking condition when the transmitter section is not enabled.                                                                                                                                  |

| 27                   | BB                   | RECEIVED DATA          | I ·        | This input receives serial data into the ASTRO.                                                                                                                                                                                                                                     |

| 38                   | CA                   | REQUEST TO SEND        | 0          | This output is enabled by bit 1 of Control Register 1<br>and remains in a low state during transmitted data<br>from the ASTRO.                                                                                                                                                      |

| 36                   | CB                   | CLEAR TO SEND          | I          | This input, when low, enables the transmitter section of the ASTRO.                                                                                                                                                                                                                 |

| 28                   | CC                   | DATA SET READY         | a<br>1     | This input generates an interrupt when going ON or<br>OFF while the Data Terminal Ready signal is ON.<br>It appears as bit 6 in the Status Register.                                                                                                                                |

| 16                   | CD                   | DATA TERMINAL<br>READY | 0          | This output is generated by bit 0 in Control Register<br>1 and indicates Controller readiness.                                                                                                                                                                                      |

| 18                   | CE                   | RING INDICATOR         | I<br>I     | This input from the Data Set generates an interrupt when made low with Data Terminal Ready in the OFF condition.                                                                                                                                                                    |

| 29                   | CF                   | CARRIER DETECTOR       | İ          | This input from the Data Set generates an interrupt<br>when going ON or OFF if Data Terminal Ready is<br>ON. It appears as bit 5 in the Status Register.                                                                                                                            |

| 35                   | DB                   | TRANSMITTER<br>TIMING  | , <b>1</b> | This input is the Transmitter 1X Data Rate Clock.<br>Its use is selected by bits 0-2 of Control Register 2.<br>The transmitted data changes on the negative<br>transition of this signal.                                                                                           |

| 34                   | DD                   | RECEIVER TIMING        |            | This input is the Receiver 1X Data Rate Clock. Its<br>use is selected by bits 0-2 of Control Register 2. The<br>Received Data is sampled by the ASTRO on the<br>positive transition of this signal.                                                                                 |

| 19                   | MISC                 | MISCELLANEOUS          | 0          | This output is controlled by bits 4 and 5 of Control<br>Register 1 and is used as an extra programmable<br>signal.                                                                                                                                                                  |

#### **Device Programming**

The two 8-bit Control Registers of the ASTRO determine the operative conditions of the ASTRO chip.

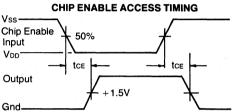

| BIT 7                                                         | 6                                                                                                                                                                                                            | 5                                                                                                                                                                                                                                                                                                                                                      | 4                                                                                                                                                                         | 3                                                                                                                                                                                           | 2                                                                      | 1                                                                     | 0                                                                            |