# Z80 MICROPROCESSOR FAMILY DATABOOK

1<sup>st</sup> EDITION

# Z80 MICROPROCESSOR FAMILY

1<sup>th</sup> EDITION

### **JANUARY 1990**

#### USE IN LIFE SUPPORT DEVICES FOR SYSTEMS MUST BE EXPRESSLY AUTHORIZED

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF SGS-THOMSON Microelectronics. As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## TABLE OF CONTENTS

| ALPHANUMERICAL INDEX       | Page  | 5   |

|----------------------------|-------|-----|

| PRODUCT GUIDE              |       | 7   |

| Z80 FAMILY OVERVIEW        |       | 8   |

| CROSS REFERENCE            |       | 9   |

| PART NUMBER IDENTIFICATION |       | 10  |

| CMOS FAMILY DATASHEETS     |       | 11  |

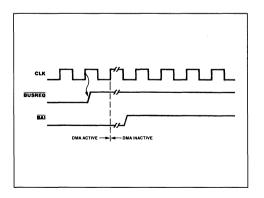

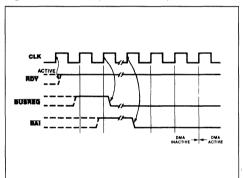

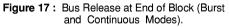

| NMOS FAMILY DATASHEETS     | · · · | 117 |

### ALPHANUMERICAL INDEX -

| Type<br>Number | Function                                 | Page<br>Number |

|----------------|------------------------------------------|----------------|

| Z84C00         | Z80C CPU CMOS Version                    | 13             |

| Z84C10         | Z80C DMA CMOS Version                    | 45             |

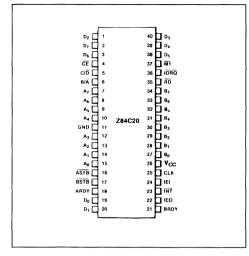

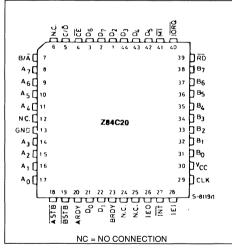

| Z84C20         | Z80C PIO CMOS Version                    | 65             |

| Z84C30         | Z80C CTC CMOS Version                    | 79             |

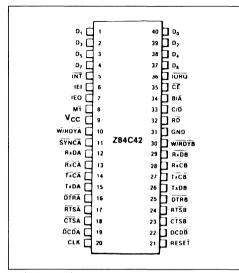

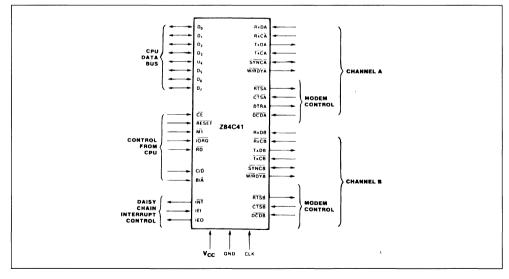

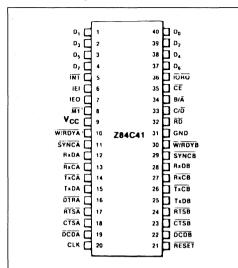

| Z84C40         | Z80C SIO CMOS Version                    | 93             |

| Z84C41         | Z80C SIO CMOS Version                    | 93             |

| Z84C42         | Z80C SIO CMOS Version                    | 93             |

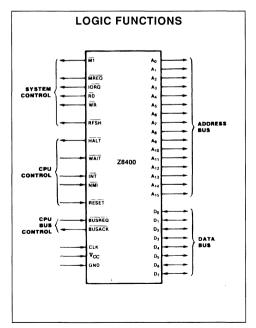

| Z8400          | Z80 CPU Control Process Unit             | 119            |

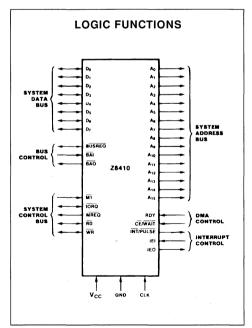

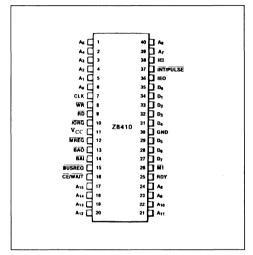

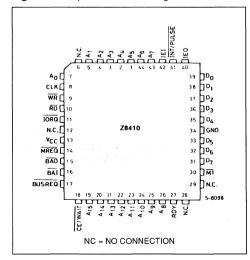

| Z8410          | Z80 DMA Direct Memory Access Central     | 153            |

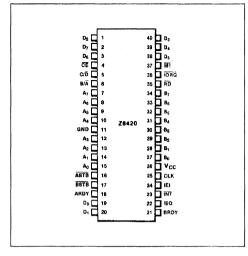

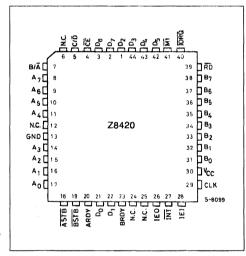

| Z8420          | Z80 PIO Parallel Input/Output Controller | 175            |

| Z8430          | Z80 CTC Counter Timer Circuit            | 191            |

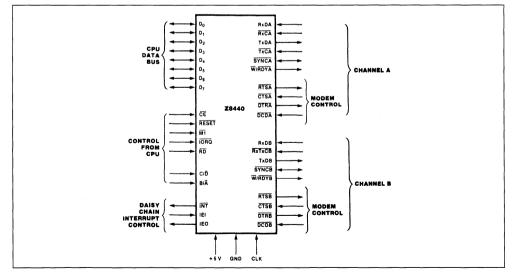

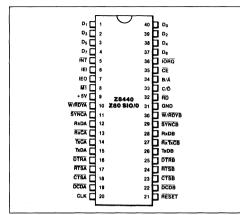

| Z8440          | Z80 SIO Serial Input/Output Controller   | 205            |

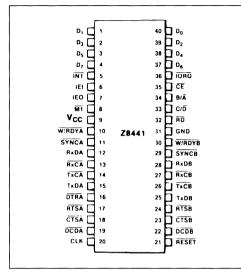

| Z8441          | Z80 SIO Serial Input/Output Controller   | 205            |

| Z8442          | Z80 SIO Serial Input/Output Controller   | 205            |

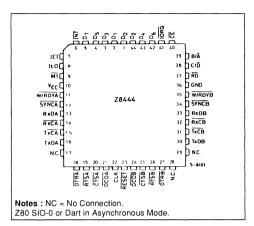

| Z8470          | Z80 DART Serial Input/Output Controller  | 225            |

## **PRODUCT GUIDE**

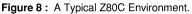

Estabilished as the industry standard, the Z80 CPU offers many features not found on comparable microprocessors: on chip refresh for dynamic memories, comprehensive bit test, reset instructions, block transfer and search instructions, two 16 bit index registers, powerful vectored interrupts and a dual register bank for fast context switching. Complementing the power of the CPU is a complete family of versatile peripheral components.

And today, with the introduction of low power CMOS versions, the Z80 is more than ever the first choice for 8-bit applications.

#### **Central Processor Unit**

The Z80 CPU features 158 instruction, software compatible whit all the 78 of the 8080A with added powerfu bit, word and string operations. Three modes of high speed interrupt including a unique vectored interrupt. Dual register sets for context switching plus two 16-bit index registers for memory reference.

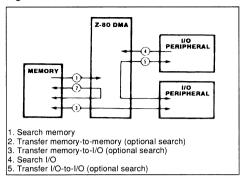

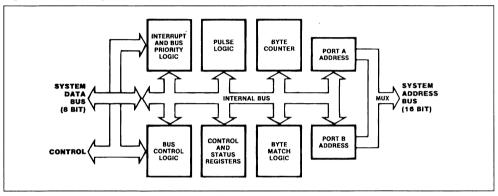

#### **Direct Memory Access**

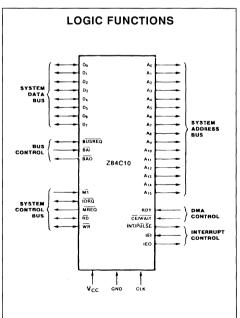

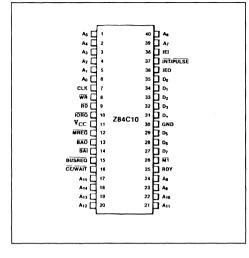

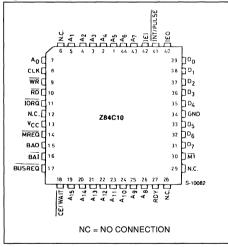

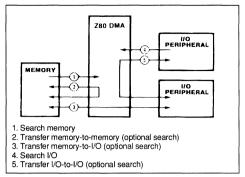

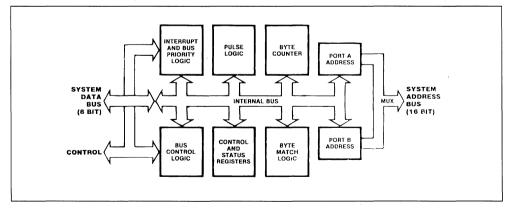

The Z80 DMA performs data transfers and searches in a wide variety of 8-bit CPU environments. It is unique among DMA's in that it takes full control of the systems address, data and control buses - and is therefore a special purpose processor - when enabled by the CPU to do so. The DMA also provides complete interfacing to the system bus.

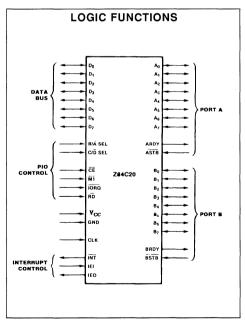

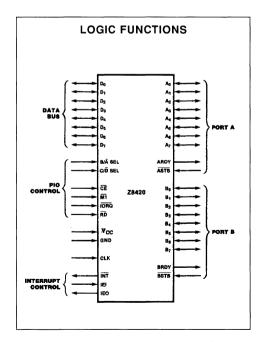

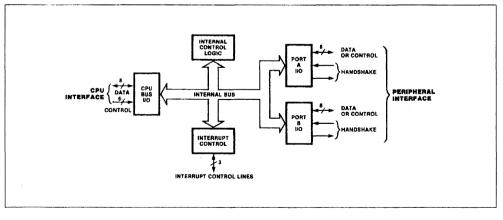

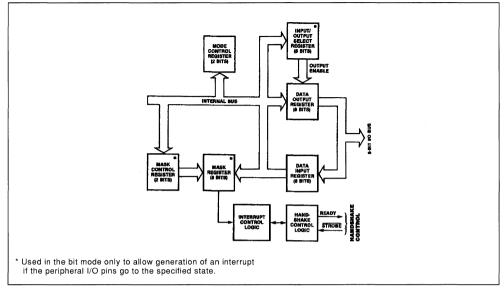

#### **Parallel Input/Output**

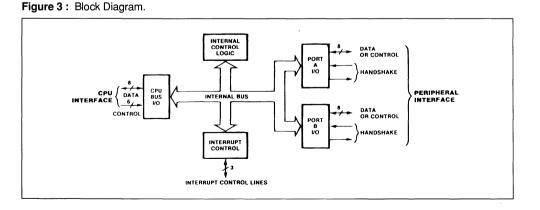

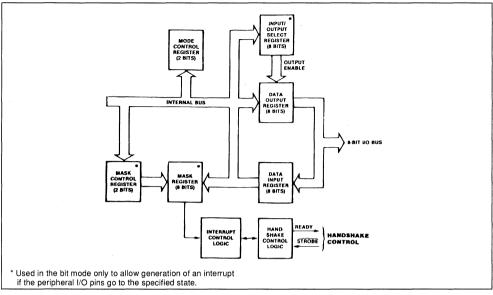

The Z80 PIO is a programmable two port device which provides a TTL compatible interface between peripheral devices and the Z80 CPU. The programmer can configure the Z80 PIO to interface with a wide range of peripheral devices with no other external logic required.

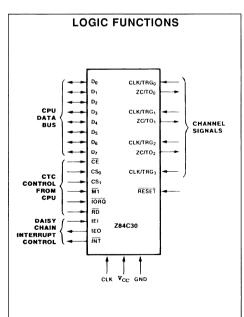

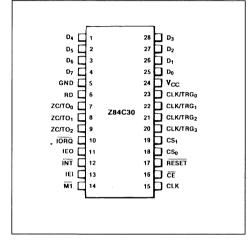

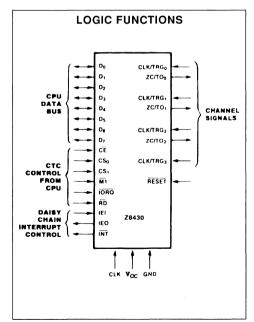

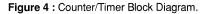

#### **Counter/Timer Circuit**

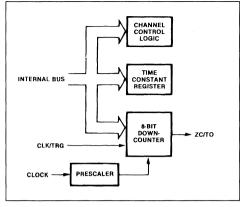

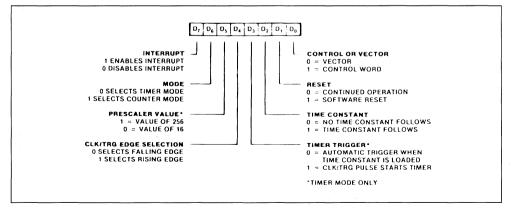

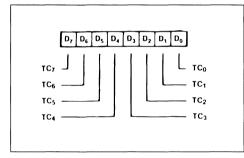

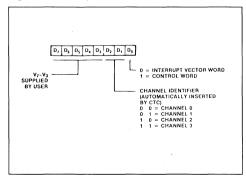

The Z80 CTC is a programmable component with four independent channel that provide counting and timing functions for microcomputer system based on the Z80 CPU.

The programmer can configure the CTC to operate under various modes to interface with a wide range of devices.

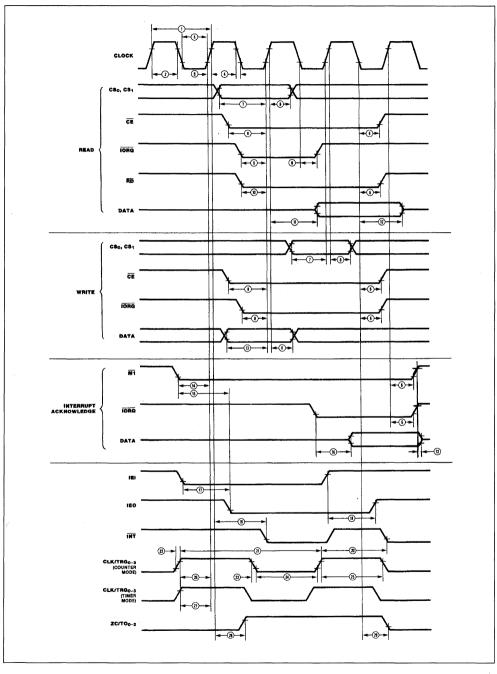

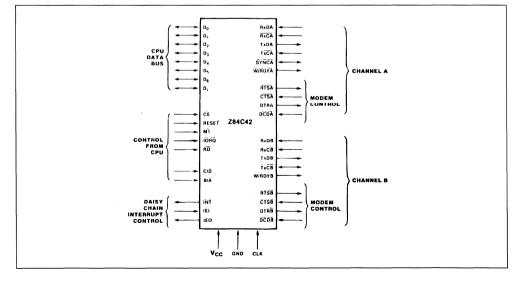

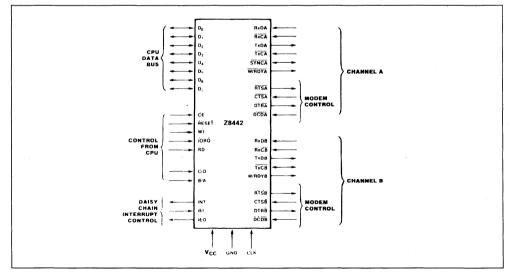

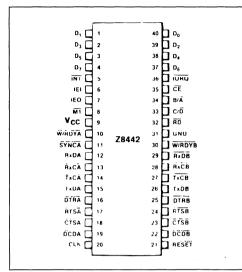

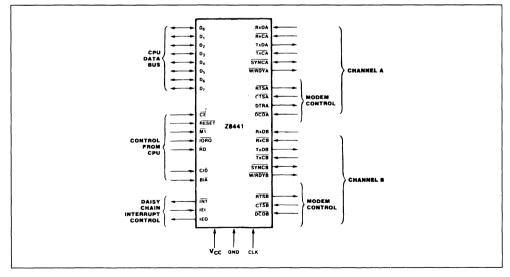

#### Serial Input/Output

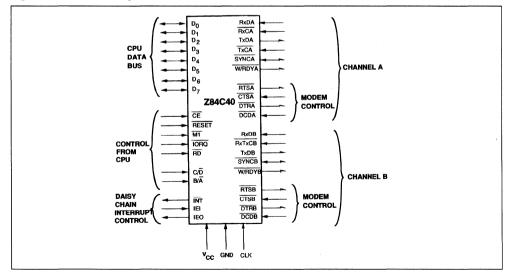

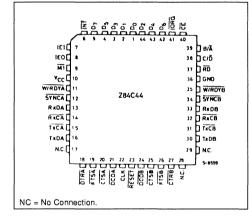

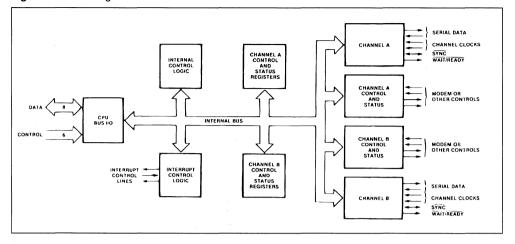

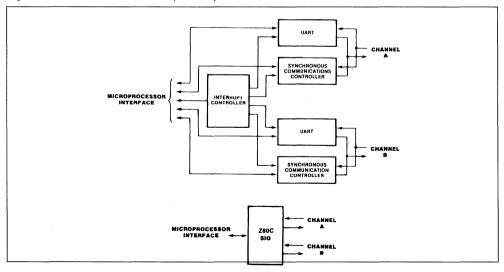

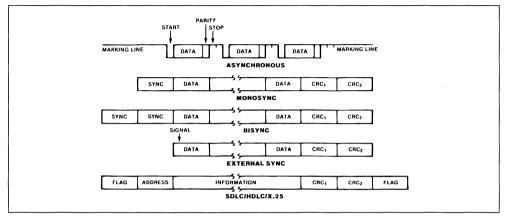

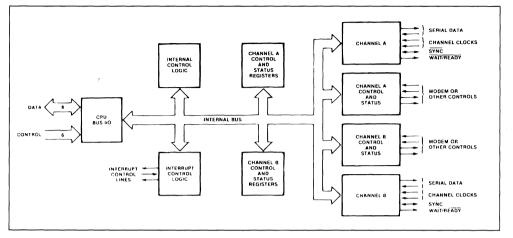

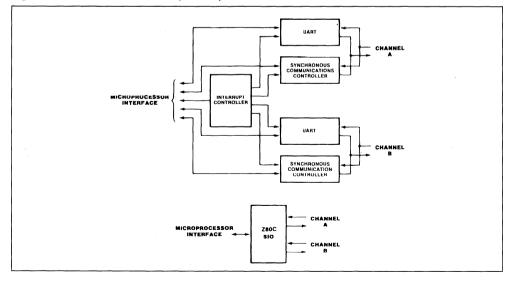

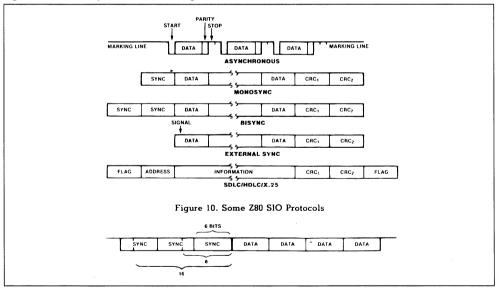

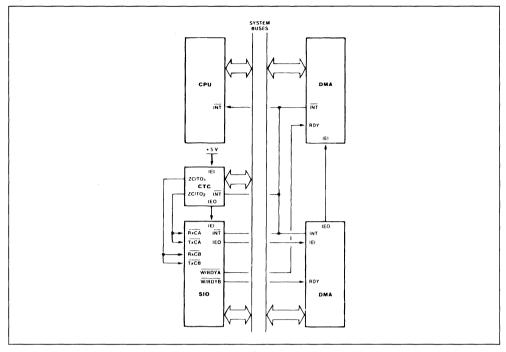

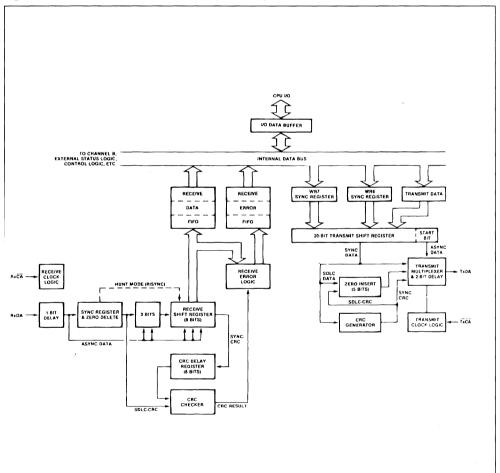

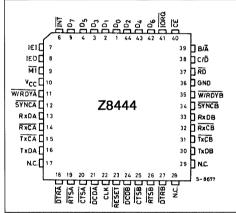

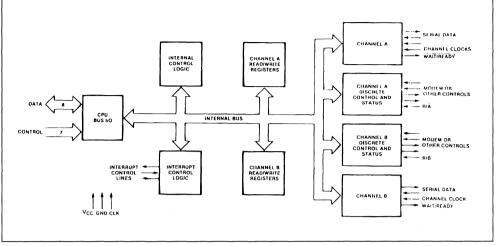

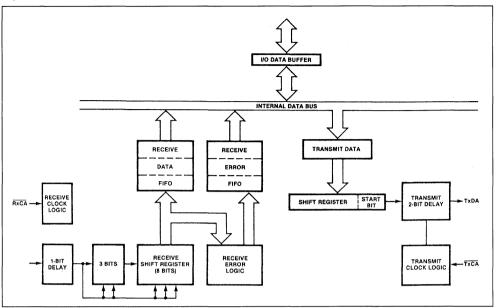

The Z80 SIO is a dual channel multi-function peripheral component designed to satisfy a wide variety of serial data communications requirements in microcomputer systems.

Its basic function is a serial-to-parallel, parallel-toserial converter/controller but within that role its personality is software configurable so that it can be optimized for a given serial data communications application.

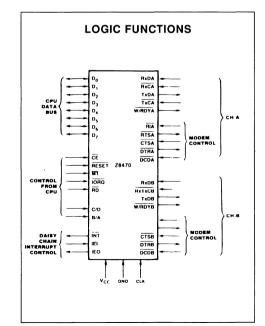

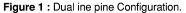

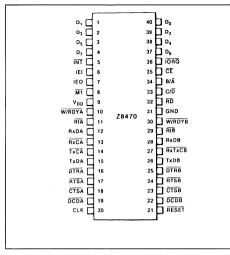

#### **Dual Asynchronous Receiver Transmitter**

The Z80 DART is a dual channel multi-function peripheral component that satisfies a wide variety of serial data communications requirements in microcomputer systems. The Z80 DART is used as a serial-to-parallel, parallel-to-serial converter/controller in asynchronous applications.

In addition it also provides modem controls for both channels.

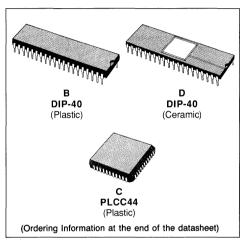

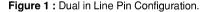

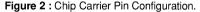

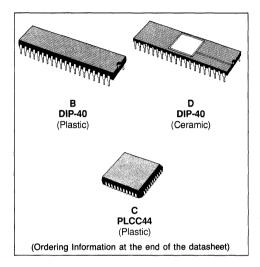

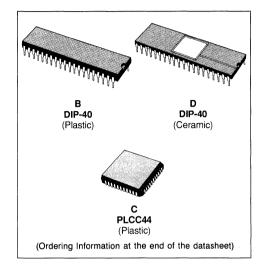

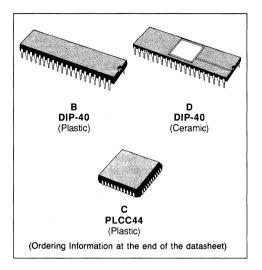

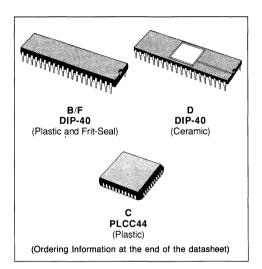

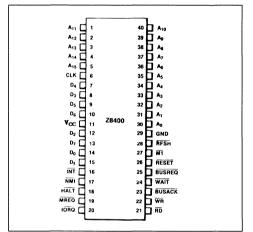

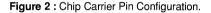

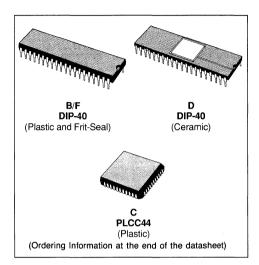

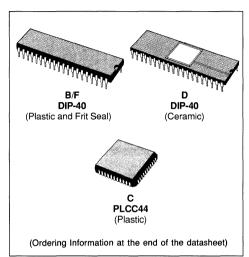

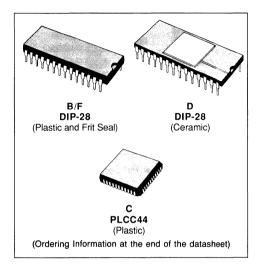

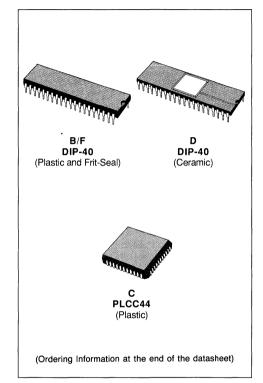

#### 4 Clock Speeds and 4 Package Types

The NMOS & CMOS family Z80 offers a wide selection of speeds with 2.5, 4, 6 and 8 MHz versions and come in plastic and ceramic dual-in-line packages as well as leaded plastic quad-in-line packages.

|             |                     |             |              | :             | SUFFIX      | DESC     | RIPT       | ION | 67 A       |    |         |              |               |  |  |  |

|-------------|---------------------|-------------|--------------|---------------|-------------|----------|------------|-----|------------|----|---------|--------------|---------------|--|--|--|

|             |                     |             |              |               |             |          |            |     |            |    | TEN     | TEMP. SUFFIX |               |  |  |  |

|             | BASE PART<br>NUMBER | SPEI<br>2.5 | ED SU<br>4.0 | FFIX (<br>6.0 | MHz)<br>8.0 | P.<br>PL | ACK/<br>FR |     | SUFF<br>PL |    | 0/+70°C | - 40/ + 85°C | - 55/ + 125°C |  |  |  |

| SGS-THOMSON | Z84XX               | *           | Α            | в             | н           | В        | F          | D   | С          | na | 1       | 6            | 2             |  |  |  |

| ZILOG       | Z084XX              | na          | 04           | 06            | 08          | Р        | D          | С   | ۷          | L  | s       | Е            | М             |  |  |  |

| SGS-THOMSON | Z84CXX              | na          | A            | в             | н           | в        | na         | D   | С          | na | na      | 6            | 2             |  |  |  |

| TOSHIBA     | TMPZ84XX            | na          | *            | -6            | - 8         | P        | na         | na  | т          | na | na      | *            | na            |  |  |  |

| ZILOG       | Z084CXX             | na          | 04           | 06            | 08          | P        | D          | С   | V          | L  | S       | Е            | м             |  |  |  |

| SHARP       | LH508X              | na          | *            | na            | na          | *        | na         | na  | na         | na | na      | *            | na            |  |  |  |

| NEC         | $\mu$ PD70008AXX    | na          | -4           | -6            | - 8         | *        | na         | na  | na         | na | na      | *            | na            |  |  |  |

|             |               |               | DEVIC         | Е ТҮРЕ        |                   |              |

|-------------|---------------|---------------|---------------|---------------|-------------------|--------------|

|             | CPU           | DMA           | PIO           | стс           | SIO               | DART         |

| SGS-THOMSON | <b>Z8400</b>  | <b>Z8410</b>  | <b>Z8420</b>  | <b>Z8430</b>  | <b>Z8440/1/2</b>  | <b>Z8470</b> |

| ZILOG       | Z08400        | Z08410        | Z08420        | Z08430        | Z08440/1/2        | na           |

| SGS-THOMSON | <b>Z84C00</b> | <b>Z84C10</b> | <b>Z84C20</b> | <b>Z84C30</b> | <b>Z84C40/1/2</b> | na           |

| TOSHIBA     | TMPZ84C00     | TMPZ84C10     | TMPZ84C20     | TMPZ84C30     | TMPZ84C40/1/2     | na           |

| ZILOG       | Z084C00       | Z084C10       | Z084C20       | Z084C30       | Z084C40/1/2       | na           |

| SHARP       | LH5080        | LH5083        | LH5081        | LH5082        | na                | na           |

| NEC         | μPD70008A     | na            | na            | na            | na                | na           |

Notes: \* Standard Version - No suffix required na: Not Available

#### PART NUMBER IDENTIFICATION

| Circuit Designa                                         | ator                         | <br>Example: | Z8400 | A B 1 |

|---------------------------------------------------------|------------------------------|--------------|-------|-------|

| No letter<br>A<br>B<br>H                                | 2.5 MHz<br>4.0<br>6.0<br>8.0 |              |       |       |

| Package                                                 |                              | <br>         |       |       |

| B Plastic<br>D Ceramic<br>F Frit-Seal<br>C Leaded Plast | tic - Chip Carrier           |              |       |       |

| Temperature R                                           | ange                         |              |       |       |

- 1

- 0 to + 70°C -40 to + 85°C -55 to + 125°C 6 2

# **CMOS FAMILY DATASHEETS**

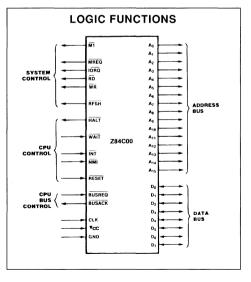

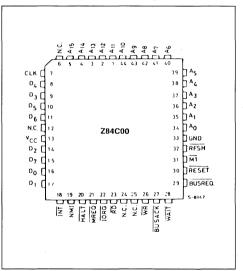

### Z84C00

THE INSTRUCTION SET CONTAINS 158 IN-STRUCTIONS. THE 78 INSTRUCTIONS OF THE 8080A ARE INCLUDED AS A SUBSET; 8080A AND Z80 SOFTWARE COMPATIBILITY IS MAINTAINED

SGS-THOMSON MICROELECTRONICS

- 8 MHz, 6 MHz AND 4 MHz CLOCKS FOR THE Z80CH, Z80CB AND Z80CA, THE Z80C CPU, RESULT IN RAPID INSTRUCTION EXECU-TION WITH CONSEQUENT HIGH DATA THROUGHPUT

- THE EXTENSIVE INSTRUCTION SET IN-CLUDES STRING, BIT, BYTE, AND WORD OPERATIONS. BLOCK SEARCHES AND BLOCK TRANSFERS TOGETHER WITH IN-DEXED AND RELATIVE ADDRESSING RE-SULT IN THE MOST POWERFUL DATA HANDLING CAPABILITIES IN THE MICRO-COMPUTER INDUSTRY

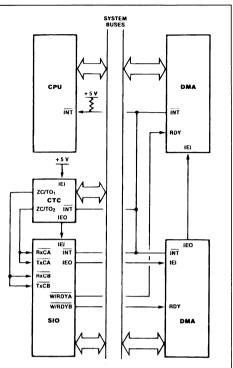

- THE Z80C MICROPROCESSORS AND ASSO-CIATED FAMILY OF PERIPHERAL CONTROL-LERS ARE LINKED BY A VECTORED INTERRUPT SYSTEM. THIS SYSTEM MAY BE DAISY-CHAINED TO ALLOW IMPLEMENTA-TION OF A PRIORITY INTERRUPT SCHEME. LITTLE, IF ANY, ADDITIONAL LOGIC IS RE-QUIRED FOR DAISY-CHAINING

- DUPLICATE SETS OF BOTH GENERAL-PUR-POSE AND FLAG REGISTERS ARE PRO-VIDED. EASING THE DESIGN AND OPERATION OF SYSTEM SOFTWARE THROUGH SINGLE-CONTEXT SWITCHING. BACKGROUND-FOREGROUND PRO-GRAMMING, AND SINGLE-LEVEL INTER-RUPT PROCESSING. IN ADDITION. TWO 16-BIT INDEX REGISTERS FACILITATE PRO-GRAM PROCESSING OF TABLES AND AR-BAYS

- THERE ARE THREE MODES OF HIGH SPEED INTERRUPT PROCESSING : 8080 SIMILAR, NON-Z80 PERIPHERAL DEVICE, AND Z80 FAMILY PERIPHERAL WITH OR WITHOUT DAISY CHAIN

- ON-CHIP DYNAMIC MEMORY REFRESH COUNTER

- SINGLE 5 V ± 10 % POWER SUPPLY

- LOW POWER CONSUMPTION :

- 9 mA TYP. AT 4 MHz

- \_ 15 mA TYP. AT 6 MHz

September 1988

### Z80C CPU CMOS VERSION

- \_ 20 mA TYP. AT 8 MHz

- LESS THAN 10  $\mu\text{A}$  IN POWER DOWN MODE

- EXTENDED OPERATING TEMPERATURE

40 °C TO + 85 °C

1/32

#### DESCRIPTION

Z80 CMOS Family is fabricated using SGS-THOM-SON' CMOS Silicon Gate Technology, which provides low power operation and high performance.

The Z80C CPU is third-generation single-chip microprocessors with exceptional computational power. They offer higher system throughput and more efficient memory utilization than comparable second-and third-generation microprocessors. The internal registers contain 208 bits of read/write memory that are accessible to the programmer. These registers include two sets of six general-purpose registers which may be used individually as either 8-bit registers or as 16-bit register pairs. In addition, there are two sets of accumulator and flag registers. A group of "Exchange" instructions makes either set of main or alternate registers accessible

to the programmer. The alternate set allows operation in foreground-background mode or it may be reserved for very fast interrupt response.

The Z80C also contains a Stack Pointer, Program Counter, two index registers, a Refresh register (counter), and an Interrupt register.

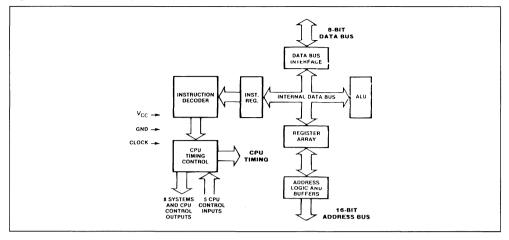

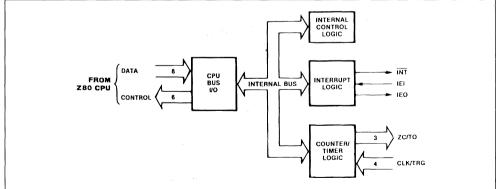

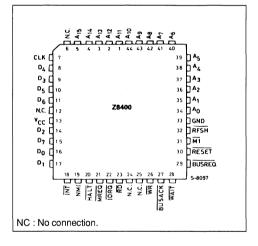

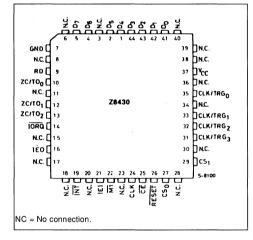

The CPU is easy to incorporate into a system since it requires only a single + 5 V power source, all output signals are fully decoded and timed to control standard memory or peripheral circuits, and is supported by an extensive family of peripheral controllers. The internal block diagram (figure 3) shows the primary functions of the Z80C processors. Subsequent text provides more detail on the Z80C I/O controller family, registers, instruction set, interrupts and daisy chaining, and CPU timing.

#### Figure 3 : CPU Block Diagram.

#### **CPU REGISTERS**

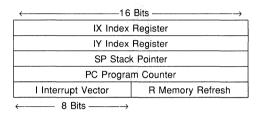

Figure 4 shows three groups of registers within the CPU. The first group consists of duplicate sets of 8-

Figure 4 : CPU Registers.

Main Register Set

# (designated by '[prime], e.g., A'). Both sets consist

bit registers : a principal set and an alternate set

| A Accumulator     | F Flag Register   | A' Accumulator     | F' Flag Register   |

|-------------------|-------------------|--------------------|--------------------|

| B General Purpose | C General Purpose | B' General Purpose | C' General Purpose |

| D General Purpose | E General Purpose | D' General Purpose | E' General Purpose |

| H General Purpose | L General Purpose | H' General Purpose | L' General Purpose |

| ←16                | Bits —→          |  |  |  |  |  |  |  |

|--------------------|------------------|--|--|--|--|--|--|--|

| IX Index Register  |                  |  |  |  |  |  |  |  |

| IY Index Register  |                  |  |  |  |  |  |  |  |

| SP Stac            | k Pointer        |  |  |  |  |  |  |  |

| PC Progra          | im Counter       |  |  |  |  |  |  |  |

| I Interrupt Vector | R Memory Refresh |  |  |  |  |  |  |  |

| ← 8 Bits           |                  |  |  |  |  |  |  |  |

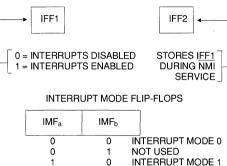

#### INTERRUPT FLIP-FLOPS STATUS

#### INTERRUPT MODE FLIP-FLOPS

| IMFa | IMFb |                  |

|------|------|------------------|

| 0    | 0    | INTERRUPT MODE 0 |

| 0    | 1    | NOT USED         |

| 1    | 0    | INTERRUPT MODE 1 |

| 1    | 1    | INTERRUPT MODE 2 |

of the Accumulator Register, the Flag Register, and six general-purpose registers. Transfer of data between these duplicate sets of registers is accomplished by use of "Exchange" instructions. The result is faster response to interrupts and easy, efficient implementation of such versatile programming techniques as background-foreground data processing. The second set of registers consists of six registers with assigned functions. These are the I (Interrupt Register), the R (Refresh Register), the IX and IY (Index Registers), the SP (Stack Pointer), and the PC (Program Counter). The third group consists of two interrupt status flip-flops, plus and additional pair of flip-flops which assists in identifying the interrupt mode at any particular time. Table 1 provides further information on these registers.

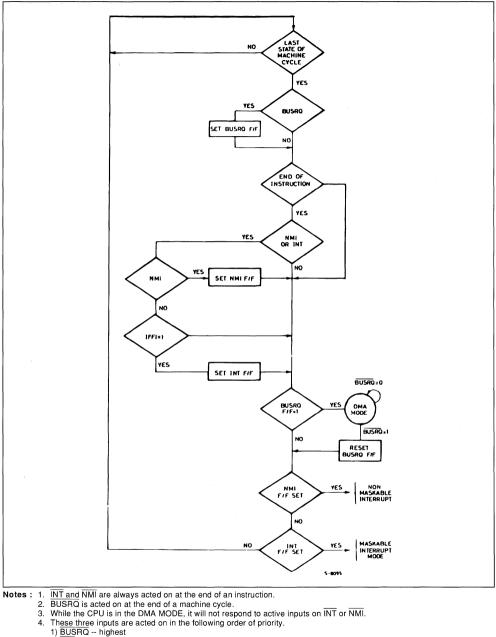

#### INTERRUPTS : GENERAL OPERATION

The <u>CPU</u> accepts two interrupt input signals : NMI and INT. The NMI is a <u>non</u>-maskable interrupt and has the highest priority. INT is a lower priority interrupt and it requires that interrupts be enabled in software in order to operate. INT can be connected to multiple peripheral devices in a wired-OR configuration. The Z80C has a single response mode for interrupt service for the <u>non</u>-maskable interrupt. The maskable interrupt, INT, has three programmable response modes available.

These are :

- Mode 0 compatible with the 8080 microprocessor.

- Mode 1 Peripheral Interrupt service, for use with non-8080/Z80 systems.

- Mode 2 a vectored interrupt scheme, usually daisy-chained, for use with Z80 Family and compatible peripheral devices.

The <u>CPU</u> services interrupts by sampling the NMI and INT signals at the rising edge of the last clock of an instruction. Further interrupt service processing depends upon the type of interrupt that was detected. Details on interrupt responses are shown in the CPU Timing Section.

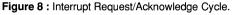

#### NON-MASKABLE INTERRUPT (NMI)

The non-maskable interrupt cannot be disabled by program control and therefore will be accepted at all times by the CPU. NMI is usually reserved for servicing only the highest priority type interrupts, such as that for orderly shut-down after power failure has been detected.

|                                    | Register           | Size (Bits) | Remarks                                                                      |

|------------------------------------|--------------------|-------------|------------------------------------------------------------------------------|

| A, A'                              | Accumulator        | 8           | Stores an Operand or the Results of an Operation                             |

| , F, F'                            | Flags              | 8           | See Instruction Set.                                                         |

| B, B'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with C.                       |

| C, C'                              | General Purpose    | 8           | See B, above.                                                                |

| D, D'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with E.                       |

| E, E'                              | General Purpose    | 8           | See D, above.                                                                |

| H, H'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with L.                       |

| L, L'                              | General Purpose    | 8           | See H, above.                                                                |

|                                    | L.                 |             | Note : The (B, C), (D, E), and (H, L) sets are combined as                   |

|                                    |                    |             | follows :                                                                    |

|                                    |                    |             | B-High Byte C-Low Byte                                                       |

|                                    |                    |             | D-High Byte E-Low Byte                                                       |

|                                    |                    |             | H–High Byte L–Low Byte                                                       |

|                                    | Interrupt Register | 8           | Stores upper eight bits of memory address for vectored interrupt processing. |

| B                                  | Refresh Register   | 8           | Provides user-transparent dynamic memory refresh. Lower                      |

|                                    | The register       | Ŭ           | seven bits are automatically incremented and all eight are                   |

|                                    |                    |             | placed on the address bus during each instruction fetch                      |

|                                    |                    |             | cycle refresh time.                                                          |

| IX                                 | Index Register     | 16          | Used for indexed addressing.                                                 |

| IY                                 | Index Register     | 16          | Same as IX, above.                                                           |

| SP                                 | Stack Pointer      | 16          | Holds address of the top of the stack. See Push or Pop in                    |

|                                    |                    |             | Instruction Set.                                                             |

| PC                                 | Program Counter    | 16          | Holds address of next instruction.                                           |

| IFF <sub>1</sub> –IFF <sub>2</sub> | Interrupt Enable   | Flip-Flops  | Set or reset to indicate interrupt status (see figure 4).                    |

| IMFa–IMFb                          | Interrupt Mode     | Flip-Flops  | Reflect Interrupt Mode (see figure 4).                                       |

#### Table 1. CPU Registers

4/32

<u>After</u> recognition of the NMI signal (providing BUS-REQ is not active), the CPU jumps to restart location 0066H. Normally, software starting at this address contains the interrupt service routine.

#### MASKABLE INTERRUPT (INT)

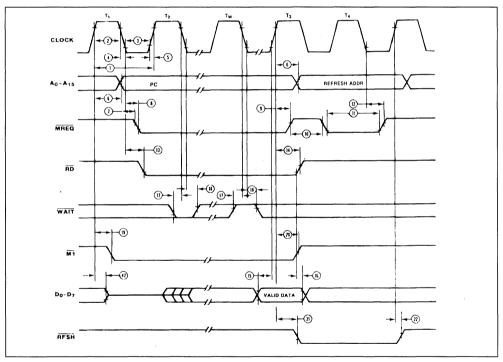

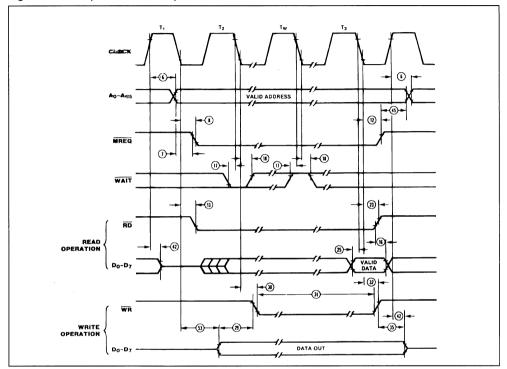

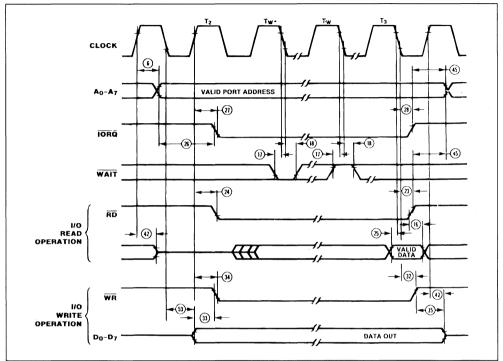

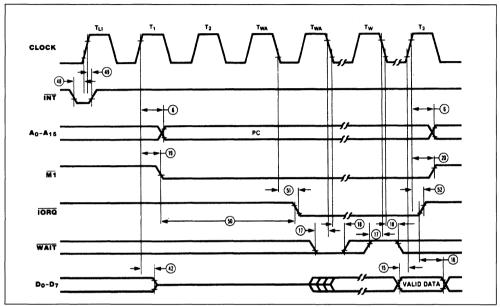

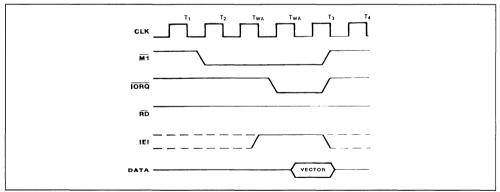

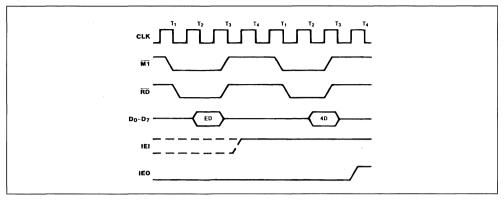

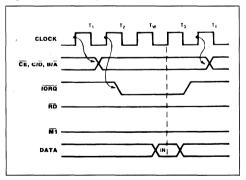

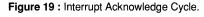

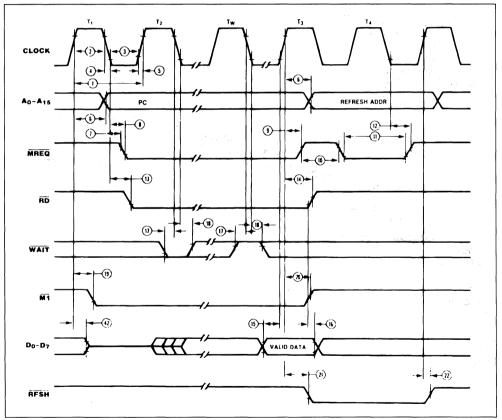

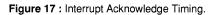

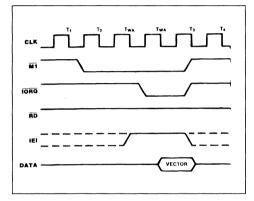

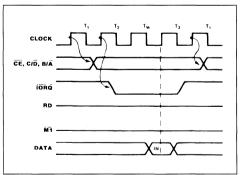

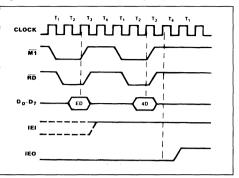

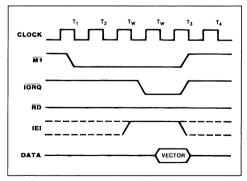

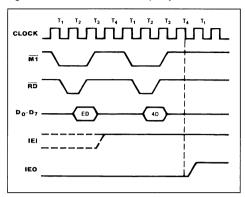

Regardless of the interrupt mode set by the user, the Z80C response to a maskable interrupt input follows a common timing cycle. After the interrupt has been detected by <u>the CPU</u> (provided that interrupts are enabled and BUSREQ is not active) a special interrupt processing cycle begins. This is a special fetch (MI) cycle in Which IORQ becomes active rather than MREQ, as in normal M1 cycle.

In addition, this <u>special</u> M1 cycle is automatically extended by two WAIT states, to allow for the time required to acknowledge the interrupt request.

#### MODE 0 INTERRUPT OPERATION

This mode is similar with the 8080 microprocessor interrupt service procedures. The interrupting device places an instruction on the data bus.

This is normally a Restart Instruction, which will initiate a call to the selected one of eight restart locations in page zero of memory. Unlike the 8080, the Z80 CPU responds to the Call instruction with only one interrupt acknowledge cycle followed by two memory read cycles.

#### MODE 1 INTERRUPT OPERATION

Mode 1 operation is very similar to that for the  $\overline{\text{NMI}}$ . The principal difference is that the Mode 1 interrupt has a restart location of 0038H only.

#### MODE 2 INTERRUPT OPERATION

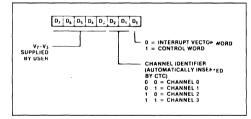

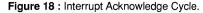

This interrupt mode has been designed to utilize most effectively the capabilities of the Z80C microprocessor and its associated peripheral family. The interrupting peripheral device selects the starting address of the interrupt service routine. It does this by placing an 8-bit vector on the data bus during the interrupt acknowledge cycle. The CPU forms a pointer using this byte as the lower 8-bits and the contents of the I register as the upper 8-bits. This points to an entry in a table of addresses for interrupt service routines. The CPU then jumps to the routine at that address. This flexibility in selecting the interrupt service routine address allows the peripheral device to use several different types of service routines.

These routines may be located at any available location in memory. Since the interrupting device supplies the low-order byte of the 2-byte vector, bit 0  $(A_0)$  must be a zero.

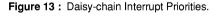

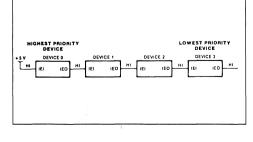

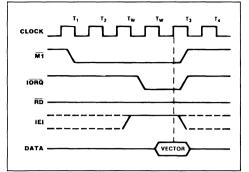

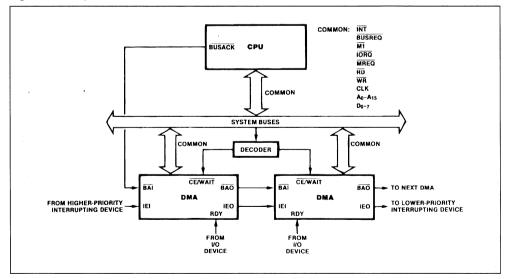

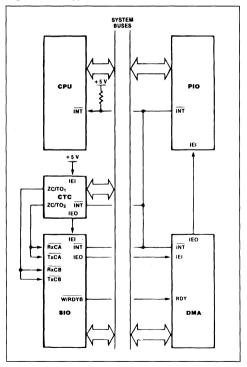

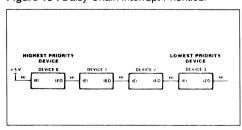

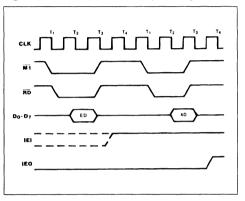

INTERRUPT PRIORITY (Daisy Chaining and Nested Interrupts).

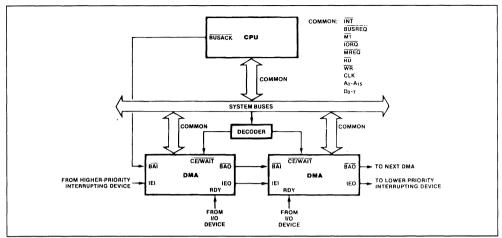

The interrupt priority of each peripheral device is determined by its physical location within a daisychain configuration. Each device in the chain has an interrupt enable input line (IEI) and an interrupt enable output line (IEO), which is fed to the next lower priority device. The first device in the daisy chain has its IEI input hardwired to a High level. The first device has highest priority, while each succeding device has a corresponding lower priority. This arrangement permits the CPU to select the highest priority interrupt from several simultaneously interrupting peripherals.

The interrupting device disables its IEO line to the next lower priority peripheral until it has been serviced. After servicing, its IEO line is raised, allowing lower priority peripherals to demand interrupt servicing.

The Z80C CPU will nest (queue) any pending interrupts or interrupts received while a selected peripheral is being serviced.

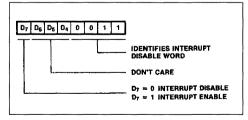

#### INTERRUPT ENABLE/DISABLE OPERATION

Two flip-flops,  $IFF_1$  and  $IFF_2$ , referred to in the register description are used to signal the CPU interrupt status. Operation of the two flip-flops is described in table 2. For more details, refer to the *Z80 CPU Technical Manual.*

#### Table 2. State of Flip-Flops

| Action                           | IFF <sub>2</sub> | IFF2             | Comments                                      |

|----------------------------------|------------------|------------------|-----------------------------------------------|

| CPU Reset                        | 0                | 0                | Maskable Interrupt<br>INT Disabled            |

| DI Instruction<br>Execution      | 0                | 0                | Maskable Interrupt                            |

| El Instruction<br>Execution      | 1                | <u>,</u> 1       | Maskable Interrupt<br>INT Enabled             |

| LD A, I Instruction<br>Execution | •                | •                | $IFF_2 \to Parity\ Flag$                      |

| LD A, R Instruction<br>Execution | •                | •                | $IFF_2 \to Parity\ Flag$                      |

| Accept NMI                       | 0                | IFF <sub>1</sub> | $IFF_1 \rightarrow IFF_2$<br>(maskable        |

|                                  |                  |                  | interrupt<br>INT disabled)                    |

| RETN Instruction<br>Execution    | IFF <sub>2</sub> | •                | $IFF_2 \rightarrow IFF_1$ at<br>Completion of |

|                                  |                  |                  | an MI Service<br>Routine.                     |

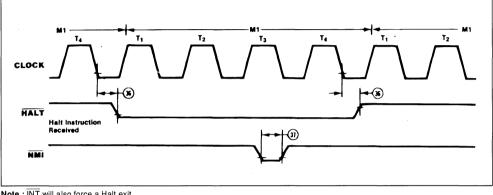

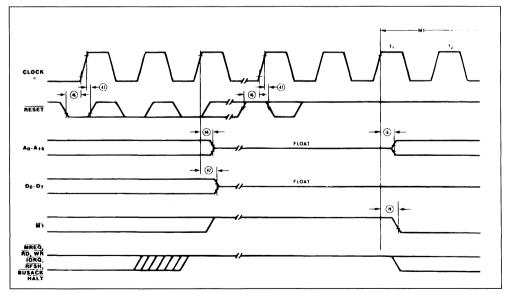

#### CPU INTERRUPT SEQUENCE

- 2) <u>NM</u>I

- 3) INT -- lowest.

#### INSTRUCTION SET

The Z80C microprocessor has one of the most powerful and versatile instruction sets available in any 8-bit microprocessor. It includes such unique operations as a block move for fast, efficient data transfers within memory or between memory and I/O. It also allows operations on any bit in any location in memory.

The following is a summary of the Z80C instruction set and shows the assembly language mnemonic, the operation, the flag status, and gives comments on each instruction. The *Z80 CPU Technical Manual and Z80 CPU Programming Manual* contain significantly more details for programming use.

The instructions are divided into the following categories :

- 8-BIT LOADS

- 16-BIT LOADS

- EXCHANGES, BLOCK TRANSFERS, AND SEARCHES

- 8-BIT ARITHMETIC AND LOGIC OPERATIONS

- GENERAL-PURPOSE ARITHMETIC AND CPU CONTROL

- 16-BIT ARITHMETIC OPERATIONS

- ROTATES AND SHIFT

- BIT SET, RESET, AND TEST OPERATIONS

- JUMPS

- CALLS, RETURNS, AND RESTARTS

- INPUT AND OUTPUT OPERATIONS

A variety of addressing modes are implemented to permit efficient and fast data transfer between various registers, memory locations, and input/output devices. These addressing modes include :

- Immediate

- Immediate extended

- Modified page zero

- Relative

- Extended

- Indexed

- Register

- Register indirect

- Implied

- Bit

|                  | Symbolic                     |    |          |            | F | lag | s   |            |    | 0  | pcod       | de         |     | N° of | N° of       | N° of       |     |          |  |

|------------------|------------------------------|----|----------|------------|---|-----|-----|------------|----|----|------------|------------|-----|-------|-------------|-------------|-----|----------|--|

| Symbol           | Operation                    | s  | z        |            | н |     | P/V | N          | с  | 76 | 543        | 210        | Hex | Bytes | M<br>Cycles | T<br>States | Cor | Comments |  |

| ADD HL, ss       | $HL \leftarrow HL + ss$      | •  | •        | X          | Х | Х   | •   | 0          | \$ | 00 | ss1        | 001        |     | 1     | 3           | 11          | SS  | Reg.     |  |

| ADC HL, ss       | $HL \leftarrow HL + ss + CY$ | 1  | 1        | X          | X | X   | V   | 0          | 1  | 11 | 101        |            | ED  | 2     | 4           | 15          | 00  | BC       |  |

|                  |                              |    |          |            |   |     |     |            |    | 01 |            | 010        |     |       |             |             | 01  | DE       |  |

| SBC HL, ss       | $HL \leftarrow HL + ss - CY$ | \$ | 1        | X          | X | X   | V   | 1          | \$ | 11 | 101        |            | ED  | 2     | 4           | 15          | 10  | IX       |  |

| ADD IX, pp       | $IX \leftarrow + pp$         |    |          | <b>.</b>   | x | v   |     | 0          | t  | 01 | ssu<br>011 | 010<br>101 | DD  | 2     | 4           | 15          | 11  | SP       |  |

| ADD IX, pp       | ix ← + hh                    | ľ  | <b> </b> | ^          | ^ | ^   | •   | 0          | +  | 01 | pp1        |            | 00  | 2     | 4           | 15          | рр  | Reg.     |  |

| ADD IY, rr       | $IY \leftarrow IY + rr$      |    |          | x          | x | x   |     | 0          | t  | 11 | 111        |            | FD  | 2     | 4           | 15          | 00  | BC       |  |

|                  |                              |    |          |            |   |     |     | -          | 1  | 00 |            | 001        |     | _     |             |             | 01  | DE       |  |

| INC ss           | $ss \leftarrow ss + 1$       | •  | •        | Х          | • | X   | •   | •          | •  | 00 | ss0        | 011        |     | 1     | 1           | 6           | 10  | IX       |  |

| INC IX           | $IX \leftarrow IX + 1$       | •  | •        | X          | • | X   | •   | а <b>•</b> | •  | 11 | 011        |            | DD  | 2     | 2           | 10          | 11  | SP       |  |

|                  |                              |    |          |            |   |     |     |            |    | 00 | 100        |            | 23  |       |             |             | rr  | Reg.     |  |

| INC IY           | $IY \leftarrow IY + 1$       | •  | •        | X          | • | X   | •   | •          | •  | 11 | 111        |            | FD  | 2     | 2           | 10          | 00  | BC       |  |

| DEC ss           | ss ↔ ss - 1                  |    |          | x          |   | x   |     |            | .  | 00 | 100<br>ss1 |            | 23  | 1     | 1           | 6           | 01  | DE       |  |

| DEC SS<br>DEC IX | $IX \leftarrow IX - 1$       |    | .        | Ŷ          |   | x   | :   |            |    | 11 | 011        |            | DD  | 2     | 2           | 10          | 10  | ĪY       |  |

|                  |                              |    |          | $ ^{\sim}$ |   |     |     |            |    | 00 | 101        |            | 2B  | 2     | -           |             | 11  | SP       |  |

| DEC IY           | $ Y \leftarrow  Y - 1 $      |    |          | x          |   | x   | •   |            |    | 11 | 111        | -          | FD  | 2     | 2           | 10          |     |          |  |

|                  |                              |    |          |            |   |     |     |            |    | 00 | 101        | 011        | 2B  | , I   |             |             |     |          |  |

Notes: ss is any of the register pairs BC, DE, HL, SP. pp is any of the register pairs BC, DE, IX, SP.

rr is any of the register pairs BC, DE, IY, SP.

7/32

#### 16-BIT ARITHMETIC GROUP

#### Z84C00

#### **INSTRUCTION SET** (continued)

#### 8-BIT LOAD GROUP

|                                        | Symbolic                                                                                   |    |    |             | F | lag         | S   |   |   | 0                     | рсо                    | de                                                                                      |                | N° of       | N° of       | N° of        |                                  |

|----------------------------------------|--------------------------------------------------------------------------------------------|----|----|-------------|---|-------------|-----|---|---|-----------------------|------------------------|-----------------------------------------------------------------------------------------|----------------|-------------|-------------|--------------|----------------------------------|

| Symbol                                 | Operation                                                                                  | s  | z  |             | н |             | P/V | N | с | 76                    | 543                    | 210                                                                                     | Hex            | Bytes       | M<br>Cycles | T<br>States  | Comments                         |

| LD r, r'<br>LD r, n                    | r ← r'<br>r ← n                                                                            | •  | •  | x<br>x      | • | X<br>X      | •   | • | • | 01<br>00<br>←         | r<br>r<br>n            | r'<br>110<br>→                                                                          |                | 1<br>2      | 1<br>2      | 4<br>7       | r, r' Reg.<br>000 B<br>001 C     |

| LD r, (HL)<br>LD r, (IX+d)             | $r \leftarrow (HL)$<br>$r \leftarrow (IX + d)$                                             | •  | •  | x<br>x      | • | x<br>x      | •   | • | • | 01<br>11<br>01<br>←   | r<br>011<br>r<br>d     | 110<br>101<br>101<br>→                                                                  | DD             | 1<br>3      | 2<br>5      | 7<br>19      | 010 D<br>011 E<br>100 H<br>101 L |

| LD r, (IY+d)                           | r ← (IY + d)                                                                               | •  | •  | х           | • | x           | •   | • | • | 11<br>01<br>←         | 111<br>r<br>d          | 101<br>110<br>→                                                                         | FD             | 3           | 5           | 19           | 111 A                            |

| LD(HL), r<br>LD(IX+d), r               | $(HL) \leftarrow r$<br>$(IX + d) \leftarrow r$                                             | •  | •  | x<br>x      | • | x<br>x      | •   | • | • | 01<br>11<br>01<br>←   | 110<br>011<br>110<br>d | r<br>101<br>r<br>→                                                                      | DD             | 1<br>3      | 2<br>5      | 7<br>19      |                                  |

| LD(IY+d), r                            | $(IY + d) \leftarrow r$                                                                    | •  | •  | х           | • | x           | •   | • | • | 11<br>01<br>←         | 110                    | 101<br>r<br>→                                                                           | FD             | 3           | 5           | 19           |                                  |

| LD(HL), n                              | (HL) ← n                                                                                   | •  | •  | х           | • | x           | •   | • | • | 00<br>←               | 110<br>n               | 110<br>→                                                                                | 36             | 2           | 3           | 10           |                                  |

| LD(IX+d), n                            | (IX + d) ← n                                                                               | •  | •  | х           | • | x           | •   | • | • | 11<br>00<br>←         | 110<br>d               | 101<br>110<br>→<br>→                                                                    | DD<br>36       | 4           | 5           | 19           |                                  |

| LD(IY+d), n                            | (IY + d) ← n                                                                               | •  | •  | x           | • | ×           | •   | • | • | 11<br>00<br>←         | 110<br>d               | $ \begin{array}{c} 101 \\ 110 \\ \rightarrow \\ \rightarrow \end{array} $               | FD<br>36       | 4           | 5           | 19           |                                  |

| LD A, (BC)<br>LD A, (DE)<br>LD A, (nn) | $\begin{array}{l} A \leftarrow (BC) \\ A \leftarrow (DE) \\ A \leftarrow (nn) \end{array}$ | •  | •  | X<br>X<br>X | • | X<br>X<br>X | •   | • | • | 00<br>00<br>00<br>¢   | 011<br>111<br>n        | $\begin{array}{c} 010\\ 010\\ 010\\ \rightarrow\\ \rightarrow\\ \rightarrow\end{array}$ | 0A<br>1A<br>3A | 1<br>1<br>3 | 2<br>2<br>4 | 7<br>7<br>13 |                                  |

| LD(BC), A<br>LD(DE), A<br>LD(nn), A    | (BC) ← A<br>(DE ← A<br>(nn) ← A                                                            | •  | •  | X<br>X<br>X | • | X<br>X<br>X | •   | • | • | 00<br>00<br>00<br>↓ ↓ | 010<br>110<br>n        | $\begin{array}{c} 010\\ 010\\ 010\\ \rightarrow\\ \rightarrow\\ \end{array}$            | 02<br>12<br>32 | 1<br>1<br>3 | 2<br>2<br>4 | 7<br>7<br>13 |                                  |

| LD A, I                                | A ← I                                                                                      | \$ | \$ | х           | 0 | X           | IFF | 0 | • | 11                    | 101                    | 101                                                                                     | ED             | 2           | 2           | 9            |                                  |

| LD A, R                                | A ← R                                                                                      | \$ | ¢  | x           | 0 | x           | IF  | 0 | • | 01                    | 010<br>101<br>011      | 111<br>101<br>111                                                                       | 57<br>ED<br>5F | 2           | 2           | 9            |                                  |

| LD I, A                                | I ← A                                                                                      | •  | •  | x           | • | x           | •   | • | • | 11<br>01              | 101<br>000             | 101<br>111                                                                              | ED<br>47       | 2           | 2           | 9            |                                  |

| LD R, A                                | R ← A                                                                                      | •  | •  | x           | • | x           | •   | • | • | 11<br>01              | 101<br>001             | 101<br>111                                                                              | ED<br>4F       | 2           | 2           | 9            |                                  |

Notes: r, r' means any of the registers A, B, C, D, E, H, L. IFF the content of the interrupt enable flip-flop, (IFF) is copied into the P/V flag. For an explanation of flag notation and symbols for mnemonic tables, see Symbolic Notation section following tables.

x

#### 16-BIT LOAD GROUP

|             | Symbolic                                               |   |   |   | F | lag | s   |   |   | 0             | pcode  |          | N° of | N° of       |             |                           |

|-------------|--------------------------------------------------------|---|---|---|---|-----|-----|---|---|---------------|--------|----------|-------|-------------|-------------|---------------------------|

| Symbol      | Operation                                              | s | z |   | н |     | P/V | N | с | 76            | 543210 | Hex      | Bytes | M<br>Cycles | T<br>States | Comments                  |

| LD dd, nn   | dd ← nn                                                | • | • | х | • | x   | •   | • | • | 00<br>↓<br>↓  |        |          | 3     | 3           | 10          | dd Pair<br>00 BC<br>01 DE |

| LD IX, nn   | IX ← nn                                                | • | • | X | • | ×   | •   | • | • |               |        | DD<br>21 | 4     | 4           | 14          | 10 HL<br>11 SP            |

| LD IY, nn   | IY ← nn                                                | • | • | X | • | x   | •   | • | • |               |        | FD<br>21 | 4     | 4           | 14          |                           |

| LD HL, (nn) | H ← (nn + 1)<br>L ← (nn)                               | • | • | х | • | x   | •   | • | • | 00<br>↓<br>↓  |        | 2A       | 3     | 5           | 16          |                           |

| LD dd, (nn) | $dd_{H} \leftarrow (nn + 1) \\ dd_{L} \leftarrow (nn)$ | • | • | x | • | ×   | •   | • | • |               |        | ED       | 4     | 6           | 20          |                           |

| LD IX, (nn) | $IX_H \leftarrow (nn + 1)$<br>$IX_L \leftarrow (nn)$   | • | • | x | • | x   | •   | • | • |               |        | DD<br>2A | 4     | 6           | 20          |                           |

| LD IY, (nn) | $IY_H \leftarrow (nn + 1)$<br>$IY_L \leftarrow (nn)$   | • | • | X | • | x   | •   | • | • |               |        | FD<br>2A | 4     | 6           | 20          |                           |

| LD (nn), HL | (nn + 1) ← H<br>(nn) ← L                               | • | • | x | • | х   | •   | • | • | 00<br>↓<br>↓  |        | 22       | 3     | 5           | 16          |                           |

| LD (nn), dd | $(nn + 1) \leftarrow dd_H$<br>$(nn) \leftarrow dd_L$   | • | • | x | • | ×   | •   | • | • |               |        | ED       | 4     | 6           | 20          |                           |

| LD (nn), IX | $(nn + 1) \leftarrow IX_H$<br>$(nn) \leftarrow IX_L$   | • | • | х | • | x   | •   | • | • |               |        | DD<br>22 | 4     | 6           | 20          |                           |

| LD (nn), IY | $(nn + 1) \leftarrow IY_H$<br>$(nn) \leftarrow IY_L$   | • | • | x | • | x   | •   | • | • | 11<br>00<br>← |        | FD<br>22 | 4     | 6           | 20          |                           |

Notes: dd is any of the register pairs BC, DE, HL, SP. qq is any of the registers pairs AF, BC, DE, HL. (PAIR)<sub>H</sub>, (PAIR)<sub>L</sub> refer to high order and low order eight bits of the register pair respectively, e.g.,  $BC_L = C$ ,  $AF_H = A$ .

16-BIT LOAD GROUP (continued)

|           | Symbolic                                                 |   |   |   | F | lag       | S   |   |   | 0  | pcode               |     | N° of | N° of       | N° of       |                |

|-----------|----------------------------------------------------------|---|---|---|---|-----------|-----|---|---|----|---------------------|-----|-------|-------------|-------------|----------------|

| Symbol    | Operation                                                | s | z |   | н |           | P/V | N | с | 76 | 543 210             | Hex | Bytes | M<br>Cycles | T<br>States | Comments       |

| LD SP, HL | $SP \leftarrow HL$                                       | • | • | Х | • | Х         | •   | • | • | 11 | 111 001             | F9  | 1     | 1           | 6           |                |

| LD SP, IX | $SP \gets IX$                                            | • | • | Х | • | X         | •   | • | • |    | 011 101             |     | 2     | 2           | 10          |                |

|           |                                                          |   |   |   |   |           |     |   |   |    | 111 001             |     |       |             |             |                |

| LD SP, IY | $SP \leftarrow IY$                                       | • | • | X | • | X         | •   | • | • |    | 111 101             |     | 2     | 2           | 10          |                |

|           |                                                          |   |   |   |   |           |     |   |   |    | 111 001             |     |       |             |             | qq Pair        |

| PUSH qq   | $(SP - 2) \leftarrow qq_{L}$                             | • | • | X | • | Х         | •   | • | • | 11 | qq0 101             |     | 1     | 3           | 11          |                |

|           | (SP – 1) ← qq <sub>H</sub>                               |   |   |   |   |           |     |   |   |    |                     |     |       |             |             | 00 BC<br>01 DE |

| DUOL IV   | $SP \rightarrow SP - 2$                                  |   |   |   |   |           |     |   |   |    |                     |     |       |             | 1           | 10 HL          |

| PUSH IX   | $(SP - 2) \leftarrow IX_L$                               | · | • | X | • | X         | •   | • | • |    | 011 10              |     | 2     | 4           | 15          | 10 HL<br>11 AF |

|           | $(SP - 1) \leftarrow IX_H$<br>SP $\rightarrow$ SP - 2    |   |   |   |   |           |     |   |   | 11 | 100 10              | E5  |       |             |             |                |

| PUSH IY   | $(SP - 2) \leftarrow IY_{L}$                             |   |   | x |   | x         |     |   |   | 44 | 111 10-             | FD  | 2     | 4           | 15          |                |

| FUSHI     | $(SP - 2) \leftarrow IY_H$<br>$(SP - 1) \leftarrow IY_H$ | 1 |   | ^ | - | <b> ^</b> |     | 1 | - |    | 100 10              |     | 2     | -           | 15          |                |

|           | $SP \rightarrow SP - 2$                                  |   |   |   |   |           |     |   |   |    | 100 10              |     |       |             |             |                |

| POP qq    | $qq_H \leftarrow (SP + 1)$                               |   |   | x |   | x         |     |   |   | 11 | qq0 00 <sup>-</sup> |     | 1     | 3           | 10          |                |

| 101 44    | $qq_{\perp} \leftarrow (SP)$                             |   |   |   |   |           |     |   |   |    | 990 00              |     |       |             |             |                |

|           | $SP \rightarrow SP + 2$                                  |   |   |   |   |           |     | 1 |   |    |                     |     |       |             |             |                |

| POP IX    | $IX_{H} \leftarrow (SP + 1)$                             |   |   | x |   | x         | •   | • | • | 11 | 011 10              | DD  | 2     | 4           | 14          |                |

|           | $IX_{L} \leftarrow (SP)$                                 |   |   |   |   |           |     |   |   | 11 | 100 00              | E1  |       |             |             |                |

|           | $SP \rightarrow SP + 2$                                  |   |   |   |   |           |     |   |   |    |                     |     |       |             |             |                |

| POP IY    | $IY_{H} \leftarrow (SP + 1)$                             | • | • | X | • | X         | •   | • | • | 11 | 111 10              | FD  | 2     | 4           | 14          |                |

|           | $IY_{L} \leftarrow (SP)$                                 |   |   |   |   |           |     |   |   | 11 | 100 00              | E1  |       |             |             |                |

|           | $SP \rightarrow SP + 2$                                  |   |   |   |   |           |     |   |   |    |                     |     |       |             |             |                |

Notes: dd is any of the register pairs BC, DE, HL, SP. qq is any of the registers pairs AF, BC, DE, HL. (PAIR)<sub>H</sub>, (PAIR)<sub>L</sub> refer to high order and low order eight bits of the register pair respectively, e.g.,  $BC_L = C$ ,  $AF_H = A$ .

#### EXCHANGE, BLOCK TRANSFER, BLOCK SEARCH GROUPS

|                          | Symbolic                                                                                                                           |   |   |        | F | lag    | s   |   |   | 0        | pcod       | е   |          | N° of | N° of       | N° of       |                                           |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------|---|---|--------|---|--------|-----|---|---|----------|------------|-----|----------|-------|-------------|-------------|-------------------------------------------|

| Symbol                   | Operation                                                                                                                          | s | z |        | н |        | P/V | N | С | 76       | 543        | 210 | Hex      | Bytes | M<br>Cycles | T<br>States | Comments                                  |

| EX DE, HL,<br>EX AF, AF' | DE ↔ HL,<br>AF ↔ AF'                                                                                                               | : | • | X<br>X | • | X<br>X | •   | • | • | 11<br>00 | 101<br>001 |     | EB<br>08 | 1     | 1           | 4           | Register<br>Bank and                      |

| EX AF, AF<br>EXX         | $\begin{array}{c} AF \leftrightarrow AF \\ BC \leftrightarrow BC' \\ DE \leftrightarrow DE' \\ HL \leftrightarrow HL' \end{array}$ | • | • | x      | • | x      | •   | • | • | 11       | 011        |     | D9       | 1     | 1           | 4           | Auxiliary<br>Register<br>Bank<br>Exchange |

| EX (SP), HL              | $\begin{array}{l} H \leftrightarrow (SP+1) \\ L \leftrightarrow (SP) \end{array}$                                                  | • | • | x      | • | x      | •   | • | • | 11       | 100        | 011 | E3       | 1     | 5           | 19          |                                           |

| EX (SP), IX              | $\begin{array}{l} IX_H \leftrightarrow (SP+1)\\ IX_L \leftrightarrow (SP) \end{array}$                                             | • | • | X      | • | x      | •   | • | • | 11<br>11 | 011<br>100 |     | DD<br>E3 | 2     | 6           | 23          |                                           |

| EX (SP), IY              | $\begin{array}{l} IY_H  \leftrightarrow  (SP  +  1) \\ IY_L  \leftrightarrow  (SP) \end{array}$                                    |   | • | X      | • | х      | •   | • | • | 11<br>11 | 111<br>100 |     | FD<br>E3 | 2     | 6           | 23          |                                           |

Notes : 1. If the result of B - 1 is zero the Z flag is set, otherwise it is reset.

2. Z flag is set upon instruction completion only.

10/32

#### EXCHANGE, BLOCK TRANSFER, BLOCK SEARCH GROUPS (continued)

|        | Symbolic                                                                                                                                              |    |        |   | F  | lag | s       |   |   | 0        | pco        | de         |          | N° of  | N° of       | N° of       |                                                                                           |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------|---|----|-----|---------|---|---|----------|------------|------------|----------|--------|-------------|-------------|-------------------------------------------------------------------------------------------|

| Symbol | Operation                                                                                                                                             | s  | z      |   | н  |     | P/V     | N | с | 76       | 543        | 210        | Hex      | Bytes  | M<br>Cycles | T<br>States | Comments                                                                                  |

| LDI    | (DE) ← (HL)<br>DE ← DE + 1<br>HL ← HL + 1<br>BC ← BC − 1                                                                                              | •  | •      | x | 0  | x   | ①<br>↓  | 0 | • | 11<br>10 | 101<br>100 | 101<br>000 | ED<br>A0 | 2      | 4           | 16          | Load (HL) into (DE<br>increment the<br>pointers and<br>decrement the byte<br>counter (BC) |

| LDIR   | $\begin{array}{l} (DE) \leftarrow (HL) \\ DE \leftarrow DE + 1 \\ HL \leftarrow HL + 1 \\ BC \leftarrow BC - 1 \\ Repeat Until \\ BC = 0 \end{array}$ | •  | •      | × | 0  | x   | 100     | 0 | • | 11<br>10 |            | 101<br>000 | ED<br>B0 | 2<br>2 | 5<br>4      | 21<br>16    | lf BC ≠ 0<br>lf BC = 0                                                                    |

| LDD    | $(DE) \leftarrow (HL)$<br>$DE \leftarrow DE + 1$<br>$HL \leftarrow HL + 1$<br>$BC \leftarrow BC - 1$                                                  | •  | •      | x | 0  | x   | ①<br>\$ | 0 | • | 11<br>10 | 101<br>101 | 101<br>000 | ED<br>A8 | 2      | 4           | 16          |                                                                                           |

| LDDR   | $(DE) \leftarrow (HL)$<br>$DE \leftarrow DE - 1$<br>$HL \leftarrow HL - 1$<br>$BC \leftarrow BC - 1$<br>Repeat Until<br>BC = 0                        | •  | •      | × | 0  | x   | 2<br>0  | 0 | • | 11<br>10 | 101<br>111 | 101<br>000 | ED<br>B8 | 2<br>2 | 5<br>4      | 21<br>16    | If BC ≠ 0<br>If BC = 0                                                                    |

| CPI    | $A \leftarrow (HL)$<br>HL $\leftarrow$ HL + 1<br>BC $\leftarrow$ BC - 1                                                                               | ¢  | 2<br>¢ | × | \$ | x   | ①<br>↓  | 1 | • | 11<br>10 | 101<br>100 | 101<br>001 | ED<br>A1 | 2      | 4           | 16          |                                                                                           |

| CPIR   | $\begin{array}{l} A = (HL)\\ HL \leftarrow HL + 1\\ BC \leftarrow BC - 1\\ Repeat Until\\ A = (HL) \text{ or } BC = 0 \end{array}$                    | ¢  | 2<br>≎ | x | \$ | x   | 1       | 1 | • | 11<br>10 | 101<br>110 | 101<br>001 | ED<br>B1 | 2<br>2 | 5           | 21<br>16    | If BC ≠ 0 and<br>A ≠ (HL)<br>If BC = 0 or<br>A = (HL)                                     |

| CPD    | A – (HL)<br>HL ← HL + 1<br>BC ← BC − 1                                                                                                                | \$ | 2<br>≎ | x | \$ | ×   | ①<br>≎  | 1 | • | 11<br>10 | 101<br>101 | 101<br>001 | ED<br>A9 | 2      | 4           | 16          |                                                                                           |

| CPDR   | $\begin{array}{l} A (HL)\\ HL HL \makebox{+-}1\\ BC BC 1\\ Repeat \ Until\\ A (HL) \ or \ BC 0 \end{array}$                                           | \$ | 2<br>≎ | × | \$ | x   | 1       | 1 | • |          | 101<br>111 |            | ED<br>B9 | 2<br>2 | 5           | 21<br>16    | If BC ≠ 0 and<br>A ≠ (HL)<br>If BC = 0 or<br>A = (HL)                                     |

Notes: ① If the result of B - 1 is zero the Z flag is set, otherwise it is reset.

② Z flag is set upon instruction completion only.

#### Z84C00

#### **INSTRUCTION SET** (continued)

#### 8-BIT ARITHMETIC AND LOGICAL GROUP

|                                                                                                      | Symbolic                                                                                                                                                                                                                                                                                                                       |                                                                                                                                          |                                                                                                                                          |        | F                                         | laç                     | s                                                                     |                                      |               | c                         | pcod                                                                                | e                             |     | N° of       | N° of       | N° of         |                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------|-------------------------|-----------------------------------------------------------------------|--------------------------------------|---------------|---------------------------|-------------------------------------------------------------------------------------|-------------------------------|-----|-------------|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                                                                               | Operation                                                                                                                                                                                                                                                                                                                      | s                                                                                                                                        | z                                                                                                                                        |        | н                                         |                         | P/V                                                                   | N                                    | с             | 76                        | 543                                                                                 | 210                           | Hex | Bytes       | M<br>Cycles | T<br>States   | Comments                                                                                                                                              |

| ADD A, r<br>ADD A, n                                                                                 | $\begin{array}{l} A \leftarrow A + r \\ A \leftarrow A + n \end{array}$                                                                                                                                                                                                                                                        | ‡<br>‡                                                                                                                                   | ‡<br>‡                                                                                                                                   | x<br>x | ↔                                         | x<br>x                  | v<br>v                                                                | 0<br>0                               | ≎             | 10<br>11<br>←             | 000<br>000<br>n                                                                     | r<br>110<br>→                 |     | 1<br>2      | 1<br>2      | 4<br>7        | r Reg.<br>000 B<br>001 C                                                                                                                              |

| ADD A, (HL)<br>ADD A, (IX+d)                                                                         | $A \leftarrow A + (HL) A \leftarrow A + (IX + d)$                                                                                                                                                                                                                                                                              | ‡<br>‡                                                                                                                                   | ¢<br>¢                                                                                                                                   | X<br>X |                                           | x<br>x                  | V<br>V                                                                | 0<br>0                               | \$            | 10<br>11<br>10<br>←       | 000<br>011<br>000<br>d                                                              | 110<br>101<br>110<br>→        | DD  | 1<br>3      | 2<br>5      | 7<br>19       | 010 D<br>011 E<br>100 H<br>101 L                                                                                                                      |

| ADD A, (IY+d)                                                                                        | $A \leftarrow A + (IY + d)$                                                                                                                                                                                                                                                                                                    | \$                                                                                                                                       | \$                                                                                                                                       | x      | \$                                        | x                       | v                                                                     | 0                                    | \$            | 11<br>10<br>←             | 111<br>000<br>d                                                                     | 101<br>110<br>→               | FD  | 3           | 5           | 19            | 111 A                                                                                                                                                 |

| ADC A, s<br>SUB s<br>SBC A, s<br>AND s<br>OR s<br>XOR s<br>CP s<br>INC r<br>INC (HL)<br>INC (IX + d) | $\begin{array}{l} A \leftarrow A + s + CY \\ A \leftarrow A - s \\ A \leftarrow A - s - CY \\ A \leftarrow A \wedge s \\ A \leftarrow A \wedge s \\ A \leftarrow A \wedge s \\ A \leftarrow A \oplus s \\ A \leftarrow s \\ r \leftarrow r + 1 \\ (HL) \leftarrow (HL) + 1 \\ (IX + d) \leftarrow \\ (IX + d) + 1 \end{array}$ | $\begin{array}{c} \uparrow \\ \uparrow $ | $\begin{array}{c} \uparrow \\ \uparrow $ | ****   | ‡<br>1<br>0<br>0<br>↓<br>↓<br>↓<br>↓<br>↓ | × × × × × × × × × × × × | $\lor$ | 0<br>1<br>0<br>0<br>1<br>0<br>0<br>0 | ↓ ↓ ↓ 0 0 0 ↓ | 00<br>00<br>11<br>00<br>← | 001<br>010<br>011<br>100<br>110<br>101<br>111<br>111<br>r<br>110<br>011<br>110<br>d | 100<br>100<br>101<br>100<br>→ | DD  | 1<br>1<br>3 | 1<br>3<br>6 | 4<br>11<br>23 | s is any of r, n,<br>(HL), (IX+d),<br>(IY+d) as shown<br>for ADD<br>instruction. The<br>indicated bits<br>replace the<br>000 in the<br>ADD set above. |

| INC (IY+d)                                                                                           | $(IY + d) \leftarrow$<br>(IY + d) + 1                                                                                                                                                                                                                                                                                          | \$                                                                                                                                       | \$                                                                                                                                       | x      | ¢                                         | x                       | V                                                                     | 0                                    | •             | 11<br>00<br>←             | 111<br>110<br>d                                                                     | 101<br>[100]<br>→             | FD  | 3           | 6           | 23            |                                                                                                                                                       |

| DEC m                                                                                                | m ← m – 1                                                                                                                                                                                                                                                                                                                      | \$                                                                                                                                       | \$                                                                                                                                       | x      | ⊅                                         | ×                       | V                                                                     | 1                                    | •             |                           |                                                                                     | 101                           |     |             |             | -             | m is any of r,<br>(HL), (IX+d),<br>(IY+d) as shown<br>for INC. DEC<br>same format<br>and states as<br>INC. Replace<br>100 with<br>101 in opcode.      |

#### GENERAL-PURPOSE ARITHMETIC AND CPU CONTROL GROUPS

|        | Symbolic                                                                                                |    |    |        | F  | lag    | S   |   |    | 0        | pcode            |       | N° of | N° of | N° of       |                                                    |

|--------|---------------------------------------------------------------------------------------------------------|----|----|--------|----|--------|-----|---|----|----------|------------------|-------|-------|-------|-------------|----------------------------------------------------|

| Symbol | Operation                                                                                               | s  | z  |        | н  |        | P/V | N | С  | 76       | 54321            | 0 He: | Bytes | M     | T<br>States | Comments                                           |

| DAA    | Converters acc ;<br>content into packed<br>BCD following add or<br>subtract with packed<br>BCD operands | \$ | \$ | x      | \$ | x      | Ρ   | • | \$ | 00       | 100 11           | 1 27  | 1     | 1     | 4           | Decimal<br>Adjust<br>Accumulator.                  |

| CPL    | $\overline{A} \to \overline{A}$                                                                         | •  | •  | ×      | 1  | x      | •   | 1 | •  | 00       | 101 11           | 1 2F  | 1     | 1     | 4           | Complement<br>Accumulator<br>(one's<br>complement) |

| NEG    | $A \leftarrow 0 - A$                                                                                    | \$ | \$ | x      | \$ | x      | V   | 1 | \$ | 11<br>01 | 101 10<br>000 10 |       |       | 2     | 8           | Negate Acc.<br>(two's<br>complement).              |

| CCF    | $CY \leftarrow \overline{CY}$                                                                           | •  | •  | x      | X  | x      | •   | 0 | \$ | 00       | 111 11           | 1 3F  | 1     | 1     | 4           | Complement<br>Carry Flag.                          |

| SCF    | CY ← 1                                                                                                  | •  | •  | x      | 0  | x      | •   | 0 | 1  | 00       | 110 11           | 1 37  | 1     | 1     | 4           | Set Carry<br>Flag.                                 |

| NOP    | No Operation                                                                                            | •  | •  | X      | 0  | X      | •   | 0 | 1  | 00       | 000 00           | 0 00  | 1     | 1     | 4           |                                                    |

| HALT   | CPU Halted                                                                                              | •  | •  | X      | •  | X      | •   | • | •  | 01       | 110 11           | 0 76  | 1     | 1     | 4           |                                                    |

| DI*    | $IFF \leftarrow 0$                                                                                      | •  | •  | X      | •  | X      | •   | • | •  | 11       | 110 01           |       |       | 1     | 4           |                                                    |

| EI*    | IFF ← 1                                                                                                 | •  | •  | X      | •  | X      | •   | • | •  | 11       | 111 01           |       |       | 1     | 4           |                                                    |

| IM 0   | Set Interrupt                                                                                           | •  | •  | X      | •  | X      | •   | • | •  | 11       | 101 10           |       |       | 2     | 8           |                                                    |

|        | Mode 0                                                                                                  |    |    |        |    |        |     |   |    | 01       | 000 11           |       |       |       |             |                                                    |

| IM 1   | Set Interrupt                                                                                           | •  | •  | X      | •  | X      | •   | • | •  | 11       | 101 10<br>010 11 |       |       | 2     | 8           |                                                    |

| IM2    | Mode 1<br>Set Interrupt                                                                                 |    |    | x      |    | x      | Ι.  |   |    | 11       | 101 10           |       |       | 2     | 8           |                                                    |

|        | Mode 2                                                                                                  | ľ  | ľ  | $ ^{}$ | ľ  | $ ^{}$ |     | ľ |    | 01       | 011 11           |       |       |       |             |                                                    |

Notes : IFF indicates the interrupt enable flip-flop. CY indicates the carry flip-flop. \* indicates interrupts are not sampled at the end of EI or DI.

#### ROTATE AND SHIFT GROUP

| Mnemonic     | Symbolic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |    |   | Fla | gs |     |   |    | Opcode                   |     | No.of | No.of M | No.of T |                                                 |

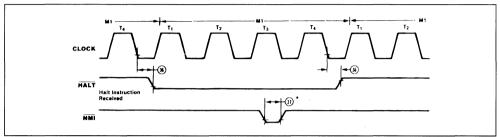

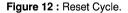

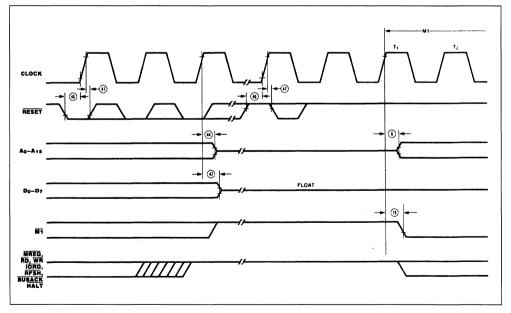

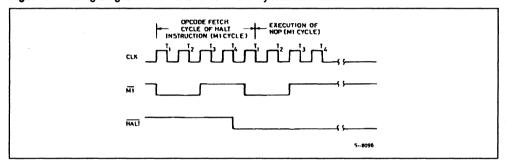

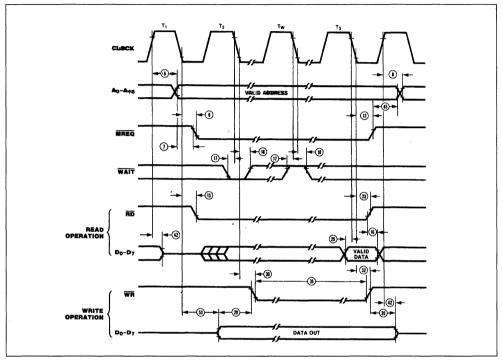

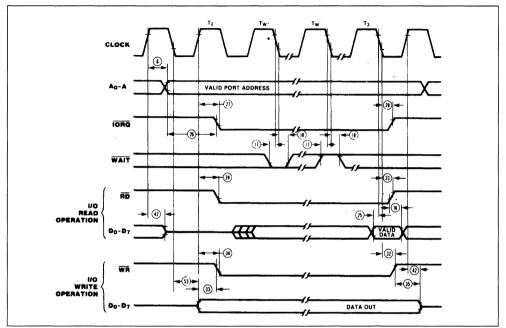

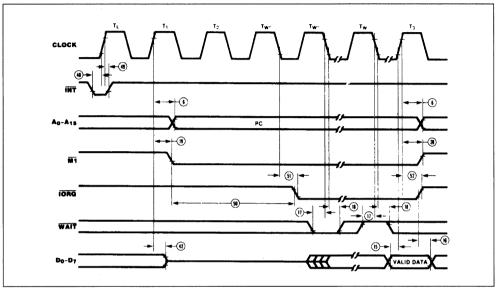

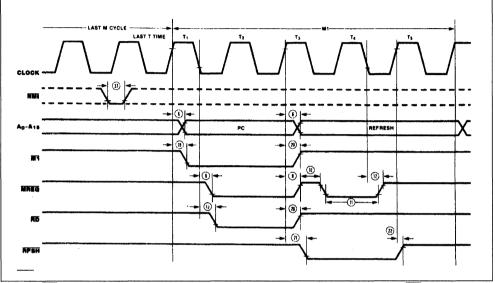

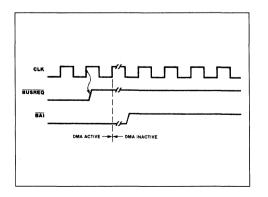

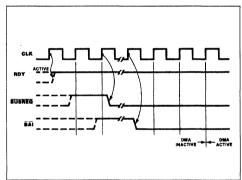

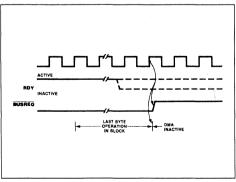

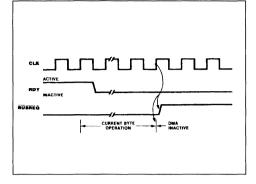

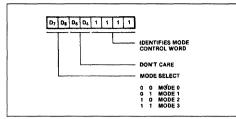

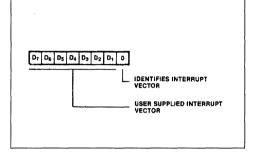

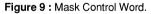

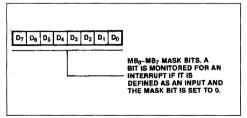

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|---|-----|----|-----|---|----|--------------------------|-----|-------|---------|---------|-------------------------------------------------|