# MEMORY PRODUCTS

## DATABOOK

1<sup>st</sup> EDITION

## **MEMORY PRODUCTS**

## DATABOOK

1<sup>st</sup> EDITION

## **JUNE 1988**

#### USE IN LIFE SUPPORT MUST BE EXPRESSLY AUTHORIZED

SGS-THOMSON' PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEM WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF SGS-THOMSON Microelectronics. As used herein:

- Life support devices or systems are devices or systems which, are intended for surgical implant into the body to support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| TABLE OF CONTENTS  |        |

|--------------------|--------|

|                    |        |

|                    |        |

|                    |        |

|                    |        |

|                    |        |

| GENERAL INDEX      | Page 5 |

| PRODUCT GUIDE      | 7      |

| EPROM DEVICES      | 23     |

| EEPROM DEVICES     | 197    |

| ROM DEVICES        | 257    |

| STATIC RAM DEVICES | 275    |

## GENERAL INDEX

#### Page

| PRODUCT GUIDE             | 7  |

|---------------------------|----|

| GENERAL INFORMATION       | 9  |

| SELECTION GUIDE           | 11 |

| CROSS REFERENCE           | 17 |

| PROCESSES CHARACTERISTICS | 21 |

### **EPROM DEVICES**

| NMOS UV EPROM               | 23  |

|-----------------------------|-----|

| ET2716 (2K×8)               | 25  |

| M2716 (2K×8)                | 25  |

| M2732A (4K×8)               | 35  |

| M2764A (8K×8)               | 43  |

| M27128A (16K×8)             | 53  |

| M27256 (32K × 8)            | 63  |

| M27512 (64K×8)              | 73  |

| CMOS UV EPROM               | 89  |

| ETC2716 (2K × 8)            | 91  |

| ETC2732 (4K × 8)            | 101 |

| TS27C64AQ (8K × 8)          | 111 |

| TS27C256Q (32K × 8)         | 121 |

| ST27C1001 (128Kx8)          | 131 |

| M27C1024 (64K × 16)         | 133 |

| NMOS OTP ROM                | 143 |

| ST2764AP (8K × 8)           | 145 |

| ST27128AP (16K × 8)         | 155 |

| ST27256P (32Kx8)            | 165 |

| CMOS OTP ROM                | 175 |

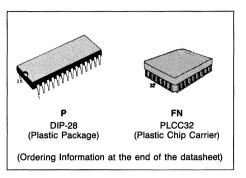

| TS27C64AFN (8K×8 - PLCC)    |     |

| TS27C64AP (8K × 8)          | 177 |

| ST27C256FN (32K × 8 - PLCC) |     |

|                             | 187 |

| EEPROM DEVICES              |     |

| NMOS EEPROM                                                                                                                                             | 197                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| M8571 (1K bit)                                                                                                                                          |                          |

| M9306 (256 bit)                                                                                                                                         |                          |

| M9346 (1K bit)                                                                                                                                          |                          |

| CMOS EEPROM           ST24C02         (2K bit)           TS59C11         (1K bit)           TS93C46         (1K bit)           ST93C56         (2K bit) | 227<br>229<br>239<br>247 |

|                                                                                                                                                         |                          |

## GENERAL INDEX

| OM DEVICES                            |                                                                                                                 |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|                                       |                                                                                                                 |

|                                       |                                                                                                                 |

| · · · ·                               |                                                                                                                 |

| · · · ·                               |                                                                                                                 |

|                                       | a da servicio de la companya de la c |

| M2365 (8K×8)                          |                                                                                                                 |

| TATIC RAM DEVICES                     |                                                                                                                 |

| ZEROPOWER                             | an a                                                                        |

|                                       |                                                                                                                 |

| , , , , , , , , , , , , , , , , , , , | an a                                                                        |

| · · · · · ·                           |                                                                                                                 |

|                                       |                                                                                                                 |

|                                       |                                                                                                                 |

|                                       |                                                                                                                 |

| MK48Z30 (32K × 8)                     | *                                                                                                               |

|                                       |                                                                                                                 |

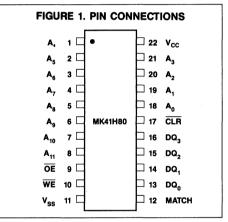

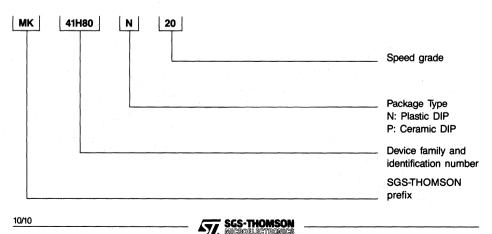

| MK41H80 (4K × 8)                      |                                                                                                                 |

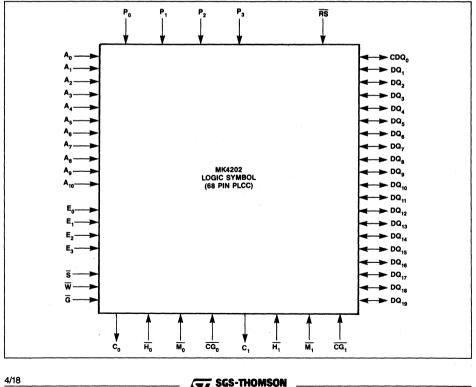

| MK4202 (2048 × 8)                     |                                                                                                                 |

| MK48H74 (8K × 8)                      | en al de la companya  |

| FIFO                                  | · · · · · · · · · · · · · · · · · · ·                                                                           |

|                                       |                                                                                                                 |

|                                       |                                                                                                                 |

| i i j                                 |                                                                                                                 |

|                                       |                                                                                                                 |

| · · · · ·                             |                                                                                                                 |

| · · · ·                               |                                                                                                                 |

|                                       |                                                                                                                 |

|                                       |                                                                                                                 |

|                                       | e proved care proved                                                                                            |

| · · · · ·                             |                                                                                                                 |

| . ,                                   |                                                                                                                 |

|                                       |                                                                                                                 |

|                                       |                                                                                                                 |

|                                       |                                                                                                                 |

| · · · · · ·                           |                                                                                                                 |

## **PRODUCT GUIDE**

The SGS-THOMSON Microelectronics Memories data book is a comprehensive collection of information on advanced, high density, high speed memory products for specific applications.

SGS-THOMSON offers 4 groups of memory products: EPROMs and OTP's, EEPROMs, ROMs and Static RAMs.

EPROMs (Electrically Programmable Read Only Memory) and OTP's (One Time Programmable Read Only Memory) are non volatile memory components for program storage.

SGS-THOMSON Microelectronics has one of the largest product range to meet your requirements:

- all densities from 16K to 1 Megabit.

- NMOS or CMOS technology.

- Jedec approved footprints for easy upgrades.

- UV EPROM in Cerdip package.

- One Time Programmable in windowless plastic package ideally suited for high volume production environment and surface mounting applications.

- very fast programming algorithm.

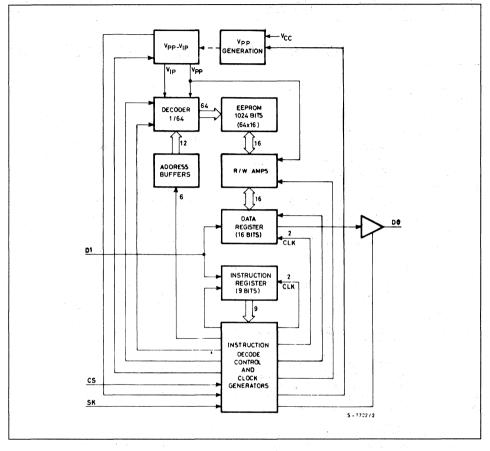

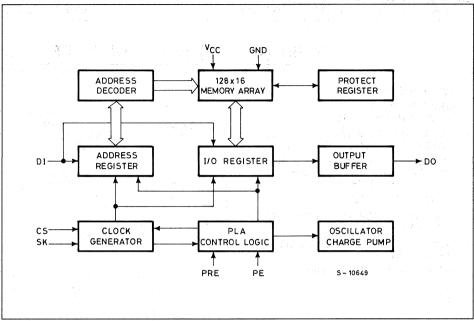

EEPROMS (Electrically Erasable Programmable Read Only Memories) embody the full range of EPROM functional advantages plus the added features of in-circuit erasability and programmability. SGS-THOMSON range comprehends serial access products, with densities ranging from 256 bit to 2K bit, including 2-wire bus compatible versions. Static RAM products cover high speed memories, biport devices and Zeropower<sup>TM</sup> Timekeeper<sup>TM</sup> RAMS.

High speed memories with a device density range of 4Kbits to 64Kbits and performance from 20ns to 55ns.

Organizational flexibility ( $4K \times 1$ ,  $16K \times 1$ ,  $4K \times 4$ ,  $64K \times 1$ ,  $8K \times 8$ ) covers a vast range of applications, including large mainframes, high speed controllers, communications, graphics display and workstations.

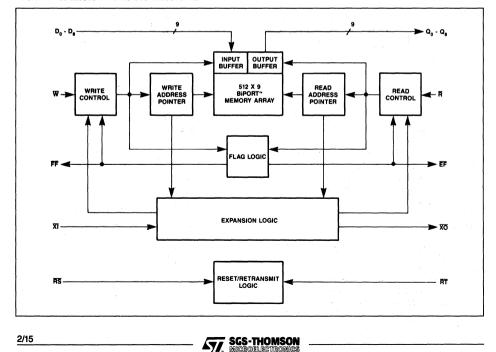

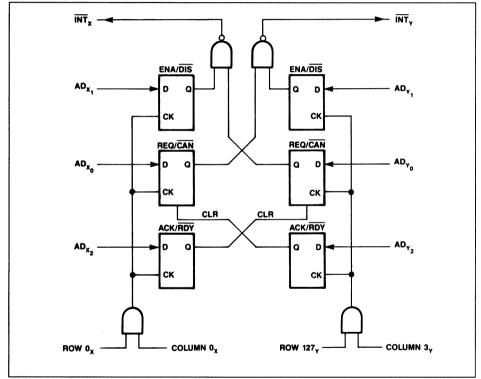

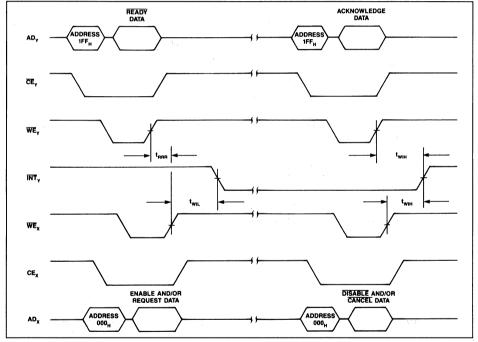

- Biport devices consist of a family of FIFO (First-In-First-Out) buffers. These FIFO's provide an interface between digital information paths with widely varying speeds. Each information source can thus operate at its own intrinsic speed, while results are processed or distributed at speeds from 25ns to 200ns. The Biport family also includes a range of veritable Dual Port Rams enabling applications in systems with two or more processors, or with distributed processors, where separate computing units must exchange data at speeds approaching real time.

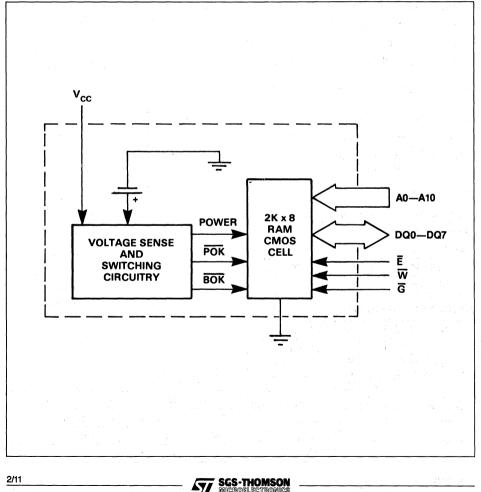

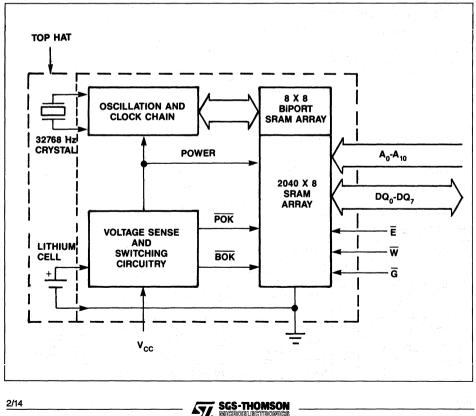

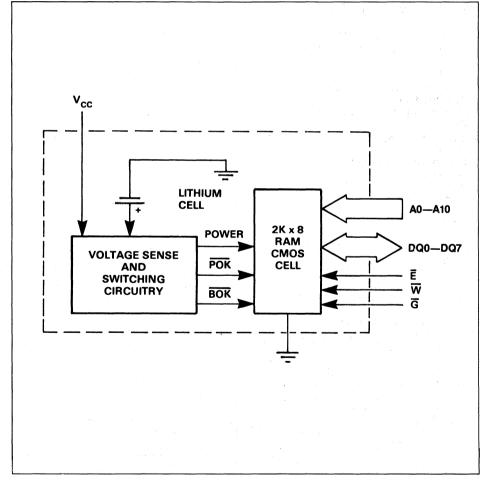

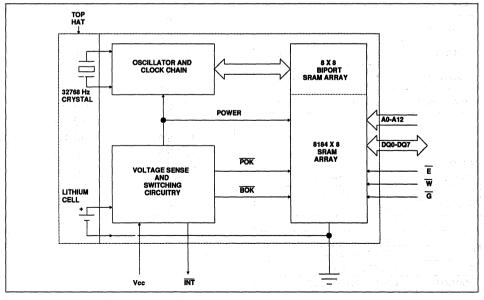

- The Zeropower and Timekeeper RAM family combines the operating simplicity of convention byte-wide SRAM's with the excellent data integrity of Zeropower technology. This integrity is achieved thanks to the use of advanced CMOS technology and long-life lithium cells. With densities from 2K × 8 to 8K × 8 and access/cycle times up to 120ns (150ns for 8K × 8), SGS-THOMSON Zeropower RAMs cover the full range of non-volatile needs for all microprocessor based systems. Thanks to the combined features of Zeropower technology with an on-chip real time clock, the 48T02 Timekeeper offers unparalleled non-volatile performance.

#### SELECTION GUIDE

####

| Part Number  | Orga.   | Access         | Icc   | MAX   | Vcc                      | Temp.                    | Pin      |

|--------------|---------|----------------|-------|-------|--------------------------|--------------------------|----------|

|              | Orga.   | Time           | Act   | St.by |                          | Range                    | Count    |

| ET2716Q      | 2K×8    | 450ns          | 100mA | 25mA  | 5V ± 5%                  | 0 to +70°C               | 24       |

| ET2716Q-1    | 2K x 8  | 350ns          | 100mA | 25mA  | 5V ± 10%                 | 0 to +70°C               | 24       |

| M2716F1      | 2K×8    | 450ns          | 100mA | 25mA  | $5V \pm 5\%$             | 0 to +70°C               | 24       |

| M2716-1F1    | 2K × 8  | 350ns          | 100mA | 25mA  | $5V \pm 10\%$            | 0 to +70°C               | 24       |

| M2716F6      | 2K×8    | 450ns          | 100mA | 25mA  | $5V \pm 5\%$             | -40 to +85°C             | 24       |

| M2716-1F6    | 2K x 8  | 350ns          | 100mA | 25mA  | $5V \pm 10\%$            | $-40$ to $+85^{\circ}C$  | 24       |

| M2732AF1     | 4K×8    | 250ns          | 125mA | 35mA  | $5V \pm 10\%$            | 0 to + 70°C              | 24       |

| M2732A-2F1   | 4K x 8  | 200ns          | 125mA | 35mA  | $5V \pm 5\%$             | 0 to +70°C               | 24       |

| M2732A-3F1   | 4K × 8  | 300ns          | 125mA | 35mA  | $5V \pm 5\%$             | 0 to +70°C               | 24       |

| M2732A-4F1   | 4K x 8  | 450ns          | 125mA | 35mA  | $5V \pm 5\%$             | 0 to +70°C               | 24       |

| M2732AF6     | 4K x 8  | 250ns          | 125mA | 35mA  | $5V \pm 5\%$             | -40 to +85°C             | 24       |

| M2732A-4F6   | 4K x 8  | 250hs<br>450hs | 125mA | 35mA  | $5V \pm 5\%$<br>5V ± 5%  | $-40$ to $+85^{\circ}C$  | 24<br>24 |

|              |         |                |       |       |                          |                          | - •      |

| M2764AF1     | 8K×8    | 250ns          | 75mA  | 35mA  | $5V \pm 5\%$             | 0 to +70°C               | 28       |

| M2764A-1F1   | 8K × 8  | 180ns          | 75mA  | 35mA  | $5V \pm 5\%$             | 0 to +70°C               | 28       |

| M2764A-2F1   | 8K × 8  | 200ns          | 75mA  | 35mA  | $5V \pm 5\%$             | 0 to +70°C               | 28       |

| M2764A-3F1   | 8K × 8  | 300ns          | 75mA  | 35mA  | 5V ± 5%                  | 0 to +70°C               | 28       |

| M2764A-4F1   | 8K × 8  | 450ns          | 75mA  | 35mA  | 5V ± 5%                  | 0 to +70°C               | 28       |

| M2764A-18F1  | 8K × 8  | 180ns          | 75mA  | 35mA  | 5V ± 10%                 | 0 to +70°C               | 28       |

| M2764A-20F1  | 8K×8    | 200ns          | 75mA  | 35mA  | 5V ± 10%                 | 0 to +70°C               | 28       |

| M2764A-25F1  | 8K × 8  | 250ns          | 75mA  | 35mA  | 5V ± 10%                 | 0 to +70°C               | 28       |

| M2764A-30F1  | 8K × 8  | 300ns          | 75mA  | 35mA  | 5V ± 10%                 | 0 to +70°C               | 28       |

| M2764A-45F1  | 8K × 8  | 450ns          | 75mA  | 35mA  | 5V ± 10%                 | 0 to +70°C               | 28       |

| M2764AF6     | 8K×8    | 250ns          | 75mA  | 35mA  | $5V \pm 5\%$             | -40 to +85°C             | 28       |

| M2764A-4F6   | 8K × 8  | 450ns          | 75mA  | 35mA  | 5V ± 5%                  | -40 to +85°C             | 28       |

| M27128AF1    | 16K × 8 | 250ns          | 85mA  | 40mA  | 5V ± 5%                  | 0 to +70°C               | 28       |

| M27128A-1F1  | 16K × 8 | 150ns          | 85mA  | 40mA  | $5V \pm 5\%$             | 0 to +70°C               | 28       |

| M27128A-2F1  | 16K × 8 | 200ns          | 85mA  | 40mA  | $5V \pm 5\%$             | 0 to +70°C               | 28       |

| M27128A-3F1  | 16K × 8 | 300ns          | 85mA  | 40mA  | $5V \pm 5\%$             | 0 to +70°C               | 28       |

| M27128A-4F1  | 16K × 8 | 450ns          | 85mA  | 40mA  | $5V \pm 5\%$             | 0 to +70°C               | 28       |

| M27128A-20F1 | 16K × 8 | 200ns          | 85mA  | 40mA  | $5V \pm 10\%$            | 0 to +70°C               | 28       |

| M27128A-25F1 | 16K x 8 | 250ns          | 85mA  | 40mA  | $5V \pm 10\%$            | 0 to +70°C               | 28       |

| M27128A-30F1 | 16K × 8 | 300ns          | 85mA  | 40mA  | $5V \pm 10\%$            | 0 to +70°C               | 28       |

| M27128A-45F1 | 16K × 8 | 450ns          | 85mA  | 40mA  | $5V \pm 10\%$            | 0 to +70°C               | 28       |

| M27128AF6    | 16K x 8 | 250ns          | 85mA  | 40mA  | $5V \pm 10\%$<br>5V ± 5% | $-40$ to $+85^{\circ}C$  | 28       |

| M27128A-4F6  | 16K × 8 | 450ns          | 85mA  | 40mA  | $5V \pm 5\%$             | $-40$ to $+85^{\circ}$ C | 28       |

|              |         | e              |       |       |                          |                          |          |

| M27256F1     | 32K × 8 | 250ns          | 100mA | 40mA  | $5V \pm 5\%$             | 0 to +70°C               | 28       |

| M27256-1F1   | 32K × 8 | 170ns          | 100mA | 40mA  | $5V \pm 5\%$             | 0 to +70°C               | 28       |

| M27256-2F1   | 32K × 8 | 200ns          | 100mA | 40mA  | 5V ± 5%                  | 0 to +70°C               | 28       |

| M27256-3F1   | 32K × 8 | 300ns          | 100mA | 40mA  | $5V \pm 5\%$             | 0 to +70°C               | 28       |

| M27256-4F1   | 32K × 8 | 450ns          | 100mA | 40mA  | $5V \pm 5\%$             | 0 to +70°C               | 28       |

| M27256-20F1  | 32K × 8 | 200ns          | 100mA | 40mA  | $5V \pm 10\%$            | 0 to +70°C               | 28       |

| M27256-25F1  | 32K × 8 | 250ns          | 100mA | 40mA  | 5V ± 10%                 | 0 to +70°C               | 28       |

| M27256-30F1  | 32K × 8 | 300ns          | 100mA | 40mA  | 5V ± 10%                 | 0 to + 70°C              | 28       |

| M27256-45F1  | 32K × 8 | 450ns          | 100mA | 40mA  | 5V ± 10%                 | 0 to +70°C               | 28       |

| M27256F6     | 32K × 8 | 250ns          | 100mA | 40mA  | $5V \pm 5\%$             | -40 to +85°C             | 28       |

| M27256-4F6   | 32K × 8 | 450ns          | 100mA | 40mA  | 5V ± 5%                  | -40 to +85°C             | 28       |

| M27512F1     | 64K × 8 | 250ns          | 125mA | 40mA  | 5V ± 5%                  | 0 to +70°C               | 28       |

| M27512-2F1   | 64K × 8 | 200ns          | 125mA | 40mA  | 5V ± 5%                  | 0 to +70°C               | 28       |

| M27512-3F1   | 64K × 8 | 300ns          | 125mA | 40mA  | $5V \pm 5\%$             | 0 to + 70°C              | 28       |

| M27512-25F1  | 64K × 8 | 250ns          | 125mA | 40mA  | 5V ± 10%                 | 0 to +70°C               | 28       |

| M27512-30F1  | 64K × 8 | 300ns          | 125mA | 40mA  | 5V ± 10%                 | 0 to +70°C               | 28       |

| M27512F6     | 64K × 8 | 250ns          | 125mA | 40mA  | $5V \pm 5\%$             | -40 to +85°C             | 28       |

#### **CMOS UV EPROM**

| Part Number    | Orga.    | Access | Icc    | MAX   | Vcc           | Temp.          | Pin   |

|----------------|----------|--------|--------|-------|---------------|----------------|-------|

| T art Hambol   | o.gu.    | Time   | Act    | St.by | Range         | Range          | Count |

| ETC2716Q       | 2K×8     | 450ns  | 10mA   | 1mA   | 5V ± 5%       | 0 to + 70°C    | 24    |

| ETC2716Q-1     | 2K×8     | 350ns  | 10mA   | 1mA   | 5V ± 5%       | 0 to + 70°C    | 24    |

| ETC2716Q-V     | 2K × 8   | 450ns  | 10mA   | 1mA   | $5V \pm 5\%$  | -40 to +85°C   | 24    |

| ETC2732Q       | 4K×8     | 450ns  | 10mA   | 1mA   | 5V ± 5%       | 0 to + 70°C    | 24    |

| ETC2732Q-3     | 4K×8     | 350ns  | 10mA   | 1mA   | 5V ± 5%       | 0 to +70°C     | 24    |

| ETC2732Q-45-V  | 4K×8     | 450ns  | 10mA   | 1mA   | $5V \pm 5\%$  | -40 to +85°C   | 24    |

| TS27C64A-15XCQ | 8K × 8   | 150ns  | 30mA   | 1mA   | 5V ± 5%       | 0 to + 70°C    | 28    |

| TS27C64A-20XCQ | 8K×8     | 200ns  | 30mA   | 1mA   | 5V ± 5%       | 0 to + 70°C    | 28    |

| TS27C64A-25XCQ | 8K×8     | 250ns  | 30mA   | 1mA   | 5V ± 5%       | 0 to +70°C     | 28    |

| TS27C64A-30XCQ | 8K×8     | 300ns  | 30mA   | 1mA   | 5V ± 5%       | 0 to + 70°C    | 28    |

| TS27C64A-15CQ  | 8K×8     | 150ns  | 30mA   | 1mA   | 5V ± 10%      | 0 to + 70°C    | 28    |

| TS27C64A-20CQ  | 8K×8     | 200ns  | 30mA   | 1mA   | 5V ± 10%      | 0 to + 70°C    | 28    |

| TS27C64A-25CQ  | 8K×8     | 250ns  | . 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C    | 28    |

| TS27C64A-30CQ  | 8K×8     | 300ns  | 30mA   | 1mA   | 5V ± 10%      | 0 to + 70°C    | 28    |

| TS27C64A-15VQ  | 8K×8     | 150ns  | 30mA   | 1mA   | 5V ± 10%      | -40 to +85°C   | 28    |

| TS27C64A-20VQ  | 8K×8     | 200ns  | 30mA   | 1mA   | 5V ± 10%      | -40 to +85°C   | 28    |

| TS27C64A-25VQ  | 8K×8     | 250ns  | 30mA   | 1mA   | 5V ± 10%      | -40 to +85°C   | 28    |

| TS27C64A-30VQ  | 8K × 8   | 300ns  | 30mA   | 1mA   | $5V \pm 10\%$ | -40 to +85°C   | 28    |

| TS27C256-15XCQ | 32K × 8  | 150ns  | 30mA   | 1mA   | 5V ± 5%       | 0 to + 70°C    | 28    |

| TS27C256-17XCQ | 32K × 8  | 170ns  | 30mA   | 1mA   | $5V \pm 5\%$  | 0 to + 70°C    | 28    |

| TS27C256-20XCQ | 32K × 8  | 200ns  | 30mA   | 1mA   | 5V ± 5%       | 0 to + 70°C    | 28    |

| TS27C256-25XCQ | 32K × 8  | 250ns  | 30mA   | 1mA   | 5V ± 5%       | 0 to +70°C     | 28    |

| TS27C256-30XCQ | 32K × 8  | 300ns  | 30mA   | 1mA   | 5V ± 5%       | 0 to +70°C     | 28    |

| TS27C256-17CQ  | 32K × 8  | 170ns  | 30mA   | 1mA   | 5V ± 10%      | 0 to +70°C     | 28    |

| TS27C256-20CQ  | 32K × 8  | 200ns  | 30mA   | 1mA   | 5V ± 10%      | 0 to +70°C     | 28    |

| TS27C256-25CQ  | 32K × 8  | 250ns  | 30mA   | 1mA   | 5V ± 10%      | 0 to +70°C     | 28    |

| TS27C256-30CQ  | 32K×8    | 300ns  | 30mA   | 1mA   | 5V ± 10%      | 0 to +70°C     | 28    |

| TS27C256-15VQ  | 32K × 8  | 150ns  | 30mA   | 1mA   | $5V \pm 5\%$  | -40 to +85°C   | 28    |

| TS27C256-17CQ  | 32K × 8  | 170ns  | 30mA   | 1mA   | 5V ± 10%      | -40 to +85°C   | 28    |

| TS27C256-20VQ  | 32K × 8  | 200ns  | 30mA   | 1mA   | 5V ± 10%      | -40 to +85°C   | 28    |

| TS27C256-25VQ  | 32K × 8  | 250ns  | 30mA   | 1mA   | 5V ± 10%      | -40 to +85°C   | 28    |

| TS27C256-30VQ  | 32K × 8  | 300ns  | 30mA   | 1mA   | 5V ± 10%      | - 40 to + 85°C | 28    |

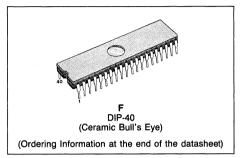

| M27C1024-12XF1 | 64K × 16 | 120ns  | 50mA   | 1mA   | $5V \pm 5\%$  | 0 to + 70°C    | 40    |

| M27C1024-15XF1 | 64K × 16 | 150ns  | 50mA   | 1mA   | $5V \pm 5\%$  | 0 to + 70°C    | 40    |

| M27C1024-20XF1 | 64K × 16 | 200ns  | 50mA   | 1mA   | $5V \pm 5\%$  | 0 to + 70°C    | 40    |

| M27C1024-25XF1 | 64K × 16 | 250ns  | 50mA   | 1mA   | $5V \pm 5\%$  | 0 to + 70°C    | 40    |

| M27C1024-12F1  | 64K × 16 | 120ns  | 50mA   | 1mA   | 5V ± 10%      | 0 to + 70°C    | 40    |

| M27C1024-15F1  | 64K × 16 | 150ns  | 50mA   | 1mA   | 5V ± 10%      | 0 to + 70°C    | 40    |

| M27C1024-20F1  | 64K × 16 | 200ns  | 50mA   | 1mA   | 5V ± 10%      | 0 to + 70°C    | 40    |

| M27C1024-25F1  | 64K × 16 | 250ns  | 50mA   | 1mA   | $5V \pm 10\%$ | 0 to + 70°C    | 40    |

| M27C1024-15XF6 | 64K × 16 | 150ns  | 50mA   | 1mA   | $5V \pm 5\%$  | -40 to +85°C   | 40    |

| M27C1024-20XF6 | 64K × 16 | 200ns  | 50mA   | 1mA   | $5V \pm 5\%$  | -40 to +85°C   | 40    |

| M27C1024-25XF6 | 64K × 16 | 250ns  | 50mA   | 1mA   | 5V ± 5%       | -40 to +85°C   | 40    |

#### **SELECTION GUIDE**

#### NMOS OTP ROM

| Part Number                                                                                                    | Orga.                                                          | Orga Access                                        |                                              | MAX                                                  | Vcc                                                  | Temp.                                                                                          | Pin                                          |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------|----------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------|

|                                                                                                                | Orga.                                                          | Time                                               | Act                                          | St.by                                                |                                                      | Range                                                                                          | Count                                        |

| ST2764A-18XCP<br>ST2764A-20XCP<br>ST2764A-18CP<br>ST2764A-20CP<br>ST2764A-20CP<br>ST2764A-25CP<br>ST2764A-30CP | 8K×8<br>8K×8<br>8K×8<br>8K×8<br>8K×8<br>8K×8                   | 180ns<br>200ns<br>180ns<br>200ns<br>250ns<br>300ns | 75mA<br>75mA<br>75mA<br>75mA<br>75mA<br>75mA | 35mA<br>35mA<br>35mA<br>35mA<br>35mA<br>35mA<br>35mA | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$ | 0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C | 28<br>28<br>28<br>28<br>28<br>28<br>28<br>28 |

| ST27128A-15XCP<br>ST27128A-20XCP<br>ST27128A-20CP<br>ST27128A-25CP<br>ST27128A-30CP                            | 16K×8<br>16K×8<br>16K×8<br>16K×8<br>16K×8<br>16K×8             | 150ns<br>200ns<br>200ns<br>250ns<br>300ns          | 85mA<br>85mA<br>85mA<br>85mA<br>85mA         | 40mA<br>40mA<br>40mA<br>40mA<br>40mA                 | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$ | 0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C               | 28<br>28<br>28<br>28<br>28<br>28             |

| ST27256-17XCP<br>ST27256-20XCP<br>ST27256-20CP<br>ST27256-20CP<br>ST27256-25CP<br>ST27256-30CP                 | 32K × 8<br>32K × 8<br>32K × 8<br>32K × 8<br>32K × 8<br>32K × 8 | 170ns<br>200ns<br>200ns<br>250ns<br>300ns          | 100mA<br>100mA<br>100mA<br>100mA<br>100mA    | 40mA<br>40mA<br>40mA<br>40mA<br>40mA                 | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$ | 0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C               | 28<br>28<br>28<br>28<br>28<br>28             |

#### CMOS OTP ROM

| Part Number    | Orga.   | Access | Icc  | MAX   | Vcc           | Temp.           | Pin   |

|----------------|---------|--------|------|-------|---------------|-----------------|-------|

|                | Jiya.   | Time   | Act  | St.by |               | Range           | Count |

| TS27C64A-15CFN | 8K × 8  | 150ns  | 30mA | 1mA   | 5V ± 10%      | 0 to × 70°C     | 32    |

| TS27C64A-20CFN | 8K × 8  | 200ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 32    |

| TS27C64A-25CFN | 8K × 8  | 250ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 32    |

| TS27C64A-30CFN | 8K × 8  | 300ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 32    |

| TS27C64A-15VFN | 8K × 8  | 150ns  | 30mA | 1mA   | 5V ± 10%      | -40 to + 85°C   | 32    |

| TS27C64A-20VFN | 8K × 8  | 200ns  | 30mA | 1mA   | 5V ± 10%      | -40 to + 85°C   | 32    |

| TS27C64A-25VFN | 8K × 8  | 250ns  | 30mA | 1mA   | 5V ± 10%      | -40 to + 85°C   | 32    |

| TS27C64A-30VFN | 8K × 8  | 300ns  | 30mA | 1mA   | 5V ± 10%      | -40 to + 85°C   | 32    |

| TS27C64A-15TFN | 8K × 8  | 150ns  | 30mA | 1mA   | 5V ± 10%      | - 40 to + 105°C | 32    |

| TS27C64A-20TFN | 8K x 8  | 200ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to +105°C   | 32    |

| TS27C64A-25TFN | 8K × 8  | 250ns  | 30mA | 1mA   | 5V ± 10%      | - 40 to + 105°C | 32    |

| TS27C64A-30TFN | 8K × 8  | 300ns  | 30mA | 1mA   | 5V ± 10%      | -40 to +105°C   | 32    |

| TS27C64A-15CP  | 8K × 8  | 150ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 28    |

| TS27C64A-20CP  | 8K × 8  | 200ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 28    |

| TS27C64A-25CP  | 8K × 8  | 250ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 28    |

| TS27C64A-30CP  | 8K x 8  | 300ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 28    |

| TS27C64A-15VP  | 8K × 8  | 150ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to + 85°C   | 28    |

| TS27C64A-20VP  | 8K × 8  | 200ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to + 85°C   | 28    |

| TS27C64A-25VP  | 8K × 8  | 250ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to + 85°C   | 28    |

| TS27C64A-30VP  | 8K x 8  | 300ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to + 85°C   | 28    |

| TS27C64A-15TP  | 8K × 8  | 150ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to +105°C   | 28    |

| TS27C64A-20TP  | 8K x 8  | 200ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to +105°C   | 28    |

| TS27C64A-25TP  | 8K×8    | 250ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to +105°C   | 28    |

| TS27C64A-30TP  | 8K × 8  | 300ns  | 30mA | 1mA   | 5V ± 10%      | -40 to +105°C   | 28    |

| ST27C256-17CFN | 32K × 8 | 170ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 32    |

| ST27C256-20CFN | 32K × 8 | 200ns  | 30mA | 1mA   | $5V \pm 10\%$ | 0 to + 70°C     | 32    |

| ST27C256-25CFN | 32K × 8 | 250ns  | 30mA | 1mA   | $5V \pm 10\%$ | 0 to + 70°C     | 32    |

| ST27C256-30CFN | 32K x 8 | 300ns  | 30mA | 1mA   | $5V \pm 10\%$ | 0 to + 70°C     | 32    |

| ST27C256-17VFN | 32K × 8 | 170ns  | 30mA | 1mA   | 5V ± 10%      | -40 to + 85°C   | 32    |

| ST27C256-20VFN | 32K × 8 | 200ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to + 85°C   | 32    |

| ST27C256-25VFN | 32K × 8 | 250ns  | 30mA | 1mA   | 5V ± 10%      | -40 to + 85°C   | 32    |

| ST27C256-30VFN | 32K x 8 | 300ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to + 85°C   | 32    |

| ST27C256-17TFN | 32K × 8 | 170ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to +105°C   | 32    |

| ST27C256-20TFN | 32K × 8 | 200ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to +105°C   | 32    |

| ST27C256-25TFN | 32K × 8 | 250ns  | 30mA | 1mA   | 5V ± 10%      | -40 to +105°C   | 32    |

| ST27C256-30TFN | 32K × 8 | 300ns  | 30mA | 1mA   | 5V ± 10%      | -40 to +105°C   | 32    |

| ST27C256-17CP  | 32K × 8 | 170ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 28    |

| ST27C256-20CP  | 32K × 8 | 200ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 28    |

| ST27C256-25CP  | 32K × 8 | 250ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 28    |

| ST27C256-30CP  | 32K × 8 | 300ns  | 30mA | 1mA   | 5V ± 10%      | 0 to + 70°C     | 28    |

| ST27C256-17VP  | 32K × 8 | 170ns  | 30mA | 1mA   | 5V ± 10%      | -40 to + 85°C   | 28    |

| ST27C256-20VP  | 32K × 8 | 200ns  | 30mA | 1mA   | 5V ± 10%      | -40 to + 85°C   | 28    |

| ST27C256-25VP  | 32K x 8 | 250ns  | 30mA | 1mA   | 5V ± 10%      | -40 to + 85°C   | 28    |

| ST27C256-30VP  | 32K × 8 | 300ns  | 30mA | 1mA   | 5V ± 10%      | -40 to + 85°C   | 28    |

| ST27C256-17TP  | 32K × 8 | 170ns  | 30mA | 1mA   | 5V ± 10%      | -40 to +105°C   | 28    |

| ST27C256-20TP  | 32K × 8 | 200ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to +105°C   | 28    |

| ST27C256-25TP  | 32K x 8 | 250ns  | 30mA | 1mA   | $5V \pm 10\%$ | -40 to +105°C   | 28    |

|                |         |        |      |       | $5V \pm 10\%$ | -40 to +105°C   | 28    |

#### SELECTION GUIDE

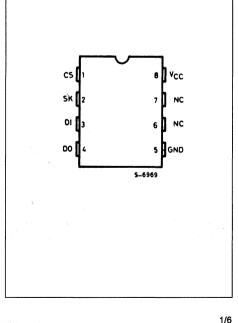

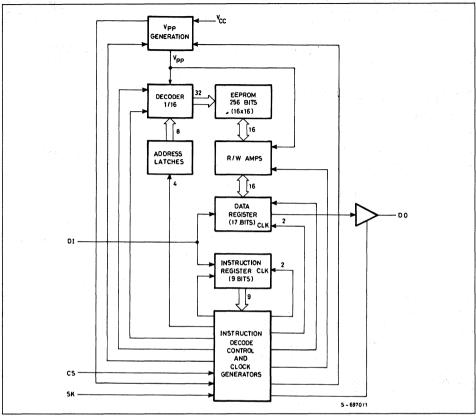

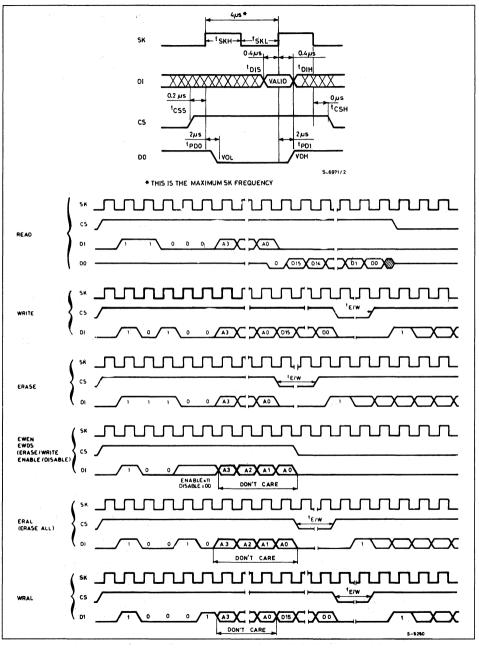

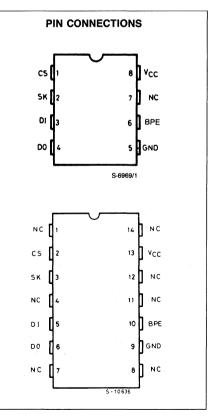

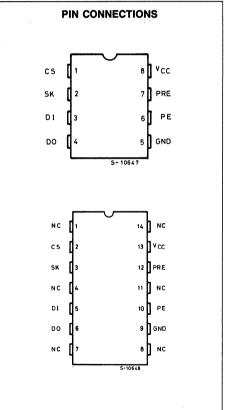

#### NMOS EEPROM

| Part Number   | Orga.   | Frequency   | ICC MAX                               |       | VCC      | Temp.        | Pin   |

|---------------|---------|-------------|---------------------------------------|-------|----------|--------------|-------|

| i alt Hallboi | o.ga.   | . requeitey | Act                                   | St.by | ••••     | Range        | Count |

| M8571B1       | 1K-bit  | 125KHz      | 20mA                                  |       | 5V ± 10% | 0 to + 70°C  | 8     |

| M8571B6       | 1K-bit  | 125KHz      | 20mA                                  |       | 5V ± 10% | -40 to +85°C | 8     |

| M9306B1       | 256-bit | 250KHz      | 6mA                                   | 3mA   | 5V ± 10% | 0 to + 70°C  | 8     |

| M9306B6       | 256-bit | 250KHz      | 6mA                                   | 3mA   | 5V ± 10% | -40 to +85°C | 8     |

| M9306M1       | 256-bit | 250KHz      | 6mA                                   | 3mA   | 5V ± 10% | 0 to + 70°C  | 8     |

| M9306M6       | 256-bit | 250KHz      | 6mA                                   | 3mA   | 5V ± 10% | -40 to +85°C | 8     |

| M9346B1       | 1-Kbit  | 250KHz      | 6mA                                   | 3mA   | 5V ± 10% | 0 to + 70°C  | 8     |

| M9346B6       | 1-Kbit  | 250KHz      | 6mA                                   | 3mA   | 5V ± 10% | -40 to +85°C | 8     |

| M9346M1       | 1-Kbit  | 250KHz      | 6mA                                   | 3mA   | 5V ± 10% | 0 to + 70°C  | 14    |

| M9346M6       | 1-Kbit  | 250KHz      | 6mA                                   | 3mA   | 5V ± 10% | -40 to +85°C | 14    |

|               |         |             | · · · · · · · · · · · · · · · · · · · |       |          |              |       |

|               |         |             |                                       |       |          |              |       |

#### CMOS EEPROM

| Part Number | Orga. Frequency |           | ICC MAX |       | Vcc      | Temp.        | Pin            |

|-------------|-----------------|-----------|---------|-------|----------|--------------|----------------|

|             | orgu.           | requeitoy | Act     | St.by | •        | Range        | Count          |

| ST24C02CP   | 2-KBIT          | 100KHz    | 3mA     | 0.1mA | 5V ± 10% | 0 to +70°C   | 8              |

| ST24C02VP   | 2-KBIT          | 100KHz    | 3mA     | 0.1mA | 5V ± 10% | -40 to +85°C | 8              |

| TS59C11CP   | 1-KBIT          | 250KHz    | 3mA     | 0.1mA | 5V ± 10% | 0 to +70°C   | 8              |

| TS59C11VP   | 1-KBIT          | 250KHz    | 3mA     | 0.1mA | 5V ± 10% | -40 to +85°C | 8              |

| TS93C46CP   | 1-KBIT          | 250KHz    | 3mA     | 0.1mA | 5V ± 10% | 0 to +70°C   | 8              |

| TS93C46VP   | 1-KBIT          | 250KHz    | 3mA     | 0.1mA | 5V ± 10% | -40 to +85°C | 8              |

| ST93C56     | 2-KBIT          | 1MHz      | 3mA     | 0.1mA | 5V ± 10% | 0 to +70°C   | 8              |

| 1           |                 |           |         |       |          |              | and the second |

|             |                 |           |         |       |          |              |                |

#### NMOS ROM

| MOS ROM     |              |       |          |       | star 2 v to   |               |       |

|-------------|--------------|-------|----------|-------|---------------|---------------|-------|

| Part Number | Orga. Access |       | ICC MAX  |       | Vcc           | Temp.         | Pin   |

|             | orga.        | Time  | Act      | St.by | VCC           | Range         | Count |

| M2316H      | 2Kx8         | 300ns | 70mA     |       | 5V ± 10%      | 0 to +70°C    | 24    |

| M2332/M2333 | 4Kx8         | 250ns | 70mA     | 1     | 5V ± 10%      | 0 to +70°C    | 24    |

| M2364       | 8Kx8         | 250ns | 80mA     |       | 5V ± 10%      | 0 to +70°C    | 24    |

| M2365       | 8Kx8         | 250ns | 70mA     |       | 5V ± 10%      | 0 to +70°C    | 28    |

|             | 1.12         |       | age to a | 1.)   | 1878 - BAR 83 | and Alexandre |       |

#### ZEROPOWER

| Part Number    | Orga.  | Access | lcc  | Max   | 1, | Vcc     | Temp.        | Pin   |

|----------------|--------|--------|------|-------|----|---------|--------------|-------|

| Fait Number    | Orga.  | Time   | Act  | St.by |    | •00     | Range        | Count |

| BATTERY BACK-U | Р      |        |      |       |    |         |              |       |

| MK48C02AN15    | 2K×8   | 150ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48C02AN20    | 2K×8   | 200ns  | 80mA | 3mA   | 5V | 1       | 0 to +70°C   | 24    |

| MK48C02AN25    | 2K×8   | 250ns  | 80mA | 3mA   | 5V | + 10%   | 0 to +70°C   | 24    |

| MK48C02AK15    | 2K×8   | 150ns  | 80mA | 3mA   | 5V | -5%     | 0 to +70°C   | 24    |

| MK48C02AK20    | 2K × 8 | 200ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48C02AK25    | 2K×8   | 250ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| TIMEKEEPER     |        |        |      |       |    |         |              |       |

| MK48T02B12     | 2K × 8 | 120ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48T02B15     | 2K × 8 | 150ns  | 80mA | 3mA   | 5V |         | 0 to + 70°C  | 24    |

| MK48T02B20     | 2K × 8 | 200ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48T02B25     | 2K x 8 | 250ns  | 80mA | 3mA   | 5V | + 10%   | 0 to + 70°C  | 24    |

| MK48T02BU12    | 2K x 8 | 120ns  | 80mA | 3mA   | 5V | -5%     | 0 to + 70°C  | 24    |

| MK48T02BU15    | 2K × 8 | 150ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48T02BU20    | 2K×8   | 200ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48T02BU25    | 2K × 8 | 250ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48T12B12     | 2K×8   | 120ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48T12B15     | 2K×8   | 150ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48T12B20     | 2K×8   | 200ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48T12B25     | 2K×8   | 250ns  | 80mA | 3mA   | 5V | + 10%   | 0 to +70°C   | 24    |

| MK48T12BU12    | 2K×8   | 120ns  | 80mA | 3mA   | 5V | - 10%   | 0 to + 70°C  | 24    |

| MK48T12BU15    | 2K×8   | 150ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48T12BU20    | 2K×8   | 200ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48T12BU25    | 2K×8   | 250ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| ZEROPOWER      |        |        |      |       |    |         |              |       |

| MK48Z02B12     | 2K × 8 | 120ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48Z02B15     | 2K×8   | 150ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48Z02B20     | 2K×8   | 200ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48Z02B25     | 2K×8   | 250ns  | 80mA | 3mA   | 5V | + 10%   | 0 to +70°C   | 24    |

| MK48Z02BU12    | 2K×8   | 120ns  | 80mA | 3mA   | 5V | - 5%    | 0 to +70°C   | 24    |

| MK48Z02BU15    | 2K×8   | 150ns  | 80mA | 3mA   | 5V |         | 0 to + 70°C  | 24    |

| MK48Z02BU20    | 2K×8   | 200ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48Z02BU25    | 2K×8   | 250ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48Z12B12     | 2K×8   | 120ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48Z12B15     | 2K × 8 | 150ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48Z12B20     | 2K × 8 | 200ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48Z12B25     | 2K × 8 | 250ns  | 80mA | 3mA   | 5V | + 10%   | 0 to +70°C   | 24    |

| MK48Z12BU12    | 2K × 8 | 120ns  | 80mA | 3mA   | 5V | - 10%   | 0 to +70°C   | 24    |

| MK48Z12BU15    | 2K × 8 | 150ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48Z12BU20    | 2K × 8 | 200ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MK48Z12BU25    | 2K×8   | 250ns  | 80mA | 3mA   | 5V |         | 0 to +70°C   | 24    |

| MKI48Z02B12    | 2K×8   | 120ns  | 80mA | 3mA   | 5V |         | -40 to +85°C | 24    |

| MKI48Z02B15    | 2K×8   | 150ns  | 80mA | 3mA   | 5V |         | -40 to +85°C | 24    |

| MKI48Z02B20    | 2K × 8 | 200ns  | 80mA | 3mA   | 5V |         | -40 to +85°C | 24    |

| MKI48Z02B25    | 2K × 8 | 250ns  | 80mA | 3mA   | 5V | + 10%   | -40 to +85°C | 24    |

| MKI48Z02BU12   | 2K × 8 | 120ns  | 80mA | 3mA   | 5V | -5%     | -40 to +85°C | 24    |

| MKI48Z02BU15   | 2K × 8 | 150ns  | 80mA | 3mA   | 5V |         | -40 to +85°C | 24    |

| MKI48Z02BU20   | 2K × 8 | 200ns  | 80mA | 3mA   | 5V |         | -40 to +85°C | 24    |

| MKI48Z02BU25   | 2K×8   | 250ns  | 80mA | 3mA   | 5V | ( · · · | -40 to +85°C | 24    |

Note: 1. Letter "U" inserted in sales type indicates "Underwriters' Laboratories" branding.

#### SELECTION GUIDE

#### ZEROPOWER

| Part Number                                                                                                              | Orga.                                                                        | Access                                                               | Icc                                                          | Max                                                  |                                                    | Vcc            | Temp.                                                                                                                                        | Pin                                                |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                                                                                                                          | orgai                                                                        | Time                                                                 | Act                                                          | St.by                                                | ]                                                  |                | Range                                                                                                                                        | Count                                              |

| MKI48Z12B12<br>MKI48Z12B15<br>MKI48Z12B20<br>MKI48Z12B25<br>MKI48Z12BU12<br>MKI48Z12BU15<br>MKI48Z12BU20<br>MKI48Z12BU20 | 2K × 8<br>2K × 8 | 120ns<br>150ns<br>200ns<br>250ns<br>120ns<br>150ns<br>200ns<br>250ns | 80mA<br>80mA<br>80mA<br>80mA<br>80mA<br>80mA<br>80mA<br>80mA | 3mA<br>3mA<br>3mA<br>3mA<br>3mA<br>3mA<br>3mA<br>3mA | 5V<br>5V<br>5V<br>5V<br>5V<br>5V<br>5V<br>5V<br>5V | + 10%<br>- 10% | -40 to +85°C<br>-40 to +85°C | 24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24 |

| MK48Z08B15<br>MK48Z08B20<br>MK48Z08B25<br>MK48Z08BU15<br>MK48Z08BU20<br>MK48Z08BU25                                      | 8K × 8<br>8K × 8<br>8K × 8<br>8K × 8<br>8K × 8<br>8K × 8                     | 150ns<br>200ns<br>250ns<br>150ns<br>200ns<br>250ns                   | 50mA<br>50mA<br>50mA<br>50mA<br>50mA<br>50mA                 | 3mA<br>3mA<br>3mA<br>3mA<br>3mA<br>3mA               | 5V<br>5V<br>5V<br>5V<br>5V<br>5V                   | + 10%<br>- 5%  | 0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C                                               | 28<br>28<br>28<br>28<br>28<br>28<br>28             |

| MK48Z18B15<br>MK48Z18B20<br>MK48Z18B25<br>MK48Z18BU15<br>MK48Z18BU20<br>MK48Z18BU25                                      | 8K × 8<br>8K × 8<br>8K × 8<br>8K × 8<br>8K × 8<br>8K × 8                     | 150ns<br>200ns<br>250ns<br>150ns<br>200ns<br>250ns                   | 50mA<br>50mA<br>50mA<br>50mA<br>50mA<br>50mA                 | 3mA<br>3mA<br>3mA<br>3mA<br>3mA<br>3mA               | 5V<br>5V<br>5V<br>5V<br>5V<br>5V<br>5V             | + 10%<br>- 10% | 0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C                                               | 28<br>28<br>28<br>28<br>28<br>28<br>28             |

| MK48Z09B15<br>MK48Z09B20<br>MK48Z09B25<br>MK48Z09BU15<br>MK48Z09BU20<br>MK48Z09BU25                                      | 8K × 8<br>8K × 8<br>8K × 8<br>8K × 8<br>8K × 8<br>8K × 8                     | 150ns<br>200ns<br>250ns<br>150ns<br>200ns<br>250ns                   | 50mA<br>50mA<br>50mA<br>50mA<br>50mA<br>50mA                 | 3mA<br>3mA<br>3mA<br>3mA<br>3mA<br>3mA               | 5V<br>5V<br>5V<br>5V<br>5V<br>5V<br>5V             | + 10%<br>- 5%  | 0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C                                               | 28<br>28<br>28<br>28<br>28<br>28<br>28<br>28       |

| MK48Z19B15<br>MK48Z19B20<br>MK48Z19B25<br>MK48Z19BU15<br>MK48Z19BU20<br>MK48Z19BU25                                      | 8K × 8<br>8K × 8<br>8K × 8<br>8K × 8<br>8K × 8<br>8K × 8                     | 150ns<br>200ns<br>250ns<br>150ns<br>200ns<br>250ns                   | 50mA<br>50mA<br>50mA<br>50mA<br>50mA<br>50mA                 | 3mA<br>3mA<br>3mA<br>3mA<br>3mA<br>3mA               | 5V<br>5V<br>5V<br>5V<br>5V<br>5V<br>5V             | + 10%<br>- 10% | 0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C<br>0 to +70°C                                               | 28<br>28<br>28<br>28<br>28<br>28<br>28             |

Note: 1. Letter "U" inserted in sales type indicates "Underwriters' Laboratories" branding.

#### FAST STATIC RAM

| Part Number | Orga.   | Access | Icc   | Max      | Vcc      | Temp.                                 | Pin   |

|-------------|---------|--------|-------|----------|----------|---------------------------------------|-------|

|             | orga.   | Time   | Act   | St.by    |          | Range                                 | Count |

| MK41H66N20  | 16K×1   | 20ns   | 120mA |          | 5V ± 10% | 0 to +70°C                            | 20    |

| MK41H66N25  | 16K×1   | 25ns   | 120mA |          | 5V ± 10% | 0 to + 70°C                           | 20    |

| MK41H66N35  | 16K × 1 | 35ns   | 120mA |          | 5V ± 10% | 0 to +70°C                            | 20    |

| MK41H67N20  | 16K×1   | 20ns   | 120mA | 10mA     | 5V ± 10% | 0 to +70°C                            | 20    |

| MK41H67N25  | 16K×1   | 25ns   | 120mA | 10mA     | 5V ± 10% | 0 to +70°C                            | 20    |

| MK41H67N35  | 16K × 1 | 35ns   | 120mA | 10mA     | 5V ± 10% | 0 to +70°C                            | 20    |

| MK41H68N20  | 4K × 4  | 20ns   | 120mA | 8mA      | 5V ± 10% | 0 to +70°C                            | 20    |

| MK41H68N25  | 4K×4    | 25ns   | 120mA | 8mA      | 5V ± 10% | 0 to +70°C                            | 20    |

| MK41H68N35  | 4K×4    | 35ns   | 120mA | 8mA      | 5V ± 10% | 0 to + 70°C                           | 20    |

| MK41H69N20  | 4K×4    | 20ns   | 120mA |          | 5V ± 10% | 0 to + 70°C                           | 20    |

| MK41H69N25  | 4K×4    | 25ns   | 120mA | <u> </u> | 5V ± 10% | 0 to + 70°C                           | 20    |

| MK41H69N35  | 4K×4    | 35ns   | 120mA |          | 5V ± 10% | 0 to +70°C                            | 20    |

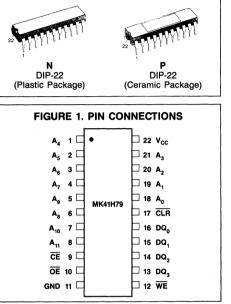

| MK41H79N20  | 4K×4    | 20ns   | 120mA | 16mA     | 5V ± 10% | 0 to +70°C                            | 22    |

| MK41H79N25  | 4K×4    | 25ns   | 120mA | 16mA     | 5V ± 10% | 0 to + 70°C                           | 22    |

| MK41H79N35  | 4K × 4  | 35ns   | 120mA | 16mA     | 5V ± 10% | 0 to +70°C                            | 22    |

| · · · · ·   |         |        |       | •        |          |                                       |       |

| TAGRAM      |         |        |       |          |          | · · · · · · · · · · · · · · · · · · · |       |

| MK41H80N20  | 4K×4    | 20ns   | 120mA |          | 5V ± 10% | 0 to +70°C                            | 22    |

| MK41H80N25  | 4K×4    | 25ns   | 120mA | ·        | 5V ± 10% | 0 to +70°C                            | 22    |

| MK41H80N35  | 4K×4    | 35ns   | 120mA | · -      | 5V ± 10% | 0 to +70°C                            | 22    |

Note: 1. Letter "U" inserted in sales type indicates "Underwiters' Laboratories" branding.

#### SELECTION GUIDE

#### BIPORT (DUAL PORT)

| Part Number | Orga. | Access | Icc  | MAX   | Vcc           | Temp.      | Pin   |

|-------------|-------|--------|------|-------|---------------|------------|-------|

|             | Urga. | Time   | Act  | St.by | ••••          | Range      | Count |

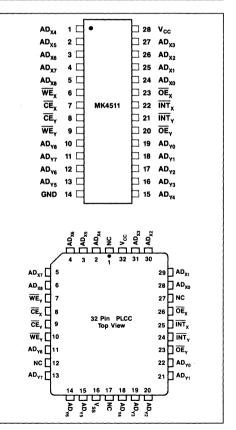

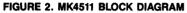

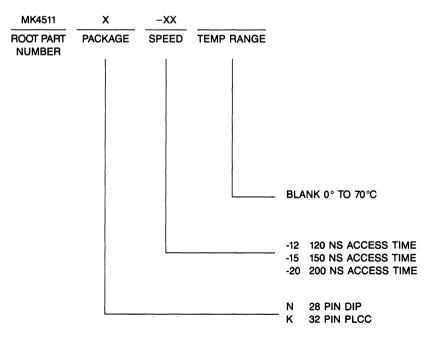

| MK4511N12   | 512×9 | 120ns  | 50mA | 5mA   | 5V ± 10%      | 0 to +70°C | 28    |

| MK4511N15   | 512×9 | 150ns  | 50mA | 5mA   | 5V ± 10%      | 0 to +70°C | 28    |

| MK4511N20   | 512×9 | 200ns  | 50mA | 5mA   | $5V \pm 10\%$ | 0 to +70°C | 28    |

#### FIFO

| Part Number | Orga.           | Access | Icc   | Max   | Vcc           | Temp.       | Pin   |

|-------------|-----------------|--------|-------|-------|---------------|-------------|-------|

|             | orgu.           | Time   | Act   | St.by | •             | Range       | Count |

| MK4501K10   | 512×9           | 100ns  | 80mA  | 8mA   | 5V ± 10%      | 0 to +70°C  | 32    |

| MK4501K12   | 512×9           | 120ns  | 80mA  | 8mA   | 5V ± 10%      | 0 to +70°C  | 32    |

| MK4501K15   | 512×9           | 150ns  | 80mA  | 8mA   | 5V ± 10%      | 0 to +70°C  | 32    |

| MK4501K20   | 512×9           | 200ns  | 80mA  | 8mA   | 5V ± 10%      | 0 to +70°C  | . 32  |

| MK4501K65   | 512×9           | 65ns   | 80mA  | 8mA   | 5V ± 10%      | 0 to + 70°C | 32    |

| MK4501K80   | 512×9           | 80ns   | 80mA  | 8mA   | 5V ± 10%      | 0 to +70°C  | 32    |

| MK4501N10   | 512×9           | 100ns  | 80mA  | 8mA   | 5V ± 10%      | 0 to +70°C  | 28    |

| MK4501N12   | 512×9           | 120ns  | 80mA  | 8mA   | 5V ± 10%      | 0 to +70°C  | 28    |

| MK4501N15   | 512×9           | 150ns  | 80mA  | 8mA   | 5V ± 10%      | 0 to +70°C  | 28    |

| MK4501N20   | 512×9           | 200ns  | 80mA  | 8mA   | 5V ± 10%      | 0 to +70°C  | 28    |

| MK4501N65   | 512×9           | 65ns   | 80mA  | 8mA   | 5V ± 10%      | 0 to +70°C  | 28    |

| MK4501N80   | 512×9           | 80ns   | 80mA  | 8mA   | $5V \pm 10\%$ | 0 to +70°C  | 28    |

| MK4503N10   | 2048 × 9        | 100ns  | 120mA | 12mA  | 5V ± 10%      | 0 to +70°C  | 28    |

| MK4503N12   | 2048 × 9        | 120ns  | 120mA | 12mA  | 5V ± 10%      | 0 to +70°C  | 28    |

| MK4503N15   | 2048 × 9        | 150ns  | 120mA | 12mA  | 5V ± 10%      | 0 to +70°C  | 28    |

| MK4503N20   | 2048 × 9        | 200ns  | 120mA | 12mA  | 5V ± 10%      | 0 to + 70°C | 28    |

| MK4503N65   | 2048 × 9        | 65ns   | 120mA | 12mA  | 5V ± 10%      | 0 to +70°C  | 28    |

| MK4503N80   | 2048 × 9        | 80ns   | 120mA | 12mA  | 5V ± 10%      | 0 to +70°C  | 28    |

| MK4505MN25  | 1024×5          | 15ns   | 100mA | _     | 5V ± 10%      | 0 to +70°C  | 24    |

| MK4505MN33  | $1024 \times 5$ | 20ns   | 100mA | _     | 5V ± 10%      | 0 to +70°C  | 24    |

| MK4505MN50  | $1024 \times 5$ | 25ns   | 100mA | _     | 5V ± 10%      | 0 to + 70°C | 24    |

| MK4505SN25  | 1024×5          | 15ns   | 100mA | _     | 5V ± 10%      | 0 to +70°C  | 20    |

| MK4505SN33  | $1024 \times 5$ | 20ns   | 100mA | _     | 5V ± 10%      | 0 to + 70°C | 20    |

| MK4505SN50  | $1024 \times 5$ | 25ns   | 100mA |       | 5V ± 10%      | 0 to + 70°C | 20    |

Note: 1. Letter "U" inserted in sales type indicates "Underwriters' Laboratories" branding.

#### UV EPROM

| PRODUCT<br>DESCRIPTION | SGS-THOMSON       | AMD       | FUJITSU    | HITACHI   | INTEL  | Microchip<br>Technol.<br>(GI) | MITSUBISHI  | NSC         | NEC         | окі       | SIGNETICS | TI         | TOSHIBA    |

|------------------------|-------------------|-----------|------------|-----------|--------|-------------------------------|-------------|-------------|-------------|-----------|-----------|------------|------------|

| 2K×8 NMOS              | ET2716Q<br>M2716F | AM2716    |            |           |        |                               |             |             |             |           |           | TMS2516    |            |

| 2K×8 CMOS              | ETC2716Q          |           |            |           |        |                               |             | NMC2716BQ   |             |           |           |            |            |

| 4K×8 NMOS              | M2732A            | AM2732    |            |           | 2732A  |                               |             |             |             |           |           | TMS2732A   |            |

| 4K×8 CMOS              | ETC2732Q          |           | _          |           |        |                               | · •         | NMC27C32BQ  |             |           |           |            |            |

| 8K×8 NMOS              | M2764AF           | AM2764    | MBM2764    |           | 2764A  |                               |             |             |             |           |           | TMS2764    | TMM2764AD  |

| 8K×8 CMOS              | TS27C64AQ         |           | MBM27C64   | HN27C64G  | 27C64  | 27C64                         |             | NMC27C64Q   |             |           | 27C64A    |            |            |

| 16K×8 NMOS             | M27128AF          | AM27128A  | MBM27128   | HN27128AG | 27128A |                               |             |             | μPD27128D   |           |           | TMS27128   | TMM27128AD |

| 16K×8 CMOS             | -                 |           |            |           | 27C128 | 27C128                        |             | NMC27C128Q  |             |           |           | TMS27C128  |            |

| 32K×8 NMOS             | M27256F           | AM27256   | MBM27256   | HN27256G  | 27256  | 27256                         | M5M27256K   |             | μPD27256D   | MSM27256  |           | TMS27256   | TMM27256AD |

| 32K×8 CMOS             | TS27C256Q         | AM27C256  | MBM27C256  | HN27C256G | 27C256 | 27C256                        | M5M27C256K  | NMC27C256Q  | μPD27C256   |           | 27C256FA  | TMS27C256  |            |

| 64K×8 NMOS             | M27512F           | AM27512   | MBM27512   | HN27512G  | 27512F |                               | M5M27512K   |             |             |           |           |            | TMM27512D  |

| 64K×8 CMOS             |                   | AM27C512  |            |           |        | 27C512                        | M5M27C512AK | NMC27C512Q  | μPD27C512D  |           |           | TMS27C512  |            |

| 128K×8 NMOS            |                   |           |            |           | 27010  |                               |             |             |             | MSM271000 |           |            |            |

| 128K×8 CMOS            | ST27C1001         |           |            | HN27C101G |        |                               | M5M27C101K  | NMC27C1023Q | μPD27C1001D |           |           |            | TC571001D  |

| 64K16 NMOS             |                   |           |            |           | 27210  |                               |             |             |             | MSM271024 |           |            |            |

| 64K16 CMOS             | M27C1024          | AM27C1024 | MBM27C1024 | HN27C1024 |        |                               | M5M27C102K  | NMC27C1024  | μPD27C1024D |           |           | TMS27C1024 | TC57C1024D |

61.

| OTP | ROM |

|-----|-----|

|-----|-----|

20

| PRODUCT<br>DESCRIPTION | SGS-THOMSON  | HITACHI   | INTEL   | MICROCHIP<br>TECHNOL.<br>(GI) | MITSUBISHI | NSC       | NEC         | окі         | SIGNETICS | TI         | TOSHIBA    |

|------------------------|--------------|-----------|---------|-------------------------------|------------|-----------|-------------|-------------|-----------|------------|------------|

| 8K×8 NMOS              | ST2764AP     |           | P2764A  |                               | M5M2764P   |           | μPD2764C    | MSM2764AZB  |           | TMS27P64   | TMM2764AP  |

| 8K×8 CMOS              | TS27C64AP/FN |           | P27C64  | P27C64                        |            | NMC27C64N | μPD27C64C   |             | 27C64A-N  |            |            |

| 16K×8 NMOS             | ST27128AP    | HN27128AP | P27128A |                               |            |           | μPD27128C   | MSM27128AZB | -         | TMS27P128  | TMM27128AP |

| 32K×8 NMOS             | ST27256P     | HN27256P  | P27256  | P27256                        | M5M27256P  |           |             | MSM27256AZB |           | TMS27P256  | TMM27256AP |

| 32K×8 CMOS             | ST27C256P/FN |           | P27C256 | P27C256                       | M5M27C256  |           | μPD27C256AC |             | 27C256-N  | TMS27PC256 | TC54256AP  |

SGS-THOMSON

### EEPROM

| PRODUCT<br>DESCRIPTION          | SGS-THOMSON | CATALYST | GENERAL<br>INSTRUM. | HYUNDAI | ЮТ       | NATIONAL               | ОКІ      | SIEMENS | SIERRA  | VALVO<br>(PHILIPS) | XICOR                     |

|---------------------------------|-------------|----------|---------------------|---------|----------|------------------------|----------|---------|---------|--------------------|---------------------------|

| SERIAL NMOS<br>256 BIT          | M9306       |          |                     |         | :        | NMC9306                |          |         |         |                    |                           |

| 1024 BIT                        | M9346       |          |                     |         |          | NMC9346                |          |         |         |                    |                           |

| 1024 BIT<br>2-WIRE BUS          | M8571       |          | PCD8572             |         |          |                        | · · · ·  | SDA2516 |         | PCF8572            |                           |

| SERIAL CMOS<br>1024 BIT         | TS59C11     | CAT59C11 | ER5911<br>(NMOS)    |         |          |                        | MSM16911 |         |         |                    |                           |

| 1024 BIT                        | TS93C46     | CAT93C46 |                     | HY93C46 | ICT93C46 | NMC93CS46<br>NMC93CS06 | MSM16811 |         | SC22011 |                    | 1                         |

| 2048 BIT<br>2-WIRE BUS          | ST24C02     |          | PCD8582             |         |          |                        |          | SDA2526 |         | PCF8582            | X24C02<br>X2402<br>(NMOS) |

| 2048 BIT<br>V <sub>CC</sub> =3V | ST93C56     |          |                     |         |          | NMC93CS56              |          |         |         |                    |                           |

#### VFSRAM

| PRODUCT<br>DESCRIPTION | SGS-THOMSON | CYPRESS | MATRA   | INMOS   | IDT      | MOTOROLA | NEC     | FUJITSU |

|------------------------|-------------|---------|---------|---------|----------|----------|---------|---------|

| (16KX1)                | MK41H67     | CY7C167 | HM65767 | IMS1403 | IDT6167A | MCM6167  | μPD4311 | MB81C67 |

| (4KX4)                 | MK41H68     | CY7C168 | HM65768 | IMS1423 | IDT6168A | MCM6168  | μPD4314 | MB81C68 |

| (64KX1)                | MK41H87     | CY7C187 | HM65787 | IMS1600 | IDT7187  | MCM6187  | μPD4361 | MB81C71 |

| (8KX8)                 | MK48H64     | CYC185  | HM65641 | IMS1630 | IDT7164  | MCM6164  | μPD4364 | MB81C78 |

| FIFO                   |             |           |           |          |          |       |

|------------------------|-------------|-----------|-----------|----------|----------|-------|

| PRODUCT<br>DESCRIPTION | SGS-THOMSON | IDT       | CYPRESS   | DALLAS   | AMD/MMI  | νтι   |

| (512 × 9)              | MK4501      | IDT7201   | CY7C412   | DS2009   | 67C201   | _     |

| (2KX9)                 | MK4503      | IDT7202/3 | CY7C424/9 | DS2010/1 | 67C202/3 | VT2F9 |

#### ZEROPOWER

| PRODUCT<br>DESCRIPTION | SGS-THOMSON | DALLAS | GREENWICH |

|------------------------|-------------|--------|-----------|

| (2KX8)                 | MK48Z02     | DS1210 | NCR2      |

| (8KX8)                 | MK48Z08     | DS1225 | NVR8      |

CROSS REFERENCE

Ы

#### **PROCESSES CHARACTERISTICS**

#### NMOS EPROM

| Process<br>Name | Channel<br>Length | Max.<br>Speed | V <sub>PP</sub><br>(external) | Main<br>Products                      |

|-----------------|-------------------|---------------|-------------------------------|---------------------------------------|

| E1              | 4 μm              | 350 ns        | 25 V                          | M2716                                 |

| E3              | 1.5 μm            | 200 ns        | 21 V                          | M2732A                                |

| E3              | 1.5 μm            | 150 ns        | 12.5 V                        | M2764A<br>M27128A<br>M27256<br>M27512 |

#### CMOS EPROM

| P2 | 5 <i>µ</i> m | 350 ns | 25 V   | ETC2716<br>ETC2732   |

|----|--------------|--------|--------|----------------------|

| 3E | 1.4 μm       | 150 ns | 12.5 V | TS27C64A<br>TS27C256 |

| E4 | 1.0 μm       | 120 ns | 12.5 V | M27C1024             |

NMOS EEPROM

| F1 | 3.5 μm | 250 KHz | 5V | M8571<br>M9306 |

|----|--------|---------|----|----------------|

|    |        |         |    | M9346          |

#### CMOS EEPROM

| STATIC RAMS |        | · · · · · · · · · · · · · · · · · · · | . 1                | n n ga a s         |

|-------------|--------|---------------------------------------|--------------------|--------------------|

| F3          | 1.5 μm | 1 MHz                                 | 5V                 | ST93C56            |

|             |        |                                       | 는 가 같다.<br>1년 - 1년 | TS93C46<br>ST24C02 |

| 2E2         | 2.0 μm | 250 KHz                               | 5V                 | TS59C11            |

#### STATIC RAMS

| Technology | Channel<br>Length | Max.<br>Speed | Metal Levels/<br>Memory Cell | Main<br>products                                      |

|------------|-------------------|---------------|------------------------------|-------------------------------------------------------|

| CMOS       | 2.0 μm            | 65 ns         | 1/8T                         | FIFO<br>MK4501<br>MK4503                              |

| CMOS       | 2.0 <i>µ</i> m    | 20 ns         | 1/8T                         | DUAL PORT<br>MK4511                                   |

| CMOS       | <b>2.0 μm</b>     | 120 ns        | 1/6T                         | ZEROPOWER/<br>TIMEKEEPER<br>MK48Z02<br>MK48T02        |

| CMOS       | 1.2 μm            | 20 ns         | 2/6T                         | VERY FAST<br>MK41H67<br>MK41H68<br>MK41H80<br>MK48H64 |

| CMOS       | 1.2 μm            | 150 ns        | 2/6T                         | ZEROPOWER<br>MK48Z08                                  |

| CMOS       | 1.2 μm            | 25 ns         | 2/8T                         | FIFO<br>MK4505                                        |

## **EPROM DEVICES**

## **NMOS UV EPROM**

23

### 16K (2K×8) NMOS UV ERASABLE PROM

- 2048 × 8 ORGANIZATION

- 525 MW MAX ACTIVE POWER, 132 MW MAX STANDBY POWER

- LOW POWER DURING PROGRAMMING

- ACCESS TIME M/ET2716-1, 350ns; M/ET2716, 450ns

- SINGLE 5V POWER SUPPLY

- STATIC-NO CLOCKS REQUIRED

- INPUTS AND OUTPUTS TTL COMPATIBLE DURING BOTH READ AND PROGRAM MODES

- THREE-STATE OUTPUT WITH OR-TIE CAPABILITY

- EXTENDED TEMPERATURE RANGE (F6)

#### DESCRIPTION

The M/ET2716 is high speed 16K UV erasable and electrically reprogrammable EPROM ideally suited for applications where fast turn around and pattern experimentation are important requirements.

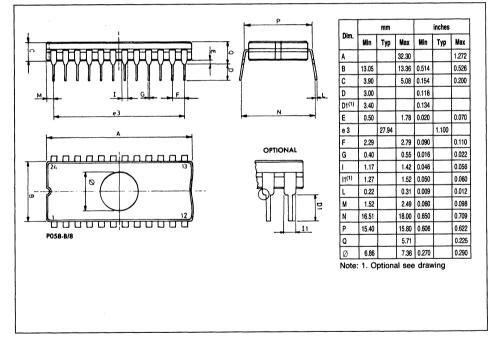

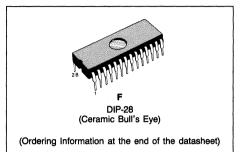

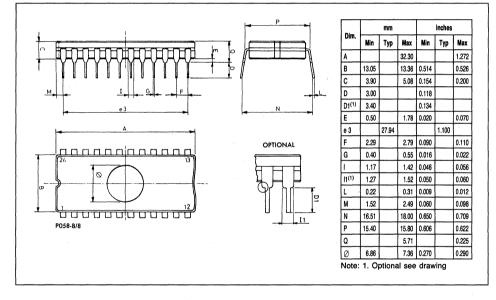

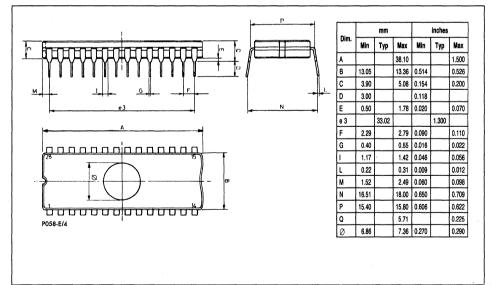

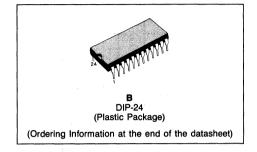

The M/ET2716 is packaged in a 24-pin dual-in-line package with transparent lid. The transparent lid allows the user to expose the chip to ultraviolet light to erase the bit pattern. A new pattern can then be written into the device by following the programming procedure.

This EPROM is fabricated with the reliable, high volume, time proven, N-channel silicon gate technology X-MOS.

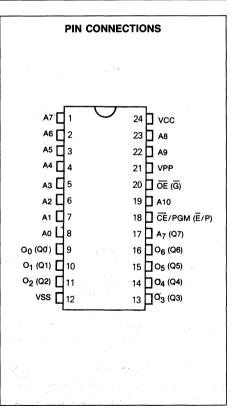

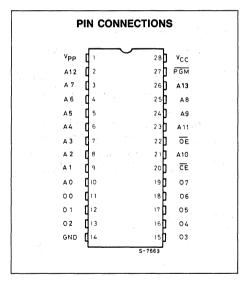

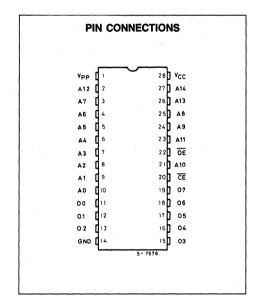

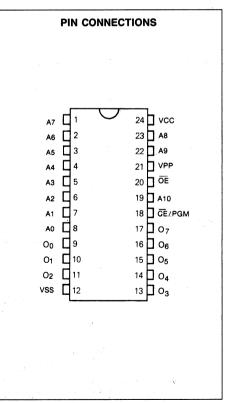

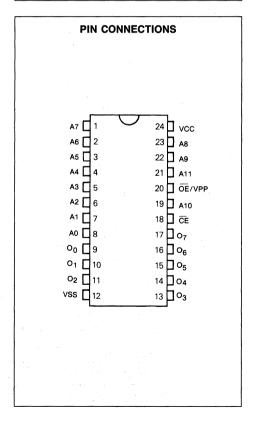

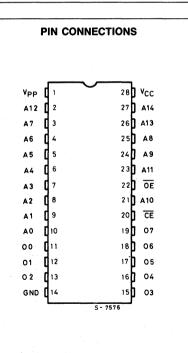

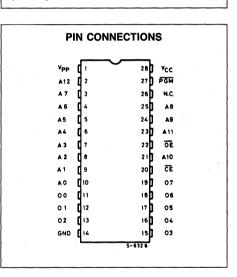

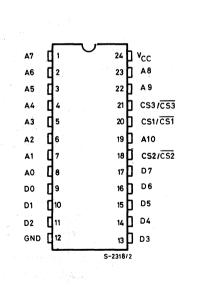

#### **PIN NAMES**

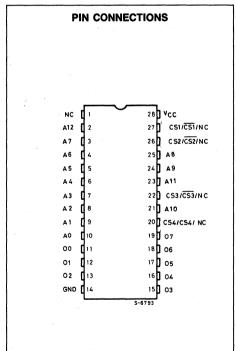

| A0—A10                                 | ADDRESS INPUTS       |

|----------------------------------------|----------------------|

| O <sub>0</sub> -O <sub>7</sub> (Q0-Q7) | DATA OUTPUTS         |

| CE/PGM (E/P)                           | CHIP ENABLE/PROGRAM  |

| OE (G)                                 | OUTPUT ENABLE        |

| V <sub>PP</sub>                        | READ 5V, PROGRAM 25V |

| V <sub>CC</sub>                        | POWER (5V)           |

| V <sub>SS</sub>                        | GROUND               |

Note: Symbols in parentheses are proposed JEDEC standard

June 1988

1/9 25

#### ET2716/M2716

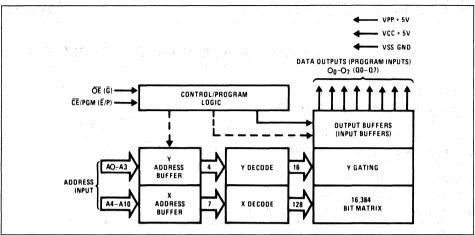

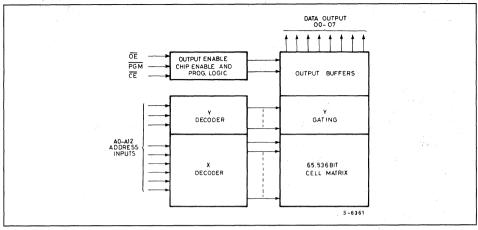

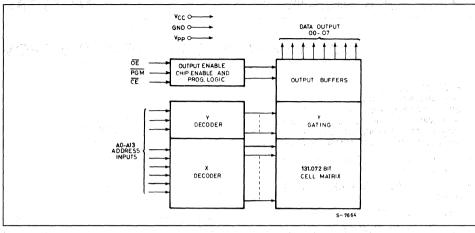

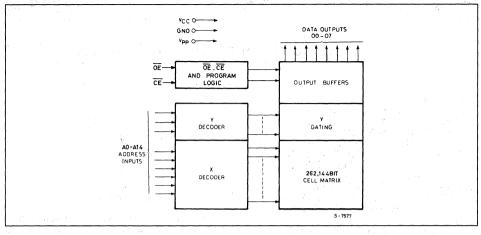

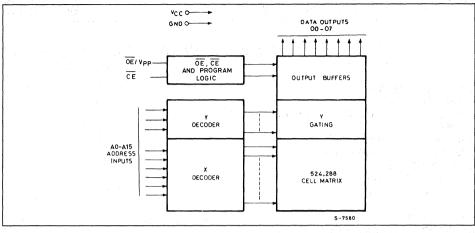

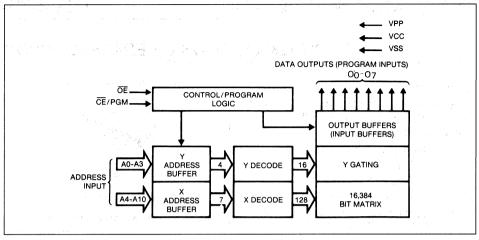

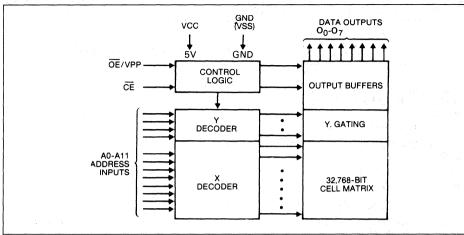

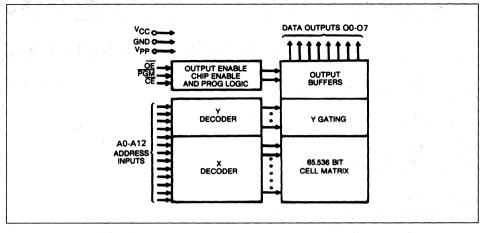

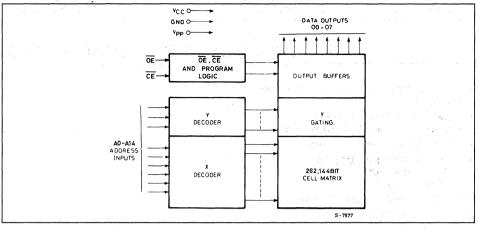

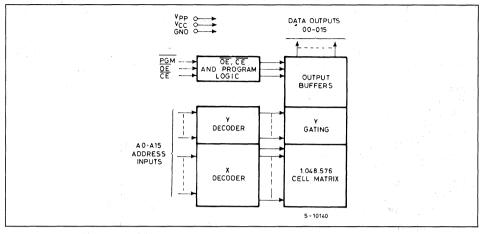

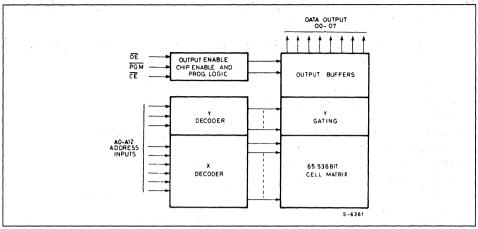

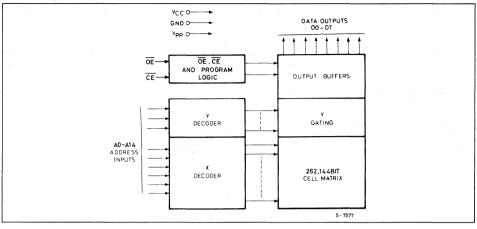

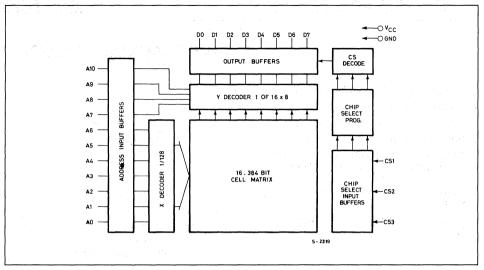

#### **BLOCK DIAGRAM**

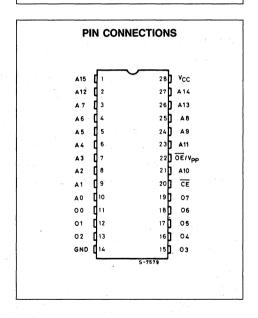

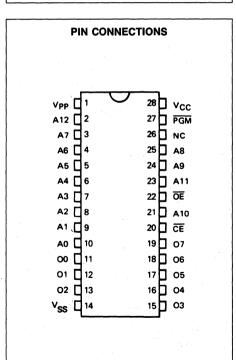

#### PIN CONNECTION DURING READ OR PROGRAM

|                 | PIN NAME/NUMBER                                              |                         |                       |                                          |                                     |  |

|-----------------|--------------------------------------------------------------|-------------------------|-----------------------|------------------------------------------|-------------------------------------|--|

| MODE            | CE/PGM<br>(E/P)<br>18                                        | 0 <u>E</u><br>(G)<br>20 | У <sub>РР</sub><br>21 | V <sub>CC</sub><br>24                    | OUTPUTS<br>9—11, 13-17              |  |

| READ<br>PROGRAM | V <sub>IL</sub><br>Pulsed V <sub>IL</sub> to V <sub>IH</sub> | V <sub>IL</sub><br>VIH  | 5<br>25               |                                          | D <sub>OUT</sub><br>D <sub>IN</sub> |  |

| * Symbols in p  | arentheses are proposed                                      | JEDEC standard.         |                       | n an | and the second second second        |  |

#### **ABSOLUTE MAXIMUM RATINGS(1)**

| Symbol           | Parameter                                                      | Value                       | Unit     |

|------------------|----------------------------------------------------------------|-----------------------------|----------|

| T <sub>amb</sub> | Temperature Under Bias<br>(Extended Temperature Range)         | - 10 to +80<br>(-50 to +95) | °C<br>°C |

| T <sub>stg</sub> | Storage Temperature                                            | -65 to +125                 | °C       |

| V <sub>PP</sub>  | V <sub>PP</sub> Supply Voltage with Respect to V <sub>SS</sub> | 26.5V to -0.3               | V        |

| V <sub>in</sub>  | All Input or Output Voltages with Respect to VSS               | 6V to -0.3                  | V        |

| PD               | Power Dissipation                                              | 1.5                         | W        |

|                  | Lead Temperature (Soldering 10 seconds)                        | + 300                       | °C       |

Note 1. "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Opera-Ing Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

#### **READ OPERATION**

DC CHARACTERISTICS<sup>(1)</sup>  $T_A = 0^{\circ}C$  to + 70°C<sup>(6)</sup>,  $V_{CC} = 5V \pm 5\%$  for M/ET2716,  $V_{CC} = 5V \pm 10\%$  for M/ET2716-1  $V_{PP} = V_{CC}^{(3)}$ ,  $V_{SS} = 0V$ , (Unless otherwise specified)

| o                | D                                        | Task Osa dikisas                                       | Values |      |                    | Unit |

|------------------|------------------------------------------|--------------------------------------------------------|--------|------|--------------------|------|

| Symbol           | Parameter                                | Test Conditions                                        | Min.   | Тур. | Max.               | Unit |

| ILI              | Input Current                            | V <sub>IN</sub> = 5.25V ORVIN = V <sub>IL</sub>        |        | —    | 10                 | μA   |

| ILO              | Output Leakage Current                   | $V_{OUT} = 5.25V, \overline{CE}/PGM = 5V$              |        | —    | 10                 | μA   |

| IPP1             | VPP Supply Current                       | V <sub>PP</sub> = 5.25V                                |        | -    | 5                  | mA   |

| ICC1             | V <sub>CC</sub> Supply Current (Standby) | $\overline{CE}/PGM = V_{IH}, \ \overline{OE} = V_{IL}$ |        | 10   | 25                 | mA   |

| I <sub>CC2</sub> | V <sub>CC</sub> Supply Current (Active)  | $\overline{CE}/PGM = \overline{OE} = V_{IL}$           | —      | 57   | 100                | mA   |

| VIL              | Input Low Voltage                        |                                                        | - 0.1  | _    | 0.8                | v    |

| VIH              | Input High Voltage                       |                                                        | 2.0    | -    | V <sub>CC</sub> +1 | v    |

| VOH              | Output High Voltage                      | l <sub>OH</sub> = - 400 μA                             | 2.4    |      | -                  | v    |

| VOL              | Output Low Voltage                       | l <sub>OL</sub> =2.1 mA                                |        |      | 0.45               | v    |

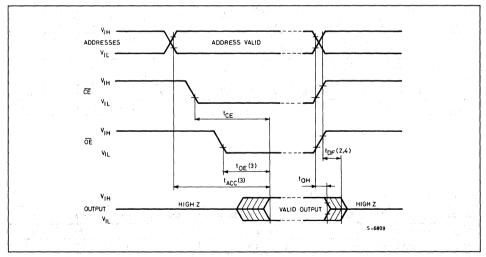

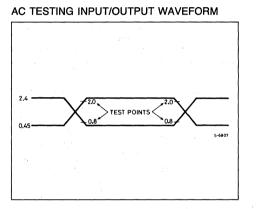

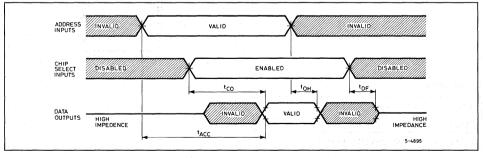

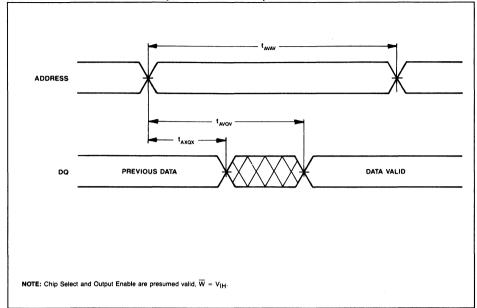

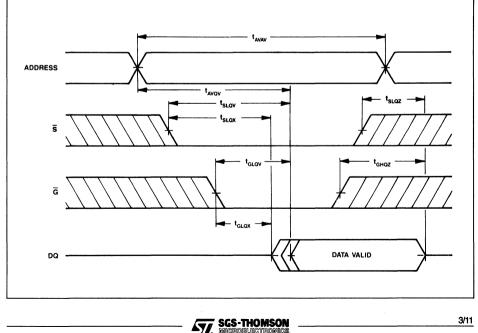

## AC CHARACTERISTICS $T_A=0^\circ C$ to + 70°C $C^{(6)},~V_{CC}=5V\pm5\%$ for M/ET2716, $V_{CC}=5V\pm10\%$ for M/ET2716-1 $V_{PP}=V_{CC}{}^{(3)},~V_{SS}=0V,$ (Unless otherwise specified).

| Symi                        | bol   |                                  |                                              | M/ET: | 2716-1 | M/ET | 2716 |      |

|-----------------------------|-------|----------------------------------|----------------------------------------------|-------|--------|------|------|------|

| Standard                    | Jedec | Parameter                        | Test Conditions                              | Min.  | Max.   | Min. | Max. | Unit |

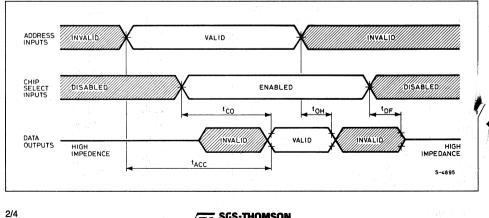

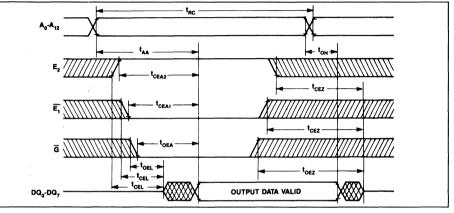

| tACC                        | TAVQV | Address to Output Delay          | $\overline{CE}/PGM = \overline{OE} = V_{IL}$ | -     | 350    | -    | 450  | ns   |

| t <sub>CE</sub>             | TELQV | CE to Output Delay               | $\overline{OE} = V_{IL}$                     | -     | 350    | -    | 450  | ns   |

| tOE                         | TGLQV | Output Enable to<br>Output Delay | $\overline{CE}/PGM = V_{IL}$                 | -     | 120    | - 1  | 120  | ns   |

| <sup>t</sup> DF<br>(Note 5) | TGHQZ | OE or CE High to<br>Output Hi-Z  | CE/PGM = V <sub>IL</sub>                     | 0     | 100    | 0    | 100  | ns   |

| tон                         | TAXQX | Address to Output Hold           | $\overline{CE}/PGM = \overline{OE} = V_{ L}$ | 0     | -      | 0    |      | ns   |

| top                         | TEHQZ | CE to Output Hi-Z                | $\overline{OE} = V_{IL}$                     | 0     | 100    | 0    | 100  | ns   |

#### CAPACITANCE $^{(4)}$ T<sub>A</sub> = 25°C, f = 1 MHz

| Symbol | Parameter          | Test Conditions      | Min. | Тур. | Max. | Units |

|--------|--------------------|----------------------|------|------|------|-------|

| CIN    | Input Capacitance  | V <sub>IN</sub> =0V  |      | 4    | 6    | pF    |

| COUT   | Output Capacitance | V <sub>OUT</sub> =0V |      | 8    | 12   | pF    |

Notes 1. VCC must be applied at the same time or before VPP and removed after or at the same time as Vpp 2. Typical conditions are for operation at: T<sub>A</sub> = 25°C, VCC = 5V, VPP = VCC, and VSS = OV

3. VPP may be connected to VCC except during program.

4. Capacitance is guaranteed by periodic testing. T<sub>A</sub> = 25°C, f = 1 MHz.

5. t<sub>D</sub>r is specified from OE or CE wich ever occurs first. This parameter as only sampled and not 100% tested.

6. T<sub>A</sub> = - 40°C To + 85°C for the F6 version (extended To range).

#### ET2716/M2716

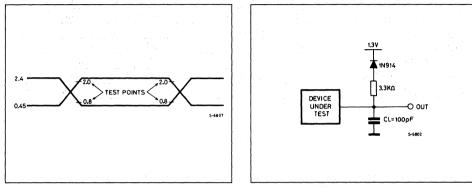

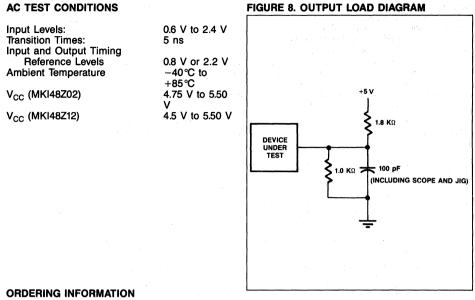

#### AC TEST CONDITIONS

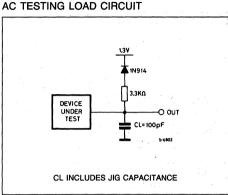

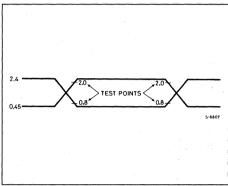

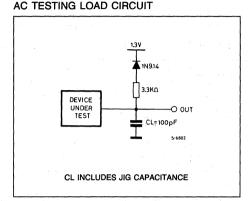

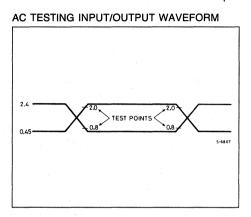

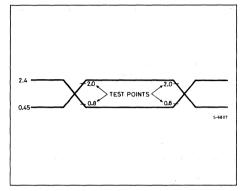

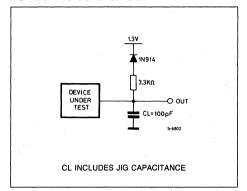

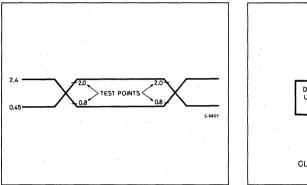

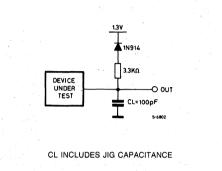

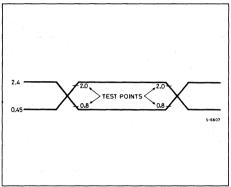

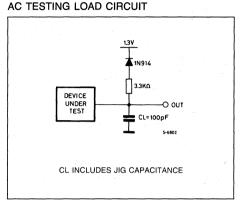

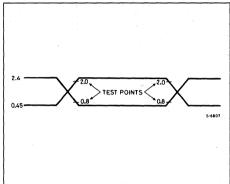

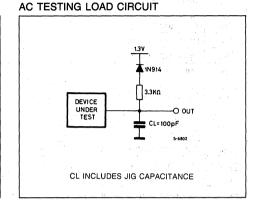

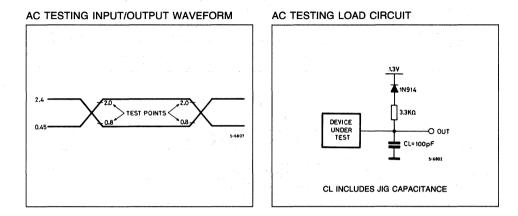

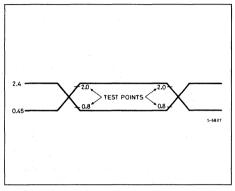

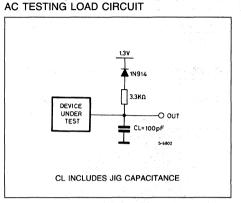

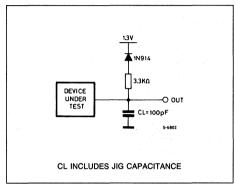

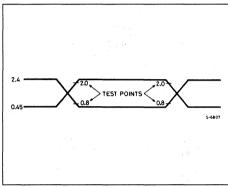

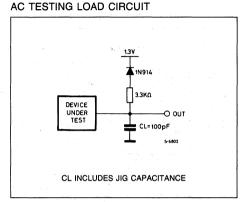

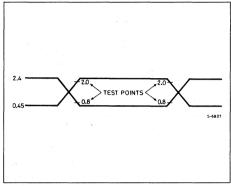

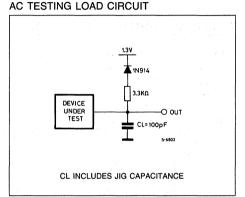

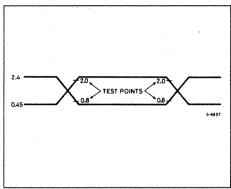

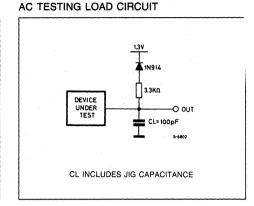

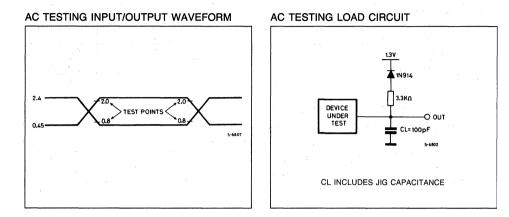

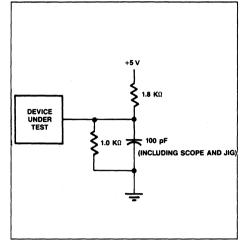

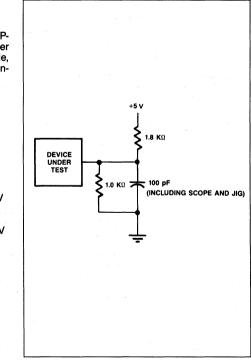

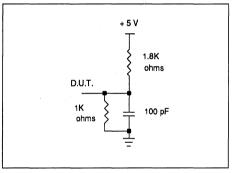

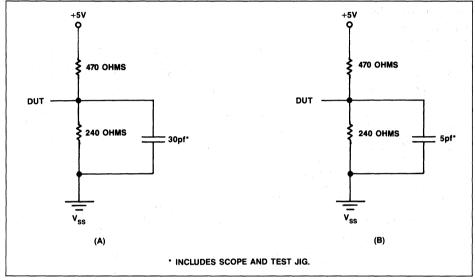

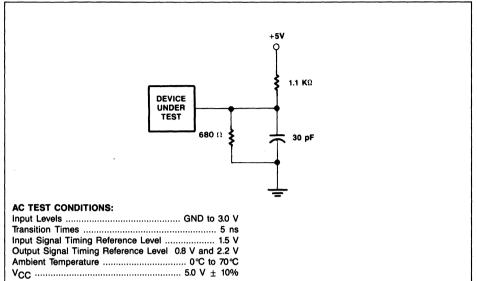

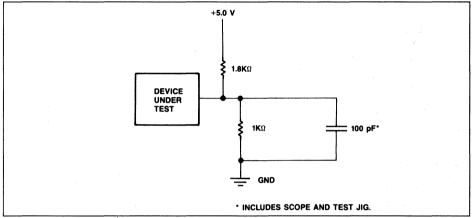

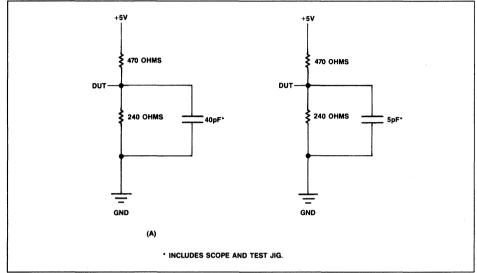

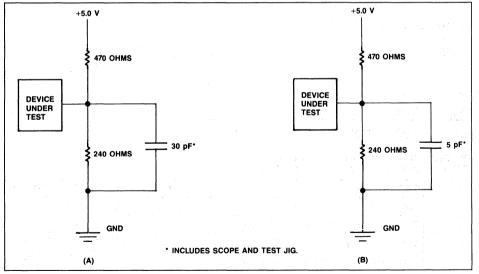

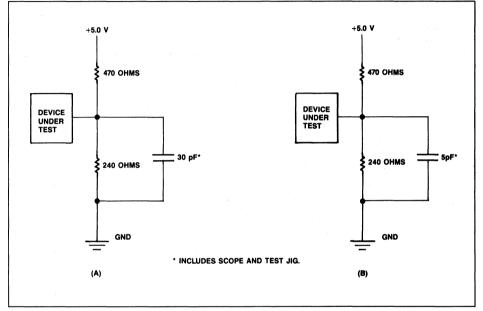

Output Load: 1 TTL gate and CL = 100 pF ≤20 ns Input Rise and Fall Times Input pulse levels: 0.45V to 2.4V Timing Measurement Reference Level Inputs, Outputs 0.8V and 2V

AC TESTING INPUT/OUTPUT WAVEFORM

#### AC TESTING LOAD CIRCUIT

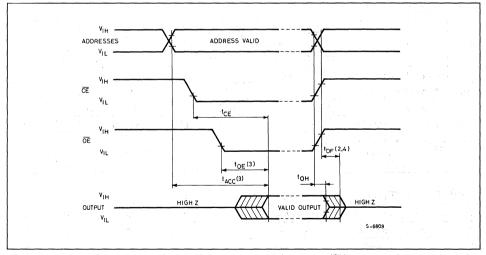

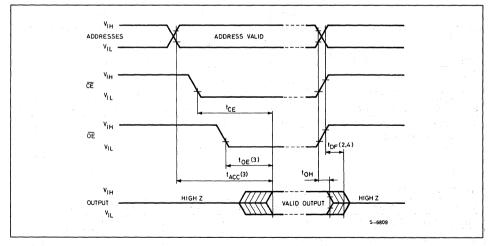

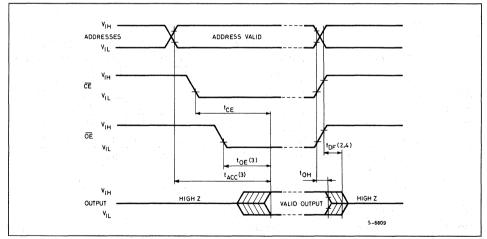

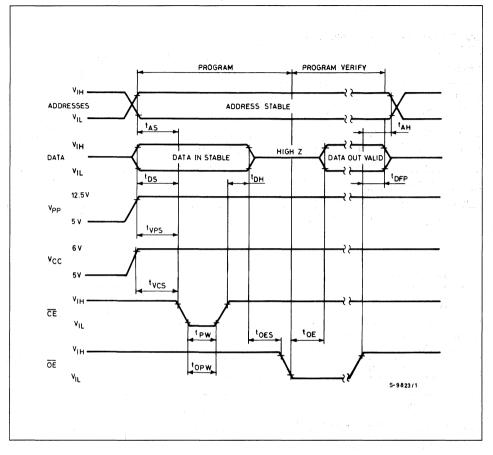

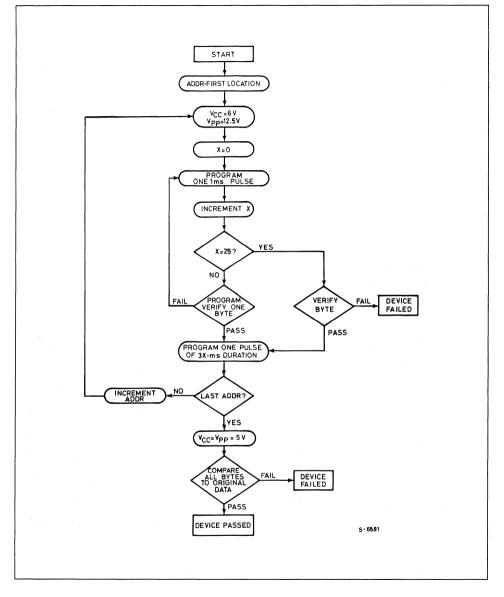

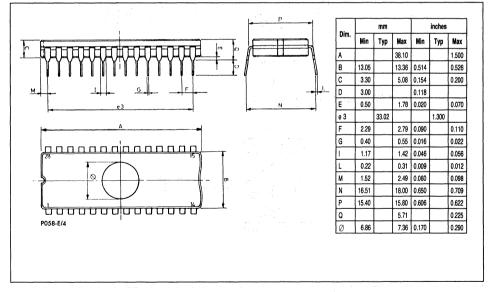

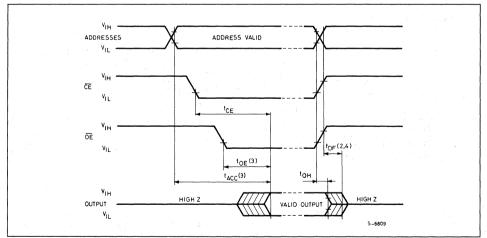

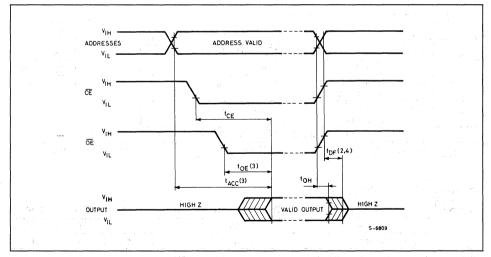

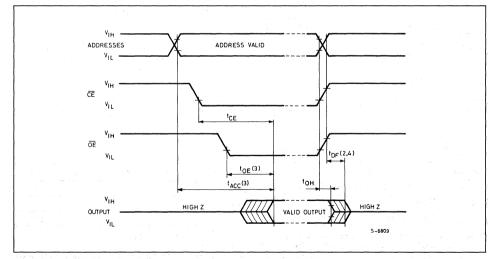

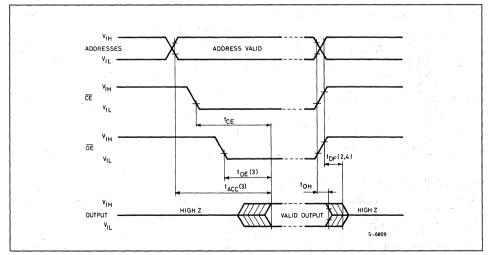

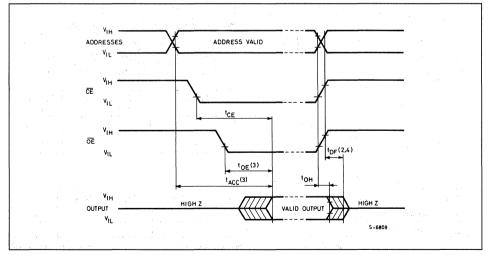

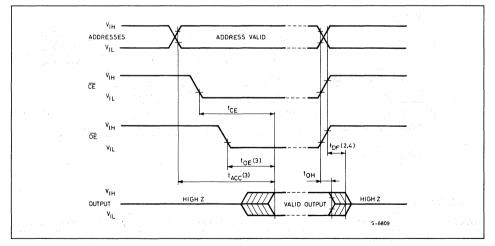

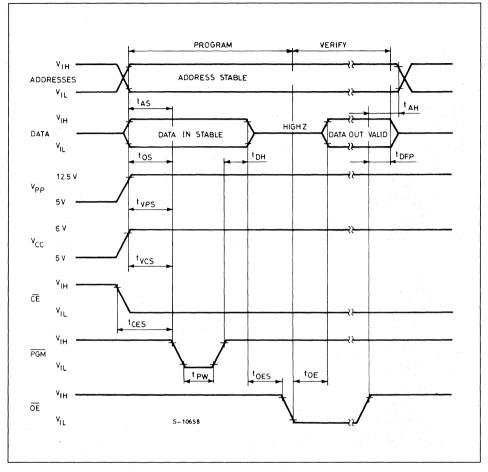

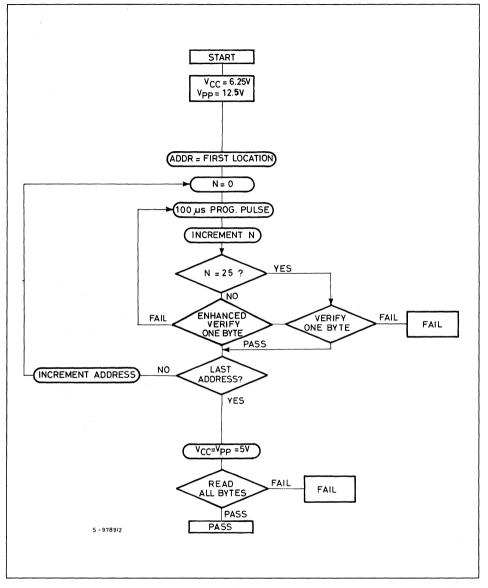

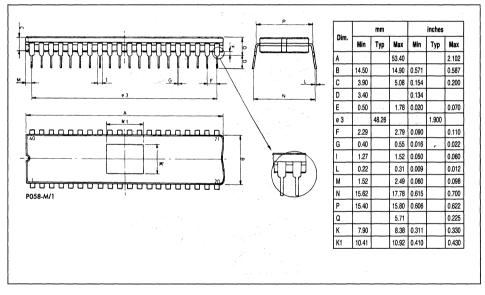

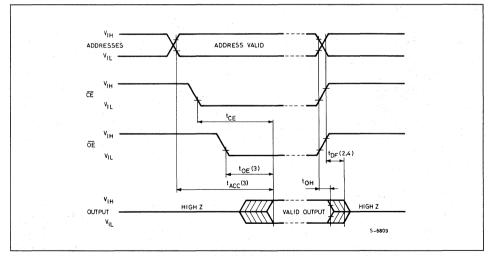

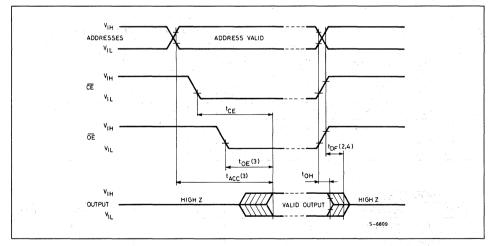

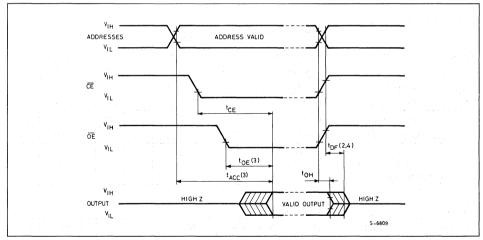

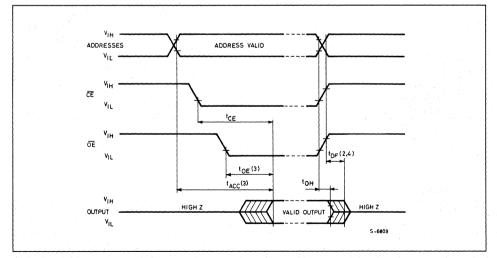

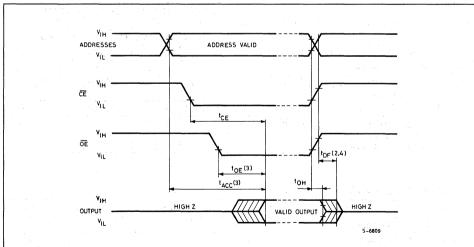

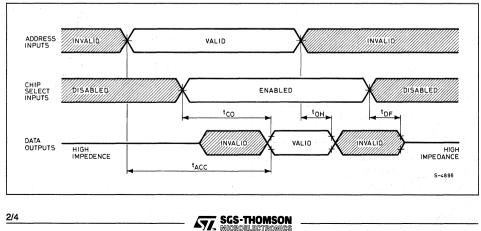

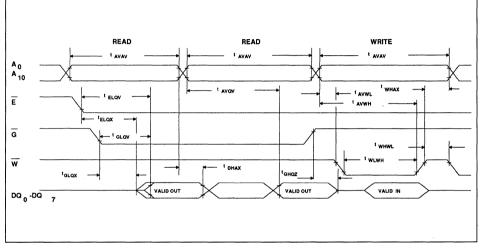

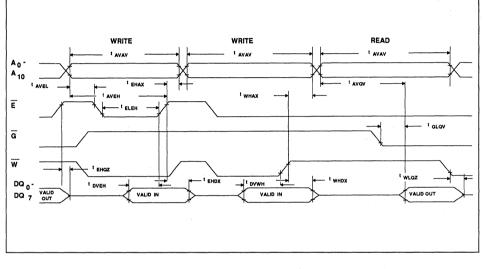

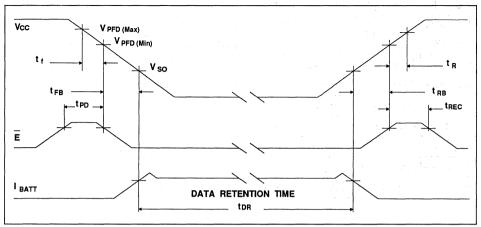

AC WAVEFORMS

#### Notes:

Typical values are for T<sub>amb</sub> = 25°C and nominal supply voltage

This parameter is only sampled and not 100% tested.

OE may be delayed up to t<u>ACC</u> + to after the falling edge CE without impact on tACC

Up is specified form OE or CE whichever occurs first.

4/9 28

#### **DEVICE OPERATION**

The M/ET2716 has 3 modes of operation in the normal system environment. These are shown in Table 1.

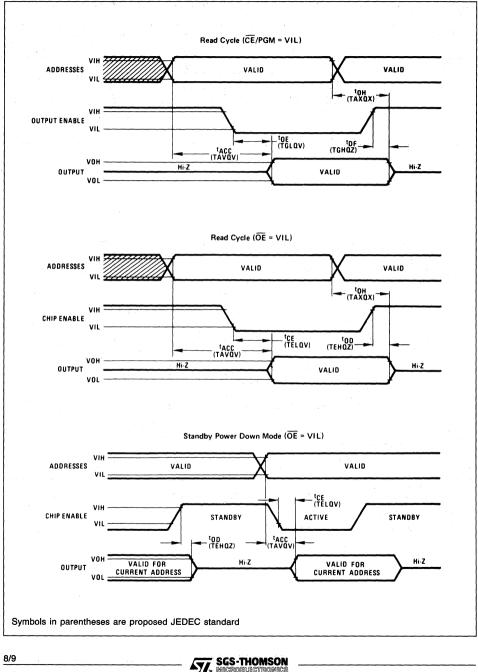

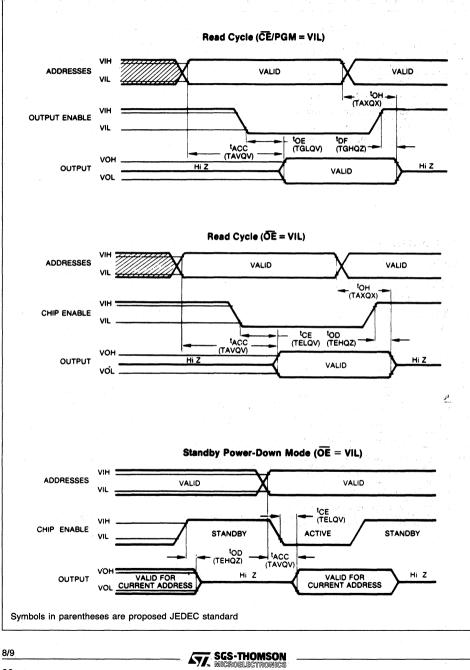

#### READ MODE

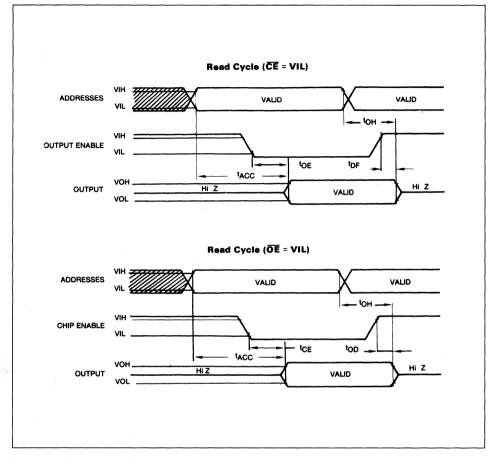

The <u>M/ET2716</u> read operation requires that  $\overline{OE}$  = VIL,  $\overline{CE}/PCM$  = VIL and that addresses A0 – A10 have been stabilized. Valid data will appear on the output pins after t<sub>ACC</sub>, t<sub>OE</sub> or t<sub>CE</sub> times (see Swithching Time Waveforms) depending on wich is limiting.

#### DESELECT MODE

The M/ET2716 is deselected by making  $\overline{OE}$  = VIH. This mode is independent of  $\overline{CE}/PGM$  and the condition of the adresses. The outputs are Hi-Z when  $\overline{OE}$  = VIH. This allows OR-tying 2 or more M/ET2716's for memory expansion.

#### STANDBY MODE (Power Down)

The M/ET2716 may be powered down to the standby mode by making CE/PGM = VIH. This is independent of OE and automatically puts the outputs in their Hi-Z state. The power is reduced to 25% (132 mW max) of the normal operating power. VCC and VPP must be maintened at 5V. Access time at power up remains either t<sub>ACC</sub> or t<sub>CE</sub> (see Switching Time Waveforms).

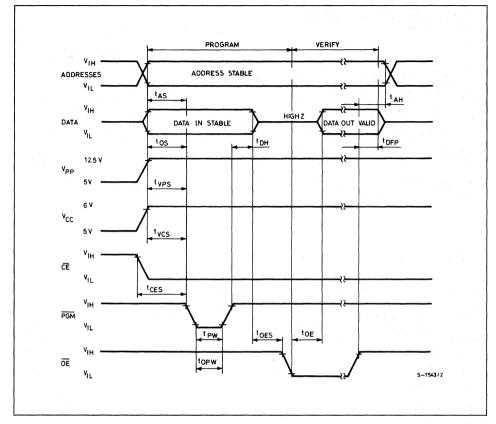

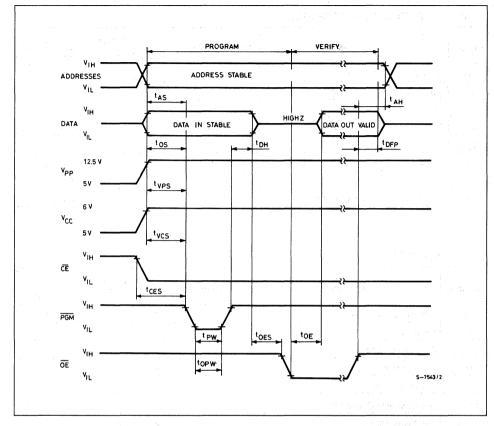

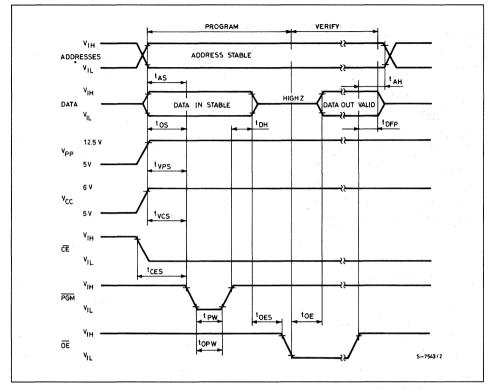

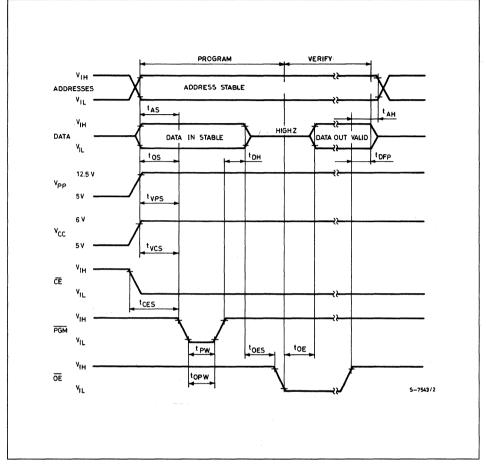

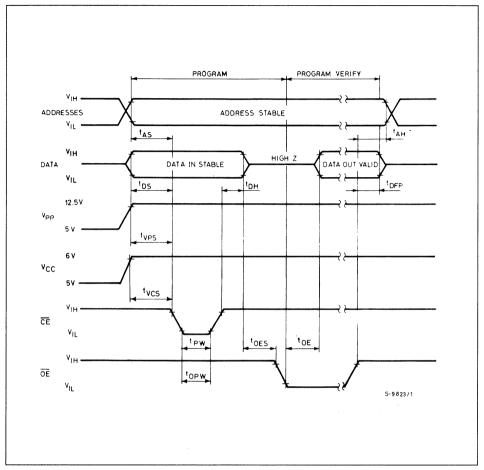

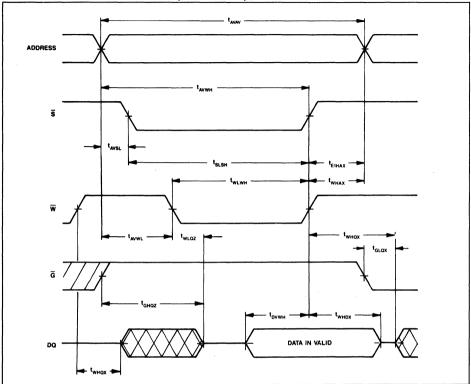

#### PROGRAMMING

The M/ET2716 is shipped from SGS-THOMSONcompletely erased. All bits will be at "1" level (output high) in this initial state and after any full erasure. Table II shows the 3 programming modes.

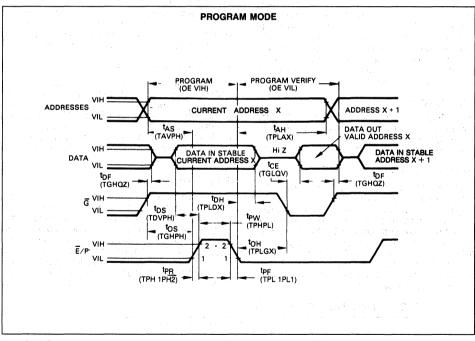

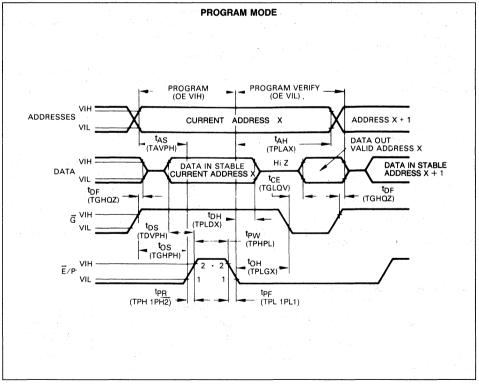

#### **PROGRAM MODE**

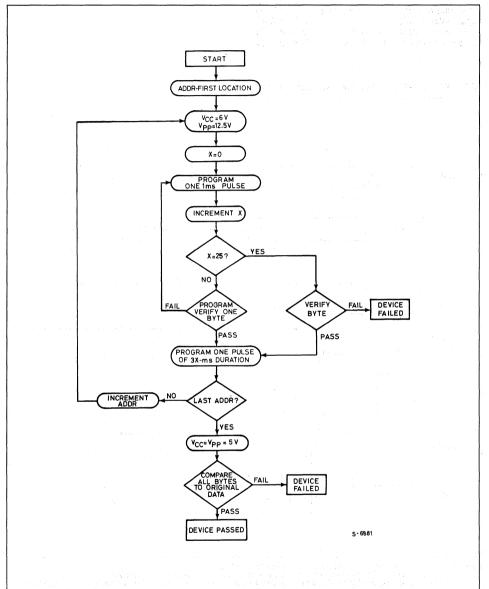

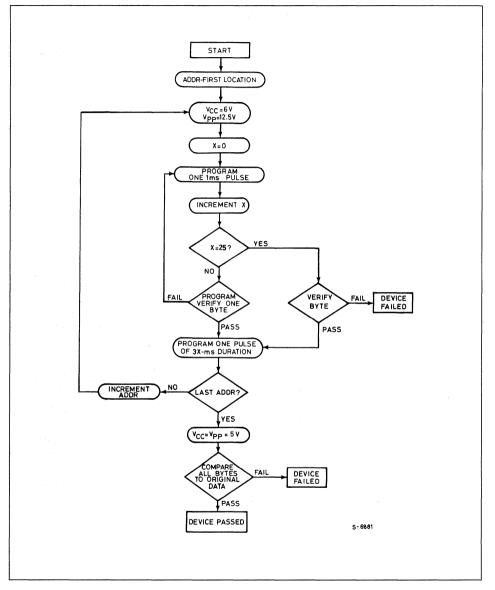

The M/ET2716 is programmed by introducing "0" s into the desidered locations. This is done 8 bits (a byte) at a time. Any individual address, a sequence of addresses, or addresses chosen at random may be programmed. Any or all of the 8 bits associated with an address location may be programmed with a single program pulse applied to the chip enable pin. All input voltage levels including the program pulse on chip enable are TTL compatible. The programming sequence is:

#### TABLE II. PROGRAMMING MODES (V<sub>CC</sub> = 5V)

|          | PIN             | PIN NAME/NUMBER |                  |  |  |

|----------|-----------------|-----------------|------------------|--|--|

| MODE     | CE/PGM<br>(E/P) | OE<br>(G)       | OUTPUTS          |  |  |

|          | 18              | 20              | 9—11, 13-17      |  |  |

| READ     | VIL             | VIL             | D <sub>OUT</sub> |  |  |

| DESELECT | Don't Care      | V <sub>IH</sub> | Hi-Z             |  |  |

| STANDBY  | VIH             | Don't Care      | Hi-Z             |  |  |

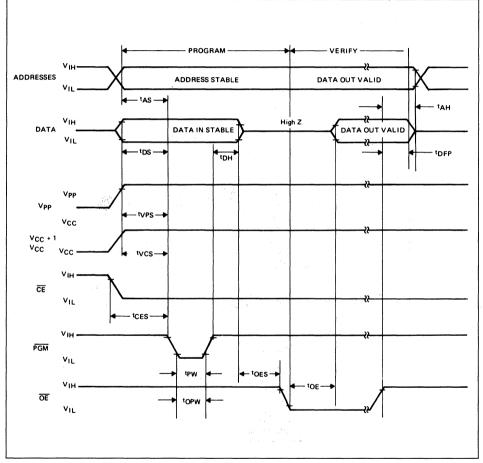

With Vpp = 25V, VCC = 5V,  $\overline{OE} = V_{IH}$  and  $\overline{CE}/PGM = V_{IL}$ , an address is selected and the desired data word is applied to the output pins. ( $V_{IL} = "0"$  and  $V_{IL} = "1"$  for both address and data). After the address and data signals are stable the program pin is pulsed from  $V_{II}$  to  $V_{IH}$