**OMTI 8640 Technical Reference Manual**

Scientific Micro Systems, Inc.

OMTI 8640 AT - ESDI Controller Technical Reference Manual June, 1989

# NOTICE

The information contained in this document is subject to change without notice

SCIENTIFIC MICRO SYSTEMS MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL; INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Scientific Micro Systems shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Scientific Micro Systems.

# SCIENTIFIC MICRO SYSTEMS, INC. 777 E. Middlefield Road, Mountain View, CA 94043

TEL: 415-964-5700 TWX: 910-379-6577 TLX: 184160 SMS MNTV

# Copyright 1989 SCIENTIFIC MICRO SYSTEMS, INC. All Rights Reserved OMTI<sub>TM</sub> is a registered trademark of Scientific Micro Systems, Inc.

PRINTED IN THE UNITED STATES OF AMERICA

### **PRINTING HISTORY**

New editions are complete revisions of the manual. The date on the title page of the manual changes only when a new edition is published.

First Edition Second Edition November, 1988 June, 1989 Rev A Rev B

# LIST OF EFFECTIVE PAGES

The List of Effective Pages gives the date of the current edition, and lists the dates of all changed pages. Changes are marked with a vertical bar in the margin.

| Current Edition<br>Second Edition            | November, 1988<br>June, 1989 | Rev A<br>Rev B |

|----------------------------------------------|------------------------------|----------------|

| Pages effected:                              |                              |                |

| Cover pages<br>Page 17<br>Page 25<br>Page 37 |                              |                |

# OMTI 8640 AT - ESDI CONTROLLER TECHNICAL MANUAL

# TABLE OF CONTENTS

| <b>SECTION 1</b>                       | : | INTRODUCTION                                                                                                                                            | 1                          |

|----------------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1.1<br>1.2                             |   | Product Description<br>Specification                                                                                                                    | 1<br>2                     |

| SECTION 2                              | : | HOST & DRIVE INTERFACE DEFINITIONS                                                                                                                      | 7                          |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5        |   | Introduction<br>Input/Ouput Channel Pin Assignments<br>Input/Output Channel Signal Description<br>Winchester Track and Sector Format<br>Pin Assignments | 7<br>7<br>10<br>14<br>15   |

| SECTION 3                              | : | CONFIGURATION AND INSTALLATION                                                                                                                          | 17                         |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5        |   | Handling<br>Installation<br>Jumper Settings<br>Installation of Controller in system with one drive<br>Installation of two drive system                  | 17<br>17<br>17<br>18<br>27 |

| <b>SECTION 4</b>                       | : | 8640 WINCHESTER SECTION                                                                                                                                 | 29                         |

| 4.1<br>4.2                             |   | Read Register Definitions<br>8640 Write Register Definitions                                                                                            | 29<br>33                   |

| <b>SECTION 5</b>                       | : | FLOPPY DISK REGISTERS                                                                                                                                   | 4 2                        |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 |   | Floppy Disk Registers<br>Floppy Disk Protocol<br>Floppy Disk Command Summary<br>Description of Symbols<br>Floppy Commands<br>Command Status Registers   | 42<br>44<br>45<br>46<br>50 |

# LIST OF FIGURES

| 1.1 | Functional Organization (Block Diagram) | 4 |

|-----|-----------------------------------------|---|

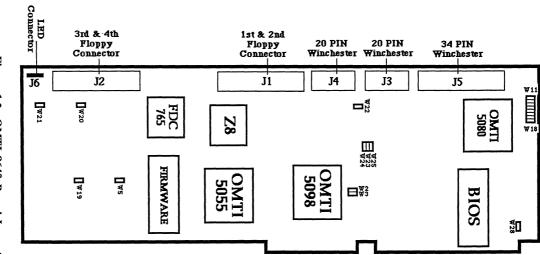

| 1.2 | 8640 Board Layout                       | 5 |

.

٠

# **1.1 PRODUCT DESCRIPTION**

The OMTI 8640 controller is a combination ESDI disk drive and floppy disk controller for IBM AT Bus compatible computers (16 bit data path). The controller is contained on a single PCB that plugs into an empty slot of the computer's motherboard.

The OMTI 8640 controller uses SMS's sophisticated VLSI circuitry to provide many advanced features. These include:

- Support for two ESDI disk drives. Drives may have different capacities or come from different manufacturers.

- Support for high capacity (up to 1.44 Megabytes) floppies.

- High performance (1:1 interleave on disk).

- 32 Kbyte buffer minimum.

- Full Track Cache Option.

- 56 bit Error Correction Code.

- · Concurrent data operations on winchester and floppy disks.

- · Support for Hard or Soft Sectored ESDI disk drives.

- Supports ESDI disks which run at a data rate of 10 Mbit/sec or the newer drives which run at 15 Mbit/sec.

- · On-board BIOS which gives the user the following features:

Low level format utility. Ability to read the ESDI drive parameters. Automatic support for non-standard drive types. Ability to automatically read the ESDI defect map. Cylinder and Head skewing options. Surface Analysis to insure data reliability.

- Sector level defect mapping. Sector sparing and sector flagging options provided.

- Variable sectors per track support.

- Conversion Mode. Based on 62 sectors per track and 16 heads. This mode automatically provides support for drives with greater than 1024 cylinders.

- 8640 is XT height.

### **1.2 SPECIFICATION**

# 1.2.1 Features

WINCHESTER DISKS

- Operates up to two hard or soft sectored ESDI compatible Winchester disks.

- Support for ESDI Drive transfer rates of 10 Mbit/sec or 15 Mbit/sec.

- Supports programmable sector size.

- Supports programmable sector interleave including one to one interleave.

- Addresses up to 2048 tracks (cylinders) and 16 heads.

- Word (16 bits) width data transfer on AT bus.

### FLOPPY DISKS

- Operates up to four floppy disk drives.

- Supports 48 and 96 TPI drives plus the high density AT compatible drives.

- Supports 250, 300, or 500 K bits/sec transfer rate including dual rotational speed floppies.

- Host has direct access to floppy disk controller chip (NEC 765 or equivalent).

# 1.2.2 Physical Specifications of the OMTI 8640 controller

| 8640         |

|--------------|

| 13.25 inches |

| 3.9 inches   |

| .75 inches   |

|              |

# 1.2.3 Environmental Specifications

|                   | Operating       | Storage                 |

|-------------------|-----------------|-------------------------|

| Temperature       | 0 to 50 ° C     | 40 to 75 ° C            |

| Relative Humidity | 10 to 95% N.C.  | 10 to 95% Noncondensing |

| Maximum Wet Bulb  | 30 deg C        | Noncondensing           |

| Altitude          | 0 to 10,000 ft. | 0 to 15,000 ft.         |

# 1.2.4 Power Requirements of the OMTI 8640 controller

| Voltage                  | 4.75 to 5.25 VDC |

|--------------------------|------------------|

| Maximum ripple and noise | 100 mv           |

| Maximum current drawn    | 1.0 Amp max      |

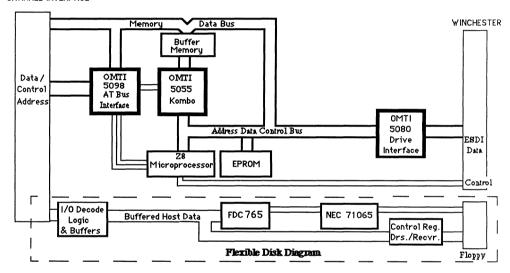

Figure 1.1 Functional Organization (Block Diagram)

•

•

. . ٠

# 2.1. INTRODUCTION

The OMTI 8640 Data Controller is electrically and mechanically compatible with the bus or Input/Output channel used in the IBM AT computer. Physically this Input/Output channel is contained on two card edge connectors.

The Input/Output channel provides the necessary hardware interface to the host CPU to allow it to communicate with the controller.

INPUT/OUTPUT CHANNEL (COMPONENT SIDE of 62 pin EDGE CONNECTOR)

### 2.2 INPUT/OUTPUT CHANNEL PIN ASSIGNMENTS

The following figures summarize pin assignments for the Input/Output channel connectors.

| I/O | Signal Name | Input/Output |

|-----|-------------|--------------|

| A1  | -I/O CH CK  | Ι            |

| A2  | SD7         | I/O          |

| A3  | SD6         | I/O          |

| A4  | SD5         | I/O          |

| A5  | SD4         | I/O          |

| A6  | SD3         | I/O          |

| A7  | SD2         | Ι/O          |

| A8  | SD1         | I/O          |

| A9  | SD0         | Í/O          |

| A10 | I/O CH RDY  | Í            |

| A11 | AEN         | 0            |

| A12 | SA19        | I/O          |

| A13 | SA18        | Ι/O          |

| A14 | SA17        | I/O          |

| A15 | SA16        | I/O          |

| A16 | SA15        | I/O          |

| A17 | SA14        | I/O          |

| A18 | SA13        | I/O          |

| A19 | SA12        | I/O          |

| A20 | SA11        | I/O          |

| A21 | SA10        | I/O          |

| A22 | SA9         | I/O          |

| A23 | SA8         | I/O          |

| A24 | SA7         | I/O          |

| A25 | SA6         | I/O          |

| A26 | SA5         | Ϊ/O          |

| A27 | SA4         | I/O          |

| A28 | SA3         | I/O          |

| A29 | SA2         | I/O          |

| A30 | SA1         | I/O          |

| A31 | SA0         | I/O          |

| r       |                  |        |  |  |

|---------|------------------|--------|--|--|

| I/O Pin | Signal Name      | I/O    |  |  |

| B1      | GND              | Ground |  |  |

| B2      | <b>RESET DRV</b> | 0      |  |  |

| B3      | +5 Vdc           | Power  |  |  |

| B4      | IRQ9             | I      |  |  |

| B5      | -5 Vdc           | Power  |  |  |

| B6      | DRQ2             | I      |  |  |

| B7      | -12 Vdc          | Power  |  |  |

| B8      | -OWS             | I      |  |  |

| B9      | +12 Vdc          | Power  |  |  |

| B10     | GND              | Ground |  |  |

| B11     | -SMEMW           | 0      |  |  |

| B12     | -SMEMR           | Ō      |  |  |

| B13     | -IOW             | I/O    |  |  |

| B14     | -IOR             | Ī/Ō    |  |  |

| B15     | -DACK3           | Ō      |  |  |

| B16     | DRQ3             | Ī      |  |  |

| B17     | -DACK1           | 0      |  |  |

| B18     | DRQ1             | I      |  |  |

| B19     | -Refresh         | Ī/O    |  |  |

| B20     | CLK              | Õ      |  |  |

| B21     | IRQ7             | Ī      |  |  |

| B22     | IRQ6             | I      |  |  |

| B23     | IRQ5             | I      |  |  |

| B24     | IRQ4             | I      |  |  |

| B25     | IRQ3             | Ī      |  |  |

| B26     | -DACK2           | Ō      |  |  |

| B27     | T/C              | ō      |  |  |

| B28     | BALE             | Ō      |  |  |

| B29     | +5 Vdc           | Power  |  |  |

| B30     | OSC              | O      |  |  |

| B31     | GND              | Ground |  |  |

# Input/Output Channel (SOLDER SIDE of 62 pin EDGE CONNECTOR)

| I/O Pin | Signal Name | I/O |  |

|---------|-------------|-----|--|

| C1      | -SBHE       | I/O |  |

| C2      | LA23        | Ϊ/O |  |

| C3      | LA22        | I/O |  |

| C4      | LA21        | I/O |  |

| C5      | LA20        | I/O |  |

| C6      | LA19        | Ι/O |  |

| C7      | LA18        | ΪO  |  |

| C8      | LA17        | Ϊ/O |  |

| C9      | -MEMR       | ΪO  |  |

| C10     | -MEMW       | Ι/O |  |

| C11     | SDO8        | Ϊ/O |  |

| C12     | SDO9        | ΪO  |  |

| C13     | SD10        | Ϊ/O |  |

| C14     | SD11        | ΪO  |  |

| C15     | SD12        | I/O |  |

| C16     | SD13        | I/O |  |

| C17     | SD14        | Ϊ/O |  |

| C18     | SD15        | Ϊ/O |  |

# Input/Output Channel (COMPONENT SIDE of 36 pin EDGE CONNECTOR)

# Input/Output Channel (SOLDER SIDE of 36 pin EDGE CONNECTOR)

| I/O Pin | Signal Name | I/O   |  |

|---------|-------------|-------|--|

| D1      | -MEM CS16   | Ι     |  |

| D2      | -I/O CS 16  | I     |  |

| D3      | IRQ10       | I     |  |

| D4      | IRÕ11       | I     |  |

| D5      | IRQ12       | I     |  |

| D6      | IRÕ13       | I     |  |

| D7      | IRÕ14       | I     |  |

| D8      | -DÂCK0      | 0     |  |

| D9,     | DRQ0        | I     |  |

| D10     | -DACK5      | 0     |  |

| D11     | DRQ5        | I     |  |

| D12     | -DACK6      | 0     |  |

| D13     | DRQ6        | I     |  |

| D14     | -DACK7      | 0     |  |

| D15     | DRQ7        | I     |  |

| D16     | +5 Vdc      | Power |  |

| D17     | -MASTER     | I     |  |

| D18     | GND         | GND   |  |

# 2.3 INPUT/OUTPUT CHANNEL SIGNAL DESCRIPTION

The following is a description of the system boards INPUT/OUTPUT channel signals. All signal lines are TTL-compatible. Input/Output adapters should be designed with a maximum of two low-power Shottky (LS) loads per line. Signals preceded by a hyphen (-) indicate that the signal is in an active low state.

# SAO through SA19 (Input/Output)

Address bits 0 through 19 are used to address memory and Input/Output devices within the system. These 20 address lines, in addition to LA17 through LA23, allow access of up to 16Mb of memory. SA0 through SA19 are gated on the system bus when "BALE" is high and are latched on the falling edge of "BALE." These signals are generated by the microprocessor or DMA Controller. They also may be driven by other microprocessors or DMA controllers that reside on the Input/Output channel.

# LA17 through LA23 (Input/Output)

These signals (unlatched) are used to address memory and Input/Output devices within the system. They give the system up to 16Mb of addressability. These signals are valid when "BALE" is high. LA17 through LA23 are not latched during microprocessor cycles and therefore do not stay valid for the whole cycle. Their purpose is to generate memory decodes for 1 wait-state memory cycles. These decodes should be latched by Input/Output adapters on the falling edge of "BALE." These signals also may be driven by other microprocessors or DMA controllers that reside on the Input/Output channel. Note that it is these signals that are decoded by the Input/Output adapter to generate "MEM CS16" for 16 bit, 1 wait -state memory cycles.

# CLK (Output)

This is the 6-MHz system clock. It is a synchronous microprocessor cycle clock with a cycle time of 167 nanoseconds. The clock has a 50% duty cycle. This signal should only be used for synchronization. It is not intended for uses requiring a fixed frequency.

### **RESET DRV (Output)**

"Reset drive" is used to reset or initialize system logic at power-up time or during a low line-voltage outage. This signal is active high.

### SD0 through SD15 (Input/Output)

These signals provide bus bits 0 through 15 for the microprocessor, memory, and Input/Output devices. DO is the least-significant bit and D15 is the most significant bit. All 8-bit devices on the Input/Output channel should use DO through D7 for communications to the microprocessor. The 16-bit devices will use DO through D15. To support 8-bit devices, the data on D8 through D15 will be gated to D0 through D7 during 8-bit transfers to these devices; 16-bit microprocessor transfers to 8-bit devices will be converted to two 8-bit transfers.

### **BALE** (Output)(buffered)

"Address latch enable" is provided by the 82288 Bus Controller and is used on the system board to latch valid addresses and memory decodes from the microprocessor. It is available to the Input/Output channel as an indicator of a valid microprocessor or DMA address (when used with "AEN"). Microprocessor addresses SA0 through SA19 are latched with the falling edge of "BALE." "BALE" is forced high during DMA cycles. Note: "BALE" is usually used by the IO adapter only to latch the LA17-LA23 address lines (or the decode of LA17-LA23 that indicates an address match for the IO adapter). "BALE" may not occur on all 8-bit Input/Output cycles (which use only address lines SA0-SA9 for device decoding) or on some 8-bit memory transfers.

### Input/Output CH RDY (Input)

"Input/Output channel ready" is pulled low (not ready) by a memory or Input/Output device to lengthen Input/Output memory cycles. Any slow device using this line should drive it low immediately upon detecting its valid address and a Read or Write command. Machine cycles are extended by an integral number of clock cycles (167 nanoseconds). This signal should be held low for no more than 2.5 microseconds.

### IRQ3-IRQ7, IRQ9-IRQ12 and IRQ 14 through 15 (Input)

Interrupt Requests 3 through 7, 9 through 12, and 14 are used to signal the microprocessor that an Input/Output device needs attention. These interrupt requests are prioritized, with IRQ9 through IRQ 12 and IRQ 14 through IRQ15 having the highest priority (IRQ9 is the highest) and IRQ3 through IRQ7 having the lowest priority (IRQ7 is the lowest). An interrupt request is generated when an IRQ line is raised from low to high. The line must be held high until the microprocessor acknowledges the interrupt request (Interrupt Service routine). Interrupt 13 is used on the system board and is not available on the Input/Output channel. Interrupt 8 is used for the real-time clock.

### -IOR (Input/Output)

'Input/Output Read' instructs an Input/Output device to drive its data onto the databus. It may be driven by the system microprocessor or DMA controller, or by a microprocessor or DMA controller resident on the Input/Output channel. This signal is active low.

### -IOW (Input/Output)

"-Input/Output Write" instructs an Input/Output device to read the data on the data bus. It may be driven by any microprocessor or DMA controller in the system. This signal is active low.

### -SMEMR (Output) -MEMR (Input/Output)

These signals instruct the memory devices to drive data onto the data bus. "-SMEMR" is active only when the memory decode is within the low 1Mb of memory space. "-MEMR" is active on all memory read cycles. "-MEMR" may be driven by any microprocessor or DMA controller in the system. -SMEMR" is derived from "-MEMR" and the decode of the low 1 Mb of memory. When a microprocessor on the Input/Output channel wishes to drive "-MEMR", it must have the address lines valid on the bus for one system clock period before driving "-MEMR active. Both signals are active LOW.

# -SMEMW (Output) -MEMW (Input/Output)

These signals instruct the memory devices to store the data present on the data bus. "-SMEMW" is active only when the memory decode is within the low 1Mb of the memory space. "-MEMW" is active on all memory read cycles. "-MEMW" may be driven by any microprocessor or DMA controller in the system. "-SMEMW" is derived from "-MEMW" and the decode of the low 1Mb of memory. When a microprocessor on the Input/Output channel wishes to drive "MEMW", it must have the address lines valid on the bus for one system clock period before driving "-MEMW" active. Both signals are active low.

# DRQ0-DRQ3 and DRQ5-DRQ7 (Input)

DMA Requests 0 through 3 and 5 through 7 are asynchronous channel requests used by peripheral devices and the Input/Output channel microprocessors to gain DMA service (or control of the system). They are prioritized, with "DRQ0" having the highest priority and "DRQ7" having the lowest. A request is generated by bringing a DRQ line to an active level. A DRQ line must be held high until the corresponding "DMA Request Acknowledge" (DACK) line goes active. "DRQ0" through "DRQ3" will perform 8-bit DMA transfers; "DRQ5" through "DRQ7" will perform 16-bit transfers. "DRQ4" is used on the system board and is not available on the Input/Output channel.

# -DACK to -DACK3 and -DACK5 to -DACK7 (Output)

-DMA Acknowledge 0 to 3 and 5 to 7 are used to acknowledge DMA requests (DRQ) through DRQ7). They are active low.

### AEN (Output)

"Address Enable" is used to degate the microprocessor and other devices from the Input/Output channel to allow DMA transfers to take place. When this line is active, the DMA controller has control of the address bus, the data-bus READ command lines (memory and Input/Output, and the Write command lines (memory and Input/Output).

### -REFRESH (Input/Output)

This signal is used to indicate a refresh cycle and can be driven by a microprocessor on the Input/Output channel.

### T/C (Output)

"Terminal Count" provides a pulse when the terminal count for any DMA channel is reached.

### -SBHE (Input/Output)

"Bus High Enable" indicates a transfer of data on the upper byte of the data bus, SD8 through SD15. Sixteen-bit devices use "-SBHE" to condition data bus buffers tied to SD8 through SD15.

13

### -SBHE AND SAO ENCODINGS:

### -SBHE SAO FUNCTION

| 0 | 0 | WORD TRANSFER             |

|---|---|---------------------------|

| 0 | 1 | BYTE TRANSFER ON SD8-SD15 |

| 1 | 0 | BYTE TRANSFER ON SD0-SD7  |

| 1 | 1 | RESERVED                  |

### -MASTER (Input)

This signal is used with DRQ line to gain control of the system. A processor or DMA controller on the Input/Output channel may issue a DRQ to a DMA channel in cascade mode and receive a "-DACK". Upon receiving the "-DACK", an Input/Output microprocessor may pull "-MASTER" low, which will allow it to control the system address, data, and control lines (a condition known as tri-state). After -MASTER" is low, the Input/Output microprocessor must wait one system clock period before driving the address and data lines, and two clock periods before issuing a Read or Write command. If this signal is held low for more than 15 microseconds, system memory may be lost because of a lack of refresh.

# -MEM CS16 (Input)

"-MEM16 Chip Select" signals the system board if the present data transfer is a 1 wait-state, 16bit memory cycle. It must be derived from the decode of LA17 through LA23. Note that this requires that all 16-bit memory devices must occupy at least 128 kbytes of address space on the Bus and must not decode the SA address lines as a condition to driving "-MEM CS16" as the SA lines are not valid in time to meet the "-MEM CS16" timing requirements. "-MEM CS16" should be driven with an open-collector or tri-state driver capable of sinking 20 mA.

#### -Input/Output CS16 (Input)

"-Input/Output 16 bit Chip Select" signals the system board that the present data transfer is a 16bit, 1 wait-state, Input/Output cycle. It is derived from an address decode. "Input/Output CS16" is active low and should be driven with an open collector or tri-state driver capable of sinking 20mA.

### OSC (Output)

"Oscillator" (OSC) is a high-speed clock with a 70 nanosecond period (14.31818 MHz). This signal is not synchronous with the system clock. It has a 50% duty cycle.

### -OWS (Input)

The "Zero Wait State" (-OWS) signal tells the microprocessor that it can complete the present bus cycle without inserting any additional wait cycles. In order to run a memory cycle to a 16-bit device without wait cycles, "-OWS" is derived from an address decode gated with a Read or Write command. In order to run a memory cycle to an 8-bit device with a minimum of two wait states, "-OWS" should be driven active one system clock after the Read or Write commands to an 8-bit device are active on the falling edge of the system clock. Note that "-OWS" must be synchronous to the system clock (CLK) and meet specific set-up and hold timing requirements to prevent undesirable system malfunction . "-OWS" is active low and should be driven with an open collector or tri-state driver capable of sinking 20mA.

# 2.4 WINCHESTER TRACK AND SECTOR FORMAT (Soft Sectored ESDI Drives)

The standard track format for Winchester Disk drives is organized into numbered data segments, or sectors.

| FORMAT TRACK FUNCTION |         |                      | START/RESTART STATE = 21h LOOP END STATE = 0Eh |                     |                     |                    |                     |                    |                     |                      |                      |                      |                       |                      |                       |        |                     |

|-----------------------|---------|----------------------|------------------------------------------------|---------------------|---------------------|--------------------|---------------------|--------------------|---------------------|----------------------|----------------------|----------------------|-----------------------|----------------------|-----------------------|--------|---------------------|

|                       | FIELD   | POST<br>INDEX<br>GAP | AM<br>ENABL<br>TIME                            | ID<br>PRE-<br>AMBLE | ID<br>PRE-<br>AMBLE | ID<br>SYNC<br>BYTE | ID<br>DATA<br>FIELD | ID<br>CRC<br>FIELD | ID<br>POST<br>AMBLE | DATA<br>PRE<br>AMBLE | DATA<br>PRE<br>AMBLE | DATA<br>SYNC<br>BYTE | USER<br>DATA<br>FIELD | DATA<br>ECC<br>FIELD | DATA<br>POST<br>AMBLE | SECTOR | PRE<br>INDEX<br>GAP |

|                       | SBO-CNT | *PRM                 | 03                                             | *PRM                | 01                  | 01                 | 04                  | 02                 | 04                  | 01                   | *PRM                 | 01                   | N                     | 06                   | 04                    | *orm   | 01(H)               |

# Standard ESDI Winchester Disk Sector Format

OMTI 8640: The number of sectors per track on most ESDI drives varies by vendor.

# 2.5 PIN ASSIGNMENTS

The following tables define the various Floppy Disk Drive's pin assignments .

# 2.5.1. FLOPPY DRIVE CONTROL AND DATA CONNECTOR (J1) PIN DESCRIPTION

| SIG<br>GND | SIG    | SIGNAL<br>PIN | SIGNAL<br>MNEMONIC            | I/O<br>NAME |

|------------|--------|---------------|-------------------------------|-------------|

| 1          | 2      | WCCNTRL-      | WRITE<br>CURRENT-<br>CONTROL- | 0           |

| 1<br>5     | 4      | NC            | CONTROL                       |             |

| -          | 6      | NC            |                               |             |

| 7          | 6<br>8 | INDEX-        | INDEX-                        | I           |

| 9          | 10     | MOTEN1-       | MOTOR-                        |             |

| -          |        |               | ENABLE1-                      | 0           |

| 15         | 16     | MOTEN2-       | MOTOR-                        | 0           |

|            | 10     |               | ENABLE2-                      | 0           |

| 11         | 12     | DS2-          | DRIVE-                        | v           |

| **         |        | 001           | SELECT2-                      | 0           |

| 13         | 14     | DS1           | DRIVE-                        | U           |

| 15         | 14     | 851           | SELECT1-                      | 0           |

| 17         | 18     | DIR           | DIRCTION                      | ŏ           |

| 19         | 20     | STEP-         | STEP-                         | U           |

| 19         | 20     | SIEI-         | PULSE-                        | 0           |

| 21         | 22     | WRT DATA-     | WRITE                         | U           |

| 21         | 22     | WKI DAIA-     | DATA-                         | 0           |

| 23         | 24     | WRT EN-       | WRITE-                        | U           |

| 23         | 24     | WKI EN-       |                               | 0           |

| 25         | 0(     | TDEA          | DATA-                         | 0<br>I      |

| 25         | 26     | TRK0          | TRACK0                        | 1           |

| 27         | 28     | WRT PROT      | WRITE                         | •           |

|            |        |               | PROTECT                       | Ĩ           |

| 29         | 30     | READ DATA     | READ DATA                     | I           |

| 31         | 32     | HS1           | HEAD SELECT1                  | 0           |

| 33         | 34     | DISKETTE      | DISKETTE                      | I           |

|            |        | CHG           | CHANGE                        |             |

Pin One is designated by a square backing on the solder side of the board.

# 2.5.2. ESDI Winchester Disk Drive Interface

# ESDI COMPATIBLE DISK DATA SIGNAL CONNECTOR (J3 & J4) RADIAL

| PINS        | FIXED DISKS                   |

|-------------|-------------------------------|

| 1           | DRIVE SELECTED                |

| 2           | SECTOR-ADDRESS MARK NOT FOUND |

| 3           | COMMAND COMPLETE              |

| 2<br>3<br>4 | ADDRESS MARK ENABLE           |

| 5           | RESERVED                      |

| 6           | GROUND                        |

| 7           | +WRITE REF CLOCK              |

| 8           | -READ REF CLOCK               |

| 9           | RESERVED                      |

| 10          | RESERVED                      |

| 11          | +READ REF CLOCK               |

| 12          | -READ REF CLOCK               |

| 13          | +NRZ WRITE DATA               |

| 14          | -NRZ WRITE DATA               |

| 15          | GROUND                        |

| 16          | GROUND                        |

| 17          | +NRZ READ DATA                |

| 18          | -NRZ READ DATA                |

| 19          | GROUND                        |

| 20          | INDEX                         |

# ESDI COMPATIBLE DISK CONTROL SIGNAL CONNECTOR (J5) CHAINED

| PINS      | FIXED DISKS                    |

|-----------|--------------------------------|

| GND 12    | HEAD SELECT 3                  |

|           | HEAD SELECT 2                  |

| 56        | WRITE GATE                     |

| 7 8       | CONFIG/-STATUS DATA            |

|           |                                |

| 9 10      | TRANSFER ACK                   |

| 11 12     | ATTENTION                      |

| 13 14     | HEAD SELECT 0                  |

| 15 16     | SECTOR/-ADDRESS MARK NOT FOUND |

| 17 18     | HEAD SELECT 1                  |

| 19 20     | INDEX                          |

| 21 22     | READY                          |

| 23 24     | TRANSFER REQ                   |

| 25 26     | DRIVE SELECT 1                 |

| 27 28     | DRIVE SELECT 2                 |

| 29 30     | DRIVE SELECT 3                 |

| 31 32     | READ GATE                      |

| GND 33 34 | COMMAND/DATA                   |

Pin One is designated by a square backing on the solder side of the board.

# 3.1 Handling (Caution)

It is recommended that you handle the controller by the edges of the card as some of the components are static sensitive and can be damaged by static.

# 3.2 Installation

The OMTI 8640 AT Compatible Data Controller is designed to plug directly into any unused 16 bit location on the system motherboard. The floppy and winchester disk drives are connected to the controller by ribbon cables. It is recommended that these cables do not exceed 20 feet in length.

# 3.3 Jumper Settings

# W2 Floppy Primary/Secondary Address Setting

\* 0 Primary Address 1 Secondary Address

# W3 Winchester Primary/Secondary Address Setting

- \*0 Primary Address

- 1 Secondary Address

# W5 Floppy Disable

\*0 Floppy is enabled 1 Floppy is disabled

# W16 Sectors per track

\*0 Read from drive 1 Calculate and set

# W17 Cache Option

- \*0 Cache disabled

- 1 Cache enabled

# W18

\*0 Disable Track Offset Command and disable Data Strobe Offset

1 Enable Track Offset Command and enable Data Strobe Offset

# W19 Dual Speed Floppy

\*0 Single Speed 1 Dual Speed

### W20 J1 Floppy Connector Polarity

| *1-2 Jumpered | Active High |

|---------------|-------------|

| 2-3 Jumpered  | Active Low  |

# W21 J2 Floppy Connector Polarity

| *1-2 Jumpered | Active High |

|---------------|-------------|

| 2-3 Jumpered  | Active Low  |

# W23 W24 BIOS Base Address

| *1 | 1 | C8000 |

|----|---|-------|

| 1  | 0 | CA000 |

| 0  | 1 | CC000 |

| 0  | 0 | CE000 |

# W25 BIOS Enable

- 0 BIOS Disabled

- 1 BIOS Enabled

### W28 Chassis Ground

- \*0 Chassis not grounded.

- 1 Chassis grounded

\*Designates how jumper is set when board is shipped.

### \*\*\*\*\*\*\*\*\*\*\*

### 3.4 Installation of Controller in system with one winchester drive.

- 1. Connect the floppy drive cable to position J1 on the 8640 Controller. Pin 1 on all connectors is specified by a square solder pad, visible on the soldered side of the board.

- 2. Winchester drive cabling requirements.

- One (1) 34-pin straight through cable.

- One (1) 20-pin straight through cable.

- 3. On winchester drive:

- Install drive select jumper to lowest Drive Select (DSO or DS1).

- Install the 34-pin winchester drive interface cable to the J5 connector.

Install the 20-pin data cable to either the J3 or J4 connector.

- 5. Attach the winchester activity LED connector to J6.

- Install the controller in any available slot on the PC/AT motherboard. CAUTION: Power must be off!

- 7. Insert system Diagnostic Diskette (or execute internal diagnostics/setup program).

- 8. Turn on the power.

- 9. Enter setup routine.

- 10. Setup system options.

- 11. A) Select proper Drive Type. Consult your Technical Reference Manual for further information on the drive type table parameters. If your system BIOS does not contain an ESDI drive type, the BIOS on the 8640 will allow you to overide the drive table in the system BIOS. In this case you should setup the system for one Winchester disk drive, type 1.

- B) For highest performance using a 1:1 interleave, it is recommended you format your drive using the BIOS on the 8640 controller. You may access the BIOS by rebooting the system with DOS and inserting a diskette with the DEBUG program on it. Once you have done this type DEBUG and press <return>. If you have entered debug you will get the following prompt:

- 12. Enter G=C800:6 and press <return>. The following screen will appear.

Screen 1

| ***** OMTI 8640 Formatter Utility *****             |        |         |            |  |

|-----------------------------------------------------|--------|---------|------------|--|

| Drive:0                                             | # Cyls | # Heads | # Secs/Trk |  |

| This utility will destroy ALL DATA on your disk!!!  |        |         |            |  |

| Press <ret> to proceed, <esc> to cancel</esc></ret> |        |         |            |  |

The utility will automatically display your drive characteristics (number of cylinders, heads and sectors per track). This utility will allow you to format your drive which will destroy all previous data on the disk.

Press <return> to continue to the next screen.

Screen 2

### \*\*\*\*\*OMTI 8640 Formatter Utility\*\*\*\*\*

DRIVE PARAMETERS MODE

- 1) Standard Table (# cylinders truncated to 1024)

- 2) Translated Table

- 3) Non-Standard Table (no cylinder truncation)

Enter choice: 1

This screen will only appear if your drive has more than 1024 cylinders. This screen allows you to choose the way in which the drive's parameters appear if your drive has more than 1024 cylinders. Option 1 will show the drive with its true head and sectors per track values but only 1024 cylinders will appear. Option 2 will show you a translation based on 16 heads and 62 sectors per track. Option 3 will show the true parameters of your drive. Remember that DOS cannot recognize a device which has more than 1024 cylinders. If your drive has more than 1024 cylinders you will require a device driver under DOS. Other operating systems such as XENIX and OS/2 also will not recognize a device with more than 1024 cylinders. When you have entered your choice, press <return> and continue.

Screen 3

\*\*\*\*\* OMTI 8640 Formatter Utility \*\*\*\*\*

### DRIVE PARAMETERS MODE

- 1) Standard Table (# cylinders truncated to 1024)

- 2) Translated Table

- 3) Non-Standard Table (no cylinder truncation)

Interleave (1-15) . . . . :

You should enter the interleave value you want to use. A value of one is recommended for highest performance.

After you have entered your value, press <return> to continue.

Screen 4

### \*\*\*\*\* OMTI 8640 Formatter Utility \*\*\*\*\*

#### DRIVE PARAMETERS MODE

1) Standard Table (# cylinders truncated to 1024)

Translated Table

Non-Standard Ta

3) Non-Standard Table (no cylinder truncation)

Interleave (1-15) ....: 1 Head Skew (0-15) ....:

You may obtain the correct Head Skew value from your drive manufacturer representative or drive reference manual. If you cannot obtain this value we recommend that you enter a value of 2, then press <return>.

Screen 5

### \*\*\*\*\* OMTI 8640 Formatter Utility \*\*\*\*\*

### DRIVE PARAMETERS MODE

Standard Table (# cylinders truncated to 1024) 1)

Translated Table

2) 3) Non-Standard Table (no cylinder truncation)

Interleave (1-15) . . . : 1 Head Skew (0-15) ...: 2 Cylinder Skew (0-10) . . . :

Cylinder Skew, like Head Skew, is a value you may obtain from your drive manufacturer. These options allow you to maximize the performance of your ESDI Disk Drive, and will vary for every drive. Please do not call OMTI Technical Support for these values, you must get them from your drive manufacturer. If you are unsure of what value to enter, we recommend that you enter a value of 4. After you have entered your Cylinder Skew value, press <return> to continue.

Screen 6

# \*\*\*\*\* OMTI 8640 Formatter Utility \*\*\*\*\* DRIVE PARAMETERS MODE Standard Table (# cylinders truncated to 1024) 1) 2) 3) Translated Table Non-Standard Table (no cylinder truncation) Interleave (1-15) . . . . . : 1 Head Skew (0-15) . . . . : 2 Cylinder Skew (0-10) . . : 4 DEFECT MANAGEMENT MENU 1) Auto Defect Management 2) 3) Manual Defect Management No Defect Management Enter choice: 1

Most ESDI disk drives have a defect map stored on the drive which the 8640 can read. You enable this feature when you choose the Auto Defect Management option. If you want to enter your own defect map you should choose the Manual Defect Management Option which begins at screen 11. If you want No Defect Management you may choose that option and then proceed to screen 15.

| Screen ' | 7 |

|----------|---|

|----------|---|

| ***** OMTI 8640 Formatter Utility *****                                                                                                           |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DRIVE PARAMETERS MODE                                                                                                                             |  |  |

| <ol> <li>Standard Table (# cylinders truncated to 1024)</li> <li>Translated Table</li> <li>Non-Standard Table (no cylinder truncation)</li> </ol> |  |  |

| Interleave (1-15) : 1<br>Head Skew (0-15) : 2<br>Cylinder Skew (0-10) : 4                                                                         |  |  |

| DEFECT MANAGEMENT MENU                                                                                                                            |  |  |

| <ol> <li>Auto Defect Management</li> <li>Manual Defect Management</li> <li>No Defect Management</li> </ol>                                        |  |  |

| Enter choice: 1                                                                                                                                   |  |  |

| <ol> <li>Sector flagging</li> <li>Sector sparing</li> </ol>                                                                                       |  |  |

| Enter Choice: 1                                                                                                                                   |  |  |

The OMTI 8640 does its defect management on the sector level versus track level. This enables you to get the maximum capacity from your drive. The sector flagging option flags each bad sector the 8640 encounters.

Sector sparing saves one sector per track for defect management. This allows the track containing a defect to appear defect free. However it decreases total available storage space and can affect data transfer rates.

Screen 8 shows what appears if you enter the Auto Defect Management option with either sector flagging or sector mapping.

ł

ł

\$

\$

Screen 8

| ***** OMTI 8640 Formatter Utility *****        |      |                    |  |

|------------------------------------------------|------|--------------------|--|

| Building Defect List for head # 0              |      |                    |  |

| (Cyl, BFI) : Cyl # # Bytes from Index          |      |                    |  |

| Building defect list for head # 1              |      |                    |  |

| (Cyl, BFI) :                                   | Cyl# | # Bytes from Index |  |

| Do you wish to see entire defect list (Y/N)? y |      |                    |  |

The above screen shows you the defect list for all heads on your drive. If you wish to see the entire defect list answer yes and press <return>.

|       | Screen 9                                |        |                       |  |

|-------|-----------------------------------------|--------|-----------------------|--|

|       | ***** OMTI 8640 Formatter Utility ***** |        |                       |  |

|       | Cylinder                                | Head   | BFI                   |  |

| 1.    | Cyl. #                                  | Head # | # of Bytes from Index |  |

| Press | Press any key to continue               |        |                       |  |

After you have reviewed the complete defect list the last screen will look like the following:

|                                          | S      | creen 10 |            |  |

|------------------------------------------|--------|----------|------------|--|

| ***** OMTI 8640 Formatter Utility *****  |        |          |            |  |

| Drive:0                                  | # Cyls | # Heads  | # Secs/Trk |  |

| Are you SURE you want to format (Y/N)? y |        |          |            |  |

If you wish to format enter a "Y" and press <return>. The format will destroy all previous data. Go to Screen 16 to continue this procedure.

\*\*\*\*\*\*

If at screen 5 you chose the Manual Defect Management you should continue here:

Screen 11 \*\*\*\*\* OMTI 8640 Formatter Utility \*\*\*\*\*\* Interleave (1-15) . . . . : 1 Head Skew (0-15) ... : 2 Cylinder Skew (0-10) . . : 4 DEFECT MANAGEMENT MENU Auto Defect Management Manual Defect Management No Defect Management Enter Choice: 2 Sector flagging Sector sparing Enter Choice: 1

The OMTI 8640 does its defect management on the sector level versus track level. This enables you to get the maximum capacity from your drive. The sector flagging option flags each bad sector the 8640 encounters.

Sector sparing saves one sector per track for defect management. This allows the track containing a defect to appear defect free. However it decreases total available storage space and can affect data transfer rates

Screen 12

\*\*\*\*\* OMTI 8640 Formatter Utility \*\*\*\*\*

**Defect Entry List** Cvlinder Head BFI

(Press <RET> to end defect list)

CYLINDER....:

The BIOS will ask you your cylinder number for your first defect. Enter that number.

1)

2) 3Ś

1)

2)

Ł

25

| Screen | 13 |

|--------|----|

|--------|----|

| ***** OMTI 8640 Formatter Utility ***** |                                        |  |  |

|-----------------------------------------|----------------------------------------|--|--|

|                                         | Defect Entry List<br>Cylinder Head BFI |  |  |

| (Press <ret> to end defect list)</ret>  |                                        |  |  |

| CYLINDER: 100<br>HEAD:                  | 100                                    |  |  |

In the example we entered a defective cylinder number of 100 and now we will enter a defective head number of 5.

#### Screen 14 \*\*\*\*\* OMTI 8640 Formatter Utility \*\*\*\*\* **Defect Entry List** Cylinder Head BFI (Press <RET> to end defect list) 100 5 1030 Cylinder . . . .: 100 Head . . . . . : 5 Bytes from Index: 1030

A defect at cylinder 100, head 5, and 1030 bytes from index has now been entered. For this example we will press <return> to leave the defect management option.

|                                          |        | Screen 15 |           |  |

|------------------------------------------|--------|-----------|-----------|--|

| ***** OMTI 8640 Formatter Utility *****  |        |           |           |  |

| Drive 0:                                 | # Cyls | # Heads   | #Secs/Trk |  |

| Are you SURE you wish to format (Y/N)? y |        |           |           |  |

To format, a "y" is entered. To leave this program and go back to DOS, enter an "n". The next screen will show the cylinder and head that is being formatted during the procedure:

# **OMTI 8640 Reference Manual**

1

|                                            |            | Screen 16                   |            |  |

|--------------------------------------------|------------|-----------------------------|------------|--|

|                                            | ***** OMTI | 8640 Formatter Utility **** | *          |  |

| Drive 0:                                   | # Cyls     | # Heads                     | # Secs/Trk |  |

| Are you SURE you want to format (Y/N//)? y |            |                             |            |  |

| Formatting Cy                              | linder #   | Head #                      |            |  |

|                                            |            |                             |            |  |

As soon as the last Cylinder and Head are formatted the following Screen will appear: Screen 17

|                    | ***** OMTI        | 8640 Formattter Utility **** | *          |

|--------------------|-------------------|------------------------------|------------|

| Drive 0:           | # Cyls            | # Heads                      | # Secs/Trk |

| Are you SURE you   | want to format    | (Y/N)? y                     |            |

| Formatting Cylinde | er#               | Head #                       |            |

| Format Complete    |                   |                              |            |

| Do you wish to per | form a surface an | alysis (Y/N)? y              |            |

|                    |                   |                              |            |

If you want to perform the surface analysis enter "y" then press <return>. If you do not want a surface analysis enter "n" then press <return> and you are finished.

| Screen 18                                    |                         |                    |            |  |

|----------------------------------------------|-------------------------|--------------------|------------|--|

| ***** OMTI 8640 Formatter Utility *****      |                         |                    |            |  |

| Drive 0:                                     | # Cyls                  | # Heads            | # Secs/Trk |  |

| Are you SURE you w                           | vant to format (Y/N)?   | у                  |            |  |

| Formatting Cylinder #                        | #                       | Head #             |            |  |

| Format Complete                              |                         |                    |            |  |

| Do you wish to perfro                        | om a surface analysis ( | (Y/N)? y           |            |  |

| Verifying Cylinder 5<br>Verifying Cylinder # |                         | < defect processed |            |  |

The utility will process all defects it encounters during the verify. Once the verify is done the screen will ask you to press any key to reboot, once you do this you will return to DOS and go on to FDisk.

| Screen 19                                  |                          |                    |            |  |

|--------------------------------------------|--------------------------|--------------------|------------|--|

| ***** OMTI 8640 Formatter Utility *****    |                          |                    |            |  |

| Drive 0:                                   | # Cyls                   | # Heads            | # Secs/Trk |  |

| Are you SURE you want to format (Y/N)? y   |                          |                    |            |  |

| Formatting Cylinder                        | <b>#</b>                 | Head #             |            |  |

| Format Complete                            |                          |                    |            |  |

| Do you wish to perfor                      | rm a surface analysis (` | Y/N)? y            |            |  |

| Verifying Cylinder 5                       | Head 9                   | < defect processed |            |  |

| Verify complete<br>Press any key to reboot |                          |                    |            |  |

- 13. Create a DOS partition by executing the FDISK utility.

- 14. Initialize the drive by executing the command: FORMAT C:/S

- 15. Your winchester should now be bootable drive C.

# 3.5 Installation of Two Drive System

- 1. On Winchester Drive

- Set Drive Select to DS2 (or DS1) for drive D:

- Install termination resistor on drive at end of daisy chain cable. Remove termination resistor on first drive on daisy chain cable.

- 2. Connect second drive to controller using 34-pin daisy chain straight through cable and one 20-pin straight through cable.

- 3. Follow steps 5 to 15 as defined in installing one drive system.

ð The OMTI 8640 contains 10 registers by which the host can communicate with the controller. This section describes the registers and command set that are supported by the Winchester disk portion of the 8640 controller.

### The 8640 Register Addresses

# Table 4.1

| <u>Primary</u>    | Secondary         | I/O Address<br><u>Read</u>      | <u>Write</u>                  |

|-------------------|-------------------|---------------------------------|-------------------------------|

| 1F0<br>1F1        | 170<br>171        | Data Register<br>Error Register | Data Register                 |

| 1F1<br>1F2<br>1F3 | 171<br>172<br>173 | Sector Count<br>Sector Number   | Sector Count<br>Sector Number |

| 1F4               | 174               | Cylinder Number<br>(LSB)        | Cylinder Number<br>(LSB)      |

| 1F5               | 175               | Cylinder Number<br>(MSB)        | Cylinder Number<br>(MSB)      |

| 1F6<br>1F7        | 176<br>177        | SDH Select<br>Status            | SDH Select<br>Command         |

# **Control and Status Registers**

| <u>Primary</u>                  | Secondary                       | I/O Address<br><u>Read</u>                                                  | Write                                                                                   |

|---------------------------------|---------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 3F2<br>3F4<br>3F5<br>3F6<br>3F7 | 372<br>374<br>375<br>376<br>377 | Main floppy status<br>Floppy Data<br>Secondary status<br>Head/Select status | Floppy Select/Control<br>Main Floppy Status<br>Floppy Data<br>Fixed Disk<br>Rate Select |

# 4.1 Read Register Definitions

### 4.1.1 Data Register 1F0 (170)

This register transfers controller data between the Host and the 8640. In Word Mode, 16 bits of data are transferred requiring I/O\_CS\_16 to be asserted and possibly deasserting I/O\_CH\_RDY. In Byte Mode, 8 bits of data are transferred leaving I/O\_CS\_16 deasserted and I/O\_CH\_RDY

4

.

# 4.1.2 Error Register 1F1 (171)

This register contains the error status of the last command executed by the controller. It can only be accessed while the controller is in the NOT BUSY state. This register is not affected by a reset. The data returned is only valid when the error bit is set.

| Bit 7 - Bad Block Found    | This indicates that the specified sector has previously<br>been formatted with the Bad Track flag set in the ID<br>field. It is not possible to access data on this sector.                                                                                                                                                                                           |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 6 - ECC Error          | This indicates that a non-zero syndrome was detected<br>in a specified data field. If the data error was<br>corrected by ECC, Bit 2 of the Status Register will<br>also be set and the command will continue if more<br>sectors are specified. If the data error was not<br>corrected by ECC, bit 0 of the Status Register will be<br>set and the command terminated. |

| Bit 5 - Not used           | Set to zero.                                                                                                                                                                                                                                                                                                                                                          |

| Bit 4 - ID not found       | This indicates that the controller was able to locate<br>the correct cylinder and head number but was unable<br>to locate the correct sector. An ID CRC error can<br>also generate this error condition.                                                                                                                                                              |

| Bit 3 - Not used           | Set to zero.                                                                                                                                                                                                                                                                                                                                                          |

| Bit 2 - Aborted Command    | The current command issued by the Host has been<br>aborted due to an undefined Command, or a Write<br>Fault/Not Ready condition exists on the selected<br>drive.                                                                                                                                                                                                      |

| Bit 1 - No Cylinder Zero   | This indicates that during a recalibration command or<br>if retries are enabled no Cylinder 000 was detected.<br>This error occurs after the controller issues 2048 step<br>pulses towards cylinder 000 and the selected drive<br>does not respond with the Track 000 signal.                                                                                         |

| Bit 0 - No Data Mark Found | This indicates that the controller was able to locate<br>the sector but was unable to locate the data mark<br>associated with it.                                                                                                                                                                                                                                     |

|                            |                                                                                                                                                                                                                                                                                                                                                                       |

# 4.1.3 Sector Count Register 1F2 (172)

The number of sectors transferred during a read, write, verify or format track command is determined by this register. A 0 in the sector count register specifies a 256 sector transfer. The initialize drive characteristics command must be performed before a multiple sector transfer. During a format command the number of sectors per track must be loaded into this register before each format track.

#### 4.1.4 Sector Number Register 1F3 (173)

This register contains the current sector number being processed by the controller. It can only be accessed while the controller is in the Not Busy state. If an error condition exists, this register contains the sector number in error. It is set to 1 after a Reset.

#### 4.1.5 Cylinder Number Register (LSB) 1F4 (174)

This register contains the least significant byte of the current cylinder number. It can only be accessed while the controller is in the Not Busy state. If an error condition exists, this register contains the least significant byte of the cylinder number in error. This register is set to 0 after a Reset.

#### 4.1.6 Cylinder Number Register (MSB) 1F5 (175)

This register contains the most significant byte of the current cylinder number. It can only be accessed while the controller is in the Not Busy state. If an error condition exists, this register contains the most significant byte of the cylinder number in error. This register is set to 0 after a Reset.

#### 4.1.7 SDH Register 1F6 (176)

This register contains the controller Error Code/Sector Size parameters along with the current Drive/Head select. It can only be accessed when the controller is Not Busy. This register is set to 0 after a reset.

#### Bit Definition

7

- Set to 1 the data field will be appended with an ECC field. Set to 0 the data field will be appended with a CRC field.

- 6 and 5 These bits indicate the sector size selected. Their definitions are:

- 6 5

| 0 | 0 - 256 Bytes per Sector |

|---|--------------------------|

| 0 | 1 - 512 Bytes per Sector |

- 0 1024 Bytes per Sector 1

- 1 128 Bytes per Sector

- 4 Drive Select 0 is Drive 0 1 is Drive 1

1

3-0 Head Select. Bit 3 is the MSB with Bit 0 being the LSB.

.

,

# 4.1.8 Status Register 1F7 (177)

The status of the command is reported in this register after its execution. A read of this register clears interrupt request. Bit Definition:

| 7 | Busy           | This bit indicates the state of the controller. If set, the controller is<br>busy executing the specified command and is not in a data transfer<br>state. Any write to the Host Read/Write registers while this bit is set<br>will be ignored. If cleared the controller is either in a Not Busy or a<br>Data Transfer state. The DRQ bit will be set if the controller is in the<br>Data Transfer state. |

|---|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 | Ready.         | This bit is an inverted copy of the Ready signal of the selected drive.                                                                                                                                                                                                                                                                                                                                   |

| 5 | Write Fault.   | This bit is an inverted copy of the Write Fault signal of the selected drive.                                                                                                                                                                                                                                                                                                                             |

| 4 | Seek Complete  | This bit is an inverted copy of the Seek Complete signal of the selected drive.                                                                                                                                                                                                                                                                                                                           |

| 3 | Data Request.  | This bit indicates that the controller is in a Data Transfer mode. While<br>this bit is set, the Busy bit will be cleared and the controller will wait<br>for data to be transferred to or from the host.                                                                                                                                                                                                 |

| 2 | Corrected      | When this bit is set it indicates the data read from the disk was<br>properly corrected with the use of ECC. If CRC is selected, this bit<br>has no meaning and is set to zero.                                                                                                                                                                                                                           |

| 1 | Index.         | This bit is set on each revolution of the disk.                                                                                                                                                                                                                                                                                                                                                           |

| 0 | Error.         | When set to 1 this indicates the previous command ended in an error<br>and that the error register has been set. The next command clears this<br>bit.                                                                                                                                                                                                                                                     |

|   | <b>a b a b</b> |                                                                                                                                                                                                                                                                                                                                                                                                           |

# 4.1.9 Secondary Status Register 3F6 (376)

This register contains the Controller/Drive status. It is identical to the Status Register at 1F7 (177).

# 4.1.10 Head\Select Status Register 3F7 (377)

This register contains the Head/Drive Select status. The bit definitions are:

Bit 7 - Diskette ChangeThis bit indicates the state of the floppy Disk Change<br/>signal If set, no diskette, door open or Drive Not<br/>Ready condition.Bit 6 - Write GateThis bit indicates the state of the Winchester 'Write<br/>Gate signal'.

# Chapter 4. 8640 Interface Registers

| Bit 5 - Head Select 3/RWC | This bit indicates the state of Head Select 3.                                    |

|---------------------------|-----------------------------------------------------------------------------------|

| Bit 4 - Head Select 2     | This bit indicates the state of Head Select 2.                                    |

| Bit 3 - Head Select 1     | This bit indicates the state of Head Select 1.                                    |

| Bit 2 - Head Select 0     | This bit indicates the state of Head Select 0.                                    |

| Bit 1 - Drive Select 1    | This bit indicates the state of Drive Select 1. If set to 0, Drive 1 is selected. |

| Bit 0 - Drive Select 0    | This bit indicates the state of Drive Select 0. If set to 0 Drive 0 is selected.  |

# 4.2 8640 Write Register Definitions

# 4.2.1 Data Register 1F0 (170)

This register transfers controller data between the 8640 and the HOST. In WORD MODE, 16 bits of data are transferred requiring I/O\_CS\_16 to be asserted and possibly de-asserting I/O\_CH\_RDY. In BYTE MODE, 8 bits of data are transferred leaving I/O\_CS\_16 deasserted and I/O\_CH\_RDY asserted.

# 4.2.2 Sector Count Register 1F2 (172)

The number of sectors transferred during a read, write, verify or format track command is determined by this register. A 0 in the sector count register specifies a 256 sector transfer. The initialize drive characteristics command must be performed before a sector transfer. During a format command the number of sectors per track must be loaded into this register before each format track.

# 4.2.3 Sector Number Register 1F3 (173)

This register specifies the starting sector number. It should be written prior to the Command Register being written. This register is set to 1 after a reset.

# 4.2.4 Cylinder Number Register (LSB) 1F4 (174)

This register specifies the least significant byte of the starting cylinder number. It should be written prior to the Command register being written. This register is set to 0 after a Reset.

.

٠

# 4.2.5 Cylinder Number Register (MSB) 1F5 (175)

This register specifies the most significant byte of the starting cylinder number. It should be written prior to the Command Register being written. This register is set to 0 after a Reset.

# 4.2.6 SDH Register 1F6 (176)

This register specifies the controller Error Code/Sector Size parameters along with the Drive/Head select. This register should be written prior to the Command Register being written. This register is set to 0 after a Reset. The bit definitions are:

- Bit

Definition

7

This bit specifies the error code to be selected. If this bit is set the data field will be appended with an ECC field. If cleared the data field will be appended with a CRC field.

- 6 and 5 These bits indicate the sector size selected. Their definitions are:

| 6 | 5                         |

|---|---------------------------|

| 0 | 0 - 256 Bytes per Sector  |

| 0 | 1 - 512 Bytes per Sector  |

| 1 | 0 - 1024 Bytes per Sector |

| 1 | 1 - 128 Bytes per Sector  |

4 Drive Select 0 is Drive 0 1 is Drive 1

**3-0** Head Select. Bit 3 is the MSB with Bit 0 being the LSB.

## 4.2.7 Command Register 1F7 (177)

This register accepts commands for Winchester operations. Table 4.2 lists the commands supported.

#### Table 4.2

| Command      | Bit<br>7 | Bit<br>6 | Bit<br>5 | Bit<br>4 | Bit<br>3 | Bit<br>2 | Bit<br>1 | Bit<br>0 |

|--------------|----------|----------|----------|----------|----------|----------|----------|----------|

| Recalibrate  | 0        | 0        | 0        | 1        | 0        | 0        | 0        | 0        |

| Seek         | 0        | 1        | 1        | 1        | 0        | 0        | 0        | 0        |

| Read Sector  | 0        | 0        | 1        | 0        | 0        | 0        | L        | R        |

| Write Sector | 0        | 0        | 1        | 1        | 0        | 0        | L        | R        |

| Format Track | Ő        | 1        | 0        | 1        | 0        | 0        | 0        | 0        |

| Read Verify  | 0        | 1        | 0        | 0        | 0        | 0        | 0        | R        |

| Diagnostic   | 1        | 0        | 0        | 1        | 0        | 0        | 0        | 0        |

|                        |          |          |          |          | •        |          |          |          |

|------------------------|----------|----------|----------|----------|----------|----------|----------|----------|

| Set Parameters         | Bit<br>1 | Bit<br>0 | Bit<br>0 | Bit<br>1 | Bit<br>0 | Bit<br>0 | Bit<br>0 | Bit<br>1 |

| Initiate ESDI          | 1        | 1        | 1        | 0        | 0        | 0        | 0        | 0        |

| Start/Stop Motor       | 1        | 1        | 1        | 0        | 0        | 0        | 0        | 1        |

| Read Data Buffer       | 1        | 1        | 1        | 0        | 0        | 1        | 0        | 0        |

| Write Data Buffer      | 1        | 1        | 1        | 0        | 1        | 0        | 0        | 0        |

| <b>Read Parameters</b> | 1        | 1        | 1        | 0        | 1        | 1        | 0        | 0        |

| Read ESDI Defect List  | 0        | 0        | 1        | 0        | 0        | 1        | 0        | 0        |

| Cache Control          | 1        | 1        | 1        | 0        | 1        | 1        | 1        | 1        |

Table 4.2 (continued)

L = When set to 1 a Read or Write Long has occurred and 4 (of 7) ECC bytes will be transferred.

**R** = When set to 1 Retries are disabled.

# 4.2.8 Recalibrate (10H)

The drive specified is stepped toward the outside cylinder until either Track Zero signal is detected or more steps have been issued than available cylinders for the device type. The controller issues one step pulse, waits for seek complete, and tests the Track 000 signal.

## 4.2.9 Seek (70H)

This command causes the read/write heads to be physically positioned to the cylinder specified in the cylinder high and low registers. If executed in the buffered mode step pulses and command complete will be issued before the seek is complete, allowing an overlapped seek.

# 4.2.10 Read Sector (20H)

This command specifies the number of sectors (1-256) to be read from the Winchester Disk with or without the ECC field appended (ECC field is appended if Read Long bit is set). The sector count register determines the number of sectors to be transferred. If a read is issued prior to initialization of a step rate the default value will be used. If the retries bit is set to 0, up to ten retries will be performed before an error is reported. If the retries bit is set to 1 only two retries will be executed. Interrupts occur as each sector is ready to be read, there is no interrupt at the end of a command.

# 4.2.11 Write Sector (30H)

This command specifies the number of sectors (1-256) to be written to the Winchester Disk with or without the ECC Bytes appended by the Host (ECC field is appended if Write Long bit is set). The sector count register is used to determine the number of sectors to be transferred. If a write is issued prior to initialization of a step rate the default value is used. If the retries bit is set to 0 up to ten retries will be performed before an error is reported. If the retries bit is set to 1 only two retries will be executed. Interrupts are generated as each sector is transferred into the Sector Buffer (except the first sector) and at the end of the command.

# 4.2.12 Format Track (50H)

The track specified in the task file is formatted with ID and data fields according to the interleave table that is transferred to the buffer. The sector count register must be loaded with the number of sectors per track before each Format Track command. An interrupt is generated at the end of this command. There are no valid errors for this command.

# 4.2.13 Read Verify (40H)

This command is similiar to a read sector with the difference being that no data is transferred during a read verify. If this command is issued prior to initialization of a step rate the default value of 7.5 msec is used and a recalibrate is performed first. Any number of sectors may be transferred up to 256, the ECC bytes generated are compared with those that were recorded to verify data integrity. An interrupt is generated at the end of this command or when an error is encountered.

# 4.2.14 Diagnostic (90H)

This command causes the Controller to perform an on-board diagnostic and report the result in the Error Register. This command tests the Interface, Buffer, RAM, Sequencer and ROM. The error codes that can be reported in the error register are:

- 01 NO ERROR

- 02 CONTROLLER INTERFACE FAILURE

- 03 CONTROLLER BUFFER RAM FAILURE

- 04 SEQUENCER FAILURE

- 05 CONTROLLER ROM FAILURE

# 4.2.15 Set Parameters (91H)

This command sets up the drive parameters specifying the maximum number of heads and sectors per track. This command must be issued before any multiple sector operations are begun. The drive/head select register should be used to specify the drive which is having its parameters set. This allows drives to have different parameters.

# 4.2.16 Read ESDI Defect List (24H)

This command causes the specified drive to return 512 bytes of drive manufacturer recorded defect list during the data-in phase of the command execution. Only the list for the specified head will be returned. The head is specified in the 1F6 register. The data is returned in the following manner:

| <u>Defect List Data Format</u><br><u>Header</u> |             |  |  |  |  |  |

|-------------------------------------------------|-------------|--|--|--|--|--|

| <u>Byte</u>                                     |             |  |  |  |  |  |

| 0                                               | MONTH       |  |  |  |  |  |

| 1                                               | DAY         |  |  |  |  |  |

| 2                                               | YEAR        |  |  |  |  |  |

| 3                                               | HEAD NUMBER |  |  |  |  |  |

| 4                                               | Zero Value  |  |  |  |  |  |

| 5                                               | Zero Value  |  |  |  |  |  |

| DEFECT Descriptor Format |                                                                                                                          |  |  |  |  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Byte                     |                                                                                                                          |  |  |  |  |  |

| 6<br>7<br>8<br>9<br>10   | Cylinder (MSB)<br>Cylinder (LSB)<br>Byte Count from Index (MSB)<br>Byte Count from Index (LSB)<br>Error Length (In Bits) |  |  |  |  |  |

Each defect is listed with a 5 byte field as described above.

# **End of List Format**

| xx-3<br>xx-2<br>xx-1 | FF<br>FF<br>FF<br>FF<br>FF |

|----------------------|----------------------------|

|----------------------|----------------------------|

Five ff bytes indicate the end of the defect list.

# 4.2.17 Start/Stop Motor (E1H)

To start the motor bit 1 of register (1F1) must be set. To stop the motor this bit must be set to 0.

# 4.2.18 Read Data Buffer (E4H)

This command causes data to be written from the host to the controller's buffer.

# 4.2.19 Write Data Buffer (E8H)

Data from the controller's buffer is returned to the host when this command is executed.

# 4.2.20 Read Parameters (ECH)

This command retrieves the drive configuration from the ESDI Drive.

# 4.2.21 Cache Control (EFH)

This command controls the read ahead buffer which is used on the 8640. To enable or disable the cache the user must write the correct code to the Precomp Register (1F1).

AA= Cache enabled 55= Cache disabled

# 4.2.22 Initiate ESDI (E0H)

This command enables the system processor to send instructions directly to the selected drive by loading the cylinder register (high and low) and executing the Initiate command, the host fills the cylinder registers with the command it wants to execute prior to issuing the Initiate ESDI command. The controller then processes the data and sends it to the drive. After the drive completes the command it sends completion status back to the controller.