# 82C465MV/MVA/MVB

# Single-Chip Mixed Voltage Notebook Solution

**Data Book**

Revision: 3.0 912-3000-016 October, 1997

www.DataSheet4U.com

#### Copyright

Copyright © 1997, OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of OPTi Incorporated, 888 Tasman Drive, Milpitas, CA 95035.

#### www.DataDisclaimer

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

Note: Before designing contact OPTi for latest Product Alerts, Applications Notes, and Errata for this product line.

#### Trademarks

OPTi and OPTi Inc. are registered trademarks of OPTi Inc. All other trademarks and copyrights are the property of their respective holders.

#### OPTi Inc.

888 Tasman Drive Milpitas, CA 95035 Tel: (408) 486-8000 Fax: (408) 486-8001 WWW: http://www.opti.com/

# Table of Contents

| 1.0             |     |          |                                                       |    |  |

|-----------------|-----|----------|-------------------------------------------------------|----|--|

| 2.0             |     |          |                                                       |    |  |

|                 | 2.1 | Upgrad   | de Comparison                                         | 4  |  |

| 3.0             | Sig | nal Defi | initions                                              | 5  |  |

| DataSheet4U.com | 3.1 | Termin   | nology/Nomenclature Conventions                       | 5  |  |

|                 | 3.2 | Pinout   | Options                                               | 5  |  |

|                 | 3.3 | Strap-S  | Selected Interface Options                            | 5  |  |

|                 |     | 3.3.1    | Mixed Voltage Interface Options                       | 7  |  |

|                 |     | 3.3.2    | Resume Reset (RSMRST#) Function                       | 7  |  |

|                 |     | 3.3.3    | Reading the 1X/2X Strap Setting                       | 7  |  |

|                 |     | 3.3.4    | Using Strap Options with TTL Logic                    | 8  |  |

|                 | 3.4 | Progra   | am Selected Interface Options                         | 9  |  |

|                 |     | 3.4.1    | DACKMUX Decoder Lines Source                          | 9  |  |

|                 |     | 3.4.2    | EPMI Signal Source<br>3.4.2.1 Additional EPMI Sources |    |  |

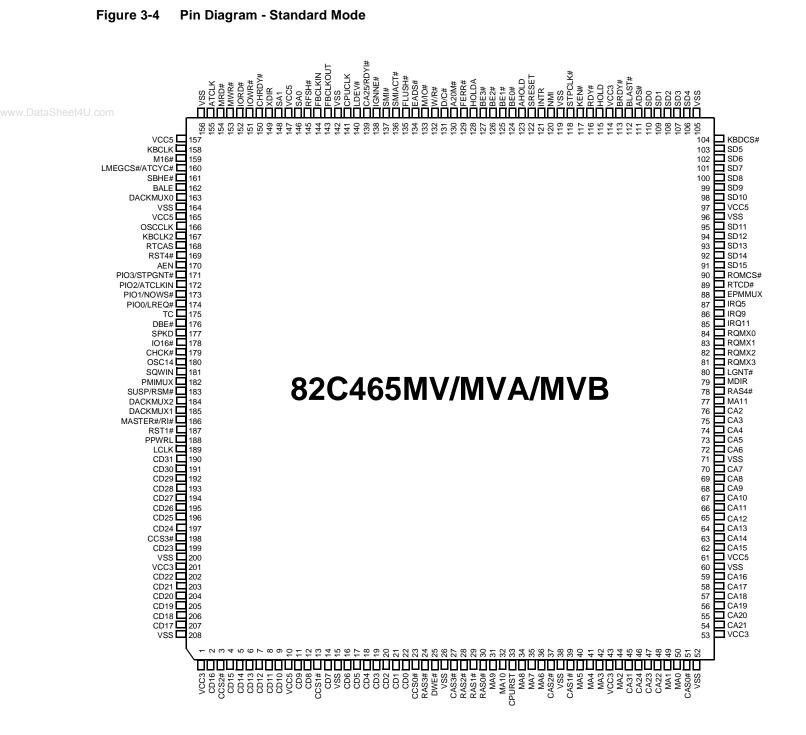

|                 | 3.5 | Standa   | ard Mode 82C465MV Interface                           | 11 |  |

|                 |     | 3.5.1    | Reduced Memory Interface Signal Group Option          | 12 |  |

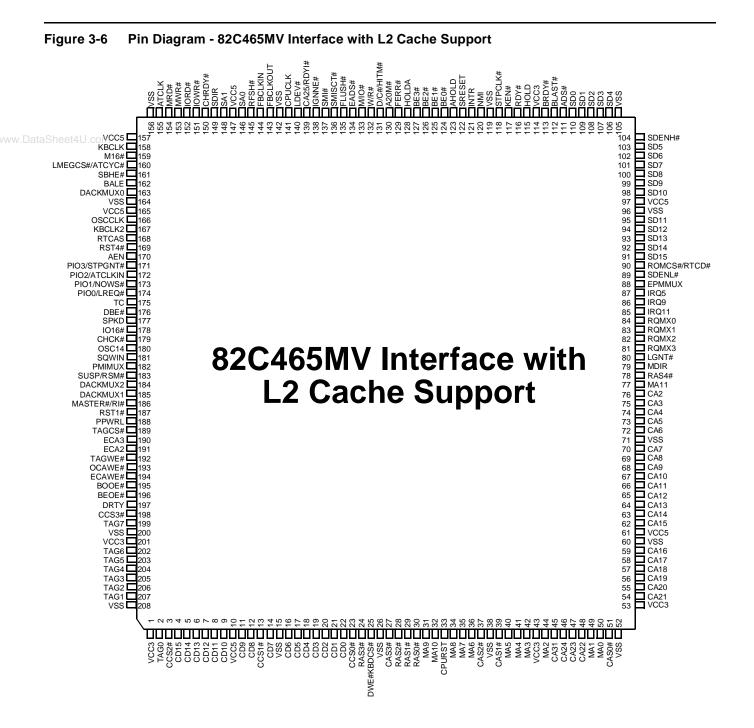

|                 |     | 3.5.2    | 82C465MV Interface with L2 Cache Support              | 14 |  |

|                 |     | 3.5.3    | 82C465MV with 386 Interface                           | 15 |  |

|                 | 3.6 | Pin Sig  | gnal Characteristics                                  | 16 |  |

|                 | 3.7 | Signal   | Descriptions                                          | 21 |  |

|                 |     | 3.7.1    | Clock and Reset Interface                             | 21 |  |

|                 |     | 3.7.2    | CPU / VL-Bus Interface                                | 22 |  |

|                 |     | 3.7.3    | DRAM Interface                                        | 25 |  |

|                 |     | 3.7.4    | L2 Cache Interface                                    | 26 |  |

|                 |     | 3.7.5    | ISA Bus Interface                                     | 26 |  |

|                 |     | 3.7.6    | IPC (82C206) Interface                                | 27 |  |

|                 |     | 3.7.7    | PMU Interface                                         | 28 |  |

|                 |     |          |                                                       |    |  |

# 82C465MV/MVA/MVB

|     |        | 3.7.8   | Miscellaneous Signal Interface                            |    |

|-----|--------|---------|-----------------------------------------------------------|----|

|     |        | 3.7.9   | Power and Ground Pins                                     | 31 |

| 4.0 | Fun    | ctional | Description                                               | 33 |

|     | 4.1    | 463/46  | 5 Chipset Programming Comparison                          | 33 |

|     | 4.2    | CPU ar  | nd VL-Bus Interface                                       | 33 |

|     | 4U.com | 4.2.1   | Basic Command Interface                                   | 33 |

|     |        |         | 4.2.1.1 Cycle Signals                                     | 33 |

|     |        | 4.2.2   | Local Device Interface                                    |    |

|     |        |         | 4.2.2.1 LDEV# Operation                                   | 34 |

|     |        |         | 4.2.2.2 LRDY# Operation                                   | 35 |

|     |        |         | 4.2.2.3 VL-Bus Arbitration Logic                          | 35 |

|     |        | 4.2.3   | VL-Bus Masters                                            |    |

|     |        |         | 4.2.3.1 Hardware Considerations                           | 36 |

|     |        |         | 4.2.3.2 Programming                                       | 36 |

|     |        | 4.2.4   | Data Bus Conversion/Data Path Logic                       |    |

|     |        |         | 4.2.4.1 CPU Data Bus Multiplex Option                     | 36 |

|     |        | 4.2.5   | Numeric Coprocessor Interface                             |    |

|     |        |         | 4.2.5.1 Hardware Considerations                           |    |

|     |        |         | 4.2.5.2 Programming                                       |    |

|     |        | 4.2.6   | Special CPU Interface Support                             |    |

|     |        |         | 4.2.6.1 Ability to Cut CPU Power During Suspend           |    |

|     |        |         | 4.2.6.2 Programmable A20M# Functionality                  | 37 |

|     |        |         | 4.2.6.3 Programmable CPU RESET Functionality              |    |

|     |        |         | 4.2.6.4 Programmable DACK2# Functionality                 |    |

|     |        |         | 4.2.6.5 Cyrix Linear Burst Mode Support                   |    |

|     |        |         | 4.2.6.6 Programmable Exclusion of Coprocessor Recognition |    |

|     |        |         | 4.2.6.7 Programmable RDYI# Functionality                  |    |

|     | 4.3    | System  | n Functions                                               | 39 |

|     |        | 4.3.1   | Reset Logic                                               | 39 |

|     |        |         | 4.3.1.1 RST1#                                             | 39 |

|     |        |         | 4.3.1.2 RST4#                                             |    |

|     |        |         | 4.3.1.3 CPURST and SRESET                                 |    |

|     |        |         | 4.3.1.4 Resume Reset (RSMRST#) Function                   |    |

|     |        |         | 4.3.1.5 Rapid RESET Generation                            |    |

|     |        |         | 4.3.1.6 Fast Reset Handling in SMM                        | 41 |

|                   |     | 4.3.2 | ,         | Clock Generation                                          |    |

|-------------------|-----|-------|-----------|-----------------------------------------------------------|----|

|                   |     |       | 4.3.2.1   | Input Clocks                                              |    |

|                   |     |       | 4.3.2.2   | Output Clocks                                             |    |

|                   |     | 4.3.3 |           | Generation                                                |    |

|                   |     |       | 4.3.3.1   | Rapid A20M# Generation                                    |    |

|                   |     |       | 4.3.3.2   | Inhibition of Fast A20M# and Fast Reset Generation        |    |

|                   |     |       | 4.3.3.3   | A20M# Handling in SMM                                     |    |

| w.DataSheet4U.com |     |       | 4.3.3.4   | Port 060/064h A20M# Setting Accessibility                 |    |

|                   | 4.4 | DRAM  | Controlle | r                                                         | 48 |

|                   |     | 4.4.1 | DRAM C    | Controller Hardware Options                               | 48 |

|                   |     | 4.4.2 | DRAM B    | Bus Drive Capability                                      | 50 |

|                   |     | 4.4.3 | Setting L | Jp DRAM Operation                                         | 50 |

|                   |     |       | 4.4.3.1   | Faster Memory Cycles                                      | 52 |

|                   |     |       | 4.4.3.2   | DRAM Mapping Scheme Enable                                | 52 |

|                   |     |       | 4.4.3.3   | DRAM Control Register 2I - SYSCFG 35h                     | 52 |

|                   |     | 4.4.4 | EDO DR    | AM Support                                                | 53 |

|                   |     | 4.4.5 | DRAM C    | Cycle Speed                                               | 53 |

|                   |     | 4.4.6 | System    | ROM and Shadow RAM                                        | 54 |

|                   | 4.5 | Cache | Control   |                                                           | 57 |

|                   |     | 4.5.1 | Global E  | nabling of Cacheability                                   | 57 |

|                   |     | 4.5.2 | Defining  | Non Cacheable Blocks                                      | 57 |

|                   |     |       | 4.5.2.1   | C000, E000, F000h Block Cache Enable                      | 58 |

|                   |     |       | 4.5.2.2   | Cache Control of C000-F000h                               | 59 |

|                   |     |       | 4.5.2.3   | Cache Invalidation Feature                                | 61 |

|                   |     | 4.5.3 | L1 Write  | -Back Cache Support                                       | 61 |

|                   |     |       | 4.5.3.1   | Hardware Considerations                                   | 61 |

|                   |     |       | 4.5.3.2   | Extra Programmable Pin Options                            |    |

|                   |     |       | 4.5.3.3   | Programming                                               |    |

|                   |     |       | 4.5.3.4   | Burst Write Feature                                       | 63 |

|                   |     | 4.5.4 | L2 Cach   | e Support                                                 | 64 |

|                   |     |       | 4.5.4.1   | Performance                                               |    |

|                   |     |       | 4.5.4.2   | L2 Cache Operation Details                                |    |

|                   |     |       | 4.5.4.3   | L2 Cache Arrangement                                      |    |

|                   |     |       | 4.5.4.4   | Differences Between L2 Support and No Cache Support Modes |    |

|                   |     |       | 4.5.4.5   | Hardware Considerations                                   |    |

|                   |     |       | 4.5.4.6   | Programming                                               |    |

|                   |     |       | 4.5.4.7   | Timing Control Register                                   | 70 |

|                   |     |       |           |                                                           |    |

| 4.6 | Periphe | 71                                                |    |

|-----|---------|---------------------------------------------------|----|

|     | 4.6.1   | ISA Bus Logic                                     | 71 |

|     |         | 4.6.1.1 Hardware Considerations                   | 71 |

|     |         | 4.6.1.2 ISA Write Cycle Inhibition                | 72 |

|     |         | 4.6.1.3 ISA Bus Clock Options                     |    |

|     |         | 4.6.1.4 ISA Bus Refresh Control                   | 73 |

|     |         | 4.6.1.5 Programming                               |    |

|     |         | 4.6.1.6 ISA Bus Address Buffer Enable Signal      | 75 |

|     |         | 4.6.1.7 Docking Station Attachment Feature        | 75 |

|     | 4.6.2   | Programmed Hardware Reset                         | 76 |

|     | 4.6.3   | Integrated Peripheral Controller                  | 76 |

|     |         | 4.6.3.1 Multiplexor Hardware Considerations       | 76 |

|     |         | 4.6.3.2 DMA Hardware Considerations               | 76 |

|     |         | 4.6.3.3 IPC Configuration Programming             | 77 |

|     |         | 4.6.3.4 Interrupt Controller Register Programming | 77 |

|     |         | 4.6.3.5 DMA Controller Programming Registers      |    |

|     |         | 4.6.3.6 Determining DMA Status Before Suspend     | 84 |

|     |         | 4.6.3.7 DMA Register Read Back Provisions         |    |

|     |         | 4.6.3.8 LDEV# Sense Control                       |    |

|     |         | 4.6.3.9 Type F DMA Support                        | 86 |

|     |         | 4.6.3.10 Timer Programming Registers              | 87 |

|     |         | 4.6.3.11 Writing/Reading I/O Port 070h            |    |

|     |         | 4.6.3.12 Additional Floppy Support                | 89 |

|     |         | 4.6.3.13 IRQ8 Polarity                            |    |

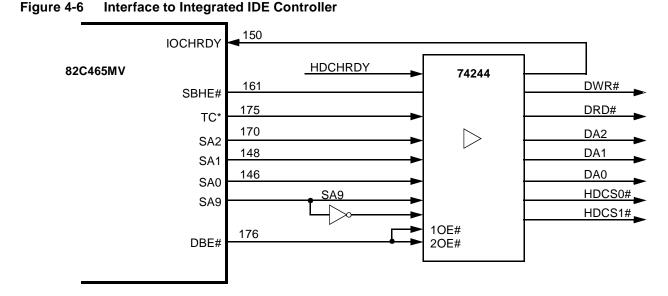

|     | 4.6.4   | Integrated Local-Bus Enhanced IDE Interface       |    |

|     |         | 4.6.4.1 Hardware Considerations                   |    |

|     |         | 4.6.4.2 Performance and Power                     |    |

|     |         | 4.6.4.3 Signal Connection                         |    |

|     |         | 4.6.4.4 DBE (TRIS) Polarity                       |    |

|     |         | 4.6.4.5 Programming                               |    |

|     |         | 4.6.4.6 Four-Drive IDE Support                    |    |

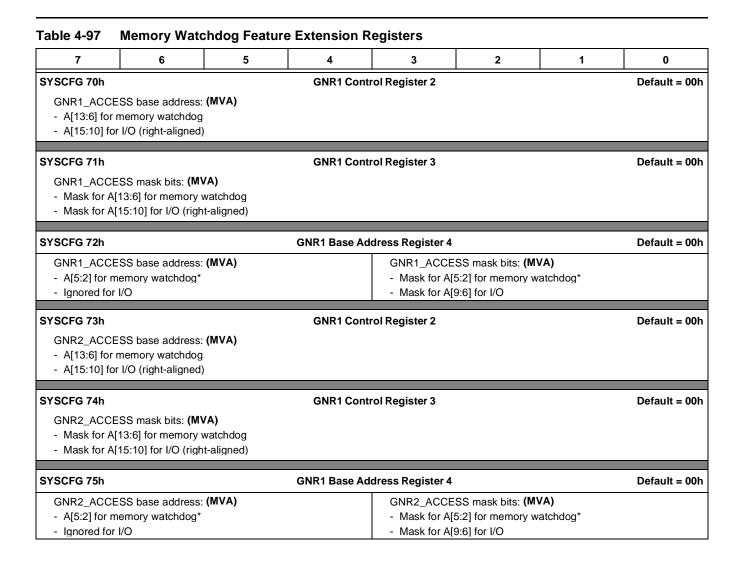

|     | 4.6.5   | Compact ISA Interface                             |    |

|     |         | 4.6.5.1 CISA Stop Clock Cycle Generation          |    |

|     |         | 4.6.5.2 Configuration Cycle Generation            |    |

|           |     |        | 4.6.5.3    | Driveback Cycle Handling                        | 100 |

|-----------|-----|--------|------------|-------------------------------------------------|-----|

|           | 4.7 | Power  | Managem    | nent Unit                                       | 102 |

|           |     | 4.7.1  | Activity I | Monitoring                                      | 102 |

|           |     |        | 4.7.1.1    | Timers                                          | 102 |

|           |     |        | 4.7.1.2    | Events                                          | 103 |

|           |     | 4.7.2  | Timers     |                                                 |     |

|           |     |        | 4.7.2.1    | Time-out Count and Time-out SMI                 | 104 |

| eet4U.com |     | 4.7.3  | ACCES      | S Events                                        |     |

|           |     |        | 4.7.3.1    | Serial (COMx) and Parallel Port (LPT) Access    |     |

|           |     |        | 4.7.3.2    | ISA Bus Floppy and Hard Drive Access            |     |

|           |     |        | 4.7.3.3    | Integrated Controller Hard Drive Access         |     |

|           |     |        | 4.7.3.4    | Keyboard Access                                 |     |

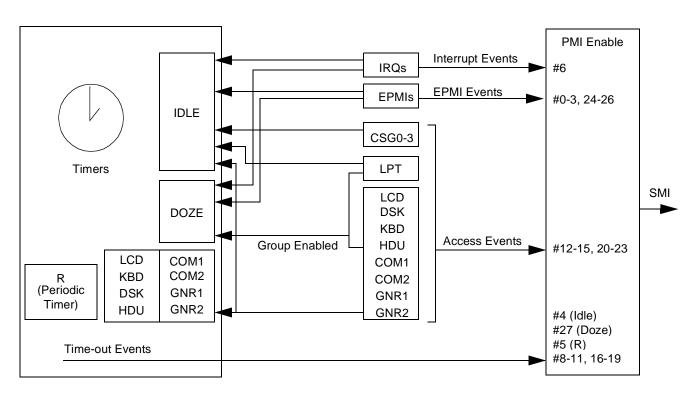

|           |     |        | 4.7.3.5    | LCD Controller Access                           | 107 |

|           |     |        | 4.7.3.6    | Chip Select Generation (CSG) Access             | 108 |

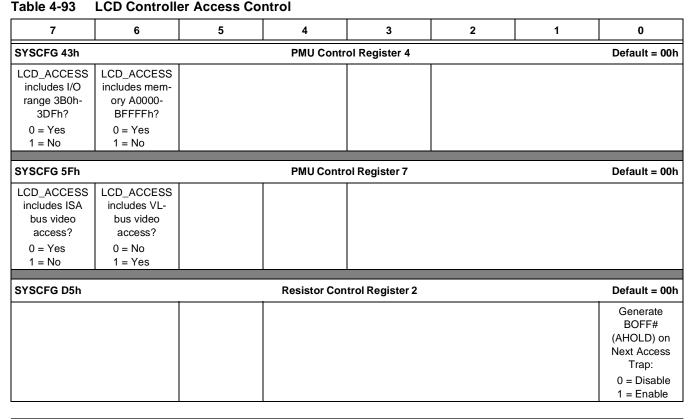

|           |     |        | 4.7.3.7    | General Purpose (GNR) Access                    | 108 |

|           |     | 4.7.4  | Activity   | Tracking                                        | 111 |

|           |     | 4.7.5  | Reloadir   | ng IDLE_TIMER                                   | 112 |

|           |     | 4.7.6  | External   | PMI Events                                      | 112 |

|           |     |        | 4.7.6.1    | Suspend/Resume Pin                              | 113 |

|           |     |        | 4.7.6.2    | EPMI Signal Relocation                          | 113 |

|           |     |        | 4.7.6.3    | Programming                                     | 114 |

|           |     |        | 4.7.6.4    | Power Management Event Status                   | 115 |

|           | 4.8 | Syster | m Manage   | ment Interrupt (SMI)                            | 116 |

|           |     | 4.8.1  | SMI Pre    | setting for Various CPU Type                    | 118 |

|           |     |        | 4.8.1.1    | Intel SL-Enhanced and AMD 5x86 CPU Settings     | 119 |

|           |     |        | 4.8.1.2    | Cyrix CPU Settings                              | 119 |

|           |     |        | 4.8.1.3    | AMD 486DXLV / IBM "Blue Lightning" CPU Settings | 119 |

|           |     |        | 4.8.1.4    | Non-SMI CPU Settings                            | 120 |

|           |     | 4.8.2  | Loading    | Initial SMM Code and Data                       | 120 |

|           |     |        | 4.8.2.1    | SMBASE Register                                 | 121 |

|           |     | 4.8.3  | Run-Tim    | ne SMI Address Relocation                       | 122 |

|           |     |        | 4.8.3.1    | Relocation with Standard Interface SMI          | 122 |

|           |     |        | 4.8.3.2    | Relocation with Alternative Interface SMI       | 122 |

|           |     | 4.8.4  | SMI Eve    | ent Generation                                  | 122 |

|           |     |        | 4.8.4.1    | Time-out Event Generation of SMI                |     |

|           |     |        | 4.8.4.2    | Access Event Generation of SMI                  |     |

|           |     |        | 4.8.4.3    | No Flush Required on Entry to SMM               | 123 |

# 82C465MV/MVA/MVB

|                  |        | 4.8.4.4   | Interrupt Event Generation of SMI     |     |

|------------------|--------|-----------|---------------------------------------|-----|

|                  |        | 4.8.4.5   | Enabling of Events to Generate SMI    |     |

|                  | 4.8.5  | DRQ Ge    | eneration of SMI                      | 126 |

|                  | 4.8.6  | Servicin  | g an SMI                              |     |

|                  |        | 4.8.6.1   | PMI Source Register Details           |     |

|                  |        | 4.8.6.2   | EPMI Pin PMI Sources                  |     |

|                  |        | 4.8.6.3   | I/O SMI Trap Indication               |     |

| .DataSheet4U.com |        | 4.8.6.4   | Utility Registers                     |     |

| 4.9              | Systen | n Power M | Nanagement                            | 129 |

|                  | 4.9.1  | STPCLK    | K# Mechanism to Change CPU Speed      |     |

|                  |        | 4.9.1.1   | Hardware Considerations               | 129 |

|                  |        | 4.9.1.2   | Programming                           | 129 |

|                  | 4.9.2  | Doze Mo   | ode                                   |     |

|                  |        | 4.9.2.1   | Dual Doze Timer Reload Selections     | 131 |

|                  |        | 4.9.2.2   | Presetting Events to Reset Doze Mode  | 133 |

|                  |        | 4.9.2.3   | LDEV# Doze Reset                      | 134 |

|                  |        | 4.9.2.4   | Doze Reset Inside SMM                 | 134 |

|                  |        | 4.9.2.5   | Automatic (Hardware) Doze Mode        | 135 |

|                  |        | 4.9.2.6   | APM (Software) Doze Mode              | 136 |

|                  |        | 4.9.2.7   | Start Doze Bit                        |     |

|                  |        | 4.9.2.8   | Using Doze Time-out to Trigger an SMI | 137 |

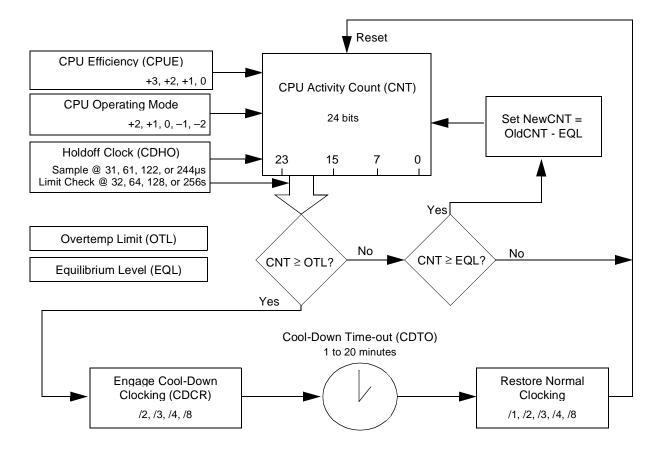

|                  | 4.9.3  | CPU Th    | ermal Management Unit                 | 138 |

|                  |        | 4.9.3.1   | Prediction of Overtemp Activity       | 138 |

|                  |        | 4.9.3.2   | Example                               | 140 |

|                  |        | 4.9.3.3   | Programming                           | 140 |

|                  | 4.9.4  | Emerge    | ncy Overtemp Sense                    | 141 |

|                  |        | 4.9.4.1   | Programming                           | 141 |

| 4.10             | Suspe  | nd and Re | esume                                 | 142 |

|                  | 4.10.1 | Suspend   | d Mode                                |     |

|                  |        | •         | Suspend Mode Power Savings            |     |

|                  | 4.10.2 | Resume    | e Event                               |     |

|                  |        |           | EPMI/IRQ Events                       |     |

|                  |        | 4.10.2.2  | SUSP/RSM and RI Events                | 145 |

|                  | 4.10.3 | Chip-Lev  | vel Power Conservation Features       |     |

|                  |        | -         | Automatic Keeper Resistors            |     |

|                  |        |           | Zero-Volt CPU Suspend                 |     |

|                  |        | 4.10.3.3  | Clock Stretching                      | 149 |

|                  |        |           |                                       |     |

|                 |      | 4.10.3.4 Stopping IPC Clock When Not In Use                               |     |

|-----------------|------|---------------------------------------------------------------------------|-----|

|                 |      | 4.10.3.5 Stopping KBCLK and KBCLK2                                        | 149 |

|                 | 4.11 | Power Control Latch and PIO Pins                                          | 150 |

|                 |      | 4.11.1 Power Control Latch                                                | 150 |

|                 |      | 4.11.1.1 Hardware Considerations                                          |     |

|                 |      | 4.11.1.2 Signal Considerations                                            |     |

| DataSheet4U.com |      | 4.11.1.3 Programming                                                      |     |

|                 |      | 4.11.2 Programmable I/O Pins<br>4.11.2.1 PIO3/STPGNT# Pin Select          |     |

|                 |      | 4.11.2.2 PIO2/CPUSPD Pin Select                                           |     |

|                 |      | 4.11.2.3 PIO1/NOWS# Pin Select                                            |     |

|                 |      | 4.11.3 Programmable Chip Select Feature                                   |     |

|                 |      | 4.11.3.1 Programmable Chip Select Limitations                             |     |

| 5.0             | Rea  | ister Summary                                                             |     |

|                 |      | ·····                                                                     |     |

| 6.0             | Elec | trical Ratings                                                            | 177 |

|                 | 6.1  | Absolute Maximum Ratings                                                  |     |

|                 | 6.2  | 5.0V DC Characteristics: TA = 0°C to +70°C, VDDS = 5.0V± 5%               |     |

|                 | 6.3  | 3.3V DC Characteristics: TA = 0°C to +70°C, VDD = 3.3V± 5%                | 178 |

|                 | 6.4  | AC Characteristics                                                        | 178 |

|                 | 6.5  | Timing Characteristics: CPU interface = 3.3V, all other interfaces = 5.0V |     |

|                 |      | 6.5.1 Cache Timing                                                        |     |

|                 |      | 6.5.2 DRAM Timing                                                         |     |

|                 |      | 6.5.3 AT Bus Timing                                                       |     |

|                 |      | 6.5.4 Reset and Local Bus Timing                                          |     |

|                 |      | 6.5.5 Power Management Timing                                             |     |

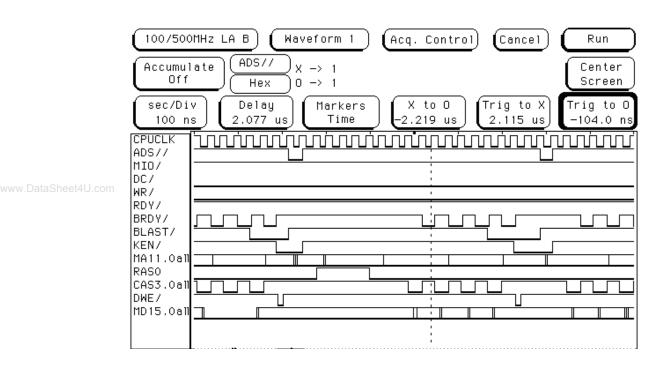

|                 | 6.6  | Timing Diagrams                                                           |     |

|                 | 6.7  | Functional Memory Timing Diagrams                                         |     |

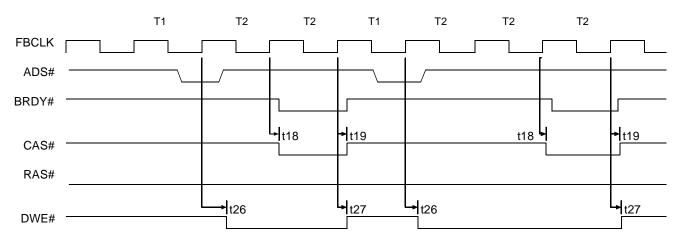

|                 |      | 6.7.1 Fast Page Mode (FPM) DRAM                                           |     |

|                 |      | 6.7.2 Extended Data Out (EDO)                                             | 213 |

|                 |      |                                                                           |     |

www.DataSheet40.com

# 82C465MV/MVA/MVB

| 7.0 | Test       | Test Mode Information 219     |                          |  |  |  |  |  |  |  |  |

|-----|------------|-------------------------------|--------------------------|--|--|--|--|--|--|--|--|

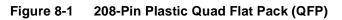

| 8.0 | Mec        | echanical Package Outline 221 |                          |  |  |  |  |  |  |  |  |

| Α.  | Inco       | npatibilities with the        | 82C463MV 223             |  |  |  |  |  |  |  |  |

|     | A.1        | Power Plane Changes           |                          |  |  |  |  |  |  |  |  |

|     | <b>A.2</b> | Read Cycle Efficiency         |                          |  |  |  |  |  |  |  |  |

|     | A.3        | ADS# Sampling                 |                          |  |  |  |  |  |  |  |  |

|     | A.4        | Removal of Sequencer          |                          |  |  |  |  |  |  |  |  |

|     | A.5        | Default Refresh Rate Cha      | ange                     |  |  |  |  |  |  |  |  |

|     | A.6        | I/O Blocking Default Cha      | nge                      |  |  |  |  |  |  |  |  |

|     | A.7        | Suspend Mode DACKML           | IX Parking               |  |  |  |  |  |  |  |  |

| в.  | Com        | -                             | -                        |  |  |  |  |  |  |  |  |

| р.  | Com        |                               | n 225                    |  |  |  |  |  |  |  |  |

|     | B.1        | Compact ISA Overview .        |                          |  |  |  |  |  |  |  |  |

|     | B.2        | Compact ISA Cycle Defin       | nition                   |  |  |  |  |  |  |  |  |

|     |            | B.2.1 Memory Cycle            |                          |  |  |  |  |  |  |  |  |

|     |            | B.2.2 I/O Cycle               |                          |  |  |  |  |  |  |  |  |

|     |            | B.2.3 DMA on the CISA         | VISA Bus230              |  |  |  |  |  |  |  |  |

|     |            | B.2.4 DACK# Cycle             |                          |  |  |  |  |  |  |  |  |

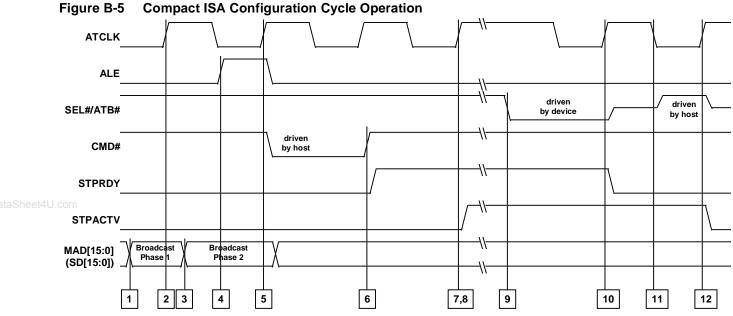

|     |            | B.2.5 Configuration Cy        | cle                      |  |  |  |  |  |  |  |  |

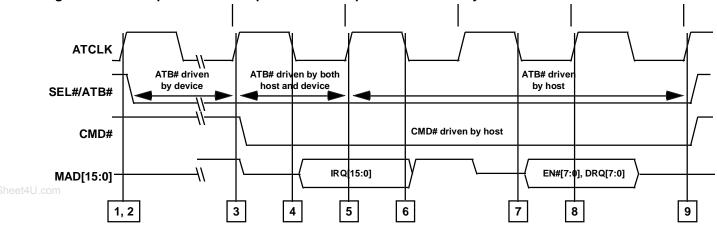

|     | B.3        | Interrupt and DMA Requ        | est Drive-Back234        |  |  |  |  |  |  |  |  |

|     |            | B.3.1 Interrupt Request       | s234                     |  |  |  |  |  |  |  |  |

|     |            | B.3.2 DMA Requests            |                          |  |  |  |  |  |  |  |  |

|     | В.4        | Performance Control           |                          |  |  |  |  |  |  |  |  |

|     | В.5        | Compatibility and Host F      | Responsibilities236      |  |  |  |  |  |  |  |  |

|     | B.6        | Shared Speaker Signal S       | Support (Optional)236    |  |  |  |  |  |  |  |  |

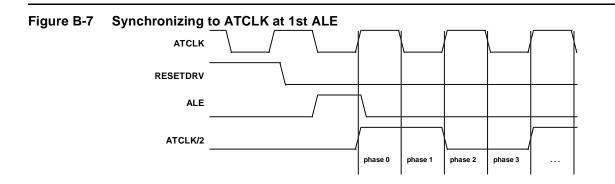

|     |            | B.6.1 Initial Synchroniz      | ation236                 |  |  |  |  |  |  |  |  |

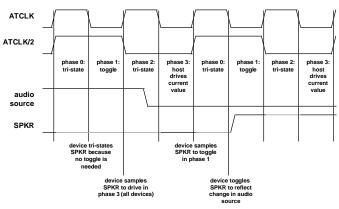

|     |            | B.6.2 SPKR Sharing D          | uring Active Mode237     |  |  |  |  |  |  |  |  |

|     |            | B.6.3 SPKR Sharing D          | uring Stop Clock Mode238 |  |  |  |  |  |  |  |  |

|     | B.6.4                    | Audio Ou                                                                                                                                                                                                | utput Circuit Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 238                                                          |

|-----|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| B.7 | Autom                    | atic Volta                                                                                                                                                                                              | ge Threshold Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 238                                                          |

| 82C | 602A N                   | lotebook                                                                                                                                                                                                | Companion Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 239                                                          |

| C.1 | Featur                   | es                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 239                                                          |

|     | C.1.1                    | General                                                                                                                                                                                                 | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 239                                                          |

|     | C.1.2                    | Power-S                                                                                                                                                                                                 | aving Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 239                                                          |

| C.2 | Overvi                   | ew                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 239                                                          |

|     | C.2.1                    | Modes/C                                                                                                                                                                                                 | Chipset Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 239                                                          |

|     | C.2.2                    | Design N                                                                                                                                                                                                | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 239                                                          |

|     | C.2.3                    | Reducing                                                                                                                                                                                                | g Suspend Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 240                                                          |

|     | C.2.4                    | 82C602/                                                                                                                                                                                                 | A Power Consumption Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 240                                                          |

|     | C.2.5                    | Internal I                                                                                                                                                                                              | Real-Time Clock (RTC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 240                                                          |

|     |                          | C.2.5.1                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                              |

|     |                          | C.2.5.2                                                                                                                                                                                                 | RTC Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 241                                                          |

|     |                          | C.2.5.3                                                                                                                                                                                                 | RTC Address Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 241                                                          |

|     |                          | C.2.5.4                                                                                                                                                                                                 | Programming the RTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 242                                                          |

|     |                          | C.2.5.5                                                                                                                                                                                                 | Square-wave Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 243                                                          |

|     |                          | C.2.5.6                                                                                                                                                                                                 | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 243                                                          |

|     |                          | C.2.5.7                                                                                                                                                                                                 | Power-Down/Power-Up Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 248                                                          |

|     |                          | C.2.5.8                                                                                                                                                                                                 | Control/Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 249                                                          |

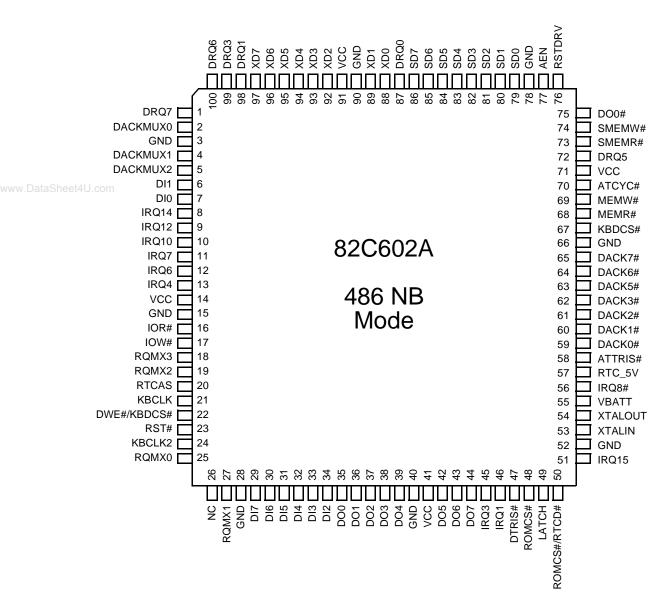

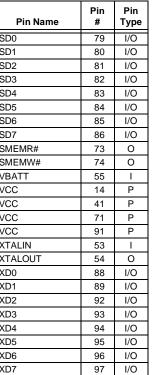

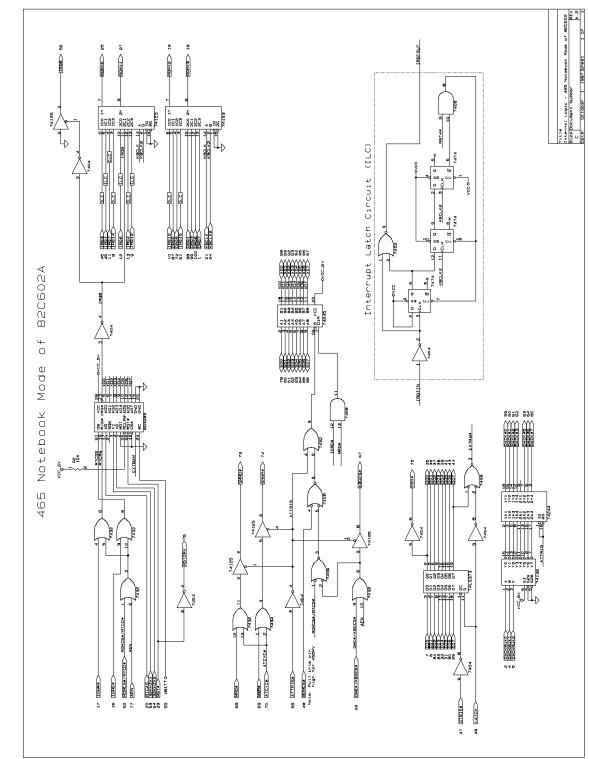

| C.3 | Signal                   | Definition                                                                                                                                                                                              | IS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 251                                                          |

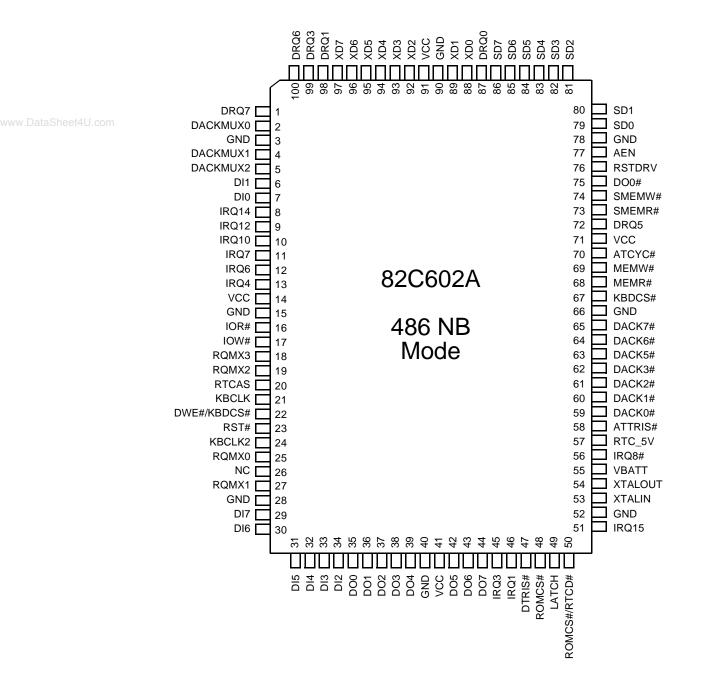

|     | C.3.1                    | 486 NB I                                                                                                                                                                                                | Mode Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 254                                                          |

|     |                          | C.3.1.1                                                                                                                                                                                                 | Clock and Reset Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 254                                                          |

|     |                          | C.3.1.2                                                                                                                                                                                                 | Interrupt/Control Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 254                                                          |

|     |                          | C.3.1.3                                                                                                                                                                                                 | ISA DMA Arbiter Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 254                                                          |

|     |                          | C.3.1.4                                                                                                                                                                                                 | Bus Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 255                                                          |

|     |                          | C.3.1.5                                                                                                                                                                                                 | Real-Time Clock and Keyboard Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 255                                                          |

|     |                          | C.3.1.6                                                                                                                                                                                                 | Miscellaneous Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 256                                                          |

|     |                          | C.3.1.7                                                                                                                                                                                                 | Power and Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 256                                                          |

| C.4 | Schem                    | natics                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 257                                                          |

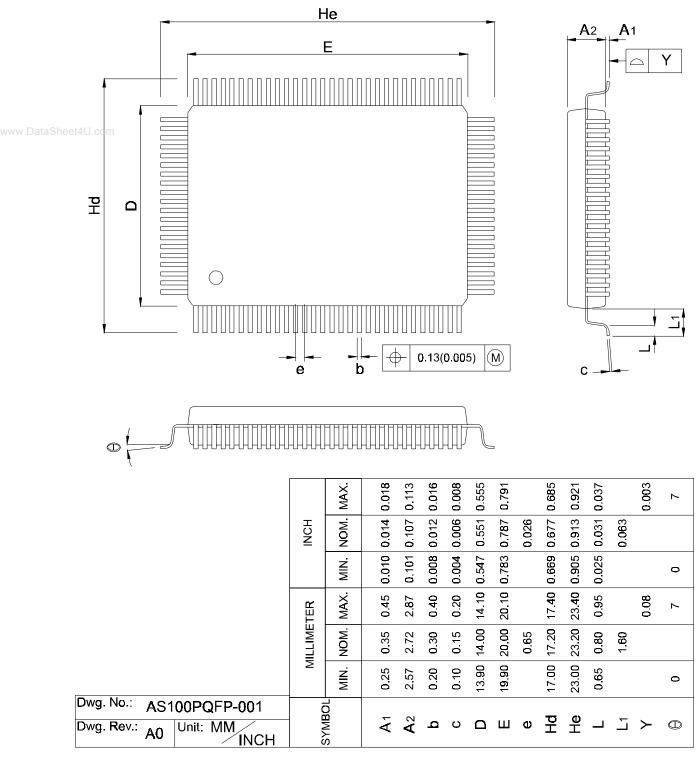

| C.5 | 82C60                    | 2A Mecha                                                                                                                                                                                                | nical Package Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 258                                                          |

|     | 82C<br>C.1<br>C.2<br>C.3 | B.7       Autom         82C:602A M       C.1         C.1       Featur         C.1.1       C.1.2         C.2       Overvia         C.2.1       C.2.3         C.2.3       C.2.4         C.2.5       C.2.5 | B.7       Automatic Volta         82C602A Notebook         C.1       Features         C.1.1       General         C.1.2       Power-S         C.2       Design N         C.2.1       Modes/O         C.2.2       Design N         C.2.3       Reducing         C.2.4       82C602/         C.2.5       Internal         C.2.5       Internal         C.2.5.1       C.2.5.3         C.2.5.2       C.2.5.3         C.2.5.3       C.2.5.4         C.2.5.4       C.2.5.5         C.2.5.5       C.2.5.6         C.2.5.7       C.2.5.8         C.3       Signal Definition         C.3.1       486 NB         C.3.1.1       C.3.1.2         C.3.1.3       C.3.1.3         C.3.1.4       C.3.1.5         C.3.1.5       C.3.1.6         C.3.1.7       C.4 | <ul> <li>B.7 Automatic Voltage Threshold Detection</li></ul> |

ww.DataSheet4U.com

Page xii

# List of Figures

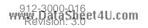

| Figure 1-1   | System Block Diagram                                                              | 1   |

|--------------|-----------------------------------------------------------------------------------|-----|

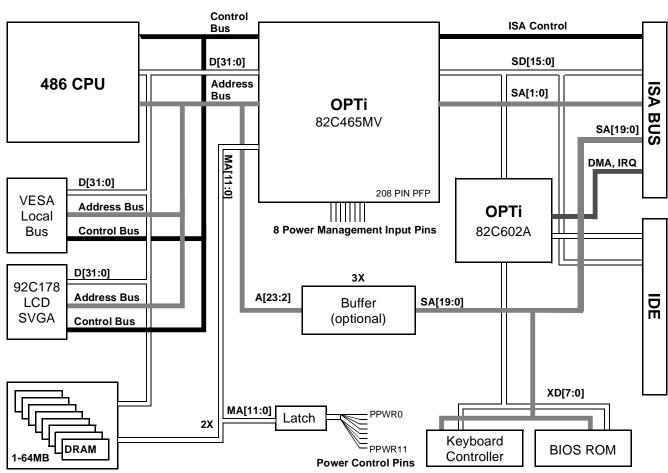

| Figure 3-1   | RST4# and Buffer Connection                                                       | 8   |

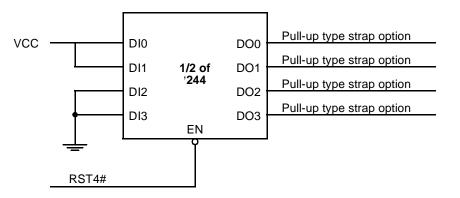

| Figure 3-2   | Standard DACKMUX0-2 Connection (SYSCFG A0h[3] = 1)                                | 9   |

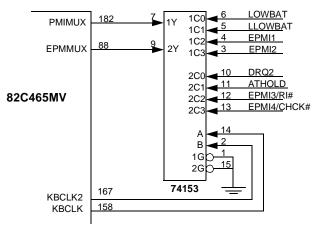

| Figure 3-3   | Multiplexed EPMI Input Connections                                                | 10  |

| Figure 3-4   | Pin Diagram - Standard Mode                                                       | 11  |

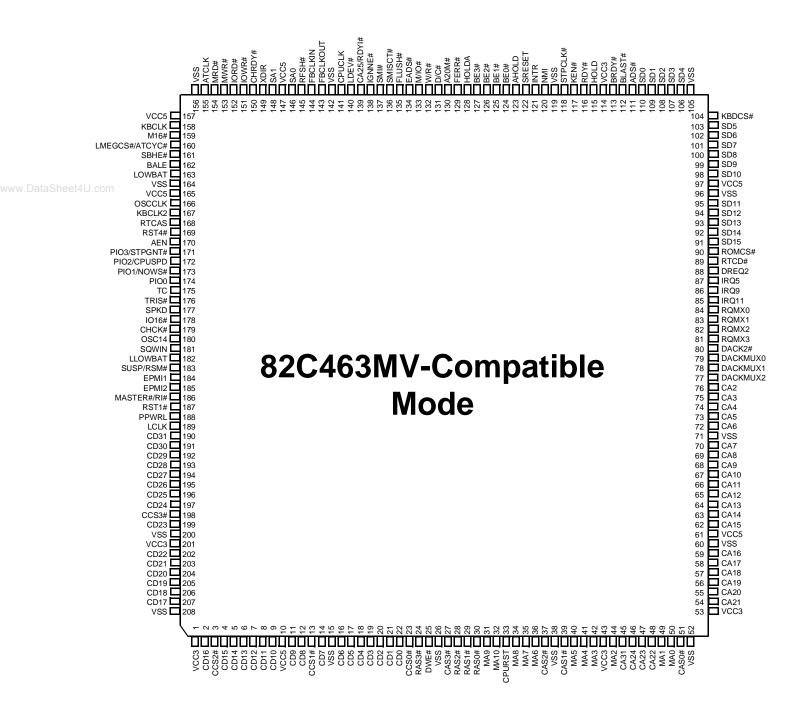

| Figure 3-5   | Pin Diagram - 82C463MV-Compatible Mode                                            | 13  |

| Figure 3-6   | Pin Diagram - 82C465MV Interface with L2 Cache Support                            | 14  |

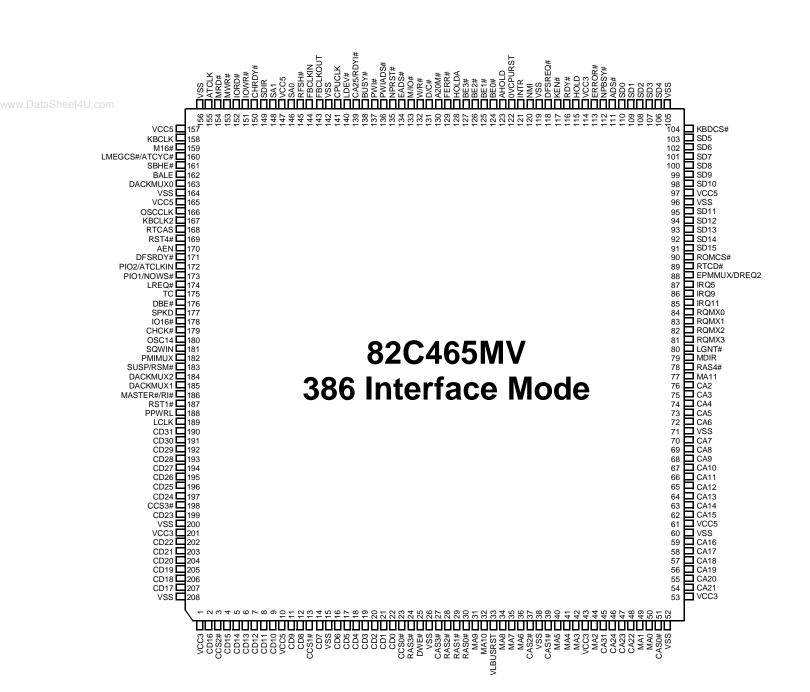

| U Figure 3-7 | Pin Diagram - 386 Interface Mode                                                  | 15  |

| Figure 4-1   | Resume Reset Function                                                             | 40  |

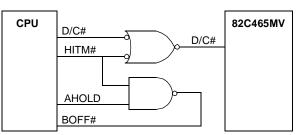

| Figure 4-2   | Generation of HITM# and BOFF#                                                     | 61  |

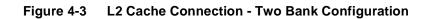

| Figure 4-3   | L2 Cache Connection - Two Bank Configuration                                      | 64  |

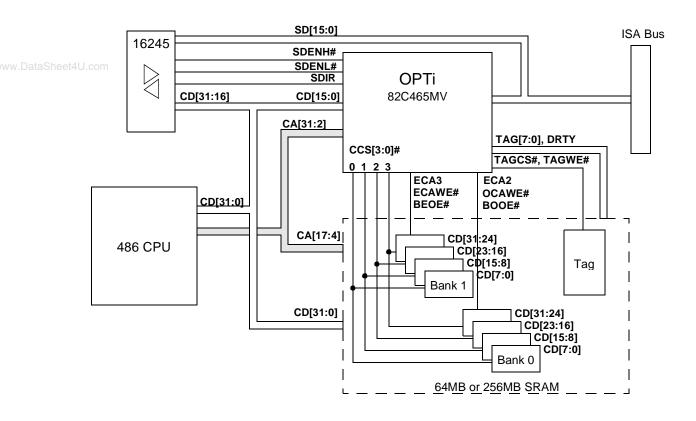

| Figure 4-4   | Correcting AEN for 16-bit DMA                                                     | 77  |

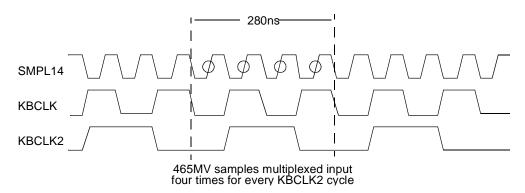

| Figure 4-5   | Multiplexed Input Sampling Points                                                 | 77  |

| Figure 4-6   | Interface to Integrated IDE Controller                                            | 90  |

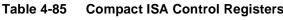

| Figure 4-7   | Activity Monitoring Block Diagram                                                 | 102 |

| Figure 4-8   | Thermal Management Block Diagram                                                  | 139 |

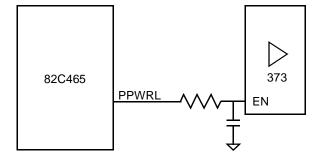

| Figure 4-9   | Damping R-C for PPWRL Spike                                                       |     |

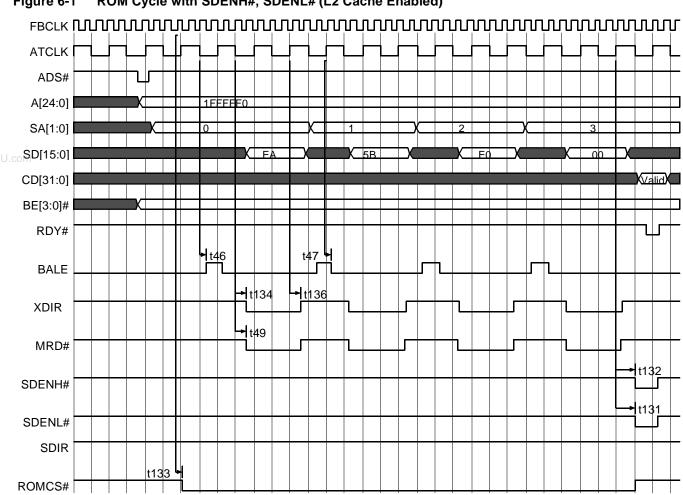

| Figure 6-1   | ROM Cycle with SDENH#, SDENL# (L2 Cache Enabled)                                  | 183 |

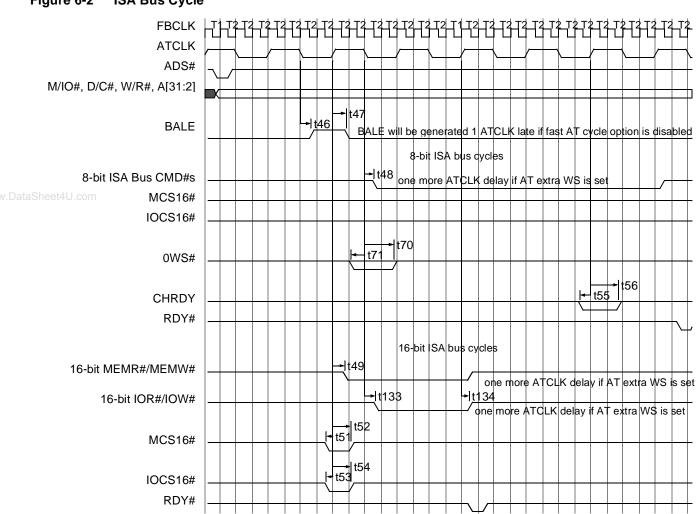

| Figure 6-2   | ISA Bus Cycle                                                                     | 184 |

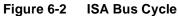

| Figure 6-3   | Keyboard Controller Access Cycle                                                  | 185 |

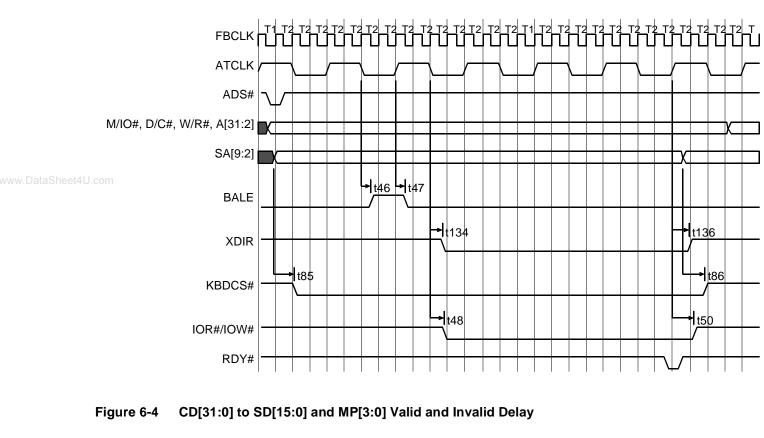

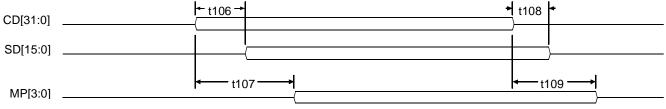

| Figure 6-4   | CD[31:0] to SD[15:0] and MP[3:0] Valid and Invalid Delay                          | 185 |

| Figure 6-5   | SD[15:0] to CD[31:0] and MP[3:0] Valid and Invalid Delay                          |     |

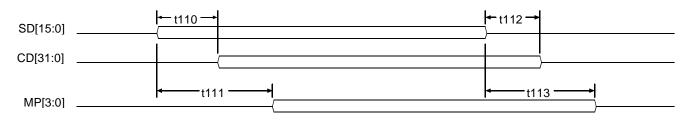

| Figure 6-6   | Data Valid and Invalid Delay Between SD[15:8] and SD[7:0] Data Swapping           |     |

| Figure 6-7   | NMI Valid Delay Related to IOCHK#                                                 | 186 |

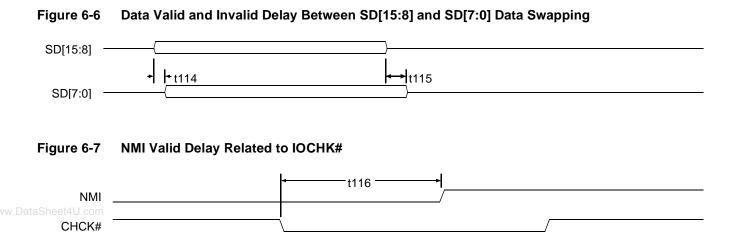

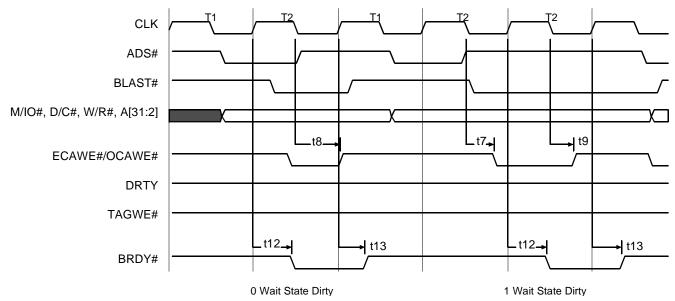

| Figure 6-8   | L2 Cache Read Miss - Dirty, Double Bank Cache                                     |     |

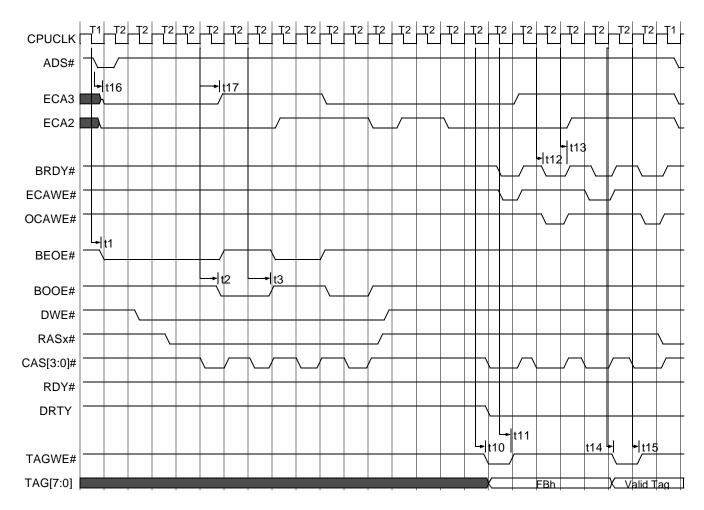

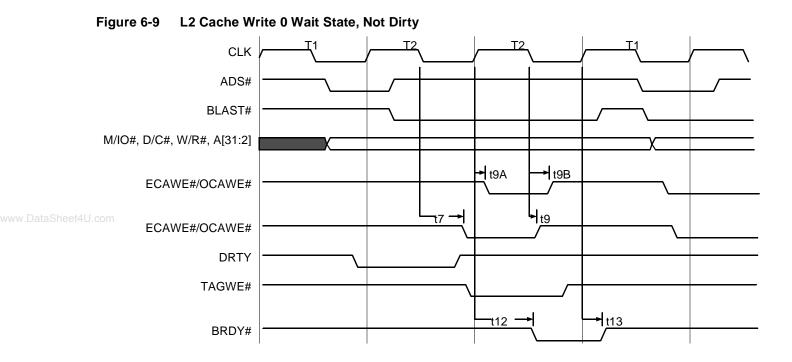

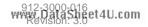

| Figure 6-9   | L2 Cache Write 0 Wait State, Not Dirty                                            | 187 |

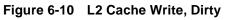

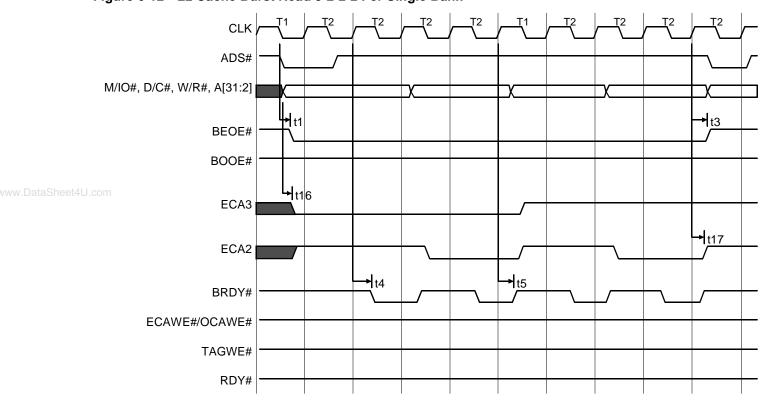

| Figure 6-10  | L2 Cache Write, Dirty                                                             | 187 |

| Figure 6-11  | L2 Cache Burst Read 3-2-2-2 For Double Bank                                       |     |

| Figure 6-12  | L2 Cache Burst Read 3-2-2-2 For Single Bank                                       |     |

| Figure 6-13  | L2 Cache Burst Read 2-1-1-1 Cycle For Double Bank                                 |     |

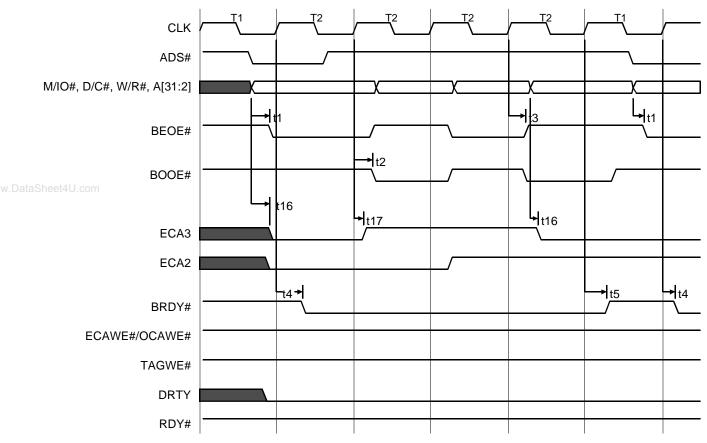

| Figure 6-14  | HITM# Active With L2 Cache Hit, L2 Cache 3-2-2-2 Write Cycle (Cache 0 Wait Write) |     |

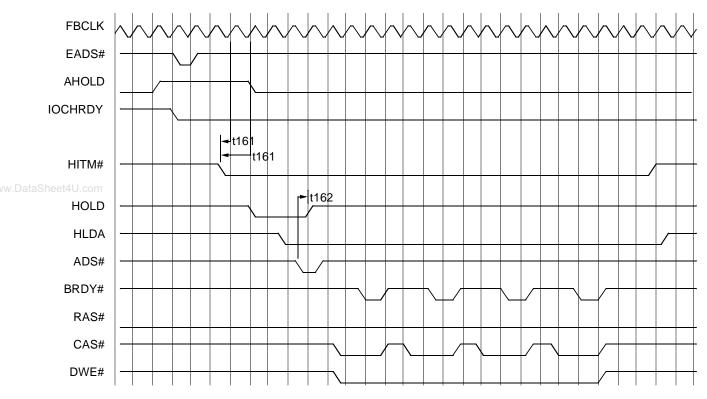

| Figure 6-15  | HITM# Signal Active, Burst Write Back Cycle, 1 Wait State DRAM Write Setup        | 192 |

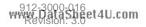

| Figure 6-16  | Refresh Cycle                                                                     |     |

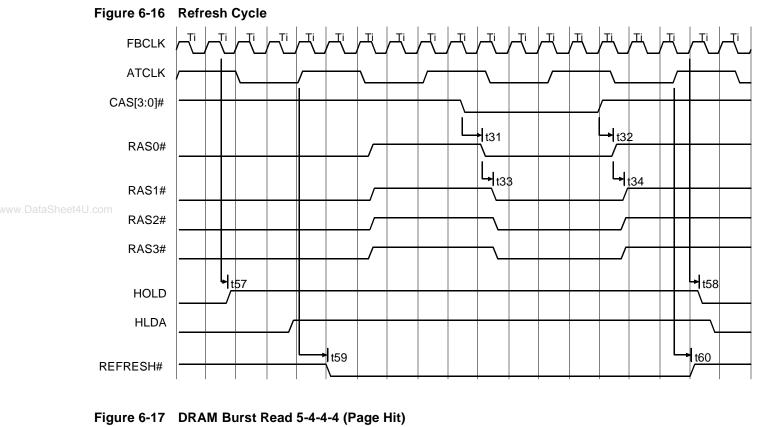

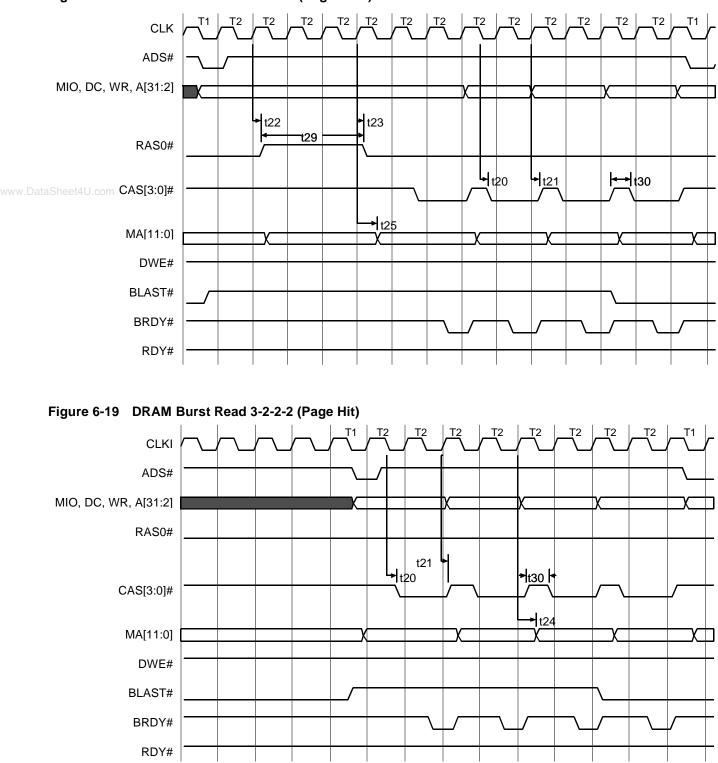

| Figure 6-17  | DRAM Burst Read 5-4-4-4 (Page Hit)                                                |     |

| Figure 6-18  | DRAM Burst Read X-2-2-2 (Page Miss)                                               |     |

| Figure 6-19  | DRAM Burst Read 3-2-2-2 (Page Hit)                                                |     |

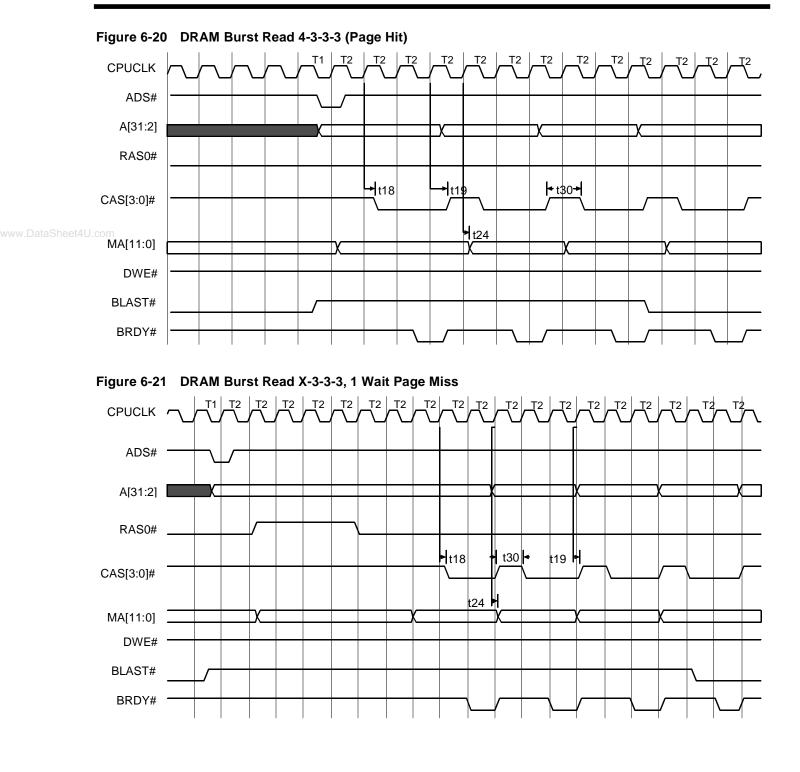

| Figure 6-20  | DRAM Burst Read 4-3-3-3 (Page Hit)                                                |     |

| Figure 6-21  | DRAM Burst Read X-3-3-3, 1 Wait Page Miss                                         |     |

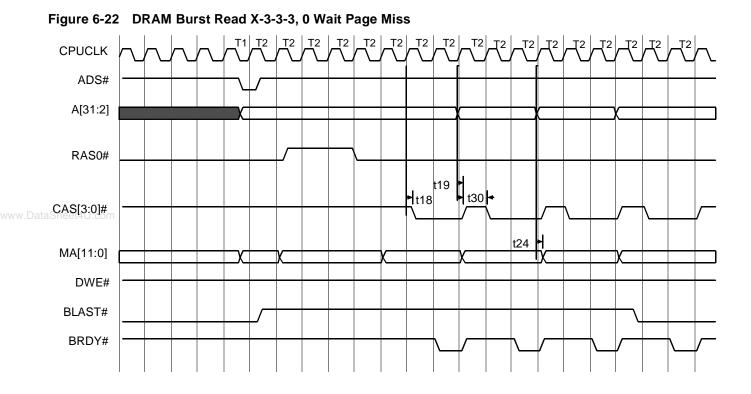

| Figure 6-22  | DRAM Burst Read X-3-3-3, 0 Wait Page Miss                                         |     |

| Figure 6-23  | DRAM Write Wait State (without L2 Cache Support)                                  | 196 |

# 82C465MV/MVA/MVB

### List of Figures (cont.)

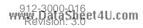

| Figure 6-24           | Single Local Bus Cycle                                                      | 197 |

|-----------------------|-----------------------------------------------------------------------------|-----|

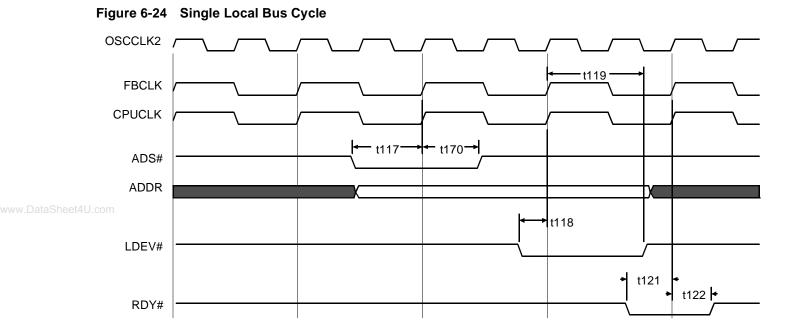

| Figure 6-25           | Reset Timing                                                                | 197 |

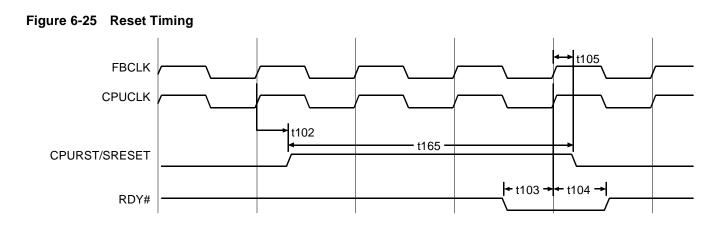

| Figure 6-26           | Low Word ISA Bus Memory Read to High Word Local Bus With SDENL#, SDENH#, ar |     |

| <b>F</b> ' 0.07       |                                                                             |     |

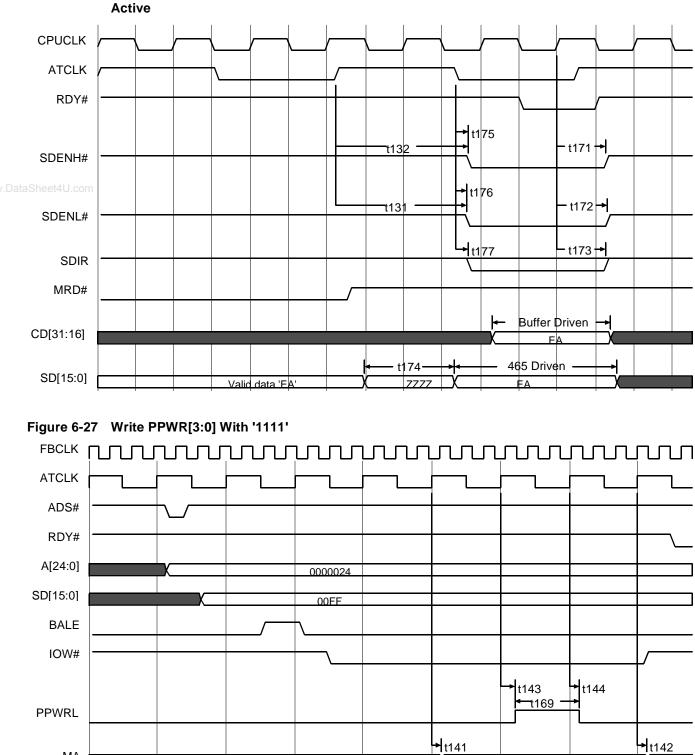

| Figure 6-27           | Write PPWR[3:0] With '1111'                                                 |     |

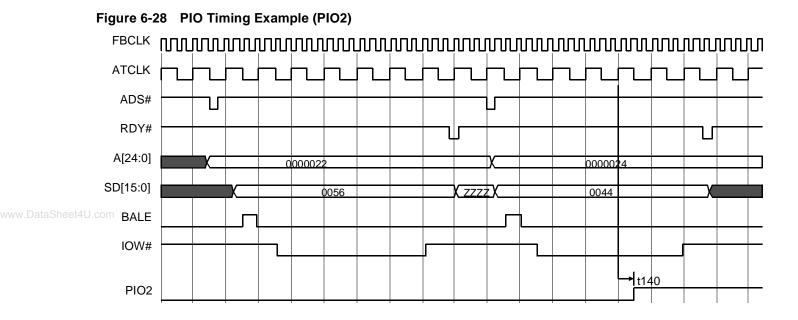

| Figure 6-28           | PIO Timing Example (PIO2)                                                   |     |

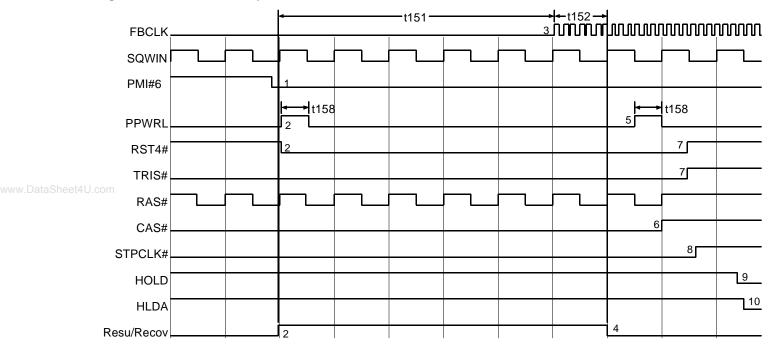

| Figure 6-29           | Suspend Sequence after Writing '1' to SYSCFG 50h[0]                         |     |

| Figure 6-30           | Resume Sequence                                                             |     |

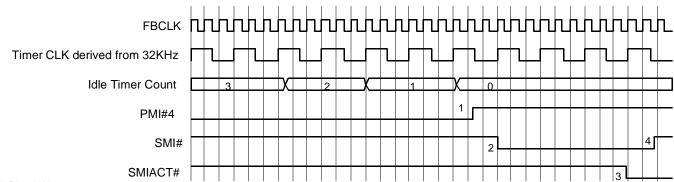

| ta <b>Figure_6-31</b> | Timer Time-out and SMI Generation Sequence                                  |     |

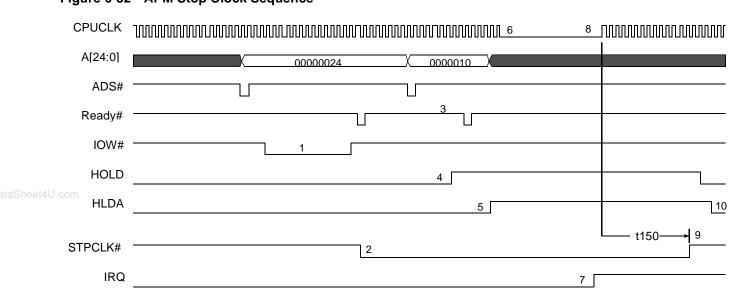

| Figure 6-32           | APM Stop Clock Sequence                                                     |     |

| Figure 6-33           | Doze Sequence                                                               |     |

| Figure 6-34           | FPM DRAM, 3-2-2-2 Page Hit Read                                             |     |

| Figure 6-35           | FPM DRAM, 5-2-2-2 Inactive Page Miss Read                                   |     |

| Figure 6-36           | FPM DRAM, 8-2-2-2 Active Page Miss Read                                     | 206 |

| Figure 6-37           | FPM DRAM, 4-3-3-3 Page Hit Read                                             |     |

| Figure 6-38           | FPM DRAM, 8-3-3-3 Inactive Page Miss Read                                   | 207 |

| Figure 6-39           | FPM DRAM, 11-3-3-3 Active Page Miss Read                                    | 208 |

| Figure 6-40           | FPM DRAM, 4-3-3-3 Page Hit Read (0 Wait State Page Miss)                    | 208 |

| Figure 6-41           | FPM DRAM, 6-3-3-3 Inactive Page Miss Read (0 Wait State Page Miss)          | 209 |

| Figure 6-42           | FPM DRAM, 9-3-3-3 Active Page Miss Read (0 Wait State Page Miss)            | 209 |

| Figure 6-43           | FPM DRAM, 5-4-4-4 Page Hit Read                                             | 210 |

| Figure 6-44           | FPM DRAM, 8-4-4-4 Inactive Page Miss Read                                   | 210 |

| Figure 6-45           | FPM DRAM, 12-4-4-4 Active Page Miss Read                                    | 211 |

| Figure 6-46           | FPM DRAM, 0 Wait State Write                                                | 211 |

| Figure 6-47           | FPM DRAM, 1 Wait State Write                                                | 212 |

| Figure 6-48           | FPM DRAM, 5-2-2-2 Inactive Page Miss with RAS 1/2 CLK Early                 | 212 |

| Figure 6-49           | EDO, 3-1-1-1 Page Hit Read                                                  | 213 |

| Figure 6-50           | EDO, 5-1-1-1 Inactive Page Miss with RAS 1/2 CLK Early                      | 214 |

| Figure 6-51           | EDO, 8-1-1-1 Active Page Miss with RAS 1/2 CLK Early                        | 214 |

| Figure 6-52           | EDO, 10-1-1-1 Active Page Miss with Normal RAS                              | 215 |

| Figure 6-53           | EDO, 3-2-2-2 Page Hit Read                                                  | 215 |

| Figure 6-54           | EDO, 6-2-2-2 Inactive Page Miss                                             | 216 |

| Figure 6-55           | EDO, 10-2-2-2 Active Page Miss Read                                         | 216 |

| Figure 6-56           | EDO, 4-2-2-2 Page Hit Read                                                  | 217 |

| Figure 6-57           | EDO, 7-2-2-2 Inactive Page Miss                                             | 217 |

| Figure 6-58           | EDO, 11-2-2-2 Active Page Miss                                              | 218 |

| Figure 8-1            | 208-Pin Plastic Quad Flat Pack (QFP)                                        | 221 |

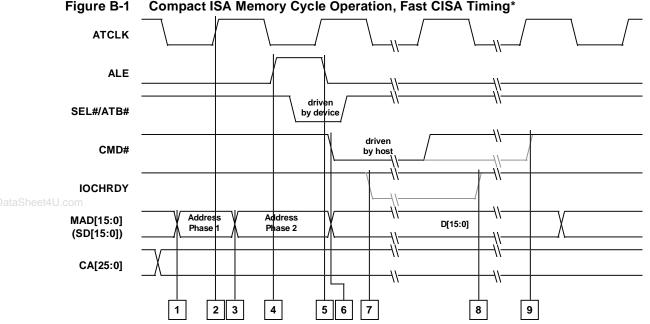

| Figure B-1            | Compact ISA Memory Cycle Operation, Fast CISA Timing*                       |     |

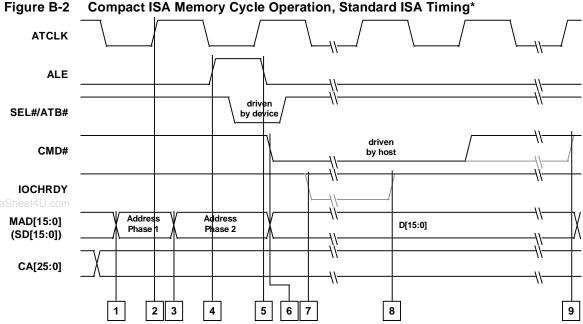

| Figure B-2            | Compact ISA Memory Cycle Operation, Standard ISA Timing*                    |     |

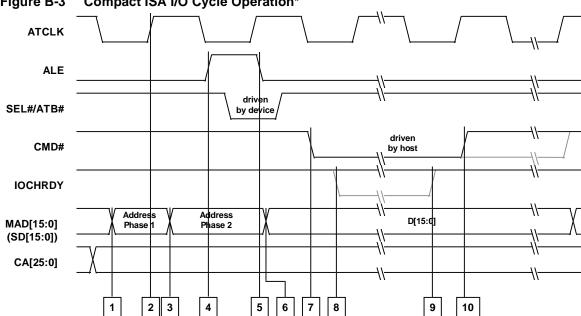

| Figure B-3            | Compact ISA I/O Cycle Operation*                                            |     |

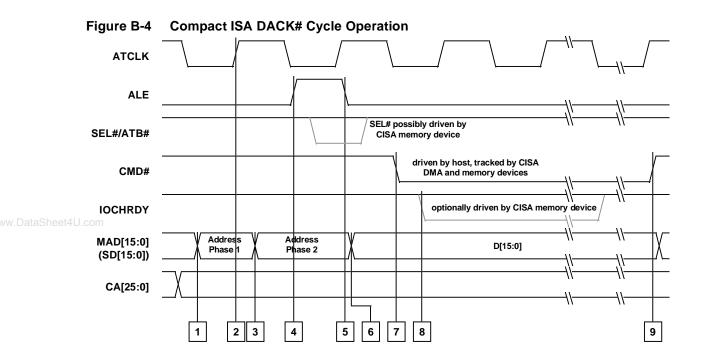

| Figure B-4            | Compact ISA DACK# Cycle Operation                                           |     |

|                       |                                                                             |     |

### List of Figures (cont.)

| Figure B-5 | Compact ISA Configuration Cycle Operation              | 233 |

|------------|--------------------------------------------------------|-----|

| Figure B-6 | Compact ISA Interrupt and DMA Request Drive-Back Cycle | 235 |

| Figure B-7 | Synchronizing to ATCLK at 1st ALE                      | 236 |

| Figure B-8 | Shared SPKROUT Signal Management                       | 237 |

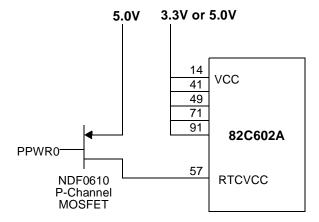

| Figure C-1 | RTCVCC Switching Circuit Example                       | 240 |

| Figure C-1 | RTC Address Map                                        | 241 |

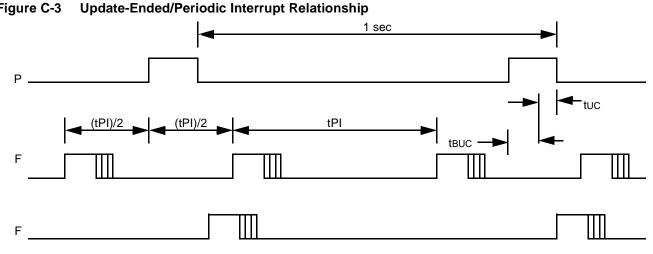

| Figure C-1 | Update-Ended/Periodic Interrupt Relationship           |     |

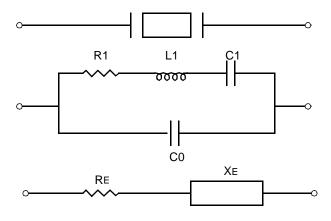

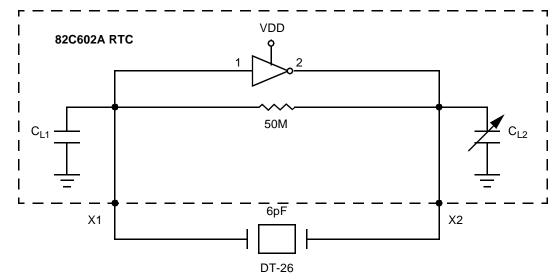

| Figure C-2 | Quartz Crystal Equivalent Circuit                      |     |

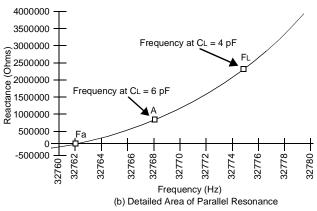

| Figure C-3 | Impedance Graph                                        | 246 |

| Figure C-4 | RTC Oscillator Circuit Block Diagram                   | 246 |

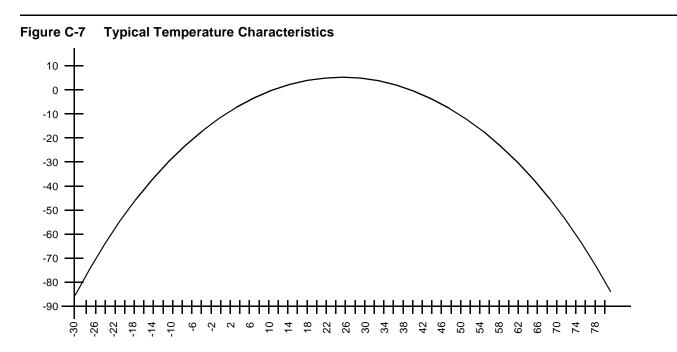

| Figure C-5 | Typical Temperature Characteristics                    | 247 |

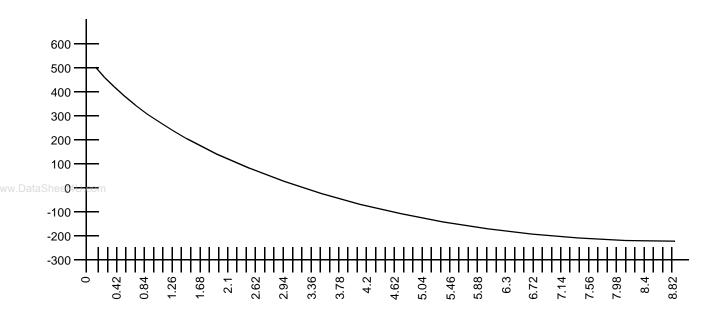

| Figure C-6 | Frequency Variation Versus Load Capacitance            | 248 |

| Figure C-1 | 486 NB Mode Pin Diagram (100-Pin PQFP)                 |     |

| Figure C-2 | 486 NB Mode Pin Diagram (100-Pin TQFP)                 | 252 |

| Figure C-1 | 82C602A Internal Circuitry in 486 Notebook Mode        | 257 |

| Figure C-2 | 82C602A 100-Pin Plastic Quad Flat Pack (PQFP)          |     |

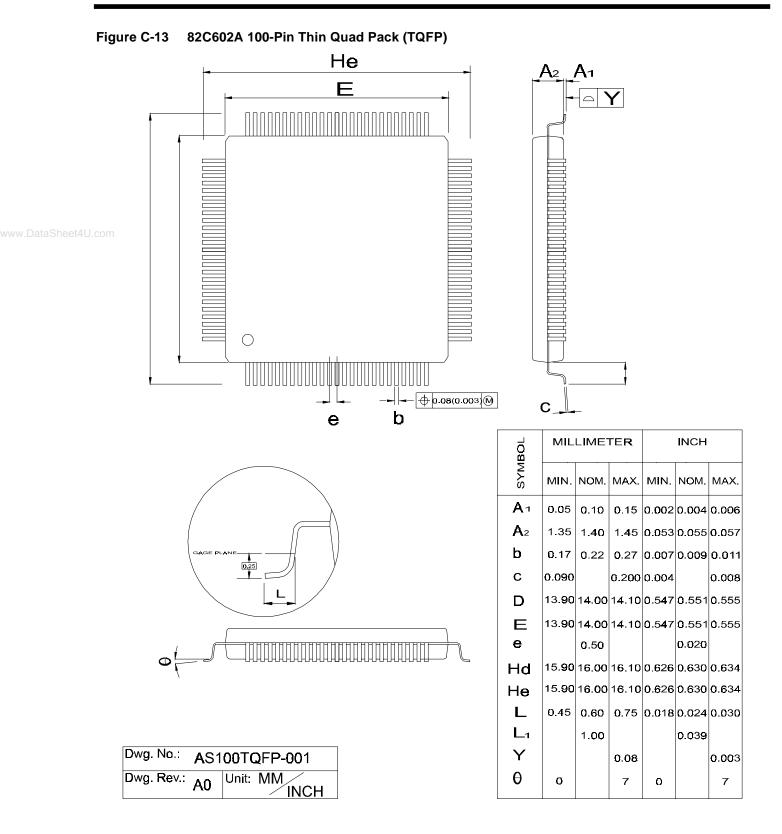

| Figure C-3 | 82C602A 100-Pin Thin Quad Pack (TQFP)                  | 259 |

|            |                                                        |     |

### List of Figures (cont.)

/ww.DataSheet4U.com

Page xvi

# List of Tables

| Table 3-1  | Signal Definitions Legend                                        | 5  |

|------------|------------------------------------------------------------------|----|

| Table 3-2  | Strap Option Summary                                             | 6  |

| Table 3-3  | Strap Settings for Interface Voltages                            | 7  |

| Table 3-4  | 1X/2X Strapping Readback Register Bit                            | 7  |

| Table 3-5  | Program-Selected DACKMUX Interface Recovery                      | 9  |

| Table 3-6  | DACKMUX Interface Option Enabling                                | 9  |

| Table 3-7  | PMIMUX Multiplex Option                                          | 10 |

| Table 3-8  | EPMMUX Multiplex Option                                          | 10 |

| Table 3-9  | EPMMUX Option Enabling                                           | 10 |

| Table 3-10 | Strap-Selected Reduced Memory Interface Option                   | 12 |

| Table 3-11 | 82C465MV Pin Characteristics                                     | 16 |

| Table 4-1  | Product Indicator Register Bit                                   | 33 |

| Table 4-2  | ADS# Sampling Control                                            | 34 |

| Table 4-3  | LDEV# Control                                                    | 34 |

| Table 4-4  | RDY# Synchronization                                             | 35 |

| Table 4-5  | Bus Master Enabling                                              | 36 |

| Table 4-6  | Special CPU Feature Programming Bits                             | 37 |

| Table 4-7  | Burst Mode Setting                                               |    |

| Table 4-8  | Resume Reset Control                                             | 39 |

| Table 4-9  | System Control Port A (PS/2 Compatibility Port)                  | 41 |

| Table 4-10 | Controlling Fast Reset                                           | 41 |

| Table 4-11 | Inhibition of SRESET in SMM                                      | 41 |

| Table 4-12 | ATCLKIN Enabling and SQWIN frequency Bits                        | 42 |

| Table 4-13 | ATCLK Rate Selection                                             |    |

| Table 4-14 | Recommended Divisor Settings for Various Input Clock Frequencies | 44 |

| Table 4-15 | AT Bus Clock Stretch Controls                                    | 44 |

| Table 4-16 | System Control Port A (PS/2 Compatibility Port)                  | 45 |

| Table 4-17 | Fast Signal Generation Control Bits                              | 46 |

| Table 4-18 | A20M# Read-Only Bit                                              |    |

| Table 4-19 | A20M# Setting within SMM                                         | 47 |

| Table 4-20 | Symmetrical DRAM Address Decoding                                |    |

| Table 4-21 | Asymmetrical DRAM Decoding, Asymmetry SYSCFG D3h[4:0] = 0        |    |

| Table 4-22 | Asymmetrical DRAM Decoding, Asymmetry SYSCFG D3h[4:0] = 1        | 49 |

| Table 4-23 | Heavy-duty Memory Bus Drive Capability Feature                   | 50 |

| Table 4-24 | DRAM Setup Registers                                             |    |

| Table 4-25 | DRAM Early RAS# Control                                          |    |

| Table 4-26 | EDO DRAM Selection                                               |    |

| Table 4-27 | Suggested EDO DRAM Cycle Speed Settings                          |    |

| Table 4-28 | ROM Select Registers                                             |    |

| Table 4-29 | Write Destination Registers                                      | 54 |

|            |                                                                  |    |

| Table 4-30 | Access Control Bit Meanings for SYSCFG 38h[4:1], 37h[7:4], 31h[3:0] | 55 |

|------------|---------------------------------------------------------------------|----|

| Table 4-31 | Shadow RAM Control Bits                                             | 55 |

| Table 4-32 | Write Protect Registers                                             | 56 |

| Table 4-33 | Global Cache Control Enable                                         | 57 |

| Table 4-34 | Size and Valid Start Address Bits of Non-Cacheable Memory Blocks    | 57 |