silicon systems

Analog/Digital Bipolar/CMOS Integrated Circuits

# **Table of Contents**

## Section 1 TELECOMMUNICATION PRODUCTS

## Section 2 MICROPERIPHERAL PRODUCTS

TELECOMMUNICATION PRODUCTS

# Section 3 CUSTOM/ SEMICUSTOM

CUSTOM/ SEMICUSTOM

### **Advanced and Preliminary Information**

In this data book the following conventions are used in designating a data sheet "Advanced" or "Preliminary."

- Advanced— indicates a product still in the design cycle, and any specifications are based on design goals only. Sample availability is indicated in the text.

- Preliminary— indicates a product not completely released to production. The specifications are based on preliminary evaluations and are not guaranteed. Small quantities are available, and SSI should be consulted for current information.

Section 4 STANDARD CELLS

# **Product Index**

|                                                                   | Page  |

|-------------------------------------------------------------------|-------|

| Customer Reply Card                                               |       |

| Table of Contents                                                 | i     |

| Product Index                                                     |       |

| Numerical Index                                                   | IV    |

| Section 1. TELECOMMUNICATIONS PRODUCTS                            |       |

| Tone Signalling Products                                          |       |

| SSI 201, DTMF Receiver (5V)                                       | 1-4   |

| SSI 202/203, DTMF Receiver (5V)                                   | 1-8   |

| SSI 204, DTMF Receiver (5V subscriber)                            | 1-12  |

| SSI 207, Integrated MF Receiver                                   | 1-16  |

| DTMF Receivers Application Guide                                  | 1-20  |

| SSI 20C89, DTMF Transceiver                                       | 1-26  |

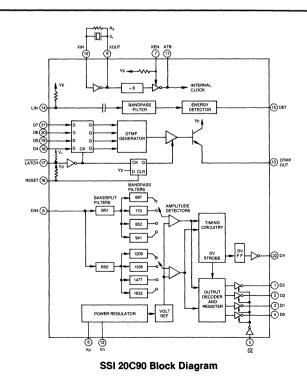

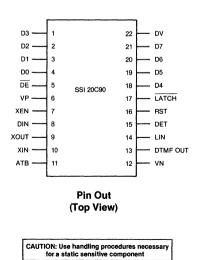

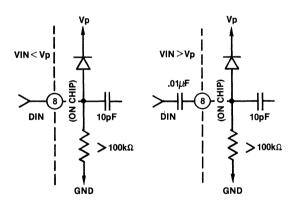

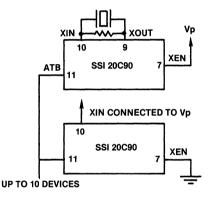

| SSI 20C90, DTMF Transceiver (Call Progress)                       | 1-32  |

| SSI 957, DTMF Receiver With Dial Tone                             | 1-38  |

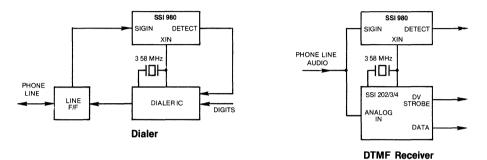

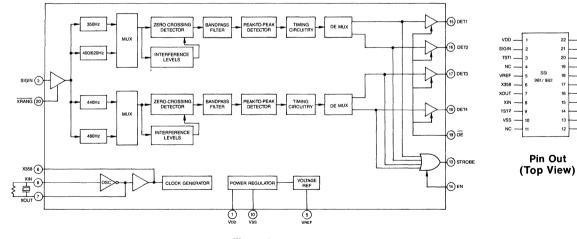

| SSI 980, Call Progress Tone Detector                              | 1-44  |

| SSI 981, Call Progress Tone Detector                              | 1-48  |

| SSI 982, Call Progress Tone Detector                              | 1-48  |

| Modem Products                                                    |       |

| SSI K212, Single Chip Bell 212 Modem                              | 1-52  |

| SSI K214, Analog Processor For V.22 bis Modems                    |       |

| SSI K222, Single Chip V.22 Modem                                  |       |

| SSI 223, 1200 Baud FSK Modem                                      |       |

| SSI K224. Single Chip V.22 bis Modem                              |       |

| SSI 291/213, 1200 BPS Full Duplex Modern Device                   |       |

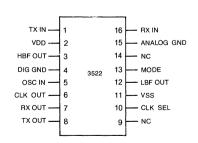

| SSI 3522, Bell 212A/V.22 Modem Filter                             |       |

|                                                                   |       |

| Speech Synthesis Products                                         | 1.00  |

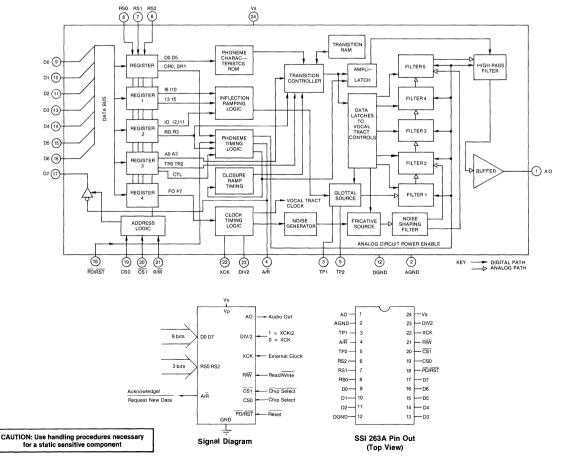

| SSI 263A, Phoneme Speech Synthesizer                              |       |

| SSI 263A, Speech Synthesizer User Guide                           | 1-94  |

| Switching Products                                                |       |

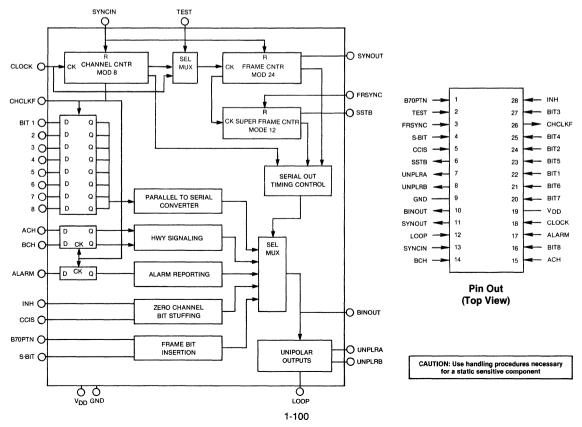

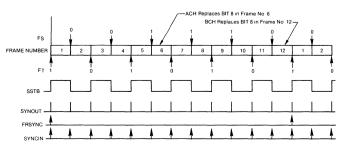

| SSI 80C50, CMOS Digital IC T-1 Transmitter                        | 1-100 |

| SSI 80C60, CMOS Digital IC T-1 Receiver                           | 1-106 |

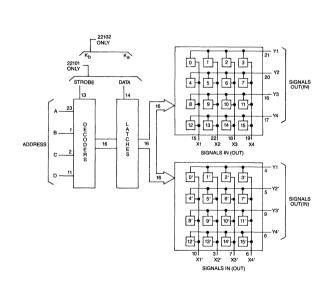

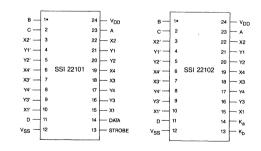

| SSI 22100, CMOS 4x4 Crosspoint Switch With Control Memory         | 1-112 |

| SSI 22101/102, CMOS 4x4x2 Crosspoint Switches With Control Memory | 1-118 |

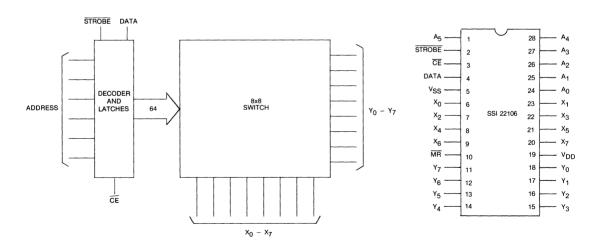

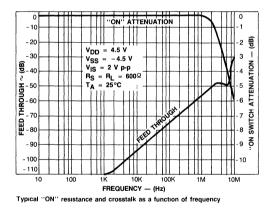

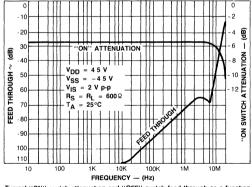

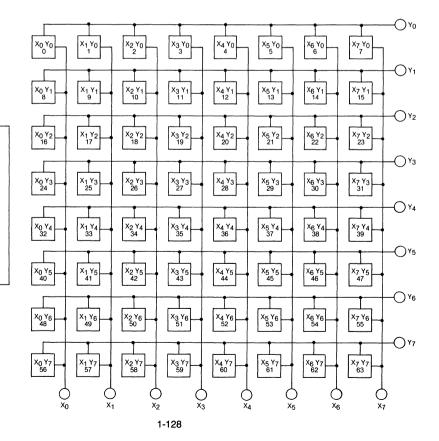

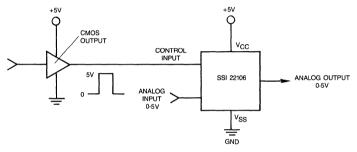

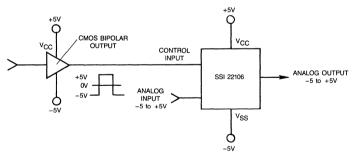

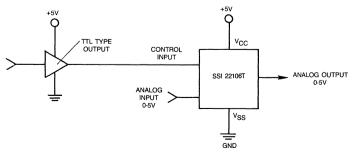

| SSI 22106, 8x8x1 Crosspoint Switch With Control Memory            | 1-124 |

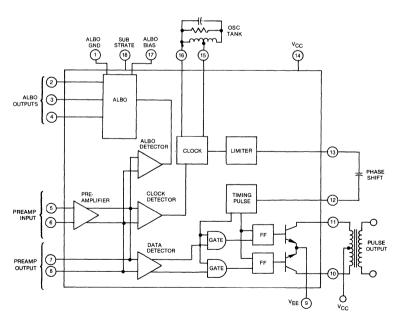

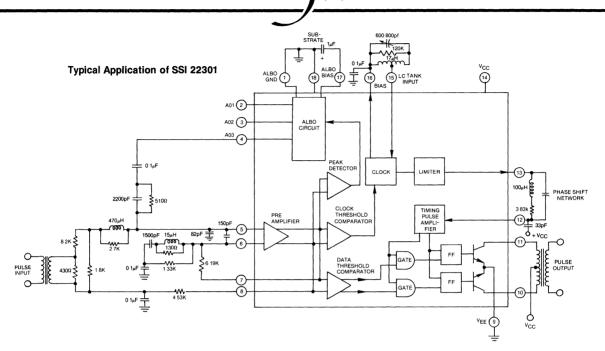

| SSI 22301, PCM Line Repeater                                      | 1-132 |

| Section 2. MICROPERIPHERAL PRODUCTS                               |       |

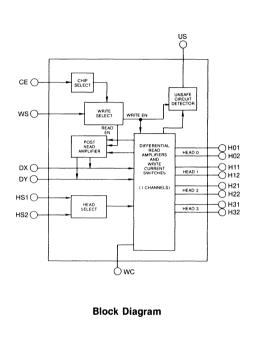

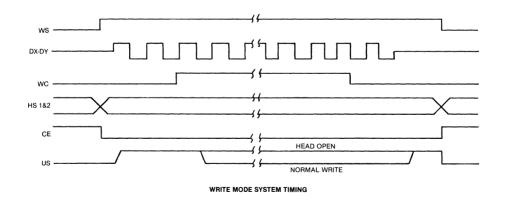

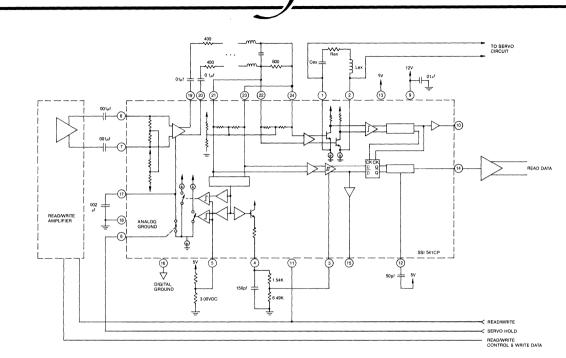

| HDD Read/Write Amplifiers                                         |       |

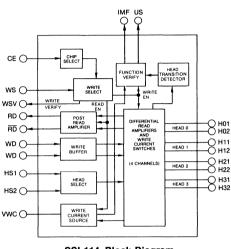

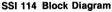

| SSI 104, 104L, 108, 122, 4 Channel R/W Circuit.                   | 2.2   |

| SSI 104, 104E, 100, 122, 4 Channel Thim R/W Circuit               |       |

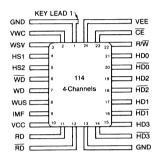

| SSI 115, Winchester R/W Circuit                                   |       |

| SSI 110, Winchester R/W Circuit                                   |       |

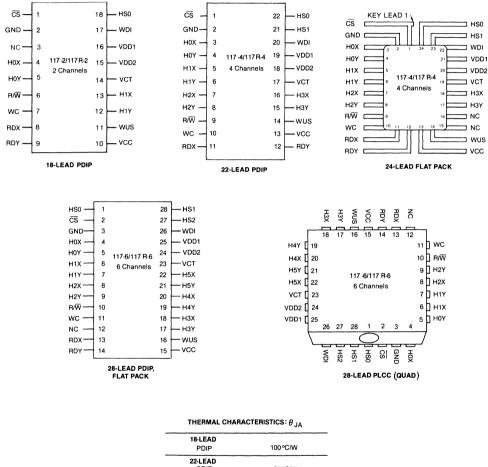

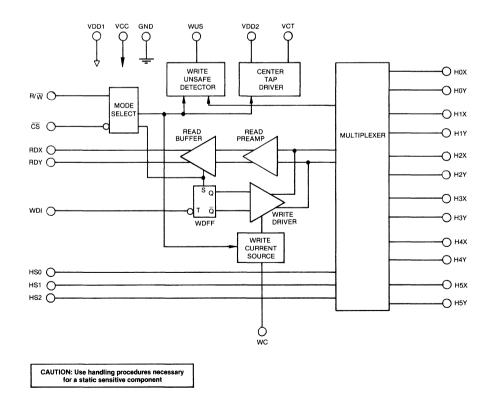

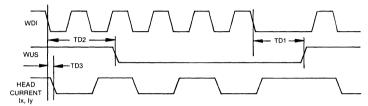

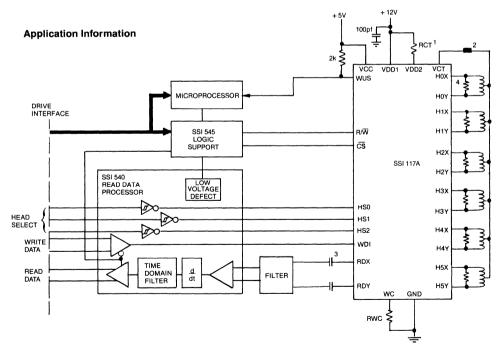

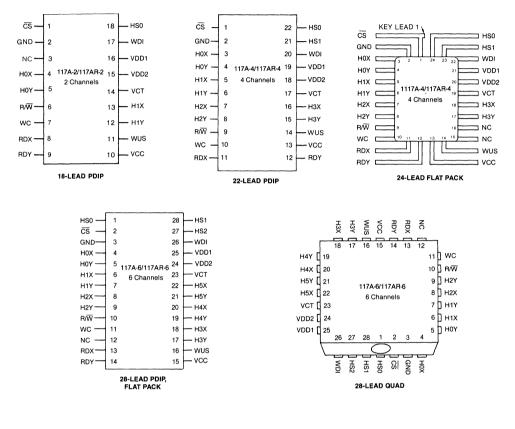

| SSI 117/117R, 2, 4, 6 Channel R/W Circuit                         |       |

| SSI 11/A/ 11/AR, 2, 4, 6 Channel R/W Circuit                      |       |

| ·                                                                 |       |

| SSI 501/501R, 6, 8 Channel R/W Circuit                            |       |

|                                                                   |       |

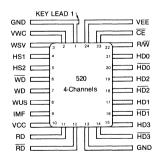

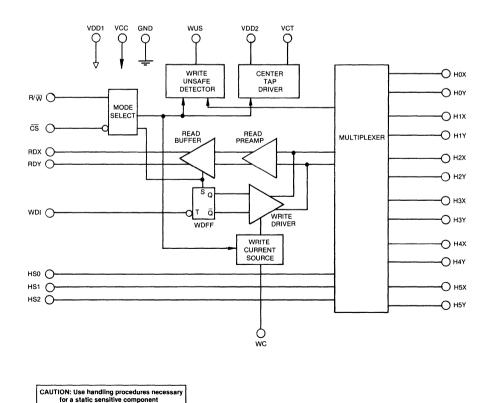

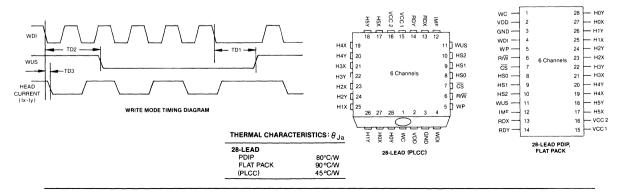

| SSI 520, 4 Channel Thin Film R/W Circuit                          |       |

| SSI 521R, 6 Channel Thin Film R/W Circuit                         | 2-30  |

| HDD Head Positioning                                              |       |

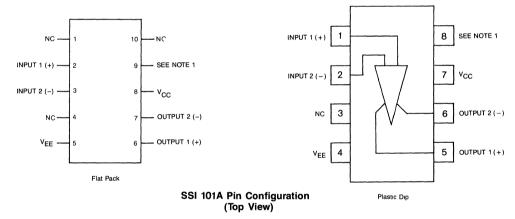

| SSI 101A Differential Amplifier                                   |       |

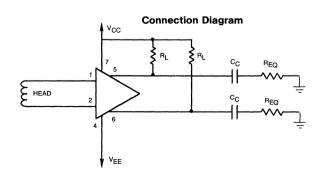

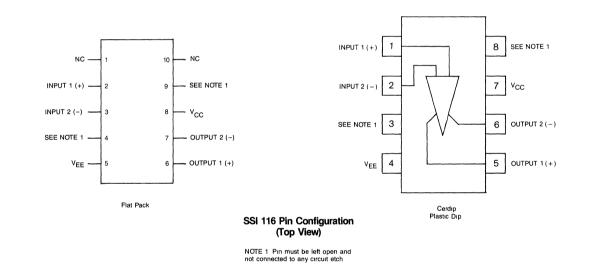

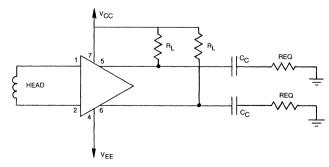

| SSI 116 Differential Amplifier                                    | 2-56  |

# Product Index (Contd.)

|                                                             | Page     |

|-------------------------------------------------------------|----------|

| HDD Read Data Path                                          |          |

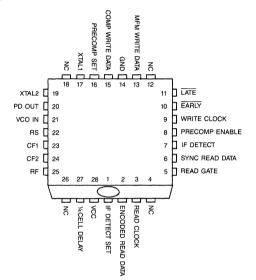

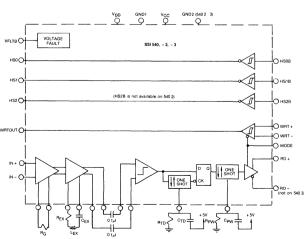

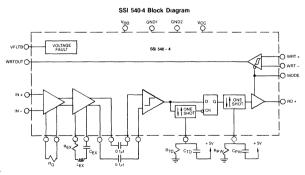

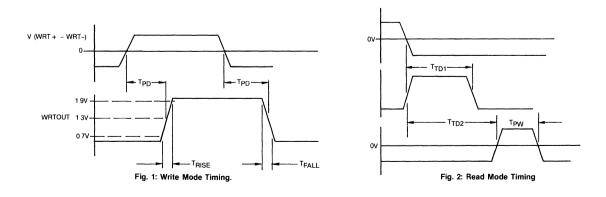

| SSI 531, Data Separator and Write Precompensation Circuit   | 2-58     |

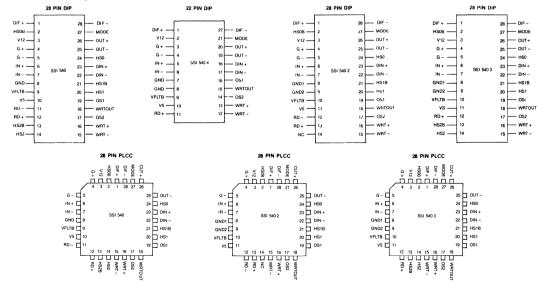

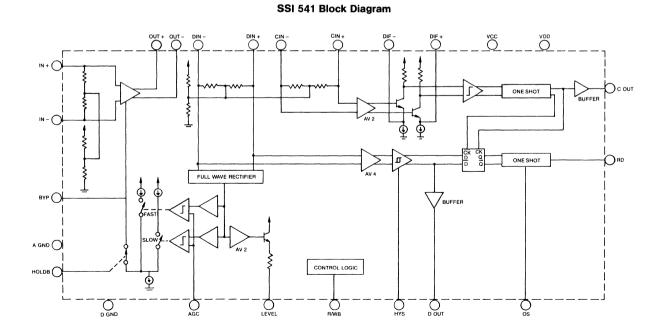

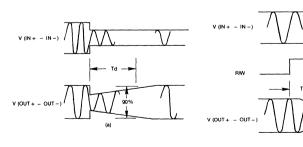

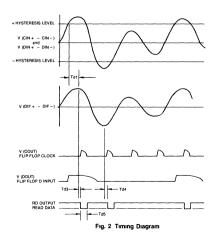

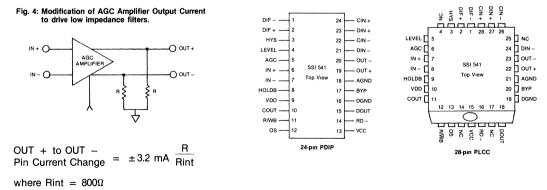

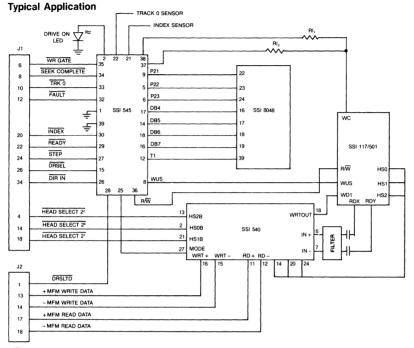

| SSI 540, Read Data Processor                                |          |

| SSI 541, Read Data Processor                                | 2-74     |

| HDD Motor Control/Support Logic                             |          |

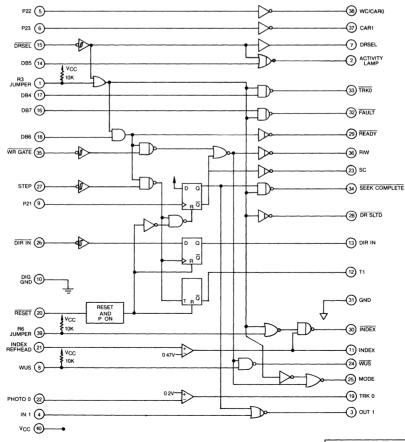

| SSI 545, Winchester Disk Drive Support Logic                | 2-80     |

| SSI 543, Winchester Disk Drive Support Logic                |          |

| SSI 590, 5% Which Speed Control                             |          |

|                                                             | 2-00     |

| Floppy Disk Drive Circuits                                  |          |

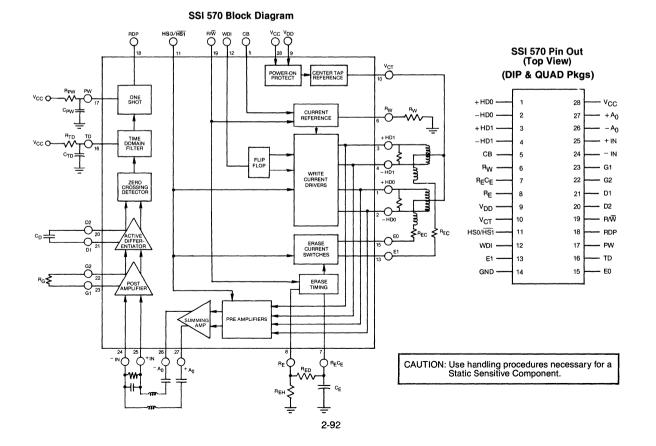

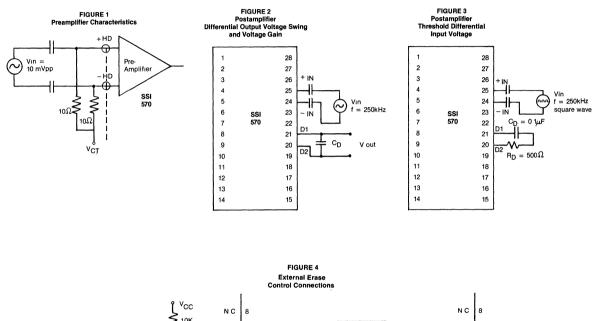

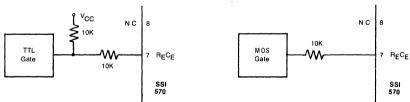

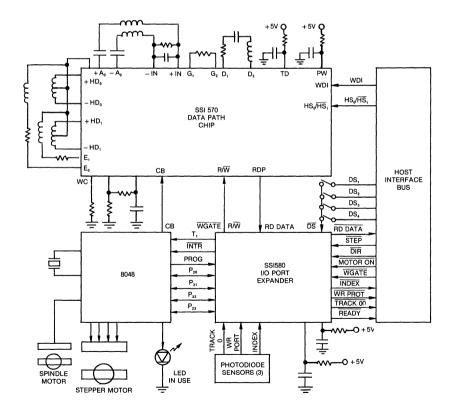

| SSI 570, 2 Channel Floppy Disk R/W Circuit                  |          |

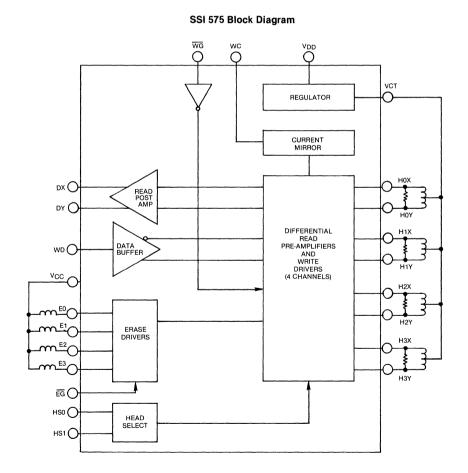

| SSI 575, 2, 4 Channel Floppy Disk R/W Circuit               |          |

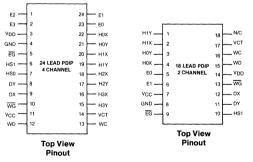

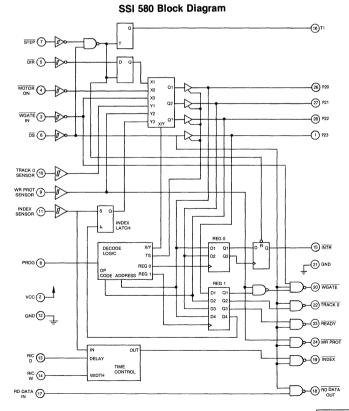

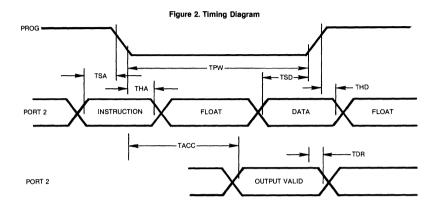

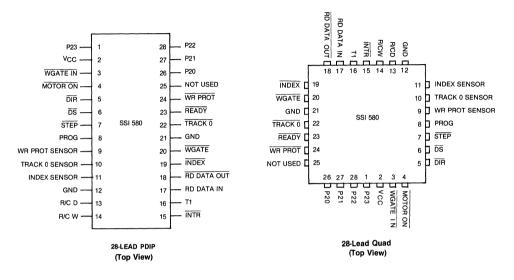

| SSI 580, Port Expander Floppy Disk Drive                    | 2-102    |

| Tape Drive Circuits                                         |          |

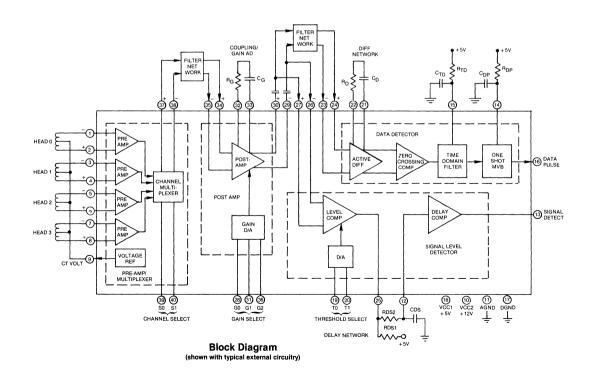

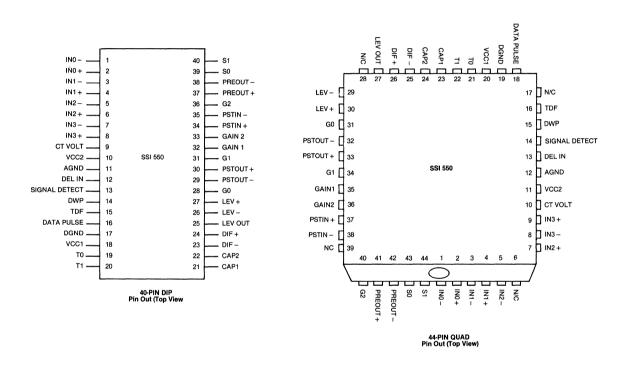

| SSI 550, 4-Channel Mag Tape Read Circuit                    | 2-108    |

|                                                             |          |

| Memory Products                                             | <b>.</b> |

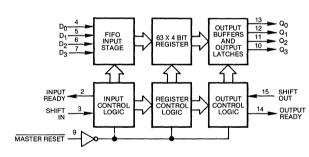

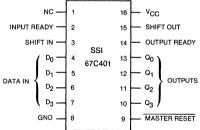

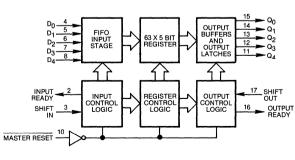

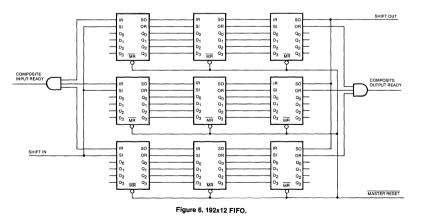

| SSI 67C401 FIFO 64x4 Memory                                 |          |

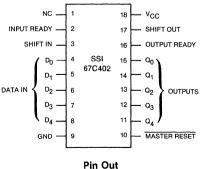

| SSI 67C402 FIFO 64x5 Memory                                 | 2-114    |

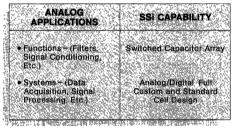

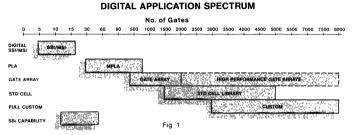

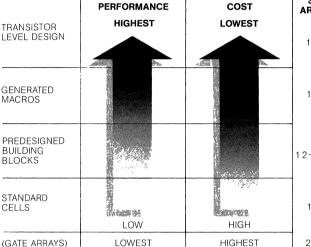

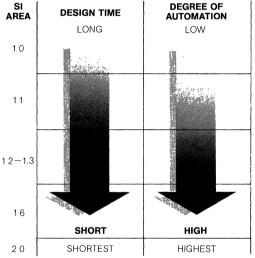

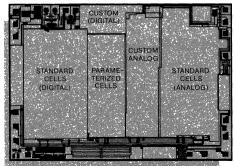

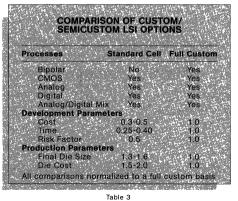

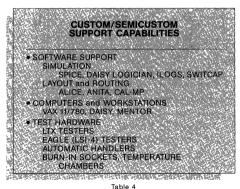

| Section 3. CUSTOM/SEMICUSTOM INTEGRATED CIRCUITS            |          |

| CMOS and Bipolar Process Charts                             | 3-2      |

| Integrated Design Methodology                               |          |

| Custom/Semicustom Options                                   |          |

| Custom Design Flow Chart                                    | 3-4      |

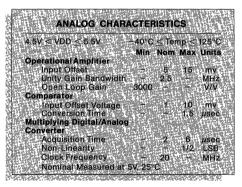

| CMOS/Bipolar Capabilities                                   | 3-5      |

| Section 4. ANALOG/DIGITAL STANDARD CELLS                    |          |

| Standard Cell Library                                       | 4.4      |

| Advanced Standard Cell Information—Basic Standard Cell List |          |

|                                                             | 4-2      |

| Section 5. GENERAL INFORMATION                              |          |

| SSI Product Selector Guide (Telecom)                        |          |

| SSI Product Selector Guide (Microperipheral)                | 5-2      |

| Packaging                                                   | 5-4      |

| Package Matrix Chart                                        | 5-5      |

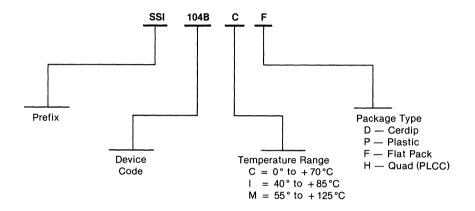

| Ordering Information                                        | 5-6      |

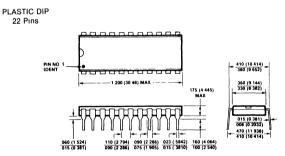

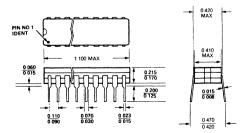

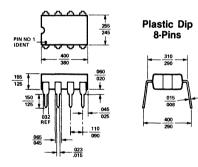

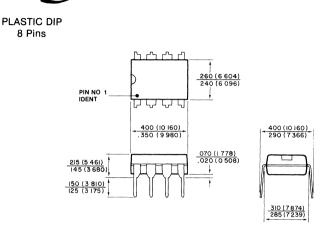

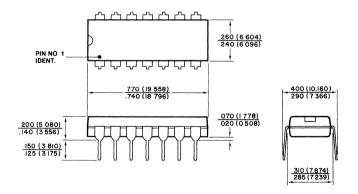

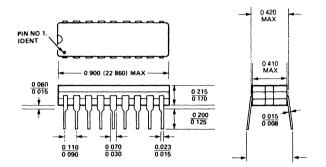

| Plastic Dip 8 Pins and 14 Pins                              | 5-7      |

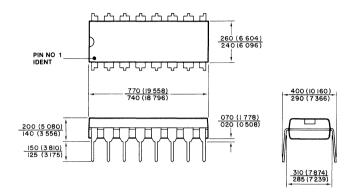

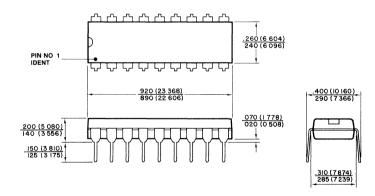

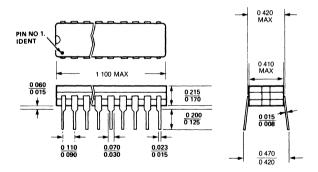

| Plastic Dip 16 Pins and 18 Pins                             | 5-8      |

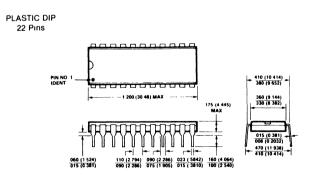

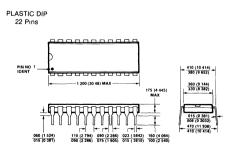

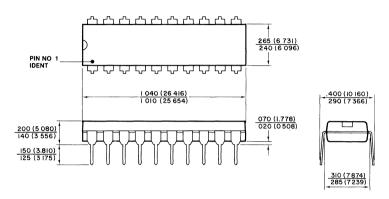

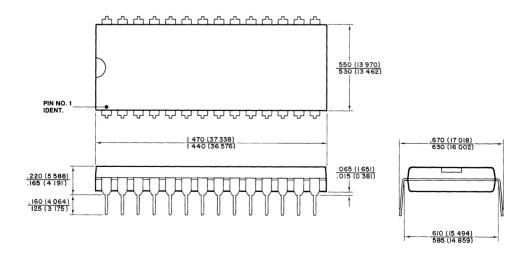

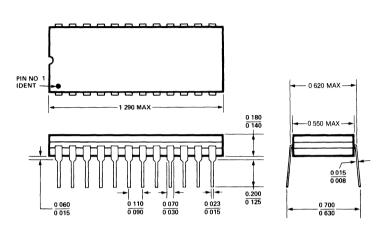

| Plastic Dip 20 Pins and 22 Pins                             | 5-9      |

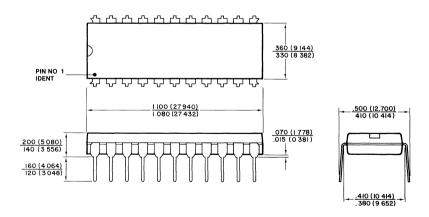

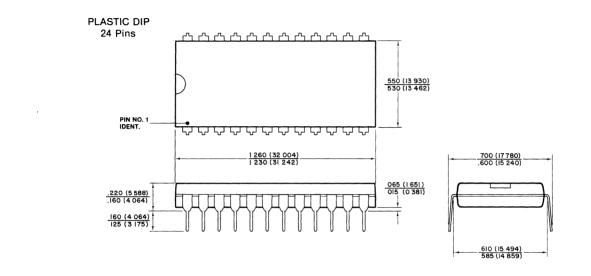

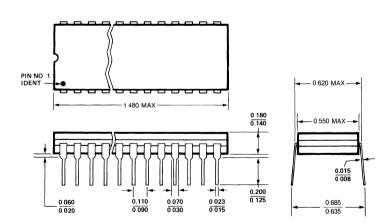

| Plastic Dip 24 Pins and 28 Pins                             | 5-10     |

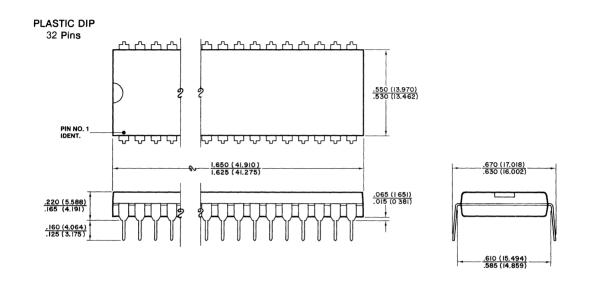

| Plastic Dip 32 Pins and 40 Pins                             | 5-11     |

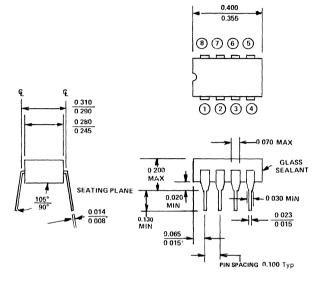

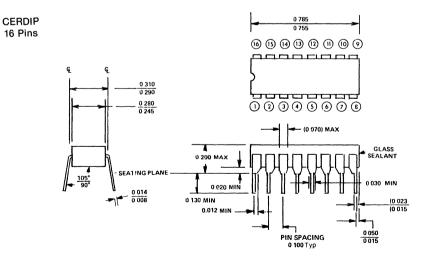

| Cerdip 8 Pins and 16 Pins                                   |          |

| Cerdip 18 Pins and 22 Pins                                  |          |

| Cerdip 24 Pins and 28 Pins                                  |          |

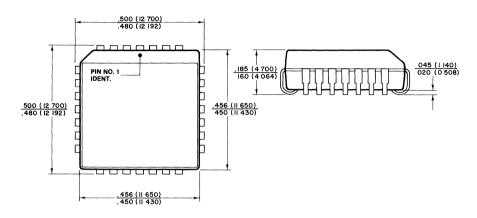

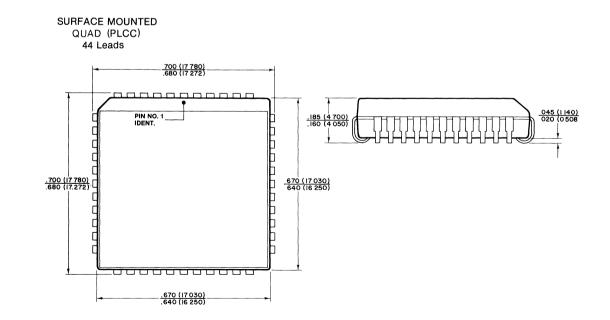

| Surface Mounted Device (PLCC) 28 and 44 Leads               |          |

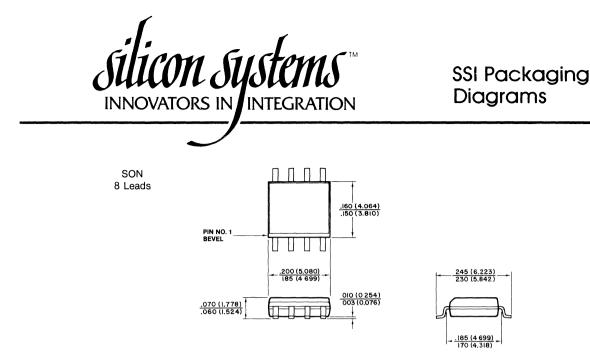

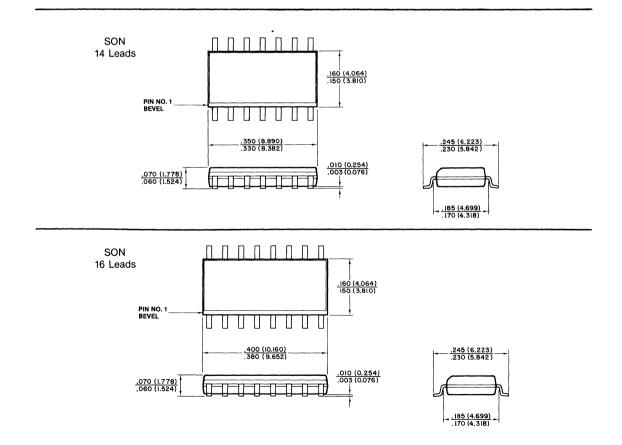

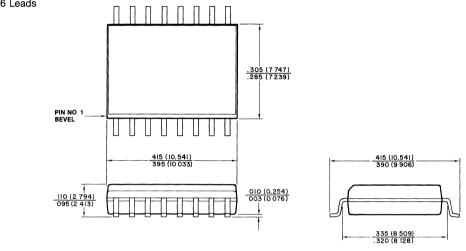

| SON 8,14 and 16 Leads                                       |          |

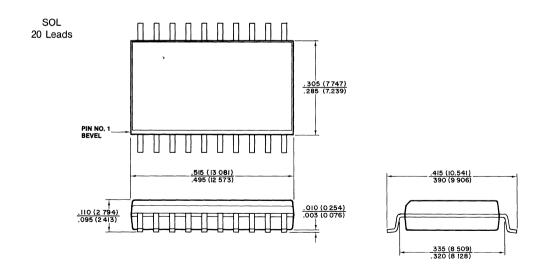

| SOL 16 and 20 Leads                                         |          |

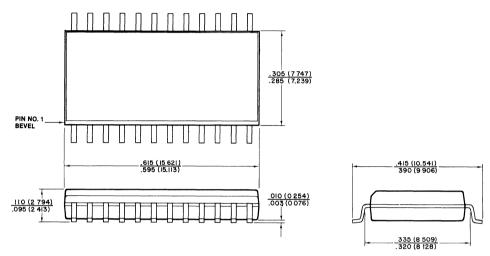

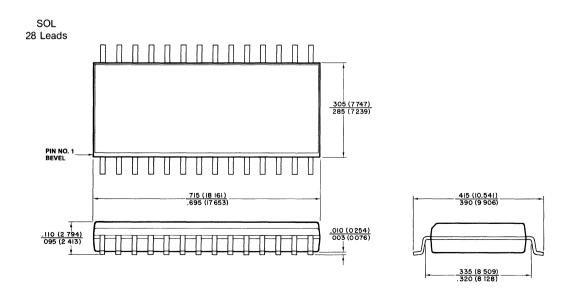

| SOL 24 and 28 Leads                                         | 5-18     |

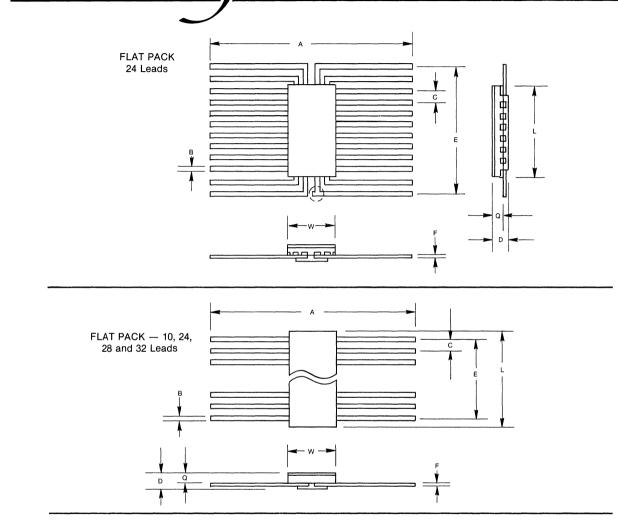

| Flat Package Dimensional Diagrams and Dimensional Chart     |          |

| 10, 24, 28, and 32 Pins                                     |          |

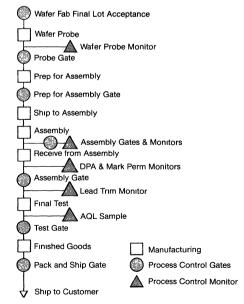

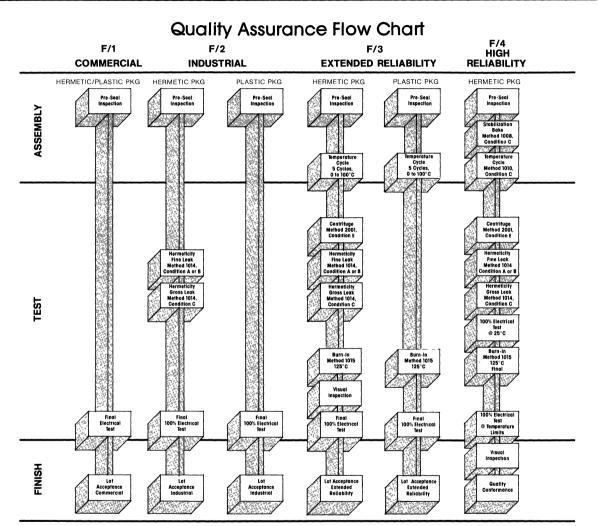

| Quality Assurance and Reliability                           |          |

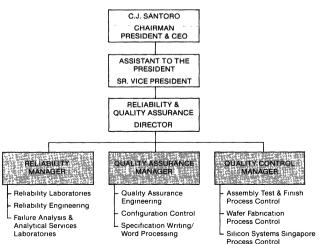

| Quality Assurance Flow Chart                                | 5-26     |

# **Numerical Index**

|                | Page  |

|----------------|-------|

| SSI 20C89      | 1-26  |

| SSI 20C90      | 1-32  |

| SSI 67C401     | 2-114 |

| SSI 67C402     | 2-114 |

| SSI 80C50      | 1-100 |

| SSI 80C60      | 1-106 |

| SSI 101A       | 2-54  |

| SSI 104        | 2-2   |

| SSI 104L       | 2-2   |

| SSI 108        | 2-2   |

| SSI 114        | 2-6   |

| SSI 115        | 2-10  |

| SSI 116        |       |

| SSI 117/117R   |       |

| SSI 117A/117AR |       |

| SSI 122        |       |

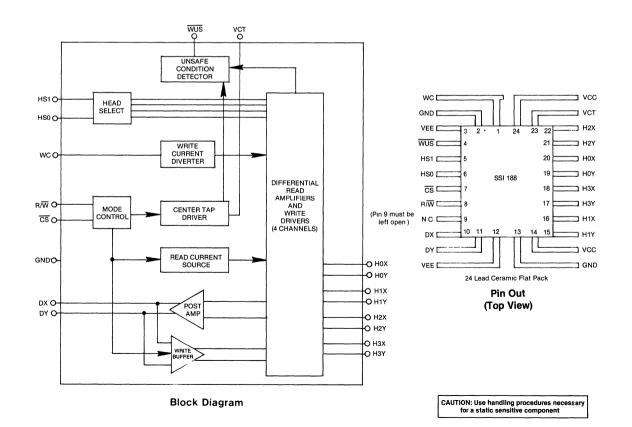

| SSI 188        |       |

| SSI 201        | 1-4   |

| SSI 202        |       |

| SSI 203        | 1-8   |

| SSI 204        | 1-12  |

| SSI 207        |       |

| SSI K212       |       |

| SSI K214       | 1-60  |

| SSI K222       |       |

| SSI 223        |       |

| SSI K224       | 1-72  |

|              | Pa    | age |

|--------------|-------|-----|

| SSI 263A     | 1-8   | 6   |

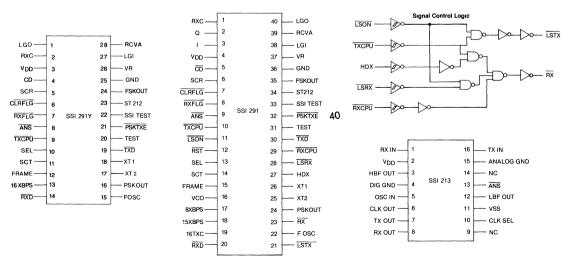

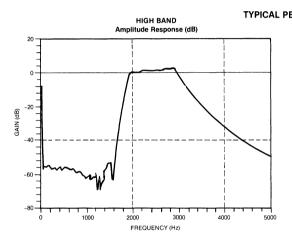

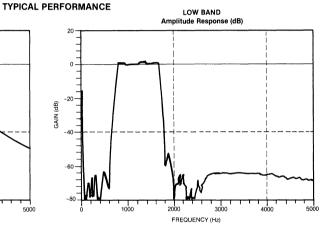

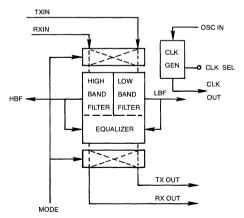

| SSI 291/213  | 1-7   | 6   |

| SSI 501/501R | 2-3   | 4   |

| SSI 510/510R | . 2-4 | 0   |

| SSI 520      | . 2-4 | 6   |

| SSI 521R     | 2-5   | 0   |

| SSI 531      | 2-5   | 8   |

| SSI 540      | . 2-6 | 6   |

| SSI 541      | 2-7   | 4   |

| SSI 545      | . 2-8 | 0   |

| SSI 550      | 2-1   | 80  |

| SSI 570      | . 2-9 | 2   |

| SSI 575      | . 2-9 | 8   |

| SSI 580      |       |     |

| SSI 590      |       |     |

| SSI 591      |       |     |

| SSI 957      |       |     |

| SSI 980      |       |     |

| SSI 981      |       |     |

| SSI 982      |       |     |

| SSI 3522     |       |     |

| SSI 22100    |       |     |

| SSI 22101    |       |     |

| SSI 22102    |       |     |

| SSI 22106    |       |     |

| SSI 22301    | 1-1   | 32  |

# Section 1 TELECOMMUNICATION PRODUCTS

### **TELECOMMUNICATIONS CIRCUITS**

|        |                  |          | Power    |         | Page |

|--------|------------------|----------|----------|---------|------|

| Device | Circuit Function | Features | Supplies | Package | No.  |

### **Tone Signaling Products**

| SSI 201   | Integrated DTMF Receiver       | Binary or 2-of-8 output                                         | 12V | 22 DIP | 1-4  |

|-----------|--------------------------------|-----------------------------------------------------------------|-----|--------|------|

| SSI 202   | Integrated DTMF Receiver       | Low-power, binary output                                        | 5V  | 18 DIP | 1-8  |

| SSI 203   | Integrated DTMF Receiver       | Binary output, Early Detect                                     | 5V  | 18 DIP | 1-8  |

| SSI 204   | Integrated DTMF Receiver       | Low-power, binary output                                        | 5V  | 14 DIP | 1-12 |

| SSI 207   | Integrated MF Receiver         | Detects central office tone signals                             |     | 20 DIP | 1-16 |

| SSI 20C89 | Integrated DTMF Transceiver    | Generator and Receiver, µP interface                            |     | 22 DIP | 1-26 |

| SSI 20C90 | Integrated DTMF Transceiver    | Generator and Receiver, $\mu P$ interface, Call Progress Detect |     | 22 DIP | 1-32 |

| SSI 957   | Integrated DTMF Receiver       | Early Detect, Dial Tone reject                                  | 5V  | 22 DIP | 1-38 |

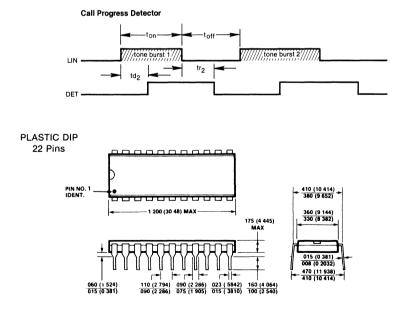

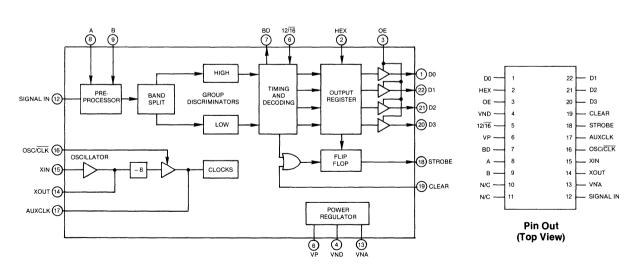

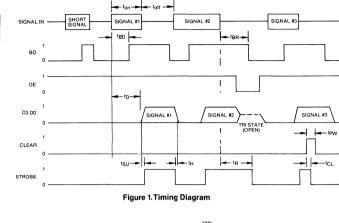

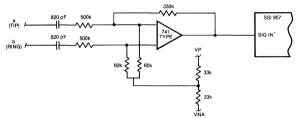

| SSI 980   | Call Progress Detector         | Detects supervision tones, Teltone second-source                | 5V  | 8 DIP  | 1-44 |

| SSI 981   | Precise Call Progress Detector | Detects supervision tones, Teltone second-source                |     | 22 DIP | 1-48 |

| SSI 982   | Precise Call Progress Detector | Detects supervision tones, Teltone second-source                | 5V  | 22 DIP | 1-48 |

### **Modem Products**

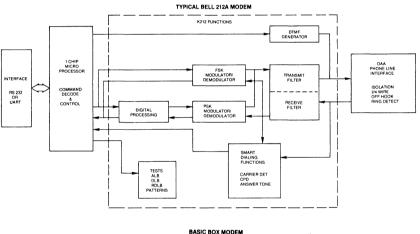

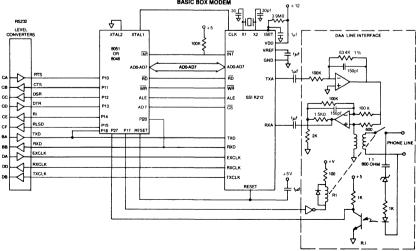

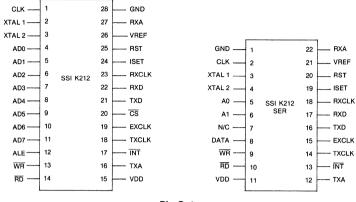

| SSI K212    | 1200/300 bps Modem                                     | DPSK/FSK, single chip, autodial, Bell 212A                       | 10V | 28, 22 DIP | 1-52 |

|-------------|--------------------------------------------------------|------------------------------------------------------------------|-----|------------|------|

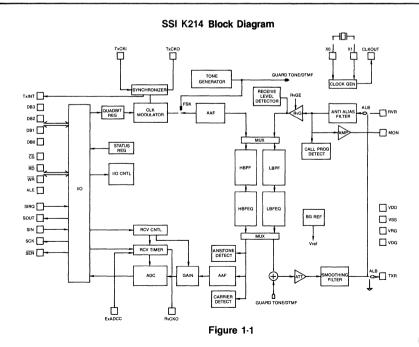

| SSI K214    | 2400 bps Analog Front End                              | 00 bps Analog Front End Analog Processor for DSP V.22 bis Modems |     | 28 DIP     | 1-60 |

| SSI K222    | 1200 bps Modem                                         | bps Modem V.22 version of K212, Pin Compatible                   |     | 28, 22 DIP | 1-62 |

| SSI 223     | 1200 bps Modem                                         | FSK, HDX/FDX                                                     |     | 16 DIP     | 1-68 |

| SSI K224    | 2400 bps Modem V.22 is version of K212, Pin Compatible |                                                                  | 10V | 28, 22 DIP | 1-72 |

| SSI 291/213 | 1200 bps Modem                                         | DPSK, two chips, low-power                                       |     | 40/16 DIP  | 1-76 |

| SSI 3522    | 1200 bps Modem Filter                                  | Bell 212 compatible, AMI second-source                           | 10V | 16 DIP     | 1-82 |

### **Speech Synthesis Products**

| SSI 263A Speech Synthesizer | Phoneme-based, low data rate, VOTRAX second-source | 5V | 24 DIP | 1-86 |

|-----------------------------|----------------------------------------------------|----|--------|------|

|-----------------------------|----------------------------------------------------|----|--------|------|

### Switching Products

| SSI 80C50   | T1 Transmitter     | Bell D2, D3, D4, serial format and mux, low power  | 5V  | 28 DIP,Q | 1-100 |

|-------------|--------------------|----------------------------------------------------|-----|----------|-------|

| SSI 80C60   | T1 Receiver        | Bell D2, D3, serial synchron. and demux, low power | 5V  | 28 DIP,Q | 1-106 |

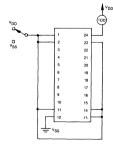

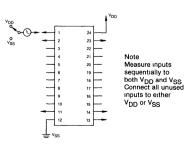

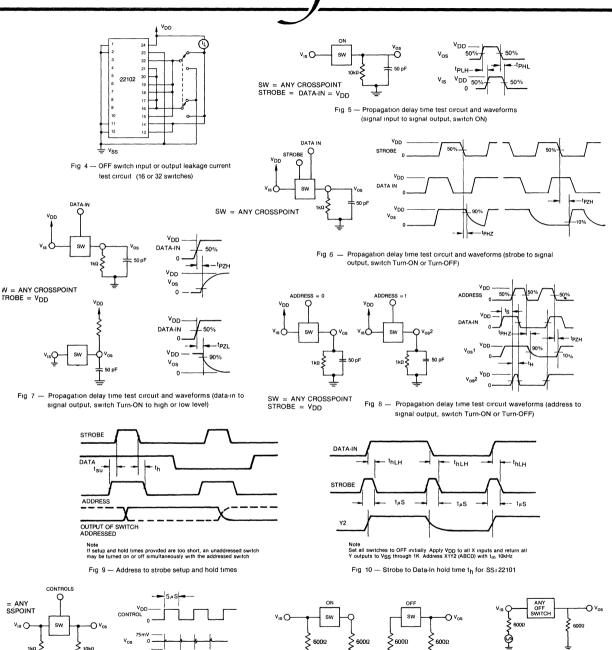

| SSI 22100   | Cross-point Switch | 4x4x1, control memory, RCA second-source           | 12V | 16 DIP   | 1-112 |

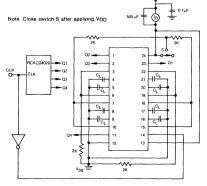

| SSI 22101/2 | Cross-point Switch | 4x4x2, control memory, RCA second-source           | 12V | 24 DIP   | 1-118 |

| SSI 22106   | Cross-point Switch | 8x8x1, control memory, RCA second-source           | 5V  | 28 DIP   | 1-124 |

| SSI 22301   | PCM Line Repeater  | T1 carrier signal recondition                      | 5V  | 18 DIP   | 1-132 |

Silicon Systems offers a broad line of standard telecommunications circuits aimed at providing cost-effective solutions for common customer application problems. At the heart of SSi's efforts in the communications market is its pioneering work with CMOS switched capacitor filters. Our early success with the DTMF receiver has enabled us to develop a family of chips utilizing the switched capacitor filter technology. As a trendsetter in the field, Silicon Systems is leading the way towards a whole new era of VLSI circuits for telecommunications. Our broad selection of DTMF receivers demonstrates not only technological leadership in our own semiconductor field but also our capability to anticipate the growing needs of the fastpaced telecommunications marketplace.

### Here are a few completed circuits that demonstrate our broad telecommunications IC capability:

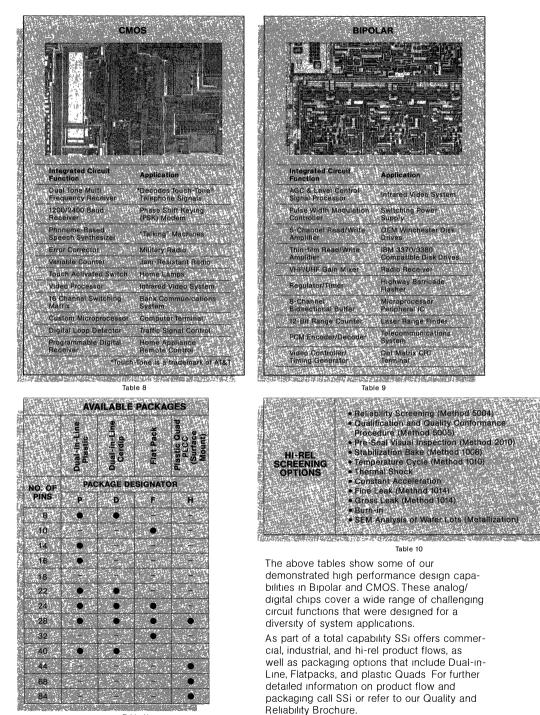

### BIPOLAR

| Integrated Circuit Function       | Application                    |

|-----------------------------------|--------------------------------|

| Audio System Receiver             | Telephone Answering<br>Machine |

| VHF/UHF Gain Mixer                | Radio Receiver                 |

| Pulse Width Modulator             | Switching Power Supply         |

| Controller                        | Home Appliance                 |

| Digital Receiver                  | Remote Control                 |

| PCM Encoder/Decoder               | Telecom System                 |

| Digital Correlator/<br>Integrator | Radio Telescope                |

### PROCESSES

Silicon Systems offers circuits in junction-isolated, bipolar, single and double-layer metal. Plus, SSi has a CMOS capability that includes not only a metal-gate process but also a silicon-gate process that produces circuits packed with more functions in a smaller size for high-speed, low-power performance. These are the most popular and reliable processes in the two basic technologies, and SSI's advanced ultra-clean wafer fab produces higher yields than ordinary facilities.

### **PRODUCT QUALITY**

Silicon Systems has made a major investment in product test and in-line quality control equipment. For example, a state-of-the-art LTX CP80 is used for functional and parametric testing of sophisticated analog, digital, and combination A/D circuits. In this way, SSi is dedicated to the delivery of complex VLSI circuits to meet the incoming quality level you require.

### MOS

| Integrated Circuit Function         | Application                               |

|-------------------------------------|-------------------------------------------|

| DTMF Receiver                       | *Decodes Touch-Tone®<br>Telephone Signals |

| 300 Baud Modem                      | Data Transmission                         |

| 1200/2400 Baud Receiver             | FSK/PSK Modem                             |

| Error Corrector                     | Military Radio                            |

| Remote Transmitter                  | Telephone Answering<br>Machine            |

| Phoneme Based Speech<br>Synthesizer | Text-to-Speech                            |

| Display Timing Generator            | TV Sets                                   |

| Video Processor                     | Infrared Video System                     |

| 16 Channel Switching<br>Matrix      | Bank Communications<br>System             |

| Digital Loop Detector               | Traffic Signal Control                    |

| Programmable Digital<br>Receiver    | Home Appliance Remote<br>Control          |

| Vocal Tract System                  | Speech Synthesis                          |

### **CUSTOMER SERVICE**

Silicon Systems provides individualized service for every customer. Our Customer Service Department is dedicated to responsive service and is staffed with personnel trained to consider our customers' needs as their most urgent requirement. Product quality and service are both viewed as cornerstones for SSi's continued growth.

No responsibility is assumed by SSI for use of these products nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of SSI. SSI reserves the right to make changes in specifications at any time and without notice

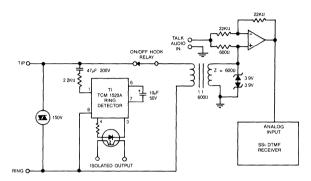

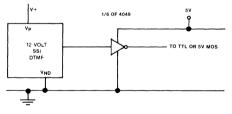

# Integrated DTMF Receiver SSI 201

# Data Sheet

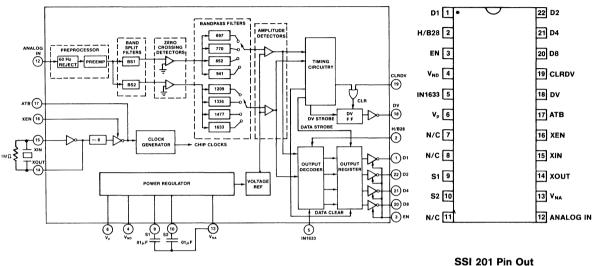

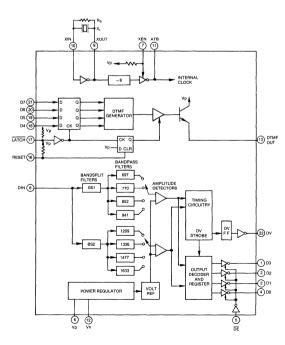

SSI 201 Block Diagram

SSI 201 Pin Out (Top View)

### FEATURES

- · Central office quality

- NO front-end band-splitting filters required

- Single, low-tolerance, 12-volt supply

- Detects either 12 or 16 standard DTMF digits

- Uses inexpensive 3.579545 -MHz crystal for reference

- Excellent speech immunity

- 22-pin DIP package for high system density

- Output in either 4-bit hexadecimal code or binary coded 2 of 8

- Synchronous or handshake interface

- Three-state outputs

### DESCRIPTION

The SSI 201 is a complete Dual Tone Multiple Frequency (DTMF) receiver detecting a selectable group of 12 or 16 standard digits No front-end pre-filtering is needed. The only externally required components are an inexpensive 3.58-MHz television "colorburst" crystal (for frequency reference) and two low-tolerance bypass capacitors. Extremely high system density is made possible by using the clock output of a crystal connected SSI 201 receiver to drive the time bases of additional receivers. The SSI 201 is a monolithic integrated circuit fabricated with low-power, complementary symmetry MOS (CMOS) processing. It requires only a single low tolerance voltage supply and is packaged in a standard 22 pin DIP.

The SSI 201 employs state-of-the-art circuit technology to combine digital and analog functions on the same CMOS chip using a standard digital semiconductor process The analog input is pre-processed by 60-Hz reject and band splitting filters and then hard-limited to provide AGC Eight bandpass filters detect the individual tones The digital post-processor times the tone durations and provides the correctly coded digital outputs Outputs interface directly to standard CMOS circuitry, and are three-state enabled to facilitate bus-oriented architectures

# Integrated DTMF Receiver SSI 201

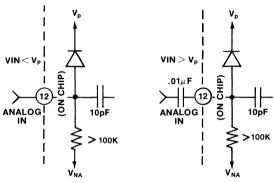

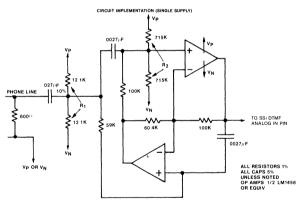

### ANALOG IN (pin 12)

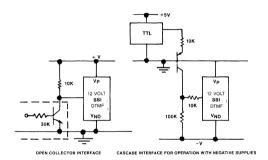

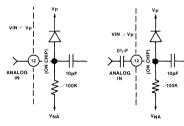

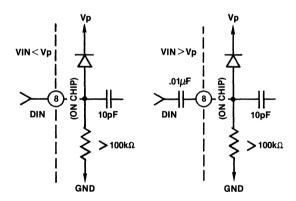

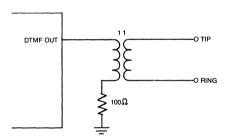

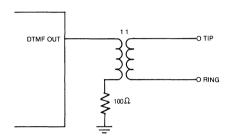

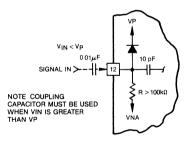

This pin accepts the analog input. It is internally biased so that the input signal may be AC coupled. The input may be DC coupled as long as it does not exceed the positive supply. Proper input coupling is illustrated below.

### **CRYSTAL OSCILLATOR**

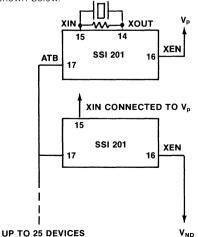

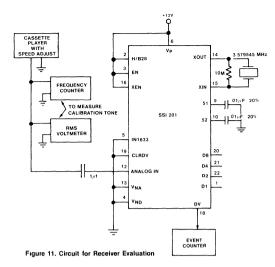

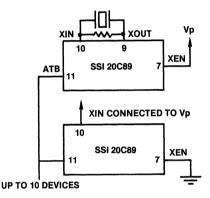

The SSI 201 contains an onboard inverter with sufficient gain to provide oscillation when connected to a low-cost television "color-burst" crystal The crystal oscillator is enabled by tying XEN (pin 16) high. The crystal is connected between XIN (pin 15) and XOUT (pin 14) A 1 MEG $\Omega$  10% resistor is also connected between these pins in this mode, ATB (pin 17) is a clock frequency output. Other SSI 201's may use the same frequency reference by tying their ATB pins to the ATB of a crystal connected device XIN and XEN of the auxiliary devices must then be tied high and low respectively Twenty-five devices may run off a single crystal-connected SSI 201 as shown below.

### H/B28 (pin 2)

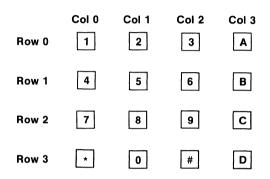

This pin selects the format of the digital output code When H/B28 is tied high, the output is hexadecimal When tied low, the output is binary coded 2 of 8 The table below describes the two output codes

|       | Hexadecimal |    |    |    | Bina | ry Co | ded 2 | of 8 |

|-------|-------------|----|----|----|------|-------|-------|------|

| Digit | D8          | D4 | D2 | D1 | D8   | D4    | D2    | D1   |

| 1     | 0           | 0  | 0  | 1  | 0    | 0     | 0     | 0    |

| 2     | 0           | 0  | 1  | 0  | 0    | 0     | 0     | 1    |

| 3     | 0           | 0  | 1  | 1  | 0    | 0     | 1     | 0    |

| 4     | 0           | 1  | 0  | 0  | 0    | 1     | 0     | 0    |

| 5     | 0           | 1  | 0  | 1  | 0    | 1     | 0     | 1    |

| 6     | 0           | 1  | 1  | 0  | 0    | 1     | 1     | 0    |

| 7     | 0           | 1  | 1  | 1  | 1    | 0     | 0     | 0    |

| 8     | 1           | 0  | 0  | 0  | 1    | 0     | 0     | 1    |

| 9     | 1           | 0  | 0  | 1  | 1    | 0     | 1     | 0    |

| 0     | 1           | 0  | 1  | 0  | 1    | 1     | 0     | 1    |

| *     | 1           | 0  | 1  | 1  | 1    | 1     | 0     | 0    |

| #     | 1           | 1  | 0  | 0  | 1    | 1     | 1     | 0    |

| А     | 1           | 1  | 0  | 1  | 0    | 0     | 1     | 1    |

| В     | 1           | 1  | 1  | 0  | 0    | 1     | 1     | 1    |

| С     | 1           | 1  | 1  | 1  | 1    | 0     | 1     | 1    |

| D     | 0           | 0  | 0  | 0  | 1    | 1     | 1     | 1    |

### IN1633 (pin 5)

When tied high, this pin inhibits detection of tone pairs containing the 1633-Hz component. For detection of all 16 standard digits, IN1633 must be tied low

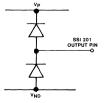

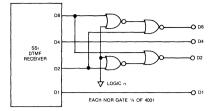

### OUTPUTS D1, D2, D4, D8 (pins 1, 22, 21, 20) and EN (pin 3)

Outputs D1, D2, D4, D8 are CMOS push-pull when enabled (EN high) and open circuited (high impedence) when disabled by pulling EN low These digital outputs provide the code corresponding to the detected digit in the format programmed by the H/B28 pin The digital outputs become valid after a tone pair has been detected and they are then cleared when a valid pause is timed

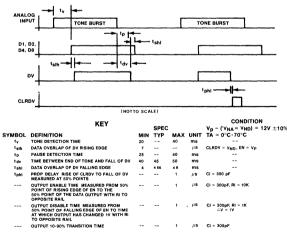

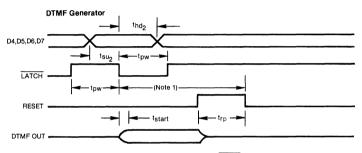

### DV (pin 18) and CLRDV (pin 19)

DV signals a detection by going high after a valid tone pair is sensed and decoded at the output pins D1, D2, D4, D8 DV remains high until a valid pause occurs or the CLRDV is raised high, whichever is earlier

### INTERNAL BYPASS PINS S1, S2 (pins 9, 10)

In order for the SSI 201 DTMF Receiver to function properly, these pins must be bypassed to  $V_{\text{NA}}$  with 0.01  $\mu F$   $\pm$  20% capacitors

### POWER SUPPLY PINS $V_{P}$ (pin 6) $V_{NA}$ (pin 13) $V_{ND}$ (pin 4)

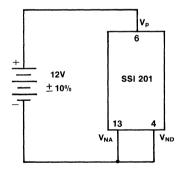

The analog (V\_{\tiny NA}) and digital (V\_{\tiny ND}) supplies are brought out separately to enhance analog noise immunity on the chip. V\_{\tiny NA} and V\_{\tiny ND} should be connected externally as shown below

### **12V SYSTEM**

### N/C PINS (pins 7, 8, 11)

These pins have no internal connection and may be left floating.

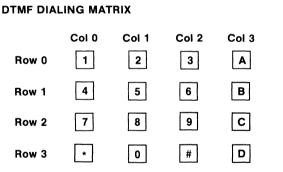

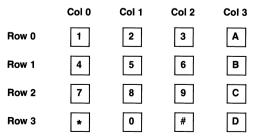

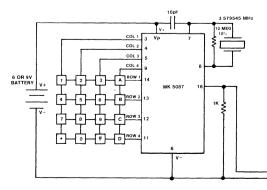

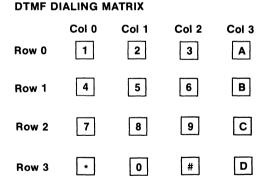

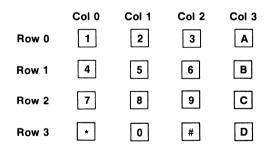

### DTMF DIALING MATRIX

Note Column 3 is for special applications and is not normally used in telephone dialing

### **DETECTION FREQUENCY**

| Low Group f <sub>o</sub> | High Group f₀      |

|--------------------------|--------------------|

| Row 0 = 697 Hz           | Column 0 = 1209 Hz |

| Row 1 = 770 Hz           | Column 1 = 1336 Hz |

| Row 2 = 852 Hz           | Column 2 = 1477 Hz |

| Row 3 = 941 Hz           | Column 3 = 1633 Hz |

1 SUSTE

14351 Myford Road, Tustin, California 92680 📕 (714) 731-7110, TWX 910-595-2809

### **ABSOLUTE MAXIMUM RATINGS\***

| DC Supply Voltage V <sub>p</sub> +16 V         |

|------------------------------------------------|

| (Referenced to $V_{NA}$ , $V_{ND}$ )           |

| Operating Temperature 40°C to +85°C Ambient    |

| Storage Temperature65°C to 150°C               |

| Power Dissipation (25°C)1 W                    |

| (Derate above T <sub>A</sub> = 25°C @ 10mW/°C) |

| Input Voltage             | $(V_p + 5V)$ to $(V_{ND}5V)$  |

|---------------------------|-------------------------------|

| (All inputs except ANALOC | G IN)                         |

| ANALOG IN Voltage         | $(V_p + 5V)$ to $(V_p - 22V)$ |

| DC Current into any Input | ±1.0mA                        |

| Lead Temperature          |                               |

| (soldering, 10 sec.)      |                               |

|                           |                               |

\*Operation above absolute maximum ratings may damage the device Note. All SSI 201 unused inputs must be connected to  $V_{\text{p}}$  or  $V_{\text{ND}},$  as appropriate

### **ELECTRICAL CHARACTERISTICS** $(-40^{\circ}C \le T_A \le +85^{\circ}C, V_p - V_{ND} = V_p - V_{NA} = 12V \pm 10\%)$

| Parameter                             | Conditions                                                      | Min                                    | Тур | Max                                                            | Units                                     |

|---------------------------------------|-----------------------------------------------------------------|----------------------------------------|-----|----------------------------------------------------------------|-------------------------------------------|

| Frequency Detect Bandwidth            |                                                                 | ±(15+2Hz)                              | ±23 | ± 30                                                           | % of $f_{o}$                              |

| Amplitude for Detection               | each tone                                                       | -24                                    |     | +6                                                             | dBm referenced to 600 $\Omega$            |

| Minimum Acceptable Twist              | twist = $\frac{\text{high tone}}{\text{low tone}}$              | -8                                     |     | +4                                                             | dB                                        |

| Detection Time                        |                                                                 | 20                                     | 25  | 40                                                             | ms                                        |

| Pause Time                            |                                                                 | 25                                     | 32  | 40                                                             | ms                                        |

| 60-Hz Tolerance                       |                                                                 |                                        |     | 2                                                              | Vrms                                      |

| Dial Tone Tolerance                   | "precise" dial tone                                             |                                        |     | 0 dB                                                           | dB referenced to lower amplitude tone     |

| Talk Off                              | MITEL tape<br>#CM 7290                                          |                                        | 2   |                                                                | hits                                      |

| Digital Outputs<br>(except XOUT)      | "0" level, 750µA load<br>"1" level, 750µA load                  | V <sub>ND</sub><br>V <sub>p</sub> - 05 |     | V <sub>ND</sub> + 0 5<br>V <sub>p</sub>                        | V<br>V                                    |

| Digital Inputs<br>(except H/B28, XEN) | "0" level<br>"1" level                                          | $V_{ND}$<br>Vp - $3(V_p - V_{ND})$     |     | $\begin{array}{c} V_{ND} + 3(V_p - V_{ND}) \\ V_p \end{array}$ | V<br>V                                    |

| Digital Inputs<br>H/B28, XEN          | "0" level<br>"1" level                                          | V <sub>ND</sub><br>V <sub>p</sub> -1   |     | V <sub>ND</sub> +1<br>V <sub>p</sub>                           | V<br>V                                    |

| Power Supply Noise                    | wide band                                                       |                                        |     | 25                                                             | mV p-p                                    |

| Supply Current                        | $T_{A} = 25^{\circ}C$<br>$V_{p}-V_{NA}=V_{p}-V_{ND}=12V\pm10\%$ |                                        | 29  | 50                                                             | mA                                        |

| Noise Tolerance                       | MITEL tape<br>#CM 7290                                          |                                        |     | -12                                                            | dB referenced to<br>lowest amplitude tone |

| Input Impedence                       | $V_p \geqslant V_{in} \geqslant V_p$ -22                        | 100K <b>Ω//</b> 15pF                   |     |                                                                |                                           |

No responsibility is assumed by SSi for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of SSi. SSi reserves the right to make changes in specifications at any time and without notice.

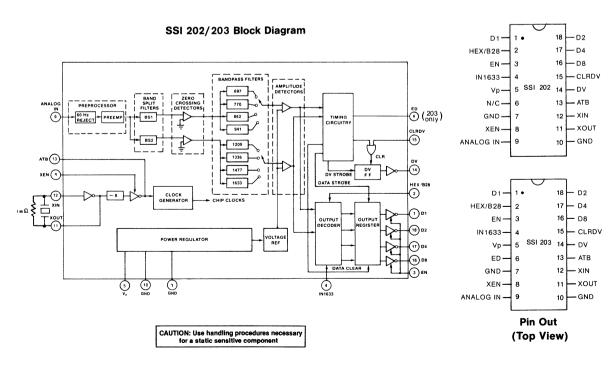

### SSI 2O2/2O3 5V Low-Power DTMF Receiver

### Data Sheet

### DESCRIPTION

The SSI 202 and 203 are complete Dual Tone Multiple Frequency (DTMF) receivers detecting a selectable group of 12 or 16 standard digits. No front-end pre-filtering is needed. The only externally required components are an inexpensive 3.58-MHz television "colorburst" crystal (for frequency reference) and a bias resistor. Extremely high system density is made possible by using the clock output of a crystal connected SSI 202 or 203 receiver to drive the time bases of additional receivers. Both are monolithic integrated circuits fabricated with low-power, complementary symmetry MOS (CMOS) processing. They require only a single low tolerance voltage supply and are packaged in a standard 18 pin plastic DIP.

The SSI 202 and 203 employ state-of-the-art circuit technology to combine digital and analog functions on the same CMOS chip using a standard digital semiconductor process. The analog input is pre-processed by 60-Hz reject and band splitting filters and then hard-limited to provide AGC. Eight bandpass filters detect the individual tones. The digital post-processor times the tone durations and provides the correctly coded digital outputs. Outputs interface directly to standard CMOS circuitry, and are three-state enabled to facilitate bus-oriented architectures.

### FEATURES

- Central office quality

- NO front-end band-splitting filters required

- Single, low-tolerance, 5-volt supply

- Detects either 12 or 16 standard DTMF digits

- Uses inexpensive 3.579545 MHz crystal for

- referenceExcellent speech immunity

- Excellent speech immunity

- Output in either 4-bit hexadecimal code or binary coded 2 of 8

- 18-pin DIP package for high system density

- Synchronous or handshake interface

- Three-state outputs

- Early detect output (SSI 203 only)

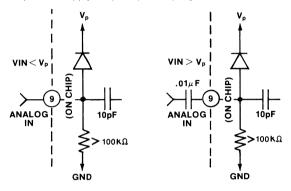

### ANALOG IN

This pin accepts the analog input. It is internally biased so that the input signal may be AC coupled. The input may be DC coupled as long as it does not exceed the positive supply. Proper input coupling is illustrated below.

The SSI 202 is designed to accept sinusoidal input wave forms but will operate satisfactorily with any input that has the correct fundamental frequency with harmonics greater than 20 dB below the fundamental

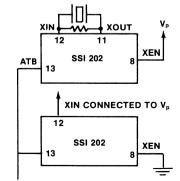

### **CRYSTAL OSCILLATOR**

The SSI 202 and 203 contain an onboard inverter with sufficient gain to provide oscillation when connected to a low-cost television "color-burst" crystal. The crystal oscillator is enabled by tying XEN high. The crystal is connected between XIN and XOUT A 1 MQ 10% resistor is also connected between these pins. In this mode, ATB is a clock frequency output. Other SSI 202's (or 203's) may use the same frequency reference by tying their ATB pins to the ATB of a crystal connected device. XIN and XEN of the auxiliary devices must then be tied high and low respectively. Ten devices may run off a single crystal-connected SSI 202 or 203 as shown below.

### HEX/B28

This pin selects the format of the digital output code When HEX/B28 is tied high, the output is hiexadecimal. When tied low, the output is binary coded 2 of 8 The table below describes the two output codes

|       | Hexadecimal |    |    | Bina | ary Co | ded 2 | of 8 |    |

|-------|-------------|----|----|------|--------|-------|------|----|

| Digit | D8          | D4 | D2 | D1   | D8     | D4    | D2   | D1 |

| 1     | 0           | 0  | 0  | 1    | 0      | 0     | 0    | 0  |

| 2     | 0           | 0  | 1  | 0    | 0      | 0     | 0    | 1  |

| 3     | 0           | 0  | 1  | 1    | 0      | 0     | 1    | 0  |

| 4     | 0           | 1  | 0  | 0    | 0      | 1     | 0    | 0  |

| 5     | 0           | 1  | 0  | 1    | 0      | 1     | 0    | 1  |

| 6     | 0           | 1  | 1  | 0    | 0      | 1     | 1    | 0  |

| 7     | 0           | 1  | 1  | 1    | 1      | 0     | 0    | 0  |

| 8     | 1           | 0  | 0  | 0    | 1      | 0     | 0    | 1  |

| 9     | 1           | 0  | 0  | 1    | 1      | 0     | 1    | 0  |

| 0     | 1           | 0  | 1  | 0    | 1      | 1     | 0    | 1  |

| *     | 1           | 0  | 1  | 1    | 1      | 1     | 0    | 0  |

| #     | 1           | 1  | 0  | 0    | 1      | 1     | 1    | 0  |

| А     | 1           | 1  | 0  | 1    | 0      | 0     | 1    | 1  |

| В     | 1           | 1  | 1  | 0    | 0      | 1     | 1    | 1  |

| С     | 1           | 1  | 1  | 1    | 1      | 0     | 1    | 1  |

| D     | 0           | 0  | 0  | 0    | 1      | 1     | 1    | 1  |

### IN1633

When tied high, this pin inhibits detection of tone pairs containing the 1633-Hz component. For detection of all 16 standard digits, IN1633 must be tied low

### OUTPUTS D1, D2, D4, D8 and EN

Outputs D1, D2, D4, D8 are CMOS push-pull when enabled (EN high) and open circuited (high impedence) when disabled by pulling EN low These digital outputs provide the code corresponding to the detected digit in the format programmed by the HEX/B28 pin The digital outputs become valid after a tone pair has been detected and they are then cleared when a valid pause is timed

### **DV and CLRDV**

DV signals a detection by going high after a valid tone pair is sensed and decoded at the output pins D1, D2, D4, D8. DV remains high until a valid pause occurs or the CLRDV is raised high, whichever is earlier

### ED (SSI 203 only)

The ED output goes high as soon as the SSI 203 begins to detect a DTMF tone pair and falls when the 203 begins to detect a pause. The D1, D2, D4, and D8 outputs are guaranteed to be valid when DV is high, but are not necessarily valid when ED is high.

### N/C PINS

These pins have no internal connection and may be left floating

Note Column 3 is for special applications and is not normally used in telephone dialing

### **DETECTION FREQUENCY**

| Low Group f <sub>o</sub> | High Group f <sub>o</sub> |

|--------------------------|---------------------------|

| Row 0 = 697 Hz           | Column 0 = 1209 Hz        |

| Row 1 = 770 Hz           | Column 1 = 1336 Hz        |

| Row 2 = 852 Hz           | Column 2 = 1477 Hz        |

| Row 3 = 941 Hz           | Column 3 = 1633 Hz        |

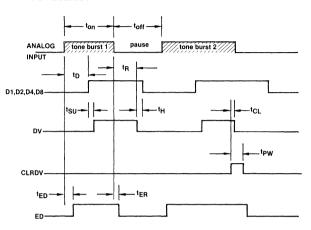

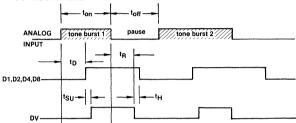

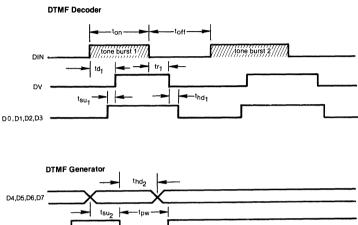

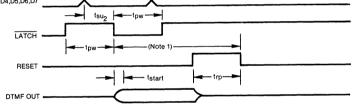

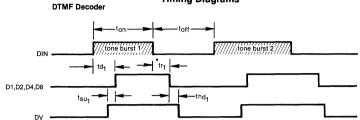

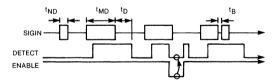

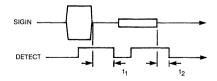

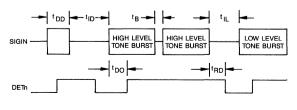

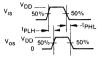

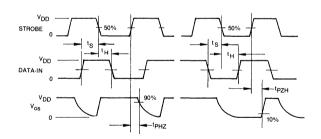

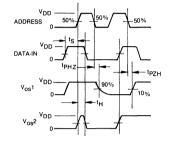

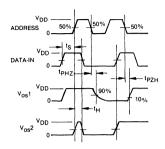

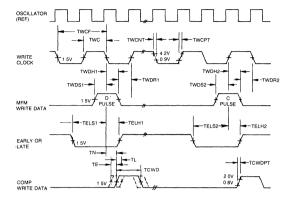

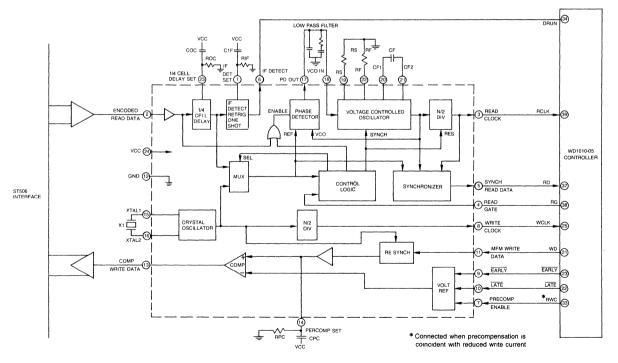

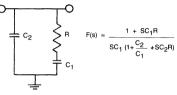

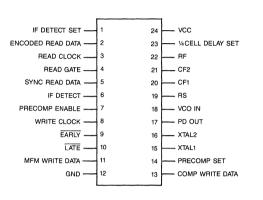

### SSI 202/203 TIMING

| PARAMETER                      | SYMBOL | MIN. | TYP. | MAX. | UNITS |

|--------------------------------|--------|------|------|------|-------|

| TONE TIME. for detection       | ton    | 40   | -    | -    | ms    |

| for rejection                  | ton    | -    | -    | 20   | ms    |

| PAUSE TIME: for detection      | tOFF   | 40   | -    | -    | ms    |

| for rejection                  | tOFF   | _    | -    | 20   | ms    |

| DETECT TIME                    | tD     | 25   | -    | 46   | ms    |

| RELEASE TIME                   | tR     | 35   | -    | 50   | ms    |

| DATA SETUP TIME                | tsu    | 7    | -    | -    | μS    |

| DATA HOLD TIME                 | tн     | 4.2  | -    | 5.0  | ms    |

| DV CLEAR TIME                  | tCL    | -    | 160  | 250  | ns    |

| CLRDV pulse width              | tpw    | 200  | -    | -    | ns    |

| ED Detect Time                 | tED    | 7    | -    | 22   | ms    |

| ED Release Time                | tER    | 2    | _    | 18   | ms    |

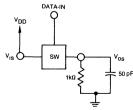

| OUTPUT ENABLE TIME             | -      | -    | 200  | 300  | ns    |

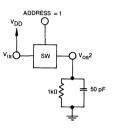

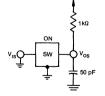

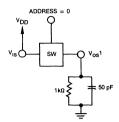

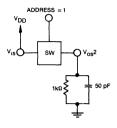

| $C_L = 50 pF R_L = 1K \Omega$  |        |      |      |      |       |

| OUTPUT DISABLE TIME            | -      | -    | 150  | 200  | ns    |

| $C_L = 35 pF R_L = 500 \Omega$ | 1      |      |      |      |       |

| OUTPUT RISE TIME               | -      | -    | 200  | 300  | ns    |

| $C_L = 50 pF$                  |        |      |      |      |       |

| OUTPUT FALL TIME               | -      | _    | 160  | 250  | ns    |

| $C_L = 50 pF$                  |        |      |      |      |       |

|                                |        |      |      |      |       |

n suste

14351 Myford Road, Tustin, CA 92680 📕 (714) 731-7110, TWX 910-595-2809

### **ABSOLUTE MAXIMUM RATINGS\***

| Input Voltage                                    |

|--------------------------------------------------|

| (All inputs except ANALOG IN)                    |

| ANALOG IN Voltage( $V_p$ + 5V) to ( $V_p$ - 10V) |

| DC Current into any Input ±1.0mA                 |

| Lead Temperature 300°C                           |

| (soldering, 10 sec.)                             |

\*Operation above absolute maximum ratings may damage the device Note All SSI 202/203 unused inputs must be connected to  $V_{\rm p}$  or Gnd, as appropriate

### **ELECTRICAL CHARACTERISTICS** $(-40^{\circ}C \le T_A \le +85^{\circ}C, V_p = 5V \pm 10\%)$

| Parameter                        | Conditions                                                 | Min                 | Тур | Max        | Units                                     |

|----------------------------------|------------------------------------------------------------|---------------------|-----|------------|-------------------------------------------|

| Frequency Detect Bandwidth       |                                                            | ±(15+2Hz)           | ±23 | ± 3 5      | % of $f_{\rm O}$                          |

| Amplitude for Detection          | each tone                                                  | -32                 |     | -2         | dBm referenced to 600 ${f \Omega}$        |

| Minimum Acceptable Twist         | twist = $\frac{\text{high tone}}{\text{low tone}}$         | -10                 |     | +10        | dB                                        |

| 60-Hz Tolerance                  |                                                            |                     |     | 0.8        | Vrms                                      |

| Dial Tone Tolerance              | "precise" dial tone                                        |                     |     | OdB        | dB referenced to<br>lower amplitude tone  |

| Talk Off                         | MITEL tape #CM 7290                                        |                     | 2   |            | hits                                      |

| Digital Outputs<br>(except XOUT) | "0" level, 400 $\mu$ A load<br>"1' level, 200 $\mu$ A load | 0<br>Vp - 05        |     | 0 5<br>Vp  | V<br>V                                    |

| Digital Inputs                   | "0" level<br>"1" level                                     | 0<br>0 7 Vp         |     | 03V,<br>V, | V<br>V                                    |

| Power Supply Noise               | wide band                                                  |                     |     | 10         | mV p-p                                    |

| Supply Current                   | $T_A = 25^{\circ}C$                                        |                     | 10  | 16         | mA                                        |

| Noise Tolerance                  | MITEL tape<br>#CM 7290                                     |                     |     | -12        | dB referenced to<br>lowest amplitude tone |

| Input Impedence                  | $V_p \geqslant V_{in} \geqslant V_{\rho}$ -10              | 100K <b>Ω∥</b> 15pF |     |            |                                           |

No responsibility is assumed by SSI for use of these products nor for any infringements of patents and trademarks or other rights of third parties resulting from its use No license is granted under any patents, patent rights or trademarks of SSI. SSi reserves the right to make changes in specifications at any time and without notice

icon systems INNOVATORS IN INTEGRATION

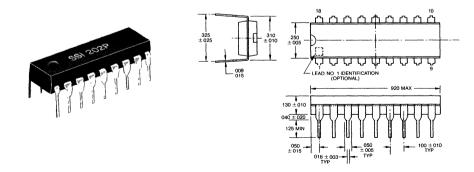

### SSI 204 5V Low Power DTMF Receiver

# Data Sheet

### DESCRIPTION

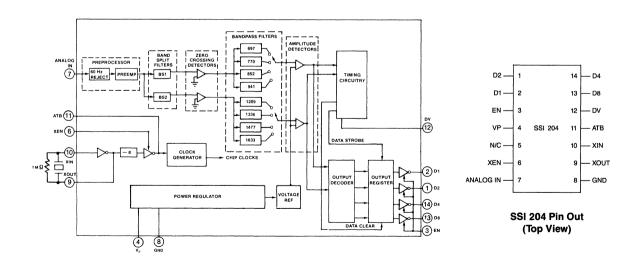

The SSI 204 is a complete Dual Tone Multiple Frequency (DTMF) receiver that detects all 16 standard digits. No front-end pre-filtering is needed. The only externally required components are an inexpensive 3.58-MHz television "color-burst" crystal for frequency reference and a bias resistor. An Alternate Time Base (ATB) is provided to permit operation of up to 10 SSI 204's from a single crystal. The SSI 204 employs state-of-theart "switched-capacitor" filter technology, resulting in approximately 40 poles of filtering, and digital circuitry on the same CMOS chip. The analog input signal is pre-processed by 60-Hz reject and band split filters and then zero-cross detected to provide AGC. Eight bandpass filters detect the individual tones. Digital processing is used to measure the tone and pause durations and to provide output timing and decoding. The outputs interface directly to standard CMOS circuitry and are three-state enabled to facilitate bus-oriented architectures.

### FEATURES

- Intended for applications with less requirements than the SSI 202

- 14-Pin plastic DIP for high system density

- NO front-end band splitting filters required

- Single low-tolerance 5-volt supply

- Detects all 16 standard DTMF digits

- Uses inexpensive 3.579545-MHz crystal

- Excellent speech immunity

- Output in 4-bit hexadecimal code

- Three-state outputs for microprocessor interface

**Block Diagram**

CAUTION: Use handling procedures necessary for a static sensitive component

### SSI 204 5V Low Power Subscriber DTMF Receiver

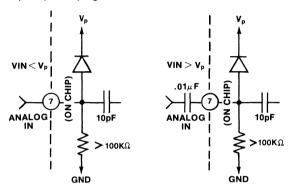

### ANALOG IN

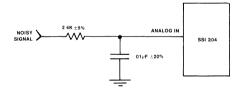

This pin accepts the analog input. It is internally biased so that the input signal may be AC coupled. The input may be DC coupled as long as it does not exceed the positive supply. Proper input coupling is illustrated below.

The SSI 204 is designed to accept sinusoidal input wave forms but will operate satisfactorily with any input that has the correct fundamental frequency with harmonics greater than 20 dB below the fundamental.

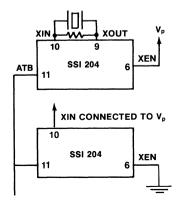

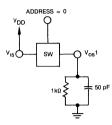

### **CRYSTAL OSCILLATOR**

The SSI 204 contains an onboard inverter with sufficient gain to provide oscillation when connected to a low-cost television "color-burst" crystal. The crystal oscillator is enabled by tying XEN high. The crystal is connected between XIN and XOUT. A 1 M $\Omega$  10% resistor is also connected between these pins. In this mode, ATB is a clock frequency output. Other SSI 204's (or 202's) may use the same frequency reference by tying their ATB pins to the ATB of a crystal connected device. XIN and XEN of the auxiliary devices must then be tied high and low respectively. Ten devices may run off a single crystal-connected SSI 204 (or 202) as shown below.

### OUTPUTS D1, D2, D4, D8, and EN

Outputs D1, D2, D4, D8 are CMOS push-pull when enabled (EN high) and open circuited (high impedance) when disabled by pulling EN low. These digital outputs provide the hexadecimal code corresponding to the detected digit. The digital outputs become valid after a tone pair has been detected and they are then cleared when a valid pause is timed. The table below describes the hexadecimal codes.

| OUTPUT CODE |             |   |   |   |  |  |  |

|-------------|-------------|---|---|---|--|--|--|

| Digit       | D8 D4 D2 D1 |   |   |   |  |  |  |

| 1           | 0           | 0 | 0 | 1 |  |  |  |

| 2           | 0           | 0 | 1 | 0 |  |  |  |

| 3           | 0           | 0 | 1 | 1 |  |  |  |

| 4           | 0           | 1 | 0 | 0 |  |  |  |

| 5           | 0           | 1 | 0 | 1 |  |  |  |

| 6           | 0           | 1 | 1 | 0 |  |  |  |

| 7           | 0           | 1 | 1 | 1 |  |  |  |

| 8           | 1           | 0 | 0 | 0 |  |  |  |

| 9           | 1           | 0 | 0 | 1 |  |  |  |

| 0           | 1           | 0 | 1 | 0 |  |  |  |

| *           | 1           | 0 | 1 | 1 |  |  |  |

| #           | 1           | 1 | 0 | 0 |  |  |  |

| Α           | 1           | 1 | 0 | 1 |  |  |  |

| В           | 1           | 1 | 1 | 0 |  |  |  |

| С           | 1           | 1 | 1 | 1 |  |  |  |

| D           | 0           | 0 | 0 | 0 |  |  |  |

|             |             |   |   |   |  |  |  |

### DV

DV signals a detection by going high after a valid tone pair is sensed and decoded at the output pins D1, D2, D4, D8. DV remains high until a valid pause occurs.

### N/C PIN

This pin has no internal connection and may be left floating.

### DTMF DIALING MATRIX

Note: Column 3 is for special applications and is not normally used in telephone dialing

| Low Group f <sub>o</sub> | High Group f <sub>o</sub> |

|--------------------------|---------------------------|

| Row 0 = 697 Hz           | Column 0 = 1209 Hz        |

| Row 1 = 770 Hz           | Column 1 = 1336 Hz        |

| Row 2 = 852 Hz           | Column 2 = 1477 Hz        |

| Row 3 = 941 Hz           | Column 3 = 1633 Hz        |

|                          |                           |

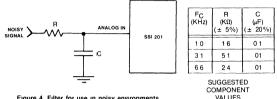

### **APPLICATION NOTES**

The SSI 204 will tolerate total input rms noise up to 12dB below the lowest amplitude tone. For most telephone applications, the combination of the high frequency attenuation of the telephone line and internal band-limiting make special circuitry at the input to the SSI 204 unnecessary. However, noise near the 56kHz internal sampling frequency will be aliased (folded back) into the audio spectrum, so if excessive noise is present above 28kHz, the simple RC filter as shown below may be employed to band limit the incoming signal.

Filter for use in extreme high frequency input noise environment

Noise will also be reduced by placing a grounded trace around XIN and XOUT pins on the circuit board layout when using a crystal. It is important to note that XOUT is not intended to drive an additional device. XIN may be driven externally; in this case leave XOUT floating.

### SSI 204 TIMING

| PARAMETER                      | SYMBOL | MIN. | TYP. | MAX. | UNITS |

|--------------------------------|--------|------|------|------|-------|

| TONE TIME for detection        | ton    | 40   | -    | -    | mS    |

| for rejection                  | ton    | -    | -    | 20   | mS    |

| PAUSE TIME. for detection      | tOFF   | 40   | -    | -    | mS    |

| for rejection                  | tOFF   | -    | -    | 20   | mS    |

| DETECT TIME                    | tD     | 25   | -    | 46   | mS    |

| RELEASE TIME                   | tR     | 35   | -    | 50   | mS    |

| DATA SETUP TIME                | tsu    | 7    | -    | -    | μs    |

| DATA HOLD TIME                 | tн     | 42   | -    | 50   | mS    |

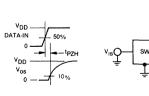

| OUTPUT ENABLE TIME             | -      | -    | 200  | 300  | nS    |

| $C_L = 50 pF R_L = 1K \Omega$  |        |      |      |      |       |

| OUTPUT DISABLE TIME            | _      |      | 150  | 200  | nS    |

| $C_L = 35 pF R_L = 500 \Omega$ |        |      |      |      |       |

| OUTPUT RISE TIME               | -      | _    | 200  | 300  | nS    |

| $C_L = 50 pF$                  |        |      |      |      |       |

| OUTPUT FALL TIME               | _      | _    | 160  | 250  | nS    |

| $C_L = 50 pF$                  |        |      |      |      |       |

|                                |        |      |      |      |       |

### **ABSOLUTE MAXIMUM RATINGS\***

| DC Supply Voltage Vp +7 Volts                             |

|-----------------------------------------------------------|

| Operating Temperature $\dots - 40$ °C to $+85$ °C Ambient |

| Storage Temperature                                       |

| Power Dissipation (25°C)                                  |

| Input Voltage                                             |

| ANALOG IN Voltage $(V_p + 0.5V)$ to $(V_p - 10V)$        |

|----------------------------------------------------------|

| DC Current into any Input                                |

| Lead Temperature                                         |

| *Operation above absolute maximum ratings may damage the |

device.

Note All SSI 204 unused inputs must be connected to  $\mathrm{V}_\mathrm{p}$  or Gnd as appropriate

n systems " 14351 Myford Road, Tustin, CA 92680 (714) 731-7110, TWX 910-595-2809

### **ELECTRICAL CHARACTERISTICS** (-40°C $\leq$ T<sub>A</sub> $\leq$ +85°C, V<sub>p</sub> = 5V $\pm$ 10%)

| Parameter                        | Conditions                                       | Min                             | Тур | Max          | Units                                    |

|----------------------------------|--------------------------------------------------|---------------------------------|-----|--------------|------------------------------------------|

| Frequency Detect Bandwidth       | _                                                | ±(15+2Hz)                       | ±23 | ±35          | % of $t_{o}$                             |

| Amplitude for Detection          | each tone                                        | - 32                            |     | -2           | dBm referenced to 600 $\Omega$           |

| Minimum Acceptable Twist         | $twist = \frac{high tone}{low tone}$             | -8                              |     | +4           | dB                                       |

| 60-Hz Tolerance                  |                                                  |                                 |     | 0.8          | Vrms                                     |

| Dial Tone Tolerance              | "precise" dial tone                              |                                 |     | 0dB          | dB referenced to<br>lower amplitude tone |

| Talk-Off                         | MITEL tape<br>#CM 7290                           |                                 | 2   |              | hits                                     |

| Digital Outputs<br>(except XOUT) | "0" level, 400 µA load<br>"1" level, 200 µA load | <b>0</b><br>V <sub>p</sub> - 05 |     | 05<br>Vp     | V<br>V                                   |

| Digital Inputs                   | "0" level<br>"1" level                           | 0<br>07Vp                       |     | 0 3 Vp<br>Vp | V<br>V                                   |

| Power Supply Noise               | wide band                                        |                                 |     | 10           | mV p-p                                   |

| Supply Current                   | T <sub>A</sub> = 25°C                            |                                 | 10  | 16           | mA                                       |

| Noise Tolerance                  | MITEL tape<br>#CM 7290                           |                                 |     | -12          | dB referenced to lowest amplitude tone   |

| Input Impedance                  | $V_p \geqslant V_m \geqslant V_p-10V$            | 100K <b>Ω//</b> 15pF            |     |              |                                          |

No responsibility is assumed by SSI for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent

rights or trademarks of SSI SSI reserves the right to make changes in specifications at any time and without notice

silicon systems INNOVATORS IN INTEGRATION

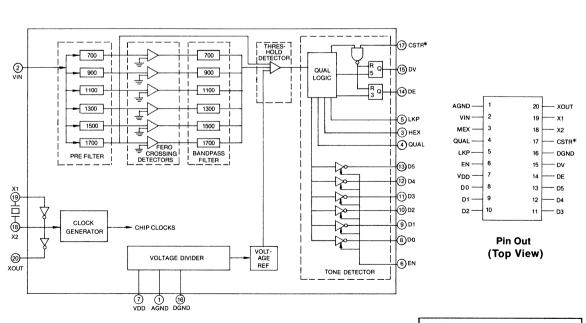

SSI 207 Integrated MF Receiver

### Preliminary Data Sheet

### **GENERAL DESCRIPTION**

The SSI 207 is a complete Multi-Frequency (MF) receiver that can detect all 15 tone-pairs, including ST and KP. This receiver is intended for use in equal access applications and thus meets Bell and CCITT R1 central office register signalling specifications.

No anti-alias filtering is needed if the input signal is bandlimited to 26 KHz. The only external component required is an inexpensive television "color burst" 3.58 MHz crystal.

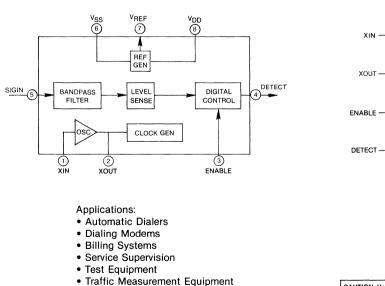

The SSI 207 employs state-of-the-art switched capacitor filters in CMOS technology. The receiver consists of a bank of channel-separation bandpass filters followed by zero-crossing detectors and frequency-measurement bandpass filters, an amplitude check circuit, a timer and decoder circuit, and a clock generator. The device does not attempt to identify strings of digits by the KP (key pulse) and ST (stop) tone pairs.

The outputs interface directly with standard DMOS or TTL circuitry and are three-state enabled to facilitate bus-oriented architecture.

### FEATURES

- Meets Bell and CCITT R1 specifications.

- · 20-pin plastic DIP.

- Single low-tolerance 5V supply.

- · Detects all 15 tone-pairs including ST and KP

- Long KP capability

- Built-in amplitude discrimination.

- Excellent noise tolerance.

- Outputs in either "n of 6" or hexadecimal code.

- Three-state outputs, CMOS-compatible and TTLcompatible.

### SSI 207 Block Diagram

CAUTION: Use handling procedures necessary for a static sensitive component

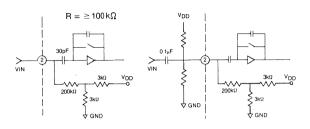

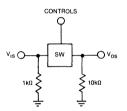

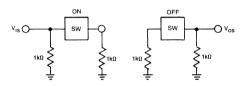

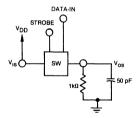

### VIN

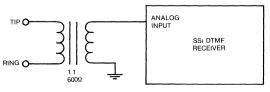

This pin accepts the analog input. It is internally biased to half the supply and is capacitively coupled to the channel separation filters. The input may be DC coupled as long as it does not exceed the positive supply. Proper input coupling is illustrated below.

### **Crystal Oscillator**

The SSI 207 contains an on-board inverter with sufficient gain to provide oscillation when connected to a low cost television "color-burst" crystal. The on-chip clock signals are generated based on the oscillator. The crystal is connected between X1 and X2. X-OUT is a 3.58 MHz square wave capable of driving other circuits as long as the capacitive load does not exceed 50 pF.

The digital output format is neither "n of 6" or 4-bit hexadecimal.

| DV       | : | Data Strobe                     |

|----------|---|---------------------------------|

| DE       |   | Data Error Strobe               |

| DO to D5 | : | <b>Tristate Digital Outputs</b> |

### n of 6 MODE (HEX pulled low)

Whenever a valid 2 of 6 code has been recognized, the DV strobe rises. It remains high until the code goes away, or the CSTR\* line is activated. It will not reactivate until a new code is detected. Whenever an invalid 2 of 6 code is recognized, (1 of 6, 3 of 6, etc.) the DE strobe rises to indicate a transmission error. The DE strobe remains high until all errors stop, a valid tone pair is detected, or the CSTR\* line is activated. Once cleared by CSTR, it will not reactivate until a new invalid condition is detected. The DE and DV strobes will never be high simultaneously.

The off-chip output register can be clocked by either the rising or falling edge of the strobe. The outputs will be cleared to zero when no valid tone is present.

In the "n of 6" mode (HEX pulled low), each output represents one of the six frequencies according to the following table:

| Frequency | Output Pin |

|-----------|------------|

| 700       | D0         |

| 900       | D1         |

| 1100      | D2         |

| 1300      | D3         |

| 1500      | D4         |

| 1700      | D5         |

### HEX MODE (HEX pulled high)

In the "hex" mode, D0 to D3 provide a 4-bit code identifying one of the 15 **valid** tone combinations according to the following table:

| Channels | Tone Pair Freq.  | Name | D3 | D2 | D1 | D0 |

|----------|------------------|------|----|----|----|----|

| 0-1      | 700, 900         | 1    | 0  | 0  | 0  | 1  |

| 0-2      | 700, 1100        | 2    | 0  | 0  | 1  | 0  |

| 1-2      | 500, 1100        | 3    | 0  | 0  | 1  | 1  |

| 0-3      | 700, 1300        | 4    | 0  | 1  | 0  | 0  |

| 1-3      | 900, 1300        | 5    | 0  | 1  | 0  | 1  |

| 2-3      | 1100, 1300       | 6    | 0  | 1  | 1  | 0  |

| 0-4      | 700, 1500        | 7    | 0  | 1  | 1  | 1  |

| 1-4      | 900, 1500        | 8    | 1  | 0  | 0  | 0  |

| 2-4      | 1100, 1500       | 9    | 1  | 0  | 0  | 1  |

| 3-4      | 1300, 1500       | 0    | 1  | 0  | 1  | 0  |

| 2-5      | 1100, 1700       | KP   | 1  | 0  | 1  | 1  |

| 4-5      | 1500, 1700       | ST   | 1  | 1  | 0  | 0  |

| 1-5      | 900, 1700        | ST1  | 1  | 1  | 0  | 1  |

| 3-5      | 1300, 1700       | ST2  | 1  | 1  | 1  | 0  |

| 0-5      | 700, 1700        | ST3  | 1  | 1  | 1  | 1  |

|          | any other signal | -    | 0  | 0  | 0  | 0  |

NOTE In the hex mode, D4 = DE and D5 = DV

The outputs will be cleared to zero when no valid tone pair is present.

### LKP

The KP timer control. When high, the KP pulse must be longer than the other tone pairs before it will be detected. When low, the KP pulse is treated as any other pulse.

### QUAL

Enables tone pair qualification. When low, the threshold detector outputs are passed to the data outputs (DO-D5), without validation, in the format selected by the HEX pin. These outputs, plus strobes DV and DE, are updated once per 2.3 ms frame. (DV and DE represent "2-of-6" indicators in this mode). Note that the strobes will cycle once per frame (even when the inputs are stable). As always, data changes only when both strobes are low.

### CSTR\*

This input clears both the DV and DE strobes. After CSTR\* is released, the strobes will remain low until a new detect (or error) occurs. The output data is latched by CSTR\* and will not change while CSTR\* is low, even in the event that a new detect is qualified internally. (Note that improper use of CSTR\* may result in missed detects.

### EN\*

The tristate enable control — When low, the DO-D5 outputs are in the low impedence state. In an interrupt oriented microprocessor interface,  $EN^*$  and  $CSTR^*$  will often be tied together to provide automatic reset of the strobes when the output data is enabled.

### DC Specifications (0°C $\leqslant$ TA $\leqslant$ 70°C, V<sub>DD</sub> = 5V $\pm$ 10%)

| Rating                                              | Symbol | Min.      | Max. | Unit |

|-----------------------------------------------------|--------|-----------|------|------|

| Supply Current                                      | Idd    | _         | 20   | mA   |

| Output Logic 0                                      | Vol    | -         |      |      |

| lol =8mA                                            | _      | _         | 0.5  | V    |

| lol = 1mA                                           | _      | _         | 0.4  | V    |

| Output Logic 1                                      | Voh    | -         |      | -    |

| loh = -4mA                                          | _      | VDD-1.0   |      | V    |

| loh = -1mA                                          | —      | VDD-0.5   |      | V    |

| Input Logic 1                                       | Vih    | 2.0       |      | V    |

| Input logic 0                                       | Vil    | -         | 0.8  | V    |

| Analog Input Impedance (Input between VDD and AGND) | Zin    | 100k/30pF |      | Ω    |

| Digital Input Current (Input between VDD and OGND)  | lin    | - 50      | 50   | μΑ   |

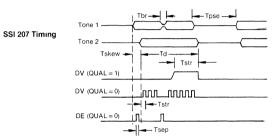

### **Timing Specifications**

| Parameter                 | Symbol | Min. | Max. | Unit |

|---------------------------|--------|------|------|------|

| TONE DETECTION            | Td     |      | _    |      |

| KP (LKP = VDD)            |        | 55   | _    | ms   |

| KP (LKP = DGND)           |        | 30   | _    | ms   |

| All others                | _      | 30   | _    | ms   |

| TONE REJECTION            | Tr     |      | -    | _    |

| KP (LKP = VAN)            | —      |      | 30   | ms   |

| KP (LKP = DGND)           |        |      | 10   | ms   |

| All others                | —      |      | 10   | ms   |

| Tone Skew Tolerance       | Tskew  | 4    | _    | ms   |

| Pause Duration            | Tpse   | 20   |      | ms   |

| Bridged Pause Duration    | Tbr    | _    | 10   | ms   |

| Minimum Strobe PW         | Tstr   |      | _    |      |

| QUAL High                 |        | 20   |      | ms   |

| QUAL Low                  |        | 2    |      | ms   |

| Minimum Strobe Separation | Тѕер   |      |      |      |

| QUAL High                 |        | 20   | -    | ms   |

| QUAL Low                  |        | 2    | _    | ms   |

| Rise Time                 | Tr     |      | 100  | ns   |

| Fall Time                 | Tf     |      | 100  | ns   |

| CSTR* Width               | Tw     | 50   | _    | ns   |

| Data Enable Time          | Ten    |      | 100  | ns   |

| Data Disable Time         | Tdis   |      | 100  | ns   |

| Strobe Reset Time         | Trst   |      | 100  | ns   |

n sustem

14351 Myford Road, Tustin, California 92680 (714) 731-7110, TWX 910-595-2809

### **Absolute Maximum Ratings**

| Input Voltage             | (Vp to 3V) to -0.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC Current into any input | <u>+</u> 10mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Lead Temperature          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (Soldering, rosel)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| **                        | and the second |

\*Operating above absolute maximuum ratings may damage the device.

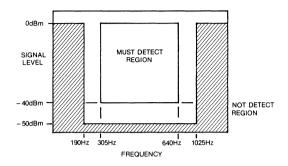

### AC Characteristics (0 °C $\leq$ TA 70 °C, V<sub>DD</sub> = 5V $\pm$ 10%)

| Parameter                | Conditions                                           | Symbol | Min                | Max   | Units |

|--------------------------|------------------------------------------------------|--------|--------------------|-------|-------|

| Frequency for Detect     | _                                                    | F      | ± (0.015*<br>Fo+5) | —     | Hz    |

| Amplitude for Detect     | each tone                                            | A      | - 25               | 0     | dBm   |

|                          |                                                      |        | 0.123              | 2.191 | Vpp   |

| Amplitude for No Detect  | _                                                    | An     |                    | - 35  | dBm   |

|                          |                                                      |        | -                  | 0.039 | Vpp   |

| Twist Tolerance          | $TW = \frac{high tone}{low tone}$                    | TW     | 6                  |       | dB    |

| Third MF Tone Reject Amp | relative to highest tone                             | Т3     | - 15               |       | dB    |

| Noise Tolerance          | $N_n = {one false operation \over 2500 (10 digits)}$ | Nn     | 20                 |       | dB    |

| 60 HZ Tolerance          | same as above                                        | N60    | 81                 |       | dBrn  |

|                          |                                                      |        | 0.777              |       | Vpp   |

| 180 HZ Tolerance         | same as above                                        | N180   | 68                 |       | dBrn  |

|                          |                                                      |        | 0.174              |       | Vpp   |

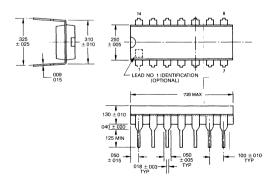

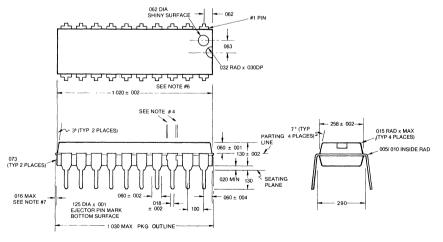

Notes<sup>.</sup>

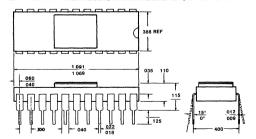

- Package to frame mismatch not greater than .004" in any direction. To be measured in molded strip form

- 2 Side to side and end to end package mismatch (top half vs bottom half alignment) not greater than 003"

- Leads to be within .010" of true position

Shoulder intrusion/protrusion not greater

- than 002"

Raised letters spelling "Singapore" on one bottom ejector pin area. Letters must not

- extend out past bottom package surface and are to be less than 003" in depth Letters to be arranged in a radial pattern with at least a 040" character size

- 6 Maximuum flash between leads to be 003" 7 End flash not to exceed 010" Total package

- length including this flash must be maintained as shown on drawing 8 Package surface to be matte finish (23-27

- charmilles) except for ejector pin, index notch and pin 1 identification markings

The "PRELIMINARY" designation on an SSi data sheet indicates that the product is not yet released for production. The specifications are subject to change, are based on design goals or preliminary part evaluation, and are not guaranteed. SSi should be consulted for current information before using this product. No responsibility is assumed by SSi for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of SSi. SSi reserves the right to make changes in specifications at any time and without notice.

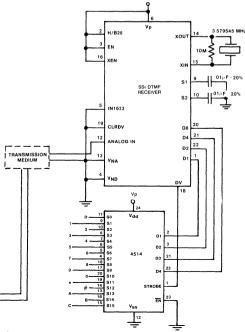

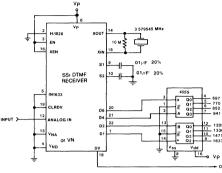

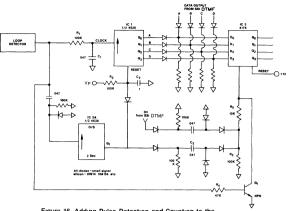

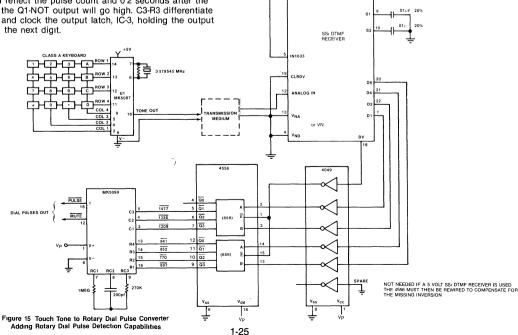

Application Guide for SSi Monolithic Dual-Tone Multi-Frequency (DTMF) Receivers

The SSi integrated DTMF Receivers are complete Touch-Tone detection systems. Each can operate in a stand-alone mode for the majority of telecommunications applications, thereby providing the most economical implementation of DTMF signaling systems possible. Each combines precision active filters and analog circuits with digital control logic on a mono-lithic CMOS integrated circuit. SSi DTMF Receiver use is straightforward and the external component requirements are minimal. This application guide describes device operation, performance, system requirements, and typical application circuits for the SSi DTMF Receiver circuits

### How the SSi DTMF Circuits Work

### **General Description of Operation**

The task of a DTMF Receiver is to detect the presence of a valid tone pair on a telephone line or other transmission medium. The presence of a valid tone pair indicates a single dialed digit; to generate a valid digit sequence, each tone pair must be separated by a valid pause.

The following table gives the established Bell system standards for a valid tone pair and a valid pause:

| One Low-Group Tone<br>— and —          | 697 or 770 or 852 or 941 Hz                                                                  |

|----------------------------------------|----------------------------------------------------------------------------------------------|

| One High-Group Tone                    | 1209 or 1336 or 1477 or<br>1633 Hz                                                           |

| Frequency Tolerance<br>Amplitude Range | $f_0 \pm (15\% + 2 Hz)$<br>- 24 dBm $\le A \le + 6 dBm @ 600\Omega$<br>(Dynamic Range 30 dB) |

| Relative Amplitude<br>(Twist)          | $-8 \text{ dB} \le \frac{\text{High-Group Tone}}{\text{Low-Group Tone}} \le +4 \text{ dB}$   |

| Duration                               | 40ms or longer                                                                               |

| Inter-tone Pauses                      | 40ms or longer                                                                               |

|                                        |                                                                                              |

The SSi DTMF Receivers meet or exceed these standards.

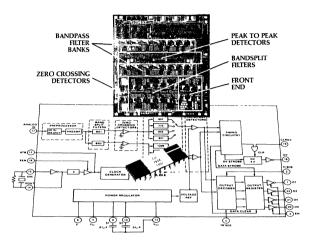

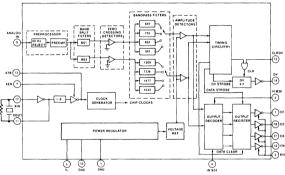

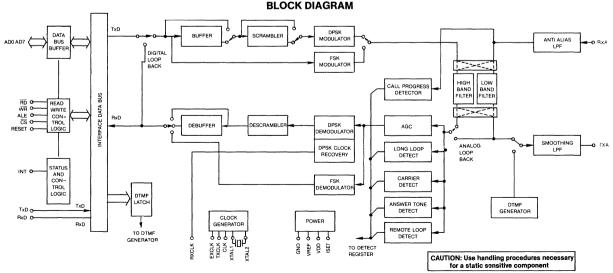

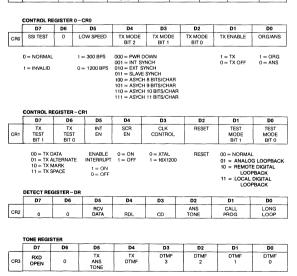

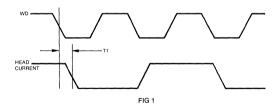

Similar device architecture is used in all the SSi DTMF Receivers. Figure 1 shows the SSI 202 Block Diagram. In general terms, the detection scheme is as follows: The input signal is pre-filtered and then split into two bands, each of which contains only one DTMF tone group. The output of each band-split filter is amplified and limited by a zero-crossing detector. The limited signals, in the form of square waves, are passed through tone frequency band pass filters. Digital logic is then used to provide detector sampling and determine detection validity, to present the digital output data in the correct format, and to provide device timing and control.

### **Detailed Description of Operation**

### Noise and Speech Immunity

The two largest problems confronting a DTMF Receiver are:

- Distinguishing between valid tone pairs (or pauses) and other stray signals (or speech) that contain valid tone pair frequencies.

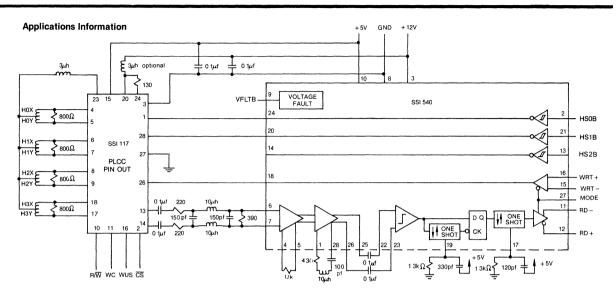

- Detecting valid tone pairs in the presence of noise, which is typically found in the telephone (or other transmission medium) environment.