# INTEGRATED CIRCUITS FOR -

# COMMUNICATIONS PRODUCTS

LAN/WAN • PCMCIA • Datacom/FAX Modems • Wireless Communication •

## Modem Device Sets • Ethernet Media Access Controllers • UARTs

# 1993 DATA BOOK

# The Company

Silicon Systems' Santa Cruz facility, site of six-inch wafer fabrication line.

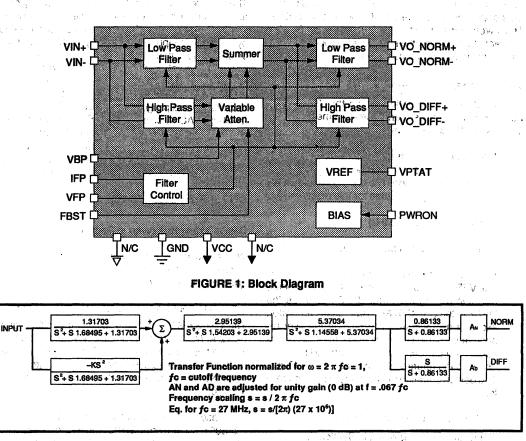

Dilicon Systems specializes in the design and manufacture of application-specific, mixed-signal integrated circuits (MSICs®). If offers a sophisticated line of custom and standard ICs aimed primarily at the storage, communications and automotive products marketplace.

The company, which is headquartered in California, 30 miles south of Los Angeles, was founded in 1972 as a design center. It soon entered into manufacturing and today has two fabrication sites in California and approximately 2,000 employees worldwide. Additional operations include assembly and test facilities in California and Singapore and design engineering centers in California as well as in Tokyo and Singapore.

Reliability and quality are built into Silicon Systems' products through the use of statistical problem solving techniques, analytical controls, and other quantitative methods. The company is committed to the goal of customer satisfaction through the on-time delivery of defect-free products that meet or exceed the customer's expectations and requirements. This statement reflects the corporate quality mission and contains key elements instrumental in attaining true customer satisfaction. Listed in the back of this publication is a worldwide network of sales representatives and distributors ready to serve you.

silicon system

© Copyright 1992 Silicon Systems, Inc. All rights reserved. Product and company names listed are trademarks of their respective companies.

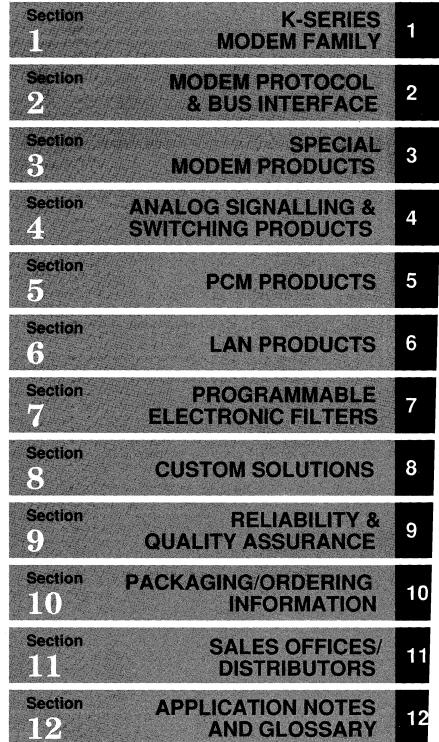

# Table of Contents

Target, Advanced and Preliminary Information

In this data book the following conventions are used in designating a data sheet "Target," "Advanced" or "Preliminary":

#### Target Specification-

The target specification is intended as an initial disclosure of specification goals for the product. Product is in first stages of design cycle.

#### Advance Information-

Indicates a product still in the design cycle, undergoing testing processes, and any specifications are based on design goals only. Do not use for final design.

#### Preliminary Data-

Indicates a product not completely released to production. The specifications are based on preliminary evaluations and are not guaranteed. Small quantities are available, and Silicon Systems should be consulted for current information.

## Index

#### Page #

| Table of Contents                     |      |

|---------------------------------------|------|

| Product Index                         |      |

| Numerical Product Index               |      |

| Discontinued Parts List               | V    |

| Disclaimer                            | V    |

| Product Selector Guide                | VI   |

| Portable/Wireless Custom Capabilities | VIII |

#### Section 1. K-SERIES SINGLE-CHIP MODEM FAMILY

| K-Series Modem | Family Introduction                               |       |

|----------------|---------------------------------------------------|-------|

| 73K212/K212L   | Bell 212A/103 Single-Chip Modem                   |       |

| 73K221/K221L   | CCITT V.22, V.21 Single-Chip Modem                |       |

| 73K222/K222L   | V.22, V.21, Bell 212A Single-Chip Modem           | 1-51  |

| 73K222U        | Single-Chip Modem with UART                       |       |

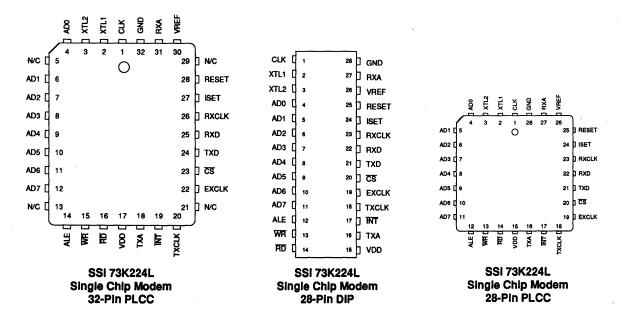

| 73K224L        | V.22bis Single-Chip Modem                         | 1-117 |

| 73K302L        | Bell 212A, 103, 202 Single-Chip Modem             |       |

| 73K312L        | CCITT V.23, V.21 Single-Chip Modem                | 1-177 |

| 73K321L        | CCITT V.23, V.21 Single-Chip Modem                |       |

| 73K322L        | CCITT V.23, V.22, V.21 Single-Chip Modem          |       |

| 73K324L        | CCITT V.22bis, V.22, V.21, V.23 Single-Chip Modem | 1-253 |

### Section 2. MODEM PROTOCOL & BUS INTERFACE PRODUCTS

|     | 73D2240      | V.22bis 2400 Bit/s Low Power Modern Device Set          | 2-1 |

|-----|--------------|---------------------------------------------------------|-----|

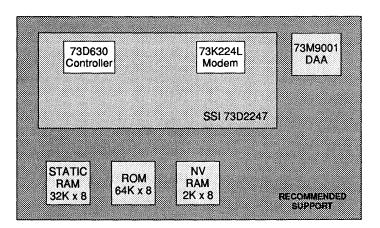

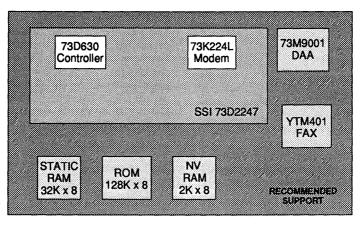

|     | 73D2247      | MNP5, V.42bis, Datacom Modem Device Set2                | -25 |

|     | 73D2247-F    | MNP5, V.42bis, Datacom/FAX Modern Device Set            | -33 |

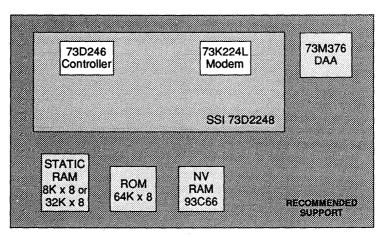

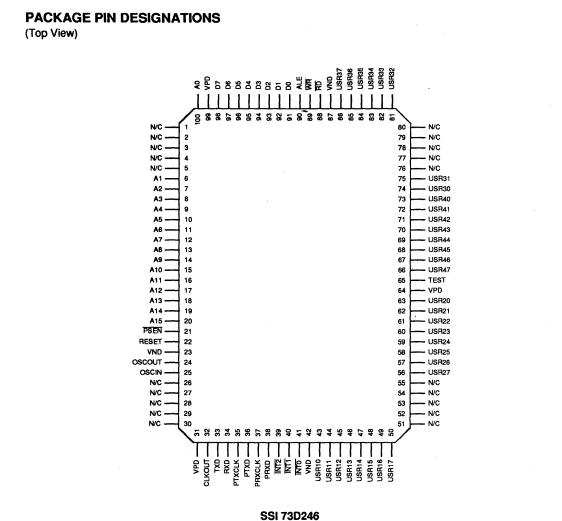

| NEW | 73D2248/2348 | MNP5 Datacom Modem Device Set2                          | -41 |

|     | 73M450L/     | Universal Asynchronous Receiver/Transmitter2-           | -51 |

|     | 1450/2450    |                                                         |     |

|     | 73M550/      | Universal Asynchronous Receiver/Transmitter with FIFOs2 | -85 |

|     | 1550/2550    |                                                         |     |

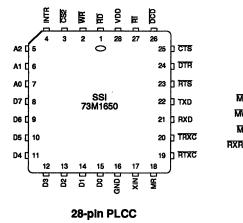

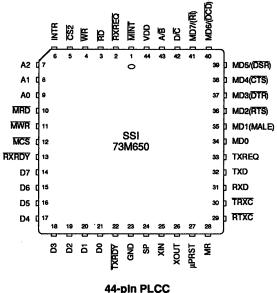

|     | 73M650/1650  | Serial Packet Controller                                | *   |

#### Section 3. SPECIAL MODEM PRODUCTS

| 73M214 | Modem Analog Front End                  | * |

|--------|-----------------------------------------|---|

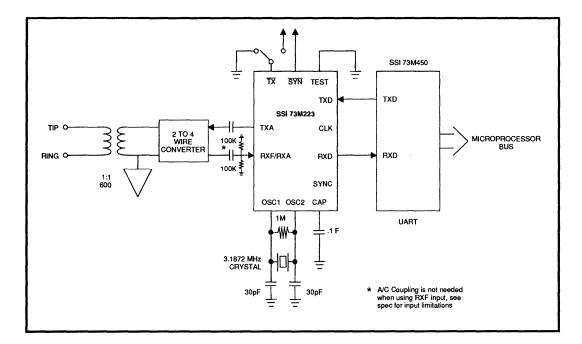

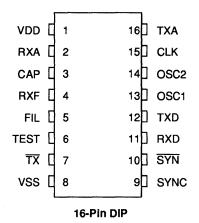

| 73M223 | 1200 Baud FSK Modem                     | 1 |

| 73M376 | K-Series Integrated Line Interface Unit | 7 |

#### Section 4. ANALOG SIGNALLING & SWITCHING PRODUCTS

| 4-1            |

|----------------|

|                |

| 4-17           |

| 4-25           |

| See Section 12 |

|                |

|                |

|                |

|                |

\* Data Sheet available upon request

#### Page #

### Section 5. PCM PRODUCTS

-

|             | 78P233A                                                      | DS-1 Line Interface                                                               |                         |

|-------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------|

|             | 78P234                                                       | 2048 KBit/s PCM Interface Unit                                                    |                         |

|             | 78P236                                                       | DS-3 Line Interface                                                               | 5-25                    |

|             | 78P2361                                                      | STS-1 Line Interface                                                              |                         |

|             | 78P2362                                                      | 34.368 Mbit/s Line Interface                                                      |                         |

|             |                                                              | ard Description                                                                   |                         |

|             | 78P300                                                       | T1/E1 Short-Haul Transceiver with Receive Jitter Attenuation                      |                         |

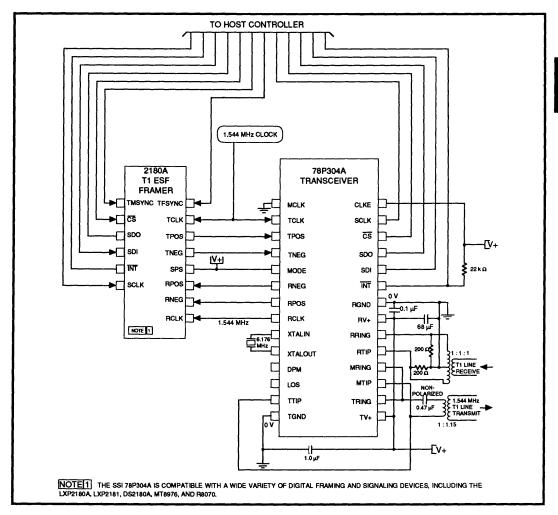

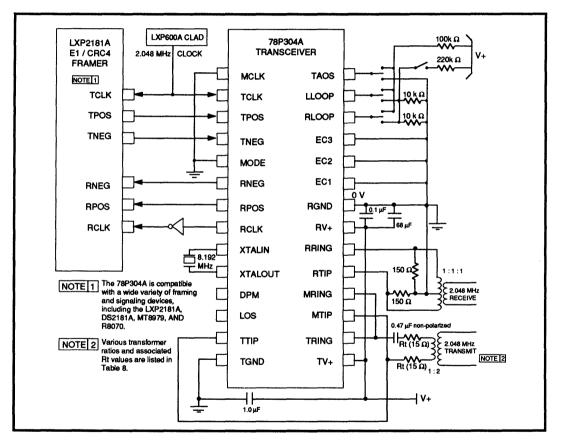

| NEW         | 78P304A                                                      | Low-Power T1/E1 Integrated Short Haul Transceiver with Receive Jitter Attenuation | 5-71                    |

|             | 78P7200                                                      | DS-3 Line Interface with Receive Equalizer                                        | 5-89                    |

|             |                                                              |                                                                                   |                         |

| Section 6.  | LAN PRODUC                                                   | TS                                                                                |                         |

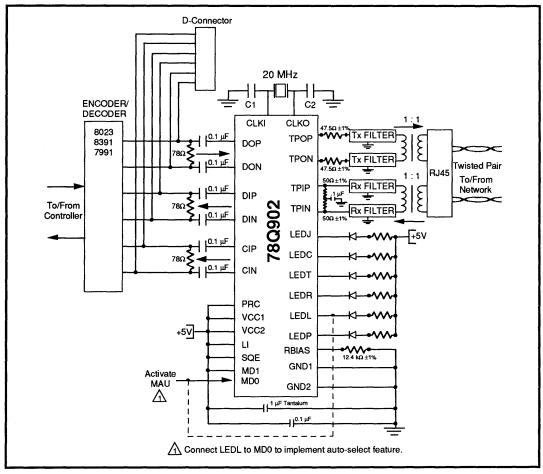

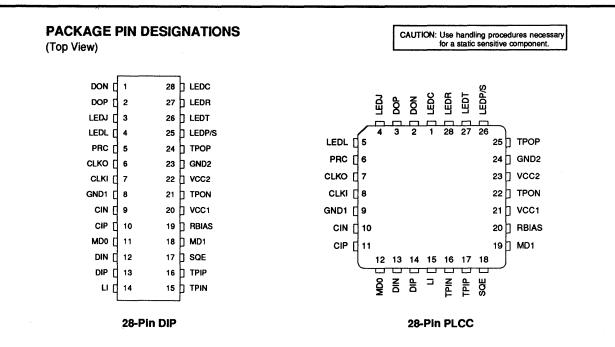

|             | 78Q902                                                       | Ethernet Twisted-Pair Media Attachment Unit                                       | 6-1                     |

|             | 78Q903                                                       | 10Base-T Hub Transceiver                                                          | *                       |

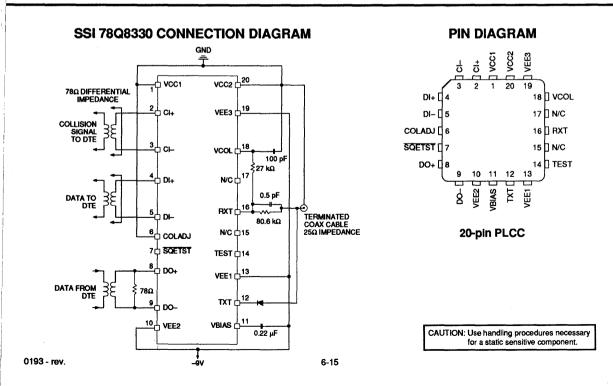

|             | 78Q8330/8330A                                                | Ethernet Coaxial Transceiver                                                      | 6-15                    |

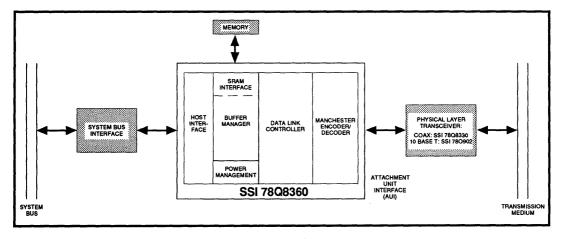

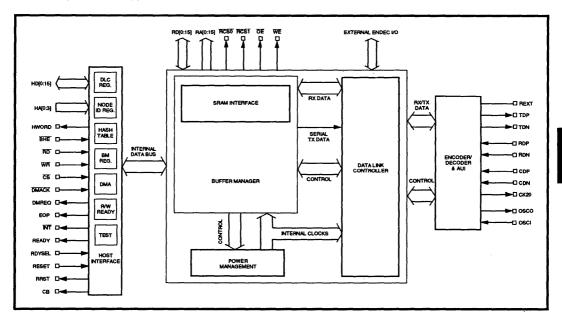

|             | 78Q8360                                                      | Ethernet Controller/ENDEC Combo                                                   | 6-27                    |

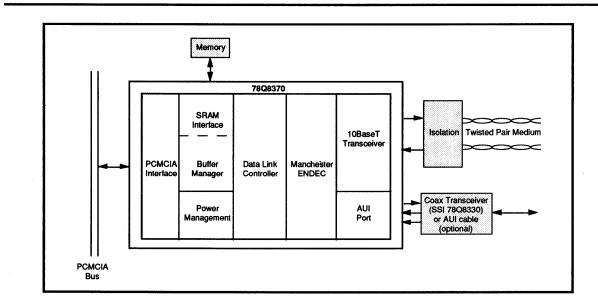

| NEW         | 78Q8370                                                      | PCMCIA Ethernet Combo                                                             | 6-63                    |

| Section 7.  |                                                              | BLE ELECTRONIC FILTERS                                                            |                         |

| Jechon 7.   | • • • • • • • • • • • • • • • • • • • •                      |                                                                                   | <b>.</b>                |

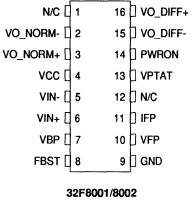

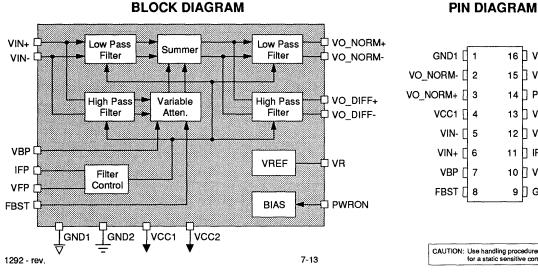

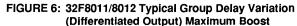

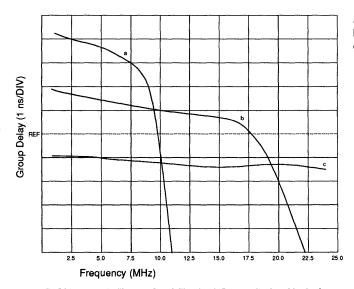

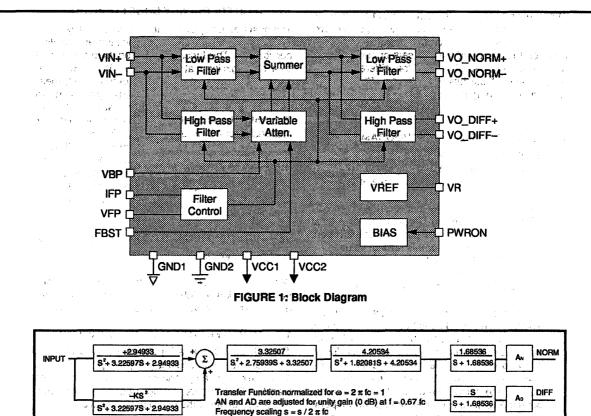

|             | 32F8001/8002                                                 | Low-Power Programmable Electronic Filter                                          |                         |

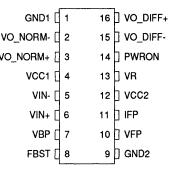

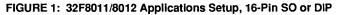

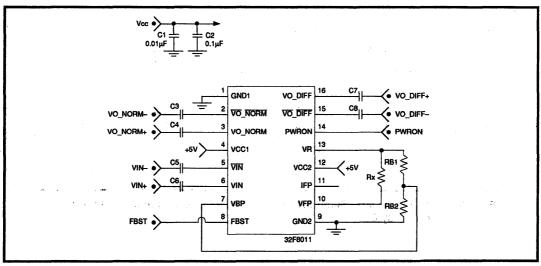

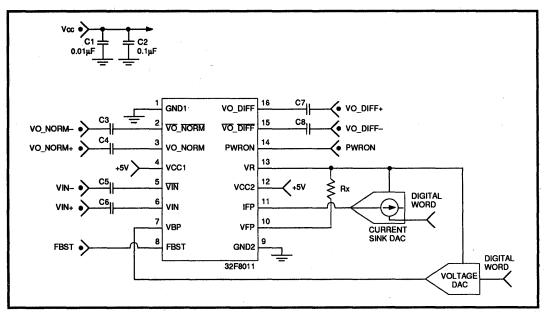

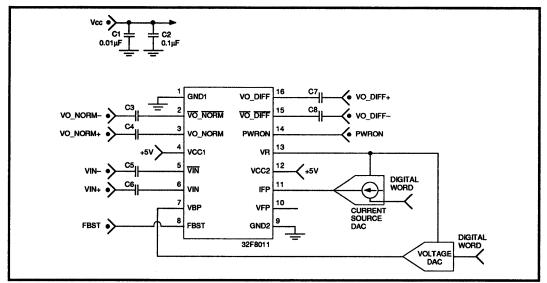

|             | 32F8011/8012                                                 | Programmable Electronic Filter                                                    |                         |

|             | 32F8020/8022                                                 | Programmable Electronic Filter                                                    |                         |

| NEW         |                                                              | / Low-Power Programmable Electronic Filter                                        | 7-25                    |

|             | 8021/8023                                                    |                                                                                   |                         |

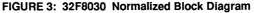

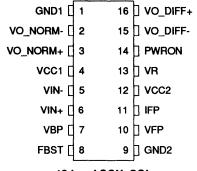

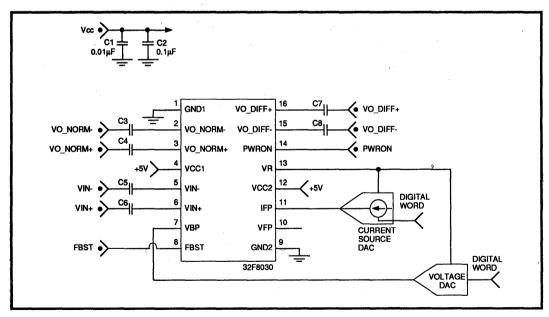

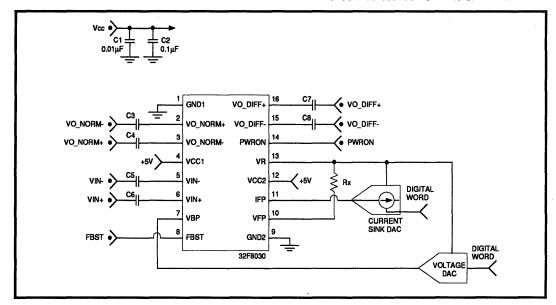

|             | 32F8030                                                      | Programmable Electronic Filter                                                    |                         |

| NEW         | 32F8101/8102/                                                | Low-Power Programmble Electronic Filter                                           | 7-47                    |

|             | 8103/8104                                                    |                                                                                   |                         |

|             | 32F8120                                                      | Low-Power Programmable Electronic Filter                                          |                         |

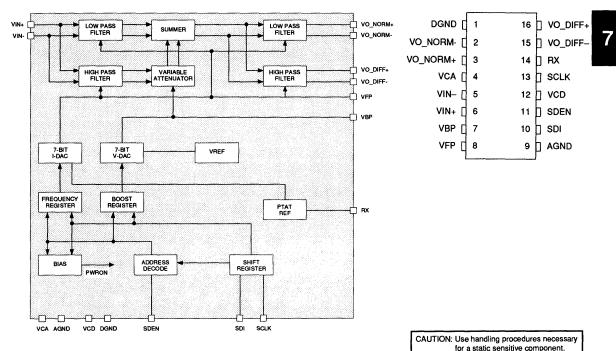

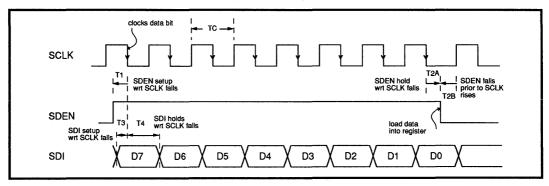

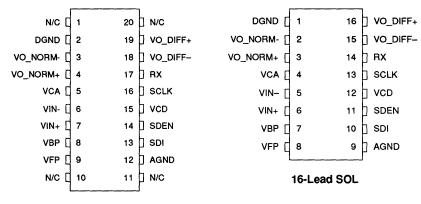

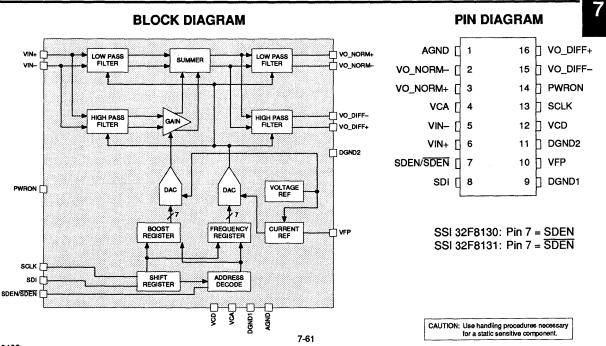

|             | 32F8130/8131                                                 | Low-Power Programmable Electronic Filter                                          | 7-61                    |

| Contion 9   | CUSTON SOL                                                   | UTIONS                                                                            |                         |

| Section 8.  |                                                              |                                                                                   |                         |

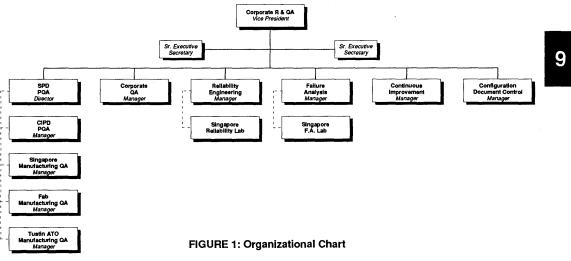

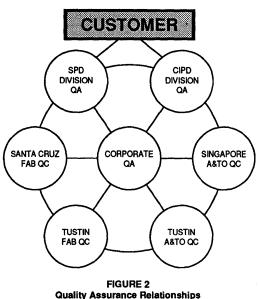

| Section 9.  | QUALITY ASS                                                  |                                                                                   | 9-0                     |

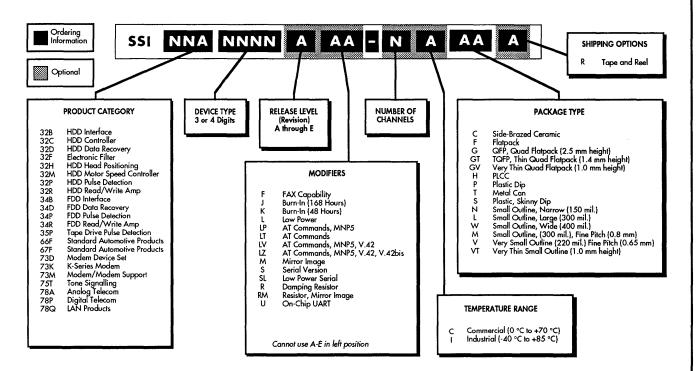

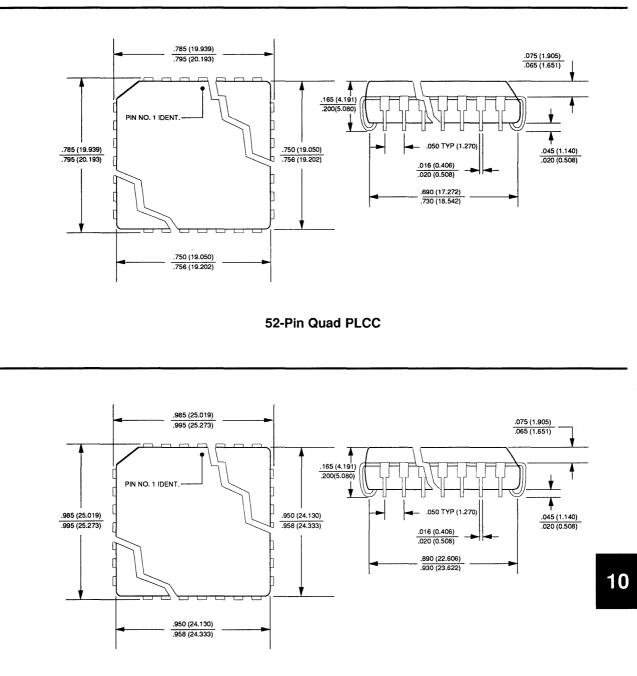

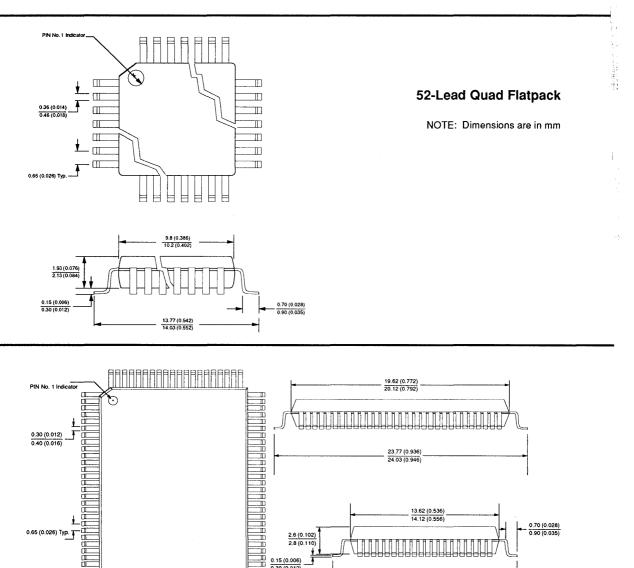

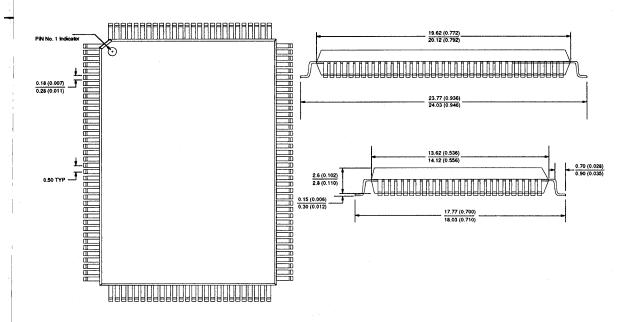

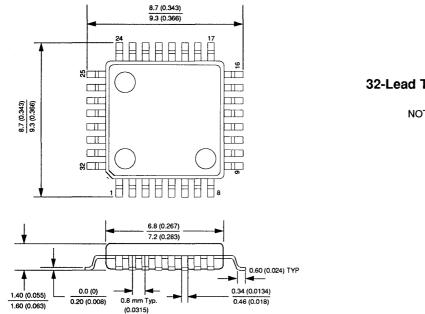

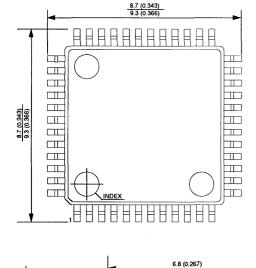

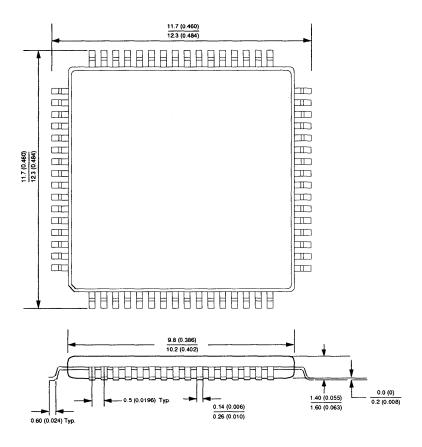

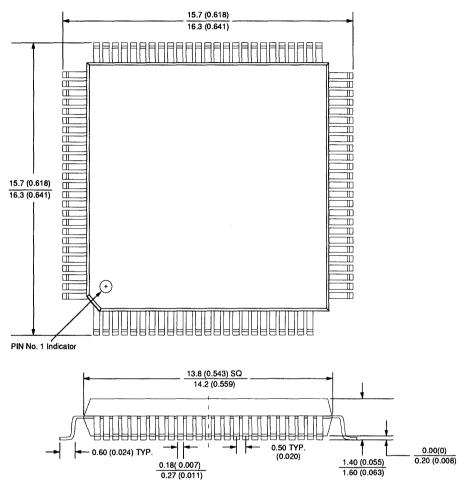

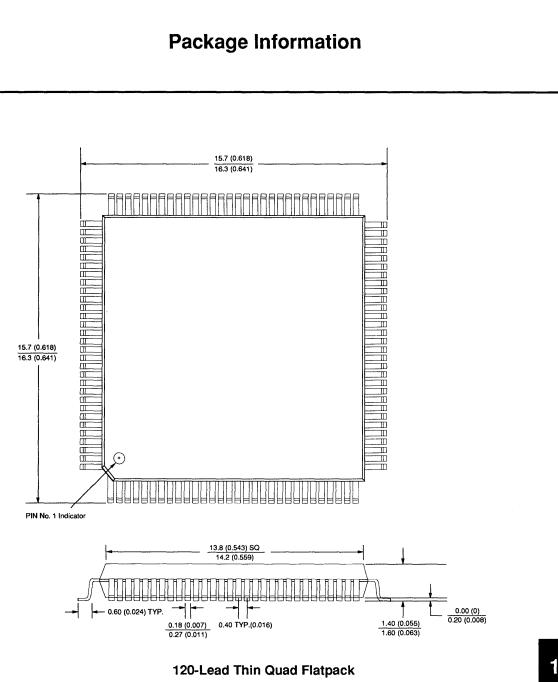

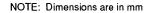

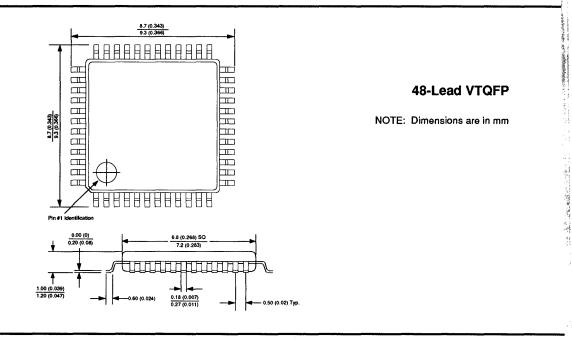

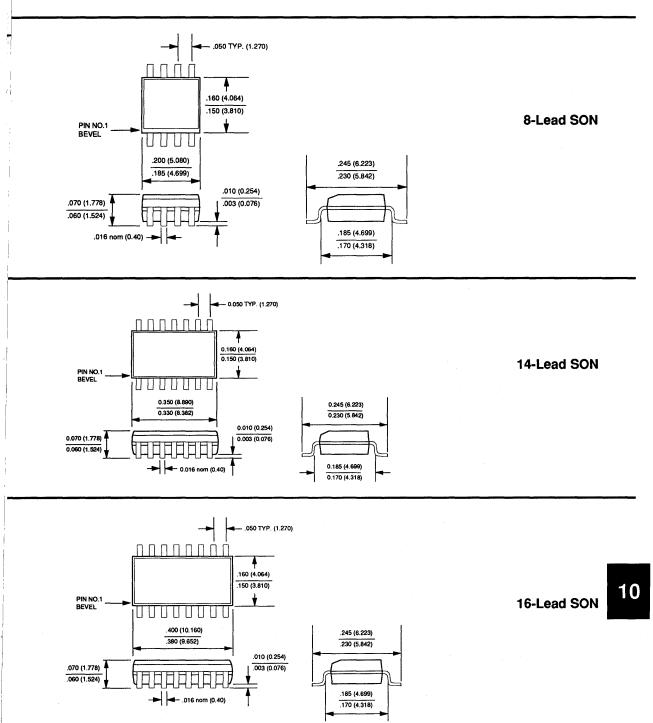

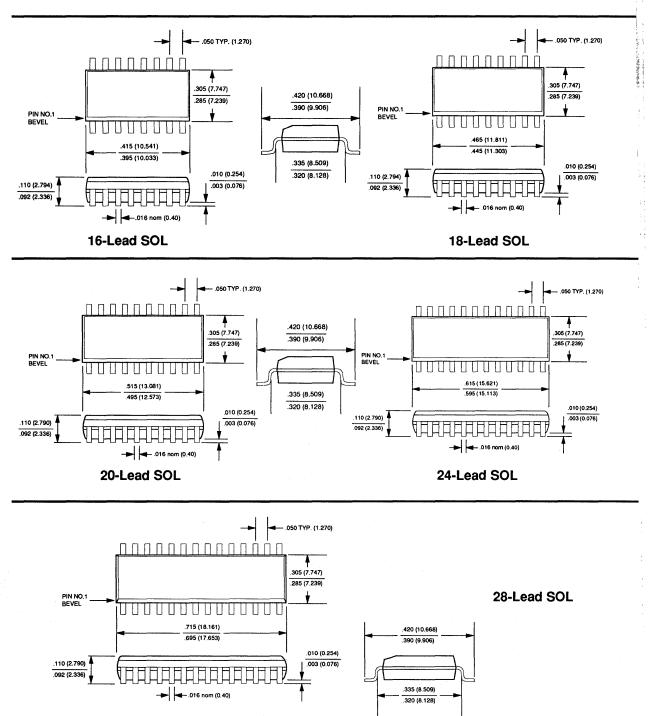

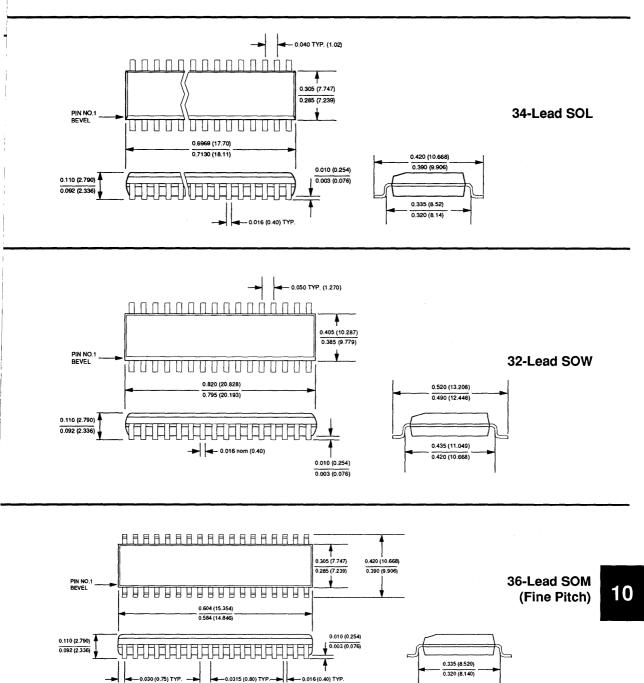

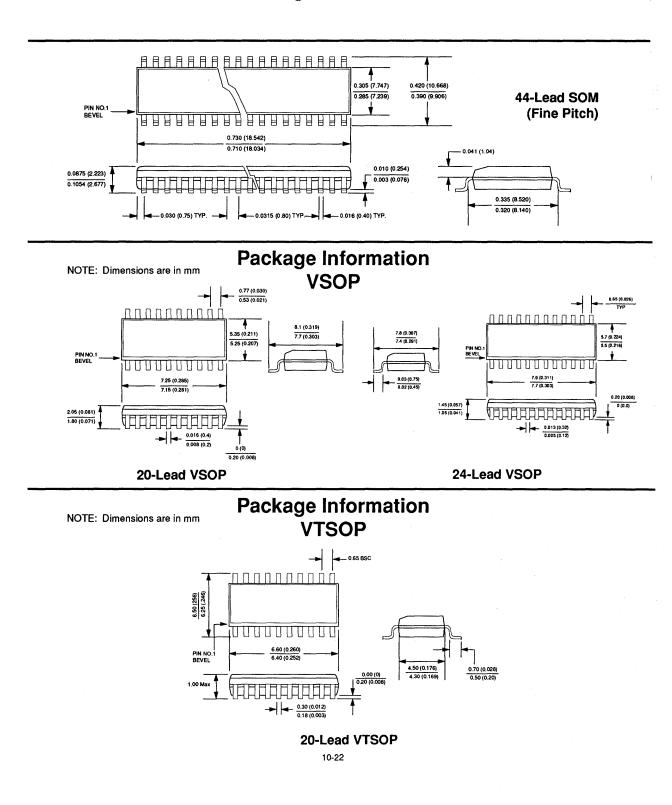

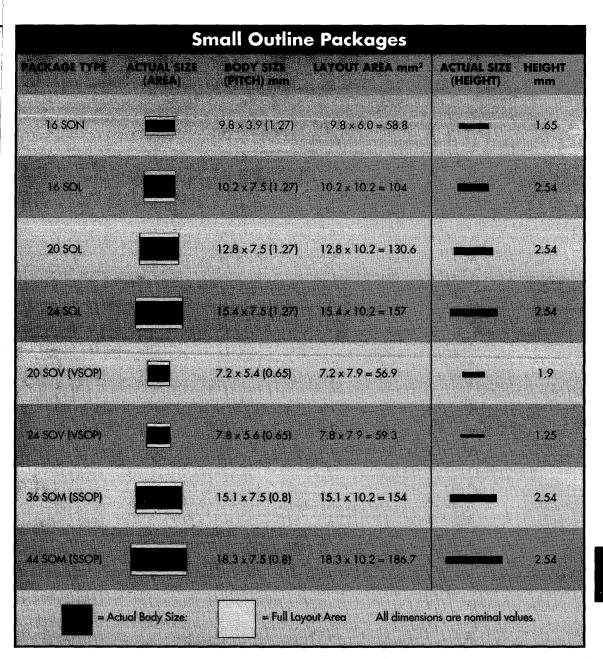

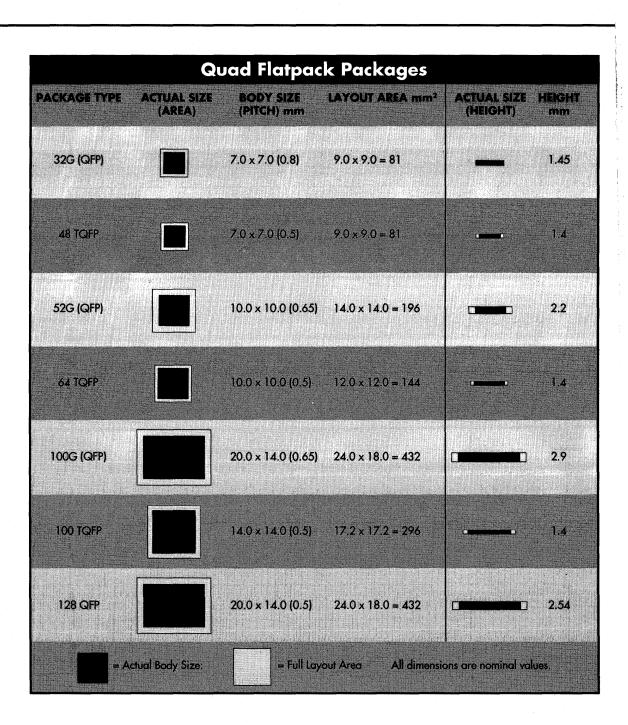

| Section 10. | PACKAGING/C                                                  | DRDERING INFORMATION                                                              |                         |

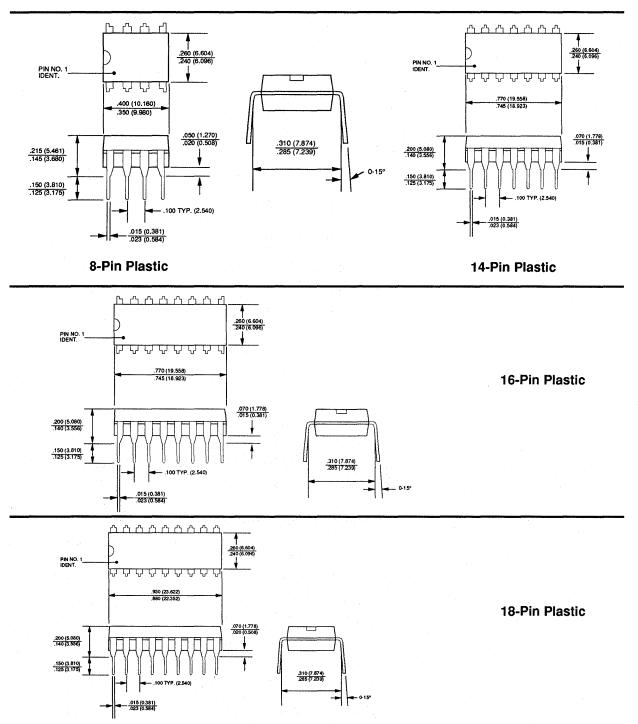

|             | Package Index                                                |                                                                                   | 10-0                    |

|             |                                                              | on                                                                                |                         |

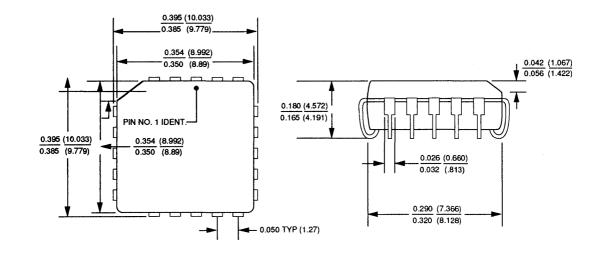

|             |                                                              | 16 and 18 Pins                                                                    |                         |

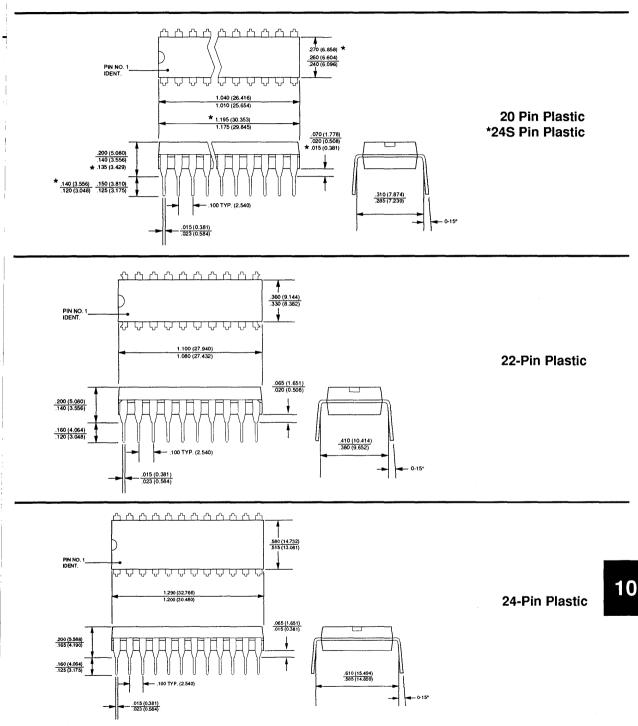

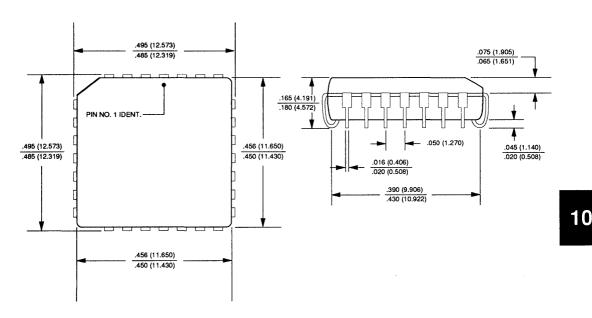

|             |                                                              | , 24 and 24S Pins                                                                 |                         |

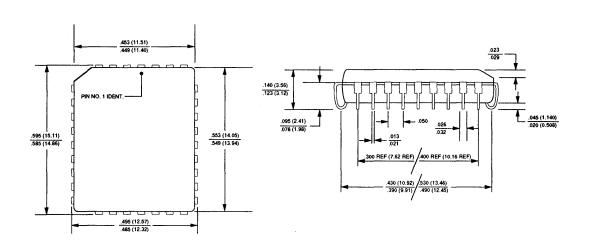

|             |                                                              | and 40 Pins                                                                       |                         |

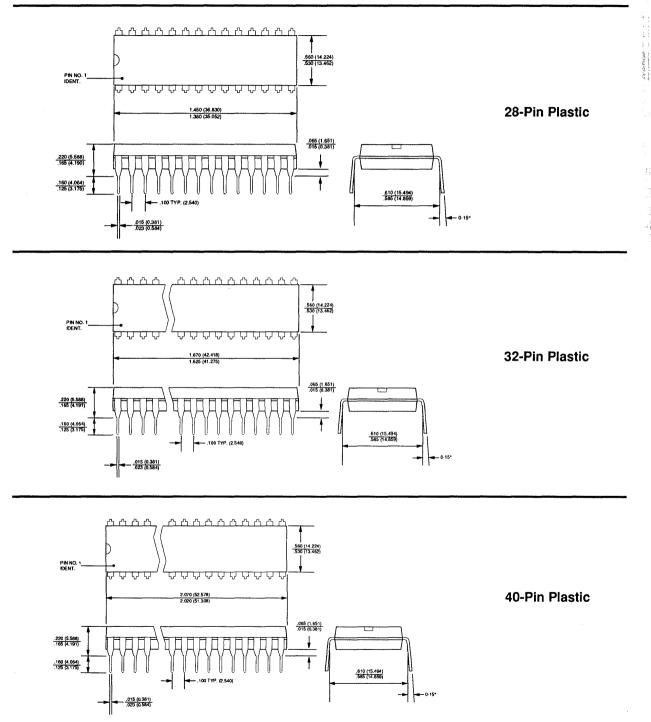

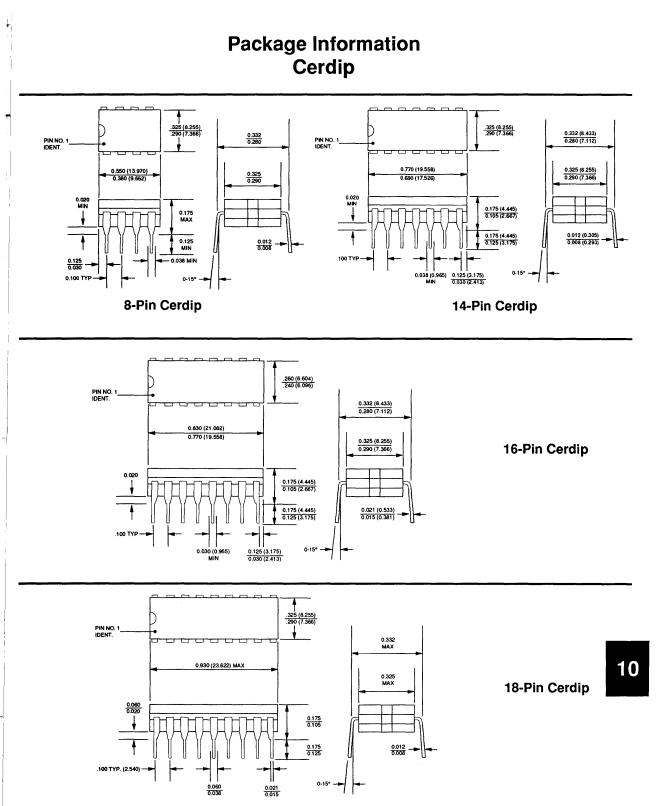

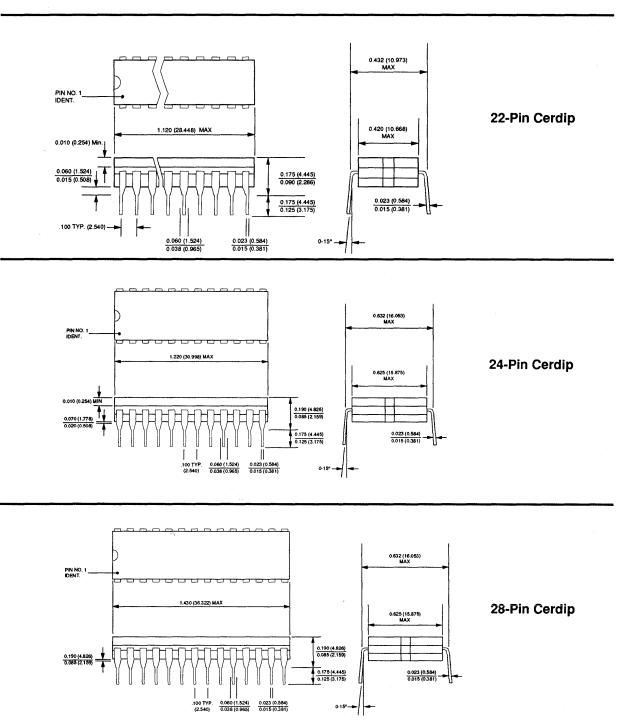

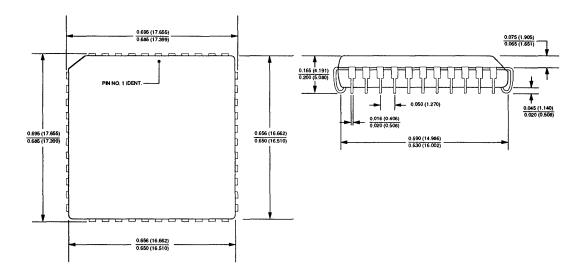

|             |                                                              | nd 18 Pins                                                                        |                         |

|             |                                                              | 28 Pins                                                                           |                         |

|             |                                                              | and 28 Leads                                                                      |                         |

|             |                                                              | and 44 Leads                                                                      |                         |

|             |                                                              | and 68 Leads                                                                      |                         |

|             |                                                              | FP) 52, 100 Leads                                                                 |                         |

| NEW         |                                                              | FP) 128 Leads                                                                     |                         |

| 19 5 90     |                                                              | * (TQFP) 32, 48 Leads                                                             |                         |

|             |                                                              | * (TQFP) 64 Leads                                                                 |                         |

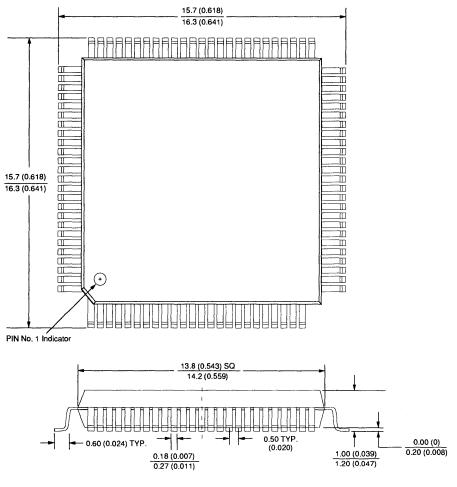

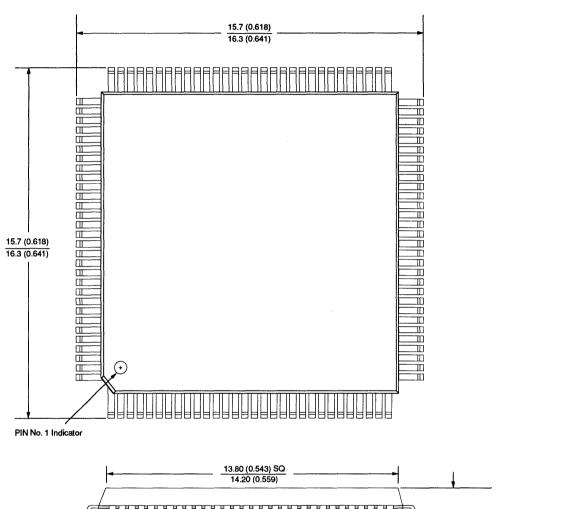

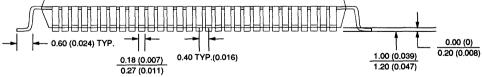

| NEW         |                                                              | * (TQFP) 100 Leads                                                                |                         |

| NEW         |                                                              |                                                                                   |                         |

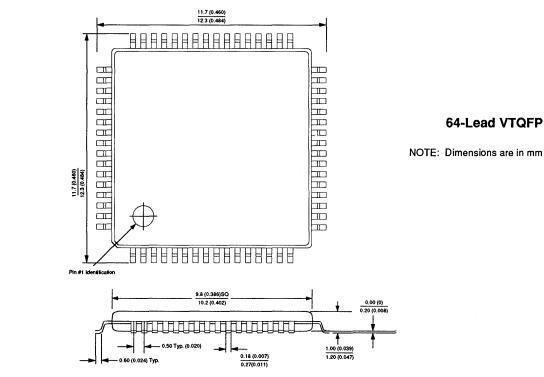

| NEW         | Von Thin Oued E                                              | x (TQFP) 120 Leads<br>latpack (VTQFP) 48 and 64 Leads                             | 10-15                   |

| NEW         | Very This Quad Fl                                            | latpack (VTQFP) 48 and 64 Leaos                                                   | 10-17                   |

| NEW         |                                                              | latpack (VTQFP) 100 Leads                                                         |                         |

| 1.4 52 9.8  |                                                              |                                                                                   |                         |

|             |                                                              | Leads                                                                             |                         |

|             | - SUL 10, 18, 20, 24                                         | 4 and 28 Leads                                                                    |                         |

|             |                                                              |                                                                                   | 10 04                   |

|             | SOL 34 Leads                                                 |                                                                                   |                         |

|             | SOL 34 Leads<br>SOW 32 Leads                                 |                                                                                   | 10-21                   |

|             | SOL 34 Leads<br>SOW 32 Leads<br>SOM 36 Leads                 |                                                                                   | 10-21<br>10-21          |

|             | SOL 34 Leads<br>SOW 32 Leads<br>SOM 36 Leads<br>SOM 44 Leads |                                                                                   | 10-21<br>10-21<br>10-22 |

NEW NEW - is sold and

| Section 11. | SALES OFFICES/DISTRIBUTORS                                  |  |  |  |  |  |  |

|-------------|-------------------------------------------------------------|--|--|--|--|--|--|

| Section 12. | APPLICATIONS NOTES AND GLOSSARY                             |  |  |  |  |  |  |

|             | K-Series Application Notes                                  |  |  |  |  |  |  |

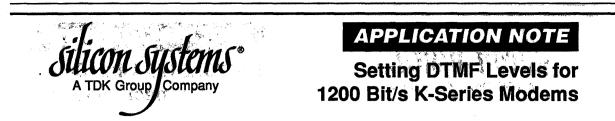

|             | Setting DTMF Levels for 1200 Bit/s K-Series Modems          |  |  |  |  |  |  |

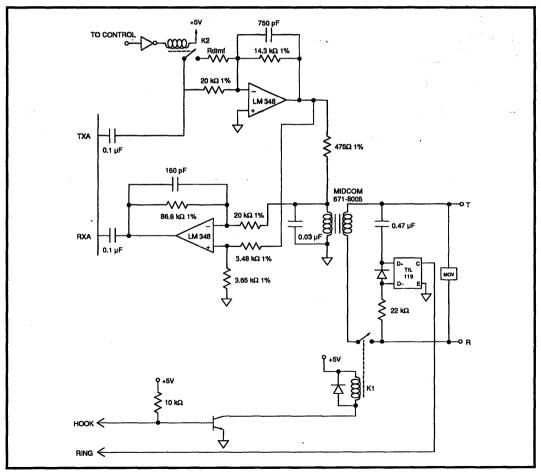

|             | - SSI 73K212A High Speed Connect Sequence                   |  |  |  |  |  |  |

|             | V.22 & V.22bis Connect Sequences                            |  |  |  |  |  |  |

|             | - Remote Loop Handshake Sequence                            |  |  |  |  |  |  |

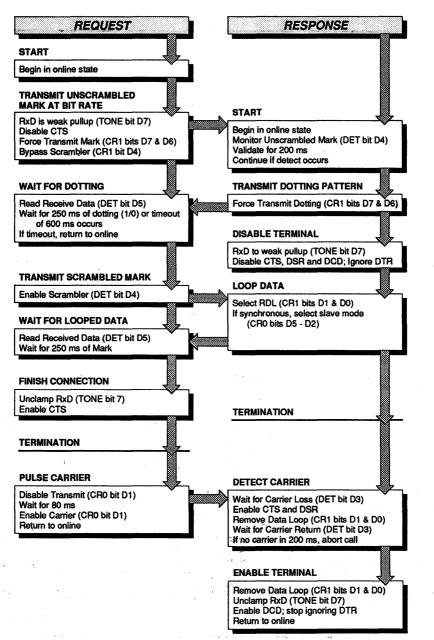

|             | - SSI 73K224L Retrain at 2400 bit/s                         |  |  |  |  |  |  |

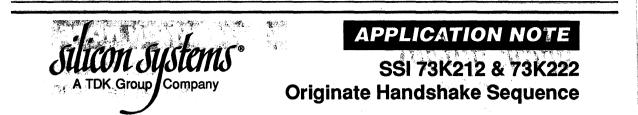

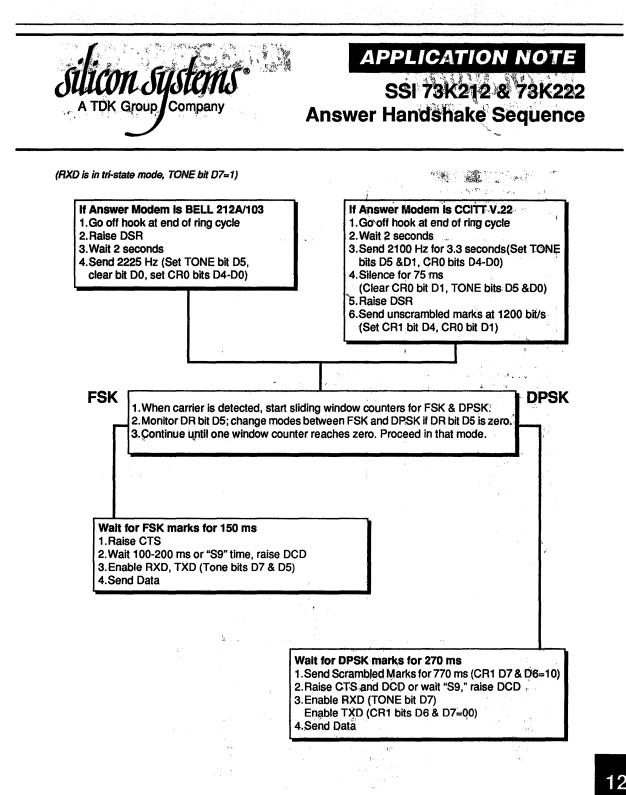

|             | - SSI 73K212, 73K222 Originate & Answer Handshake Sequences |  |  |  |  |  |  |

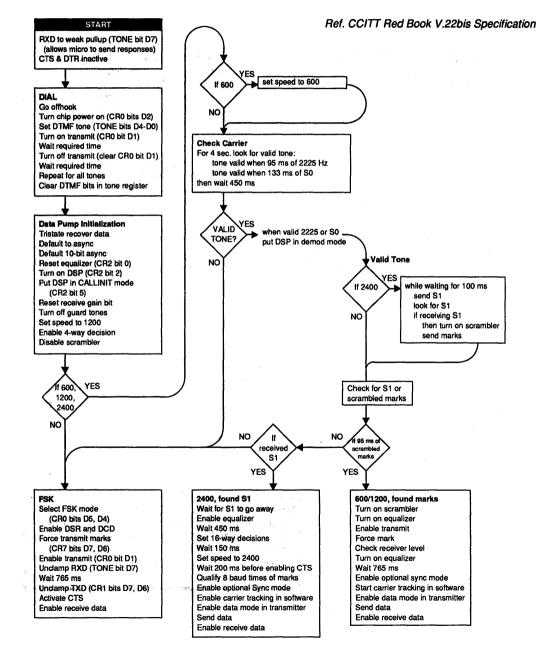

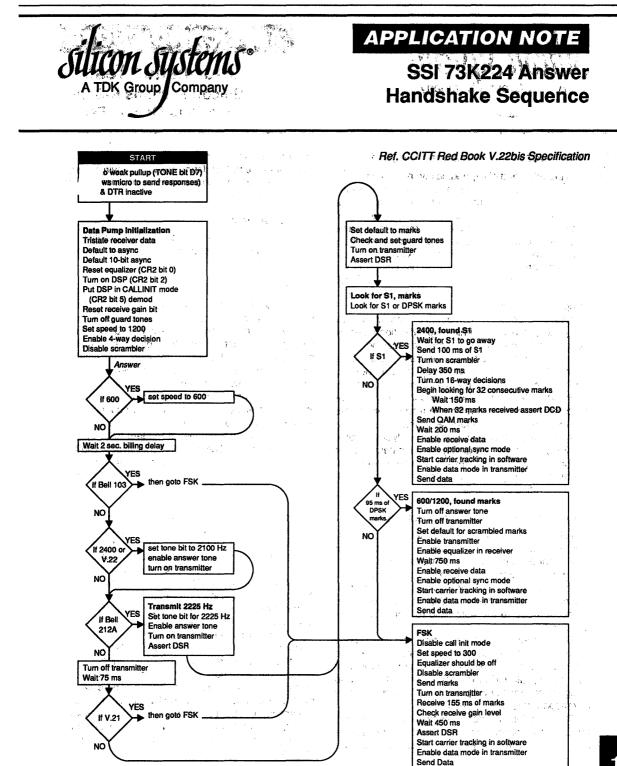

|             | - SSI 73K224L Originate & Answer Handshake Sequences        |  |  |  |  |  |  |

|             | - Modern Performance Testing                                |  |  |  |  |  |  |

|             | - Troubleshooting the Modem Design12-16                     |  |  |  |  |  |  |

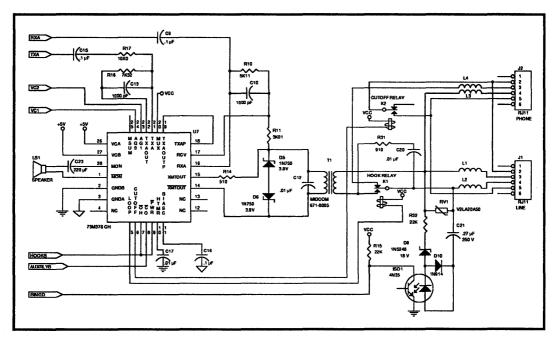

| NEW         | 73M376 Integrated Line Interface Application Note           |  |  |  |  |  |  |

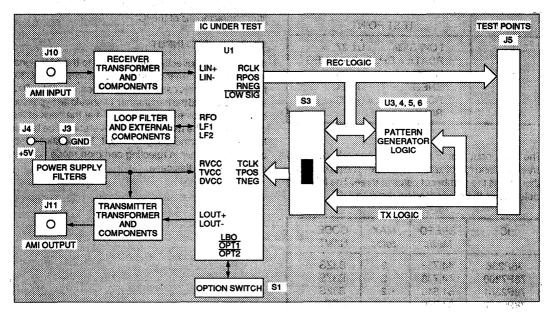

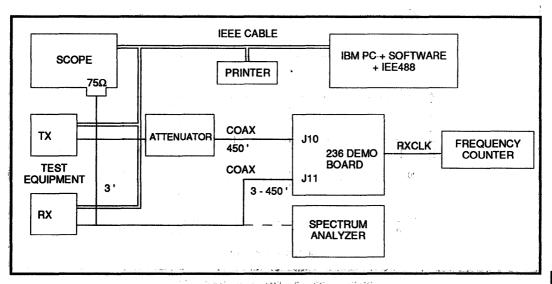

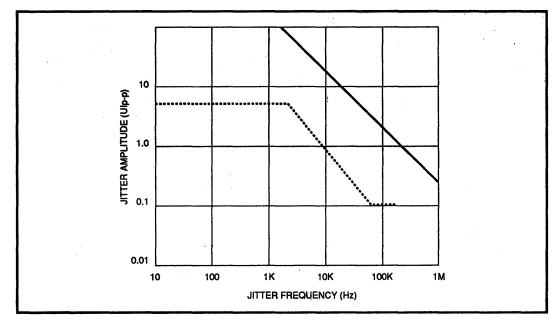

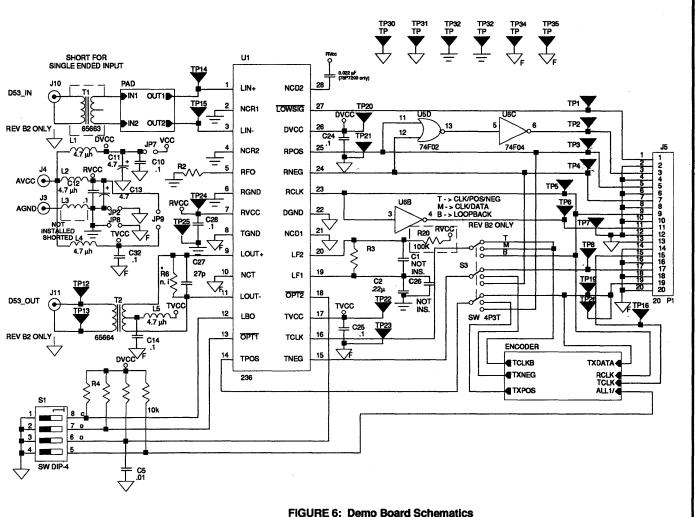

|             | 78P236/2361/2362/7200 Demo Board Application Note           |  |  |  |  |  |  |

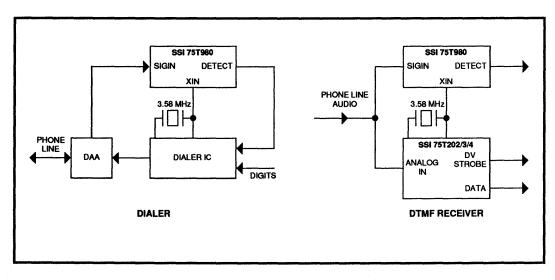

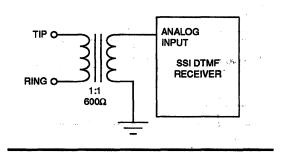

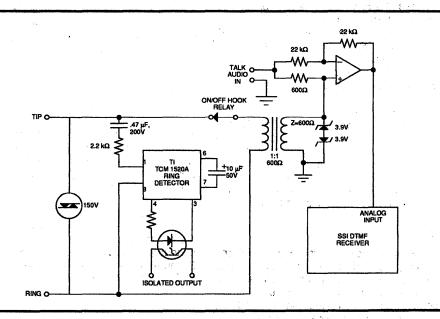

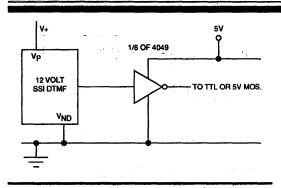

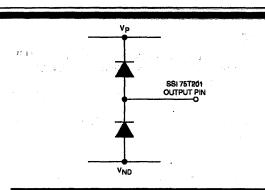

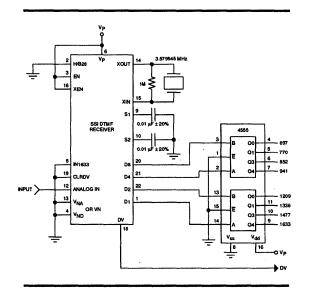

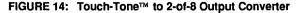

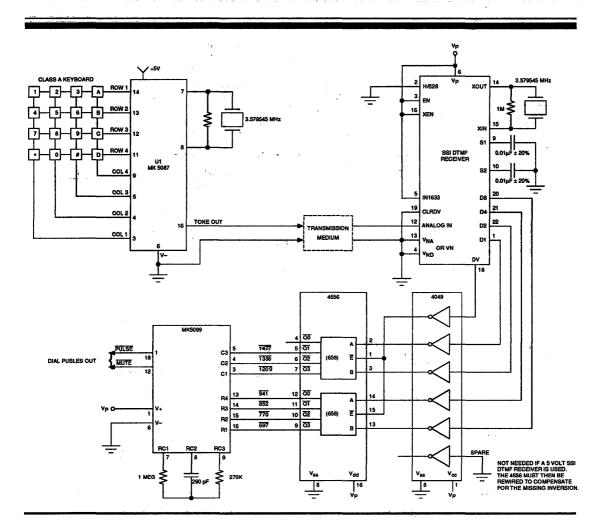

|             | DTMF Receiver Application Guide                             |  |  |  |  |  |  |

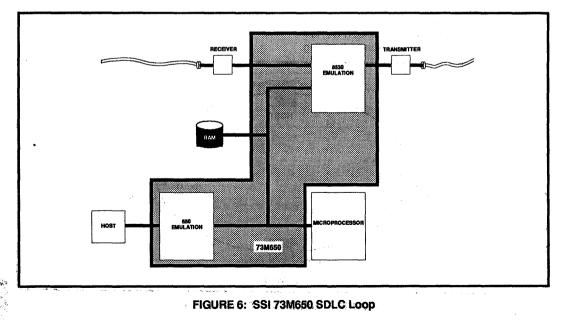

| NEW         | Serial Packet Controller Application Note                   |  |  |  |  |  |  |

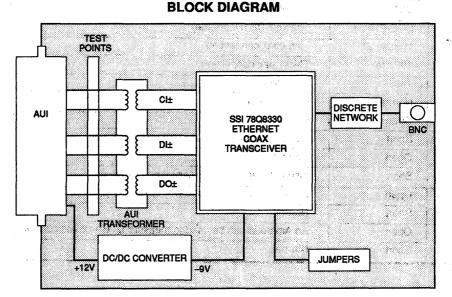

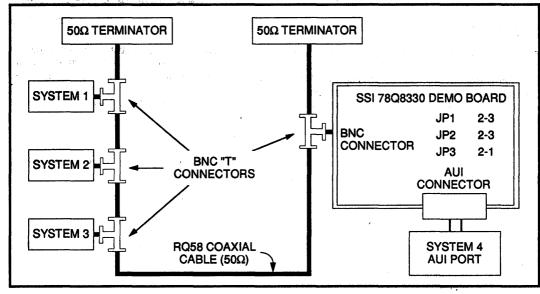

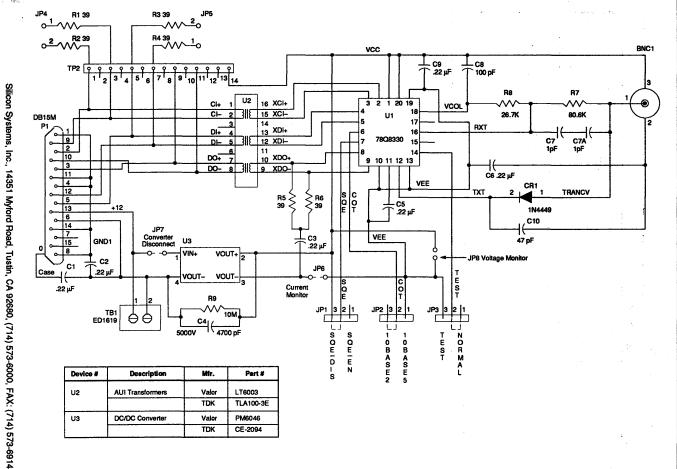

| NEW         | 78Q8330 Demo Board Application Note                         |  |  |  |  |  |  |

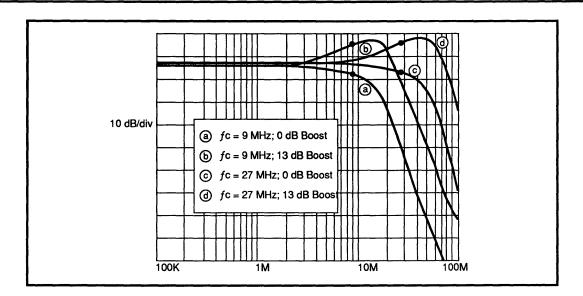

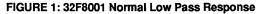

| NEW         | 32F8001 Application Note                                    |  |  |  |  |  |  |

| NEW         | 32F8011 Application Note                                    |  |  |  |  |  |  |

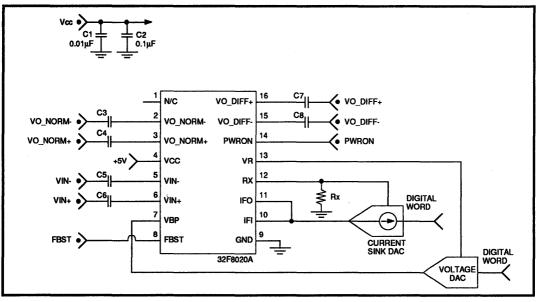

| NEW         | 32F8020A Application Note                                   |  |  |  |  |  |  |

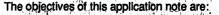

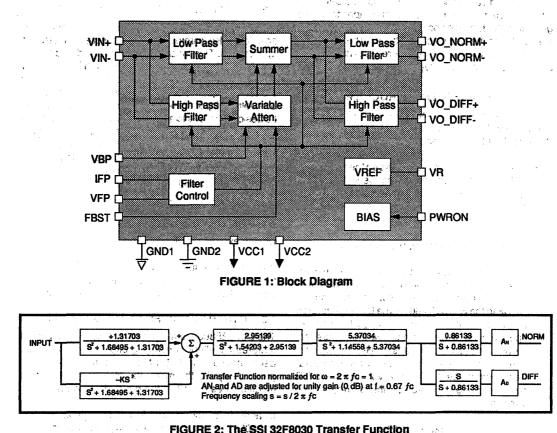

| NEW         | 32F8030 Application Note                                    |  |  |  |  |  |  |

|             | GLOSSARY                                                    |  |  |  |  |  |  |

|             | Voiceband Modern Standards Reference Chart                  |  |  |  |  |  |  |

## Numerical Index

| SSI Device Numbers       | Page # | SSI Device Numbers | Page # |

|--------------------------|--------|--------------------|--------|

| 32F8001/8002             | 7-1    | 73M376             |        |

| 32F8011/8012             | 7-13   | 73M450L/1450/2450  |        |

| 32F8020/8022             | *      | 73M550/1550/2550   |        |

| 32F8020A/8022A/8021/8023 | 7-25   | 73M650/1650        | *      |

| 32F8030                  | 7-37   | 75T201             |        |

| 32F8101/8102/8103/8104   | 7-47   | 75T202/203         |        |

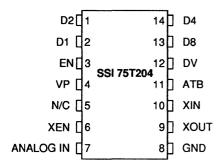

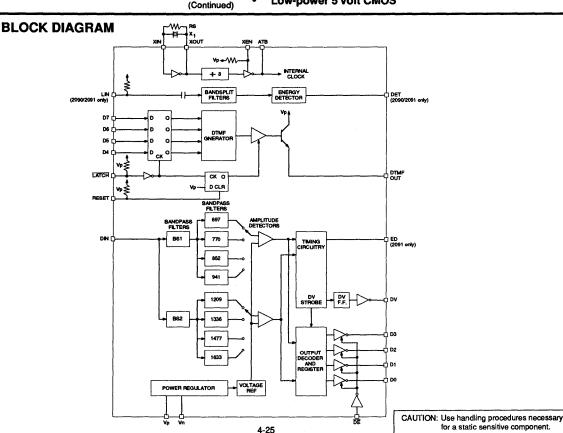

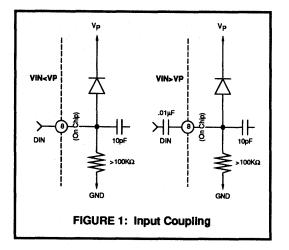

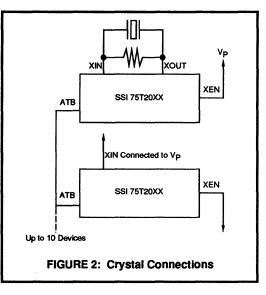

| 32F8120                  |        | 75T204             | 4-17   |

| 32F8130/8131             | 7-61   | 75T2089/2090/2091  |        |

| 73D2240                  | 2-1    | 75T980             |        |

| 73D2247                  | 2-25   | 78A093A/B          | 4-39   |

| 73D2247-F                | 2-33   | 78A207             |        |

| 73D2248/2348             | 2-41   | 78P233A            | 5-1    |

| 73K212/212L              | 1-1    | 78P234             | 5-13   |

| 73K221/221L              | 1-25   | 78P236             | 5-25   |

| 73K222/222L              | 1-51   | 78P2361            | 5-35   |

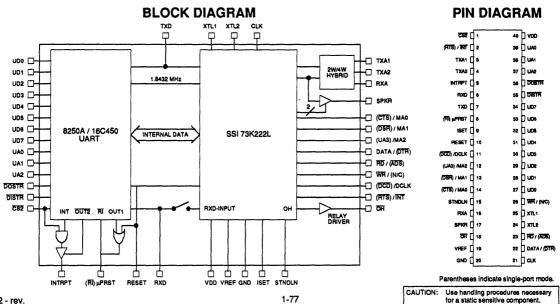

| 73K222U                  | 1-77   | 78P2362            | 5-45   |

| 73K224L                  | 1-117  | 78P300             | 5-55   |

| 73K302L                  | 1-149  | 78P304A            | 5-71   |

| 73K312L                  | 1-177  | 78P7200            | 5-89   |

| 73K321L                  | 1-201  | 78Q902             | 6-1    |

| 73K322L                  |        | 78Q903             | *      |

| 73K324L                  | 1-253  | 78Q8330/8330A      | 6-15   |

| 73M214                   | *      | 78Q8360            | 6-27   |

| 73M223                   | 3-1    | 78Q8370            | 6-63   |

\*Data Sheet available upon request

### **Discontinued Parts List**

The following parts are no longer supplied or supported by Silicon Systems. Please note alternate sources.

| Part #           | Alternate Source | Part #      | Alternate Source    |

|------------------|------------------|-------------|---------------------|

| SSI 32F8000      | SSI 32F8001      | SSI 75T957  | Teltone Corporation |

| SSI 73D2180      | None             | SSI 75T981  | Teltone Corporation |

| SSI 73D2404      | None             | SSI 75T982  | Teltone Corporation |

| SSI 73D2420/2421 | None             | SSI 78P8050 | Rockwell            |

|                  |                  | SSI 78P8060 | Rockwell            |

### DISCLAIMER

All products listed herein and subsequently sold by Silicon Systems, Inc. are covered by the warranty, limitation of liability and patent indemnification provisions reflected in the Silicon Systems Order Acknowledgement Form only. Silicon Systems, Inc. makes no warranty, express or implied, statutory or by description regarding the information set forth herein and/or freedom from patent infringement. Silicon Systems, Inc. reserves the right to discontinue production, change specifications and prices at any time and without notice.

Applications requiring mechanical and electrical parameters outside of the published specifications are not recommended without additional review and acceptance by Silicon Systems, Inc. Silicon Systems, Inc. further assumes no responsibility for the use of any integrated circuit technology other than integrated circuit technology embodied in a Silicon Systems, Inc. product. These products are not authorized for use as components in life support devices or systems, No patents or licenses regarding the integrated circuit technology herein are implied unless otherwise stated.

### **COMMUNICATION PRODUCTS REFERENCE**

|                  | 8212<br>8103 | 8302      | Y.AL       | V 23 | CCHT<br>17:22 |   |                                                                                                |      |                                         |

|------------------|--------------|-----------|------------|------|---------------|---|------------------------------------------------------------------------------------------------|------|-----------------------------------------|

| -SERIES SINGLE   | CHIP MOD     | em famil  | Y          |      |               |   |                                                                                                |      |                                         |

| SSI 73K212       | x            |           |            |      |               |   | Bell 212A/103                                                                                  | +12V | 28 DIP, 28 PLCC                         |

| SSI 73K212S 🕜    | ×            |           |            |      |               |   | 73K212 with serial interface only                                                              | +12V | 22 DIP                                  |

| SSI 73K212L      | x            |           |            |      |               |   | Low Power 73K212                                                                               | +5V  | 28 DIP, 28 PLCC                         |

| SSI 73K212SL     | x            |           |            |      |               |   | 73K212L with serial interface only                                                             | +5V  | 22 DIP                                  |

| SSI 73K221       |              |           | . <b>X</b> |      | ×             |   | CCITT V.22/V.21                                                                                | +12V | 22, 28 DIP, 28 PLCC                     |

| SSI 73K221S      |              |           | x          |      | x             |   | 73K221 with serial interface only                                                              | +12V | 22 DIP                                  |

| SSI 73K221L      |              |           | x          |      | ×             |   | Low Power 73K221                                                                               | +5V  | 22, 28 DIP, 28 PLCC                     |

| SSI 73K221SL     |              |           | x          |      | ×             |   | 73K221L with serial interface only                                                             | +5V  | 22 DIP                                  |

| SSI 73K222       | x            |           | x          |      | x             |   | Bell 212A/103, CCITT V.22/V.21                                                                 | +12V | 22, 28 DIP, 28 PLC                      |

| SSI 73K222S      | x            |           | x          |      | ×             |   | 73K222 with serial interface only                                                              | +12V | 22 DIP                                  |

| SSI 73K222L      | x            |           | x          |      | x             |   | Low Power 73K222                                                                               | +5V  | 22, 28 DIP, 28 PLCC                     |

| SSI 73K222SL     | . <b>x</b>   |           | ×          |      | x             |   | 73K222L with serial interface only                                                             | +5V  | 22 DIP                                  |

| SSI 73K222U      | ×            |           | ×          |      | ×             |   | 73K222L with 16C450 UART                                                                       | +5V  | 40 DIP, 44 PLCC                         |

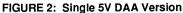

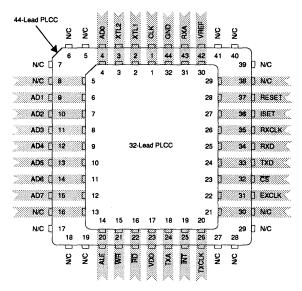

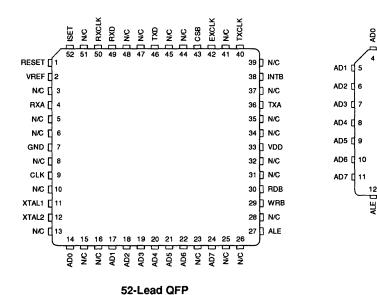

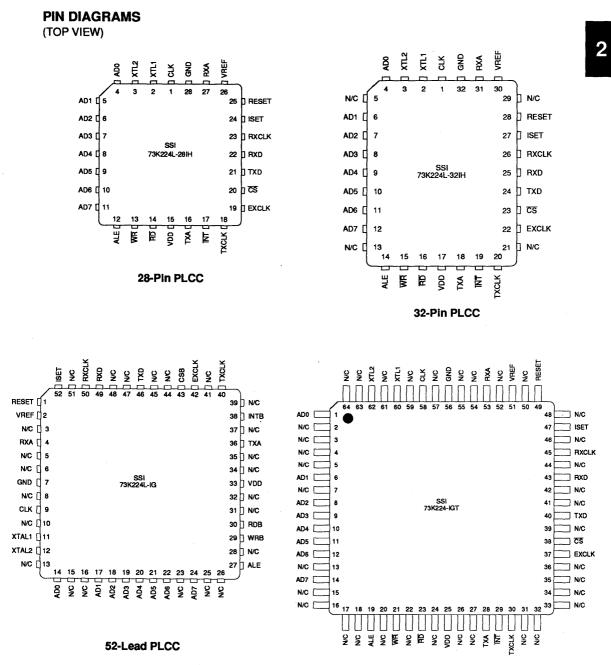

| SSI 73K224L      | x            |           | x          |      | ×             | × | Bell 212A/103, CCITT V.22bis/V.22/V.21                                                         | +5V  | 28 DIP, 28, 32 PLCC,<br>52 QFP, 64 TQFP |

| SSI 73K224SL     | x            |           | x          |      | x             | x | 73K224L with serial interface                                                                  | +5V  | 22 DIP                                  |

| SSI 73K302L      | x            | x         |            |      |               |   | Bell 212A/202/103                                                                              | +5V  | 28 DIP, 28 PLCC                         |

| SSI 73K302SL     | X            | x         |            |      |               |   | Bell 212A/202/103; serial interface only                                                       | +5V  | 22 DIP                                  |

| SSI 73K312L      | B103         | ×         | ×          | ×    |               |   | BELL 202/103; CCITT V.21/V.23                                                                  | +5V  | 28 DIP, 28 PLCC,<br>52 QFP, 64 TQFP     |

| SSI 73K321L      |              |           | x          | x    |               |   | CCITT V.23/V.21                                                                                | +5V  | 28 DIP, 28 PLCC                         |

| SSI 73K321SL     |              |           | ×          | x    |               |   | 73K321L with serial interface only                                                             | +5V  | 22 DIP                                  |

| SSI 73K322L      |              |           | x          | ×    | ×             |   | CCITT V.23/V.22/V.21                                                                           | +5V  | 28 DIP, 28 PLCC                         |

| SSI 73K322SL     |              |           | x          | x    | x             |   | 73K322L with serial interface only                                                             | +5V  | 22 DIP                                  |

| SSI 73K324L      | B212         |           | ×          | ×    | ×             | × | CCITT V.22bis/V.22/V.23/V.21                                                                   | +5V  | 28 DIP, 28, 32 PLCC<br>52 QFP, 64 TQFP  |

| MODEM PROTOG     | ol produ     | CTS/ DEVI | CE SETS    |      |               |   |                                                                                                |      |                                         |

| SSI 73D2240      | x            | ×         | ×          | x    |               |   | Modern Device Set w/ AT (73K224L based design)                                                 | +5V  | Various DIP & PLCC                      |

| SSI 73D2247/Z    | ×            | ×         | ×          | ×    | ×             | × | Modern Device Set w/ AT, MNP 48.5                                                              | +5V  | Various DIP & PLCC                      |

| SSI 73D2248/2348 |              |           |            | X    | X             | X | Modern Device Set w/AT, MNP<br>can be ordered with or upgraded to 9600 bit/s send/receive FAX. | +5V  | Various QFP & TQFP                      |

≤

| Device Number     | Circuit Function                    | Features                                                           | Power       | Available Packages       |

|-------------------|-------------------------------------|--------------------------------------------------------------------|-------------|--------------------------|

| SPECIAL MODEM PR  | ODUCTS                              |                                                                    |             |                          |

| SSI 73M214        | 2400 bit/s Modem Filter             | V.22bis/V.22/V.21, Bell 212/103 modes                              | ±5V         | 28 DIP, PLCC             |

| SSI 73M223        | 1200 bit/s Modem IC                 | Compact HDX V.23 modem                                             | +5V         | 16 DIP, 16 SOL           |

| SSI 73M376        | Integrated Line Interface           | The active components of a DAA in a chip used on 73M9001           | +5V         | 28 PLCC, 24 VSOP         |

| ANALOG SIGNALLIN  | IG AND SWITCHING PRODUCTS           |                                                                    |             |                          |

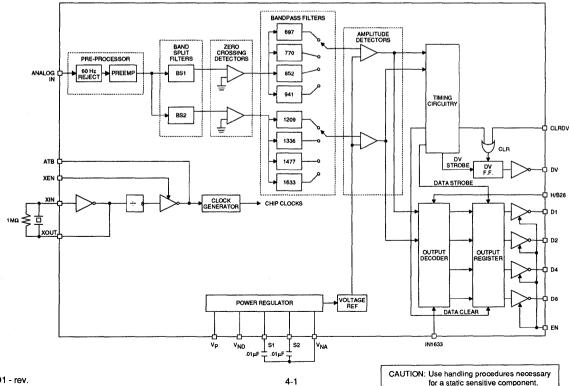

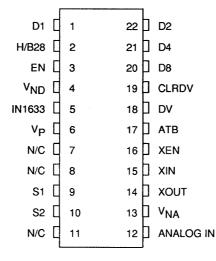

| SSI 75T201        | Integrated DTMF Receiver            | Binary coded 2-of-8 output                                         | +12V        | 22 DIP                   |

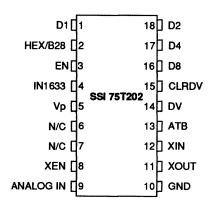

| SSI 75T202        | Integrated DTMF Receiver            | Low power, binary output                                           | +5V         | 18 DIP                   |

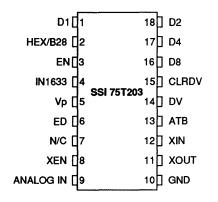

| SSI 75T203        | Integrated DTMF Receiver            | Early detect, binary output                                        | +5V         | 18 DIP                   |

| SSI 75T204        | Integrated DTMF Receiver            | Low power, binary output                                           | +5V         | 14 DIP, 16 SO            |

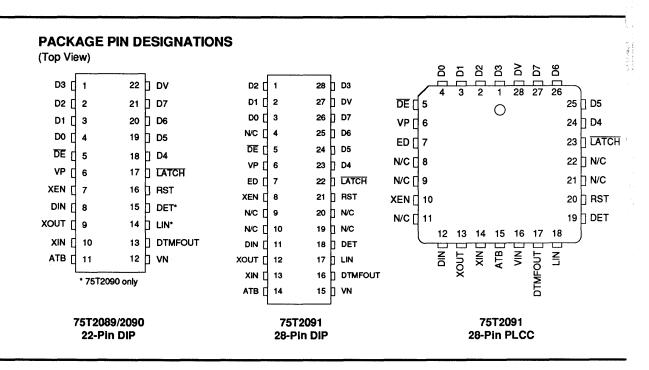

| SSI 75T2089       | Integrated DTMF Transceiver         | Generator & receiver, µP interface                                 | +5V         | 22 DIP                   |

| SSI 75T2090       | Integrated DTMF Transceiver         | Like 75T2089 w/ call progress detect                               | +5V         | 22 DIP                   |

| SSI 75T2091       | Integrated DTMF Transceiver         | Like 75T2090 w/ early detect                                       | +5V         | 28 DIP, PLCC             |

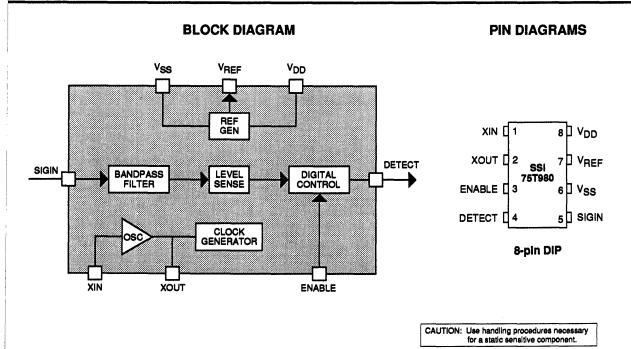

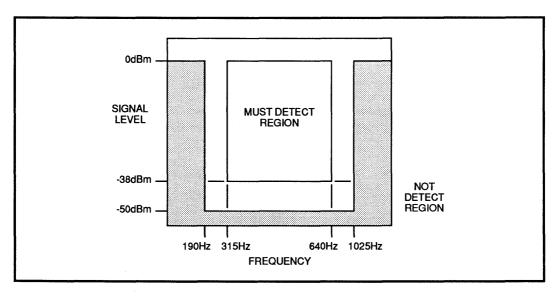

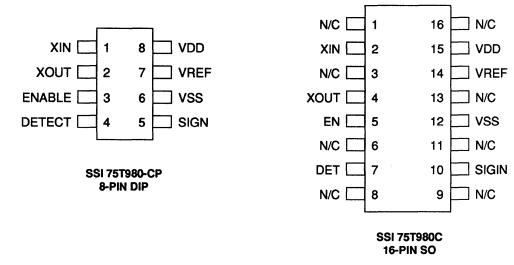

| SSI 75T980        | Imprecise Call Progress Detector    | Energy detect in 305-640 Hz band, Teltone                          | +5V         | 8 DIP                    |

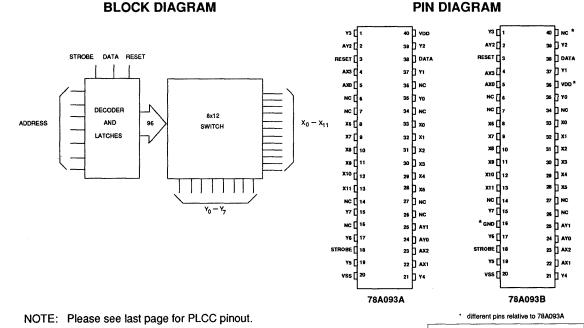

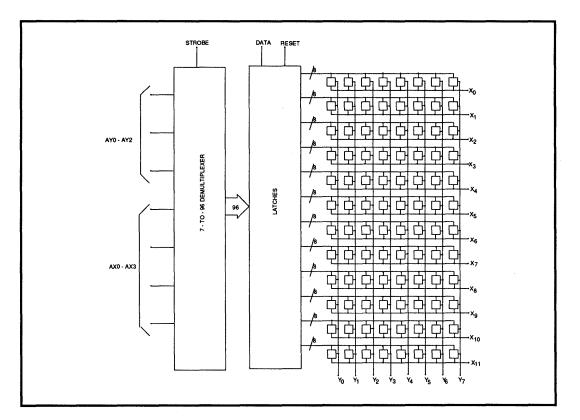

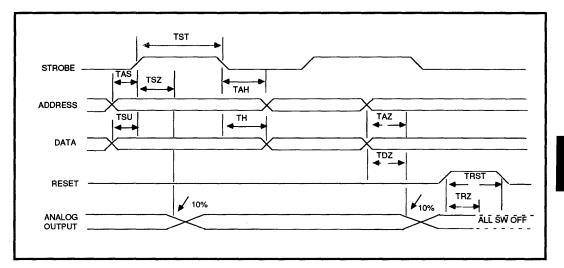

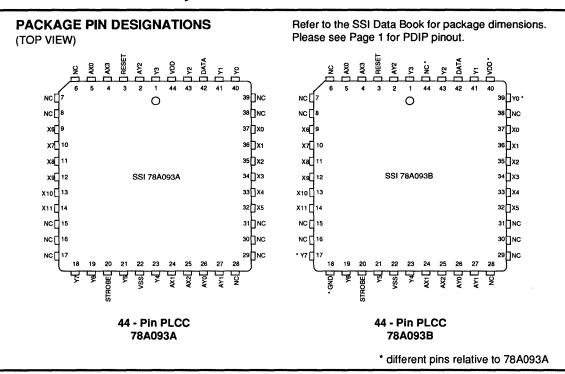

| SSI 78A093A/B     | 12x8x1 Crosspoint Switch            | Low ON resistance, two versions                                    | +5, +12V    | 40 DIP, 44 PLCC          |

| SSI 78A207        | Integrated MF Receiver              | Detects central office toll signals                                | +5V         | 20 DIP                   |

| PCM PRODUCTS      |                                     |                                                                    |             |                          |

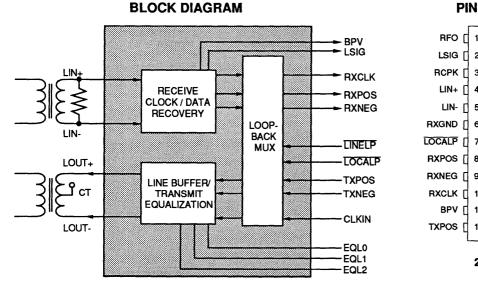

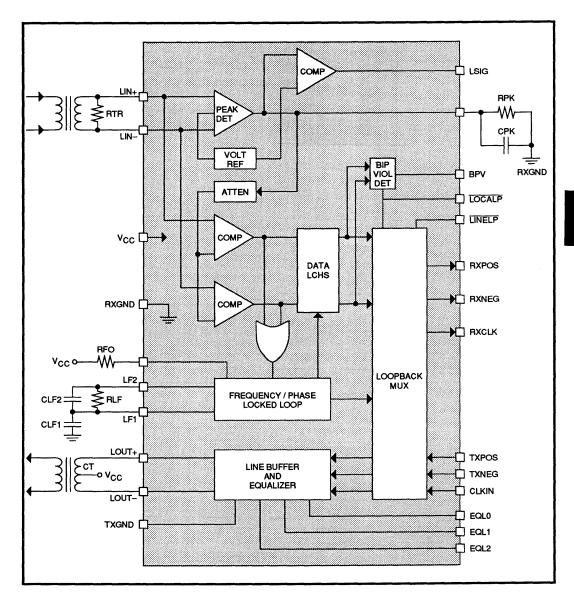

| SSI 78P233        | DS-1 Line Interface                 | T1 clock & data recovery, transmit equalization                    | +5V         | 24 DIP, SDIP, SO         |

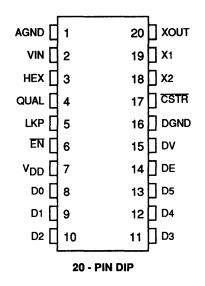

| SSI 78P234        | 2048 kBit/s PCM Interface           | Receive clock & data recovery, transmit drivers                    | +5V         | 20 DIP, SO               |

| SSI 78P236        | DS-3 Line Interface                 | T3 clock & data recovery, transmit equalization                    | +5V         | 28 DIP                   |

| SSI 78P300        | T1/E1 Short Haul Transceiver        | Receive jitter attenuation                                         | +5V         | 28 DIP, PLCC             |

| SSI 78P2361       | STS-1 Line Interface Transceiver    | STS-1 clock & data recovery, transmit equalization                 | +5V         | 28 DIP                   |

| SSI 78P2362       | CEPT E-3 Line Interface Transceiver | E3 clock & data recovery, transmit equalization                    | +5V         | 28 DIP                   |

| SSI 78P7200       | DS-3 Line Interface Transceiver     | DS-3 Transceiver w/Receive equalization & higher transmitter drive | +5V         | 28 DIP                   |

| LAN PRODUCTS      |                                     |                                                                    |             | 그렇고 있는 것이 없을까? 말을 가 있는 것 |

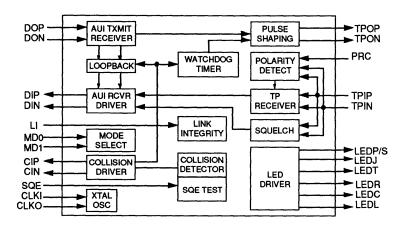

| SSI 78Q902        | 10BaseT MAU Transceiver             | Direct interface to twisted pair and AUI                           | +5V         | 28 DIP, PLCC             |

| SSI 78Q903        | 10BaseT Hub Transceiver             | Programmable squelch, detect/correct reverse polarity              | +5V         | 24 DIP, 28 PLCC          |

| SSI 78Q8330       | 802.3 Coax Transceiver              | 10Base-2 applications                                              | +9V         | 20 DIP, PLCC, 64 TQFP    |

| SSI 78Q8330A      | 802.3 Coax Transceiver              | 10Base-2/10Base-5 applications                                     | +9V         | 20 DIP, PLCC, 64 TQFP    |

| SSI 78Q8360       | Ethernet Controller/ENDEC Combo     | Fully integrated MAC ENDEC & AUI                                   | +5V         | 100 QFP, TQFP            |

| SSI 78Q8370       | PCMCIA Ethernet Combo               | Highly integrated PCMCIA MAC ENDEC & AUI                           | +5V         | 100 QFP, TQFP            |

| BUS INTERFACE PRO | DUCTS                               |                                                                    | an an an an |                          |

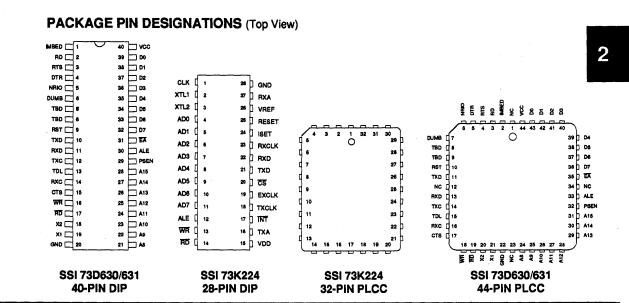

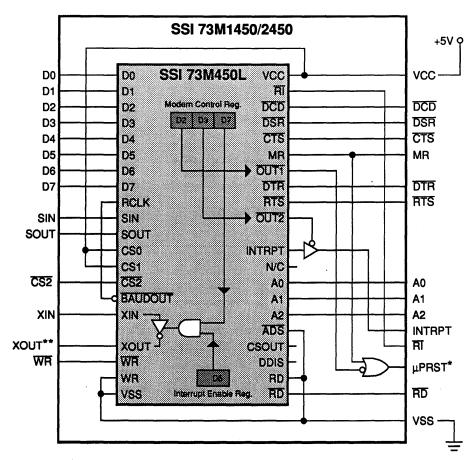

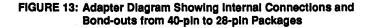

| SSI 73M450L       | 16C450 pin compatible UART          |                                                                    | +5V         | 40 DIP, 44 PLCC          |

| SSI 73M1450       | 28-pin version of SSI 73M450        | Full UART in 28-pin package                                        | +5V         | 28 DIP, PLCC             |

| SSI 73M2450       | 28-pin version of 73M450            | Adds µPRST function                                                | +5V         | 28 DIP, PLCC             |

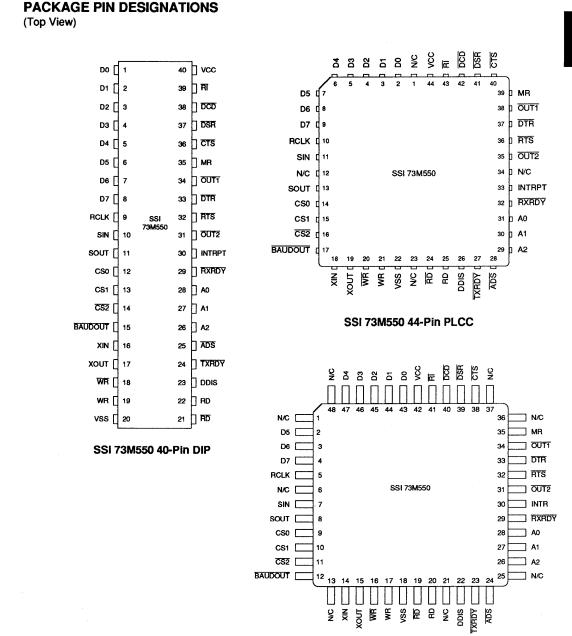

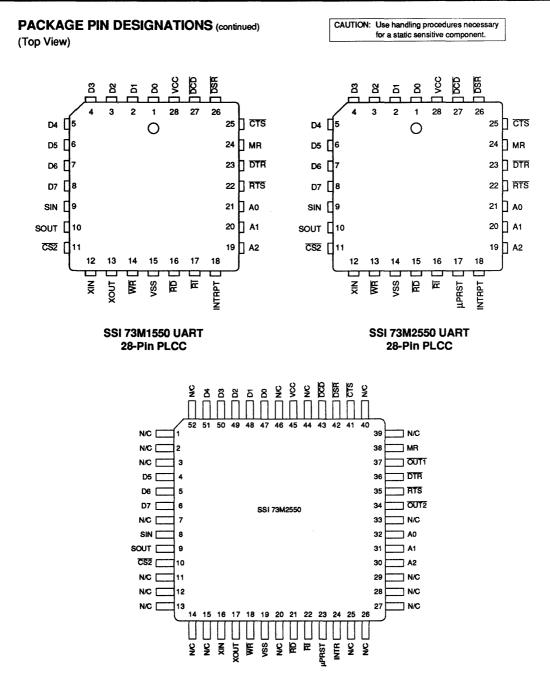

| SSI 73M550        | 16C550 pin compatible UART          | Receive and Transmit FIFOs                                         | +5V         | 40 DIP, 44 PLCC, 48 GT   |

| SSI 73M1550       | 28-pin version of SSI 73M550        | Full UART in 28-pin package                                        | +5V         | 28 DIP, PLCC             |

| SSI 73M2550       | 28-pin version of 73M550            | Adds uPRST function                                                | +5V         | 28 DIP, PLCC             |

and the second second

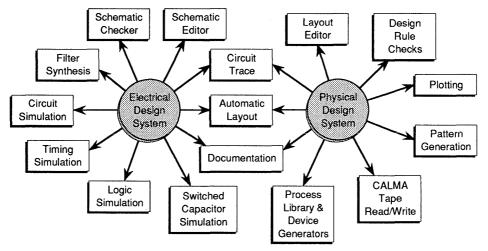

### **Communications ICs at Silicon Systems**

Silicon Systems has built its 21-year reputation on the design and manufacture of both custom and standard mixed-signal ICs, or MSICs®.

All communications ICs, to one degree or another, involve mixedsignal design. All input or output real-world, analog signals and digitize them somewhere in between. In fact, the digital signal processing in modem design gave birth to the DSP found in most of today's computers.

Silicon Systems' designers are experts in protocol and signal processing — analog, digital, wired and wireless. But you should know that easily half of our business is in custom design, and all of our ICs are application-specific. We think this gives us an edge in customer-driven engineering.

We can build mixed-signal circuits which conform to almost limitless requirements for partitioning, cost, footprint, performance and power. In other words, we have the tools to do the job exactly the way you want it.

Why not send for a free copy of our *Tool Kit* brochure for a look at what we've developed in the past and what we can develop for you in the future. Bring us your application, and we'll break out the tools.

# Section

# K-SERIES MODEM FAMILY

### Silicon Systems' K-Series Family of One-Chip Modems

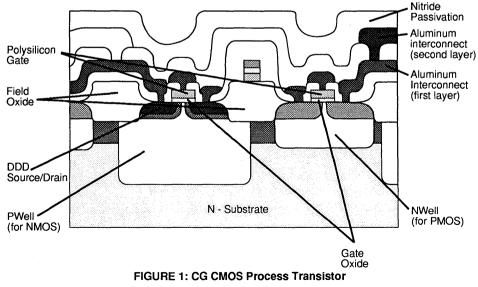

Silicon Systems is a leader in the design and manufacturing of CMOS VLSI modems. Currently, Silicon Systems offers the most extensive line of one-chip modem ICs available, with high-performance, costeffective designs suitable for a wide range of applications. Silicon Systems' fully compatible modem IC family has redefined the modem IC as a universal component which can be easily integrated into any system. Designs can be upgraded to meet different standards and speeds by simply substituting one K-Series IC for another. Using a K-Series family modem IC in your application eliminates product obsolesence, and minimizes development costs.

The Silicon Systems modem IC family consists of four basic products:

- The SSI 73K222L, a multi-mode device which combines both Bell 212A/103 and V.22/V.21 capability in one chip, with operating modes at 0 - 30, 600 and 1200 bit/s.

- The SSI 73K222U which combines the functionality of the 73K222L with the industry standard 16C450 UART.

- The SSI 73K224L, a major technological breakthrough which provides 2400 bit/s V.22bis operation in addition to V.22/V.21 and Bell 212A/103 modes in a single IC.

- The SSI 73K322L provides CCITT V.22/V.21 plus V.23 Videotex modes.

New additions to Silicon Systems' modem IC family extend the available operating modes and provide features which greatly simplify integral modem design. The SSI 73K324L offers V.22bis, V.22/V.21 and V.23 operating modes on one chip. These products dramatically reduce external circuitry required for dedicated integral modem designs.

Silicon Systems' one-chip modem IC products represent technical achievements unmatched in the industry. An advanced Digital Signal Processor resides on the same chip with sophisticated analog circuitry in the SSI 73K224L and SSI 73K324L products. "U" versions of the K-Series devices integrate an industry standard UART with full modem capability on a single chip. In addition, an innovative bus structure makes a separate controller unnecessary in dedicated integral designs. All K-Series devices are available in low-power versions. This feature allows optimal performance with single +5V supply operation and is unique to Silicon Systems' products.

Silicon Systems' single-chip modem IC family is designed to be the most effective solution for a wide variety of modem applications. The products provide for a full range of communications standards and speeds up to 2400 bit/s. Moreover, features can be extended to include additional modes and higher operating speeds without impacting existing designs. Take advantage of these capabilities. Design for tomorrow's needs today by using Silicon Systems' K-Series modem IC family.

#### K-Series Modem Design Manual

The Silicon Systems K-Series Modem Design Manual contains a large body of application literature for the K-Series family of single chip modem products. This manual is intended as a tutorial for those users who may be designing with modems for the first time, and also as a helpful guide for more experienced modem designers.

The K-Series Modem Design Manual is available through our worldwide network of representatives and distributors.

December 1992

1

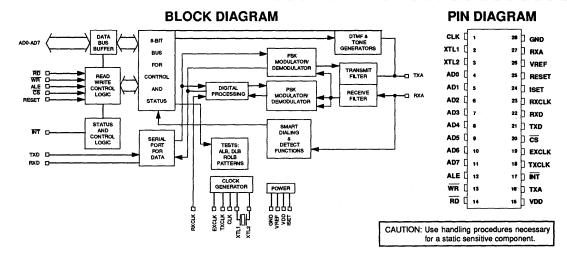

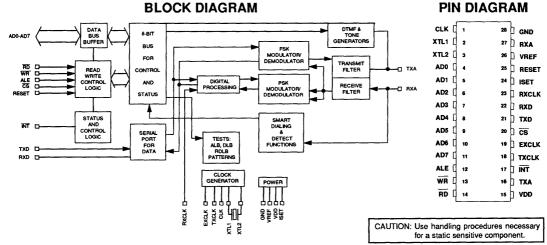

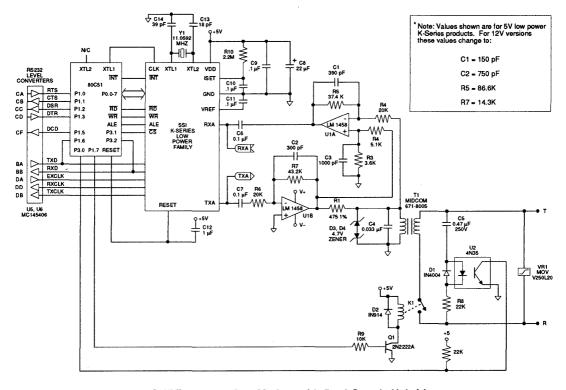

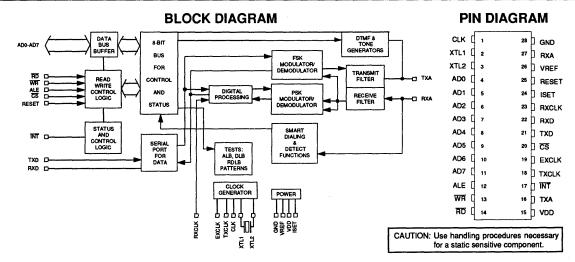

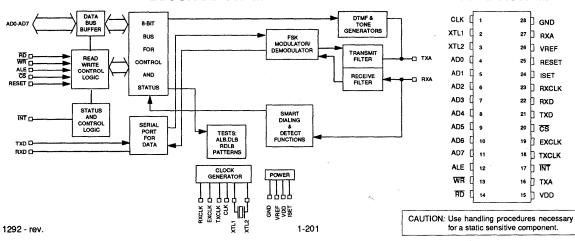

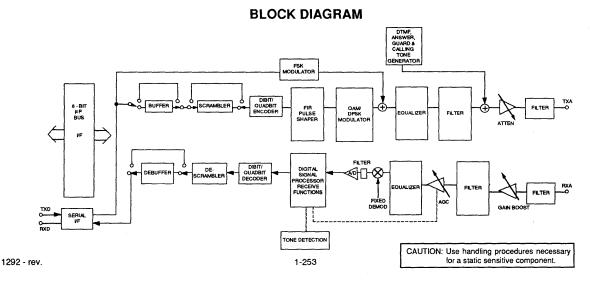

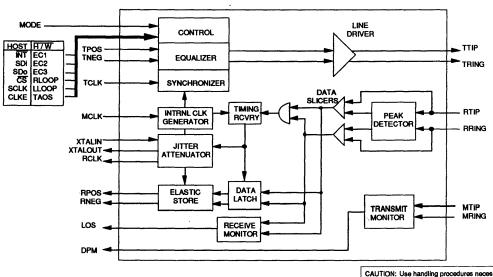

### DESCRIPTION

The SSI 73K212 is a highly integrated single-chip modem IC which provides the functions needed to construct a typical Bell 212A full-duplex modem. Using an advanced CMOS process that integrates analog, digital and switched-capacitor filter functions on a single substrate, the SSI 73K212 offers excellent performance and a high level of functional integration in a single 28- or 22-pin DIP configuration. The SSI 73K212L low power version of the SSI 73K212 provides identical performance and features, but operates from a single +5V supply with substantially lower power consumption.

on sustems\*

A TDK Group Company

The SSI 73K212 includes the DPSK and FSK modulator/demodulator functions, call progress and handshake tone monitor test modes and a DTMF dialer. This device supports all Bell 212A modes of operation allowing both synchronous and asychronous communications.

Test features such as analog loop, digital loop, and remote digital loopback are provided. Internal pattern generators are also included for self-testing. The SSI73K212 is designed to appear to the systems designer as a microprocessor peripheral, and will easily interface with popular one-chip microprocessors

### FEATURES

- One-chip Bell 212A and 103 standard compatible modem data pump

- Full-duplex operation at 0-300 bit/s (FSK) or 1200 bit/s (DPSK)

- Pin and software compatible with other SSI K-Series 1-chip modems

- Interfaces directly with standard microprocessors (8048, 80C51 typical)

- Serial or parallel microprocessor bus for control

- Serial port for data transfer

- Both synchronous and asynchronous modes of operation

- Call progress, carrier, precise answer tone and long loop detectors

- DTMF generators

- Test modes available: ALB, DL, RDL, Mark, Space, Alternating bit patterns

- Precise automatic gain control allows 45 dB

dynamic range

- CMOS technology for low power consumption using 30 mW @ 5V or 180 mW @ 12V

- Single +5V (73K212L) or +12V (73K212) versions

(Continued)

### **DESCRIPTION** (Continued)

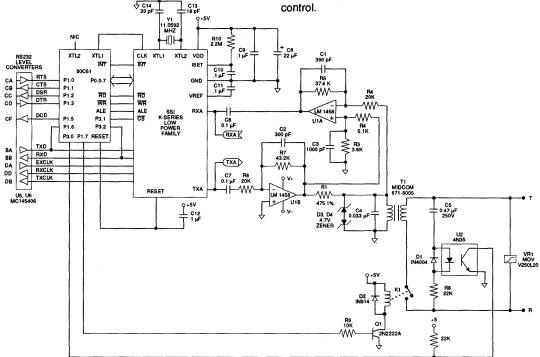

(80C51 typical) for control of modem functions through its 8-bit multiplexed address/data bus or serial control bus. An ALE control line simplifies address demultiplexing. Data communications occurs through a separate serial port only.

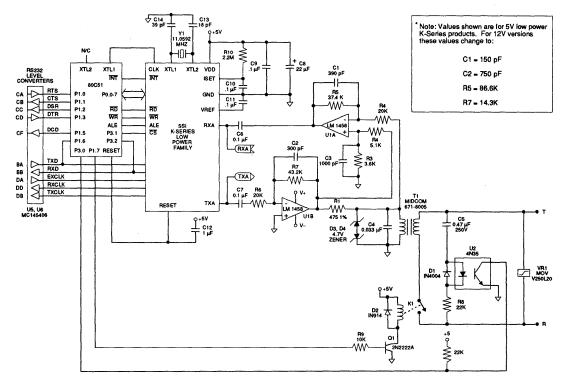

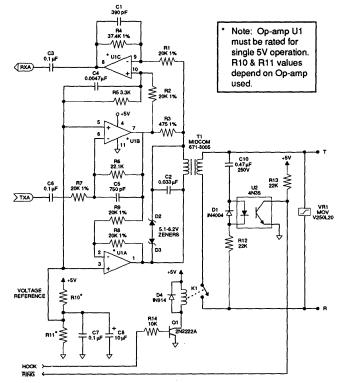

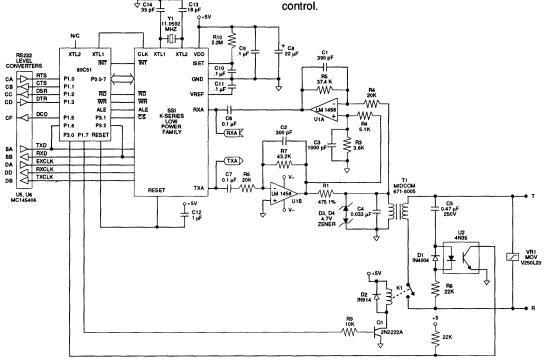

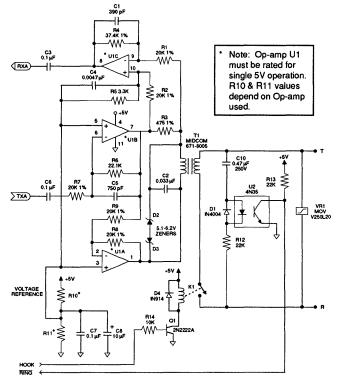

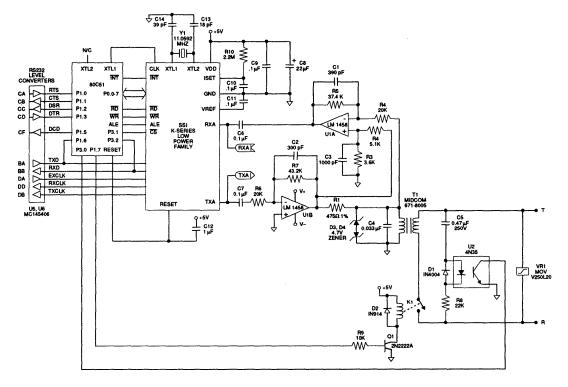

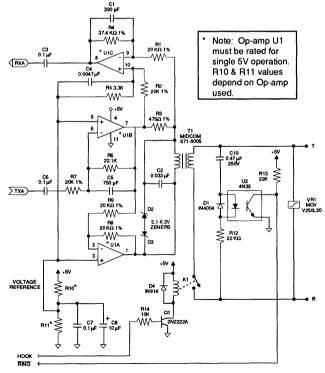

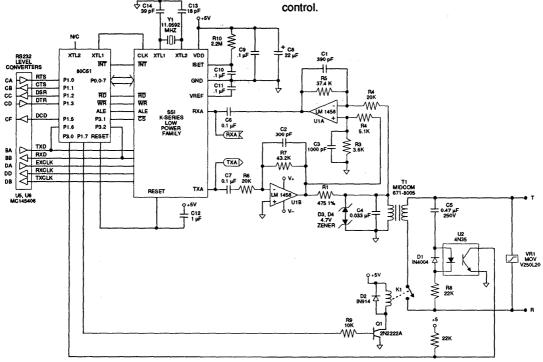

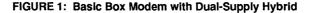

The SSI 73K212 is ideal for use in either free standing or integral system modem products where full-duplex 1200 bit/s data communications over the 2-wire switched telephone network is desired. Its high functionality, low power consumption and efficient packaging simplify design requirements and increase system reliability. A complete modem requires only the addition of the phone line interface, a control microprocessor, and RS-232 level convertor for a typical system. The SSI 73K212 is part of SSi's K-Series family of pin and function compatible single-chip modem products. These devices allow systems to be configured for higher speeds and Bell or CCITT operation with only a single component change.

### OPERATION

### ASYNCHRONOUS MODE

Data transmission for the DPSK mode requires that data ultimately be transmitted in a synchronous fashion. The SSI 73K212 includes ASYNC/SYNC and SYNC/ASYNC converters which delete or insert stop bits in order to transmit data within a 0.01% rate. In asynchronous mode the serial data comes from the TXD pin into the ASYNC/SYNC converter. The ASYNC/SYNC converter accepts the data provided on the TXD pin which normally must be 1200 bit/s +1.0%, -2.5%. The rate converter will then insert or delete stop bits in order to output a signal which is 1200 bit/s ± .01% (±.01% is the required synchronous data rate accuracy).

The serial data stream from the ASYNC/SYNC converter is passed through the data scrambler and onto the analog modulator. The data scrambler can be bypassed under processor control when unscrambled data must be transmitted. The ASYNC/SYNC rate converter and the data scrambler are bypassed in all FSK modes. If serial input data contains a break signal through one character (including start and stop bits) the break will be extended to at least  $2 \cdot N + 3$  bits long (where N is the number of transmitted bits/character). Serial data from the demodulator is passed first through the data descrambler and then through the SYNC/ASYNC rate converter. The SYNC/ASYNC convertor will reinsert any deleted stop bits and transmit output data at an intra-character rate (bit-to-bit timing) of no greater than 1219 bit/s. An incoming break signal (low through two characters) will be passed through without incorrectly inserting a stop bit.

いるななながです。

#### SYNCHRONOUS MODE

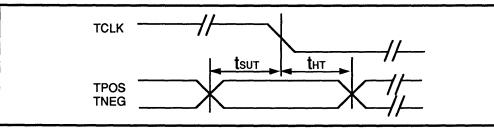

The Bell 212A standard defines synchronous operation only at 1200 bit/s. Operation is similar to that of the asynchronous mode except that data must be synchronized to a provided clock and no variation in data transfer rate is allowable. Serial input data appearing at TXD must be valid on the rising edge of TXCLK.

TXCLK is an internally derived 1200 Hz signal in internal mode and is connected internally to the RXCLK pin in slave mode. Receive data at the RXD pin is clocked out on the falling edge of RXCLK. The ASYNCH/SYNCH converter is bypassed when synchronous mode is selected and data is transmitted out at the same rate as it is input.

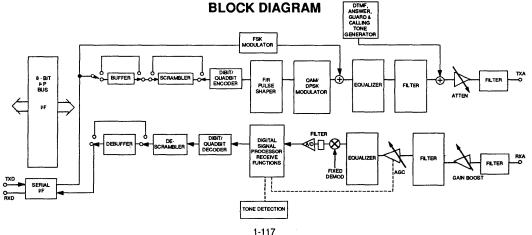

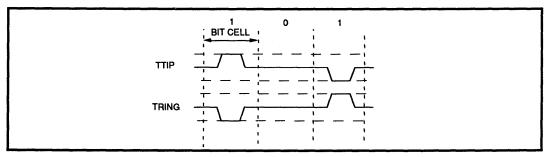

### DPSK MODULATOR/DEMODULATOR

The SSI 73K212 modulates a serial bit stream into dibit pairs that are represented by four possible phase shifts as prescribed by the Bell 212A standard. The baseband signal is then filtered to reduce intersymbol interference on the bandlimited 2-wire telephone line. Transmission occurs using either a 1200 Hz (originate mode) or 2400 Hz carrier (answer mode). Demodulation is the reverse of the modulation process, with the incoming analog signal eventually decoded into di-bits and converted back to a serial bit stream. The demodulator also recovers the clock which was encoded into the analog signal during modulation. Demodulation occurs using either a 1200 Hz carrier (answer mode or ALB originate mode) or a 2400 Hz carrier (originate mode or ALB answer mode). The SSI 73K212 uses a phase locked loop coherent demodulation technique for optimum receiver performance.

#### FSK MODULATOR/DEMODULATOR

The FSK modulator produces a frequency modulated analog output signal using two discrete frequencies to represent the binary data. In the Bell 103, the standard frequencies of 1270 and 1070 Hz (originate, mark and

space) or 2225 and 2025 Hz (answer, mark and space) are used. V.21 mode uses 980 and 1180 Hz (originate, mark and space) or 1650 and 1850 Hz (answer, mark and space). Demodulation involves detecting the received frequencies and decoding them into the appropriate binary value. The rate converter and scrambler/descrambler are bypassed in the 103 mode.

#### PASSBAND FILTERS AND EQUALIZERS

High and low band filters are included to shape the amplitude and phase response of the transmit and receive signals and provide compromise delay equalization and rejection of out-of-band signals in the receive channel. Amplitude and phase equalization are necessary to compensate for distortion of the transmission line and to reduce intersymbol interference in the bandlimited receive signal. The transmit signal filtering approximates a 75% square root of raised Cosine frequency response characteristic.

### AGC

The automatic gain control maintains a signal level at the input to the demodulators which is constant to within 1 dB. It corrects quickly for increases in signal which would cause clipping and provides a total receiver dynamic range of >45 dB.

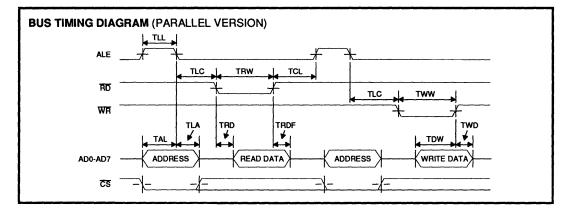

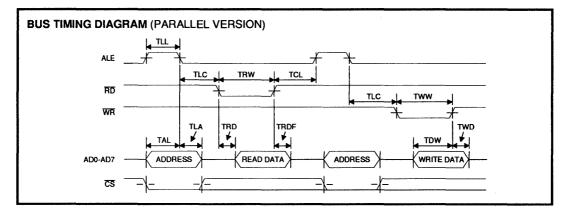

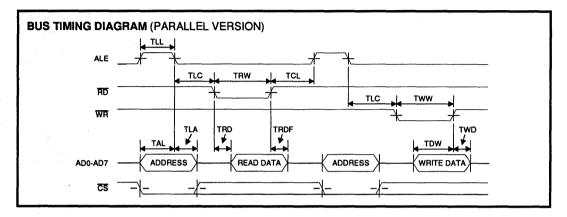

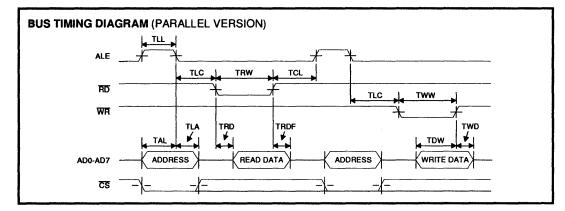

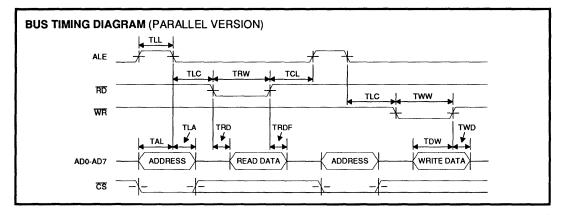

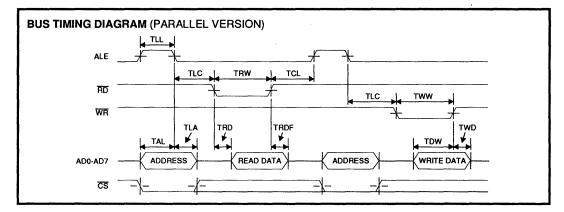

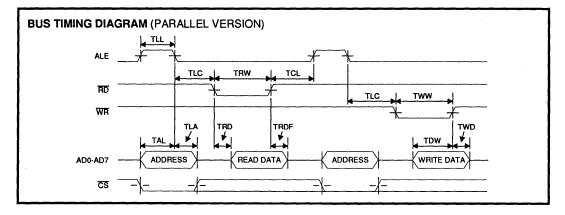

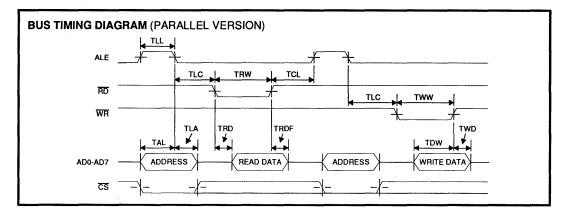

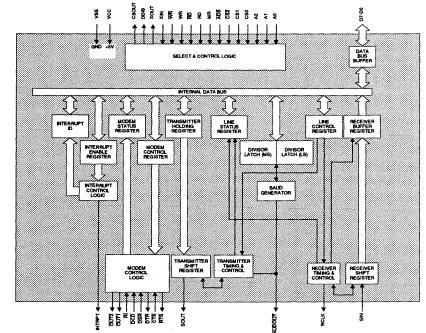

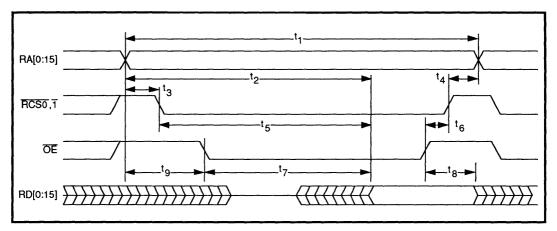

### PARALLEL BUS INTERFACE

Four 8-bit registers are provided for control, option select and status monitoring. These registers are addressed with the AD0, AD1, and AD2 multiplexed address lines (latched by ALE) and appear to a control microprocessor as four consecutive memory locations. Two control registers and the tone register are read/write memory. The status detect register is read only and cannot be modified except by modem response to monitored parameters.

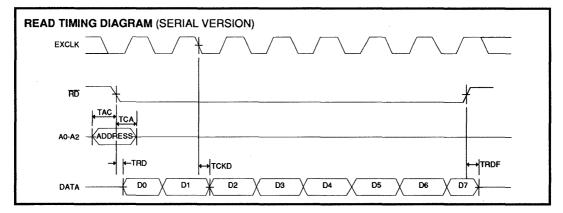

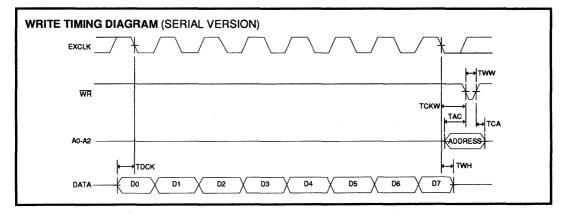

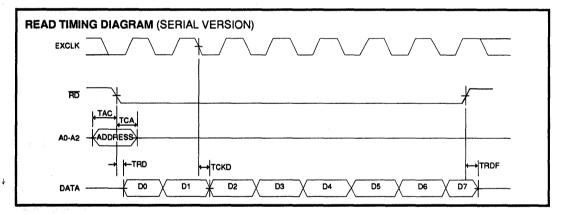

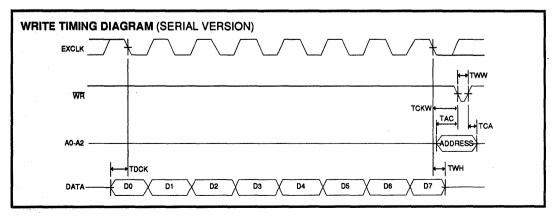

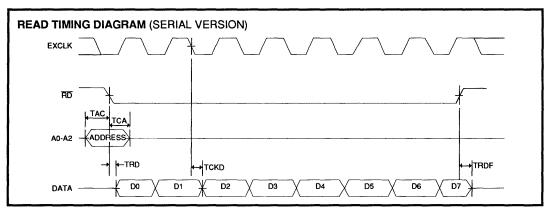

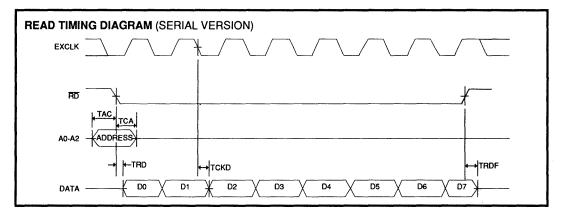

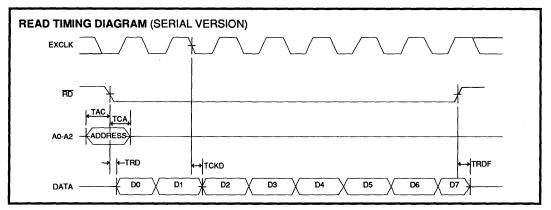

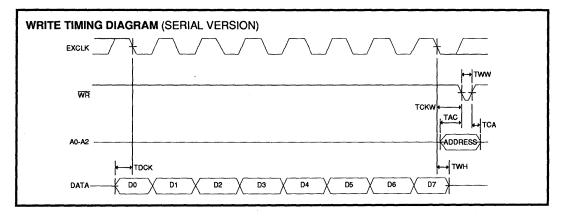

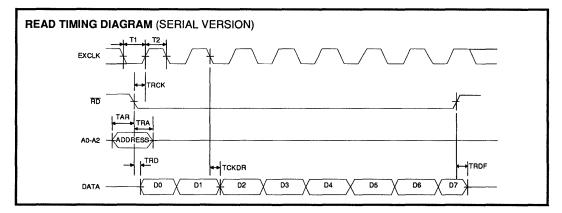

### SERIAL COMMAND INTERFACE

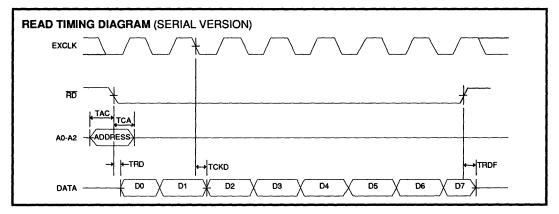

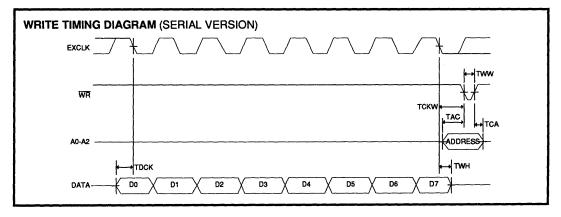

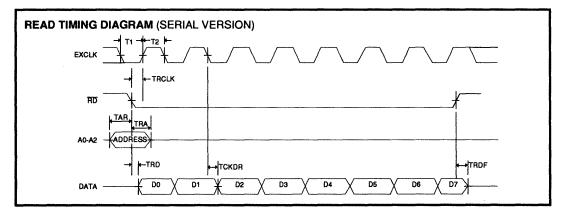

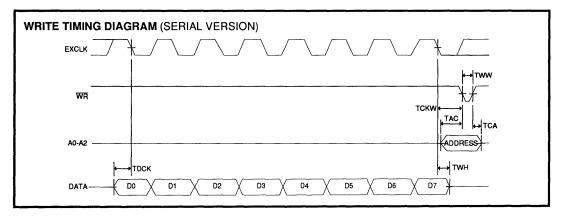

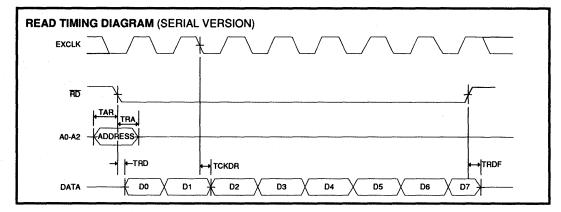

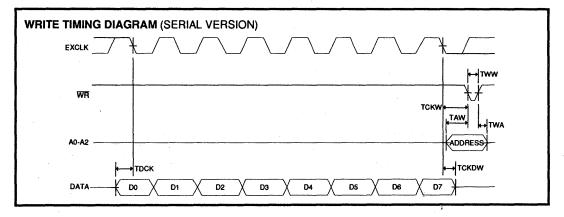

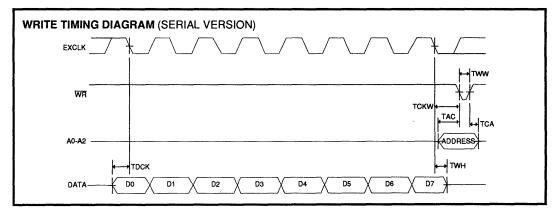

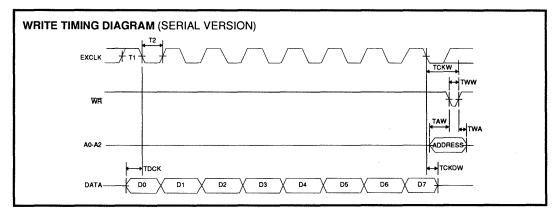

The serial command mode allows access to the SSI 73K212 control and status registers via a serial command port (22-pin version only). In this mode the A0, A1 and A2 lines provide register addresses for data passed through the data pin under control of the RD and WR lines. A read operation is initiated when the RD line is taken low. The next eight cycles of EXCLK will then transfer out eight bits of the selected address location LSB first. A write takes place by shifting in eight bits of data LSB first for eight consecutive cycles of

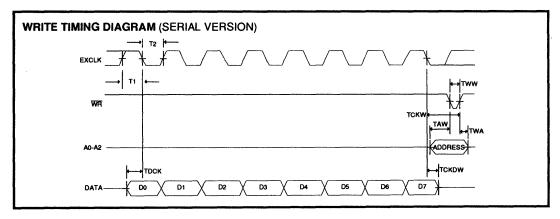

EXCLK.  $\overline{WR}$  is then pulsed low and data transferred into the selected register occurs on the rising edge of  $\overline{WR}$ .

### SPECIAL DETECT CIRCUITRY

The special detect circuitry monitors the received analog signal to determine status or presence of carrier, call-progress tones, answer tone and weak received signal, (long loop condition). An unscrambled mark request signal is also detected when the received data out of the DPSK demodulator before the descrambler has been high for 165.5 ms  $\pm$  6.5 ms minimum. The appropriate detect register bit is set when one of these conditions changes and an interrupt is generated for all purposes except long loop. The interrupts are disabled (masked) when the enable interrupt bit is set to 0.

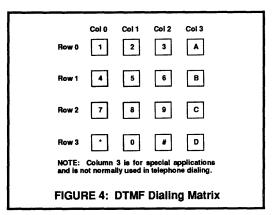

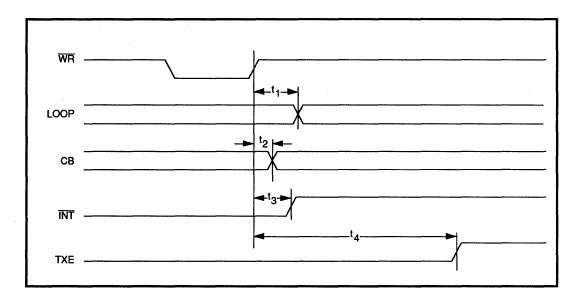

### DTMF GENERATOR

The DTMF generator will output one of 16 standard tone pairs determined by a 4-bit binary value and TX DTMF mode bit previously loaded into the tone register. Tone generation is initiated when the DTMF mode is selected using the tone register and the transmit enable (CR0 bit D1) is changed from 0 to 1.

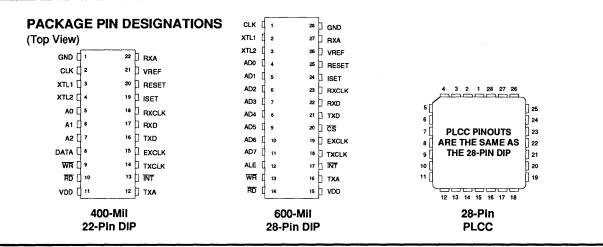

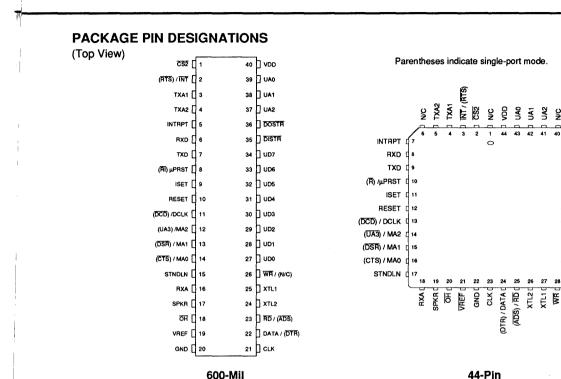

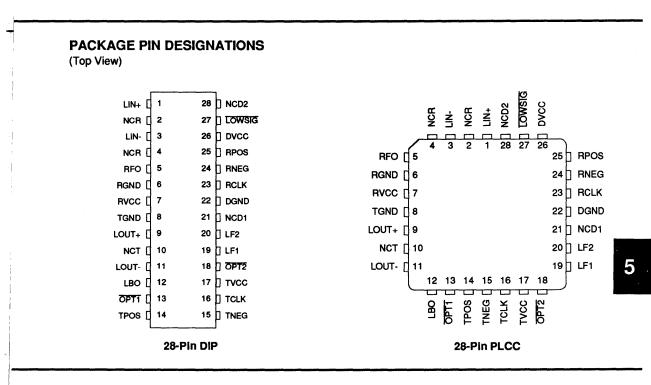

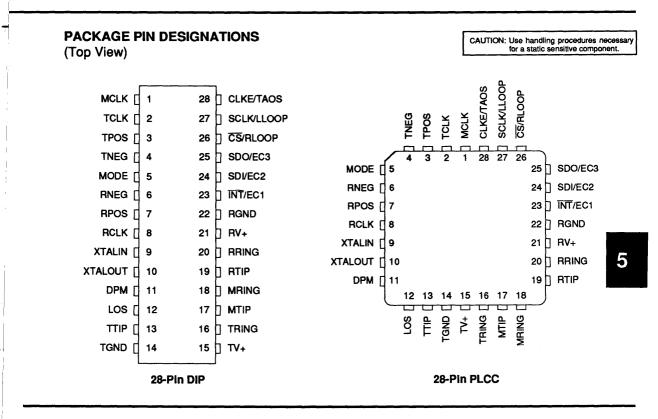

### **PIN DESCRIPTION**

### POWER

| NAME | 28-PIN | 22-PIN | ТҮРЕ | DESCRIPTION                                                                                                                                                                                               |

|------|--------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND  | 28     | 1      | 1    | System Ground.                                                                                                                                                                                            |

| VDD  | 15     | 11     | 1    | Power supply input, 12V +10%, -20% (73K212) or 5V 10% (73K212L). Bypass with .1 and 22 µF capacitors to ground.                                                                                           |

| VREF | 26     | 21     | 0    | An internally generated reference voltage. Bypass with .1 µF capacitor to GND.                                                                                                                            |

| ISET | 24     | 19     | I    | Chip current reference. Sets bias current for op-amps. The chip current is set by connecting this pin to VDD through a 2 M $\Omega$ resistor. ISET should be bypassed to GND with a .1 $\mu$ F capacitor. |

### PARALLEL MICROPROCESSOR INTERFACE

| ALE       | 12   | +  | 1   | Address latch enable. The falling edge of ALE latches the address on AD0-AD2 and the chip select on $\overline{CS}$ .                                                                                                                                                                               |  |  |

|-----------|------|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AD0-AD7   | 4-11 | -  | 1/0 | Address/data bus. These bidirectional tri-state multi-<br>plexed lines carry information to and from the internal<br>registers.                                                                                                                                                                     |  |  |

| <u>cs</u> | 20   | -  | 1   | Chip select. A low during the falling edge of ALE on this allows a read cycle or a write cycle to occur. AD0-AD7 not be driven and no registers will be written if $\overline{CS}$ (latch is not active. The state of $\overline{CS}$ is latched on the falling e of ALE.                           |  |  |

| CLK       | 1    | 2  | 0   | Output clock. This pin is selectable under processor control<br>to be either the crystal frequency (for use as a processor<br>clock) or 16 x the data rate for use as a baud rate clock in<br>DPSK modes only. The pin defaults to the crystal frequency<br>on reset.                               |  |  |

| ĪNT       | 17   | 13 | 0   | Interrupt. This open drain output signal is used to inform the processor that a detect flag has occurred. The processor must then read the detect register to determine which detect triggered the interrupt. INT will stay low until the processor reads the detect register or does a full reset. |  |  |

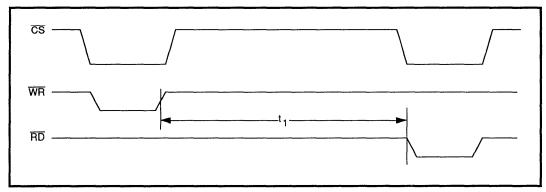

| RD        | 14   | -  | I   | Read. A low requests a read of the SSI 73K212 internal registers. Data cannot be output unless both $\overline{\text{RD}}$ and the latched $\overline{\text{CS}}$ are active or low.                                                                                                                |  |  |

### PARALLEL MICROPROCESSOR INTERFACE (Continued)

| NAME  | 28-PIN | 22-PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                              |

|-------|--------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

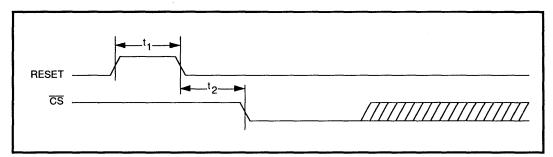

| RESET | 25     | 20     | I    | Reset. An active high signal on this pin will put the chip into<br>an inactive state. All control register bits (CR0, CR1, Tone)<br>will be reset. The output of the CLK pin will be set to the<br>crystal frequency. An internal pull down resistor permits<br>power on reset using a capacitor to VDD. |

| WR    | 13     | -      | I    | Write. A low on this informs the SSI 73K212 that data is available on AD0-AD7 for writing into an internal register. Data is latched on the rising edge of $\overline{WR}$ . No data is written unless both $\overline{WR}$ and the latched $\overline{CS}$ are low.                                     |

### SERIAL MICROPROCESSOR INTERFACE

| A0-A2 |                                                                                                                                                                                                                                         | - | 5-7 | I   | Register Address Selection. These lines carry register addresses and should be valid during any read or write operation.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DATA  |                                                                                                                                                                                                                                         | - | 8   | I/O | Serial Control Data. Data for a read/write operation is clocked in or out on the falling edge of the EXCLK pin. The direction of data flow is controlled by the RD pin. RD low outputs data. RD high inputs data.                                                                                                                                                                                                                                                               |  |  |  |  |  |

| RD    |                                                                                                                                                                                                                                         | - | 10  | I   | Read. A low on this input informs the SSI 73K212 that data<br>or status information is being read by the processor. The<br>falling edge of the $\overline{RD}$ signal will initiate a read from the<br>addressed register. The $\overline{RD}$ signal must continue for eight<br>falling edges of EXCLK in order to read all eight bits of the<br>referenced register. Read data is provided LSB first. Data<br>will not be output unless the $\overline{RD}$ signal is active. |  |  |  |  |  |

| WR    |                                                                                                                                                                                                                                         | - | 9   | 1   | Write. A low on this input informs the SSI 73K212 that data or status information has been shifted in through the DATA pin and is available for writing to an internal register. The normal procedure for a write is to shift in data LSB first on the DATA pin for eight consecutive falling edges of EXCLK and then to pulse $\overline{WR}$ low. Data is written on the rising edge of $\overline{WR}$ .                                                                     |  |  |  |  |  |

| Note: | In the serial, 22-pin version, the pins AD0-AD7, ALE and $\overline{CS}$ are removed and replaced with the pins; A0, A1, A2, DATA, and an unconnected pin. Also, the $\overline{RD}$ and $\overline{WR}$ controls are used differently. |   |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       | The Serial Control mode is provided in the parallel control versions by tying ALE high and $\overline{CS}$ low.<br>In this configuration AD7 becomes DATA and AD0, AD1 and AD2 become A0, A1 and A2, respectively.                      |   |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

1

### DTE USER INTERFACE

| NAME  | 28-PIN | 22-PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|-------|--------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| EXCLK | 19     | 15     | I    | External Clock. This signal is used in synchronous trans-<br>mission when the external timing option has been selected.<br>In the external timing mode the rising edge of EXCLK is<br>used to strobe synchronous DPSK transmit data applied to<br>the TXD pin. Also used for serial control interface.                                                                                                                                                                                                                         |  |  |

| RXCLK | 23     | 18     | 0    | coincident with the transitions in the serial received d<br>output. The rising edge of RXCLK can be used to latch<br>valid output data. RXCLK will be valid as long as a car<br>is present.                                                                                                                                                                                                                                                                                                                                    |  |  |

| RXD   | 22     | 17     | 0    | Received Data Output. Serial receive data is available on<br>this pin. The data is always valid on the rising edge of<br>RXCLK when in synchronous mode. RXD will output con-<br>stant marks if no carrier is detected.                                                                                                                                                                                                                                                                                                        |  |  |

| TXCLK | 18     | 14     | 0    | Transmit Clock. This signal is used in synchronous trans-<br>mission to latch serial input data on the TXD pin. Data must<br>be provided so that valid data is available on the rising edge<br>of the TXCLK. The transmit clock is derived from different<br>sources depending upon the synchronization mode<br>selection. In Internal Mode the clock is generated internally.<br>In External Mode TXCLK is phase locked to the EXCLK pin.<br>In Slave Mode TXCLK is phase locked to the RXCLK pin.<br>TXCLK is always active. |  |  |

| TXD   | 21     | 16     | I    | Transmit Data Input. Serial data for transmission is applied<br>on this pin. In synchronous modes, the data must be valid<br>on the rising edge of the TXCLK clock. In asynchronous<br>modes (1200 bit/s or 300 baud) no clocking is necessary.<br>DPSK data must be 1200 bit/s +1%, -2.5%.                                                                                                                                                                                                                                    |  |  |

### ANALOG INTERFACE AND OSCILLATOR

| RXA          | 27     | 22     | 1 | Received modulated analog signal input from the tele-<br>phone line interface.                                                                                                                                                                 |

|--------------|--------|--------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТХА          | 16     | 12     | 0 | Transmit analog output to the telephone line interface.                                                                                                                                                                                        |

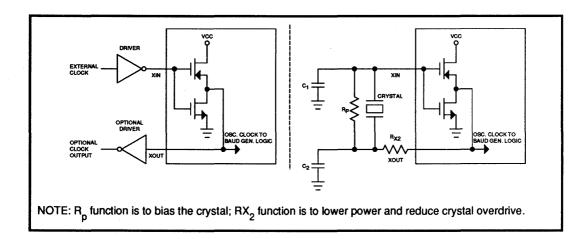

| XTL1<br>XTL2 | 2<br>3 | 3<br>4 | I | These pins are for the internal crystal oscillator requiring<br>a 11.0592 MHz parallel mode crystal and two load capaci-<br>tors to Ground. Consult crystal manufacturer for proper<br>valves. XTL2 can also be driven from an external clock. |

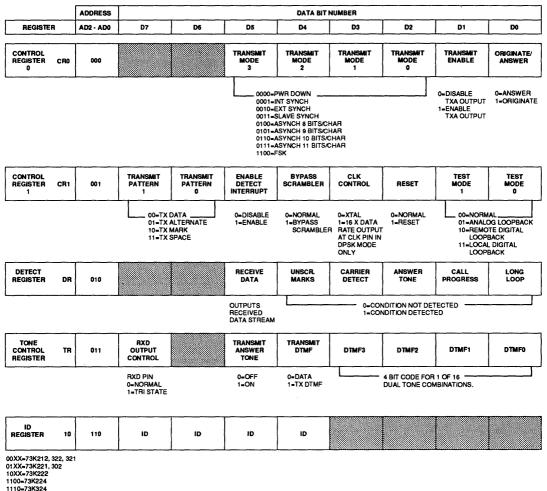

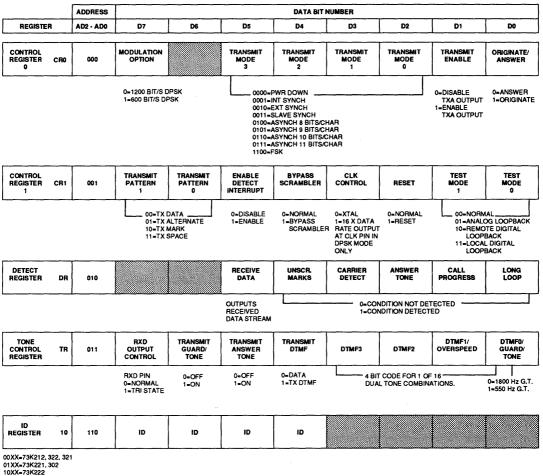

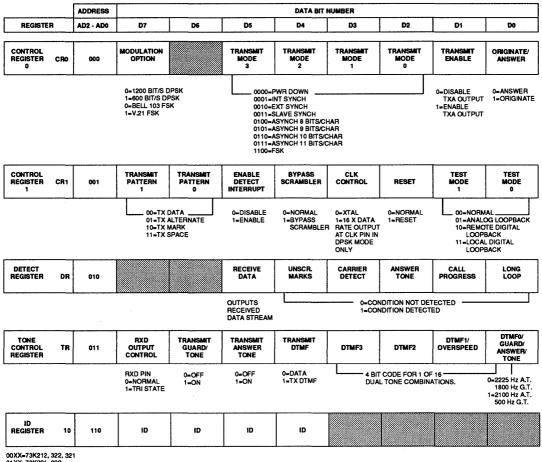

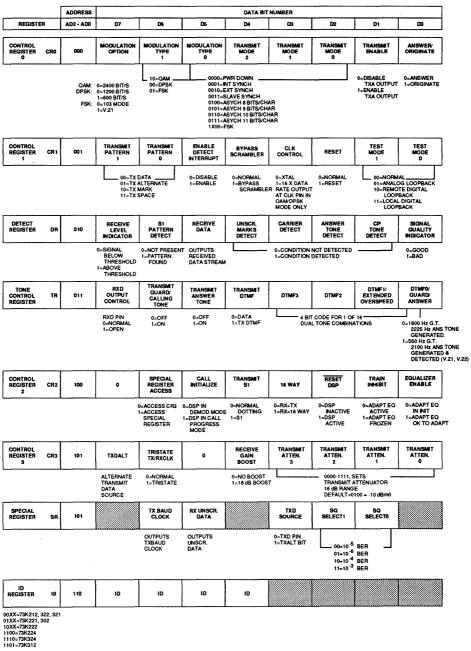

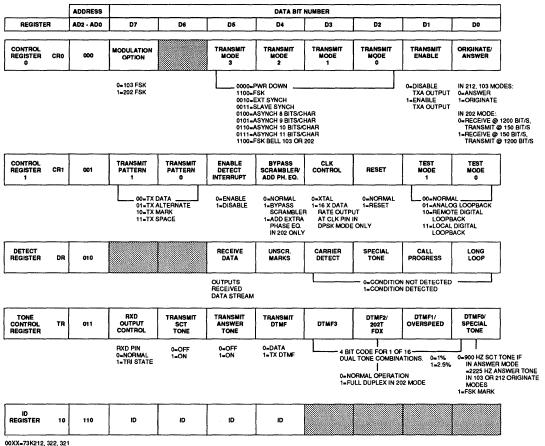

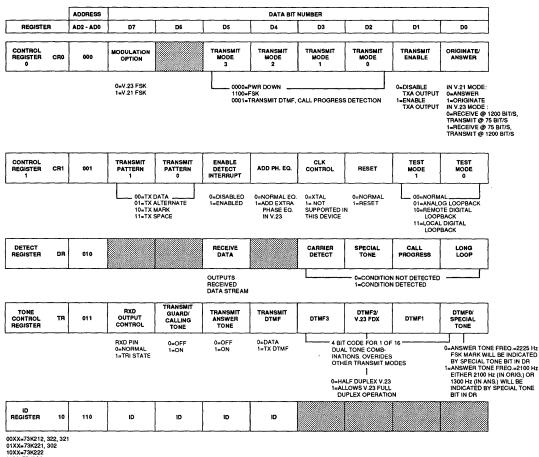

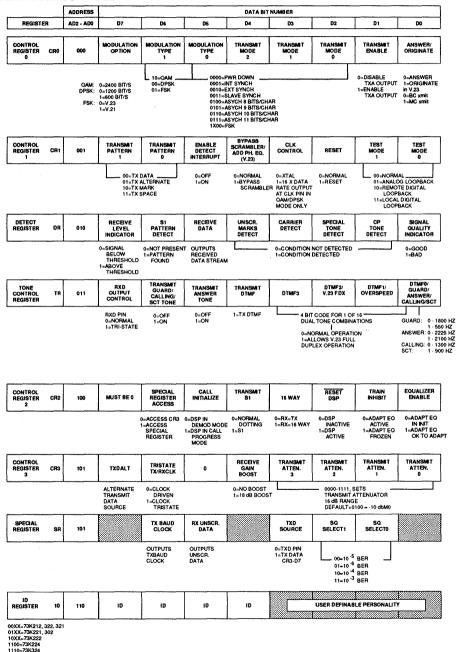

### **REGISTER DESCRIPTIONS**

Four 8-bit internal registers are accessible for control and status monitoring. The registers are accessed in read or write operations by addressing the A0, A1 and A2 address lines in serial mode, or the AD0, AD1 and AD2 lines in parallel mode. In parallel mode the address lines are latched by ALE. Register CR0 controls the method by which data is transferred over the phone line. CR1 controls the interface between the microprocessor and the SSI 73K212 internal state. DR is a detect register which provides an indication of monitored modern status conditions. TR, the tone control register, controls the DTMF generator, answer and guard tones and RXD output gate used in the modern initial connect sequence. All registers are read/write except for DR which is read only. Register control and status bits are identified below:

|                             |     | ADDRESS   |                          |                          |                               | DATA BIT                               | NUMBER                |                       |                    |                      |  |

|-----------------------------|-----|-----------|--------------------------|--------------------------|-------------------------------|----------------------------------------|-----------------------|-----------------------|--------------------|----------------------|--|

| REGISTE                     | R   | AD2 - AD0 | D7                       | D6                       | D5                            | D4                                     | D3                    | D2                    | D1                 | D0                   |  |

| CONTROL<br>REGISTER<br>0    | CRO | 000       |                          |                          | TRANSMIT<br>MODE<br>3         | TRANSMIT<br>MODE<br>2                  | TRANSMIT<br>MODE<br>1 | TRANSMIT<br>MODE<br>0 | TRANSMIT<br>ENABLE | ANSWER/<br>ORIGINATE |  |

| CONTROL<br>REGISTER<br>1    | CR1 | 001       | TRANSMIT<br>PATTERN<br>1 | TRANSMIT<br>PATTERN<br>0 | ENABLE<br>DETECT<br>INTERRUPT | BYPASS<br>SCRAMBLER                    | CLK<br>CONTROL        | RESET                 | TEST<br>MODE<br>1  | TEST<br>MODE<br>0    |  |

| DETECT<br>REGISTER          | DR  | 010       |                          |                          | RECEIVE<br>DATA               | UNSCR.<br>MARKS                        | CARRIER<br>DETECT     | ANSWER<br>TONE        | CALL<br>PROGRESS   | LONG<br>LOOP         |  |

| TONE<br>CONTROL<br>REGISTER | TR  | 011       | RXD<br>OUTPUT<br>CONTROL |                          | TRANSMIT<br>ANSWER<br>TONE    | TRANSMIT<br>DTMF                       | DTMF3                 | DTMF2                 | DTMF1              | DTMFO                |  |

| CONTROL<br>REGISTER<br>2    | CR2 | 100       |                          |                          | [                             | THESE RE                               | GISTER LOCATIO        | NS ARE RESER          | VED FOR            |                      |  |

| CONTROL<br>REGISTER<br>3    | CR3 | 101       |                          |                          |                               | USE WITH OTHER K-SERIES FAMILY MEMBERS |                       |                       |                    |                      |  |

| ID<br>REGISTER              | ID  | 110       | ID                       | ID                       | ID                            | ID                                     |                       |                       |                    |                      |  |

#### **REGISTER BIT SUMMARY**

NOTE: When a register containing reserved control bits is written into, the reserved bits must be programmed as 0's.

**REGISTER ADDRESS TABLE**

1110=73K324 1101=73K312

| CON  | TROL | REGIS  | TER 0 |

|------|------|--------|-------|

| 0011 |      | 112010 |       |

|               | D7  | D6                   | D5             |     | Γ    | D4    | D3                                                                                                               | D2                                           | D1                            | D0                                                                  |  |

|---------------|-----|----------------------|----------------|-----|------|-------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------|---------------------------------------------------------------------|--|

| CR0<br>000    |     |                      | TRANSI<br>MODE |     |      | RANSM |                                                                                                                  | TRANSMIT<br>MODE 0                           | TRANSMIT<br>ENABLE            | ANSWER/<br>ORIGINATE                                                |  |

| BIT NO        |     | NAME                 | CC             | DND | ITIC | Л     | DESCRIPTI                                                                                                        | ON                                           |                               |                                                                     |  |

| D0            |     | Answer/<br>Originate |                | C   | )    |       | Selects answing low band)                                                                                        |                                              | nsmit in high                 | band, receive                                                       |  |

|               |     |                      |                | 1   |      |       | Selects originate mode (transmit in low band, receive in high band).                                             |                                              |                               |                                                                     |  |

| D1            |     | Transmit             |                | 0   | )    |       | Disables transmit output at TXA.                                                                                 |                                              |                               |                                                                     |  |

|               |     | Enable               |                | 1   |      |       | Enables transmit output at TXA.                                                                                  |                                              |                               |                                                                     |  |

|               |     |                      |                |     |      |       | Note: Answer tone and DTMF TX control require TX enable.                                                         |                                              |                               |                                                                     |  |

|               |     |                      | D5             | D4  | D3   | D2    |                                                                                                                  |                                              |                               |                                                                     |  |

| D5, D4,<br>D2 | D3, | Transmit<br>Mode     | 0              | 0   | 0    | 0     |                                                                                                                  | er down mode<br>ept digital inte             |                               | S                                                                   |  |

|               |     |                      | 0              | 0   | 0    | 1     | internally de<br>appearing at                                                                                    | rived 1200 H<br>TXD must be<br>ceive data is | lz signal. Se<br>valid on the | e TXCLK is an<br>rial input data<br>rising edge of<br>of RXD on the |  |

|               |     |                      | 0              | 0   | 1    | 0     | internal sync                                                                                                    | hronous, but<br>CLK pin, and                 | TXCLK is co                   | n is identical to<br>onnected inter-<br>clock must be               |  |

|               |     |                      | 0              | 0   | 1    | 1     | synchronous                                                                                                      |                                              | LK is connect                 | ation as other<br>ed internally to                                  |  |

|               |     |                      | 0              | 1   | 0    | 0     |                                                                                                                  | K asynchrono<br>data bits, 1 s               |                               | bits/character                                                      |  |

|               |     |                      | 0              | 1   | 0    | 1     | Selects DPS<br>(1 start bit, 7                                                                                   | K asynchrono<br>data bits, 1 s               | ous mode - 9<br>top bit).     | bits/character                                                      |  |

|               |     |                      | 0              | 1   | 1    | 0     | Selects DPSK asynchronous mode - 10 bits/character<br>(1 start bit, 8 data bits, 1 stop bit).                    |                                              |                               |                                                                     |  |

|               |     |                      | 0              | 1   | 1    | 1     | Selects DPSK asynchronous mode - 11 bits/character (1 start bit, 8 data bits, Parity and 1 stop or 2 stop bits). |                                              |                               |                                                                     |  |

|               |     |                      | 1              | 1   | 0    | 0     | Selects FSK operation.                                                                                           |                                              |                               |                                                                     |  |

| D6            |     |                      |                |     | 0    |       | Not used, m                                                                                                      | ust be written                               | as "0."                       |                                                                     |  |

1

### **CONTROL REGISTER 1**