## DATA HANDBOOK

Signetics

Programmable

Logic

Devices

Signetics

**Philips Components**

**PHILIPS**

PLD Data Handbook 1990

**Programmable Logic Devices**

# Programmable Logic Devices

**Philips Components**

**PHILIPS**

Signetics reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Signetics assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Signetics makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Signetics Products are not designed for use in life support appliances, devices, or systems where malfunction of a Signetics Product can reasonably be expected to result in a personal injury. Signetics customers using or selling Signetics Products for use in such applications do so at their own risk and agree to fully indemnify Signetics for any damages resulting from such improper use or sale.

Signetics registers eligible circuits under the Semiconductor Chip Protection Act.

© Copyright 1990 NAPC.

### **Preface**

#### **Programmable Logic Devices**

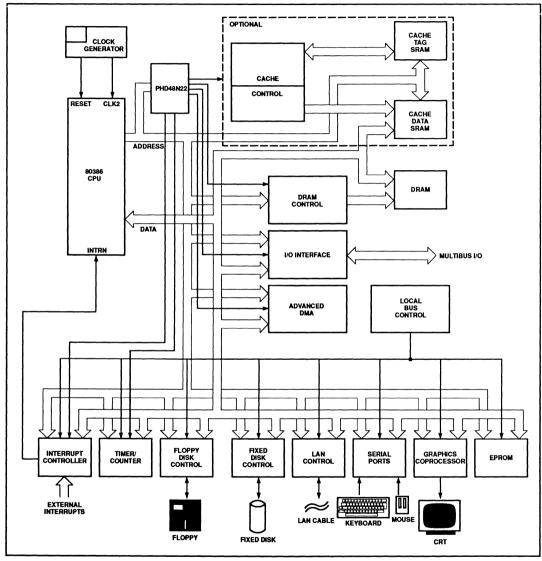

The 1990 Philips Components—Signetics PLD Data Handbook is loaded with information on new parts. Using the fastest technologies in the most innovative architectures, today's system designer can pick from the largest selection of PLDs in the industry. Some highlights of this handbook include the fastest silicon PLDs available (PHD16N8 and PHD48N22)—at 5 nanoseconds! These devices make ideal decoders to squeeze maximum performance from powerful microprocessors.

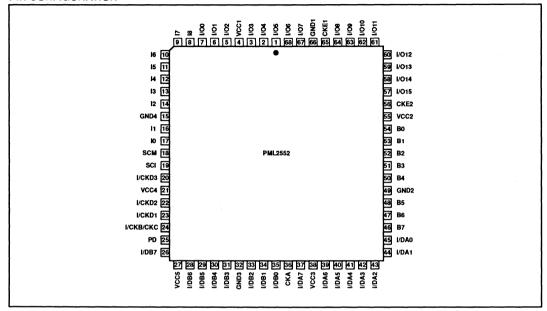

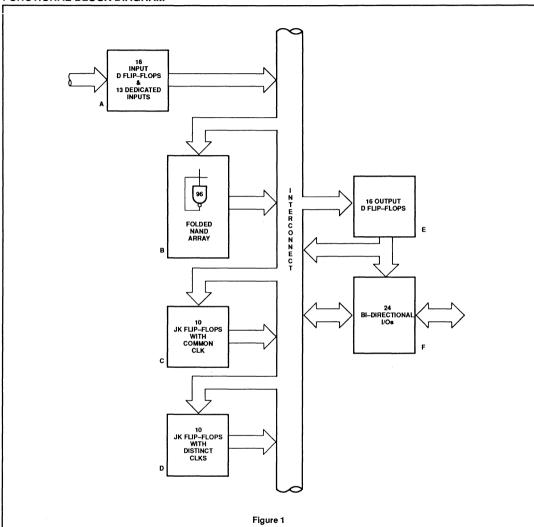

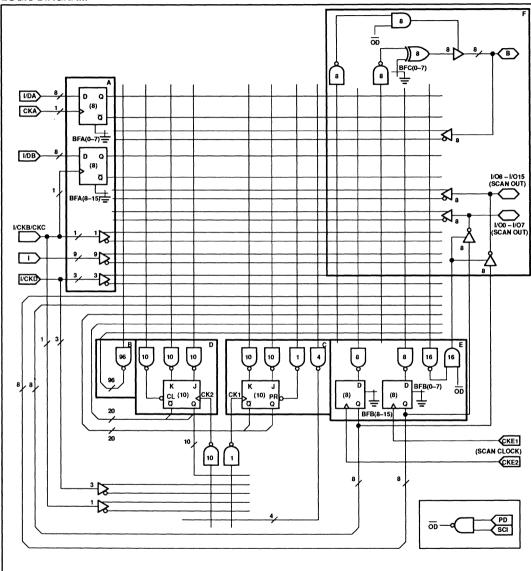

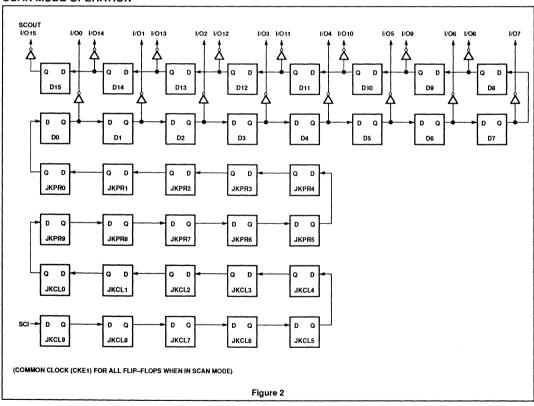

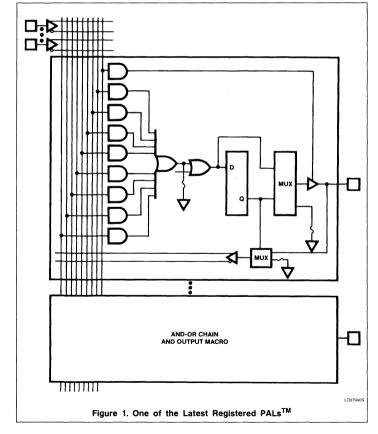

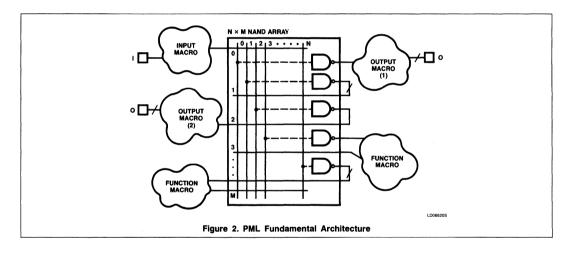

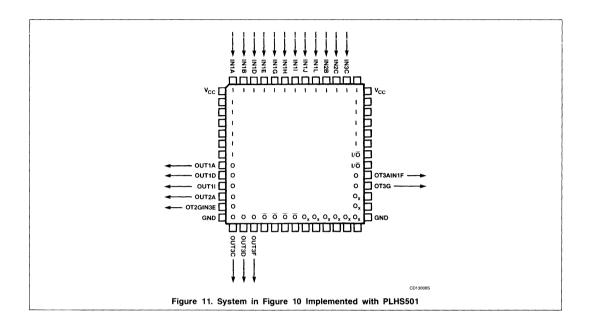

Designers using DRAM, VRAM and graphics will appreciate the speed and power of the new line of sequencers which include the PLC415, PLC42VA12, PLUS405 and PLUS105. These sequencers also make innovative bus and LAN controllers for emerging standard protocols. At last, the logical power of dual programmable arrays comes forth in the PLUS153 and PLUS173 devices—at 10 nanosecond propagation delays. The PLC18V8Z is the only zero power 20—pin device which can replace 16V8's! And finally, our –7 and D speed PAL-type devices are the industry's fastest. For maximum density in a truly compact system, the Programmable Macro Logic family now boasts four members—the PML2552 and PLHS601 are added to the original PLHS501 and PLHS502. The PML2552 is the PLD industry's first dense device to implement SCAN test.

To complement the devices, AMAZE design software is offered through our Sales Offices (see Section 11) and SNAP software is available for high level support. Read about them under Product Support.

Expanding customer service has been an ongoing effort. Our Applications staff is available to answer your technical questions on PLD designs and our free computer Bulletin Board, with 24-hour service, is at (800)451-6644.

New PLD users are encouraged to read the Introduction and AN8 for an overview of PLD ideas. More seasoned PLD users are encouraged to go through the PLD applications and PML applications at the end of the handbook to gain understanding and ideas for new designs.

### **Product Status**

**Programmable Logic Devices**

| DEFINITIONS                                     |                        |                                                                                                                                                                                                                                              |  |  |  |  |

|-------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Data Sheet<br>Identification                    | Product Status         | Definition                                                                                                                                                                                                                                   |  |  |  |  |

| Objective Specification                         | Formative or in Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                           |  |  |  |  |

| Preliminary Specification Preproduction Product |                        | This data sheet contains preliminary data and supplementary data will be published at a later date. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |  |  |  |  |

| Product Specification                           | Full Production        | This data sheet contains Final Specifications. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                      |  |  |  |  |

### Contents

#### **Programmable Logic Devices**

| Preface                                            |                                                                                         | ii  |

|----------------------------------------------------|-----------------------------------------------------------------------------------------|-----|

| Product Status                                     |                                                                                         | iv  |

| Selection Guide                                    | nation                                                                                  | 4   |

|                                                    | grammable Logic                                                                         |     |

| Section 3 – PAL <sup>®</sup> -Type De<br>Series 20 | vices Data Sheets                                                                       |     |

| PLHS16L8A/B                                        | PAL <sup>®</sup> -Type Devices (16 × 64 × 8)                                            | 39  |

| PLUS16R8D/-7                                       | PAL®—Type Devices (Includes: PLUS16L8D/–7, PLUS16R4D/–7, PLUS16R6D/–7, PLUS16R8D/–7)    |     |

| PHD16N8-5                                          | Programmable High Speed Decoder (16 × 16 × 8); 5ns                                      |     |

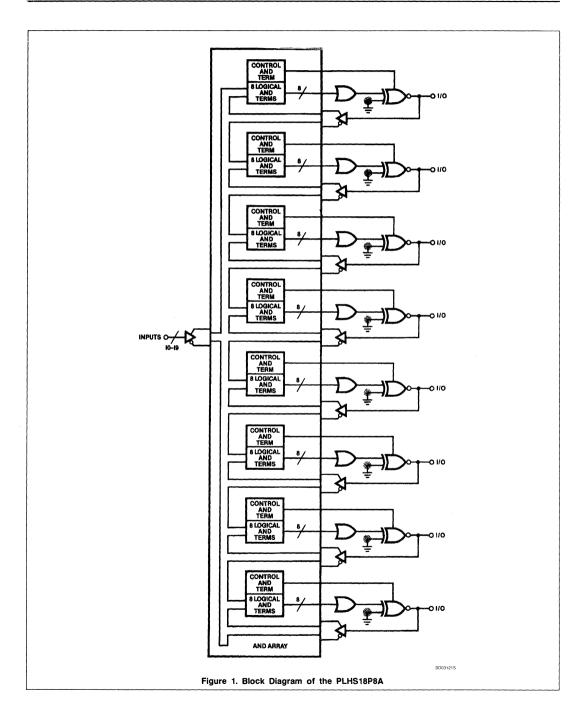

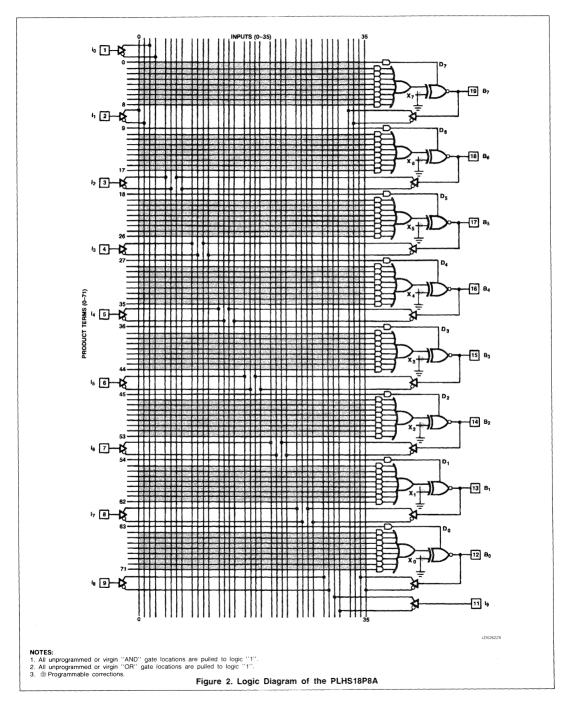

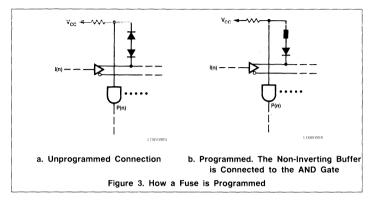

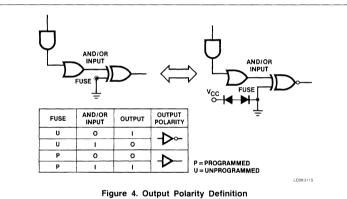

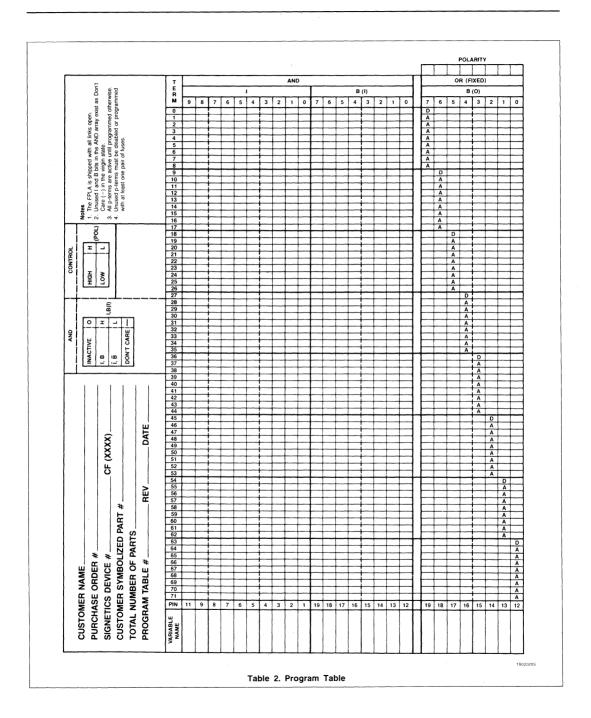

| PLHS18P8A/B                                        | PAL®-Type Devices                                                                       |     |

| PLC18V8Z/I<br>Series 24                            | PAL®-Type Devices                                                                       |     |

| 10H20EV8/10020EV8                                  | ECL PAL®-Type Devices                                                                   | 87  |

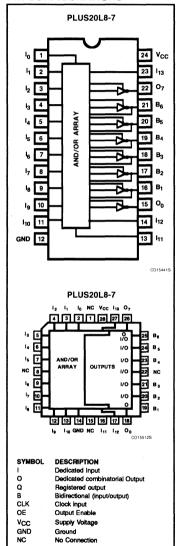

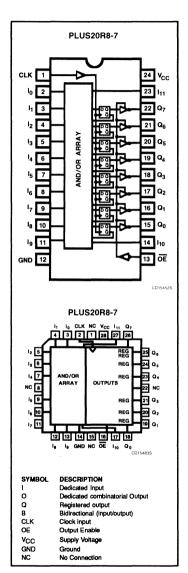

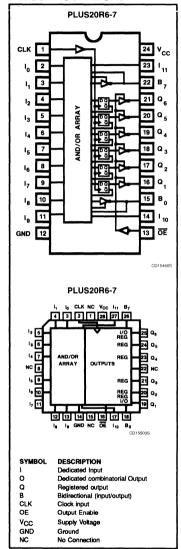

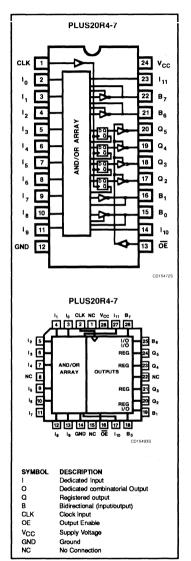

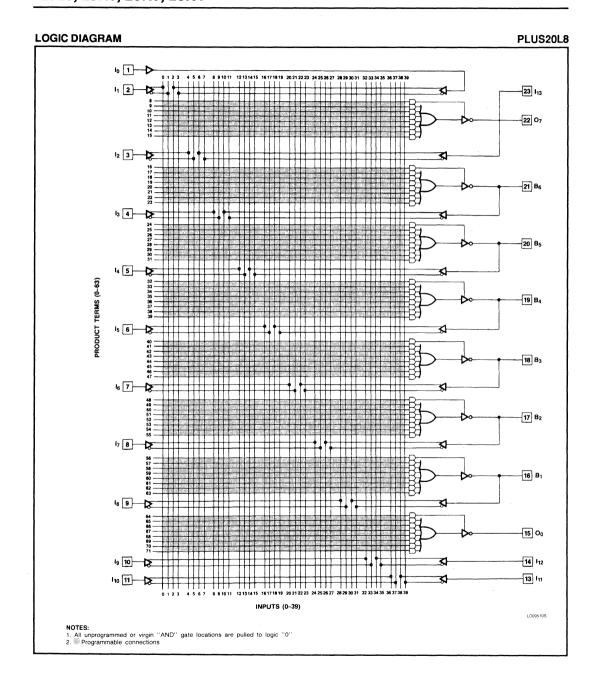

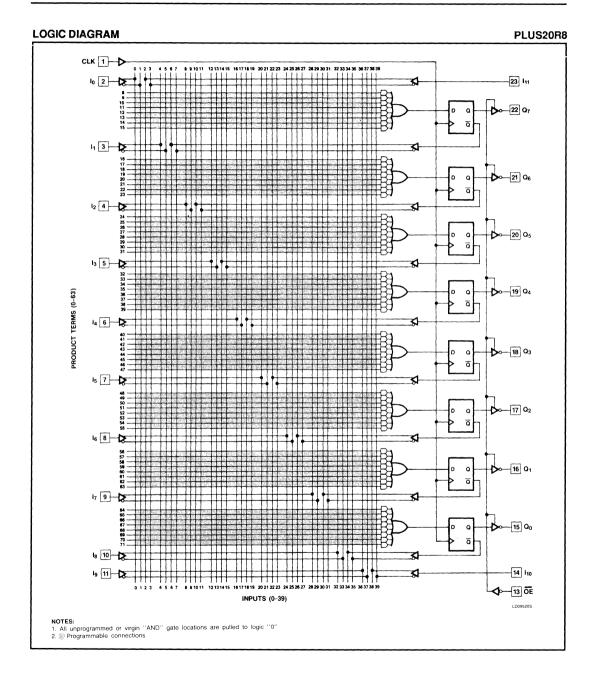

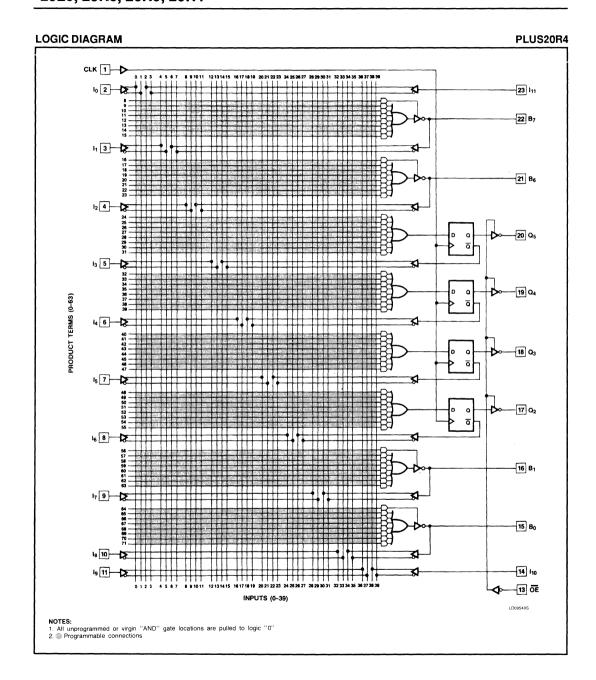

| PLUS20R8D/-7                                       | PAL®-Type Devices<br>(Includes: PLUS20L8D/-7, PLUS20R4D/-7, PLUS20R6D/-7, PLUS20R8D/-7) |     |

| Series 68                                          |                                                                                         |     |

| PHD48N22-7                                         | Programmable High Speed Decoder (48 × 73 × 22); 7.5ns                                   | 115 |

| Section 4 – Programmable<br>Series 20              | e Logic Array Devices Data Sheets                                                       |     |

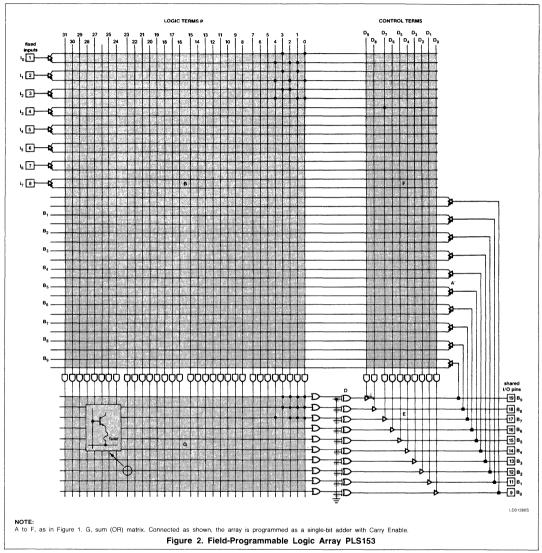

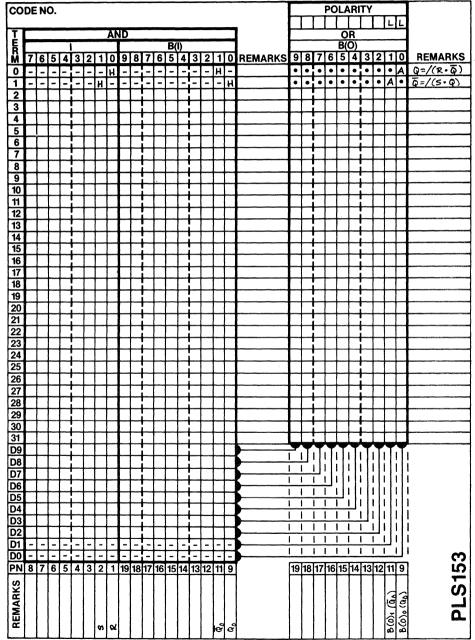

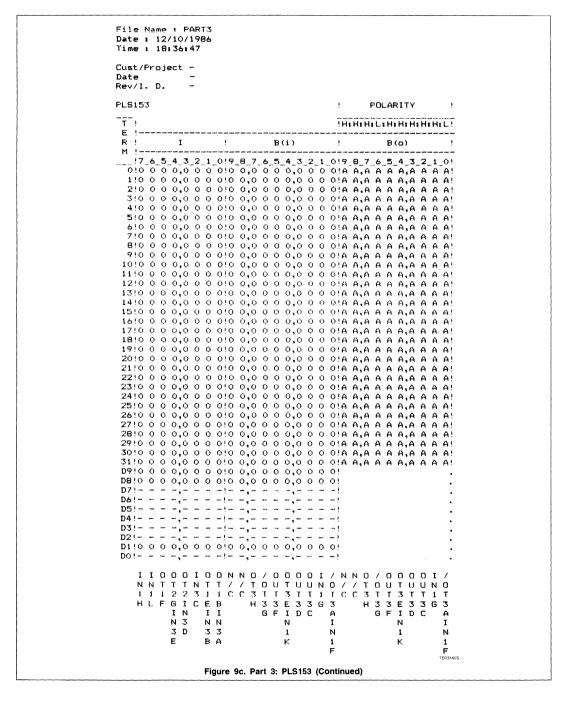

| PLS153/A                                           | Programmable Logic Arrays (18 × 42 × 10); 40/30ns                                       | 127 |

| PLUS153B/D                                         | Programmable Logic Arrays (18 × 42 × 10); 15/12ns                                       |     |

| PLUS153-10<br>Series 24                            | Programmable Logic Array (18 × 42 × 10); 10ns                                           |     |

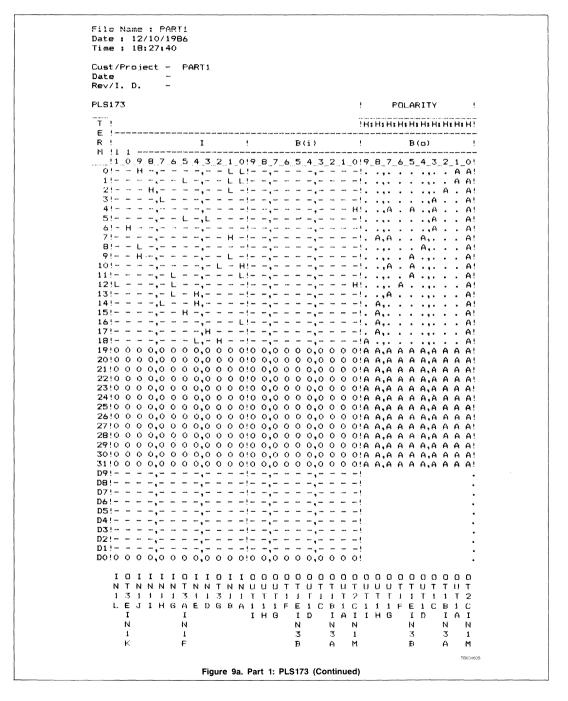

| PLS173                                             | Programmable Logic Array (22 × 42 × 10); 30ns                                           | 148 |

| PLUS173B/D                                         | Programmable Logic Arrays (22 × 42 × 10); 15/12ns                                       |     |

| PLUS173-10                                         | Programmable Logic Array (22 × 42 × 10); 10ns                                           |     |

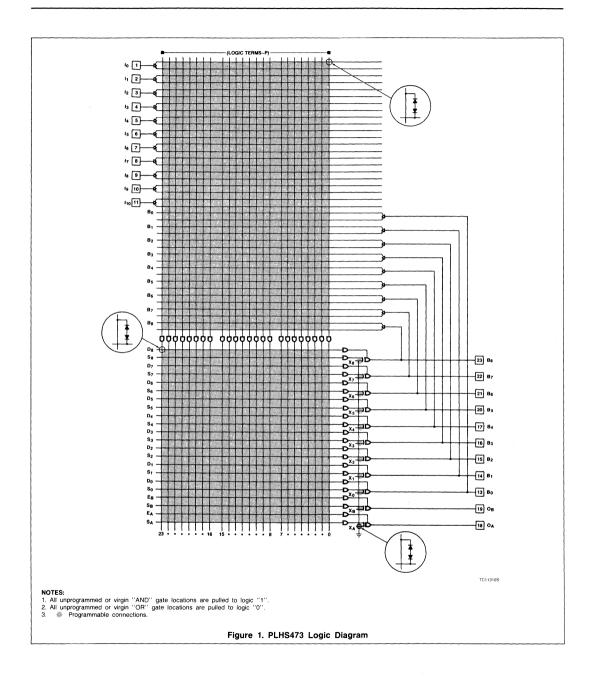

| PLHS473                                            | Programmable Logic Array (20 × 24 × 11); 22ns                                           |     |

| PLHS473S<br>Series 28                              | Programmable Logic Array (20 × 24 × 11); 25ns                                           |     |

| PLS100/101                                         | Programmable Logic Arrays (16 × 48 × 8); 50ns                                           | 181 |

#### **Contents**

| Section 5 – Programmab<br>Series 20 | ele logic Sequencer Devices Data Sheets                          |            |

|-------------------------------------|------------------------------------------------------------------|------------|

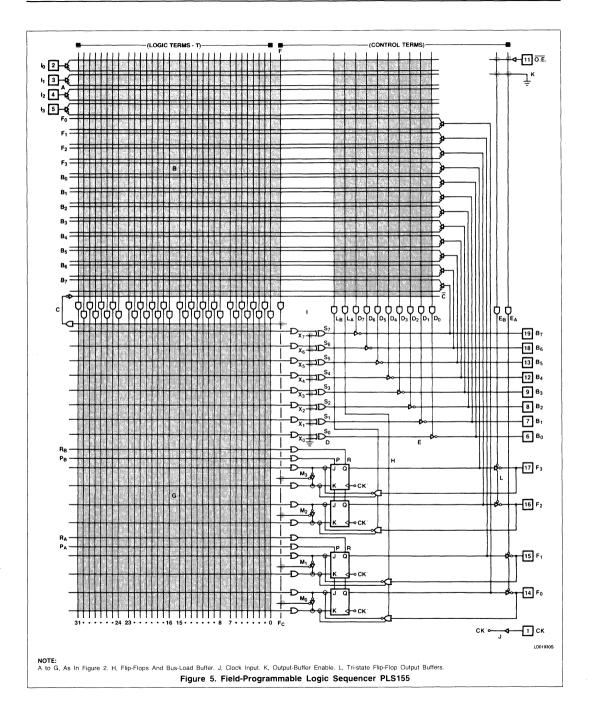

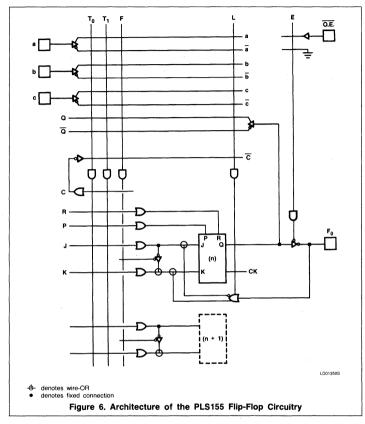

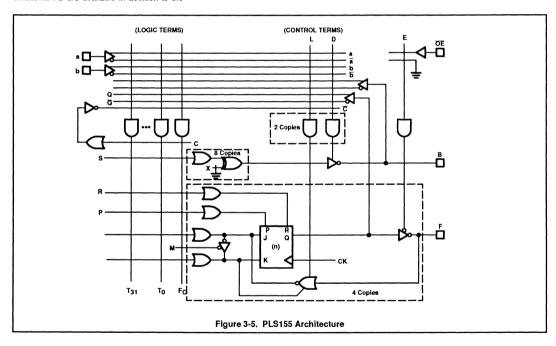

| PLS155                              | Programmable Logic Sequencer (16 × 45 × 12); 14MHz               | 191        |

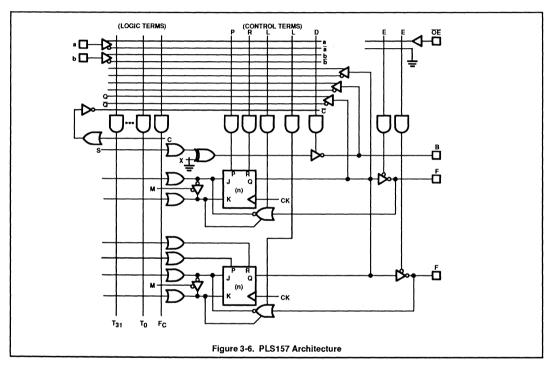

| PLS157                              | Programmable Logic Sequencer (16 × 45 × 12); 14MHz               | 202        |

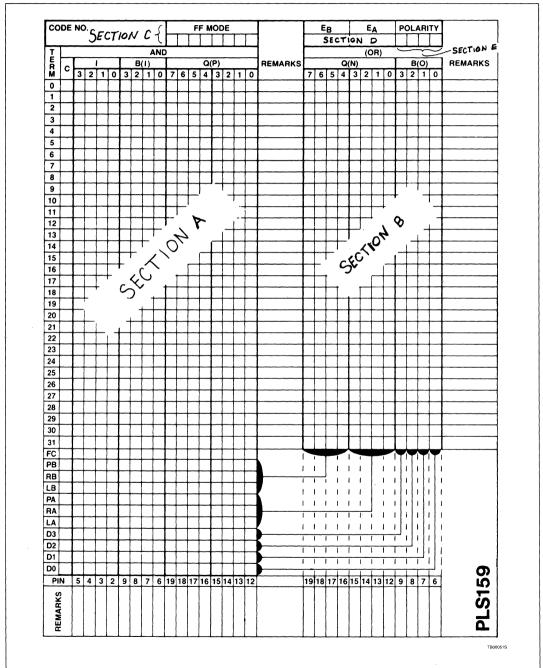

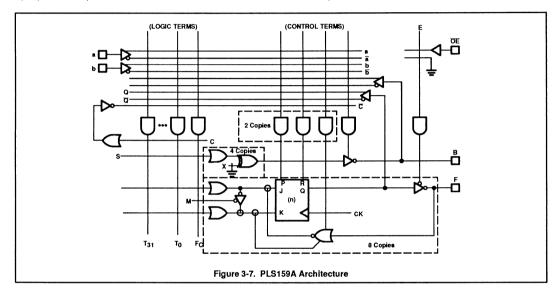

| PLS159A                             | Programmable Logic Sequencer (16 × 45 × 12); 18MHz               | 213        |

| Series 24                           |                                                                  |            |

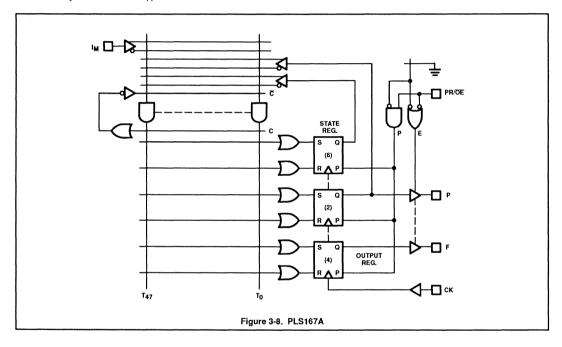

| PLS167/A                            | Programmable Logic Sequencers (14 × 48 × 6); 14, 20MHz           | 223        |

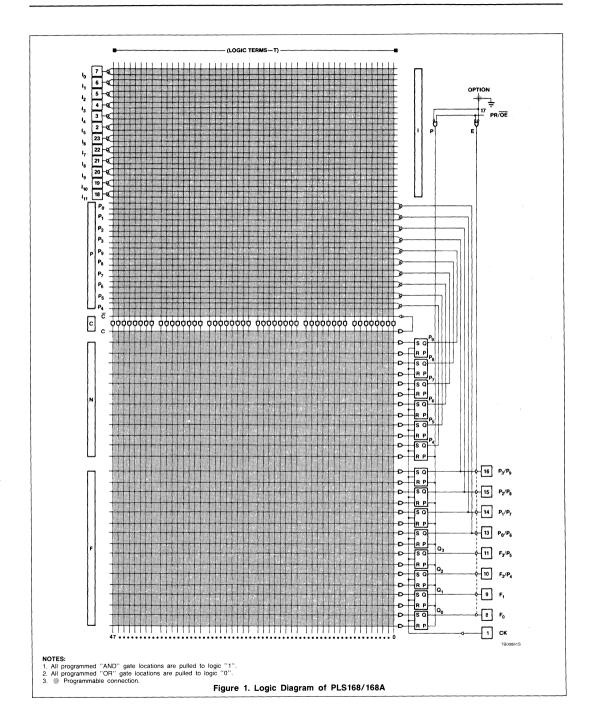

| PLS168/A                            | Programmable Logic Sequencers (12 × 48 × 8); 14, 20MHz           | 234        |

| PLS179                              | Programmable Logic Sequencer (20 $\times$ 45 $\times$ 12); 18MHz | 245        |

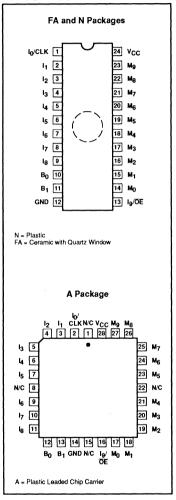

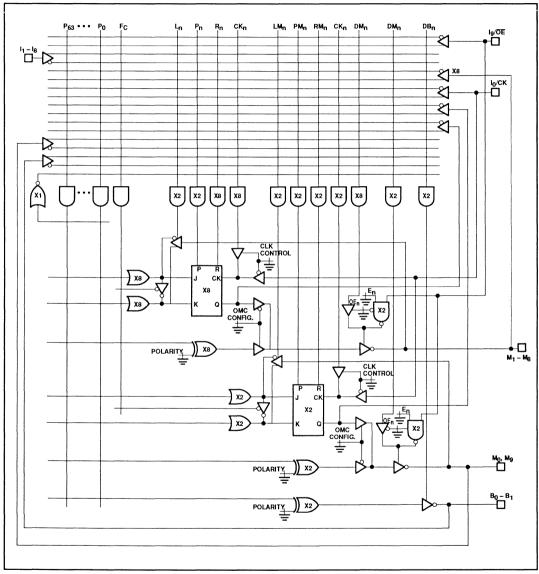

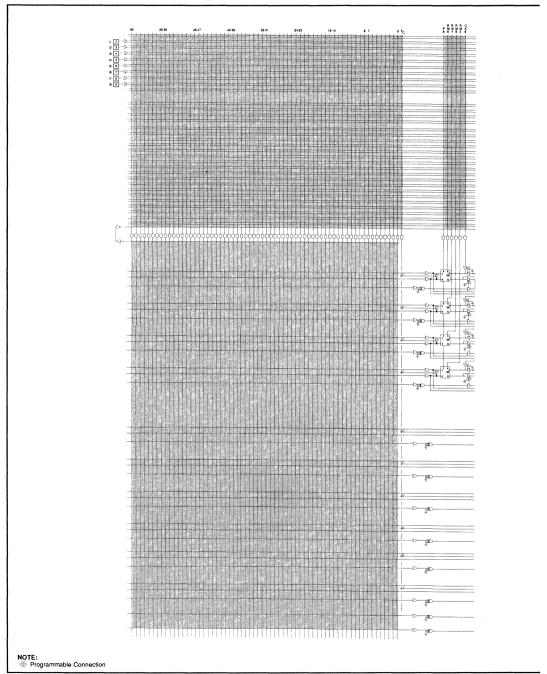

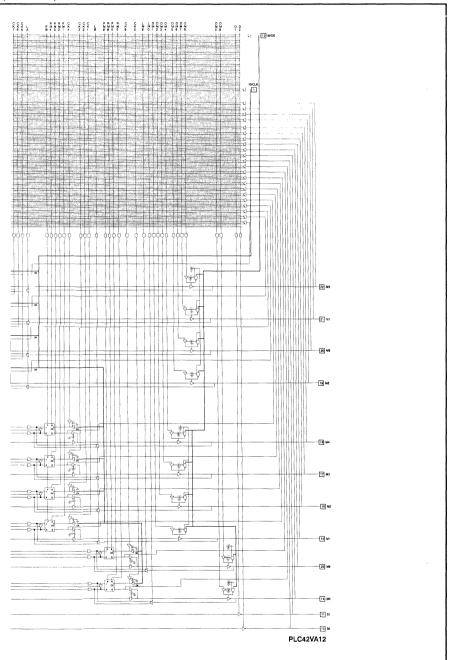

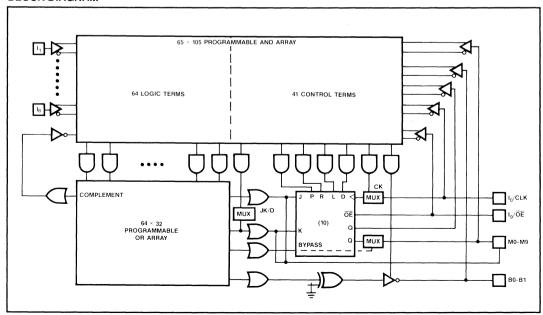

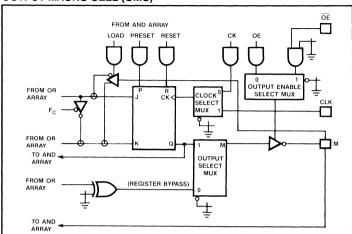

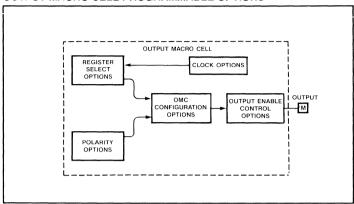

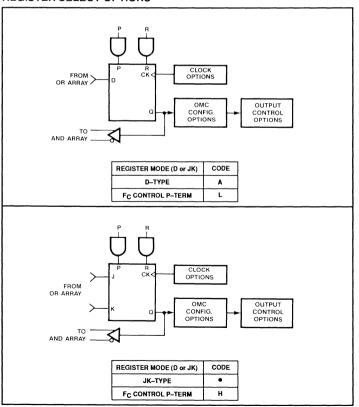

| PLC42VA12<br>Series 28              | CMOS Programmable Logic Sequencer (42 × 105 × 12); 25MHz         | 256        |

| PLC415-16                           | Programmable Logic Sequencer (17 × 68 × 8); 16MHz                | 275        |

| PLS105/A                            | Programmable Logic Sequencers (16 × 48 × 8); 14, 20MHz           | 294        |

| PLUS105-40                          | Programmable Logic Sequencer (16 × 48 × 8); 40MHz                | 305        |

| PLUS105-55                          | Programmable Logic Sequencer (16 × 48 × 8); 55MHz                | 317        |

| PLUS405-37/-45                      | Programmable Logic Sequencers (16 × 64 × 8); 37, 45MHz           | 329        |

| PLUS405-55                          | Programmable Logic Sequencer (16 × 64 × 8); 55MHz                | 344        |

| Section 6 – Programmab              | ole Macro Logic Devices Data Sheets                              |            |

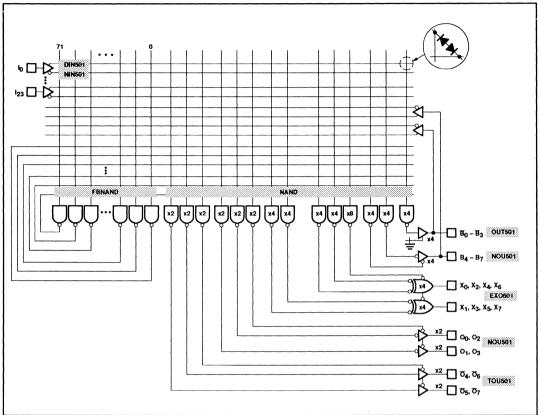

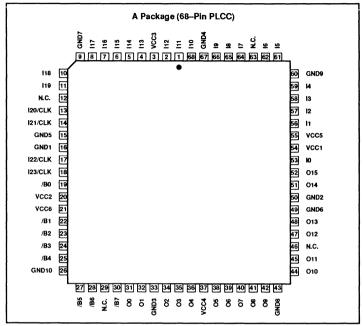

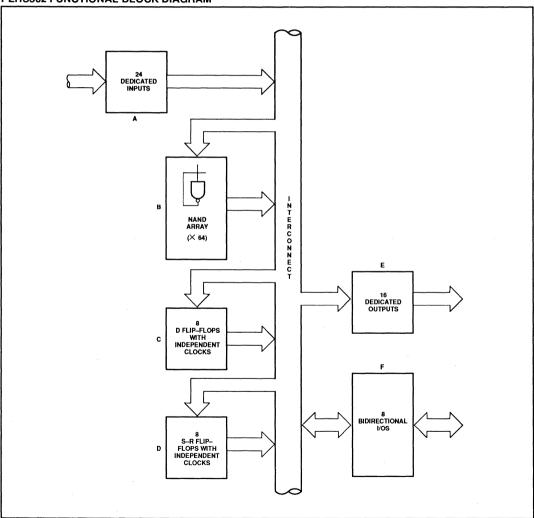

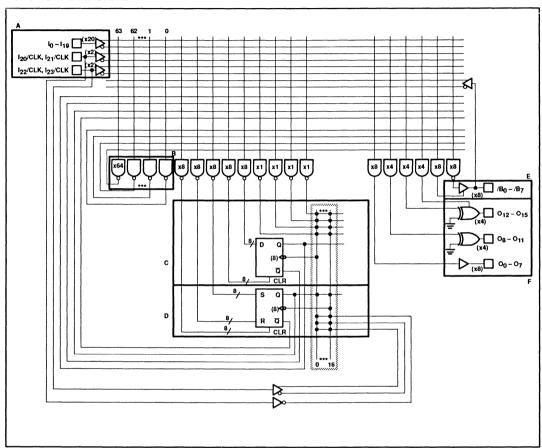

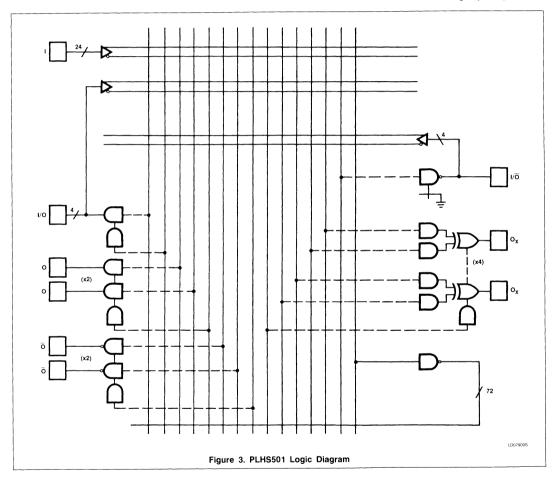

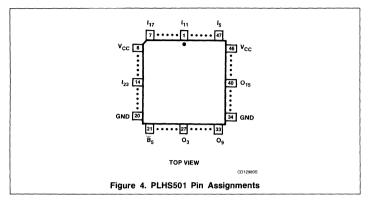

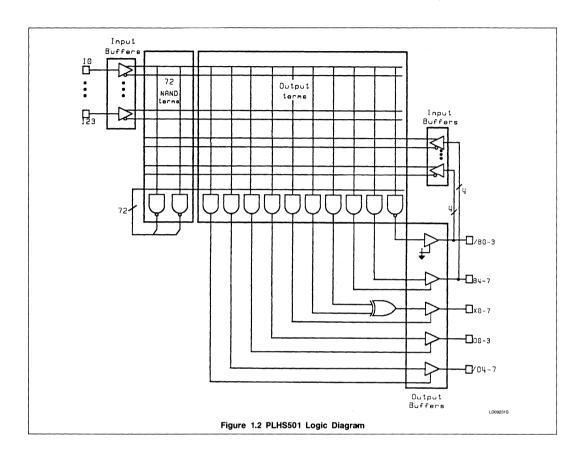

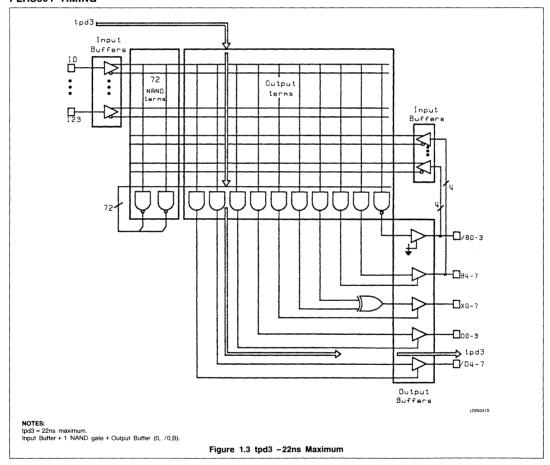

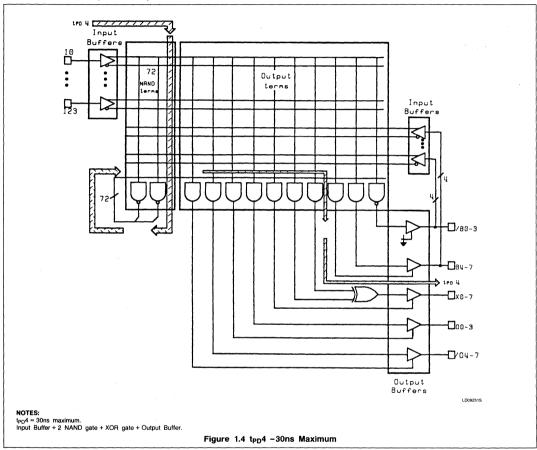

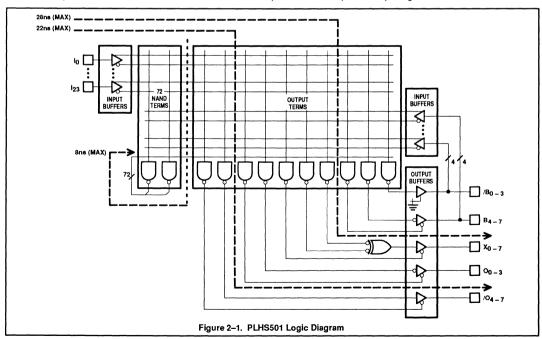

| PLHS501                             | Programmable Macro Logic                                         | 361        |

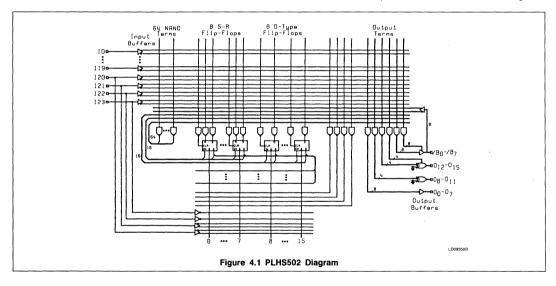

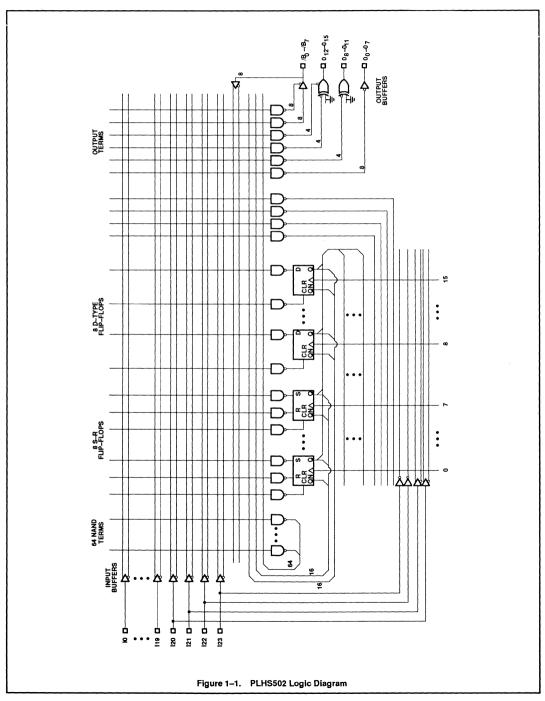

| PLHS502                             | Programmable Macro Logic                                         | 372        |

| PLHS601                             | Programmable Macro Logic                                         | 384        |

| PML2552                             | Programmable Macro Logic                                         | 395        |

| Section 7 – Military Prod           | ucts                                                             |            |

|                                     | Military Selection Guide                                         | 417        |

| Section 8 – Development             | t Software                                                       |            |

|                                     | AMAZE – Automatic Map and Zap Equations Design Software          | 421        |

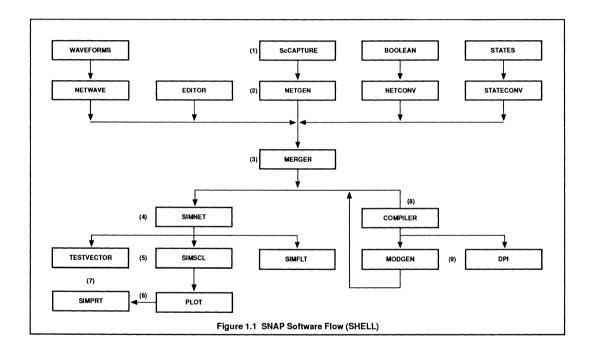

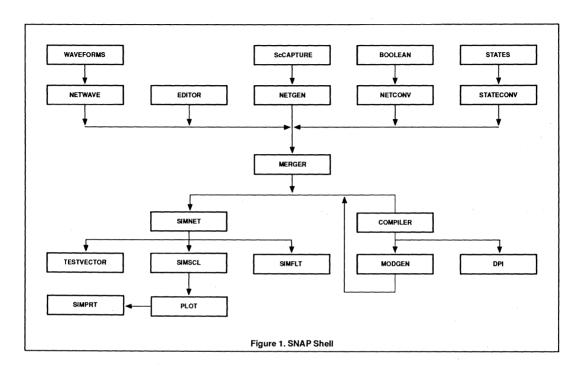

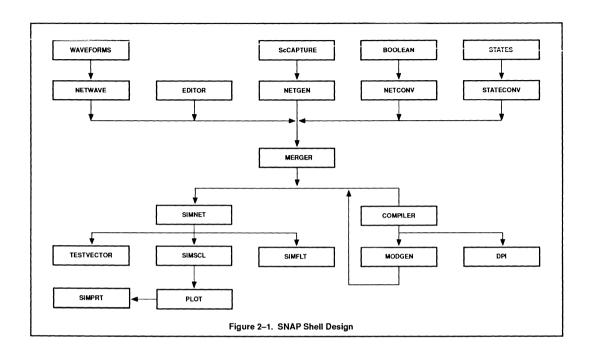

|                                     | SNAP – Synthesis Netlist Analysis and Program Software           | 425        |

|                                     | SNAP Data Sheet                                                  | 427        |

|                                     | Device Programmer Reference Guide                                | 429        |

| Section 9 – Application N           | Notes                                                            |            |

| PLD Application Not                 | es                                                               |            |

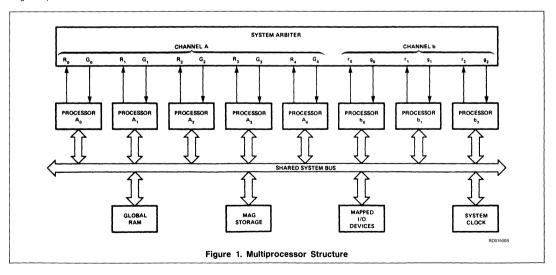

| AN7                                 | Single Chip Multiprocessor Arbiter                               | 435        |

| AN8                                 | Introduction to Signetics Programmable Logic                     | 447        |

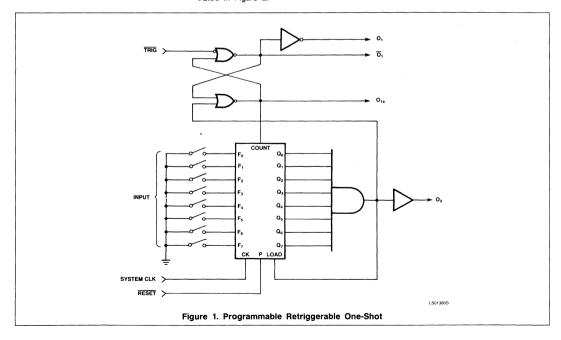

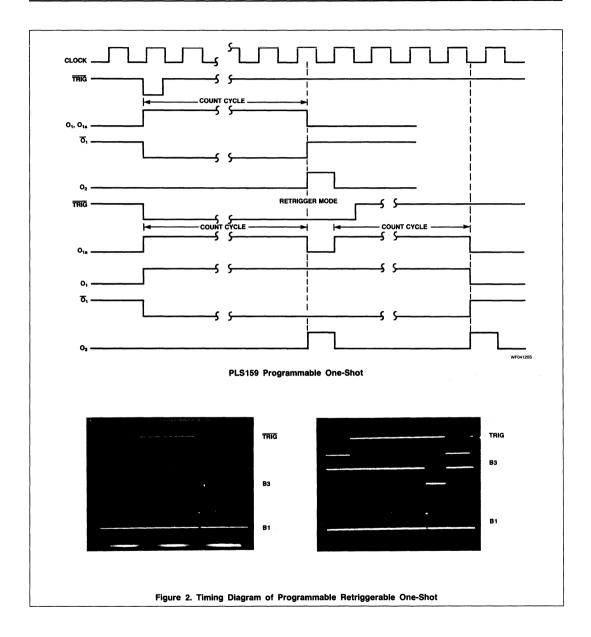

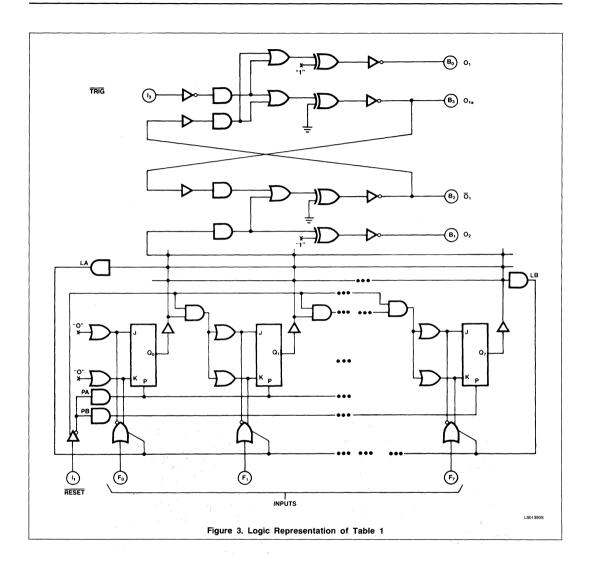

| AN11                                | PLD Programmable Retriggerable One–Shot                          | 459        |

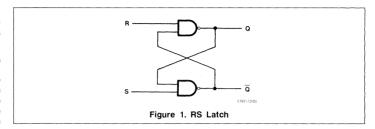

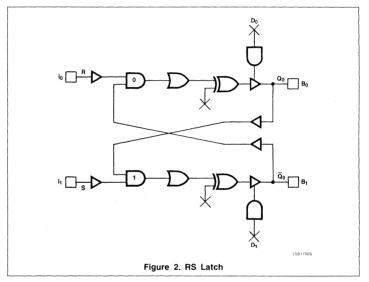

| AN14                                | Latches and Flip–Flops with PLS153                               | 463        |

| AN15                                | PLS159 Primer                                                    | 476        |

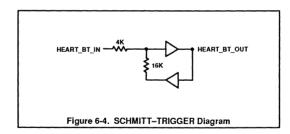

| AN18<br>AN21                        | Schmitt Trigger Using PLS153 and PLS159                          | 487        |

| AN23                                | 9–Bit Parity Generator/Checker with PLS153/153A                  | 495        |

| AN24                                | PLS168/168A Primer                                               | 501<br>514 |

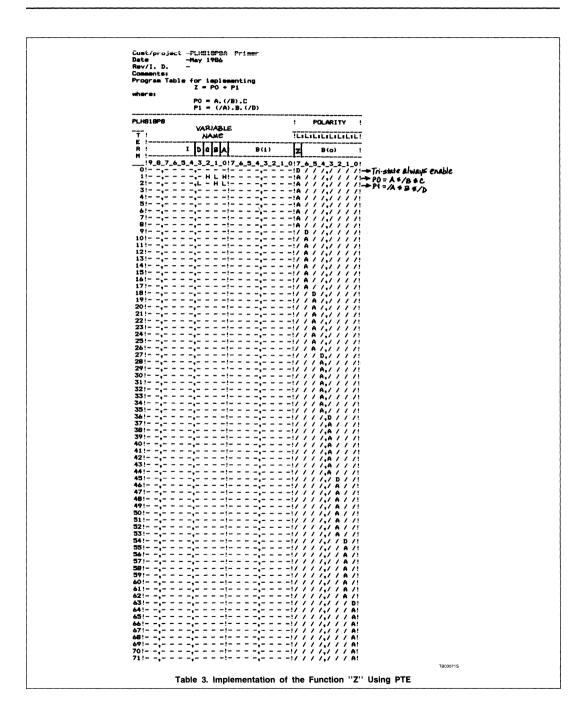

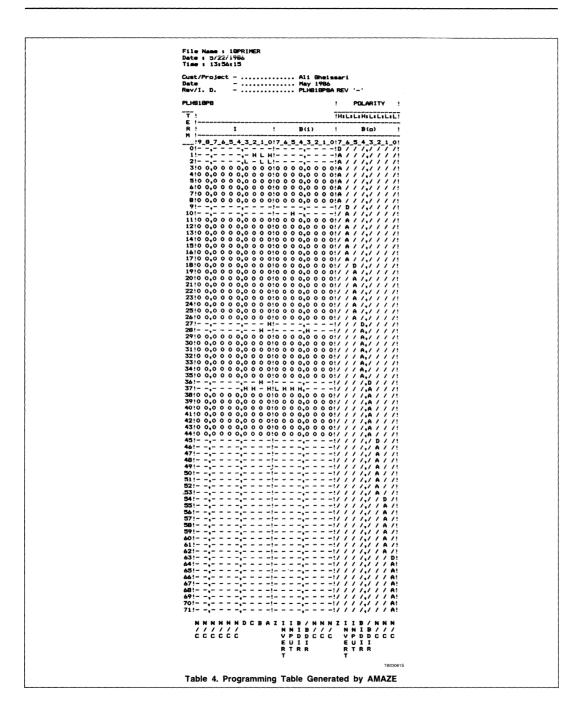

| AN26                                | PLHS18P8A Primer                                                 | 520        |

| AN27                                | PLHS473 Primer                                                   | 529        |

| AN28                                | High-Speed 12-Bit Tracking A/D Converter Using PLS179            | 537        |

| PML Application Not                 |                                                                  |            |

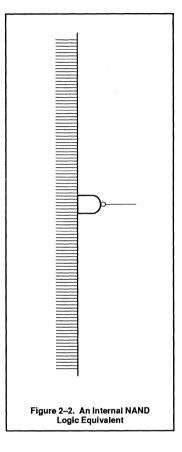

| AN29                                | PLHS501 Programmable Macro Logic Primer                          | 547        |

| PLHS501 Application                 | n Notes, Vol. 1: Designing with Programmable Macro Logic         |            |

| Chapter 1                           | Introduction to PML Design Concepts                              | 562        |

|                                     | Performance                                                      | 562        |

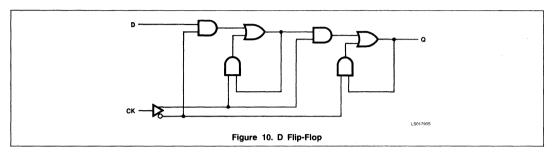

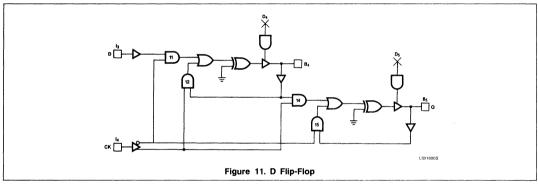

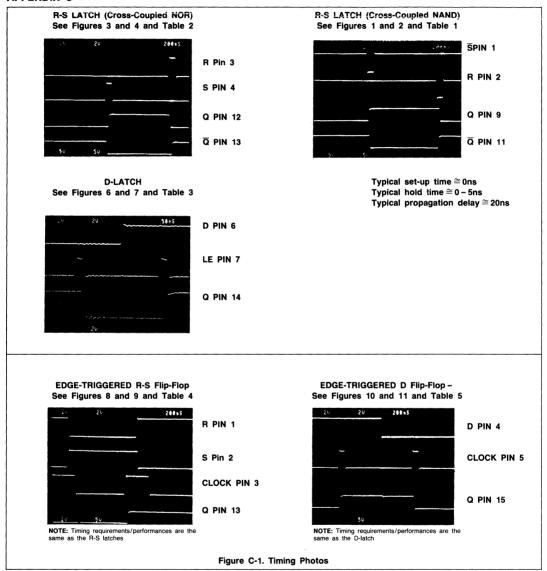

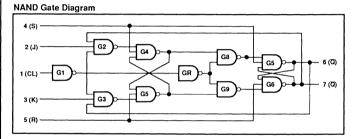

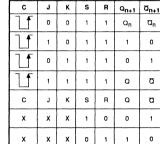

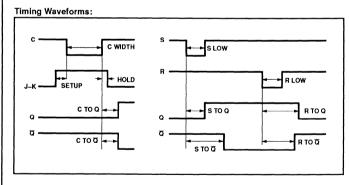

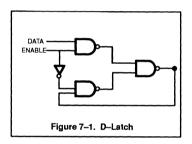

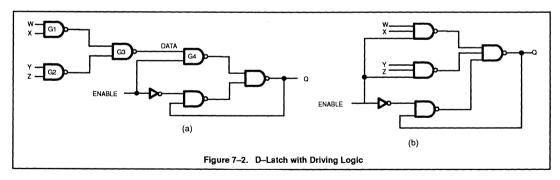

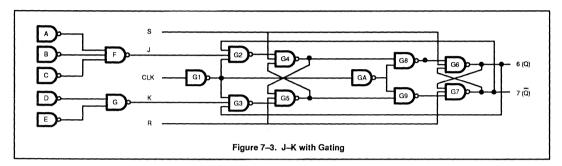

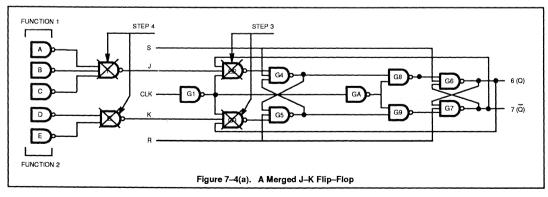

|                                     | NAND Gate Flip-Flops                                             | 569        |

| Chapter 2                           | Functional Fit                                                   | 572        |

| Chapter 3                           | Design Examples                                                  | 575        |

| Chapter 4                           | Successor Architectures                                          | 580        |

January 1990

#### **Contents**

| Chapter 5                    | Support Issues                                        | 581 |

|------------------------------|-------------------------------------------------------|-----|

| Chapter 6                    | PLHS501 Examples Using AMAZE Revision 1.6             | 582 |

|                              | Simple Gate Implementations                           | 582 |

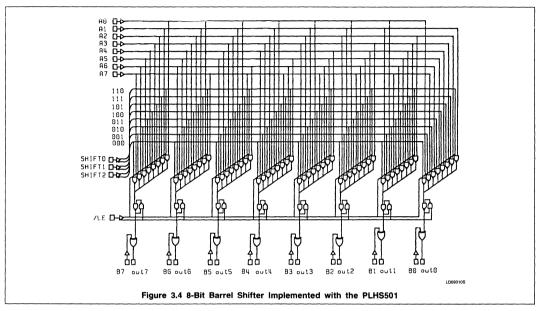

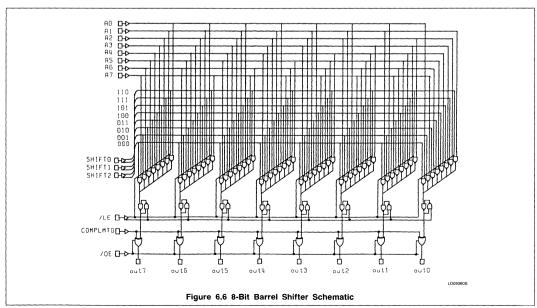

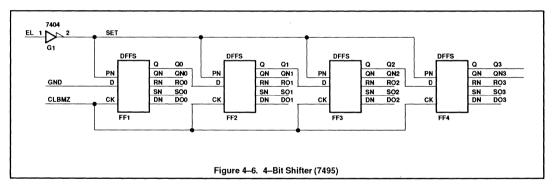

|                              | 8-Bit Barrel Shifter                                  | 585 |

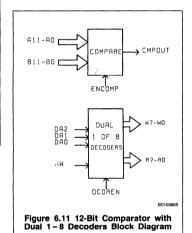

|                              | 12-Bit Comparator with Dual 1-of-8 Decoders           | 591 |

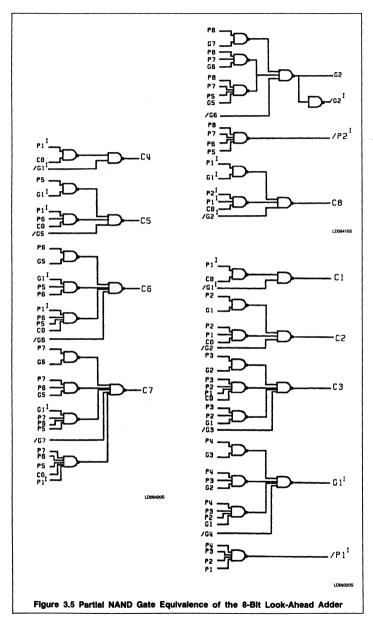

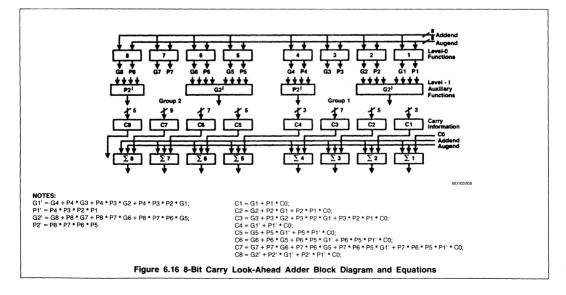

|                              | 8-Bit Carry Look-Ahead Adder                          | 594 |

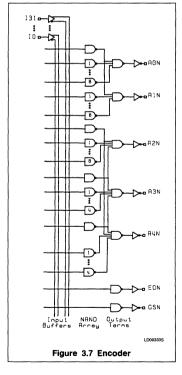

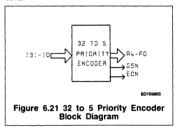

|                              | 32-to-5-Bit Priority Encoder                          | 597 |

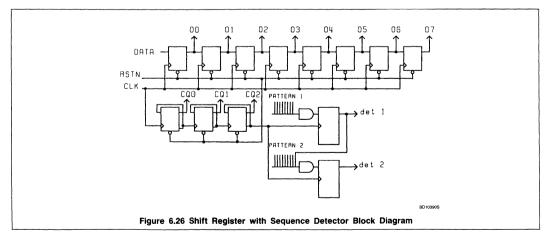

|                              | 8-Bit Shift Register with Sequence Detector           | 602 |

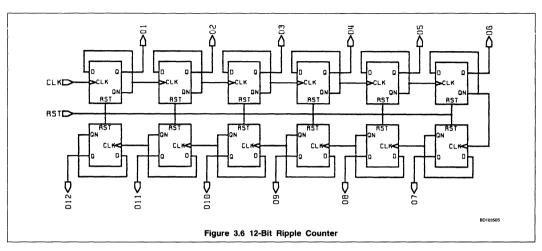

|                              | 4-Bit Synchronous Counter                             | 608 |

| PLHS501 Application No       | otes, Vol. 2: Designing with Programmable Macro Logic |     |

| Chapter 1                    | Introduction                                          | 612 |

| Chapter 2                    | PLHS501 Review                                        | 613 |

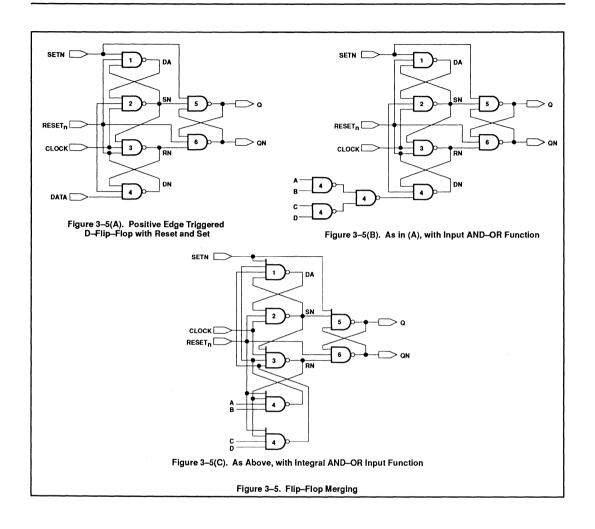

| Chapter 3                    | Flip-Flop Basics                                      | 615 |

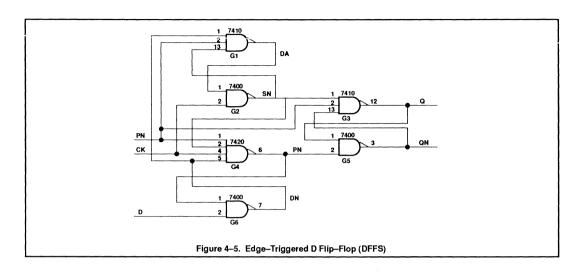

| •                            | Notation                                              | 615 |

|                              | Flip-Flop Merging                                     | 615 |

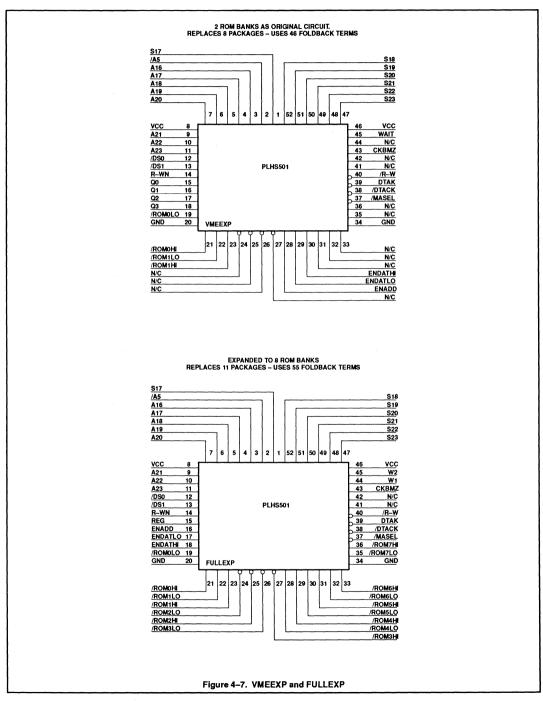

| Chapter 4                    | VME Bus Examples                                      | 621 |

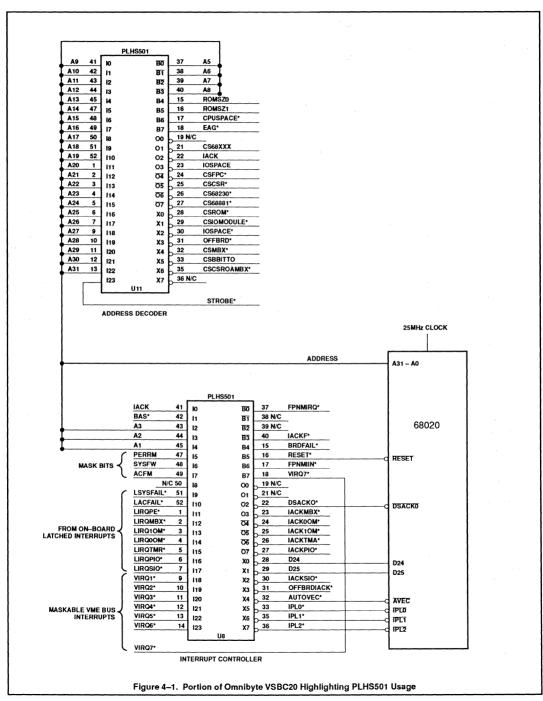

| ·                            | Omnibyte VSBC20 Mailbox Interrupt Structure           | 621 |

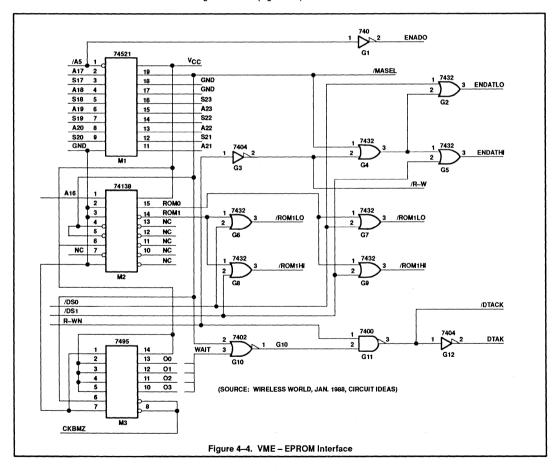

|                              | VME Bus EPROM Interface                               | 626 |

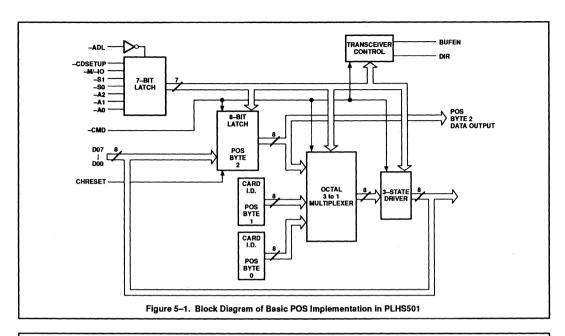

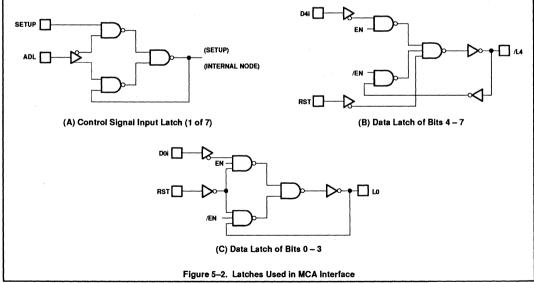

| Chapter 5                    | Micro Channel Interface                               | 633 |

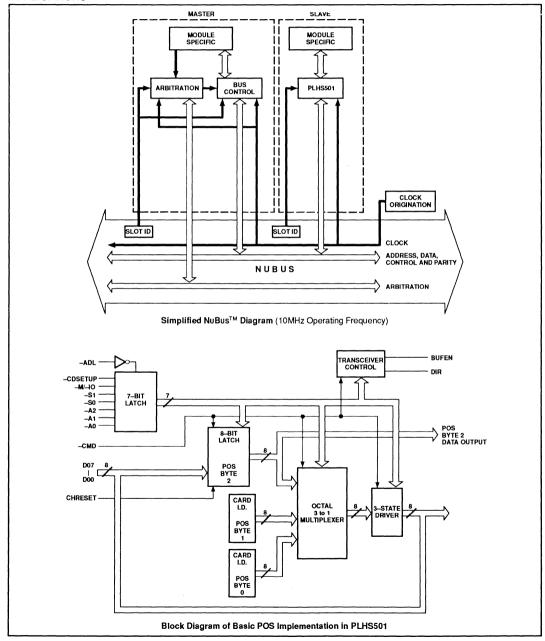

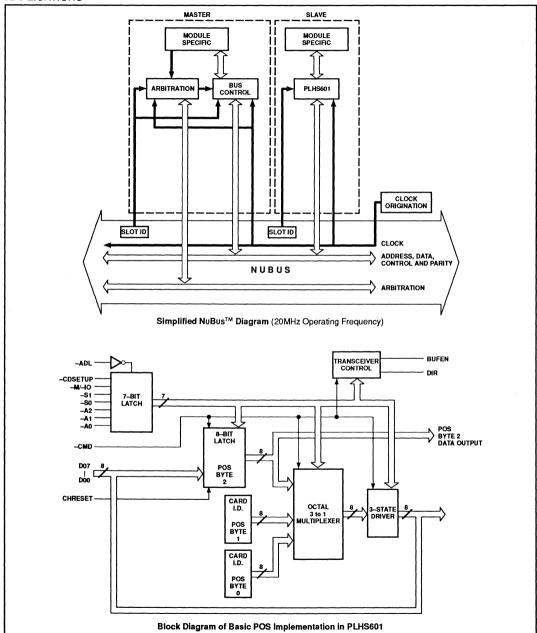

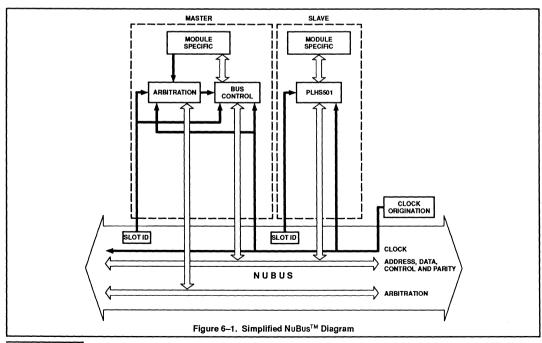

| Chapter 6                    | NuBus Interface                                       | 638 |

| Chapter 7                    | Nuggets                                               | 644 |

| ·                            | Data Bus Parity                                       | 644 |

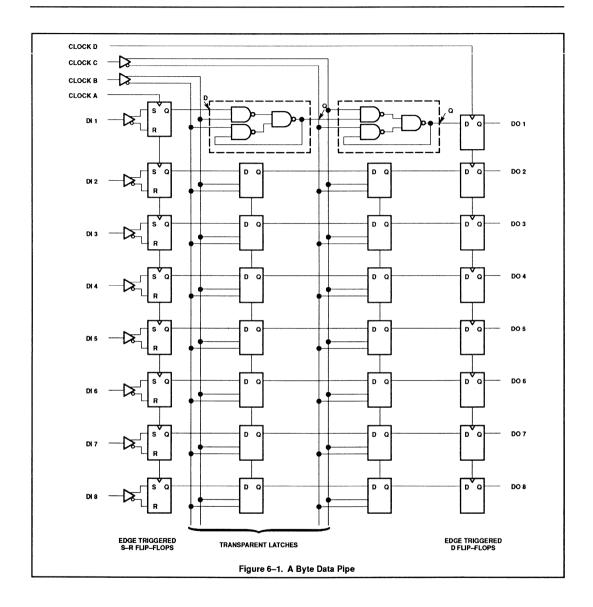

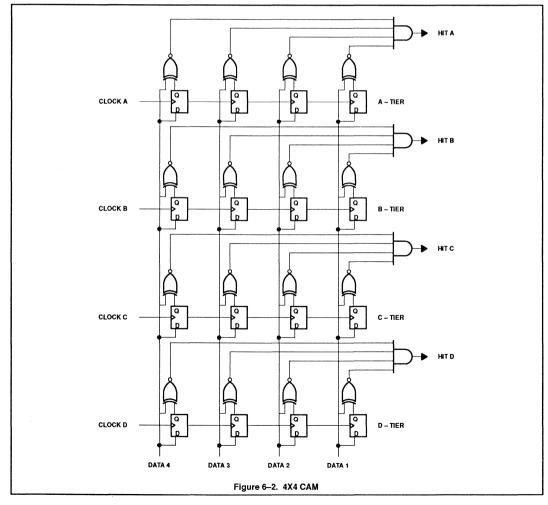

|                              | Data Bus Operations                                   | 651 |

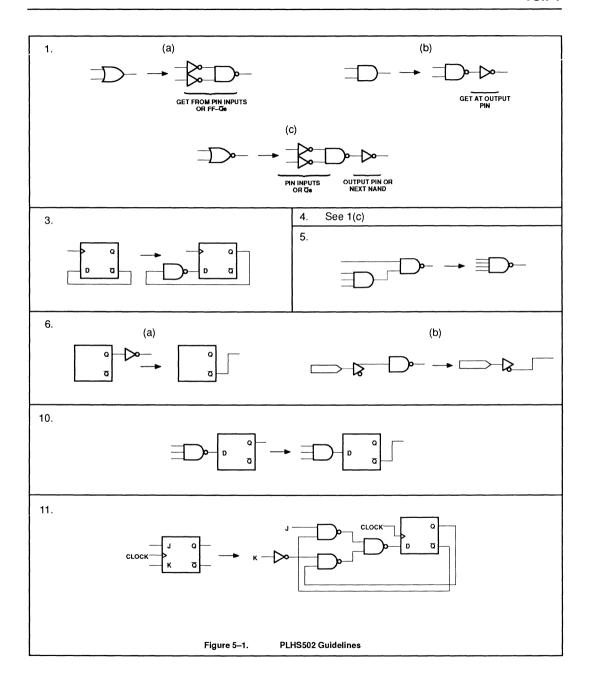

| PLHS502 Application No       | otes, Vol. 1: Designing with Programmable Macro Logic |     |

| Chapter 1                    | Introduction                                          | 652 |

| Chapter 2                    | Development Support                                   | 654 |

| Chapter 3                    | Capacity and Partitioning Considerations              | 656 |

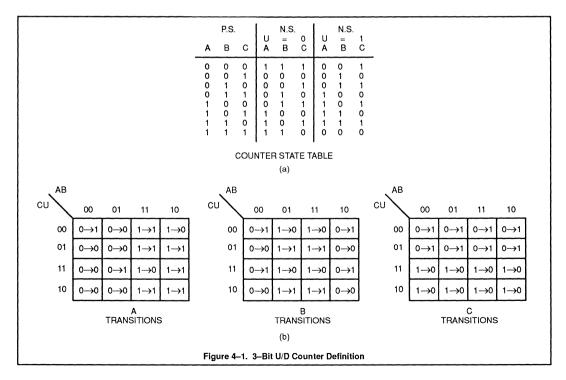

| Chapter 4                    | State Machine Design                                  | 657 |

| Chapter 5                    | Additional Design Guidelines                          | 668 |

| Chapter 6                    | Additional PLHS501 Applications                       | 670 |

| Chapter 7                    | Advanced Flip-Flop Merging                            | 689 |

| Programmable Logic De        | sign and Application Notes                            |     |

|                              | Introduction                                          | 691 |

|                              | Acknowledgements                                      | 691 |

|                              | AMAZE Software                                        | 691 |

| Product Section Introduction | on                                                    | 691 |

| Chapter 1                    | PLA Devices                                           | 692 |

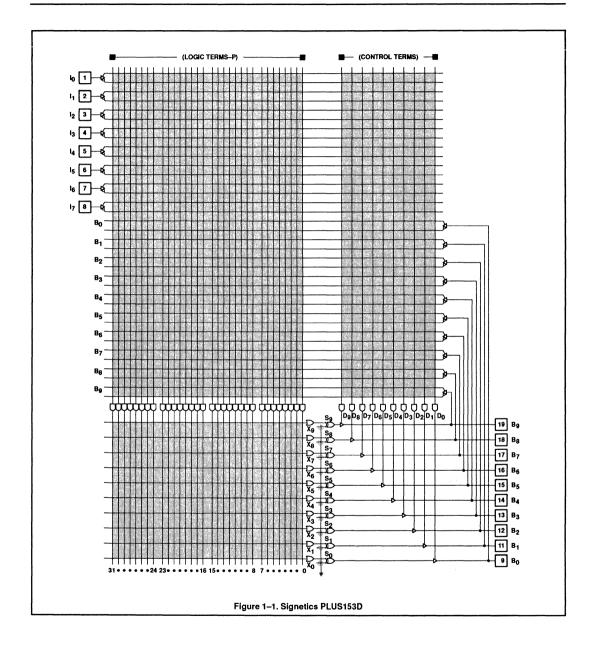

| ·                            | Signetics PLUS153D                                    | 692 |

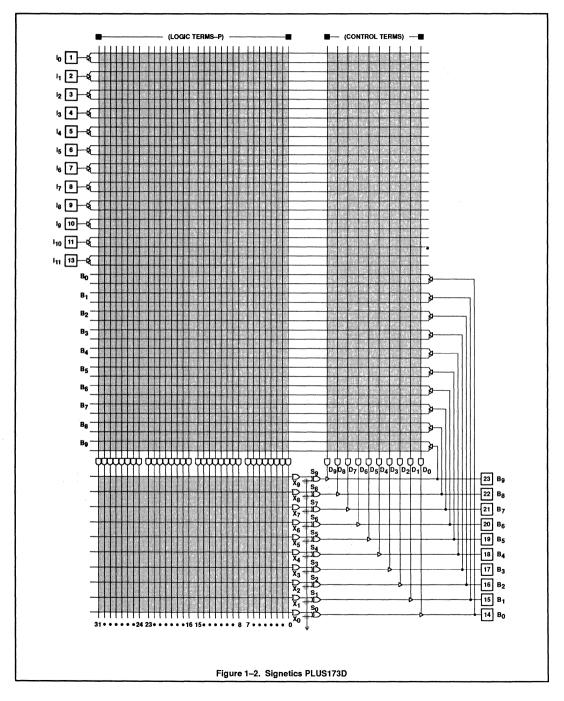

|                              | Signetics PLUS173D                                    | 692 |

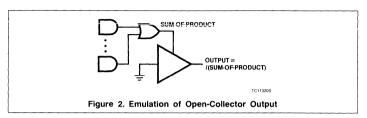

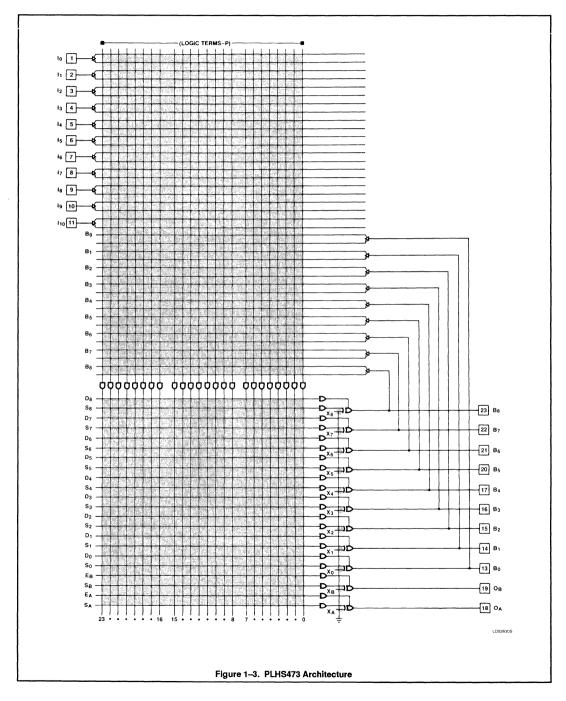

|                              | The PLHS473                                           | 692 |

| Chapter 2                    | PAL-Type Devices                                      | 696 |

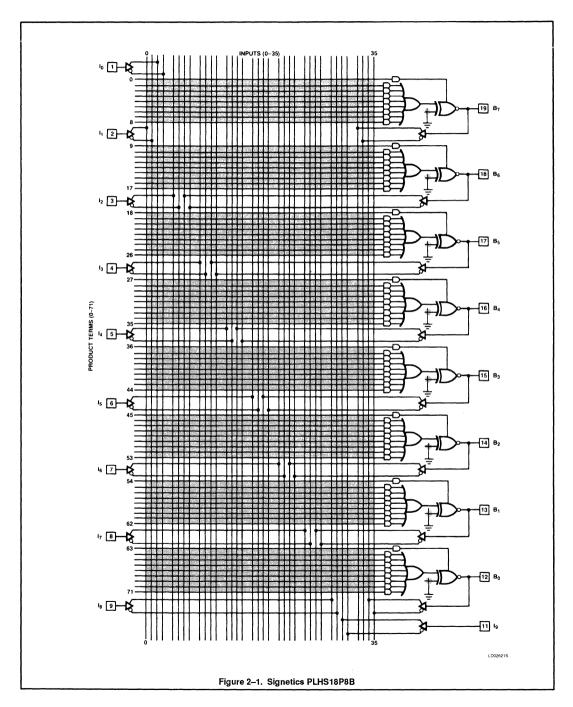

|                              | Signetics PLHS18P8B                                   | 696 |

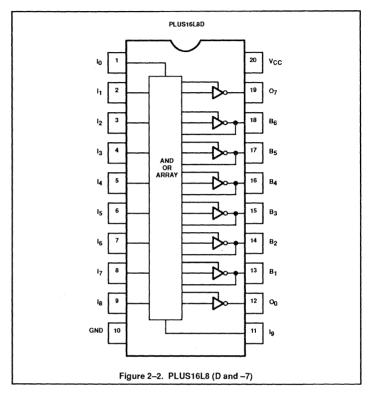

|                              | The PLUS16L8D and –7                                  | 698 |

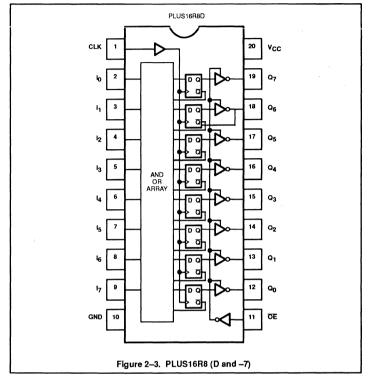

|                              | The PLUS16R8D and –7                                  | 699 |

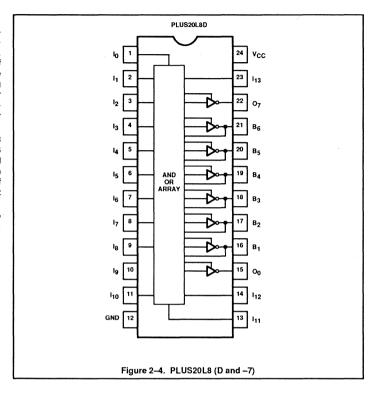

|                              | The PLUS20L8D and –7                                  | 700 |

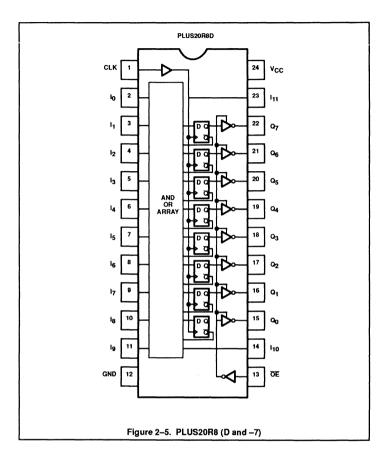

|                              | The PLUS20R8D and –7                                  | 701 |

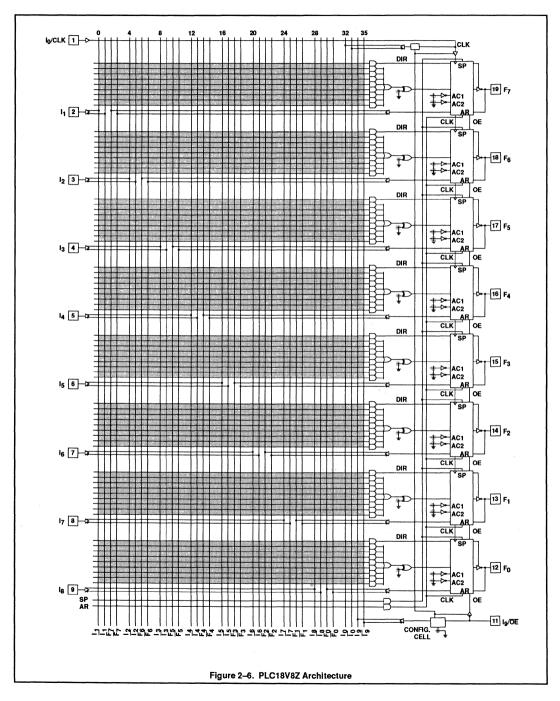

|                              | The PLC18V8Z                                          | 701 |

| Chapter 3                    | Sequencer Devices                                     | 703 |

|                              | Introduction                                          | 703 |

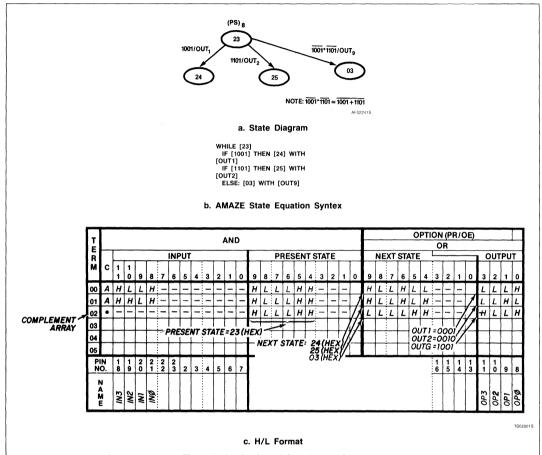

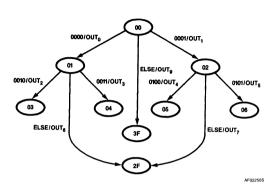

|                              | State Equation Tutorial                               | 704 |

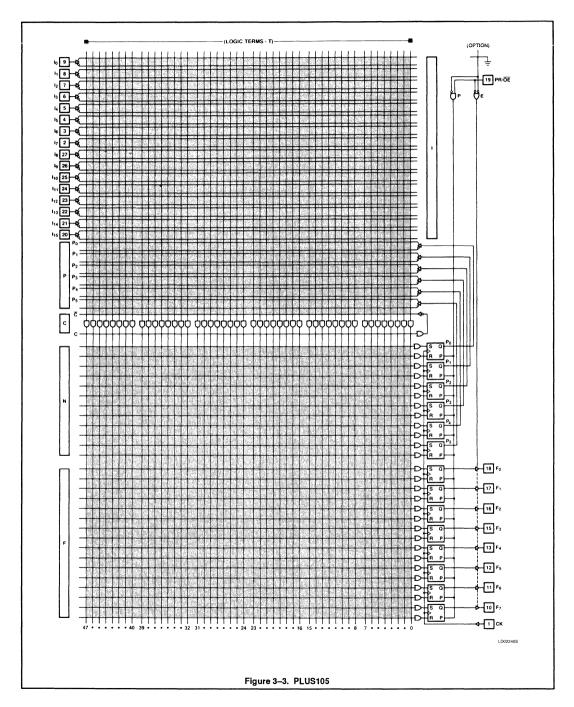

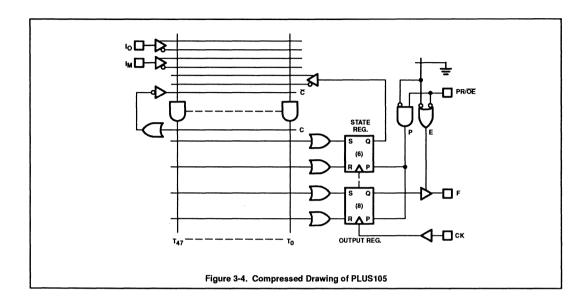

|                              | The PLUS105                                           | 704 |

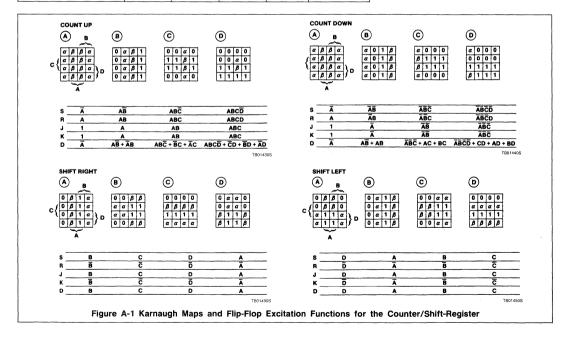

|                              | The PLS155                                            | 707 |

|                              | The PLS157                                            | 708 |

|                              | The PLS159A                                           | 709 |

|                              | The PLS167A                                           | 710 |

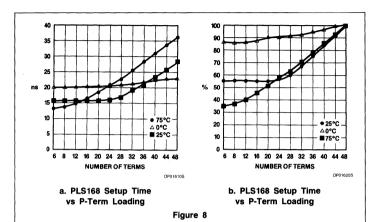

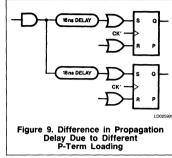

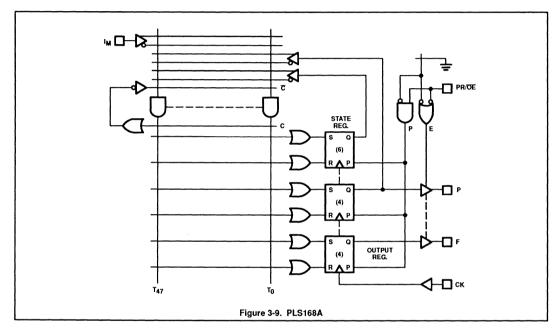

|                              | The PLS168A                                           | 711 |

|                              |                                                       |     |

#### **Contents**

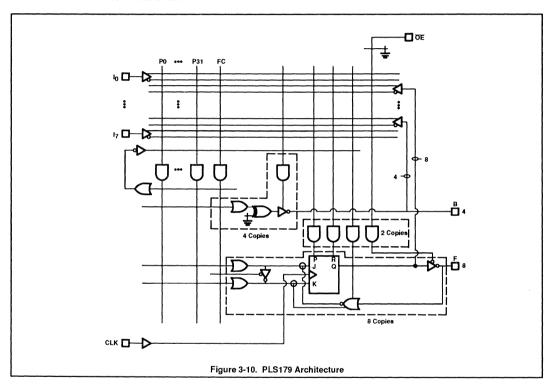

|                                          | The PLS179                                       | 712  |

|------------------------------------------|--------------------------------------------------|------|

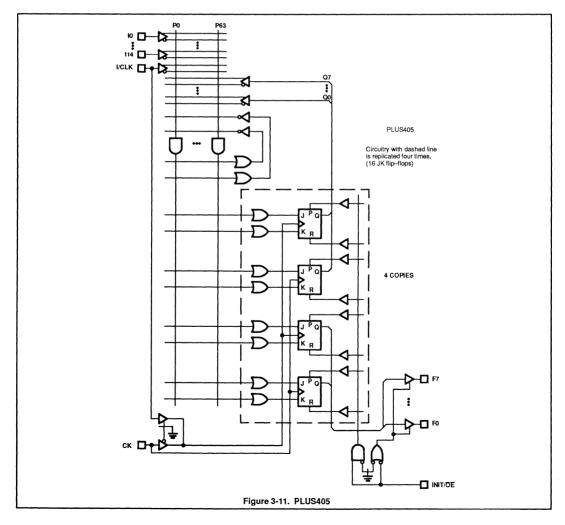

|                                          | The PLUS405                                      | 713  |

| • • • • • • • • • • • • • • • • • • • •  | n Introduction                                   | 715  |

| Chapter 4                                | Microprocessor Interfacing with Signetics PLDs   | 715  |

|                                          | Introduction                                     | 715  |

|                                          | System Partitioning                              | 715  |

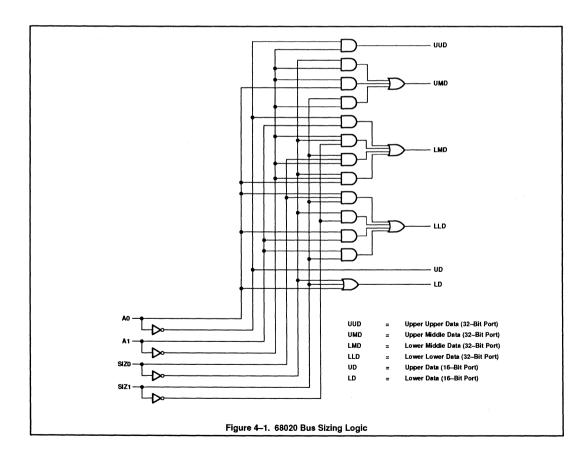

|                                          | Bus Size Decoding for the 68020 — PLUS18P8B      | 716  |

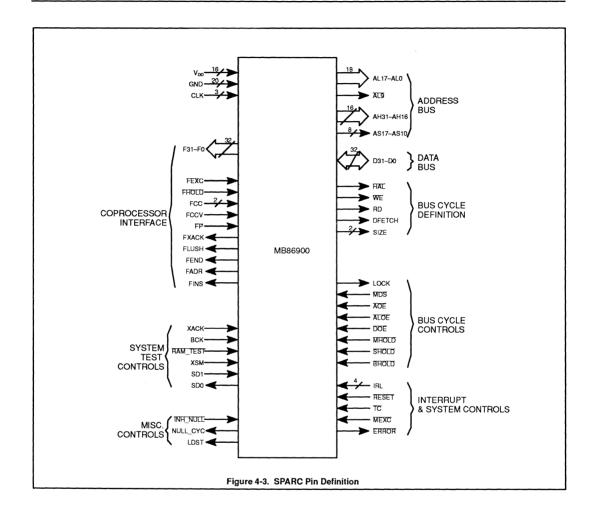

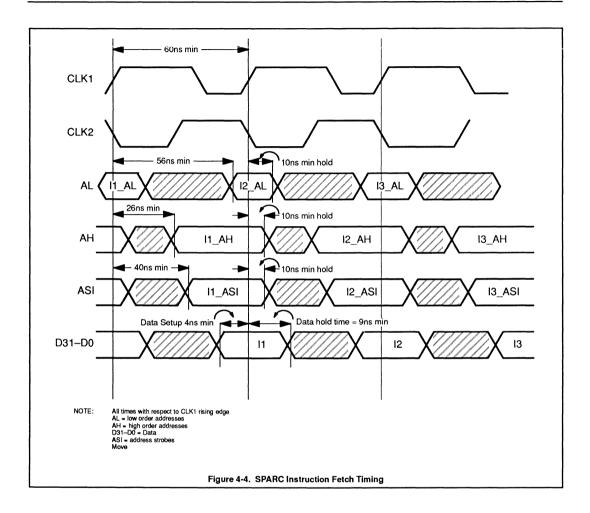

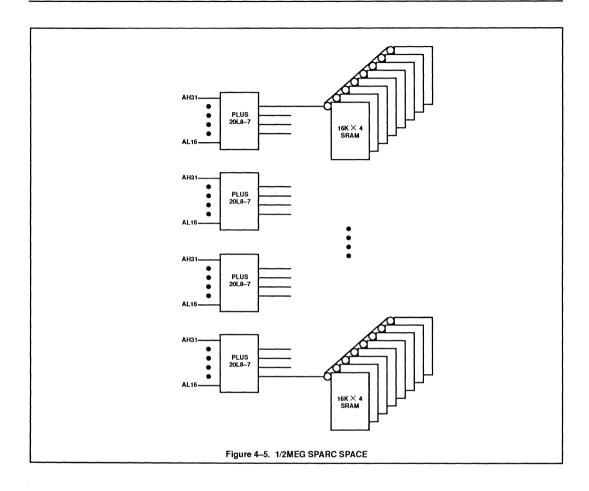

|                                          | Interfacing to SPARC — PLUS20L8-7                | 717  |

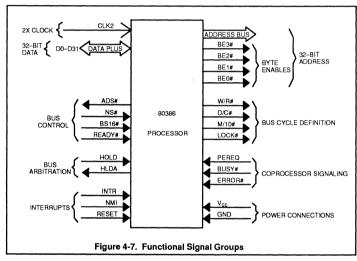

|                                          | The 80386 Pipeline Decoder — PLUS153D            | 721  |

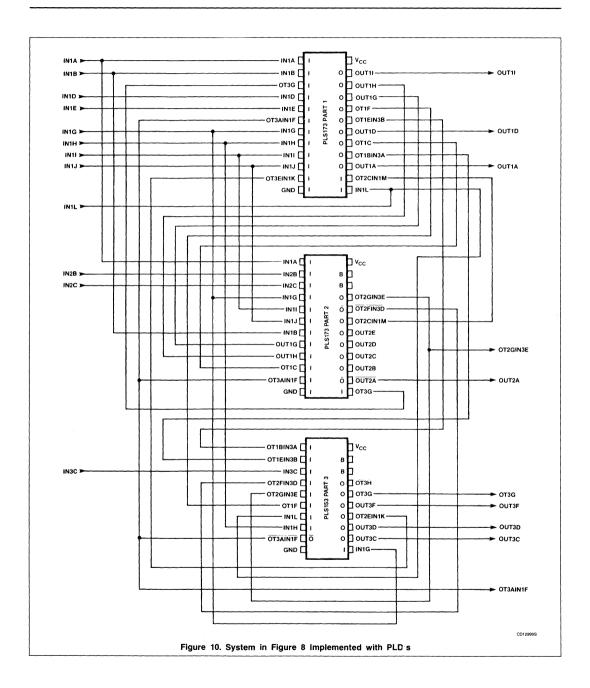

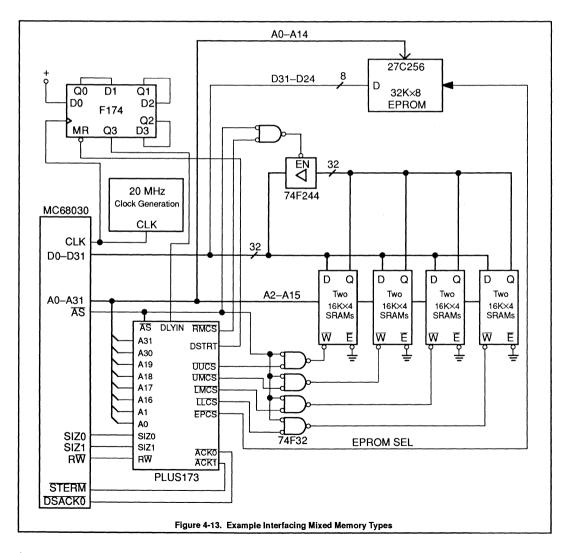

|                                          | 68030 Address Decoding — PLUS173D                | 725  |

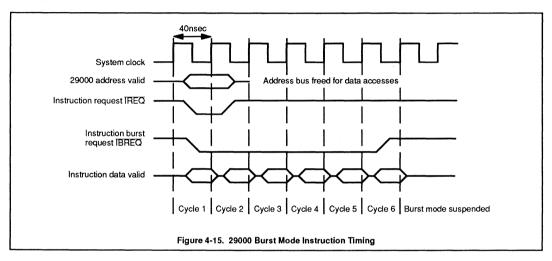

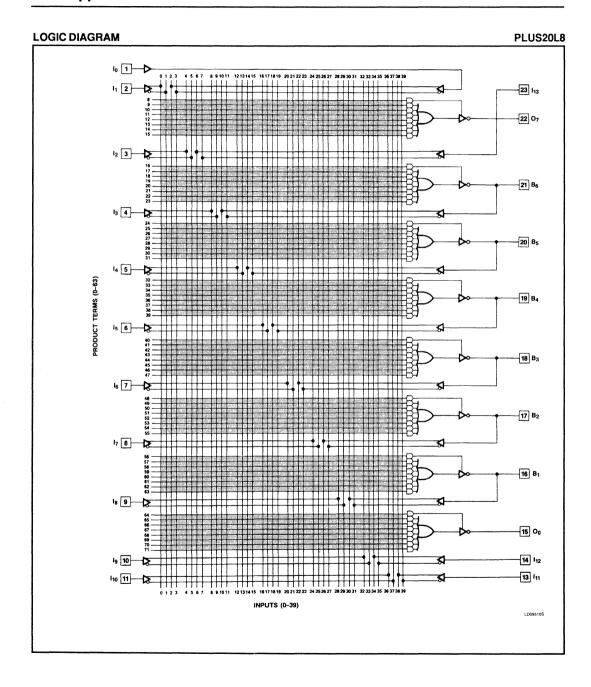

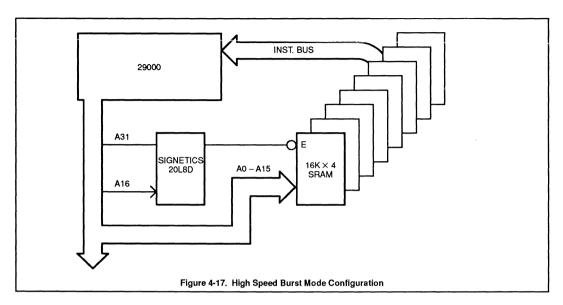

|                                          | The 29000, SRAM and the PLUS20L8D                | 727  |

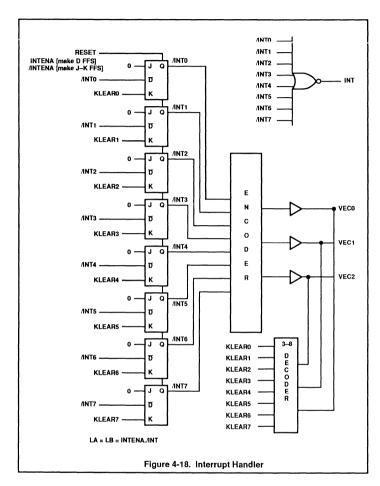

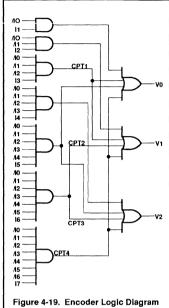

|                                          | Interrupt Handler — PLS179                       | 730  |

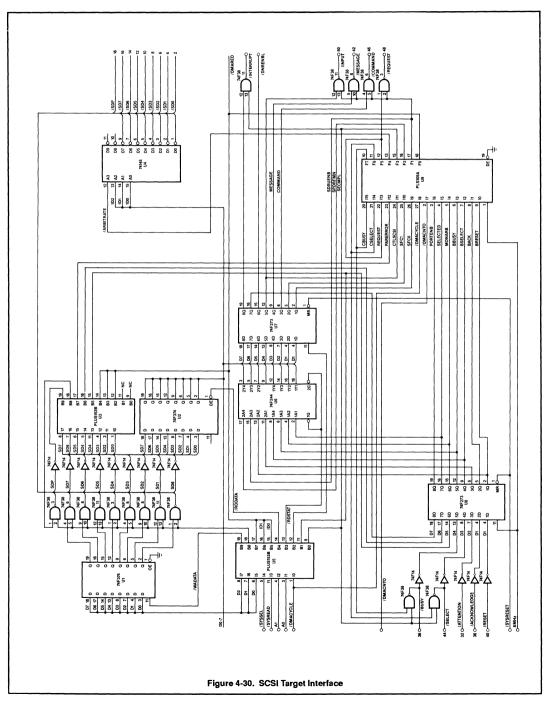

|                                          | SCSI Target Interface — PLS105A and PLUS153B     | 735  |

|                                          | Introduction                                     | 735  |

|                                          | Functional Description                           | 735  |

|                                          | Programmer's Interface                           | 735  |

|                                          | Port Operation                                   | 736  |

|                                          | Arbitration Software Sequence                    | 737  |

|                                          | RESELECT Software Sequence                       | 737  |

|                                          | TRANSFER Software Sequence                       | 737  |

|                                          | DISCONNECT Software Sequence                     | 737  |

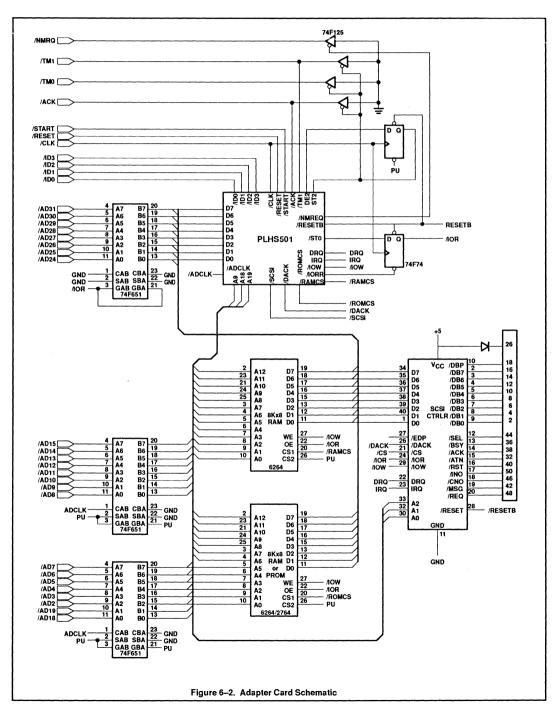

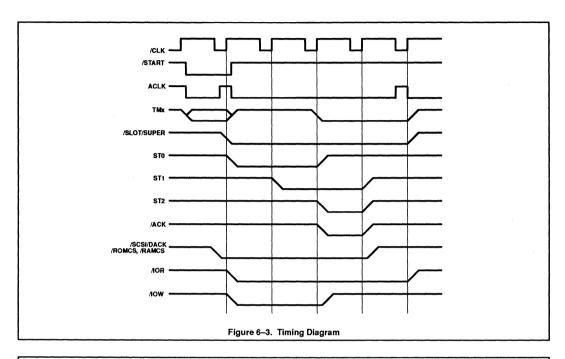

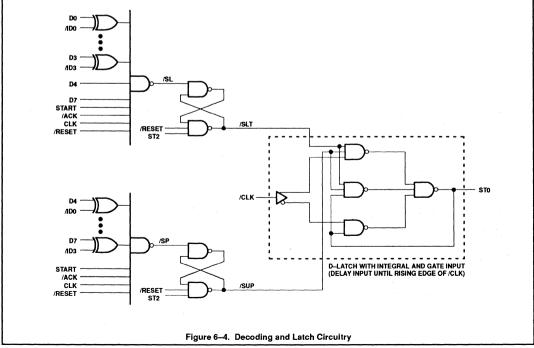

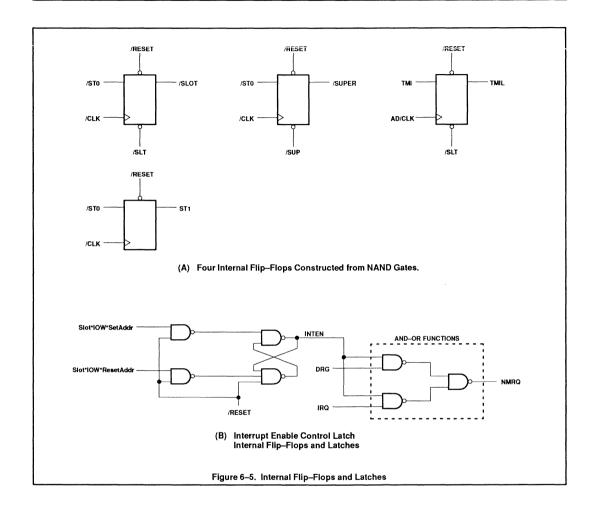

|                                          | Hardware Description                             | 738  |

| Chapter 5                                | Communications using PLDs                        | 750  |

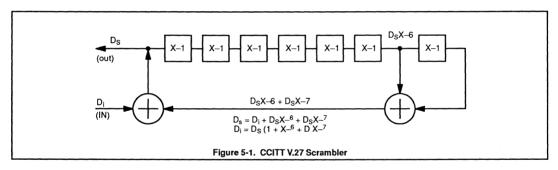

| onapior o                                | The CCITT V2.7 Scrambler — PLC18V8Z              | 750  |

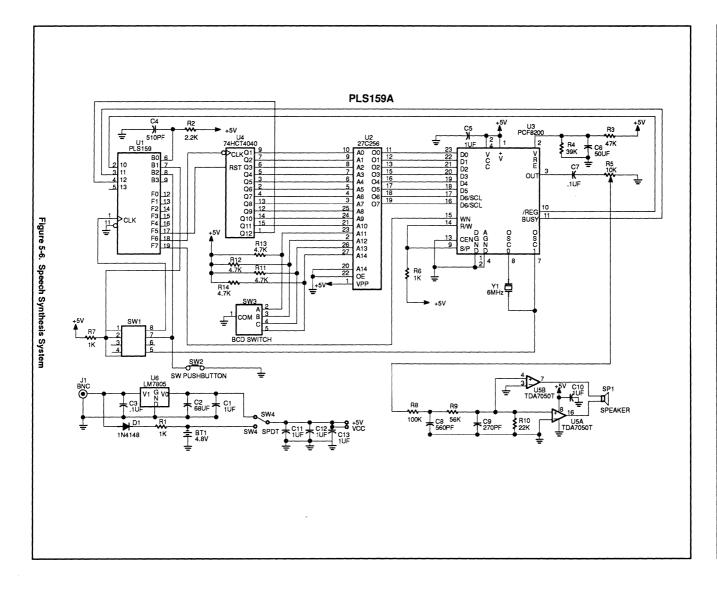

|                                          | A Novel Speech Synthesizer — PLS159A             | 752  |

|                                          | CCITT Forward CRC Polynomial — PLUS405           | 755  |

| Chapter 6                                | Instrumentation                                  | 757  |

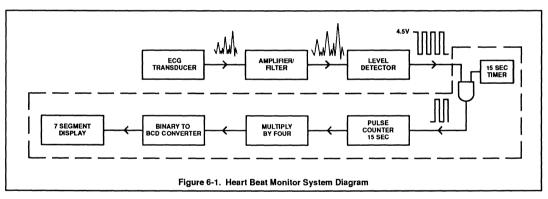

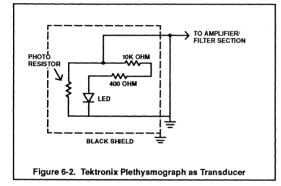

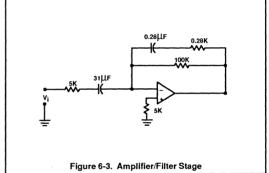

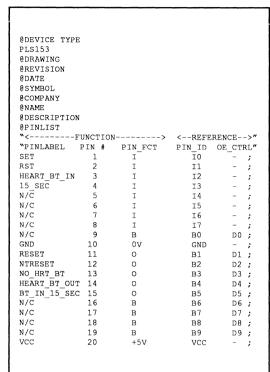

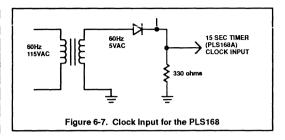

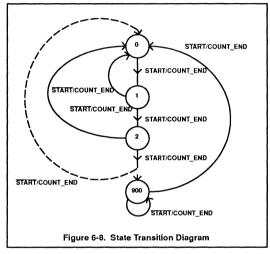

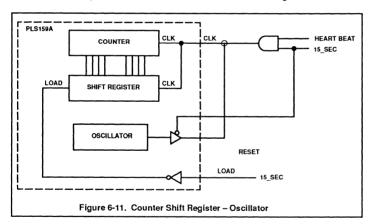

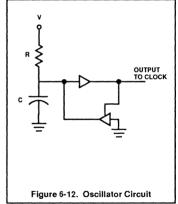

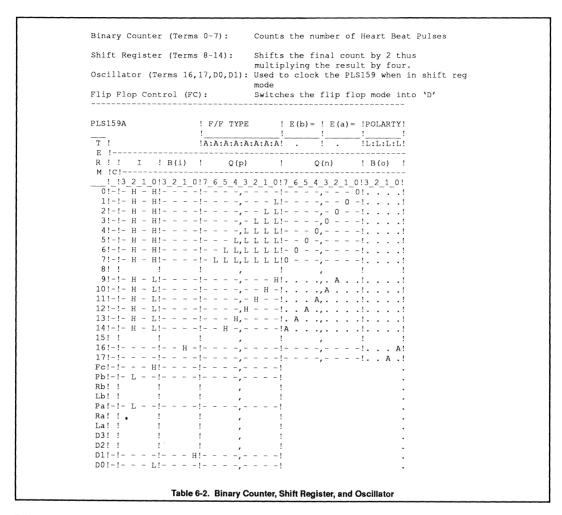

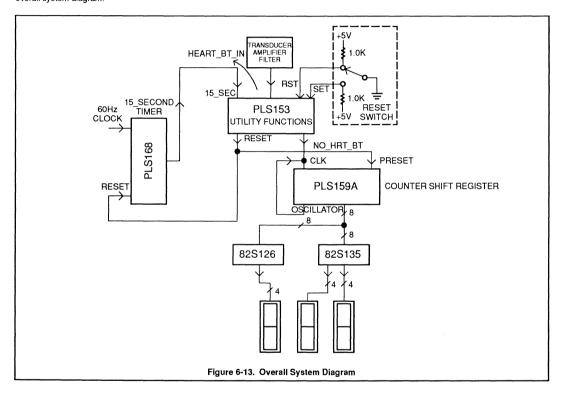

| Onapter 0                                | Heart Beat Monitor — PLS159A, PLS168A and PLS153 | 757  |

|                                          | The Pulse Width Monitor — PLS168                 | 764  |

|                                          | Scope Trace Sweep Circuit — PLS153 and PLS155    | 769  |

| Chantar 7                                | · · · · · · · · · · · · · · · · · · ·            | 772  |

| Chapter 7                                | General Applications                             |      |

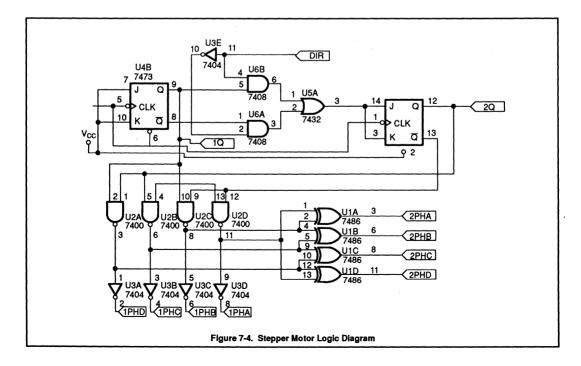

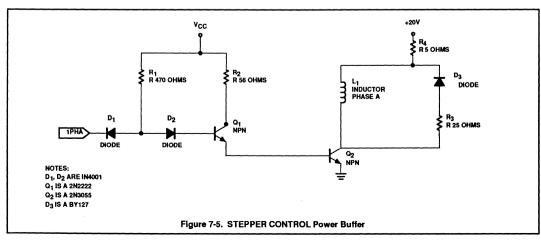

| Chantan 0                                | Motor Stepper Controller with the PLS155         | 772  |

| Chapter 8                                | Security Systems                                 | 776  |

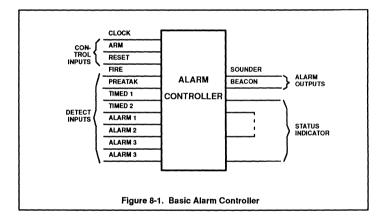

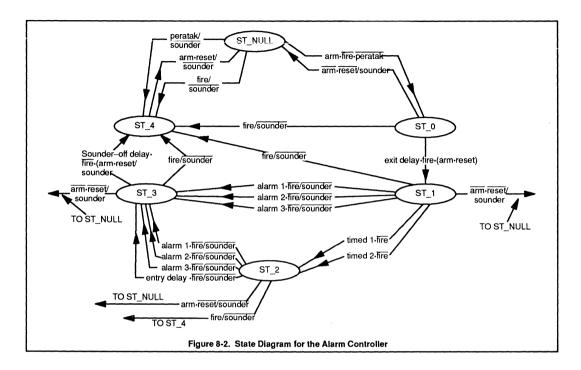

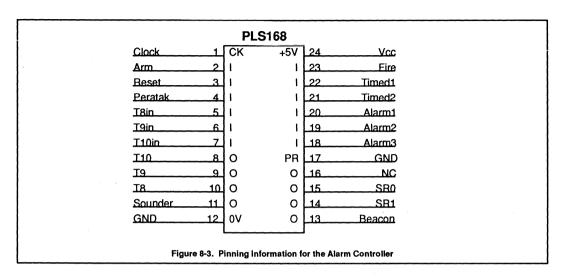

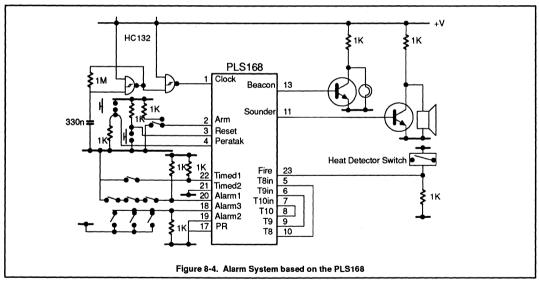

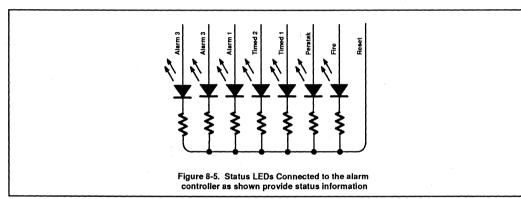

|                                          | A Programmable Alarm System — PLS168             | 776  |

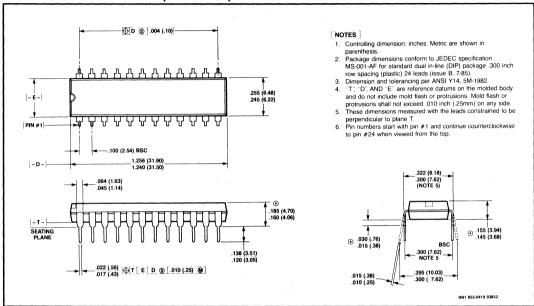

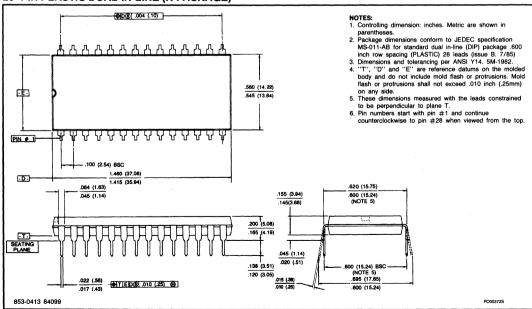

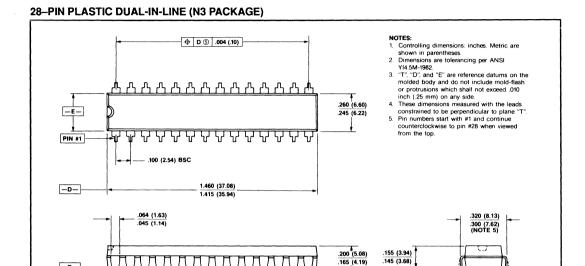

| Section 10 - Package                     | Outlines                                         |      |

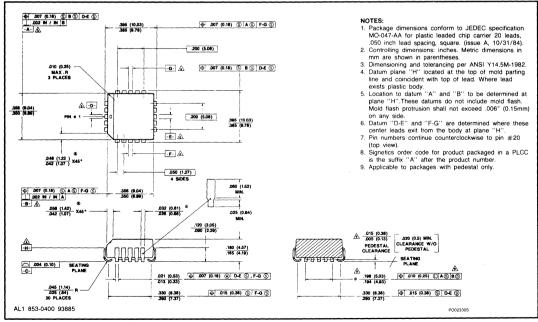

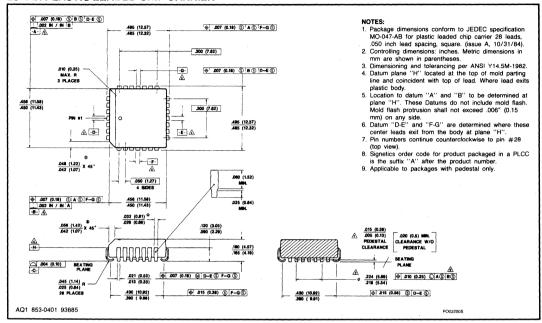

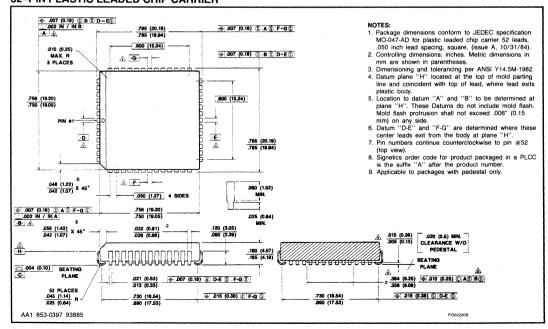

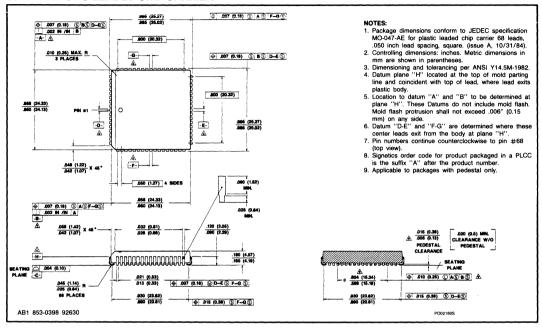

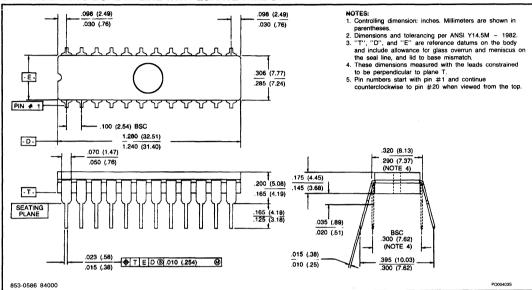

| A                                        | Plastic Leaded Chip Carrier                      | 785  |

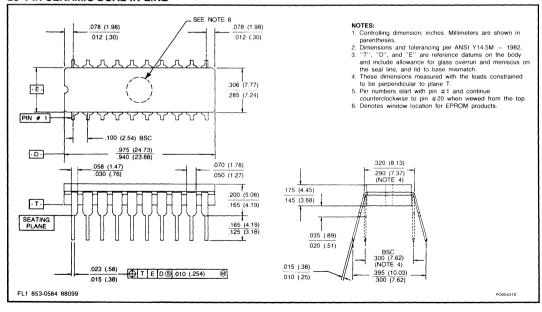

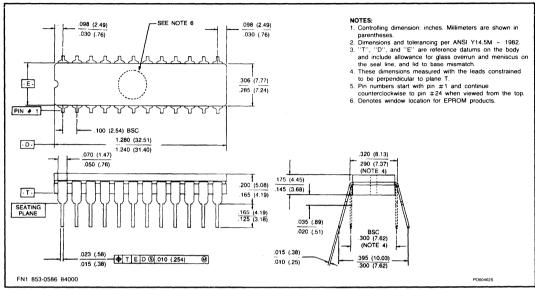

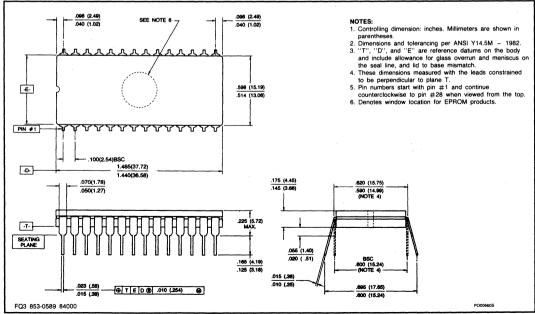

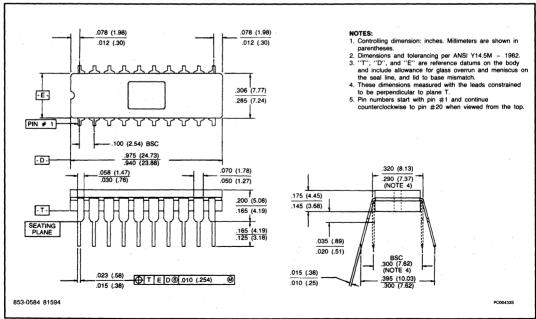

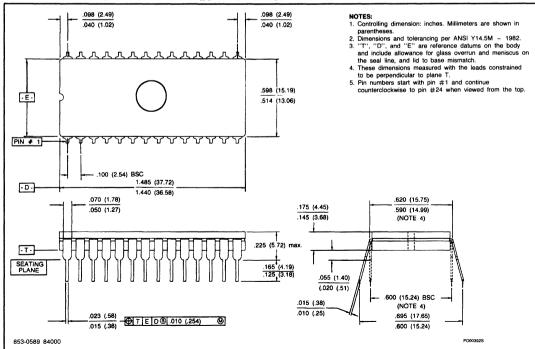

| · F                                      | Ceramic Dual-In-Line                             | 788  |

| FA                                       | Ceramic Dual-In-Line with Quartz Window          | 790  |

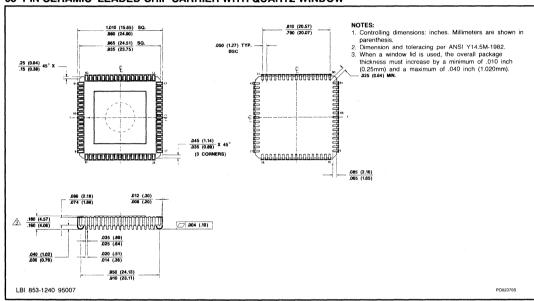

| LA                                       | Ceramic Leaded Chip Carrier with Quartz Window   | 792  |

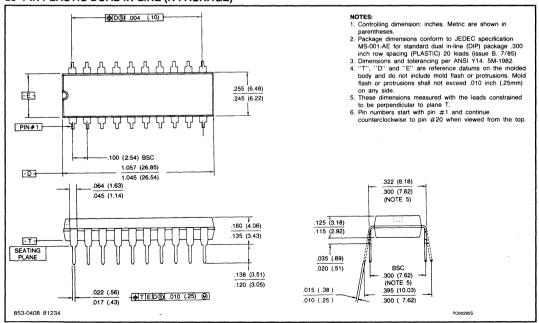

| N.                                       | Plastic Dual-In-Line                             | 793  |

|                                          |                                                  | , 50 |

| Section 11 – Sales Off<br>Office Listing | fices                                            | 799  |

|                                          |                                                  |      |

January 1990 viii

### Section 1 General Information

**Programmable Logic Devices**

#### INDEX

| Alphanumeric Index   | 3 |

|----------------------|---|

| Selection Guide      | 4 |

| Ordering Information | 6 |

### Alphanumeric Index

#### **Programmable Logic Devices**

| AN7               |           | Single Chip Multiprocessor Arbiter                       |       |

|-------------------|-----------|----------------------------------------------------------|-------|

| AN8               |           | Introduction to Signetics Programmable Logic             |       |

| AN11              |           | PLD Programmable Retriggerable One-Shot                  | . 459 |

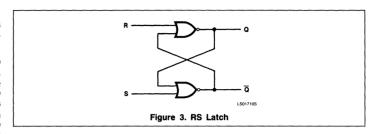

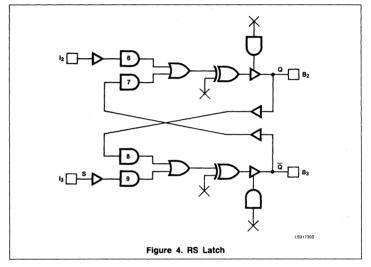

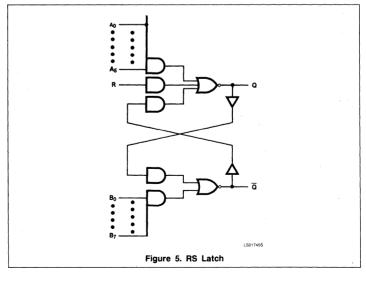

| AN14              |           | Latches and Flip–Flops with PLS153                       | . 463 |

| AN15              |           | PLS159 Primer                                            | . 476 |

| AN18              |           | Schmitt Trigger Using PLS153 and PLS159                  | . 487 |

| AN21              |           | 9-Bit Parity Generator/Checker with PLS153/153A          |       |

| AN23<br>AN24      |           | PLS168/168A Primer                                       |       |

| AN26              |           | PLHS18P8A Primer                                         |       |

| AN27              |           | PLHS473 Primer                                           |       |

| AN28              |           | High-Speed 12-Bit Tracking A/D Converter Using PLS179    |       |

| AN29              |           | PLHS501 Programmable Macro Logic Primer                  |       |

| PHD16N85          | Series 20 | Programmable High-Speed Decoder (16 × 16 × 8); 5ns       |       |

| PHD48N22-7        | Series 68 | Programmable High-Speed Decoder (48 × 73 × 22); 7.5ns    |       |

| PLC18V8Z/I        | Series 20 | PAL®-Type Devices                                        |       |

| PLC42VA12         | Series 24 | CMOS Programmable Logic Sequencer (42 × 105 × 12); 25MHz |       |

| PLC415-16         | Series 28 | Programmable Logic Sequencer (17 × 68 × 8); 16MHz        |       |

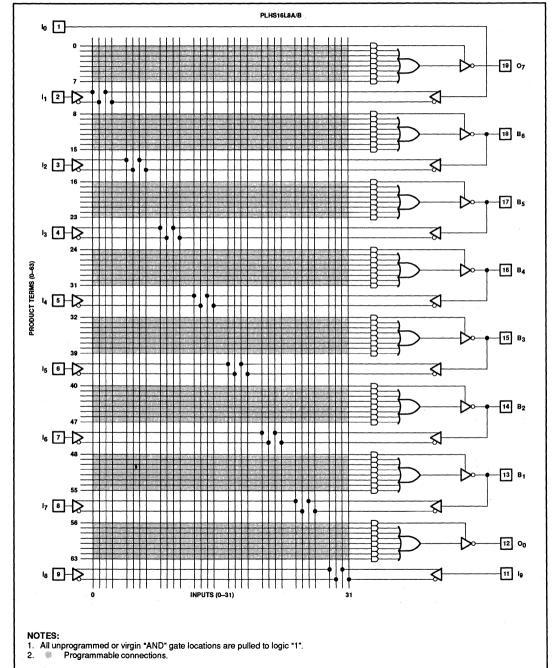

| PLHS16L8A/B       | Series 20 | PAL®—Type Devices (16 × 64 × 8)                          | 39    |

| PLHS18P8A/B       | Series 20 | PAL®-Type Devices                                        |       |

| PLHS473           | Series 24 | Programmable Logic Array (20 × 24 × 11); 22ns            |       |

| PLHS473S          | Series 24 | Programmable Logic Array (20 × 24 × 11); 25ns            |       |

| PLHS501           |           | Programmable Macro Logic                                 | . 361 |

| PLHS502           |           | Programmable Macro Logic                                 |       |

| PLHS601           |           | Programmable Macro Logic                                 |       |

| PLS100/101        | Series 28 | Programmable Logic Arrays (16 × 48 × 8); 50ns            |       |

| PLS105/A          | Series 28 | Programmable Logic Sequencers (16 × 48 × 8); 14, 20MHz   |       |

| PLS153/A          | Series 20 | Programmable Logic Arrays (18 × 42 × 10); 40/30ns        |       |

| PLS155            | Series 20 | Programmable Logic Sequencer (16 × 45 × 12); 14MHz       | . 191 |

| PLS157            | Series 20 | Programmable Logic Sequencer (16 × 45 × 12); 14MHz       | . 202 |

| PLS159A           | Series 20 | Programmable Logic Sequencer (16 × 45 × 12); 18MHz       |       |

| PLS167/A          | Series 24 | Programmable Logic Sequencers (14 × 48 × 6); 14, 20MHz   | . 223 |

| PLS168/A          | Series 24 | Programmable Logic Sequencers (12 × 48 × 8); 14, 20MHz   |       |

| PLS173            | Series 24 | Programmable Logic Array (22 × 42 × 10); 30ns            |       |

| PLS179            | Series 24 | Programmable Logic Sequencer (20 × 45 × 12); 18MHz       |       |

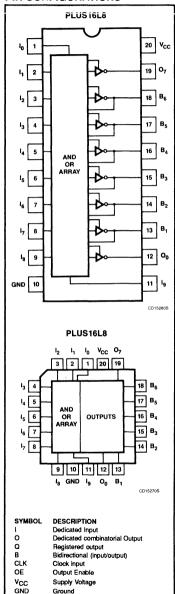

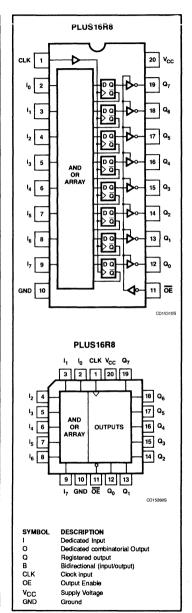

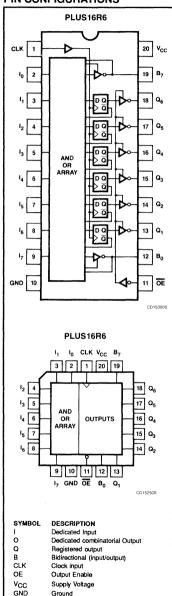

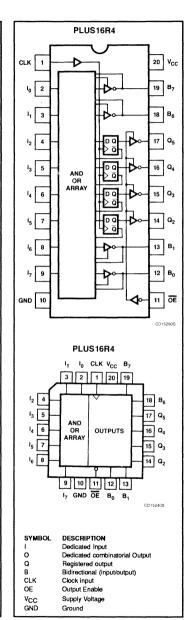

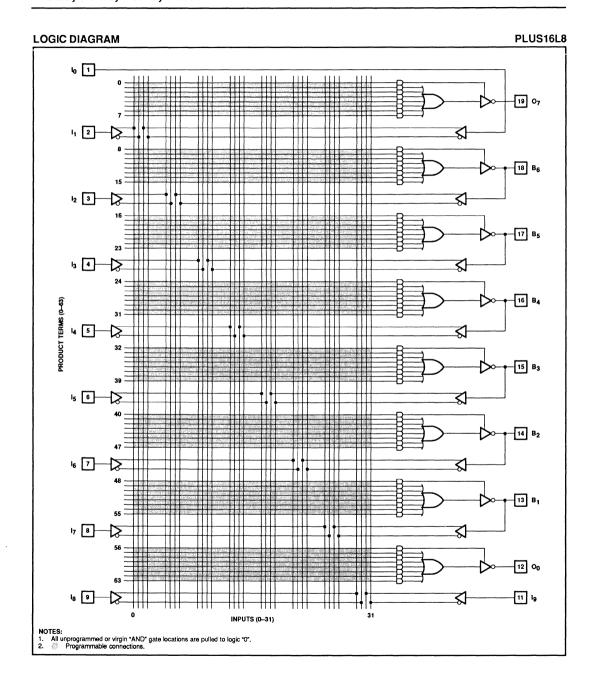

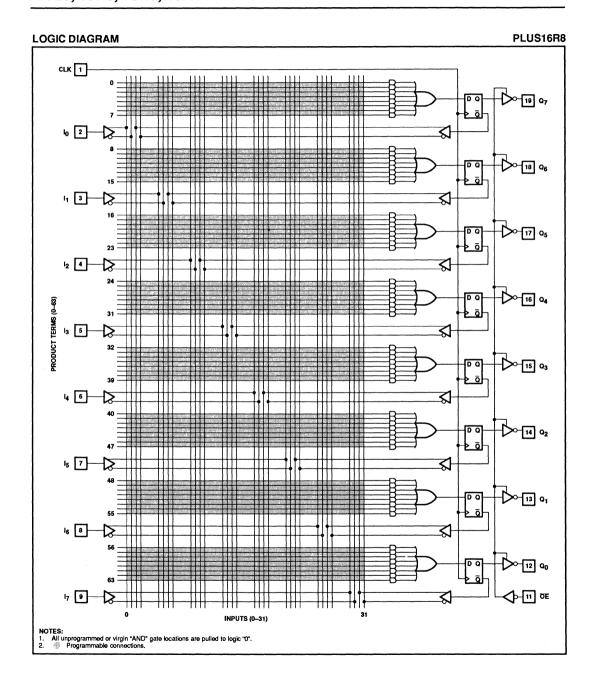

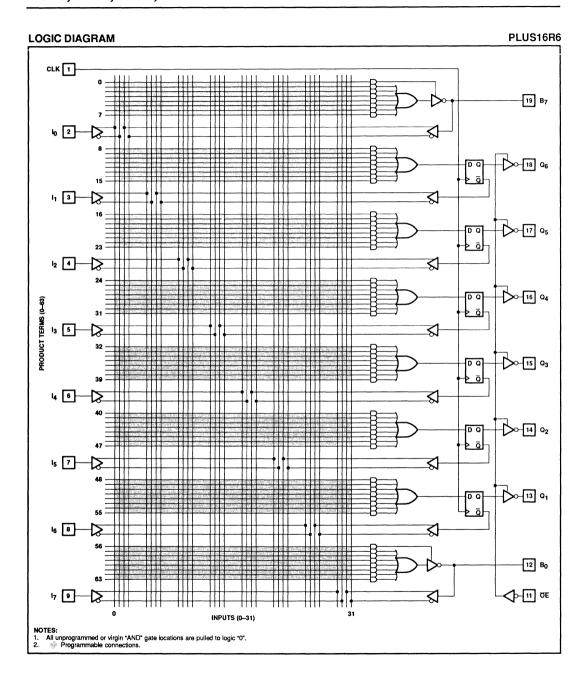

| PLUS16R8D/7       | Series 20 | PAL®-Type Devices                                        | 46    |

| PLUS20R8D/7       | Series 24 | PAL®-Type Devices                                        |       |

| PLUS10540         | Series 28 | Programmable Logic Sequencer (16 × 48 × 8); 40MHz        |       |

| PLUS105-55        | Series 28 | Programmable Logic Sequencer (16 × 48 × 8); 55MHz        | . 317 |

| PLUS153B/D        | Series 20 | Programmable Logic Arrays (18 × 42 × 10); 15/12ns        | . 134 |

| PLUS153-10        | Series 20 | Programmable Logic Array (18 × 42 × 10); 10ns            | . 141 |

| PLUS173B/D        | Series 24 | Programmable Logic Arrays (22 × 42 × 10); 15/12ns        | . 154 |

| PLUS173-10        | Series 24 | Programmable Logic Array (22 × 42 × 10); 10ns            | . 161 |

| PLUS405-37/-45    | Series 28 | Programmable Logic Sequencers (16 × 64 × 8); 37, 45MHz   | . 329 |

| PLUS405-55        | Series 28 | Programmable Logic Sequencer (16 × 64 × 8); 55MHz        |       |

| PML2552           |           | Programmable Macro Logic                                 |       |

| 10H20EV8/10020EV8 | Series 24 | ECL PAL®-Type Devices                                    | 87    |

January 1990

### Selection Guide

#### **Programmable Logic Devices**

| SIGNETICS<br>PART NUMBER       | ARCHITECTURE<br>(INPUTS × TERMS<br>× OUTPUTS) | PACKAGE | TOTAL<br>INPUTS<br>(# Dedicated) | LOGIC<br>TERMS | INTERNAL STATE<br>REGISTERS<br>(# Dedicated) | OUTPUTS<br>C, I/O, R, R I/O | t <sub>PD</sub> (Max) | f <sub>MAX</sub> | I <sub>CC</sub> (Max) |

|--------------------------------|-----------------------------------------------|---------|----------------------------------|----------------|----------------------------------------------|-----------------------------|-----------------------|------------------|-----------------------|

| PAL <sup>®</sup> -TYPE DEVICES |                                               |         |                                  |                |                                              |                             |                       |                  |                       |

| PLUS16L8-7                     | 16×64×8                                       | 20-Pin  | 16 (10)                          | 64             | 0                                            | 2 C, 6 I/O                  | 7.5ns                 |                  | 180mA                 |

| PLUS16R4-7                     | 16×64×8                                       | 20-Pin  | 16 (8)                           | 64             | 4 (0)                                        | 4 VO, 4 R                   | 7.5ns                 | 74MHz            | 180mA                 |

| PLUS16R6-7                     | 16×64×8                                       | 20-Pin  | 16 (8)                           | 64             | 6 (0)                                        | 2 I/O, 6 R                  | 7.5ns                 | 74MHz            | 180mA                 |

| PLUS16R8-7                     | 16×64×8                                       | 20-Pin  | 16 (8)                           | 64             | 8 (0)                                        | 8 R                         |                       | 74MHz            | 180mA                 |

| PLUS16L8D                      | 16×64×8                                       | 20Pin   | 16 (10)                          | 64             | 0                                            | 2 C, 6 I/O                  | 10ns                  |                  | 180mA                 |

| PLUS16R4D                      | 16×64×8                                       | 20Pin   | 16 (8)                           | 64             | 4 (0)                                        | 4 I/O, 4 R                  | 10ns                  | 60MHz            | 180mA                 |

| PLUS16R6D                      | 16×64×8                                       | 20-Pin  | 16 (8)                           | 64             | 6 (0)                                        | 2 I/O, 6R                   | 10ns                  | 60MHz            | 180mA                 |

| PLUS16R8D                      | 16×64×8                                       | 20-Pin  | 16 (8)                           | 64             | 8 (0)                                        | 8 R                         |                       | 60MHz            | 180mA                 |

| PLUS20L8-7                     | 20×64×8                                       | 24-Pin  | 20 (14)                          | 64             | 0                                            | 2 C, 6 I/O                  | 7.5ns                 |                  | 210mA                 |

| PLUS20R4-7                     | 20×64×8                                       | 24-Pin  | 20 (12)                          | 64             | 4 (0)                                        | 4 I/O, 4 R                  | 7.5ns                 | 74MHz            | 210mA                 |

| PLUS20R6 7                     | 20 × 64 × 8                                   | 24-Pin  | 20 (12)                          | 64             | 6 (0)                                        | 2 I/O, 6 R                  | 7.5ns                 | 74MHz            | 210mA                 |

| PLUS20R8 7                     | 20 × 64 × 8                                   | 24–Pin  | 20 (12)                          | 64             | 8 (0)                                        | 8 R                         |                       | 74MHz            | 210mA                 |

| PLUS20L8D                      | 20×64×8                                       | 24-Pin  | 20 (14)                          | 64             | 0                                            | 2 C, 6 I/O                  | 10ns                  |                  | 210mA                 |

| PLUS20R4D                      | 20×64×8                                       | 24-Pin  | 20 (12)                          | 64             | 4 (0)                                        | 4 I/O, 4R                   | 10ns                  | 60MHz            | 210mA                 |

| PLUS20R6D                      | 20×64×8                                       | 24-Pin  | 20 (12)                          | 64             | 6 (0)                                        | 2 I/O, 6 R                  | 10ns                  | 60MHz            | 210mA                 |

| PLUS20R8D                      | 20×64×8                                       | 24–Pin  | 20 (12)                          | 64             | 8 (0)                                        | 8 R                         |                       | 60MHz            | 210mA                 |

| PLHS16L8A                      | 16×64×8                                       | 20-Pin  | 16 (10)                          | 64             | o                                            | 2 C, 6 I/O                  | 20ns                  |                  | 155mA                 |

| PLHS16L8B                      | 16×64×8                                       | 20-Pin  | 16 (10)                          | 64             | 0                                            | 2 C, 6 I/O                  | 15ns                  |                  | 155mA                 |

| PLHS18P8A                      | 18×72×8                                       | 20-Pin  | 18 (10)                          | 72             | o                                            | 8 I/O                       | 20ns                  |                  | 155mA                 |

| PLHS18P8B                      | 18×72×8                                       | 20-Pin  | 18 (10)                          | 72             | 0                                            | 8 1/0                       | 15ns                  |                  | 155mA                 |

| PHD16N8-5                      | 16×16×8                                       | 20-Pin  | 16 (10)                          | 16             | 0                                            | 2 C, 6 I/O                  | 5ns                   |                  | 180mA                 |

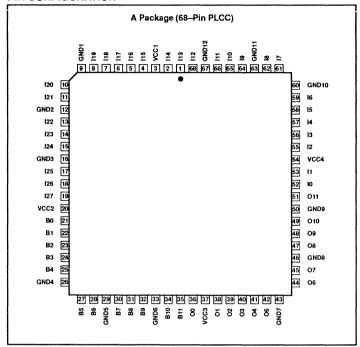

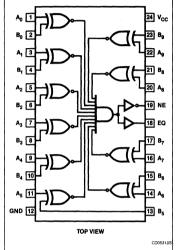

| PHD48N22-7**                   | 48×73×22                                      | 68–Pin  | 48 (36)                          | 73             | 0                                            | 10 C, 12 I/O                | 7.5ns                 |                  | 420mA                 |

| PLC18V8Z/18V8ZI                | 18×74×8                                       | 20-Pin  | 18 (8)                           | 74             | 8 (0)                                        | 8 varied                    | 35, 40ns              | 21MHz            | 100µA,<br>1mA/MHz     |

| 10H20EV8/10020EV8**            | 20×90×8                                       | 24-Pin  | 20 (12)                          | 90             | 0                                            | 8 varied                    | 4.5ns                 | 222MHz           | 230mA                 |

| PLA                            |                                               |         |                                  |                |                                              |                             |                       |                  | , 1                   |

| PLS100/101                     | 16×48×8                                       | 28-Pin  | 16 (16)                          | 48             | 0                                            | 8 C                         | 50ns                  |                  | 170mÅ                 |

| PLS153                         | 18×42×10                                      | 20-Pin  | 18 (8)                           | 42             | 0                                            | 10 I/O                      | 40ns                  |                  | 155mA                 |

| PLS153A                        | 18×42×10                                      | 20-Pin  | 18 (8)                           | 42             | 0                                            | 10 I/O                      | 30ns                  |                  | 155mA                 |

| PLUS153B                       | 18×42×10                                      | 20Pin   | 18 (8)                           | 42             | . 0                                          | 10 VO                       | 15ns                  |                  | 200mA                 |

| PLUS153D                       | 18×42×10                                      | 20-Pin  | 18 (8)                           | 42             | 0                                            | 10 VO                       | 12ns                  |                  | 200mA                 |

| PLUS153-10**                   | 18×42×10                                      | 20-Pin  | 18 (8)                           | 42             | 0                                            | 10 VO                       | 10ns                  |                  | 200mA                 |

| PLS173                         | 22×42×10                                      | 24–Pin  | 22 (12)                          | 42             | 0                                            | 10 I/O                      | 30ns                  |                  | 170mA                 |

| PLUS173B                       | 22×42×10                                      | 24-Pin  | 22 (12)                          | 42             | 0                                            | 10 VO                       | 15ns                  |                  | 200mA                 |

| PLUS173D                       | 22×42×10                                      | 24-Pin  | 22 (12)                          | 42             | 0                                            | 10 VO                       | 12ns                  |                  | 200mA                 |

| PLUS173-10**                   | 22×42×10                                      | 24-Pin  | 22 (12)                          | 42             | 0                                            | 10 VO                       | 10ns                  |                  | 200mA                 |

| PLHS473                        | 20×42×11                                      | 24-Pin  | 20 (11)                          | 24             | o                                            | 2 C, 9 I/O                  | 22ns                  |                  | 155mA                 |

| PLHS473S**                     | 20×42×11                                      | 24-Pin  | 20 (11)                          | 24             | 0                                            | 2 C. 9 I/O                  | 25ns                  |                  | 155mA                 |

#### **Selection Guide**

| SIGNETICS<br>PART NUMBER | ARCHITECTURE<br>(INPUTS×TERMS<br>×OUTPUTS) | PACKAGE | TOTAL<br>INPUTS<br>(# Dedicated) | LOGIC<br>TERMS | INTERNAL STATE<br>REGISTERS<br>(# Dedicated) | OUTPUTS<br>C, I/O, R, R I/O  | t <sub>PD</sub> (Max) | f <sub>MAX</sub> | I <sub>CC</sub> (Max) |

|--------------------------|--------------------------------------------|---------|----------------------------------|----------------|----------------------------------------------|------------------------------|-----------------------|------------------|-----------------------|

| PLS                      |                                            |         |                                  |                |                                              |                              |                       |                  |                       |

| PLS105                   | 22×48×8                                    | 28-Pin  | 22 (16)                          | 48             | 6 (6)                                        | 8 R                          |                       | 14MHz            | 180mA                 |

| PLS105A                  | 22 × 48 × 8                                | 28–Pin  | 22 (16)                          | 48             | 6 (6)                                        | 8 R                          |                       | 20MHz            | 180mA                 |

| PLS105-40                | 22×48×8                                    | 28-Pin  | 22 (16)                          | 48             | 6 (6)                                        | 8 R                          |                       | 40MHz            | 200mA                 |

| PLS105-55**              | 22×48×8                                    | 28-Pin  | 22 (16)                          | 48             | 6 (6)                                        | 8 R                          |                       | 55MHz            | 200mA                 |

| PLUS405-37               | 24×64×8                                    | 28-Pin  | 24 (16)                          | 64             | 8 (8)                                        | 8 R                          |                       | 37MHz            | 225mA                 |

| PLUS405-45               | 24×64×8                                    | 28-Pin  | 24 (16)                          | 64             | 8 (8)                                        | 8 R                          |                       | 45MHz            | 225mA                 |

| PLUS405-55**             | 24×64×8                                    | 28-Pin  | 24 (16)                          | 64             | 8 (8)                                        | 8 R                          |                       | 55MHz            | 225mA                 |

| PLS155                   | 16×45×12                                   | 20-Pin  | 16 (4)                           | 45             | 4 (0)                                        | 8 I/O, 4 R I/O               | 50ns                  | 14MHz            | 190mA                 |

| PLS157                   | 16×45×12                                   | 20-Pin  | 16 (4)                           | 45             | 6 (0)                                        | 6 I/O, 6 R I/O               | 50ns                  | 14MHz            | 190mA                 |

| PLS159A                  | 16×45×12                                   | 20-Pin  | 16 (4)                           | 45             | 8 (0)                                        | 4 I/O, 8 R I/O               | 35ns                  | 18MHz            | 190mA                 |

| PLS167                   | 22×48×6                                    | 24-Pin  | 22 (14)                          | 48             | 8 (6)                                        | 6R                           |                       | 14MHz            | 180mA                 |

| PLS167A                  | 22×48×6                                    | 24Pin   | 22 (14)                          | 48             | 8 (6)                                        | 6R                           |                       | 20MHz            | 180mA                 |

| PLS168                   | 22×48×6                                    | 24-Pin  | 22 (12)                          | 48             | 10 (6)                                       | 8 R                          |                       | 14MHz            | 180mA                 |

| PLS168A                  | 22×48×6                                    | 24-Pin  | 22 (12)                          | 48             | 10 (6)                                       | 8 R                          |                       | 20MHz            | 180mA                 |

| PLS179                   | 20×45×12                                   | 24Pin   | 20 (8)                           | 45             | 8 (0)                                        | 4 I/O, 8 R I/O               | 35ns                  | 18MHz            | 210mA                 |

| PLC42VA12**              | 42×105×12                                  | 24-Pin  | 42 (10)                          | 105            | 10 (0)                                       | 10 C or R I/O, 2 I/O         | 35ns                  | 25MHz            | 90mA*                 |

| PLC415-16                | 25×68×8                                    | 28-Pin  | 25 (17)                          | 68             | 8 (8)                                        | 8 R                          |                       |                  | 100µА/<br>80mA        |

| PML <sup>TM</sup>        |                                            |         |                                  |                |                                              |                              |                       |                  |                       |

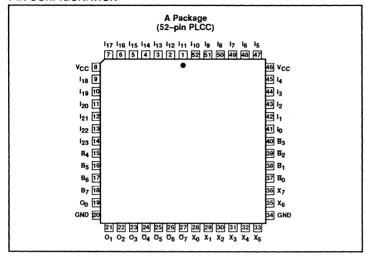

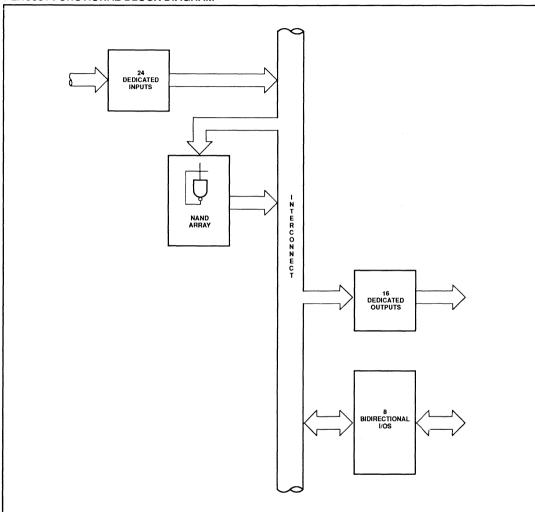

| PLHS501                  | 104×116×24                                 | 52-Pin  | 24                               | 116            | 0                                            | 16 C, 8 I/O                  | 22ns                  |                  | 295mA                 |

| PLHS502                  | 128×144×24                                 | 68–Pin  | 24                               | 144            | 16 (16)                                      | 16 C or R,<br>8 I/O or R I/O | 20ns                  | 50MHz            | 370mA                 |

| PLHS601**                | 68 × 134 × 24                              | 68–Pin  | 28                               | 134            | 0                                            | 12 C, 12 I/O                 | 20ns                  |                  | 340mA                 |

| PML2552**                | 185 × 226 × 24                             | 68–Pin  | 29                               | 226            | 36 (20)                                      | 24 C, 16 R, 16 I/O           | 40, 50ns              | 50, 33MHz        | 100mA                 |

PAL—Type = Programmable Array Logic (Fixed OR Array)—Type

PHD = Programmable High—Speed Decoder

PLA = Programmable Logic Array

PLS = Programmable Logic Sequencer

PML = Programmable Macro Logic

#### **OUTPUTS:**

C = Combinatorial output R = Registered output I/O = Combinatorial I/O

R I/O = Registered I/O

#### NOTES:

f<sub>MAX</sub> = 1/(t<sub>IS</sub> + t<sub>CKO</sub>) worst case

\* Measured at 15MHz (TTL input level)

\*\* Under development

PAL is a trademark of AMD/MMI.

PML is a trademark of Philips Components-Signetics.

# Ordering Information

#### **Programmable Logic Devices**

Signetics Programmable Logic Devices may be ordered by contacting either the local Signetics sales office, Signetics representatives or authorized distributors. A complete listing is located in the back of this handbook.

Table 1 provides part number definition for Signetics PLDs. The Signetics part number system allows complete ordering information to specified in the part number. The part number and product description is located on each data sheet.

Military versions of these commercial products may be ordered. Please refer to the military products data handbook for complete ordering information.

#### **New Signetics PLD Part Numbering System**

| P(L) | XX | YYYY Z | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |    |        | Package Designator F - 20-, 24-, 28-Pin CERDIP DIP N - 20-, 24-, 28-Pin Plastic DIP A - 20-, 28-lead Plastic Leaded Chip Carrier FA - 20-, 24-Pin CERDIP DIP with Quartz Window  Performance Indicator (May be blank, A, B, D, etc. to designate speed variations in basic part.)  Basic Part Number (3 to 8 characters) (e.g., 100, 105, 153, 168, 173, 18P8, 42VA12)  Process/Architecture Indicator S - Bipolar Junction Isolated Schottky - Nichrome fuses C - CMOS - EPROM cells HS - High Speed Bipolar Oxide Isolated - Vertical Fuse US - High Speed Bipolar Oxide Isolated - Lateral Fuse HD - High Speed Decoder ML - Macro Logic (Blank for ECL devices) |

| L    |    |        | Indicator for Signetics Programmable Logic (Can be either P. PL, or blank) (P for PHD and PML and blank for ECL devices)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### Section 2 Introduction

**Programmable Logic Devices**

| INDEX                                |

|--------------------------------------|

| What is Signetics Programmable Logic |

| Quality and Reliability              |

### Introduction Signetics Programmable Logic

#### **Programmable Logic Devices**

### WHAT IS PROGRAMMABLE LOGIC

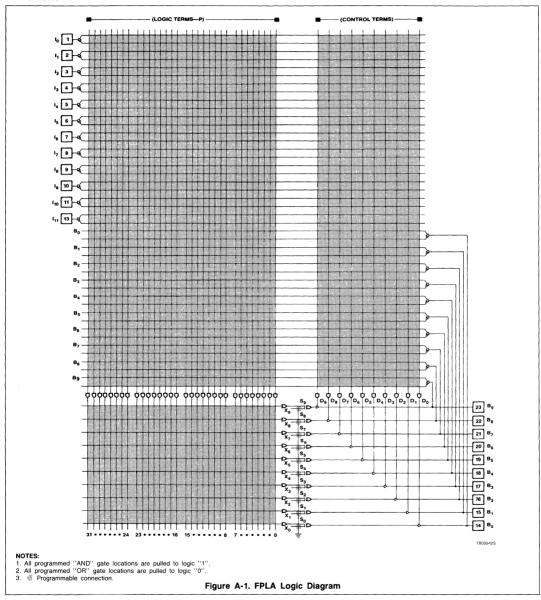

In 1975, Signetics Corporation developed a new product family by combining its expertise in semi-custom gate array products and fuse-link Programmable Read Only Memories (PROMs). Out of this marriage came Signetics Programmable Logic Family. The PLS100 Field-Programmable Logic Array (FPLA) was the first member of this family. The FPLA was an important industry first in two ways. First, the AND/OR/INVERT architecture allowed the custom implementations of Sum of Product logic equations. Second, the three-level fusing allows complete flexibility in the use of this device family. All logic interconnections from input to output are programmable.

#### Introduction

Table 1. PLD Product Family

| PART NUMBER           | TYPE        | CONFIGURATION                                                               |  |  |  |  |  |

|-----------------------|-------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| 20-PIN                |             |                                                                             |  |  |  |  |  |

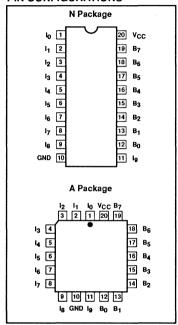

| PHD16N8               | PHD         | 12-Input/8-Output                                                           |  |  |  |  |  |

| PLS153/153A           | PLA         | 18-Input/10-Output - 42-Term                                                |  |  |  |  |  |

| PLUS153B/153D/153-10  | PLA         | 18-Input/10-Output - 42-Term                                                |  |  |  |  |  |

| PLS155-159A           | PLS         | 16-Input/12-Output 45-Term                                                  |  |  |  |  |  |

| PLS155                | PLS         | 4 Registered Outputs                                                        |  |  |  |  |  |

| PLS157                | PLS         | 6 Registered Outputs                                                        |  |  |  |  |  |

| PLS159A               | PLS         | 8 Registered Outputs                                                        |  |  |  |  |  |

| PLHS18P8A/B           | PAL-Type    | 18-Input/10-Output - 72-Term                                                |  |  |  |  |  |

| PLHS16L8A/B           | PAL-Type    | 16Input/8Output 64Term                                                      |  |  |  |  |  |

| PLC18V8Z/I            | PAL-Type    | 18-Input/8-Output - 72-Term                                                 |  |  |  |  |  |

| PLUS16L8D/-7          | PAL-Type    | 16-Input/8-Output - 72-Term                                                 |  |  |  |  |  |

| PLUS16R4D/7           | PAL-Type    | 16-Input/4-Output, 4 Registers                                              |  |  |  |  |  |

| PLUS16R6D/-7          | PAL-Type    | 16-Input/6-Output, 6 Registers                                              |  |  |  |  |  |

| PLUS16R8D/-7          | PAL-Type    | 16-Input/8-Output, 8 Registers                                              |  |  |  |  |  |

|                       | 24-PIN      |                                                                             |  |  |  |  |  |

| PLS167/A              | PLS         | 14-Input/6-Output - 48-Term<br>8-Bit State Registers<br>6-Output Registers  |  |  |  |  |  |

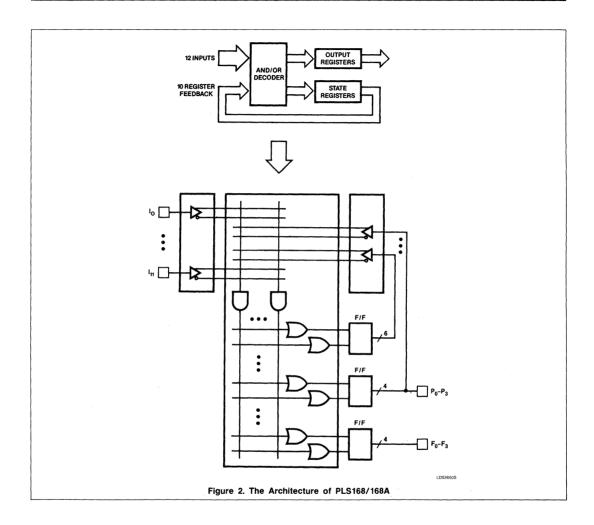

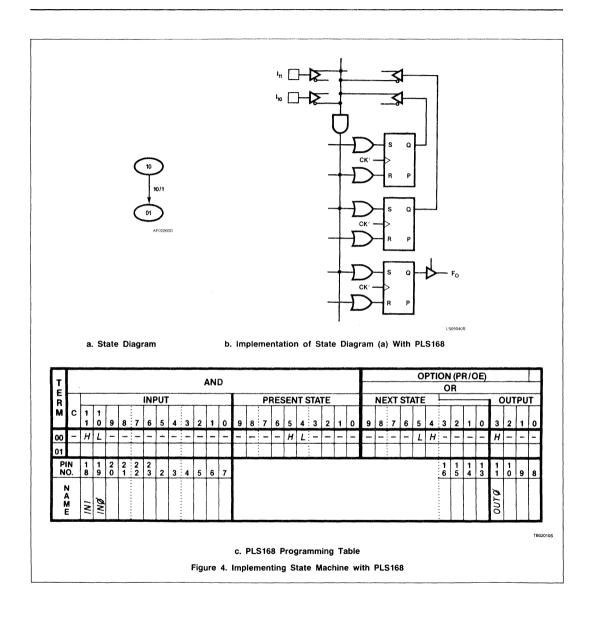

| PLS168/A              | PLS         | 12-Input/8-Output - 48-Term<br>10-Bit State Registers<br>8-Output Registers |  |  |  |  |  |

| PLS173/PLUS173B/D/-10 | PLA         | 22-Input/10-Output - 42-Term                                                |  |  |  |  |  |

| PLS179                | PLS         | 22-Input/10-Output - 42-Term                                                |  |  |  |  |  |

| PLHS473               | PLA         | 20-Input/11-Output - 24-Term                                                |  |  |  |  |  |

| PLC42VA12             | PLS         | 42-Input/12-Output, 10 Registers                                            |  |  |  |  |  |

| PLUS20L8D/7           | PAL-Type    | 20-Input/8-Output                                                           |  |  |  |  |  |

| PLUS20R4D/-7          | PAL-Type    | 20-Input/4-Output                                                           |  |  |  |  |  |

| PLUS20R6D/-7          | PAL-Type    | 20-Input/6-Output                                                           |  |  |  |  |  |

| PLUS20R8D/-7          | PAL-Type    | 20-Input/8-Output                                                           |  |  |  |  |  |

|                       | 28-PIN      | •                                                                           |  |  |  |  |  |

| PLS100/101            | PLA         | 16-Input/8-Output - 48-Term                                                 |  |  |  |  |  |

| PLS105/105A/PLUS105   | PLS         | 16-Input/8-Output - 48-Term<br>6-Bit State Register<br>8-Output Registers   |  |  |  |  |  |

| PLUS405               | PLS         | 16-Input/8-Output - 64-Term<br>8-Bit State and Output Registers             |  |  |  |  |  |

|                       | 52-, 68-PIN |                                                                             |  |  |  |  |  |

| PLHS501               | PML         | 32-Input/24-Output - 116-Term                                               |  |  |  |  |  |

| PLHS502               | PML         | 32-Input/24Output - 144-Term                                                |  |  |  |  |  |

| PLHS601               | PML         | 40-Input/24-Output 150-Term                                                 |  |  |  |  |  |

| PML2552               | PML         | 55-Input/24-Output - 226-Term                                               |  |  |  |  |  |

| PHD48N22              | PHD         | 48-Input/22-Output                                                          |  |  |  |  |  |

|                       |             | 1                                                                           |  |  |  |  |  |

#### Introduction

#### Introduction

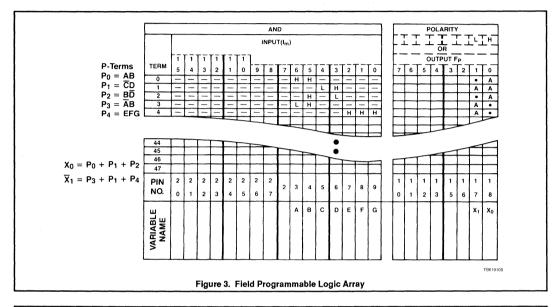

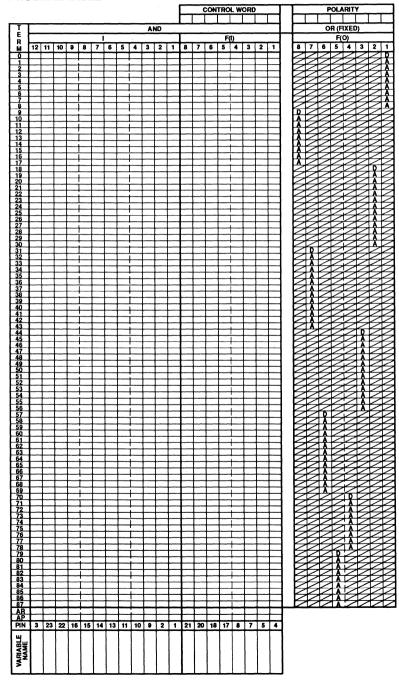

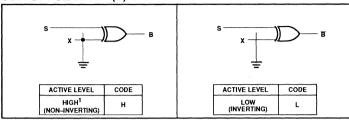

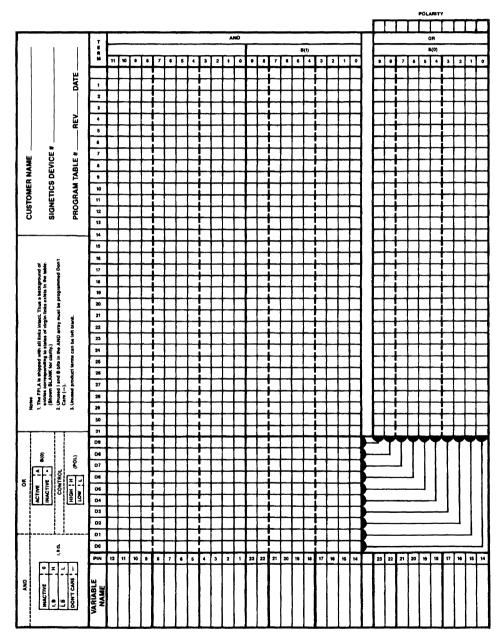

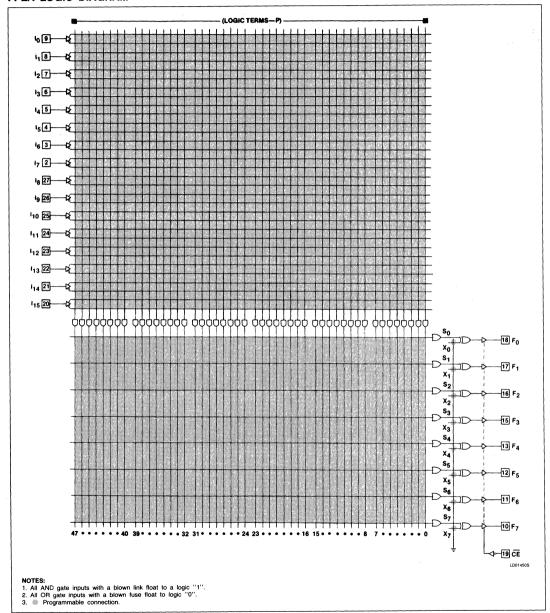

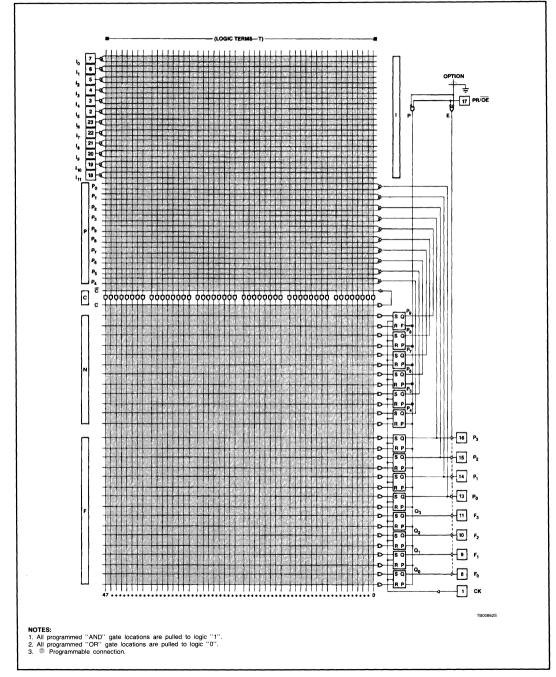

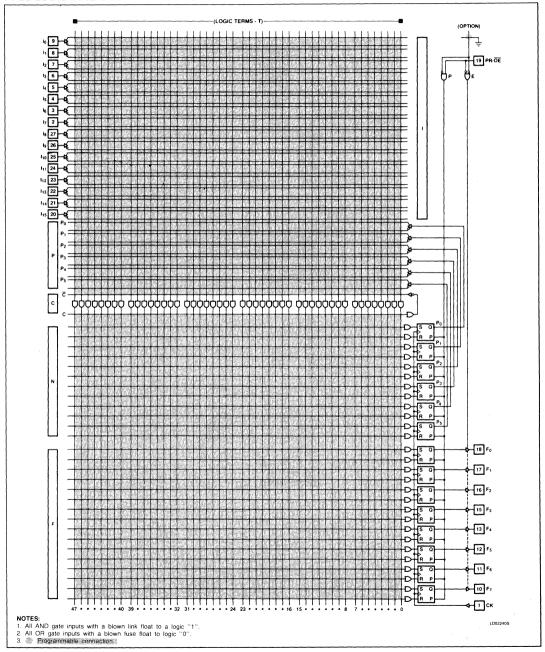

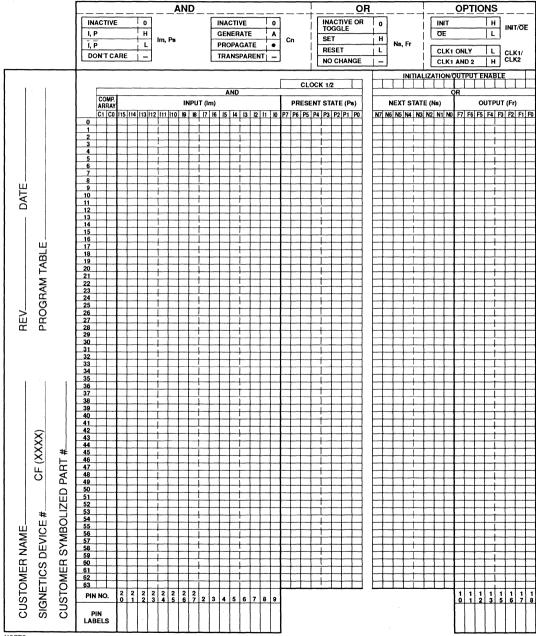

#### **PLD LOGIC SYNTHESIS**

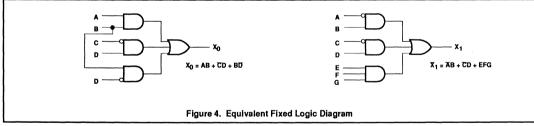

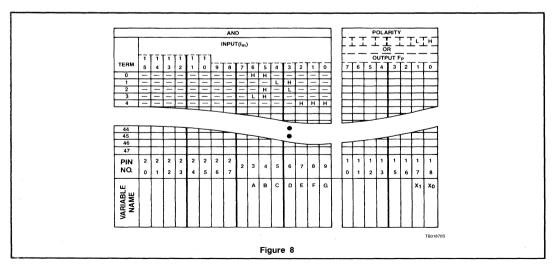

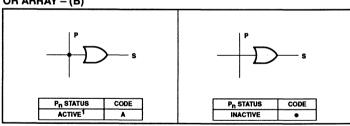

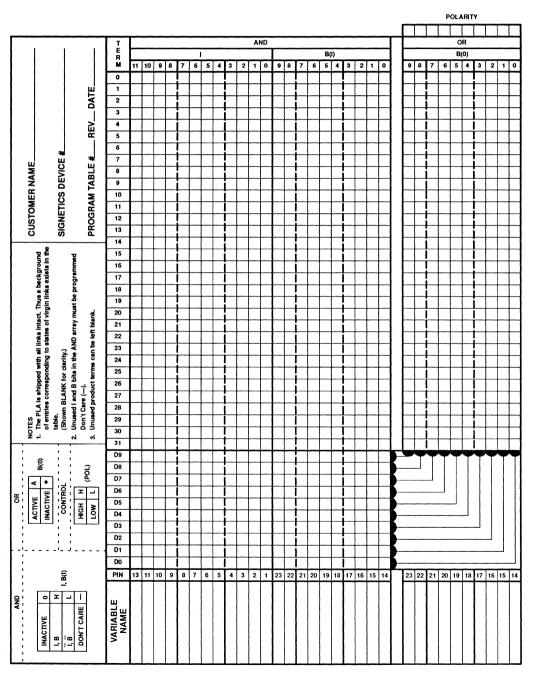

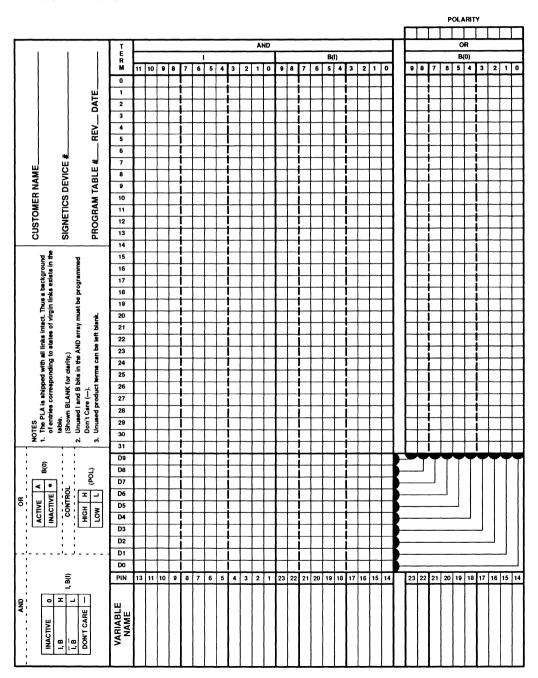

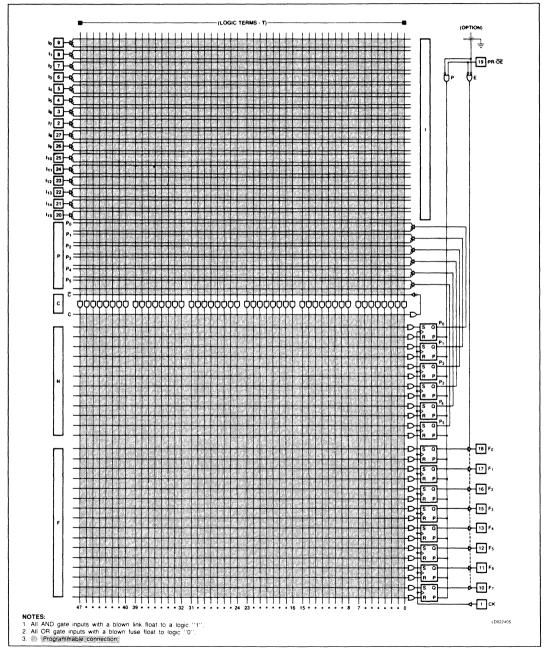

No intermediate step is required to implement Boolean Logic Equations with PLDs. Each term

in each equation simply becomes a direct entry into the Logic Program Table. The following example illustrates this straightforward concept:  $X_0 = AB + \overline{C}D + B\overline{D}$

$X_1 = \overline{A}B + \overline{C}D + EFG$

#### Introduction

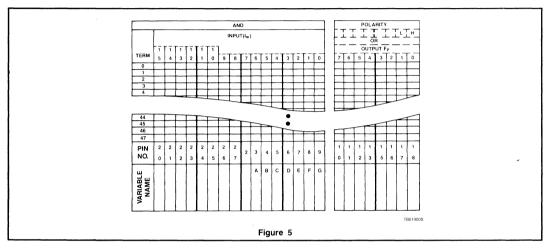

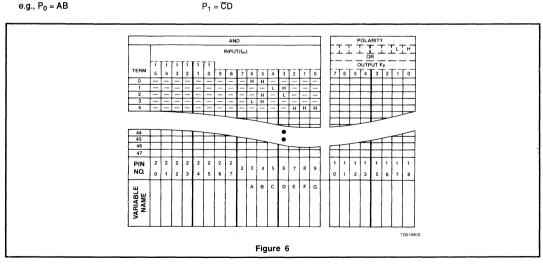

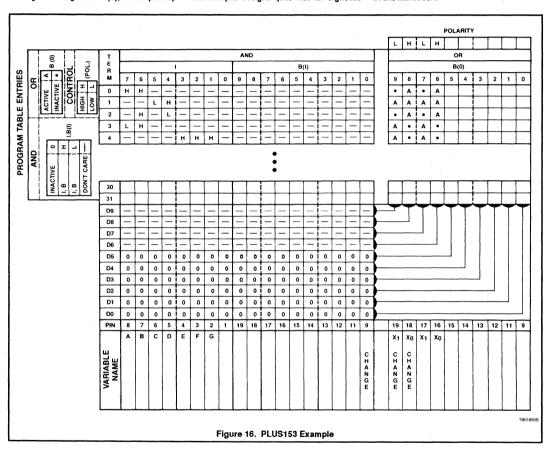

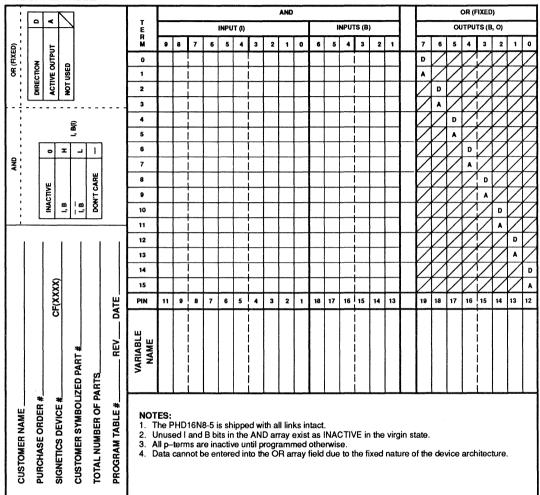

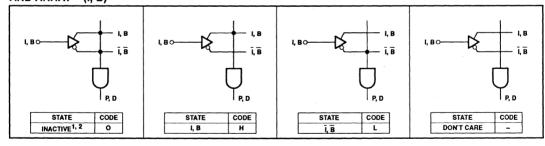

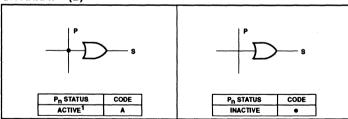

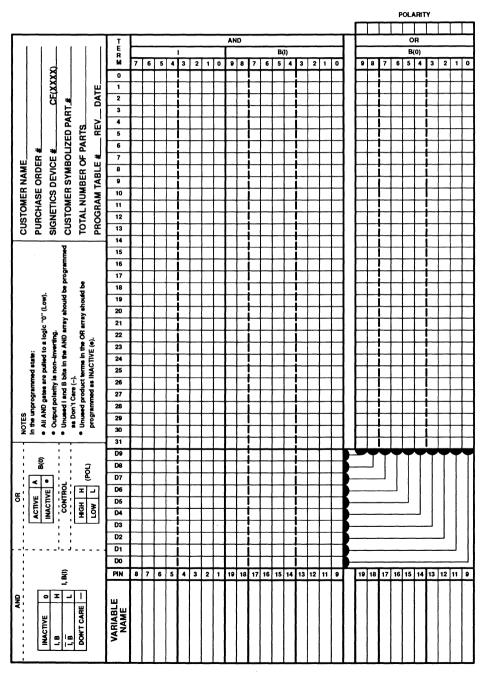

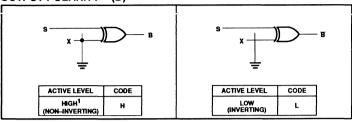

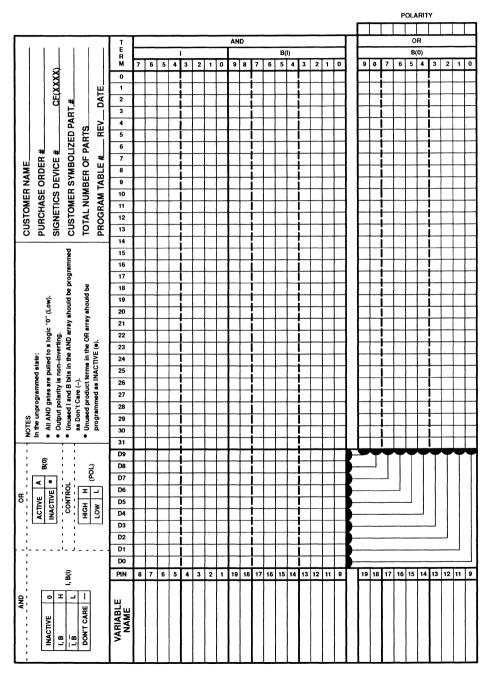

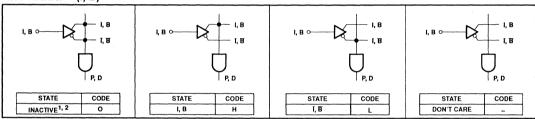

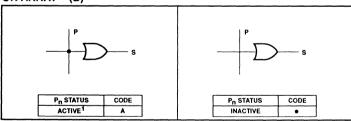

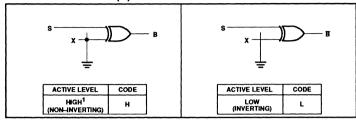

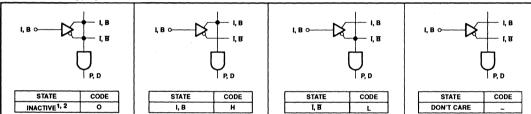

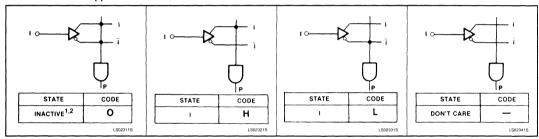

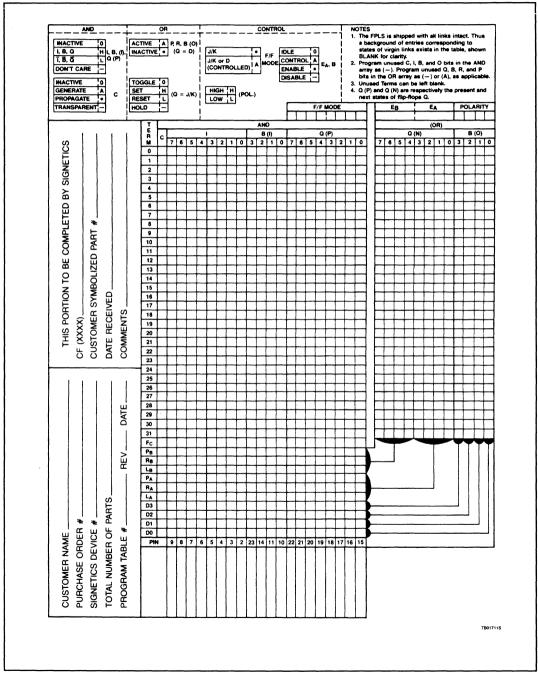

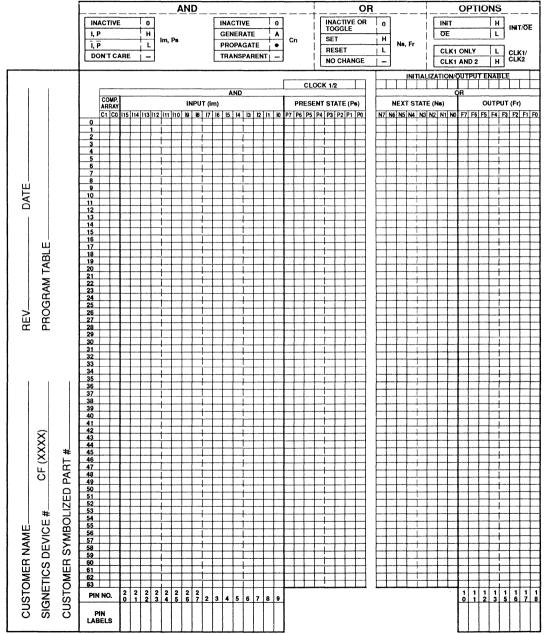

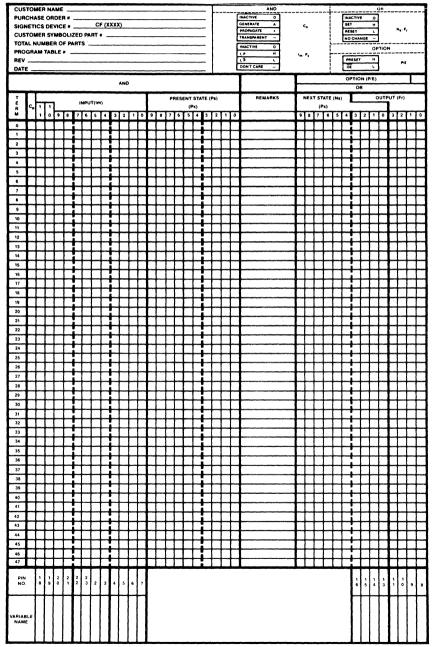

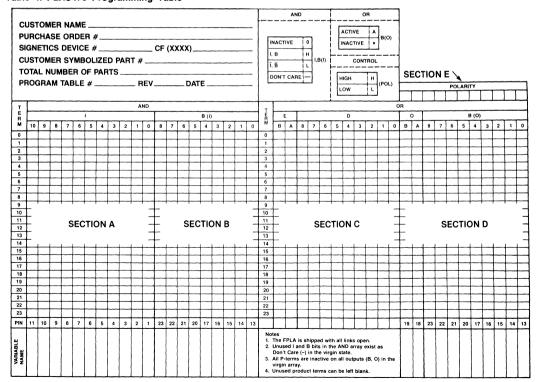

In the previous example, the two Boolean Logic equations were broken into Product terms. Each P-term was then programmed into the P-term section of the PLA Program Table. This was accomplished in the following manner:

#### Step 1

Select which input pins  $I_0 - I_{15}$  will correspond to the input variables. In this case A - G are the input variable names. I6 through Io were selected to accept inputs A - G respectively.

Step 2

Transfer the Boolean Terms to the PLA Program Table. This is done simply by defining each term and entering it on the Program Table.

e.g.,  $P_0 = AB$

This P-term translates to the Program Table by selecting  $A = I_6 = H$  and  $B = I_5 = H$  and entering the information in the appropriate column.

This term is defined by selecting  $C = I_4 = L$  and  $D = I_3 = H$ , and entering the data into the Program Table. Continue this operation until all P-terms are entered into the Program Table.

#### Introduction

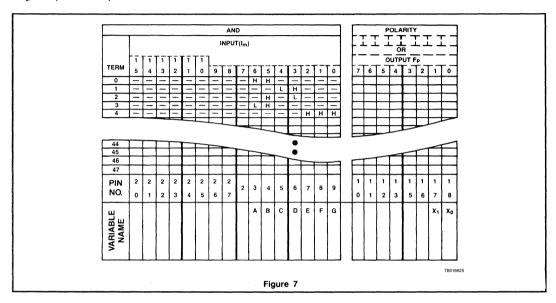

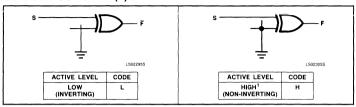

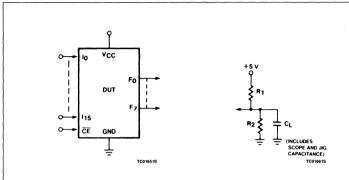

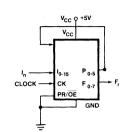

Step 3 Select which output pins correspond to each output function. In this case  $F_0 = Pin \ 18 = X_0$ , and  $F_1 = Pin \ 17 = X_1$ .

Step 4

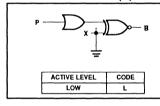

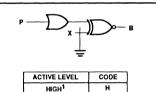

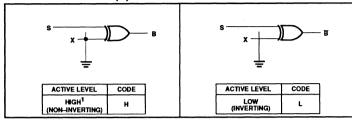

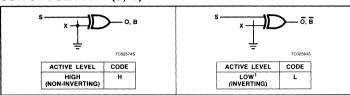

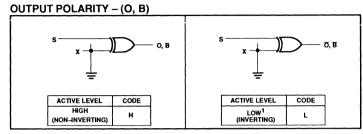

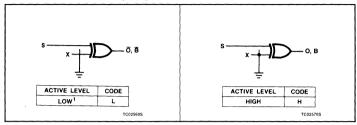

Select the Output Active Level desired for each Output Function. For X<sub>0</sub> the active level

is high for a positive logic expression of this equation. Therefore, it is only necessary to place an (H) in the Active Level box above Out-

put Function 0,  $(F_0)$ . Conversely,  $X_1$  can be expressed as  $X_1$  by placing an (L) in the Active Level box above Output Function 1,  $(F_1)$ .

#### Introduction

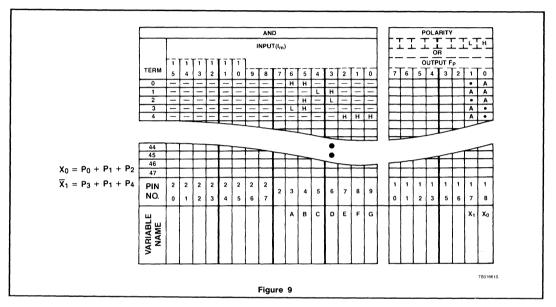

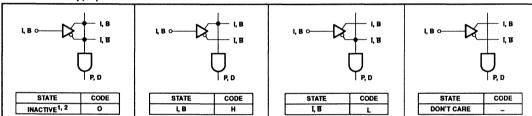

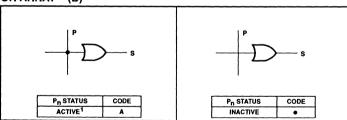

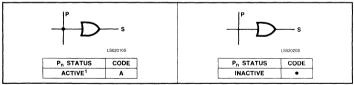

#### Step 5

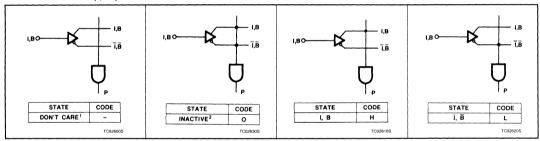

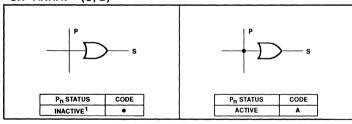

Select the P-Terms you wish to make active for each Output Function. In this case  $X_0 = P_0 + P_1 + P_2$ , so an A has been placed in the intersection box for  $P_0$  and  $X_0$ ,  $P_1$  and  $X_0$  and  $P_2$  and  $X_0$ .

Terms which are not active for a given output are made inactive by placing a (\*) in the box under that P-term. Leave all unused P-terms unprogrammed.

Continue this operation until all outputs have been defined in the Program Table.

#### Step 6

Enter the data into a Signetics approved programmer. The input format is identical to the Signetics Program Table. You specify the P-terms, Output Active Level, and which P-terms are active for each output exactly the way it appears on the Program Table.

#### Introduction

#### **PLD LOGIC SYNTHESIS**

(Continued)

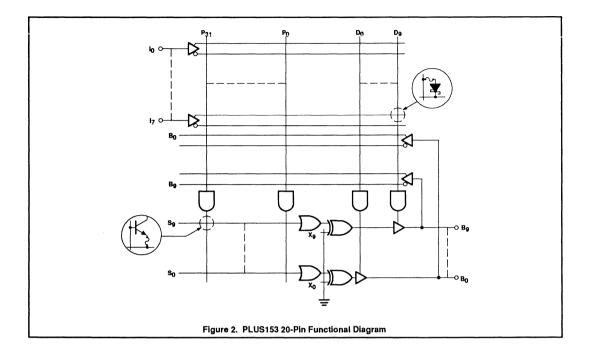

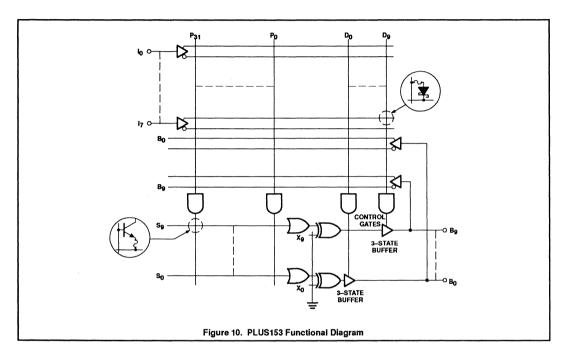

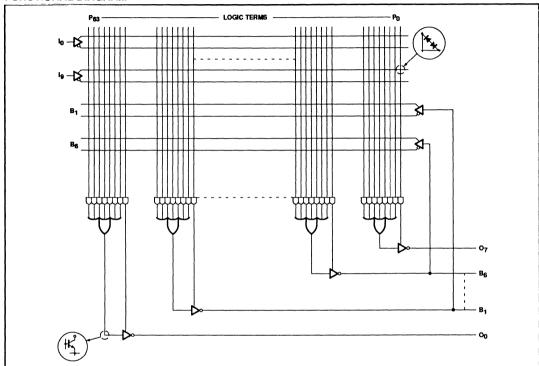

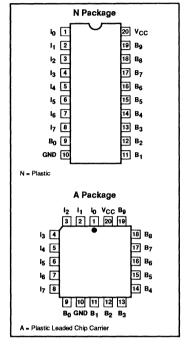

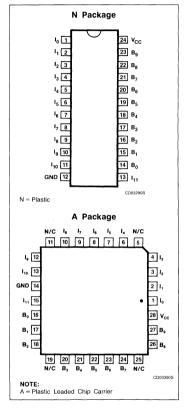

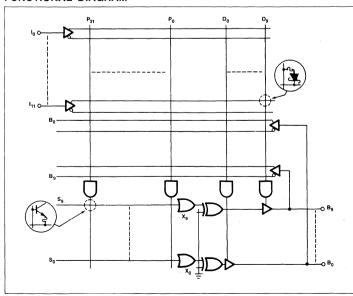

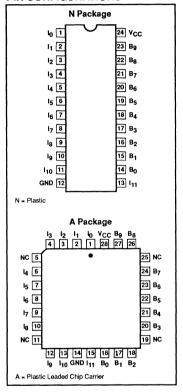

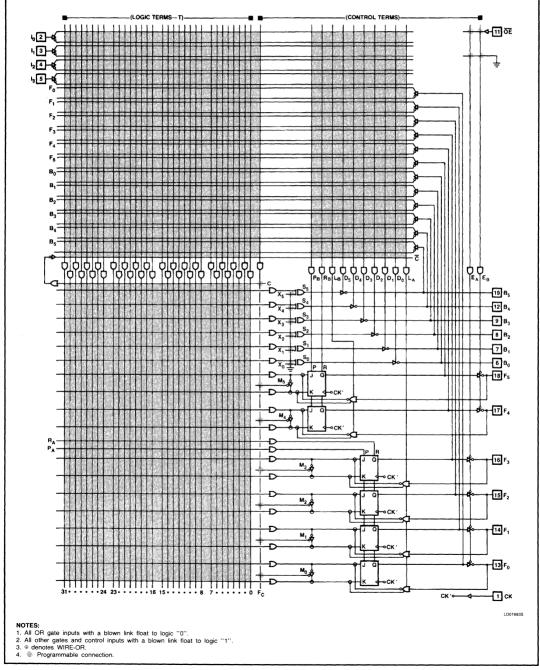

When fewer inputs and outputs are required in a logic design and low cost is most important, the Signetics 20-pin PLD should be considered first choice. The PLUS153 is a PLA with 8 inputs, 10 I/O pins, and 42 product terms. The user can configure the device by defining the direction of the I/O pins. This is easily accomplished by using the direction control terms

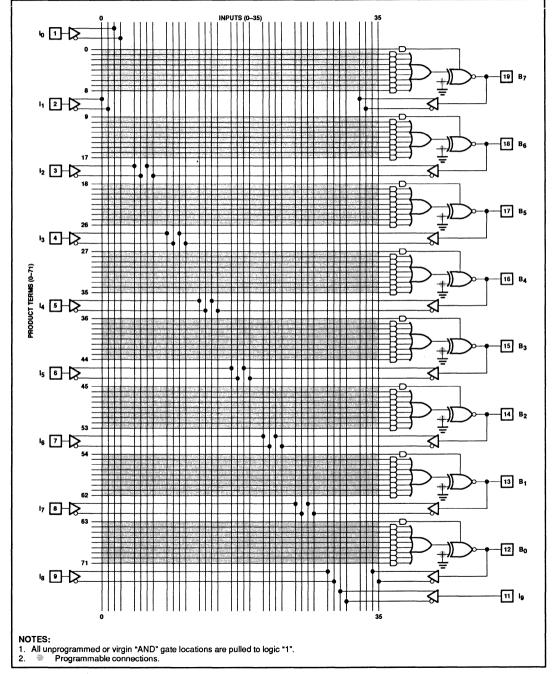

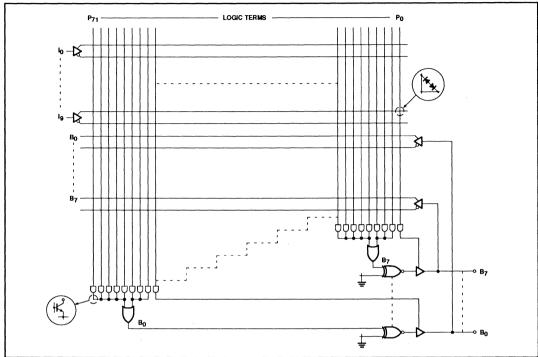

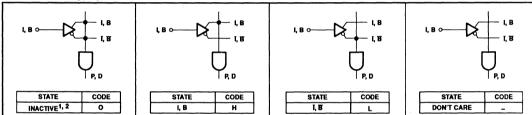

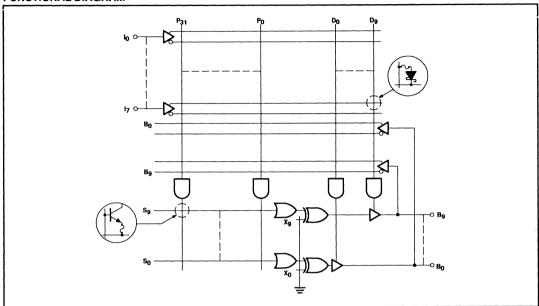

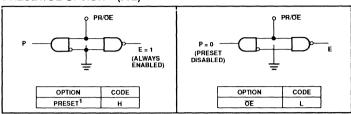

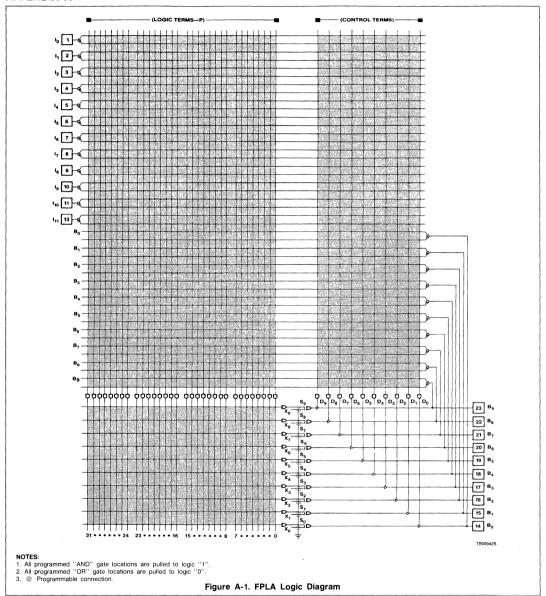

$D_0-D_9$  to establish the direction of pins  $B_0-B_9$ . The D-terms control the 3–State buffers found on the outputs of the Ex–OR gates. Figures 10 and 11 show how the D-term configures each By pin.

#### Introduction

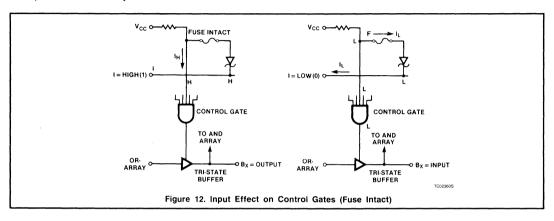

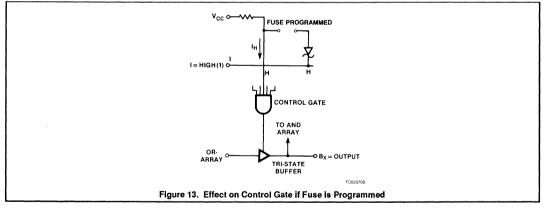

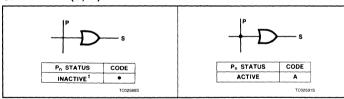

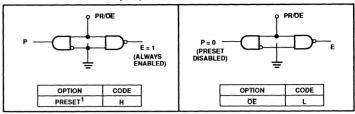

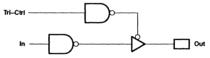

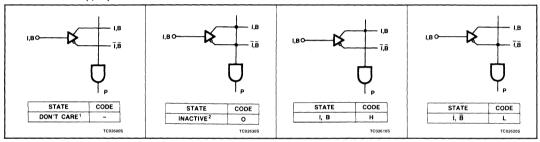

To control each D-term, it is necessary to understand that each control gate is a 36-input AND gate. To make the 3-State buffer active ( $B_x$  pin an output), the output of the control gate must be at logic HIGH (1). This can be accomplished in one of two ways. A HIGH can

be forced on all control gate input nodes, or fuses can be programmed. When a fuse is programmed, that control gate input node is internally pulled up to HIGH (1). See Figure 12 and Figure 13. Programming the fuse permanently places a HIGH (1) on the input to the control gate. The input pin no longer has any effect on that state.

#### Introduction

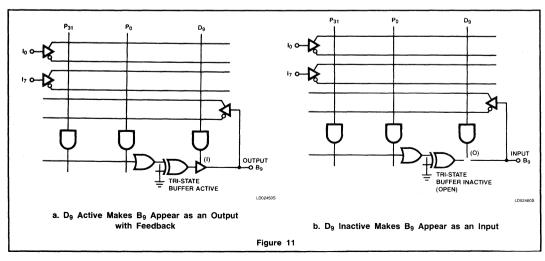

#### **DEDICATING BY PIN DIRECTION**

Since each input to the D-terms is true and complement buffered (see Figure 11), when the device is shipped with all fuses intact, all control gates have half of the 36 input lines at logic low (0). The result of this is all Control Gate outputs are low (0) and the 3-State buffers are inactive. This results in all B<sub>X</sub> pins being in the input condition. the resultant device is, therefore, an 18-input, 0-output FPLA. While useful as a bit

bucket or Write—Only—Memory (WOM), most applications require at least one output. Clearly, the first task is to determine which of the  $B_X$  pins are to be outputs. The next step is to condition the control gate to make the 3–State buffer for those gates active. To dedicate  $B_0$  and  $B_1$  as outputs, it is necessary to program all fuses to the inputs to Control Gates  $D_0$  and  $D_1$ . This internally pulls all inputs to those gates to HIGH (1) permanently, since all inputs to the Control

Gates are HIGH (1), the output is HIGH (1) and the 3–State buffers for  $B_0$  and  $B_1$  are active. This permanently enables  $B_0$  and  $B_1$  as outputs. Note that even though  $B_0$  and  $B_1$  are outputs, the output data is available to the AND array via the internal feedback (see Figure 11a).

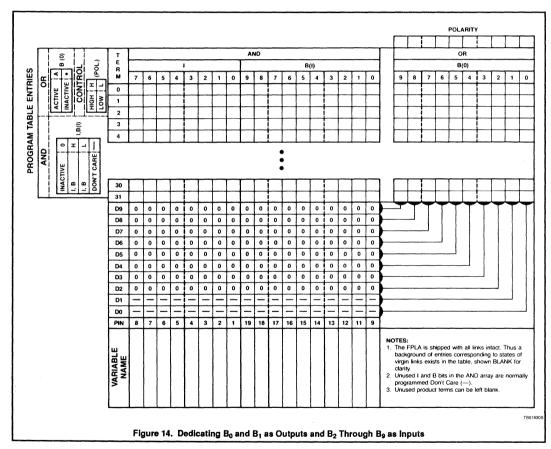

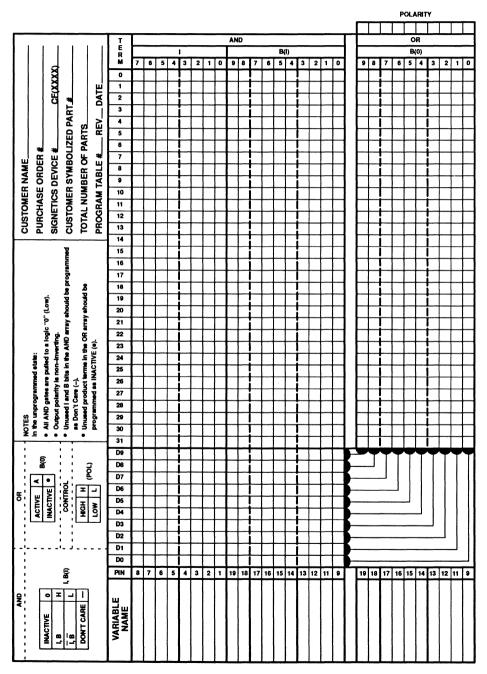

To program this data, the PLUS153 Program Table is used as shown in Figure 14.

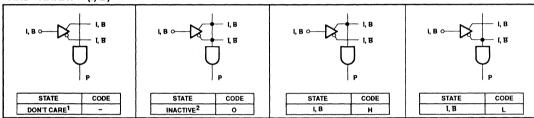

#### Introduction

By placing a (—) Don't Care in each input box you are specifying that the True and Complement fuses are programmed on each Control Gate, thus permanently dedicating the  $B_0$  and  $B_1$  pins as outputs. By placing a (0) in all input boxes for  $B_2-B_9$ , you are specifying that both True and Complement fuses are intact. This causes a low (0) to be forced on half of the Control Gate inputs, guaranteeing the output of the Control Gate outputs are low (0). When the Control Gate outputs are low (0), the 3–State buffer is inactive and the  $B_2-B_9$  pins are

enabled as inputs. All  $B_X$  pin directions can be controlled in this manner.

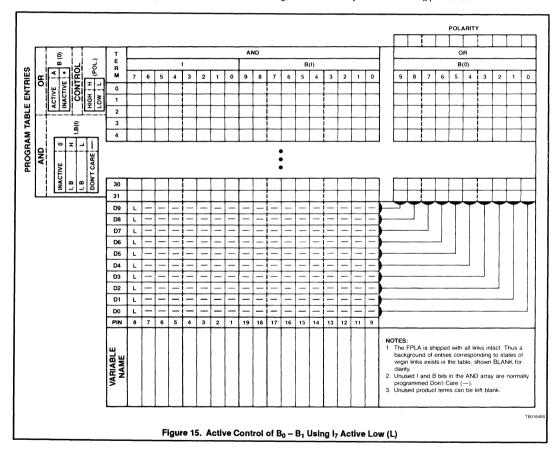

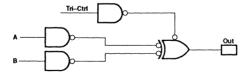

#### **ACTIVE DIRECTION CONTROL**

Sometimes it is necessary to be able to actively change the direction of the B<sub>X</sub> pins without permanently dedicating them. Some applications which require this include 3–State bus enable, multi-function decoding, etc. This can easily be

done by programming the Control Gate to respond to one or more input pins. It is only necessary to select which  $I_X$  and  $B_X$  pins will control the pin directions and the active level HIGH (H) or LOW (L) that will be used. The PLUS153 Program Table in Figure 15 shows the method of controlling  $B_0-B_9$  with  $I_7$ . When  $I_7$  is LOW (L), pins  $B_0-B_9$  are outputs; when  $I_7$  is HIGH (H), pins  $B_0-B_9$  are inputs. Note that by programming all other  $I_X$  and  $B_X$  pins as DON'T CARE (—), they are permanently disconnected from control of  $B_X$  pin direction.

#### Introduction

The previous 28-pin logic synthesis example could be done on the PLUS153 as follows:

$X_0 = AB + \overline{C}D + B\overline{D}$

X1 = AB + CD + EFG

Note that  $B_0$  was used as a CHANGE input. When  $B_0$  is HIGH (H) the outputs appear on  $B_8$  and  $B_9$ . When  $B_0$  is LOW (L), the outputs ap-

pear on  $B_6$  and  $B_7$ .  $B_1$  through  $B_5$  are not used and therefore left unprogrammed.

Signetics offers two packages for user friendly design assistance. The first package, AMAZE, has evolved over 10 years to support Signetics programmable products with logic equation, state equation, and schematic entry. AMAZE can compile designs quite well for Signetics

lower density parts. However, to satisfy the needs of Programmable Macro Logic users, Signetics developed an additional software package called SNAP. SNAP expands upon the capabilities of AMAZE in its approach to design implementation, more closely resembling a gate array methodology. Both of these products are described in more depth at a later point in this handbook.

#### Introduction

### SEQUENTIAL LOGIC CONSIDERATIONS

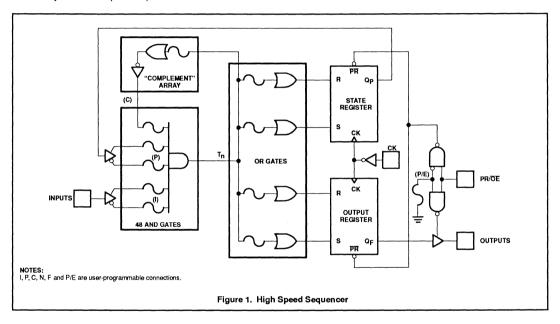

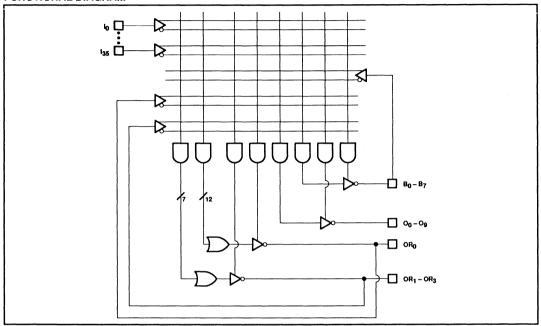

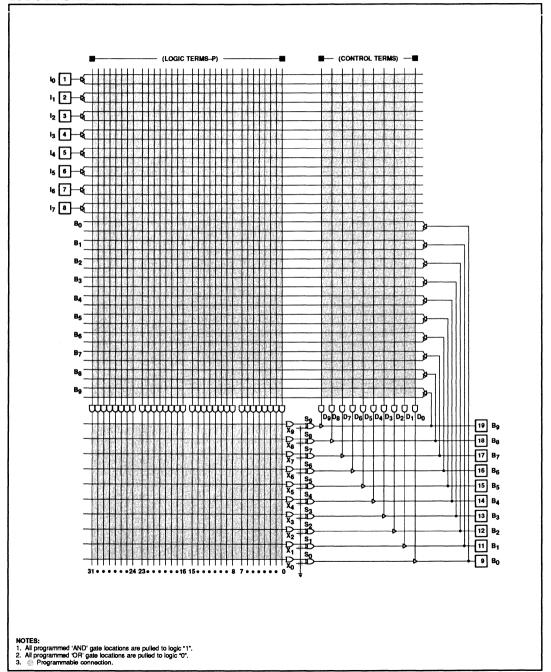

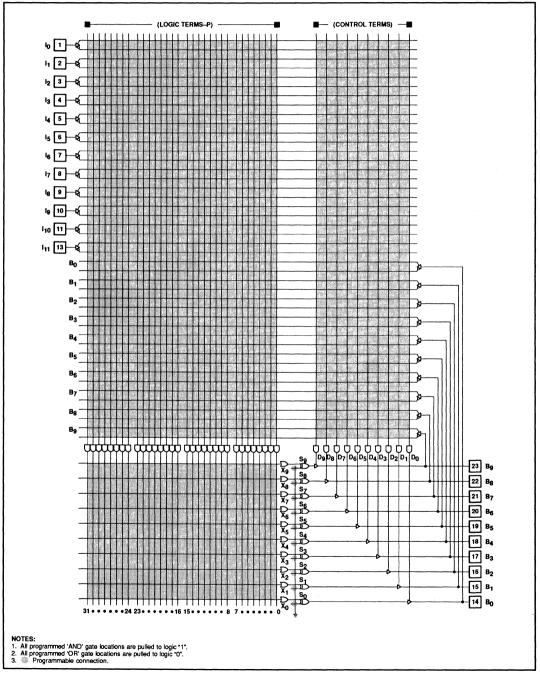

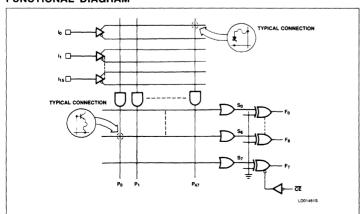

The PLUS405, PLUS105 and PLC42VA12 represent significant increases in complexity when compared to the combinatorial logic devices previously discussed. By combining the AND/OR combinatorial logic with clock output flip-flops and appropriate feedback, Signetics has created the first family of totally flexible sequential logic machines.

The PLUS405 (Programmable Logic Sequencer) is an example of a high-order machine whose applications are many. Application areas for this device include VRAM, DRAM, Bus and LAN control. The PLUS405 is fully capable of performing fast sequential operations in relatively high-speed processor systems. By placing repetitive sequential operations on the PLUS405, processor overhead is reduced.

The following pages summarize the PLUS405 architecture and features.

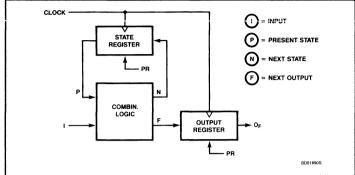

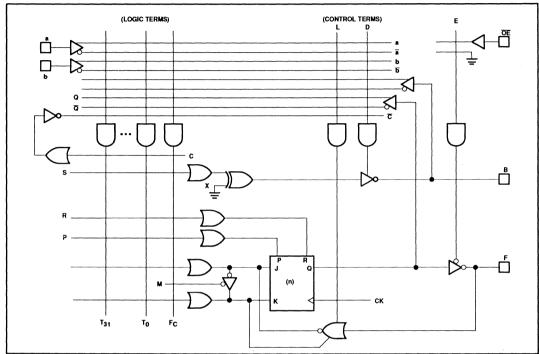

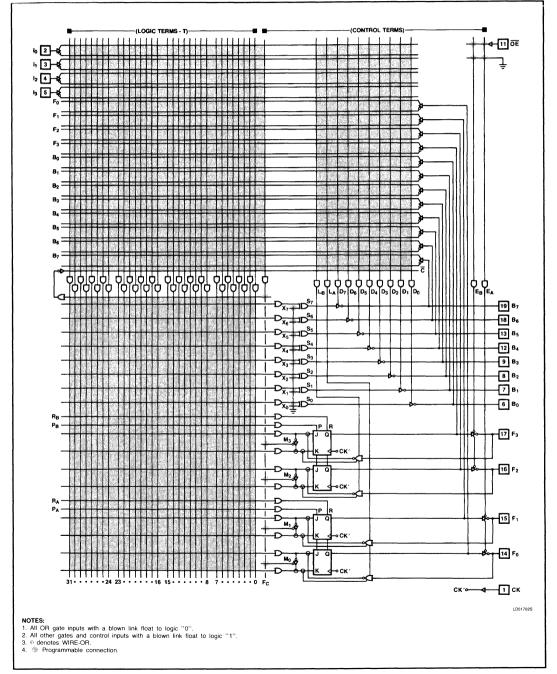

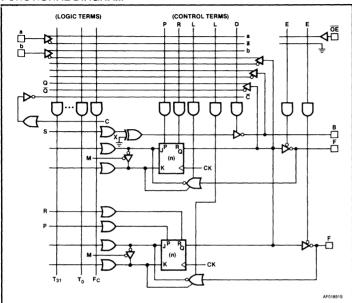

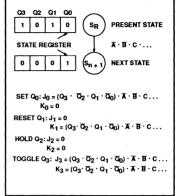

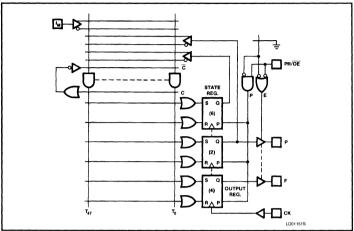

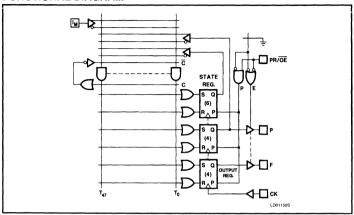

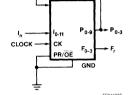

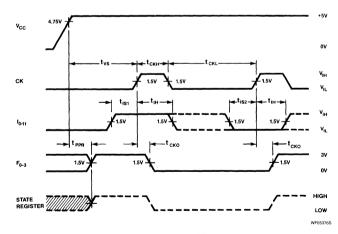

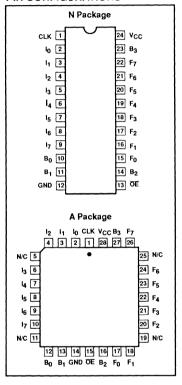

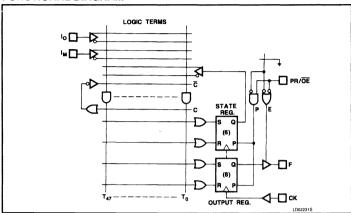

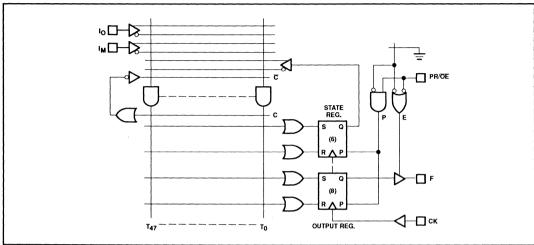

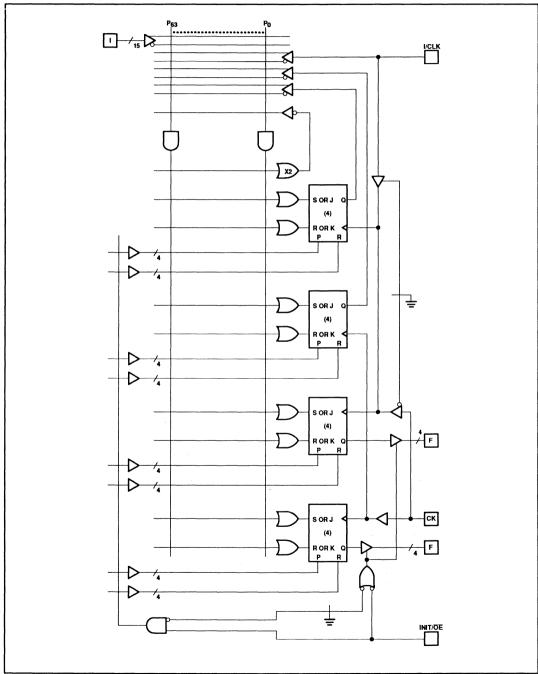

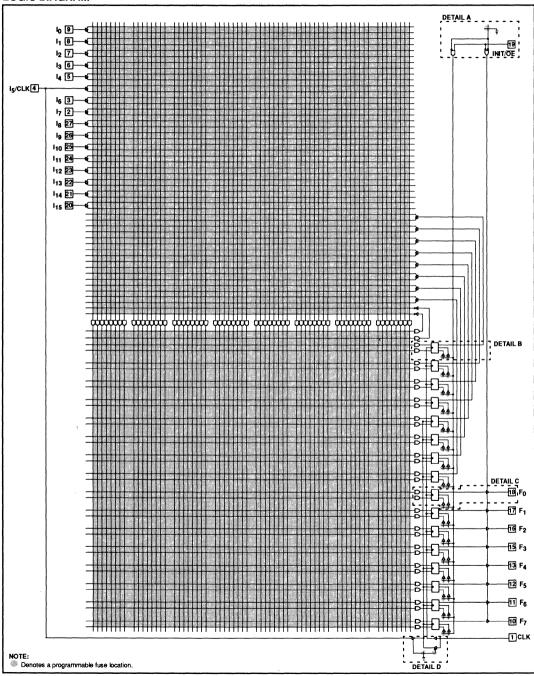

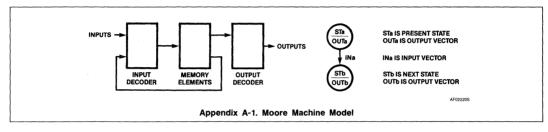

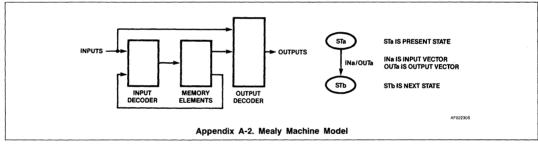

#### Sequencer Architecture

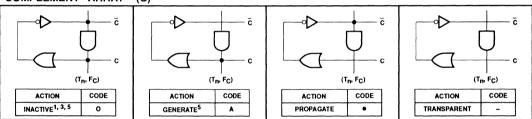

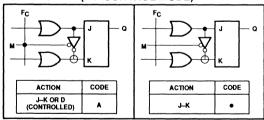

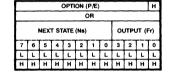

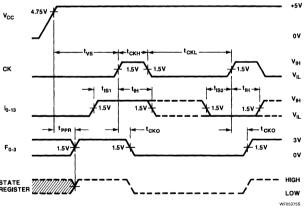

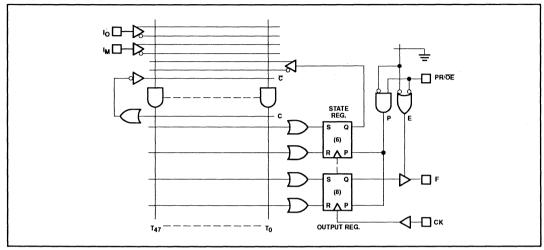

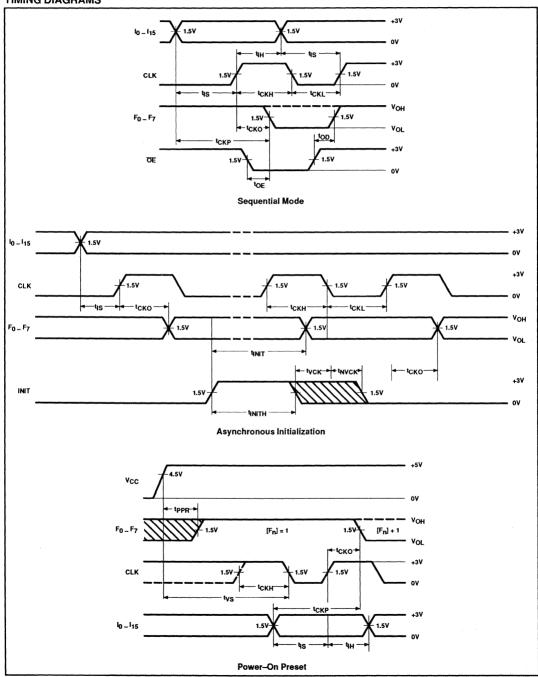

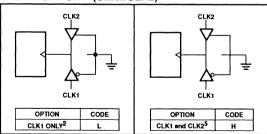

The PLUS405 Logic Sequencer is a programmable state machine, in which the output is a function of the present state and the present input

With the PLUS405, a user can program any logic sequence expressed as a series of jumps between stable states, triggered by a valid input condition (I) at clock time (t). All stable states are stored in the State Register. The logic output of the machine is also programmable, and is stored in the Output Register. The PLUS105 is a subset of the PLUS405.

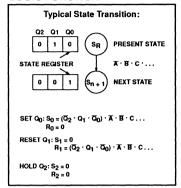

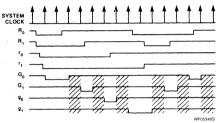

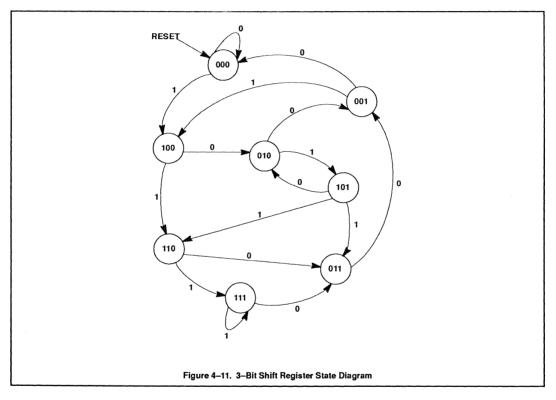

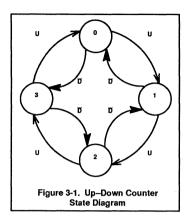

#### **Clocked Sequence**

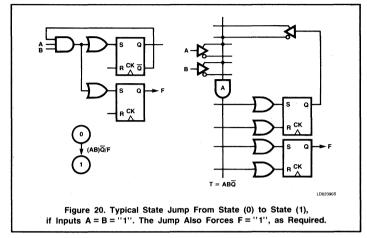

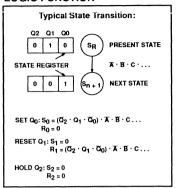

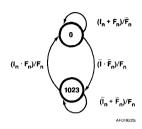

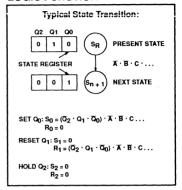

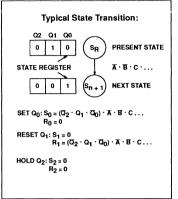

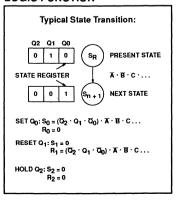

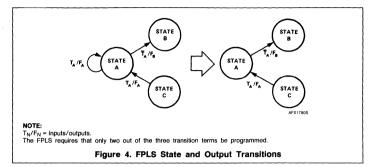

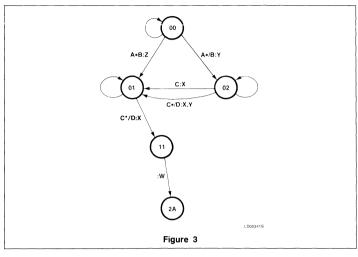

A synchronous logic sequence can be represented as a group of circles interconnected with arrows. The circles represent stable states, labeled with an arbitrary numerical code (binary, hex, etc.) corresponding to discrete states of a suitable register. The arrows represent state transitions, labeled with symbols denoting the jump condition and the required change in output. The number of states in the sequence depends on the length and complexity of the desired algorithm.

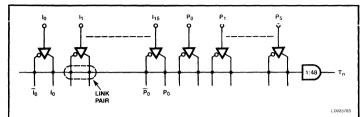

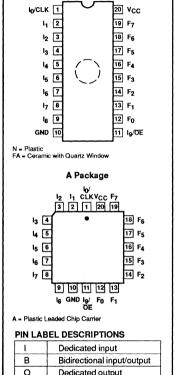

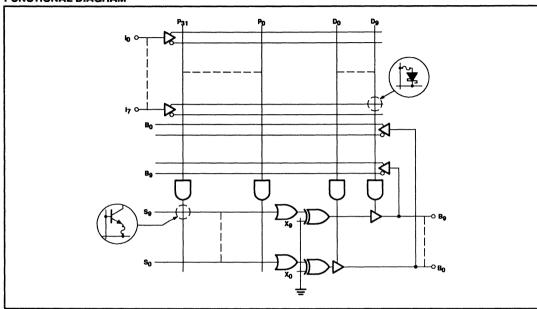

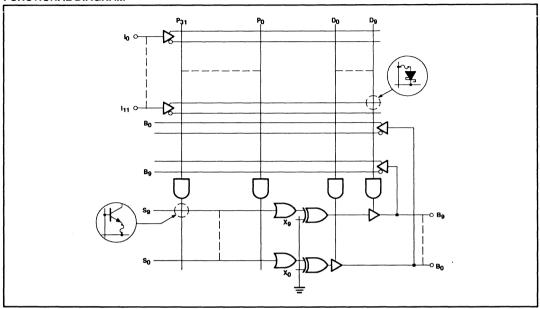

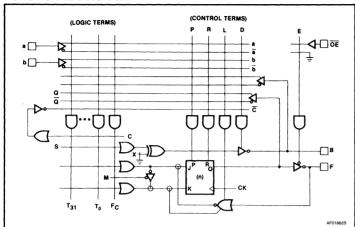

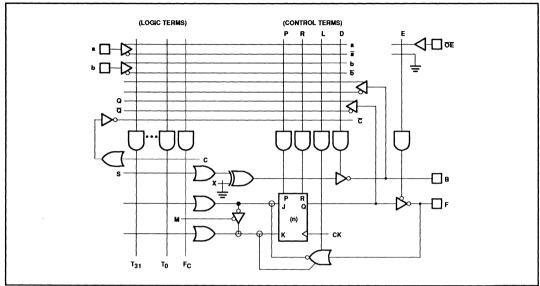

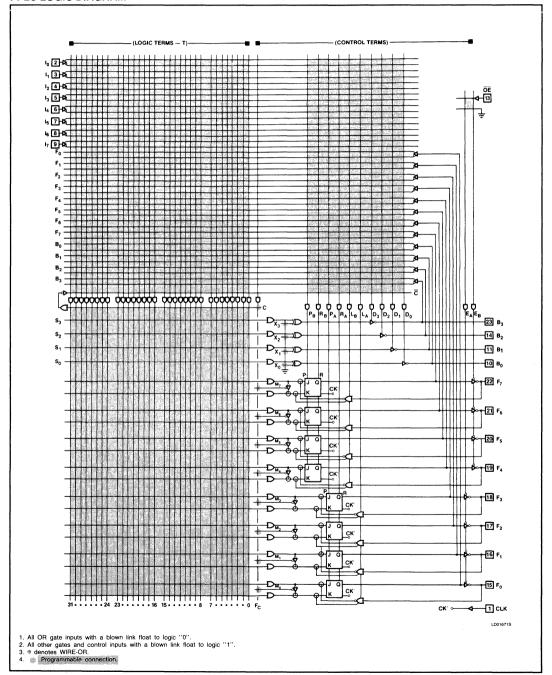

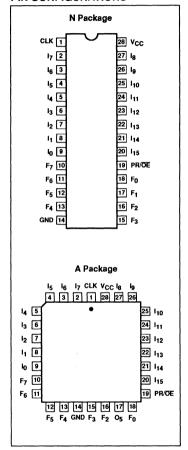

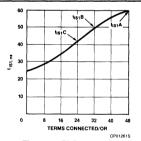

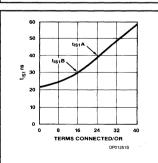

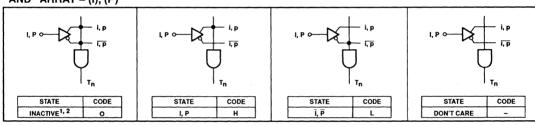

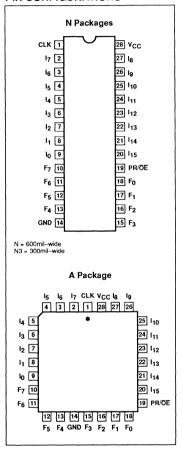

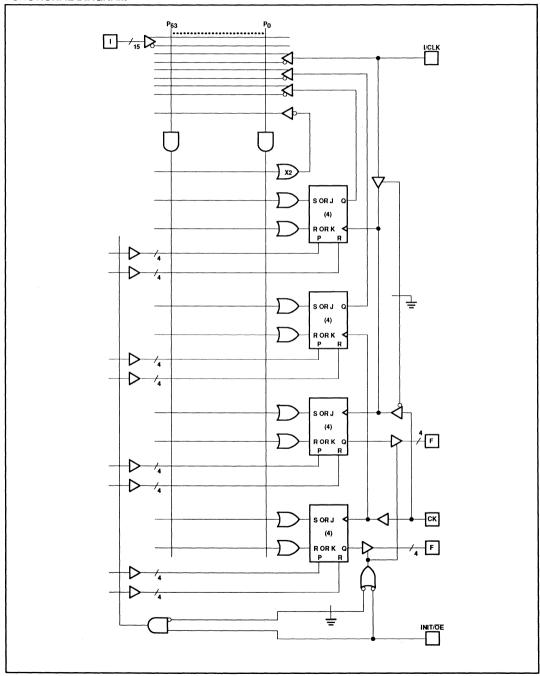

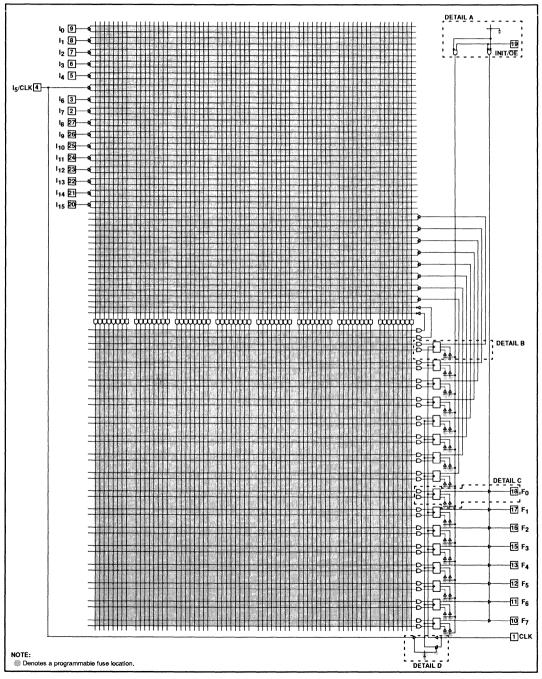

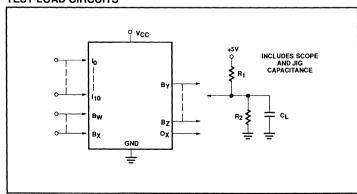

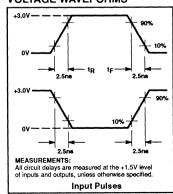

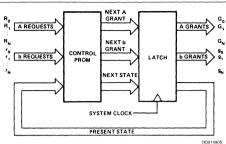

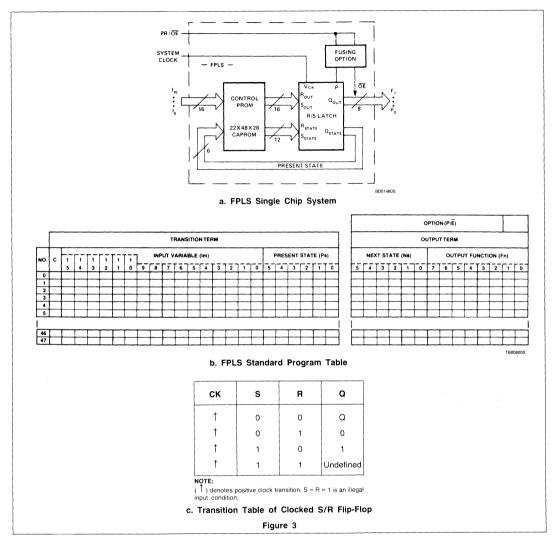

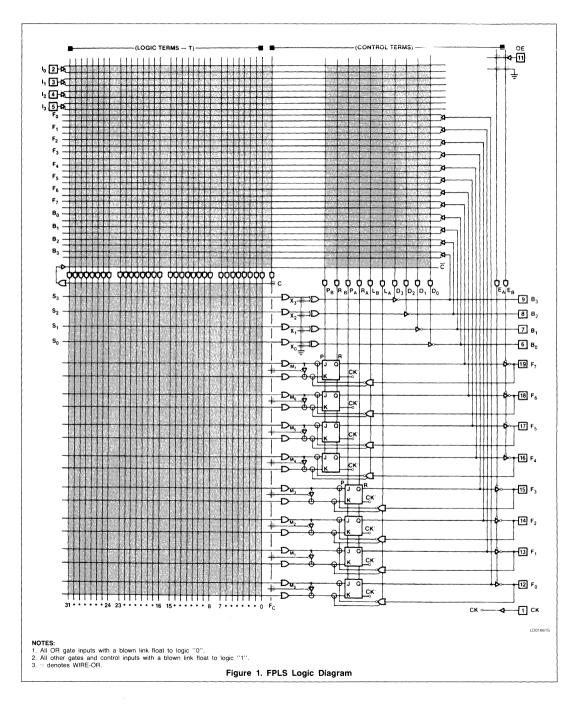

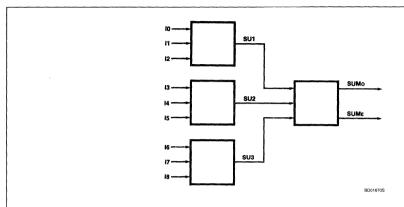

Figure 17. Basic Architecture of PLS105 FPLS. I, P, N, and F are Multi-line Paths Denoting Groups of Binary Variables Programmed by The User.

Figure 18. Typical State Diagram. I<sub>1-3</sub> Are Jump Conditions Which Must be Satisfied Before Any Transitions Take Place. F<sub>r</sub> Are Changes in Output Triggered by I<sub>m</sub>, and Stored in The Output Register. State Transitions a → b and c → d Involve No Output Change.

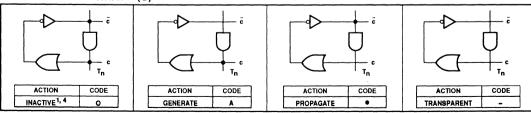

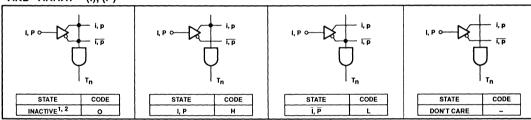

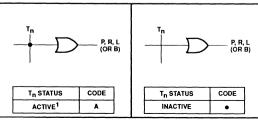

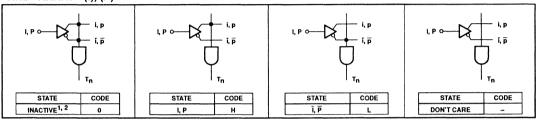

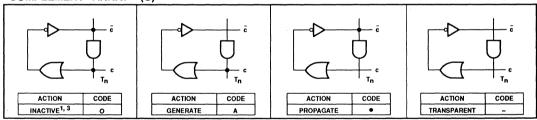

Figure 19. Typical State Transition Between Any Two States of Figure 18. The Arrow Connecting the Two States Gives Rise to a Transition Term T<sub>n</sub>. I is the Jump Condition.

#### Introduction

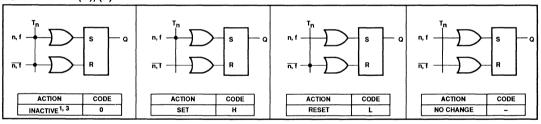

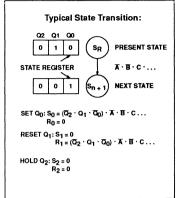

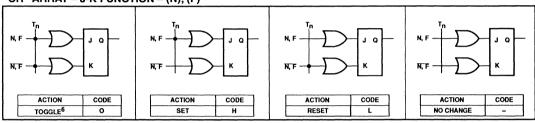

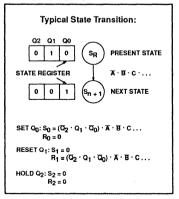

#### State Jumps

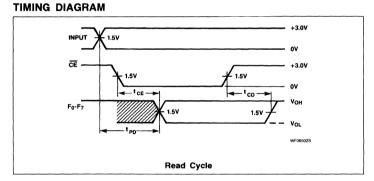

The state from which a jump originates is referred to as the Present state (P), and the state to which a jump terminates is defined as the Next state (N). A state jump always causes a change in state, but may or may not cause a change in machine output (F).

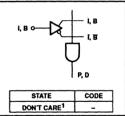

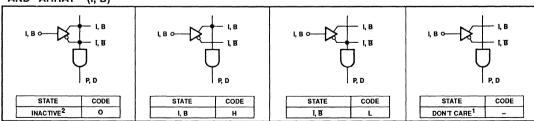

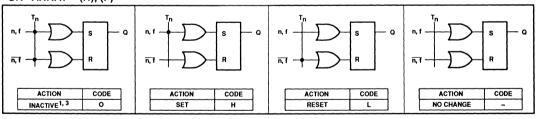

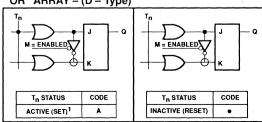

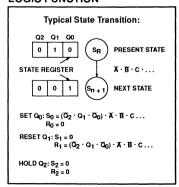

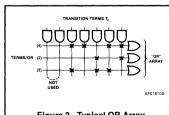

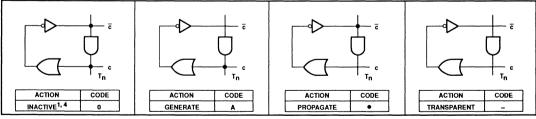

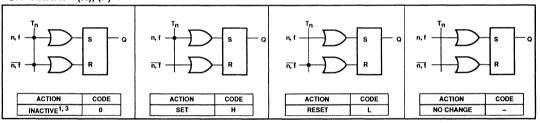

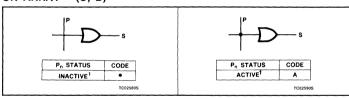

State jumps can occur only via "transition terms"  $T_n$ . These are logical AND functions of the clock (f), the Present state (P), and a valid input (I). Since the clock is actually applied to the State Register,  $T_n = I \bullet P$ . When  $T_n$  is "true", a control signal is generated and used at clock time (t) to force the contents of the State Register from (P) to (N), and to change the contents of the Output Register (if necessary). The simple state jump in Figure 20, involving 2 inputs, 1 state bit, and 1 output bit, illustrates the equivalence of discrete and programmable logic implementations.

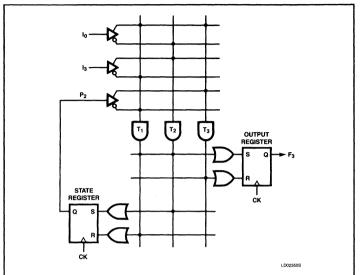

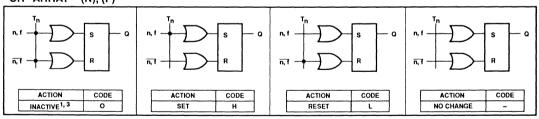

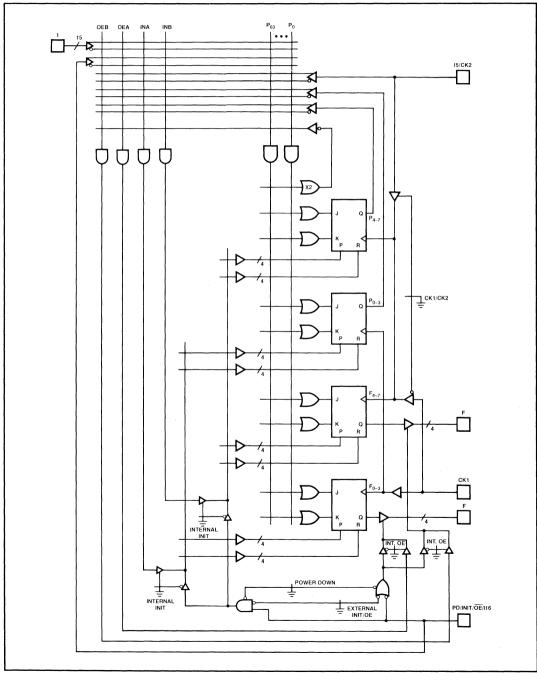

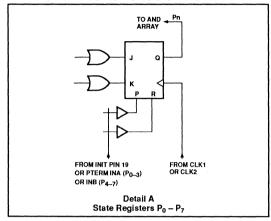

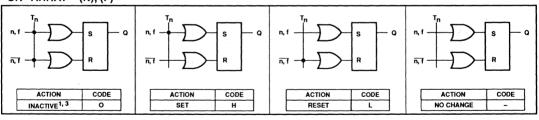

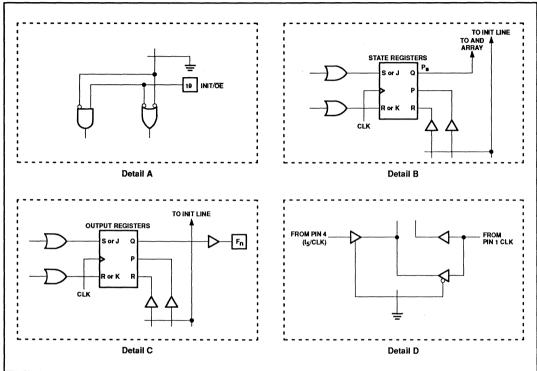

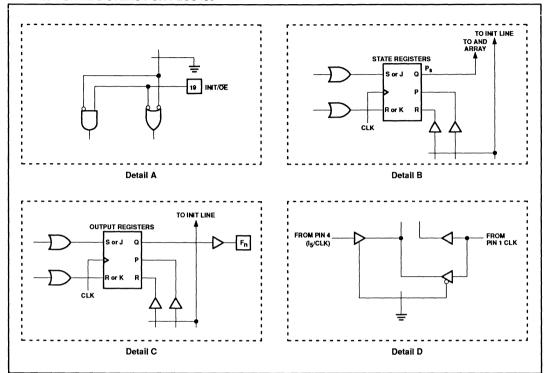

#### **Sequencer Logic Structure**

The Sequencer consists of programmable AND and OR gate arrays which control the Set and Reset inputs of a State Register, as well as monitor its output via an internal feedback path. The arrays also control an independent Output Register, added to store output commands generated during state transitions, and to hold the output constant during state sequences involving no output changes. If desired, any number of bits of the Output Register can be used to extend the width of the State Register, via external feedback.

#### Introduction

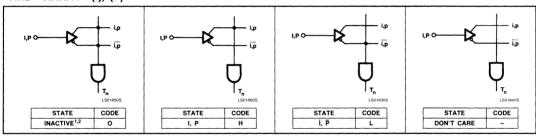

Figure 22. Typical AND Gate Coupled to (I) and (P) Inputs. If at Least One Link Pair Remains Intact,  $\mathbf{T}_n$  is Unconditionally Forced Low.

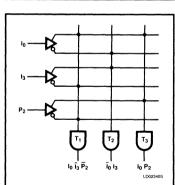

Figure 24. Typical Transition Terms Involving Arbitrary Inputs and State Variables. All Remaining Gate Inputs Are Programmed Don't Care. Note That T<sub>2</sub> Output is State Independent.

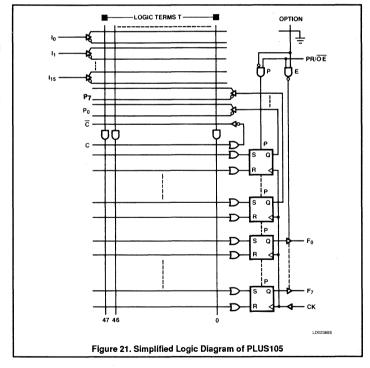

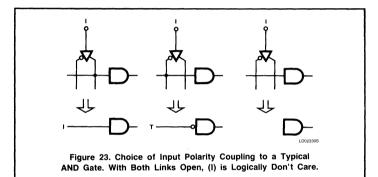

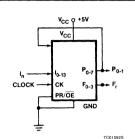

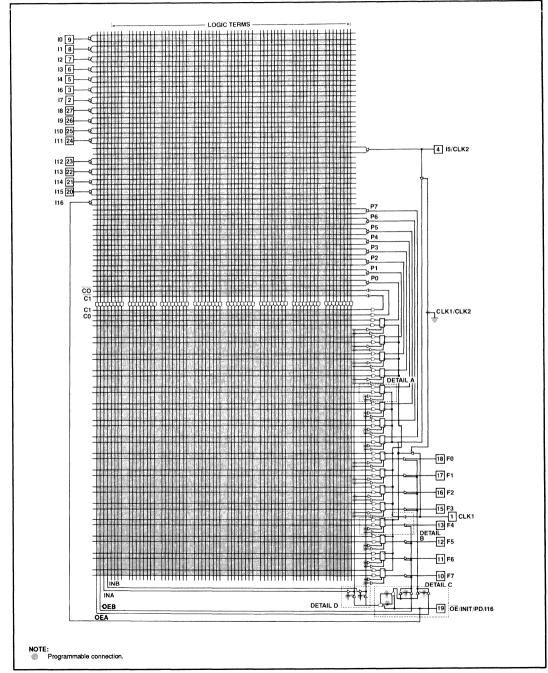

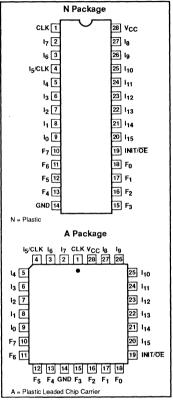

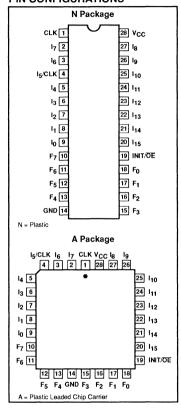

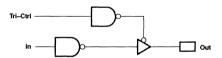

#### **Input Buffers**

16 external inputs ( $I_m$ ) and 6 internal inputs ( $P_s$ ), fed back from the State Register, are combined in the AND array through two sets of True/Complement (T/C) buffers. There are a total of 22 T/C buffers, all connected to multi–input AND gates via fusible links which are initially intact.

Selective fusing of these links allows coupling either True, Complement, or Don't Care values of  $(I_m)$  and  $(P_s)$ .

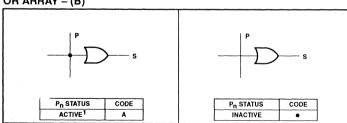

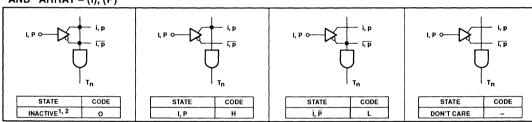

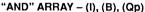

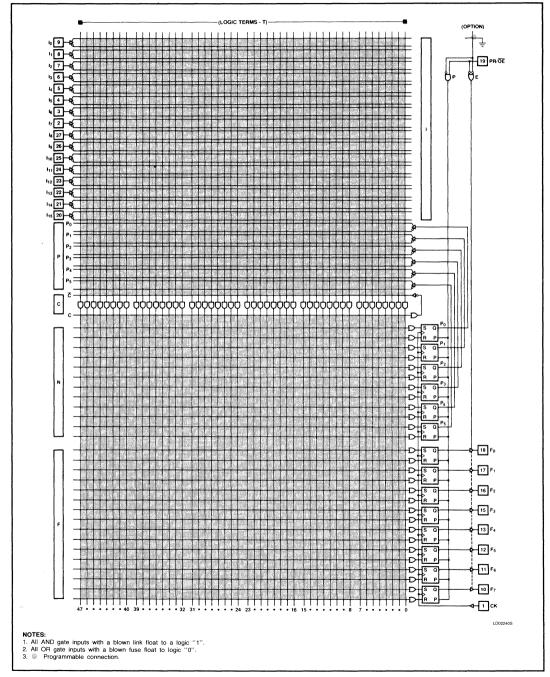

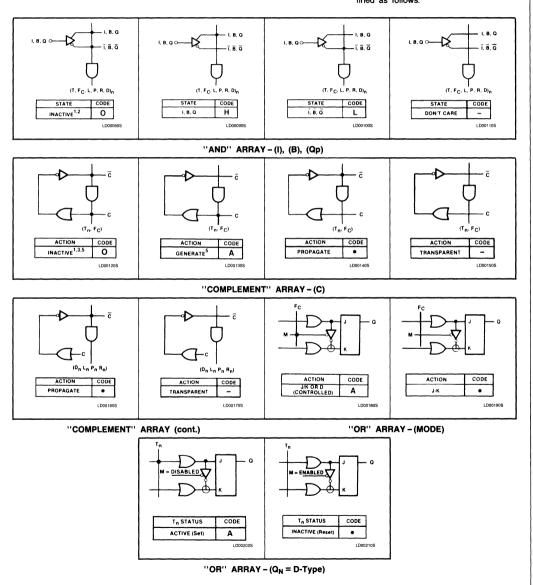

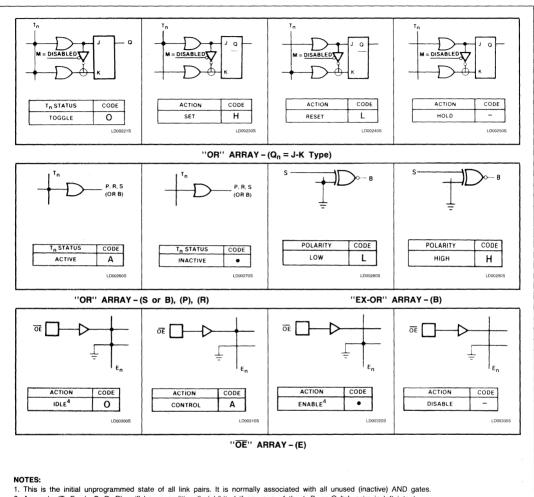

#### "AND" Array

State jumps and output changes are triggered at clock time by valid transition terms  $T_n$ . These are logical AND functions of the present state (P) and the present input (I).

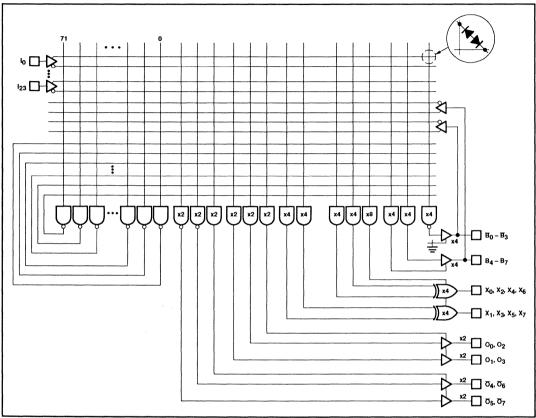

The PLUS105 AND Array contains a total of 48 AND gates. Each gate has 45 inputs – 44 connected to 22 T/C input buffers, and 1 dedicated to the Complement Array. The outputs of all AND gates are propagated through the OR Array, and used at clock time (t) to force the contents of the State Register from (P) to (N), they are also used to control the Output Register, so that the FPLS 8-bit output F, is a function of the inputs and the present state. The PLUS405 contains 64 AND gates in its' AND array.

#### Introduction

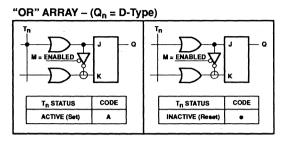

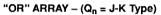

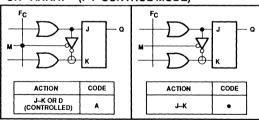

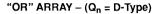

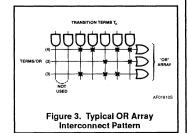

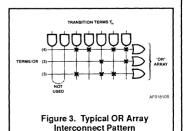

#### "OR" Array

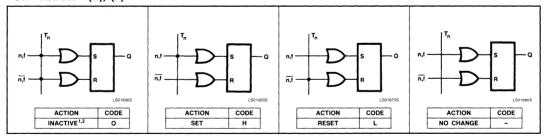

In general, a docked sequence will consist of several stable states and transitions, as determined by the complexity of the desired algorithm. All state and output changes in the state diagram imply changes in the contents of State and Output Registers.

Thus, each flip–flop in both registers may need to be conditionally set or reset several times with  $T_n$  commands. This is accomplished by selectively ORing through a programmable OR Array all AND gate outputs  $T_n$  necessary to activate the proper flip–flop control inputs.

The PLUS105 OR Array consists of 14 pairs of OR gates, controlling the S/R inputs of 14 State and Output Register stages, and a single NOR gate for the Complement Array. All gates have 48 inputs for connecting to all 48 AND gates. The PLUS405 uses 64 input gates.

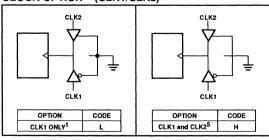

The PLUS405 contains 16 pairs of OR gates controlling state transitions and output stages and two additional NOR gates for dual complement arrays.

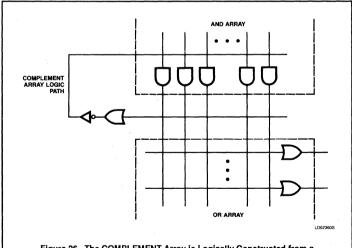

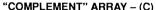

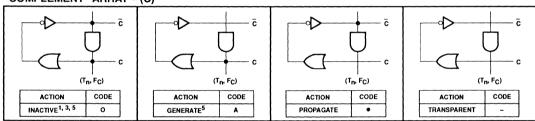

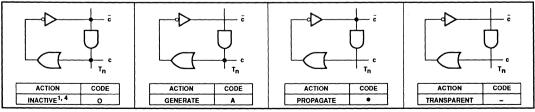

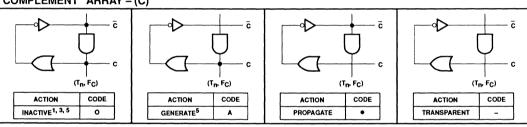

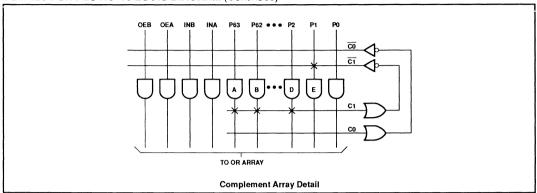

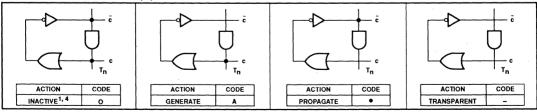

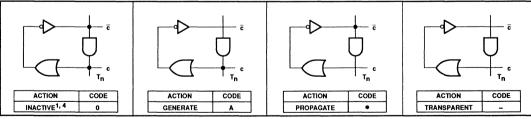

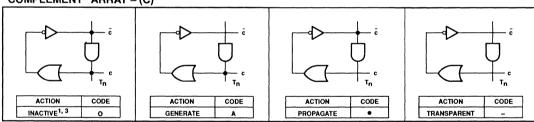

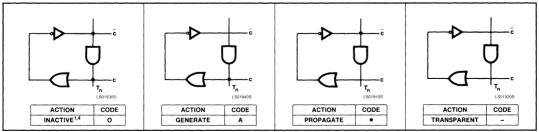

#### Complement Array

The COMPLEMENT Array provides an asynchronous feedback path from the OR Array back to the AND Array.

This structure enables the sequencer to perform both direct and complement sequential state jumps with a minimum of transition (AND) terms

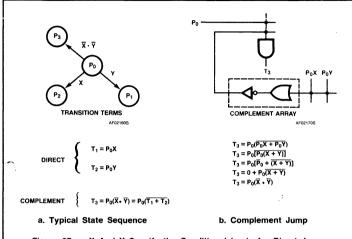

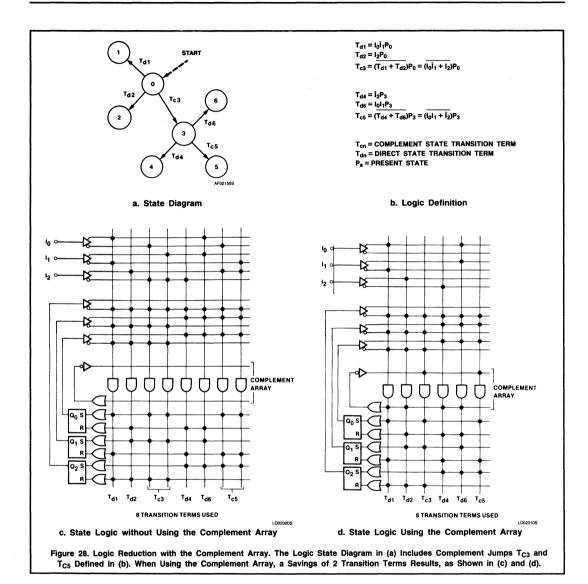

Typically direct jumps, such as  $T_1$  and  $T_2$  in Figure 27 require only a single AND gate each. But a complement jump such as  $T_3$  generally requires many AND gates if implemented as a direct jump. However, by using the Complement Array, the logic requirements for this type of jump can be handled with just one more gate from the AND Array. Because it can be split into separate machines (2 clocks), the PLUS405 incorporates two COMPLEMENT Arrays.

Figure 25. Typical OR Array Gating of Transition Terms T<sub>1,2,3</sub> Controlling Arbitrary State and Output Register Stages.

Figure 26. The COMPLEMENT Array is Logically Constructed from a multiple input Programmable NOR Gate. All AND Terms Coupled to the OR Gate are Complemented at the Inverter Output, and Can be Fed Back as Inputs to the AND Array.

#### Introduction

As indicated in Figure 28, the single Complement Array gate may be used for many states of the state diagram. This happens because all transition terms linked to the OR gate include the present state as a part of their conditional logic. In any particular state, only those transition terms which are a function of that state are enabled; all other terms coupled to different states are disabled and do not influence the output of the Complement Array. As a general rule of thumb, the Complement Array can be used as many times as there are states.

Figure 27. a. X And Y Specify the Conditional Logic for Direct Jump Transition Terms  $T_1$  and  $T_2$ . The Complement Jump Term  $T_3$  is True Only When Both  $T_1$  and  $T_2$  are False. b. Note that the Complementary Logic Expression for  $T_3$ ,  $\overline{T}_1 + \overline{T}_2$ , Corresponds Exactly to the Logic Structure of the Complement Array.

#### Introduction

Additional features are available depending on a specific part. In particular, the PLC42VA12 has everything mentioned here, and more.

More details on PLAs, PAL-Type devices and Sequencers can be found in the application section later in the manual.

Programmable Macro Logic, Signetics very high density logic is fully described in detail in its own section.

### Quality and Reliability

#### **Programmable Logic Devices**

### SIGNETICS PROGRAMMABLE

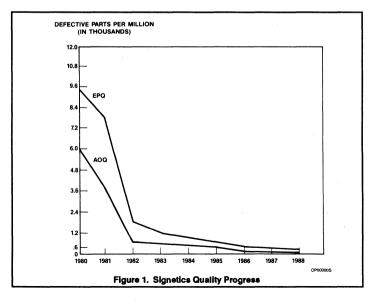

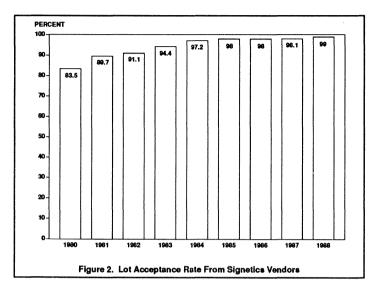

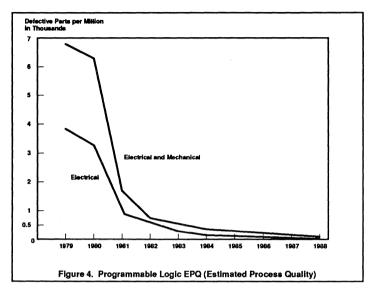

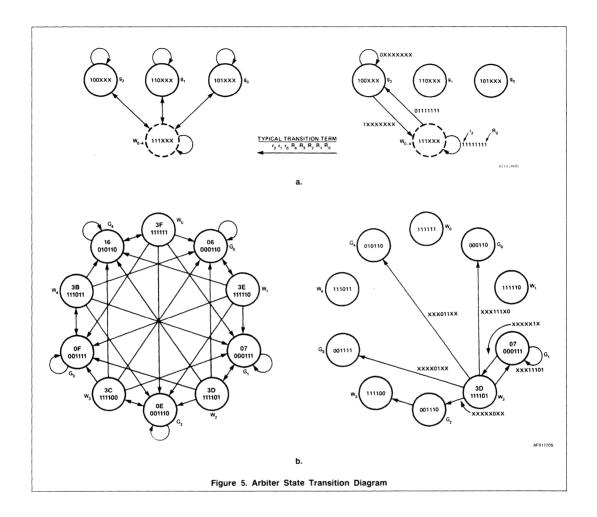

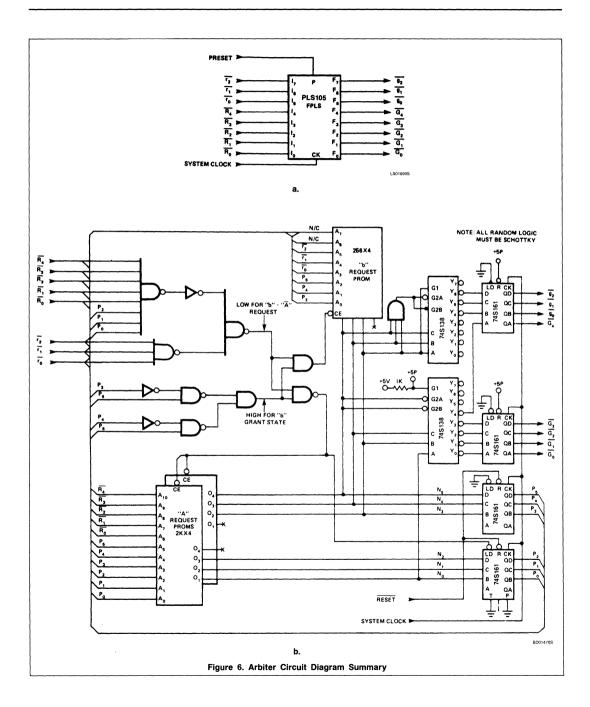

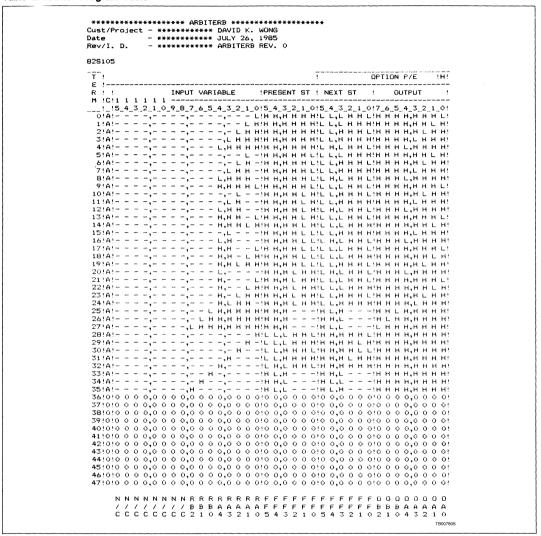

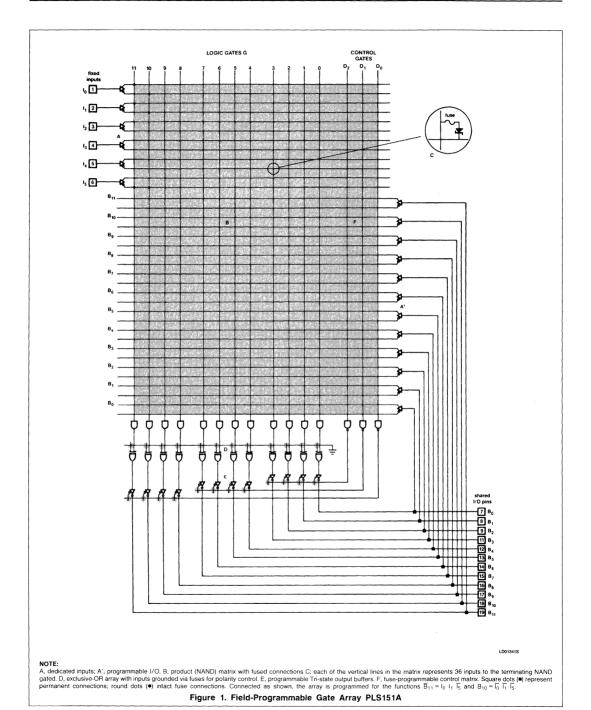

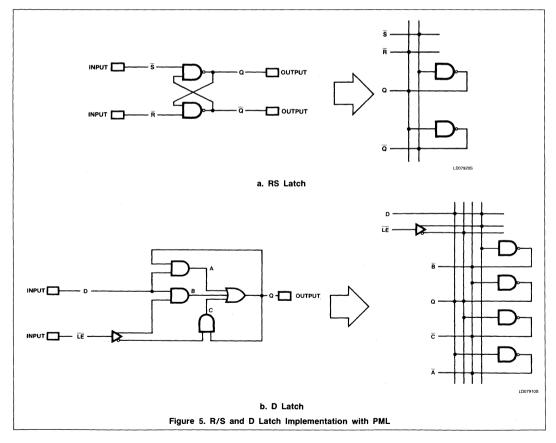

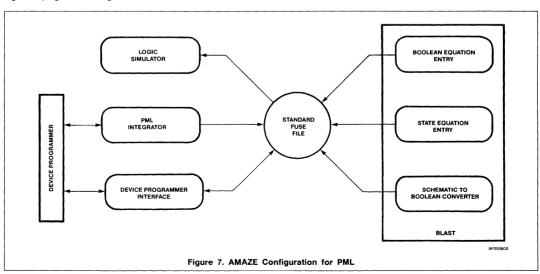

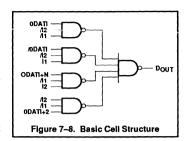

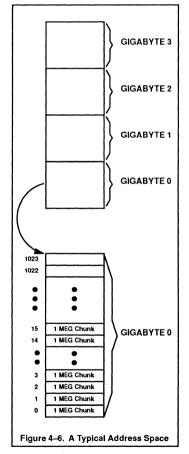

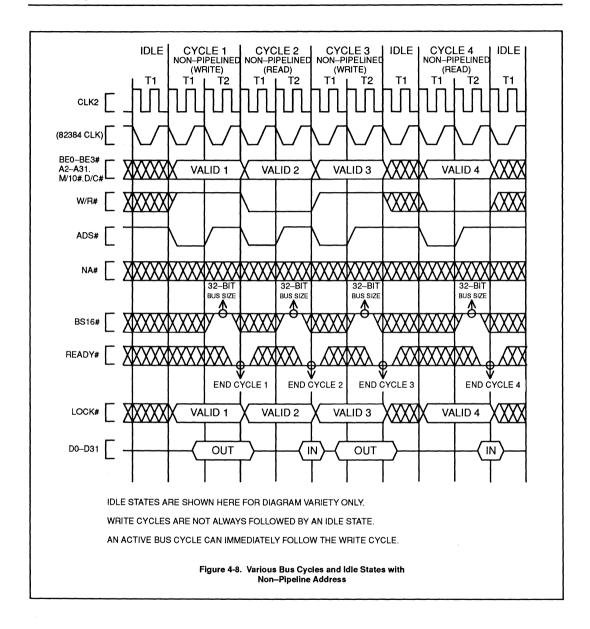

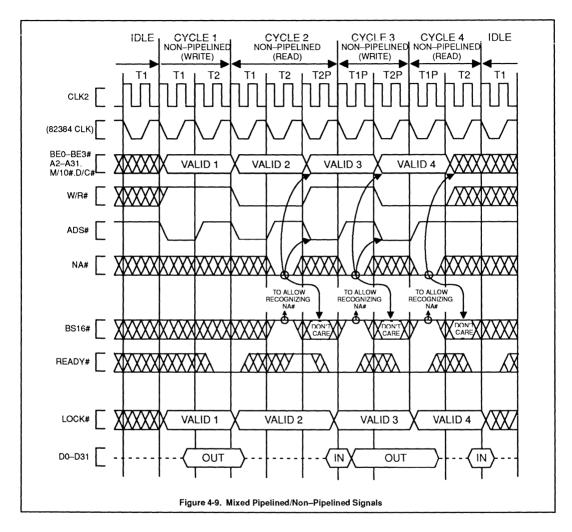

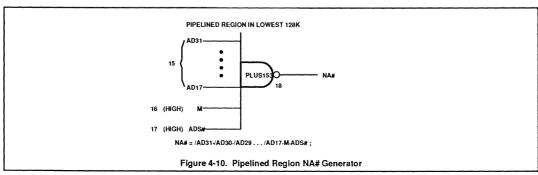

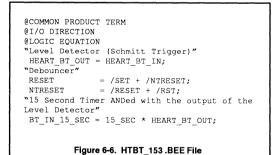

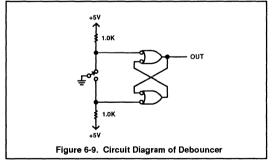

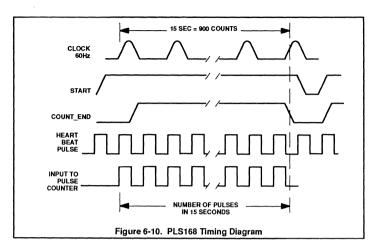

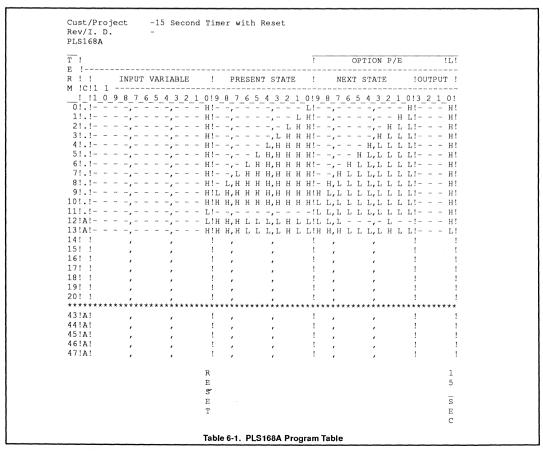

Signetics has put together winning processes for manufacturing Programmable Logic. Our standard is zero defects, and current customer quality statistics demonstrate our commitment to this goal.