# SIGNETICS LINEAR PHASE LOCKED LOOPS APPLICATIONS BOOK

#### TABLE OF CONTENTS

| SECTION | TITLE                             | PAGE |

|---------|-----------------------------------|------|

| 1       |                                   | 3    |

|         | Introduction                      | 5    |

|         | Phase Locked Loop Terminology     | 7    |

| 2       |                                   | 9    |

|         | The Phase Locked Loop Principle   | 11   |

|         | Phase Locked Loop Building Blocks | 15   |

|         | Functional Applications           | 18   |

| 3       |                                   | 21   |

|         | General Loop Setup and Tradeoffs  | 23   |

|         | PLL Measurement Techniques        | 26   |

|         | Monolithic Phase Locked Loops     | 30   |

|         | Expanding Loop Capability         | 42   |

| 4       |                                   | 49   |

|         | Specific Applications             | 51   |

1

#### COPYRIGHT 1972 SIGNETICS CORPORATION

Signetics Corporation reserves the right to make changes in the products contained in this book in order to improve design or performance and to supply the best possible product.

١.

Signetics Corporation assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

INTRODUCTION PHASE LOCKED LOOP TERMINOLOGY

.

·

. .

.

.

. .

#### INTRODUCTION

Phase Locked Loops (PLLs) are a new class of monolithic circuits developed by Signetics, but they are based on frequency feedback technology which dates back 40 years.

A phase locked loop is basically an electronic servo loop consisting of a phase detector, a low pass filter and a voltage controlled oscillator. Its controlled oscillator phase makes it capable of locking or synchronizing with an incoming signal. If the phase changes, indicating the incoming frequency is changing, the phase detector output voltage increases or decreases just enough to keep the oscillator frequency the same as the incoming frequency, preserving the locked condition. Thus, the average voltage applied to the controlled oscillator is a function of the frequency of the incoming signal. In fact, the low pass filter voltage is the demodulated output when the incoming signal is frequency modulated (provided the controlled oscillator has a linear voltage-to-frequency transfer characteristic). The synchronous reception of radio signals using PLL techniques was described (Ref. 1) in the early thirties. You may have heard of the "homodyne" receiver.

The first widespread use of phase lock, however, was in TV receivers to synchronize the horizontal and vertical sweep oscillators to the transmitted sync pulses. Lately, narrowband phase locked receivers have proved to be of considerable benefit in tracking weak satellite signals because of their superior noise immunity. Applications such as these were implemented primarily in discrete component form and involved considerable complexity even after the advent of transistors. This complexity made PLL techniques impractical or uneconomical in the majority of systems.

The development of complete, single-chip phase locked loops has changed this situation considerably. Now, a single packaged device with a few external components will offer the user all the benefits of phase locked loop operation, including independent center frequency and bandwidth adjustment, high noise immunity, high selectivity, high frequency operation and center frequency tuning by means of a single external component. Signetics makes three basic classes of single-chip PLL circuits: the general purpose PLL, the PLL with an added multiplier and the PLL tone decoder.

The 560B, 562B and 565 are general purpose phase locked loops containing an oscillator, phase detector and amplifier. When locked to an incoming signal, they provide two outputs: a voltage proportional to the frequency of the incoming signal (FM output) and the square wave oscillator output which, during lock, is equal to the incoming frequency. All general purpose devices are optimized to provide a linear frequency-to-voltage transfer characteristic.

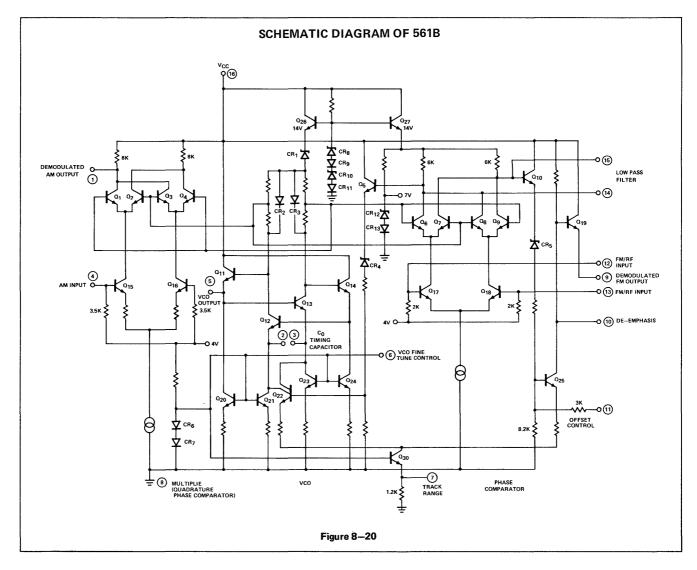

The 561B contains a complete PLL as those above, plus the additional multiplier or quadrature phase detector required for AM demodulation. In addition to the standard FM and oscillator outputs, it also provides an output voltage which is proportional to the amplitude of the incoming signal (AM output). The 561B is optimized for highly linear FM and AM demodulation.

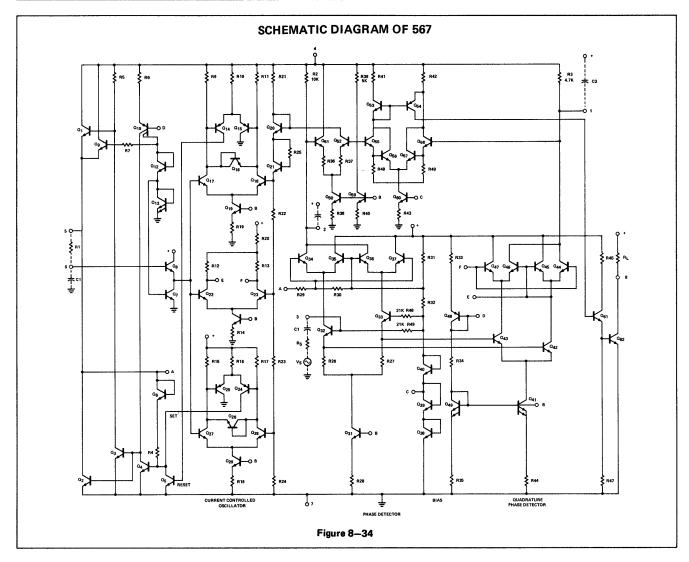

The 567 is a special purpose phase locked loop intended solely for use as a tone decoder. It contains a complete PLL including oscillator, phase detector and amplifier as well as a quadrature phase detector or multiplier. If the signal amplitude at the locked frequency is above a minimal value, the driver amplifier turns on, driving a load as much as 200mA. It, thus, gives an output whenever an in-band tone is present. The 567 is optimized for both center frequency and bandwidth stability.

The 566 is not a phase locked loop, but a precision voltagecontrollable waveform generator derived from the oscillator of the 565 general purpose loop. Because of its similarity to the 565 and because it lends itself well to use in, and in conjunction with, phase locked loops, it has been included in this section.

Table 8–1 summarizes the characteristics of Signetics phase locked loop products.

#### USER'S QUICK-LOOK GUIDE TO SIGNETICS PLLs

|       | Upper<br>Frequency<br>(MHz) | Maximum<br>Lock Range<br>(% f <sub>o</sub> ) | FM<br>Distortion | Output<br>Swing<br>±5%<br>Deviation<br>(volts p.p.) | Center<br>Frequency<br>Stability<br>(ppm/ <sup>o</sup> C) | Frequency<br>Drift with<br>Supply<br>Voltage<br>(%/volt) | Input<br>Resistance | AM<br>Output<br>Available | Typical<br>Supply<br>Current<br>(mA) | Supply<br>Voltage<br>Range<br>(volts) |

|-------|-----------------------------|----------------------------------------------|------------------|-----------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|---------------------|---------------------------|--------------------------------------|---------------------------------------|

| NE560 | 30                          | 40%                                          | .3%              | 1                                                   | ±600                                                      | .3                                                       | 2K**                | No                        | 9                                    | +15 to +26                            |

| NE561 | 30                          | 40%                                          | .3%              | 1                                                   | ±600                                                      | .3                                                       | 2K**                | Yes                       | 10                                   | +15 to +26                            |

| NE562 | 30                          | 40%                                          | .5%              | 1                                                   | ±600                                                      | .3                                                       | 2K**                | No                        | 12                                   | +15 to +30                            |

| NE565 | .5                          | 120%                                         | .2%              | .15                                                 | ±200                                                      | .16                                                      | 5K                  | No                        | 8                                    | ± 5 to ±12                            |

| SE565 | .5                          | 120%                                         | .2%              | .15                                                 | ±100                                                      | .08                                                      | 5K                  | No                        | 8                                    | ± 5 to ±12                            |

| NE567 | .5                          | 14%                                          | 5%*              | .20                                                 | 35±60                                                     | .7                                                       | 20K**               | Yes*                      | 7                                    | + 4.5 to +9                           |

| SE567 | .5                          | 14%                                          | 5%*              | .20                                                 | 35±60                                                     | .5                                                       | 20K**               | Yes*                      | 6                                    | + 4.5 to +9                           |

| NE566 | .5                          |                                              | .2%              | 30%/V***                                            | ±200                                                      | .16                                                      |                     |                           | 7                                    | +10 to +26                            |

| SE566 | .5                          |                                              | .2%              | 30%/V***                                            | ±100                                                      | .08                                                      |                     |                           | 7                                    | +10 to +26                            |

|       |                             |                                              |                  |                                                     |                                                           |                                                          |                     |                           |                                      |                                       |

\* The 567 AM and FM outputs are available, but are not optimized for linear demodulation.

.

\*\* Input biased internally.

\*\*\* Figure shown is VCO gain in percent deviation per volt.

A considerable quantity of detailed specifications and publications information for these products is included in the Linear Spec. Handbook. Because many readers are likely to be unfamiliar with the terminology and operating characteristics of phase locked loops, a glossary of terms and a general explanation of PLL principles are included here with a detailed discussion of the action of the individual loop elements.

The tradeoff and setup section will assist the reader in some of the considerations involved in selecting and applying the loop products to meet system requirements. A brief summary of measurement techniques has been presented to aid the user in achieving his performance goals.

Detailed descriptions have been provided for each of the loop products. The user can supplement the suggested connection diagrams with his own schemes.

Perhaps the best way to become familiar with the many uses of phase locked loops is to actually study the various application circuits provided. These circuits have been drawn from many sources – textbooks, users, Signetics' applications engineers and the 1970 Signetics–EDN Phase Locked Loop contest. Every effort has been made to provide usable, workable circuits which may be copied directly or used as jumping-off points for other imaginative applications.

The section on interfacing will aid the user in driving different forms of logic from PLL outputs and the section on expanding loop capabilities will show how to achieve improved performance in certain difficult applications.

#### PHASE LOCKED LOOP TERMINOLOGY

The following is a brief glossary of terms encountered in PLL literature.

CAPTURE RANGE (2  $\omega_{\rm C}$ ) – Although the loop will remain in lock throughout its lock range, it may not be able to acquire lock at the tracking range extremes. The range over which the loop *can* acquire lock is termed capture range. The capture range is sometimes called the LOCK-IN RANGE. (The latter refers to how close a signal must be to the center frequency before acquisition can occur. It is thus one-half the capture range or  $\omega_{\rm C}$ .)

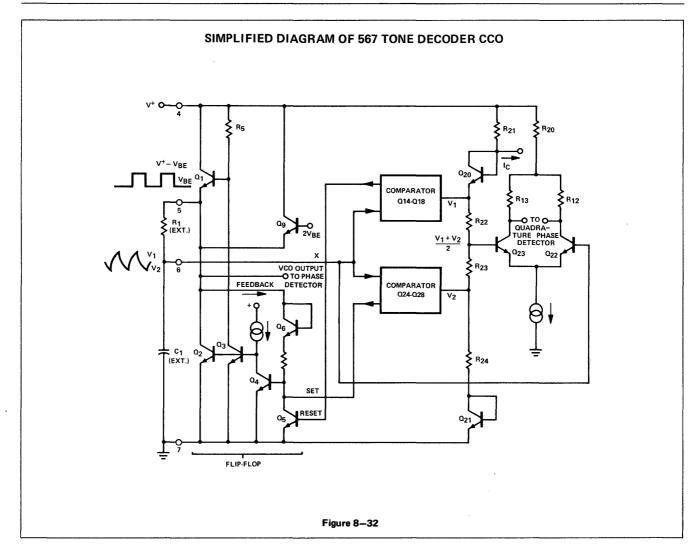

CURRENT CONTROLLED OSCILLATOR (CCO) - An oscillator similar to a VCO in which the frequency is determined by an applied current.

DAMPING FACTOR ( $\zeta$ ) – The standard damping constant of a second order feedback system. In the case of the PLL, it refers to the ability of the loop to respond quickly to an input frequency step without excessive overshoot. FREE-RUNNING FREQUENCY ( $f_0, \omega_0$ ) – Also called the CENTER FREQUENCY, this is the frequency at which the loop VCO operates when not locked to an input signal. The same symbols ( $f_0, \omega_0$ ) used for the free-running frequency are commonly used for the general oscillator frequency. It is usually clear which is meant from the context.

LOCK RANGE (2  $\omega_L$ ) – The range of input frequencies over which the loop will remain in lock. It is also called the TRACKING RANGE or HOLD-IN RANGE. (The latter refers to how far the loop frequency can be deviated from the center frequency and is one-half the lock range or  $\omega_L$ .)

LOOP GAIN ( $K_v$ ) – The product of the dc gains of all the loop elements, in units of (sec)<sup>-1</sup>.

LOOP NOISE BANDWIDTH ( $B_L$ ) – A loop property related to damping and natural frequency which describes the effective bandwidth of the received signal. Noise and signal components outside this band are greatly attenuated.

LOW PASS FILTER (LPF) - A low pass filter in the loop which permits only dc and low frequency voltages to travel around the loop. It controls the capture range and the noise and out-band signal rejection characteristics.

NATURAL FREQUENCY ( $\omega_n$ ) – The characteristic frequency of the loop, determined mathematically by the final pole positions in the complex plane. May be determined experimentally as the modulation frequency for which an underdamped loop gives the maximum output and at which phase error swing is the greatest.

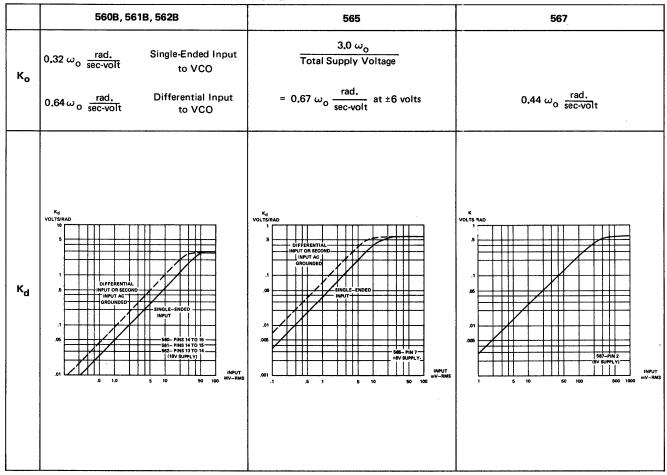

PHASE DETECTOR GAIN FACTOR ( $K_d$ ) – The conversion factor between the phase detector output voltage and the phase difference between input and VCO signals in volts/radian. At low input signal amplitudes, the gain is also a function of input level.

PHASE DETECTOR (PD) – A circuit which compares the input and VCO signals and produces an error voltage which is dependent upon their relative phase difference. This error signal corrects the VCO frequency during tracking. Also called PHASE COMPARATOR. A MULTIPLIER or MIXER is often used as a phase detector.

QUADRATURE PHASE DETECTOR (QPD) – A phase detector operated in quadrature (90<sup>o</sup> out of phase) with the loop phase detector. It is used primarily for AM demodulation and lock detection.

VCO CONVERSION GAIN ( $K_0$ ) – The conversion factor between VCO frequency and control voltage in radians/ second/volt.

VOLTAGE CONTROLLED OSCILLATOR (VCO) – An oscillator whose frequency is determined by an applied control voltage.

# SECTION 2

THE PHASE LOCKED LOOP PRINCIPLE PHASE LOCKED LOOP BUILDING BLOCKS FUNCTIONAL APPLICATIONS

, "

· .

.

#### THE PHASE LOCKED LOOP PRINCIPLE

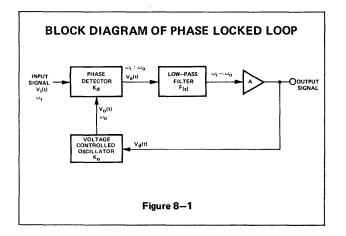

The phase locked loop is a feedback system comprised of a phase comparator, a low pass filter and an error amplifier in the forward signal path and a voltage-controlled oscillator (VCO) in the feedback path. The block diagram of a basic PLL system is shown in Figure 8–1. Detailed analysis of the PLL as a feedback control system has been discussed in the literature (Ref. 2). Perhaps the single most important point to realize when designing with the PLL is that it is a feedback system and, hence, is characterized mathematically by the same equations that apply to other, more conventional feedback systems. The parameters in the equations are somewhat different, however, since the feedback error signal in the phase locked system is a phase rather than a current or voltage signal, as is usually the case in conventional feedback systems.

#### LOOP OPERATION

A rigorous mathematical analysis of the system is quite cumbersome and will not be repeated here. However, from a qualitative point of view, the basic principle of PLL operation can be briefly explained as follows: With no signal input applied to the system, the error voltage V<sub>d</sub> is equal to zero. The VCO operates at a set frequency  $\omega_0$ , which is known as the free-running frequency. If an input signal is applied to the system, the phase comparator compares the phase and the frequency of the input with the VCO frequency and generates an error voltage  $V_{\rho}(t)$ that is related to the phase and the frequency difference between the two signals. This error voltage is then filtered, amplified and applied to the control terminal of the VCO. In this manner, the control voltage  $V_d(t)$  forces the VCO frequency to vary in a direction that reduces the frequency difference between fo and the input signal. If the input frequency  $\omega_i$  is sufficiently close to  $\omega_0$ , the feedback nature of the PLL causes the VCO to synchronize or lock with the incoming signal. Once in lock, the VCO frequency is identical to the input signal except for a finite phase difference. This net phase difference  $\theta_{0}$  is necessary to generate the corrective error voltage V<sub>d</sub> to shift the VCO frequency from its free-running value to the input signal

frequency  $\omega_{\rm i}$  and, thus, keep the PLL in lock. This self-correcting ability of the system also allows the PLL to track the frequency changes of the input signal once it is locked. The range of frequencies over which the PLL can maintain lock with an input signal is defined as the "lock range" of the system. The band of frequencies over which the PLL can acquire lock with an incoming signal is known as the "capture range" of the system and is never greater than the lock range.

Another means of describing the operation of the PLL is to observe that the phase comparator is in actuality a multiplier circuit that mixes the input signal with the VCO signal. This mix produces the sum and difference frequencies  $\omega_i \pm \omega_0$  shown in Figure 8–1. When the loop is in lock, the VCO duplicates the input frequency so that the difference frequency component  $(\omega_i - \omega_0)$  is zero; hence, the output of the phase comparator contains a dc component. The low pass filter removes the sum frequency component  $(\omega_i + \omega_0)$  but passes the dc component which is then amplified and fed back to the VCO. Notice that when the loop is in lock, the difference frequency component is always dc, so the lock range is independent of the band edge of the low pass filter.

#### LOCK AND CAPTURE

Consider now the case where the loop is not yet in lock. The phase comparator again mixes the input and VCO signals to produce sum and difference frequency components. Now, however, the difference component may fall outside the band edge of the low pass filter and be removed along with the sum frequency component. If this is the case, no information is transmitted around the loop and the VCO remains at its initial free-running frequency. As the input frequency approaches that of the VCO, the frequency of the difference component decreases and approaches the band edge of the low pass filter. Now some of the difference component is passed, which tends to drive the VCO towards the frequency of the input signal. This, in turn, decreases the frequency of the difference component and allows more information to be transmitted through the low pass filter to the VCO. This is essentially a positive feedback mechanism which causes the VCO to snap into lock with the input signal. With this mechanism in mind, the term "capture range" can again be defined as the frequency range centered about the VCO initial freerunning frequency over which the loop can acquire lock with the input signal. The capture range is a measure of how close the input signal must be in frequency to that of the VCO to acquire lock. The "capture range" can assume any value within the lock range and depends primarily upon the band edge of the low pass filter together with the closed loop gain of the system. It is this signal capturing phenomenon which gives the loop its frequency selective properties.

#### PHASE LOCKED LOOP APPLICATIONS

It is important to distinguish the "capture range" from the "lock range" which can, again, be defined as *the frequency* range usually centered about the VCO initial free-running frequency over which the loop can track the input signal once lock has been achieved.

When the loop is in lock, the difference frequency component on the output of the phase comparator (error voltage) is dc and will always be passed by the low pass filter. Thus, the lock range is limited by the range of error voltage that can be generated and the corresponding VCO frequency deviation produced. The lock range is essentially a dc parameter and is not affected by the band edge of the low pass filter.

#### THE CAPTURE TRANSIENT

The capture process is highly complex and does not lend itself to simple mathematical analysis. However, a qualitative description of the capture mechanism may be given as follows: Since frequency is the time derivative of phase, the frequency and the phase errors in the loop can be related as

$$\Delta \omega = \frac{\mathrm{d}\theta_{\mathrm{o}}}{\mathrm{d}_{\mathrm{t}}}$$

where  $\Delta \omega$  is the instantaneous frequency separation between the signal and VCO frequencies and  $\theta_0$  is the phase difference between the input signal and VCO signals.

If the feedback loop of the PLL was opened, say between the low pass filter and the VCO control input, then for a given condition of  $\omega_0$  and  $\omega_i$  the phase comparator output would be a sinusoidal beat note at a fixed frequency  $\Delta\omega$ . If  $\omega_i$  and  $\omega_0$  were sufficiently close in frequency, this beat note would appear at the filter output with negligible attenuation. Now suppose that the feedback loop is closed by connecting the low pass filter output to the VCO control terminal. The VCO frequency will be modulated by the beat note. When this happens,  $\Delta\omega$  itself will become a function of time. If during this modulation process, the VCO frequency moves closer to  $\omega_i$  (i.e., decreasing  $\Delta\omega$ ), then  $\frac{d\theta_0}{d_t}$  decreases and the output of the phase comparator becomes a slowly varying function of

time. Similarly, if the VCO is modulated away from  $\omega_i$ ,  $\frac{d\theta_0}{dt}$  increases and the error voltage becomes a rapidly

dt

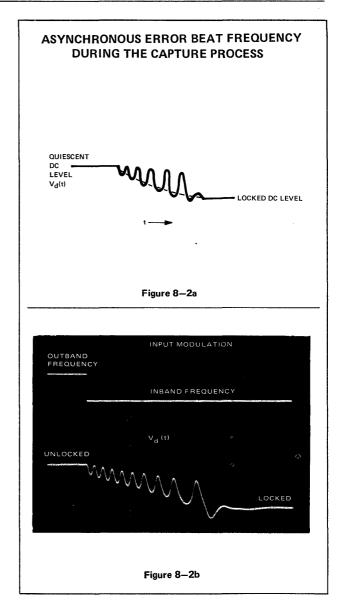

varying function of time. Under this condition the beat note waveform no longer looks sinusoidal; it looks like a series of aperiodic cusps, depicted schematically in Figure 8–2a. Because of its asymmetry, the beat note waveform contains a finite dc component that pushes the average value of the VCO toward  $\omega_i$ , thus decreasing  $\Delta \omega$ . In this manner, the beat note frequency rapidly decreases toward zero, the VCO frequency drifts toward  $\omega_i$  and the lock is established. When the system is in lock,  $\Delta \omega$  is equal to zero and only a steady-state dc error voltage remains.

Figure 8–2b displays an oscillogram of the loop error voltage V<sub>d</sub> in an actual PLL system during the capture process. Note that as lock is approached,  $\Delta \omega$  is reduced, the low pass filter attenuation becomes less and the amplitude of the beat note increases.

The total time taken by the PLL to establish lock is called the pull-in time. Pull-in time depends on the initial frequency and phase differences between the two signals as well as on the overall loop gain and the low pass filter bandwidth. Under certain conditions, the pull-in time may be shorter than the period of the beat note and the loop can lock without an oscillatory error transient.

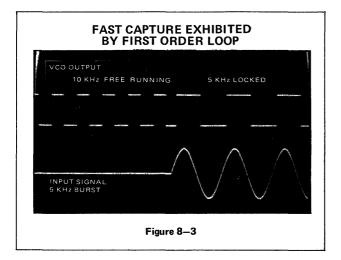

A specific case to illustrate this is shown in Figure 8–3. The 565 PLL is shown acquiring lock within the first cycle of the input signal. The PLL was able to capture in this short time because it was operated as a first order loop (no low pass filter) and the input tone-burst frequency was within its lock and capture range.

#### EFFECT OF THE LOW PASS FILTER

In the operation of the loop, the low pass filter serves a dual function: First, by attenuating the high frequency error components at the output of the phase comparator, it enhances the interference-rejection characteristics; second, it provides a short-term memory for the PLL and ensures a rapid recapture of the signal if the system is thrown out of lock due to a noise transient. The low pass filter bandwidth has the following effects on system performance:

- a.) The capture process becomes slower, and the pull-in time increases.

- b.) The capture range decreases.

- c.) Interference-rejection properties of the PLL improve since the error voltage caused by an interfering frequency is attenuated further by the low pass filter.

- d.) The transient response of the loop (the response of the PLL to sudden changes of the input frequency within the capture range) becomes underdamped.

The last effect also produces a practical limitation on the low pass loop filter bandwidth and roll-off characteristics from a stability standpoint. These points will be explained further in the following analysis.

#### LINEAR ANALYSIS FOR LOCK CONDITION – FREQUENCY TRACKING

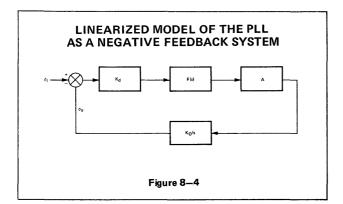

When the PLL is in lock, the non-linear capture transients are no longer present. Therefore, under lock condition, the PLL can often be approximated as a linear control system (see Figure 8–4) and can be analyzed using Laplace transform techniques. In this case, it is convenient to use the net phase error in the loop ( $\theta_s - \theta_o$ ) as the system variable. Each of the gain terms associated with the blocks can be defined as follows:

$K_d$  = conversion gain of phase detector (volt/rad)

- F(s) = transfer characteristic of low pass filter

- A = amplifier voltage gain

- $K_{\theta}$  = VCO conversion gain (rad/volt-sec)

Note that, since the VCO converts a voltage to a frequency and since phase is the integral of frequency, the VCO functions as an integrator in the feedback loop.

The open loop transfer function for the PLL can be written as

$$T(s) = \frac{K_V F(s)}{s}$$

where  $K_v$  is the total loop gain, i.e.,  $K_v = K_0 K_d A$ . Using linear feedback analysis techniques, the closed loop transfer characteristics H(s) can be related to the open loop performance as

$$H(s) = \frac{T(s)}{1 + T(s)}$$

and the roots of the characteristic system polynominal can be readily determined by root-locus techniques.

From these equations, it is apparent that the transient performance and frequency response of the loop is heavily dependent upon the choice of filter and its corresponding transfer characteristic, F(s).

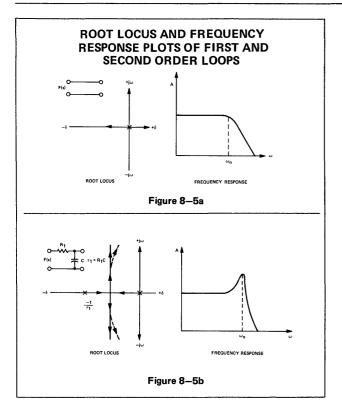

The simplest case is that of the first order loop where F(s) = 1 (no filter). The closed loop transfer function then becomes

$$T(s) = \frac{K_v}{s + K_v}$$

This transfer function gives the root locus as a function of the total loop gain  $K_v$  and the corresponding frequency response shown in Figure 8–5a. The open loop pole at the origin is due to the integrating action of the VCO. Note that the frequency response is actually the amplitude of the difference frequency component versus modulating frequency when the PLL is used to track a frequency modulated input signal. Since there is no low pass filter in this case, sum frequency components are also present on the phase detector output and must be filtered outside of the loop if the difference frequency component (demodulated FM) is to be measured.

With the addition of a single pole low pass filter  $\mathsf{F}(\mathsf{s})$  of the form

$$=(s) = \frac{1}{1+\tau_1 s}$$

where  $\tau_1 = R_1C$ , the PLL becomes a second order system with the root locus shown in Figure 8–5b. Here, we again have an open loop pole at the origin because of the integrating action of the VCO and another open loop pole at a position equal to  $\frac{-1}{\tau_1}$  where  $\tau_1$  is the time constant of the low pass filter.

One can make the following observations from the root locus characteristics of Figure 8-5b.

- a.) As the loop gain K  $_{\rm V}$  increases for a given choice of  $\tau_1$ , the imaginary part of the closed loop poles increase; thus, the natural frequency of the loop increases and the loop becomes more and more underdamped.

- b.) If the filter time constant is increased, the real part of the closed loop poles becomes smaller and the loop damping is reduced.

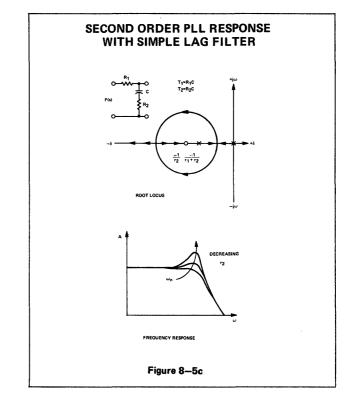

As in any practical feedback system, excess shifts or non-dominant poles associated with the blocks within the PLL can cause the root loci to bend toward the right half plane as shown by the dashed line in Figure 8–5b. This is likely to happen if either the loop gain or the filter time constant is too large and may cause the loop to break into sustained oscillations. The stability problem can be eliminated by using a lag-lead type of filter, as indicated in Figure 8–5c. This type of a filter has the transfer function

F(s) =

$$\frac{1 + \tau_2 s}{1 + (\tau_1 + \tau_2) s}$$

where  $\tau_2 = R_2C$  and  $\tau_1 = R_1C$ . By proper choice of  $R_2$ , this type of filter confines the root locus to the left half plane and ensures stability. The lag-lead filter gives a frequency response dependent on the damping, which can now be controlled by the proper adjustment of  $\tau_1$  and  $\tau_2$ . In practice, this type of filter is important because it allows the loop to be used with a response between that of the first and second order loops and it provides an additional control over the loop transient response. If  $R_2 = 0$ , the loop behaves as a second order loop and if  $R_2 = \infty$ , the loop behaves as a first order loop due to a pole-zero cancellation. Note, however, that as first order operation is approached, the noise bandwidth increases and interference rejection decreases since the high frequency error components in the loop are now attenuated to a lesser degree.

In terms of the basic gain expressions in the system, the lock range of the PLL  $\omega_{\rm L}$  can be shown to be numerically equal to the dc loop gain

$$2\omega_{\rm L} = 4\pi f_{\rm L} = 2K_{\rm V}$$

Since the capture range  $\omega_{L}$  denotes a transient condition, it is not as readily derived as the lock range. However, an approximate expression for the capture range can be written as

$$2\omega_{c} = 4\pi f_{c} \simeq 2K_{v} F(j\omega_{c})$$

where  $F(j\omega_c)$  is the low pass filter amplitude response at  $\omega = \omega_L$ . Note that at all times the capture range is smaller than the lock range. If the simple lag filter of Figure 8–5b is used, the capture range equation can be approximated as

$$2\omega_{\rm c} \simeq 2 \sqrt{\frac{\omega_{\rm L}}{\tau_{\rm 1}}} = 2 \sqrt{\frac{\kappa_{\rm v}}{\tau_{\rm 1}}}$$

Thus, the capture range decreases as the low pass filter time constant is decreased, whereas the lock range is unaffected by the filter and is determined solely by the loop gain.

Figure 8-6 shows the typical frequency-to-voltage transfer characteristics of the PLL. The input is assumed to be a sine wave whose frequency is swept slowly over a broad frequency range. The vertical scale is the corresponding loop error voltage. In Figure 8-6a, the input frequency is being gradually increased. The loop does not respond to the signal until it reaches a frequency  $\omega_1$ , corresponding to the lower edge of the capture range. Then, the loop suddenly locks on the input and causes a negative jump of the loop error voltage. Next,  $V_d$  varies with frequency with a slope equal to the reciprocal of VCO gain  $(1/K_0)$  and goes through zero as  $\omega_i = \omega_0$ . The loop tracks the input until the input frequency reaches  $\omega_2$ , corresponding to the upper edge of the lock range. The PLL then loses lock and the error voltage drops to zero. If the input frequency is swept slowly back now, the cycle repeats itself, but it is inverted, as shown in Figure 8-6b. The loop recaptures the signal at  $\omega_3$  and tracks it down to  $\omega_4$ . The total capture and lock ranges of the system are:

$$2\omega_c = \omega_3 - \omega_1$$

and  $2\omega_L = \omega_2 - \omega_4$

Note that, as indicated by the transfer characteristics of Figure 8–6, the PLL system has an inherent selectivity about the center frequency set by the VCO free-running frequency  $\omega_0$ ; it will respond only to the input signal frequencies that are separated from  $\omega_0$  by less than  $\omega_c$  or  $\omega_L$ , depending on whether the loop starts with or without an initial lock condition. The linearity of the frequency-to-voltage conversion characteristics for the PLL is determined solely by the VCO conversion gain. Therefore, in most PLL applications, the VCO is required to have a highly linear voltage-to-frequency transfer characteristic.

#### PHASE LOCKED LOOP BUILDING BLOCKS

#### **VOLTAGE CONTROLLED OSCILLATOR**

Since three different forms of VCO have been used in the Signetics PLL series, the VCO details will not be discussed until the individual loops are described. However, a few general comments about VCOs are in order.

When the PLL is locked to a signal, the VCO voltage is a function of the frequency of the input signal. Since the VCO control voltage is the demodulated output during FM demodulation, it is important that the VCO voltage-to-frequency characteristic be linear so that the output is not distorted. Over the linear range of the VCO, the conversion gain is given by  $K_{\rm O}$  (in radian/volt-sec).

$$K_0 = \frac{\Delta \omega_0}{\Delta V_0}$$

Since the loop output voltage is the VCO voltage, we can get the loop output voltage as

$$\Delta V_{o} = \frac{\Delta \omega_{o}}{K_{o}}$$

The gain  $K_0$  can be found from the data sheet by taking the change in VCO control voltage for a given percentage frequency deviation and multiplying by the center frequency. When the VCO voltage is changed, the frequency change is virtually instantaneous.

#### PHASE DETECTOR

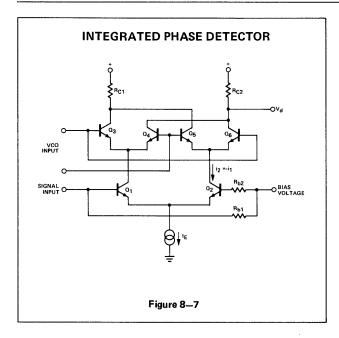

All Signetics phase locked loops use the same form of phase detector-often called the doubly-balanced multiplier or mixer. Such a circuit is shown in Figure 8-7.

#### PHASE LOCKED LOOP APPLICATIONS

The input stage formed by transistors  $Q_1$  and  $Q_2$  may be viewed as a differential amplifier which has a collector resistance  $R_C$  and whose differential gain at balance is the ratio of  $R_C$  to the emitter resistance  $r_e$  of  $Q_1$  and  $Q_2$ .

$$A_{d} = \frac{R_{C}}{r_{e}} = \frac{\frac{R_{C}}{0.026}}{\frac{1}{I_{e}/2}} = \frac{R_{C}}{0.013 I_{e}}$$

The switching stage formed by  $\Omega_3 - \Omega_6$  is switched on and off by the VCO square wave. Since the collector current swing of  $\Omega_2$  is the negative of the collector current swing of  $\Omega_1$ , the switching action has the effect of multiplying the differential stage output first by +1 and then by -1. That is, when the base of  $\Omega_4$  is positive,  $R_{C2}$  receives  $I_1$  and when the base of  $\Omega_6$  is positive,  $R_{C2}$  receives  $I_2 = -I_1$ . Since we have called this a multiplier, let us perform the multiplication to gain further insight into the action of the phase detector.

Suppose we have an input signal which consists of two added components: a component at frequency  $\omega_i$  which is close to the free-running frequency and a component at frequency  $\omega_k$  which may be at any frequency. The input signal is

$$V_i + V_k = V_i \sin(\omega_i t + \theta_i) + V_k \sin(\omega_k t + \theta_k)$$

where  $\theta_i$  and  $\theta_k$  are the phase in relation to the VCO signal. The unity square wave developed in the multiplier by the VCO signal is

$$\frac{4}{\pi(2n+1)}$$

sin [(2n + 1)  $\omega_0$ t]

where  $\omega_0$  is the VCO frequency. Multiplying the two terms, using the appropriate trigonometric relationship and inserting the differential stage gain  $A_d$ , we get

$$\frac{2A_{d}}{\pi} \left[ \sum_{n=0}^{\infty} \frac{V_{i}}{(2n+1)} \cos \left[ (2n+1) \omega_{0} t - \omega_{i} t - \theta_{i} \right] \right]$$

$$-\sum_{n=0}^{\infty} \frac{V_i}{(2n+1)} \cos \left[ (2n+1) \omega_0 t + \omega_i t + \theta_j \right]$$

+

$$\sum_{n=0}^{\infty} \frac{V_k}{(2n+1)} \cos \left[ (2n+1)\omega_0 t - \omega_k t - \theta_k \right]$$

$$-\sum_{n=0}^{\infty} \frac{V_k}{(2n+1)} \cos \left[ (2n+1)\omega_0 t + \omega_k t + \theta_k \right]$$

Assuming the V<sub>k</sub> is zero, temporarily, if  $\omega_i$  is close to  $\omega_o$ , the first term (n = 0) has a low frequency difference frequency component. This is the beat frequency component that feeds around the loop and causes lock up by modulating the VCO. As  $\omega_o$  is driven closer to  $\omega_i$ , this difference component becomes lower and lower in frequency until  $\omega_o = \omega_i$  and lock is achieved. The first term then becomes

$$\frac{2A_{d}V_{i}}{\pi}\cos\theta_{i}$$

which is the usual phase detector formula showing the dc component of the phase detector during lock. This component must equal the voltage necessary to keep the VCO at  $\omega_0$ . It is possible for  $\omega_0$  to equal  $\omega_i$  momentarily during the lock up process and, yet, for the phase to be incorrect so that  $\omega_0$  passes through  $\omega_i$  without lock being achieved. This explains why lock is usually not achieved instantaneously, even when  $\omega_i = \omega_0$  at t = 0.

If  $n \neq 0$  in the first term, the loop can lock when  $\omega_i = (2n + 1) \omega_0$ , giving the dc phase detector component

$$\frac{2A_dV_i}{\pi(2n+1)} \quad \cos \theta_i$$

showing that the loop can lock to odd harmonics of the center frequency. The (2n + 1) term in the denominator shows that the phase detector output is lower for harmonic lock, which explains why the lock range decreases as higher and higher odd harmonics are used to achieve lock.

Note also that the phase detector output during lock is (assuming  $A_d$  is constant) also a function of the input amplitude  $V_i$ . Thus, for a given dc phase detector output  $V_d$ , an input amplitude decrease must be accompanied by a phase change. Since the loop can remain locked only for  $\theta_i$  between 0 and 180°, the lower  $V_i$  becomes, the more reduced is the lock range.

Going to the second term, we note that during lock the lowest possible frequency is  $\omega_0 + \omega_i = 2\omega_i$ . A sum frequency component is always present at the phase detector output. This component is usually greatly attenuated by the low pass filter capacitor connected to the phase detector output. However, when rapid tracking is required (as with high-speed FM detection or FSK-frequency shift keying), the requirement for a relatively high frequency cutoff in the low pass filter may leave this component unattenuated to the extent that it interferes with detection. At the very least, additional filtering may be required to remove this component. Components caused by  $n \neq 0$  in the second term are both attenuated and of much higher frequency, so they may be neglected.

Suppose that we have other frequencies represented by  $V_k$  present. What is their effect for  $V_k \neq 0$ ?

The third term shows that  $V_k$  introduces another difference frequency component. Obviously, if  $\omega_{\mathbf{k}}$  is close to  $\omega_{\mathbf{i}}$ , it can interfere with the locking process since it may form a beat frequency of the same magnitude as the desired locking beat frequency. Suppose lock has been achieved, however, so that  $\omega_0 = \omega_i$ . In order for lock to be maintained, the average phase detector output must be constant. If  $\omega_0 = \omega_k$  is relatively low in frequency, the phase  $\theta_i$  must change to compensate for this beat frequency. Broadly speaking, any signal in addition to the signal to which the loop is locked causes a phase variation. Usually this is negligible since  $\omega_{\mathbf{k}}$  is often far removed from  $\omega_i$ . However, it has been stated that the phase  $\theta_i$  can move only between 0 and 180°. Suppose the phase limit has been reached and  $V_k$  appears. Since it cannot be compensated for, it will drive the loop out of lock. This explains why extraneous signals can result in a decrease in the lock range. If  $V_{\boldsymbol{k}}$  is assumed to be an instantaneous noise component, the same effect occurs. When the full

swing of the loop is being utilized, noise will decrease the lock or tracking range. We can reduce this effect by decreasing the cutoff frequency of the low pass filter so that the  $\omega_0 - \omega_k$  is attenuated to a greater extent, which illustrates that noise immunity and out-band frequency rejection is improved (at the expense of capture range since  $\omega_0 - \omega_i$  is likewise attenuated) when the low pass filter capacitor is large.

The third term can have a dc component when  $\omega_k$  is an odd harmonic of the locked frequency so that (2n + 1)( $\omega_0 - \omega_i$ ) is zero and  $\theta_k$  makes its appearance. This will have an effect on  $\theta_i$  which will change the  $\theta_i$  versus frequency  $\omega_i$ . This is most noticeable when the waveform of the incoming signal is, for example, a square wave. The  $\theta_k$  term will combine with the  $\theta_i$  term so that the phase is a linear function of input frequency. Other waveforms will give different phase versus frequency functions. When the input amplitude  $V_i$  is large and the loop gain is large, the phase will be close to  $90^{\circ}$  throughout the range of VCO swing, so this effect is often unnoticed.

The fourth term is of little consequence except that if  $\omega_k$  approaches zero, the phase detector output will have a component at the locked frequency  $\omega_0$  at the output. For example, a dc offset at the input differential stage will appear as a square wave of fundamental  $\omega_0$  at the phase detector output. This is usually small and well attenuated by the low pass filter. Since many out-band signals or noise components may be present, many  $V_k$  terms may be combining to influence locking and phase during lock. Fortunately, we need only worry about those close to the locked frequency.

The quadrature phase detector action is exactly the same except that its output is proportional to the sine of the phase angle. When the phase  $\theta_i$  is 90°, the quadrature phase detector output is then at its maximum, which explains why it makes a useful lock or amplitude detector. The output of the quadrature phase detector is given by:

$$V_q = \frac{2A_qV_i}{\pi} \quad \sin\theta_i$$

where  $V_i$  is the constant or modulated AM signal and  $\theta_i \approx 90^0$  in most cases so that sine  $\theta_i = 1$  and

$$V_{q} = \frac{2A_{q}V_{i}}{\pi}$$

This is the demodulation principle of the autodyne receiver and the basis for the 567 tone decoder operation.

#### FUNCTIONAL APPLICATIONS

#### LOW PASS FILTER

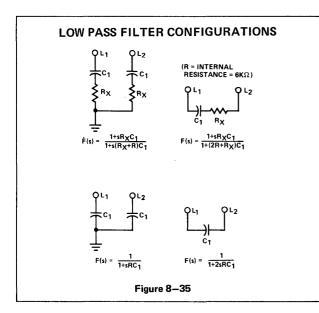

The simplest type of low pass filter for the second order loop is a single pole RC type shown in Figure 8–5b. In all Signetics' loops, the resistor is internal and the capacitor is external. The inside resistor greatly improves the center frequency stability of the loop with temperature variations. Fortunately, the capture range and loop damping are related to the square root of this internal resistor value, so variations in its absolute value have little effect on loop performance. The nominal value of the internal resistor for each loop is given in the circuit diagrams of the detailed circuit descriptions in this chapter. The typical tolerance on these integrated resistors is  $\pm 20\%$ .

As a functional building block, the phase locked loop is suitable for a wide variety of frequency related applications. These applications generally fall into one or more of the following categories:

- a.) FM Demodulation

- b.) Frequency Synthesizing

- c.) Frequency Synchronization

- d.) Signal Conditioning

- e.) AM Demodulation

#### **FM DEMODULATION**

If the PLL is locked to a frequency modulated (FM) signal, the VCO tracks the instantaneous frequency of the input signal. The filtered error voltage, which forces the VCO to maintain lock with the input signal then becomes the demodulated FM output. The linearity of this demodulated signal depends solely on the linearity of the VCO controlvoltage-to-frequency transfer characteristic.

It should be noted that since the PLL is in lock during the FM demodulation process, the response is linear and can be readily predicted from a root locus plot.

FM demodulation applications are numerous; however, some of the more popular are:

#### **Broadcast FM Detection**

Here, the PLL can be used as a complete IF strip, limiter and FM detector which may be used for detecting either wide or narrow band FM signals with greater linearity than can be obtained by other means. For frequencies within the range of the VCO, the PLL functions as a self contained receiver since it combines the functions of frequency selectivity and demodulation. One increasingly popular use of the PLL is in scanning-receivers where a number of broadcast channels may be sequentially monitored by simply varying the VCO free-running frequency.

#### FM Telemetry

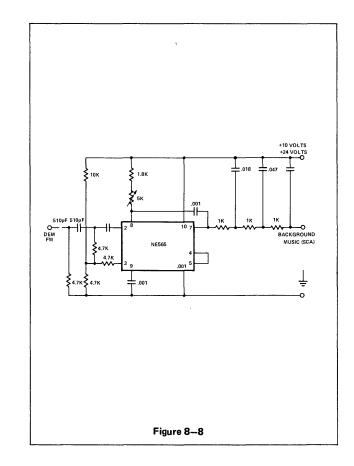

This application involves demodulation of a frequency modulated subcarrier of the main channel. A popular example here is the use of the PLL to recover the SCA (storecast music) signal from the combined signal of many commercial FM broadcast stations. The SCA signal is a 67kHz frequency modulated subcarrier which puts it above the frequency spectrum of the normal stereo or monaural FM program material. By connecting the circuit of Figure 8–8 to a point between the FM discrimator and the de-emphasis filter of a commercial band (home) FM receiver and tuning the receiver to a station which broadcasts an SCA signal, one can obtain hours of commercial free background music.

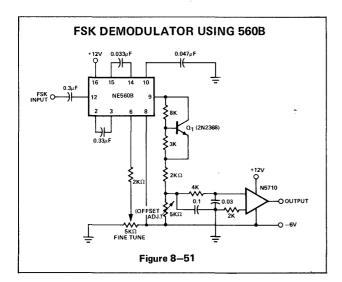

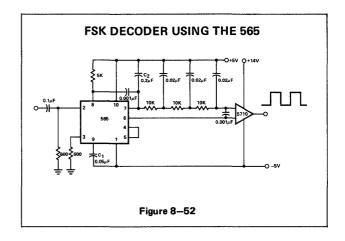

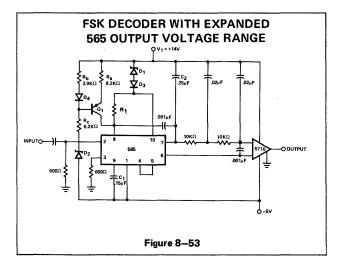

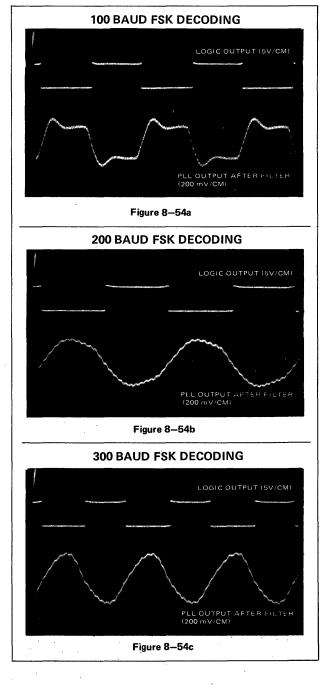

#### Frequency Shift Keying (FSK)

This refers to what is essentially digital frequency modulation. FSK is a means for transmitting digital information by a carrier which is shifted between two discrete frequencies. In this case, the two discrete frequencies correspond to a digital "1" and a digital "0," respectively. When the PLL is locked to a FSK signal, the demodulated output (error voltage) shifts between two discrete voltage levels, corresponding to the demodulated binary output. FSK techniques are often used in modems (modulator-demodulators), intended for transmitting data over telephone lines.

#### **FREQUENCY SYNTHESIS**

Frequency Multiplication can be achieved with the PLL in two ways:

- a.) Locking to a harmonic of the input signal

- b.) Insertion of a counter (digital frequency divider) in the loop

Harmonic locking is the simplest and can usually be achieved by setting the VCO free-running frequency to a multiple of the input frequency and allowing the PLL to lock. A limitation on this scheme, however, is that the lock range decreases as successively higher and weaker harmonics are used for locking. This limits the practical harmonic locking range to multiples of approximately less than ten. For larger multiples, the second scheme is more desirable.

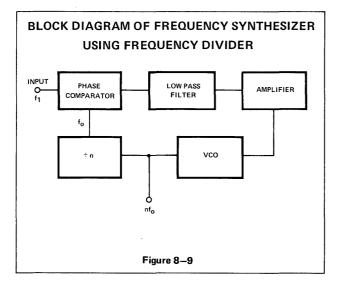

A block diagram of the second scheme is shown in Figure 8–9. Here, the loop is broken between the VCO and the phase comparator and a counter is inserted. In this case, the fundamental of the *divided* VCO frequency is locked to the input frequency so that the VCO is actually running at a multiple of the input frequency. The amount of multiplication is determined by the counter. An obvious practical application of this multiplication property, is the use of the PLL in wide range frequency synthesizers.

In frequency multiplication applications it is important to take into account that the phase comparator is actually a mixer and that its output contains sum and difference frequency components. The difference frequency component is dc and is the error voltage which drives the VCO to keep the PLL in lock. The sum frequency components (of which the fundamental is twice the frequency of the input signal) if not well filtered, will induce incidental FM on the VCO output. This occurs because the VCO is running at many times the frequency of the input signal and the sum frequency component which appears on the control voltage to the VCO causes a periodic variation of its frequency about the desired multiple. For frequency multiplication it is generally necessary to filter quite heavily to remove this sum frequency component. The tradeoff, of course, is a reduced capture range and a more underdamped loop transient response.

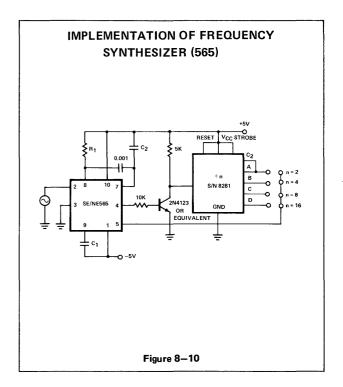

For the case of frequency fractionalization, both harmonic locking and frequency countdown could be used to generate, for instance, a frequency exactly 16/3 the input. In this case, the circuit of Figure 8–10 could be used with the initial VCO frequency set to approximately 16/3 the expected input frequency. The counter then divides the VCO frequency by 16, and the input is locked to the 3rd harmonic of the counter output. Now the output can be taken as the VCO output and it will be exactly 16/3 of the input frequency as long as the loop is in lock.

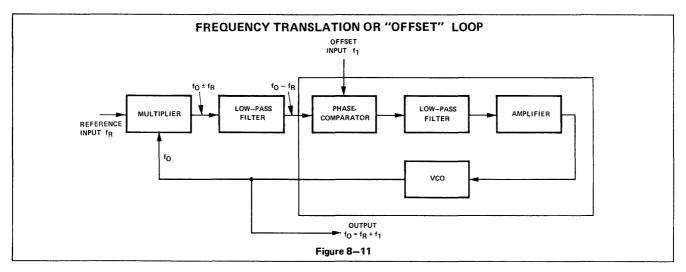

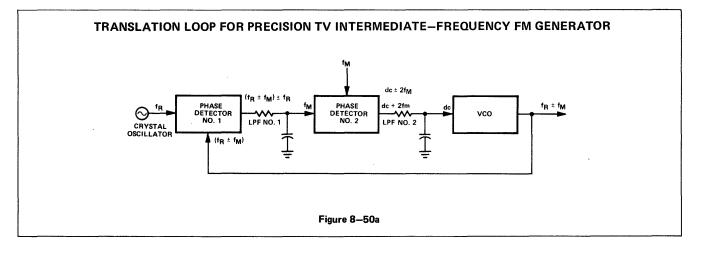

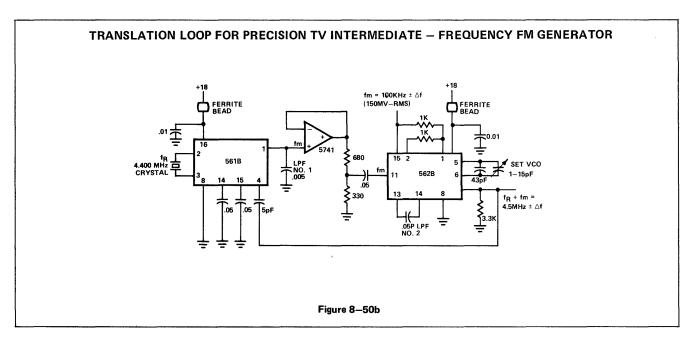

Frequency translation can be achieved by adding a mixer and a low pass filter stage to the basic PLL as shown in Figure 8–11. With this system the PLL can be used to translate the frequency of a highly stable but fixedfrequency reference oscillator by a small amount in frequency.

In this case, the reference input  $f_R$  and the VCO output  $f_o$  are applied to the inputs of the mixer stage. The mixer output is made up of the sum and the difference components of  $f_R$  and  $f_o$ . The sum component is filtered by the first low pass filter. The translation or offset frequency  $f_1$  is applied to the phase comparator along with the  $f_R - f_o$  component of the mixer output. When the system is in lock, the two inputs of the phase comparator are at identical frequency, that is,

$$f_o - f_R = f_1$$

or  $f_o = f_R + f_1$

#### **FREQUENCY SYNCHRONIZATION**

Using the phase locked loop system, the frequency of the less precise VCO can be phase locked with a low level but highly stable reference signal. Thus, the VCO output reproduces the reference signal frequency at the same per-unit accuracy, but at a much higher power level. In some applications, the synchronizing signal can be in the form of a low duty cycle burst at a specific frequency. Then, the PLL can be used to regenerate a coherent CW reference frequency blocking onto this short synchronizing pulse. A typical example of such an application is seen in the phase locked chroma-reference generators of color television receivers.

In digital systems, the PLL can be used for a variety of synchronization functions. For example, two system clocks can be phase locked to each other such that one can function as a back up for the other; or PLLs can be used in synchronizing disk or tape drive mechanisms in information storage and retrieval systems. In pulse-code modulation (PCM) telemetry receivers or in repeater systems, the PLL is used for bit synchronization.

Other popular applications include locking to WWVB to generate a cheap laboratory frequency standard and synchronizing tape speed for playback of a tape recorded at an irregular speed.

#### SIGNAL CONDITIONING

By proper choice of the VCO free-running frequency, the PLL can be made to lock to any one of a number of signals present at the input. Hence, the VCO output reproduces the frequency of the desired signal, while greatly attenuating the undesired frequencies of sidebands present at the input.

If the loop bandwidth is sufficiently narrow, the signal-tonoise ratio at the VCO output can be much better than that at the input. Thus, the PLL can be used as a noise filter for regenerating weak signals buried in noise.

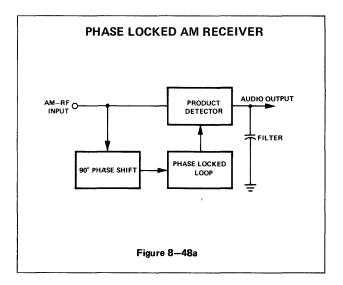

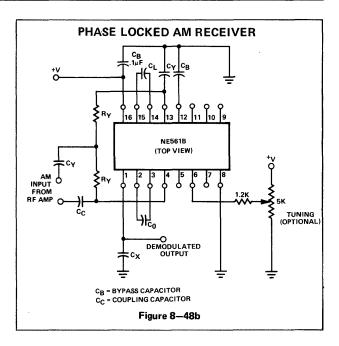

#### AM DEMODULATION

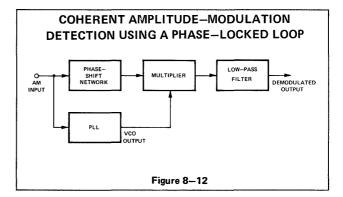

AM demodulation may be achieved with PLL by the scheme shown in Figure 8-12. In this mode of operation, the PLL functions as a synchronous AM detector. The PLL locks on the carrier of the AM signal so that the VCO output has the same frequency as that of the carrier but no amplitude modulation. The demodulated AM is then obtained by multiplying the VCO signal with the modulated input signal and filtering the output to remove all but the difference frequency component. It may be recalled from the initial discussion that when the frequency of the input signal is identical to the free-running frequency of the VCO, the loop goes into lock with these signals 90° out of phase. If the input is now shifted 90° so that it is in phase with the VCO signal and the two signals are mixed in a second phase comparator, the average dc value (difference frequency component) of the phase comparator output will be directly proportional to the amplitude of the input signal.

The PLL still exhibits the same capture range phenomena discussed earlier so that the loop has an inherent high degree of selectivity centered about the free-running VCO frequency. Because this method is essentially a coherent detection technique which involves averaging of the two compared signals, it offers a higher degree of noise immunity than can be obtained with conventional peak-detector-type AM demodulators.

GENERAL LOOP SETUP AND TRADEOFFS PHASE LOCKED LOOP MEASUREMENT TECHNIQUES MONOLITHIC PHASE LOCKED LOOP DESCRIPTIONS EXPANDING LOOP CAPABILITIES

#### **GENERAL LOOP SETUP AND TRADEOFFS**

In a given application, maximum PLL effectiveness can be achieved if the user understands the tradeoffs which can be made. Generally speaking, the user is free to select the frequency, tracking or lock range, capture range and input amplitude.

#### CENTER FREQUENCY SELECTION

Setting the center frequency is accomplished by selecting one or two external components. The center frequency is usually set in the center of the expected input frequency range. Since the loop's ability to capture is a function of the *difference* between the incoming and free-running frequencies, the band edges of the capture range are *always* an equal distance (in Hz) from the center frequency. Typically, the lock range is also centered about the freerunning frequency. Occasionally, the center frequency is chosen to be offset from the incoming so that detection or tracking range is limited on one side. This permits rejection of an adjacent higher or lower frequency signal without paying the penalty for narrow band operation (reduced tracking speed).

All of Signetics' loops use a multiplier in which the input signal is multiplied by a unity square wave at the VCO frequency. The odd harmonics present in the square wave permit the loop to lock to input signals at these odd harmonics. Thus, the center frequency may be set to, say, 1/3 or 1/5 of the input signal. The tracking range however, will be considerably reduced as the higher harmonics are utilized.

The foregoing phase detector discussion would suggest that the PLL cannot lock to subharmonics because the phase detector cannot produce a dc component if  $\omega_i$  is less than  $\omega_0$ .

The loop can lock to both odd harmonic and subharmonic signals in practice because such signals often contain harmonic components at  $f_0$ . For example, a square wave of fundamental  $f_0/3$  will have a substantial component at  $f_0$  to which the loop can lock. Even a pure sine wave input signal can be used for harmonic locking if the PLL input stage is overdriven (the resultant internal limiting generates harmonic frequencies). Locking to even harmonics or subharmonics is the least satisfactory since the input or VCO signal must contain second harmonic distortion. If locking to even harmonics is desired, the duty cycle of the input and VCO signals must be shifted away from the symmetrical to generate substantial even harmonic content.

In evaluating the loop for a potential application, it is best to actually compute the magnitude of the expected signal component nearest  $f_0$ . This magnitude can be used to estimate the capture and lock range.

All of Signetics' loops are stabilized against center frequency drift due to power supply variations. Both the 565 and the 567 are temperature compensated over the entire military temperature range (-55 to  $+125^{\circ}$ C). To benefit from this inherent stability, however, the user must provide equally stable (or better) external components. For maximum cost effectiveness in some noncritical applications, the user may wish to trade some stability for lower cost external components.

#### TRACKING OR LOCK RANGE CONTROL

Two things limit the lock or tracking range. First, any VCO can only swing so far; if the input signal frequency goes beyond this limit, lock will be lost. Second, the voltage developed by the phase detector is proportional to the product of both the phase and the amplitude of the in-band component to which the loop is locked. If the signal amplitude decreases, the phase difference between the signal and the VCO must increase in order to maintain the same output voltage and, hence, the same frequency deviation. It often happens with low input amplitudes that even the full  $\pm 90^{\circ}$  phase range of the phase detector cannot generate enough voltage to allow tracking wide deviations. When this occurs, the effective lock range is reduced. We must, therefore, give up some tracking capability and accept greater phase errors if the input signal is weak. Conversely, a strong input signal will allow us to use the entire VCO swing capability and keep the VCO phase (referred to the input signal) very close to 90<sup>0</sup> throughout the range. Note that tracking range does not depend on the low pass filter. However, if a low pass filter is in the loop, it will have the effect of limiting the maximum rate at which tracking can occur. Obviously, the LPF capacitor voltage cannot change instantly, so lock may be lost when large enough step changes occur. Between the constant frequency input and the step-change frequency input is some limiting frequency slew rate at which lock is just barely maintained. When tracking at this rate, the phase difference is at its limit of 0 or 180<sup>o</sup>. It can be seen that if the LPF cutoff frequency is low, the loop will be unable to track as fast as if the LPF cutoff frequency is higher. Thus, when maximum tracking rate is needed, the LPF should have a high cutoff frequency. However, a high cutoff frequency LPF will attenuate the sum frequencies to a lesser extent so that our output contains a significant and often bothersome signal

#### PHASE LOCKED LOOP APPLICATIONS

at twice the input frequency. (Remember that the multiplier forms both the sum and difference frequencies. During lock, the difference frequency is zero, but the sum frequency of twice the locked frequency is still present.) This sum frequency component can then be filtered out with an external low pass filter.

#### CAPTURE RANGE CONTROL

There are two main reasons for making the low pass filter time constant large. First, a large time constant provides an increased memory effect in the loop so that it remains at or near the operating frequency during momentary fading or loss of signal. Second, the large time constant integrates the phase detector output so that increased immunity to noise and out-band signals is obtained.

Besides the lower tracking rates attendant to large loop filters, other penalties must be paid for the benefits gained. The capture range is reduced and the capture transient becomes longer. Reduction of capture range occurs because the loop must utilize the magnitude of the difference frequency component at the phase detector to drive the VCO towards the input frequency. If the LPF cutoff frequency is low, the difference component amplitude is reduced and the loop cannot swing as far. Thus, the capture range is reduced.

#### CHOICE OF INPUT LEVEL

Whenever amplitude limiting of the in-band signal occurs, whether in the loop input stages or prior to the input, the tracking (lock) and capture range becomes independent of signal amplitude.

Better noise and out-band signal immunity is achieved when the input levels are below the limiting threshold since the input stage is in its linear region and the creation of crossmodulation components is reduced. Higher input levels will allow somewhat faster operation due to greater phase detector gain and will result in a lock range which becomes constant with amplitude as the phase detector gain becomes constant. Also, high input levels will result in a linear phase versus frequency characteristic.

#### LOCK-UP TIME AND TRACKING SPEED CONTROL

In tracking applications, lock-up time is normally of little consequence, but occasions do arise when it is desirable to keep lock-up time short to minimize data loss when noise or extraneous signals drive the loop out of lock. Lock-up time is of great importance in tone decoder type applications. Tracking speed is important if the loop is used to demodulate an FM signal. Although the following discussion dwells largely on lock-up time, the same comments apply to tracking speed.

No simple expression is available which adequately describes the acquisition or lock-up time. This may be appreciated when we review the following factors which influence lock-up time.

- a.) Input phase

- b.) Low pass filter characteristic

- c.) Loop damping

- d.) Deviation of input frequency from center frequency

- e.) In-band input amplitude

- f.) Out-band signals and noise

- g.) Center frequency

Fortunately, it is usually sufficient to know how we can improve the lock-up time and what we must tradeoff to get faster lock-up. Suppose we have set up a loop or tone decoder and find that occasionally the lock-up transient is too long. What can be done to improve the situationkeeping in mind the factors that influence lock?

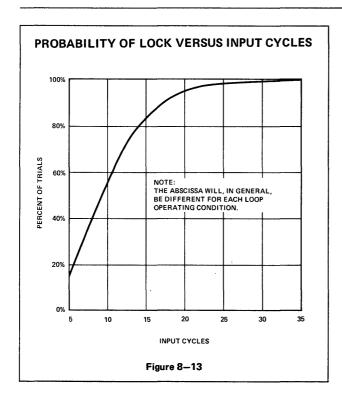

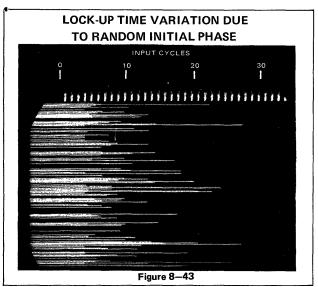

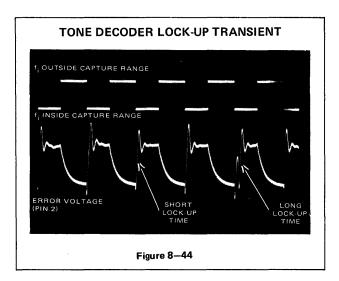

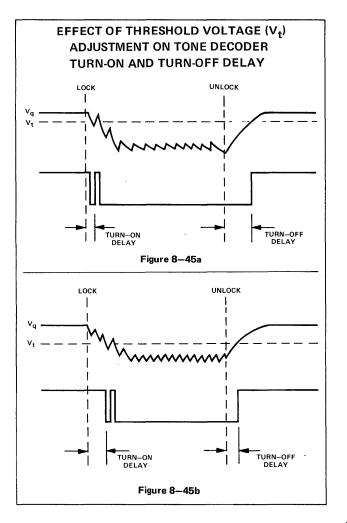

- a.) Initial phase relationship between incoming signal and VCO - This is the greatest single factor influencing the lock time. If the initial phase is wrong, it first drives the VCO frequency away from the input frequency so that the VCO frequency must walk back on the beat notes. Figure 8-13 gives a typical distribution of lock-up times with the input pulse initiated at random phase. The only way to overcome this variation is to send phase information all the time so that a favorable phase relationship is guaranteed at t = 0. For example, a number of PLLs or tone decoders may be weakly locked to low amplitude harmonics of pulse train and the transmitted tone phaserelated to the same pulse train. Usually, however, the incoming phase cannot be controlled.

- Low pass filter The larger the low pass filter b.) time constant, the longer will be the lock-up time. We can reduce lock-up time by decreasing the filter time constant, but in doing so, we sacrifice some of the noise immunity and out-band signal rejection which caused us to use a large filter in the first place. We must also accept a sum frequency (twice the VCO frequency) component at the low pass filter and greater phase jitter resulting from out-band signals and noise. In the case of the tone decoder (where control of the capture range is required since it specifies the device bandwidth) a lower value of low pass capacitor automatically increases the bandwidth. We gain speed only at the expense of added bandwidth.

c.) Loop damping – Loop damping for a simple time constant low pass filter is:

$$\zeta = \frac{1}{2} \sqrt{\frac{1}{\tau K_{\rm V}}}$$

Damping can be increased not only by reducing  $\tau$ , as discussed above, but also by reducing the loop gain K<sub>v</sub>. By using the loop gain reduction to control bandwidth or capture and lock range, we achieve better damping for narrow bandwidth operation. The penalty for this damping is that more phase detector output is required for a given deviation so that phase errors are greater and noise immunity is reduced. Also, more input drive may be required for a given deviation.

- d.) Input frequency deviation from free-running frequency – Naturally, the further an applied input signal is from the free-running frequency of the loop, the longer it will take the loop to reach that frequency due to the charging time of the low pass filter capacitor. Usually, however, the effect of this frequency deviation is small compared to the variation resulting from the initial phase uncertainty. Where loop damping is very low, however, it may be predominant.

- e.) In-band input amplitude Since input amplitude is one factor in the phase detector gain  $K_d$  and since  $K_d$  is a factor in the loop gain  $K_v$ , damping is also a function of input amplitude. When the input amplitude is low,

the lock-up time may be limited by the rate at which the low pass capacitor can charge with the reduced phase detector output (see d above).

- f.) Out-band signals and noise Low levels of extraneous signals and noise have little effect on the lock-up time, neither improving or degrading it. However, large levels may overdrive the loop input stage so that limiting occurs, at which point the in-band signal starts to be suppressed. The lower effective input level can cause the lock-up time to increase, as discussed in e above.

- g.) Center frequency Since lock-up time can be described in terms of the number of cycles to lock, fastest lock-up is achieved at higher frequencies. Thus, whenever a system can be operated at a higher frequency, lock will typically take place faster. Also, in systems where different frequencies are being detected, the higher frequencies on the average will be detected before the lower frequencies. However, because of the wide variation due to initial phase, the reverse may be true for any single trial.

#### PLL MEASUREMENT TECHNIQUES

This section deals with user measurements of PLL operation. The techniques suggested are meant to help the user in evaluating the performance of his PLL during the initial setup period as well as to point out some pitfalls that may obscure loop evaluation. Recognizing that the user's test equipment may be limited, we have stressed the techniques which require a minimum of standard test items.

#### **CENTER FREQUENCY**

Center frequency measurements are easily made by connecting a frequency counter or oscilloscope to the VCO output of the loop. The loop should be connected in its final configuration with the chosen values of input, bypass and low pass filter capacitors. No input signal should be present. As the center frequency is read out, it can be adjusted to the desired value by the adjustment means selected for the particular loop. It is important not to make the frequency measurement directly at the timing capacitor unless the capacity added by the measurement probe is much less than the timing capacitor value since the probe capacity will then cause a frequency error.

When the frequency measurement is to be converted to a dc voltage for production readout or automated testing, a calibrated phase locked loop can be used as a frequency meter (see Applications Section).

#### CAPTURE AND LOCK RANGE

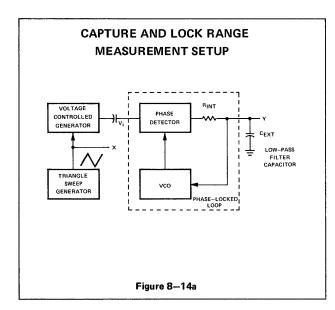

Figure 8-14a shows a typical measurement setup for capture and lock range measurements. The signal input from a variable frequency oscillator is swept linearly through the frequency range of interest and the loop FM output is displayed on a scope or (at low frequencies) X-Y recorder. The sweep voltage is applied to the X axis.

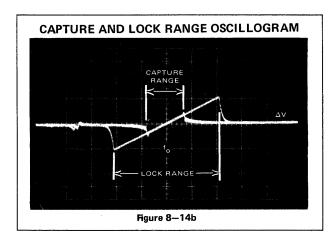

Figure 8–14b shows the type of trace which results. The lock range (also called hold-in or tracking range) is given by the outer lines on the trace, which are formed as the incoming frequency sweeps *away* from the center frequency. The inner trace, formed as the frequency sweeps *toward* the center frequency, designates the capture range. Linearity of the VCO is revealed by the straightness of the trace portion within the lock range. The slope  $(\Delta f/\Delta V)$  is the gain or conversion factor for the VCO.

By using the sweep technique, the effect on center frequency, capture range and lock range of the input amplitude, supply voltage, low pass filter and temperature can be examined.

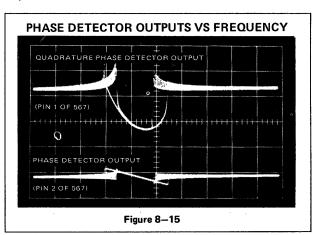

Because of the lock-up time duration and variation, the sweep frequency must be very much lower than the center frequency, especially when the capture range is below 10% of center frequency. Otherwise, the *apparent* capture and lock range will be a function of sweep frequency. It is best to start sweeping as slow as possible and, if desired, increase the rate until capture range begins to show an apparent reduction—indicating that the sweep is too fast. Typical sweep frequencies are in the range of 1/1000 to 1/100,000 of the center frequency. In the case of the 561 and 567, the quadrature detector output may be similarly displayed on the Y axis, as shown in Figure 8–15, showing the output level versus frequency for one value of input amplitude.

Capture and lock range measurements may also be made by sweeping the generator manually through the band of interest. Sweeping must be done very slowly as the edges of the capture range are approached (sweeping toward center frequency) or the lock-up transient delay will cause an error in reading the band edge. Frequency should be read from the generator rather than the loop VCO because the VCO frequency gyrates wildly around the center frequency just before and after lock. Lock and unlock can be readily detected by simultaneously monitoring the input and VCO signals, the dc voltage at the low pass filter or the ac beat frequency components at the low pass filter. The latter are greatly reduced during lock as opposed to frequencies just outside of lock.

#### FM AND AM DEMODULATION DISTORTION

These measurements are quite straightforward. The loop is simply setup for FM or AM (561 or 567) detection and the test signal is applied to the input. A spectrum analyzer or distortion analyzer (HP 333 A) can be used to measure distortion at the FM or AM output.

For FM demodulation, the input signal amplitude must be large enough so that lock is not lost at the frequency extremes. The data sheets give the lock (or tracking) range as a function of input signal and the optional range control adjustments. Due to the inherent linearity of the VCOs, it makes little difference whether the FM carrier is at the free-running frequency or offset slightly as long as the tracking range limits are not exceeded. The faster the FM modulation in relation to the center frequency, the lower the value of the capacitor in the low pass filter must be for satisfactory tracking. As this value decreases, however, it attenuates the sum frequency component of the phase detector output less. The demodulated signal will appear to have greater distortion unless this component is filtered out before the distortion is measured. The same comment applies to the measurement of AM distortion on the 561.

When AM distortion is being measured, the carrier frequency offset becomes more important. The lowest absolute value of carrier voltage at the modulation valleys must be high enough to maintain lock at the frequency deviation present. Otherwise, lock will periodically be lost and the distortion will be unreasonable. For example, the typical tracking range as a function of input signal graph in the 561 data sheet gives a total 3% tracking range at 0.3mV rms input. Thus, for a carrier deviation of 1.5%, the carrier must not drop below 0.3V rms in the modulation valleys. Naturally, the AM amplitude must not be too high or the AM information will be suppressed.

#### NATURAL FREQUENCY ( $\omega_n$ )

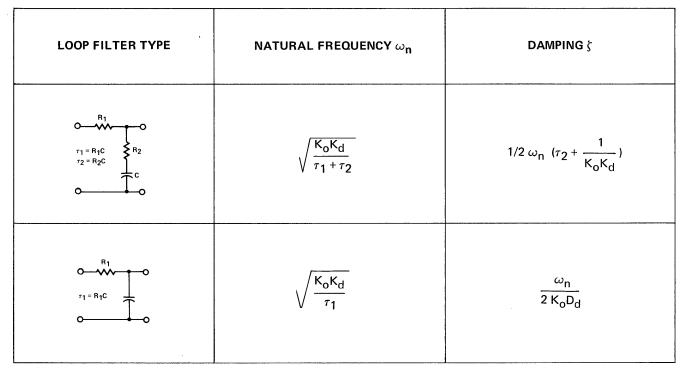

Expressions for the natural frequency in terms of the loop gains and filter parameters are given in Table 8-2.

#### EXPRESSIONS FOR $\omega_{\mathbf{n}}$ and $\zeta$ in second order loop

#### PHASE LOCKED LOOP APPLICATIONS

The natural frequency  $(\omega_n)$  of a loop in its final circuit configuration can be measured by applying a frequency modulated signal of the desired amplitude to the loop (Table 8–2 shows that the natural frequency is a function of K<sub>d</sub>, in turn a function of input amplitude). As the modulation frequency  $(\omega_m)$  is increased, the phase relationship between the modulation and recovered sine wave will go through 90° at S<sub>m</sub> =  $\omega_n$  and the output amplitude will peak.

#### DAMPING (ζ)

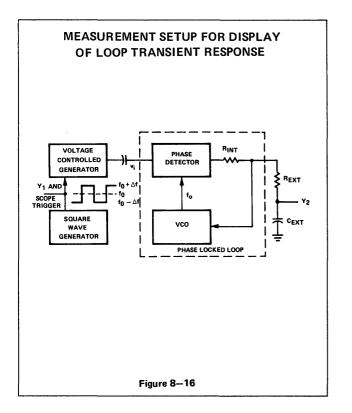

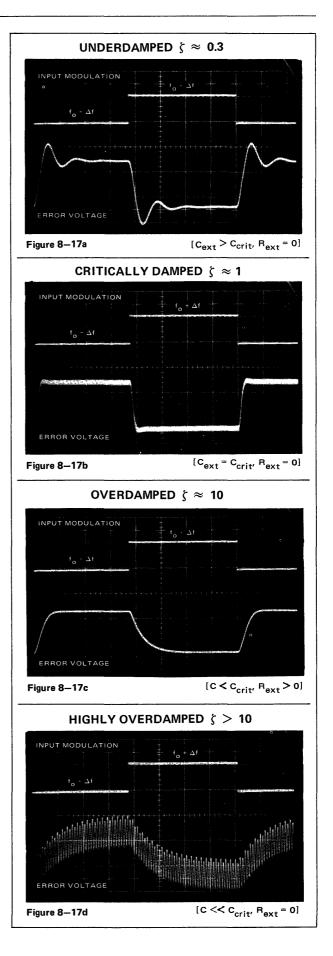

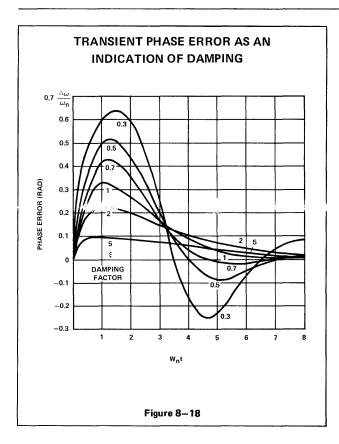

As shown in Table 8–2 in the discussion on low pass filter, damping is a function of  $K_0$ ,  $K_d$  and the low pass filter. Since  $K_0$  and  $K_d$  are functions of center frequency and input amplitude, respectively, damping is highly dependent on the particular operating condition of the loop. Damping estimates for the desired operating condition can be made by applying an input signal which is frequency modulated within the lock range by a square wave. The low pass filter voltage is then monitored on an oscilloscope which is synchronized to the modulating waveform, as shown in Figure 8–16. Figure 8–17 shows typical waveforms displayed. The loop damping can be estimated by comparing the number and magnitude of the overshoots with the graph of Figure 8–18, which gives the transient phase error due to a step in input frequency.

Another way of estimating damping is to make use of the frequency response plot measured for the natural frequency ( $\omega_n$ ) measurement. For low damping constants, the frequency response measurement peak will be a strong function of damping. For high damping constants, the 3dB-down point will give the damping. Table 8–3 gives the approximate relationship.

### ESTIMATING DAMPING FROM MODULATING FREQUENCY ( $\omega_m$ ) RESPONSE

| \$  | AMPLITUDE | $\frac{\omega - 3 dB}{\omega}$ n |  |  |  |  |

|-----|-----------|----------------------------------|--|--|--|--|

| .3  | 6.0dB     | 1.8                              |  |  |  |  |

| .5  | 3.2dB     | 2.1                              |  |  |  |  |

| .7  | 2.2dB     | 2.5                              |  |  |  |  |

| 1.0 | 1.3dB     | 4.3                              |  |  |  |  |

| 5.0 | .5dB      | 10                               |  |  |  |  |

|     |           |                                  |  |  |  |  |

| l   |           |                                  |  |  |  |  |

#### NOISE EFFECTS

The effect of input noise on loop operation is very difficult to predict. Briefly, the input noise components near the center frequency are converted to phase noise. When the phase noise becomes so great that the  $\pm 90^{\circ}$  permissible phase variation is exceeded, the loop drops out of lock or fails to acquire lock. The best technique is to actually apply the anticipated noise amplitude and bandwidth to the input and then perform the capture and lock range measurements as well as perform operating tests with the anticipated input level and modulation deviations. By including a small safety factor in the loop design to compensate for small processing variations, satisfactory operation can be assured.

#### SIMPLIFIED MEASUREMENT EQUIPMENT

The majority of the PLL tests described can be done with a signal generator, a scope and a frequency counter. Most laboratories have these. A low-cost digital voltmeter will facilitate accurate measurement of the VCO conversion gain. Where the need for a FM generator arises, it may be met in most cases by the VCO of a Signetics PLL. (See the applications in this section.) Any of the loops may be set up to operate as a VCO by simply applying the modulating voltage to the low pass filter terminal(s). The resulting generator may be checked for linearity by using the counter to check frequency as a function of modulating voltage. Since the VCOs may be modulated right down to dc, the calibration may be done in steps. Moreover, Gardner<sup>\*</sup> shows how loop measurements may be made by applying a *constant* frequency to the loop input and the modulating signal to the low pass filter terminal to simulate the effect of a FM input so that a FM generator may be omitted for many measurements.

\*see references

## SIGNETICS MONOLITHIC PHASE LOCKED LOOPS

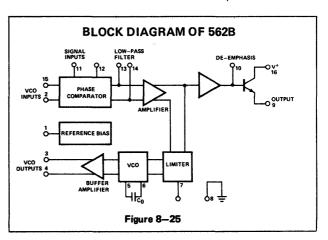

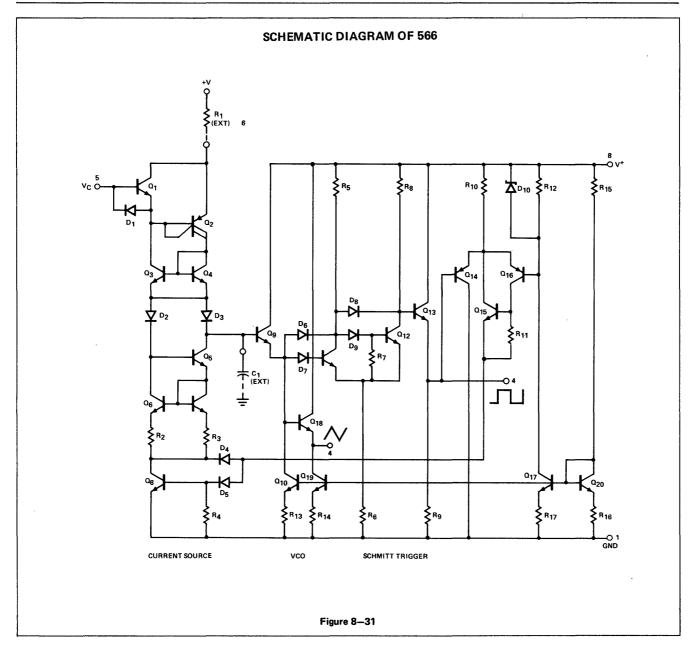

#### DETAILED DESCRIPTION OF 560B, 561B AND 562B

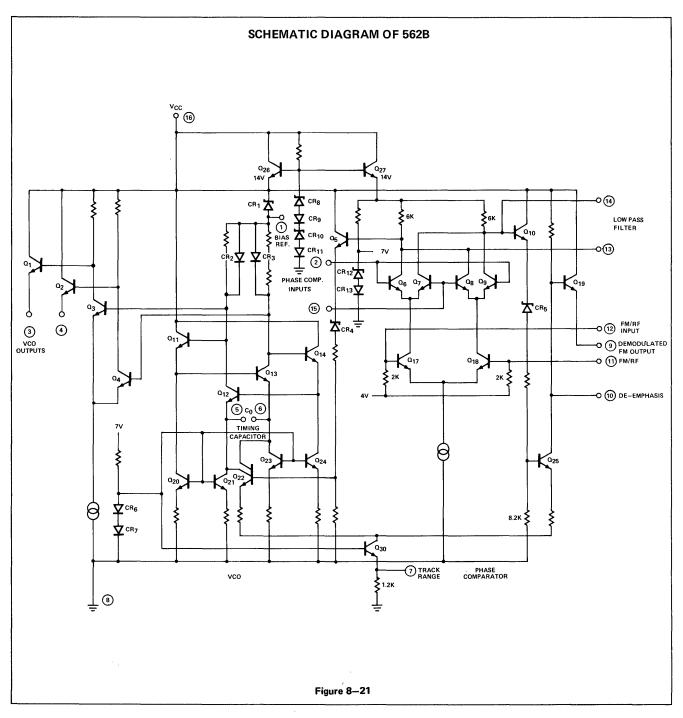

The 560B, 561B and 562B phase locked loops are all derived from the same monolithic die with different metal interconnections. Each device contains the same VCO,

phase detector and voltage regulator stage and, hence, the basic loop parameters are the same for all three circuits.

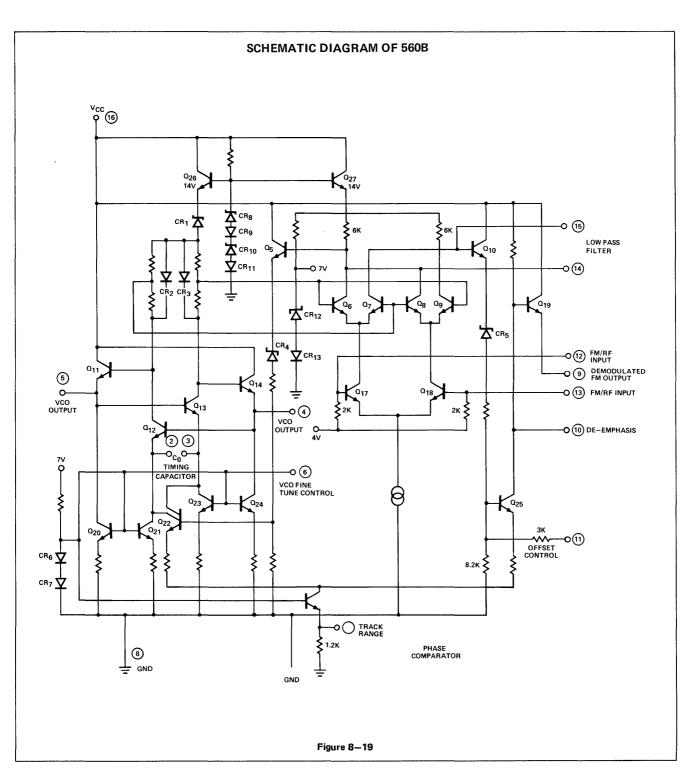

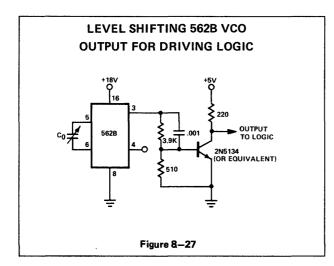

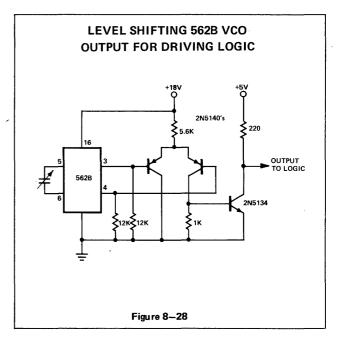

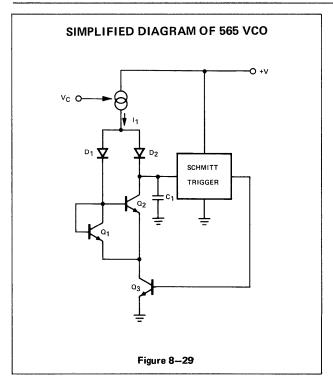

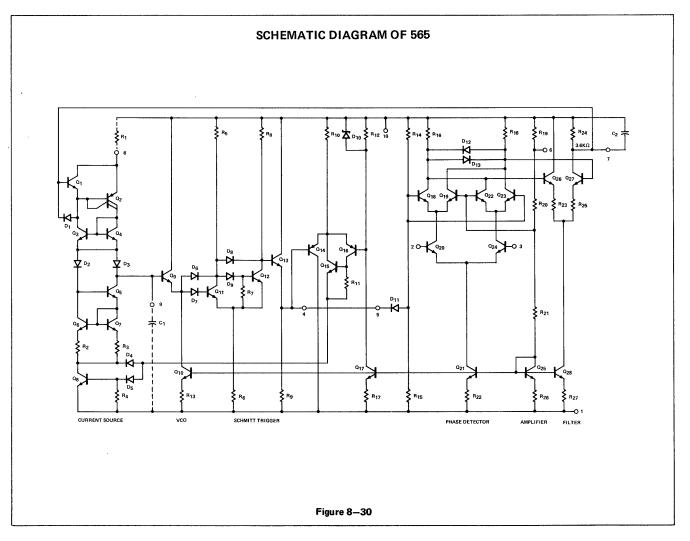

The 560B is the most fundamental of the three circuits, having a block diagram equivalent to that shown in Figure 8-1. The actual circuit diagram is shown in Figure 8-19.