# ST212 PRODUCT MANUAL

March 24, 1986<sup>©</sup> 36010-001, Revision B

Seagate reserves the right to change, without notice, the specifications contained in this manual.

Seagate ■ 920 Disc Drive, Scotts Valley, CA 95066-4544, USA Tel. (408) 438-6550 ■ Telex 176455 SEAGATE SCVL

· "你是你们的,你们就不是你的我们的你们,你不必要的。" 我们们,你们不知道你?""我们不是你们的你们就能是你?"

•

| <b>1.0 SPECIFICATION SUMMARY</b>                                        |   |

|-------------------------------------------------------------------------|---|

| 1.1 Performance Specifications                                          | 1 |

| 1.1.1 Access Time Definition and Timing                                 | 1 |

| 1.2 Functional Specifications                                           |   |

| 1.3 Physical Specifications.                                            |   |

| 1.4 Reliability Specifications                                          |   |

| 1.4.1 Read Error Rates         1           1.4.1.1 Bit Jitter         2 |   |

| 1.4.1.1 Bit Jitter                                                      |   |

| 1.5 Environmental Specifications                                        |   |

| 1.5.1 Ambient Temperature                                               |   |

| 1.5.2 Temperature Gradient                                              |   |

| 1.5.3 Relative Humidity                                                 | 2 |

| 1.5.4 Altitude Limits                                                   |   |

| 1.5.5 Operating Shock                                                   |   |

| 1.5.6 Nonoperating Shock                                                |   |

| 1.6 DC Power Requirements                                               |   |

| 1.6.1 Input Noise Ripple                                                |   |

| 1.6.2 Input Noise Frequency                                             |   |

| 1.7 Mounting Requirements.                                              |   |

| 1.7.1 Handling and Static-Discharge Precautions                         |   |

|                                                                         |   |

| 2.0 ST212 HOST/DRIVE INTERFACE.                                         |   |

| 2.1 Control/Status Signals: PCB Edge-Connector J1                       | b |

| 2.2 Data Signals: PCB Edge-Connector J2                                 | 5 |

| 2.3 DC Power: Connector J3                                              |   |

| 2.4 Frame Grounding: Lug J1010                                          |   |

| 3.0 DRIVE CONFIGURATION11                                               | 1 |

| 3.1 Drive Configuration: Shunt J9 (MLC-01)                              | 1 |

| 3.2 Drive Select                                                        | 1 |

| 3.2.1 Daisy-chain                                                       | 1 |

| 3.3 Radial                                                              | 2 |

| 3.4 Write Fault                                                         | 2 |

| 3.5 Life Test                                                           | 2 |

| 4.0 CONTROL INPUT SIGNALS                                               | 2 |

| 4.1 Head Select $2^{\circ}$ , $2^{\circ}$ , $2^{\circ}$ , $2^{\circ}$   |   |

| 4.2 Write Gate                                                          |   |

| 4.3 Step                                                                |   |

| 4.3.1 Buffered Seek                                                     |   |

| 4.3.2 Slow-step (Single-track)                                          |   |

| 4.3.3 Auto-truncation                                                   |   |

| 4.4 Direction In                                                        |   |

| 4.5 Drive Select                                                        |   |

|                                                                         |   |

| 5.0 CONTROL OUTPUT SIGNALS                                              |   |

| 5.1 Drive Selected                                                      |   |

| 5.2 Index                                                               |   |

| 5.3 Track Ø                                                             |   |

| 5.4 Ready                                                               | ð |

| 5.5 Seek Complete                                                       | 9 |

| 5.6 Write Fault.                                                        |   |

| 5.6.1 Write Fault Signal Generation                                     |   |

| 5.6.1.1 Write Current Interruption                                      |   |

| 5.7 Fault Detection: PC Board 20292-XXX                                 |   |

| 5.7.1 Voltage and Head Select Comparator                                |   |

| 5.7.2 Write Fault Reset                                                 |   |

| 5.8 Fault Detection: PC Board 20243-XXX                                 |   |

| 5.8.1 Voltage Comparator                                                | 1 |

| 5.8.2 Head Select Comparators2                                          |   |

| 6.0 READ/WRITE OPERATIONS2                                              | 2 |

| 6.1 Write Operation: PC Board 20292-XXX                                 | 2 |

| 6.1.1 MFM Write Data                                                    | 2 |

| 6.1.2 Write Gate6.1.3 Write Data Processing                                                     | .23  |

|-------------------------------------------------------------------------------------------------|------|

| <ul><li>6.1.4 Precompensation.</li><li>6.2 Write Operation: PC Board 20243-XXX.</li></ul>       | .23  |

| 6.2.1 Write Gate                                                                                |      |

| 6.2.2 Line Receiver                                                                             | .24  |

| 6.3 Formatting.                                                                                 |      |

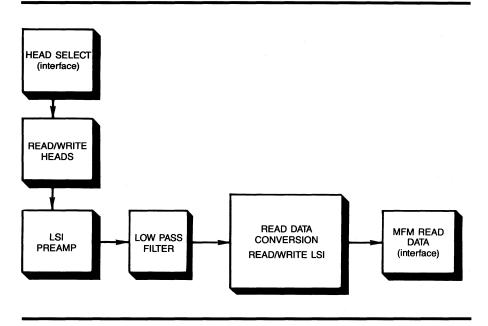

| 6.4 Read Operation: PC Board 20292-XXX                                                          |      |

| 6.4.2 Head Select                                                                               |      |

| 6.4.3 LSI Preamp                                                                                | .26  |

| 6.4.4 Low Pass Filter                                                                           |      |

| <ul><li>6.4.5 Read Data Conversion.</li><li>6.5 Read Operation: PC Board 20243-XXX.</li></ul>   |      |

| 6.5.1 Head Select                                                                               |      |

| 6.5.2 LSI Preamp.                                                                               | .27  |

| 6.5.3 Low Pass Filter                                                                           |      |

| 6.5.4 Phase Shifter                                                                             |      |

| 6.5.5 Zero Cross Detector         6.5.6 Time Domain Filter                                      | .27  |

| 6.5.7 Line Driver                                                                               |      |

| · ·                                                                                             |      |

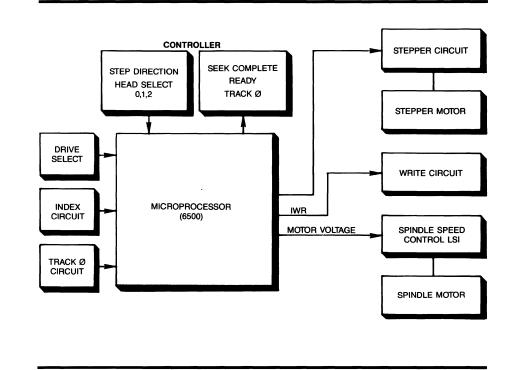

| 7.0 MICROPROCESSOR                                                                              | .29  |

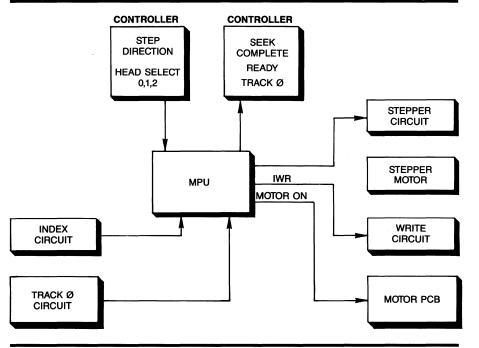

| 7.2 MPU: PC Board 20243-XXX                                                                     |      |

|                                                                                                 |      |

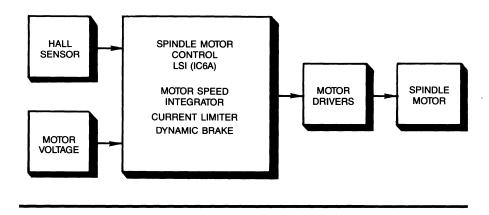

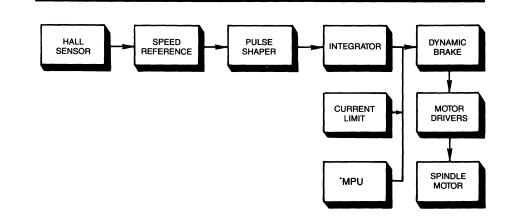

| <ul><li>8.0 MOTOR SPEED CONTROL.</li><li>8.1 Motor Speed Control: PC Board 20292-XXX.</li></ul> |      |

| 8.1.1 Hall Effect Transducer                                                                    | .31  |

| 8.1.2 Spindle Motor Control LSI.                                                                | .31  |

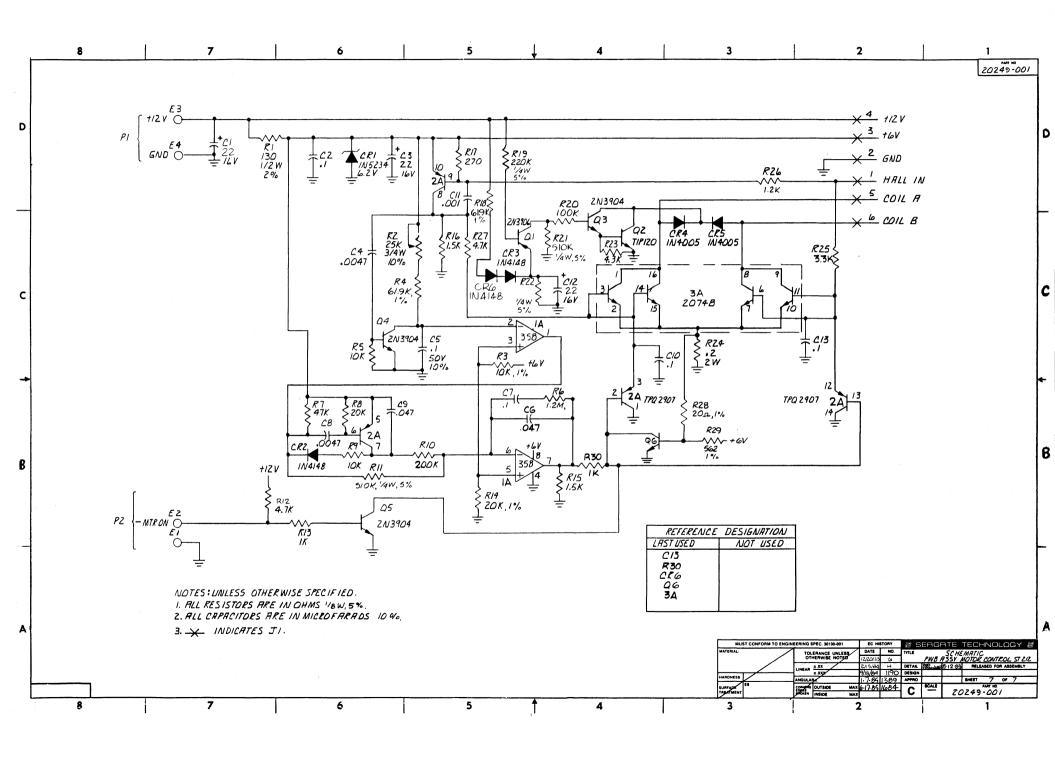

| 8.2 Motor Speed Control PC Board: 20249-XXX                                                     |      |

| 8.2.1 Hall Effect Transducer.                                                                   |      |

| <ul><li>8.2.2 Speed Reference Circuit.</li><li>8.2.3 Pulse Shaper.</li></ul>                    |      |

| 8.2.4 Integrator                                                                                |      |

| 8.2.5 Current Limit.                                                                            |      |

| 8.2.6 Microprocessor: Motor On                                                                  |      |

| 8.2.7 Motor Drivers.                                                                            |      |

| 8.2.8 Dynamic Brake                                                                             | .32  |

| 9.0 FIELD SERVICE.                                                                              | .33  |

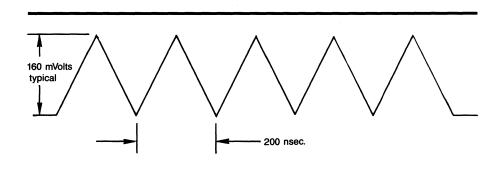

| 9.1 Test Point Data: PC Board 20292-XXX                                                         | .33  |

| 9.1.1 Differential Read Filter: Test Points 1 and 2<br>9.1.2 Track Ø Sensor: IC 3B, Pin 1       |      |

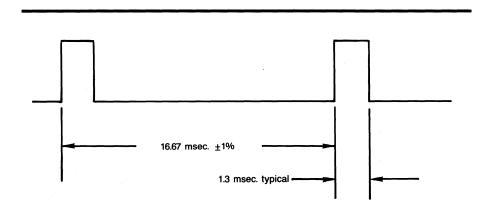

| 9.1.3 Index Sensor: Test Point 9                                                                |      |

| 9.2 Test Point Data: PC Board 20243-XXX                                                         |      |

| 9.2.1 Differential Read Filter: Test Points 1 and 2                                             |      |

| 9.2.2 Read Data: Test Points 3 and 4                                                            |      |

| 9.2.3 Track Ø: Test Point 5           9.2.4 Index Sensor: Test Point 6                          |      |

| 9.3 Field Accessible Components.                                                                |      |

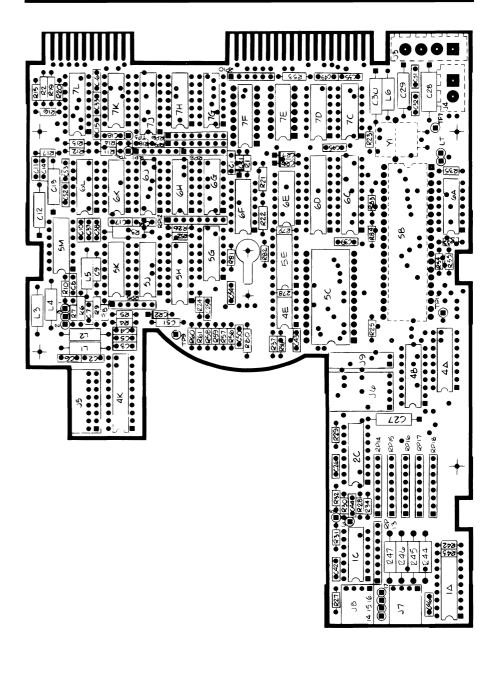

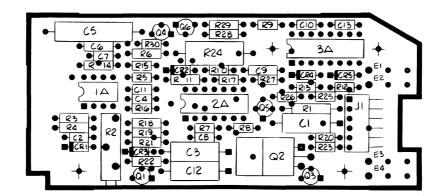

| 9.3.1 Main Control PC Board                                                                     | .37  |

| 9.3.2 Motor Control PC Board Removal (MLC-00 only)                                              |      |

| 9.3.3 Index Sensor Removal.                                                                     |      |

| 9.3.4 Installing the Optional Full-height Front Panel<br>9.3.5 Track Ø Sensor Removal           |      |

|                                                                                                 | . 39 |

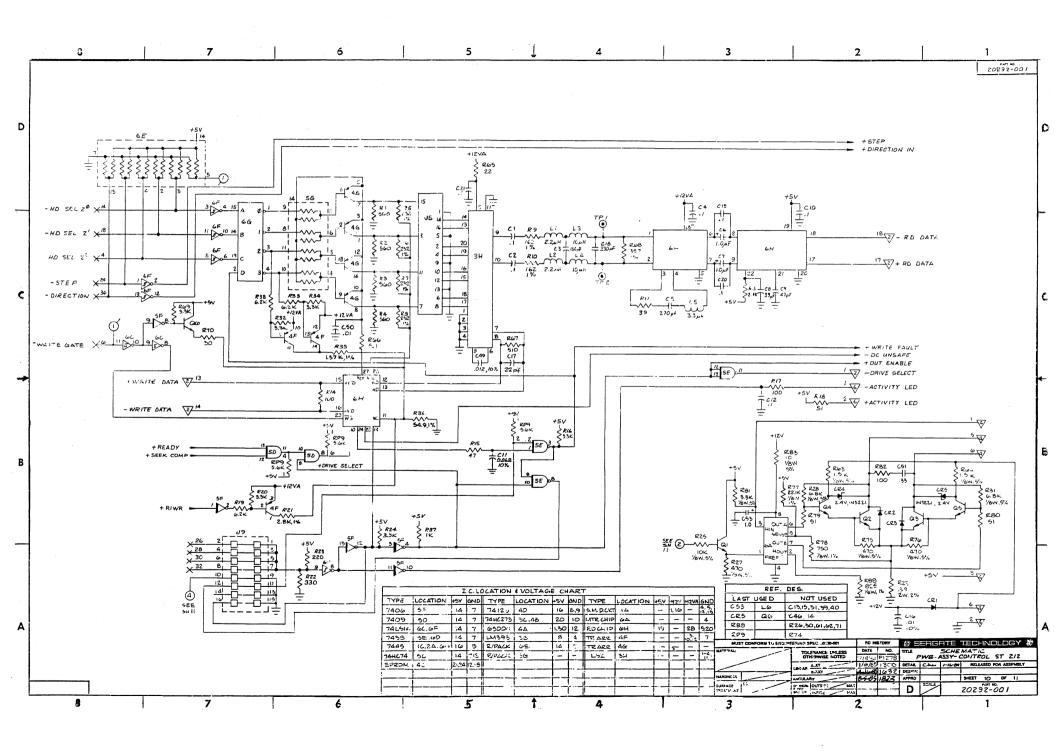

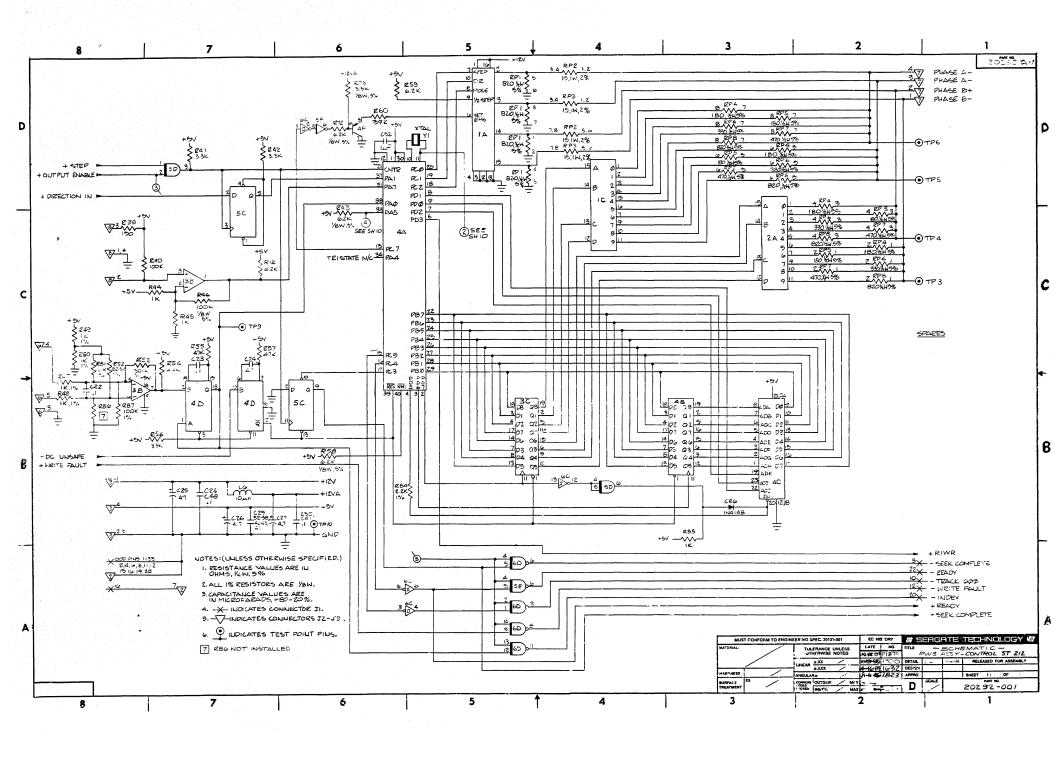

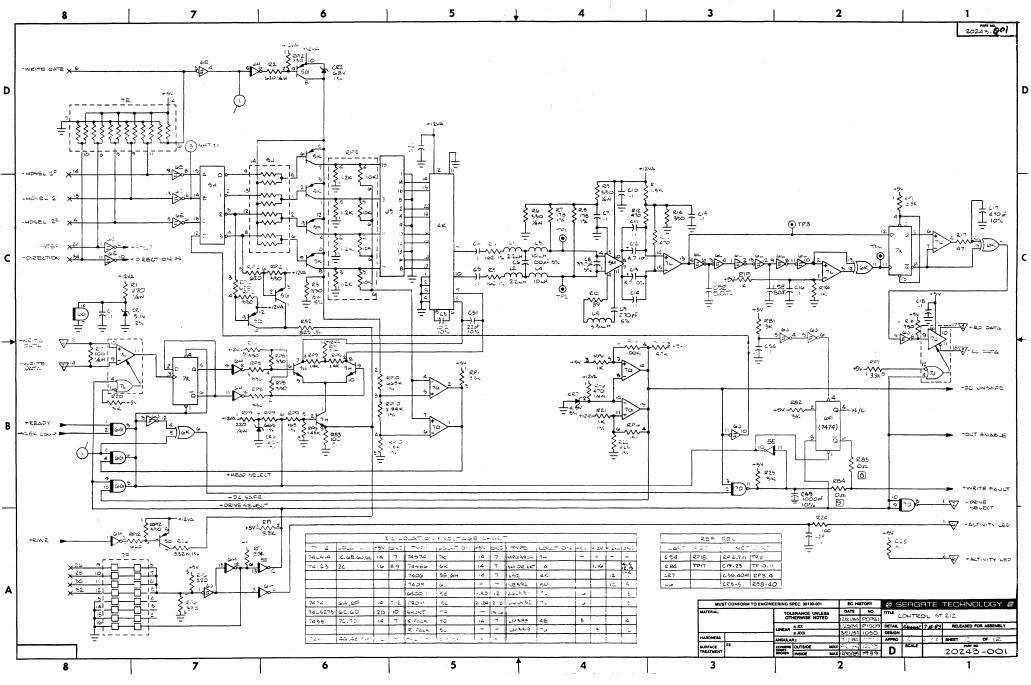

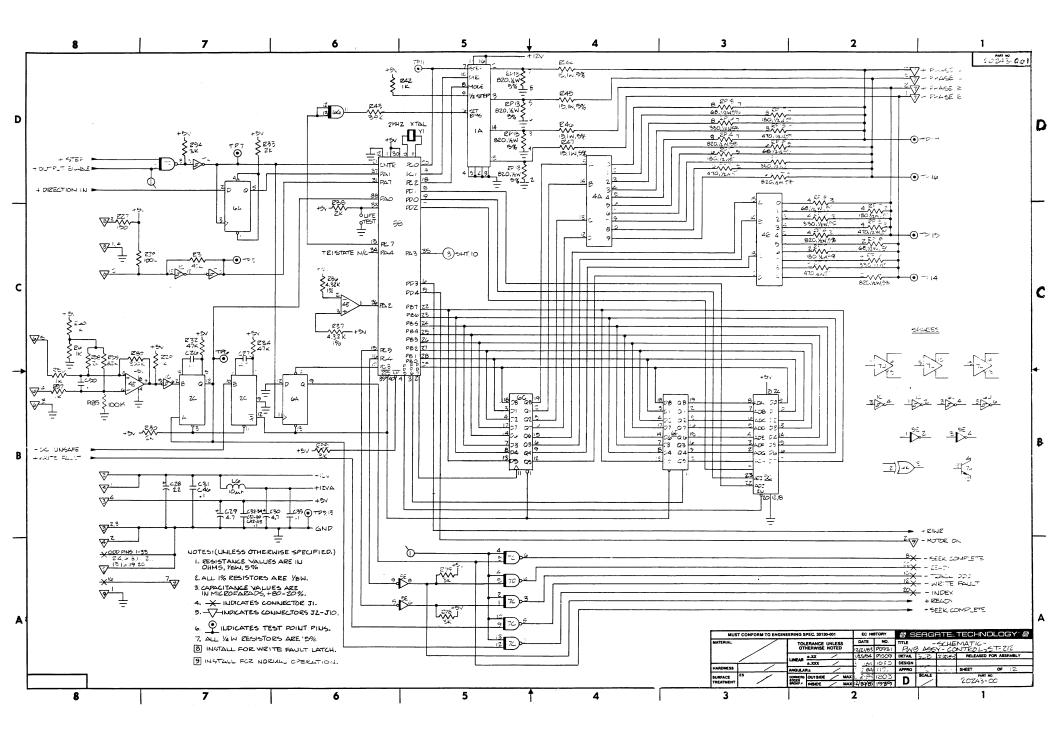

| Schematics                                                                                      |      |

| PCB 20243-XXX<br>PCB 20249-XXX                                                                  |      |

| PCB 20292-XXX                                                                                   |      |

|                                                                                                 |      |

# FIGURES

| FIGURE | 1: Typical +12 Volt DC Start-up Current Profile | 3  |

|--------|-------------------------------------------------|----|

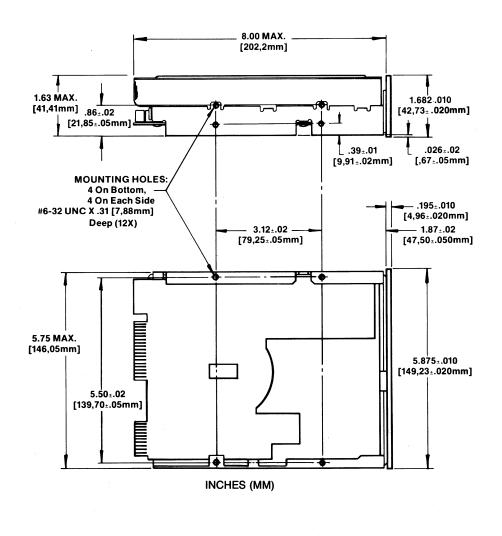

| FIGURE | 2: Mounting Dimensions                          | 4  |

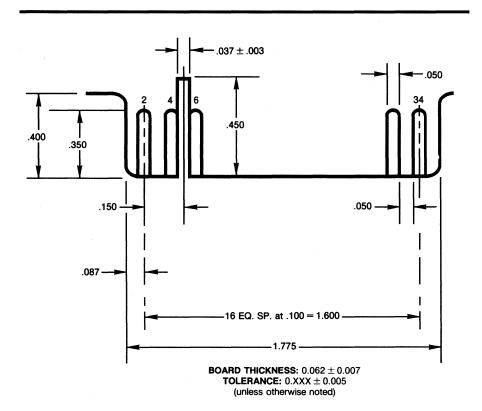

| FIGURE | 3: J1 Connector Dimensions                      | 6  |

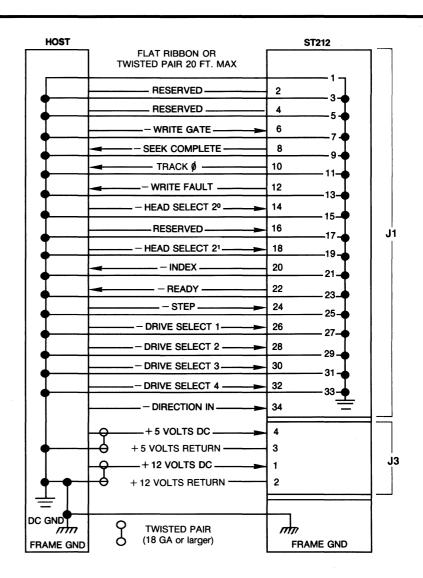

| FIGURE | 4: Control/Status Signals                       | 7  |

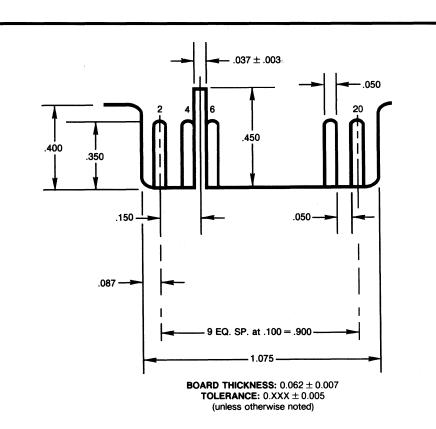

| FIGURE | 5: J2 Connector Dimensions                      | 8  |

| FIGURE |                                                 |    |

| FIGURE | 7: Host/Drive Interface and Drive Configuration | 10 |

| FIGURE |                                                 |    |

| FIGURE |                                                 |    |

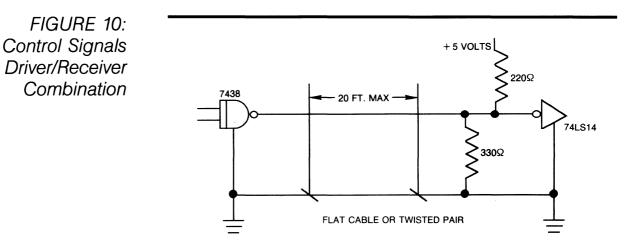

|        | 10: Control Signals Driver/Receiver Combination |    |

|        | 11 Read/Write Timing                            |    |

|        | 12 General Step Timing                          |    |

|        | 13: Slow-step Timing                            |    |

| FIGURE | 14: Auto-truncation Timing                      | 16 |

|        | 15: Drive Select                                |    |

|        | 16: Typical Power-up Sequence                   |    |

|        | 17: Fault Detection PC Board 20292-XXX          |    |

|        | 18: Fault Detection PC Board 20243-XXX          |    |

|        | 19: Data Signal Driver/Receiver Combination     |    |

|        | 20: Write Operation PC Board 20292-XXX          |    |

|        | 21: Write Operation PC Board 20243-XXX          |    |

|        | 22: 17-Sector, 512-Byte/Sector Format Example   |    |

|        | 23: Read Operation PC Board 20292-XXX           |    |

|        | 24: Read Operation PC Board 20243-XXX           |    |

|        | 25: MPU: PC Board 20292-XXX                     |    |

|        | 26: MPU: PC Board 20243-XXX                     |    |

|        | 27: Motor Speed Control: PC Board 20292-XXX     |    |

|        | 28: Motor Speed Control: PC Board 20249-XXX     |    |

|        | 29: Test Point Locations PC Board 20292-XXX     |    |

|        | 30: Differential Read Filter                    |    |

|        | 31: Index Sensor                                |    |

|        | 32: Test Point Locations PC Board 20243-XXX     |    |

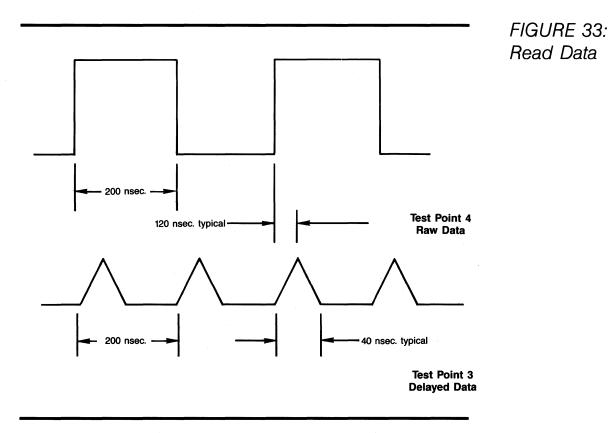

|        | 33: Read Data                                   |    |

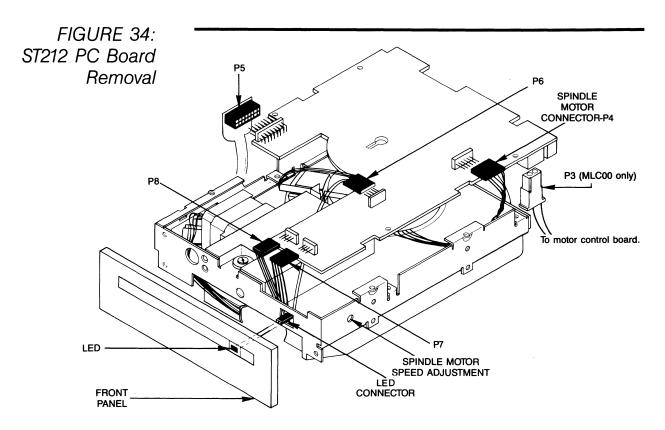

|        | 34: ST212 PC Board Removal                      |    |

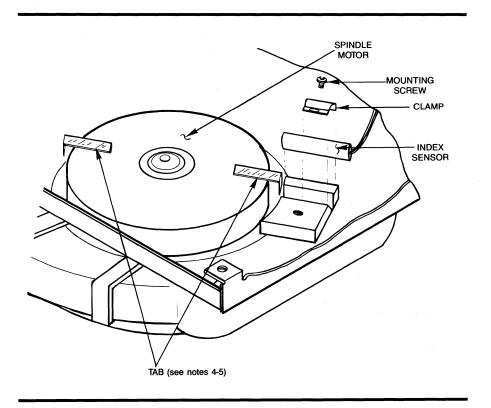

|        | 35: Index Sensor Adjustment/Removal             |    |

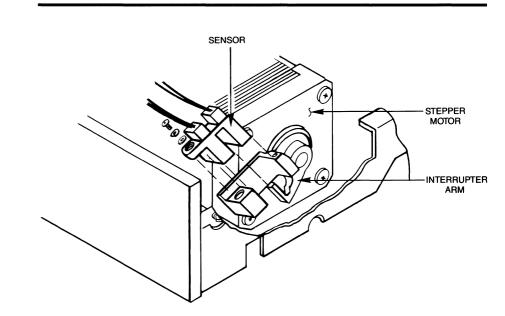

| FIGURE | 36: Track Ø Sensor Removal                      | 39 |

|        |                                                 |    |

# TABLES

| TABLE 1: J1 Host/Drive Pin Assignments | 7  |

|----------------------------------------|----|

| TABLE 2: J2 Host/Drive Pin Assignments | 9  |

| TABLE 3: Precompensation Pattern    2  | 23 |

.v

# 1.0 **SPECIFICATION SUMMARY**

# **PERFORMANCE SPECIFICATIONS**

| CAPACITY           | UNFORMATTED  |

|--------------------|--------------|

| Per Drive:         | 12.76 MB     |

| Per Surface:       | 6.38 MB      |

| Per Track:         | 10,416 Bytes |

| Per Sector:        | NA           |

| Sectors Per Track: | NA           |

FORMATTED 10.0 MB 5.0 MB 8,192 Bytes 256 Bytes 32 Sectors

## ACCESS TIME DEFINITION AND TIMING

Access time is defined as the time from the leading edge of the last Step pulse received to SEEK COMPLETE (including settling). The Step pulse period must be between 5  $\mu$ sec. to 500  $\mu$ sec.

| Track-to-Track: | 23.0 msec. max.              |

|-----------------|------------------------------|

| Average:        | 65.0 msec. max. <sup>1</sup> |

| Maximum:        | 170.0 msec.                  |

# FUNCTIONAL SPECIFICATIONS

**Rotational Speed:**  $3,600 \text{ RPM} \pm 1\%$ Average Latency: 8.33 msec. **Recording Density:** 10,560 BPI/FCI 550 TPI Track Density: Cylinders: 306 Tracks: 1,224 Discs: 1 **Recording Method:** MFM Data Transfer Rate: 5.0 Megabits/second

# PHYSICAL SPECIFICATIONS

Height: Width: Depth: Weight:

1.63 inches max. (41.4 mm) 5.75 inches max. (146.05 mm) 8.00 inches max. (203.2 mm) 3.00 lbs (1.4 Kg)

# **RELIABILITY SPECIFICATIONS**

MTBF: PM: MTTR: Service Life:

11,000 Power-on Hours<sup>2</sup> Not Required 30 Minutes 5 Years

## **READ ERROR RATES**

1 per 10<sup>10</sup> bits read <sup>3</sup> **Recoverable Read Errors:** 1 per 10<sup>12</sup> bits read <sup>4</sup> Nonrecoverable Read Errors: 1 per 10<sup>6</sup> seeks Seek Errors:

- 1. Buffered-Seek

- 2. Typical usage at 25 °C at sea level. Calculated per Mil. Spec. 217.

- 3. Recoverable within 16 retries

- 4. Not recoverable within 16 retries

1

1.3

1.4

1.4.1

1.1

1.1.1

1.2

# 1.4.1.1

Bit jitter reduction determines the relationship between the leading edge of Read data and the center of the data window.

The specified Read error rates are based on the following bit jitter specification: The data separator must provide at least -40 dB of bit jitter reduction at 2F with an offset error of less than 1.5 nsec. shift from the center of the data window.

# 1.4.2

#### MEDIA DEFECTS

A media defect is a Read error when data, which has been correctly written, cannot be recovered within 16 retries.

A printout will be provided with each drive shipped listing the location of any defect by head, cylinder, sector and byte.<sup>5</sup> It will also specify the number of bytes from Index.

There will be no more than four (4) defects per Read/Write head for a maximum total of sixteen (16) per drive. Cylinder Zero will be free of defects.

# ENVIRONMENTAL SPECIFICATIONS

#### 1.5.1

1.5

**Operating:** Nonoperating: AMBIENT TEMPERATURE

10°C to 45°C (50°F to 113°F) -40°C to 60°C (-40°F to 140°F)

# 1.5.2

# **TEMPERATURE GRADIENT**

**Operating:** Nonoperating: 10°C/hr (18°F/hr) max. Below condensation

# 1.5.3

**Operating:**

Nonoperating:

Maximum Wet Bulb:

#### **RELATIVE HUMIDITY**

8 to 80% noncondensing 26°C (78.8°F) 5 to 95% noncondensing

## 1.5.4

# **ALTITUDE LIMITS**

-1,000 ft to 10,000 ft **Operating:** Nonoperating:

-1,000 ft to 30,000 ft

#### 1.5.5

# **OPERATING SHOCK**

Maximum permitted shock without incurring nonrecoverable errors: 10 G's <sup>6.7</sup>

#### 1.5.6

#### NONOPERATING SHOCK

Maximum permitted shock without incurring physical damage or degradation in performance: 40 G's<sup>8</sup>.

5. Based on a 32-sector, 256 byte/sector format

6. 11 msec. half-sine wave shock pulse.

7. Input levels at the drive mounting screws, drive mounted in an approved orientation.

8. 11 msec., half sine-wave

# **DC POWER REQUIREMENTS**

The ST212 is listed in accordance with UL 478 and CSA C22.2 (0-M1982), and meets all applicable sections of IEC 380 and VDE 0806/08.81, as tested by TUV-Rheinland, North America.

Power may be applied or removed in any sequence without loss of data or damage to the drive.

| +12 VDC                          |                                            |

|----------------------------------|--------------------------------------------|

| Voltage Tolerance (inc. ripple): | $\pm$ 5% Both seek and non-seek conditions |

| Maximum Current at Power-on:     | 3.2 Amp                                    |

|                                  | 1.0 Amp typical                            |

| +5 VDC:                          |                                            |

| Voltage Tolerance (inc. ripple): | $\pm$ 5% Both seek and non-seek conditions |

| Maximum Current at Power-on:     | 1.2 Amp                                    |

|                                  | 1.0 Amp typical                            |

| POWER:                           | 17 Watts typical                           |

### **INPUT NOISE RIPPLE**

1.6.1

1.6

The maximum permitted ripple is 50 mV (peak-to-peak) on either +12 Volts or +5 Volts.

# **INPUT NOISE FREQUENCY**

1.6.2

20 MHz max. on both the +12 VDC and +5 VDC lines.

Typical AMPS +12Volt DC Profile 4.0 3.5 3.2 3.0 2.5 2.0 1.5 1.0 .5 0.0

FIGURE 1: Start-up Current

0

5

SECONDS

10

15

# FIGURE 2: Mounting Dimensions

# 1.7

# **MOUNTING REQUIREMENTS**

The ST212 may be mounted in the following orientations:

| Horizontal: | Spindle motor down |

|-------------|--------------------|

| Sides:      | Left or right      |

Refer to Figure 2 for mounting dimensions.

The drive should not be tilted front to back, in any position, by more than  $\pm 5^{\circ}$ . For optimum performance the drive should be formatted in the same orientation as it will be mounted in the host system.

A minimum clearance of 0.050 inch should be allowed around the entire perimeter of the drive to allow for cooling airflow and motion during mechanical shock or vibration.

It is recommended that any external shock mounts between the drive and the host frame be designed so that the composite system has a vertical resonant frequency of 25Hz or lower.

#### HANDLING & STATIC-DISCHARGE PRECAUTIONS

After unpacking, and prior to system integration, the drive is exposed to potential handling and ESD hazard.

Do not touch the PCB edge-connectors, board components or the printed circuit cable without observing static-discharge precautions. Handle the drive by the frame only.

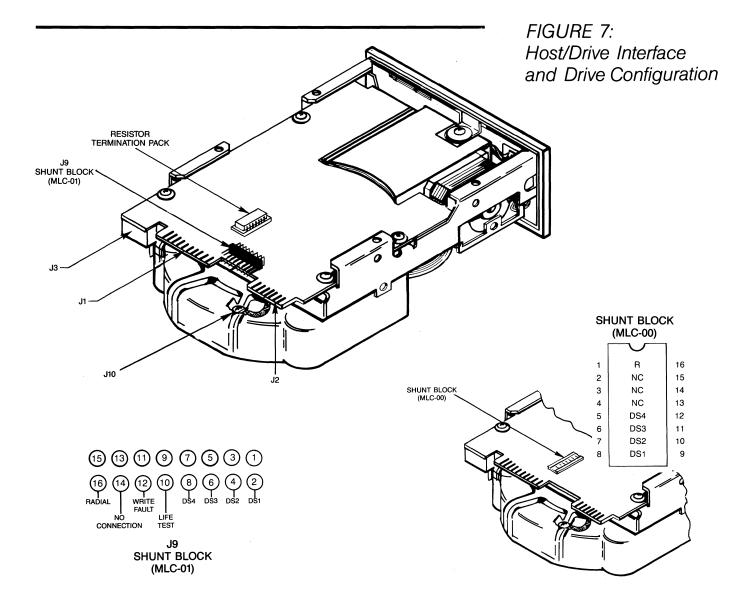

It is strongly recommended that the drive always rest on a padded surface until it is mounted in the host system. This section details the physical specifications of the host/drive interface connectors. Connector dimensions and pin assignments follow under each section. Refer below to *Figure 7* for an overall view of the drive interface connectors.

# 2.1

# CONTROL AND STATUS SIGNALS: PCB EDGE-CONNECTOR J1

Do not touch the PCB edge-connectors, board components or the printed circuit cable without observing static-discharge precautions. Handle the drive by the frame only.

Control and status signals between the host and the drive are transmitted through a 34-pin PCB edge-connector, J1. *Figure 3* indicates connector dimensions and *Table 1* lists the pin assignments. A host/drive interconnection is illustrated in *Figure 4*.

With the drive resting on a padded surface, oriented with the Main Control PCB up and the edge-connectors toward you, J1 is to your left and J2 is on the right. Refer to *Figure 7*.

J1 pins are numbered 1 through 34 with the even pins located on the component side of the PCB. All odd pins are ground. A key slot is provided between pins 4 and 6. Pin 2 is labeled. The recommended mating connector for J1 is AMP ribbon connector part number 88373-3.

# **2.0** ST212 HOST/DRIVE INTERFACE

FIGURE 3: J1 Connector

Dimensions

# TABLE 1: J1 Host/Drive Pin Assignments

| GROUND<br>RTN PIN | SIGNAL<br>PIN                     | SIGNAL NAME     |  |  |  |  |  |  |  |  |

|-------------------|-----------------------------------|-----------------|--|--|--|--|--|--|--|--|

| 1                 | 2                                 | RESERVED        |  |  |  |  |  |  |  |  |

| 3                 | 4                                 | RESERVED        |  |  |  |  |  |  |  |  |

| 5                 | 6                                 | -WRITE GATE     |  |  |  |  |  |  |  |  |

| 7                 | 8†                                | -SEEK COMPLETE  |  |  |  |  |  |  |  |  |

| 9                 | 10                                | -TRACK Ø        |  |  |  |  |  |  |  |  |

| 11                | 12†                               | -WRITE FAULT    |  |  |  |  |  |  |  |  |

| 13                | 14                                | -HEAD SELECT 2º |  |  |  |  |  |  |  |  |

| 15                | 16                                | RESERVED        |  |  |  |  |  |  |  |  |

| 17                | 18                                | -HEAD SELECT 21 |  |  |  |  |  |  |  |  |

| 19                | 20†                               | -INDEX          |  |  |  |  |  |  |  |  |

| 21                | 22†                               | -READY          |  |  |  |  |  |  |  |  |

| 23                | 24                                | -STEP           |  |  |  |  |  |  |  |  |

| 25                | 26                                | -DRIVE SELECT 1 |  |  |  |  |  |  |  |  |

| 27                | 28                                | -DRIVE SELECT 2 |  |  |  |  |  |  |  |  |

| 29                | 30                                | -DRIVE SELECT 3 |  |  |  |  |  |  |  |  |

| 31                | 32                                | -DRIVE SELECT 4 |  |  |  |  |  |  |  |  |

| 33                | 34                                | -DIRECTION IN   |  |  |  |  |  |  |  |  |

| 1:                | †STATUS ENABLED WITH DRIVE SELECT |                 |  |  |  |  |  |  |  |  |

FIGURE 4: Control/Status Signals

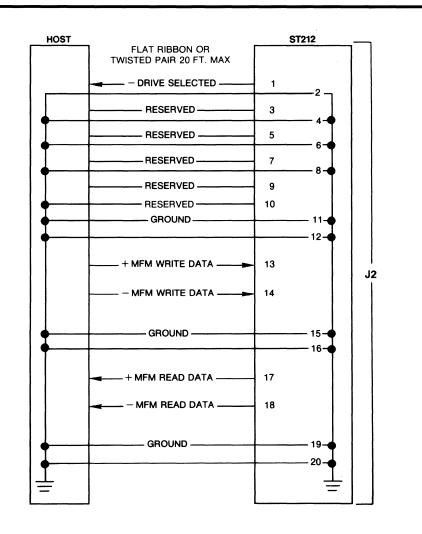

# 2.2 DATA SIGNALS: PCB EDGE-CONNECTOR J2

Do not touch the PCB edge-connectors, board components or the printed circuit cable without observing static-discharge precautions. Handle the drive by the frame only.

Read/Write data signals are received and transmitted over a 20-pin PCB edgeconnector, J2. *Figure 5* indicates connector dimensions and *Table 2* lists the pin assignments. A host/drive interconnection is illustrated in *Figure 6*.

With the drive resting on a padded surface, oriented with the Main Control PCB up and the edge-connectors toward you, J2 is to your right and J1 is on the left. Refer to *Figure 7*.

J2 pins are numbered 1 through 20 with the even pins located on the component side of the PCB. A key slot is provided between pins 4 and 6. Pin 2 is labeled. The recommended mating connector for J2 is AMP ribbon connector, part number 88373-6.

FIGURE 5: J2 Connector Dimensions TABLE 2: J2 Host/Drive Pin Assignments

| ground<br>RTN PIN | SIGNAL<br>PIN | SIGNAL NAME      |

|-------------------|---------------|------------------|

| 2                 | 1             | -DRIVE SELECTED  |

| 4                 | 3             | RESERVED         |

| 6                 | 5             | RESERVED         |

| 8                 | 7             | RESERVED         |

| 10                | 9             | RESERVED         |

| 12                | 11            | GROUND           |

|                   | 13            | + MFM WRITE DATA |

|                   | 14            | - MFM WRITE DATA |

| 16                | 15            | GROUND           |

|                   | 17            | + MFM READ DATA  |

|                   | 18            | - MFM READ DATA  |

| 20                | 19            | GROUND           |

FIGURE 6: Data Signals

9

# **DC POWER: CONNECTOR J3**

Do not touch the PCB edge-connectors, board components or the printed circuit cable without observing static-discharge precautions. Handle the drive by the frame only.

DC power is transmitted from the host to the drive via the power connector, J3. J3 is a 4-pin AMP "Mate-N-Lock" connector, AMP part number 350211-1, mounted on the solder side of the PCB. The recommended mating connector is AMP part number 1-480424-0.

Applications using cable lengths less than five feet, may use #18AWG wire and AMP 61314-4 strip pins. For applications requiring cable lengths greater than five feet, #14AWG wire is recommended using AMP 61117-4 strip pins.

# 2.4

2.3

# FRAME GROUNDING: LUG J10

J10 is an AMP "Faston," part number 61761-2. It is located on the casting between and below the host/drive interface connectors. The recommended mating connector is AMP part number 62187-2. Refer below to *Figure 7*.

# 3.0 DRIVE CONFIGURATION

The ST212 may be configured for specific system requirements. These options are detailed in *Sections 3.1* through 3.5.

# DRIVE CONFIGURATION: SHUNT J9 (MLC-01) 3.1

J9 is a 16-pin right-angle shunt located midway between J1 and J2. Use the provided shorting blocks to enable the DRIVE SELECT lines and any required option. *Figure* 7 illustrates J9 and indicates pin 1.

Earlier drives employed a shunt which required cutting the jumpers to enable DRIVE SELECT. To enable DS1, for example, cut DS2, DS3 and DS4. Refer to *Figure 7*.

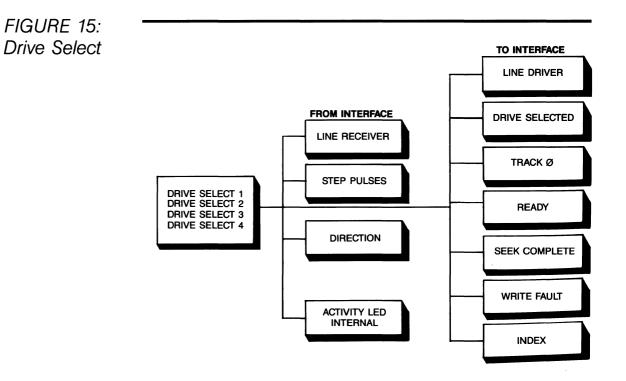

# **DRIVE SELECT**

The DRIVE SELECT line enables the controller to select and address the drive.

Pins 1-2 shorted enable DRIVE SELECT 1 Pins 3-4 shorted enable DRIVE SELECT 2 Pins 5-6 shorted enable DRIVE SELECT 3 Pins 7-8 shorted enable DRIVE SELECT 4

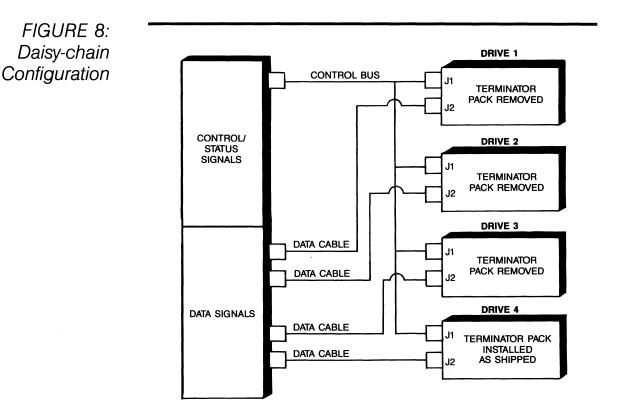

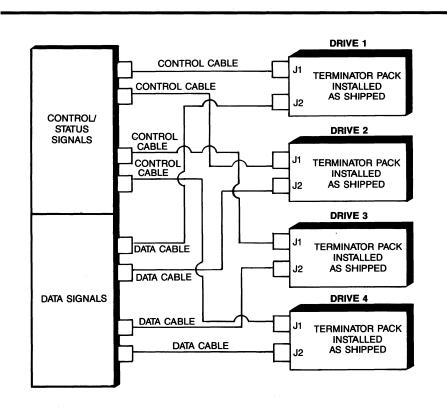

# **DAISY-CHAIN**

3.2.1

3.2

Each drive in the chain must be selected as either DRIVE SELECT 1, 2, 3 or 4, so that only one DRIVE SELECT LINE activates a device. The last drive in the chain must have the 220/330  $\Omega$  resistor termination pack installed on the Main Control PCB.

ST212 PRODUCT MANUAL/Rev. B

The Radial option is enabled by shorting pins 15 and 16 at the J9 shunt. Drives configured to this option are always selected and respond to all control signals issued on the attached control cable. The 220/330  $\Omega$  resistor termination pack must remain installed on each radially-connected drive. *Figure 9* illustrates a host/drive Radial interconnection.

# FIGURE 9: Radial Configuration

The WRITE FAULT signal is internally latched. A selectable option is provided to clear this latch. The standard configuration, with the shorting block removed, resets the WRITE FAULT latch when WRITE GATE is dropped and reasserted after the detected fault has been cleared. With pins 11 and 12 shorted, WRITE FAULT latch is reset when DRIVE SELECT is dropped and reasserted after the detected fault has been cleared.

# 3.5

3.4

# WRITE FAULT

LIFE TEST

This function is used during the manufacturing process and is **not recommend**ed for field use. When pins 9 and 10 are shorted, the stepper motor will continuously seek between Track  $\emptyset$  and the maximum cylinder. When in this mode the drive will ignore control signals sent via the interface.

ST212 PRODUCT MANUAL/Rev. B

# 4.0 CONTROL INPUT SIGNALS

The control signals are of two types: those to be multiplexed in a multiple drive system and those intended to do the multiplexing.

The signals to be multiplexed are WRITE GATE, HEAD SELECT 2°, HEAD SELECT 2', HEAD SELECT 2', HEAD SELECT 2', HEAD SELECT 2', DIRECTION IN, and STEP. These lines are terminated with a removable 220/330  $\Omega$  resistor pack.

The multiplexing signals are DRIVE SELECT 1, DRIVE SELECT 2, DRIVE SELECT 3, and DRIVE SELECT 4. These lines are terminated in a single fixed 220/330  $\Omega$  resistor pack.

Control signals are transmitted across the driver/receiver combination illustrated in *Figure 10*. Control input signals are activated in accordance with the following specifications:

True: 0.0 VDC to 0.4 VDC at I = -48 mAmp max. False: 2.5 VDC to 5.25 VDC at I = +250  $\mu$ Amp (open collector) Termination: 220/330  $\Omega$  resistor pack

# HEAD SELECT 2º, 21, 22, 23

4.1

4.2

These signals allow the selection of each Read/Write head in a binary code sequence. The lines are numbered 0 through 3. HEAD SELECT line  $2^{\circ}$  is the least significant line. When all HEAD SELECT lines are high on the interface, Head 0 is selected.

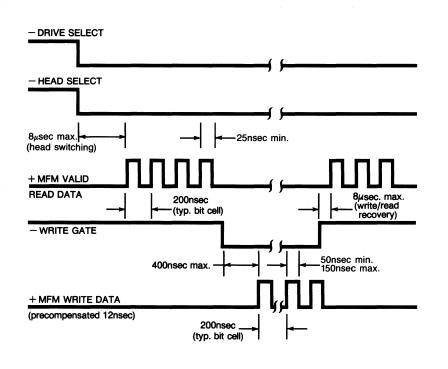

# WRITE GATE

The active state of this signal, or low level, enables data to be written to the disc and inhibits carriage motion if WRITE FAULT is active on the receipt of the first Step pulse. When inactive, or high, this signal enables data to be transferred from the drive and enables Step pulses to move the heads. Heads may not be switched while WRITE GATE is active.

# FIGURE 11: Read/Write Timing

# 4.3

STEP

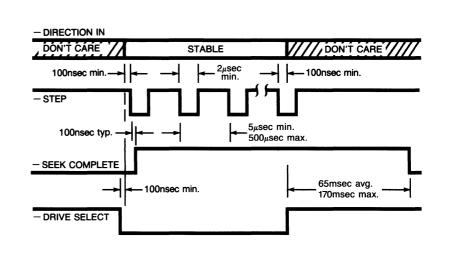

The STEP signal is a 2  $\mu$ sec. minimum width pulse that initiates Read/Write head motion. The number of pulses issued determines distance traveled. The rate of Step pulses determines the access method.

If the period between pulses is from 5  $\mu$ sec. to 500  $\mu$ sec., the access method will be Buffered-Seek. Slow-Step is employed if the period between pulses is greater than or equal to 3 msec.

DIRECTION IN must be stable 100 nsec. before the leading edge of the first step pulse and remain stable for 100 nsec. after the last pulse in a string of Step pulses. Step pulses issued between 500  $\mu$ sec. and 3 msec. may be lost.

If excessive Step pulses are issued which would cause a seek inward beyond cylinder 306 or outward beyond Cylinder Zero, the drive will enter the Auto-Truncation mode. Refer to Section 4.3.4.

### 4.3.1

### **BUFFERED SEEK**

To minimize access time, pulses may be issued at an accelerated rate and buffered in a counter. Initiation of a seek starts immediately after the first pulse is received. Head motion occurs during pulse accumulation, and the seek is completed following receipt of all pulses. FIGURE 12: General Step Timing

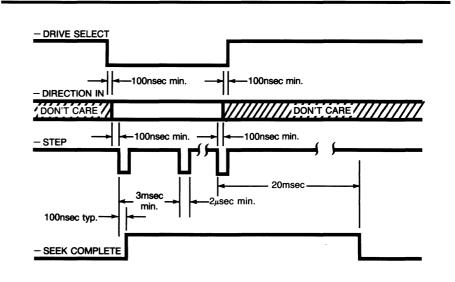

# SLOW-STEP (Single-Track)

4.3.2

In Slow-Step, the stepper motor is settled and SEEK COMPLETE is issued 20 msec. max. after the leading edge of the last Step pulse.

FIGURE 13: Slow-step Timing

# 4.3.3

#### **AUTO-TRUNCATION**

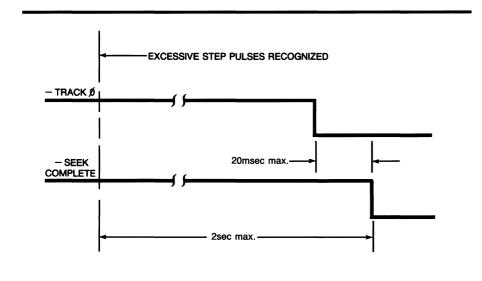

The drive will enter the Auto-Truncation mode if the controller issues an excessive number of Step pulses, which would place the Read/Write heads outward beyond Track  $\emptyset$  or inward beyond cylinder 306.

With the Auto-Truncation mode active, the drive disallows additional pulses, takes control of the stepper motor and recalibrates the heads to Track  $\emptyset$ .

CAUTION: If the controller is still issuing Slow-Step pulses after the drive issues SEEK COMPLETE from Auto-Truncation mode, the ST212 will either reenter Auto-Truncation mode with DIRECTION IN false, or step the remaining cylinders with DIRECTION IN true.

# FIGURE 14: Auto-truncation Timing

# 4.4

# DIRECTION IN

DIRECTION IN defines the direction the Read/Write heads will move when the STEP line is pulsed. With DIRECTION IN true, each pulse causes the heads to move one cylinder inward toward the spindle. With DIRECTION IN false, each pulse causes the heads to move one cylinder outward toward Track  $\emptyset$ .

# 4.5

# DRIVE SELECT

The DRIVE SELECT line is activated by the controller to select and address the drive. Refer to Section 3.0.

The control output signals are gated to the interface when selected. They are: DRIVE SELECTED, INDEX, TRACK Ø, READY, SEEK COMPLETE and WRITE FAULT.

# 5.0 CONTROL OUTPUT SIGNALS

# 5.1

# DRIVE SELECTED

DRIVE SELECTED is a status signal transmitted over J2, which informs the host system of the selection status of the drive. The signal is driven by a TTL open collector, as illustrated in *Figure 10*. The signal goes low (true) on the interface only when the device is correctly configured (see *Sections 3.1-3.5*) and the DRIVE SELECT line is activated by the host system.

# 5.2

# INDEX

This signal is provided by the drive once each revolution to indicate the beginning of a track. The nominal period is 16.67 msec., with a typical pulse width of 1.5 msec. Normally this signal is at a high level and the transition to low indicates INDEX. Only the transition from high to low, or the leading edge, is valid.

# 5.3

# TRACK Ø

This signal is low (true) only when the Read/Write heads are positioned at Cylinder Zero.

Track  $\emptyset$  is the only cylinder that provides interface recognition. The drive is designed to recalibrate to Track  $\emptyset$  during power-on and Auto-Truncation operations.

Track  $\emptyset$  may also be accessed via conventional Buffered-Seek and Slow-Step modes. After Track  $\emptyset$  is true, no actions may be taken by the controller until SEEK COMPLETE is also true.

# 5.4

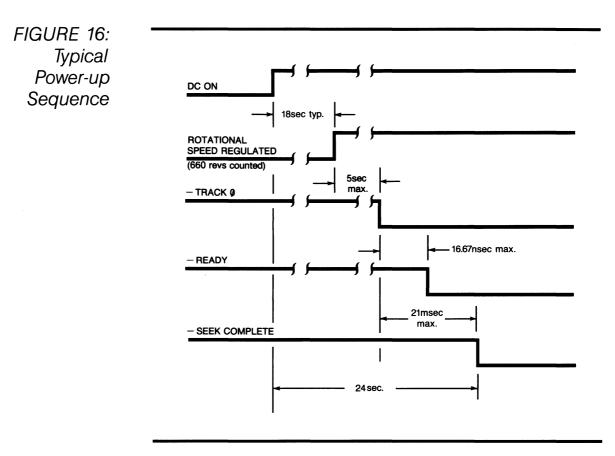

# READY

This signal, when true together with SEEK COMPLETE, indicates that the drive is ready to Read, Write or Step and that all control input signals are valid. When this line is high, all reading, writing and stepping are inhibited. The typical time after power-on for READY to be true is 24 seconds.

**READY** remains false during the power-up sequence until:

- 1. The recalibration to Track  $\emptyset$  is complete

- 2. Spindle speed is stable within  $\pm$  1% of nominal

- 3. Drive initialization routines are complete

- 4. DC voltages are within tolerance.

# SEEK COMPLETE

This signal goes low on the interface when the Read/Write heads have settled on track upon completion of a seek. Seeking, reading or writing should not be attempted when SEEK COMPLETE is false. SEEK COMPLETE goes false in the following four cases:

- 1. When a recalibration sequence is initiated (by drive logic) at power-on.

- 2. 100 nsec. max. after the leading edge of a Step pulse.

- 3. If either +5 Volts or +12 Volts are detected as unsafe.

# WRITE FAULT

This signal indicates that a condition exits at the drive which, if not corrected, may cause an incorrect write operation. WRITE FAULT will remain true until the condition causing the fault is corrected. The controller should edge detect this signal.

## WRITE FAULT SIGNAL GENERATION

With DRIVE SELECT active, and one of the following conditions true, the WRITE FAULT signal will be issued to the interface and Write Current will be inhibited.

- 1. Write Gate true with no Write Current flowing to the head

- 2. Write Current to the heads with no Write Gate

5.5

5.6

5.6.1

### 5.6.1.1

# WRITE CURRENT INTERRUPTION

Any of the following conditions will cause Write Current to be inhibited when Write Gate is true:

- 1. Multiple heads selected

- 2. No head selected

- 3. SEEK COMPLETE false

- 4. READY false

- 5. DC Voltages out of tolerance

- 6. A Step pulse is received

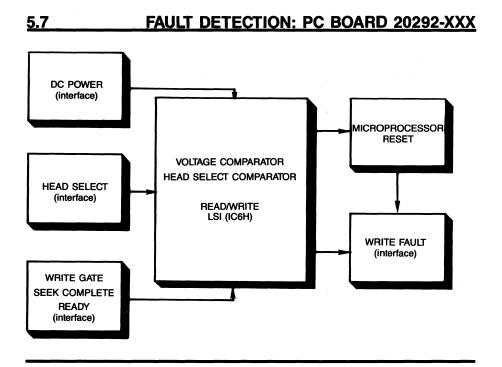

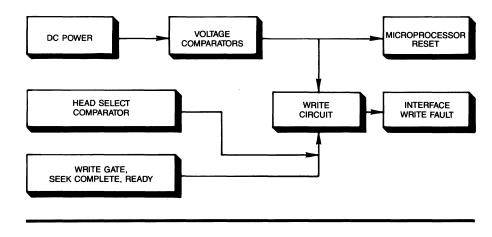

FIGURE 17: Fault Detection PC Board 20292-XXX

# 5.7.1

# VOLTAGE AND HEAD SELECT COMPARATOR

The Read/Write LSI (IC 6H) continually monitors the +5 and +12 Volt lines for a low voltage condition. If + Volts > 15% low or +12 is > 20% low, the DC-unsafe signal is activated (IC 6H, pin 25) causing:

- 1. Write current to be disabled

- 2. The microprocessor is reset

- 3. The fault line is activated (IC 6H, pin 24)

- 4. The heads are deselected

If multiple heads are selected, the Read/Write LSI will disable the write circuitry and send a Write Fault to the interface (IC 6H, pin 24).

# 5.7.2

# WRITE FAULT RESET

A selectable option is provided to clear a Write Fault. The standard configuration resets the Write Fault latch when Write Gate is dropped and reasserted (after the detected fault has been cleared). Shorting pins 11 and 12 at connector J9 causes the Write Fault latch to be reset when DRIVE SELECT is dropped and reasserted after the detected fault has been cleared.

# FAULT DETECTION: PC BOARD 20243-XXX

FIGURE 18: Fault Detection PC Board 20243-XXX

# VOLTAGE COMPARATOR

Comparators at IC 7G continually monitor both the +5 and +12 Volt lines to detect a low voltage condition. If +5V is > 15% low or +12V is > 20% low, Write current will be disabled, the microprocessor reset, the fault line activated and the heads deselected.

## HEAD SELECT COMPARATORS

When a single head is selected (normal operation), IC 7G (pins 1 and 2) will be high. If more than one head is selected, the voltage will increase at 7G (pin 4) forcing its output low. An attempt to write with no head selected will decrease the voltage at 7G (pin 4) forcing its output low. A low on either comparator will disable the Write circuitry and send a Write Fault to the interface.

5.8.1

5.8.2

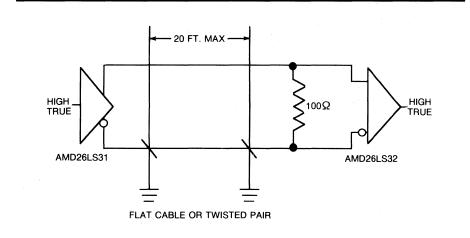

Two pairs of balanced signals are employed for data transfer: MFM WRITE DATA and MFM READ DATA. Data transfer lines between the host system and the drive are differential in nature and may not be multiplexed. Refer to *Table 2* for data transfer pin assignments and *Figure 6* for a host/drive interconection example.

FIGURE 19: Data Signal Driver/Receiver Combination

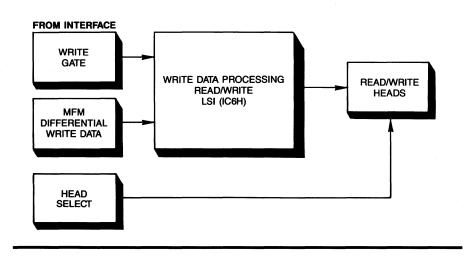

# WRITE OPERATION: PC BOARD 20292-XXX

# FIGURE 20: Write Operation PC Board 20292-XXX

In order to Write, the following conditions must be satisfied:

WRITE FAULT inactive SEEK COMPLETE active READY active DRIVE SELECT active Write Gate active

# 6.1.1

6.1

#### MFM WRITE DATA

WRITE DATA is transmitted by a differential pair which defines the transitions to be written on the disc. The +MFM WRITE DATA line going more positive than the -MFM WRITE DATA line is the active transition. This signal must be driven to an inactive state when in READ mode.

#### WRITE GATE

A write sequence is initiated when Write Gate is activated which causes the Read/Write LSI (IC 6H, pin 26) to apply +12 Volts to the center tap of the selected head. Concurrently, data is sent to the Read/Write LSI, pins 15 and 16.

# WRITE DATA PROCESSING

Differential MFM write data is received from the controller by the Read/Write LSI and changed to digital pulse data. Depending on whether plus or minus data is to be written, the Read/Write LSI (which controls the amount of current to be written) activates either pin 7 or 8 of the preamp LSI (IC 3H). When writing to the inner heads (2 and 3), Write current is reduced to lessen the problems of pulse crowding.

#### PRECOMPENSATION

Precompensation is recommended on cylinders 128 through 306 in order to achieve optimum performance. The optimum amount of precompensation is 12 nsec. for both early and late bits. *Table 3* below indicates the bit patterns and the direction to be compensated. An X denotes a "don't care" state.

TABLE 3: Precompensation Pattern

| PRE\ | lous | SENDING | NEXT | TIMING            |

|------|------|---------|------|-------------------|

| х    | 0    | 1       | 1    | WRITE DATA LATE   |

| Х    | 1    | 1 1     | 0    | WRITE DATA EARLY  |

| 1    | 0    | 0       | 0    | WRITE CLOCK LATE  |

| 0    | 0    | 0       | 1    | WRITE CLOCK EARLY |

ALL OTHER PATTERNS NOMINAL

6.1.3

6.1.4

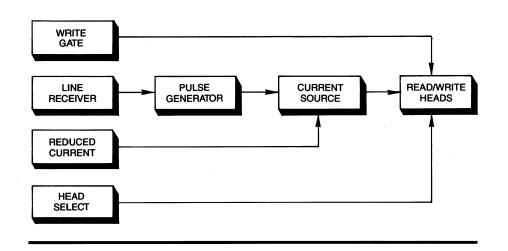

# WRITE OPERATION: PC BOARD 20243-XXX

FIGURE 21: Write Operation PC Board 20243-XXX

# 6.2.1

#### WRITE GATE

A write sequence is initiated when Write Gate is activated and applies +12 Volts to the center tap of the selected head. At the same time, data is sent to the line receiver 7L.

#### 6.2.2

#### LINE RECEIVER

Differential Write Data (precompensated MFM) is received from the controller and changed to single line. It is then fed into the pulse generator (7K) which changes square wave data to pulse data. Depending on whether plus or minus data is to be written, either pin 7 or pin 9 of 7H is activated. The amount of current to be written is primarily established by R53. When writing to the inner heads, 2 and 3, Write current is reduced by adding R52 in parallel which reduces the problems of pulse crowding.

# FORMATTING

Figure 22 illustrates a suggested format example.

| GAP 1<br>16 X 4E         693 X 4<br>(NOMINA           FIELD         571 BYTES TOTAL           FIELD         GAP 2           DATA FIELD         GAP 3           ID FIELD         GAP 2           DATA FIELD         GAP 3           INTER RECORD GAP           INTER RECORD GAP           INTER RECORD GAP           NUMBER<br>I 3 1 1 2 1 1 2 3 13 1 1           SYNC ADDR CYUNDER HEAD SCTR CRC TURNON COLSPAN           DATA SYNC SYNC ADDR DATA SYNC SYNC GADR DATA           DATA FIELD           DATA SYNC CRC TURNOR           NUMBER TO ADDR CYUNDER HEAD SCTR CRC TURNOR CRC TURNOR           NUMBER TO ADDR NO           DATA SYNC SYNC ADDR DATA           DATA           DATA           CRC TURNOR CRC TURNOR           TOTA SYNC SYNC ADDR MARK           DATA           DATA           TOTA SYNC TURNOR           TOTA SYNC TURNOR           TOTA SYNC TURNOR           TOTA SYNC TURNOR         TOTA SY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                |               |               |                   |             |             |     | 0       |      |      |               |       |         |                    |          | -                         |                                     |                           |                           |                           |                           |                          |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|---------------|---------------|-------------------|-------------|-------------|-----|---------|------|------|---------------|-------|---------|--------------------|----------|---------------------------|-------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------|--|--|

| 512-Byte/Sector     1     13     ID VP0 LOCK     A field of all scrope dicek to not the VD of the D       Format Example     2     1     SYNC BYTE     "A" He with a dropped clock to not try the controller that data follows.       3     1     ADDRESS     "FF" Hes defining that ID field data follows.       4     2     CYLINDER     A numerical value in Hes defining the ND field data follows.       5     1     HEAD     A numerical value in Hes defining the rotation.       6     1     SECTOR     A numerical value in Hes defining the rotation.       7     2     CRC     Chick and the rotation.       7     2     CRC     Chick and the rotation.       7     2     CRC     Chick and the rotation.       8     3     WRITE     Zeros writen during format to isolate and the rotation.       9     13     DATA SYNC     Yfe dottol fail and the rotation.       10     1     SYNC BYTE     "Yfe write shife and the rotation.       11     1     ADDRESS     Fifther defining that user data follows.       12     512     DATA     This area available for user to sync the YPO for the data field normation used to verify the value in the defining the value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                | F             |               |                   |             |             |     |         |      |      |               |       |         |                    |          | FIE                       | LD DI                               | ESCR                      | RIPTIO                    | N                         |                           |                          |  |  |

| Format Example     2     1     SYNC BYTE     "A" He with a dropped clock to not fy the controller that data follows.       3     1     ADDRESS     "FE" Hes defining that ID field data follows.       4     2     CXLINDER     A numerical value in Hes defining the the defining the head deleted.       5     1     NLMBER     A numerical value in Hes defining the head deleted.       6     1     SECTOR     A numerical value in Hes defining the head deleted.       7     2     CRC     Cyclic Redundancy       7     2     CRC     Cyclic Redundancy       8     3     WRITE     Zaros writen during format to isolate events of the rotation.       8     3     WRITE     Zaros writen during format to isolate events of the rotation.       9     13     DATA SYNC     A field of all zeros to sync the VPO for the data field number of the d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | 5              | 12-           |               |                   |             |             |     |         | 1    |      | 13            |       | ID V    | FO L               | ОСК      |                           |                                     | all z                     | eros to                   | sync                      | the                       | VFO for                  |  |  |

| MARk     follows.       4     2     CVLINDER     A numerical value in Hex defining the detent position of the actuator.       5     1     HEAD     A numerical value in Hex defining the bead selected.       6     1     SECTOR     A numerical value in Hex defining the bead selected.       7     2     CRC     Cyclic Redundancy       7     2     CRC     Cyclic Redundancy       8     3     WRITE     Zeros write quiter format to isolate the validity of the ID field information used to verify the validity of the ID field information used to verify the validity of fold anumber and allows the 13 bytes required for Data VFO lock.       9     13     DATA SYNC       9     13     DATA SYNC       10     1     SYNC BYTE       11     1     ADDRESS       12     512     DATA       13     2     CRC       14     3     WRITE       15     15     INTER R       RECORD GAP     A field of all zeros writen data field information used to verify the valid of th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                |               |               |                   |             |             |     |         | 2    |      | 1             |       | SYN     | C BY               | ГЕ       |                           |                                     |                           |                           |                           |                           |                          |  |  |

| S     1     HEAD<br>NUMBER     A numerical value in Hex defining the<br>head selected.       6     1     SECTOR     A numerical value in Hex defining the<br>head selected.       7     2     CRC     Cyclic Redundancy<br>Cyclic Redundancy<br>Cycli Redundancy<br>Cycli Redundancy<br>Cyclic Redundancy<br>Cycli Redund                                                                                                                                                                                                       |                |                |               |               |                   |             |             |     |         | 3    |      | 1             |       |         |                    | 5        |                           |                                     | defi                      | ning th                   | at ID                     | fiel                      | d data                   |  |  |

| NUMBER     head selected.       6     1     SECTOR     A numerical value in Hex defining the sector for this section of the rotation.       7     2     CRC     Cyclic Redundancy       7     2     CRC     Cyclic Redundancy       8     3     WRITE     Zeros writen during format to isolate the write splic created. This field assures valid reading of field number of Data SYNC       9     13     DATA SYNC     A field of all zeros to sync the VFO for Data SYNC BYTE       10     1     SYNC BYTE     "A" He write a dropped clock to not fy the controller that data follows.       11     1     ADDRESS     "FB" Hex defining that user data follows.       12     512     DATA     This area available for user data.       13     2     CRC     Cyclic Redundancy       14     3     WRITE     Zeros writen during update to isolate to isolate and allows the 15 field assures valid reading of field number of VFO lock for the ID field of the next splic created. This field assures valid reading of redundancy       14     3     WRITE       15     15     INTER RECORD GAP       16     1     2     A field of all zeros which acts as a splic field number of VFO lock for the ID field of the next splic created. This field assures valid reading of field number of VFO lock for the ID field of the next splic created. This field assures valid reading of redundancy Chield assures valid reading of redundancy Chield assu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                |               |               |                   |             |             |     |         | 4    |      | 2             |       |         |                    |          |                           |                                     |                           |                           |                           |                           | ing the                  |  |  |

| NUMBER         sector for this section of the rotation.           7         2         CRC         Ordic Redundancy<br>Check information used to verify the<br>read.           8         3         WRITE<br>TURN-ON<br>GAP         Turnet to isolat<br>the write splic created. This field<br>assures valid reading of field number i<br>and allows this data field.           9         13         DATA SYNC         A field of all zeros to sync the VFO f<br>VFO LOCK           10         1         SYNC BYTE         "A field of all zeros to sync the VFO f<br>the controller that data follows.           11         1         ADDRESS         "RF" He defining that user data<br>follows.           12         512         DATA         This area available for user data.           13         2         CRC         Ordic read.           14         3         WRITE<br>GAP         To all zeros to allow for<br>field number           15         15         INTER<br>RECORD GAP         A field of all zeros which acts as a<br>buffer between sectors to allow for<br>speed variation.           15         15         INTER<br>RECORD GAP         A field of all zeros which acts as a<br>buffer between sectors to allow for<br>speed variation.           16         1         2         3         6         7         9         10         11         12         13         1           10         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |                |               |               |                   |             |             |     |         | 5    |      | 1             |       |         |                    |          |                           |                                     |                           | lue in                    | Hex o                     | lefin                     | ing the                  |  |  |

| 8       3       WRITE<br>TURN-ON<br>GAP       Cress write the D field information is loaler<br>the write splic created. This field<br>assues valid reading of field number<br>the write splic created. This field<br>assues valid reading of field number<br>the write splic created. This field<br>assues valid reading of field number<br>the write splic created. This field<br>assues valid reading of field number<br>the write splic created. This field<br>assues valid reading of field number<br>the write splic created. This field<br>assues valid reading of field number<br>the write splic created. This field<br>assues valid reading of field number<br>the write splic created. This field<br>assues valid reading of field informa-<br>tion just read.         10       1       SYNC BYTE<br>VFO LOCK       A field of all zeros to sync the VFO f<br>the data field.         11       1       ADDRESS<br>MARK       "R8" He defining that user data<br>follows.         12       512       DATA<br>13       2       CRC         14       3       WRITE<br>TURN-OFF<br>GAP       Zeros written during update to isolate<br>assues valid reading of field number<br>and allows the 13 bytes required for<br>VFO lock for the ID field of the next<br>sector.         15       15       INTER<br>RECORD GAP       A field of all zeros which acts as a<br>buffer between sectors to allow for<br>speed variation.         14       5       6       7       8       9       10       11       12       13       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                |               |               |                   |             |             |     |         | 6    |      | 1             |       |         |                    |          |                           |                                     |                           |                           |                           |                           |                          |  |  |

| TURN-ON<br>GAP     the write splice created. This field<br>assures valid reading of field number<br>Data VPO lock.       9     13     DATA SYNC<br>VFO LOCK     A field of all zeros to sync the VFO f<br>the data field.       10     1     SYNC BYTE     "AI" Hex with a dropped clock to not<br>fy the controller that data follows.       11     1     ADDRESS     "AI" Hex with a dropped clock to not<br>fy the controller that data follows.       12     512     DATA     This area available for user data.       13     2     CRC     Cyclic Redundancy<br>Check information used to verify the<br>validity of the user data field informa<br>too just read.       14     3     WRITE<br>TURN-OFF     Zeros writen during update to isolate<br>the write splice created. This field<br>assures valid reading of field number<br>and allows the 13 bytes required for<br>VFO lock for the ID field of the next<br>sector.       15     15     INTER<br>RECORD GAP     A field of all zeros which acts as a<br>buffer between sectors to allow for<br>sector.       16     1     2     3     4     5     6     7     8     9     10     11     12     13     14     15       INTER<br>RECORD GAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                |               |               |                   |             |             |     |         | 7    |      | 2             |       | CRC     |                    |          | Che<br>valie              | ck inf<br>dity of                   | orma                      | tion us                   |                           |                           |                          |  |  |

| VFO LOCK     the data field.       10     1     SYNC BYTE     "A!" Hex with a dropped clock to noil for the data follows.       11     1     ADDRESS     "F8" Hex defining that user data follows.       12     512     DATA     This area available for user data.       13     2     CRC     Cyclic Redundancy<br>Check information used to verify the validity of the user data field information just read.       14     3     WRITE<br>TURN-OFF     Zeros written during update to isolate the write spic created. This field assures valid reading of field number       15     15     INTER<br>RECORD GAP     A field of all zeros which acts as a buffer between sectors to allow for speed variation.       INDEX     0     1     2     3     4     5     6     7     8     9     10     11     12     13     14     15       INDEX     0     1     2     3     4     5     6     7     8     9     10     11     12     13     14     15       INDEX     0     1     2     3     4     5     6     7     8     9     10     11     12     13     14     15       INDEX     0     1     2     3     4     5     6     7     8     9     10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                |               |               |                   |             |             |     |         | 8    |      | 3             |       | TUR     | N-ON               | 1        | the<br>assu<br>and        | write s<br>res va<br>allows         | splice<br>lid re<br>s the | create<br>ading<br>13 byt | d. Th<br>of fiel          | is fie<br>ld πι           | eld<br>1mber 7           |  |  |

| 11     1     ADDRESS<br>MARK     "F8" Hex defining that user data<br>follows.       12     512     DATA     This area available for user data.       13     2     CRC     Cyclic Redundancy<br>Check information used to verify the<br>validity of the user data field informa-<br>tion just read.       14     3     WRITE<br>TURN-OFF<br>GAP     Zeros writen during update to isolate<br>the write splice created. This field<br>assures valid reading of field number<br>and allows the 13 bytes required for<br>VFO lock for the ID field of the next<br>sector.       15     15     INTER<br>RECORD GAP     A field of all zeros which acts as a<br>buffer between sectors to allow for<br>speed variation.       INDEX     0     1     2     3     4     5     6     7     8     9     10     11     12     13     14     15       INDEX     0     1     2     3     4     5     6     7     8     9     10     11     12     13     14     15       INDEX     0     1     2     3     4     5     6     7     8     9     10     11     12     13     14     15       INDEX     0     1     2     3     4     5     6     7     8     9     10     11     12     13     14     15       INDEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                |               |               |                   |             |             |     |         | 9    |      | 13            |       |         |                    |          |                           |                                     |                           | eros to                   | sync                      | the                       | VFO for                  |  |  |

| 11       1       ADDRESS<br>MARK       "F8" Hex defining that user data<br>follows.         12       512       DATA       This area available for user data.         13       2       CRC       Cyclic Redundancy<br>Check information used to verify the<br>validity of the user data field informa<br>tion just read.         14       3       WRITE<br>TURN-OFF<br>GAP       Zeros written during update to isolate<br>the write splic created. This field<br>assures valid reading of field number<br>and allows the 13 bytes required for<br>VFO lock for the ID field of the next<br>sector.         15       15       INTER<br>RECORD GAP       A field of all zeros which acts as a<br>buffer between sectors to allow for<br>speed variation.         INDEX       0       1       2       3       4       5       6       7       8       9       10       11       12       13       14       15         INDEX       0       1       2       3       4       5       6       7       8       9       10       11       12       13       14       15         INDEX       0       1       2       3       4       5       6       7       8       9       10       11       12       13       14       15         TYPE       0       1       2       3       13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                |               |               |                   |             |             |     |         |      |      | 10            |       | 1       |                    | SYN      | C BY                      | TE                                  |                           |                           |                           |                           |                          |  |  |

| 13       2       CRC       Cyclic Redundancy<br>Check information used to verify the<br>validity of the user data field informa<br>tion just read.         14       3       WRITE<br>TURN-OFF<br>GAP       Zeros written during update to isolate<br>the write splice created. This field<br>assures valid reading of field number<br>and allows the 13 bytes required for<br>VFO lock for the ID field of the next<br>sector.         15       15       INTER<br>RECORD GAP       A field of all zeros which acts as a<br>buffer between sectors to allow for<br>speed variation.         Import       0       1       2       3       4       5       6       7       8       9       10       11       12       13       14       15         Import       GAP 1       5/1 BYTES TOTAL       DATA FIELD       Out 7       METERECORD GAP         FIELD       GAP 2       DATA FIELD       DATA       DATA       Out 7       METERECORD GAP         WETER       13       1       1       2       3       13       1       1       5/2       2       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |                |               |               |                   |             |             | 11  |         | 1    |      |               |       | 5       |                    |          | defi                      | ning th                             | at use                    | er da                     | ita                       |                           |                          |  |  |