# Quantum

### Quantum Fireball CR 4.3/6.4/8.4/12.7 GB AT Product Manual

Preliminary

## Quantum Fireball CR 4.3/6.4/8.4/12.7 GB AT Product Manual

**Preliminary**

November, 1998 81-119270-01 Quantum reserves the right to make changes and improvements to its products, without incurring any obligation to incorporate such changes or improvements into units previously sold or shipped.

You can request Quantum publications from your Quantum Sales Representative or order them directly from Quantum.

Publication Number: 81-119270-01

#### UL/CSA/TUV/CE

UL standard 1950 recognition granted under File No. E78016

CSA standard C22.2 No. 950 certification granted under File No. LR49896

TUV Rheinland EN 60 950 granted under File No. R 9677196

Tested to FCC Rules for Radiated and Conducted Emissions, Part 15, Sub Part J, for Class-B Equipment.

#### SERVICE CENTERS

Quantum Service Center 715 Sycamore Avenue Milpitas, California 95035 Phone: (408) 894-4000 Fax: (408) 894-3218 http://www.quantum.com Quantum Asia-Pacific Pte. Ltd. 50 Tagore Lane #b1-04 Singapore, 2678 Phone: (65) 450-9333 Fax: (65) 452-2544 Quantum Customer Service Group Quantum Ireland Ltd. Finnabair Industrial Park Dundalk County Louth, Ireland Tel: (353) 42-55350 Fax: (353) 45-55355

#### PATENTS

These products are covered by or licensed under one or more of the following U.S. Patents: 4,419,701; 4, 538,193 4,625,109; 4,639,798; 4,647,769; 4,647,997; 4,661,696; 4,669,004; 4,675,652; 4,703,176; 4,730,321; 4,772,974; 4,783,705; 4,819,153; 4,882,671; 4,920,442; 4,920,434; 4,982,296; 5,005,089; 5,027,241; 5,031,061; 5,084,791; 5,119,254; 5,160,865; 5,170,229; 5,177,771; Other U.S. and Foreign Patents Pending.

<sup>®</sup> 1998 Quantum Corporation. All rights reserved. Printed in U.S.A.

Quantum, the Quantum logo, and AIRLOCK are trademarks of Quantum Corporation, registered in the U.S.A. and other countries. Capacity for the extraordinary, Quantum Fireball CR, AutoTransfer, AutoRead, AutoWrite, DisCache, DiskWare, Defect Free Interface, and WriteCache are trademarks of Quantum Corporation. All other brand names of trademarks are the property of their manufacturers.

This product or document is protected by copyright and distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Quantum and its licensors, if any.

**RESTRICTED RIGHTS LEGEND:** Use, duplication, or disclosure by the government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 and FAR 52.227-19.

THIS PUBLICATION IS PROVIDED "AS IS' WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT.

## Table of Contents

| Chapter 1                                   |     |

|---------------------------------------------|-----|

| ABOUT THIS MANUAL                           |     |

| AUDIENCE DEFINITION                         |     |

| MANUAL ORGANIZATION                         |     |

| TERMINOLOGY AND CONVENTIONS                 |     |

| REFERENCES                                  |     |

|                                             |     |

| Chapter 2                                   |     |

| GENERAL DESCRIPTION                         |     |

| PRODUCT OVERVIEW                            | 2 1 |

| KEY FEATURES                                |     |

|                                             |     |

| STANDARDS AND REGULATIONS                   |     |

| HARDWARE REQUIREMENTS                       |     |

|                                             |     |

| Chapter 3                                   |     |

| INSTALLATION                                |     |

| SPACE REQUIREMENTS                          |     |

| UNPACKING INSTRUCTIONS                      |     |

| HARDWARE OPTIONS                            |     |

| Cable Select (CS) Jumper                    |     |

| Drive Select (DS) Jumper                    |     |

| Jumper Parking (PK) Position                |     |

| Master Jumper configuration                 |     |

| Reserved Position                           |     |

| ATA BUS ADAPTER                             |     |

| 40-Pin ATA Bus Connector                    |     |

| Adapter Board                               |     |

| MOUNTING                                    |     |

| Orientation                                 |     |

| Clearance                                   |     |

| Ventilation                                 |     |

| COMBINATION CONNECTOR (J1)                  |     |

| DC Power (J1, Section A)                    |     |

| External Drive Activity LED                 |     |

| ATA Bus Interface Connector (J1, Section C) |     |

| FOR SYSTEMS WITH A MOTHERBOARD ATA ADAPTER  |     |

| FOR SYSTEMS WITH AN ATA ADAPTER BOARD       |     |

| Adapter Board Installation                  |     |

| TECHNIQUES IN DRIVE CONFIGURATION           |     |

| The 528-Megabytes Barrier    | 3-15 |

|------------------------------|------|

| The 8.4-Gigabytes Barrier    |      |

| Operating system limitations |      |

| SYSTEM STARTUP AND OPERATION | 3-17 |

#### Chapter 4

| SPECIFICATIONS                 |  |

|--------------------------------|--|

| SPECIFICATION SUMMARY          |  |

| FORMATTED CAPACITY             |  |

| DATA TRANSFER RATES            |  |

| TIMING SPECIFICATIONS          |  |

| POWER                          |  |

| Power Sequencing               |  |

| Power Reset Limits             |  |

|                                |  |

| ACOUSTICS                      |  |

|                                |  |

|                                |  |

| SHOCK AND VIBRATION            |  |

| HANDLING the DRIVE             |  |

| RELIABILITY                    |  |

| ELECTROMAGNETIC SUSCEPTIBILITY |  |

| EMITTED VIBRATION              |  |

| DISK ERRORS                    |  |

|                                |  |

## Chapter 5 BASIC PRINCIPLES OF OPERATION

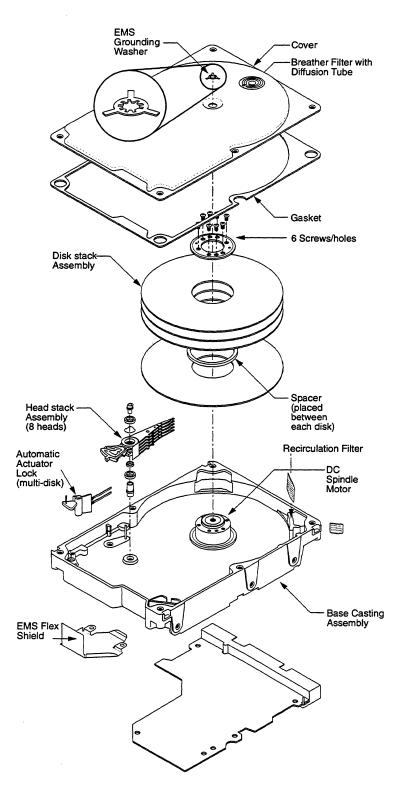

| Quantum Fireball CR DRIVE MECHANISM                                  | 5-1  |

|----------------------------------------------------------------------|------|

| Base Casting Assembly                                                | 5-3  |

| DC Motor Assembly                                                    | 5-3  |

| Disk Stack Assemblies                                                |      |

| Headstack Assembly                                                   | 5-4  |

| Rotary Positioner Assembly                                           |      |

| Automatic Actuator Lock                                              |      |

| Air Filtration                                                       |      |

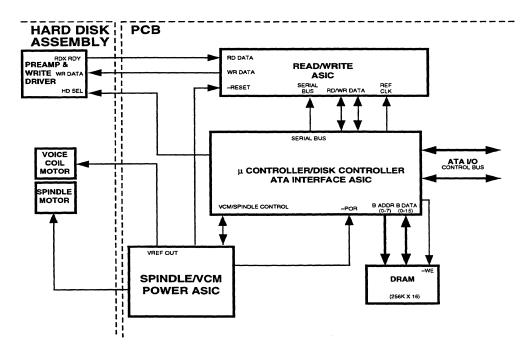

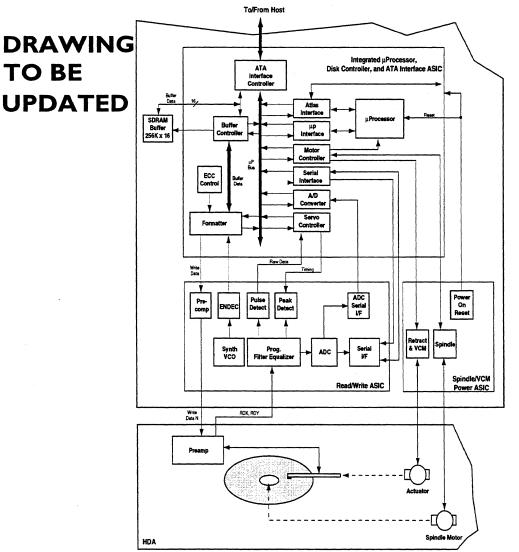

| DRIVE ELECTRONICS                                                    |      |

| Integrated µProcessor, Disk Controller and ATA Interface Electronics |      |

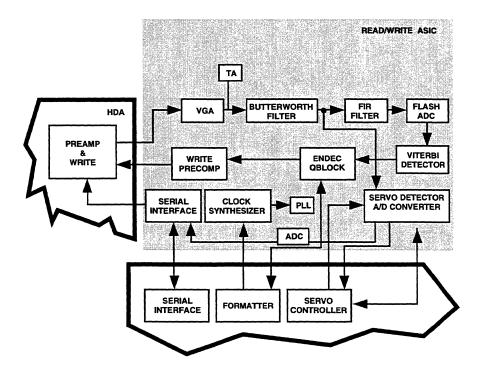

| Read/Write ASIC                                                      |      |

| PreAmplifier and Write Driver                                        | 5-10 |

| FIRMWARE FEATURES                                                    |      |

| Disk Caching                                                         |      |

| Head and Cylinder Skewing                                            |      |

| Error Detection and Correction                                       |      |

| Defect Management                                                    |      |

|                                                                      |      |

| Chapter 6                          |  |

|------------------------------------|--|

| ATA BUS INTERFACE AND ATA COMMANDS |  |

| INTRODUCTION                       |  |

| SOFTWARE INTERFACE                 |  |

| MECHANICAL DESCRIPTION             |  |

| Drive Cable and Connector          |  |

| ELECTRICAL INTERFACE               |  |

| ATA Bus Interface                  |  |

| Host Interface Timing              |  |

| REGISTER ADDRESS DECODING          |  |

| REGISTER DESCRIPTIONS              |  |

| Control Block Registers            |  |

| Command Block Registers            |  |

| COMMAND DESCRIPTIONS               |  |

| Recalibrate 1xh                    |  |

| Read Sectors 20h                   |  |

| Write Sector 30h                   |  |

| Read Verify Sectors 40h            |  |

| Seek 7xh                           |  |

| Execute Drive Diagnostic 90h       |  |

| Initialize Drive Parameters 91h    |  |

| Download Microcode                 |  |

| SMART BOh                          |  |

| Read Multiple C4h                  |  |

| Write Multiple C5h                 |  |

| Set Multiple Mode C6h              |  |

| Read DMA C8h                       |  |

| Write DMA CAh<br>Read Buffer E4h   |  |

| Flush Cache                        |  |

| Write Buffer E8h                   |  |

| Power Management Commands          |  |

| Identify Drive – ECh               |  |

| Set Features EFh                   |  |

| Set Features (Ultra ATA/66)        |  |

| Read Defect List                   |  |

| Configuration                      |  |

| Host Protected Mode Feature        |  |

| ERROR REPORTING                    |  |

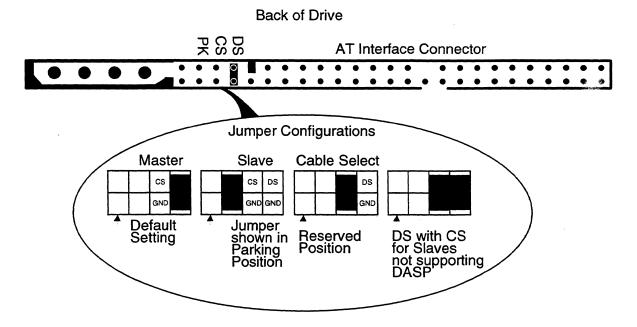

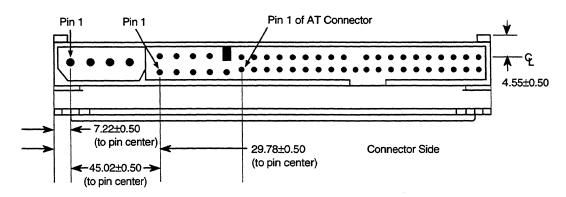

| Figure 3-1 Mechanical Dimensions of                             |        |

|-----------------------------------------------------------------|--------|

| Quantum Fireball CR Hard Disk Drive                             | 3-1    |

| Figure 3-2 Drive Packing Assembly                               | 3-2    |

| Figure 3-3 Drive Packing Assembly of a 20-Pack Container        | 3-3    |

| Figure 3-4 Jumper Locations for the                             |        |

| Quantum Fireball CR Hard Disk Drive                             | 3-4    |

| Figure 3-5 Jumper Locations on the Interface Connector          | 3-4    |

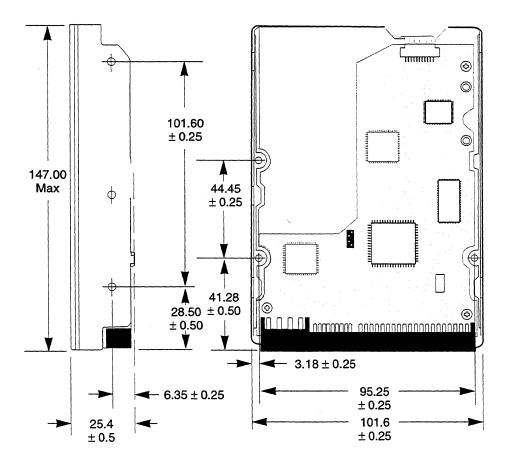

| Figure 3-6 AT Connector and Jumper Location                     | 3-6    |

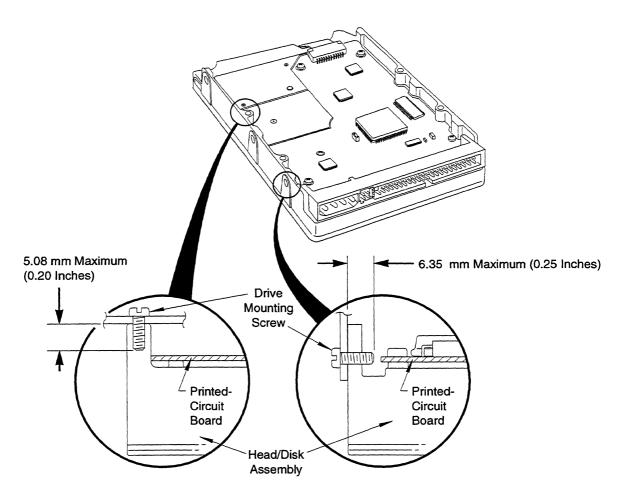

| Figure 3-7 Mounting Dimensions for the                          |        |

| Quantum Fireball CR Hard Disk Drives                            | 3-8    |

| Figure 3-8 Mounting Screw Clearance for the                     |        |

| Quantum Fireball CR Hard Disk Drives                            | 3-9    |

| Figure 3-9 Breather Filter                                      |        |

| Figure 3-10 J1 DC Power and ATA Bus Combination Connector       |        |

| Figure 3-11 Drive Power Supply and ATA Bus Interface Cables     |        |

| Figure 3-12 Completing the Drive Installation                   | 3-15   |

| Figure 5-1 Quantum Fireball CR 4.3/6.4/8.4/12.7AT               |        |

| Hard Disk Drive Exploded View                                   | 5-2    |

| Figure 5-2 Quantum Fireball CR 4.3/6.4/8.4/12.7AT               |        |

| Hard Disk Drive Block Diagram                                   |        |

| Figure 5-3 Block Diagram                                        |        |

| Figure 5-4 Read/Write ASIC Block Diagram                        |        |

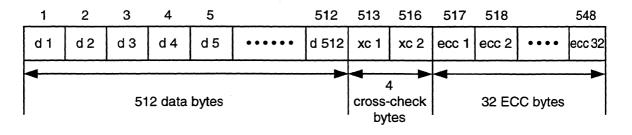

| Figure 5-5 Sector Data Field with ECC Check Bytes               |        |

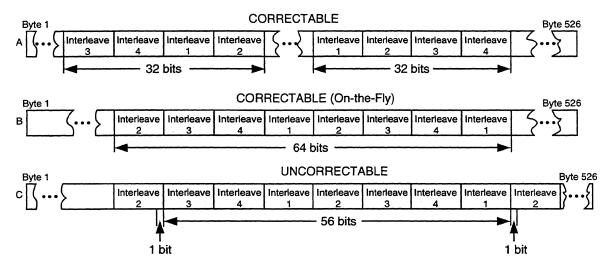

| Figure 5-6 Byte Interleaving                                    |        |

| Figure 5-7 Correctable and Uncorrectable Double-Burst Errors    |        |

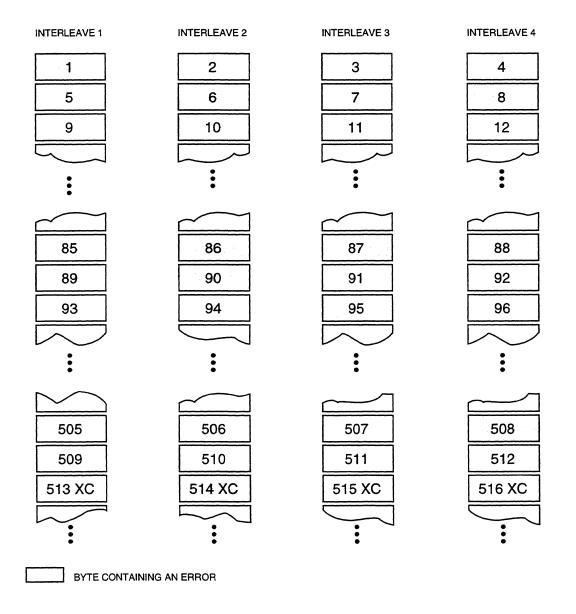

| Figure 5-8 Correctable and Uncorrectable Quadruple-Burst Errors |        |

| Figure 5-9 Twelve Correctable Random Burst Errors               |        |

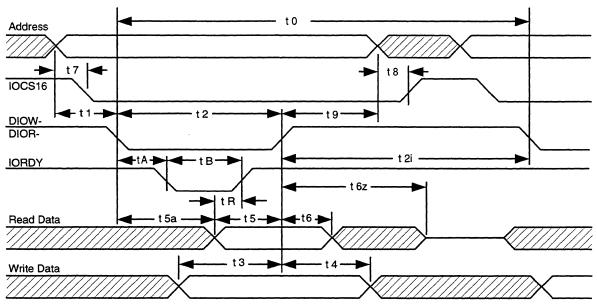

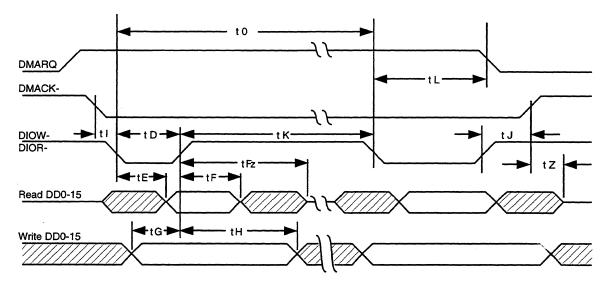

| Figure 6-1 PIO Interface Timing                                 |        |

| Figure 6-2 Multiword DMA Bus Interface Timing                   |        |

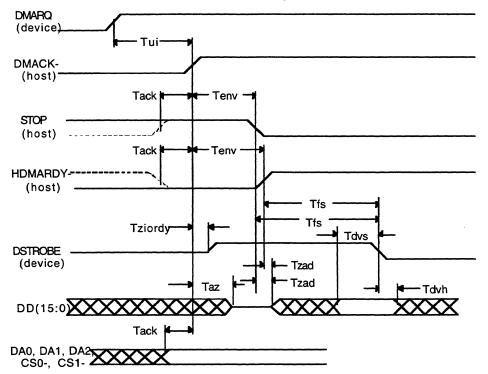

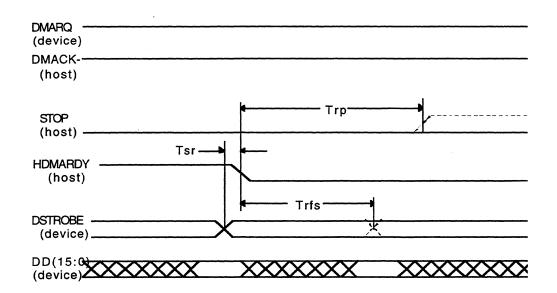

| Figure 6-3 Initiating a Data In Burst                           |        |

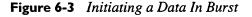

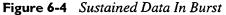

| Figure 6-4 Sustained Data In Burst                              |        |

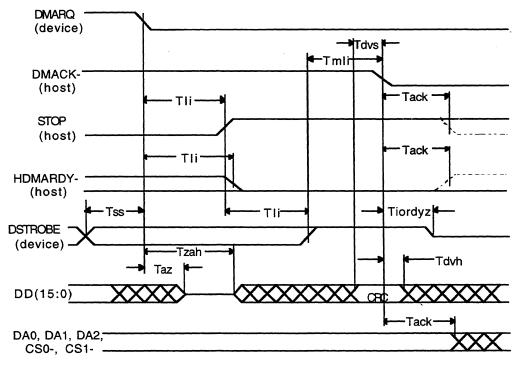

| Figure 6-5 Host Pausing a Data In Burst                         |        |

| Figure 6-6 Device Terminating a Data In Burst                   |        |

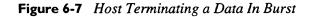

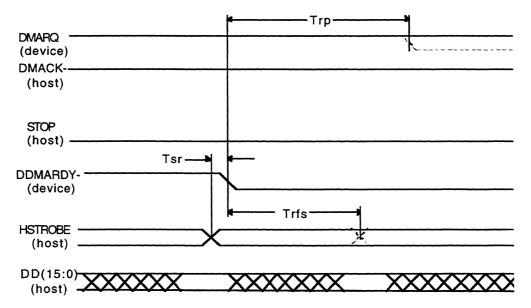

| Figure 6-7 Host Terminating a Data In Burst                     |        |

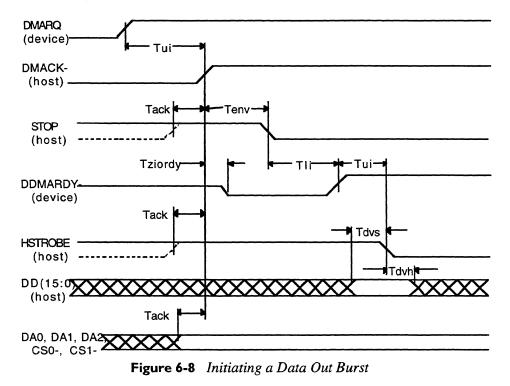

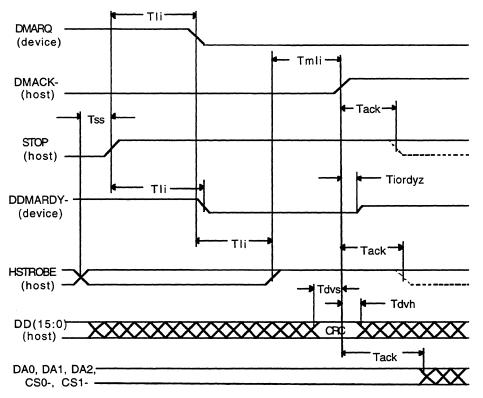

| Figure 6-8 Initiating a Data Out Burst 6                        |        |

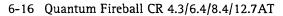

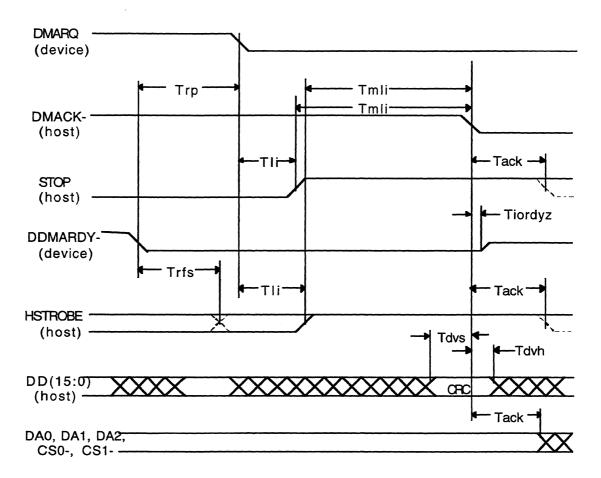

| Figure 6-9 Sustained Data Out Burst                             | . 6-17 |

=

| Figure 6-10 Device Pausing a Data Out Burst     | 6-17 |

|-------------------------------------------------|------|

| Figure 6-11 Host Terminating a Data Out Burst   | 6-18 |

| Figure 6-12 Device Terminating a Data out Burst | 6-19 |

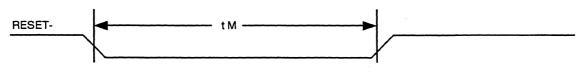

| Figure 6-13 Host Interface RESET Timing         | 6-19 |

| Table 3-1  | AT Jumper Options                                                   | 3-5  |

|------------|---------------------------------------------------------------------|------|

| Table 3-2  | J1 Power Connector, Section A                                       | 3-12 |

| Table 3-3  | Logical Addressing Format                                           | 3-17 |

| Table 4-1  | Specifications                                                      | 4-1  |

| Table 4-2  | Formatted Capacity                                                  | 4-3  |

| Table 4-3  | Timing Specifications                                               | 4-4  |

| Table 4-4  | Power Reset Limits                                                  |      |

| Table 4-5  | Typical Power and Current Consumption                               | 4-6  |

| Table 4-6  | Acoustical Characteristics-Sound Pressure                           | 4-7  |

| Table 4-7  | Acoustical Characteristics-Sound Power                              | 4-7  |

| Table 4-8  | Environmental Specifications                                        | 4-8  |

| Table 4-9  | Shock and Vibration Specifications                                  | 4-9  |

| Table 4-10 | Error Rates                                                         | 4-10 |

| Table 5-1  | Cylinder Contents                                                   | 5-3  |

| Table 5-2  | Skews Offsets                                                       |      |

| Table 6-1  | Drive Connector Pin Assignments (J1, Section C)                     | 6-3  |

| Table 6-2  | Series Termination for Ultra ATA/66                                 | 6-6  |

| Table 6-3  | Signal Line Definitions                                             | 6-7  |

| Table 6-4  | Interface Signal Name Assignments                                   | 6-8  |

| Table 6-5  | PIO Host Interface Timing                                           | 6-9  |

| Table 6-6  | Multiword DMA Host Interface Timing                                 | 6-10 |

| Table 6-7  | Ultra DMA Data Transfer Timing Requirements                         | 6-11 |

| Table 6-8  | Host Interface RESET Timing                                         | 6-19 |

| Table 6-9  | I/O Port Functions and Selection Addresses                          | 6-20 |

| Table 6-10 | Command Block Register Initial Values                               | 6-21 |

| Table 6-11 | Device Control Register Bits                                        | 6-22 |

| Table 6-12 | Drive Address Register Bits                                         | 6-23 |

| Table 6-13 | Error Register Bits                                                 | 6-24 |

| Table 6-14 | Drive Head Register Bits                                            | 6-25 |

| Table 6-15 | Status Register Bits                                                |      |

| Table 6-16 | Quantum Fireball CR 4.3/6.4/8.4/12.7AT Command Codes and Parameters | 6-27 |

| Table 6-17 | Diagnostic Codes                                                    | 6-30 |

| Table 6-18 | Device attribute thresholds data structure                          | 6-36 |

| Table 6-19 | Individual threshold data structure                                 | 6-37 |

| Table 6-20 | Device attributes data structure                                    |      |

| Table 6-21 | Individual attribute data structure                                 | 6-39 |

| Table 6-22 | Valid Count Range                                                   | 6-48 |

| Table 6-23 | Identify Drive Parameters                                           | 6-50 |

| Table 6-24 | Transfer/Mode Values                                                | 6-55 |

| Table 6-25 | READ DEFECT LIST LENGTH Command Bytes                               | 6-56 |

| Table 6-26 | AT READ DEFECT LIST Command Bytes                                   | 6-57 |

| Table 6-27 | DEFECT LIST DATA FORMAT                                             | 6-57 |

| Table 6-28 | DEFECT ENTRY DATA FORMAT                                       | 6-57 |

|------------|----------------------------------------------------------------|------|

| Table 6-29 | Accessing the READ CONFIGURATION Command                       | 6-58 |

| Table 6-30 | Accessing the SET CONFIGURATION Command                        | 6-59 |

| Table 6-31 | Accessing the SET CONFIGURATION WITHOUT SAVING TO DISK Command | 6-60 |

| Table 6-32 | Configuration Command Format                                   | 6-60 |

| Table 6-33 | Command Errors                                                 | 6-64 |

•

This chapter gives an overview of the contents of this manual, including the intended audience, how the manual is organized, terminology and conventions, and references.

#### I.I AUDIENCE DEFINITION

The Quantum Fireball CR<sup>™</sup>4.3/6.4/8.4/12.7AT Product Manual is intended for several audiences. These audiences include: the end user, installer, developer, original equipment manufacturer (OEM), and distributor. The manual provides information about installation, principles of operation, interface command implementation, and maintenance.

#### 1.2 MANUAL ORGANIZATION

This manual is organized into the following chapters:

- Chapter 1 About This Manual

- Chapter 2 General Description

- Chapter 3 Installation

- Chapter 4 Specifications

- Chapter 5 Basic Principles of Operation

- Chapter 6 ATA Bus Interface and ATA Commands

#### 1.3 TERMINOLOGY AND CONVENTIONS

In the Glossary at the back of this manual, you can find definitions for many of the terms used in this manual. In addition, the following abbreviations are used in this manual:

- ASIC application-specific integrated circuit

- ATA advanced technology attachment

- bpi bits per inch

- dB decibels

- dBA decibels, A weighted

- ECC error correcting code

- fci flux changes per inch

- Hz hertz

- KB kilobytes

- LSB least significant bit

- mA milliamperes

- MB megabytes (1 MB = 1,000,000 bytes when referring to disk storage and 1,048,576 bytes in all other cases)

- Mbit/s megabits per second

- MB/s megabytes per second

- MHz megahertz

- ms milliseconds

- MSB most significant bit

- mv millivolts

- ns nanoseconds

- tpi tracks per inch

- µs microseconds

- V volts

The typographical and naming conventions used in this manual are listed below. Conventions that are unique to a specific table appear in the notes that follow that table.

Typographical Conventions:

- Names of Bits: Bit names are presented in initial capitals. An example is the Host Software Reset bit.

- Commands: Interface commands are listed in all capitals. An example is WRITE LONG.

- Register Names: Registers are given in this manual with initial capitals. An example is the Alternate status Register.

- Parameters: Parameters are given as initial capitals when spelled out, and are given as all capitals when abbreviated. Examples are Prefetch Enable (PE), and Cache Enable (CE).

- Hexadecimal Notation: The hexadecimal notation is given in 9-point subscript form. An example is 30<sub>H</sub>.

- Signal Negation: A signal name that is defined as active low is listed with a minus sign following the signal. An example is RD-.

- Messages: A message that is sent from the drive to the host is listed in all capitals. An example is ILLEGAL COMMAND.

Naming Conventions:

- Host: In general, the system in which the drive resides is referred to as the host.

- Computer Voice: This refers to items you type at the computer keyboard. These items are listed in 10-point, all capitals, Courier font. An example is FORMAT C:/S.

#### I.4 REFERENCES

For additional information about the AT interface, refer to:

- IBM Technical Reference Manual #6183355, March 1986.

- ATA Common Access Method Specification, Revision 4.0.

1-4 Quantum Fireball CR 4.3/6.4/8.4/12.7AT

## Chapter 3 INSTALLATION

This chapter explains how to unpack, configure, mount, and connect the Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drive prior to operation. It also explains how to start up and operate the drive.

#### 3.1 SPACE REQUIREMENTS

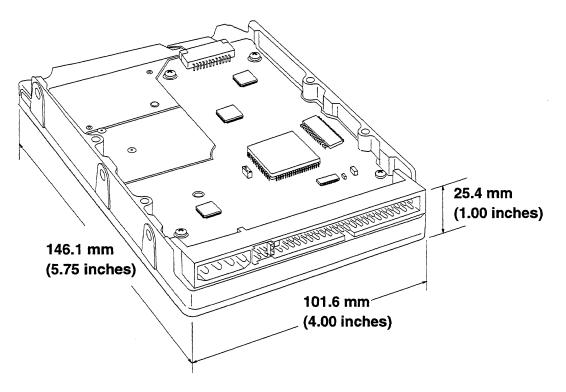

The Quantum Fireball CR hard disk drives are shipped without a faceplate. Figure 3-1 shows the external dimensions of the Quantum Fireball CR 4.3/6.4/8.4/12.7AT drives.

Figure 3-1 Mechanical Dimensions of Quantum Fireball CR Hard Disk Drive

#### 3.2 UNPACKING INSTRUCTIONS

CAUTION: The maximum limits for physical shock can be exceeded if the drive is not handled properly. Special care should be taken not to bump or drop the drive. It is highly recommended that Quantum Fireball CR drives are not stacked or placed on any hard surface after they are unpacked. Such handling could cause media damage.

- 1. Open the shipping container and remove the packing assembly that contains the drive.

- 2. Remove the drive from the packing assembly.

| CAUTION: | During shipment and handling, the antistatic electrostatic dis-<br>charge (ESD) bag prevents electronic component<br>damage due to electrostatic discharge. To avoid accidental damage<br>to the drive, do not use a sharp instrument to open the ESD bag<br>and do not touch PCB components. Save the packing materials for<br>possible future use. |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

3. When you are ready to install the drive, remove it from the ESD bag.

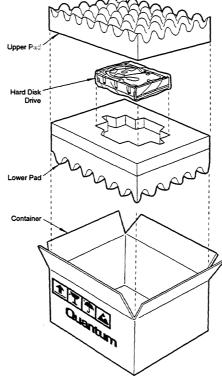

Figure 3-2 shows the packing assembly for a single Quantum Fireball CR hard disk drive. A 20-pack shipping container is available for multiple drive shipments.

#### DRAWING TO BE UPDATED

Figure 3-2 Drive Packing Assembly

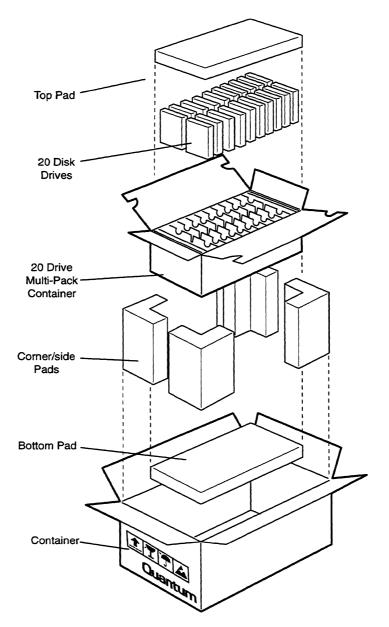

### DRAWING TO BE UPDATED

Figure 3-3 Drive Packing Assembly of a 20-Pack Container

Note: The 20-pack container should be shipped in the same way it was received from Quantum. When individual drives are shipped from the 20-pack container then it should be appropriately packaged (not supplied with the 20-pack) to prevent damage.

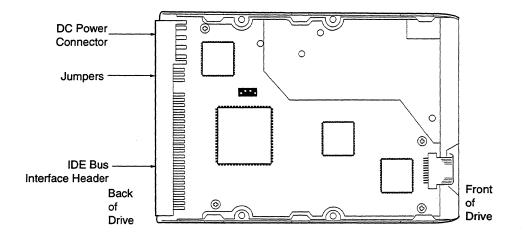

#### 3.3 HARDWARE OPTIONS

The configuration of a Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drive depends on the host system in which it is to be installed. This section describes the hardware options that you must take into account prior to installation. Figure 3-4 shows the printed circuit board (PCB) assembly, indicating the jumpers that control some of these options.

Figure 3-4 Jumper Locations for the Quantum Fireball CR Hard Disk Drive

Figure 3-5 Jumper Locations on the Interface Connector

The configuration of the following four jumpers controls the drive's mode of operation:

- CS Cable Select

- DS Drive Select

- PK- Jumper Parking Position (Slave mode)

The AT PCB has two jumper locations provided for configuration options in a system. These jumpers are used to configure the drive for master/slave operation in a system. The default configuration for the drive as shipped from the factory is with a jumper across the DS location, and open positions in the CS and PK positions.

Table 3-1 defines the operation of the jumpers and their function relative to pin 28 on the interface. *1* indicates that the specified jumper is installed; *0* indicates that the jumper is not installed.

| CS | DS | РК | PIN<br>28 | DESCRIPTION                                                                       |

|----|----|----|-----------|-----------------------------------------------------------------------------------|

| 0  | 0  | Х  | Х         | Drive is configured as a slave                                                    |

| 0  | I  | X  | х         | Drive is configured as a Master                                                   |

| 1  | 0  | ×  | Open      | Drive is configured as a slave                                                    |

| 1  | 0  | X  | Gnd       | Drive is configured as a Master                                                   |

| 1  | 0  | X  | Gnd       | Drive is configured as a Master with slave present                                |

| 1  | 1  | ×  | X         | Drive is configured as a Master with an attached slave that does not support DASP |

Table 3-I

AT Jumper Options

Note: In Table 3-1, a 0 indicates that the jumper is removed, a 1 indicates that the jumper is installed, and an X indicates that the jumper setting does not matter.

#### 3.3.1 Cable Select (CS) Jumper

When two Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drives are daisy-chained together, they can be configured as Master or Slave either by the CS or DS jumpers. To configure the drive as a Master or Slave with the CS feature, the CS jumper is installed (1).

Once you install the CS jumper, the drive is configured as a Master or Slave by the state of the Cable Select signal: pin 28 of the ATA bus connector. Please note that pin 28 is a vendor-specific pin that Quantum is using for a specific purpose. More than one function is allocated to CS, according to the ATA CAM specification (see reference to this specification in Chapter 1). If pin 28 is a 0 (grounded), the drive is configured as a Master. If it is a 1 (high), the drive is configured as a Slave. In order to configure two drives in a Master/Slave relationship using the CS jumper, you need to use a cable that provides the proper signal level at pin 28 of the ATA bus connector. This allows two drives to operate in a Master/Slave relationship according to the drive cable placement.

#### 3.3.2 Drive Select (DS) Jumper

You can also daisy-chain two drives on the ATA bus interface by using their Drive Select (DS) jumpers. To use the DS feature, the CS jumper must be removed.

To configure a drive as the Master (Drive 0), a jumper must be installed on the DS pins.

The Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drives are shipped from the factory as a Master (Drive 0 - DS jumper installed). To configure a drive as a Slave (Drive 1), the DS jumper must be removed. In this configuration, the spare jumper removed from the DS position may be stored on the PK jumper pins.

Note: The order in which drives are connected in a daisy chain has no significance.

#### 3.3.3 Jumper Parking (PK) Position

The PK position is used as a holding place for the jumper for a slave drive in systems that do not support Cable Select. The pins used for the parking position are vendor unique. The drive will bias the parking position pins to detect the presence of this jumper. When doing so it will maintain a minimum impedance of 4.7 K $\Omega$  to the +5 volt supply and 2.4K $\Omega$  to ground.

#### 3.3.4 Master Jumper configuration

In combination with the current DS or CS jumper settings, the Slave Present (SP) jumper can be implemented if necessary as follows:

• When the drive is configured as a Master (DS jumper installed or CS jumper installed, and the Cable Select signal is set to (0), adding an additional jumper (both jumpers DS and CS now installed) will indicate to the drive that a Slave drive is present. This Master with Slave Present jumper configuration should be installed on the Master drive only if the Slave drive does *not* use the Drive Active/Slave Present (DASP-) signal to indicate its presence.

#### 3.3.5 Reserved Position

Do not put a jumper at the reserved position (RSVD).

Figure 3-6 AT Connector and Jumper Location

#### 3.4 ATA BUS ADAPTER

There are two ways you can configure a system to allow the Quantum Fireball CR hard disk drives to communicate over the ATA bus of an IBM or IBM-compatible PC:

- 1. Connect the drive to a 40-pin ATA bus connector (if available) on the motherboard of the PC.

- 2. Install an IDE-compatible adapter board in the PC, and connect the drive to the adapter board.

#### 3.4.1 40-Pin ATA Bus Connector

Most PC motherboards have a built-in 40-pin ATA bus connector that is compatible with the 40-pin ATA interface of the Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drives. If the motherboard has an ATA connector, simply connect a 40-pin ribbon cable between the drive and the motherboard.

You should also refer to the motherboard instruction manual, and refer to Chapter 6 of this manual to ensure signal compatibility.

#### 3.4.2 Adapter Board

If your PC motherboard does not contain a built-in 40-pin ATA bus interface connector, you must install an ATA bus adapter board and connecting cable to allow the drive to interface with the motherboard. Quantum does not supply such an adapter board, but they are available from several third-party vendors.

Please carefully read the instruction manual that comes with your adapter board, as well as Chapter 6 of this manual to ensure signal compatibility between the adapter board and the drive. Also, make sure that the adapter board jumper settings are appropriate.

#### 3.5 MOUNTING

Drive mounting orientation, clearance, and ventilation requirements are described in the following subsections.

#### 3.5.1 Orientation

The mounting holes on the Quantum Fireball CR 4.3/6.4/12.7AT hard disk drives allow the drive to be mounted in any orientation. Figures 3-6 and 3-7 show the location of the three mounting holes on each side of the drive. The drive can also be mounted using the four mounting hole locations on the PCB side of the drive.

Note: It is highly recommended that the drive is hard mounted on to the chassis of the system being used for general operation, as well as for test purposes. Failure to hard mount the drive can result in erroneous errors during testing.

Drives can be mounted in any orientation. Normal position is with the PCB facing down.

All dimensions are in millimeters. For mounting, #6-32 UNC screws are recommended.

Figure 3-7 Mounting Dimensions for the Quantum Fireball CR Hard Disk Drives

Figure 3-8 Mounting Screw Clearance for the Quantum Fireball CR Hard Disk Drives

CAUTION: The PCB is very close to the mounting holes. Do not exceed the specified length for the mounting screws. The specified screw length allows full use of the mounting hole threads, while avoiding damaging or placing unwanted stress on the PCB. Figure 3-8 specifies the minimum clearance between the PCB and the screws in the mounting holes. To avoid stripping the mounting hole threads, the maximum torque applied to the screws must not exceed 8 inch-pounds. A maximum screw length of 0.25 inches may be used.

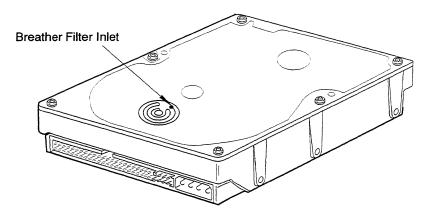

Figure 3-9 Breather Filter

| CAUTION: | The Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drives use<br>a breather filter to eliminate pressure differences that may develop<br>between the inside and outside of the Head Disk Assembly (HDA).<br>Blockage of this air inlet could result in pressure building up inside<br>the HDA and could cause damage to the gasket sealing the HDA<br>(see Section 5.1.7 for more details). |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                                                                                                                                                                                                                                                                                                                                               |

#### 3.5.2 Clearance

Clearance from the drive to any other surface (except mounting surfaces) must be a minimum of 1.25 mm (0.05 inches).

#### 3.5.3 Ventilation

The Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drives operate without a cooling fan, provided the ambient air temperature does not exceed 131°F (55°C) at any point along the drive form factor envelope.

#### 3.6 COMBINATION CONNECTOR (JI)

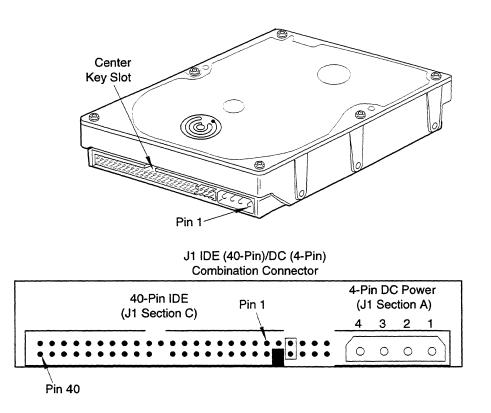

J1 is a three-in-one combination connector. The drive's DC power can be applied to section A. The ATA bus interface (40-pin) uses section C. The connector is mounted on the back edge of the printed-circuit board (PCB), as shown in Figure 3-10.

Figure 3-10 J1 DC Power and ATA Bus Combination Connector

#### 3.6.1 DC Power (JI, Section A)

The recommended mating connectors for the +5 VDC and +12 VDC input power are listed in Table 3-2.

| PIN<br>NUMBER    | VOLTAGE<br>LEVEL               | MATING CONNECTOR TYPE AND PART NUMBER<br>(OR EQUIVALENT)                             |

|------------------|--------------------------------|--------------------------------------------------------------------------------------|

| JI Section A (4- | Pin):                          |                                                                                      |

| I                | +12VDC                         | 4-Pin Connector:                                                                     |

| 2                | Ground<br>Return for<br>+12VDC | AMP P/N 1-480424-0<br>Loose piece contacts:<br>AMP P/N VS 60619-4<br>Strip contacts: |

| 3                | Ground<br>Return for +5<br>VDC | AMP P/N VS 61117-4                                                                   |

| 4                | +5VDC                          |                                                                                      |

Note: Labels indicate the pin numbers on the connector. Pins 2 and 3 of section A are the +5 and +12 volt returns and are connected together on the drive.

#### 3.6.2 External Drive Activity LED

An external drive activity LED may be connected to the DASP-I/O pin 39 on J1. For more details, see the pin description in Table 6-1.

#### 3.6.3 ATA Bus Interface Connector (JI, Section C)

On the Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drives, the ATA bus interface cable connector (J1, section C) is a 40-pin Universal Header, as shown in Figure 3-10.

To prevent the possibility of incorrect installation, the connector has been keyed by removing Pin 20. This ensures that a connector cannot be installed upside down.

See Chapter 6, "ATA Bus Interface and ATA Commands," for more detailed information about the required signals. Refer to Table 6-1 for the pin assignments of the ATA bus connector (J1, section C).

#### 3.7 FOR SYSTEMS WITH A MOTHERBOARD ATA ADAPTER

You can install the Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drives in an ATcompatible system that contains a 40-pin ATA bus connector on the motherboard.

To connect the drive to the motherboard, use a 40 conductor ribbon cable (80 conductor ribbon cable if using UltraATA/66 drive) 18 inches in length or shorter. Ensure that pin 1 of the drive is connected to pin 1 of the motherboard connector.

#### 3.8 FOR SYSTEMS WITH AN ATA ADAPTER BOARD

To install the Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drive in an ATcompatible system without a 40-pin ATA bus connector on its motherboard, you need a third-party IDE-compatible adapter board.

#### 3.8.1 Adapter Board Installation

Carefully read the manual that accompanies your adapter board before installing it. Make sure that all the jumpers are set properly and that there are no address or signal conflicts. You must also investigate to see if your AT-compatible system contains a combination floppy and hard disk controller board. If it does, you must disable the hard disk drive controller functions on that controller board before proceeding.

Once you have disabled the hard disk drive controller functions on the floppy/hard drive controller, install the adapter board. Again, make sure that you have set all jumper straps on the adapter board to avoid addressing and signal conflicts.

Note: For Sections 3.7 and 3.8, power should be turned off on the computer before installing the drive.

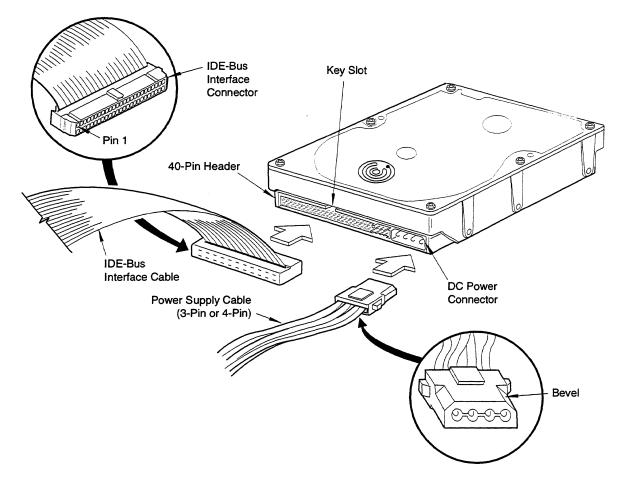

#### 3.8.1.1 Connecting the Adapter Board and the Drive

Use a 40-pin ribbon cable to connect the drive to the board. See Figure 3-11. To connect the drive to the board:

- 1. Insert the 40-pin cable connector into the mating connector of the adapter board. Make sure that pin 1 of the connector matches with pin 1 on the cable.

- 2. Insert the other end of the cable into the header on the drive. When inserting this end of the cable, make sure that pin 1 of the cable connects to pin 1 of the drive connector.

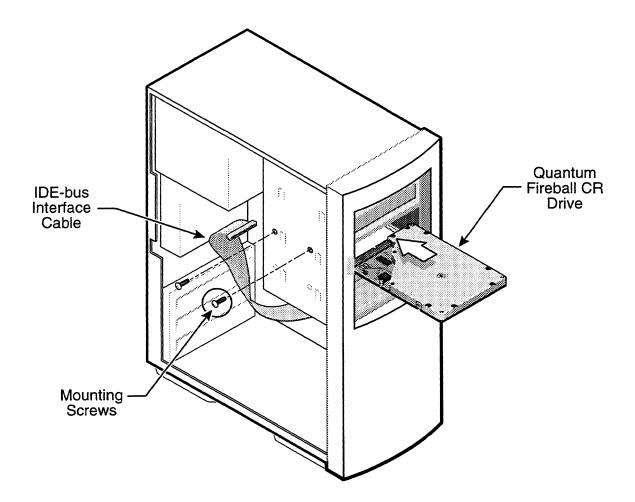

- 3. Secure the drive to the system chassis by using the mounting screws, as shown in Figure 3-12.

Figure 3-11 Drive Power Supply and ATA Bus Interface Cables

Figure 3-12 Completing the Drive Installation

#### 3.9 TECHNIQUES IN DRIVE CONFIGURATION

#### 3.9.1 The 528-Megabytes Barrier

Older BIOS that only support Int 13 commands for accessing ATA drives through DOS based operating systems will be limited to use only 1024 cylinders. This will reduce the effective capacity of the drive to 528 Mbytes.

Whenever possible the Quantum Fireball CR 4.3/6.4/8.4/12.7AT drive should be used on systems that support LBA translation to ensure the use of the entire capacity of the disk drive. If that is not possible the following are some techniques that can be used to overcome this barrier.

- Use a third party software program that translates the hard drive parameters to an acceptable configuration for MS-DOS.

- Use a hard disk controller that translates the hard drive parameters to an appropriate setup for both MS-DOS and the computer system's ROM-BIOS.

#### 3.9.2 The 8.4-Gigabytes Barrier

Newer BIOS allow users to configure disk drives go beyond the 528 MB barrier by using several BIOS translation schemes. However, while using these translations the BIOS using Int 13 functions are limited to 24 bits of addressing which results in another barrier at the 8.4 GB capacity.

To overcome this barrier a new set of Int 13 extensions are being implemented by most BIOS manufacturers. The new Int 13 extension allows for four words of addressing space (64 bits) resulting on 9.4 Terrabytes of accessible space.

Whenever possible the Quantum Fireball CR 4.3/6.4/8.4/12.7AT drive should be used on systems with BIOS that support Int 13 extensions. If that is not possible the following are some techniques that can be used to overcome this barrier:

- Use a third party software that supplements the BIOS and adds Int 13 extension support.

- Obtain a BIOS upgrade from the system board manufacturer. Many system board manufacturers allow their BIOS to be upgraded on the field using special download utilities. Information on BIOS upgrades can be obtained on the System Board Customer Service respective web sites on the Internet.

#### 3.9.3 Operating system limitations

Most popular operating systems available today have additional limitations which affects the use of a large capacity drives. However, these limitations can not be corrected on the BIOS and it is up to the operating system manufacturers to release improved versions to address these problems.

The most popular operating systems available today, DOS and Win 95, use a File Allocation Table (FAT) size of 16 bits which will only support portions up to 2.1 GB drives. A newer release of Win 95 called OSR2 which 32 bits FAT has been released to system manufacturers only. This new FAT size table will support partitions of up to 2.2 Terrabytes.

#### 3.10 SYSTEM STARTUP AND OPERATION

Once you have installed the Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drive, and adapter board (if required) in the host system, you are ready to partition and format the drive for operation. To set up the drive correctly, follow these steps:

- 1. Power on the system.

- 2. Run the SETUP program. This is generally on a Diagnostics or Utilities disk, or within the system's BIOS. Some system BIOS have an auto-detecting feature making SETUP unnecessary.

- 3. Enter the appropriate parameters.

The SETUP program allows you to enter the types of optional hardware installed—such as the hard disk drive type, the floppy disk drive capacity, and the display adapter type. The system's BIOS uses this information to initialize the system when the power is switched on. For instructions on how to use the SETUP program, refer to the system manual for your PC.

During the AT system CMOS setup, you must enter the drive type for the Quantum Fireball CR hard disk drives. The drive supports the translation of its physical drive geometry parameters such as cylinders, heads, and sectors per track to a logical addressing mode. The drive can work with different BIOS drive-type tables of the various host systems.

You can choose any drive type that does not exceed the capacity of the drive. Table 3-3 gives the logical parameters that provide the maximum capacity on the Quantum Fireball CR family of hard disk drives.

|                              | QUANTUM FIREBALL CR |            |             |            |  |  |

|------------------------------|---------------------|------------|-------------|------------|--|--|

|                              | 4.3                 | 6.4        | 8.4         | 12.7       |  |  |

| LBA Capacity                 | 4.3 GB              | 6.4 GB     | 8.6 GB      | 12.9 GB    |  |  |

| CHS Capacity                 | 4,320 MB            | 6,480 MB   | 8,640 MB    | 12,960 MB  |  |  |

| Logical Cylinders            | TBD                 | TBD        | TBD         | TBD        |  |  |

| Logical Heads                | 15                  | 15         | 16          | 16         |  |  |

| Logical Sectors/Track        | 63                  | 63         | 63          | 63         |  |  |

| Total Number Logical Sectors | 8,391,600           | 12,586,896 | 165,514,064 | 24,901,632 |  |  |

#### Table 3-3 Logical Addressing Format

Note: \* The AT capacity is artificially limited to a 2.1 GB partition boundary.

To match the logical specifications of the drive to the drive type of a particular BIOS, consult the system's drive-type table. This table specifies the number of cylinders, heads, and sectors for a particular drive type.

You must choose a drive type that meets the following requirements:

For the 4.3 AT:

Logical Cylinders x Logical Heads x Logical Sectors/Track x 512 = 4,296,499,200For the 6.4 AT:

Logical Cylinders x Logical Heads x Logical Sectors/Track x 512 = 6,444,490,752For the 8.4 AT:

Logical Cylinders x Logical Heads x Logical Sectors/Track x 512 = 8,455,200,768

For the 12.7 AT:

Logical Cylinders x Logical Heads x Logical Sectors/Track x 512 = 12,749,635,584

4. Boot the system using the operating system installation disk-for example, *MS-DOS*-then follow the installation instructions in the operating system manual.

This chapter gives a detailed description of the physical, electrical, and environmental characteristics of the Quantum Fireball CR hard disk drives.

#### 4.1 SPECIFICATION SUMMARY

Table 4-1 gives a summary of the Quantum Fireball CR hard disk drives.

| DECODIPTION                          | QUANTUM FIREBALL CR                                                                                              |                                |                                |                                |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|--|

| DESCRIPTION                          | 4.3 AT                                                                                                           | 6.4 AT                         | 8.4 AT                         | 12.7 AT                        |  |

| Formatted Capacity                   | 4,320 MB                                                                                                         | 6,480 MB                       | 8,640 MB                       | 12,960 MB                      |  |

| Nominal rotational speed (rpm)       | 5,400                                                                                                            | 5,400                          | 5,400                          | 5,400                          |  |

| Number of Disks                      | 1                                                                                                                | 2                              | 2                              | 3                              |  |

| Number of R/W heads                  | 2                                                                                                                | 3                              | 4                              | 6                              |  |

| Data Organization:                   | •                                                                                                                | L                              | L                              |                                |  |

| Zones per surface                    | 15                                                                                                               | 15                             | 15                             | 15                             |  |

| Tracks per surface                   | 12,515                                                                                                           | 12,515                         | 12,515                         | 12,515                         |  |

| Total tracks                         | 25,030                                                                                                           | 37,545                         | 50,060                         | 75,090                         |  |

| Sectors per track:                   | Langer and the second | I                              | L                              |                                |  |

| Inside zone                          | 250                                                                                                              | 250                            | 250                            | 250                            |  |

| Outside zone                         | 406                                                                                                              | 406                            | 406                            | 406                            |  |

| Total User Sectors                   | 8,391,600                                                                                                        | 12,586,896                     | 165,514,064                    | 24,901,632                     |  |

| Bytes per sector                     | 512                                                                                                              | 512                            | 512                            | 512                            |  |

| Number of tracks per cylinder        | 2                                                                                                                | 3                              | 4                              | 6                              |  |

| Recording:                           |                                                                                                                  |                                | k                              |                                |  |

| Recording technology                 | Multiple                                                                                                         | Multiple                       | Multiple                       | Multiple                       |  |

|                                      | Zone                                                                                                             | Zone                           | Zone                           | Zone                           |  |

| Maximum linear density               | 260,000 fci                                                                                                      | 260,000 fci                    | 260,000 fci                    | 260,000 fci                    |  |

| Encoding method                      | 16/17,<br>24/25 PRML                                                                                             | 16/17,<br>24/25 PRML           | 16/17,<br>24/25 PRML           | 16/17,<br>24/25 PRML           |  |

| Interleave                           | 1:1                                                                                                              | 1:1                            | 1:1                            | 1:1                            |  |

| Track density                        | 13,000 tpi                                                                                                       | 13,000 tpi                     | 13,000 tpi                     | 13,000 tpi                     |  |

| Maximum effective areal den-<br>sity | 3,250<br>Mbits/in <sup>2</sup>                                                                                   | 3,250<br>Mbits/in <sup>2</sup> | 3,250<br>Mbits/in <sup>2</sup> | 3,250<br>Mbits/in <sup>2</sup> |  |

#### Table 4-1 Specifications

Quantum Fireball CR 4.3/6.4/8.4/12.7AT 4-1

| DESCRIPTION                                                     |                                                | QUANTUM                                        | FIREBALL CR                                    |                                                |

|-----------------------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|

| DESCRIPTION                                                     | 4.3 AT                                         | 6.4 AT                                         | 8.4 AT                                         | 12.7 AT                                        |

| Performance:                                                    |                                                |                                                |                                                |                                                |

| Seek times:                                                     |                                                |                                                |                                                |                                                |

| Read-on-arrival                                                 | 9.5 ms typ.<br>11.5 ms max.                    | 9.5 ms typ.<br>11.5 ms max.                    | 9.5 ms typ.<br>11.5 ms max.                    | 9.5 ms typ.<br>11.5 ms max                     |

| Track-to-track                                                  | I.5 ms<br>typical                              | l.5 ms<br>typical                              | I.5 ms<br>typical                              | I.5 ms<br>typical                              |

| Average write                                                   | 11.0 ms typ.<br>13.0 ms max.                   | 11.0 ms typ.<br>13.0 ms max.                   | 11.0 ms typ.<br>13.0 ms max.                   | 11.0 ms typ.<br>13.0 ms max                    |

| Full stroke                                                     | 18.0 ms typ.<br>22.0 ms max.                   | 18.0 ms typ.<br>22.0 ms max.                   | 18.0 ms typ.<br>22.0 ms max.                   | 18.0 ms typ.<br>22.0 ms max                    |

| Data transfer Rates:                                            |                                                | L                                              | I                                              |                                                |

| Disk to Read Once a Revolution <sup>1,</sup><br>2               | 76.6 MB/sec<br>min.<br>128.6 MB/sec<br>max.    | 76.6 MB/sec<br>min.<br>128.6 MB/sec<br>max.    | 76.6 MB/sec<br>min.<br>128.6 MB/sec<br>max.    | 76.6 MB/sec<br>min.<br>128.6 MB/sec<br>max.    |

| Disk to Read<br>Instantaneously <sup>1</sup>                    | I03.52 MB/<br>sec min.<br>I71.3 MB/sec<br>max. | I03.52 MB/<br>sec min.<br>I71.3 MB/sec<br>max. | 103.52 MB/<br>sec min.<br>171.3 MB/sec<br>max. | 103.52 MB/<br>sec min.<br>171.3 MB/sec<br>max. |

| Read Buffer to ATA Bus<br>(PIO Mode with IORDY)                 | I6.7 MB/sec.<br>max.                           | 16.7 MB/sec.<br>max.                           | I6.7 MB/sec.<br>max.                           | I 6.7 MB/sec<br>max.                           |

| Read Buffer to ATA Bus<br>(Ultra ATA Mode)                      | 33 MB/sec.<br>max.                             | 33 MB/sec.<br>max.                             | 33 MB/sec.<br>max.                             | 33 MB/sec.<br>max.                             |

| Buffer Size                                                     | 512 KB                                         | 512 KB                                         | 512 KB                                         | 512 KB                                         |

| Reliability:<br>Seek error rate <sup>2</sup>                    | in 10 <sup>6</sup>                             | l in 10 <sup>6</sup>                           | l in 10 <sup>6</sup>                           | l in 10 <sup>6</sup>                           |

| Unrecoverable error rate <sup>2</sup>                           | 1 in 10 <sup>14</sup>                          | l in 10 <sup>14</sup>                          | l in 10 <sup>14</sup>                          | l in 10 <sup>14</sup>                          |

| Error correction method<br>(with cross check)                   | 288-bit<br>Reed<br>Solomon                     | 288-bit<br>Reed<br>Solomon                     | 288-bit<br>Reed<br>Solomon                     | 288-bit<br>Reed<br>Solomon                     |

| Projected MTBF <sup>3</sup>                                     | 625,000 hrs                                    | 625,000 hrs                                    | 625,000 hrs                                    | 625,000 hrs                                    |

| Contact Start/Stop Cycles <sup>4</sup><br>(Ambient temperature) | 50,000 min.                                    | 50,000 min.                                    | 50,000 min.                                    | 50,000 min.                                    |

| Auto head-park method                                           | AirLock®                                       | with Magnetic A                                | ctuator Bias                                   |                                                |

- 1. Disk to read buffer transfer rate is zone-dependent, instantaneous

- 2. Refer to Section 4.12, "DISK ERRORS" for details on error rate definitions.

- 3. CSS specifications assumes a duty cycle of one power off operation for every one idle spin down.

# 4.2 FORMATTED CAPACITY

At the factory, the Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drives receive a low-level format that creates the actual tracks and sectors on the drive. Table 4-2 shows the capacity resulting from this process. Formatting done at the user level, for operation with DOS, UNIX, or other operating systems, may result in less capacity than the physical capacity shown in Table 4-2.

|                                      | QUANTUM FIREBALL CR |            |             |            |  |

|--------------------------------------|---------------------|------------|-------------|------------|--|

|                                      | 4.3 AT              | 6.4 AT     | 8.4 AT      | 12.7 AT    |  |

| Formatted Capacity                   | 4,320 MB            | 6,480 MB   | 8,640 MB    | 12,960 MB  |  |

| Number of 512-byte sectors available | 8,391,600           | 12,586,896 | 165,514,064 | 24,901,632 |  |

Note: \* The AT capacity is artificially limited to a 2.1 GB partition boundary.

# 4.3 DATA TRANSFER RATES

Data is transferred from the disk to the read buffer at a rate of up to 171 Mb/s in bursts. Data is transferred from the read buffer to the ATA bus at a rate of up to 16.7 MB/s using programmed I/O with IORDY, or at a rate of up to 66 MB/s using UltraATA/66. For more detailed information on interface timing, refer to Chapter 6.

# 4.4 TIMING SPECIFICATIONS

Table 4-3 illustrates the timing specifications of the Quantum Fireball CR hard disk drives.

| PARAMETER                                         |              | WORST<br>CASE <sup>2</sup> |

|---------------------------------------------------|--------------|----------------------------|

| Sequential Cylinder Switch Time <sup>3</sup>      | 3.0 ms       | 4.0 ms                     |

| Sequential Head Switch Time <sup>4</sup>          | 2.5 ms       | 3.0 ms                     |

| Random Average (Read or Seek) <sup>9</sup>        | 9.5 ms       | 11.5 ms                    |

| Random Average (Write) <sup>9</sup>               | 11.0 ms      | 13.0 ms                    |

| Full-Stroke Seek                                  | 18.0 ms      | 22.0 ms                    |

| Average Rotational Latency                        | 5.59 ms      |                            |

| Power On <sup>5</sup> to Drive Ready <sup>6</sup> | 9.0 seconds  | 12.0 seconds               |

| Standby <sup>7</sup> to Interface Ready           | 9.0 seconds  | 12.0 seconds               |

| Spindown Time, Standby Command                    | 20.0 seconds | 15 seconds <sup>8</sup>    |

| Spindown Time, Power loss                         | 18.0 seconds | 30 seconds <sup>8</sup>    |

| Table 4- | •3 Ti | iming. | Speci | fications |

|----------|-------|--------|-------|-----------|

|----------|-------|--------|-------|-----------|

- 1. Nominal conditions are as follows:

- •Nominal temperature 77°F (25°C)

- •Nominal supply voltages (12.0V, 5.0V)

- •No applied shock or vibration

- 2. Worst case conditions are as follows:

- •Worst case temperature extremes 32 to 131°F (5°C to 55°C)

- •Worst case supply voltages (12.0V  $\pm$ 10%, 5.0 V  $\pm$ 5%)

- 3. Sequential Cylinder Switch Time is the time from the conclusion of the last sector of a cylinder to the first logical sector on the next cylinder (no more than 6% of cylinder switches exceed this time).

- 4. Sequential Head Switch Time is the time from the last sector of a track to the beginning of the first logical sector of the next track of the same cylinder (no more than 6% of head switches exceed this time).

- 5. Power On is the time from when the supply voltages reach operating range to when the drive is ready to accept any command.

- 6. Drive Ready is the condition in which the disks are rotating at the rated speed, and the drive is able to accept and execute commands requiring disk access without further delay at power or start up. Error recovery routines may extend the time to as long as 45 seconds for drive ready.

- 7. Standby is the condition at which the microprocessor is powered, but not the HDA. When the host sends the drive a shutdown command, the drive parks the heads away from the data zone, and spins down to a complete stop.

- 8. After this time it is safe to move the disk drive

- 9. Average random seek is defined as the average seek time between random logical cylinders (LBA).

# 4.5 **POWER**

The Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drives operate from two supply voltages:

- +12V ±10%

- +5V ±5%

The allowable ripple and noise is 250 mV peak-to-peak for the +12 Volt supply and 100 mV peak-to-peak for the +5 Volt supply.

# 4.5.1 **Power Sequencing**

You may apply the power in any order, or open either the power or power return line with no loss of data or damage to the disk drive. However, data may be lost in the sector being written at the time of power loss. The drive can withstand transient voltages of +10% to -100% from nominal while powering up or down.

## 4.5.2 Power Reset Limits

When powering up, the drive remains reset until both  $V_{HT}$  reset limits in Table 4-4 are exceeded. When powering down, the drive becomes reset when either supply voltage drops below the  $V_{LT}$  threshold.

| DCVOLTAGE | THRESHOLD                                                                                            | HYSTERESIS       |

|-----------|------------------------------------------------------------------------------------------------------|------------------|

| +5V       | $V_{LT}$ = 4.65V maximum,<br>4.4V minimum<br>$V_{HT}$ = 4.71V maximum,<br>4.43V minimum              | 70 mV (typical)  |

| +12V      | V <sub>LT</sub> = 9.3V maximum,<br>8.7V minimum<br>V <sub>HT</sub> = 9.58V maximum,<br>8.82V minimum | 200 mV (typical) |

| Table 4-4         Power Reset Limit | Table | 4-4 | Power | Reset | Limits |

|-------------------------------------|-------|-----|-------|-------|--------|

|-------------------------------------|-------|-----|-------|-------|--------|

# 4.5.3 **Power Requirements**

Table 4-5 lists the voltages and typical average corresponding currents for the various modes of operation of the Quantum Fireball CR hard disk drives.

| MODE OF                          | TYPICAL AVERAGE CURRENT <sup>2</sup><br>(MA RMS UNLESS OTHERWISE NOTED) |      |      |      |     |     |     |      |

|----------------------------------|-------------------------------------------------------------------------|------|------|------|-----|-----|-----|------|

| OPERATION                        |                                                                         | +1   | +12V |      |     | +5V |     |      |

| MODEL NUMBER                     | 4.3                                                                     | 6.4  | 8.4  | 12.7 | 4.3 | 6.4 | 8.4 | 12.7 |

| Startup <sup>1</sup> (peak)      | 1703                                                                    | 1670 | 1670 | 1682 | 627 | 624 | 624 | 652  |

| ldle <sup>3</sup>                | 192                                                                     | 224  | 224  | 280  | 436 | 434 | 434 | 450  |

| Operating <sup>4</sup>           | 381                                                                     | 407  | 407  | 462  | 442 | 440 | 440 | 456  |

| Maximum Seeking <sup>5</sup>     | 664                                                                     | 687  | 687  | 742  | 441 | 439 | 439 | 455  |

| Standby <sup>6</sup>             | 38                                                                      | 38   | 38   | 38   | 110 | 110 | 110 | 110  |

| Sleep <sup>7</sup>               | 38                                                                      | 38   | 38   | 38   | 110 | 110 | 110 | 110  |

| Read/Write On Track <sup>8</sup> | 192                                                                     | 220  | 220  | 273  | 449 | 444 | 444 | 460  |

## **Table 4-5** Typical Power and Current Consumption

| MODE OF<br>OPERATION             | TYPICAL AVERAGE POWER <sup>2</sup> (WATTS) |      |      |      |  |  |

|----------------------------------|--------------------------------------------|------|------|------|--|--|

| MODEL NUMBER                     | 4.3 6.4 8.4 12.7                           |      |      |      |  |  |

| Startup <sup>1</sup> (peak)      | 23.6                                       | 23.2 | 23.2 | 23.4 |  |  |

| Idle <sup>3</sup>                | 4.5                                        | 4.9  | 4.9  | 5.6  |  |  |

| Operating <sup>4</sup>           | 6.8                                        | 7.1  | 7.1  | 7.8  |  |  |

| Maximum Seeking <sup>5</sup>     | 10.2                                       | 10.4 | 10.4 | 11.2 |  |  |

| Standby <sup>6</sup>             | 10                                         | 10   | 10   | 10   |  |  |

| Sleep <sup>7</sup>               | 10                                         | 10   | 10   | 10   |  |  |

| Read/Write On Track <sup>8</sup> | 4.5                                        | 4.9  | 4.9  | 5.6  |  |  |

- 1. Current is rms except for startup. Startup current is the typical peak current of the peaks greater than 10 ms in duration.

- 2. Power requirements reflect nominal for +12V and +5V power.

- 3. Idle mode is in effect when the drive is not reading, writing, seeking, or executing any commands. A portion of the R/W circuitry is powered down, the motor is up to speed and the Drive Ready condition exists.

- 4. Operating mode is defined as when data is being read from or written to the disk. It is computed based on 40% seeking, 30% on-track read, 20% idle, and 10% on-track write.

- 5. Maximum seeking is defined as continuous random seek operations with minimum controller delay.

- 6. Standby mode is defined as when the motor is stopped, the actuator is parked, and all electronics except the interface control are in low power state. Standby occurs after a programmable time-out after the last host access. Drive ready and seek complete status exist. The drive leaves standby upon receipt of a command that requires disk access or upon receiving a spinup command.

- 7. Sleep is defined as when the spindle and actuator motors are off and the heads are latched in the landing zone. Receipt of a reset causes the drive to transition from the sleep to the standby mode.

- 8. Read/Write On Track is defined as 50% read operations and 50% write operations on a single physical track.

# 4.6 ACOUSTICS

Table 4-6 and Table 4-7 specify the acoustical characteristics of the Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drives.

| OPERATING MODE | MEASURED NOISE<br>(SOUND PRESSURE)   | DISTANCE      |

|----------------|--------------------------------------|---------------|

| Idle On Track  | 32 dBA (typical)<br>35 dBA (maximum) | 39.3 in (1 m) |

## Table 4-6 Acoustical Characteristics–Sound Pressure

| Table 4-7 | Acoustical   | Characteristics-Sound Power |

|-----------|--------------|-----------------------------|

|           | 110000000000 |                             |

| OPERATING MODE |           | MEASURED NOISE<br>(SOUND POWER PER ISO 7779) |          |  |

|----------------|-----------|----------------------------------------------|----------|--|

|                |           | TYPICAL                                      | MAXIMUM  |  |

| Idle On Track  | I, 2-Disk | 3.5 Bels                                     | 3.6 Bels |  |

|                | 3, 4-Disk | 3.8 Bels                                     | 3.9 Bels |  |

# 4.7 MECHANICAL

| Height: 1.0 in. | (25.4 mm)                    |                  |

|-----------------|------------------------------|------------------|

| Width: 4.0 in.  | (101.6 mm)                   |                  |

| Depth: 5.75 in. | (146.1 mm)                   |                  |

| Weight:         | Quantum Fireball CR 4.3AT    | TBD lb (.xxx kg) |

|                 | Quantum Firebal CR 6.4/8.4AT | TBD lb (.xxx kg) |

|                 | Quantum Fireball CR12.73AT   | TBD lb (.xxx kg) |

# 4.8 ENVIRONMENTAL CONDITIONS

Table 4-8 summarizes the environmental specifications of the Quantum Fireball CR hard disk drives.

| PARAMETER                                                                 | OPERATING                                 | NON-OPERATING                              |  |  |  |  |

|---------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------|--|--|--|--|

| Temperature <sup>1</sup><br>(Non-condensing)                              | 5° to 55°C<br>(41° to 131°F)              | -40° to 65°C<br>(-40° to 149°F)            |  |  |  |  |

| Temperature Gradient<br>(Non-condensing)                                  | 24°C/hr maximum<br>(75.2°F/hr)            | 48°C/hr maximum<br>(118.4°F/hr)            |  |  |  |  |

| Humidity <sup>2</sup> (Non-condensing)<br>Maximum Wet Bulb<br>Temperature | 10% to 85% RH<br>30°C (86°F)              | 5% to 95% RH<br>40°C (104°F)               |  |  |  |  |

| Humidity Gradient                                                         | 30% / hour                                | 30% / hour                                 |  |  |  |  |

| Altitude <sup>3, 4</sup>                                                  | -200 m to 3,000 m<br>(-650 to 10,000 ft.) | -200 m to 12,000 m<br>(-650 to 40,000 ft.) |  |  |  |  |

| Altitude Gradient                                                         | 1.5 kPa/min                               | 8 kPa/min                                  |  |  |  |  |

Table 4-8

Environmental Specifications

- 1. Maximum operating temperature must not exceed the drive at any point along the drive form factor envelope. Airflow or other means must be used as needed to meet this requirement.

- 2. The humidity range shown is applicable for temperatures whose combination does not result in condensation in violation of the wet bulb specifications.

- 3. Altitude is relative to sea level.

- 4. The specified drive uncorrectable error rate will not be exceeded over these conditions.

# 4.9 SHOCK AND VIBRATION

The Quantum Fireball CR 4.3/6.4/8.4/12.7AT hard disk drives can withstand levels of shock and vibration applied to any of its three mutually perpendicular axes, or principal base axis, as specified in Table 4-9. A functioning drive can be subjected to specified operating levels of shock and vibration. When a drive has been subjected to specified nonoperating levels of shock and vibration, with power to the drive off, there will be no loss of user data at power on.

When packed in its 1-pack shipping container, the Quantum Fireball CR drives can withstand a drop from 30 inches onto a concrete surface on any of its surfaces, six edges, or three corners. The 12-pack shipping container can withstand a drop from 30 inches onto a concrete surface on any of its surfaces, six edges, or three corners.

|                                                           | OPERATING                                   | NONOPERATING                                                                                                                                        |

|-----------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Shock<sup>1</sup></b><br>1/2 sine wave, 11 ms duration | 20.0 Gs                                     | 70 Gs                                                                                                                                               |

| 1/2 sine wave, 3 ms duration                              | 18 Gs                                       | N/A                                                                                                                                                 |

| 1/2 sine wave, 2 ms duration                              | N/A                                         | I I 0 Gs<br>200 Gs Rotational: 15,000 rad/sec <sup>2</sup> 2 ms<br>applied at actuator pivot point<br>Trapezoidal: 80 Gs, 18 in/sec velocity change |

| Vibration <sup>1</sup>                                    |                                             |                                                                                                                                                     |

| Random Vibration (G <sup>2</sup> /Hz)                     | 0.004 (10 – 300Hz)<br>0.0006 (300 – 450 Hz) | 0.05 (10 – 300 Hz)<br>0.012 (300 – 500 Hz)                                                                                                          |

| Sine wave (peak to peak)<br>1/2 octave per minute sweep   | I GP-P 5-400 Hz                             | 2 Gs P-P 5–500 Hz                                                                                                                                   |

Table 4-9

Shock and Vibration Specifications

1. The specified drive unrecovered error rate will not be exceeded over these conditions.

## 4.10 HANDLING the DRIVE

Before handling the Quantum hard disk drive some precautions need to be taken to ensure that the drive is not damaged. Use both hands while handling the drive and hold the drive by its edges. Quantum drives are designed to withstand normal handling, however, hard drives can be damaged by electrostatic discharge (ESD), dropping the drive, rough handling, and mishandling. Use of a properly grounded wrist strap to the earth is strongly recommended. Always keep the drive inside its special antistatic bag until ready to install.

Note: To avoid causing any damage to the drive do not touch the Printed Circuit Board (PCB) or any of its components when handling the drive.

# 4.11 RELIABILITY

| Mean Time Between Failures (MTBF): | The projected field MTBF is 625,000 hours.<br>The Quantum MTBF numbers represent Bell-<br>Core TR-332 Issue #6, December 1997 MTBF<br>predictions and represent the minimum MTBF<br>that Quantum or a customer would expect from<br>the drive. |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Component Life:                    | 5 years                                                                                                                                                                                                                                        |

| Preventive Maintenance (PM):       | Not required                                                                                                                                                                                                                                   |

| Start/Stop:                        | 50,000 cycles at ambient temperature<br>(minimum)                                                                                                                                                                                              |

Note: CSS specification assumes a duty cycle of one power off operation for every one idle mode spin downs.

# 4.12 ELECTROMAGNETIC SUSCEPTIBILITY

.4 Volts/meter over a range of 20Hz to 20 MHz.

# 4.13 EMITTED VIBRATION

.07 Gs peak.

# 4.14 DISK ERRORS

Table 4-10 provides the error rates for the Quantum Fireball CR hard disk drives.

| Table | 4-10 | Error Rates |  |

|-------|------|-------------|--|

|       |      |             |  |

| ERROR TYPE                               | MAXIMUM NUMBER OF ERRORS               |

|------------------------------------------|----------------------------------------|

| Retry recovered read errors <sup>1</sup> | l event per 10 <sup>9</sup> bits read  |

| Multi read recovered errors <sup>2</sup> | l event per 10 <sup>12</sup> bits read |

| Unrecovered data errors <sup>3</sup>     | l event per 10 <sup>14</sup> bits read |

| Seek errors <sup>4</sup>                 | l error per 10 <sup>6</sup> seeks      |