W.A. WELCH

SERIAL NO.

PHILCO 2000 SYSTEM

COMPUTER, MODEL 210

MEMORY, SERIES 2200

PART II

# PHILCO CORPORATION

GOVERNMENT AND INDUSTRIAL GROUP • COMPUTER DIVISION 3900 WELSH ROAD, WILLOW GROVE, PENNSYLVANIA

# TABLE OF CONTENTS

|      |                   |                                                                                                                                                                                                | Page                                   |

|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1.   | TRAN              | ISISTOR SWITCHING CIRCUITS                                                                                                                                                                     | 1-1                                    |

|      | 1.1<br>1.2        | Introduction                                                                                                                                                                                   | 1 - Î<br>1 - Î                         |

| 2.   | PHIL              | CO 2000 CIRCUITS                                                                                                                                                                               | 2-1                                    |

|      | 2.1<br>2.2<br>2.3 | Standard Logic Circuits                                                                                                                                                                        | 2-1<br>2-6<br>2-9                      |

|      |                   | TRICAL FAULT DIAGNOSIS OF S-2000 LOGIC UITS                                                                                                                                                    | 3-1                                    |

|      | •                 | Introduction                                                                                                                                                                                   | 3-1<br>3-1<br>3-2                      |

|      |                   | Improper Use of Equipment  High Resistance or Open Solder Joints  Emitter-Follower Failures  Grounded-Emitter Failures  Printed Circuit Faults  High Resistance or Open Contacts  Other Faults | 3-3<br>3-5<br>3-6<br>3-6<br>3-7<br>3-8 |

| ,    |                   | Detection of Faults with the Oscilloscope                                                                                                                                                      | 3-9<br>3-15                            |

| 4. 1 | MAGI              | VETIC CORE MEMORY                                                                                                                                                                              | 4-1                                    |

| 4    | 4.2<br>4.3        | Principles of Operation                                                                                                                                                                        | 4-1<br>4-5<br>4-8<br>4-11              |

# LIST OF ILLUSTRATIONS

| Figure |                                           | Page          |

|--------|-------------------------------------------|---------------|

| 1-1    | Conducting Junction                       | 1-12          |

| 1-2    | Back-Biased Diode Junction                | 1-12          |

| 1-3    | PNP Junction Transistor                   | 1-12          |

| 1-4    | Inverter                                  | 1-12          |

| 1-5    |                                           | 1-13          |

| 1-6    | Direct Coupled Transistor Circuitry       | 1-13          |

| 1-7    | RC Circuit                                | 1-14          |

| 2-1    | Inverter or Common Emitter Circuit        | 2-20          |

| 2-2    | Emitter Follower Circuit                  | 2-20          |

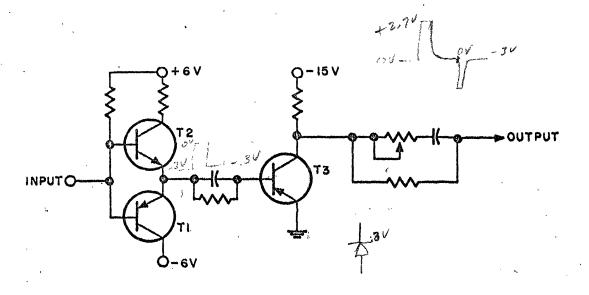

| 2-3    | Common Emitter-Emitter Follower           | 2-20          |

| 2-4    | Series or Two High Gate                   | 2-21          |

| 2-5    | Parallel Collector Gate                   | 2-21          |

| 2-6    | Parallel Emitter Follower Gate            | 2-22          |

| 2-7    | Parallel RC Gate                          | 2-22          |

| 2-8    | Two High Selection Tree                   | 2-23          |

| 2=9    | Two High Selection Gate                   | 2-24          |

| 2-10   | Flipflop                                  | 2-25          |

| 2~11   | Resistance Coupled Single Shot            | 2-26          |

| 2-12   | Neon Driver                               | 2-27          |

| 2-13   | Relay Driver                              | 2-27          |

| 2-14   | Manual Set Circuit                        | 2-27          |

| 2-15   | CA Card                                   | 2-28          |

| 2-16   | SSI Module                                | 2-29          |

| 2-17   | Computer and Console                      | 2-30          |

| 2-18   | Computer Neon Identification              | 2-31          |

| 2-19   | Memory and Index Registers Cabinets (8192 |               |

|        | Word Memory)                              | 2-32          |

| 2-20   | Power Supply Front Panels, Block          | 2-33          |

| 2-21   | Power Supply Cabling                      | 2-34          |

| 2-22   | Power Supply Control Circuit              | 2=35          |

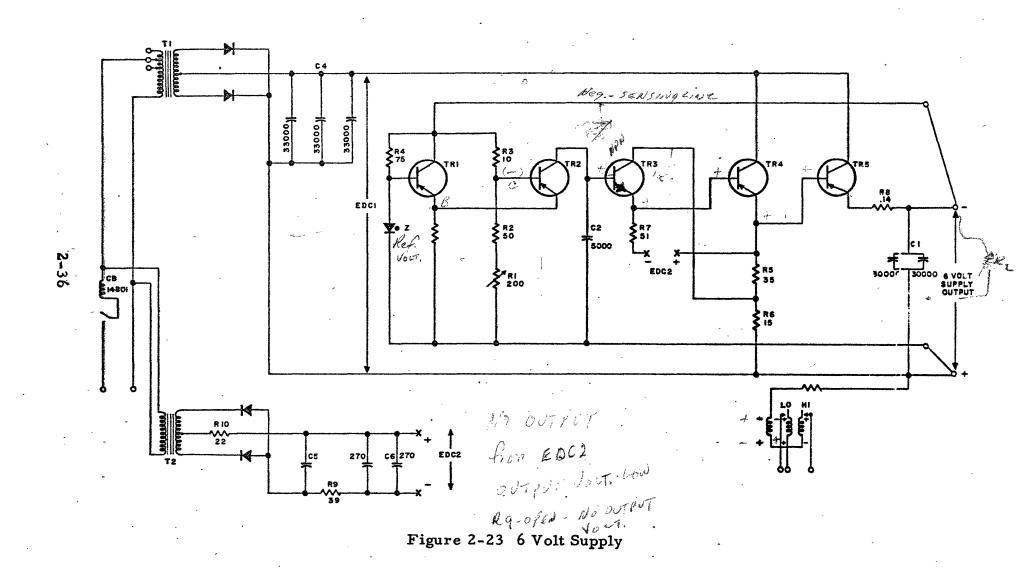

| 2-23   | 6 Volt Supply                             | 2-36          |

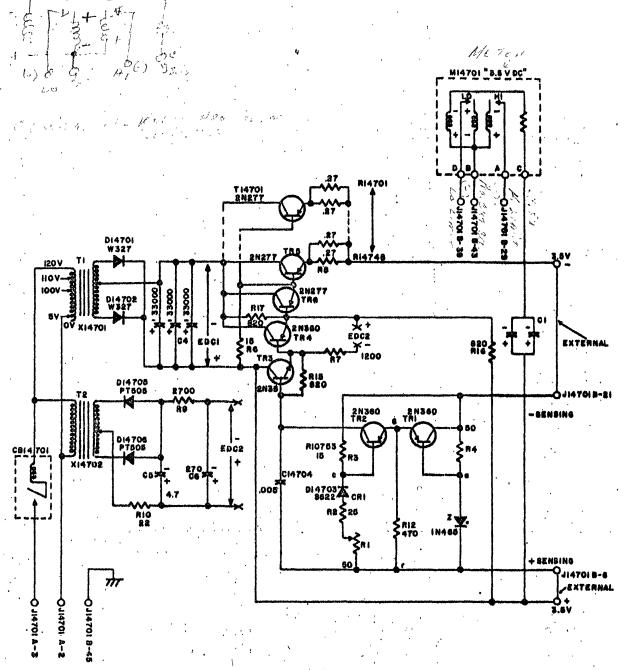

| 2-24   | 3.5 Volt Supply                           | 2-37          |

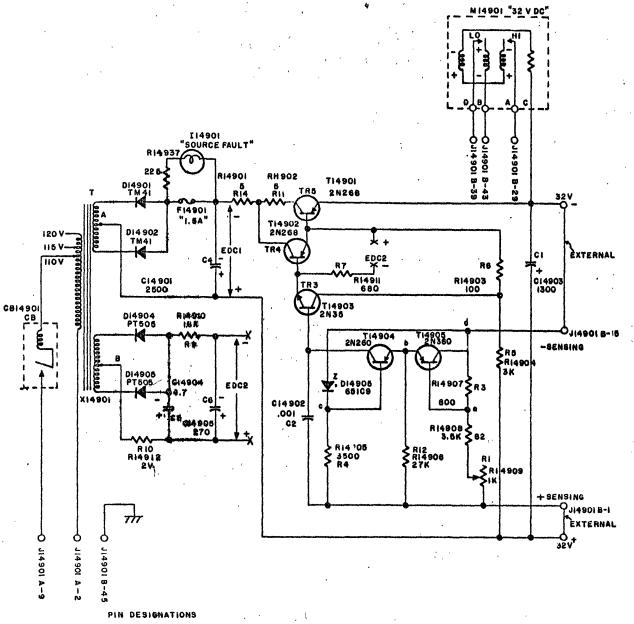

|        | 32 Volt Supply                            | 2-38          |

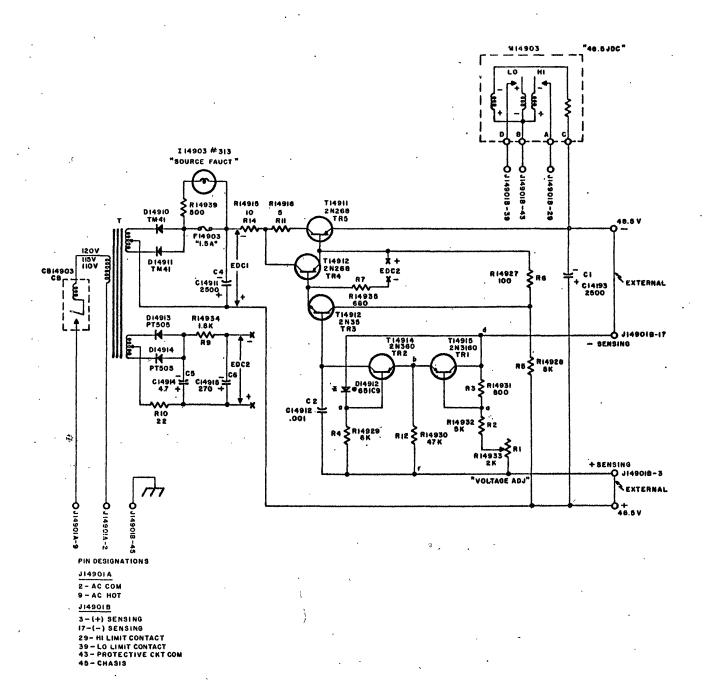

| 2-26   | 48.5 Volt Supply                          | ,             |

| 2-27   | 41.5 Volt Supply                          | 2-40          |

| 3-1    | Illustrative Logic Circuit                | 3 <b>-</b> 16 |

# LIST OF ILLUSTRATIONS (Continued)

| Figure      |                                             | Page   |

|-------------|---------------------------------------------|--------|

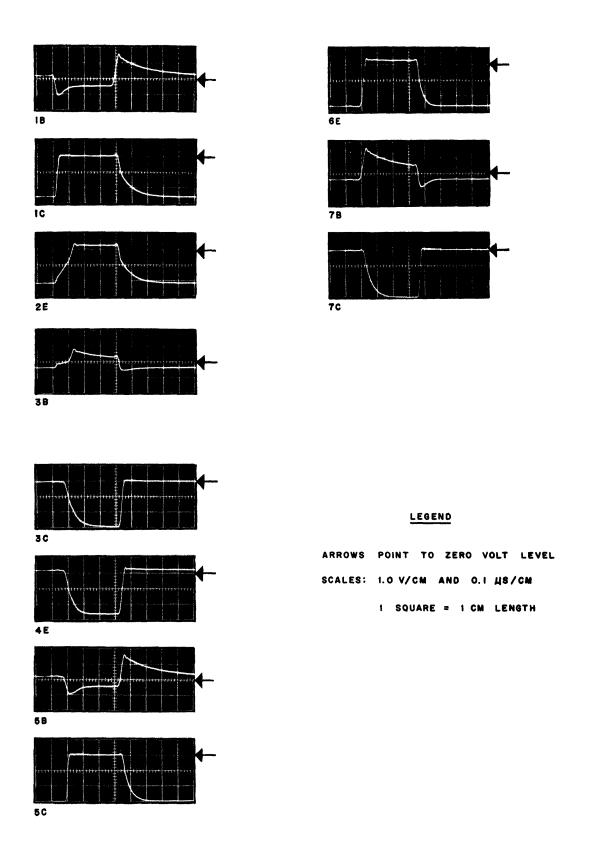

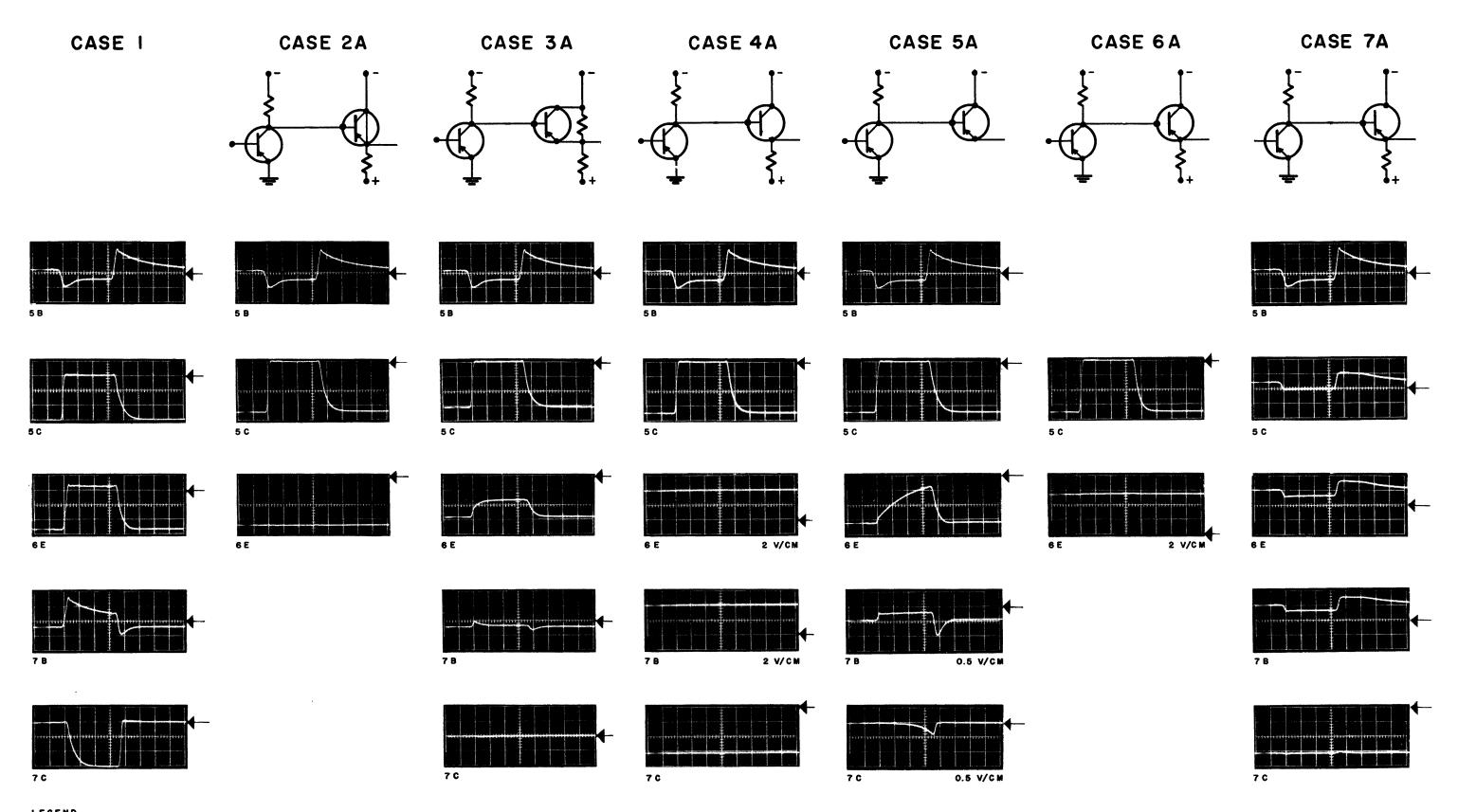

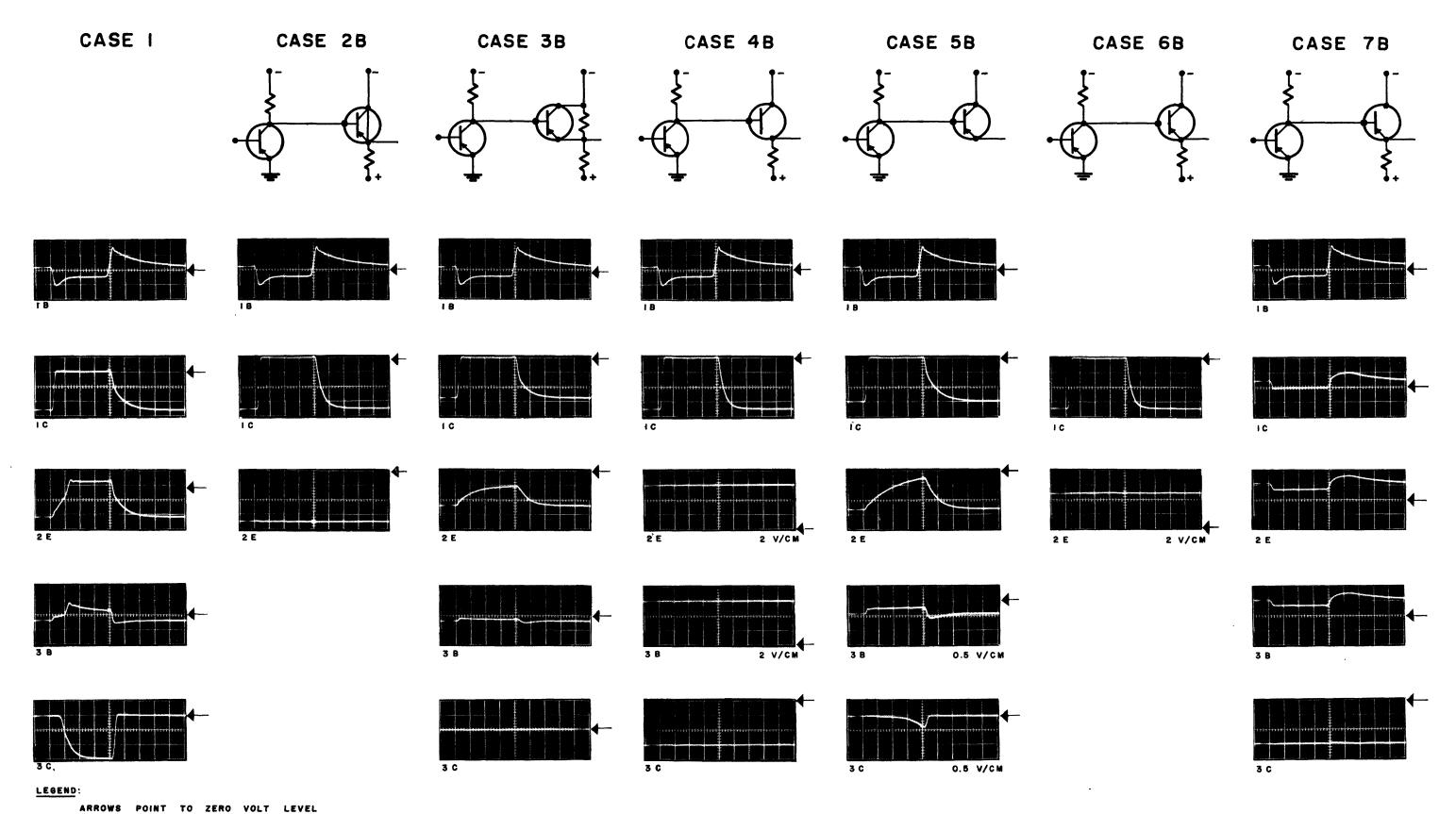

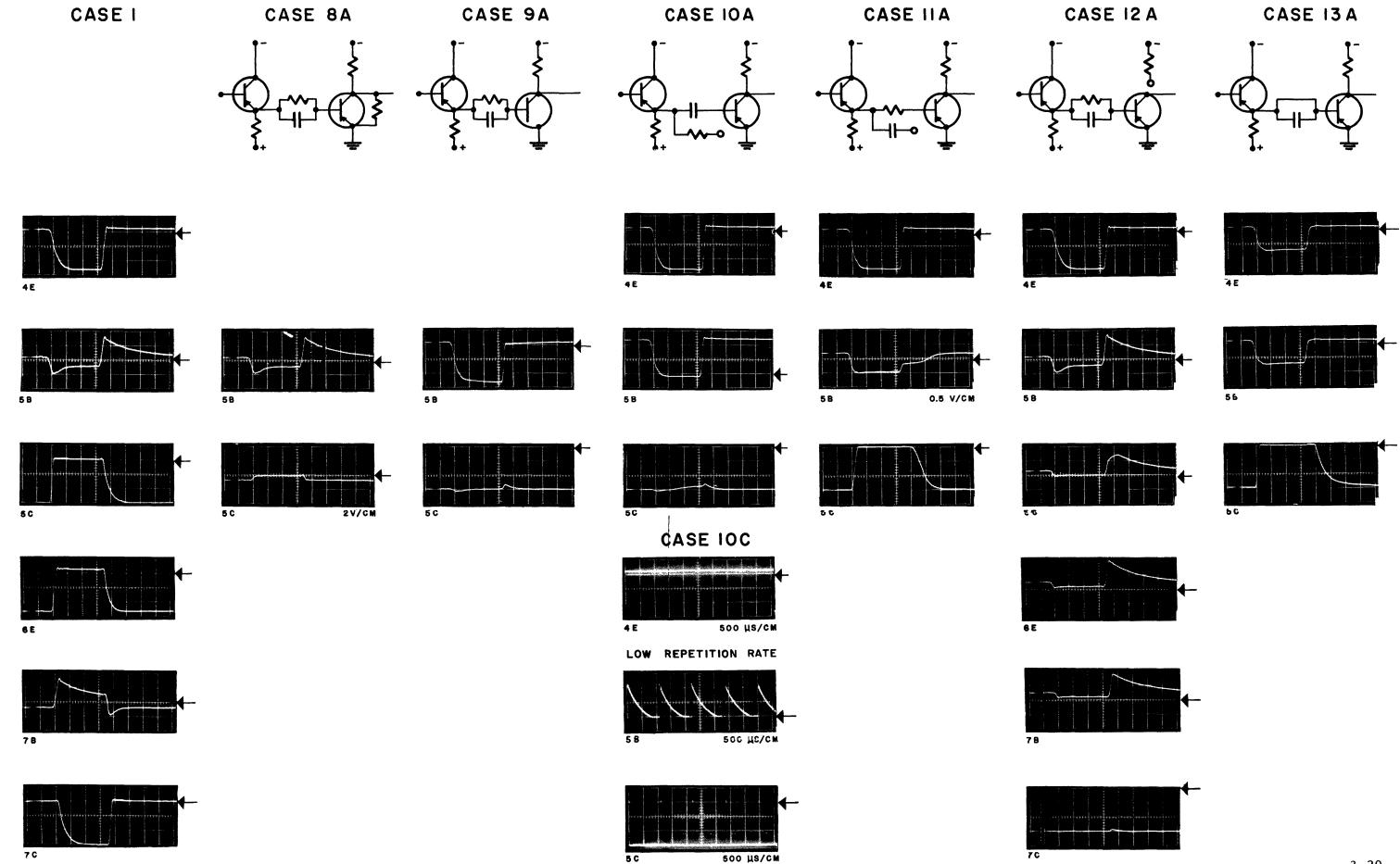

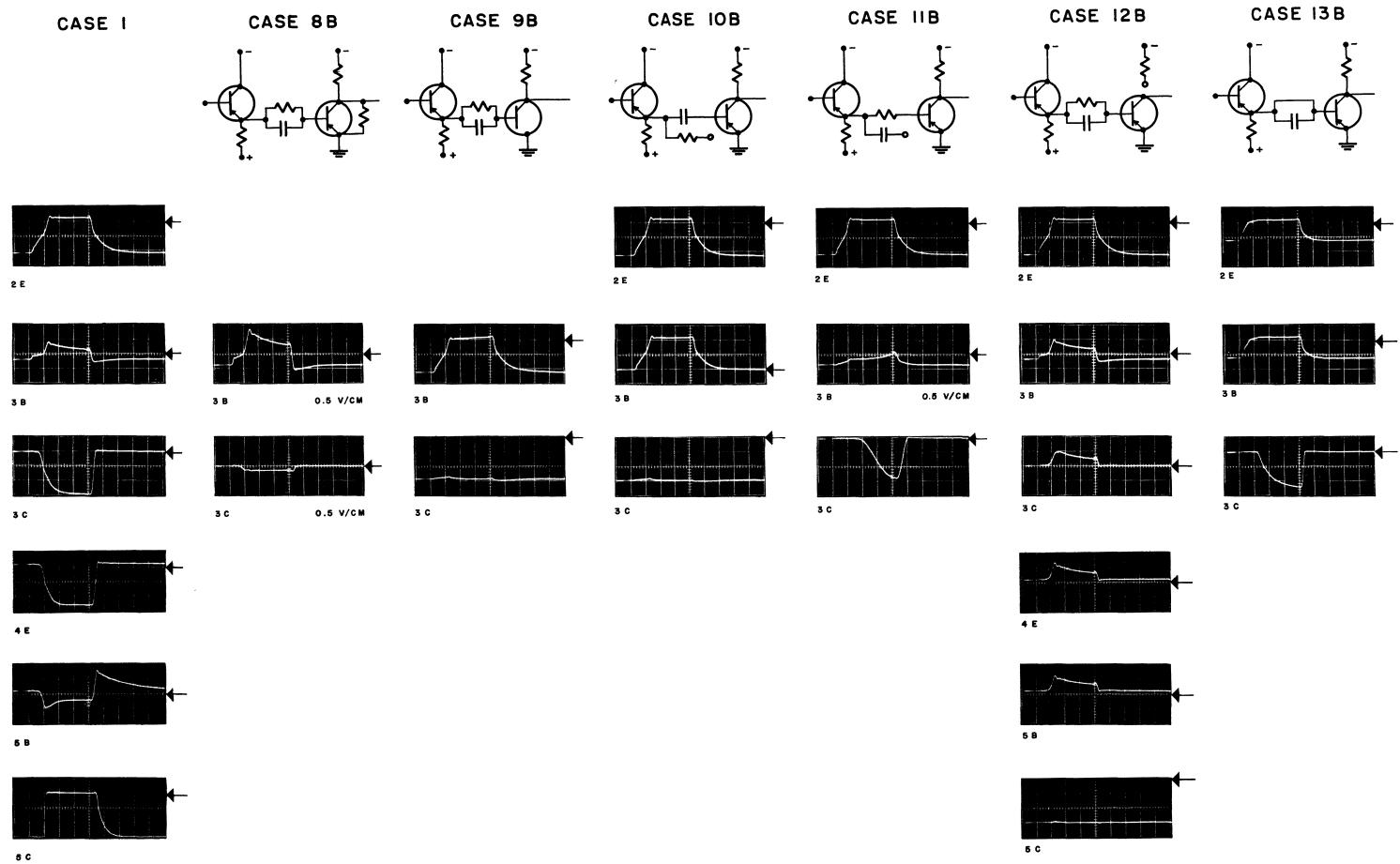

| 3-2         | Case I, Normal Circuit                      | 3-17   |

| 3-3         | EF Troubles, Light Loading                  | 3 • 18 |

| 3-4         | EF Troubles, Heavy Loading                  | 3-19   |

| 3 <b></b> 5 | GE Troubles, Light Loading                  | 3-20   |

| 3•6         | GE Troubles, Heavy Loading                  | 3-21   |

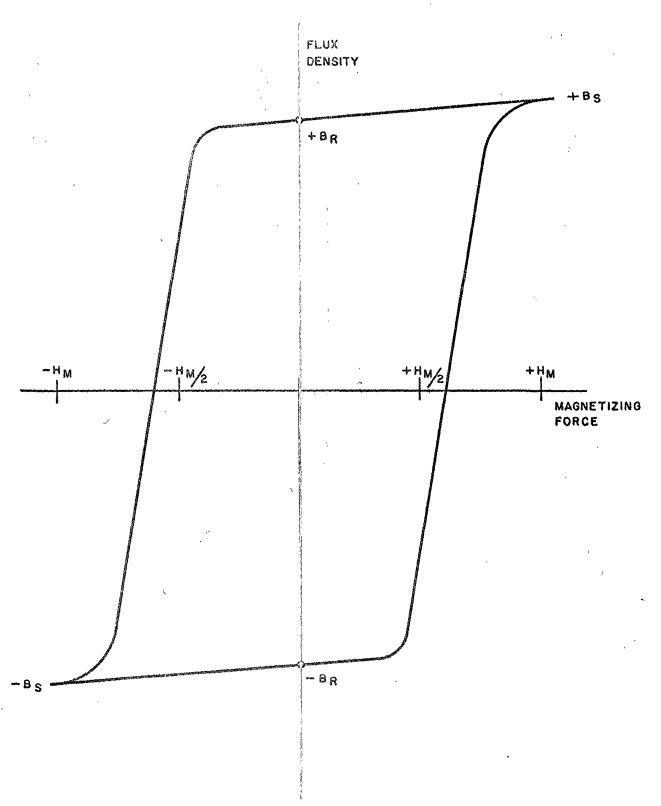

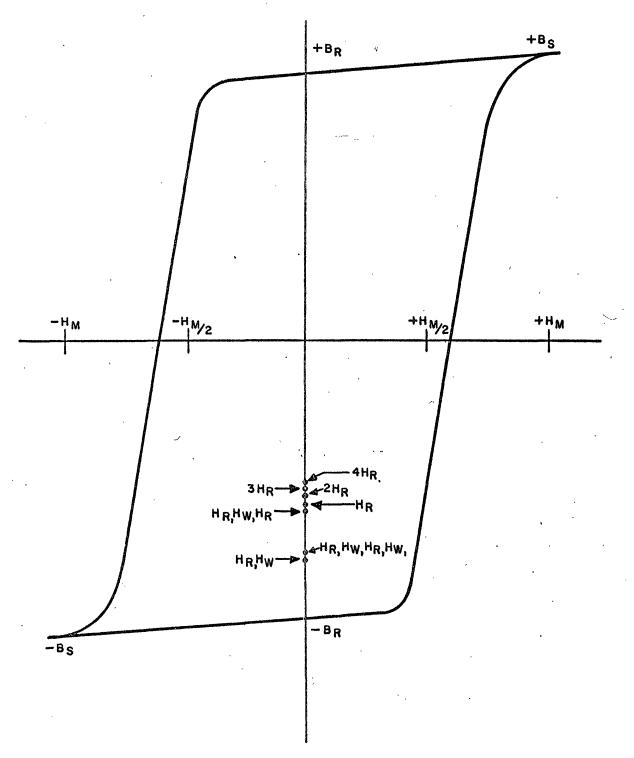

| 4-1         | Rectangular B+H Loop                        | 4-17   |

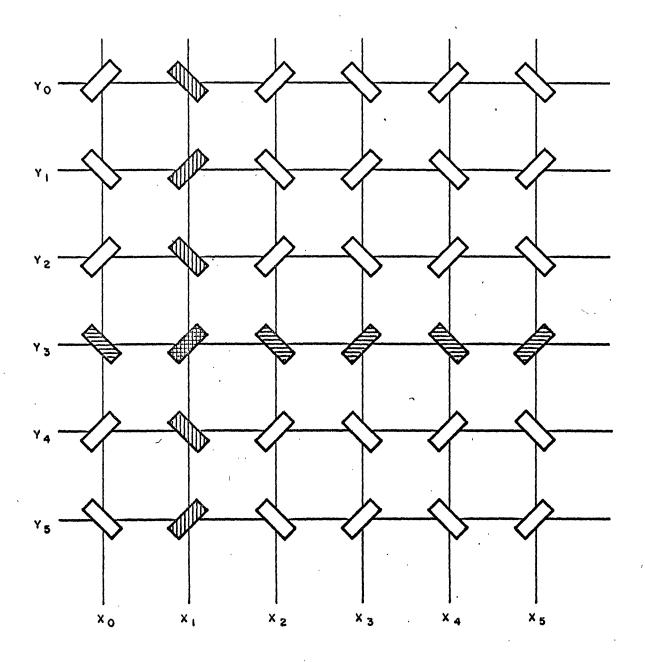

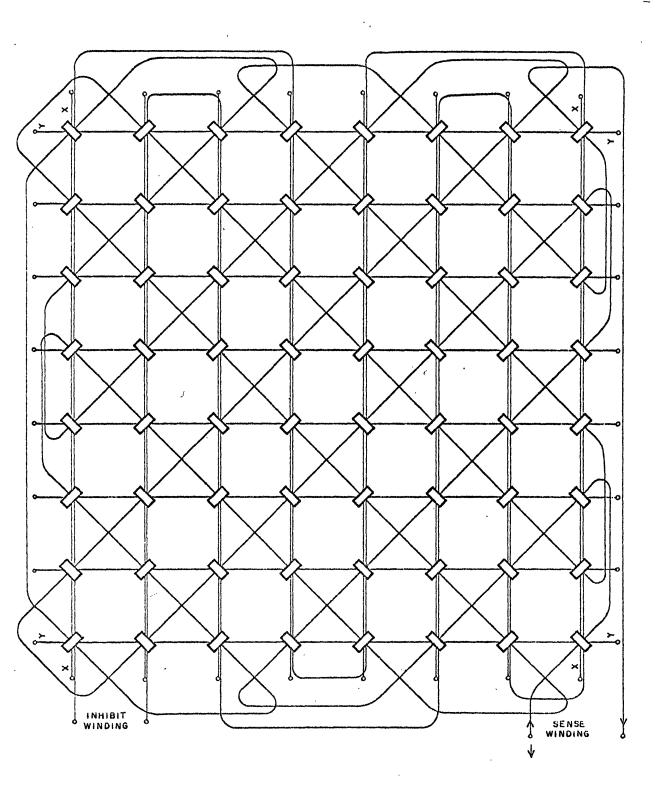

| 4-2         | 36 Bit Core Plane                           | 4-18   |

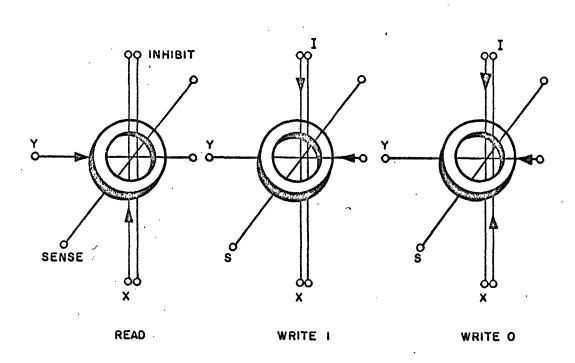

| 4-3         | Current Direction for Various Functions     | 4-19   |

| 4-4         | Half Selected Core Response                 | 4-20   |

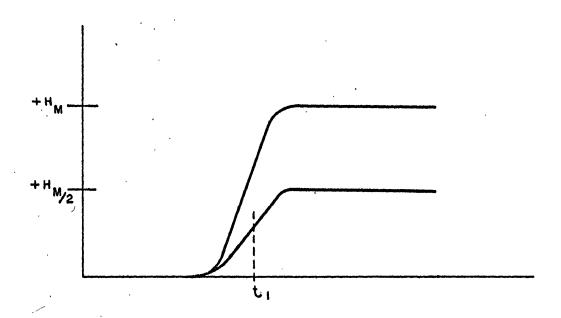

| 4-5         | Current Rise Times in Driver Core           | 4-21   |

| 4-6         | 8 x 8 Core Plane Writing Schematic          | 4-22   |

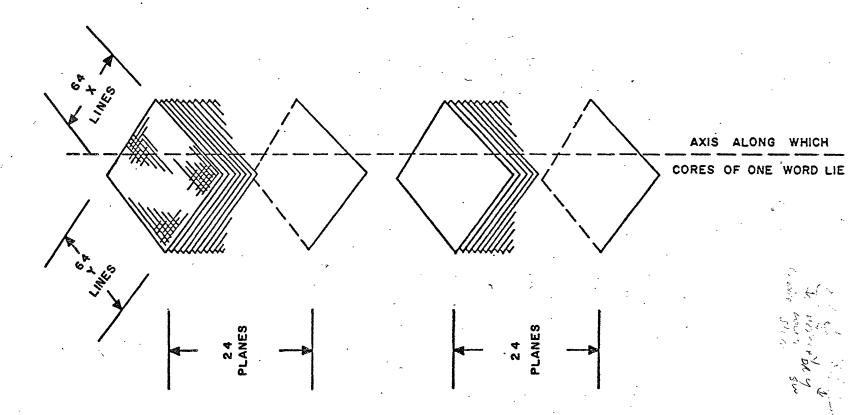

| 4-7         | Memory Core Stack                           | 4.23   |

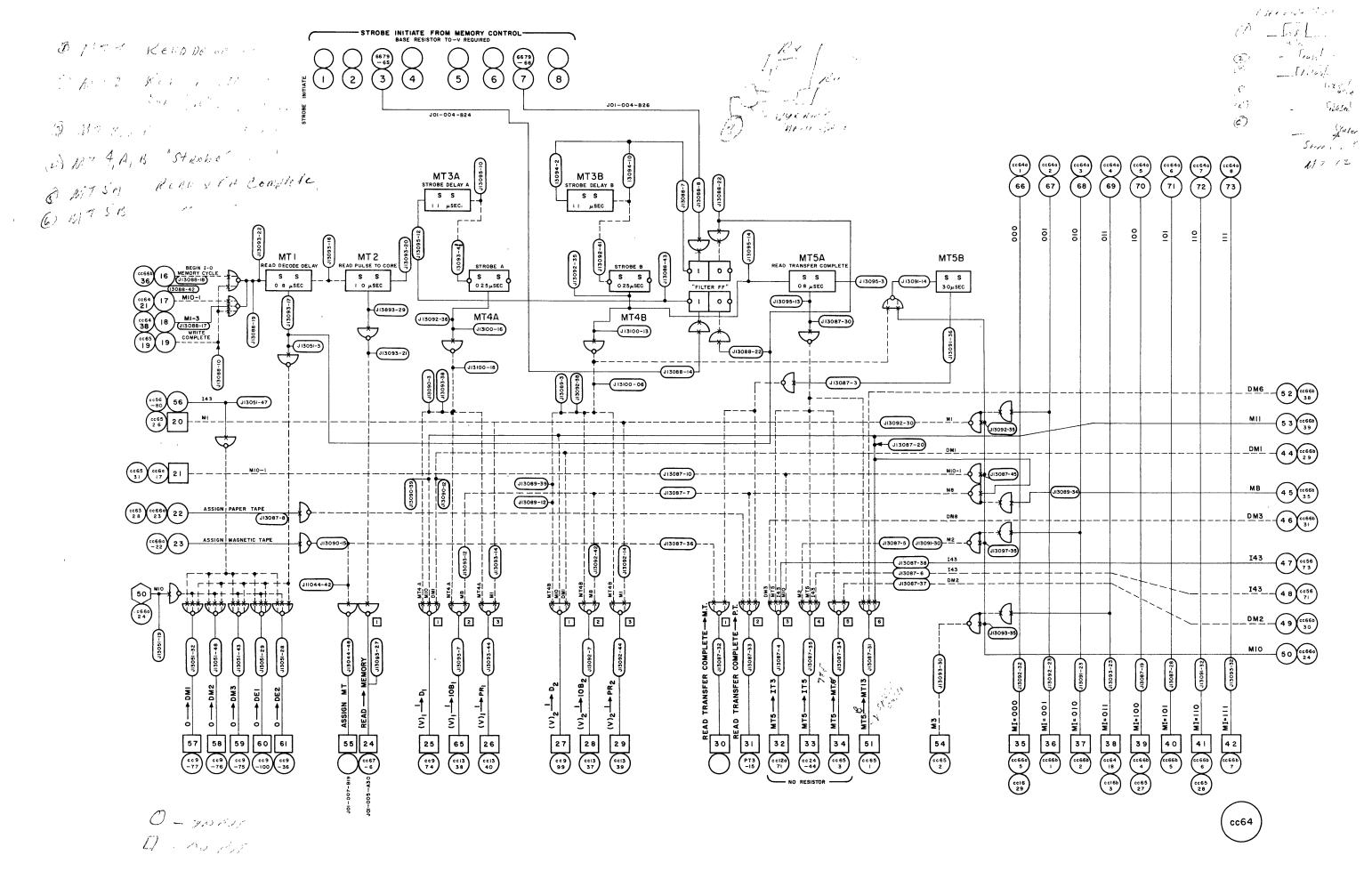

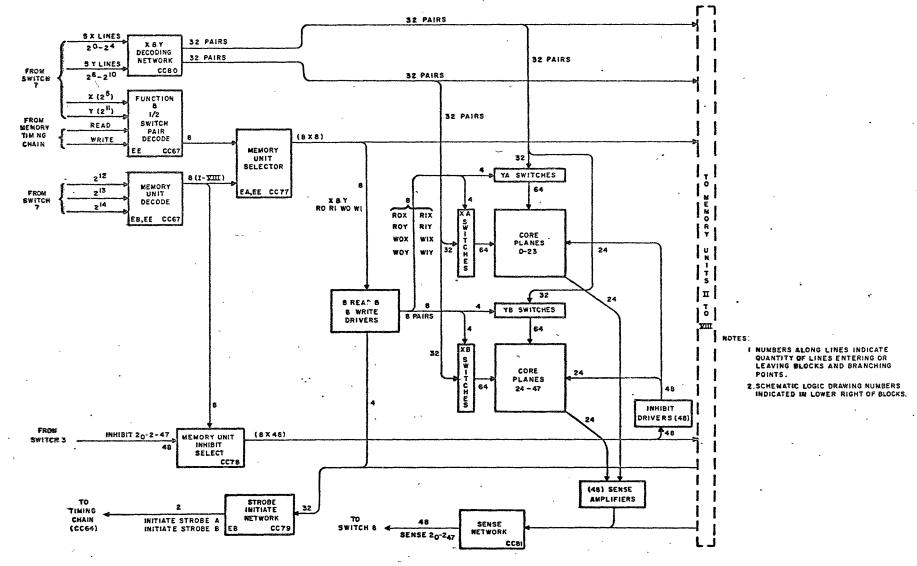

| 4-8         | Block Diagram - Memory Signal Routing       | 4-24   |

| 4-9         | Memory Timing Chain for Read (Sheet 1 of 2) | 4-25   |

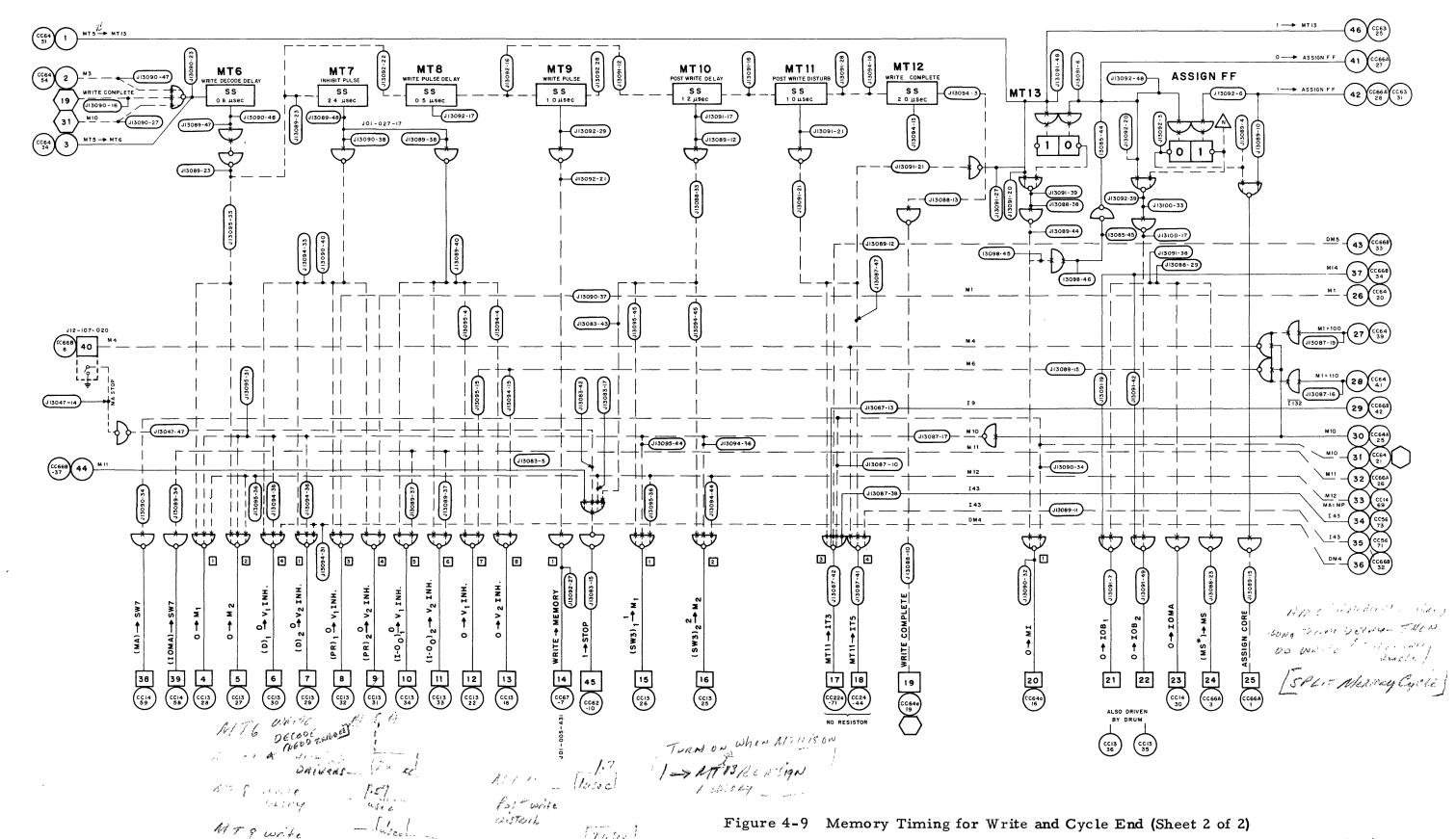

| 4-9         | Memory Timing for Write and Cycle End       |        |

|             | (Sheet 2 of 2)                              | 4-26   |

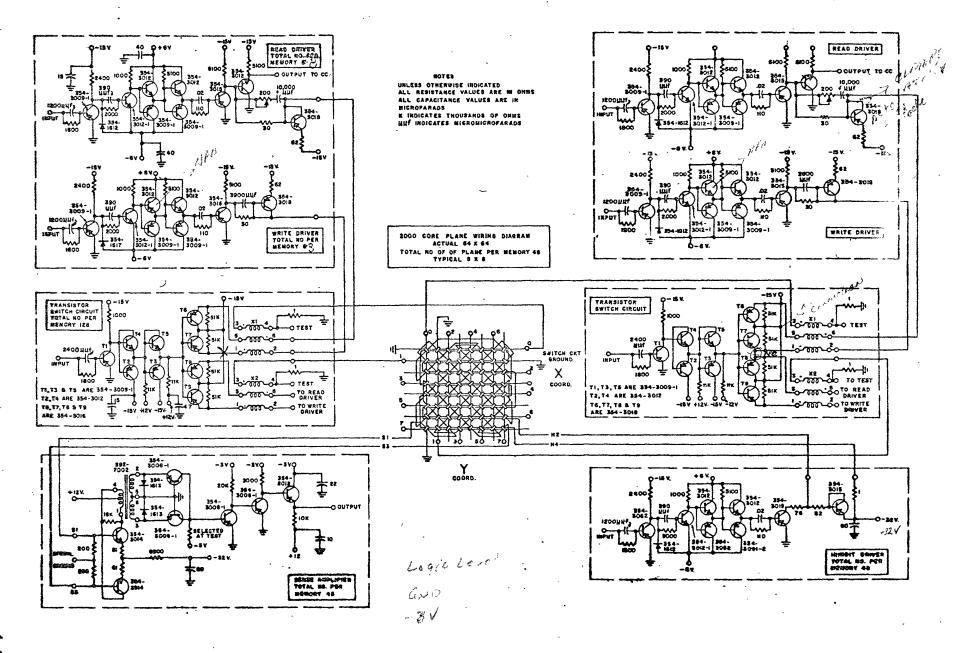

| 4-10        | PHILCO 2000 Memory Circuits                 | 4-27   |

| 4-11        | Complementary Symmetry Circuit              | 4-28   |

# 1. TRANSISTOR SWITCHING CIRCUITS

# 1.1 INTRODUCTION

PHILCO 2000 uses all transistor logical circuitry. Accordingly, a good working knowledge of the operation of transistor digital circuits is essential to anyone maintaining the machine.

This section will describe in detail a theory of transistor operation, leading through transistor digital circuits, S-2000 logical circuits and hardware arrangement. A theory of transistor operation is presented to give some insight which may help to understand why transistor circuits behave as they do. Also described are special driver circuits, A.C. distribution and control scheme and the D.C. transistor power supplies.

The discussion of transistor operation will concern principally the germaium junction type of transistor. Operation of the junction transistor is essentially similar to the surface barrier type used in S-2000.

#### 1.2 PRINCIPLES OF TRANSISTOR SWITCHING

A transistor at first examination appears to be nothing more than two semiconductor diodes (rectifiers) connected back to back. Therefore, the study may reasonably begin with the basic P-N junction which forms a semiconductor diode. Following will be an extension to transistor operation and then a study of basic amplifier circuits.

#### P-N JUNCTION

The basic diode junction might be loosely defined as an area where in nearly pure germanium changes in impurity concentration in a very specific manner. Minute concentrations of impurities in germanium material have a profound effect upon its conducting ability.

#### GERMANIUM PROPERTIES

Germanium is classed as a semiconductor material.

Apparently it is neither a good conductor nor a good insulator. Metals, being good conductors, are characterized by the presence of many free electrons due to their atomic structure. Conversely, good insulators have

practically no free electrons because the electrons are tightly bound by an interatomic relationship. A semiconductor material has its electron bonds relatively easily broken by heat energy so that it has appreciable conduction at room temperature. The number of free electrons which may be found is a function of temperature and increases with increasing temperature.

Atoms of a material are held together because they tend to share electrons so that the imperfection of each atom is complemented by adjacent atoms. Thus, pure germanium with four electrons of the eight electrons needed to fill the outer electron shell is bound in a crystaline lattice structure similar to a diamond (carbon). Each atom shares the electrons with its neighbor.

However, as stated above, at room temperature germanium is observed to be a reasonably good conductor. Not all of the electrons are bound in the crystaline lattice. Due to temperature agitation many are able to escape. The free electrons can serve as a means of conducting current. If a voltage is applied across the crystal so that an electric field is set up within the crystal the electrons will drift toward the positive electrode. Electrons pass into the positive electrode from the crystal and are supplied to the crystal from the negative electrode. So far the discussion sounds very similar to current condution through a wire. The difference is that those electrons existing in the crystal are thermally generated.

Generation of a free electron from the interatomic structure implies that a vacancy must exist in the atomic lattice due to departure of the electron from the structure. This vacancy called a "hole" has a positive charge equivalent to the charge of the missing electron. Moreover, this hole is free to move through the crystal. Motion is accomplished by filling the vacancy from an adjacent atom thereby creating a new hole as a result of eliminating the former one. Now to embellish the picture above a little more, let us assume that a voltage is applied as above. Electron flow is from the crystal to the positive electrode. Hole movement is toward the negative electrode because electrons are supplied at that point.

The concept of electron and hole conduction is a very important concept for the understanding of transistor operation. Already familiar is the concept of electron flow normally used for vacuum tubes where current flow is known to exist almost entirely by means of electrons. Less sophisticated scientists years ago admittedly did not know which polarity the current carriers had nor were they sure that current was carried by only one type of carrier. Their choice of "conventional flow

(from the positive source) has been used successfully to explain, in a consistant manner, most of the phenomena found in electrical science. "Electron" flow may be employed with equal success. We may conclude that the choice of current flow, no matter how absurd it may seem, in view of actual physical theory, may be a very satisfactory tool for understanding. Moreover, since the electrons or holes or whatever there are never become confused by man's conventions, we are relatively free to select any convention we wish as long as it is applied in exactly the same manner each time and the results are predicted with accuracy. In this discussion as in any other such discussion of semiconductors, the use of two current carriers or "carriers" (electrons and holes) makes the understanding of transistor operation much simpler. Scientists have found that the two carriers actually have some distinctive individual characteristics although they differ essentially only in the matter of polarity.

The conducting ability of germanium at a given temperature may be enhanced by the addition of minute quantities of impurities into the crystaline structure.

# DOPING TO GIVE N TYPE OR P TYPE MATERIAL

A number of chemical elements are similar to germanium (such as carbon above). Also a number of chemical elements have five of the eight electrons needed to fill the outer shell and there are chemical elements having three of the eight electrons.

Suppose one such element, Arsenic, is added to the germanium lattice. Arsenic is a material having five electrons in its outer electron shell. In the lattice four of its five electrons complete the interatomic structure of the crystal. The fifth atom is free to move in a random fashion because it is not required by the lattice of the crystal. The crystal conduction is improved because of the free electrons thus made available. The crystal is called "N" type because it can act as a donor of electrons.

Suppose, instead, that Indium is added to the germanium lattice. Indium is a material having three electrons in its outer electron shell. In the lattice all three of its electrons are used and a vacancy exists as well. This vacancy is usually termed a "hole". The crystal is called "P" type because it can act as an acceptor of free electrons. The crystal conduction is improved because electrons can be supplied externally at one contact point and removed at another contact point. Conduction may be assumed to occur by holes rather than electrons.

One must realize that there are always two types of carriers present in a particular structure (N or P type) simultaneously.

One carrier is the "majority" carrier due to doping as discussed. "The other carrier is the "minority" carrier due to breaking of the bonds to thermally. Thus pure germanium at some temperature above absolute zero will have an equal number of carriers (holes and electrons). Doped germanium at the same temperature will have the same total number of carriers but the largest number of them will be either holes or electrons depending upon how the material was doped.

#### SURFACE CHARACTERISTICS

As just discussed, doping of the germanium can produce either N or P type material. Both N and P type characteristics can be found in a crystal of N type germanium near the surface of the crystal. As discussed above, sharing of electrons completes the outer electron shell of each atom with eight electrons, a full shell. However, near the surface of the crystal there are no adjacent atoms from which to borrow electrons. Electrons are drawn from the internal body of the N type crystal to help complete these shells. After some of the closer electrons have moved to the surface, a net negative charge accumulates near the surface tending to repel any further electrons so that a barrier is set up. Thus on the surface side of the barrier a predominantly acceptor material exists (holes) and on the crystal side of the barrier a predominantly donor material exists (electrons). This mechanism for hole production is important for the surface barrier transistor but is not used in the junction transistor.

Having understood the concept of hole and electron carriers, one is ready to study rectifier action of the junction

# UNIDIRECTIONAL CONDUCTION

More precisely defined, a junction is the area where in the donor-acceptor concentration of the germanium changes in a specific manner. The rectifying junction is contained in a single crystal of material. The donor to acceptor concentration changes across the junction from P type to N type. The change may be abrupt or gradual with minor significance in regard to operation but is generally considered to be abrupt for purpose of explanation.

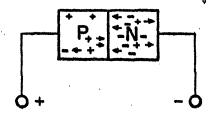

Assume such a junction as shown in Figure 1-1, last page of this chapter. With voltage applied across the junction having the indiscated polarity the N type region is made negative with respect to the P type region. Free electrons and holes (majority) carriers are swept to-

ward the junction from N and P type material respectively and cross it to combine. Since there are a large number of current carriers moving across the junction, the resistance of the junction is very low. The voltage drop across the junction is typically a fraction of a volt. Only the majority carriers are important here.

If the applied voltage is reversed, the minority carriers become important.

#### LEAKAGE CURRENT

With voltage applied as in Figure 1-2, the majority carriers are drawn away from the junction. However, the minority carriers (generated by thermal agitation) tend to move to the junction where they recombine. Thus a small "leakage" current flows. This current tends to remain nearly constant without any relation to the applied voltage (if greater than about -0.1 volt) until a point is reached where current increases rapidly as voltage is increased. This is the breakdown point and the voltage is called the breakdown voltage of the junction. The most common mechanism of breakdown is by avalanche where collisions of carriers and atoms results in generation of additional carriers due to the large energy supplied to the original carriers.

Since the minority carriers result from thermal agitation, leakage increases as the temperature increases. Moreover, leakage does not increase directly with temperature but rather very much more rapidly (nearly doubles with each  $10^{\circ}$ C increase). For this reason, careful attention to the ambient temperature of any junction is extremely important. While careful circuit design may allow a relatively wide range of temperature, a germanium diode or transistor becomes relatively useless in the region above about  $75^{\circ}$  C because of leakage current. Silicon types are usable somewhat above  $125^{\circ}$ C. Typical designs with germanium material permit operation around 40 to  $50^{\circ}$ C maximum where no special attention is given to temperature compensation. S-2000 has no special temperature componsating circuit design because the ambient temperature is not expected to become excessive.

#### TRANSISTOR ACTION

The junction transistor is essentially two P-N junctions back-to-back with a region common to both junctions. They may be arranged P-N-P or N-P-N depending upon the manufacturing technique

and the circuit requirements. Operation of the two types is essentially the same. The P-N-P is the more common type. The following explanation applies also to N-P-N junction transistors if the terms "electrons" and "holes" are interchanged.

# TRANSISTOR OPERATION

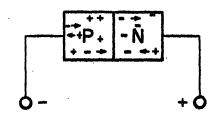

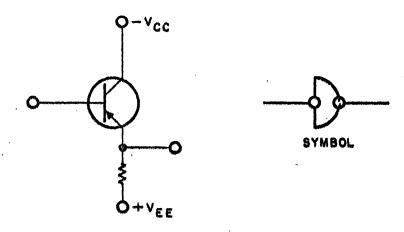

Shown in Figure 1-3 is the arrangement and symbol for the P-N-P junction transistor. External circuit connections are such that the left hand junction is usually forward biased (electron flow is from base to emitter). In other words the emitter and base are functioning as a junction diode in its forward conducting direction. The collector and base junction is reverse-biased so that leakage current would flow. However, one osbserves a much larger current than that due to leakage alone. The explanation is that not all of the carriers entering the base region from the emitter recombine in the base. Most of the carriers diffuse across the base and enter the collector region due to the electric field set up by the reverse collector-sbase bias. The carriers crossing into the collector are minority carriers in the collector region. As previously discussed, these carriers recombine in the collector region and provide current flow through the base-collector junction. There are two components of collector current: (1) that due to leakage of the reverse biased collector-base junction and (2) and that due to holes emitted from the emitter which survive the trip across the base region and enter the collector.

Obviously not all of the holes can cross the base. Some are bound to recombine in the base region. However, 98% to 99% of them are successful as a rule. The base region is very narrow so that carriers stand an excellent chance of crossing without recombining.

To summarize, the emitter-base junction is forward biased to a varying degree by controlling the current flow for the purpose of injecting holes into the base region; the collector-base junction is reverse biased for the purpose of collecting nearly all of the emitted holes. Power amplification occurs because the forward voltage drop of the emitter-base junction is very small (usually a few tenths of a volt) whereas the collector-base voltage is comparatively high (limited only by the breakdown voltage of the junction). Thus the product of collector voltage and current is higher than the product of emitter voltage and current even though the emitter current is a little greater than the collector current.

Transistors have some terms applied to them which are similar to vacuum tube terminology. A transistor is "cut-off" when only leakage current flows across the collector-base junction. This corresponds to minimum emitter-base current or a reverse biased emitter-base junction. A P-N-P transistor is "saturated" when holes are injected into the base region much more rapidly than they can be removed by the available collector current. The "dissipation" of a transistor is approximately the product of the collector-base voltage and the collector current. Both "cut-off" and "saturation" conditions provide the minimum dissipation for a transistor. At "cut-off", the collector current is very small. At "saturation", the collector-base voltage is very small (a few tenths of a volt). Thus for digital applications (on-off) a small transistor may operate a load in watts many times greater than its maximum dissipation (15 or 20 times). Such a feat could hardly be expected from vacuum tubes. Because drift due to changing leakage current can be effectively "designed out" of digital circuitry and because of its high efficiency as an electronic switch the transistor is ideally suited to digital circuits with one qualification. It should always operate in the region where it is either close to "cut-off" or "saturation". Otherwise depending upon circuit design, dissipation may become excessive and prevent proper operation of the circuit and possible destruction of the transistor.

# SURFACE BARRIER TRANSISTOR

The surface barrier has the same characteristics as any other P-N junction. Only the method of carrier production is different. Thus when the emitter-base junction is forward biased, holes are repelled from the barrier region into the crystal by the metalic electrode attached to the crystal. Similarly to the junction transistor, the injected holes diffuse across the narrow base region to recombine at the collector surface barrier or junction.

#### TIME CONSIDERATIONS

The speed of response of a transistor circuit is dependent upon the particular transistor employed and the circuits into which it is designed. In general, the larger transistors are relatively slower in speed of response than the smaller transistors. One of the most significant problems in digital circuits is the phenomena of minority carrier storage in the base region when the transistor is operated in a saturated mode. Because holes are being injected into the base region faster than the collector can remove them, they tend to accumulate to some degree with

time. Then when the transistor is switch off by reducing the emitter base current, the collector current continues until the minority carriers are all swept out by the collector.

#### TRANSISTOR AMPLIFIER-SWITCH

As discussed above, the transistor is a highly efficient switch and provides power amplification as well. One may show many similarities to vacuum tube circuit arrangements. However, there are some striking differences as well. Following is a discussion of the basic circuits compared and contrasted with vacuum tube equivalent circuits.

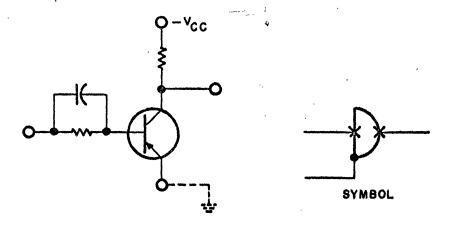

#### TRANSISTOR INVERTER

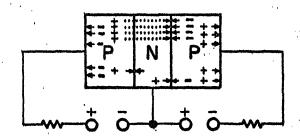

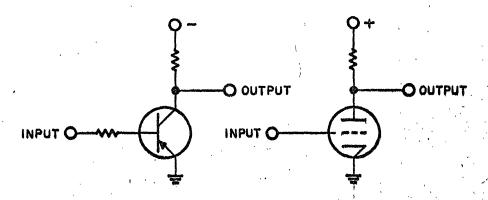

Figure 1-4 shows a transistor inverter circuit and a vacuum tube inverter circuit arranged to operate in substantially the same manner. The principal difference is that the transistor is controlled by current supplied to the base such that the emitter-base junction is forward biased whereas the vacuum tube is controlled by the voltage applied between the cathode and the grid. Assume both the transistor and the tube are "cutoff". This would be obtained by a negative signal on the grid for the tube. The transistor would be cut-off by a slightly positive voltage from base to emitter. Output terminal (a) is at the same potential as the supply voltage. If a positive going signal is applied to the grid of the tube (relative to ground) such that the effect of the previous negative signal is cancelled, the tube conducts heavily and terminal (a) changes to a very small value of voltage. Similarly as the base of the transistor has applied a negative going signal: such that emitter base current flows, increased current flow through the transistor changes the potential of terminal (a) to a very small value of voltage.

Since the tube is made "active" or conducting by the positive signal which in turn causes the tube output load voltage to be less positive, the tube circuit is termed an inverter. Similarly the transistor is an inverter because a negative signal caused the output of the transistor circuit to be less negative. A "grounded cathode" tube circuit is thus shown to be nearly equivalent of a "grounded emitter" transistor circuit in function. There are two differences in the circuits shown, the P-N-P transistor operates with negative going signals instead of positive going signals and current <u>must</u> be supplied to control a transistor.

The control current required by the transistor is typically

about 1/20 to 1/50 of the load current it switches in a grounded emitter configuration although in some particular transistors a much smaller current may be adequate.

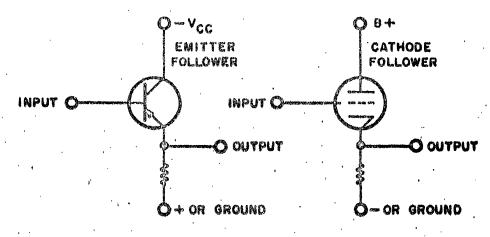

Although there are a variety of different circuit equivalents between the two devices, the only other one here considered is the emitter follower transistor circuit and its vacuum tube equivalent.

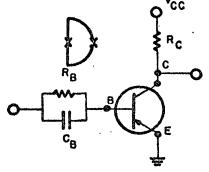

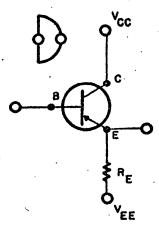

# TRANSISTOR EMITTER FOLLOWER

The "emitter follower" transistor circuit is very similar to the vacuum tube "cathode follower" circuit, (See Figure 1-5). The cathode of the vacuum tube tends to follow any variation of the grid voltage relative to ground. It does not change quite as much as the grid voltage so that some slight loss of voltage swing results. Similarly the emitter of the transistor tends to follow the base voltage changes and a slight loss of voltage swing also results. Both circuits find application where power amplification (increased current capacity) is required and/or a lower driving impedance is needed for circuits driven by them. Both circuits do not invert the input signal. The output changes in the same direction as the input.

# SBT OPERATING CHARACTERISTICS

A surface barrier transistor, as used in S-2000, when switched "on" has only a fraction of a volt dropped across it. Typically this voltage is on the order of O-2 volts.

- 02 to 05

A transistor switched "off" conducts a current on the order of 20 microamps.

Depending on the circuit values and the particular logic configuration, the collector to ground voltage in "on" and "off" states varies. A standard definition of these levels for the grounded emitter configuration is:

On: Collector to ground voltage not more than 0.1 volts negative.

Off: Collector to ground voltage not less than 1.0 volts negative.

Thus with these defining levels one may determine the state of a given portion of the circuitry by measurement.

The time required to switch from one state to the other is on the order of one tenth of a microsecond.

Transistor circuitry for TRANSAC may be "direct coupled" or " resistance coupled".

# D. C. TRANSISTOR COUPLING

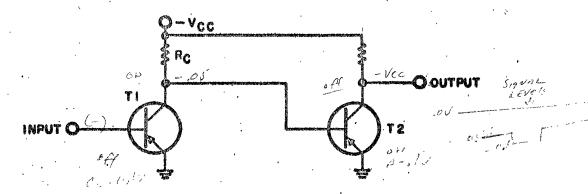

Coupling is the term describing the manner of connecting several stages of transistors to form a logical network. One of these methods is "direct coupling".

In this method, the base of the driven transistor is connected directly to the collector of the driving transistor. As shown in Figure 1-6, if transistor 1 is "on" the emitter-base voltage of transistor 2 is -0.1 volt or less (the drop across the conducting transistor). Transistor 2 is cut-off because virtually no current is supplied to the base. Not all junction transistors will be cut-off by such an emitter-base voltage, but the surface barrier transistor is readily cut-off. If transistor 1 is cut-off, current will be drawn through the collector resistance, R<sub>C</sub>, and the emitter-base junction of transistor 2 to bias it in the forward direction. Transistor 2 is thus held "on". (Note that in this purely direct coupled circuitry, the collector of transistor 1 will not be sufficiently negative to meet the definition above of the ON condition because the emitter-base forward drop of transistor 2 is appreciably less than a volt.)

The principal advantages of the direct coupled circuitry are the use of only one supply voltage (2 or 3 volts), and the small number of additional components used in addition to the transistors. The main disadvantage is that an inversion of the signal occurs in each stage because only the inverter circuit can be used. Also one transistor usually can drive only one other base.

Resistance coupled circuitry can offset some of the disadvantages while retaining most of the advantages.

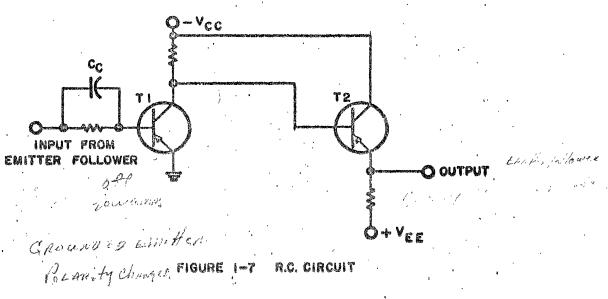

# R.C. TRANSISTOR COUPLING

As shown by Figure 1-7, the inverter has an additional

resistor placed in series with the base. The inverter is normally driven by an emitter follower as in Figure 1-5. The emitter follower is capable of driving about six R. C. inputs (inverter inputs). Capacitor C<sub>c</sub> is added to the circuit to speed the response of the driven transistor. In switching the transistor "on" it provides a larger base current initially. In switching the transistor "off", the capacitor provides assistance in removing the excess holes in the base region by means of stored charge.

The resistor in the emitter circuit of the emitter follower is connected to a positive source of voltage whose value is so chosen to provide a nearly constant current flow through the transistor but without causing excessive heat dissipation.

The S-2000 uses resistance coupled transistor logic (RCTL).

FIGURE I-I. CONDUCTING JUNCTION

FIGURE 1-2. BACK-BIASED DIODE JUNCTION

FIGURE 1-3. PNP JUNCTION TRANSITOR

FIGURE 1-4. INVERTER

FIGURE 1-8

DIRECT COUPLED TRANSISTOR CIRCUITRY

R.C. CIRCUIT

#### 2. S-2000 CIRCUITS

# 2.1 STANDARD LOGIC CIRCUITS

The following discussion will describe the standard building block circuits used to perform arithmetic and control operations. Emphasis will be placed upon understanding of circuit operation. Conventional symbols will be shown as convenient in the text. No attempt is made to cover the complete arrangements of components in all possible logic configurations. A few of the more common combinational schemes will be pointed out.

# INVERTER OR COMMON EMITTER CIRCUIT

Shown in Figure 2-1 is the inverter or common emitter circuit. It is R.C. coupled as discussed above. The emitter may be either grounded or connected as discussed below for other circuit functions. Its output is used to drive one emitter follower.

# EMITTER FOLLOWER

Shown in Figure 2-2 is the emitter follower circuit. Its operation was described above, and can drive up to six common emitters. Essentially it serves as the power amplifier for a resistance coupled stage. A resistor may be added in series with the base when an emitter-follower is driven by another emitter-follower to suppress oscillation. Frequently the combination of inverter to emitter-follower is found as shown in Figure 2-3. Logically the combination functions as an inverter but with a higher load capability.

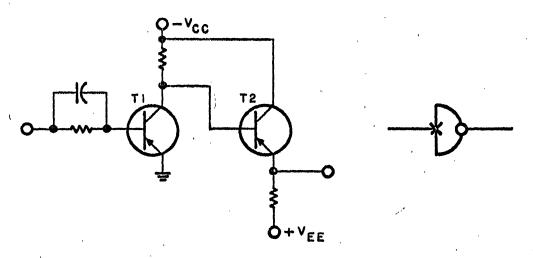

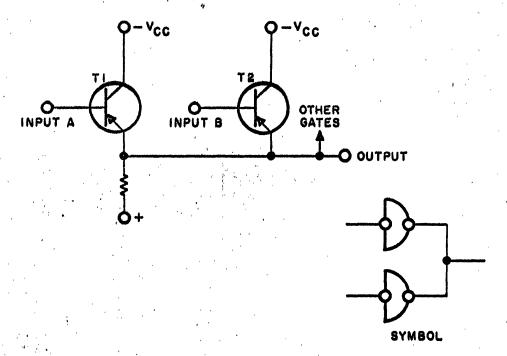

#### SERIES GATES

Logical operations of "and" and "or" can only be provided by combinational circuitry. An example is the "series gate" or "two-high gate" shown in Figure 2-4. This circuit is an inverter if both transistor bases are driven by negative going signals. Thus if both transistors are switched "on", the voltage from the top transistor collector to ground will be positive going. If either one or both are switched "off", the upper collector will be negative going. In critical timing applications a resistor may be added (shown dotted) between  $V_{CC}$  and the bottom transistor collector. The purpose of this resistor is to provide a means of dissipating stored holes in the bottom transistor. Supposing that the bottom transistor is

driven and then has the driving signal removed without having switched the top transistor "on". Ordinarily the stored holes can be recombined by the reverse bias, collector-base current. Since the top transistor never functioned to connect the bottom transistor collector, the normal means of hole storage dissipation was not provided. If a short time later, a signal is applied to the upper transistor base, a positive output will result until the excess holes are removed from the bottom transistor. Thus the bottom transistor would tend to store an input condition which would give a temporary false output from the gate. The additional resistor provides the means to assure that the bottom transistor is "cleaned up".

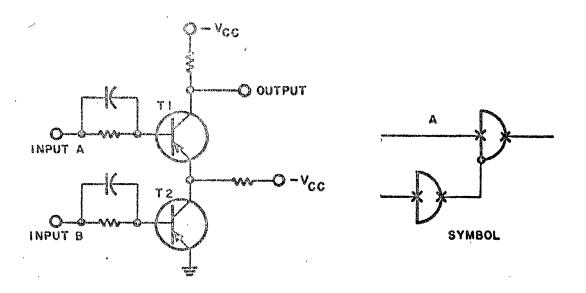

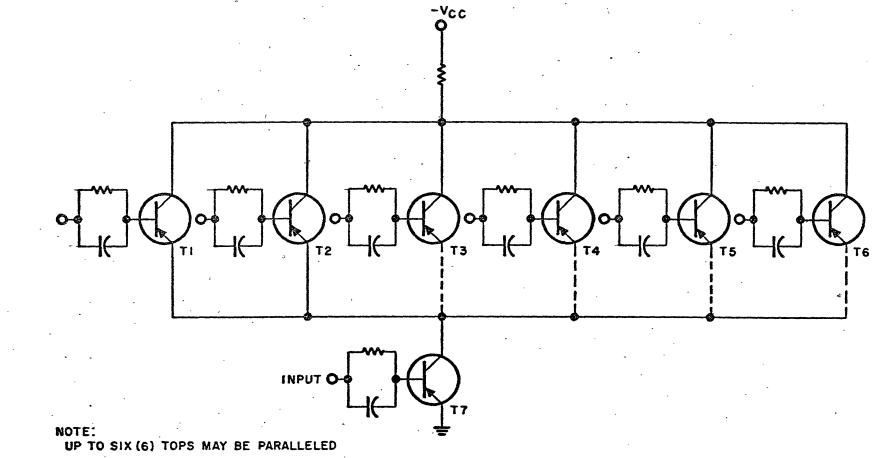

#### PARALLEL GATES

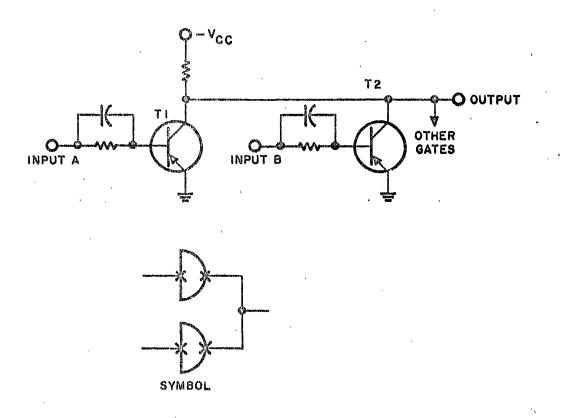

Parallel gates may be made by paralleling the collectors of inverters or the emitters of emitter-followers. The parallel gate-common emitter is shown in Figure 2-5. Negative input to either transistor base produces a positive going output. If both inputs are negative and subsequently both are switched positive, the time for hole storage clean-up is increased somewhat in the parallel collector gate over clean-up time in a simple inverter.

Figure 2-6 shows a parallel emitter gate. Negative input to either base produces negative output.

## TYPICAL CIRCUIT ARRANGEMENTS FOR LOGIC FUNCTIONS

From the preceding discussions, one observes that a large variety of logic functions can be provided by series and parallel combinations. Some typical examples are given below:

A parallel R.C. gate circuit as shown in Figure 2-7 parallels inverters and two-high gates.

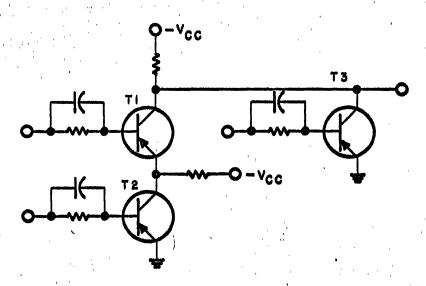

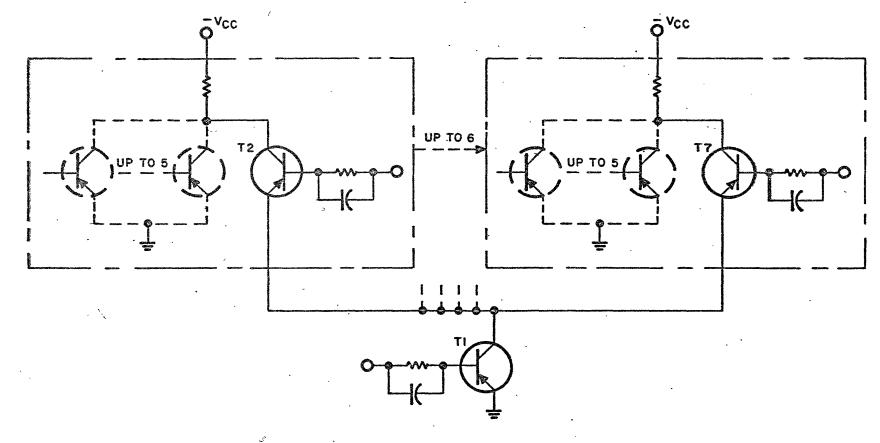

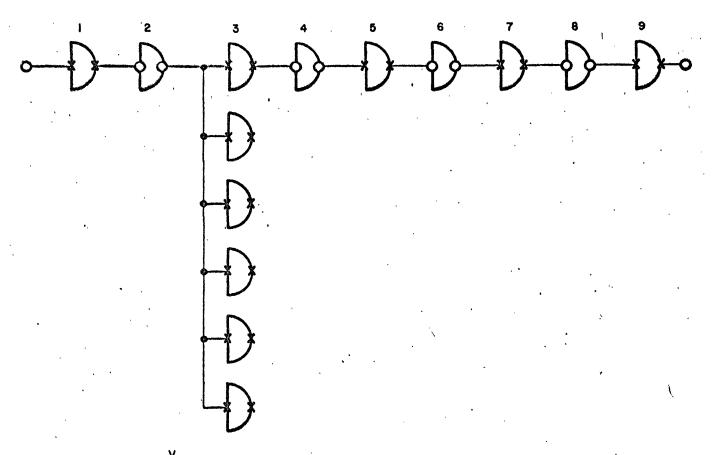

The Two-High Selection Tree shown in Figure 2-8 is another combination.

In the Two-High Selection Gate Circuit of Figure 2-9, the upper transistor of the series gate actually consists of a group of paralleled inverters.

#### **FLIPFLOP**

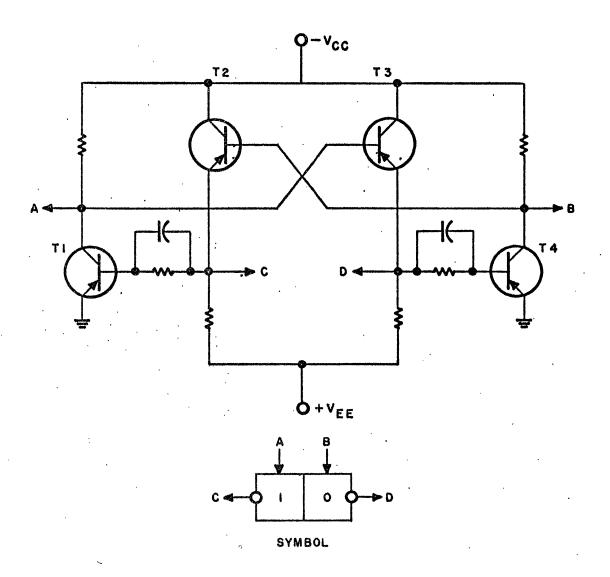

Shown in Figure 2-10 is the flipflop consisting of two inverteremitter follower combinations. Each emitter follower output is connected to the base of the opposing inverter. If one inverter is "on" (i.e., its output signal is positive) its load, the emitter follower, will also have a positive output. A positive input to the other inverter will hold it "off" (i.e., its collector is negative). So also is the driver emitter follower output. A negative input to the first inverter holds it stably in the state first assumed/

Setting of the flipflop, to 1 or 0, is accomplished by a positive signal at A or B, respectively. (As the logic usually develops a negative set signal, an inverter not shown in Figure 2-10 is used to produce the required input polarity to the flipflop.)

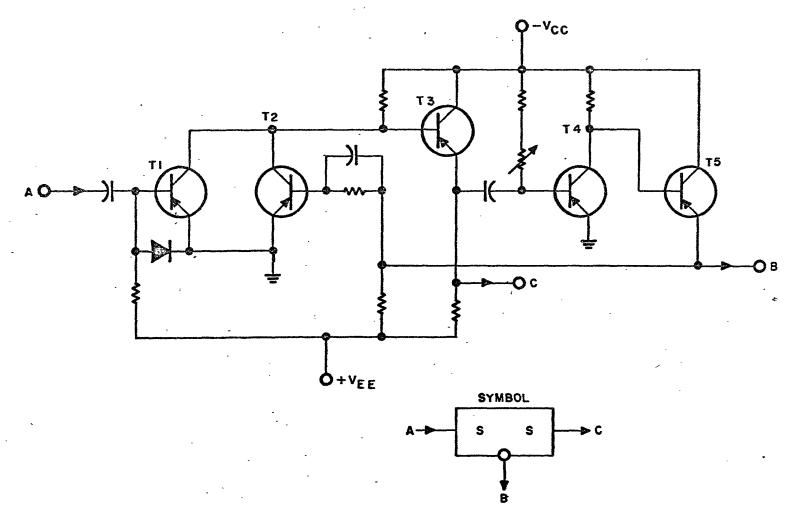

#### SINGLE SHOT

The single shot consists essentially of a flipflop with additional RC coupling arrangements to give a specific transient performance. Upon application of a negative-going input pulse at A the singleshot assumes the opposite condition to its normal one. This condition is maintained for a definite length of time and then the singleshot returns to its normal state. Terminal B goes negative and C positive during the active (instable) period.

Comparison of the circuits of Figure 2-10 with Figure 2-11 shows that a resistor and capacitor have been added between an emitter-follower and an inverter. A differentiating circuit is placed at the single-shot input so that only the leading edge of the input driving pulse is utilized to drive the single-shot. The singleshot will respond only once to a negative signal, regardless of its duration.

A negative going input signal gives a positive output from the parallel gate to the emitter follower it is driving. The emitter-follower in turn supplies a positive input through the discharge capacitor to hold the next inverter cut-off temporarily. After passing through another emitter follower the parallel gate is held "on" to continue the active state of the singleshot.

After the interstage capacitor C<sub>2</sub> has charged sufficiently to permit the base of the inverter input it drives to swing apprecially negative, this inverter output begins to swing positive. This causes the inverters in the parallel gate to swing negative so that the singleshot assumes its normal state.

The time that the singleshot is in the active condition is a function of the capacitor C<sub>2</sub> and the adjustable resistance. Larger resistance and capacitance values will give a longer output pulse duration. The diode checks the swing of the parallel gate base when the input signal is positive going to prevent large voltages on this base.

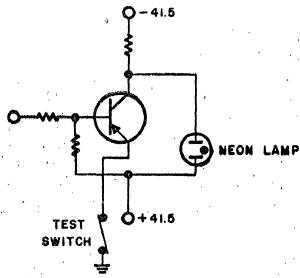

# NEON DRIVER

Shown in Figure 2-12 is the neon driver circuit. The neon lamp is fired if about 90 volts is dropped across its electrodes. It is extinguished if the voltage across its electrodes is dropped under about 42 volts.

If the transistor is switched "off', its collector will tend to swing toward the negative collector supply voltage of -48.5 volts. Because the other electrode of the lamp is tied to + 41.5 volts, 90 volts are dropped across the lamp to fire it. It remains lit at the operating voltage peculiar to each particular lamp (less than 90 volts) with current limited by the resistors in series with it. Regardless of any signal levels customarily supplied to the transistor base, should the switch be open, the transistor will be "off" and the lamp lit.

Lif the switch is closed and a negative going signal is applied as input to the transistor base the transistor is switched "on". Its collector is positive going (1. e., at about ground potential). Only +41.5 volts are available for the neon lamp. This is insufficient to maintain the gas discharge in the lamp. As a result the lamp is extinguished.

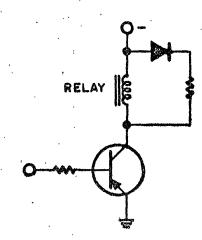

#### RELAY DRIVER

The relay driver schematic is shown in Figure 2-13. It is essentially an inverter type of circuit except that the collector resistor is replaced by the solenoid of the relay. Since a negative signal turns the transistor "on", a negative signal actuates the relay.

The diode and resistor combination provides a path for current sustained by the solenoid flux decay. When the transistor is switched "off" the inductance of the solenoid attempts to maintain the "on" current flow. Without the discharge circuit the transistor would be required to dissipate the stored energy possibly at an excessively high collector voltage. The resistor provides a path for discharge current thereby limiting transistor collector voltage and dissipation.

#### MANUAL SET CIRCUIT

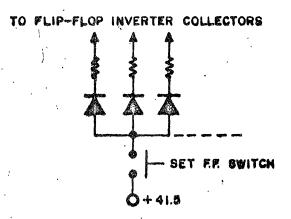

As shown in Figure 2-14, the manual set circuit switches 41.5 volts through a 10K resistor to an inverter collector. Since the flipflop is set by means of a positive signal at the collector, any source of positive going voltage is adequate.

The SG-22 diodes shown eliminate sneak paths from one flipflop to another when the manual set switch is not being operated. The diode is not necessary if only one flipflop is being set from the switch.

#### 2.2 ASSEMBLIES AND PHYSICAL LAYOUT

The hardware of the computer is organized by standardizing the circuitry into units. A unit may consist of a circuit stage or part

of a stage. The units are produced on an etched circuit "module" whose

dimensions are approximately 4-7/8" x 13/16". A module may contain

several units of the same type. For example, the HG2 module contains all

the circuitry for a series gate (two-High Gate) with the exception of the

collector resis or. The HG2 module contains two such units.

The collector resistor is placed on the module that contains the emitter follower unit, such as the En module. (El has our collector-resistor emitter-follower units). One propose in placing that resistor in the emitter follower module is to enable joining several grounded emitters to one resistor to form a parallel gate. The GGl module, for example, has four grounded emitter units minus the collector resistors. It may be reasonably deduced that most modules contain four transistors. Another module, Cl, contains four units, each having a collector resistor and an emitter follower, but lacing the emitter resistor. This, of course, nables forming an emitter follower gate.

For inverter stages, the GO1 module has two units, each comprised of a complete grounded emitter and emitter follower configuation. This same module, with the required connections will also form a flipflop. It is so used, with two units on adjacent GO1 modules joined to form the flipflop.

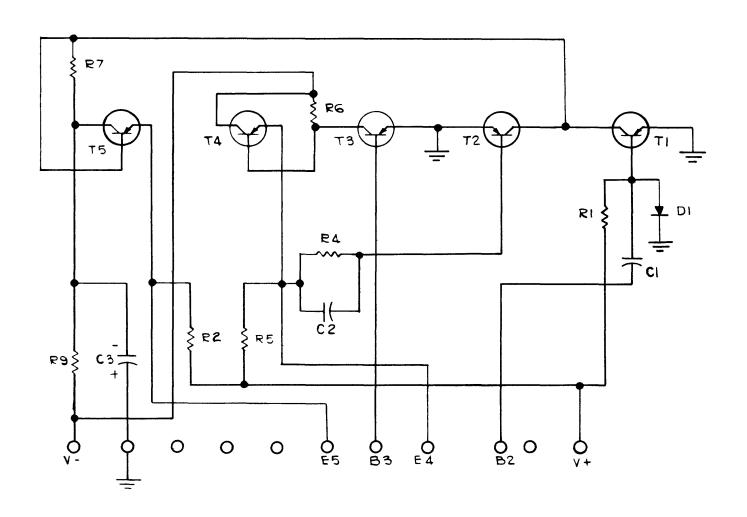

The single shot occupies an entire module. SSI is a typical single shot module. In this instance, the module contains five transistors.

In all, over fifty module types are used in the computer.

The module contains etched circuitry on one surface. Components are location on the other side. The transistors are mounted by pairs in two white nylon receptacles, which are riveted to the module. The transistor leads are soldered to the appropriate points of the etched circuits. Advantage is taken of the etching process to clearly mark the wiring points, on the module, for each component lead. Small etched letters and numbers adjacent to the drilled holes indicate the connections for the leads. For transistors, the letters "C", "E" and "B" identify the connections for the collector, emitter and base respectively.

The transistor is marked with a red line near the collector lead. Looking downward at the glass base seal of the transistor, the leads are arrayed clockwise, collector, base, emitter. When the transistor is placed in the nylon receptacle, a small nylon disk with three holes is inserted over the leads to keep them separated. The disk has a triangular notch on its circumference adjacent to one of the holes. The collector lead is always inserted through this hole; and the collector lead is subsequently identified by this notch.

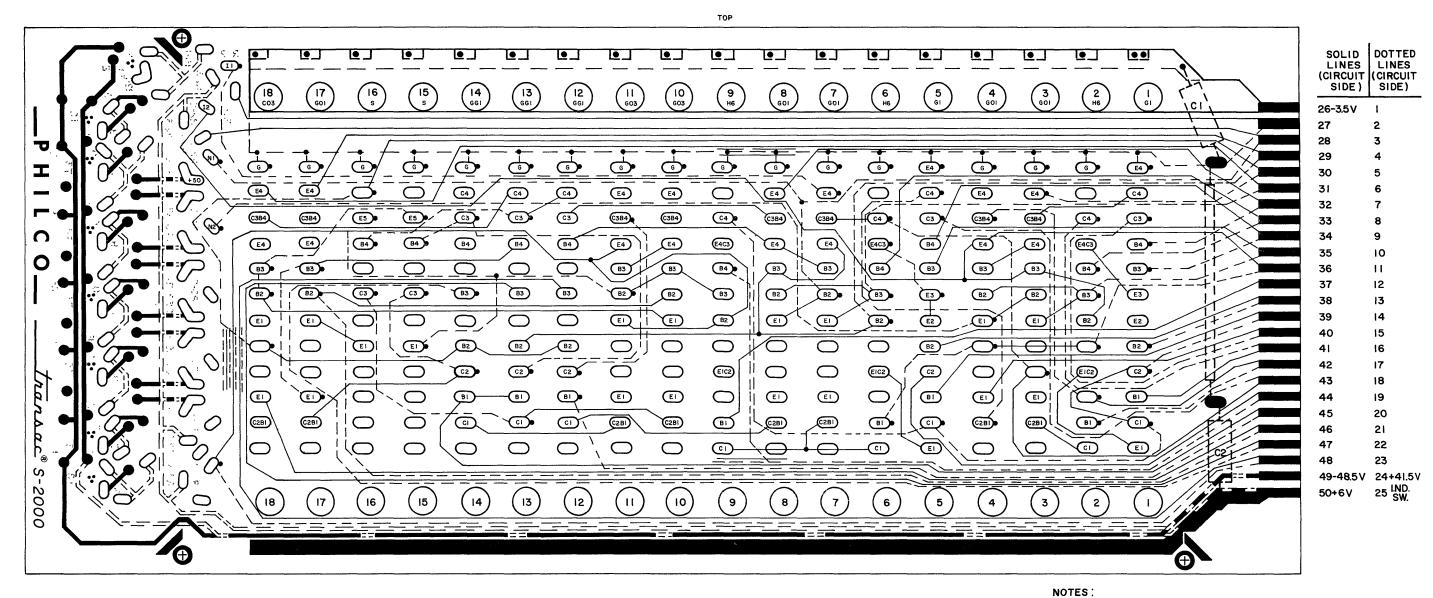

Up to twenty-one modules may be mounted on a "card", an etched circuit board measuring approximately 5-1/4" x 12-1/4" (See Figure 2-15). A maximum of fourteen jumper wires is used for connections between a module and its card. Two (the ones at each end of the module) are the voltage connections. The remainder of the connecting circuit points are identified by relating them to one of the three terminals of a transistor. If a module terminal is designated as "E4", for example, that terminal is connected by an etched circuit line to join the emitter lead of transistor number 4. The five transistor locations are standardized and numbered.

Figure 2-16 shows the SSI module schematic and physical layout. If the <u>card</u> is vertically held so that when looking at the component side, the cards' terminals are at the left end, the transistor locations on any module, reading from bottom to top, are 1, 2, 5, 3 and 4. The other components are given the same number as the transistor with which they are functionally related. The transistor 5 position is not always used.

The card, Figure 2-15, has numbered module positions. The CA card uses eighteen modules, for example, the locations indicated by the etched numbers within the circles.

The modules are mounted on one surface of the card. Etched lines are used on both sides. Connections between the sides are made by "feed-throughs", wires soldered to the etching on both sides through drilled holes in the card. The etching area surrounding a hole is known as a "land".

The card has fifty terminals, twenty-five on each side and numbered 1 to 50. Terminals 26 to 50 are at the module side of the card, terminals 1 to 25 on the other. Terminals 1 and 26 are at the top of the card.

The outer terminals are used for the voltages:

| Terminals 1, 2 | ground   |

|----------------|----------|

| Terminals 26   | -3.5 V   |

| Terminals 24   | + 41.5 V |

| Terminals 49   | -48.5 V  |

| Terminals 50   | +6 V     |

The components, not on modules, at the end of the card are the neon indicator circuits. The name of the card is given, in etched letters, at this end.

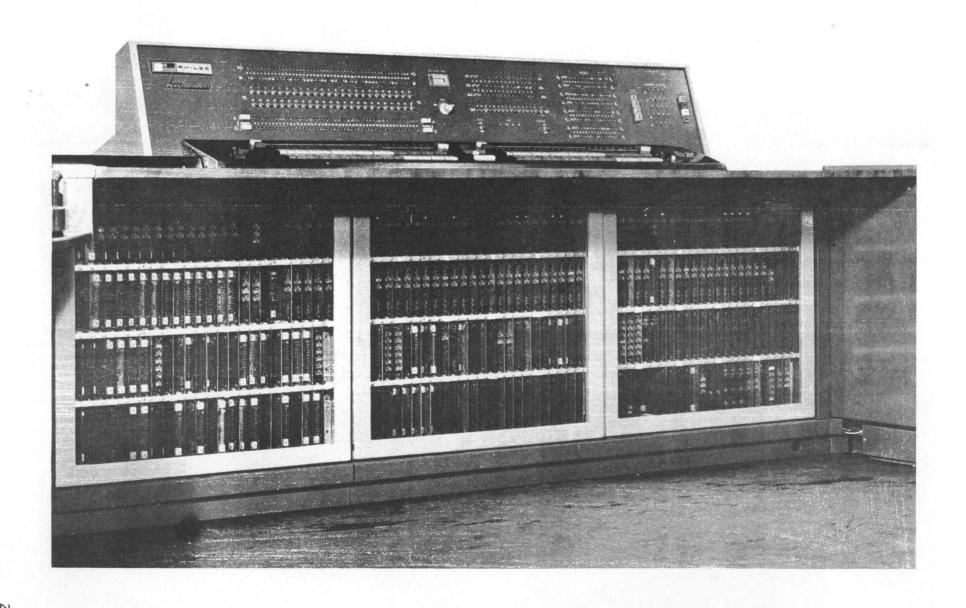

Cards plug into connector jacks in the computer cabinets. The back panel wiring interconnects the 300 card positions. Figure 2-17 shows the console and cabinets of the computer.

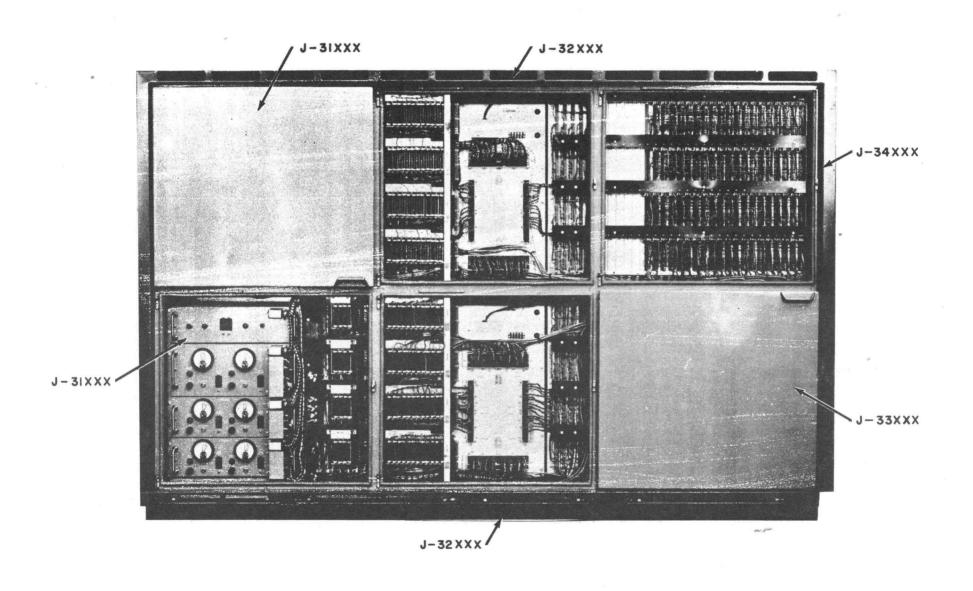

Each cabinet has one hundred card positions, four horizontal rows of twenty-five cards numbered 001 to 100. Viewed from the front, the 001 position is at the upper left corner. The cabinets are in turn identified as J11XXX, J12XXX and J13XXX, left to right from the front view. (The cards are inserted on this side.)

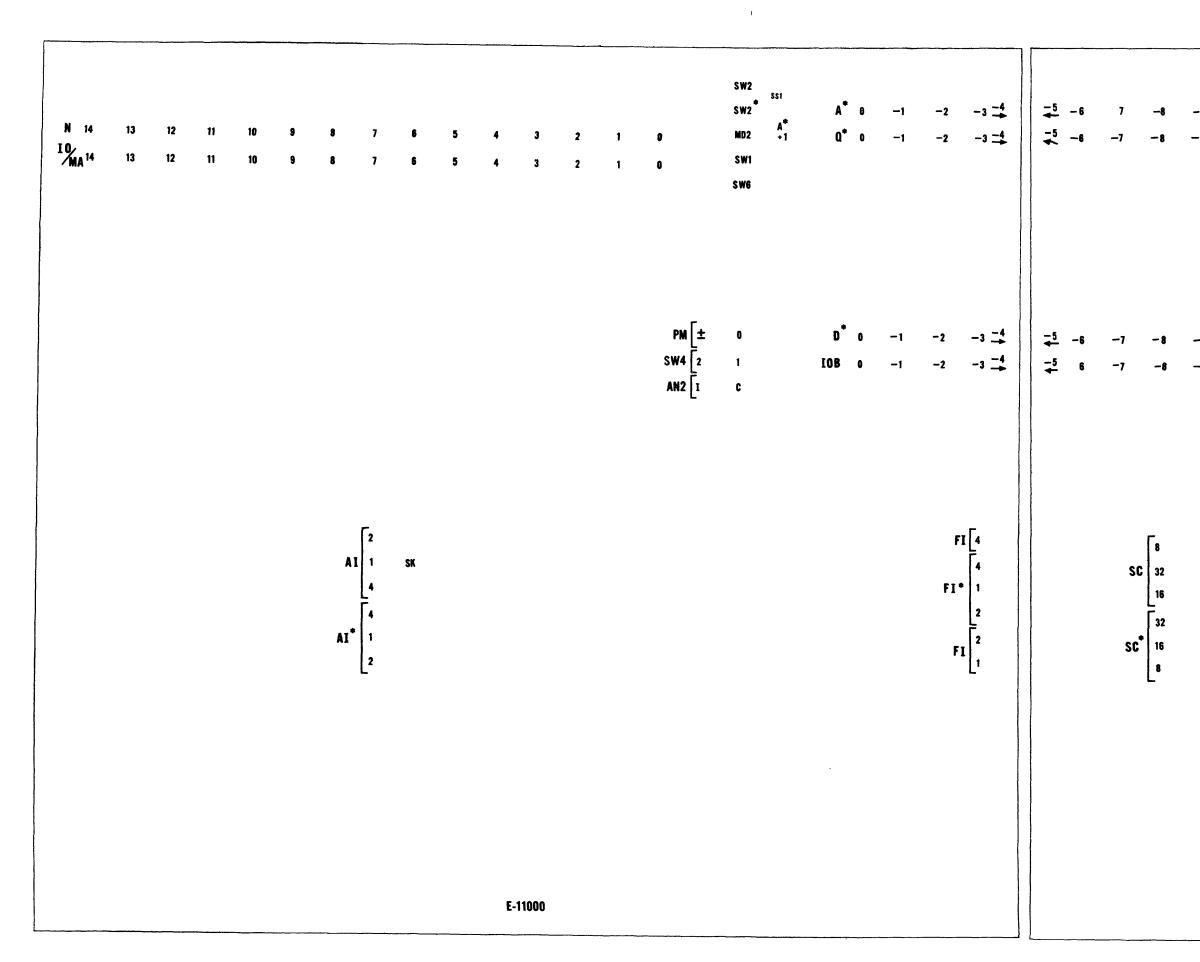

The cabinet doors are panelled with transparent plastic sheets to permit viewing the neon indicators with the doors closed. The panels are imprinted to identify each neon. These neons display the contents of registers, flipflops, counters etc., that are not displayed at the console above. Figure 2-18 is a reproduction of the imprinting on the door panels. The numbers give the bit position of the register or counter.

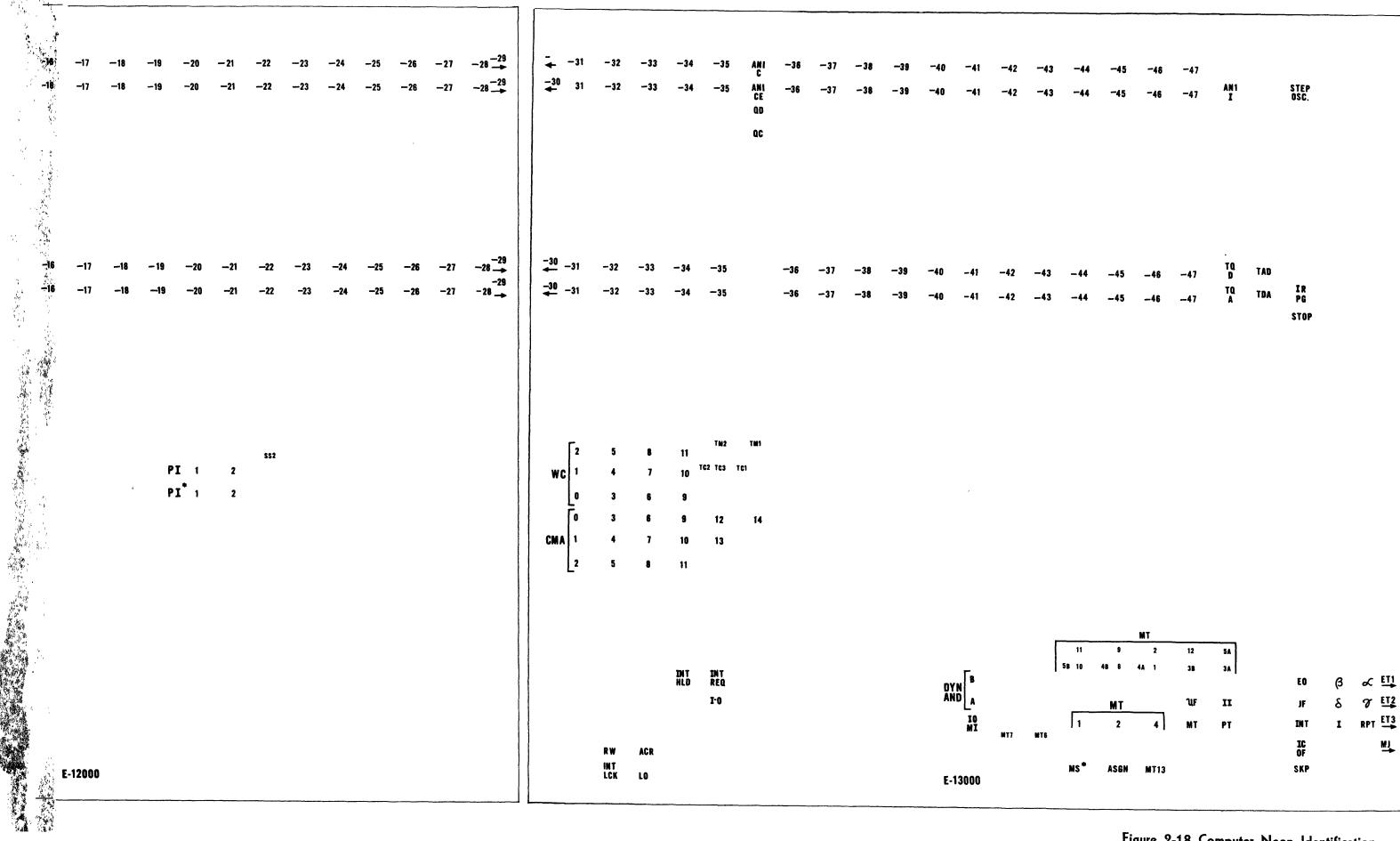

Figure 2-19 is the back plane view of the six cabinets comprising the index register and an 8192 word memory circuitry.

The index registers are located in the J34XXX cabinet in the lower right. The other cabinets (shown with the doors removed) comprise the memory. The six cabinets are located to the right of and just behind the console.

#### 2.3 POWER

Despite the size and complexity of the S-2000, a relatively small number of power supplies are required. However a fairly elaborate A.C. distribution system is required to turn these supplies on and off in an ordered sequence, as well as control of the power to the various fans, heaters, motors and alarm circuits. The following section describes the A.C. distribution and the D.C. power supplies.

#### A.C. DISTRIBUTION AND CONTROL

The A.C. distribution and control system distributes regulated and unregulated A.C. from the power mains to the power supplies, cooling fans and other equipment at the control of the operator. Upon depressing the START switch, on the console, power is supplied to the fans and the D.C. power supplies. The computer supply comes on first, and after a few seconds, the supply for memory is turned on. This is to ensure no loss of data stored in the memory during the turn-on. The reverse order is used in turn-off. The power to the cooling fans is maintained for an interval after power is removed from the D.C. supplies to dissipate the residual heat.

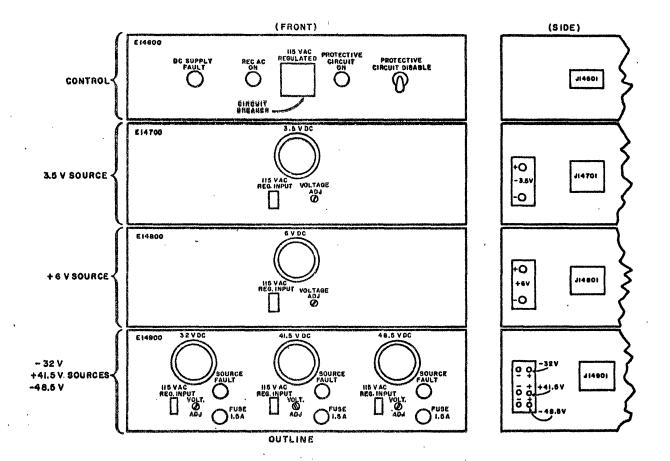

The Power Supply consists of five package units. These units are: (Figure 2-20 shows the front panels of the units)

- (1) Line Voltage Regulator General Radio Co. 1570-AL.

- (2) Control

- (3) (-) 3.5 volt source.

- (4) (+) 6 volt source.

- (5) (+)41.5, (-)32, and (-)48.5 volt sources

For information concerning line voltage regulator see manufacturer's data.

The descriptions to follow will be broken down into description of the control unit followed by descriptions of each individual voltage source. Although three sources are combined in one unit, as listed above, each source is essentially isolated except for a common line voltage input and common protective circuitry contact arrangements. For definitions of symbols used in the text and schematic refer to the referenced drawing for each description.

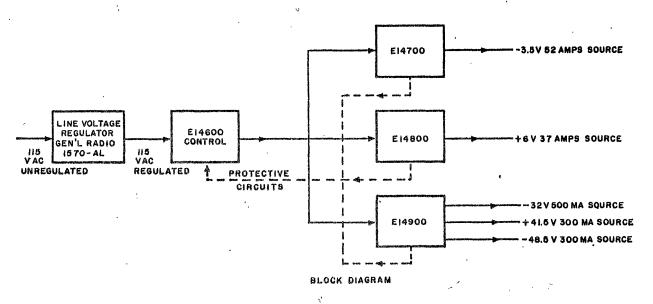

Interconnections between units are shown in Figure 2-21.

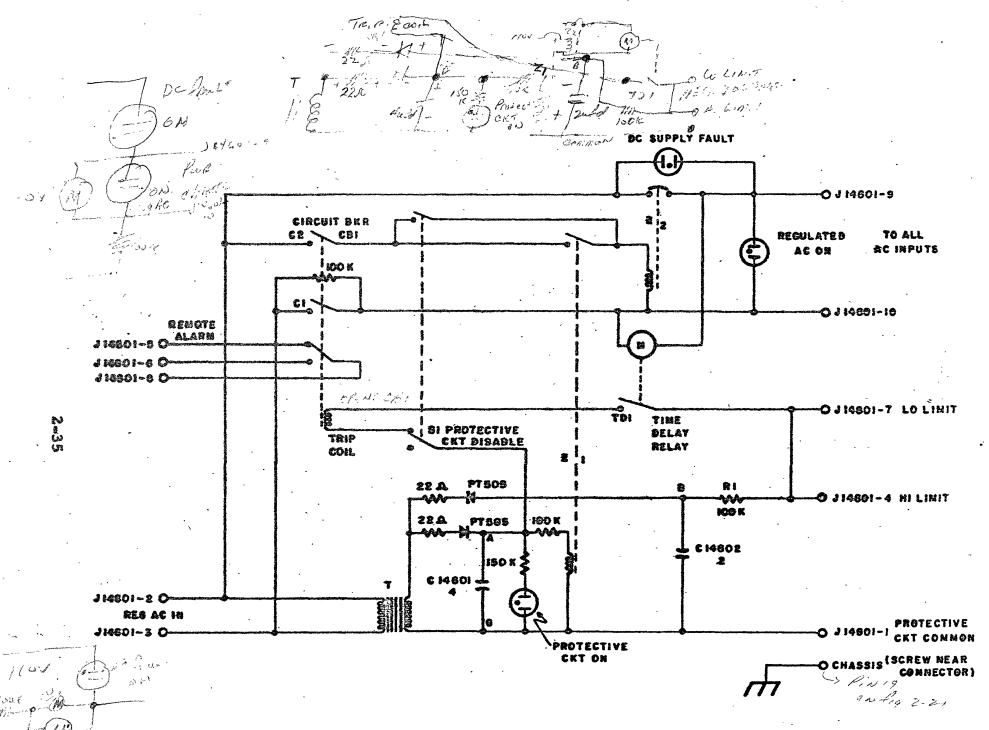

#### CONTROL UNIT

The Control Unit (Figure 2-22) controls the application of A.C. input power to the sources and contains the protective circuitry (except meter relays) which a sure operation of the power supply only with output voltages within the limits set by the meter relays. The controls are the master circuit breaker for the entire power supply and "Protective Circuit Disable switch. Indication provided are "Protective Circuit On", "D.C. Supply Fault", and "Regula et A.C. On". All connections are hrough the Cannon Connector J14601.

#### Normal Starting Sequence:

With regulated A.C. "on", voltage is supplied to terminals 2 and 3. Transformer T is energized and positive voltage appears between points (a) to (g) and negative voltage from points (b) to (g). The "Protective Circuit On" light is lighted and relay Z1 is actuated. With the voltage source inputs connected between terminals 9 and 10, "D.C. Supply Fault" light is lighted. Unit is ready for actuation of the circuit breaker.

With CBl switched "on", contact C' completes a path from terminal 3 to terminal 10. Contact C2 completes a circuit from terminal 2 through con act of Zl, through coil of relay Z2 to terminal 3 actuating Z2. A circuit is completed through Z2 contacts from terminal 2 to 9. "Regulated A.C. on" light is lighted and A.C. power is delivered to the voltage source inputs. "D.C. Supply fault" light is extinguished. Time delay motor M in TDl begins to run with the actuation of Z2 commencing a three second delay period. Terminals 4, 7 are connected to point (b) to supply negative voltage to meter relay locking contacts and prevent meter lower limit contacts from sticking.

At the end of the 3 second period, TDl contacts are actuated closing the circuit from point (a) through "protective circuit disable" switch Sl, circuit breaker trip coil, TDl contacts to terminals 4, 7. Resistance Rl limits the current through the trip coil due to the voltage between points (a) and (b) such that a negligible drop in voltage across the CBl trip coil results. Thus terminals 4, 7 are essentially at the same potential as point (a) relative to point (g) after completion of the time delay period. Protective circuit is now fully operative.

#### NORMAL SHUT OFF SEQUENCE

The circuit breaker is tripped off manually. Contact C2 breaks the circuit through relay Z2 operating coil. Contact Z2 opens the circuit from terminals 2 to terminals 9. Contact C1 opens circuit from terminals 3 to terminals 10. "Regulated A.C. on" light is extinguished and "D.C. Supply Fault" light is lighted. A.C. power is removed from the input of the voltage sources. Time Delay, TD1 resets supplying negative voltage to terminals 4, 7.

#### FAULT SHUT-OFF SEQUENCE

Any meter contact striking either high or low limits connects terminals 4, 7 to point (g) through the locking coil contacts. Voltage is dropped from point (a) through "Protective Circuit Disable" switch S1, Trip Coil, TD1 Contact, through terminals 4, 7, Meter Relay returning through terminal 1 and then to point (g). Sufficient current flows through CB1 trip coil to trip the circuit breaker. Shut off is the same as B above except that circuit breaker is not tripped manually.

#### OPERATION WITH PROTECTIVE CIRCUIT OVER-RIDE

Operation is similar to A above except relay contact Z1 is shunted by actuation of switch S1 and the trip coil circuit is broken by S1. Thus the circuit breaker must be tripped either by manual operation of circuit breaker or release of "Protective Circuit Disable" switch S1.

#### NOTES:

In case of failure of Protection Circuit supply as evidenced by "Protective Circuit On" light being extinguished, relay Zl will open circuit of relay coil Z2 removing power from inputs of voltage sources. The circuit breaker will not be tripped. Actuation of Sl will reapply power to the source inputs.

#### D.C. POWER SUPPLIES

Transistorized D.C. power supplies are relatively new. Essentially the circuitry is similar to vacuum tube type voltage regulators. A transistor is used as a variable resistance in series with the load and an ordinary transformer-rectifier-filter combination. The output D.C. voltage is sensed and compared with a reference voltage in the supply

(Zener reference diode). Any error is amplified and used to change the effective resistance of the regulating ("pass") transistor.

Special meters and circuitry are used to switch off the supply if the output voltage exceeds the preset limits in either direction.

One representative supply is described here, as they are similar in design.

# (+) 6 Volt Supply (Figure 2-23)

This Vol age Source of the Computer and Control Unit Power Supply contains three important functional sections.

- (a) EDC1 Load and Regulator Voltage Supply

- (b) EDC2 Bias Supply

- (c) Voltage Regulator

# EDC1 Load and Regulator Voltage Supply

With voltage supplied to the primary of Tl input voltage and CB 14801 closed, the dodes connected to Tl rectify the A.C. voltage to provide a pulsating uni-directional current flow through capacitor C4, the voltage regulator amplifiers and the external load returning to Tl secondary center top. Sufficient capacitance is provided so that the average load current can be supplied from a nearly constant source. Any small ripple on EDCl is substantially removed by the voltage regulator before appearing as output voltage.

#### EDC2 Bias Voltage

Similarly EDC2 is developed by the diodes connected to T2 to provide pulsating unidirectional current to filter consisting of R9, C5 and C6. The additional components R9 and C6 provide improved filtering over that obtainable with a single capacitor. Since substantially pure D.C. bias current is required and no regulator is provided, necessary filtering must be provided by the two stage network employed in the EDC2 supply. Resistor R10 limits the inrush current drawn from T2 and protects T2 in case of short or overload on EDC2 supply.

#### Voltage Regulator

The voltage regulator consists of a voltage reference and a high gain direct coupled transistor amplifier. These are connected as a closed loop regulating system.

In the regulating system, a reference voltage (the drop across a voltage reference diode) is compared with the output terminal voltage by means of a suitable network. Any error detected is amplified and use to adjust current passed by a transistor in series with the external load. As load voltage tends to become too high, less current is passed to the load. As load voltage tends to become too low, more current is passed. Thus the error is corrected by automatically adjusting load current to the proper value such that a virtually constant output voltage is maintained.

Following is a detailed discussion of the amplifier operation assuming the output voltage tends to become too high.

Transistors TR1 and TR2 are carefully matched low leakage transistors connected to form a differential D.C. amplifier. This circuit has the property of tending to cancel almost entirely the temperature changing characteristics of one transistor by equivalent changes in a second transistor. With sensing terminals properly connected to the voltage output terminals as shown, current flows through two parallel branches: resistor R4 and Z; and the series network containing R1, R2 and R3. Diode Z is the reference diode. Since the voltage sensed is higher than the inverse break-down voltage of the diode, a nearly constant voltage appears across Z.

The base of TR1 will tend to remain at a fixed voltage more negative than the +output terminal of the supply regardless of potential between the + and - output terminals of the supply.

TR1, being an emitter follower, will tend to maintain its emitter, and that of TR2, at a fixed potential more negative than the + output terminal. However the voltage at the base of TR2 will vary proportionally as any potential change between the + and - terminals.

Output terminal voltage changes will cause a direct variation in the forward bias on TR2. For example, if the terminal voltage increases, the voltage level at the base of TR2 would become more negative with respect to its emitter voltage level.

This would result in a larger TR2 collector current and a positive-going signal at the base of TR3. TR3, an NPN in an emitter follower configuration, will respond with an increase in its emitter current. Its emitter will swing more positive.

Voltage EDC2 tends to bias TR4 into saturation so that maximum collector current would flow. Transistor TR3 tends to supply current in opposition to the bias current of TR4. As TR3 conducts increasing collector current, (due to increasing output voltage from the supply), TR4 conducts less collector current. Transistor TR4 operates as an emitter follower to control TR5.

Transistor TR5 is connected in series with the load on the voltage source. Reduced collector current in TR4 causes reduced emitter-base current in TR5. Thus TR5 increases the effective resistance in series with the load by decreasing the current passed to the load tending to correct the error in output voltage. The resistors R5 and R6 bleed off the leakage current of TR5.

Capacitor Cl provides the necessary low output impedance for high frequency components of load current. C2 tends to suppress any tendency for oscillation in the differential amplifier current.

# - 3.5 Volt Supply (Figure 2-24)

The (-) 3.5 Volt Source of the Computer and Control Power Supply essentially functions similarly to the (+) 6 Volt Source except for the addition of another transistor amplifier in the regulator and other minor details of circuitry. Parts symbols are the same on both schematic diagrams for equivalent functional components.

Input power is supplied to connector J14701A pins 2 and 3. Diode CRl is utilized to assist in temperature compensation of Z. Because of the low output voltage of this source, a reference diode having a negligible temperature coefficient of voltage can not be used. The change in forward drop of the specially chosen diode CRl due to temperature just cancels the change in Z reference voltage. Sensing terminals 6 and 21 must be connected as shown.

Transistors are used for TR5 to provide the required load current without excessive dissipation. An extra stage of emitter follower amplification is provided by TR6 to improve the regulator performance.

Leakage bleed off is provided as follows: TR5 by R6 and TR6 by R16. Resistors R17 and R16 stabilize the operating point of TR6. The sensing coil of Meter Relay M, 14701 is connected to the (-) output terminal because the supply develops a negative voltage with reference to the S-2000 ground point.

# -32 Volt Supply (Figure 2-25)

The functioning of the EDC1 and EDC2 supplies of the computer and Control Power Supply (-) 32 Volt source is the same as the (-) 6 volt source. A single transformer, T, having two secondaries A and B is used. Voltage regulator operation differs in details. Input power is applied to connector J14901A pins 2 and 9.

#### VOLTAGE REGULATOR

Following is a detailed discussion of the voltage regulator amplifier operation assuming the output voltage tends to become too high.

Transistors TR1 and TR2 are carefully matched low leakage transistors connected to form a differential D.C, amplifier. This circuit has the property of tending to cancel almost entirely the temperature changing characteristics of one transistor by equivalent changes in a second transistor. With sensing terminals properly connected to the voltage output terminals as shown, current flows through two parallel branches: resistor R4 and Z; and the series network containing R1, R2 and R3. Diode Z is the reference diode. Since the voltage sensed is higher than the inverse breakdown voltage of the diode, a nearly constant voltage drop appears across Z.

The differential amplifier maybe considered as emitter coupled. Transistor TRI is an emitter follower. Thus voltage from point (a) to point (r) is slightly greater in magnitude than the voltage from point (b) to point (r). However, voltage between points (b) and (r) varies directly as the voltage between points (a) and (r). Because of the common emitter connection, TR2 has this same voltage between points (b) and (r) as its emitter voltage. Transistor TR2 collector current varies with the difference in voltage between points (b) and (c) or more precisely, the current flow between points (b) and (c). As point (b) tends to become more positive with respect to point (c), TR2 collector current increases. Thus as point (a) tends to become more positive with respect to point (c) TR2 collector current increases.

Since point (c) is connected through the reference diode to the (-) sensing terminal, point (c) will follow an increase in terminal voltage such that point (c will change approximately the same number of mill volts as the (-) output terminal. Point (a) will increase only as a fraction of the output voltage change due to the divider network Rl, R2, R3. Consequently point (a) will tend to become more positive with respect to point (c) increasing TR2 collector current.

Transi tor TR3 collector current increases due to the increased current supplied to its base by the TR2 collector.

Voltage EDC2 tends to bias TR4 into saturation so that maximum collector current would flow Transistor TR3 tends to supply current in opposition to the bias current of TR4. As TR3 conducts increasing collector currents, (due to increasing output voltage from the supply), TR4 conducts ess collector current. Transistor TR4 operates as an emitter follower to control TR5.

Transistor TR5 is connected to series with the load on the voltage source. Reduced collector current in TR4 causes reduced emitter-base current in TR5. This TR5 increases the effective resistance in series with the load by decreasing the current passed to the load tending to correct the error in output voltage. Resistor R11 limits the maximum current from the supply and permits TR4 to satura e TR5 more fully when necessary because TR4 collector supply voltage is slightly higher than TR5. The resistors R5 and R6 bleed off the leakage current of TR5.

Capacitor Cl provides the necessary low output impedance for high frequency components of load current.

Capacitor C2 tends to suppress any tendency for oscillation in the differential amp office current.

Resistor R14 limits the max mum current which can be drawn from winding A.

# - 48.5 Volt Supply (Figure 2-26)

The (-) 48.5 Volt Source of the Computer and Control Power Supply essentially functions the same as the (-) 32 Volt Source. Parts symbols on both schematic diagrams are the same for equivalent functional components. Sensing terminals 3 and 17 must be connected as shown.

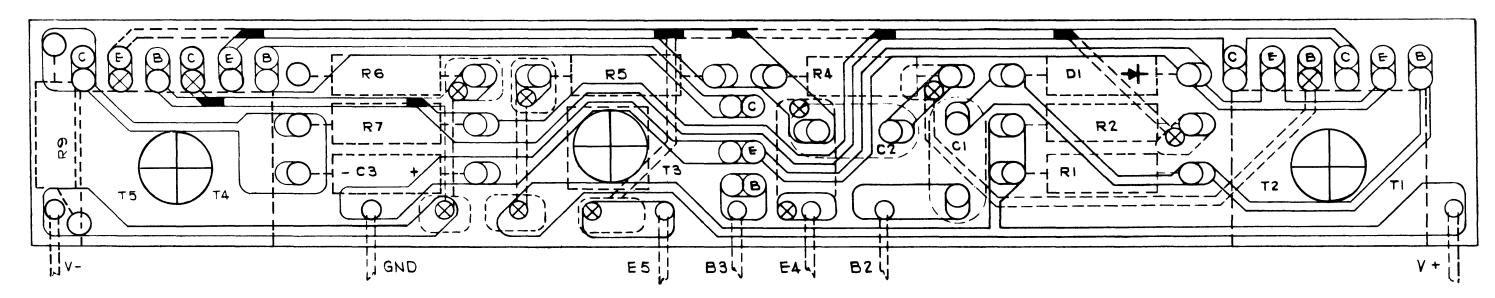

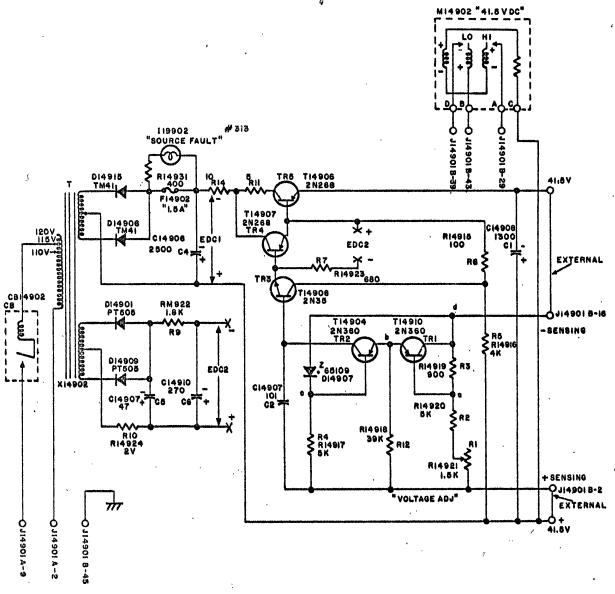

# 41.5 Volt Supply (Figure 2-27)

The (+) 41.5 Volt Source of the Computer and Control Power Supply essentially functions the same as the (-32) Volt Source. Parts symbols on both schematic diagrams are the same for equivalent functional components. Sensing terminals 2 and 16 must be connected as shown. The sensing coil of the Meter Relay is connected to the (+) output terminal because the supply develops a positive voltage with reference to the S-2000 ground point, pins 1 and 3. Diode CR2 is not necessary in the (+) 12 Volt Supply because the voltage which may be dropped across TR4 and TR5 is not sufficient to cause any damage to them. Sensing terminals 16 and 2 must be connected as shown. Two pass transistors TR5, are adequate for this source. Capacitor C3 is needed with this Source. The sensing coil of Meter Relay M35802 is connected to the (+) output terminal because the supply develops a positive voltage with reference to the S-2000 ground point.

# POWER SUPPLY ADJUSTMENTS

These adjustments may be made to each individual Voltage Source

- Source output voltage is adjusted with screwdriver adjustment adjacent to each Meter Relay.

- MARGINAL 1.

CHECK PAG

CEFABLISHING 2.

Whith howariant as there supply 3.

(DONOT DO HERE)

- Upper limit contact of Meter Relay is adjusted with the right hand screw on the Meter face.

- Example

- Lower limit contact of Meter Relay is adjusted with the left hand screw on the Meter face.

Say 67 63 PRECAUTIONS

Be sure that sensing leads are connected to the proper polarity output terminals. Failure to do so may result in damage to the voltage regulator components.

Do not adjust the lower Meter Relay adjusting screw (center of movement face). The meter has been calibrated at the check point (arrow) to 1% accuracy. Tampering with this screw affects the meter accuracy.

#### MAINTENANCE PROCEDURES

To simplify the checking of the supply in case of a malfunction, the following procedure is recommended.

Procedure: (output voltage too high)

- 1. With supply input voltage switched "off", measure the resistance of each of the pass transistors (TR5 on the schematic drawings) and transistors TR4, TR6 and TR3 from collector to emitter. Resistance should read about 100 ohms. If resistance measures zero or nearly zero, one or more pass transistors are shorted. Defective pass transistors will read zero others will read about 1/4 ohm.

- 2. If step (1) shows the transistors to be satisfactory, switch the supply "on". Place a 1K ohms variable resistor across TR3 from emitter to collector. If output varies around the nominal output voltage (plus or minus a few percent) the amplifier following TR3 is operating properly.

- 3. If steps 1 and 2 are satisfactory, remove the 1K resistor and connect a 10K ohms variable resistor from TR3 base to the (-) sensing line. If output varies around the nominal voltage, TR3 is operating properly.

- 4. If the sense leads have been connected improperly to the output terminals, diode Z and transistors TR1 and TR2 have probably been destroyed. With the D.C. voltmeter, check the reference diode voltage. (This will be 5.4 volts on units having output voltages greater than 3.5 volts and 2.5 to 3 volts on the low voltage units).

- 5. If all previous steps have been completed satisfactorily the differential amplifier transistors are presumably defective and should be replaced with another matched pair.

Procedure: (if current voltage is too low)

- Measure EDC2 output voltage to be about

to 6 volts. Defective component is in EDC2

supply if voltage is very much lower than 5 volts.

- 2. Measure EDC1 output voltage to be greater than the nominal output voltage of the particular Voltage Source being tested. If less or zero, EDC1 supply is probably defective.

FIGURE 2-1 INVERTER OR COMMON EMITTER CIRCUIT

FIGURE 2-2 EMITTER FOLLOWER CIRCUIT

FIGURE 2-3 COMMON EMITTER-EMITTER FOLLOWER

FIGURE 2-4 SERIES OR TWO-HIGH GATE

FIGURE 2-5 PARALLEL COLLECTOR GATE

FIGURE 2-6 PARALLEL EMITTER FOLLOWER GATE

FIGURE 2-7 PARALLEL RC GATE

$\frac{\partial}{\partial x} = \frac{\partial}{\partial x} \left( \frac{\partial}{\partial x} - \frac{\partial}{\partial x} \right) \left( \frac{\partial}{\partial x} - \frac{\partial}{\partial x} - \frac{\partial}{\partial x} \right) \left( \frac{\partial}{\partial x} - \frac{\partial}{\partial x} - \frac{\partial}{\partial x} - \frac{\partial}{\partial x} \right) \left( \frac{\partial}{\partial x} - \frac{\partial}{\partial x} - \frac{\partial}{\partial x} - \frac{\partial}{\partial x} \right) \left( \frac{\partial}{\partial x} - \frac{\partial}{\partial x} -$

FIGURE 2-8 TWO HIGH SELECTION TREE

FIGURE 2-9 TWO HIGH SELECTION GATE

FIGURE 2-10 FLIP-FLOP

FIGURE 2-11 RESISTANCE COUPLED SINGLE SHOT

FIGURE 2-12 NEON DRIVER

FIGURE 2-13 RELAY DRIVER

Figure 2-14 Manual Set Circuit

I. FEED THRU IS

INDICATED AT LAND

NEAREST DOT.

Figure 2-15 CA Card

Figure 2-16 SS1 Module

Figure 2-17 Computer and Console

ADV. Filt.

Figure 2-18 Computer Neon Identification

Figure 2-19 Memory and Index Registers Cabinets (8192 Word Memory)

LINE VOLTAGE REGULATOR NOT SHOWN, IS MOUNTED EXTERNAL TO MACHINE

Figure 2-20 Power Supply Front Panels, Block

Figure 2-21 Power, Supply Cabling

Figure 2-22 Power Supply Control Circuit

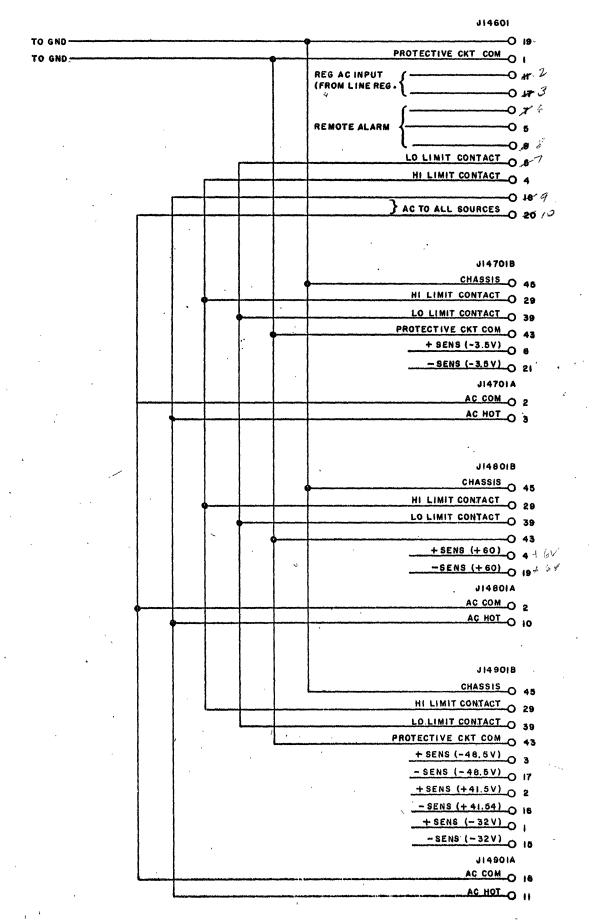

#### PIN DESIGNATIONS

J14701 A

2 - AC COM

- AC HOT

J14701 B

6-(+) Bensing 21-(-) Bensing 29-HI LIMIT CONTACT

39-LO LIMIT CONTACT 48-PROTECTIVE CKT COM 45-CHASSIS

Figure 2-24 3, 5 Volt Supply

J14901 A

2-AC COM

9-AC HOT

J14901 B

I - (+) SENSING

IS - (-) SENSING

29 - HI LIMIT CONTACT

39 - LO LIMIT CONTACT

43- PROTECTIVE CKT COM 45- CHASSIS

32 Volt Supp y Figure 2-25

Figure 2-26 48.5 Volt Supply

PIN DESIGNATIONS

J14901A 2- AC COM 9- AC HOT J14901B

2-(+) SENSING

16-(-) SENSING

29-HI LIMIT CONTACT

39-LO LIMIT CONTACT

42-PROTECTIVE CKT COM

48-CHASSIS

Figure 2-27 41.5 Volt Supply

# INTRODUCTION

In debugging or maintaing a computer, the oscilloscope is a powerful diagnostic instrument. When properly utilized it can be used to very quickly and accurately locate and determine the type of trouble or failure. A great deal of success, however, remains in the ability of the operator to correctly use and correctly interpret the instrument's presentation.

It is the purpose of this section to discuss the type of electrical faults that occur in the S-2000 logic circuits and the characteristic effects each displays. The discussion will assume that the logic is correct and will limit itself to fault conditions occasioned by component and/or material failure and/or drift. Usually logic errors create (or destroy) signals which are correct from circuit and electrical viewpoints, but are in error in time or position. These errors may be determined by recourse to logic, flow and block diagrams. Material or component faults, however, create signals (waveforms and/or levels) that are abnormal. Proper interpretation is necessary to specifically locate the fault.

### 3.1 TYPES OF FAULTS

The most common faults that occur in S-2000 are listed in relative decreasing order of occurence:

- 1. Improper use of oscilloscope and test equipment.

- 2. High resistance or open solder joints.

- 3. Leaky or shorted collector-to-emitter of emitter-follower.

- 4. Open emitter or emitter-follower

- 5. High leakage current in grounded-emitter.

- 6. Shorted collector-to-emitter of grounded-emitter.

- 7. Open printed circuit line.

- \* Surface-barrier transistor logic circuits.

- 8. Shorted printed circuit lines.

- 9. High resistance or open contact of card corrector.

- 10. Improper component or value of component.

- 11. Broken bus lead.

#### Less common faults are:

- 1. Open base or collector of emitter-follower.

- 2. Open base, emitter or collector of grounded-emitter.

- 3. Collector-to-base short of grounded-emitter.

### Relatively rare faults are:

- 1. Open or shorted capacitor.

- 2. Open or shorted resistor.

- 3. Out-of-tolerance resistor or capacitor.

Note that many of the above faults will have similar symptoms and their relative occurrence is a guide to the type of failure at hand. For example; open or shorted resistors and capacitors rarely, if ever, occur. Generally it is a poor solder joint, open contact, open printed circuit line or shorted circuit lines.

### CAUSES OF FAULTS

The typical causes of the various type faults are described below: a knowledge of which will help prevent faults and also help interpret the "case histories" of failures.

# Improper Use of Equipment

Improper use of the oscilloscope is one of the most common faults, especially among inexperienced personnel. An oscilloscope misused and misinterpreted can cause considerable lost time in searching for and correcting non-existent fault conditions, and may even

be destructive to the circuitry. One should take care to be certain that the oscilloscope probe is properly adjusted and calibrated. Most oscilloscopes have built-in 1,000 cycle square wave calibration signals. The ground return to the probe lead should be short when waveforms are to be critically analyzed. One should not connect the probe to the circuit under study with hook-up wire. Proper connections may be inconvenient, but are essential when fast rise times, short pulse widths and noise are to be observed and studied.

The probe should be used at all times. Makeshift connections greatly negate the useful characteristics of the oscilloscope (particularly wide bandwidth and low input capacity) and are often the cause of peculiar waveforms. They may even be the cause of circuit malfunction because of excessive stray capacity, coupling into other wires, and shorted pins. This is particularly important around single shots and timing flip-flops.

One should always be careful not to cause shorts when connecting test equipment or temporary wires to the connector pins. Most emitter-follower failures are directly caused by such oversights.

# High Resistance or Open Solder Joints

High resistance or open solder joints are a common problem. They may occur at any time and have a tendency to be temperature sensitive because of unequal expansion of the wire, solder and/or printed board material. They are especially prevalent after extended periods of operation at relatively high ambient temperatures. This is because the physical processes which effect their failure are proportional to the integrated product of time and temperature. A rough measure of this product is the amount of gray coloration that appears on the surface of the solder.

Poor solder joints occur most often between the solder and tinned bus wire, sometimes between solder and component leads, and, only rarely, between the solder and printed circuit lines. Feed through wires are more susceptible since there are two solder-to-bus-wire joints. This is generally attributed to the fact that tinned wire and leads suffer from surface changes when stored for long periods (as is the case in production stocking) and exposed to oxygen, sulfur and human perspiration. The printed circuit lines have an immersion gold coating and thus suffer much less. Considerable attention is given to proper storage of wire and components, and where possible, immersion gold-coating. Considerable care is given in production (and should be given in repair) to a proper soldering procedure, especially concerning temperature and flux. The temperature should be such that the solder flows easily and wets the surface. Only pine rosin and alcohol (usually butyl) should be used. Any

residue must be completely removed with a solvent. Ethylene dichloride, amyl acetate (banana oil) and butyl alcohol are suitable solvents. All of these solvents are inflammable. They can be toxic if left on the skin for long periods or if inhaled to excess. Small amounts should be used in a well ventilated place. Smoking during use is undesirable. Flux residues tend to be hygroscopic and sticky, thus collecting dust and salts in an electolytic medium. This will attack the joint. No other fluxes can be used as they invariably contain ionic substances that are difficult to remove and will always attack the joint.

Care should be taken to keep the cards clean and free from corrosive substances such as: human perspiration; sulfur bearing substances as rubber products and food particles; and tar bearing substances, such as cigar and cigarette smoke.

The above may seem trivial but is really of great importance when it is remembered that there are nearly a quarter million solder joints in the central arithmetic and memory control alone, that each must go through at least 2,000 hours of debugging and testing time, and must have a useful life of at least ten years.

Particular attent on should be paid to the effects of changing temperature on poor solder joints, and in generating poor solder joints among the weak sisters. The rise in ambient air temperature in the central computer is about 8° Celsius (Centigrade) over that of the intake air. Some of the component leads and solder joints may be as high as 15°C over that of the intake air. Since the coefficients of thermal expansion of copper and eutectic solder differ by 12 X 10° per degree Celsius, this 15°C temperature rise and fall (when turning the computer on and off) causes a differential movement between the copper and solder of two parts in ten thousand. This is not serious in properly "wetted" solder joints, but will eventually cause failure in poor joints. Since the solder has the larger co-efficient of thermal expansion, there is a greater tendency for a marginal joint to be open when the computer is running warm (the ambient air temperature is high) than when it is running coller.

The thermal time constants are rather long for the card about 20 minutes and for a module cabinet about one hour. It requires about four to five thermal time constants to obtain thermal equilibrium. Thus, about 4 to 5 hours are required for all the internal components to reach thermal equilibrium and about 80 to 100 minutes for a card, if it is put cold into a warm cabinet.