Section 2

Rigid Disk Data

Separators/Synchronizers

and ENDECs

# **Section 2 Contents**

| DD9461/DD9465 Data Computation                                                |       |

|-------------------------------------------------------------------------------|-------|

| DP8461/DP8465 Data Separator                                                  | 2-3   |

| DP8451/DP8455 Data Synchronizer                                               | 2-3   |

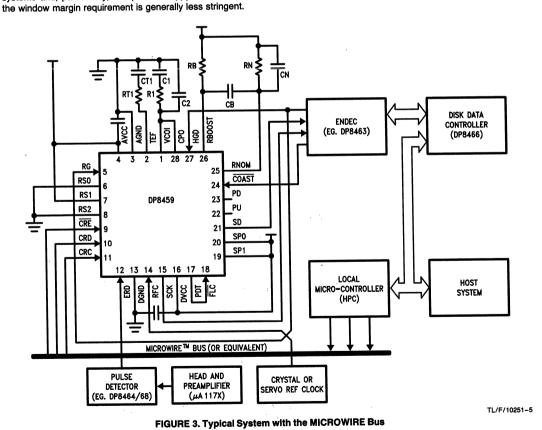

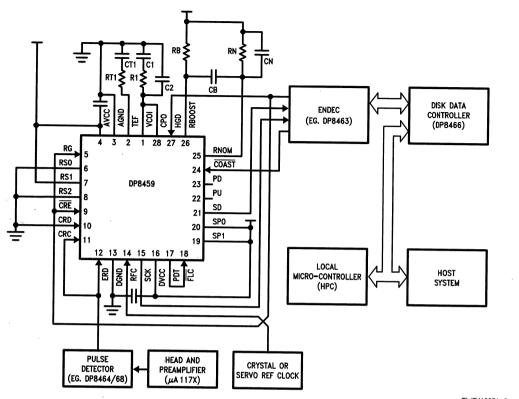

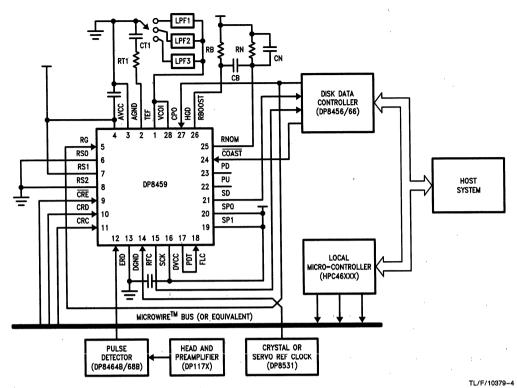

| DP8459 All-Code Data Synchronizer                                             | 2-29  |

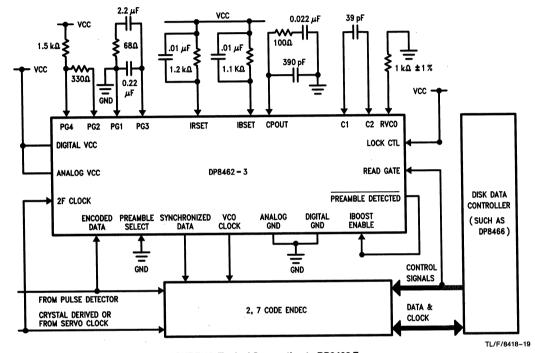

| DP8462 2, 7 Code Data Synchronizer                                            | 2-64  |

| DP8463B (2, 7) ENDEC                                                          | 2-85  |

| DP8469 Synchronizer/2, 7 ENDEC                                                | 2-100 |

| AN-414 Precautions for Disk Data Separator (PLL) Designs—How to Avoid Typical |       |

| Problems                                                                      | 2-119 |

| AN-415 Designing with the DP8461                                              | 2-123 |

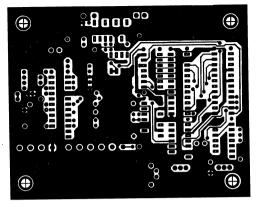

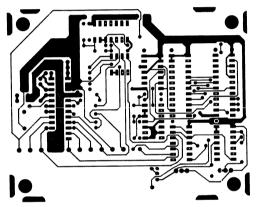

| AN-494 Designing with the DP8462                                              | 2-128 |

| AN-416 Designing with the DP8465                                              | 2-126 |

| AN-581 Application Issues for the DP8465 Family of Data Synchronizers         | 2-140 |

| AN EZO DO 450 Mindou Other English of Data Synchronizers                      |       |

| AN-578 DP8459 Window Strobe Function                                          | 2-154 |

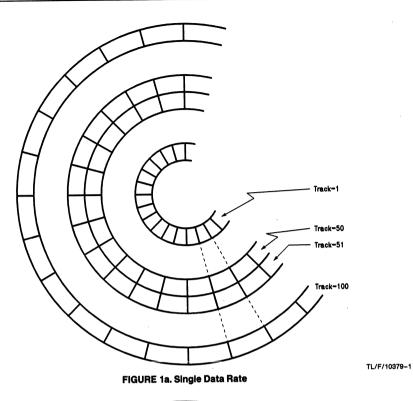

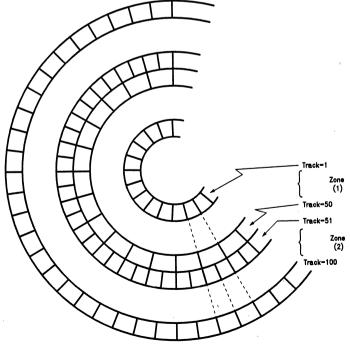

| AN-599 DP8459 Zoned Bit Recording                                             | 2-163 |

| AN-502 DP8459 Evaluation Board                                                | 0.100 |

# National Semiconductor

# DP8461/65 Data Separator DP8451/55 Data Synchronizer

## **General Description**

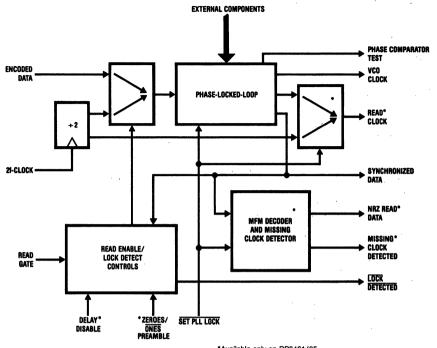

#### DP8461/65

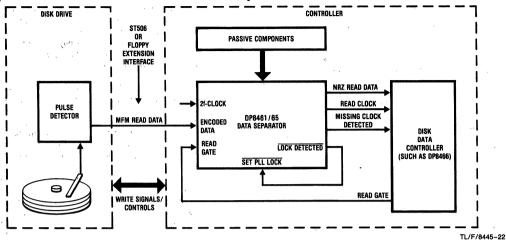

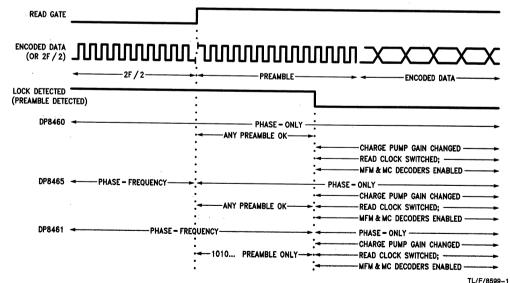

The DP8461/65 Data Separators are designed for applications in disk drive memory systems, and depending on system requirements, may be located either in the drive or in the controller. They receive digital pulses from a pulse detector circuit (such as the DP8464 Disk Pulse Detector) if situated in the drive, or from an ST506 type interface if situated in the controller. After locking on to the frequency of these input pulses, they separate them into synchronized data and clock signals. While in the non-read mode, both of these circuits employ a phase-frequency comparator to keep the VCO locked to the 2F input (this signal may be derived from a crystal or a servo track). The DP8465 switches to a phase only comparator when the read mode is entered. The DP8461 continues to use a phase-frequency comparator until the preamble detection circuit has detected two bytes of preamble. This feature thus restricts the DP8461 to use with codes employing the 1010 ... preamble, MFM, and certain RLL Codes such as 1.7 and 1.8 employ such a preamble. If a Run Length Limited code is used or if the user wishes to do his own data separation, the synchronized data output is available to allow external circuitry to perform the data decoding function.

All of the digital input and output signals are TTL compatible and only a single  $+5\mathrm{V}$  supply is required. The chip is housed in a narrow 24-pin dual-in-line package (DIP) and is fabricated using Advanced Schottky bipolar analog and digital circuitry. This high speed I.C. process allows the chip to work with data rates up to 20 Mbit/sec. There are two versions of the chip, each having a different decode window error specification. These two versions (-3, -4) are designed to operate from 2 to 20 Mbit/sec and are tested for their respective window tolerances, as specified in the Electrical Characteristics Table.

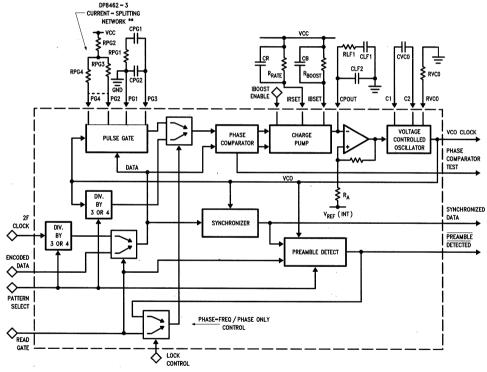

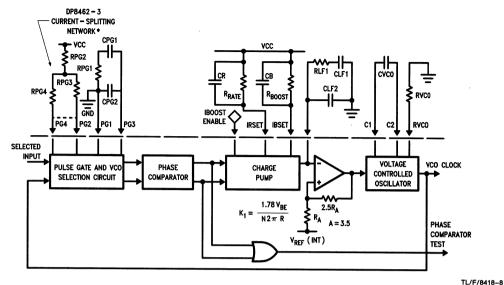

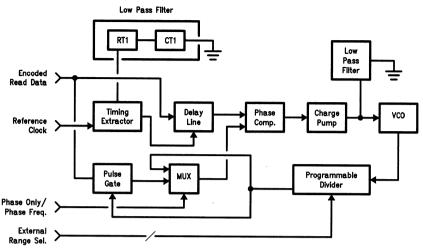

The DP8461/65 feature a phase-lock-loop (PLL) consisting of a phase-frequency comparator, pulse gate (to allow for phase-only operation in the read mode), charge pump, buffering amplifier, and voltage-controlled-oscillator (VCO). Pins are provided for the user to select the values of the external filtering components required for the VCO, and two current setting resistors for the charge pump. The DP8461/65 have been designed to be capable of locking onto the incoming preamble data pattern within the first two bytes, using an available high rate of charge pump current. Once lock-on has been achieved, the charge pump can be switched to a

lower rate (both rates being determined by the external resistors) to improve bit-jitter immunity for the remainder of the read operation. At this time the READ CLOCK OUTPUT switches, without glitching, from half the 2F-CLOCK frequency to half the VCO CLOCK frequency. After lock-on, with soft sectored disks, the MISSING CLOCK DETECTED output indicates when a missing clock occurs so the controller can align byte boundaries to begin deserialization of the incoming data.

#### DP8451/55

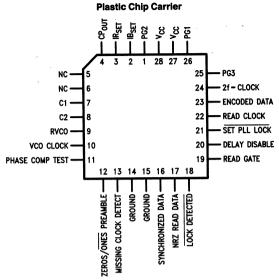

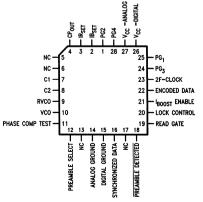

The DP8451/55 perform the same data synchronization function of the DP8461/65 with no MFM related circuitry. As with the DP8461, the DP8451 continues in the phase-frequency comparison mode until two bytes of preamble are detected. The DP8451/55, which are packaged in 20 pin DIPs or 20-pin PCC's, exclude the READ CLOCK generating circuitry along with the MFM Decoder, Missing Clock Detector, and Read Enable Delay. Users who require only the SYNCHRONIZED DATA OUTPUT and VCO CLOCK OUTPUT can use the DP8451/55 as alternatives to the DP8461/65.

#### **Features**

- Operates at data rates up to 20 Mbit/sec

- Phase-Frequency comparison in non-read mode

- Phase-Frequency comparison in preamble—DP8461/51

- Separates MFM data into read clock and serial NRZ data (DP8461/65)

- 4 byte preamble-lock indication capability

- Preamble recognition of MFM encoded "0"s or "1"s

- User-determined PLL loop filter network

- PLL charge pump has two user-determined tracking rates

- External control of track rate switchover

- No glitch on READ CLOCK at switchover (DP8461/65)

- Synchronized data provided as an output (for RLL codes) (all four devices)

- ORed phase comparator outputs for monitoring bit-shift

- Missing clock detected for soft sectored disks

- Less then ½W power consumption

- Standard narrow 24-pin DIP or 28 pin Plastic Chip Carrier Package

- Single +5V supply

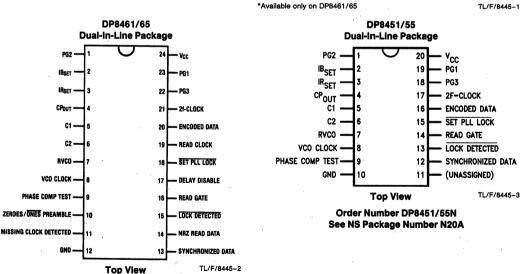

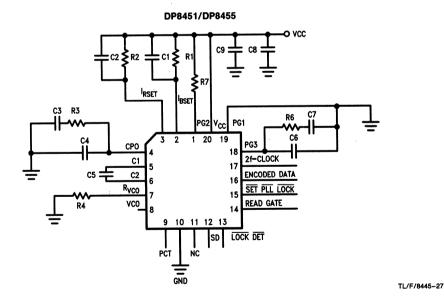

# **Simplified Block and Connection Diagrams**

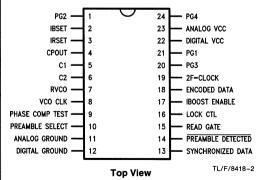

Order Number DP8461/65J or N See NS Package Number J24F or N24C

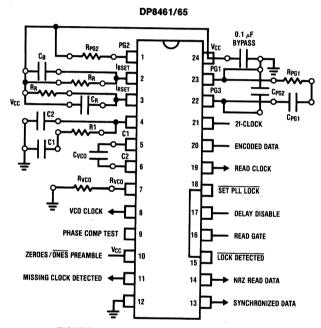

#### Pin Descriptions\*

Power Supply 24 V<sub>CC</sub> +5V ±5%

12 Ground

TTL Level Logic Inputs

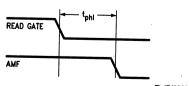

16 READ GATE: This is an active high input signal that sets the DP8461/65 Data Separator into the Read Mode.

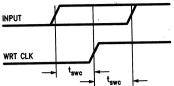

- 17 DELAY DISABLE: This input determines the delay from READ GATE going high to the time the DP8461/65 enters the Read Mode. If DELAY DISABLE is set high, this delay is within one cycle of the V<sub>CO</sub>-CLOCK signal. If DELAY DIS-ABLE is set low, the delay is thirty two-cycles of the VCO CLOCK, as shown in Figure 1.

- 18 SET PLL LOCK: This input allows the user to control the on-chip PLL track rate. A high level at this input results in the PLL being in the high track rate. If this input is connected to the LOCK DETECTED output, the PLL will go into the low track rate mode immediately after lock is detected. A low level on this pin is also used to enable the MFM Decoder, the Missing Clock Detector, and to switch the Read Clock Multiplexer from half-2F-CLOCK to half-VCO.

- 10 ZEROES/ONES PREAMBLE: A high level on this input enables the MFM Decoder circuit to recognize an All Zeros data preamble. A low level results in the recognition of an All Ones data preamble.

- 20 ENCODED DATA: This input is connected to the output of the head amplifier/pulse-detecting network located in the disk drive. Each positive edge of the ENCODED DATA waveform identifies a change of flux on the disk. In the case of MFM encoded data, the input will be raw MFM.

- 21 2f-CLOCK: This is a system clock input, which is either a signal generated from the servo track (for systems utilizing servo tracks), or a signal buffered from a crystal, 2f CLOCK MUST ALWAYS BE APPLIED TO THIS INPUT FOR PROP-ER OPERATION.

TTL Level Logic Outputs

- 8 VCO CLOCK: This is the output of the on-chip VCO, transmitted from an Advanced Schottky-TTL buffer. It is synchronized to the MFM data output.

- 15 LOCK DETECTED: This output goes active low only after both PLL Lock has occurred and 16 pulses of the pream-

ble pattern have been recognized. It remains low until READ GATE goes inactive.

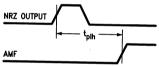

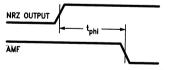

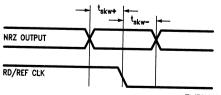

- 14 NRZ READ DATA: This is the NRZ (decoded MFM) data output, whose leading edges coincide with the trailing edge of READ CLOCK.

- 13 SYNCHRONIZED DATA: This output is the same encoded data that is input to the chip, but is synchronous with the negative edge of the VCO CLOCK.

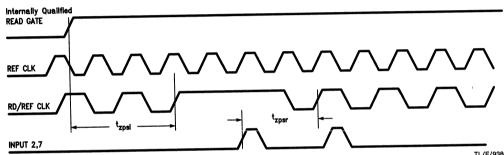

- 11 MISSING CLOCK DETECTED: When an MFM missing clock is detected, this output will be a single pulse (of width equal to one cycle of READ CLOCK) occurring as shown in Figure 2.

- 19 READ CLOCK: This is half VCO CLOCK frequency when SET PLL LOCK is low; it is half 2f-CLOCK frequency at all other times. A deglitcher is utilized to ensure that no short clock periods occur during either switchover.

- 9 PHASE COMP TEST: This output is the logical "OR" of the Phase Comparator outputs, and may be used as a bitshift indicator on for PLL analysis purpose.

Analog Signals

- 23, 22, PG1, PG3: The external capacitors and resistor of the Pulse Gate filter are connected to these pins. PG1 should be connected directly to the ground pin, pin 12.

- 1 PG2: This is the Pulse Gate current supply.

- 3 IRSET: The current into the rate set pin (VBF/RBATE) is used to set the charge pump output current for the low tracking rate.

- 2 IBSET: The current into the boost set pin (VBE/RBOOST) is used to set the amount by which the charge pump current is increased for the high tracking rate. (I<sub>INPUT</sub> = I<sub>RATE</sub> Set + I<sub>BOOST</sub> Set).

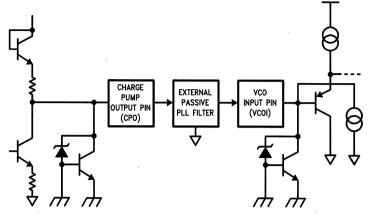

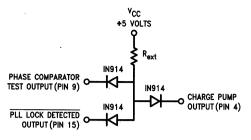

- 4 CPOUT: CHARGE PUMP OUT/BUFFER AMP IN is available for connection of external filter components for the phase-lock-loop. In addition to being the charge pump output node, this pin is also the noninverting input to the Buffer Amplifier.

- 7 RVCO: The current at this pin determines the operating currents within the VCO.

- 5, 6 VCO C1, C2: An external capacitor connected between these pins sets the nominal VCO frequency.

#### Absolute Maximum Ratings

If Military/Aerospace specified devices are required. please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage 7V 7V

TTL Inputs

Output Voltages 7V Input Current (CPOUT, IRSET, IBSET, RVCO) 2 mA Storage Temperature -65°C to 150°C

## **Operating Conditions**

| Symbol          | Parameter                       | Conditions          | Min  | Тур  | Max           | Units      |

|-----------------|---------------------------------|---------------------|------|------|---------------|------------|

| V <sub>CC</sub> | Supply Voltage                  |                     | 4.75 | 5.00 | 5.25          | V          |

| T <sub>A</sub>  | Ambient Temperature             |                     | 0    | 25   | 70            | <b>°</b> C |

| ОН              | High Logic Level Output Current | VCO Clock<br>Others |      |      | -2000<br>-400 | μΑ         |

| l <sub>OL</sub> | Low Logic Level Output Current  | VCO Clock<br>Others |      |      | 20<br>8       | mA         |

<sup>\*</sup>Pin Number Designations apply only to the DP8461/65. See Connection Diagram for DP8451/55.

## Operating Conditions (Continued)

| Symbol                           | Parameter                                                                                                     | Conditions | Min          | Тур | Max | Units    |

|----------------------------------|---------------------------------------------------------------------------------------------------------------|------------|--------------|-----|-----|----------|

| <sup>f</sup> DATA                | Input Data Rate                                                                                               |            | 2.0          |     | 20  | Mbit/sec |

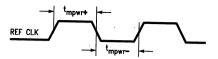

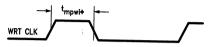

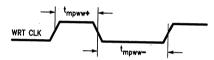

| <sup>t</sup> wcĸ                 | Width of 2f-CLOCK, High or Low                                                                                |            | 10           |     |     | ns       |

| twpD                             | Width of ENCODED                                                                                              | HIGH       | 5 ns + 0.10t |     |     | ns       |

|                                  | DATA Pulse, (Note 2)                                                                                          | LOW        | 0.4t         |     |     |          |

| V <sub>IH</sub>                  | High Logic Level Input Voltage                                                                                |            | 2            |     |     | ٧        |

| $V_{IL}$                         | Low Logic Level Input Voltage                                                                                 |            |              |     | 0.8 | ٧        |

| tsetup<br>(READ Gate)            | Min. Amount of Time Which a<br>Positive Edge of READ Gate<br>Must Precede a Negative Edge<br>of a VCO (Pin 8) |            | 20           |     |     | ns       |

| <sup>t</sup> HOLD<br>(READ Gate) | Min. Time Required for a Positive Edge of a READ Gate to be Held after a Negative Edge of a VCO (Pin 8)       |            | 10           |     |     | ns       |

# DC Electrical Characteristics Over Recommended Operating Temperature Range

| Symbol          | Parameter                        | Conditions                                                                                         | Min                                                                                                                                    | Тур                                                                                                                  | Max                                                                                                                                          | Units |

|-----------------|----------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|

| V <sub>IC</sub> | Input Clamp<br>Voltage           | $V_{CC} = Min.,$ $I_{I} = -18 \text{ mA}$                                                          |                                                                                                                                        |                                                                                                                      | -1.5                                                                                                                                         | ٧     |

| V <sub>OH</sub> | High Level Output<br>Voltage     | $V_{CC} = Min.,$ $I_{OH} = Max.$                                                                   | V <sub>CC</sub> -2V                                                                                                                    | V <sub>CC</sub> -1.6V                                                                                                | •                                                                                                                                            | ٧     |

| V <sub>OL</sub> | Low Level Output<br>Voltage      | $V_{CC} = Min.,$ $I_{OL} = Max.$                                                                   | -                                                                                                                                      |                                                                                                                      | 0.5                                                                                                                                          | V     |

| lн              | High Level Input<br>Current      | $V_{CC} = Max.,$ $V_{I} = 2.7V$                                                                    |                                                                                                                                        |                                                                                                                      | 20                                                                                                                                           | μΑ    |

| I <sub>ΙL</sub> | Low Level Input<br>Current       | V <sub>CC</sub> = Max., V <sub>I</sub> = 0.4V                                                      |                                                                                                                                        |                                                                                                                      | -200                                                                                                                                         | μΑ    |

| ю               | Output Drive<br>Current (Note 1) | V <sub>CC</sub> = Max.,<br>V <sub>O</sub> = 2.125V                                                 | 12                                                                                                                                     |                                                                                                                      | -110                                                                                                                                         | mA    |

| Icc             | Supply Current                   | V <sub>CC</sub> = Max.                                                                             |                                                                                                                                        |                                                                                                                      | 100                                                                                                                                          | mA    |

| lout            | Charge Pump<br>Output Current    | $500 \mu A \le I_{RSET} + I_{BSET} \le 2000 \mu A$ $200 \mu A \le I_{RSET} + I_{BSET} < 500 \mu A$ | I <sub>TYP</sub> 18 (I <sub>R</sub> + I <sub>B</sub> )<br>- 30 μA<br>I <sub>TYP</sub> 08 (I <sub>R</sub> + I <sub>B</sub> )<br>- 80 μA | 1.95 (I <sub>RSET</sub> + I <sub>BSET</sub> )<br>- 70 μA<br>1.95 (I <sub>RSET</sub> + I <sub>BSET</sub> )<br>- 70 μA | I <sub>TYP</sub> + .18 (I <sub>R</sub> + I <sub>B</sub> )<br>+ 30 μA<br>I <sub>TYP</sub> + .08 (I <sub>R</sub> + I <sub>B</sub> )<br>+ 80 μA | μА    |

Note 1: This value has been chosen to produce a current that closely approximates one-half of the true short-circuit output current. IOS.

Note 2: t is defined as the period of the encoded MFM data, or two times the VCO period.

# AC Electrical Characteristics Over Recommended V<sub>CC</sub> and Operating Temperature Range.

(All Parts unless stated otherwise)

$(t_{R} = t_{F} = 2.0 \text{ ns}, V_{IH} = 3.0 \text{V}, V_{IL} = 0 \text{V})$

| Parameter                                                                                                     | Min                                                                                                                                                                                                                                                                                                                                                                     | Тур                                                                                                                                                                                                                                                                                                                                                                     | Max                                                                                                                                                                                                                                                                                                                                                                     | Units                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Positive READ CLOCK transitions from READ GATE set active until PLL Lock sequence begins (DELAY DISABLE low)  |                                                                                                                                                                                                                                                                                                                                                                         | 16                                                                                                                                                                                                                                                                                                                                                                      | 17                                                                                                                                                                                                                                                                                                                                                                      | ×-                                                                                                                                                                                                                                                                                                                                                                                  |

| Positive READ CLOCK transitions from READ GATE set active until PLL Lock sequence begins (DELAY DISABLE high) |                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                     |

| Number of READ CLOCK cycles required to output each decoded MFM data bit (Note 3, 4)                          | _                                                                                                                                                                                                                                                                                                                                                                       | 2                                                                                                                                                                                                                                                                                                                                                                       | 3                                                                                                                                                                                                                                                                                                                                                                       | T-clock                                                                                                                                                                                                                                                                                                                                                                             |

| Positive READ CLOCK transitions required to transmit input MFM to output                                      | 1                                                                                                                                                                                                                                                                                                                                                                       | 2                                                                                                                                                                                                                                                                                                                                                                       | 3                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                               | Positive READ CLOCK transitions from READ GATE set active until PLL Lock sequence begins (DELAY DISABLE low)  Positive READ CLOCK transitions from READ GATE set active until PLL Lock sequence begins (DELAY DISABLE high)  Number of READ CLOCK cycles required to output each decoded MFM data bit (Note 3, 4)  Positive READ CLOCK transitions required to transmit | Positive READ CLOCK transitions from READ GATE set active until PLL Lock sequence begins (DELAY DISABLE low)  Positive READ CLOCK transitions from READ GATE set active until PLL Lock sequence begins (DELAY DISABLE high)  Number of READ CLOCK cycles required to output each decoded MFM data bit (Note 3, 4)  Positive READ CLOCK transitions required to transmit | Positive READ CLOCK transitions from READ GATE set active until PLL Lock sequence begins (DELAY DISABLE low)  Positive READ CLOCK transitions from READ GATE set active until PLL Lock sequence begins (DELAY DISABLE high)  Number of READ CLOCK cycles required to output each decoded MFM data bit (Note 3, 4)  Positive READ CLOCK transitions required to transmit | Positive READ CLOCK transitions from READ GATE set active until PLL Lock sequence begins (DELAY DISABLE low)  16 17  Positive READ CLOCK transitions from READ GATE set active until PLL Lock sequence begins (DELAY DISABLE high)  1 1  Number of READ CLOCK cycles required to output each decoded MFM data bit (Note 3, 4)  Positive READ CLOCK transitions required to transmit |

Note: For Further Information Refer to Application Notes AN-414, AN-415, and AN-416.

# **AC Electrical Characteristics** Over Recommended $V_{CC}$ and Operating Temperature Range. (Continued) (All Parts unless stated otherwise) $(t_B = t_F = 2.0 \text{ ns}, V_{IH} = 3.0 \text{V}, V_{II} = 0 \text{V})$

| Symbol                        | Parameter                                                                                                            | Min                                   | Тур                                   | Max                                   | Units      |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|------------|

| <sup>†</sup> READ ABORT       | Number of READ CLOCK cycles after READ GATE set low to read operation abort                                          |                                       |                                       | 2                                     | T-clock    |

| twindow                       | Variance of center of decode window from nominal DP84XX-3 (Note 7) DP84XX-4                                          |                                       |                                       | 6<br>10                               | ns         |

| ΦLINEARITY                    | Phase range for charge pump output linearity (Note 2)                                                                | $-\pi$                                |                                       | $+\pi$                                | Radians    |

| K <sub>1</sub>                | Phase Comparator—Charge Pump gain constant (Note 5)<br>(N = $f_{VCO}/f_{INPUT\ DATA}$ , 2 $\leq$ N $\leq$ 4 for MFM) |                                       | 1.78V <sub>BE</sub><br>N2πR           | ,                                     | Amps/rad   |

| VCONTROL                      | Charge pump output voltage swing from nominal                                                                        |                                       | ±100                                  |                                       | mV         |

| $K_{VCO}$ (= $A \times K_2$ ) | VCO gain constant ( $\omega_{VCO} = VCO$ center frequency in rad/s) (Note 1, 6)                                      | 1.20ω <sub>C</sub><br>V <sub>BE</sub> | 1.40ω <sub>C</sub><br>V <sub>BE</sub> | 1.60ω <sub>C</sub><br>V <sub>BE</sub> | rad/sec. V |

| f <sub>VCO</sub>              | VCO center frequency variation over temperature and V <sub>CC</sub>                                                  | -5                                    |                                       | +5                                    | %          |

| fMAX VCO                      | VCO maximum frequency                                                                                                |                                       | 60                                    |                                       | MHz        |

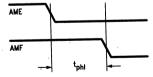

| tHOLD                         | Time READ CLOCK is held low during changeover after lock detection has occurred (Note 3)                             |                                       |                                       | 11/2                                  | T-clock    |

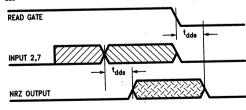

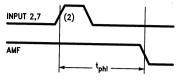

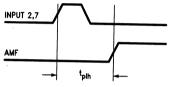

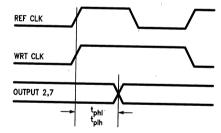

| t <sub>PHL</sub>              | Prop. Delay. VCO Neg. Edge to Synchronized Data Neg. Edge                                                            |                                       | 15                                    | 30                                    | ns         |

| t <sub>PLH</sub>              | Prop. Delay. VCO Negative Edge to<br>Synchronized Data Positive Edge                                                 | *                                     | 10                                    | 25                                    | ns         |

| t <sub>2F/RC</sub>            | Delay from 2F positive edge to READ CLOCK positive on negative edge (SET PLL LOCK high)                              | 10                                    |                                       | 35                                    | ns         |

Note 1: A sample calculation of frequency variation vs. control voltage:  $V_{IN} = \pm 0.1 V$ ;

$$K_{VCO} = \frac{\omega OUT}{V_{IN}} = \frac{0.4\omega_C}{0.2V} = \frac{2.0\omega_C}{V} \frac{\text{(rad/sec)}}{\text{(volt)}}$$

**Note 2:**  $-\pi$  to  $+\pi$  with respect to 2f VCO CLOCK

Note 3: T-clock is defined as the time required for one period of the READ CLOCK to occur.

Note 4: This number remains fixed after PLL Lock occurs.

Note 5: With respect to VCO CLOCK; I<sub>PUMP OUT</sub> = 1.9 I<sub>SET</sub>

$$I_{SET} = \frac{V_{BE}}{R_{SET}}$$

Note 6: Although specified as the VCO gain constant, this is the gain from the Buffer Amplifier input to the VCO output.

Note 7: This specification is guaranteed only for the conditions under which the parts were tested. However, significant variation from the formula is not expected for other data rates and filters. The filter values below were chosen for operation in an automatic test system (static window) environment. Different criteria may apply for choosing filter values in a disk system. See Loop Filter section for sample calculations of other filter values.

# Static Window Margin Test Loop Filter Component Values

| Part Type         | Data Rate Tested | C <sub>1</sub> | C <sub>2</sub> | R <sub>1</sub> | R <sub>RATE</sub> | R <sub>BOOST</sub> |

|-------------------|------------------|----------------|----------------|----------------|-------------------|--------------------|

| DP8451/55/61/65-4 | 5 Mbit/Sec       | 0.02 μF        | 150 pF         | 200Ω           | 750Ω              | 1.6 kΩ             |

| DP8451/55/61/65-3 | 10 Mbit/Sec      | .082 μF        | 1600 pF        | 27Ω            | 820Ω              | 619Ω               |

# External Component Selection (All Parts) (Note 1)

| Symbol             | Component                                                    | Min | Тур | Max  | Units |

|--------------------|--------------------------------------------------------------|-----|-----|------|-------|

| R <sub>VCO</sub>   | VCO Frequency Setting Resistor (Note 2)                      | 990 |     | 1010 | Ω     |

| C <sub>VCO</sub>   | VCO Frequency Setting Capacitor (Note 3, 4)                  | 20  |     | 245  | pF    |

| R <sub>RATE</sub>  | Charge Pump I <sub>RATE</sub> Set Resistor (Note 6)          | 0.4 |     | 4.0  | kΩ    |

| R <sub>BOOST</sub> | Charge Pump (High Rate) I <sub>BOOST</sub> Resistor (Note 6) | 0.5 |     | ∞    | kΩ    |

| C <sub>R</sub>     | I <sub>RATE</sub> Bypass Capacitor (Note 5)                  | .01 |     |      | μF    |

| C <sub>B</sub>     | I <sub>BOOST</sub> Bypass Capacitor (Note 5)                 | .01 |     |      | μF    |

Note 1: External component values for the Loop Filter and Pulse Gate are shown in tables 1 & 2.

Note 2: A 1% Component Tolerance is Required.

Note 3: These MIN and MAX values correspond to the MAX and MIN data rates respectively.

Note 4: The Component Tolerance is system dependent on how much center frequency deviation can be tolerated.

Note 5: Component Tolerance 15%.

**Note 6:** The minimum value of the parallel combination of  $R_{RATE}$  and  $R_{BOOST}$  is 350 $\Omega$ .

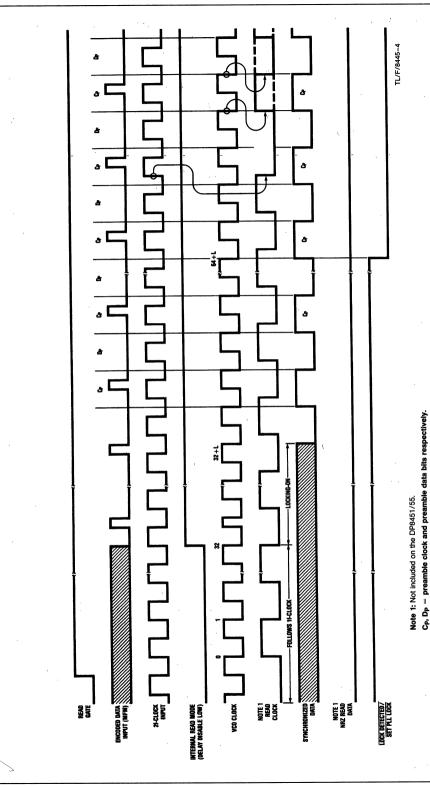

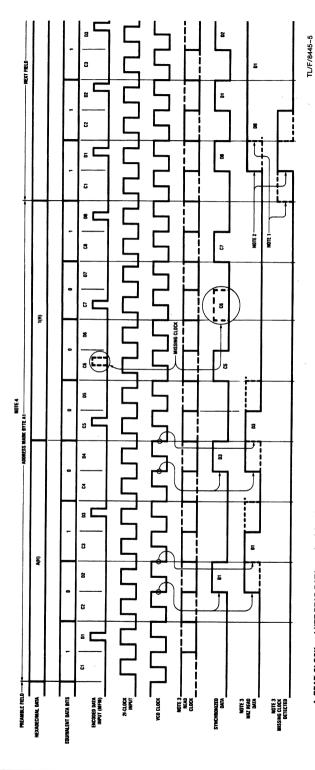

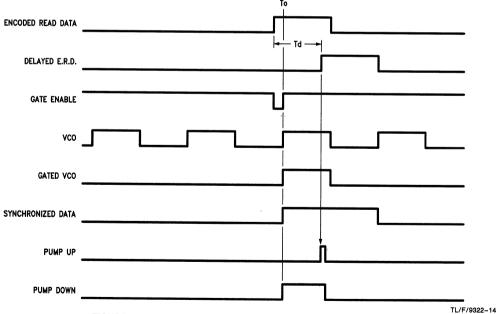

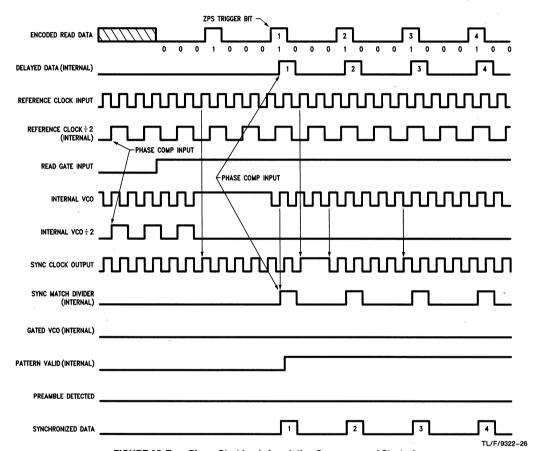

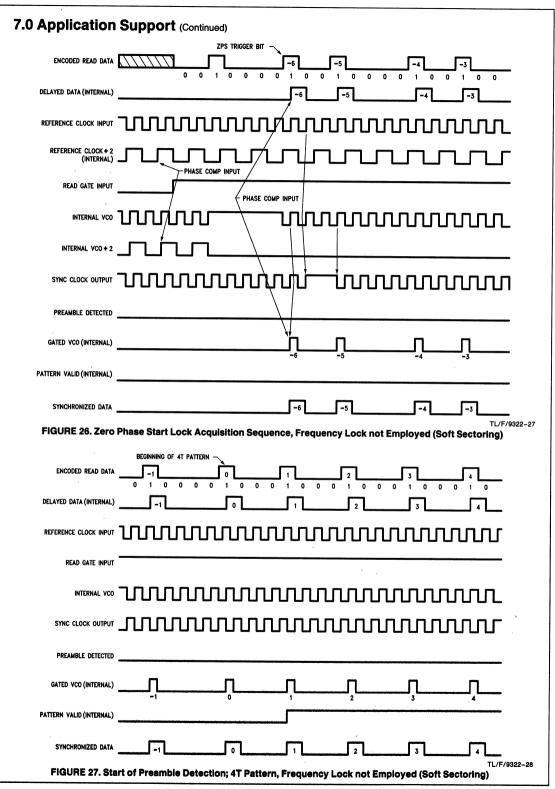

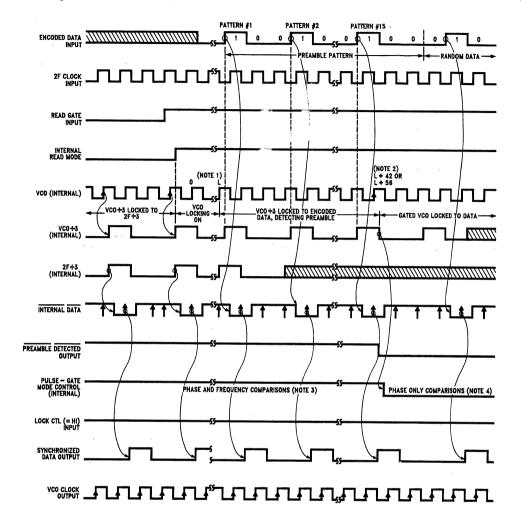

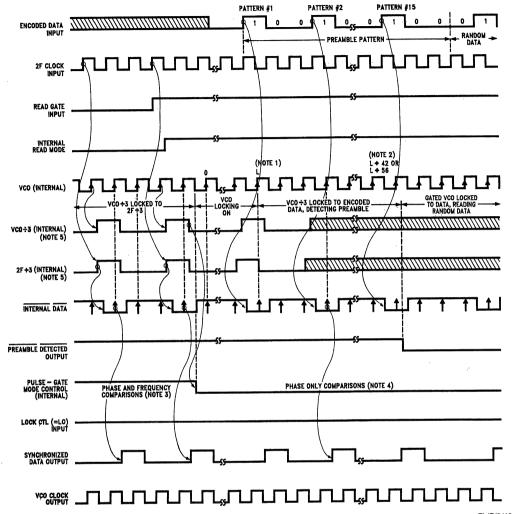

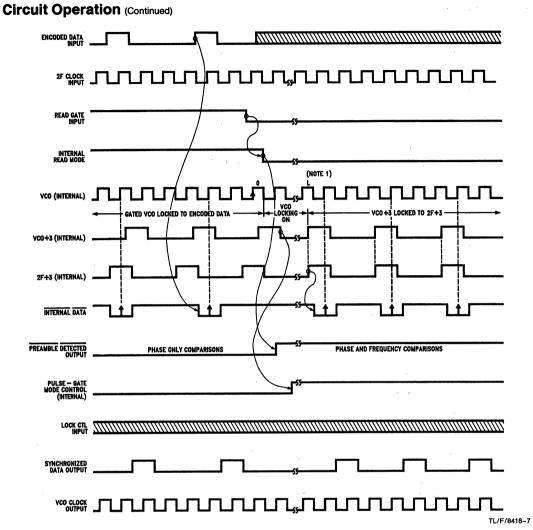

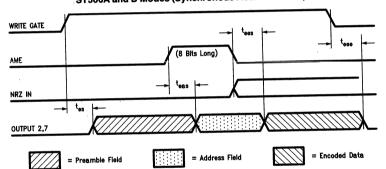

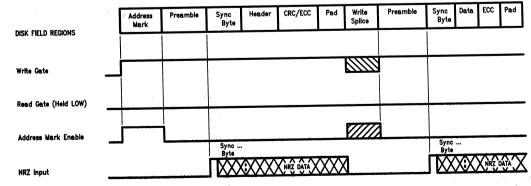

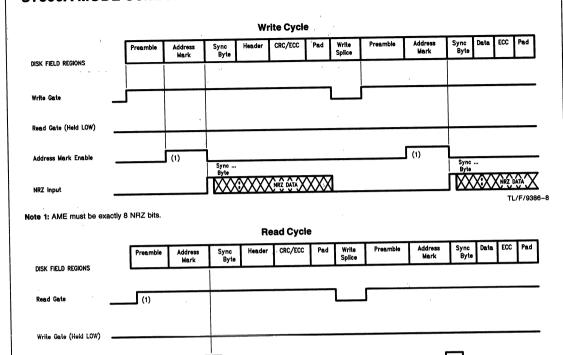

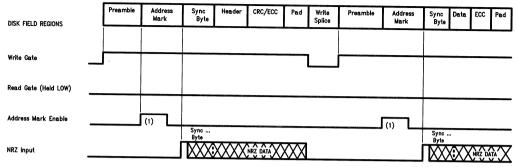

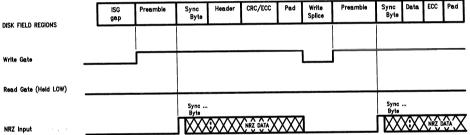

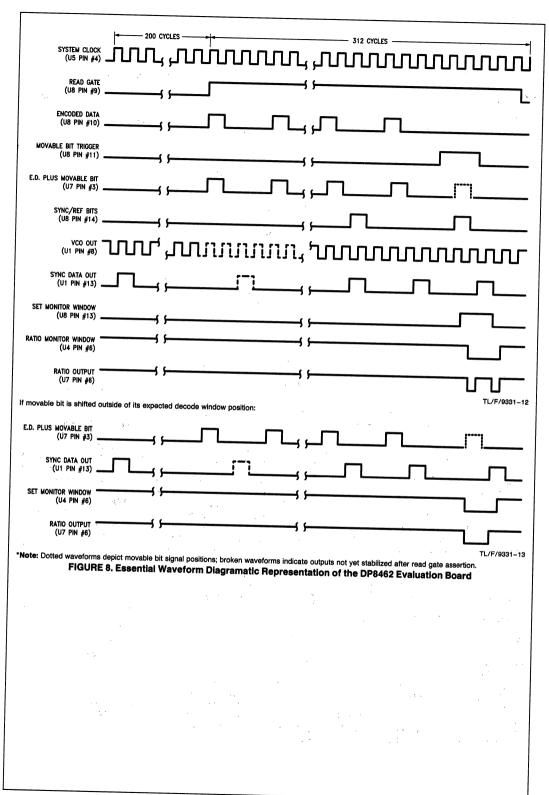

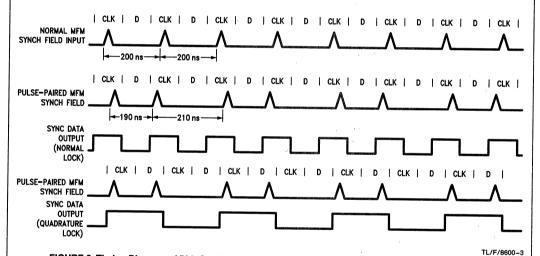

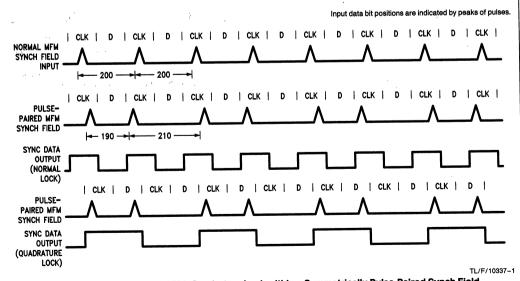

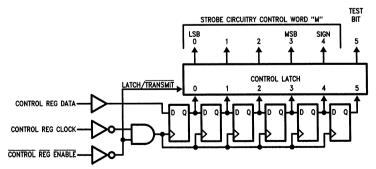

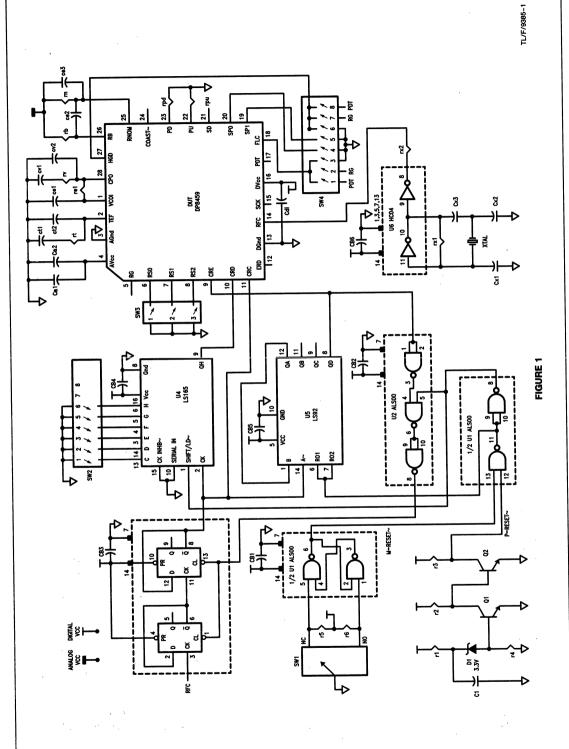

FIGURE 1. Lock-on Sequence Waveform Diagram

For DP8451/55 delay disable does not exist and part functions as if this input is always high.

At 64 + L, circuit has confirmed lock (has been in lock for 16 MFM clock bits). This sequence shows the MFM all-zeros preamble pattern.

L = Number of 2f-clock cycles required for VCO to lock, determined by external loop filter component values

At 32 + L, VCO has just locked.

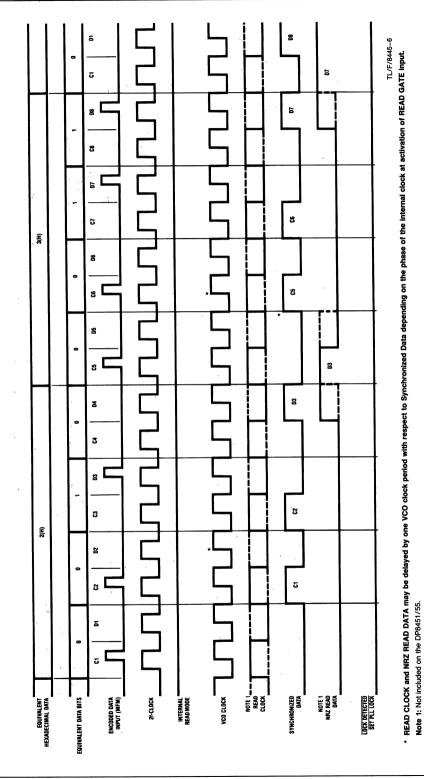

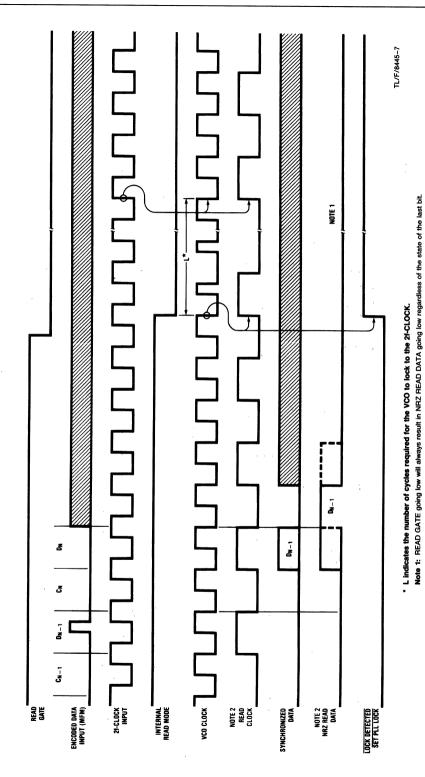

- \* READ CLOCK and NRZ READ DATA may be delayed by one VCO clock period depending on the phase of the internal clock at activation of READ GATE input.

- O MISSING CLOCK DETECTED is one READ CLOCK period ahead of the chip issuing D8 on the NRZ READ DATA output when READ CLOCK is delayed by one VCO clock period.

- MISSING CLOCK DETECTED is synchronous with the chip issuing D8 on the NRZ READ DATA Output when READ CLOCK is not delayed.

- ® Not included on the DP8451/55.

- The AI byte is shown only as an example address mark byte. Any missing clock bit which is framed by two existing clock bits will produce a missing clock detected pulse.

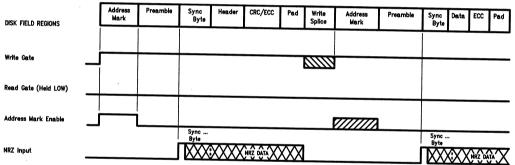

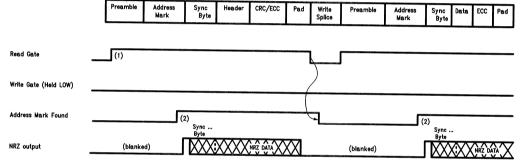

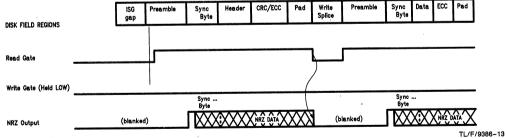

FIGURE 2. Missing Clock Detection Waveform Diagram

FIGURE 3. Locked-On Waveform Diagram

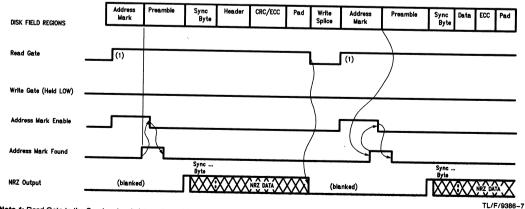

Note 2: Not included on the DP8451/55.

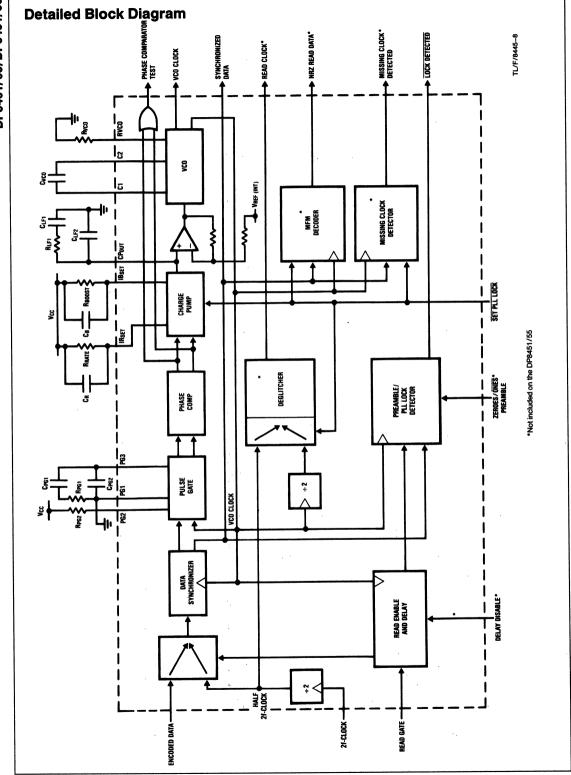

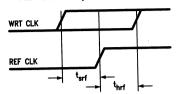

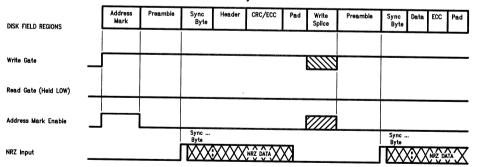

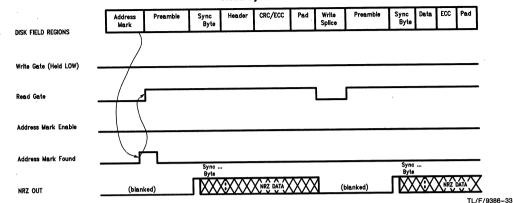

FIGURE 4. Lock-Ending Sequence Waveform Diagram

## **Circuit Operation**

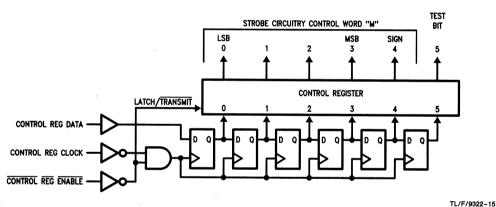

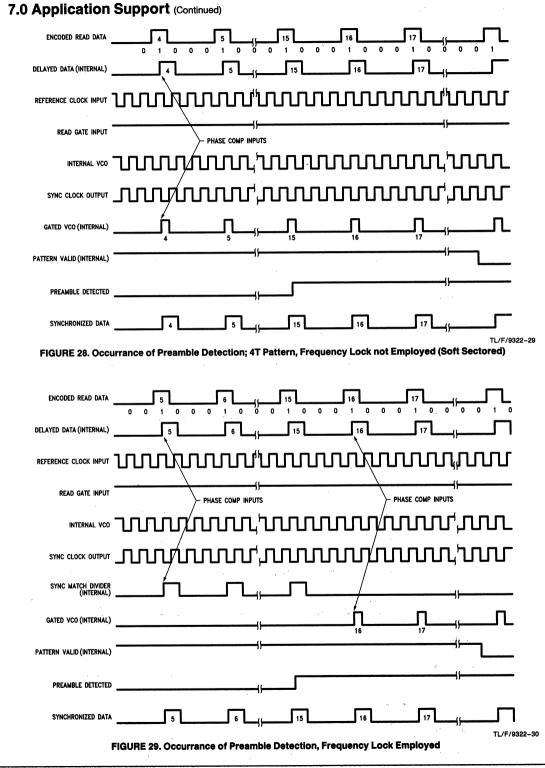

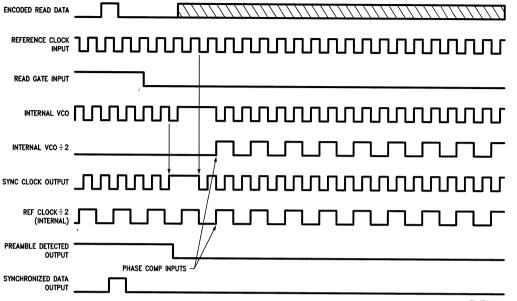

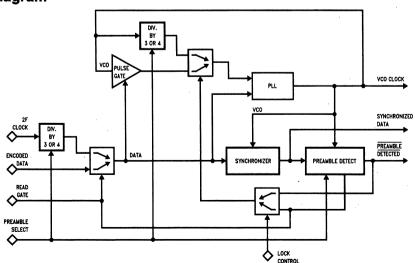

When the READ GATE input goes high, the DP8461/65 will enter the read mode after a period determined by the state of the DELAY DISABLE pin. This may be either one or thirty two VCO CLOCK cycles. Once in the read mode the DP8465 switches from using a phase-frequency comparator to a phase-only comparator, i.e. the pulse gate is activitated. At this time, however, the DP8461 continues to use a phase-frequency comparator. Referring to Figure 1, as the read mode is entered, the phase-locked-loop reference signal is switched from 2F-CLOCK INPUT to the ENCODED DATA. The PLL, initially in the high-tracking rate mode, then attempts to lock onto the incoming encoded data stream. As soon as two bytes of the selected preamble are detected. (the selection is determined by the ZEROES/ONES PREAMBLE pin) the LOCK DETECTED OUTPUT goes low. At this time the DP8461 switches from using a phase-frequency comparator to using the pulse gate, thus beginning phase only comparisons. In a typical MFM disk drive application, the LOCK DETECTED OUTPUT is directly connected to the SET PLL LOCK INPUT. With this connection, track rate selection, clock output switchover, and data output enabling will occur after two consecutive preamble bytes have been detected by the chip. Typically it takes less than one byte time for the VCO to lock to the data sufficiently for preamble detection to begin following the start of the Read

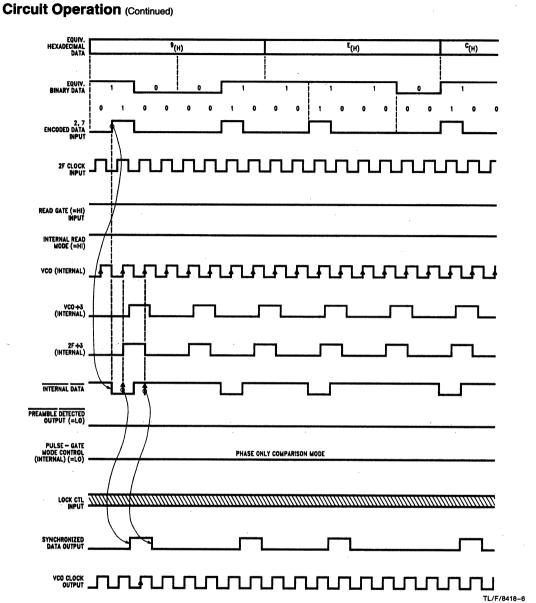

A low level on the SET PLL LOCK causes the PLL Charge Pump to switch from the high to low tracking rate. At the same time, the source of the READ CLOCK signal is switched from half the frequency of the 2F-CLOCK to half the VCO CLOCK. The MFM decoder also becomes enabled and begins to output decoded NRZ data. If a zeroes data preamble is present, the NRZ READ DATA OUTPUT will remain low until the end of the preamble. It will then output whatever NRZ data is present after the preamble field has ended, as shown in Figures 2 and 3.

When the READ GATE goes low, signifying the end of a read operation, the DP8461/65 will return to phase-frequency comparator operation. Figure 4 shows the sequence when READ GATE goes low. The PLL reference signal is switched back to half the 2F-CLOCK and the LOCK DETECTED OUTPUT (and therefore the SET PLL LOCK INPUT) goes high. The PLL then returns to the high track rate, and the output signals return to their initial conditions. The 2F-CLOCK MUST BE APPLIED AT ALL TIMES to the DP8461/65 and DP8451/55 for proper operation.

Since the DP8461/51 employs a phase-frequency comparator until two bytes of the preamble (actually any 16 pulses within a 1010 ... pattern) have been detected, care must be taken to ensure that when using this circuit the READ GATE is applied only within a field containing the 1010 ... pattern. In soft sectored drives the head may be positioned anywhere on the track when initiating a read operation. Therefore, either a controller which only issues READ GATE when a high frequency synchronization field is present, or a simple external circuit between the controller and DP8461/51 to qualify the READ GATE, must be used.

#### **CIRCUIT DESCRIPTION**

1. Read Enable and Delay (DP8461/65 only): If the DELAY DISABLE input is connected low, then thirty two VCO CLOCK cycles after READ GATE goes active, the DP8461/65 will go into the read mode. If the DELAY DIS-

ABLE input is connected high, the chip will go into the read mode one VCO CLOCK cycle after READ GATE goes active. (The 32 cycle delay is permanently disabled in the DP8451/55).

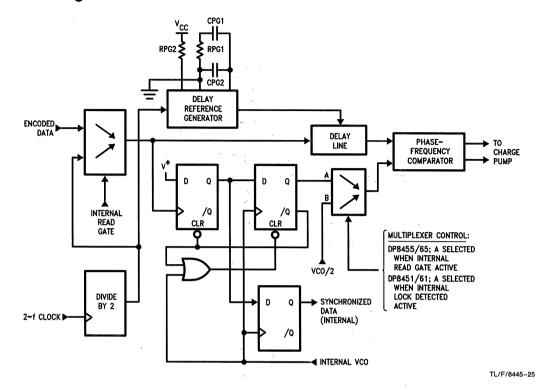

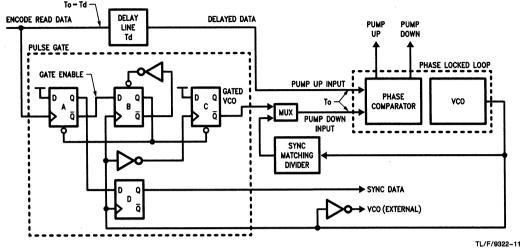

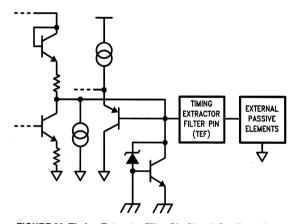

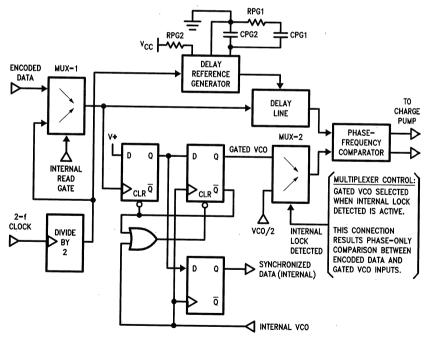

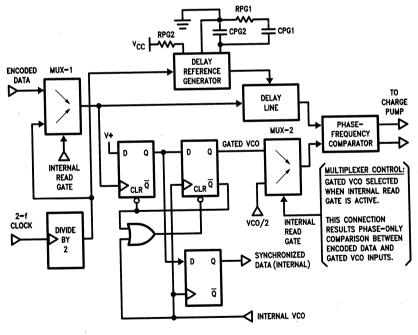

2. Pulse Gate, including Multiplexer and Data Synchronizer: The Input Multiplexer selects the input to the phase-lock-loop. While the chip is in the bypassed (non-read) mode, the VCO frequency is phase and frequency locked to the 2F-CLOCK INPUT frequency. In the read mode the Input Multiplexer switches to the ENCODED DATA signal and the VCO CLOCK then begins to synchronize with the ENCODED DATA signal. Also, as soon as the read mode is entered, the DP8455/65 cease phase and frequency comparisons by employing the Pulse Gate.

In the DP8461/51 option, switchover from the phase-frequency comparator to the pulse gate (phase-only comparator) occurs after two bytes of the 1010 ... pattern have been detected by the preamble pattern detector.

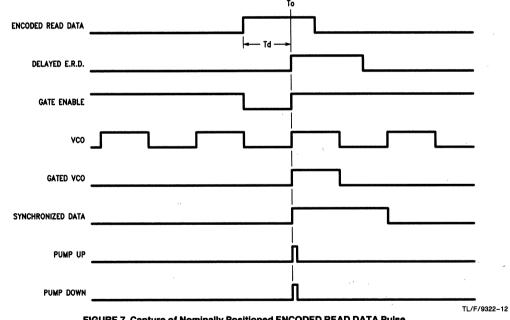

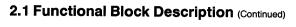

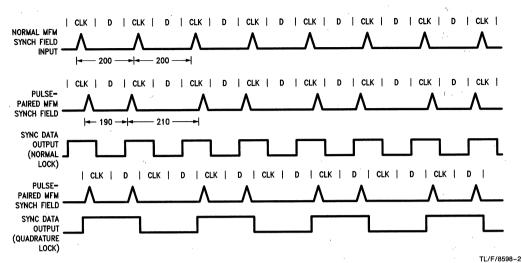

The Pulse Gate allows a reference pulse from the VCO into the Phase Comparator only after an ENCODED DATA bit has arrived. It utilizes a scheme which delays the incoming data by one-half the period of the 2F-CLOCK. This optimizes the position of the decode window and allows input jitter of approximately half the 2F-CLOCK period. The decode window error can be determined from the specification in the Electrical Characteristics Table.

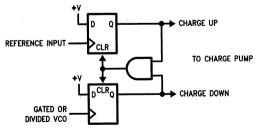

- Phase Comparator: The Phase Comparator receives its inputs from the Pulse Gate, and is edge-triggered from these inputs to provide charge-up and charge-down outputs.

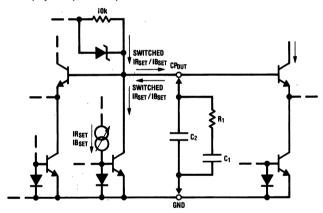

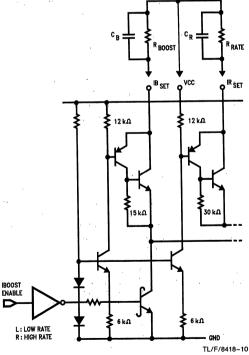

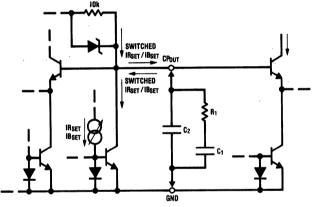

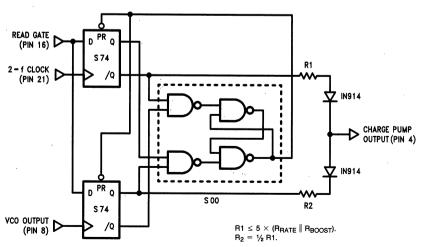

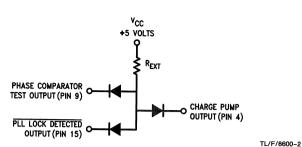

- 4. Charge Pump: The high speed charge pump consists of a switchable constant current source and sink. The charge pump constant current is set by connecting external resistors to  $V_{\rm CC}$  from the charge current rate set (IRSET) and current boost set (IBSET) pins. Before lock is indicated, the PLL is in the high tracking rate and the parallel combination of the resistors determines the current. In the low tracking rate after lock-on, only the IRSET resistor determines the charge pump current. The output of the charge pump subsequently feeds into external filter components and the Buffer Amplifier.

- 5. Buffer Amplifier: The input of the Buffer Amplifier is connected to the charge pump's constant current source/sink output as well as the external Loop Filter components. The Buffer Amplifier is configured as a high input impedance amplifier which allows for the connection of external PLL filter components to the Charge Pump output pin CPOUT. The output of the Buffer Amplifier is internally connected to the VCO control input.

- 6. VCO: The Voltage-Controlled-Oscillator requires a resistor from the RVCO pin to ground and a capacitor between pins C1 and C2, to set the center frequency. The VCO frequency can be varied from nominal by approximately  $\pm\,20\%$ , as determined by its control input voltage.

- 7. PLL Lock-on/Preamble Pattern Detector: To recognize preamble, the preamble pattern from the disk must consist exclusively of either MFM data bit zeroes (encoded into ..10.. MFM clock pulses) when the ZEROES/ONES PRE-AMBLE pin is set high, or MFM data bit ones (encoded into ..01.. MFM pulses) when set low (DP8461/65 only). The preamble pattern must be long enough to allow the PLL to lock, and subsequently for the Preamble Pattern Detector circuit to detect two complete bytes.

Once the chip is in the read mode, the VCO proceeds to lock on to the incoming data stream. The Preamble Pattern

Detector then searches for a continuous pattern of 16 consecutive pulses at one-half the VCO frequency to indicate lock has been achieved.

The LOCK DETECTED output then goes low. At this time, in the DP8461/51 option, the PLL switches from using a phase-frequency comparator to employing a pulse gate and thus doing only phase comparisons. Any deviation from the above-mentioned one-zero pattern at any time before PLL Lock is detected will reset the PLL Lock Detector. The lock detection procedure will then start again.

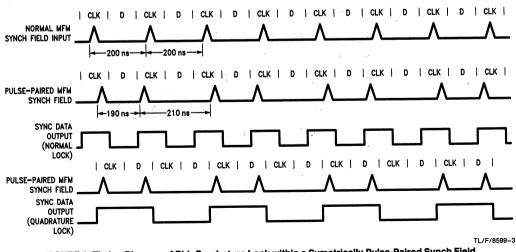

- MFM Decoder (DP8461/65 only): The MFM Decoder receives synchronized MFM data from the Pulse Gate and converts it to NRZ READ DATA. For run-length-limited codes the MFM Decoder and Missing Clock Detector will not be used.

- 9. Missing Clock Detector (DP8461/65 only): This block is only required for soft-sectored drives, and is used to detect a missing clock violation of the MFM pattern. The missing clock is inserted when writing to soft-sectored disks to indicate the location of the Address Mark in both the ID and the Data fields of each sector. Once PLL Lock has been indicated, the Missing Clock Detector circuit is enabled. MISSING CLOCK DETECTED will go active if at any time the incoming data pattern contains one suppressed clock bit framed by two adjacent clock bits. (This condition is not constrained to any particular byte pattern such as "A1.") The output signal goes high for one cycle of READ CLOCK.

- 10. Clock Multiplexer and Deglitcher (DP8461/65 only): When the SET PLL LOCK input changes state this circuit switches the source of the READ CLOCK signal between the half 2f-CLOCK frequency and the half VCO CLOCK frequency. A deglitcher circuit is utilized to ensure that no short clock periods occur during either switchover.

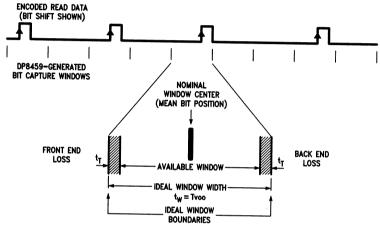

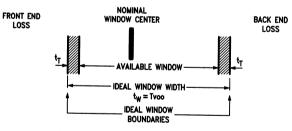

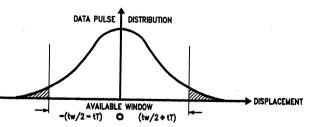

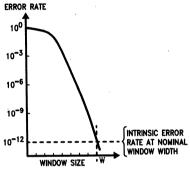

#### **BIT JITTER TOLERANCE**

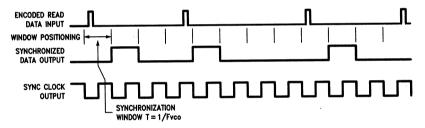

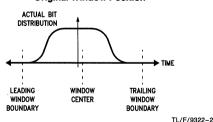

The spec, t-window, as defined in the AC Electrical Characteristics table, describes the distance from the optimum window boundary a single shifted data bit may be placed (following complete PLL lock and stabilization) before it risks

being interpreted as residing in the adjacent synchronization window. This is known as the **static window measure-ment**, which combines all contributing factors of window jitter and displacement within the data separator into a single specification.

The two options of the DP8451/55/61/65, the -4 and -3 offer decreasing static window errors (respectively) so that the parts may be selected for different data rates (up to 20 Mbit/sec). The -4 part will be used in most low data rate applications. As an example, at the 5 Mbit/sec MFM data rate of most  $5\frac{1}{4}$  inch drives, the chip contributes up to  $\pm 10$  ns of window error, out of the total available window of 100 ns. This allows the disk drive to have a margin of 40 ns of jitter from nominal bit position before an error will occur.

#### **ANALOG CONNECTIONS**

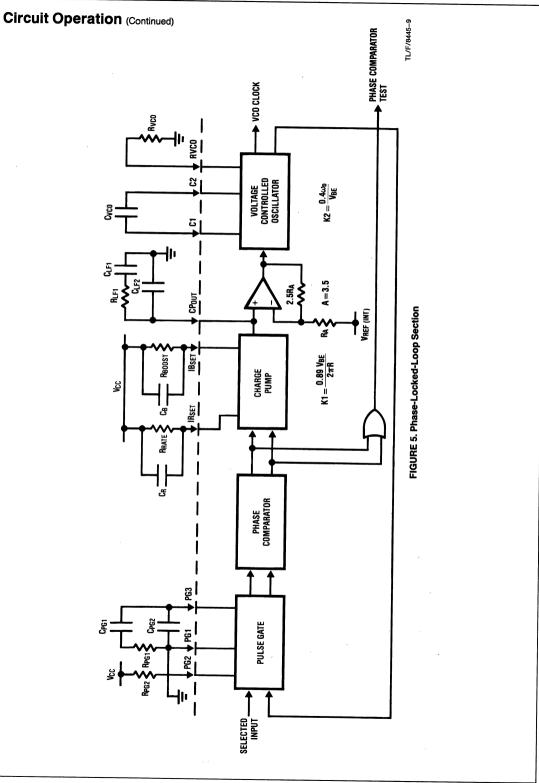

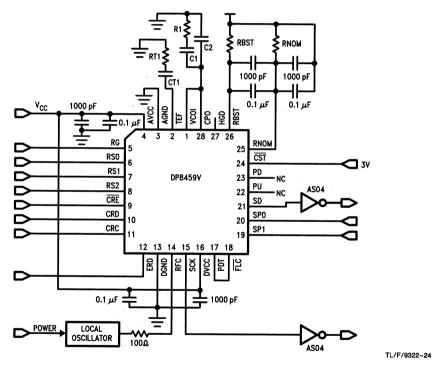

External passive components are required for the Pulse Gate, Charge Pump, Loop Filter and VCO as shown in Figure 5. The information provided here is for guidelines only. The user should select values according to his own system requirements. Phase-Locked Loops are complex circuits that require detailed knowledge of the specific system. Factors such as loop gain, stability, response to change of signal, lock-on time, etc are all determined by the external components. In many disk systems these factors are critical, and National Semiconductor recommends the designer be knowledgeable of phase-locked-loops, or seek the advice of an expert. Inaccurate design will probably result in excessive disk error rates. The phase-locked-loop in the DP8461/65 has many advantages over all but the most sophisticated discrete designs, and if the component values are selected correctly, it will offer significant performance advantages. This should result in a reduction of disk error rates over equivalent discrete designs. Please refer to the National Semiconductor Application Note AN-414, Precautions for Disk Data Separator Designs, AN-415, Designing with the DP8461, AN-416, Designing with the DP8465, and to the Disk Interface Design Guide and User's Manual, Chapter 1.

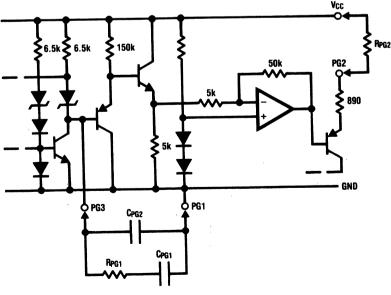

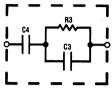

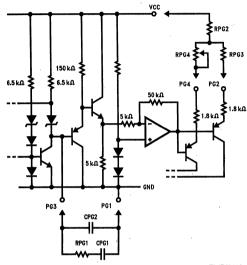

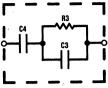

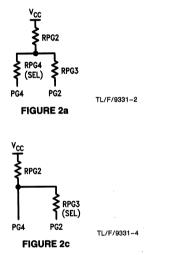

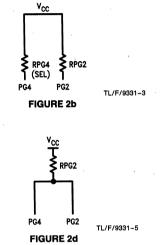

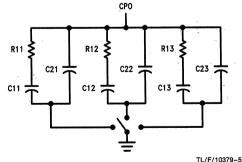

#### **Pulse Gate**

There are four external components connected to the Pulse Gate as shown in *Figure 6* with the associated internal components. The values of RpG<sub>1</sub>, RpG<sub>2</sub>, CpG<sub>1</sub>, and CpG<sub>2</sub> are dependent on the data rate. CpG<sub>1</sub> and CpG<sub>2</sub> are proportional to the data rate, while RpG<sub>1</sub> and RpG<sub>2</sub> are inversely proportional. Table I shows component values for the data rates given. Component values are calculated by selecting RpG<sub>2</sub> from Table I. Next calculate

$$C_{PG1} = \left(\frac{2.12 \times 10^5}{890 + R_{PG2}}\right) \left(\frac{1}{100 \times R_S}\right)^2$$

$$C_{PG2} = \frac{1}{10} \, C_{PG1} \text{, and } R_{PG1} = \left( \frac{890 + R_{PG2}}{2.38 \times 10^5} \right) (100 \times R_S).$$

In the above equations  $R_S$  is the rotational speed and, for 3600 RPM,  $R_S=60$  Hz. A rotational speed of 3600 RPM was assumed for the calculations in Table I. For data rates not listed,  $R_{PG2}$  may be approximated as (30  $k\Omega/f_{DATA})-1.20~k\Omega=R_{PG2}$  where  $f_{DATA}$  is the data rate in Megabits/second.

TABLE I. Pulse Gate Component Selection Chart Components with 10% tolerance will suffice

| Data Rate   | R <sub>PG2</sub> | R <sub>PG1</sub> | C <sub>PG1</sub> | C <sub>PG2</sub> |

|-------------|------------------|------------------|------------------|------------------|

| 2 Mbit/sec  | 15 kΩ            | 430Ω             | .39 μF           | .039 μF          |

| 5 Mbit/sec  | 4.7 kΩ           | 150Ω             | 1 μF             | 0.1 μF           |

| 10 Mbit/sec | 1.8 kΩ           | 68Ω              | 2.2 μF           | .22 µF           |

| 15 Mbit/sec | 750Ω             | 39Ω              | 3.9 μF           | .39 μF           |

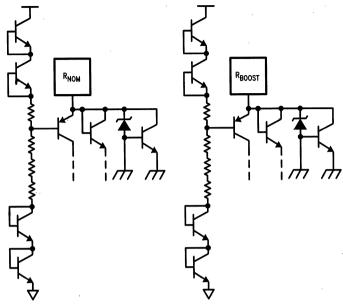

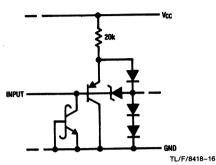

#### **Charge Pump**

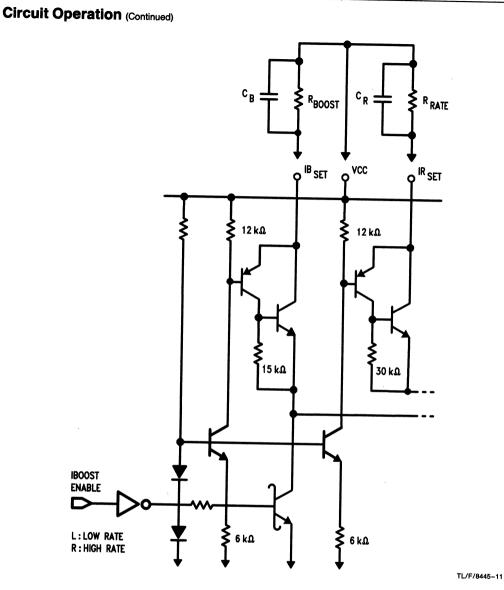

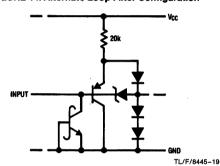

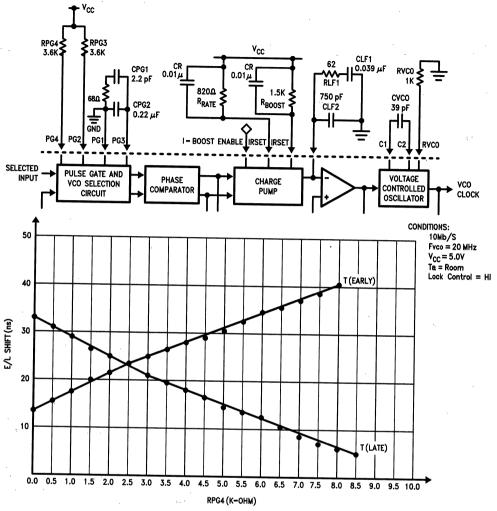

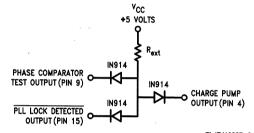

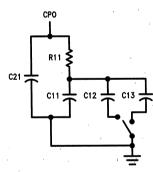

Resistors R<sub>RATE</sub> and R<sub>BOOST</sub> determine the charge pump current. The Charge Pump bidirectional output current is approximately 1.9  $\times$  the input current (See DC Electrical Characteristics for exact relationship). In the high tracking rate with SET PLL LOCK high, the input current is  $I_{\rm BSET}+I_{\rm R.SET}$ , i.e., the sum of the currents through  $R_{\rm BOOST}$  and  $R_{\rm RATE}$  from V<sub>CC</sub>. In the low tracking rate, with SET PLL LOCK low, this input current is  $I_{\rm RSET}$  only.

A recommended approach for selecting values for RRATE and Recost is described in the design example in the Loop Filter Section. A typical loop gain change of 2:1 for high to low tracking rate would require RBOOST = RRATE. Selecting  $R_{BATE}$  to be 820 $\Omega$  would then result in  $R_{BOOST}$  equaling 820 $\Omega$ . Referring to Figure 7, the input current is effectively  $V_{\text{BE}}/R_{\text{RATE}}$  in the low tracking rate, where  $V_{\text{BE}}$  is an internal voltage. This means that the current into or out of the loop filter is approximately (1.95  $\times$  V<sub>BE</sub>/820) - 70  $\mu$ A = 1.72 mA. Note that although it would seem the overall gain is dependant on VBE, this is not the case. The VCO gain is altered internally by an amount inversely proportional to VBE, as detailed in the section on the Loop Filter. This means that as VBE varies with temperature or device spread, the gain will remain constant for a particular fixed set of values of RRATE and RBOOST. This alleviates the need for potentiometers to select values for each device. The tolerance required for these two resistors will depend on the total loop gain tolerance allowed, but 5% would be typical. Also V<sub>CC</sub> bypass capacitors are required for these two resistors. A value of .01 µF is suitable for each.

FIGURE 6. Pulse Gate Controls

FIGURE 7. I<sub>RATE</sub> Set and I<sub>BOOST</sub> Set

vco

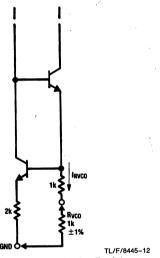

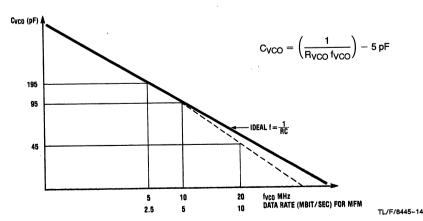

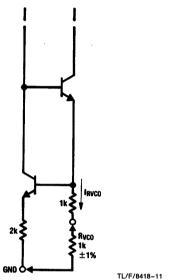

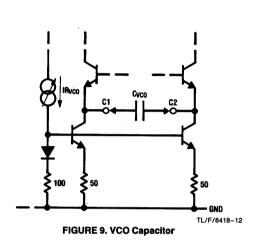

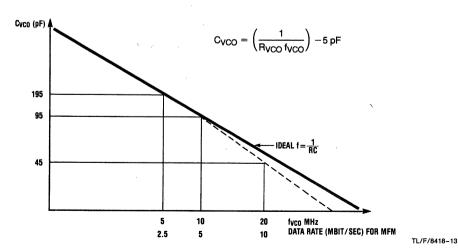

The value of R<sub>VCO</sub> is fixed at 1 k $\Omega$  ±1% in the External Component Limits table. Figure 8 shows how RVCO is connected to the internal components of the chip. This value was fixed at 1  $k\Omega$  to set the VCO operating current such that optimum performance of the VCO is obtained for production device spreads. This means fixed value components will be adequate to set the VCO center frequency for production runs. The value of CVCO can therefore be determined from the VCO frequency  $f_{VCO}$ , using the equation:  $C_{VCO} = [1/$ (R<sub>VCO</sub>) (f<sub>VCO</sub>)] - 5 pF where f<sub>VCO</sub> is twice the input data rate. As an example, for a 5 Mbit/sec data rate, f<sub>VCO</sub> = 10 MHz, requiring that C<sub>VCO</sub> = 95 pF. This does not take into account any inter-lead capacitance on the printed circuit board; the user must account for this. The amount of toler ance a particular design can afford on the center frequency will determine the capacitor tolerance. The capacitor is conected to internal circuitry of the chip as shown in Figure 9. As the data rate increases and  $C_{VCO}$  gets smaller, the effects of unwanted internal parasitic capacitances influence the frequency. As a guide the graph of Figure 10 shows approximately the value of  $C_{VCO}$  for a given data rate.

The VCO control input operational range (pin 4) lies at approximately 1.4 volts with a control swing of ± 100 millivolts. The VCO itself is constrained to swing a maximum of approximately ±20% of its center frequency, and will remain clamped if the voltage at pin 4 exceeds its operational limit. The VCO center frequency may then be determined by: 1) holding pin 4 at ground potential and measuring the VCO frequency (-20% value); 2) holding pin 4 at approximately 3 volts and measuring the VCO frequency (+20% value); 3) averaging the two measured frequencies for the equivalent center frequency.

FIGURE 8. VCO Current Setting Resistor

FIGURE 9. VCO Capacitor

FIGURE 10. VCO Capacitor Value for Disk Data Rates

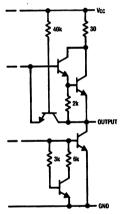

#### **Loop Filter**

The input current into the Buffer Amplifier is offset by a matched current out of the Charge Pump, and even so is much less than the switching current in or out of the Charge Pump. It can therefore be assumed that all the Charge Pump switching current goes into the Loop Filter components  $\rm R_1$  and  $\rm C_1$  and  $\rm C_2$ . The tolerance of these components should be the same as  $\rm R_{RATE}$  and  $\rm R_{BOOST}$ , and will determine the overall loop gain variation. The three components connected to the Charge Pump output are shown in Figure 11. Note the return current goes to analog GND, which should be electrically very close to the GND pin itself.

The value of capacitor  $C_1$  determines loop bandwidth  $\dots$  the larger the value the longer the loop takes to respond to an input change. If  $C_1$  is too small, the loop will track any jitter on the ENCODED DATA input and the VCO output will follow this jitter, which is undesirable. The value of  $C_1$  solud therefore be large enough so that the PLL is fairly immune to phase jitter but not large enough that the loop won't respond to longer term data rate changes that occur on the disk drive.

The damping resistor R<sub>1</sub> is required to regulate the secondorder behavior of the closed-loop system (overshoot). A value of  $R_1$  that would give a phase margin of around 45 degrees would be a reasonable starting point.

The main function of the capacitor  $C_2$  is to smooth the action of the charge pump at the VCO input. Typically its value will be less than one tenth of  $C_1$ . Further effects of  $C_2$  will be discussed later.

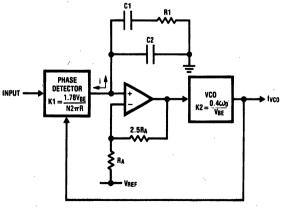

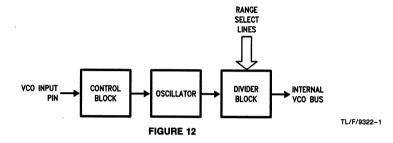

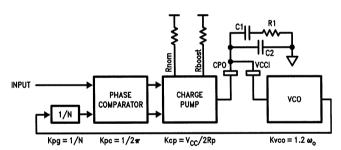

Figure 12 shows the relevant phase-locked-loop blocks that determine system response, namely the Phase Detector, Filter/Buffer Amplifier, and VCO. The Phase Detector (Phase Comparator and Charge Pump) produces an aggregate output current i which is proportional to the phase difference between the input signal and the VCO signal. The constant (K<sub>1</sub>) is

$$\frac{1.78 \text{ V}_{BE}}{\text{N}2\pi \text{R}} \text{ amps per radian, where N} = \frac{\text{f}_{VCO}}{\text{f}_{DATA}}$$

R is either R<sub>RATE</sub> or R<sub>RATE</sub>  $\parallel$  R<sub>BOOST</sub>. The amplified aggregate current feeds into or out of the filter impedance (Z), producing a voltage to the VCO that regulates the VCO frequency. The VCO gain constant is 0.4  $\omega_{VCO}/V_{BE}$  radians per second per volt. Under steady state conditions, i will be zero and there will be no phase difference between the input signal and the VCO. Any change of input signal will pro-

FIGURE 11. Charge Pump Out

TL/F/8445-15

**FIGURE 12. Loop Response Components**

duce a change in VCO frequency that is determined by the loop gain equation. This equation is determined from the gain constants  $K_1$ , A and  $K_2$  and the filter  $\nu/i$  response.

The impedance Z of the filter is:

$$\frac{1}{sC_2} \left\| \left( \frac{1}{sC_1} + R_1 \right) = \frac{1 + sC_1R_1}{sC_1 \left( 1 + \frac{C_2}{C_1} + sC_2R_1 \right)}$$

If C<sub>2</sub> ≪ C<sub>1</sub> then the impedance Z approximates to:

$$\frac{1 + sC_1R_1}{sC_1 (1 + sC_2R_1)}$$

The overall loop gain is then

$$G(s) = \frac{K_1AK_2}{s} \times \frac{1 + sC_1R_1}{sC_1(1 + sC_2R_1)}$$

Let  $G_{(K)} = K_1 A K_2$

$$F(s) = \frac{1 + SC_1R_1}{SC_1(1 + SC_2R_1)}$$

The Overall Closed Loop Gain is:

$$\frac{\phi_{OUT}}{\phi_{IN}} = \frac{G_{(K)} F(s)}{s + G_{(K)} F(s)}$$

Substituting, We Get

$$\begin{split} \frac{\varphi_{OUT}}{\varphi_{IN}} &= \frac{G_{(K)}\left(SC_1R_1 + 1\right)}{S^3\,R_1\,C_1\,C_2 + S^2\,C_1 + GK\left(SC_1R_1 + 1\right)} \\ &= \frac{\left(G_{(K)}/C_1\right)\left(SR_1C_1 + 1\right)}{S^3R_1C_2 + S^2 + SG_{(K)}R_1 + G_{(K)}/C_1} \end{split}$$

If  $C_2 \ll C_1$ , we can ignore the 3rd Order Component introduced by  $C_2$  then:

$$\frac{\phi_{OUT}}{\phi_{IN}} = \frac{(G_{(K)}/C_1)(SR_1C_1 + 1)}{S^2 + SG_{(K)}R_1 + G_{(K)}/C_1}$$

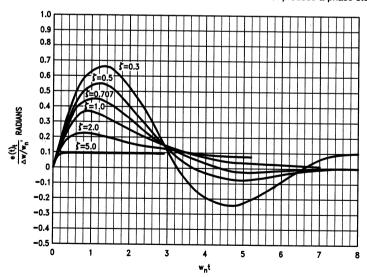

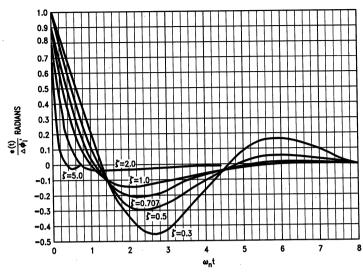

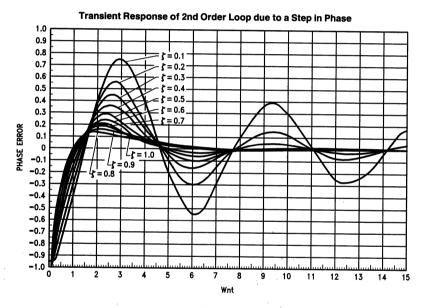

This is a second Order Loop and can be solved as follows:

$$\begin{split} S^2 + SG_{(K)}R_1 + G_{(K)}/C_1 &= S^2 + 2\zeta\,\omega_nS + \omega_n^2 \\ & \therefore C_1 = \frac{G_{(K)}}{\omega_n^2} \\ R_1 &= \frac{2\zeta\omega_n}{G_{(K)}} \end{split}$$

$\zeta = 1.0$  For Critically Damped Response

From the above equations:

where above equations:

$$\omega = \sqrt{\frac{G_{(K)}}{C_1}}$$

$$G_{(K)} = K_1 A K_2 = \frac{0.89 \times V_{BE}}{2\pi R} \times \frac{0.4 \times \omega_{VCO}}{V_{BE}} \times 3.5$$

MFM encoded data has a two to one frequency range within the data field. The expression  $K=(0.89\times V_{BE}\ /\ 2\pi R)$  is valid when the MFM data pattern is at its maximum frequency. In order to make this equation more general, it may be written as follows:  $K=(1.78\times V_{BE}\ /\ 2\pi RN)$  where N is defined as the  $V_{CO}$  frequency divided by the encoded data

frequency, or, N is equal to  $F_{VCO}/F_{DATA}$  (N = 2 for maximum data rate i.e., MFM = 101010 ... and N = 4 for minimum data rate) i.e., MFM = 100010001 .... Now  $G_{(K)}$  can be written as follows:

$$\begin{split} G_{(K)} &= \frac{1.78 \times V_{BE}}{2\pi RN} \times \frac{0.4 \times \omega_{VCO}}{V_{BE}} \times 3.5 \\ &= \frac{2.5 \times F_{VCO}}{RN} \\ &= \sqrt{\frac{2.5 \times F_{VCO}}{C_1 RN}} \end{split}$$

$R = R_{RATE}$  in the low track rate

$R = R_{BATE} // R_{BOOST}$  in the high track rate

From the above equations:

$$\begin{split} \omega_n &= \frac{R_1 \, G_{(K)}}{2 \zeta} \\ G_{(K)} &= \, C_1 \, \omega_n^2 \\ \zeta &= \text{(damping factor)} = \frac{R_1 \, \omega_n \, C_1}{2} \end{split}$$

The damping factor should approach, but not fall below, 0.5 when  $\omega_n$  is minimum. Response to bit shift is minimized when the damping factor is small; however, if the damping factor drops much below 0.5, the system tends to be oscillatory (underdamped).

Additionally, loop performance is poor (excessive phase ac-

quisition times) if the damping factor becomes significantly greater than 1.0. Any increase in loop bandwidth (due to R

decreasing in the high track rate) produces a proportional increase in the damping factor, and this should be limited to the point where the maximum damping factor does not significantly exceed 1.0. With the damping factor range established, loop design can now proceed. The following design example is for a 5 Mbit/sec MFM system.

A 1550 Krads/sec bandwidth in the non read mode results in a wide capture range; a 4% frequency difference between the crystal and recorded data would not cause an acquisition problem. (This bandwidth may seem excessive to some and if the user does not think it is necessary, he may design his filter with a more desirable bandwidth. For an in-depth discussion of this point, it is suggested that the reader refer to the Disk Interface Design Guide and User's Manual, chapter 1, sections 1.3 through 1.7.

This design example assumes that the SET PLL LOCK pin is tied to the PLL LOCK DETECTED pin. This results in the track rate being switched from high to low after two bytes of preamble are detected. As an alternative, the SET PLL LOCK pin may be tied to an inverted READ GATE signal, resulting in the track rate switching immediately to low when READ GATE is asserted. This is discussed further in the above mentioned reference material.

#### TABLE II.

| Data Rate<br>(NRZ) | Non-Read                        |      | Read Charge Pump                |      | Non-Read Read                |                    |                                                      | Loop Filte           | r                    |

|--------------------|---------------------------------|------|---------------------------------|------|------------------------------|--------------------|------------------------------------------------------|----------------------|----------------------|

|                    | <sup>ω</sup> n(MAX)<br>rads/sec | ζ    | <sup>ω</sup> n(MIN)<br>Rads/sec | ζ    | $\mathbf{R}_{\mathbf{RATE}}$ | $R_{\text{BOOST}}$ | $egin{array}{c} oldsymbol{R_1} \ \Omega \end{array}$ | C <sub>1</sub><br>μF | C <sub>2</sub><br>pF |

| 5 Mbit/sec         | 1550K                           | 1.12 | 797K                            | 0.55 | 820                          | 820                | 120                                                  | 0.012                | 300                  |

| 5 Mbit/sec         | 903K                            | 0.99 | 435K                            | 0.48 | 1500                         | 1300               | 100                                                  | 0.022                | 390                  |

| 5 Mbit/sec         | 659K                            | 1.55 | 248K                            | 0.52 | 1500                         | 590                | 69                                                   | 0.068                | 1500                 |

In the non read mode or high track rate.

$$\omega_{n} = \sqrt{\frac{2.5 \times F_{VCO}}{C_{1} RN}}$$

Choose R = R<sub>RATE</sub> // R<sub>BOOST</sub> = 410

In the non-read mode N = 2

1,550 Krads/sec =

$$\sqrt{\frac{2.5 \times 10^7}{C_1 \times 410 \times 2}}$$

$C_1 = 0.012 \, \mu F$

In the preamble, after two bytes are detected and PLL LOCK DETECT goes low

$$\omega_{n} = \sqrt{\frac{2.5 \times F_{VCO}}{C_{1}RN}}$$

$R = R_{BATF} = 820$

N = 2

$\omega_n = 1127 \, \text{Krads/sec}$

Again, in the data field, the minimum data frequency is equal to one half the preamble frequency. This means that N=4 in the bandwidth equation. This reduces the bandwidth to:

$$\omega_{\text{n(min)}} = \frac{1}{\sqrt{2}} \times 1107 \text{ Krads/sec} = 797 \text{ Krads/sec}$$

Before, we stated that the minimum value of  $\zeta$  should be 0.5; knowing  $\omega_{n(min)}$  we can now solve for R<sub>1</sub>

$$\zeta = \frac{\omega_n R_1 C_1}{2}$$

Choose  $\zeta_{(min)} = 0.55$

$$R_1 = \frac{2\zeta}{\omega_n \, C_1}$$

$R_1 = 115\Omega$  (choose  $120\Omega$ )

The maximum damping value occurs in the high track rate;

$$\zeta_{(max)} = \omega_{n(max)} R_2 C_1/2$$

= 1550 Krads/sec × 120 × 0.012 µF/2

$\zeta_{\text{(max)}} = 1.12$

The maximum damping value in the read mode is as follows:

$\zeta_{\text{(max-read)}} = 1127 \text{ Krads/sec} \times 120 \times 0.012 \,\mu\text{F/2}$

$\zeta_{\text{(max-read)}} = 0.81$

The continuous behavior (non-quantized) approximation used to predict loop performance assumes that the phase detector output is constantly proportional to the input phase difference. In reality, the phase detector output is a pulse applied for a period of time equal to the phase difference. The function of  $\mathsf{C}_2$  is to smooth the phase detector output (VCO control voltage) over each cycle.  $\mathsf{C}_2$  also adds a second pole to the filter transfer function. This pole should be far enough outside the loop bandwidth (at least one order of magnitude) that its phase and amplitude contribution is negligible in the loop bandwidth. If:

$$C_2 = C_1/50 = 240 \text{ pF}$$

(choose 300 pF)

The final loop component is  $R_{BOOST}.$  Since  $R_{RATE}$  and the parallel combination of  $R_{RATE}$  and  $R_{BOOST}$  are known, we can calculate  $R_{BOOST}.$

$R_{BOOST} = (R_P) (R_{RATE}) / (R_{RATE} - R_P) = 820\Omega$

The above filter values and those for other bandwidths are listed on preceding page.

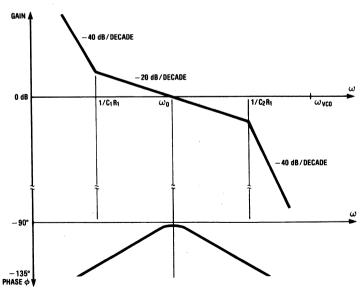

FIGURE 13. Bode Plot of Loop Response

The calculated values are only a guide, the user should then empirically test the loop and determine stability, lock-on time, jitter tolerance, etc.

The desired Bode plot of gain and phase is shown in *Figure 13*, with 20 dB/decade slope at  $\omega_0$  for stability at unity gain.

75, with 25 do decade stope at  $w_0$  for stability at unity gain. Capacitor  $C_2$  governs the PLL's ability to reject instantaneous bit jitter. As  $C_2$  increases in value, the effective jitter rejection will also increase. However, as the frequency of the pole  $R_1$  and  $C_2$  produce (while increasing  $C_2$ ) decreases, loop stability will decrease, and the second-order approximation used to analyze the circuit becomes inaccurate. Thus, it is recommended that  $C_2$  remain one tenth (or less) the value of  $C_1$ .

The value of resistor  $R_1$  inversely effects the break frequencies on the Bode plot, and directly effects the loop's damping ratio (overshoot response). The capacitor  $C_1$  governs the bandwith of the loop. Too high a value will slow down the response time, but make the PLL less prone to jitter or frequency shift whereas too low a value will improve response time while tending to increase the PLL's reaction to litter.

Other filter combinations may be used, other than  $R_1$  in series with  $C_1$ , all in parallel with  $C_2$ . For example the filter shown in *Figure 14* will also perform similarly, and in fact for some systems it will yield superior performance.

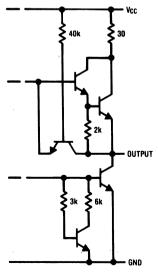

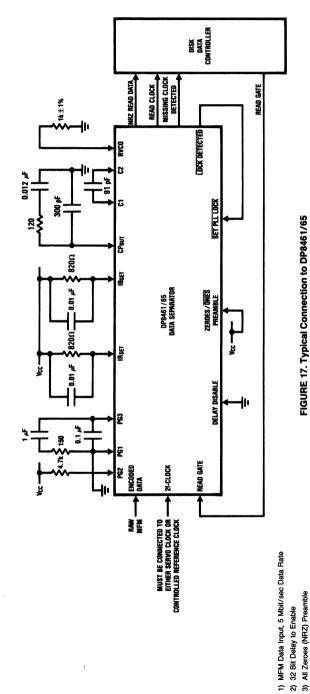

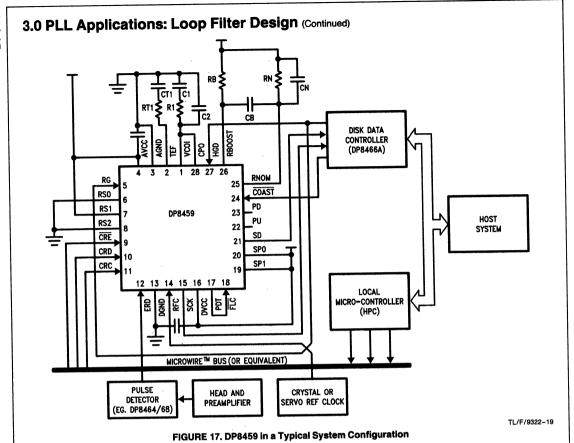

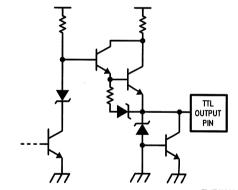

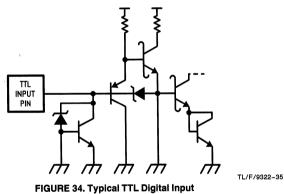

#### **DIGITAL CONNECTIONS TO THE DP8461/65**

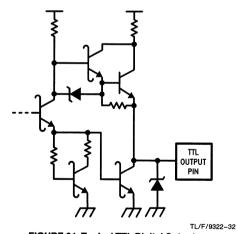

Figure 17 shows a connection diagram for the DP8461/65 in a typical application. All logic inputs and outputs are TTL compatible as shown in Figure 15 and 16. The VCO CLOCK output is 74AS compatible. All other outputs are 74ALS compatible and therefore can be driven easily from any 74 series devices. The raw MFM from the pulse detector in the drive is connected to the ENCODED DATA input. The DELAY DISABLE input de-

termines whether attempting lock-on will begin immediately after READ GATE is set or after 2 bytes. Typically in a hard-sectored drive, READ GATE is set active as the sector pulse appears, meaning a new sector is about to pass under the head. Normally the preamble pattern does not begin immediately, because gap bytes from the preceding sector usually extend just beyond the sector pulse. Allowing 2 bytes to pass after the sector pulse helps ensure that the PLL will begin locking on to preamble, and will not be chasing non-symmetrical gap bits. Thus DELAY DISABLE should be set low for this kind of disk drive.

FIGURE 14. Alternate Loop Filter Configuration

FIGURE 15. Logic Inputs

FIGURE 16. Logic Outputs

# **Connection Diagram**

FIGURE 17. Typical Connection to DP8461/65

## **Block Diagram**

## Circuit Operation (Continued)

For soft sectored drives, the controller normally will not wait for the index pulse before it attempts lock-on, so that READ GATE may go active at any time. Chances are the head will not be over a preamble field and therefore there is no need to wait 2 bytes before attempting lock-on. DELAY DISABLE can therefore be set high. If a non-preamble field is passing by as READ GATE goes active, the DP8461/65 will not indicate lock, and no data decoding will occur nor will MISSING CLOCK DETECTED go active. Normally, if lock-on has not been achieved after a certain time limit, the controller will de-activate READ GATE and then try again.

For MFM encoded disk drives, the LOCK DETECTED output will be connected back to the SET PLL LOCK input. As the PLL achieves lock-on, the DP8461/65 will automatically switch to the lower tracking rate and decoded data will appear at the NRZ READ DATA output. Also the READ CLOCK output will switch from half the 2F-CLOCK frequency to the disk data rate frequency. If a delay is required before the changeover occurs, a time delay may be inserted between the two pins.

Some drives have an all-ONES data preamble instead of all-ZEROES and the DP8461/65 must be set to the type being used before it can properly decode data. The ZEROES/ONES PREAMBLE input selects which preamble type the chip is to base its decoding phase on.

#### **USE WITH RUN-LENGTH-LIMITED CODES (RLL)**

If the drive uses a Run-Length-Limited Code (RLL) such as 1,7 or 1,8 instead of MFM, the user might choose to use the DP8451/55. These circuits contain the PLL portion of the DP8461/65 and thus perform the data synchronization function. RAW DATA is input to pin 16 and the 2F-CLOCK is applied to pin 17. Instead of supplying NRZ DATA, SYN-CHRONIZED DATA OUTPUT is issued at pin 12. The VCO CLOCK, pin 8, is used to clock this data into external decoding circuitry. As long as the high frequency pattern of . . . 1010 . . . is used for the preamble, the user may choose the DP8451 if he desires to have the circuit perform phase and frequency comparisons until two bytes of preamble are detected by the on chip preamble pattern detector.

If a 2,7 code is being used the DP8465/55 may be used. Again, since the DP8465 MFM decoding function will not be used, the user may choose to use the DP8455. However, the National Semiconductor DP8462 is designed specifically for the 2,7 code. It is recommended that the user reviews the DP8462 specification for the added advantages the circuit offers with the 2,7 format.

# Applications of the DP8461/65 Data Separator

The DP8461/65 are the first integrated circuits to place on one chip a PLL with features that offer the improved speed and reliability required by the disk industry. Not only does each chip simplify disk system design, but also provides fast lock-on to the incoming preamble. Once locked on, the loop is set into a more stable mode. This inherent loop stability allows for a sizeable amount of jitter on the data stream, such as is encountered in many disk systems. Once in the stable tracking rate, the SYNCHRONIZED DATA output represents the incoming ENCODED DATA and is synchronous with VCO CLOCK. If the disk is MFM encoded, then the chip can decode the synchronized data into NRZ READ DATA and READ CLOCK. These are available as outputs from the chip allowing the NRZ READ DATA to be deserialized using the READ CLOCK.

The DP8461/65 are capable of operating at up to 20 Mbits/sec data rates and so are compatible with a wide assortment of disk drives. The faster data rates of the 8-inch and 14-inch disk drives will mandate the selection of the DP8461/65–3 parts with their narrower window margins on the incoming data stream. This will also be the case when 51/4-inch drives achieve higher data rates. Some 8-inch and 14-inch disk drives incorporate the functions of the DP8461/65, but use many discrete ICs. In these cases, replacing these components with the DP8461/65 will offer reduced P.C. board area, lower cost, and improved performance while simplifying circuit testing.

Most 51/4-inch and many 8-inch and 14-inch disk drives manufactured at present do not incorporate any of the functions of the DP8461/65. This is so primarily because the PLL function is difficult to design and implement and requires circuitry which covers a large area of the printed circuit card. This is undesirable both from the drive size aspect and from the cost aspect (the cost includes soldering, testing, and adjusting the components). Consequently, most smaller disk drives output MFM encoded data so that the phase-locked-loop and data separation have to be performed by the controller. The DP8461/65 will therefore replace these functions in controller designs, as shown in Figure 18.

System design criteria has become more flexible because the DP8461/65 provide a one-chip solution, requiring only a few external passive components with fixed values. Each operates from a +5V supply, typically consumes about 0.3W, and is housed in a narrow 24-pin package. The circuitry has been designed so that the external resistors and capacitors need not be adjustable; the user chooses the values according to the disk drive requirements. Once selected, they will be fixed for that particular drive type. These features make it possible to transfer these functions to the disk drive, as shown in Figure 19. Apart from a slight increase in board area, the advantages outweigh the disadvantages. First, the components selected are fixed for each type of drive and this facilitates the problem of interchangeability of drives. At present, controllers are adjusted to function with each specific drive; with the DP8461/65 in the drive, component adjustment will no longer be required. Second there is often a problem of reliability of data transfer. The data returning from the disk drive is susceptible to noise, bit shift, etc. Soft errors will occur when the incoming disk data bit position is outside the Pulse Gate window as it is being synchronized to the VCO clock in the phase-lockedloop. Obviously, the nearer the PLL is to the data source. the less chance there is that extraneous noise or transmission line imbalances will cause errors to occur. Thus placing the DP8461/65 in the drive will increase the reliability of data transfer within the system.

A third advantage is data rate upgrading. Most 5½-inch drives have 5 Mbit/sec data rate because the early drives were made with this data rate. This meant the controllers had to be designed with PLLs which operate at this data rate. It is therefore difficult for drive manufacturers to introduce new drives that are not compatible with existing controllers. Since no new standard data rate has emerged, they must continue to produce drives at this data rate to be compatible with the controllers on the market. With the DP8461/65 in the drive, and associated components set for the drive's data rate, it no longer becomes a problem to increase the data rate, assuming the controllers digital circuitry can accommodate the change. This will allow the manufactures to increase the bit density and therefore the capacity of their drives.

## Applications of the DP8461/65 Data Separator (Continued)

FIGURE 18. DP8461/65 in the Controller

PART OF DISK DRIVE ESDI OR ANSI X3.101 SMD INTERFACE PASSIVE COMPONENTS NRZ READ DATA 2f-CLOCK READ CLOCK CONTROLLER MISSING CLOCK PHI SE DP8461/65 DETECTED DETECTOR ENCODED DATA SEPARATOR (SUCH AS DATA DP8464) LOCK DETECTED READ GATE SET PLL LOCK READ GATE WRITE SIGNALS CONTROLS

FIGURE 19. DP8461/65 in the Disk Drive

TL/F/8445-23

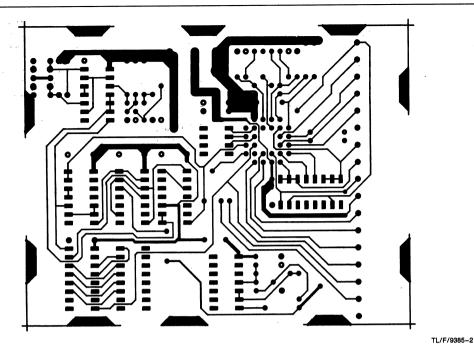

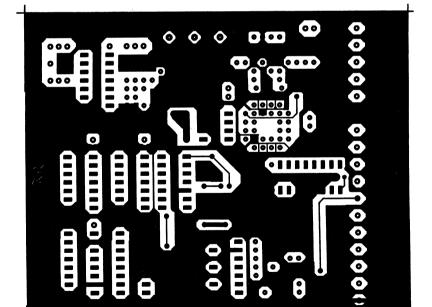

# PRECAUTIONS IN BREADBOARDING AND PCB LAYOUT

The DP8461/65 contains a high performance analog PLL and certain precautions must be taken when breadboarding or designing a PCB layout. The following guidelines should be adhered to when working with the DP8461/65:

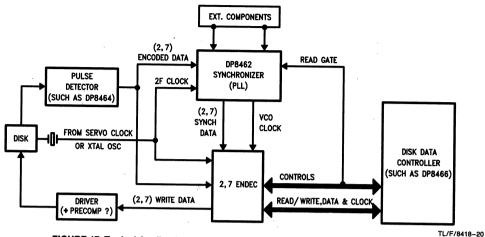

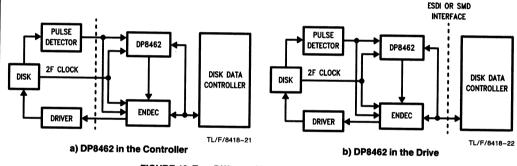

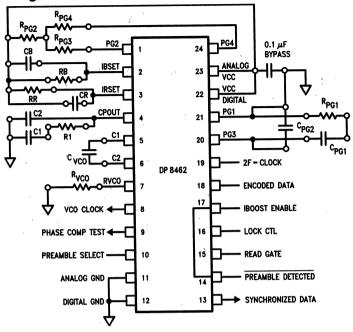

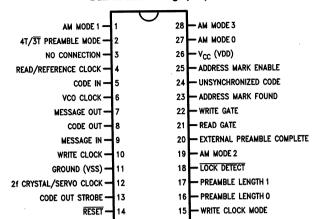

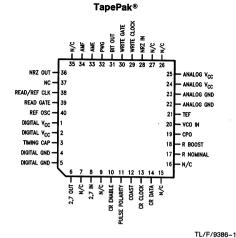

- 1) Do not wire wrap.