# A DISCUSSION OF THE CIRCUITRY USED IN THE LINCOLN TX-2 COMPUTER

BY

JONATHAN R. FADIMAN

## TX-2 CIRCUITRY HANDBOOK\*

A discussion of the circuitry used in the Lincoln TX-2 Computer.

Jonathan R. Fadiman \*\*

1 October, 1958

<sup>\*</sup> The research reported in this document was supported jointly by the Army, Navy, and Air Force under contract with the Massachusetts Institute of Technology.

<sup>\*\*</sup> Lincoln Laboratory, Massachusetts Institute of Technology.

#### ACKNOWLEDGEMENT

I am indebted to Mr. Ben Gurley for his many suggestions and valuable aid in the preparation of this paper and for the section on the display system; to Mr. Frank Hazel for his assistance in editing; to Mr. Arthur Grennel for the block schematic drawings in the reference manual; to Mrs. Madeline Higgins for the typing; and to many other members of Group 63 for their suggestions and corrections.

## TABLE OF CONTENTS

| CIRCUIT<br>NUMBER | TITLE                         | DISCUSSION ON PAGE |

|-------------------|-------------------------------|--------------------|

|                   | Introduction                  | 1                  |

|                   | General Discussion            | 2                  |

|                   | Packaging                     | 3                  |

|                   | Transistors                   | 3                  |

|                   | Logic                         | 8                  |

|                   | Counting Circuits             | 12                 |

|                   | Inverter Circuit              | 15                 |

|                   | Emitter Follower Circuit      | 19                 |

| 08                | Cascode and Cable Driver      | 20                 |

|                   | Timing Pulses                 | 22                 |

| 09                | Register Driver               | 23                 |

| 01                | High Speed Flip-Flop          | 24                 |

|                   | Marginal Checking             | 31                 |

| 46                | s-8ra                         | 34                 |

| 22                | Power Protector               | 35                 |

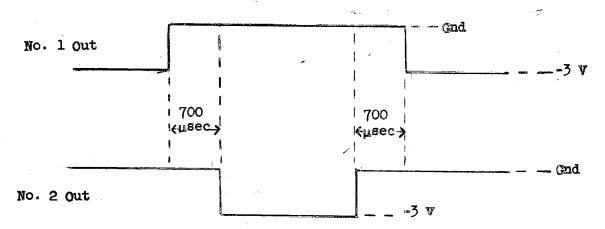

|                   | Variable Delay Units          | 36                 |

| 23                | Variable Delay Unit           |                    |

| 51                | Variable Delay Auxiliary Unit |                    |

| 49                | Variable Delay Coupling Unit  |                    |

## 6p-2631

## TABLE OF CONTENTS (Contod)

| CIRCUIT<br>NUMBER | TITLE                           | DISCUSSION ON PAGE |

|-------------------|---------------------------------|--------------------|

|                   | Delay Lines                     | 38                 |

| 57                | .15 µsec 50 ohm Delay Line      |                    |

| 48                | Inhibit Level Delay Line        |                    |

| 58                | .4 µsec 75 ohm Delay Line       |                    |

| 56                | Gated Pulse Amplifier           | 40                 |

|                   | Index Memory                    | 41                 |

| 19                | Read Driver                     |                    |

| 21                | Write Driver                    | •                  |

| 16                | Read Amplifier and Digit Driver |                    |

| 17                | Select Circuit First Level      |                    |

| 18                | Select Circuit Second Level     |                    |

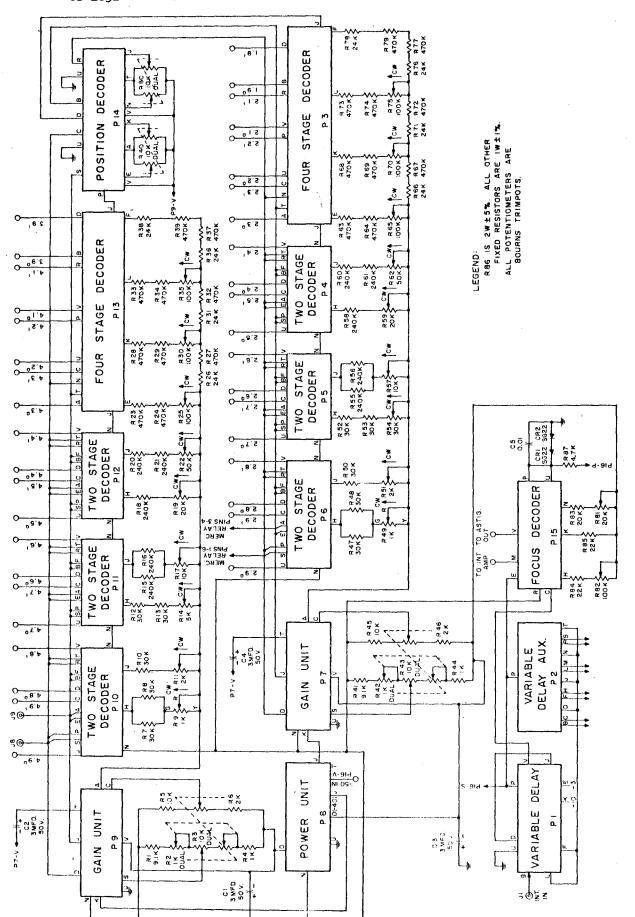

|                   | Display System                  | 43                 |

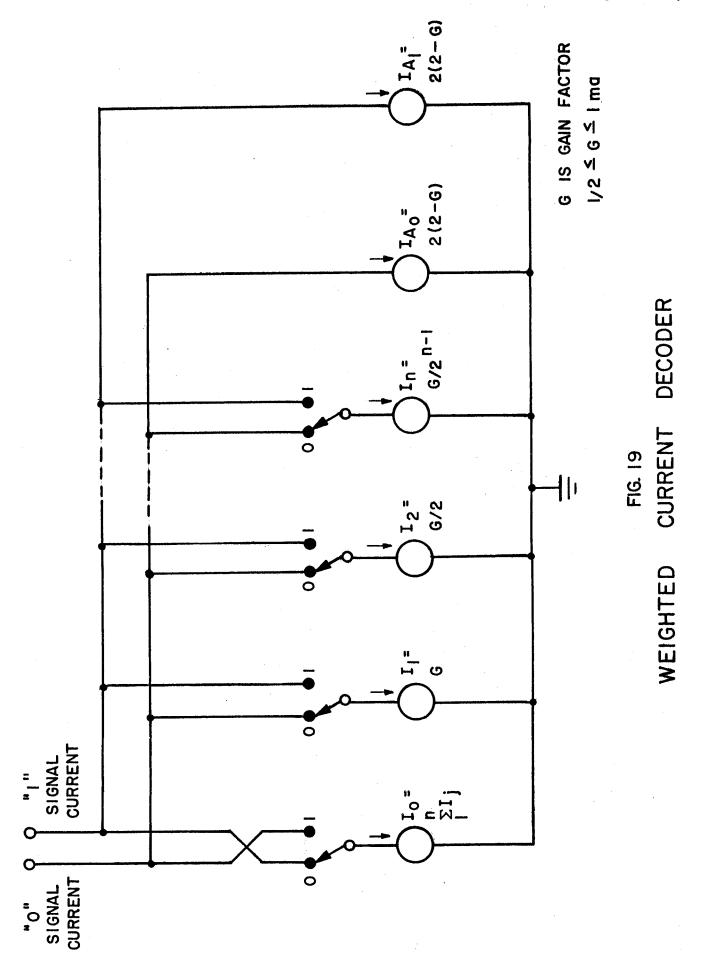

| 27                | Four Stage Decoder              |                    |

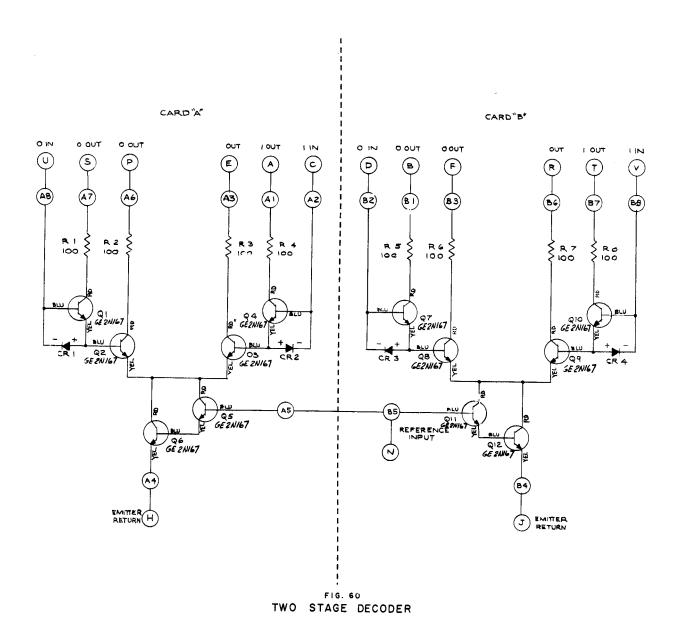

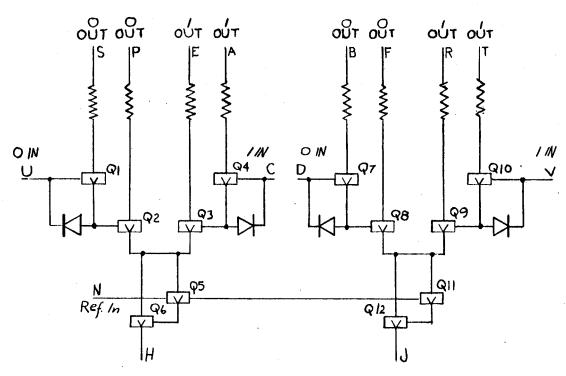

| 26                | Two Stage Decoder               |                    |

| 29                | Focus Decoder                   |                    |

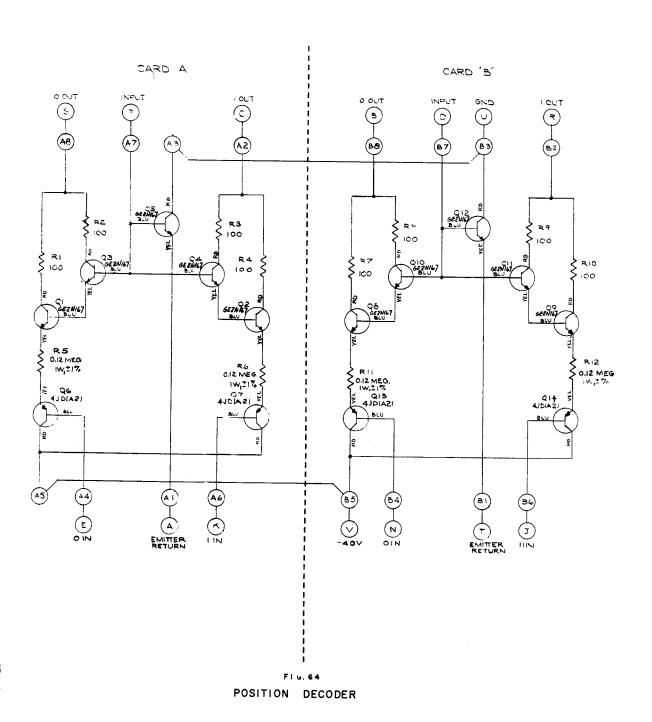

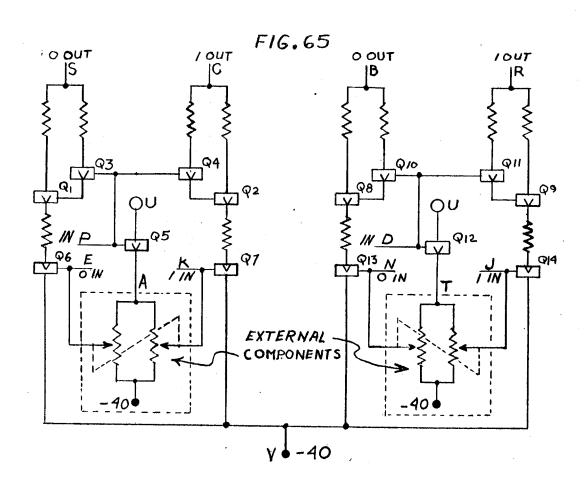

| 28                | Position Decoder                |                    |

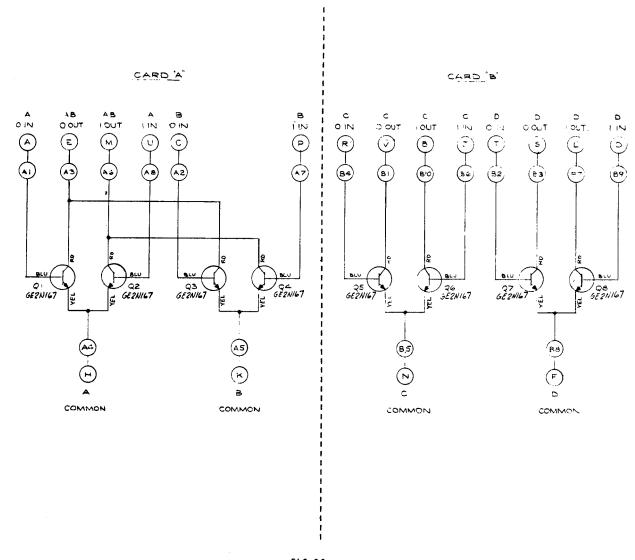

| 30                | Decoder Gain Section            |                    |

| 31                | Decoder Power Unit              |                    |

|                   | Toggle Switch Storage           | 52                 |

| 39                | TSS Resistor Driver             |                    |

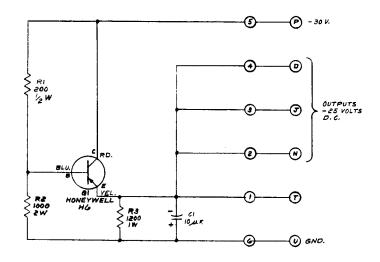

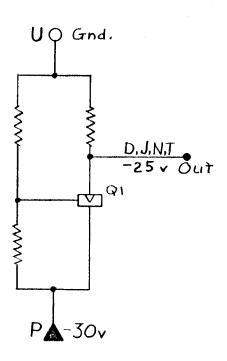

| 41                | TSS 25 volt Power Supply Unit   |                    |

| 40                | TSS Digit Detector Unit         |                    |

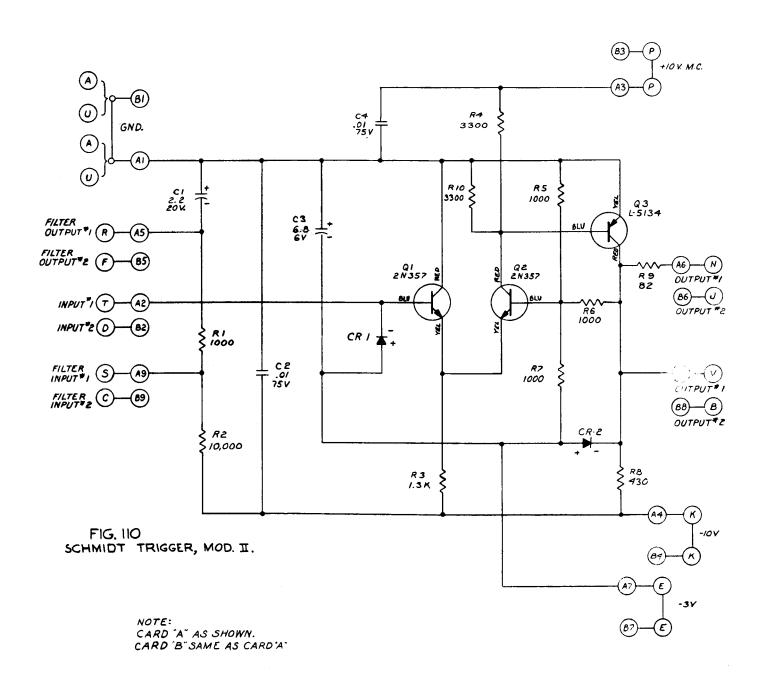

| 53                | Schmidt Trigger Mod II          | 53                 |

| 54                | PETR Amplifier                  | 54                 |

# TABLE OF CONTENTS (Cont'd)

| CIRCUIT<br>NUMBER | TITIE                          | DISCUSSION ON PAGE |

|-------------------|--------------------------------|--------------------|

|                   | Electric Typewriter Circuitry  | 55                 |

| 38                | Solenoid Driver                |                    |

| 42                | Four H-6 Unit                  |                    |

| 44                | Typewriter Diode Unit          |                    |

| 68                | Lamp Lighter                   | 56                 |

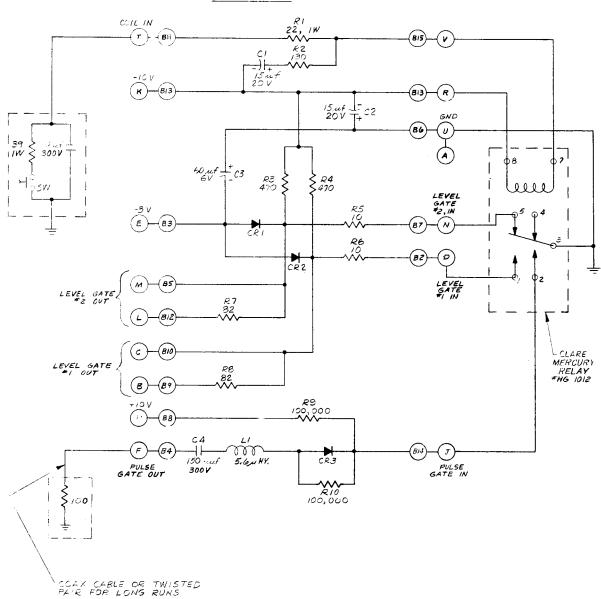

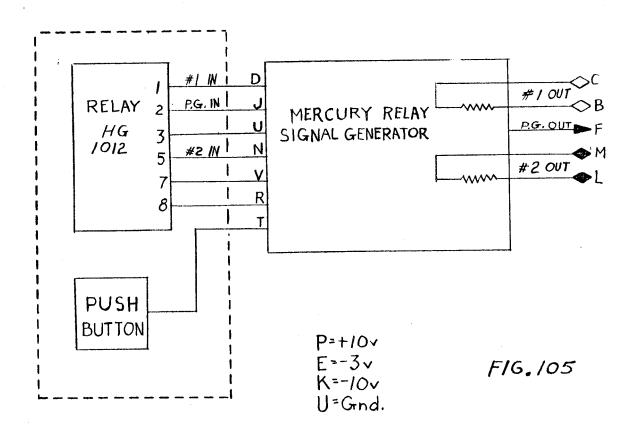

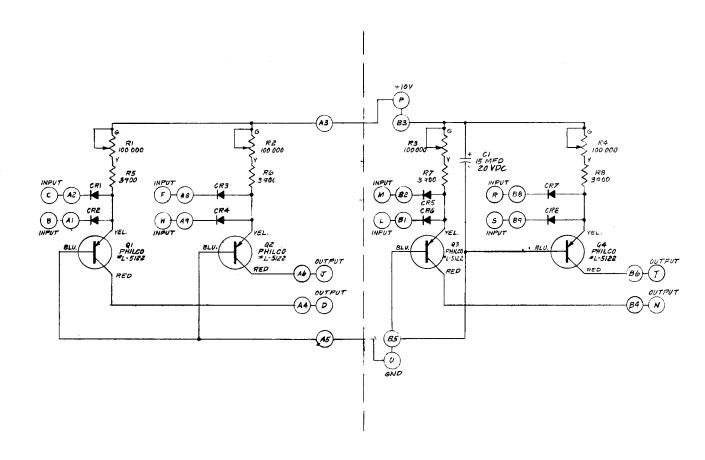

| 50                | Mercury Relay Signal Generator | 57                 |

| 55                | .l µsec Pulse Former           | 59                 |

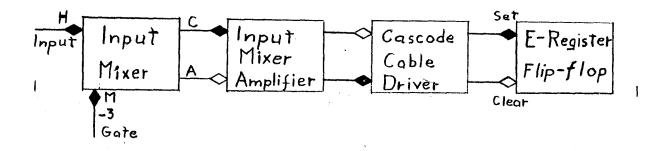

| 45                | Input Mixer                    | 60                 |

| 52                | Imput Mixer Amplifier          | 61                 |

|                   | In-Out Logic Circuits          | 62                 |

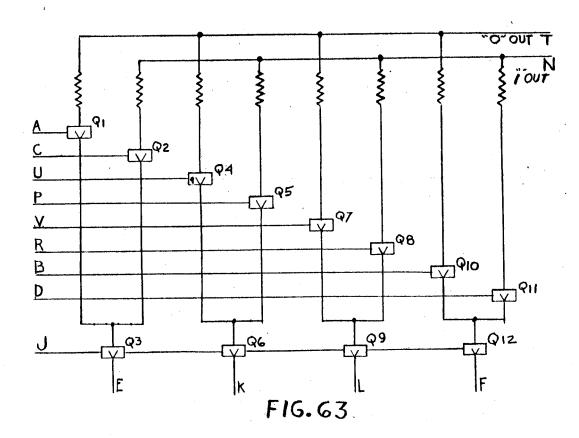

| 63                | Capacitor-Diode Gate           | 63                 |

| 60                | .3 µsec Pulse Former Mod II    | 64                 |

| 59                | Output Distributor             | 65                 |

| 65                | Output Mixer                   | 65                 |

| 66                | Line Driver                    | 66                 |

| 61                | Dual Flip-Flop Mod II          | 67                 |

| 62                | Synchronizer                   | 71                 |

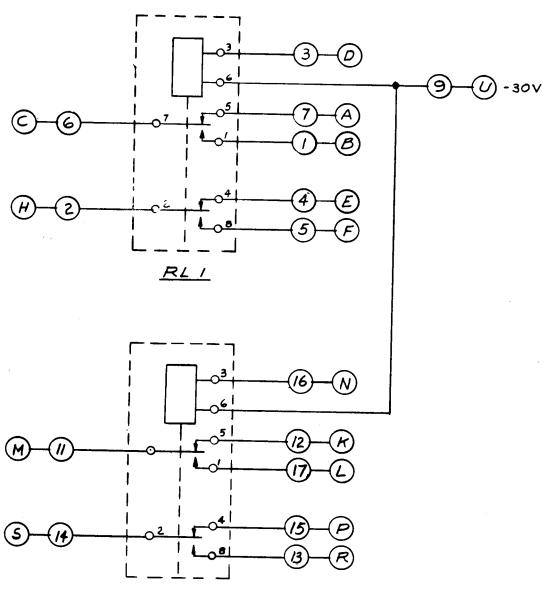

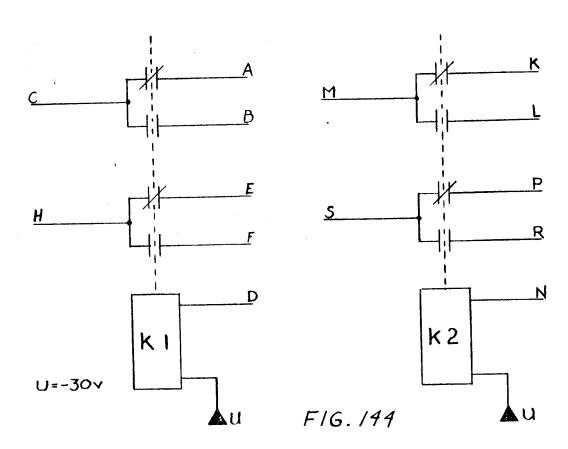

| 69                | Relay Unit                     | 72                 |

## 6**p-**2631

## TABLE OF CONTENTS (Cont'd)

|                                              | PAGE |

|----------------------------------------------|------|

| Reference Manual                             | 73   |

| Appendix                                     |      |

| List of Transistors Used in TX-2 Circuitry   | 199  |

| Surface Barrier Transistor Specifications    | 201  |

| List of M-Notes Pertaining to TX-0, TX-2 and |      |

| Surface Barrier Transistors                  | 203  |

## LIST OF ILLUSTRATIONS

| FIGURE NO.      | DRAWING NO.            | PAGE    |

|-----------------|------------------------|---------|

| Fig. 1          | <b>SA-</b> 87034       | 4 and 5 |

| Fig. 2          | B-69408: "A" reduction | 6       |

| Fig. 3          | P488-70                | 7       |

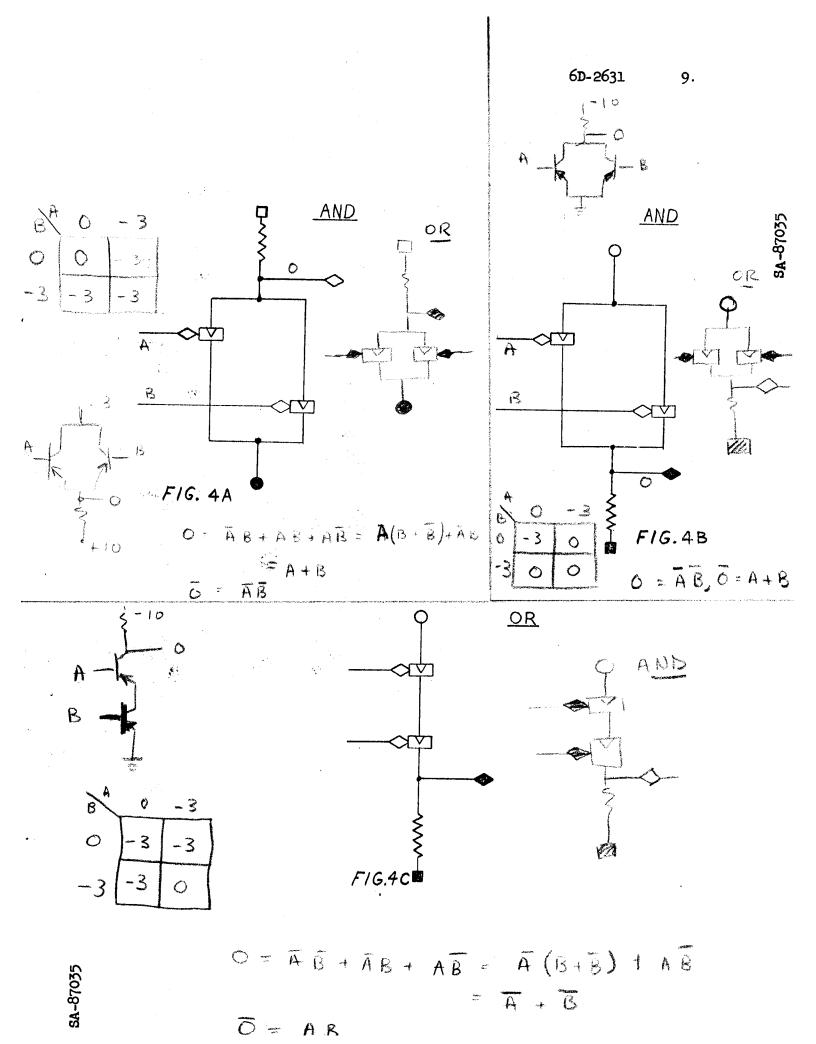

| Fig. 4A, 4B, 4C | <b>SA-</b> 87035       | 9       |

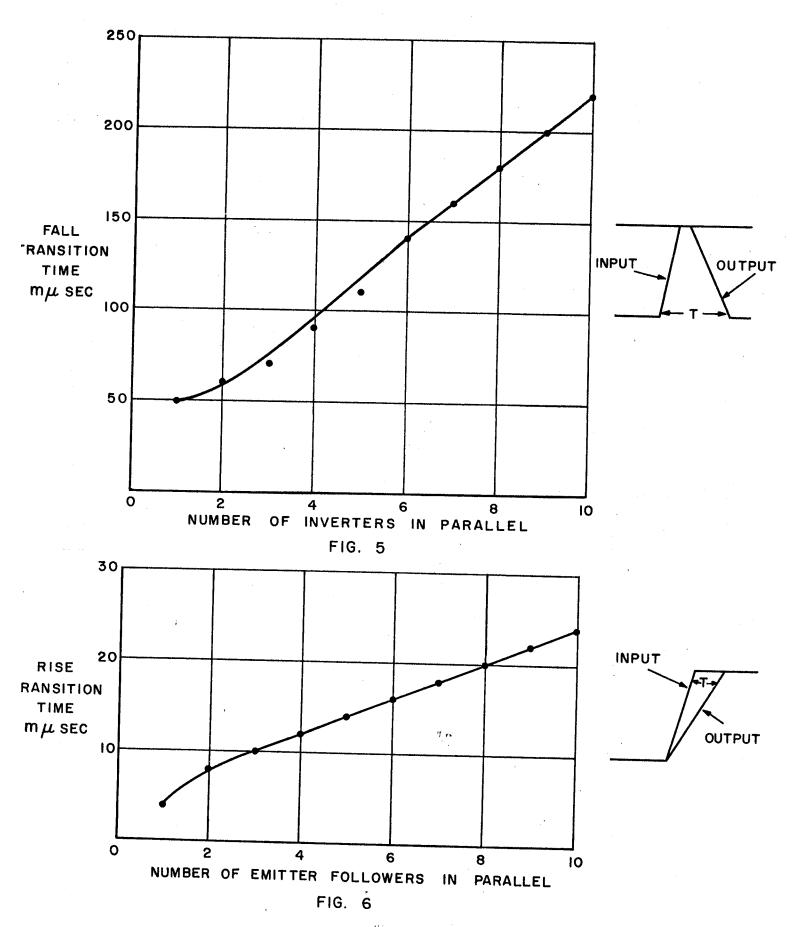

| Fig. 5, Fig. 6  | <b>A-8</b> 4966        | 11      |

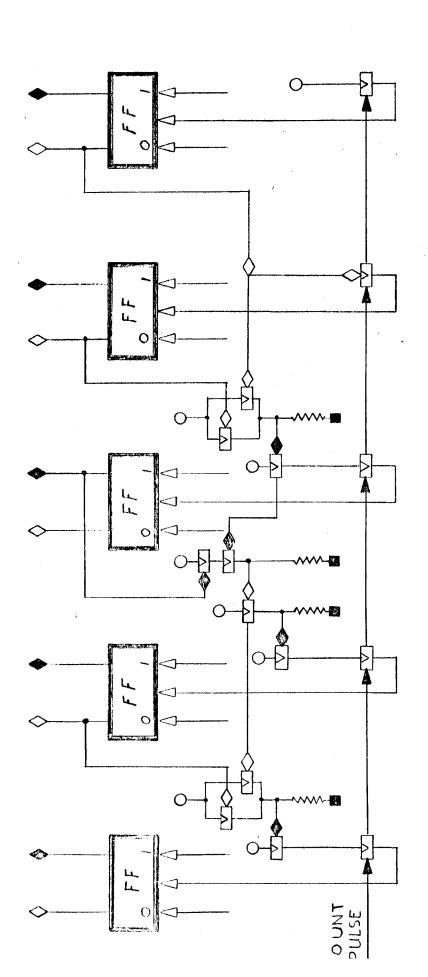

| Fig. 7          | SA-87036               | 13      |

| Fig. 8          | SA-87037               | 14      |

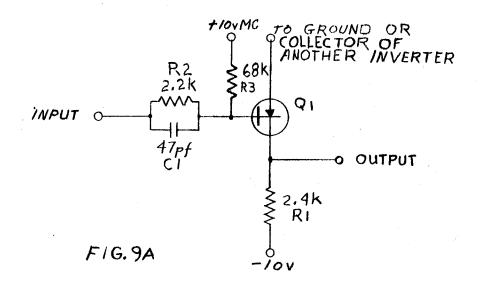

| Fig. 9A, 9B     | SA-87038               | 17      |

| Fig. 10         | <b>A-</b> 84967        | 18      |

| Fig. 11A, 11B   | <b>SA-</b> 87039       | 25      |

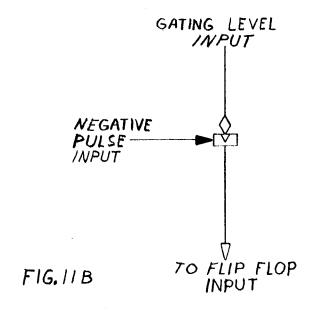

| Fig. 12         | <b>A-</b> 84968        | 27      |

| Fig. 13         | A-84969                | 28      |

| FIGURE NO. | DRAWING NO.           | PAGE |

|------------|-----------------------|------|

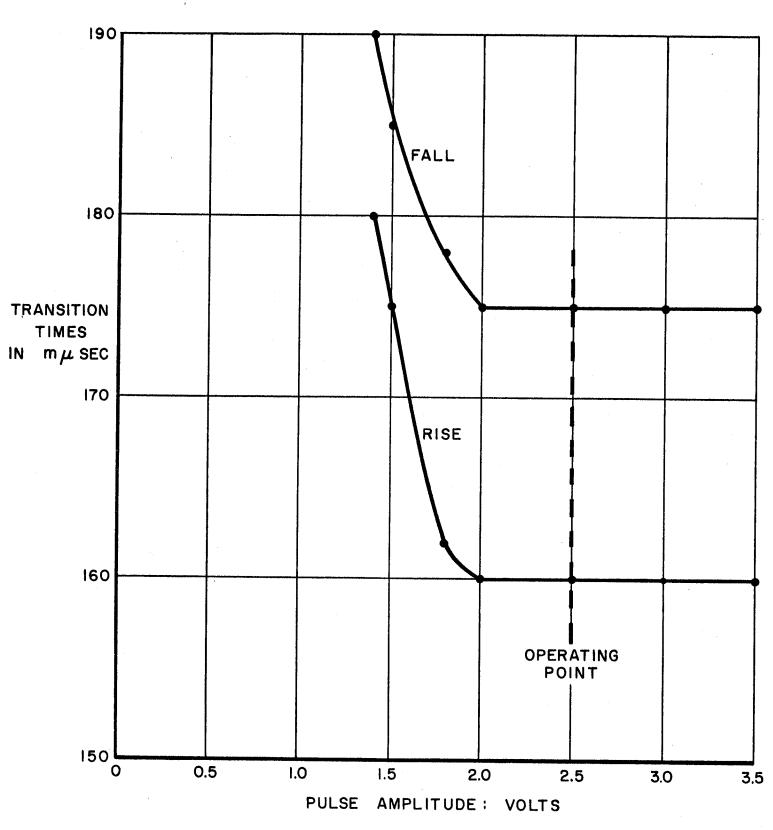

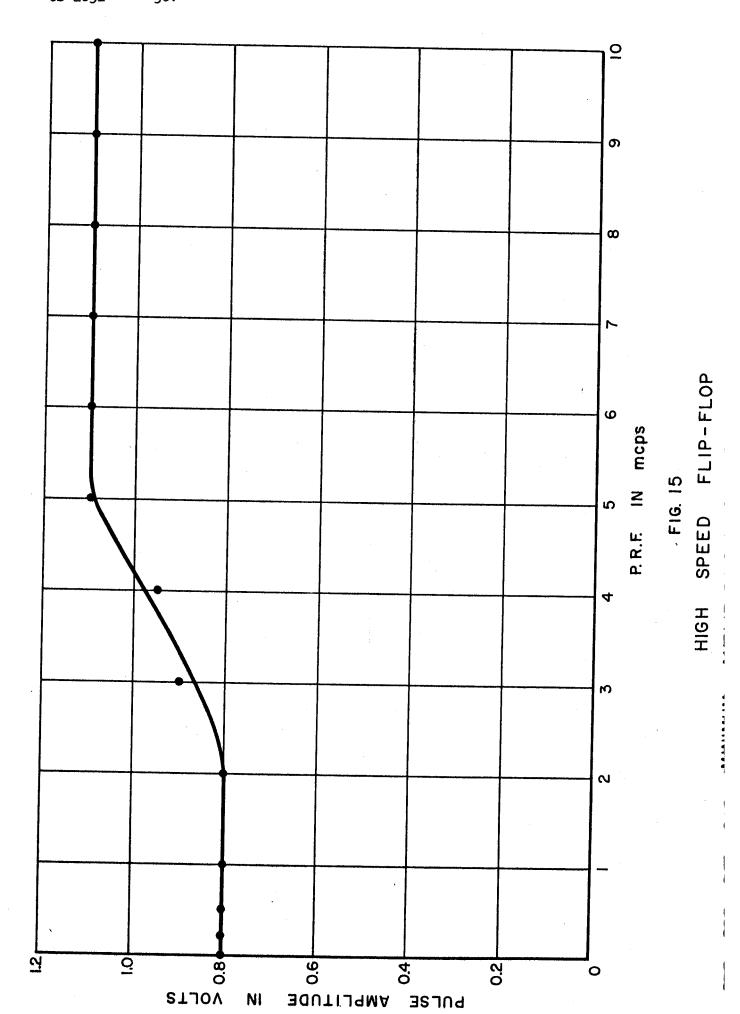

| Fig. 14    | <b>A-</b> 84971       | 29   |

| Fig. 15    | A-84973               | 30   |

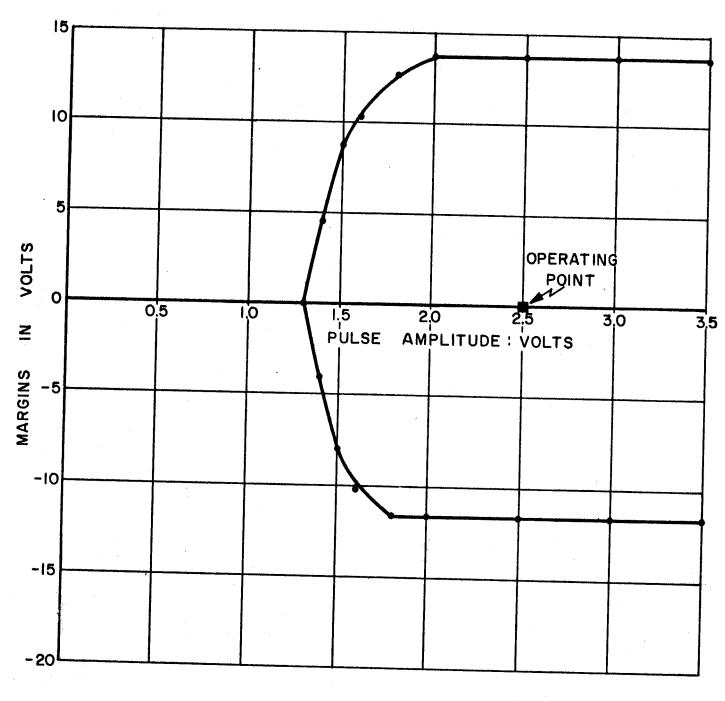

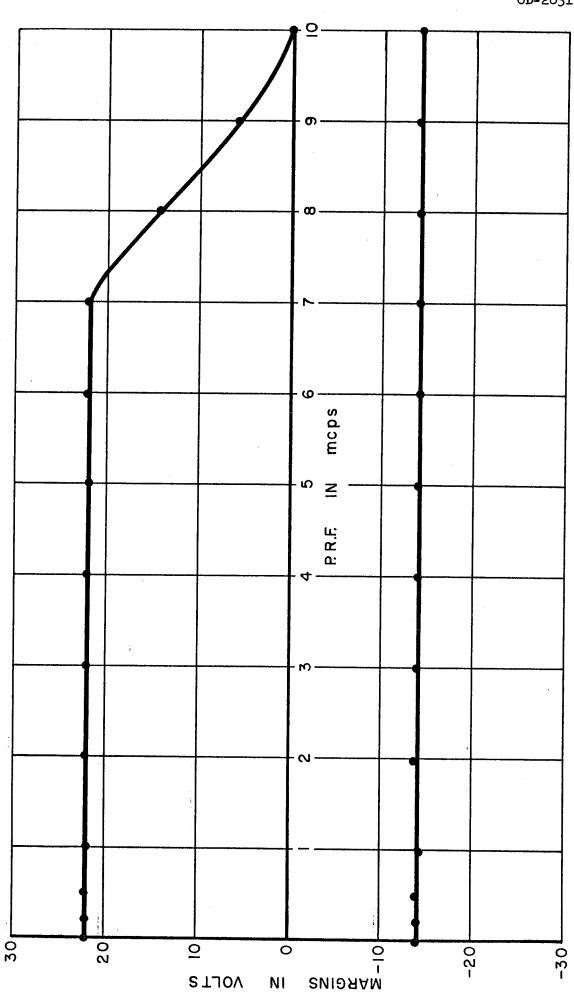

| Fig. 16    | A-84970               | 32   |

| Fig. 17    | A-84972               | 33   |

| Fig. 18    | c-88012               | 44   |

| Fig. 19    | A-87053               | 45   |

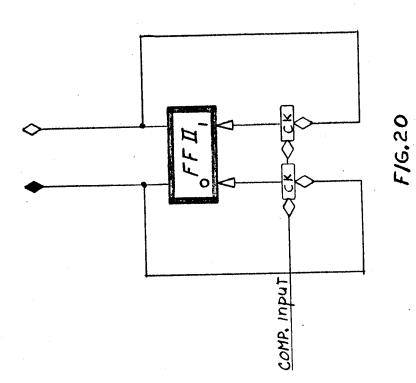

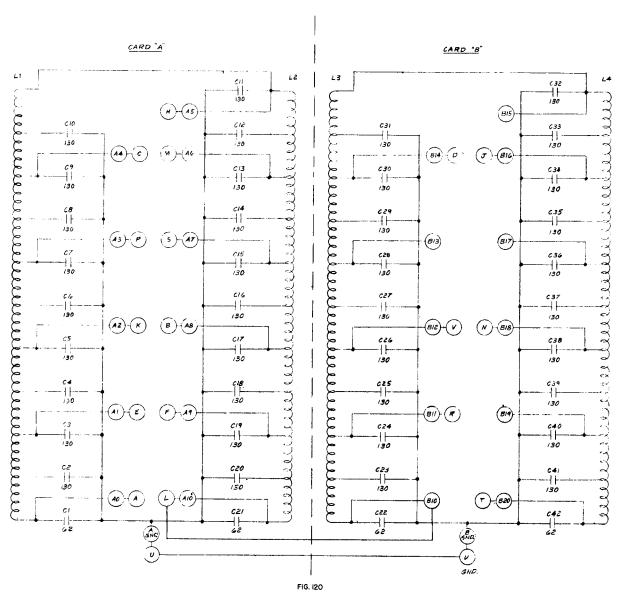

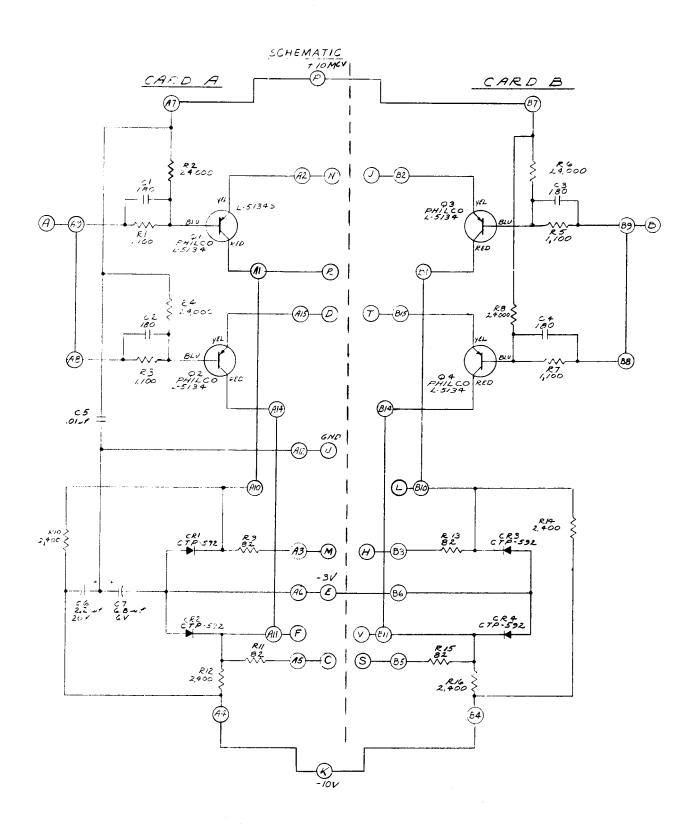

| Fig. 20    | <b>SA-</b> 87040      | 68   |

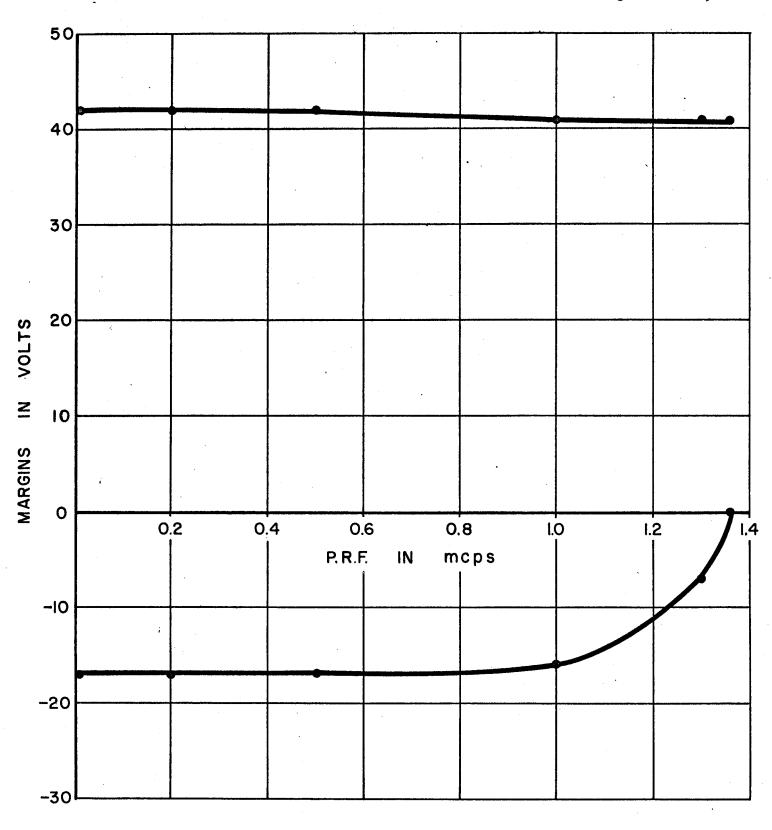

| Fig. 21    | A-84974               | 69   |

| Fig. 22    | A-84975               | 70   |

| Fig. 23    | D-84997 "A" reduction | 74   |

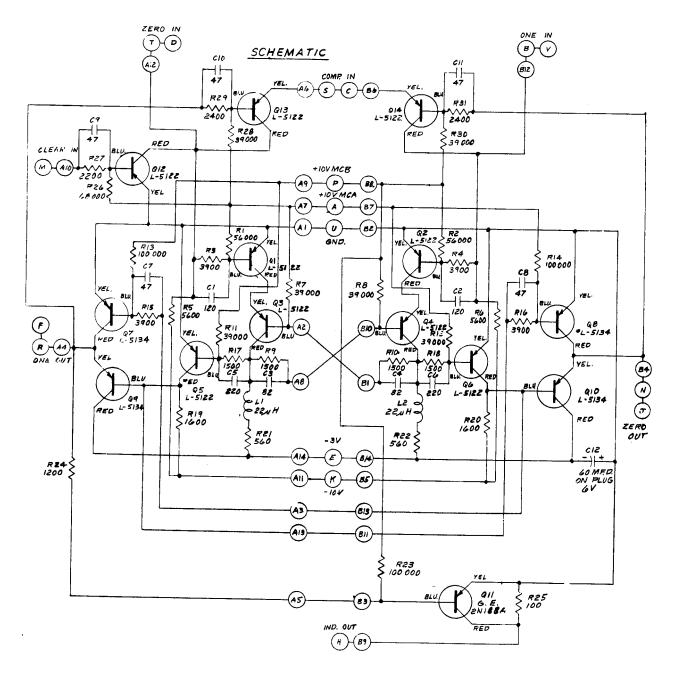

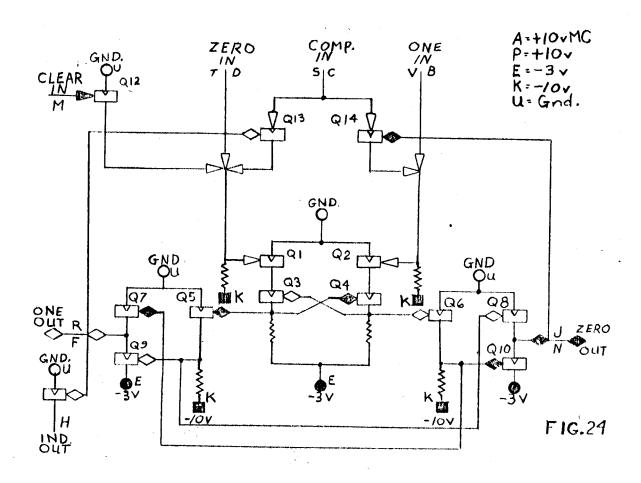

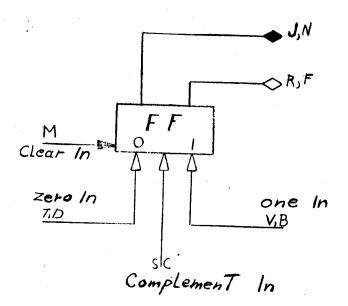

| Fig. 24    |                       | 75   |

| Fig. 25    |                       | 76   |

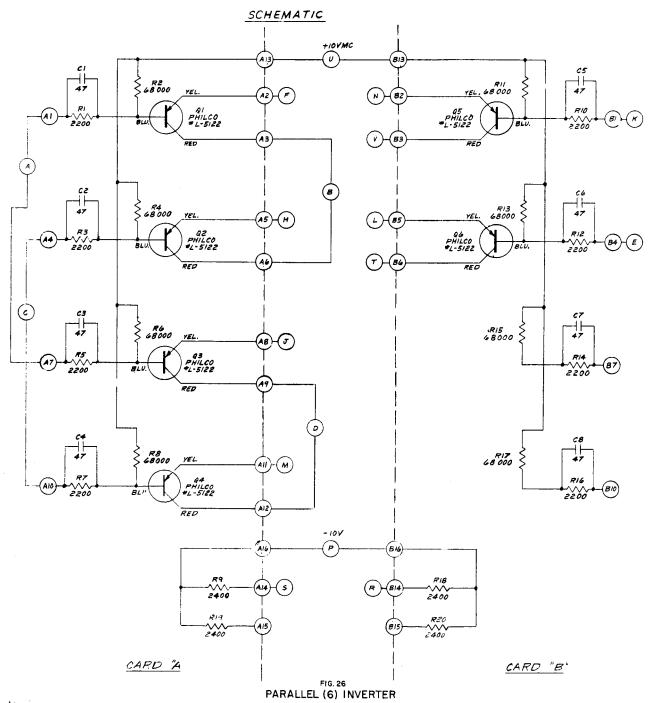

| Fig. 26    | D-86866 "A" reduction | 78   |

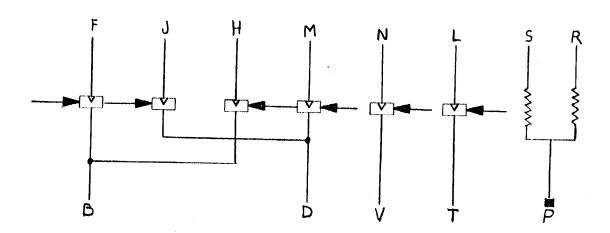

| Fig. 27    |                       | 79   |

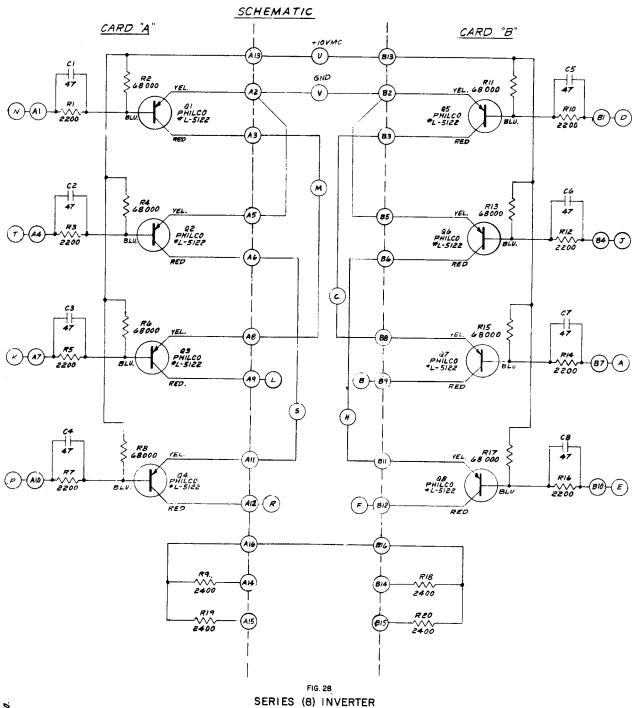

| Fig. 28    | D-86867 " "           | 80   |

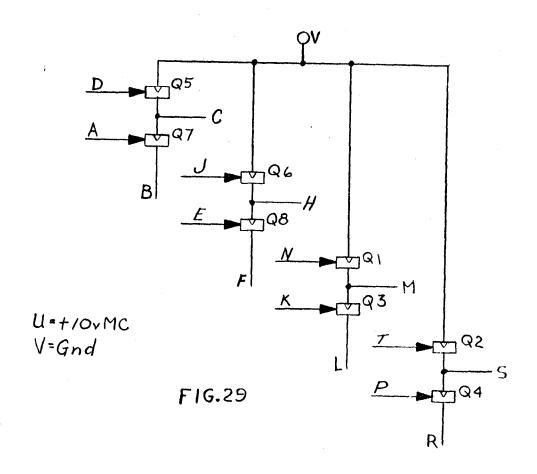

| Fig. 29    |                       | 81   |

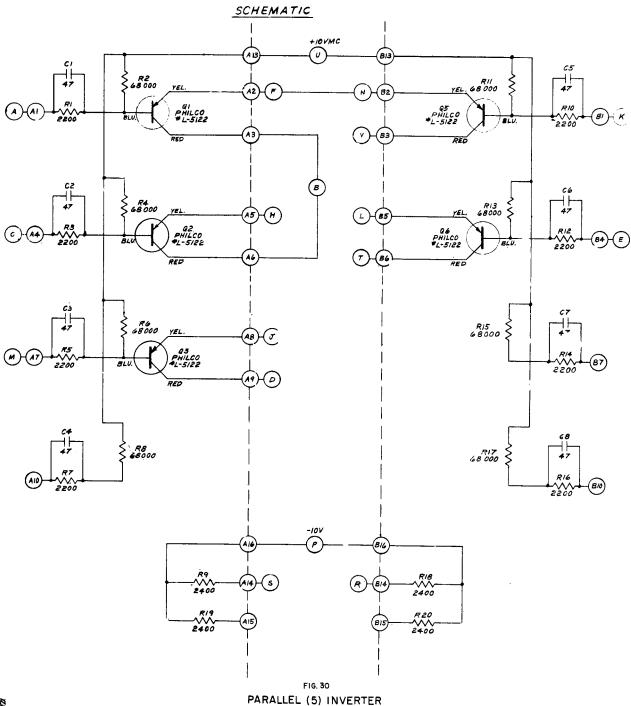

| Fig. 30    | <b>p-</b> 86518 " "   | 82   |

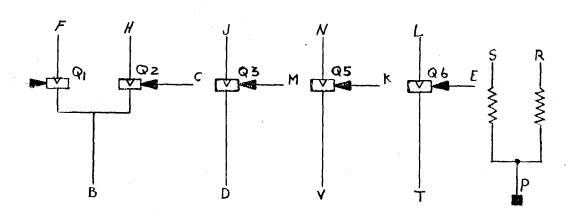

| Fig. 31    |                       | 83   |

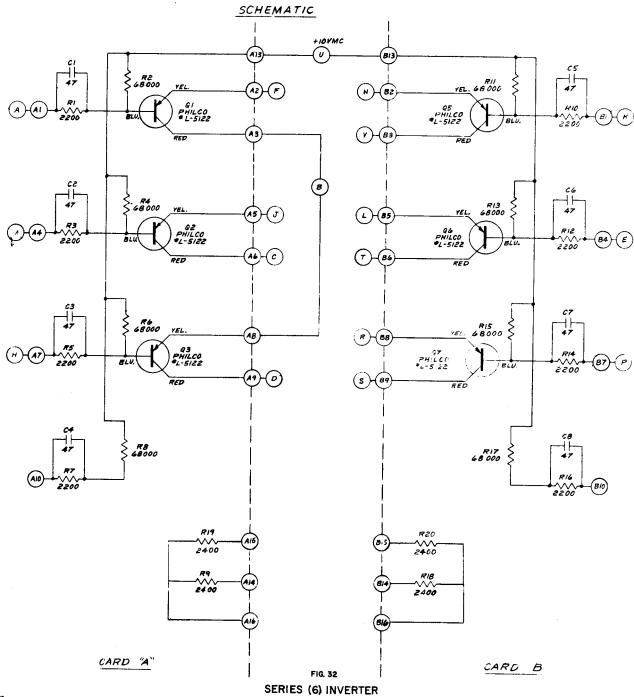

| Fig. 32    | <b>p-</b> 86865 " "   | 84   |

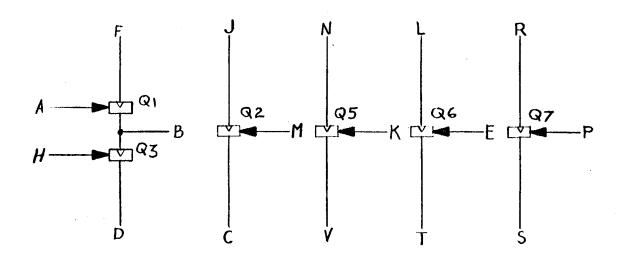

| Fig. 33    |                       | 85   |

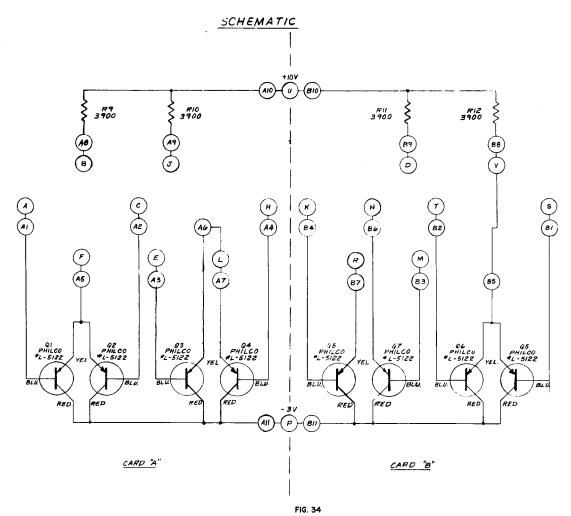

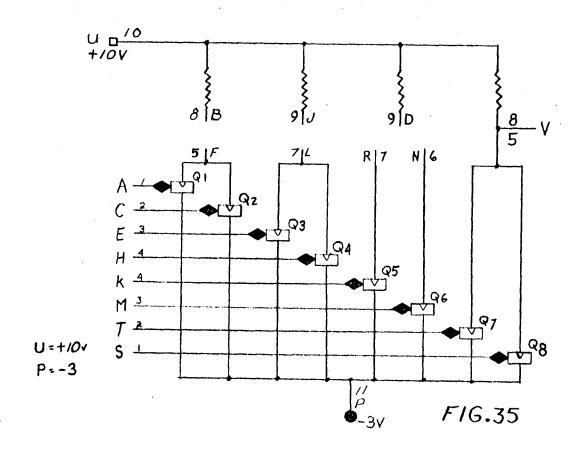

| Fig. 34    | D-86827 " "           | 86   |

| FIGURE NO.     | DRAWING NO.                  | PAGE |

|----------------|------------------------------|------|

| Fig. 35        | •                            | 87   |

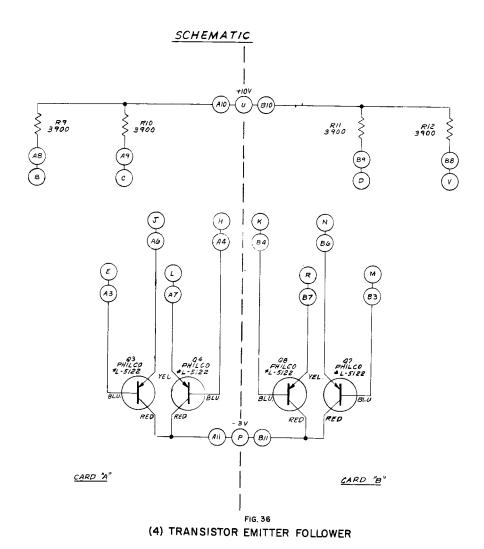

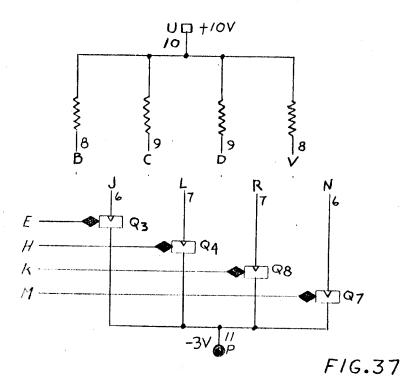

| Fig. 36        | p-86826 A" reduction         | 88   |

| Fig. 37        |                              | 89   |

| Fig. 38        | <b>p-</b> 86555 ** **        | 90   |

| Fig. 39        |                              | 91   |

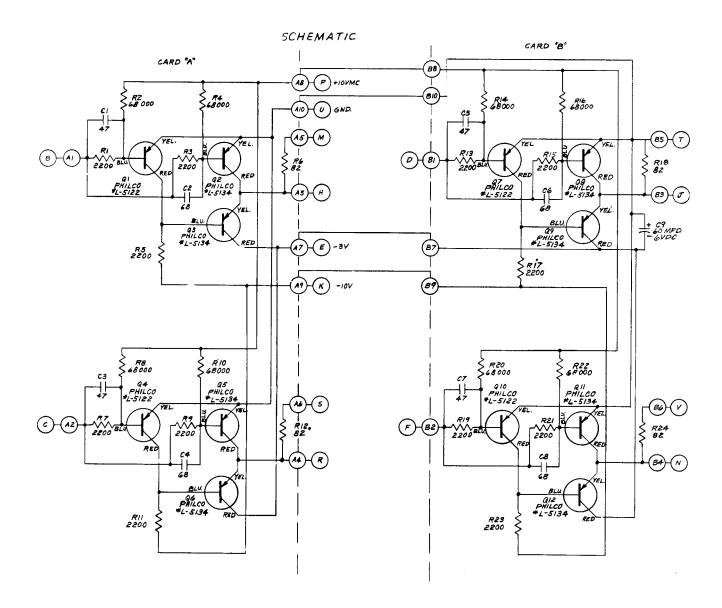

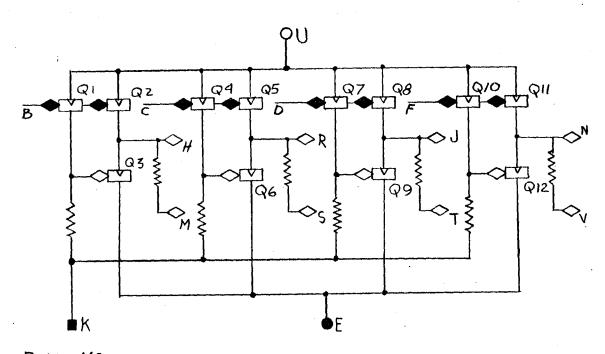

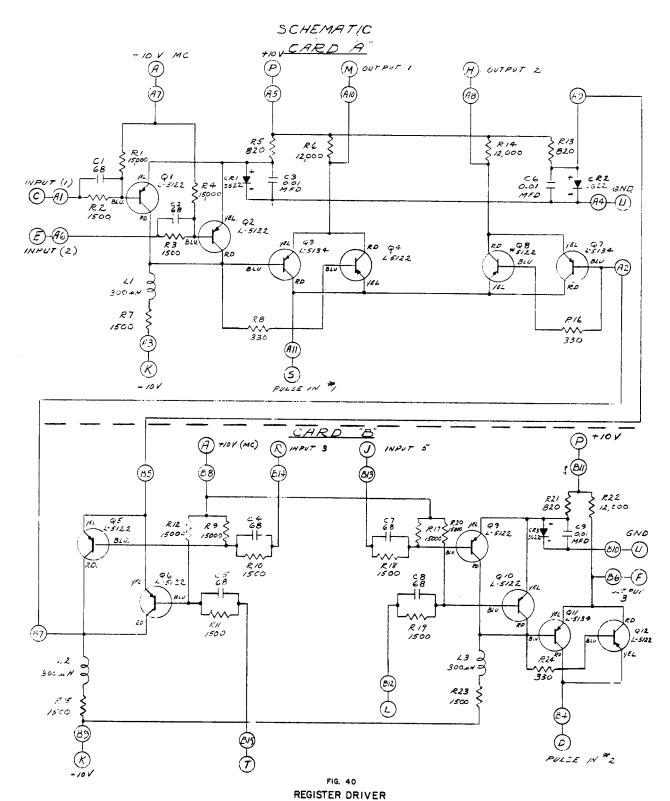

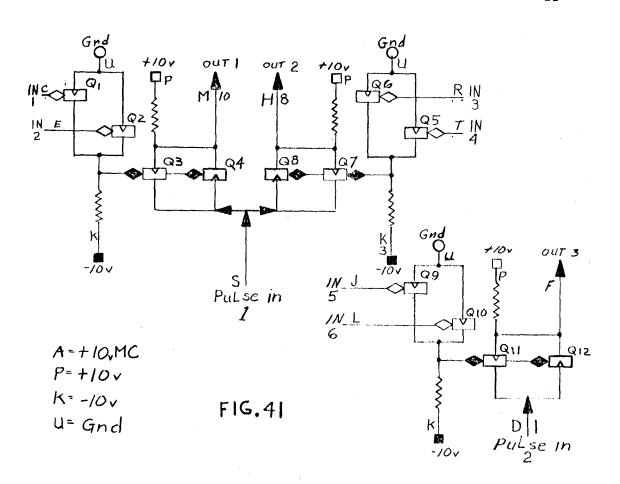

| Fig. 40        | <b>p-</b> 84924 ** **        | 92   |

| Fig. 41        |                              | 93   |

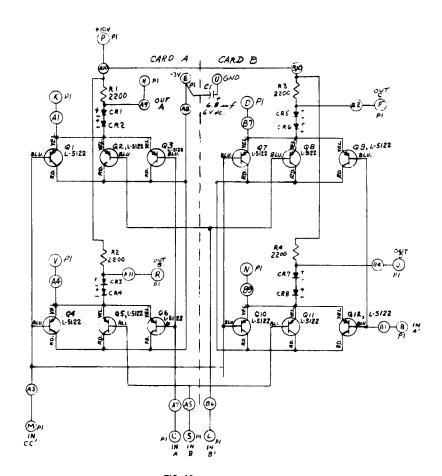

| Fig. 42        | <b>p-</b> 67141 ** **        | 94   |

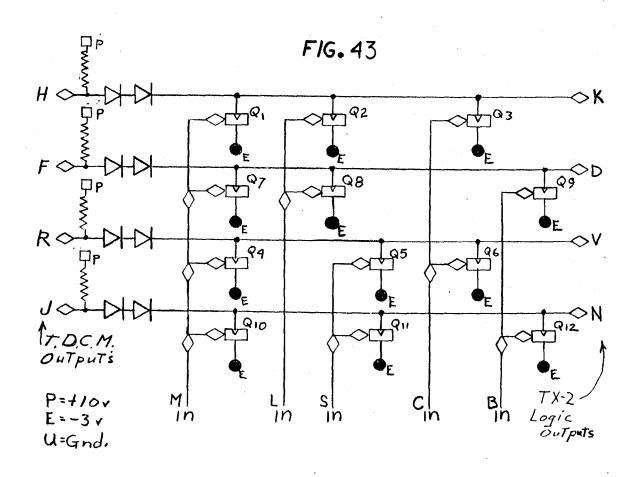

| Fig. 43        |                              | 95   |

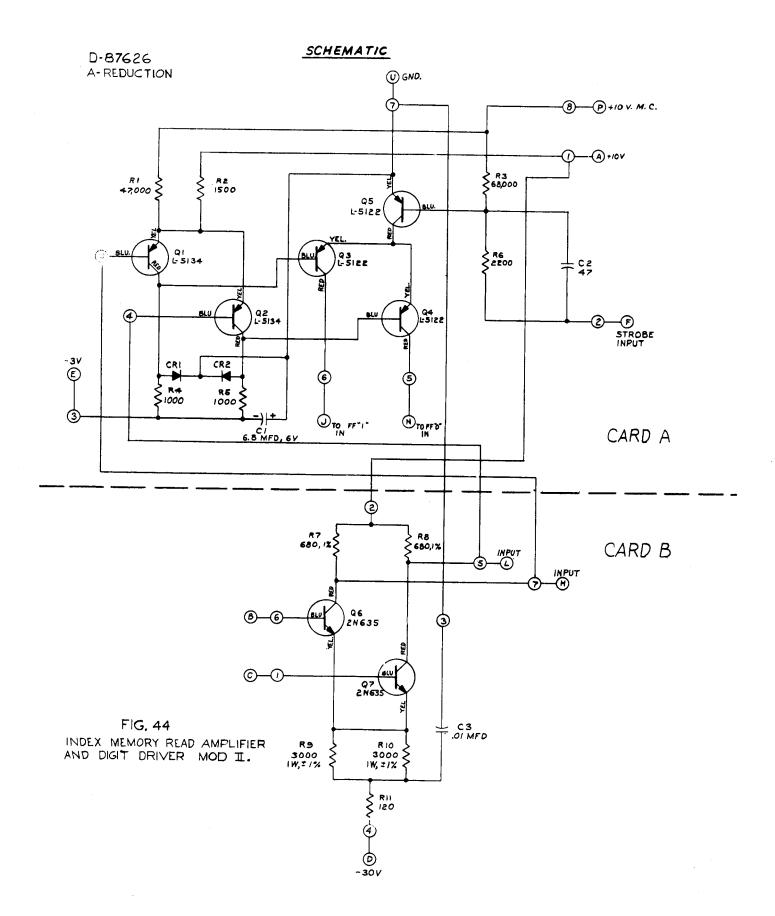

| Fig. 44        | D-87626 ** **                | 96   |

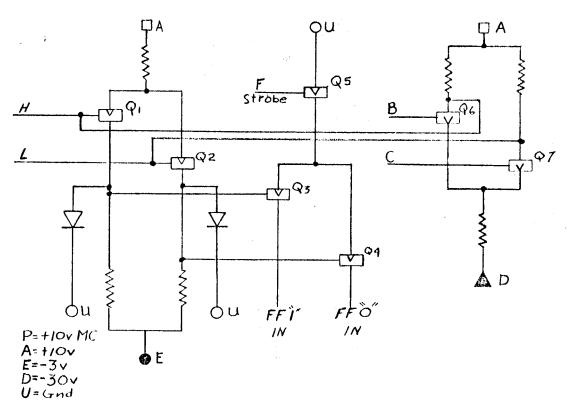

| Fig. 45        |                              | 97   |

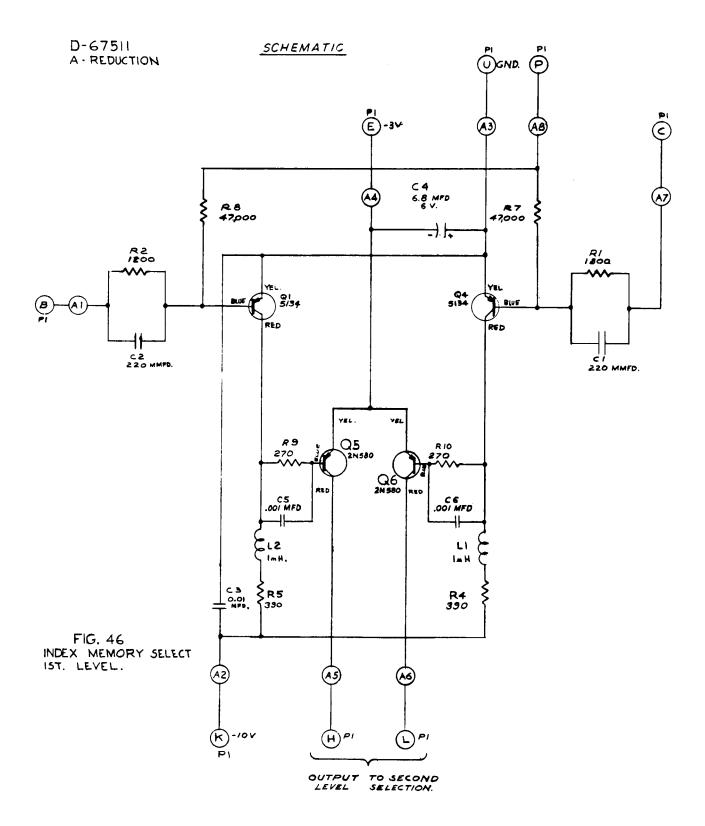

| Fig. 46        | D-67511 " "                  | 98   |

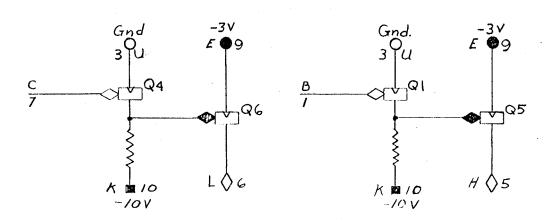

| Fig. 47        |                              | 99   |

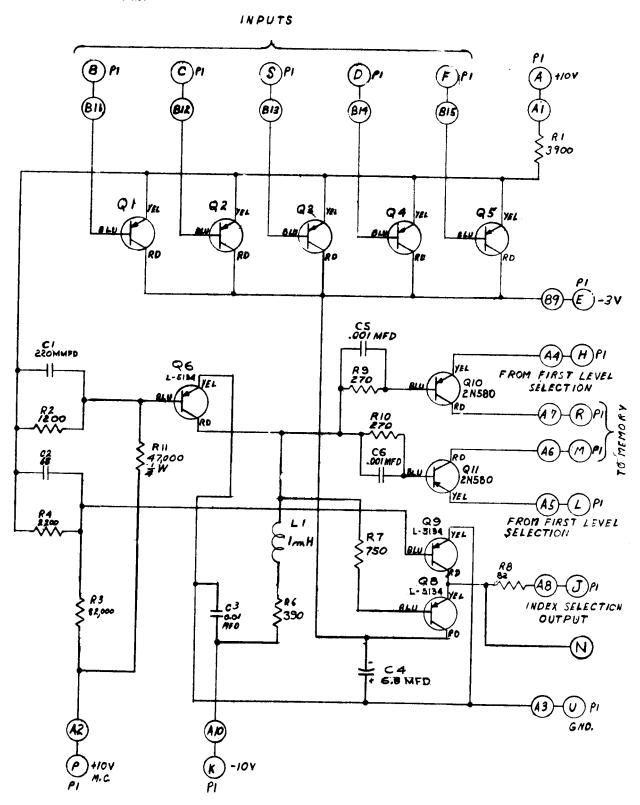

| Fig. 48        | <b>D-</b> 67572 <sup>®</sup> | 100  |

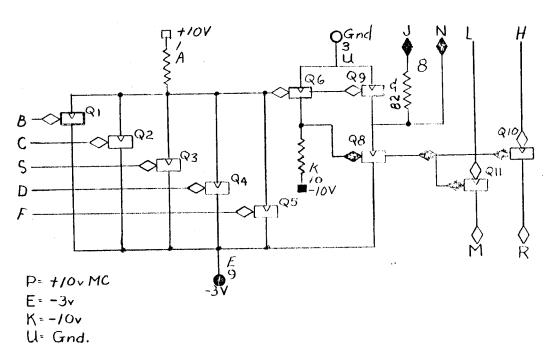

| Fig. 49        |                              | 101  |

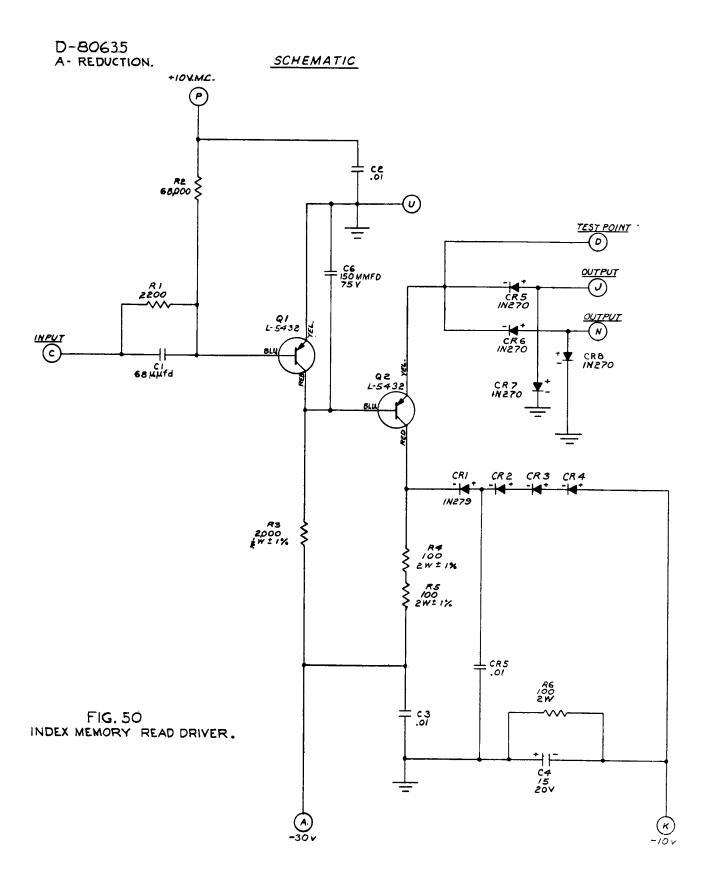

| Fig. 50        | D-80635 " "                  | 102  |

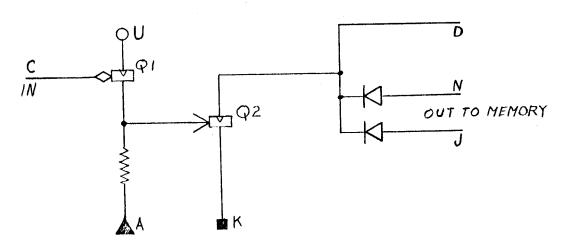

| Fig. 51        |                              | 103  |

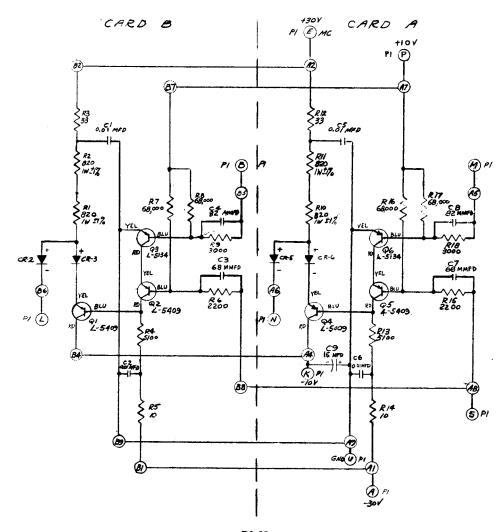

| Fig. 52        | D-67573 " "                  | 104  |

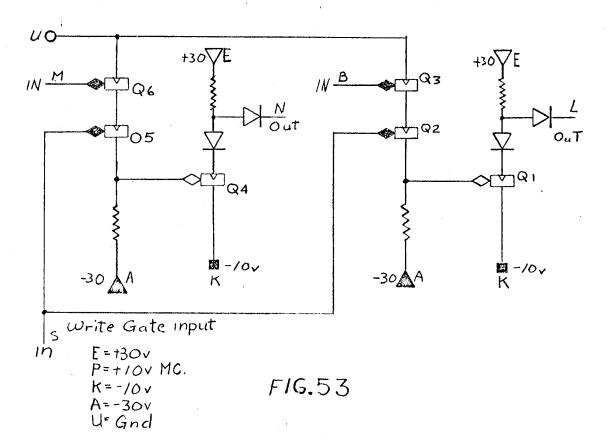

| Fig. 53        |                              | 105  |

| Fig. 54        | D-82709 ° °                  | 106  |

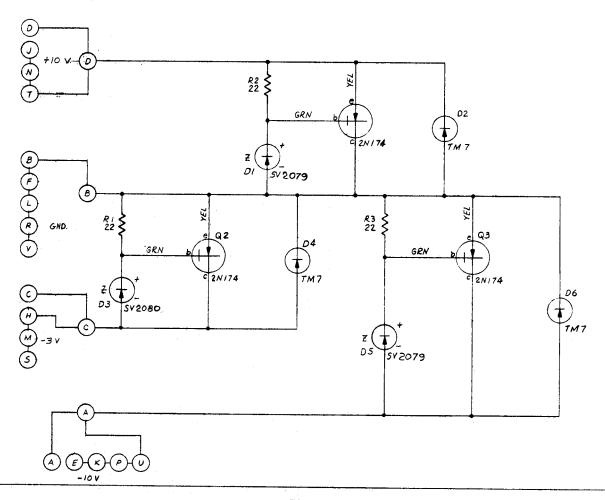

| <b>Fig.</b> 55 |                              | 107  |

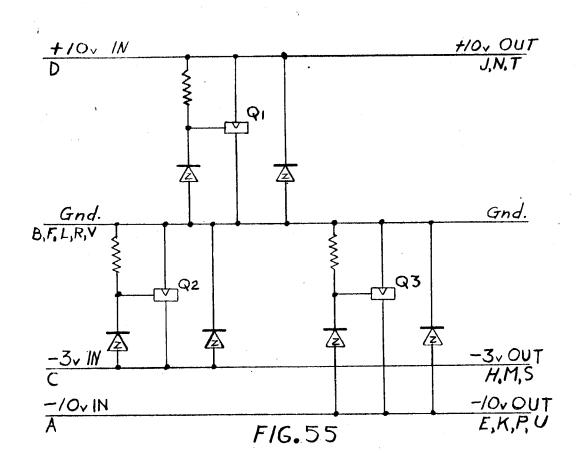

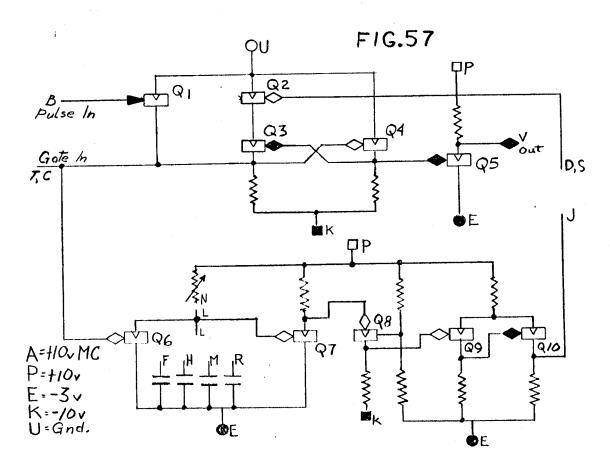

| <b>Fig.</b> 56 | D-84175 " "                  | 108  |

| FIGURE NO.      | DRAWING         | NO. |                    | PAGE |

|-----------------|-----------------|-----|--------------------|------|

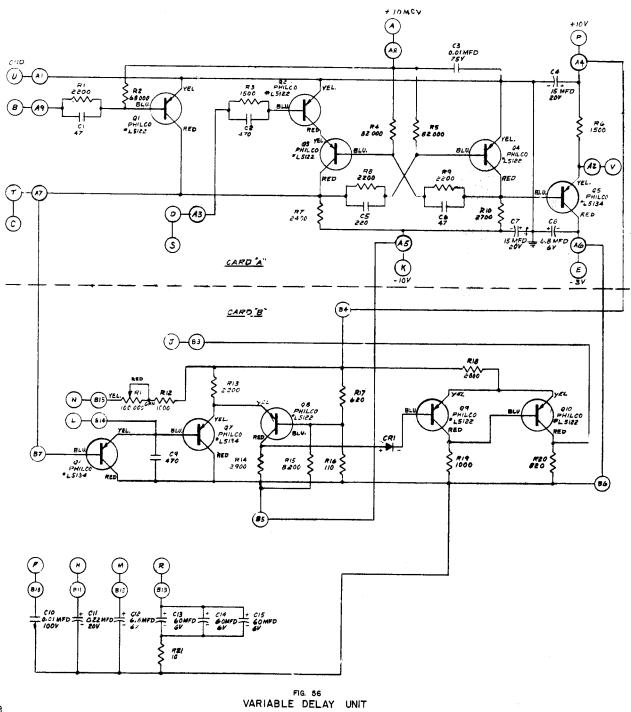

| Fig. 57         |                 |     |                    | 109  |

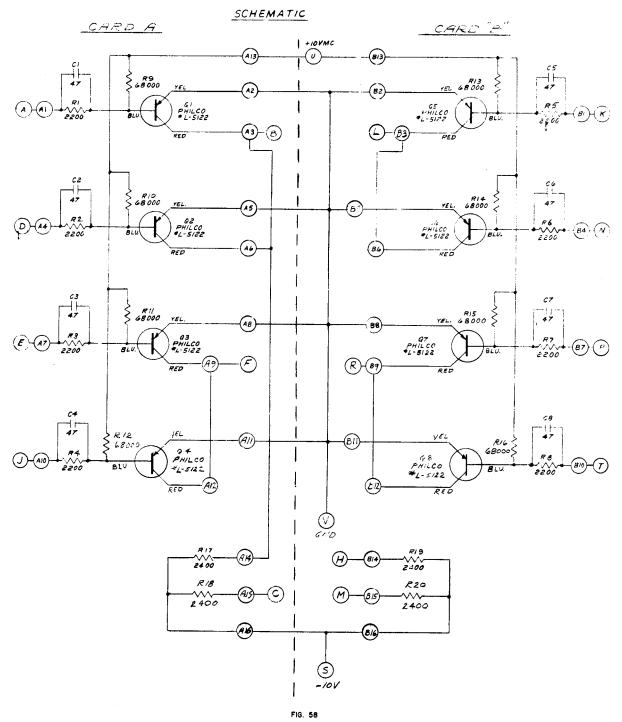

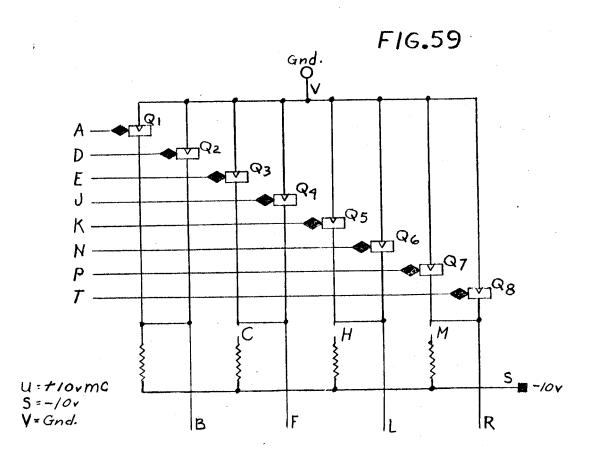

| Fig. 58         | <b>D-</b> 86886 | "A" | reduction          | 110  |

| <b>Fig.</b> 59  |                 |     |                    | 111  |

| <b>Fig.</b> 60  | <b>p</b> -68017 | . # | 11                 | 112  |

| Fig. 61         |                 |     |                    | 113  |

| Fig. 62         | D-67993         | **  | ##                 | 114  |

| Fig. 63         |                 |     |                    | 115  |

| <b>Fig.</b> 64  | D-67844         | Ħ   | gr <b>#</b> to the | 116  |

| <b>Fig.</b> 65  |                 |     |                    | 117  |

| <b>Fig.</b> 66  | <b>D-</b> 67904 | tt  | #1                 | 118  |

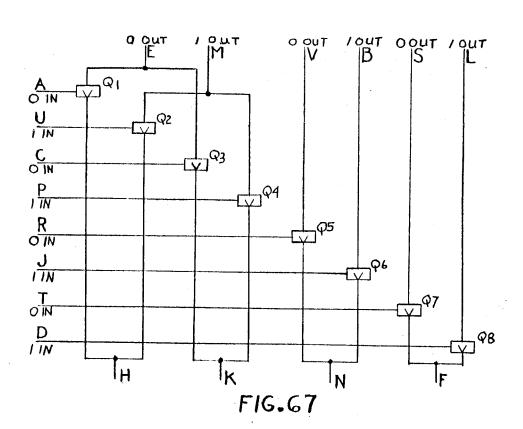

| <b>Fig</b> . 67 |                 |     |                    | 119  |

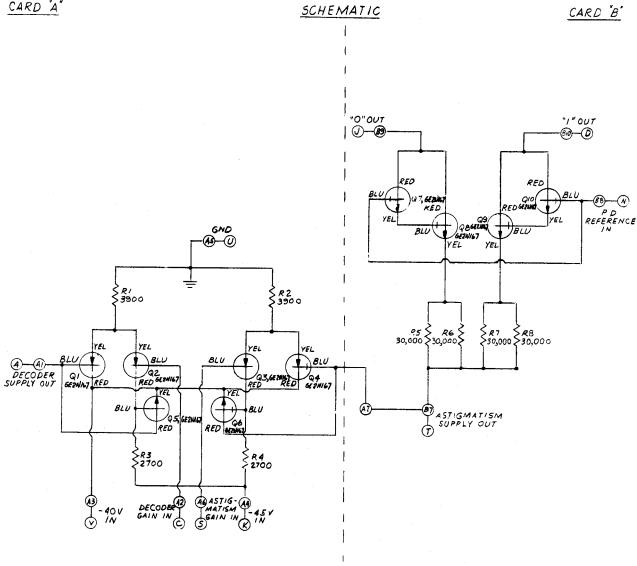

| Fig. 68         | <b>D-</b> 69151 | 98  | n                  | 120  |

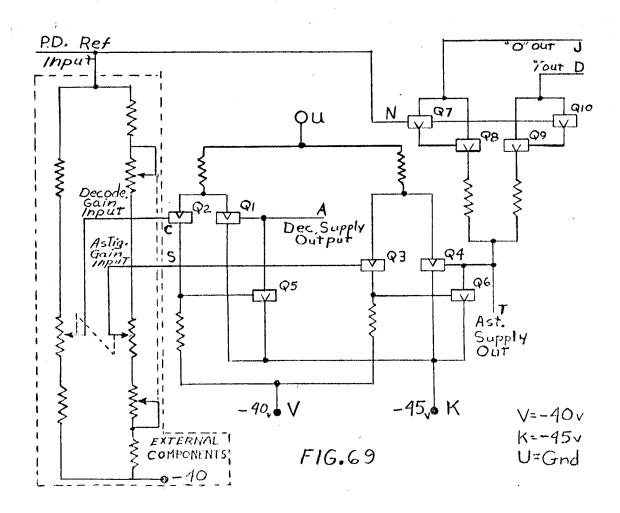

| Fig. 69         |                 |     | <b></b> • • • •    | 121  |

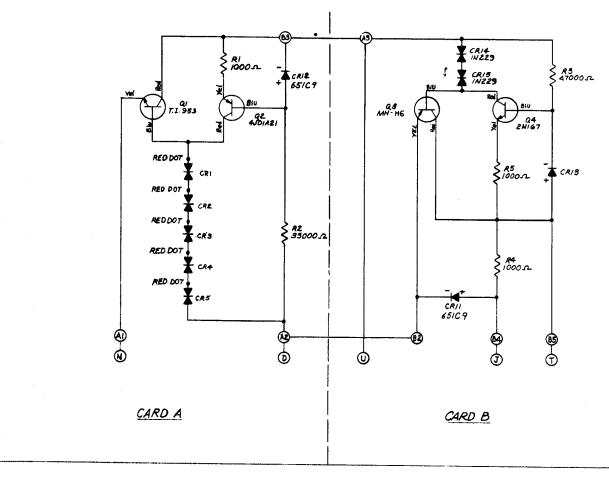

| Fig. 70         | <b>D-</b> 69152 | 99  | 99                 | 122  |

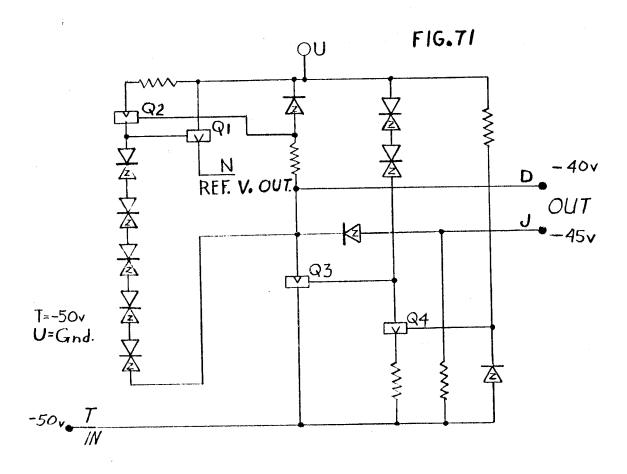

| Fig. 71         |                 |     |                    | 123  |

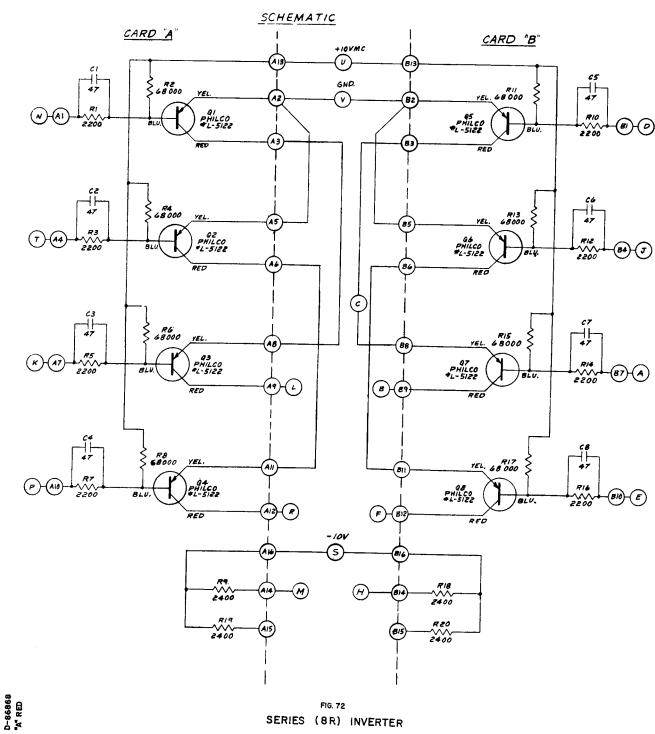

| Fig. 72         | <b>p-</b> 86868 | 99  | 90                 | 124  |

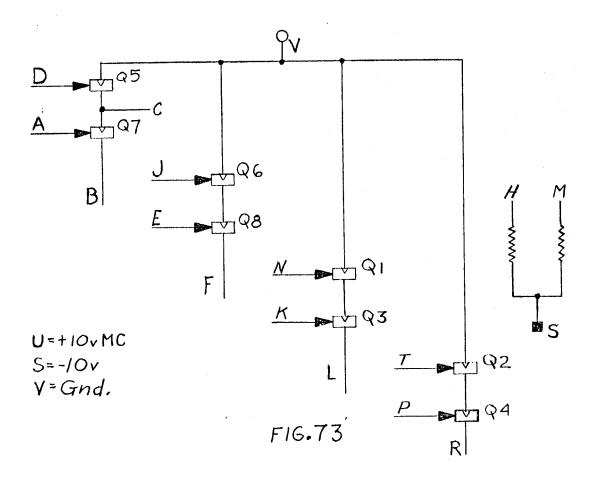

| Fig. 73         |                 |     |                    | 125  |

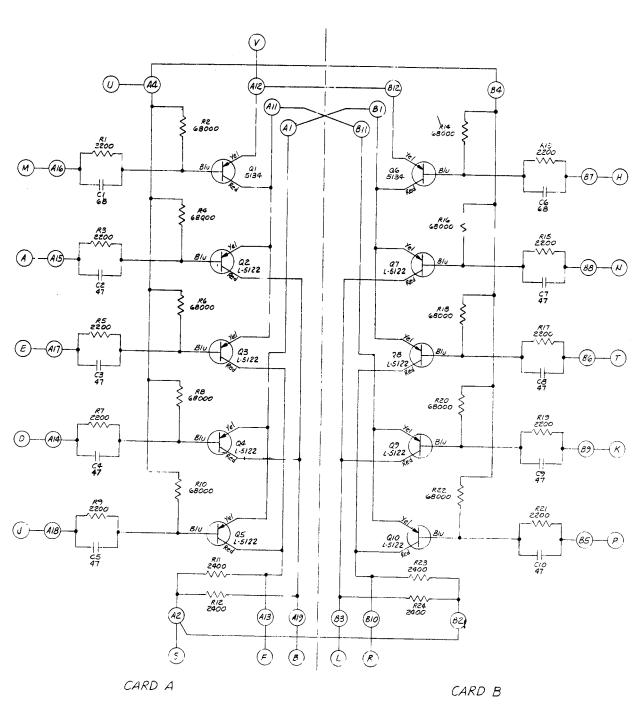

| <b>Fig</b> . 74 | <b>D</b> -81274 | Ħ.  | 99                 | 126  |

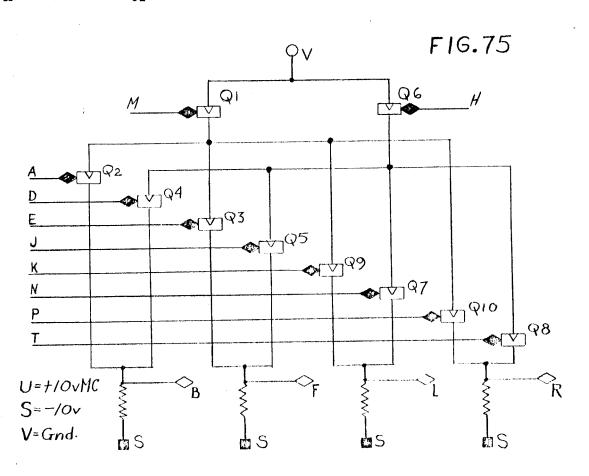

| Fig. 75         |                 |     |                    | 127  |

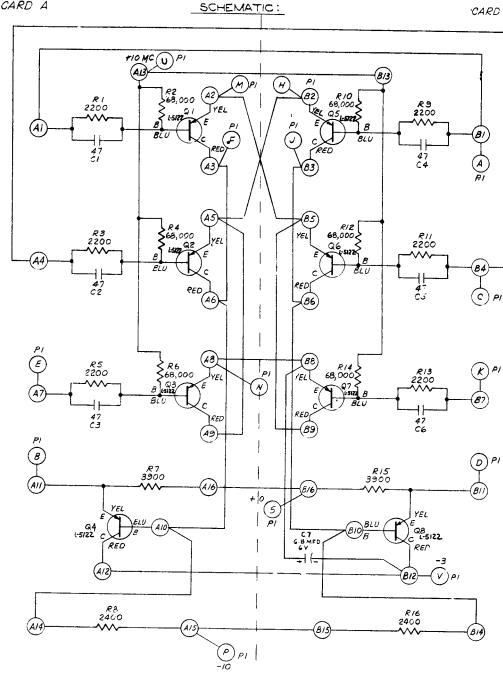

| Fig. 76         | <b>D-</b> 81271 | Ħ   | #1                 | 128  |

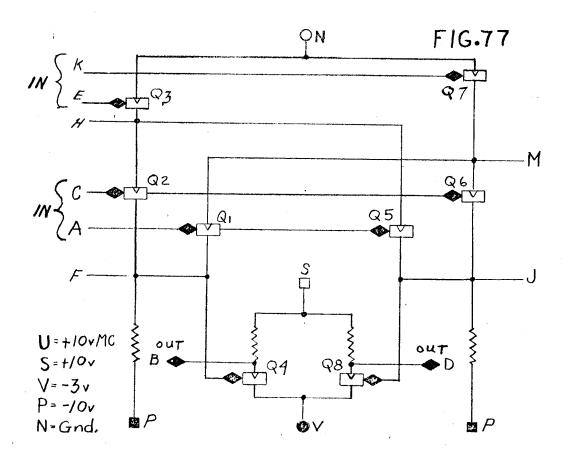

| Fig. 77         |                 |     |                    | 129  |

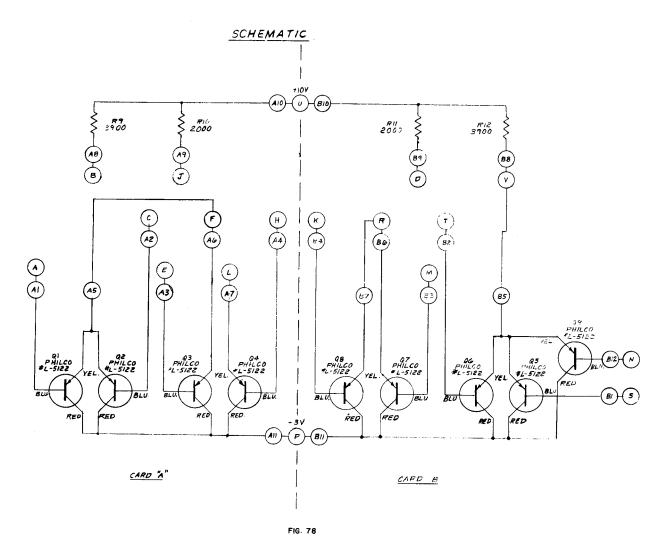

| Fig. 78         | <b>p</b> -86828 | 11  | *                  | 130  |

# 6**p-**2631

| FIGURE NO.       | DRAWING         | NO ·          | PAGE |

|------------------|-----------------|---------------|------|

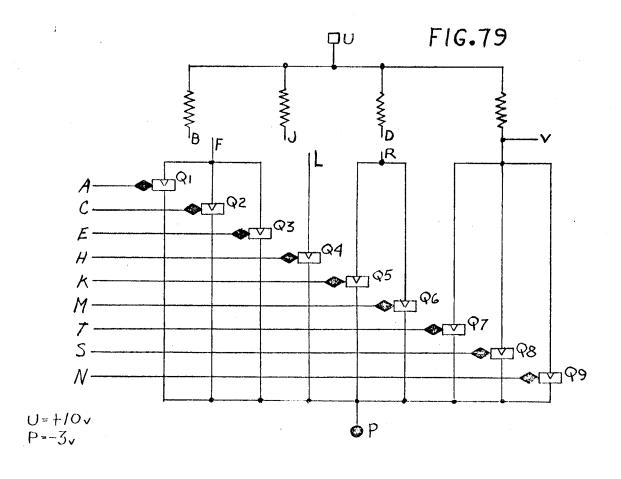

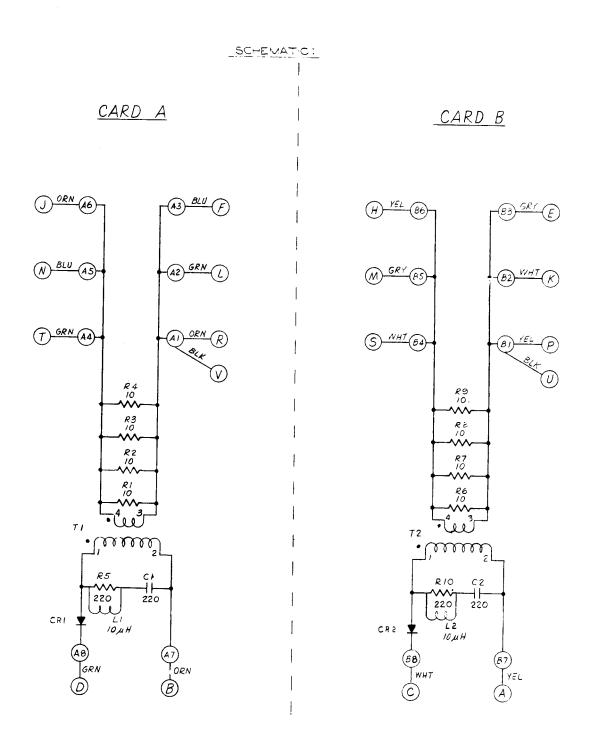

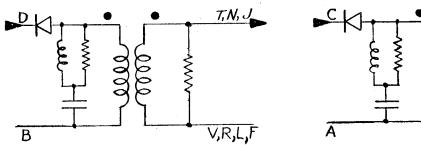

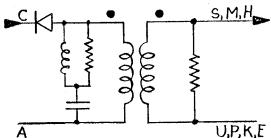

| Fig. 79          |                 |               | 131  |

| Fig. 80          | D-82342         | "A" reduction | 132  |

| Fig. 81          |                 |               | 133  |

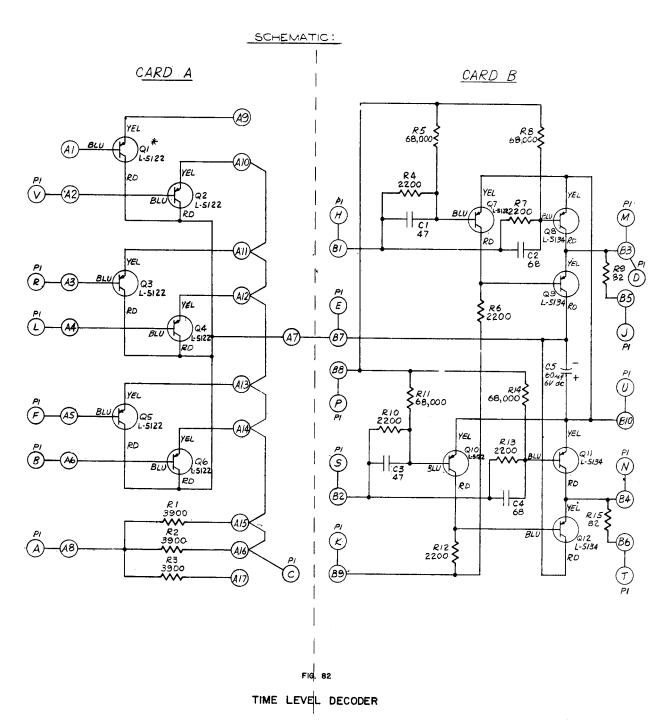

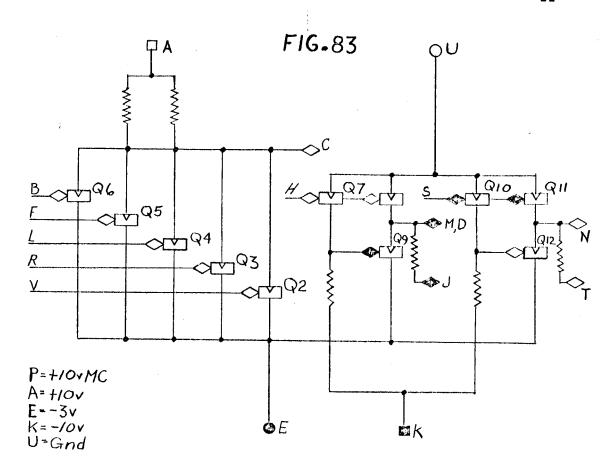

| Fig. 82          | <b>D-</b> 82908 | 86 99         | 134  |

| Fig. 83          |                 |               | 135  |

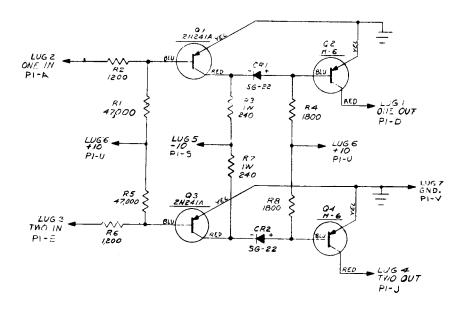

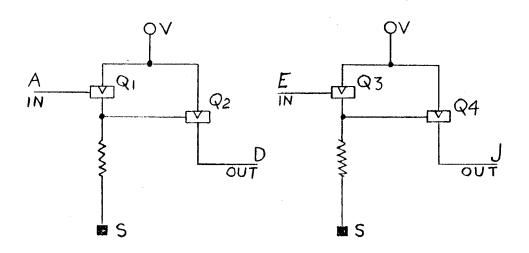

| Fig. 84          | <b>D-</b> 84655 | 88 89         | 136  |

| Fig. 85          |                 |               | 137  |

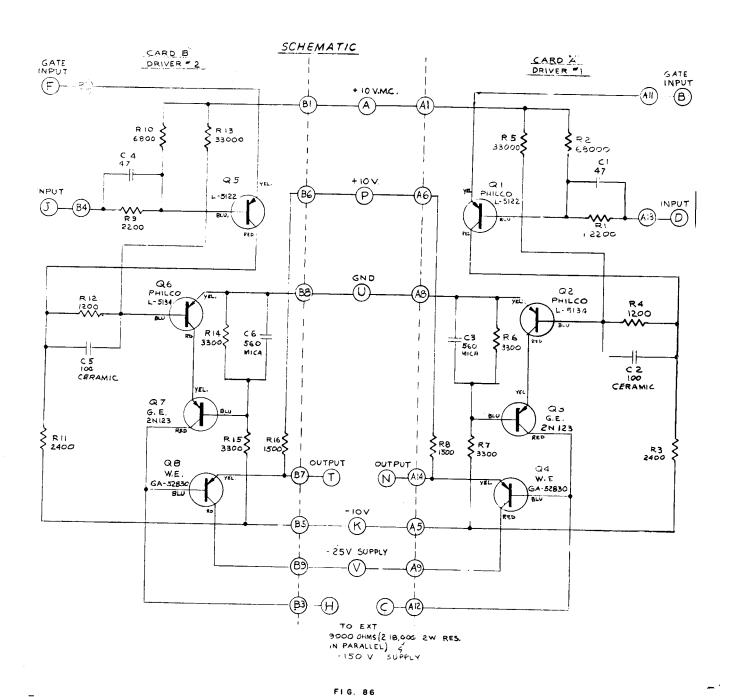

| Fig. 86          | <b>D-</b> 82581 | BI by .       | 138  |

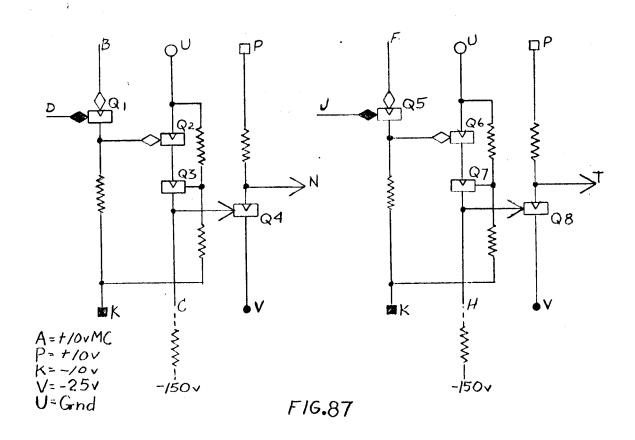

| Fig. 87          |                 |               | 139  |

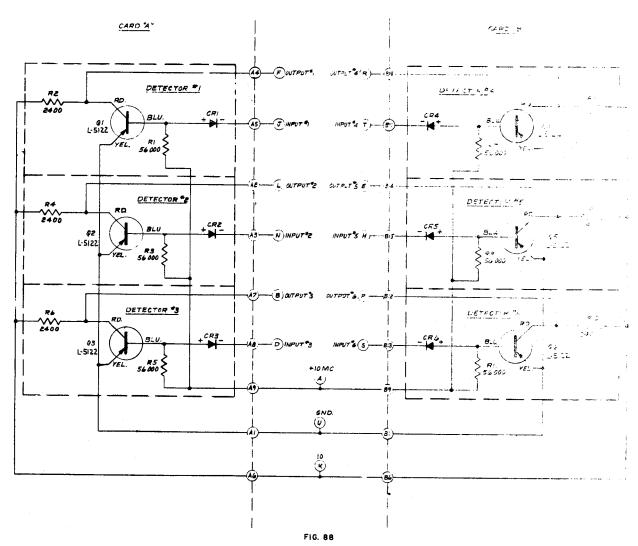

| Fig. 88          | <b>D-82557</b>  | 99 99         | 140  |

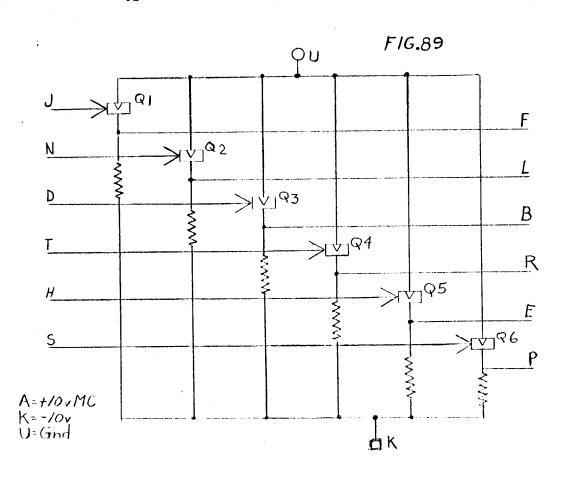

| Fig. 89          |                 |               | 141  |

| <b>Fig.</b> 90   | D-82691         | 69 69         | 142  |

| Fig. 91          |                 |               | 143  |

| <b>Fig</b> . 92  | <b>D-</b> 84761 | n n           | 144  |

| <b>Fig</b> . 93  |                 |               | 145  |

| Fig. 94          | <b>D-</b> 85686 | 98 69         | 146  |

| <b>Fig.</b> 95   |                 |               | 147  |

| <b>Fig</b> . 96  | <b>p</b> -85545 | 69 69         | 148  |

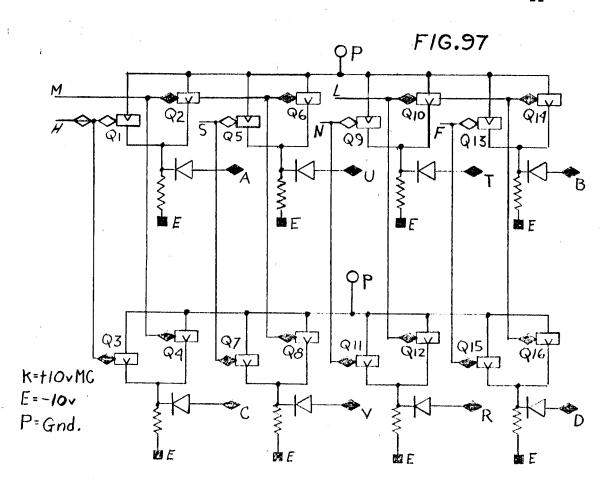

| Fig. 97          |                 |               | 149  |

| <b>Fig.</b> 98   | <b>p-</b> 85386 | 99 99         | 150  |

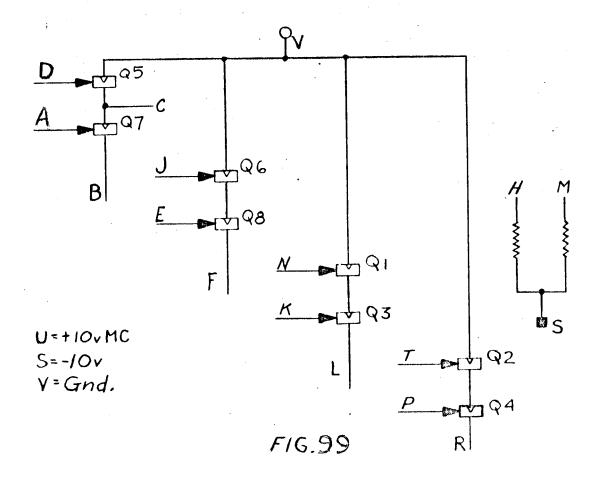

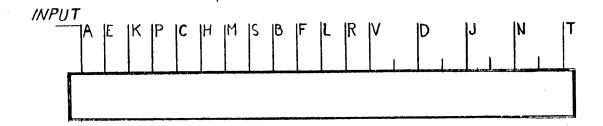

| Fig. 99          |                 |               | 151  |

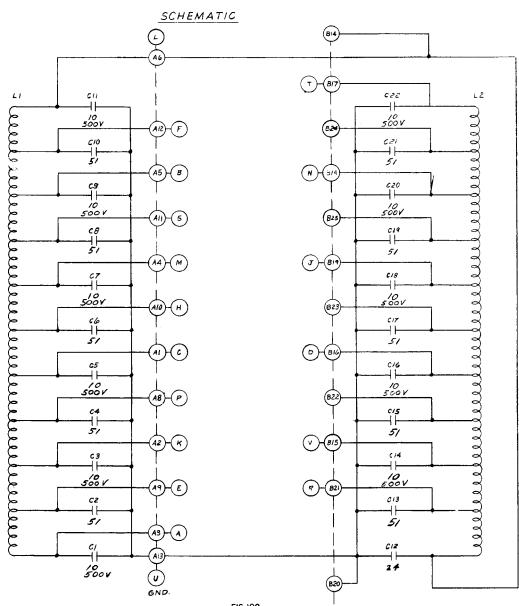

| <b>Fig</b> . 100 | <b>D-</b> 84995 | 98 98         | 152  |

| FIGURE NO. | DRAWING         | NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PAGE |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 101   | *               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 153  |

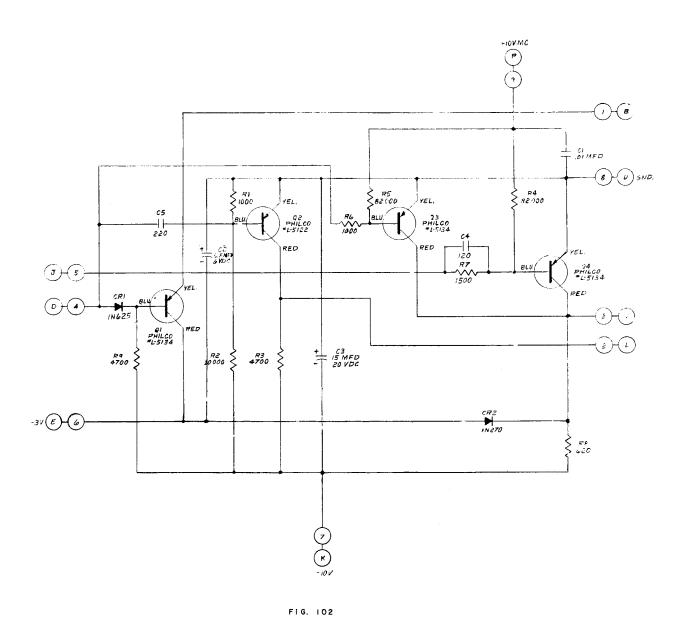

| Fig. 102   | <b>p-</b> 80513 | "A" reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 154  |

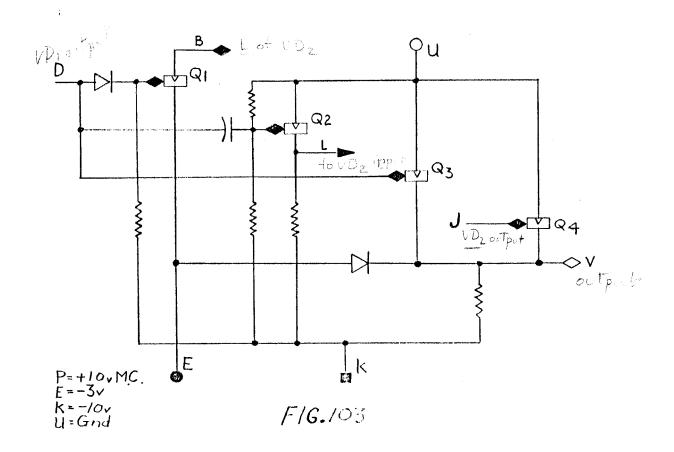

| Fig. 103   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 155  |

| Fig. 104   | <b>D-80700</b>  | es es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 156  |

| Fig. 105   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 157  |

| Fig. 106   | <b>D-</b> 85673 | 9.0 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 158  |

| Fig. 107   | •               | e de la companya de l | 159  |

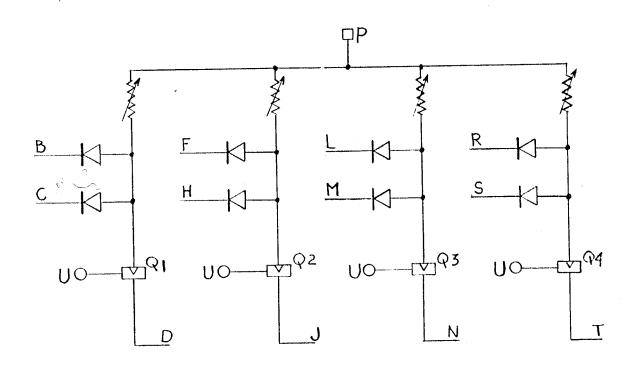

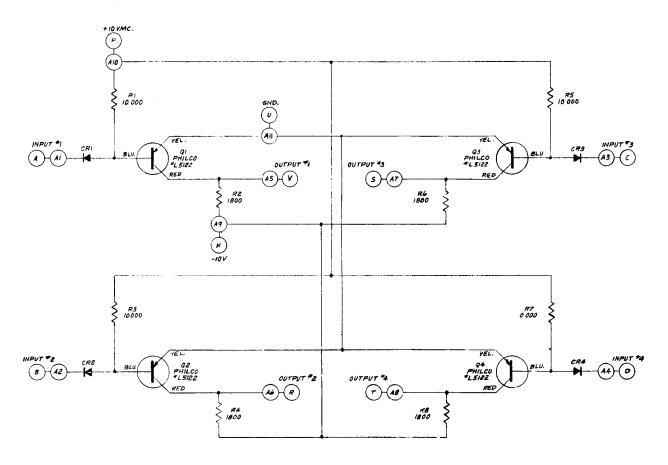

| Fig. 108   | <b>D-</b> 85744 | ff ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 160  |

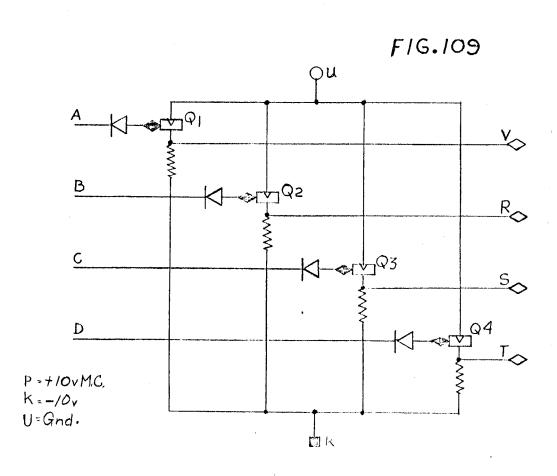

| Fig. 109   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 161  |

| Fig. 110   | <b>D-</b> 87685 | . # ***                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 162  |

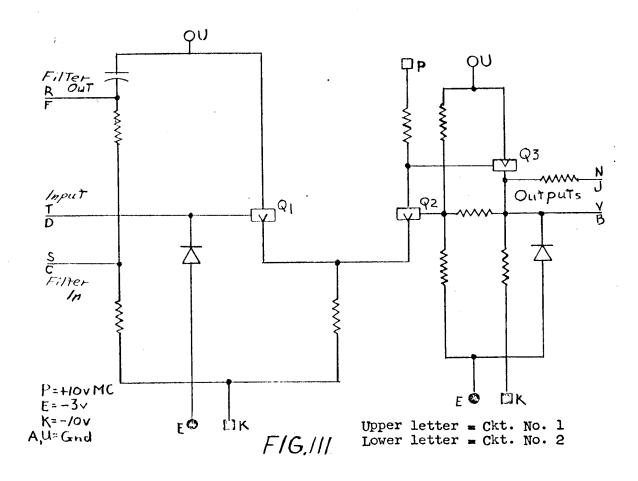

| Fig. 111   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 163  |

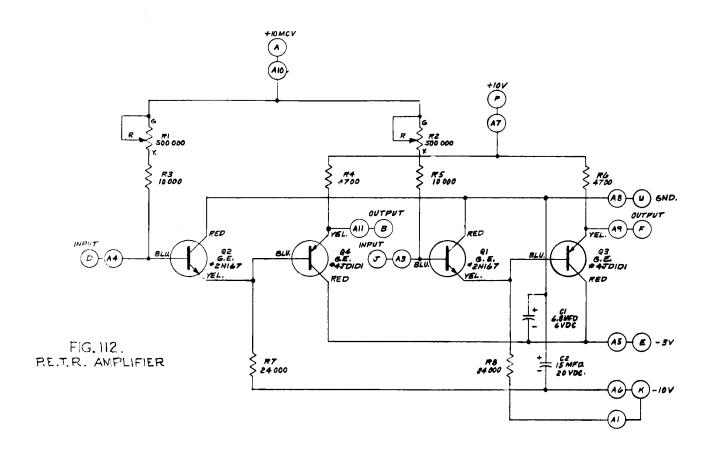

| Fig. 112   | <b>p-</b> 80515 | 99 '89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 164  |

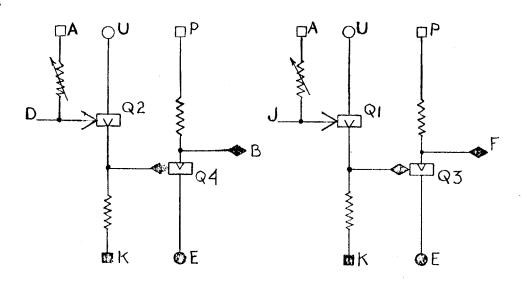

| Fig. 113   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 165  |

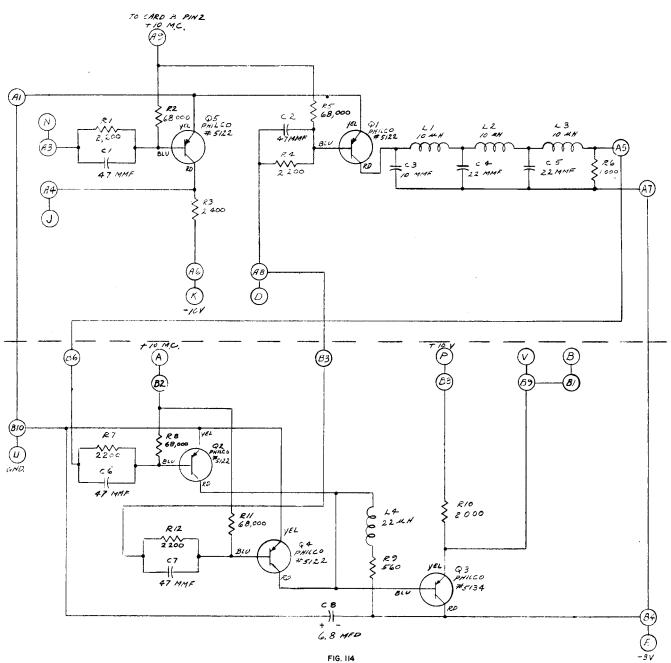

| Fig. 114   | <b>D-</b> 80514 | H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 166  |

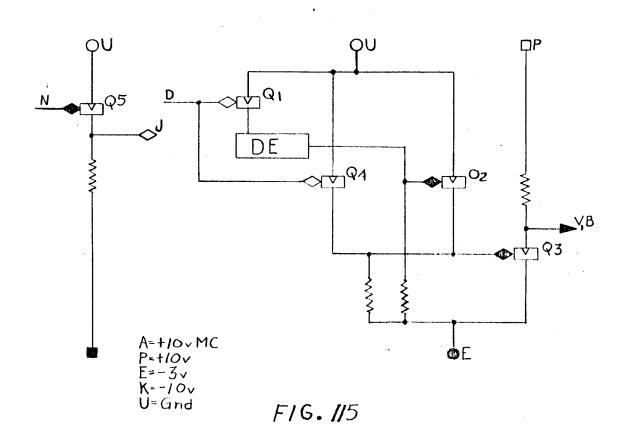

| Fig. 115   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 167  |

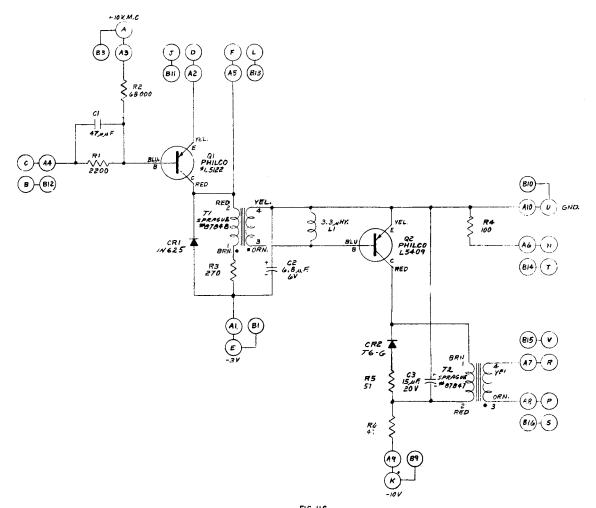

| Fig. 116   | <b>D-</b> 85748 | 11 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 168  |

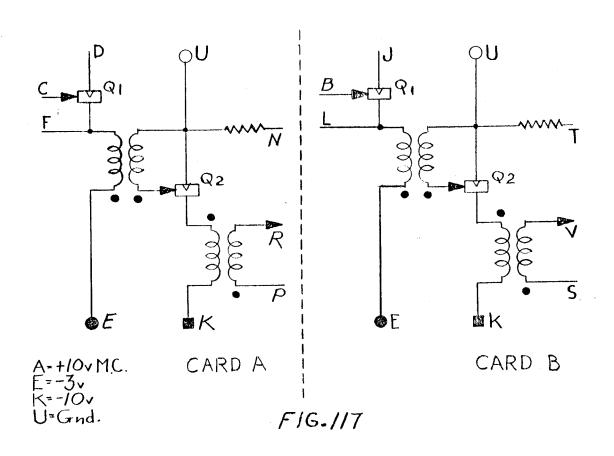

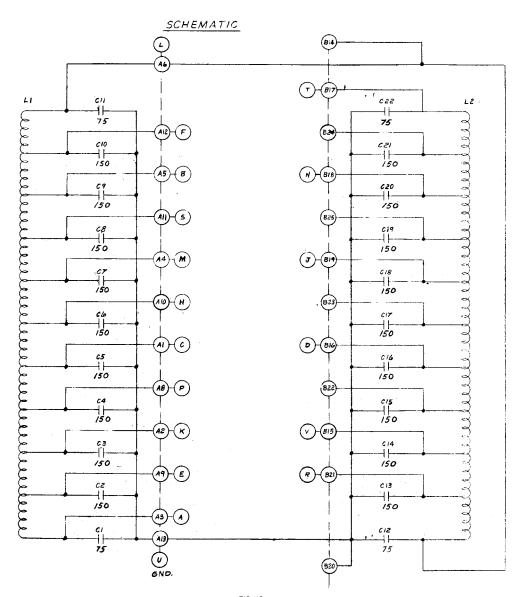

| Fig. 117   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 169  |

| Fig. 118   | <b>p-</b> 85568 | 91 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 170  |

| Fig. 119   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 171  |

| Fig. 120   | <b>p-</b> 85746 | 11 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 172  |

| Fig. 121   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 173  |

| Fig. 122   | <b>D-</b> 85745 | 91 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 174  |

# 6**p-**2631

| FIGURE NO.      | DRAWING NO.           | PAGE |

|-----------------|-----------------------|------|

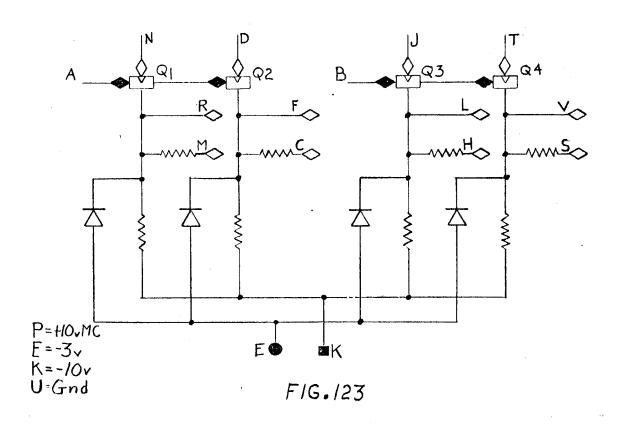

| Fig. 123        |                       | 175  |

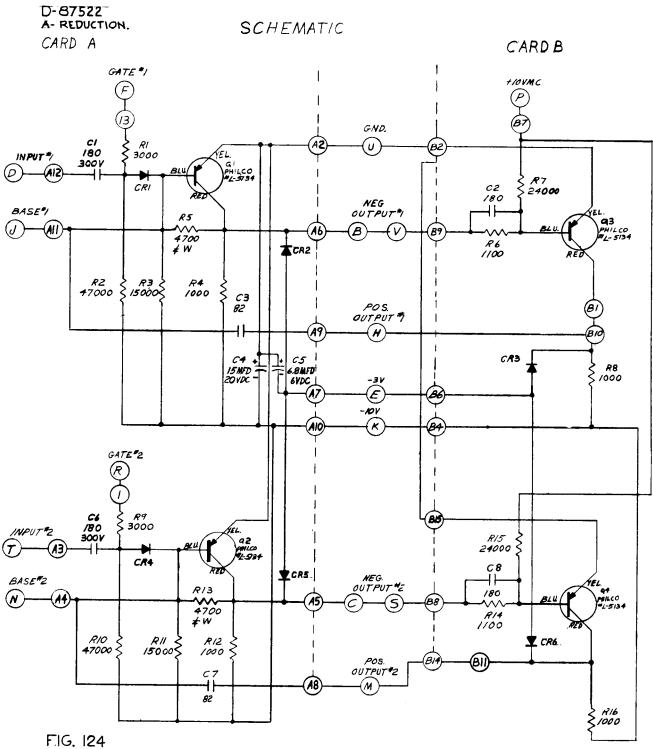

| Fig. 124        | D-87522 "A" reduction | 176  |

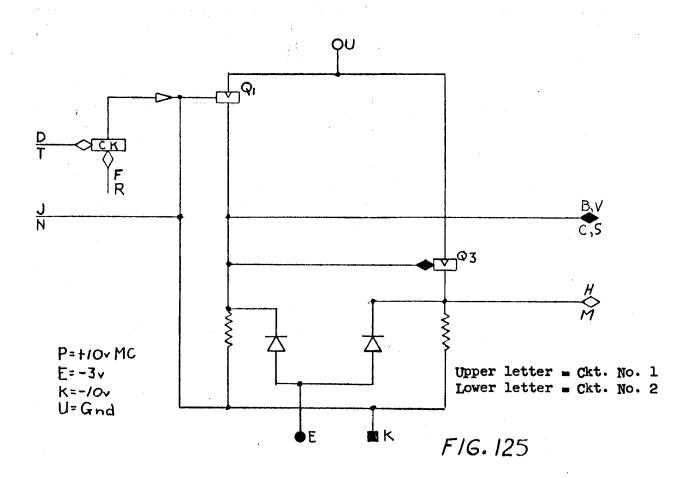

| Fig. 125        |                       | 177  |

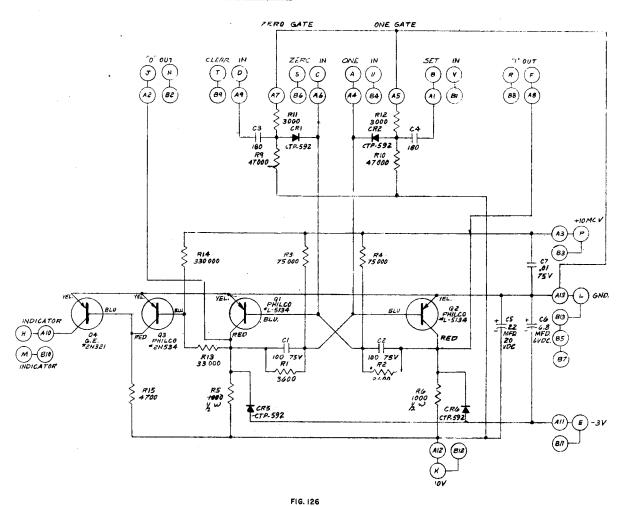

| Fig. 126        | <b>p-</b> 85749 " "   | 178  |

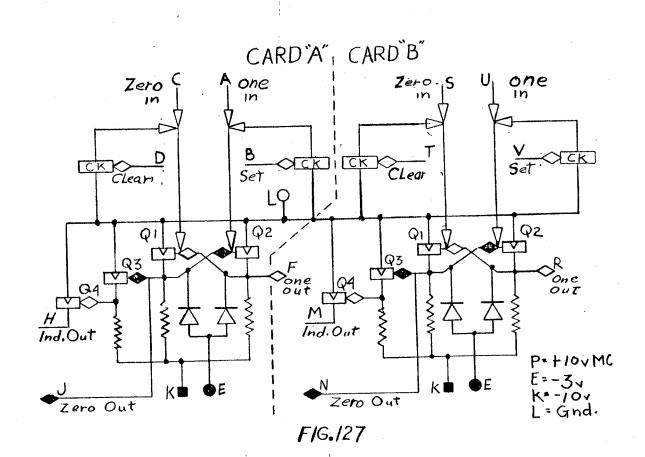

| Fig. 127        |                       | 179  |

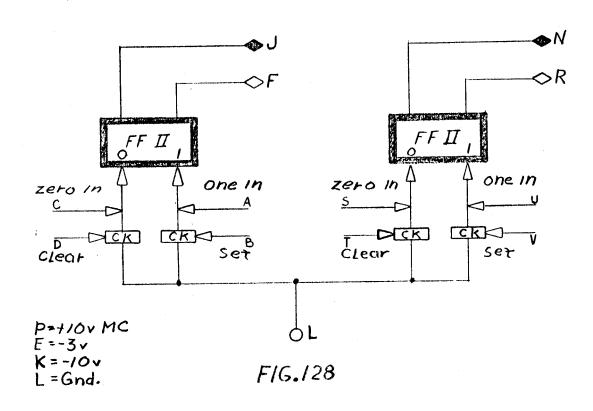

| Fig. 128        |                       | 180  |

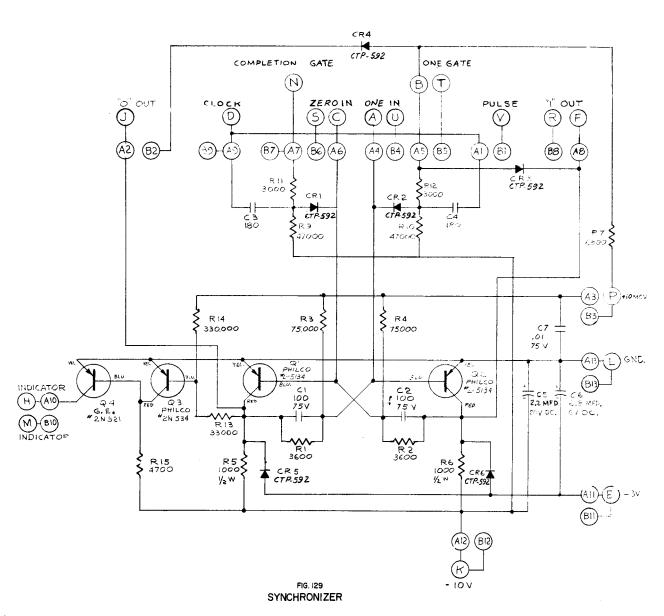

| Fig. 129        | <b>D-</b> 85888 " "   | 182  |

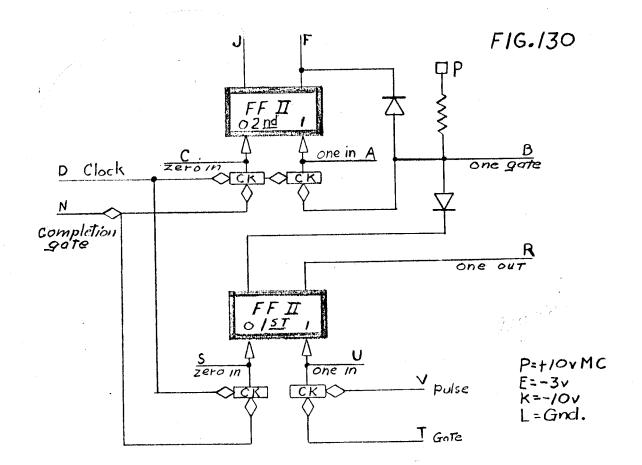

| Fig. 130        |                       | 183  |

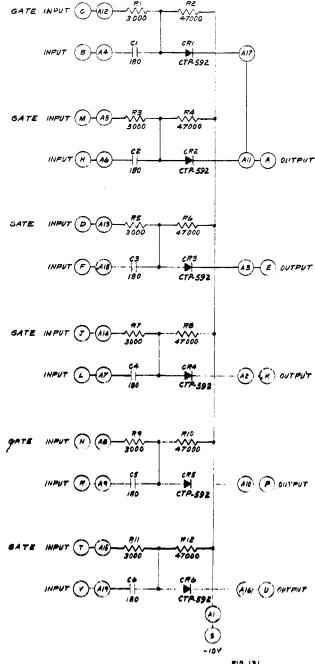

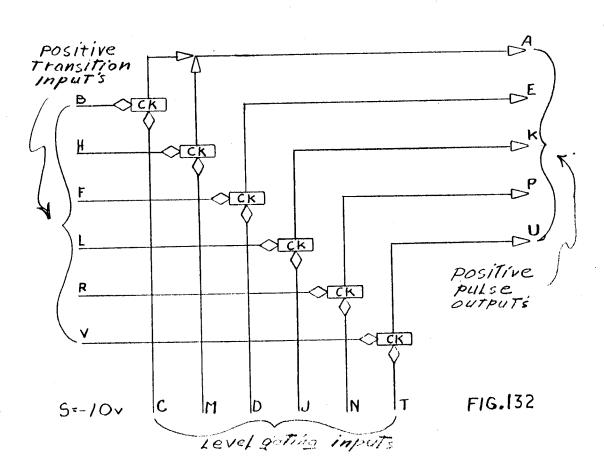

| Fig. 131        | D-85747 " "           | 184  |

| Fig. 132        |                       | 185  |

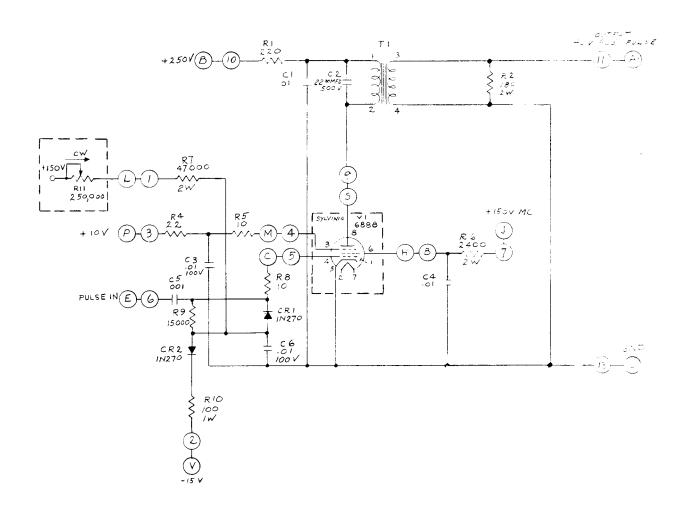

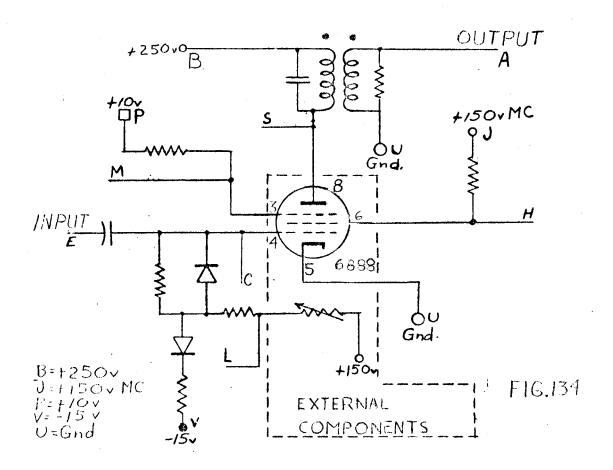

| Fig. 133        | <b>p-</b> 85751 " "   | 186  |

| Fig. 134        |                       | 187  |

| Fig. 135        | p-86317 " "           | 188  |

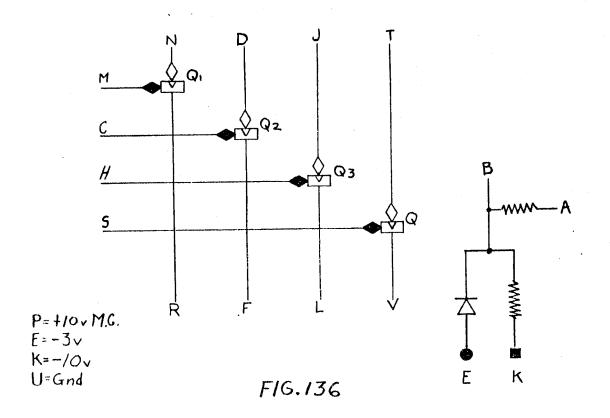

| <b>Fig.</b> 136 |                       | 189  |

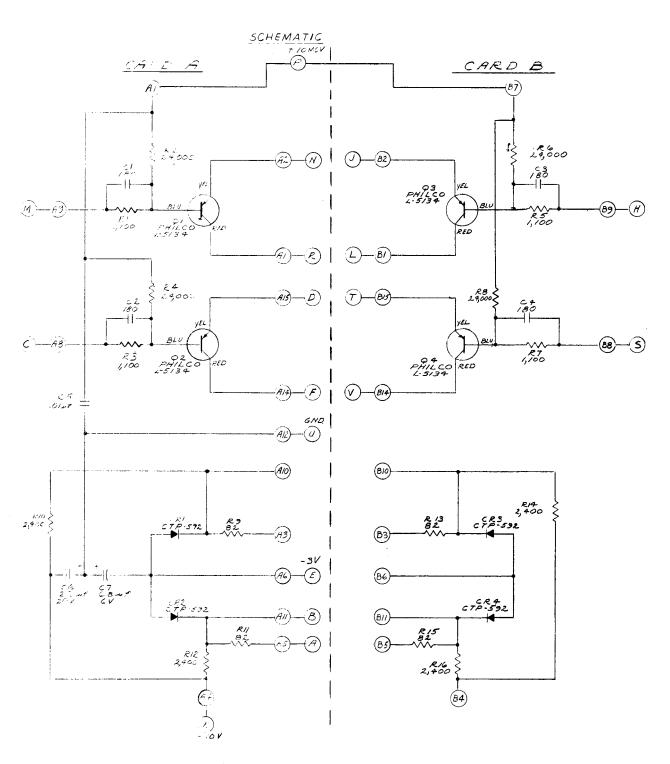

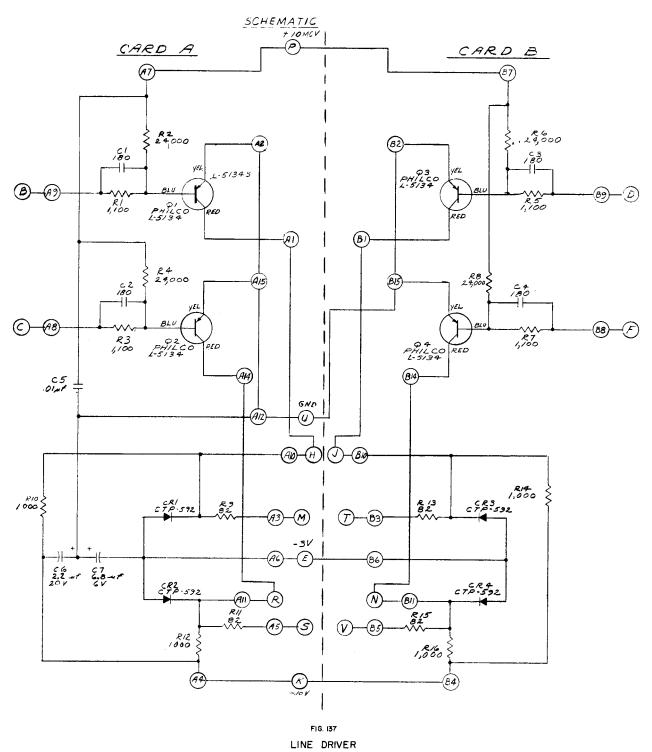

| Fig. 137        | D-86893 " "           | 190  |

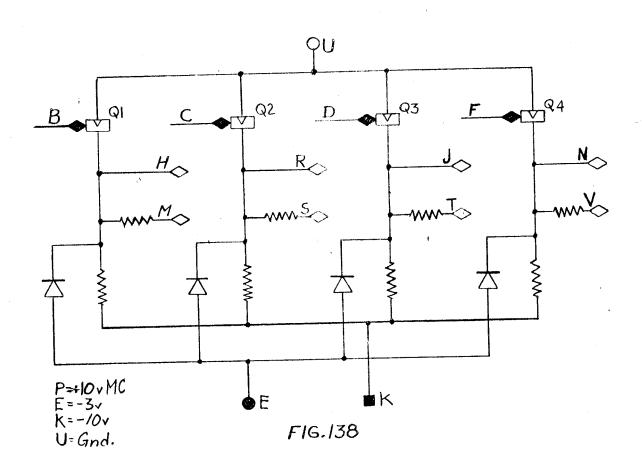

| Fig. 138        |                       | 191  |

| Fig. 139        | <b>D-</b> 84996 * "   | 192  |

| Fig. 140        |                       | 193  |

| Fig. 141        | <b>p</b> -87007 " "   | 194  |

| Fig. 142        |                       | 195  |

| Fig. 143        | <b>p</b> -87655 " "   | 196  |

#### PART I

#### INTRODUCTION

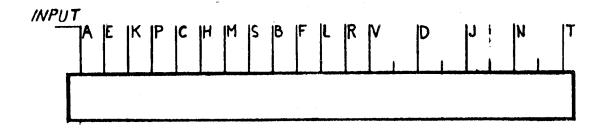

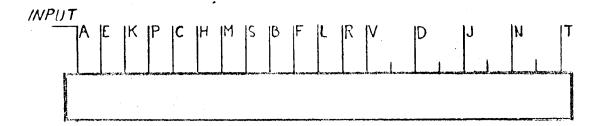

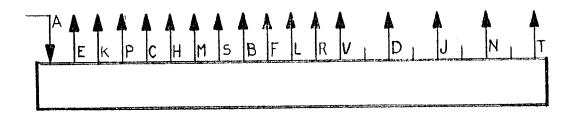

This bandbook is a discussion of the transistor circuitry used in the Lincoln TX-2 computer. The circuitry itself, the operation, and the use of all of the TX-2 plug-in units are explained. These units include all those used in the central machine, index memory, display system, toggle switch storage system, input-output units, and control. Part I describes the general methods by which transistor circuitry is used to implement the logic of the computer.

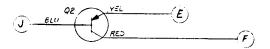

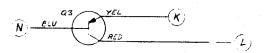

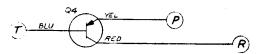

Part II gives a detailed description of each of the plug-in units used in TX-2. Each plug-in unit is assigned a serial number, which is mentioned in the text where the unit is discussed. This number is indicated by the color code on the handle of the unit itself (the colors are read from outside to inside).

Part III, the reference manual, lists the serial numbers of each of the units in order. Each left-hand page carries a circuit diagram of the unit; on the facing page is a block schematic diagram and a few salient facts about the unit. The user will find it advantageous to refer to the reference manual in connection with his study of the circuit discussed.

In order to avoid needless duplication, numerous references are made in the text of this handbook to M-notes issued by Division 6, which contain information pertinent to the TX-2 circuitry. Of special importance is 6M-4968, "The Lincoln TX-2 Computer," by W.A. Clark et al, issued April 1st, 1957. It contains a logic outline of the computer, a discussion of the input-output system, a discussion of the memories and memory circuitry, and a general outline of the central computer circuitry. It is recommended that 6M-4968 be read in conjunction with this handbook, although it must be remembered that the M-note was written before the actual construction of the machine, and thus there are many details which have been changed.

6p-2631 2.

At the end of this handbook is included a list of M-notes pertaining to TX-O (a small general purpose transistor computer constructed as a precursor to TX-2), TX-2 itself, and surface barrier transistors in general. The specifications of the various types of surface barrier transistors used in TX-2 are also given.

TX-2 is an experimental research machine; frequent additions and modifications will be made as more knowledge is gained from the construction and operation of the computer. These changes will be incorporated in new pages punched for easy insertion in this handbook.

#### GENERAL DISCUSSION

In TX-2 there are two logic levels of information: ground and -3 volts. Timing pulses are negative, with an amplitude of from 2.5 to 3 volts and a width of from 80 to 100 musec. The principal supply voltages used for the surface barrier transistor (SBT) circuitry are -3, -10, and +10 volts. The +10 volts on some of the lines can be varied from 0 to +20 volts for marginal checking. In addition there is a -30 volt supply used for input-output devices, driving relays, etc.

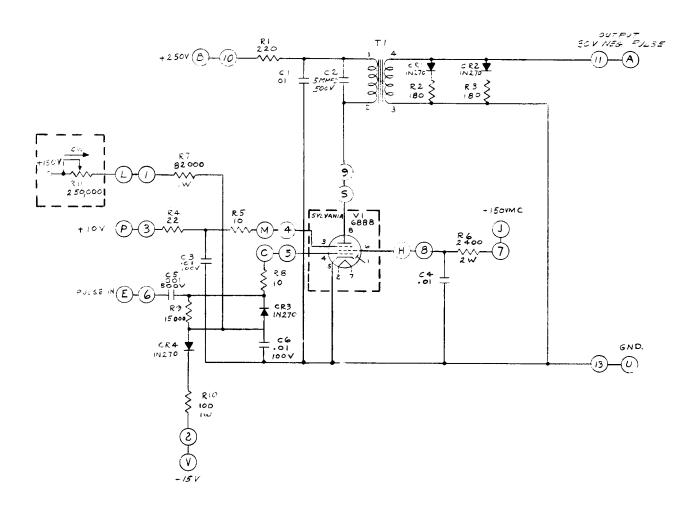

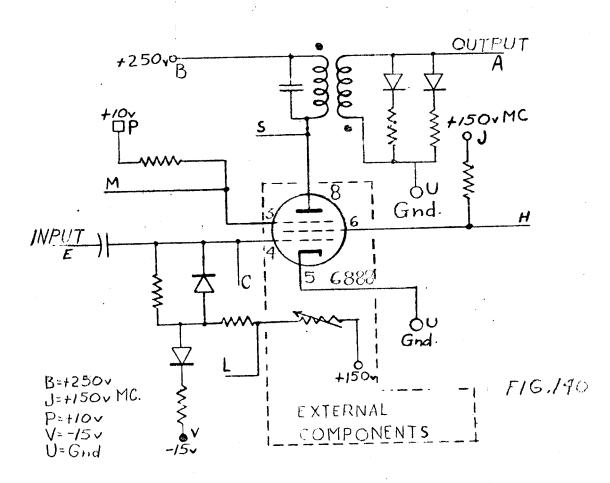

The L-5122 and L-5134 SBT's are used for high speed work. AND and OR gates are formed from inverter or emitter follower combinations. Timing pulses, generated by vacuum tube circuits, are stepped down by pulse transformers to 3 volt, O.1 µsec negative pulses which are used in the computer. These pulses are gated by the register driver circuit. The cascode configuration is used as a power amplifier to obtain fast rise and fall times. There is a high speed flip-flop capable of 5 mcps operation, and a much simpler dual flip-flop for low speed work to 800 kcps.

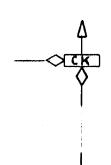

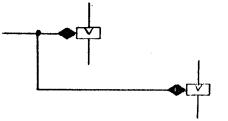

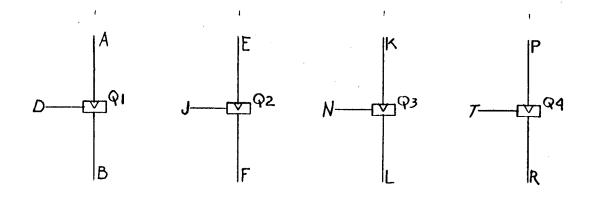

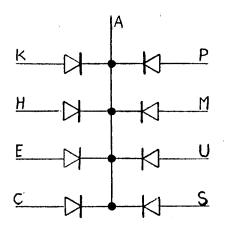

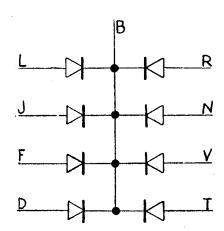

A standard set of symbols shown in Figure 1 is used for all TX-2 block schematic drawings, and for all drawings in this handbook. Figure 2 is a system schematic drawing of TX-2, showing the principal registers and information paths.

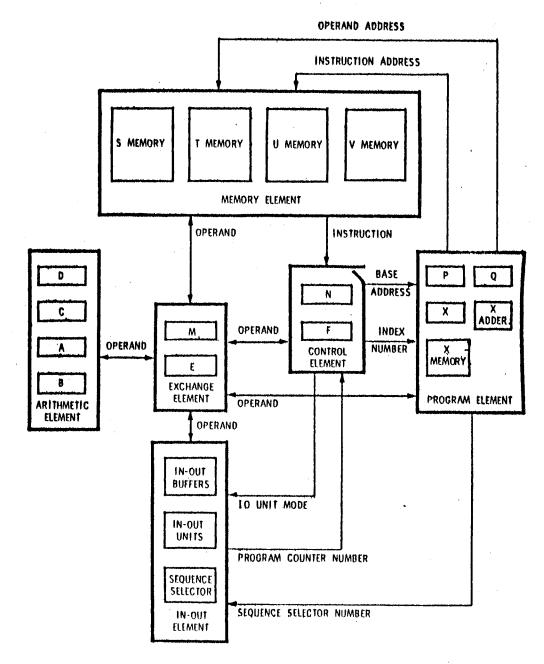

#### PACKAGING

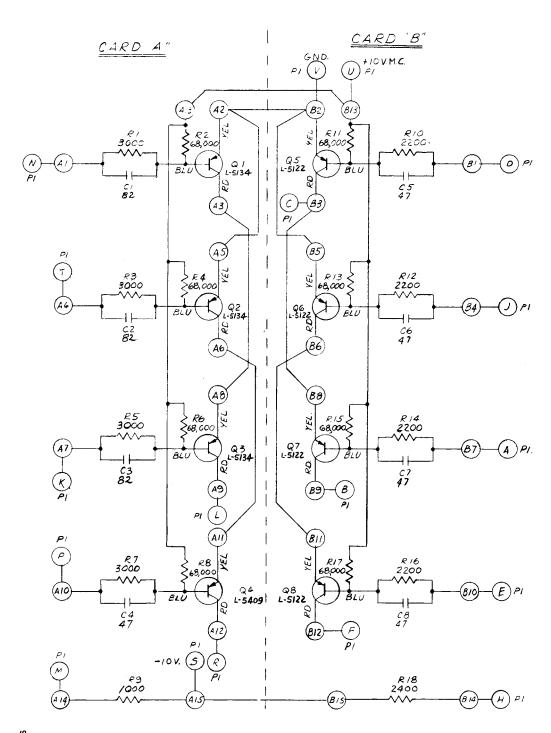

All TX-2 circuitry is packaged in plug-in units each measuring approximately 1 by 2 by 6 inches long, and containing from 4 to 14 transistors and associated resistors and condensers. (For the central computer there is an average of 8 transistors per PTU.) In general there are two etched wired cards per plug-in unit; these are connected by wires to an 18-pin plug and mounted in a steel frame to prevent flexing. The components are mounted on the etched cards by hand-soldering either to solid turret lugs or small eyelets. Pictures of two typical plug-in units (one using turret lugs and the other using eyelets) are shown in Figure 3.

### TRANSISTORS

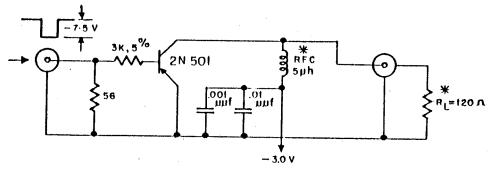

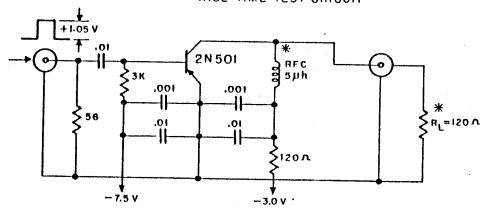

The high speed logic circuitry for TX-2 is based on the use of Philos surface barrier transistors for which the specifications are given in an appendix to this handbook. Also in the appendix is a transistor nomenclature reference which lists the transistor manufacturer and the experimental type designations plus the ETA or MTL designations which may have since been assigned. With certain exceptions that will be noted later, all inverters and emitter followers are L-5122 (2N240) transistors. Micro-alloy L-5134 (2N393) transistors are used where a high current gain at relatively high current levels (10 - 70 ma) is required. Thus the L-5134 is used as the power output stage of the high speed flip-flop, in the inverting cascode and cable driver, as the pulse gating transistor in the register driver, and in some input-output circuitry. There are a few places in the machine where a very high frequency, high current transistor is needed, and here the Philco microalloy diffused-base transistor 2N501 (previously known as the L-5409) is used. For a detailed discussion of the L-5122 parameters, refer to 6M-4955 by D. J. Eckl, for some notes on the L-5134 transistor refer to 6M-5193 by J. W. Langford, and for some notes on the 2N501 refer to 6M-5856 by J. W. Langford.

## TX-2 BLOCK SYMBOLS

emiller base-PNP Transistor collector base -NPN Transistor emitter Diode (Ge or Si) Zener Diode Double Anode Diode -3 Volt Level Ground Level Non Standard Level Negative 0.1 µsec. Pulse Positive Pulse: Input to Flip-Flop +30 Volt Supply +10 Volt Supply Ground -3 Volt Supply -10 Volt Supply -30 Volt Supply

Figure 1.

1-87034 (Sheet 2 of 2)

#### TX-2 BLOCK SYMBOLS (Cont.)

Non Standard Positive Voltage Supply

Non Standard Negative Voltage Supply

Dual Flip-Flop Mod II (1 FF)

Capacitor-Diode Gate

High Speed Flip-Flop

is equivalent to:

FIG. 2

TX-2 System Schematic

FIG.

#### LOGIC

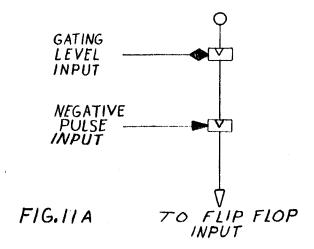

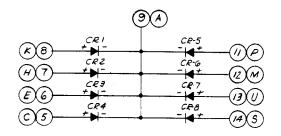

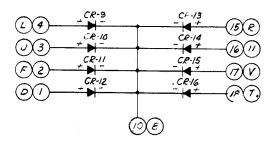

All the high speed logic for TX-2 is performed with transistors by what might be termed "level logic". The AND and OR functions are obtained by mixing and gating levels; never is one pulse used to gate another. The levels are generated by flip-flops, which are set, cleared, or complemented by pulses arriving at a basic synchronous clock rate. The levels are transmitted throughout the computer by means of open wire or twisted pair wire depending upon the length of line. The necessary logic operations are performed with these levels which may be used to gate pulses on or off through register driver circuits. The pulses coming out of register driver circuits are sent directly to flip-flops. They may be gated by other levels at the input to each flip-flop, and, by means of transistors a number of pulses may be mixed at this point. In the TX-2 system pulses can be gated only twice; once at the register driver and once at the flip-flop itself. Therefore when many consecutive stages of logic are to be performed, they must make use of levels rather than pulses.

Logic levels at ground and -3 volt potentials are used to convey information. In TX-2 a flip-flop is said to be set to the ONE state when the ONE output is at -3 volts. Therefore if one wishes a -3 volt level to be the result of setting a flip-flop, one connects the output wire to the ONE output; conversely, a ground level results if this wire is connected to the ZERO output.

The AND and OR gates that perform level logic in TX-2 are formed from either emitter followers in parallel or inverters in series and/or parallel. The AND gate for ground level in, ground level out, is formed by connecting emitter followers in parallel as shown in Figure 4A. An inverting AND gate for ground level in, -3 level out, is formed by connecting inverters in parallel as shown in Figure 4B. An inverting OR gate for ground level in, -3 level out, is formed by connecting inverters in series as shown in Figure 4C. The polarity of the input signal determines whether a given gate is AND or OR. Thus, in order to specify the logic function of any particular circuit configuration, it is necessary to specify the polarity of either the input or the output.

Only two L-5122 inverters can be connected in series for two reasons:

1) the 0.15 volt drop across one saturated transistor is multiplied by the number (n) of inverters in series and the output then becomes 0.15n volts below the required ground level; and 2) the collector current  $I_c$  of the transistor  $Q_1$  nearest ground is equal to  $\frac{E_s}{R_L} + \frac{I_b}{2} + \frac{I_b}{2}$

etc. where E<sub>s</sub> is the supply voltage, R<sub>L</sub> is the load resistance, and I<sub>b2</sub>, I<sub>b</sub> etc. are the base currents of all transistors between Q<sub>1</sub> and the supply voltage. Thus the transistor nearest ground will tend to come out of saturation if there are many transistors below it. The number of inverters that may be placed in parallel is limited by the delay which can be tolerated. The fall transition time (measured at the 10% points from the point at which the input starts up from -3 volts to the point at which the output returns to -3 volts) is shown as a function of the number of inverters in parallel in Figure 5. (The input rise time is about 20 mµsec.)

When emitter followers are placed in parallel to form an AND gate, the transition delay time is considerably less than that of inverters. The rise transition time, as a function of the number of emitter followers in parallel, is shown in Figure 6. The rise transition time is measured at the 10% point near the ground level.

TRANSITION TIMES VS NUMBER OF TRANSISTORS IN PARALLEL

## PART II - CIRCUIT DETAILS

#### CENTRAL COMPUTER

Counting Circuits for TX-2 logic are formed by flip-flops and inverters as shown by the block diagram, Figure 7. Each count pulse is separated by 0.4  $\mu$ sec to compensate for the delay imposed by the flip-flop and the inverters.

If a faster counting rate is required, emitter follower circuits (Figure 8) are used which need only 0.2  $\mu sec$  between each count pulse. These circuits, however, use more transistors, and so complicate counters containing a large number of digits.

STAGE COUNTER USING INVERTERS Ŋ

Inverter In the circuit shown in Figure 9A the values of load resistance  $(R_1)$ , input resistance  $(R_2)$ , and positive bias resistance  $(R_3)$  are chosen to give maximum tolerance to signal variations, noise voltages, and transistor parameter variations consistent with the necessary driving capabilities. The result is a circuit for which the maximum output current at -3 volts is 2.9 ma; minimum input current is 1.0 ma (1.2 ma at -3 volts); positive bias current from +10 volt is .15 ma, which gives a positive bias of .31 volts above ground. All of the inverters work from a -10 volt supply.

The actual voltage at the collector, however, is never allowed to exceed -5 volts; it is clamped to -3 by an emitter follower, or by a voltage divider to ground formed by the input resistance to an inverter following it. However if the inverter is accidentally unloaded it will not be damaged. The minimum punch-through voltage (emitter-to-collector voltage) of the L-5122 and L-5134 is 6 volts. If the transistor were to punch through at this voltage, the power dissipation would be only 10 mw -- not enough to damage the transistor. The value of the capacitor  $(C_1)$  is chosen so that with a 3 volt input signal, the capacitor will store a charge at least as large as that contributed by the hole storage of a transistor with the maximum allowable hole storage coefficient. Thus sufficient overdrive is provided for minimum rise and fall transition times. A single inverter provides enough current to drive either two other inverters, three emitter followers, or one inverter and one emitter follower. The d-c transfer characteristic of the TX-2 inverter circuit is shown in Figure 10.

The following plug-in units consist of L-5122 inverters such as are described above:

```

Inverter P-6 (No. 02)

Inverter S-8 (No. 03)

Inverter P-5 (No. 04)

Inverter S-6 (No. 05)

Inverter P-8 (No. 24)

Inverter S-8R (No. 32)

Inverter P-10 (No. 33) (Two transistors nearest ground are L-5134)

Parity Circuit (No. 34) (Also contains 2 emitter followers)

Inverter S-8RA (No. 46) (Contains 3 L-5134 and 1 2N501)

```

## INVERTER

# EMITTER FOLLOWER

CHARACTERISTIC

TX-2

INVFRTFR

1-8496

TRANSFER

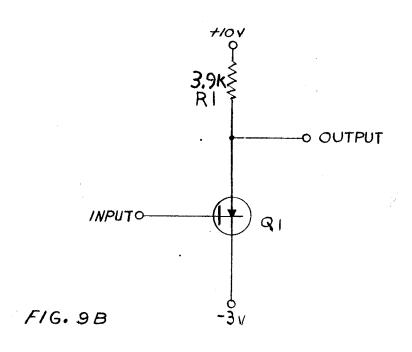

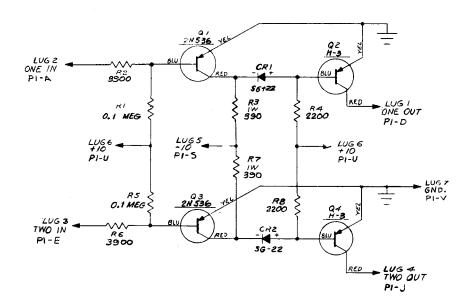

The circuit shown in Figure 9B is used as a logic Emitter Follower element and as a current amplifier. An emitter follower may be driven from an inverter, in which case it is kept in saturation when turned on since its base is returned to -10 volts through the load resistance of the previous inverter. An emitter follower may also be driven from a cascode circuit or from another emitter follower. In these cases, the base is returned to -3 volts through the very low resistance of a saturated transistor. One emitter follower may drive another only if the first is driven by an inverter, and is thus saturated from -10 volts. Usually the emitter is returned to +10 volts through a 3.9K resistance to limit the total emitter current to 10 ma. Thus the maximum output current is 6.7 ma. If a larger reverse current from +10 volts is needed (as when driving several inverter bases as fast as possible, or when driving the emitter of a pulsed transistor) the load resistance may be decreased to 2K (or two 3.9K resistors in parallel) provided there are at least two emitter followers in parallel in the same unit to share the dissipation in the "off" condition. In this case the output current is limited to 3.5 ma. Therefore one emitter follower will drive a maximum of 3 inverter bases if sufficient time is available or 5 emitter follower bases if the current limitation is observed.

The following plug-in units consist of L-5122 emitter followers such as are described above:

```

Emitter Follower 8 (No. 06)

Emitter Follower 4 (No. 07)

Address Decoder (No. 13) (Contains 12 emitter followers and 4 sets of output diodes.)

Emitter Follower 9 (No. 35)

```

Time Level Decoder (No. 37) (Contains 5 emitter followers and 2 cascode circuits.)

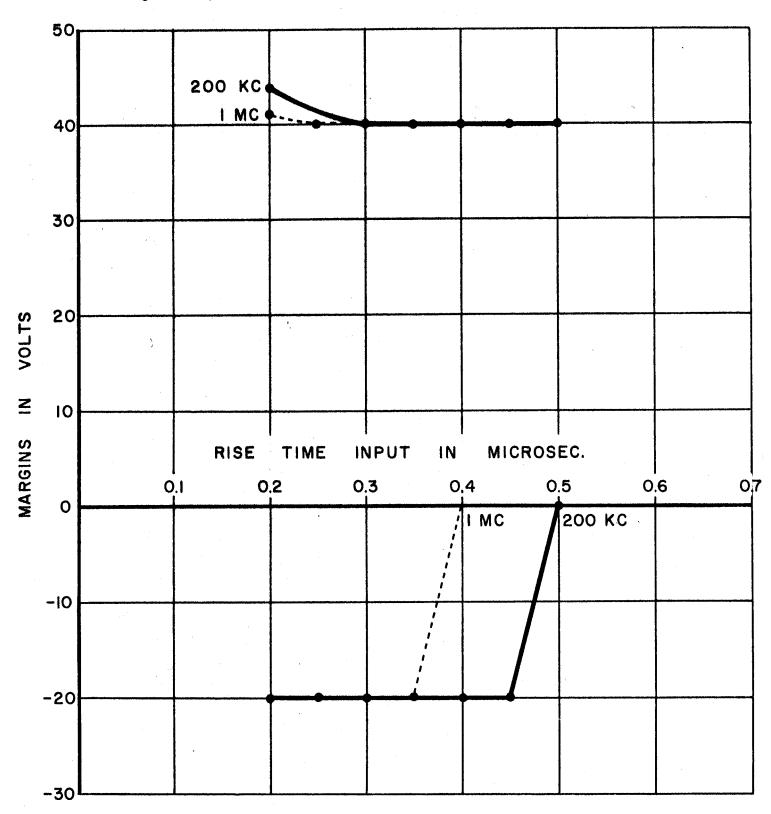

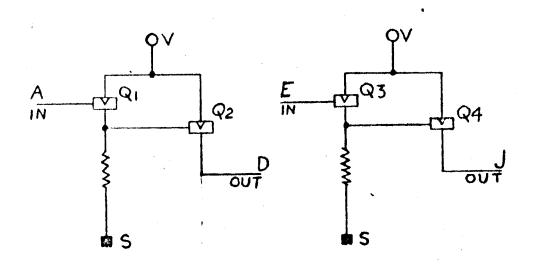

Cascode and Cable Driver (No. 08) The circuit shown in Figure 38 (in Reference Manual) is used in TX-2 as a power amplifier to provide fast rise and fall times and to supply a large amount of current in both the ground and -3 volt states. Consequently it is used as the output stage of the high speed flip-flop, as a power amplifier for driving a large number of bases, and as a cable driver. The input signal is applied simultaneously to the bases of the inverters,  $Q_1$  and  $Q_2$ . The output of the inverter  $\mathbf{Q}_1$  drives the base of  $\mathbf{Q}_3$ . Therefore the inputs to  $Q_{\gamma}$  and  $Q_{\gamma}$  are always opposite in phase so that in the steady state only one transistor is conducting.  $Q_3$  acts as an emitter follower which provides the driving current in the -3 state, and pulls the output quickly down to -3 volts. Q, acts as an inverter which provides the driving current in the ground state, and pulls the output quickly up to ground. Thus, the circuit exploits the fast fall time of the emitter follower, the fast rise time of the inverter, and makes the total current available to the load since none is required in load resistances.