| APPLICATION |         |                 | REVISIONS                 |          |          |  |  |  |  |

|-------------|---------|-----------------|---------------------------|----------|----------|--|--|--|--|

| NEXT ASSY   | USED ON | LTR DESCRIPTION |                           | DATE     | APPROVED |  |  |  |  |

|             | -       | 1               | PRELIMINARY               | 3/14/79  | Shin .   |  |  |  |  |

| •           |         | 2               | PRELIMINARY REVISED       | 3/29/79  | Sohr     |  |  |  |  |

|             |         | A               | PRODUCTION RELEASE ENQ411 | 10/30/79 | Sphe     |  |  |  |  |

The information hereon is the property of MICROPOLIS CORP-ORATION. No portion of this data shall be released, disclosed, used, or duplicated for procurement or manufacturing purposes without specific written consent of MICROPOLIS.

| UNLESS OTHERWISE SPECIFIED:<br>DIMENSIONS ARE IN INCHES.<br>TOLERANCES ON:<br>FRAC- DECIMALS ANGLES | CONTRACT NO.        | MICROPΩLIS™                 |       |           |        |                |            |      |

|-----------------------------------------------------------------------------------------------------|---------------------|-----------------------------|-------|-----------|--------|----------------|------------|------|

| TIONS .XX .XXX ±<br>± ± ±                                                                           | DR BY SEL           | SPECIFICATION - 1220 SERIES |       |           |        |                |            |      |

| MATERIAL                                                                                            | CHK BY              |                             |       | RIGID DIS | SK DRI | VE SUBSYS      | TEMS       |      |

| FINISH                                                                                              | APPROV<br>SSL clude | VED BY<br>K. 3/14/79        |       | CODE IDEN | IT NO. | dwg no.<br>100 | 292        | REV. |

| DO NOT SCALE DRAWING                                                                                |                     |                             | SCALE |           |        |                | SHEET 1 OF | 40   |

| DIETERICH-POST CLEARPRINT 10                                                                        | 20-10               | · ·                         |       |           |        |                | · · ·      |      |

**APPLICATION**

REVISIONS

#### 1.0 INTRODUCTION

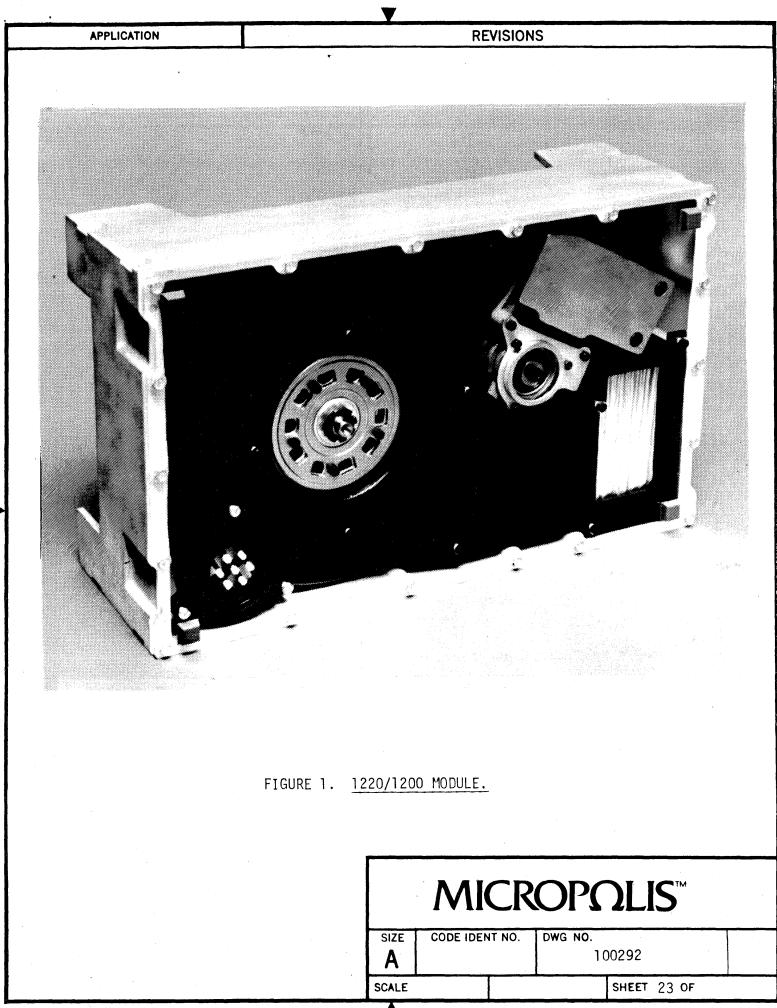

This specification describes the Micropolis Model 1220/1200 series of fixed disk systems. These products are intended for mini or microcomputer applications which require medium capacity fixed disk storage at low cost.

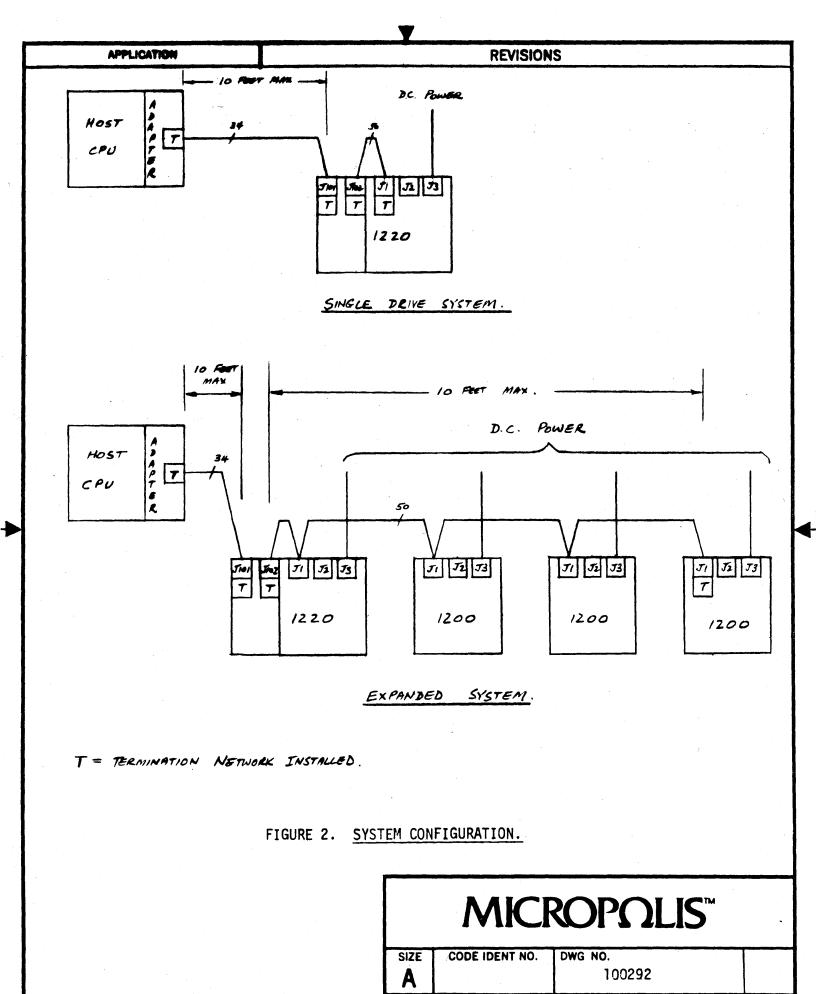

Model 1220 consists of a Micropolis 8" fixed disk drive with an integral controller board, and is the minimum system configuration. The 1220 fits within the outline of a Shugart 8" flexible disk drive and requires the same D.C. supply voltages. The controller provides full data transfer and control facilities in six standard sectoring arrangements and can be easily attached to the host computer through a simple bus-oriented interface.

Model 1200 is an add-on module similar to the 1220 except that no controller is provided. Up to three 1200's may be added to the 1220.

These modules are available in three configurations depending on the number of data surfaces in use and offer the following formatted storage capacities:

| DATA      | DATA                       |                                                     | 12                                                     |                                                                                                                                             |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                          | TED CAP                                                                                                                                                                                                                                                 | ACITY                                                                                                                                                                                                                                                                             | (M B                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|----------------------------|-----------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4         |                            |                                                     |                                                        |                                                                                                                                             |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PER DRIVE | FER SURFALE                |                                                     | 256                                                    |                                                                                                                                             |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                         | 100                                                                                                                                                                                                                                                                               | 056                                                                                                                                                                                                                                                                                                                           | States and s                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | and the second secon                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |                            | 120                                                 | 200                                                    | 208                                                                                                                                         | 320                                                                                                                                                                                                                 | 512                                                                                                                                                                                                                                      | 1024                                                                                                                                                                                                                                                    | 128                                                                                                                                                                                                                                                                               | 256                                                                                                                                                                                                                                                                                                                           | 268                                                                                                                                                                                                                                                                                                                                                     | 320                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 512                                                                                                                                                                                                                                                                                                                                                                                          | 1024                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1         | 580                        | 4.90                                                | 6.24                                                   | 1 6.2                                                                                                                                       | 2 6.68                                                                                                                                                                                                              | 3 7.1                                                                                                                                                                                                                                    | 3 7.13                                                                                                                                                                                                                                                  | 19,6                                                                                                                                                                                                                                                                              | 24.9                                                                                                                                                                                                                                                                                                                          | 24.9                                                                                                                                                                                                                                                                                                                                                    | 26.7                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28,5                                                                                                                                                                                                                                                                                                                                                                                         | 28.5                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3         | 580                        | 14.7                                                | 18.7                                                   | 18.7                                                                                                                                        | 20.0                                                                                                                                                                                                                | 21.4                                                                                                                                                                                                                                     | 21,.4                                                                                                                                                                                                                                                   | 58,8                                                                                                                                                                                                                                                                              | 74.8                                                                                                                                                                                                                                                                                                                          | 74.6                                                                                                                                                                                                                                                                                                                                                    | 80.2                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85.6                                                                                                                                                                                                                                                                                                                                                                                         | 85.6                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5         | 580                        | 24.5                                                | 31.2                                                   | 31.1                                                                                                                                        | 33.4                                                                                                                                                                                                                | 35.6                                                                                                                                                                                                                                     | 35.6                                                                                                                                                                                                                                                    | 98.0                                                                                                                                                                                                                                                                              | 125                                                                                                                                                                                                                                                                                                                           | 124                                                                                                                                                                                                                                                                                                                                                     | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 143                                                                                                                                                                                                                                                                                                                                                                                          | 143                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | SURFACES<br>PER DRIVE<br>1 | SURFACES<br>PER DRIVE PER SURFACE<br>1 580<br>3 580 | SURFACES<br>PER DRIVETRACKS<br>PER SURFACE158035803580 | SURFACES         TRACKS           PER DRIVE         PER SURFACE           1         580           3         580           14.7         18.7 | SURFACES         TRACKS         P           PER DRIVE         PER SURFACE         SEC           1         580         4.90         6.24         6.22           3         580         14.7         18.7         18.7 | SURFACES<br>PER DRIVE         TRACKS<br>PER SURFACE         PER DRI<br>SECTOR LE           1         580         4.90         6.24         6.22         6.68           3         580         14.7         18.7         18.7         20.0 | SURFACES<br>PER DRIVE         TRACKS<br>PER SURFACE         PER DRIVE           1         580         4.90         6.24         6.22         6.68         7.13           3         580         14.7         18.7         18.7         20.0         21.4 | SURFACES<br>PER DRIVE         TRACKS<br>PER SURFACE         PER DRIVE           1         580         4.90         6.24         6.22         6.68         7.13         7.13           3         580         14.7         18.7         18.7         20.0         21.4         21.4 | SURFACES<br>PER DRIVE         TRACKS<br>PER SURFACE         PER DRIVE         PER DRIVE           1         580         4.90         6.24         6.22         6.68         7.13         7.13         19.6           3         580         14.7         18.7         18.7         20.0         21.4         21.4         58.8 | SURFACES<br>PER DRIVE         TRACKS<br>PER SURFACE         PER DRIVE         PER DRIVE           1         580         4.90         6.24         6.22         6.68         7.13         7.13         19.6         24.9           3         580         14.7         18.7         18.7         20.0         21.4         21.4         58,8         74.8 | SURFACES<br>PER DRIVE         TRACKS<br>PER SURFACE         Ref DRIVE         PE<br>SECTOR LENGTH         PE<br>SECTOR LENGTH         PE<br>SECTOR         SECTOR           1         580         4.90         6.24         6.22         6.68         7.13         7.13         19.6         24.9         24.9           3         580         14.7         18.7         18.7         20.0         21.4         21.4         58.8         74.8         74.6 | SURFACES<br>PER DRIVE         TRACKS<br>PER SURFACE         PER DRIVE         PER SYS           1         580         4.90         6.24         6.22         6.68         7.13         19.6         24.9         24.9         26.7           3         580         14.7         18.7         18.7         20.0         21.4         21.4         58.8         74.8         74.6         80.2 | SURFACES<br>PER DRIVE         TRACKS<br>PER SURFACE         PER DRIVE         PER SYSTEM           1         580         4.90         6.24         6.22         6.68         7.13         19.6         24.9         24.9         26.7         28.5           3         580         14.7         18.7         18.7         20.0         21.4         21.4         58.8         74.8         74.6         80.2         85.6 |

TABLE 1

In addition, the controller has select capability which allows two such systems to be attached to the host via a common interface cable.

#### 2.0 FEATURES

- -- Buffered for asynchronous transfers between host and controller. Full error checking and error recovery procedures are automatically performed.

- Controller may be operated in a direct mode for synchronous transfers between the disk and host at disk speed. Error recovery procedures in direct mode are determined by the host.

- -- Error correction (ECC) option is provided to ensure high data integrity.

| с.<br> | MIC            | ROP     | ∩LIS™      |   |

|--------|----------------|---------|------------|---|

| SIZE   | CODE IDENT NO. | DWG NO. |            |   |

| A      |                | 10      | 0292       |   |

| SCALE  |                |         | SHEET 2 OF | 1 |

#### REVISIONS

-- Six standard recording formats are available (others by special order):

| 66 | Sectors. | 9 | 128  | bytes |

|----|----------|---|------|-------|

| 42 | Sectors  | 0 | 256  | bytes |

| 40 | Sectors  | ø | 268  | bytes |

| 36 | Sectors  | 0 | 320  | bytes |

| 24 | Sectors  | 0 | 512  | bytes |

| 12 | Sectors  | მ | 1024 | bytes |

- Interfaces easily to the host via an 8-bit bi-directional bus and 9 control lines. The interface structure is suitable for use with either programmed I/O or DMA data transfers.

- -- Provides capability to initialize the disk with a wide range of sector sequences to optimize thruput for specific applications.

- -- Data transfers may be from one sector to a full track per command. Sectors are normally accessed in logical order. Special commands are also included which transfer a full track in physical sector order to facilitate loading/dumping the disk.

- -- Overlap seek is provided. Seeks or read/write operations on the selected drive may be performed simultaneously with seeks on all other drives.

- -- High thruput In buffered mode, the buffer may be filled/unloaded at any rate up to disk speed (approximately 1µs/byte). Since transfers are buffered, the host interface need not provide special logic to account for DMA latency for the first data request of each block. In direct mode, the host interface must provide for response to all data requests at disk speed.

- -- Most media defects which appear during the life of the system can be eliminated under host control. One spare sector per track is provided for this purpose.

- -- Host may verify the correct transmission of each byte of a command to the controller before the command is executed.

- -- Cylinder accessing may be logical or physical.

| MICROPΩLIS™ |           |       |            |  |  |  |  |

|-------------|-----------|-------|------------|--|--|--|--|

| SIZE        | CODE IDEN | T NO. | DWG NO.    |  |  |  |  |

| Α           |           |       | 100292     |  |  |  |  |

| SCALE       |           |       | SHEET 3 OF |  |  |  |  |

|             |           |       |            |  |  |  |  |

#### 3.0 GENERAL DESCRIPTION

Model 1220 consists of a 1200 series rigid disk drive and a controller board which is housed within the drive outline. These combine to form a flexible, low cost disk sub-system which can be easily attached to any computer system. Three additional 1200's can be attached to the 1220 for expanded storage capacity.

#### 3.1 Disk Drive Mechanics

This consists of a die cast deck whose lower half is devoted to the recording heads, platters and the voice coil motor components. This lower half is sealed and air is circulated throughout the area by disk rotation induced flow. This flow is directed through a 0.3 micron absolute filter. The sealed area breathes to the outside via a similar filter.

There are no active electronic parts in the "clean" area and electrical connection is made between this area components and the electronics package via a PCB, which also seals the "clean" area from the rest of the casting.

#### 3.2 Drive Motor

Rotational drive for the platters is provided by a direct coupled brushless D.C. motor. This combination provides a very low profile allowing 3 platters to be packaged in an envelope only 4.62" high. Switching information for the electronic commutator is supplied by 3 photo transistor/LED combinations attached to the motor control PCBA.

#### 3.3 Positioner System

The positioner is a balanced swing arm mechanism supported on two preloaded bearings which reference to a stub shaft rigidly attached to the casting. The system is designed to accept between 2 and 4 arms depending on the model number. The voice coil is attached to the system on the opposite side of the bearings from the head and the whole mechanism is statically balanced. The magnet is of the short coil long magnet type and utilizes a Ferrite magnet. Position reference is made to tracks recorded on a dedicated surface on the platter nearest the deck. These tracks are recorded with position information in the "Modified Dibit"

#### 3.4 Read/Write Head

This consists of a single gap slider assembly of the Winchester type with the slider surface modified to run at 3600rpm.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |        | ROPS    |         | 5  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|---------|---------|----|--|

| SIZE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CODE IDEN | IT NO. | DWG NO. |         |    |  |

| Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |        | 1       | 00292   |    |  |

| SCALE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | -      |         | SHEET 4 | OF |  |

| The second value of the se |           |        |         |         |    |  |

#### REVISIONS

#### 3.5 Electronics Package:

Three boards are associated with the basic drive mechanism:

- a) Preamplifier PCBA

- b) Motor Control PCBA

- c) Device Electronics PCBA

Figure 7 lists the basic drive interface signals. See Specification 100198 - 1200 Series Disk Drives, for a detailed description of the drive and drive interface signals.

#### 3.6 Controller PCBA

This is a microprocessor-based controller which performs such functions as data formatting, encoding, decoding, sector buffering, error detection and recovery, and general housekeeping functions. It consists of a  $8" \times 14"$  board which resides in the 1220 drive assembly. Error correction is provided by an optional ECC board which attaches to the controller. D.C. power is drawn from the disk drive.

External connection is made through two edge connectors at the rear of the drive assembly:

a) Host Interface, J101. (34 pin edge connector)

This attaches to the host system (and another 1220 in an expanded system). Signal and pin assignments for this interface are shown in Figure 8.

b) Drive Interface, J102. (50 pin header)

This attaches to the drive interface connector, Jl, and add-on 1220's, if any. Pin assignments are shown in Figure 7.

A detailed description of the host interface and controller operation is given in the following sections of this specification.

|           | MICROPΩLIS™ |        |         |         |    |  |  |  |

|-----------|-------------|--------|---------|---------|----|--|--|--|

| size<br>A | CODE IDEN   | IT NO. | DWG NO. | 00292   |    |  |  |  |

| SCALE     |             |        |         | SHEET 5 | OF |  |  |  |

|     | APPL | ICATION                    | REVISIONS                                 |

|-----|------|----------------------------|-------------------------------------------|

| 4.0 | SDEC | IFICATION SUMMARY          |                                           |

| 4.0 |      |                            |                                           |

|     | 4.1  | Disk Drives                |                                           |

|     |      | Spindle Speed              | 3600 rpm                                  |

|     |      | Speed Variation            | ±.5%                                      |

|     |      | Latency                    | 3.3 ms                                    |

|     |      | Track Density              | 478 tpi                                   |

|     |      | Available Tracks           | 580                                       |

|     |      | Access Time                |                                           |

|     |      | Track-to-Track             | 4 ms                                      |

|     |      | Average (1/3 stroke)       | 34 ms                                     |

|     |      | Settling                   | 8 ms                                      |

|     |      | Data Surfaces              |                                           |

|     |      | 1221-1                     | 1                                         |

|     |      | 1222-1                     | 3                                         |

|     |      | 1223-1                     | 5                                         |

|     |      | Media                      | 200 mm oxide coated (IBM 3350 technology) |

|     |      |                            |                                           |

|     | 4.2  | 1220/1200 System           |                                           |

|     |      | Sectoring Method           | Hard                                      |

|     |      | Number of Sectors          | Six standard formats (See Table 1)        |

|     |      | Encoding Method            | EPM (modified 3PM).                       |

|     |      | Data Density (inner track) | 8623 bpi                                  |

|     |      | Flux Density (inner track) | 5749 frpi                                 |

|     |      | Transfer Rate              | 922 Kbytes/sec maximum                    |

|     |      | Formatted Capacity         | See Table 1                               |

|     | 4.3  | Physical (each module)     |                                           |

|     |      |                            |                                           |

|     |      | Environmental              | 10 40%                                    |

|     |      | Ambient Temperature        | $10 - 40^{\circ}$ C                       |

|     |      | Relative Humidity          | 10 - 80% non condensing                   |

|     |      |                            |                                           |

|     |      |                            |                                           |

|     |      |                            |                                           |

|     |      |                            | MICROPΩLIS™                               |

|     |      |                            |                                           |

| SIZE  | CODE IDEI | NT NO. | DWG NO.   |   |

|-------|-----------|--------|-----------|---|

| Α     |           |        | 100292    |   |

| SCALE |           |        | SHEET 6 0 | F |

|              | APPLI                       | CATION                                                  |                                             |                                                     |                             | RE                                 | VISION                   | IS                                                                                                 |        |

|--------------|-----------------------------|---------------------------------------------------------|---------------------------------------------|-----------------------------------------------------|-----------------------------|------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------|--------|

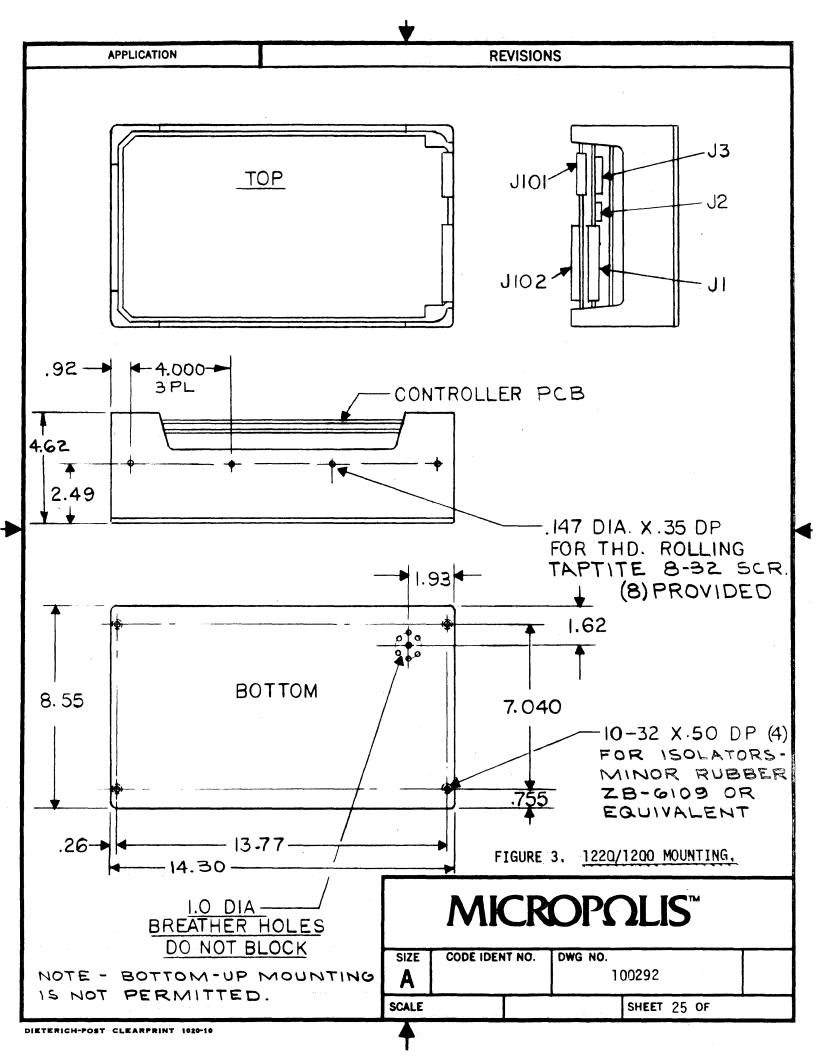

|              |                             | Mechanical (See                                         | e Figure                                    | 3)                                                  |                             |                                    |                          |                                                                                                    |        |

|              |                             | Depth                                                   | <u>-</u>                                    | - /                                                 | 1                           | 4,25" (362                         | 2 mm)                    |                                                                                                    |        |

|              |                             | Width                                                   |                                             |                                                     |                             | 8.55" (21)                         | 7 mm)                    |                                                                                                    |        |

|              |                             | Height                                                  |                                             |                                                     |                             | 4.62" (11)                         | 7 mm.)                   |                                                                                                    |        |

|              |                             | Weight                                                  |                                             |                                                     |                             | 22 1bs. (                          | 10 KG)                   | ).                                                                                                 |        |

|              | 4.4                         | Dissipation                                             |                                             |                                                     |                             |                                    |                          |                                                                                                    |        |

|              |                             | Total dissipat                                          | ion inclu                                   | uding po                                            | sition                      | ing:                               |                          |                                                                                                    |        |

|              |                             | 1220                                                    |                                             |                                                     | 9                           | 5 watts                            |                          |                                                                                                    |        |

|              |                             | 1200                                                    |                                             |                                                     | 7                           | 5 watts                            |                          |                                                                                                    |        |

|              | 4.5                         | Reliability (ex                                         | kcluding                                    | error c                                             | orrect                      | ion)                               |                          |                                                                                                    |        |

|              |                             | Soft Read Erro                                          | rs                                          |                                                     | ۱                           | in 10 <sup>10</sup>                |                          |                                                                                                    |        |

|              |                             | Hard Read Error                                         | rs                                          |                                                     | 1                           | in 10 <sup>12</sup>                |                          |                                                                                                    |        |

|              |                             | MTBF (Total Un                                          | it)                                         |                                                     | ۱                           | 0,000 hrs                          | •                        |                                                                                                    |        |

|              |                             | MTBF "Clean" An<br>Components                           |                                             |                                                     | 2                           | 5,000 hrs                          | •                        |                                                                                                    |        |

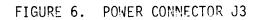

| 5.0          | DC P                        | OWER REQUIREMEN                                         | TS (each                                    | module)                                             | )                           |                                    |                          |                                                                                                    |        |

|              | assi                        | ower is supplied<br>gnments are show<br>DC requirements | wn in Fi                                    | h drive<br>gure 6.                                  | via a<br>The m              | 10 pin Aŀ<br>ating con             | P conr<br>nector         | nector, J3. Pin<br>r is AMP 1-37159-0.                                                             |        |

|              |                             |                                                         | 12                                          |                                                     |                             |                                    |                          | 200                                                                                                |        |

| VOLT/        |                             |                                                         | AVE                                         | PEAK                                                | 20                          |                                    | AVE<br>2 25 A            | $\frac{PEAK}{4}$                                                                                   |        |

| +24V<br>+ 5V | ±5%<br>±5%                  |                                                         | 2.25A<br>6.0A                               | 4.5A (<br>6.0A                                      | 20 sec                      | •                                  | 2.25A<br>2.25A           | 4.5A (20 secs)<br>2.25A                                                                            |        |

| -12V         |                             |                                                         | 0.0A<br>0.8A                                | 0.8A                                                |                             |                                    | 0.5A                     | 0.5A                                                                                               |        |

| 6.0          |                             | ROLS AND INDICA                                         |                                             |                                                     |                             |                                    |                          |                                                                                                    |        |

|              | None<br>and<br>init<br>posi | . When DC power<br>controller deter                     | r is app<br>rmine th<br>ce occur<br>over cy | at all v<br>s which<br>linder (                     | voltage<br>runs t<br>). The | s are wit<br>he spindl<br>controll | hin l<br>e up t<br>er in | se circuits in the c<br>imits. At this time<br>to operating speed a<br>itializes important<br>3.0. | nd the |

|              |                             |                                                         |                                             |                                                     |                             |                                    |                          |                                                                                                    |        |

|              |                             |                                                         |                                             |                                                     |                             |                                    |                          | ROPALIS                                                                                            | м      |

|              |                             |                                                         |                                             |                                                     | size<br>A                   | CODE IDEN                          | IT NO.                   | DWG NO.<br>100292                                                                                  |        |

|              |                             |                                                         |                                             | н.<br>1917 - С. | SCALE                       |                                    |                          | SHEET 7 O                                                                                          | F      |

| ETERICH-POS  | T CLEA                      | RPRINT 1020-10                                          |                                             |                                                     |                             |                                    |                          |                                                                                                    |        |

-

REVISIONS

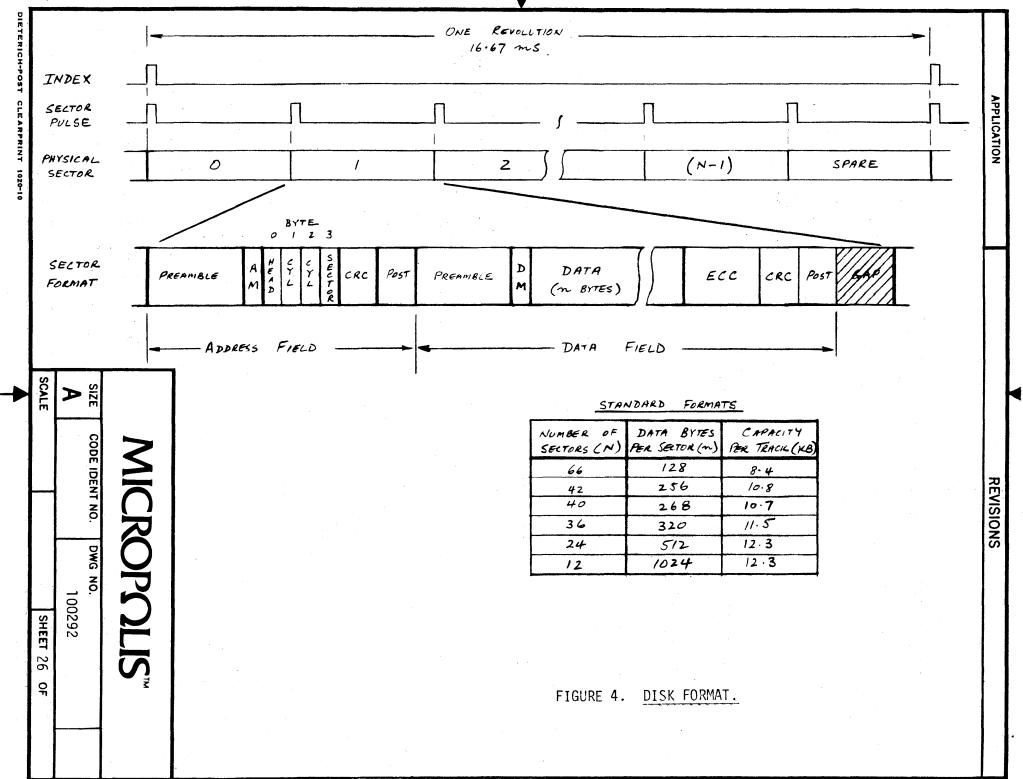

7.0 DISK FORMAT

The 1220 controller makes use of the track/sector format shown in Figure 4. Tracks are divided into a number of sectors which contain a fixed blocklength of user data. The beginning of each sector is identified by a sector pulse from the disk drive. Each track contains one spare sector which at the time of initialization can be made to fall over a defective area of the track.

Sectors are divided into an address field, a data field, and a trailing gap area. Data is recorded most significant bit first where Bit 7 is the most significant and Bit  $\emptyset$  the least significant bit of each byte. The EPM encoding method provides an increased data packing density compared to MFM while maintaining the same decoding margins and reliability.

The suffix H indicates a hexadecimal value in the following description.

7.1.1 <u>Address Field</u> -- Contains a unique track/sector address and associated information. This field is written during initialize commands only.

|               | Synchronizes read circuits<br>Identifies the beginning of an Address Field.<br>The value contained in this byte indicates<br>whether a defective sector has been spared |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | on this track.                                                                                                                                                          |

| = //H         | Normal initialize, no defective sector. The                                                                                                                             |

|               | spare sector resides at the end of the track.                                                                                                                           |

| = 7DH         | Track has been initialized to eliminate a                                                                                                                               |

|               | defective sector.                                                                                                                                                       |

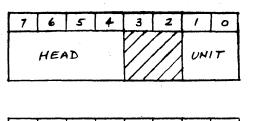

| Byte 0        | Bits 0-2 Head Address (0-4)                                                                                                                                             |

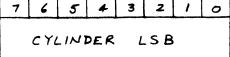

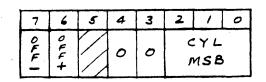

| Byte 1        | Bits O-7 Cylinder Address LSB}(O-579)<br>Bits O-1 Cylinder Address MSB                                                                                                  |

| Byte 2        | Bits 0-1 Cylinder Address MSB                                                                                                                                           |

| Byte 3        | Bits 0-6 Logical Sector Address (0-65)                                                                                                                                  |

| CRC (2 bytes) | Cyclic Redundancy Check bytes.                                                                                                                                          |

|               | Computed from contents of the                                                                                                                                           |

|               | Address Mark and bytes 0-3 using                                                                                                                                        |

|               | the polynomial $X^{16} + X^{12} + X^5 + 1$                                                                                                                              |

| Postamble     | Trailing guardband                                                                                                                                                      |

|               |                                                                                                                                                                         |

Unused bits are zeroes.

7.1.2 Data Field -- Contains user data for transfer to/from the host system:

|                | Synchronizes read circuits                            |

|----------------|-------------------------------------------------------|

| Data Mark, 44H | Identifies beginning of a Data Field                  |

| Data           | n bytes of user data                                  |

| ECC (4 bytes)  | Optional Error Correction Code computed from          |

|                | contents of Data Mark and User Data                   |

| CRC (2 bytes)  | CRC computed from contents of Data Mark               |

|                | and User Data using same polynomial as Address Field. |

| Postamble      | Trailing guardband                                    |

|                |                                                       |

|       | M         |        | ROP     | ΩLIS™      |  |

|-------|-----------|--------|---------|------------|--|

| SIZE  | CODE IDEN | IT NO. | DWG NO. |            |  |

| A     |           |        | 10      | 0292       |  |

| SCALE |           | ·      |         | SHEET 8 OF |  |

7.1.3 GAP -- Provides tolerance for disk speed variation

Six standard arrangements of this format are available as shown in Figure 4. The required format is selected by appropriate jumper connections on the drive and controller and must be specified when ordering. An additional 1K bytes of RAM must be installed in the controller for operation with the 1K byte data format.

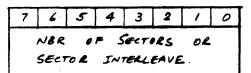

#### 7.2 Sector Interleaving

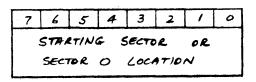

A track can be initialized with the sectors in sequential order or in a number of interleaved patterns (Figure 5). When interleaved, consecutive logical sectors (as determined by byte 3 in the address field) are physically separated from each other by one or more other sectors. This provides a sector-to-sector latency which can be chosen to optimize the host system's processing time.

In addition, the physical position of sector 0 can be specified on a track-by-track basis. For instance, the user might format the disk surface with a specific interleaved pattern which rotates by equal increments as consecutive cylinders are accessed.

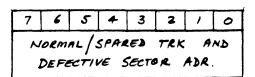

#### 7.3 Sector Sparing

Tracks are normally initialized with the spare sector located at the end of the track. If one of the data sectors becomes defective the track can be re-initialized placing the spare sector over the defective area. The sector in error and all other sectors around to index are shifted right one place maintaining the interleaved pattern. Parameter Byte 6 in the Initialize commands specifies normal/spared mode and contains the logical address of the sector to be spared. Address Mark bytes contain 77H for a normal track or 7DH for a spared track.

A maximum of one sector per track may be spared. The user can determine if a given track has already been spared by accessing the contents of an Address Mark using the Read Header command.

#### 7.4 Initialize Commands

Each data surface of the disk must be pre-recorded with the desired format before normal use. Three Initialize commands are provided for this purpose:

and ending with index) using head, cylinder, sector sequencing and sparing information contained in the accompanying parameter bytes. Data fields contain the cylinder address in the first two bytes and EEH in the remaining data byte locations.

VERIFY FORMAT ------ Verifies that track is correctly initialized. Reads entire track and compares against initialize Di

| allern    |                | CROPΩLIS™         |   |

|-----------|----------------|-------------------|---|

| size<br>A | CODE IDENT NO. | DWG NO.<br>100292 | r |

| SCALE     |                | SHEET 9 OF        |   |

|           |                |                   |   |

#### REVISIONS

INIT and VFY ----- Combination of the two above commands.

A user utility program is required to initialize then verify each track on the disk with the desired format.

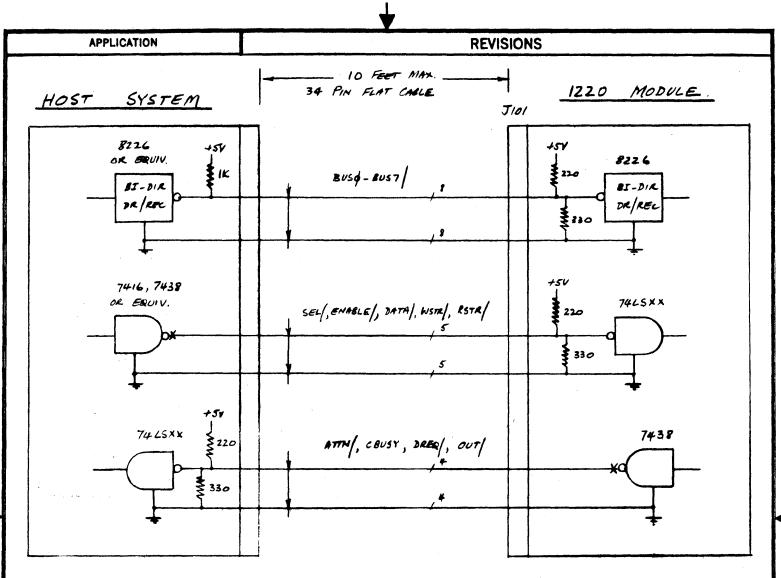

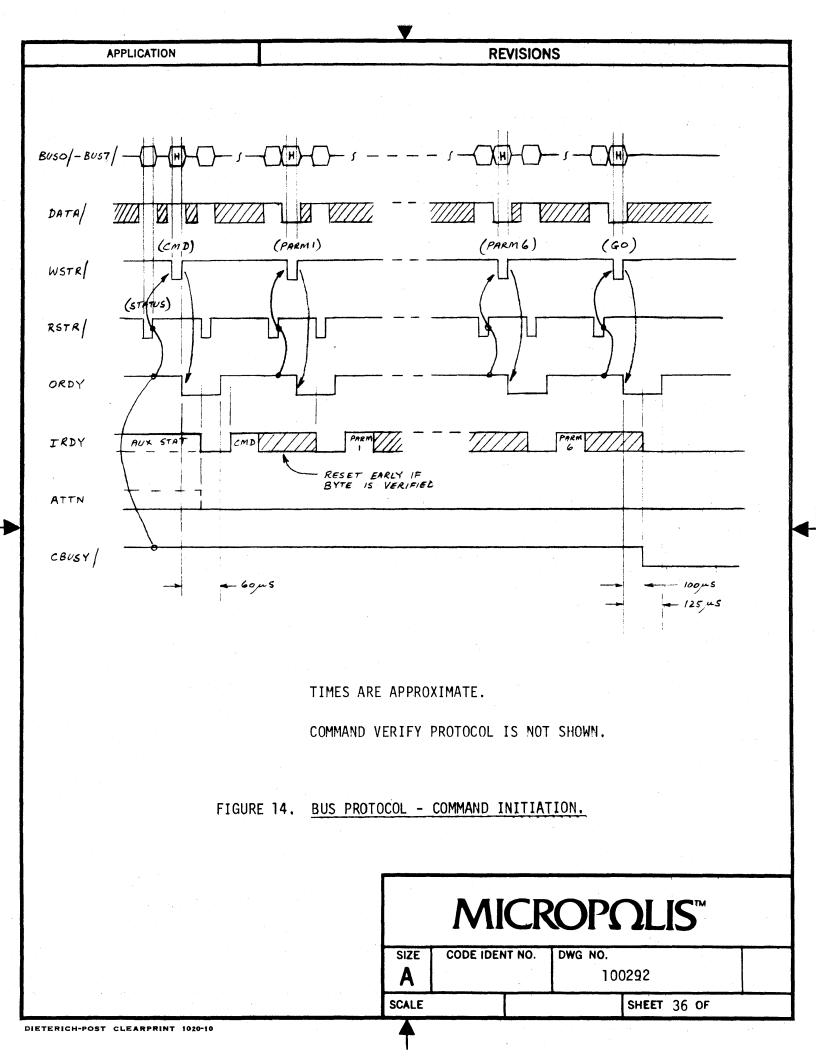

#### 8.0 HOST INTERFACE

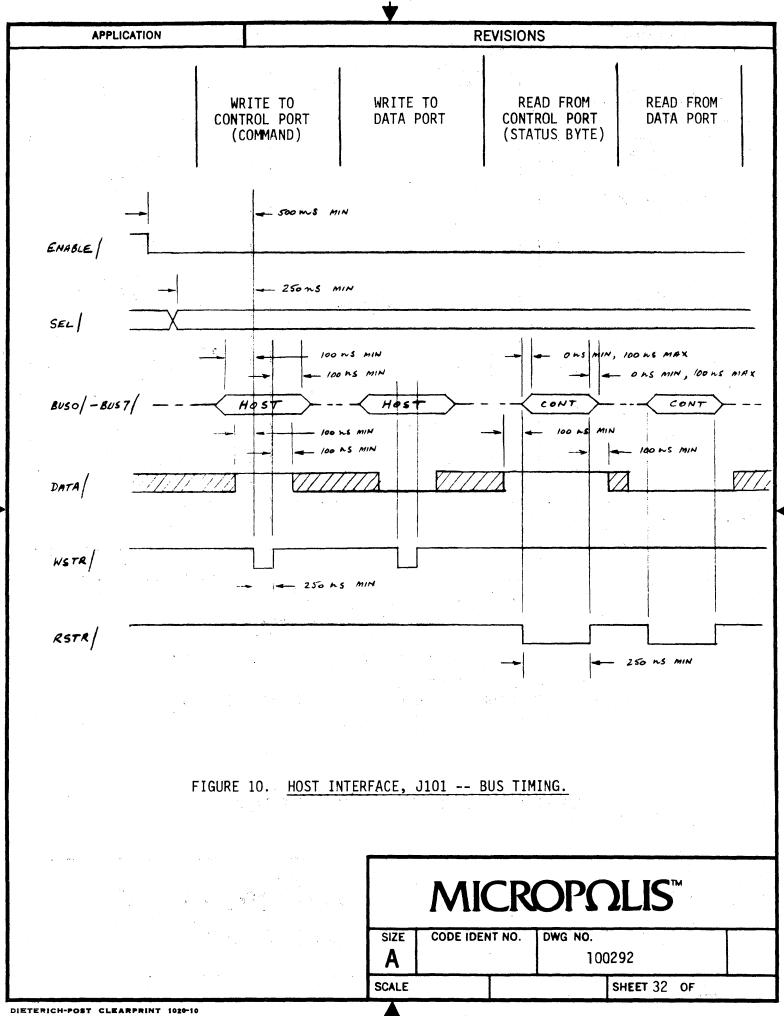

The host interface to the 1220 is made through a 34 pin edge connector, J101, located on the Controller PCBA. Pinouts, electrical characteristics, and timing requirements are shown in Figures 8-11.

All signals except CBUSY on the interface are low true (indicated by a /). However, in the remainder of this text reference will be made to the logical condition of each signal rather than it's electrical polarity. e.g. O=false, 1=true.

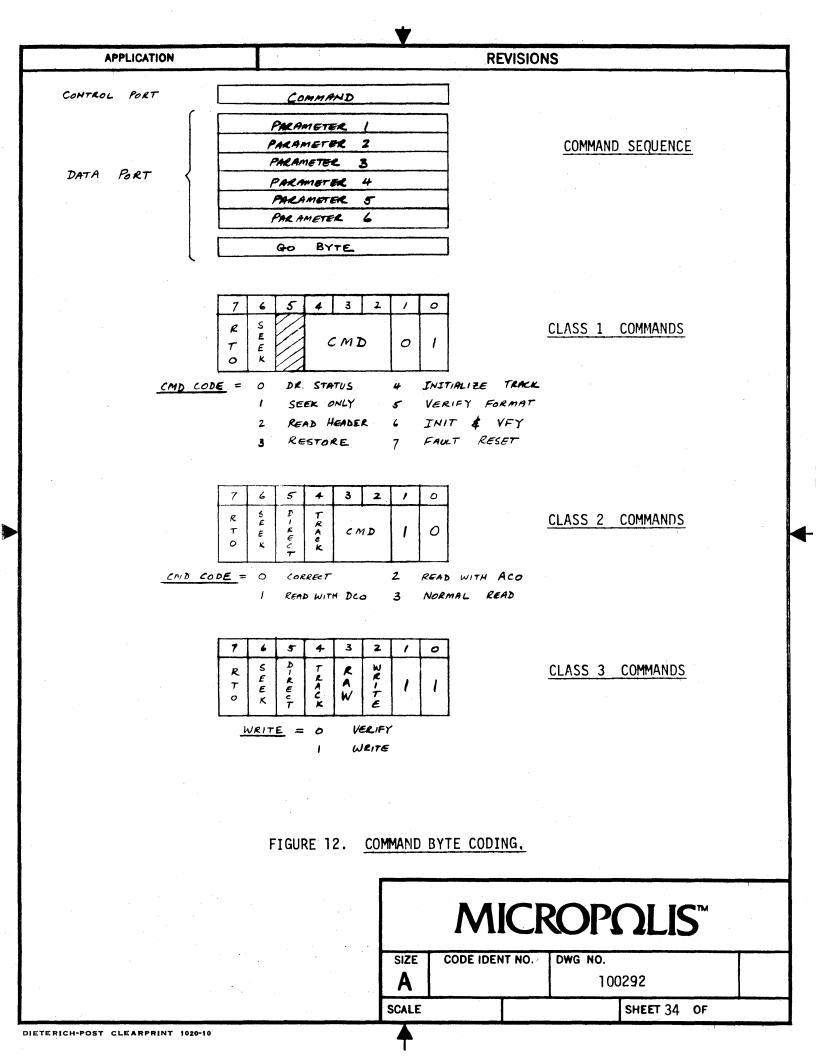

The interface is structured around an 8 bit bi-directional bus and the three control signals WSTR, RSTR, and DATA. Information is output to either a control (command) or data port using WSTR, and input from a control (status) or data port using RSTR. DATA selects the port in use.

These exchanges are controlled by the host making use of handshake flags in the status byte. Most flags appear in both the status byte and on separate interface lines to allow flexibility in the method of attachment to the host system.

8.1 Interface Signals

SEL ------ Selects the controller in one of two 1220/1200 systems attached to host interface. When selected, the controller responds to the bus control lines. The address is determined by jumpers W1, W2 on the controller PCBA.

SEL = 0 Address 0, W1 installed = 1 Address 1, W2 installed

ENABLE -----

Normally held true. When false (2µs min), the power-on sequence is invoked in all controllers (Section 9.0). Automatically initializes controller if there is no host power or if the cable is disconnected. May also be used for programmed reset.

BUSØ - BUS7 ------(8 lines)

----- Bi-directional tri-state bus which transfers information to/from the controller in parallel.

|       | M         | IC    | ROP     | JLIS™     |  |

|-------|-----------|-------|---------|-----------|--|

| SIZE  | CODE IDEN | T NO. | DWG NO. |           |  |

| Α     |           |       | 100     | 292       |  |

| SCALE |           |       | SH      | EET 10 OF |  |

\_\_\_\_

| APPLIC | CATION | REVISIONS                                                                                                                                                                                                                                                                                     |

|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ·<br>· | WSTR   | Write Strobe. When pulsed, one byte is output<br>from the host to the controller. Contents of<br>the bus are copied into an output buffer on the<br>trailing edge of WSTR. The byte is interpreted<br>as being either control (DATA=0) or data<br>(DATA=1).                                   |

|        | RSTR   | Read Strobe. When pulsed one byte is input from<br>the controller to the host. When RSTR is true,<br>the controller drives the bus with the contents<br>of either the status register (DATA=0) or input<br>buffer (DATA=1). RSTR must not be asserted while<br>the host is driving the bus.   |

|        | DATA   | above.                                                                                                                                                                                                                                                                                        |

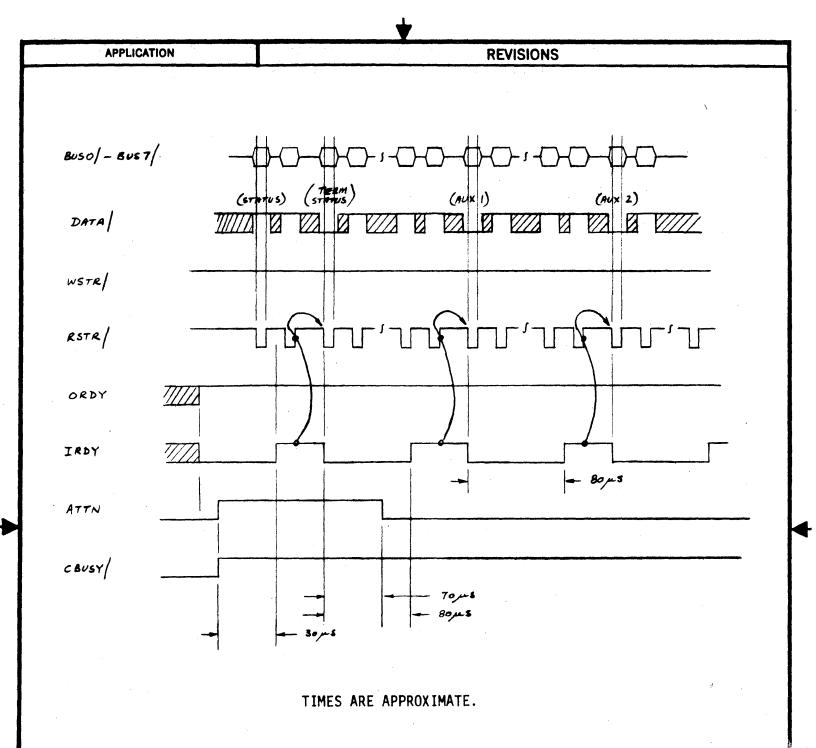

|        | CBUSY/ | Controller Busy/. Cleared when a command is issue<br>set when the command is terminated. The polarity<br>is chosen so that the controller appears busy to<br>the host when the cable is disconnected.                                                                                         |

|        |        | CBUSY/ = 0<br>= 1 Controller busy executing a command.<br>Controller not busy, a new command<br>can be accepted.                                                                                                                                                                              |

| · .    | ATTN   | Attention. Set true at the end of each command<br>when CBUSY/ changes state. The host should respon<br>by reading the TERMINATION STATUS byte which<br>indicates the success or failure of the command.<br>ATTN is cleared approximately 70µs after<br>TERMINATION STATUS is read.            |

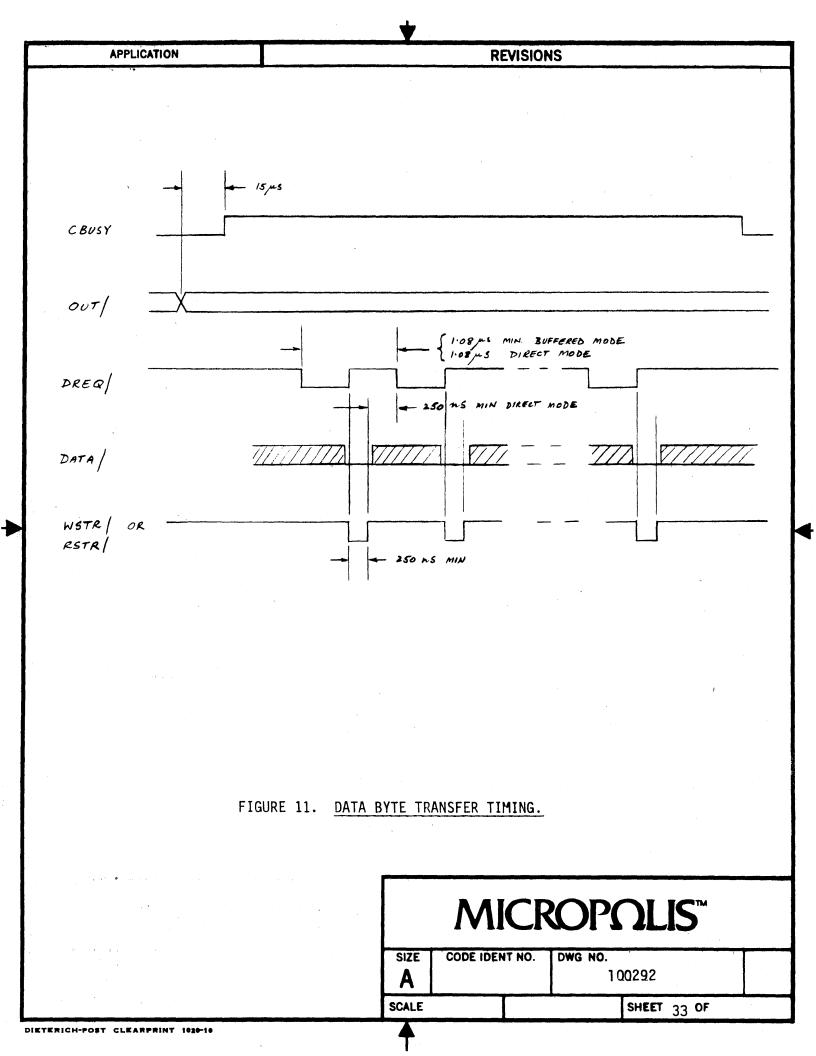

|        | DREQ   | Data Request. This flag requests the transfer of<br>each byte of user data to/from the controller.<br>The direction of transfer is specified by OUT.<br>The host must respond by writing/reading the<br>required byte to the data port. Data must be<br>transferred only in response to DREO. |

|        |        | In buffered mode the data transfer rate is<br>determined by the host (0-922KHz). In direct<br>mode transfers are synchronous with the disk,<br>and each byte must be serviced in less than one<br>byte-time. See Figure 11 for timing.                                                        |

|        | OUT    | Specifies the direction of data transfer.                                                                                                                                                                                                                                                     |

|        |        | <pre>= 0 Controller to host (Class 2 commands) = 1 Host to controller (Class 3 commands)</pre>                                                                                                                                                                                                |