# 1991 DATA BOOK

# Semi-Standard Analog

## Introduction

Founded in 1983, with headquarters in San Jose, California, Micro Linear is a leading manufacturer of high performance standard and semi-standard analog and mixed-signal ICs for specific market applications as well as supplying analog user-specific integrated circuits (USICs).

Focusing at achieving the high levels of integration customers want, Micro Linear provides ICs at the sub-system level, addressing five specific end markets: power and motion control, hard disk drives, analog telecom, local area networks and data converters/ filters. These products use a variety of bipolar and CMOS process technologies chosen to optimize performance and level of integration.

For power control applications where high volumetric efficiency is a benefit, Micro Linear offers a broad line of high-frequency switching power supply controllers. Anticipating the emerging energy and noise regulations for electronic equipment, Micro Linear introduced the industry's first power factor control IC and has followed that up with a family of products applicable to many types of electronic equipment including electronic lamp ballasts.

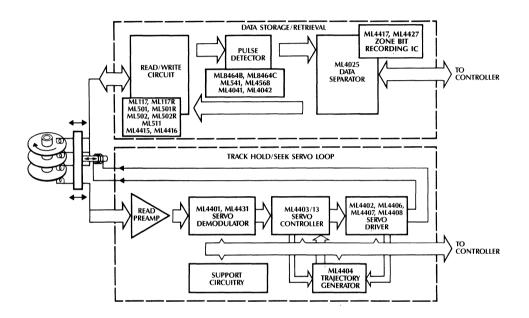

Micro Linear has emerged as a major supplier to the competitive, fast moving and high volume hard disk drive industry. High performance analog ICs are supplied for the three subsystem areas: data path signal processing, head positioning and motor control. Its products have been widely used in 3.5 inch drives, led by its dedicated servo chip set which establishes the standard for minimum access time disk drives.

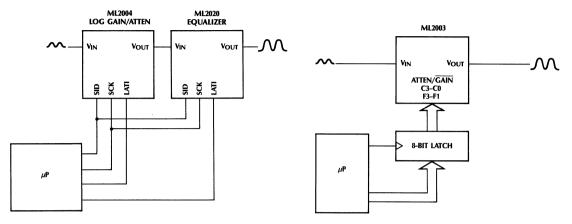

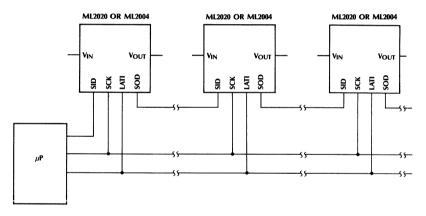

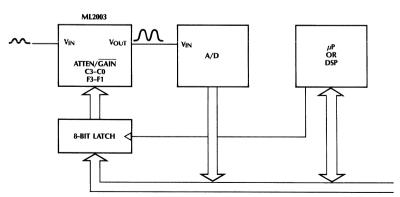

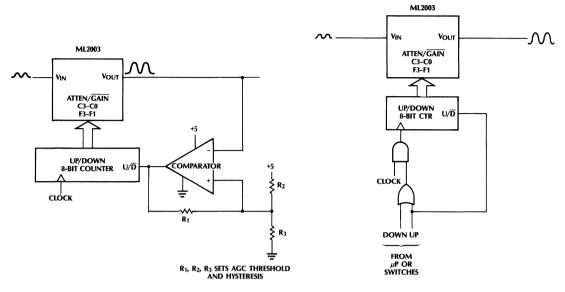

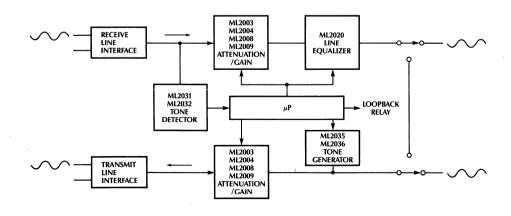

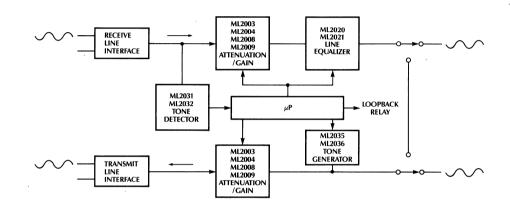

The company's telecommunications IC's meet the demanding technical specifications required for Network Communications Terminating Equipment (NCTE). The NCTE products consist of a broad line of programmable attenuators, line equalizers, tone detectors and generators.

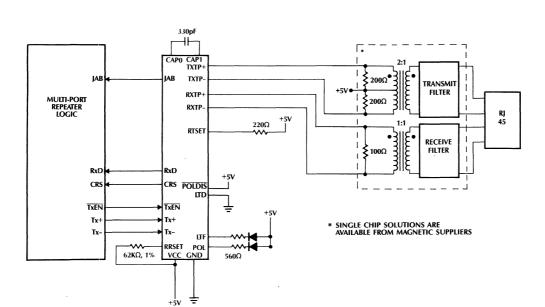

In the local area network market, Micro Linear has focused on supplying transceivers that conform to the IEEE 802 standards for transmission over twisted copper wire pairs and fiber optics. The company presently supplies standard and semi-standard 10Base-T transceivers for computer terminations and Multiport Repeaters and quantizers for fiber optic based systems.

Among its converter and filter products are high performance A/D and D/A converters and switched capacitor filters. The A/D's range from 8- to 12- bits and use electronic techniques, such as digital correction, instead of trim methods to achieve cost effective high performance parts.

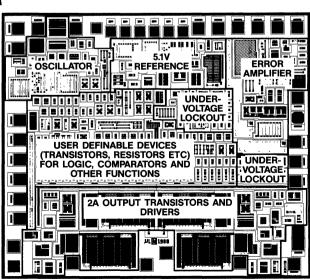

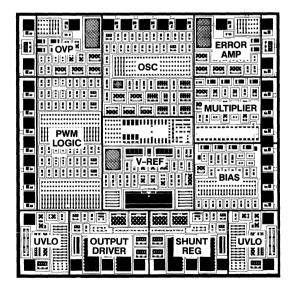

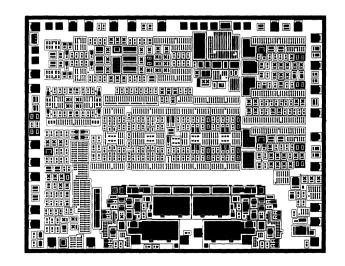

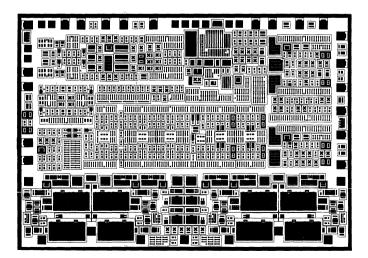

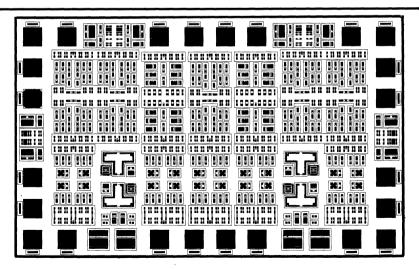

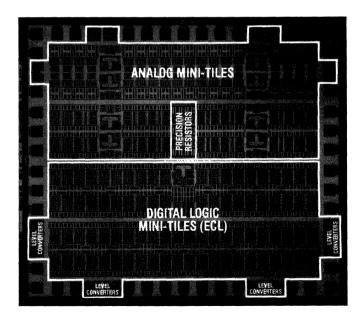

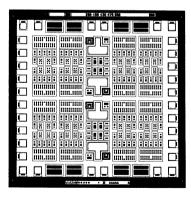

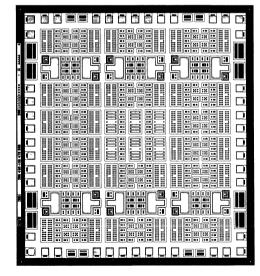

A pioneer in analog semi-custom integrated circuits, Micro Linear continues to expand its unique tile array for use in USICs. This advanced proprietary tile array approach methodology means that custom designs can be easily and quickly integrated into silicon with minimum expense.

Since its inception, Micro Linear has been committed to excellence in every facet of design and manufacturing. Micro Linear has focused its resources on supplying customers with exceptionally high quality, reliable, and responsive service.

# Micro Linear Corporation Data Book 1991

Copyright© 1991

#### LIFE SUPPORT POLICY

MICRO LINEAR'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF MICRO LINEAR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or design. Micro Linear does not assume any liability arising out of the application or use of any product described herein, neither does it convey any license under its patent right nor the rights of others.

Micro Linear uses outside vendors to provide silicon wafer processing and assembly packaging. Micro Linear reserves the right to provide products that are manufactured at any or all of its qualified vendors and to add new vendors as required.

From time to time, the company may supply silicon that has been 1) revised or 2) supply a compacted version of an array based product. When the modified version of the product completely conforms to the Micro Linear data sheet, this substitution will be done without any prior notification.

Micro Linear

# 1991 PRODUCT DATA BOOK

| GENERAL INFORMATION            |

|--------------------------------|

| A/D CONVERTERS, D/A CONVERTERS |

| TELECOM ICs                    |

| DATA COMMUNICATION ICs         |

| DISK DRIVE ICs                 |

| POWER SUPPLY ICs               |

| USICs AND SEMI-STANDARD        |

| QUALITY AND RELIABILITY        |

| /M8 MILITARY PRODUCT FLOW      |

| APPLICATION NOTES              |

| PACKAGING INFORMATION          |

|                                |

Å

1. c

# **Table of Contents**

| nAC  | - |

|------|---|

| PAL. | r |

|      |   |

i

| SECTION 1 — | GENERAL INFORMATION                                                           |       |

|-------------|-------------------------------------------------------------------------------|-------|

|             | General Ordering Information                                                  | 1-1   |

|             | Alternate Source Cross Reference                                              | 1-2   |

|             | Alpha Numeric Index                                                           | 1-5   |

| SECTION 2 — | A/D CONVERTERS, D/A CONVERTERS                                                |       |

|             | Selection Guide                                                               | 2-1   |

|             | ML2200 12-Bit Plus Sign Data Acquisition Peripheral                           | 2-5   |

|             | ML2208 12-Bit Plus Sign Data Acquisition Peripheral                           | 2-5   |

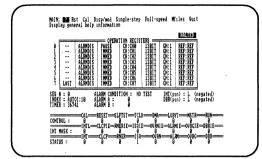

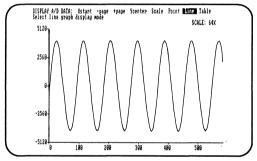

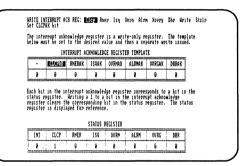

|             | ML2200EX, ML2208EX Exerciser                                                  | 2-33  |

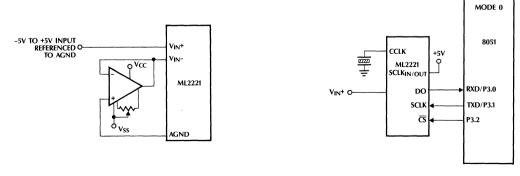

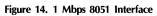

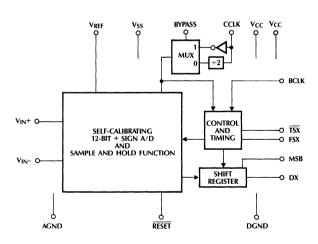

|             | ML2221 Serial Peripheral Interface 12-Bit Plus Sign A/D Converter             |       |

|             | with Sample and Hold                                                          | 2-35  |

|             | ML2222 Serial CODEC/DSP Interface 12-Bit Plus Sign A/D Converter              |       |

|             | with Sample and Hold                                                          | 2-49  |

|             | ML2223 Serial Asynchronous Interface 12-Bit Plus Sign A/D Converter           |       |

|             | with Sample and Hold                                                          | 2-50  |

|             | ML2230 $\mu$ P Compatible 12-Bit Plus Sign A/D Converter with Sample and Hold | 2-51  |

|             | ML2233 µP Compatible 12-Bit Plus Sign A/D Converter with Sample and Hold      | 2-67  |

|             | ML2252 µP Compatible 8-Bit A/D Converter with 2-Channel Multiplexer           | 2-83  |

|             | ML2258 µP Compatible 8-Bit A/D Converter with 8-Channel Multiplexer           | 2-94  |

|             | ML2259 $\mu$ P Compatible 8-Bit A/D Converter with 8-Channel Multiplexer      | 2-83  |

|             | ML2261 $\mu$ P Compatible High Speed 8-Bit A/D Converter with T/H (S/H)       | 2-105 |

|             | ML2264 4-Channel High Speed 8-Bit A/D Converter with T/H (S/H)                | 2-120 |

|             | ML2271 µP Compatible High Speed 10-Bit A/D Converter with S/H                 | 2-135 |

|             | ML2280 8-Bit Serial A/D Converter                                             | 2-148 |

|             | ML2281 8-Bit Serial A/D Converter                                             | 2-166 |

|             | ML2282 8-Bit Serial A/D Converter with 2-Channel Multiplexer                  | 2-166 |

|             | ML2283 8-Bit Serial A/D Converter with 4-Channel Multiplexer                  | 2-148 |

|             | ML2284 8-Bit Serial A/D Converter with 4-Channel Multiplexer                  | 2-166 |

|             | ML2288 8-Bit Serial A/D Converter with 8-Channel Multiplexer                  | 2-166 |

|             | ML2340 Single Supply Programmable 8-Bit D/A Converter                         | 2-186 |

|             | ML2341 Single Supply Programmable 8-Bit D/A Converter                         | 2-197 |

|             | ML2350 Single Supply Programmable 8-Bit D/A Converter                         | 2-186 |

|             | ML2351 Single Supply Programmable 8-Bit D/A Converter                         | 2-197 |

### SECTION 3 — TELECOM

| Selection Guide                                  | 3-1  |

|--------------------------------------------------|------|

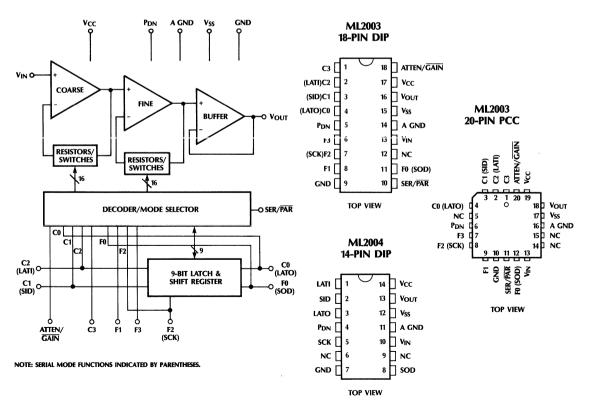

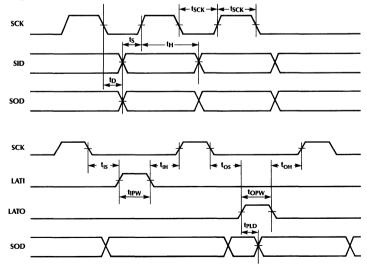

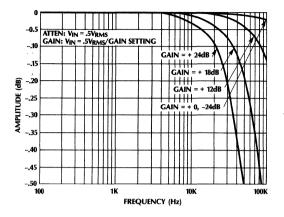

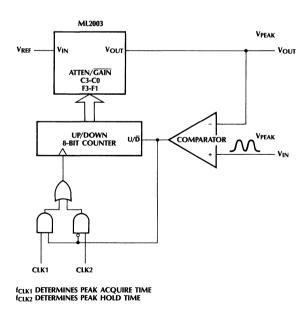

| ML2003 Logarithmic Gain/Attenuator               | 3-2  |

| ML2004 Logarithmic Gain/Attenuator               | 3-2  |

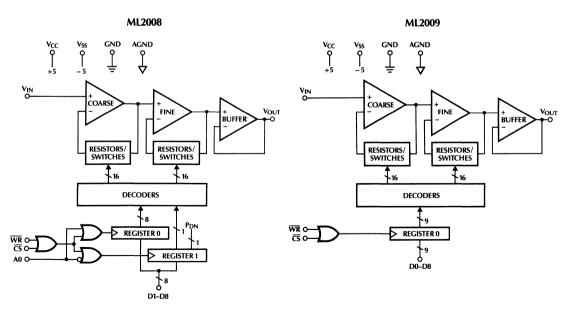

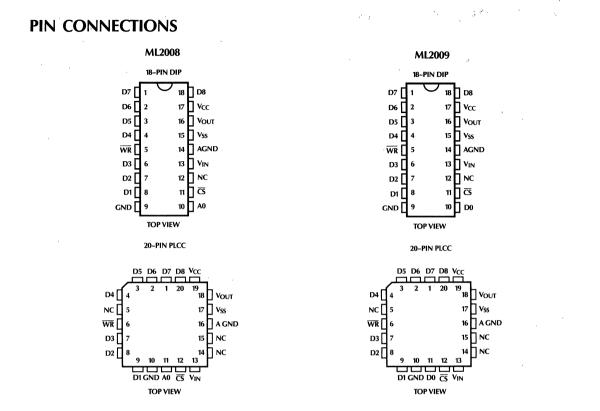

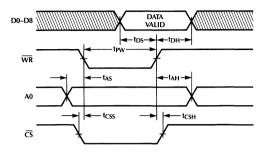

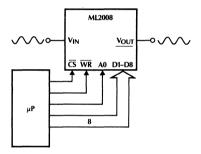

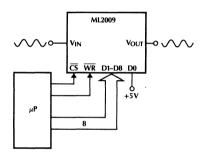

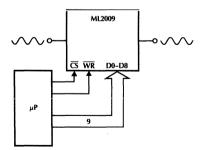

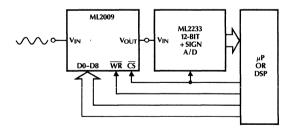

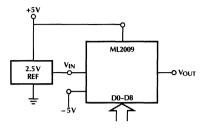

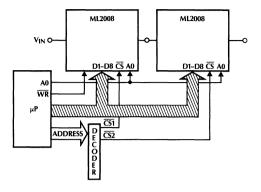

| ML2008 µP Compatible Logarithmic Gain/Attenuator | 3-13 |

| ML2009 µP Compatible Logarithmic Gain/Attenuator | 3-13 |

| ML2020 Telephone Line Equalizer                  | 3-22 |

| ML2021 Telephone Line Equalizer                  | 3-33 |

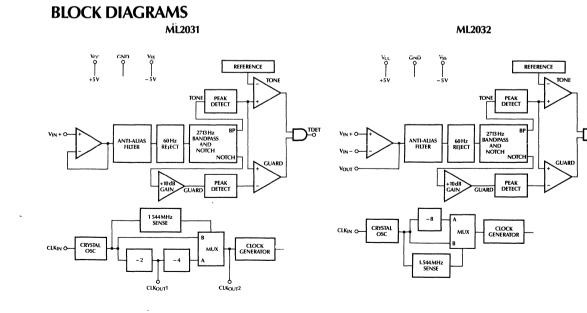

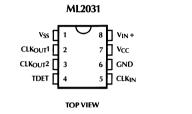

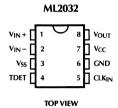

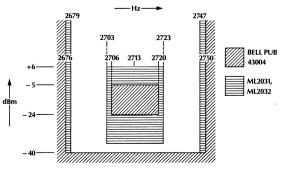

| ML2031 Tone Detector                             | 3-44 |

| ML2032 Tone Detector                             | 3-44 |

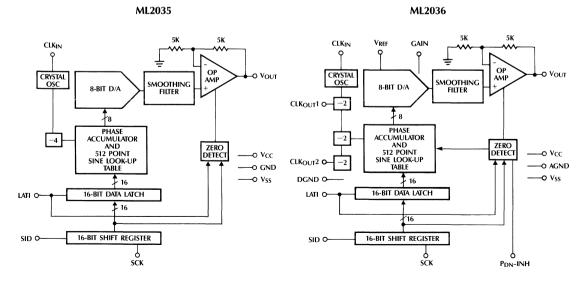

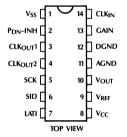

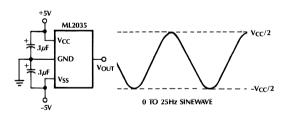

| ML2035 Programmable Sinewave Generator           | 3-52 |

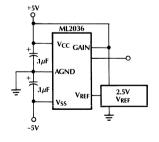

| ML2036 Programmable Sinewave Generator           | 3-52 |

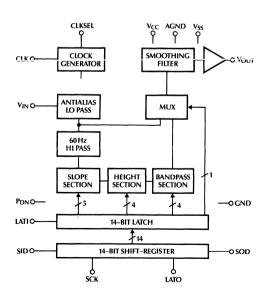

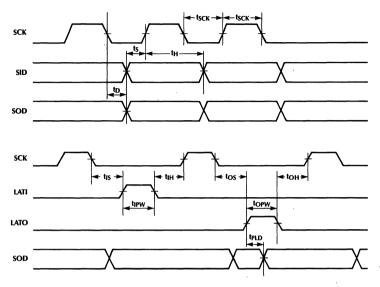

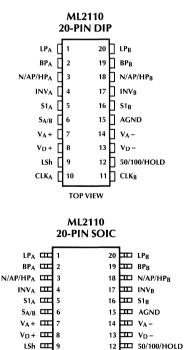

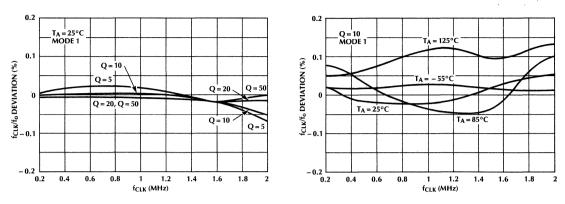

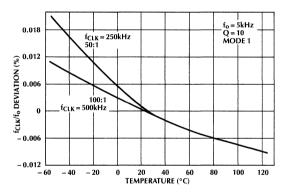

| ML2110 Universal Dual Filter                     | 3-64 |

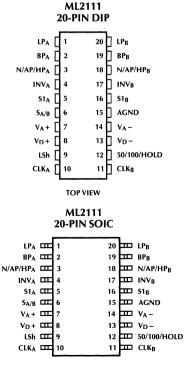

| ML2111 Universal Hi-Frequency Dual Filter        | 3-83 |

|                                                  |      |

### SECTION 4 — DATA COMMUNICATIONS

| Selection Guide                                      | 4-1  |

|------------------------------------------------------|------|

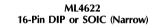

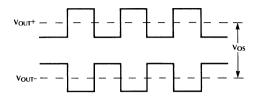

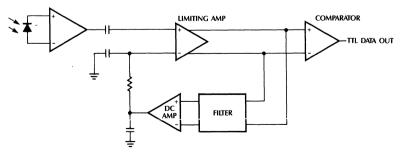

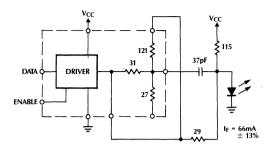

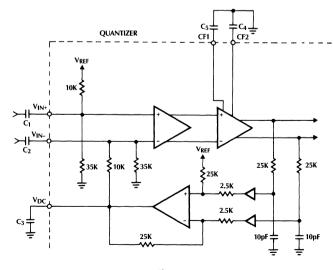

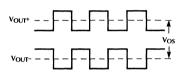

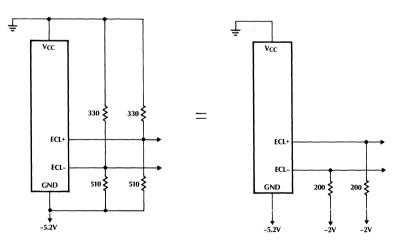

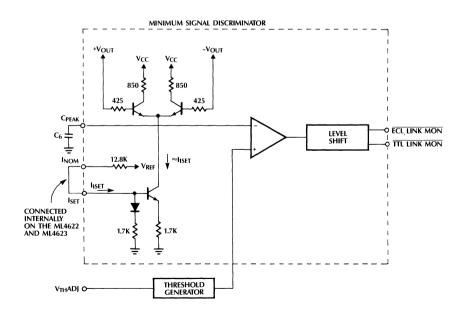

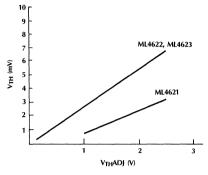

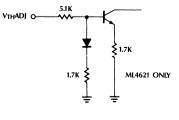

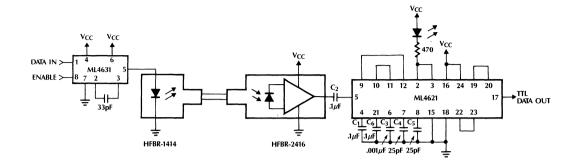

| ML4621 Fiberoptic Data Quantizer                     | 4-2  |

| ML4622 Fiberoptic Data Quantizer                     | 4-2  |

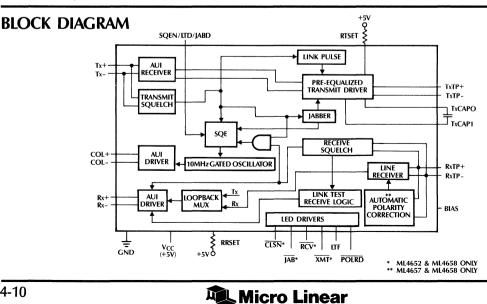

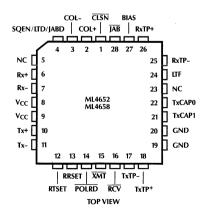

| ML4651 10BASE-T Transceiver with AUI                 | 4-10 |

| ML4652 10BASE-T Transceiver with AUI                 | 4-10 |

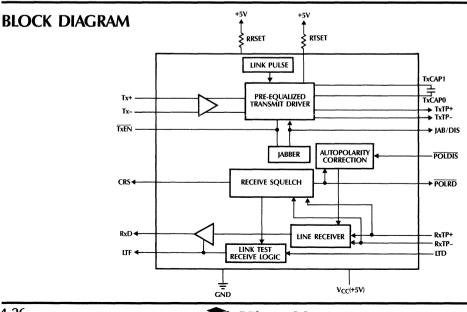

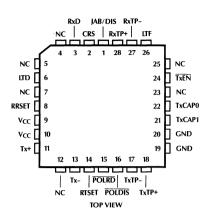

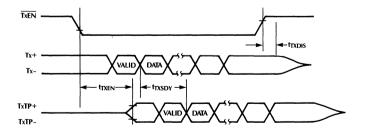

| ML4654 10BASE-T Transceiver for Multi-Port Repeaters | 4-26 |

| ML4657 10BASE-T Transceiver with Autopolarity        | 4-10 |

| ML4658 10BASE-T Transceiver with Autopolarity        | 4-10 |

| ML4661 FOIRL Transceiver                             | 4-36 |

| FB3651 LAN Transceiver Array                         | 4-46 |

|                                                      |      |

### SECTION 5 — DISK DRIVES

| Selection Guide                                  | 5-1  |

|--------------------------------------------------|------|

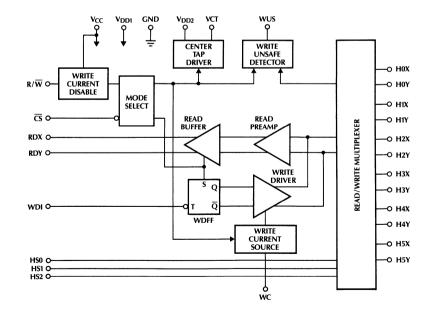

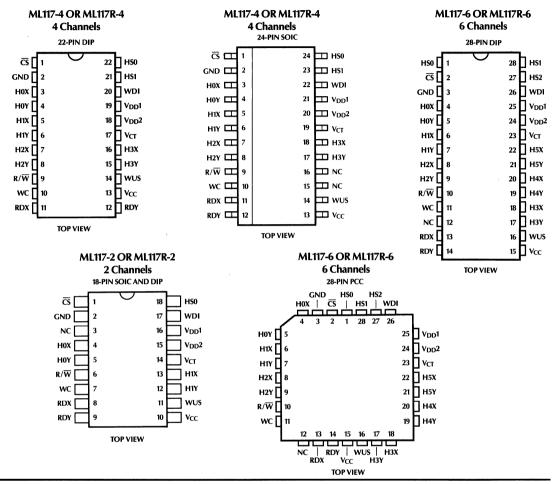

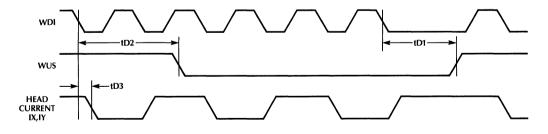

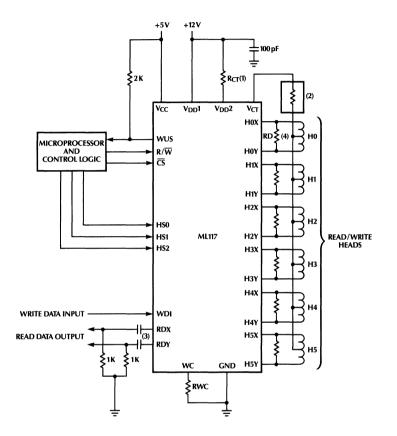

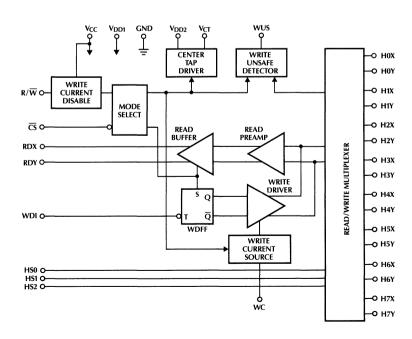

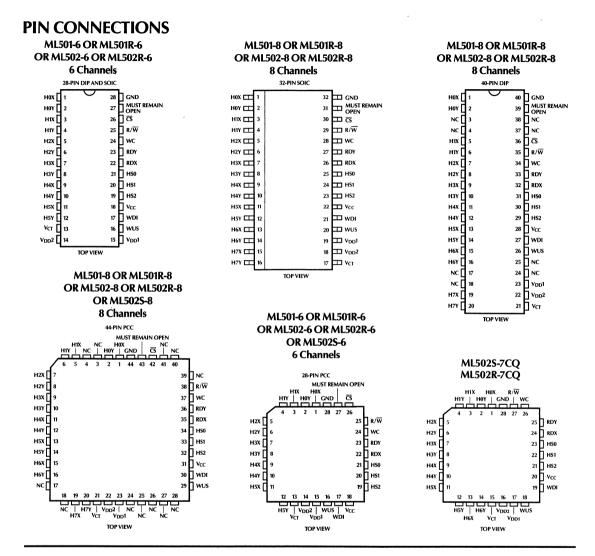

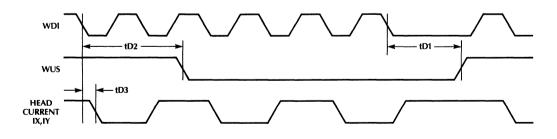

| ML117 2, 4, or 6-Channel Read/Write Circuits     | 5-3  |

| ML117R 2, 4, or 6-Channel Read/Write Circuits    | 5-3  |

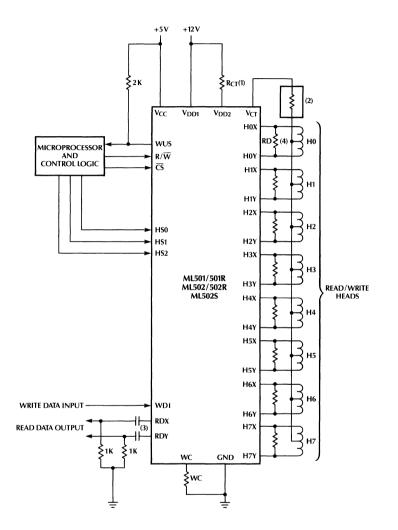

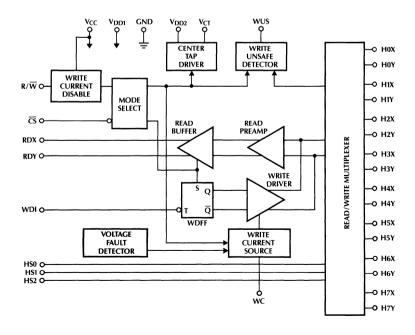

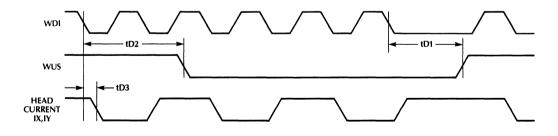

| ML501 6, 7, or 8-Channel Read/Write Circuits     | 5-11 |

| ML501R 6, 7, or 8-Channel Read/Write Circuits    | 5-11 |

| ML502 6, 7, or 8-Channel Read/Write Circuits     | 5-11 |

| ML502R 6, 7, or 8-Channel Read/Write Circuits    | 5-11 |

| ML502S 6, 7, or 8-Channel Read/Write Circuits    | 5-11 |

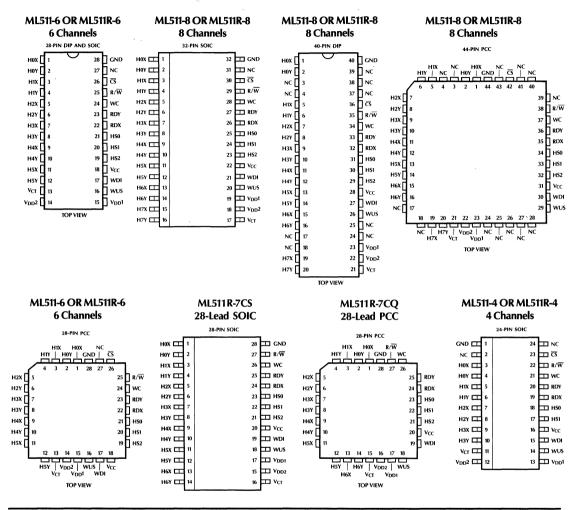

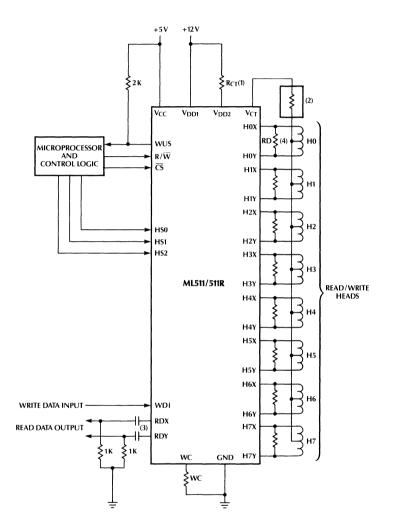

| ML511 4, 6, 7, or 8-Channel Read/Write Circuits  | 5-19 |

| ML511R 4, 6, 7, or 8-Channel Read/Write Circuits | 5-19 |

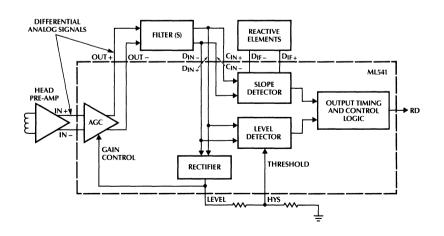

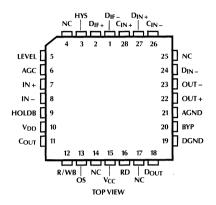

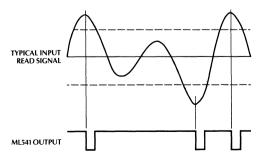

| ML541 Read Data Processor                        | 5-27 |

| ML4025 Data Separator                            | 5-37 |

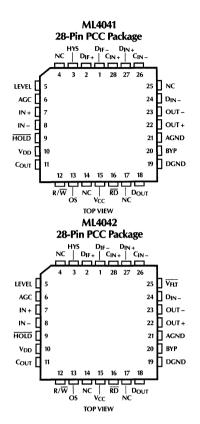

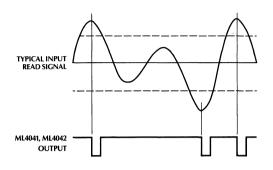

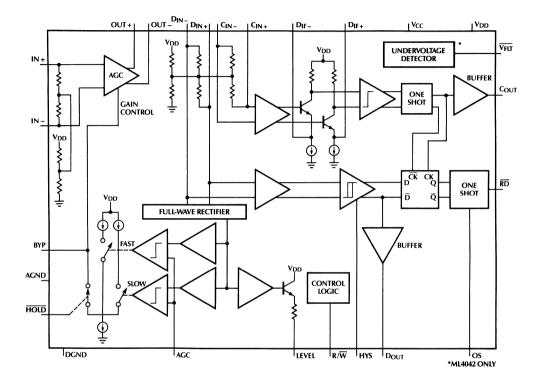

| ML4041 Read Data Processor                       | 5-46 |

| ML4042 Read Data Processor                       | 5-46 |

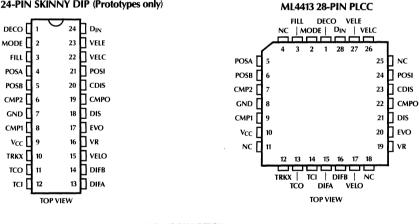

| ML4401 Servo Demodulator                         | 5-57 |

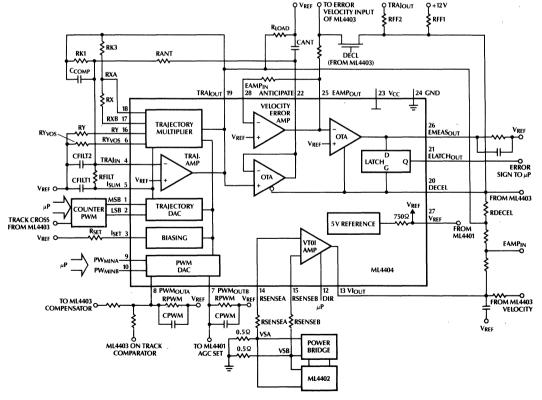

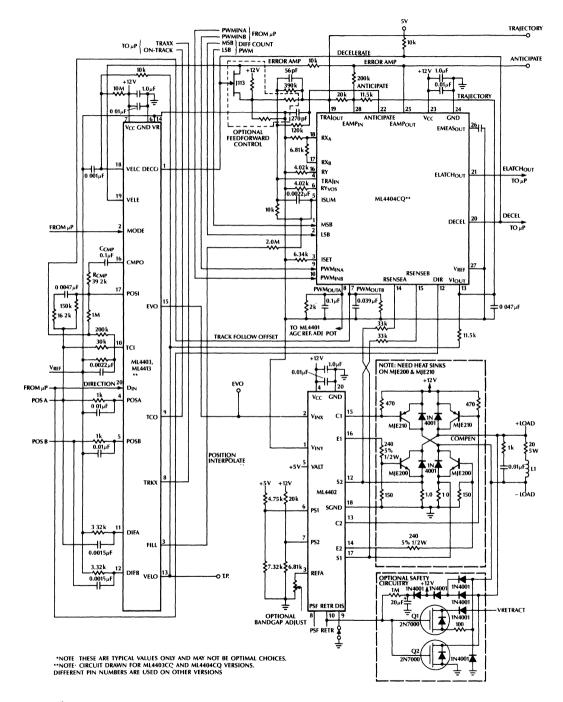

| ML4402 Servo Driver                              |      |

| ML4403 Servo Controller                          | 5-68 |

| ML4404 Trajectory Generator                      | 5-78 |

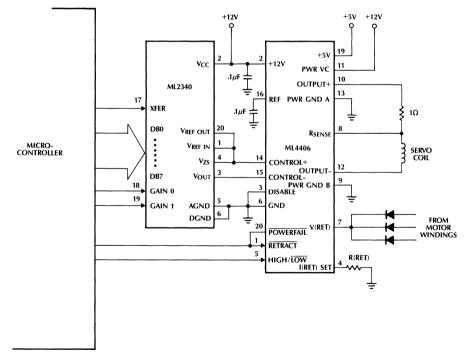

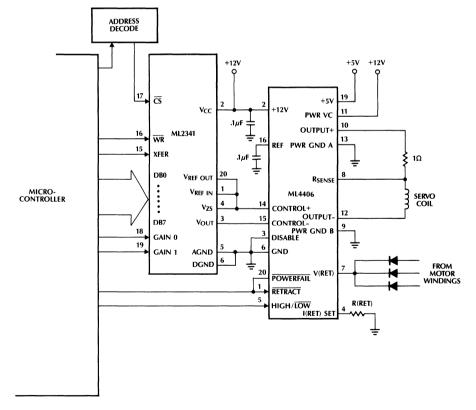

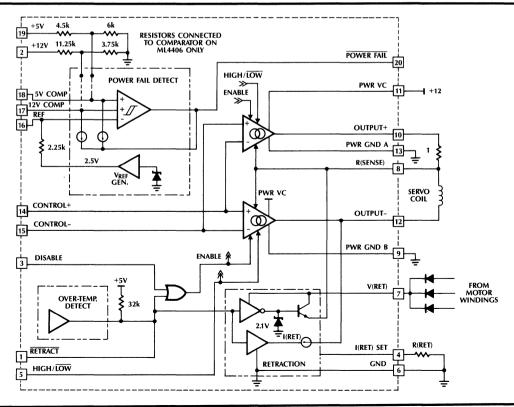

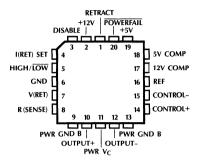

| ML4406 Disk Voice Coil Servo Driver                  | 5-89  |

|------------------------------------------------------|-------|

| ML4407 Disk Voice Coil Servo Driver                  | 5-89  |

| ML4408 Low Voltage Disk Voice Coil Servo Driver      | 5-95  |

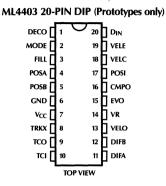

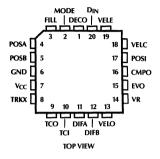

| ML4410 Sensorless Spindle Motor Controller           | 5-97  |

| ML4413 Servo Controller                              | 5-68  |

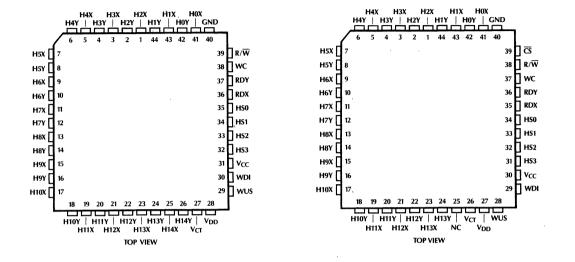

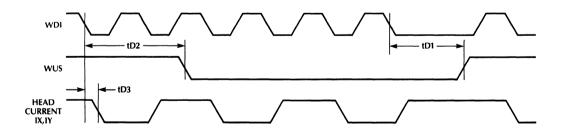

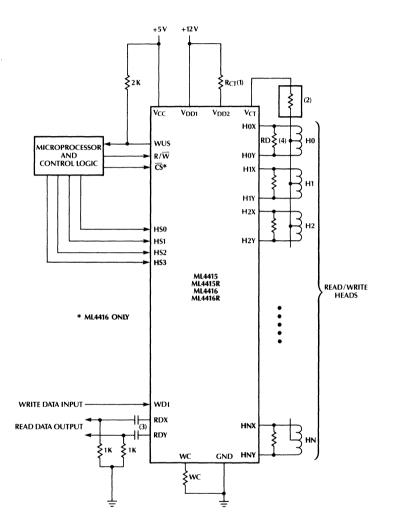

| ML4415 15-Channel Read/Write Circuit                 | 5-105 |

| ML4416 14-Channel Read/Write Circuit with CS         | 5-105 |

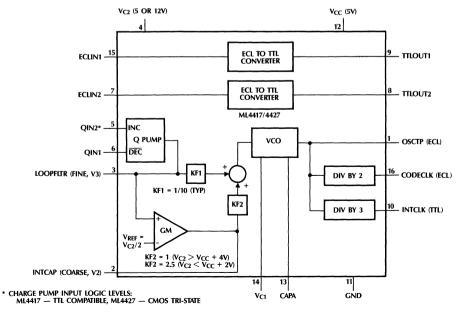

| ML4417 Zoned Bit Recording Circuit                   |       |

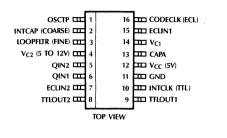

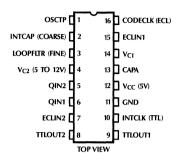

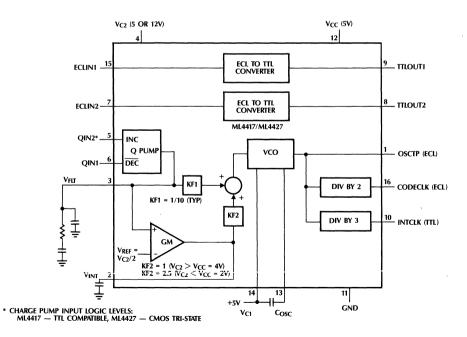

| ML4427 Zoned Bit Recording Circuit                   | 5-113 |

| ML4431 Servo Demodulator                             | 5-123 |

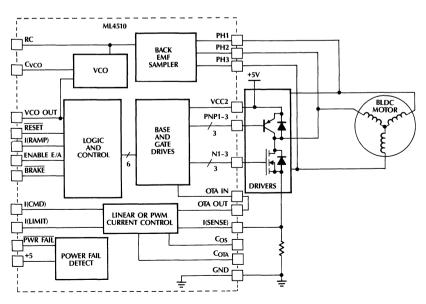

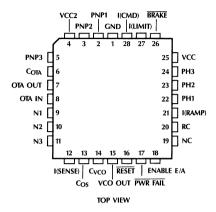

| ML4510 5V Sensorless Spindle Motor Controller        | 5-131 |

| ML4568 Disk Pulse Detector + Embedded Servo Detector | 5-133 |

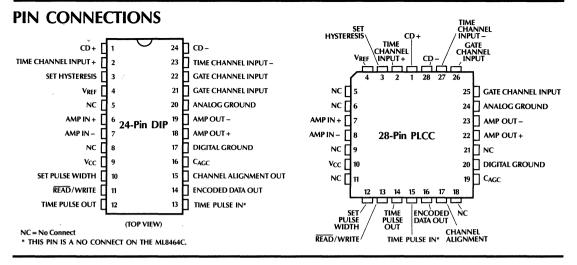

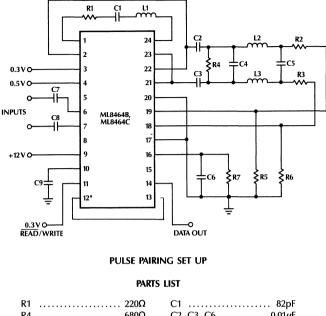

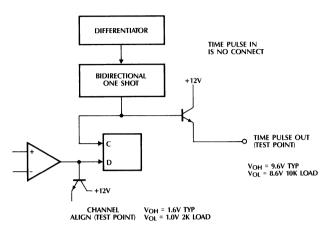

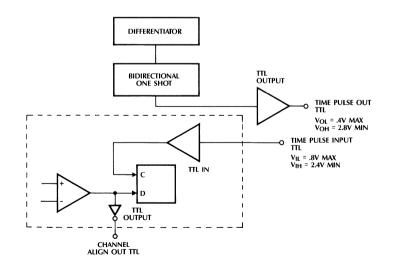

| ML8464B Pulse Detector                               | 5-141 |

| ML8464C Pulse Detector                               | 5-141 |

### SECTION 6 — POWER SUPPLIES

| Selection Guide                                      | 6-1   |

|------------------------------------------------------|-------|

| ML1825 High Frequency Power Supply Controller        | 6-2   |

| ML4809 High Frequency Current Mode PWM Controller    | 6-9   |

| ML4810 High Frequency Current Mode PWM Controllers   | 6-20  |

| ML4811 High Frequency Current Mode PWM Controllers   | 6-20  |

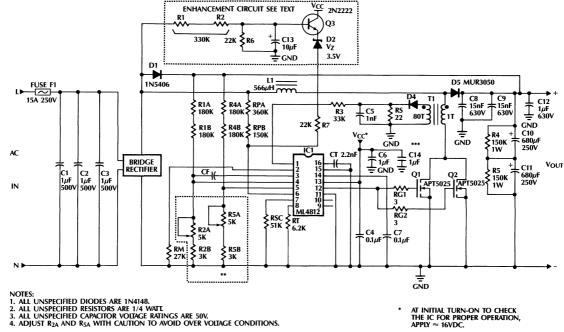

| ML4812 Power Factor Controller                       | 6-27  |

|                                                      |       |

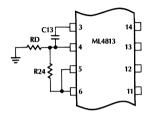

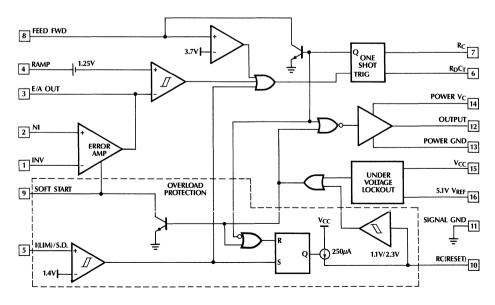

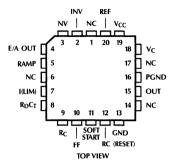

| ML4813 Flyback Power Factor Controller               | 6-42  |

| ML4815 Zero Voltage Switching Resonant Controller    | 6-54  |

| ML4816 High Frequency Multi-Mode Resonant Controller | 6-67  |

| ML4817 High Frequency Single-Ended PWM Controller    | 6-69  |

| ML4818 Phase Modulation/Soft Switching Controller    | 6-70  |

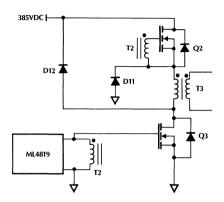

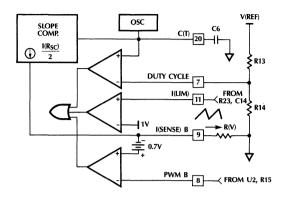

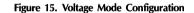

| ML4819 Power Factor and PWM Controller "Combo"       | 6-71  |

| ML4823 High Frequency Current Mode PWM Controllers   | 6-85  |

| ML4825 High Frequency Current Mode PWM Controllers   | 6-92  |

| FB3480 High Frequency Power Supply Controller Array  | 6-99  |

| FB3490 General Purpose PWM Controller Array          | 6-110 |

| FB3491 Resonant Mode Controller Array                |       |

| FB3492 Phase Modulation Controller Array             | 6-112 |

|                                                      |       |

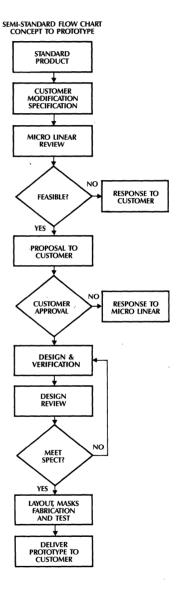

### SECTION 7 - USICS AND SEMI-STANDARD

|              | Semi-Standard Overview                                                  | 7-1   |

|--------------|-------------------------------------------------------------------------|-------|

|              | Analog and Mixed Analog/Digital Tile Arrays                             |       |

|              | FB3600 Tile Array Selection Guide                                       |       |

|              | FB3600 Mini Tile Description                                            |       |

|              | FB3605 Small High Frequency Tile Array                                  |       |

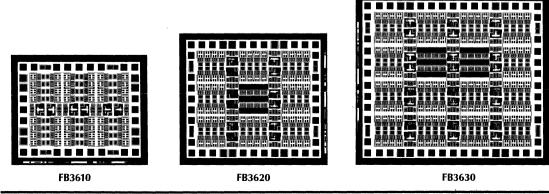

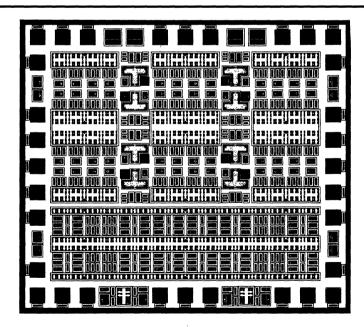

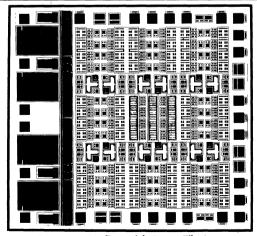

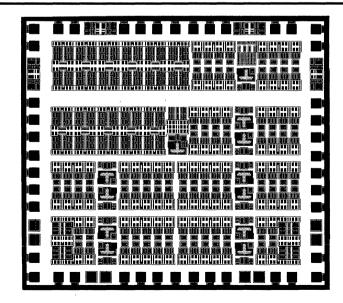

|              | FB3610 General Purpose Tile Array                                       |       |

|              | FB3620 General Purpose Tile Array                                       |       |

|              | FB3621 Medium High Frequency Tile Array                                 |       |

|              | FB3622 Medium Power Schottky Tile Array                                 |       |

|              | FB3623 Medium High Power Tile Array                                     |       |

|              | FB3630 General Purpose Tile Array                                       |       |

|              | FB3631 Large Mixed Analog/Digital Tile Array                            |       |

|              | FB3635 Large Mixed Analog/Digital Tile Array                            |       |

|              | FB3400 Tile Array Selection Guide                                       |       |

|              | FB3400 Mini Tile Description                                            |       |

|              | FB3410 Small General Purpose Tile Array                                 | 7-20  |

|              | FB3420 Medium General Purpose Tile Array                                |       |

|              | FB3430 Large General Purpose Tile Array                                 |       |

|              | USIC Package Selection Guide                                            | 7-21  |

| SECTION 8 —  | QUALITY AND RELIABILITY                                                 | 8-1   |

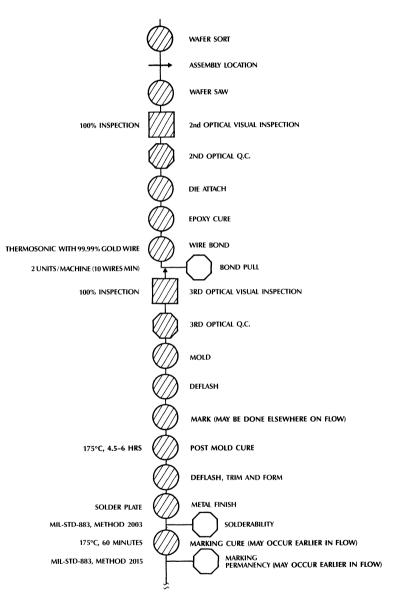

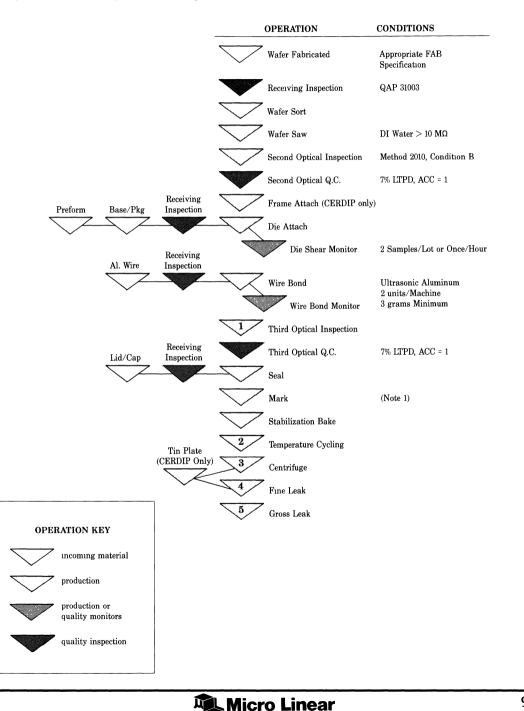

| SECTION 9 —  | /M8 MILITARY PRODUCT FLOW                                               | 9-1   |

| SECTION 10 - | APPLICATION NOTES                                                       |       |

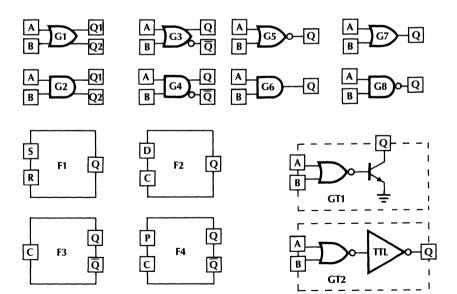

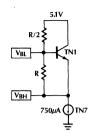

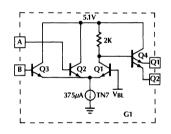

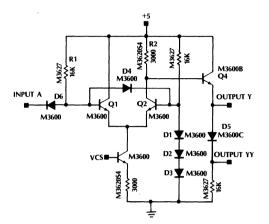

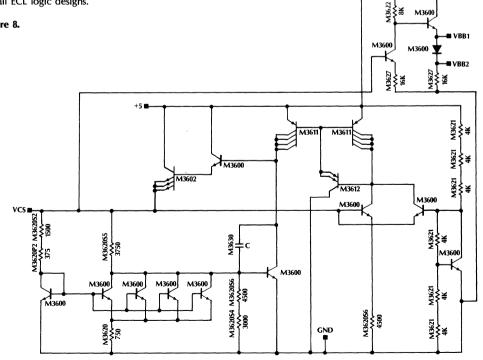

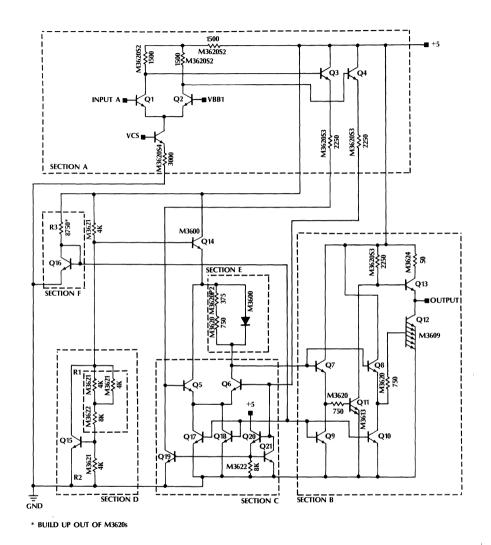

|              | Application Note 1 — FB3600 Digital Logic Design                        | 10-1  |

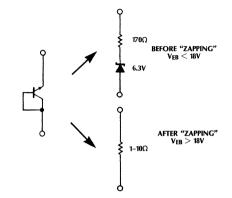

|              | Application Note 2 — Trimming Analog Bipolar Arrays                     | 10-8  |

|              | Application Note 3 — Design Techniques for Low Input Bias Current       | 10-11 |

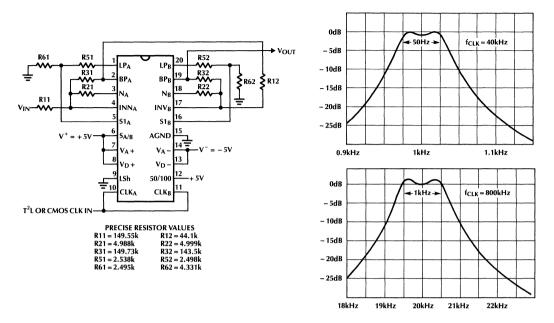

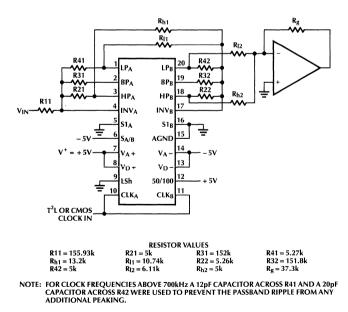

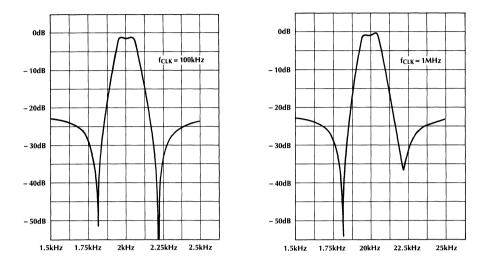

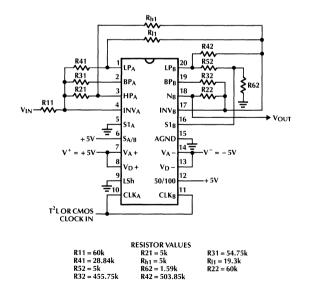

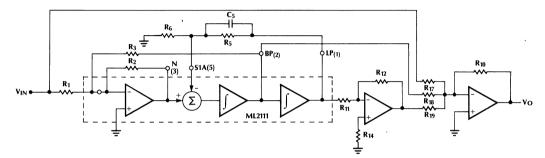

|              | Application Note 4 — High Freq. Complex Filter Design Using the ML2111  | 10-13 |

|              | Application Note 5 — ML2200, ML2208 Software Driver                     | 10-33 |

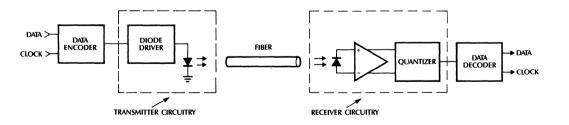

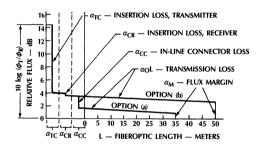

|              | Application Note 6 — Fiberoptics                                        | 10-37 |

|              | Application Note 7 — Expanding the ML2200 Input Multiplexer             | 10-49 |

|              | Application Note 8 — Micro Linear's One Pin Crystal Oscillators         | 10-54 |

|              | Application Note 10 — An Improved Method of Load Fault Detection        | 10-77 |

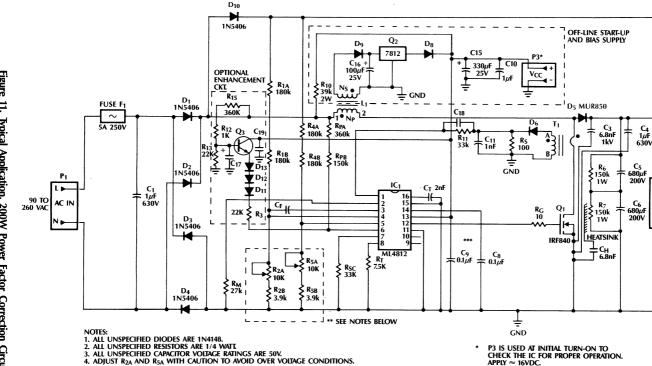

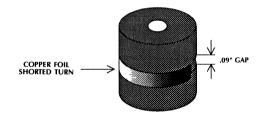

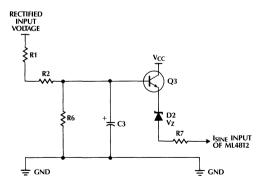

|              | Application Note 11 — Power Factor Enhancement Circuit                  | 10-79 |

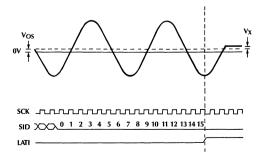

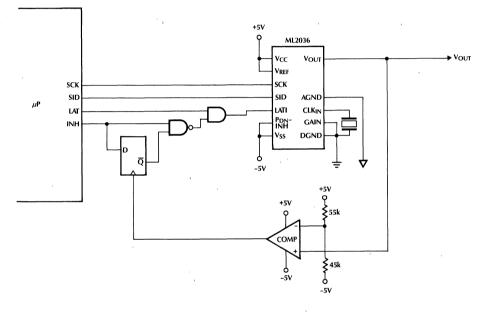

|              | Application Note 12 — Generating Phase Controlled Sinewaves with ML2036 | 10-81 |

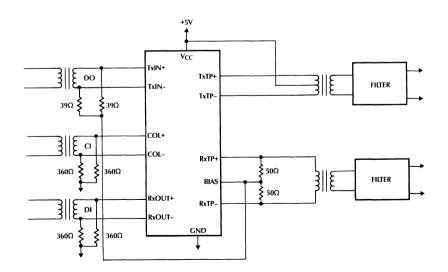

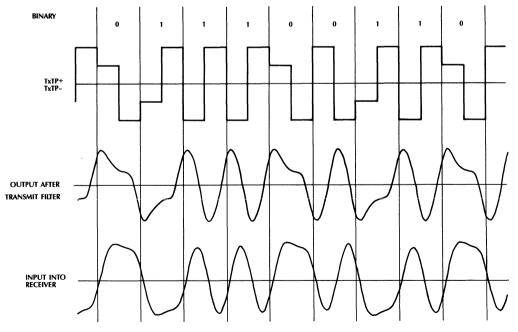

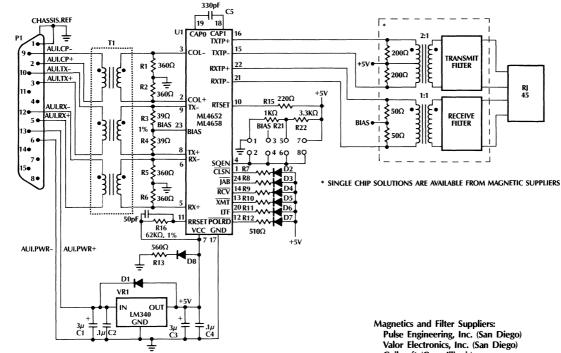

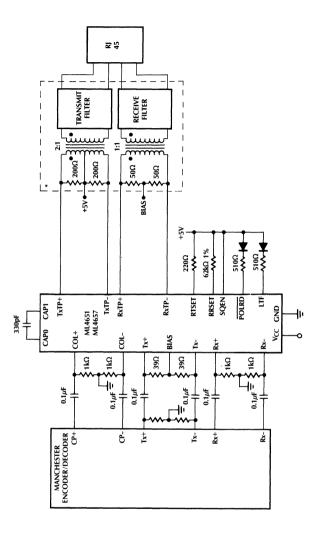

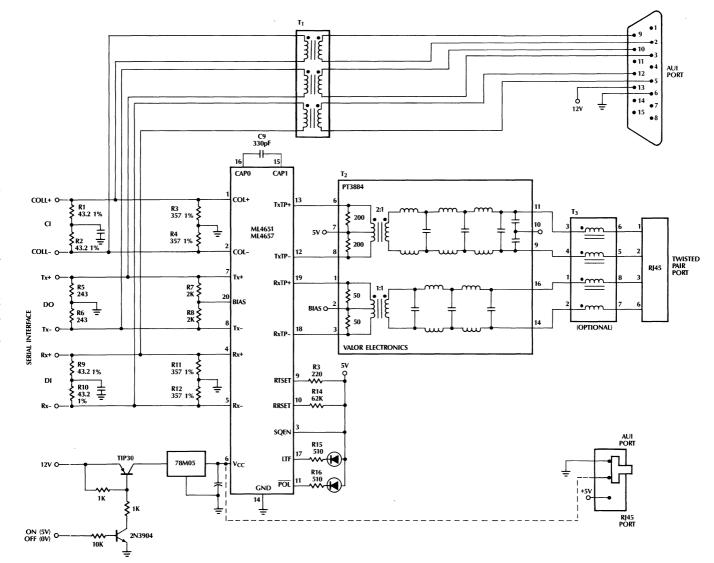

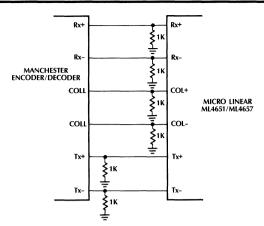

|              | Application Note 13 — Designing with 10BASE-T Transceivers              | 10-83 |

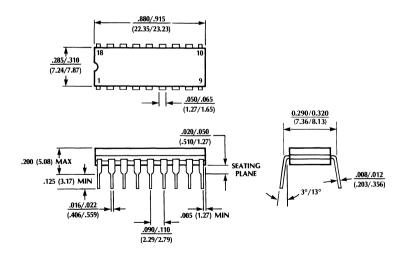

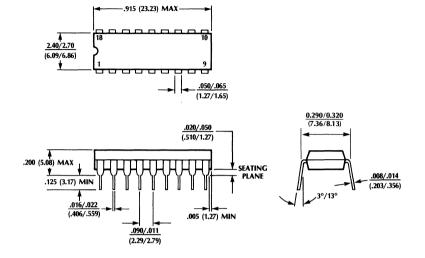

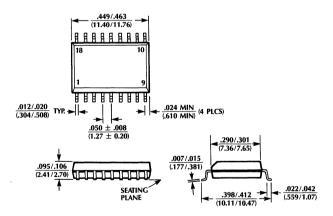

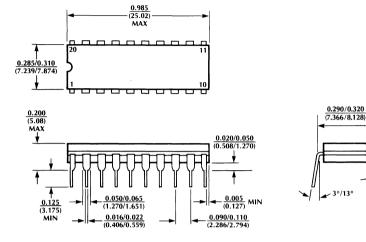

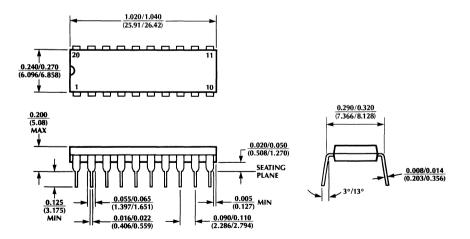

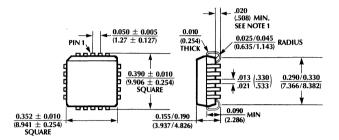

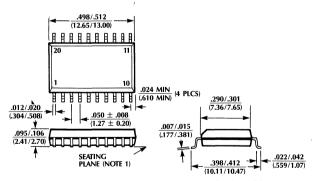

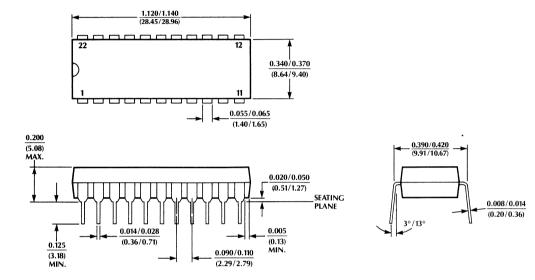

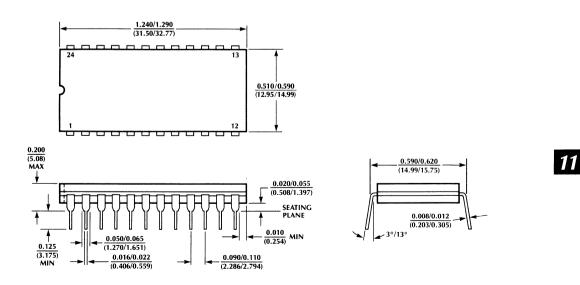

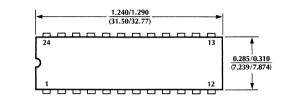

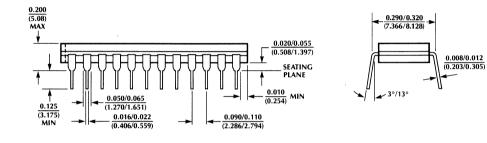

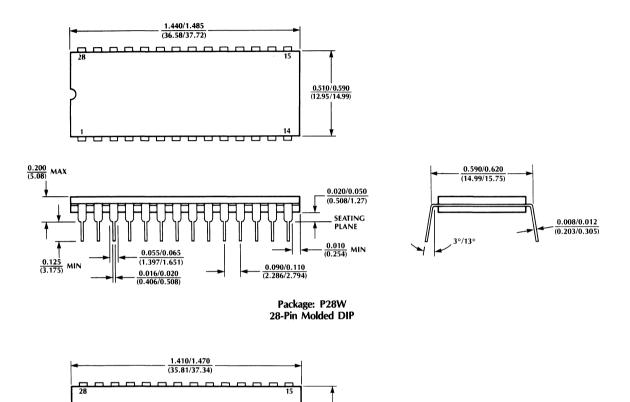

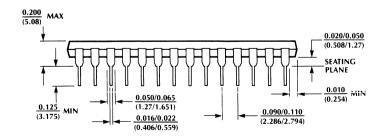

| SECTION 11 - | PACKAGING INFORMATION                                                   |       |

|              |                                                                         |       |

、私

# **General Information**

# Section 1

| General Ordering Information     | 1-1 |

|----------------------------------|-----|

| Alternate Source Cross Reference | 1-2 |

| Alpha Numeric Index              | 1-5 |

\$

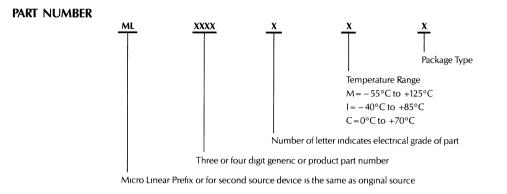

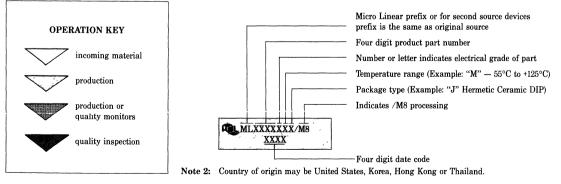

# Part Number and Package Type Explanation

### PACKAGE TYPE

| Letter Suffix | Description                         |

|---------------|-------------------------------------|

| D             | Side Brazed Hermetic DIP            |

| F             | Flat Pack                           |

| J             | Ceramic Hermetic DIP (CERDIP)       |

| L             | Ceramic Leadless Chip Carrier (LCC) |

| Р             | Plastic DIP                         |

| Q             | Plastic Chip Carrier (PCC)          |

| S             | Small Outline (SOIC)                |

# **Cross Reference Guide**

# **Alternate Source Part Number**

#### **Analog Devices**

| Analog Devices<br>Part Number | Micro Linear<br>Direct Replacement <sup>1</sup> |

|-------------------------------|-------------------------------------------------|

| AD7820BQ                      | ML2261CIJ                                       |

| AD7820CQ                      | ML2261BIJ                                       |

| AD7820KN                      | ML2261CCP                                       |

| AD7820KP                      | ML2261CCQ                                       |

| AD7820LN                      | ML2261BCP                                       |

| AD7820LP                      | ML2261BCQ                                       |

| AD7820TQ                      | ML2261CMJ                                       |

| AD7820UQ                      | ML2261BMJ                                       |

| AD7824BQ                      | ML2264CIJ                                       |

| AD7824CQ                      | ML2264BIJ                                       |

| AD7824KN                      | ML2264CCP                                       |

| AD7824LN                      | ML2264BCP                                       |

| AD7824TQ                      | ML2264CMJ                                       |

| AD7824UQ                      | ML2264BMJ                                       |

#### Exar

| Exar<br>Part Number | Micro Linear<br>Direct Replacement <sup>1</sup> |

|---------------------|-------------------------------------------------|

| XR117R-2CP          | ML117R-2CP                                      |

| XR117R-4CP          | ML117R-4CP                                      |

| XR117R-4MD          | ML117R-4CS                                      |

| XR117R-6CJ          | ML117R-6CQ                                      |

| XR117R-6CP          | ML117R-6CP                                      |

| XR117R-6MD          | ML117R-6CS                                      |

| XR117-2CN           | ML117-2CJ                                       |

| XR117-2CP           | ML117-2CP                                       |

| XR117-2MD           | ML117-2CS                                       |

| XR117-4CN           | ML117-4CJ                                       |

| XR117-4CP           | ML117-4CP                                       |

| XR117-4MD           | ML117-4CS                                       |

| XR117-6CJ           | ML117-6CQ                                       |

| XR117-6CN           | ML117-6CJ                                       |

| XR117-6CP           | ML117-6CP                                       |

| XR117-6MD           | ML117-6CS                                       |

#### Linear Technology

| LTC<br>Part Number | Micro Linear<br>Direct Replacement <sup>1</sup> |

|--------------------|-------------------------------------------------|

| LTC1060ACJ         | ML2110BIJ <sup>2</sup>                          |

| LTC1060ACN         | ML2110BCP <sup>2</sup>                          |

| LTC1060AMJ         | ML2110BMJ <sup>2</sup>                          |

| LTC1060CJ          | ML2110CIJ <sup>2</sup>                          |

| LTC1060CN          | ML2110CCP2                                      |

| LTC1060MJ          | ML2110CMJ <sup>2</sup>                          |

### National Semiconductor

| NSC<br>Part Number | Micro Linear<br>Direct Replacement <sup>1</sup> |

|--------------------|-------------------------------------------------|

| ADC0808CI          | ADC0808CI                                       |

|                    | ML2258BMI                                       |

| ADC0808CCJ         | ADC0808CCJ                                      |

|                    | ML2258BIJ                                       |

| ADC0808CCV         | ADC0808CCV                                      |

| ADCOUCCE           | ML2258BIQ                                       |

| ADC0809CCN         | ADC0808CCN                                      |

| ADCOODEEN          | ML2258CIP                                       |

| ADC0809CCV         | ADC0809CCV                                      |

| ADC0009CCV         | ML2258CIQ                                       |

| ADC0820BCI         |                                                 |

| ADC0820BCJ         | ML2261BIJ                                       |

| ADC0820BCN         | ML2261BCP                                       |

| ADC0820BCV         | ML2261BCQ                                       |

| ADC0820CCJ         | ML2261CIJ                                       |

| ADC0820CCN         | ML2261CCP                                       |

| ADC0820CCV         | ML2261CCQ                                       |

| ADC0820CJ          | ML2261CMJ                                       |

| ADC0831BCJ         | ADC0831BCJ                                      |

|                    | ML2281BIJ                                       |

| ADC0831BCN         | ADC0831BCN                                      |

|                    | ML2281BCP                                       |

| ADC0831CCJ         | ADC0831CCJ                                      |

|                    | ML2281CIJ                                       |

| ADC0831CCN         | ADC0831CCN                                      |

| / Decosteen        | ML2281CCP                                       |

| ADC0832BCJ         | ADC0832BCJ                                      |

| ADC0052DCJ         | ML2282BIJ                                       |

| ADC0832BCN         | ADC0832BCN                                      |

| ADC0032BCN         | ML2282BCP                                       |

| ADC0022CCI         |                                                 |

| ADC0832CCJ         | ADC0832CCJ                                      |

|                    | ML2282CIJ                                       |

| ADC0832CCN         | ADC0832CCN                                      |

|                    | ML2282CCP                                       |

| ADC0833BCJ         | ADC0833BCJ                                      |

|                    | ML2283BIJ                                       |

| ADC0833BCN         | ADC0833BCN                                      |

|                    | ML2283BCP                                       |

| ADC0833CCJ         | ADC0833CCJ                                      |

|                    | ML2283CIJ                                       |

| ADC0833CCN         | ADC0833CCN                                      |

|                    | ML2283CCP                                       |

| ADC0834BCJ         | ADC0834BCJ                                      |

| ·                  | ML2284BIJ                                       |

| ADC0834BCN         | ADC0834BCN                                      |

|                    | ML2284BCP                                       |

Note 1. 100% pin-for-pin compatible with improved electrical specifications.

Note 2. Consult data sheet for electrical specifications that may vary from limit or conditions of alternate source.

Note 3. Alternate source ships -40°C to +85°C product as molded; Micro Linear does this on a customer need basis.

| National | Semiconductor | (Continued) |

|----------|---------------|-------------|

|----------|---------------|-------------|

| National Semiconductor (Continued) |                                 | Silicon Systems, Inc. |                                 |  |

|------------------------------------|---------------------------------|-----------------------|---------------------------------|--|

| NSC                                | Micro Linear                    | SSI                   | Micro Linear                    |  |

| Part Number                        | Direct Replacement <sup>1</sup> | Part Number           | Direct Replacement <sup>1</sup> |  |

| ADC0834CCJ                         | ADC0834CCJ                      | SSI 32P541-CH         | ML541CQ                         |  |

|                                    | ML2284CIJ                       | SSI 32P541-P          | ML541CP                         |  |

| ADC0834CCN                         | ADC0834CCN                      | SSI 32P541A-CH        | ML4042CQ                        |  |

|                                    | ML2284CCP                       | SSI 32P541A-P         | ML4042CP                        |  |

| ADC0838BCI                         | ADC0838BCJ                      | SSI 32P541B-CH        | ML4042CQ                        |  |

|                                    | ML2288BI                        | SSI 32P541B-P         | ML4042CP                        |  |

| ADC0838BCN                         | ADC0838BCN                      | SSI 32R117R-2P        | ML117R-2CP                      |  |

|                                    | ML2288BCP                       | SSI 32R117R-4F        | ML117R-4CF                      |  |

| ADC0838BCV                         | ADC0838BCV                      | SSI 32R117R-4P        | ML117R-4CP                      |  |

|                                    | ML2288BCQ                       | SSI 32R117R-6F        | ML117R-6CF                      |  |

| ADC0838CCI                         | ADC0838CCI                      | SSI 32R117R-6H        | ML117R-6CQ                      |  |

|                                    | ML2288CIJ                       | SSI 32R117R-6P        | ML117R-6CP                      |  |

| ADC0838CCN                         | ADC0838CCN                      | SSI 32R117-2P         | ML117-2CP                       |  |

|                                    | ML2288CCP                       | SSI 32R117-4F         | ML117-4CF                       |  |

| ADC0838CCV                         | ADC0838CCV                      | SSI 32R117-4P         | ML117-4CP                       |  |

|                                    | ML2288CCQ                       | SSI 32R117-6F         | ML117-6CF                       |  |

| ADC1061CI                          | ML2271CI                        | SSI 32R117-6H         | ML117-6CQ                       |  |

| ADC1061CIN                         | ML2271CCP <sup>3</sup>          | SSI 32R117-6P         | ML117-6CP                       |  |

| ADC1061CIWM                        | ML2271CCS <sup>3</sup>          | SSI 32R501R-6H        | ML501R-6CQ                      |  |

| ADC1061CMJ                         | ML2271CMJ                       | SSI 32R501R-8F        | ML501R-8CF                      |  |

| DP5016QC                           | ML501-6CQ                       | SSI 32R501R-8H        | ML501R-8CO                      |  |

| DP5016RQC                          | ML501R-6CQ                      | SSI 32R501R-8P        | ML501R-8CP                      |  |

| DP5018QC                           | ML501-8CQ                       | SSI 32R501-6H         | ML501-6CQ                       |  |

| DP5018RQC                          | ML501R-8CQ                      | SSI 32R501-8F         | ML501-8CF                       |  |

| µA5016OC                           | ML501-6CO                       | SSI 32R501-8H         | ML501-8CQ                       |  |

| μA5016RQC                          | ML501R-6CQ                      | SSI 32R501-8P         | ML501-8CP                       |  |

| μA5018QC                           | ML501-8CQ                       | SSI 32R511R-4S        | ML511R-4CS                      |  |

| μA5018ROC                          | ML501R-8CO                      | SSI 32R511R-6H        | ML511R-6CQ                      |  |

| DP8464BN-3                         | ML8464B-3CP <sup>2</sup>        | SSI 32R511R-6P        | ML511R-6CP                      |  |

| DP8464BV-3                         | ML8464B-3CQ <sup>2</sup>        | SSI 32R511R-6S        | ML511R-6CS                      |  |

| DP8464BN-2                         | ML8464B-2CP <sup>2</sup>        | SSI 32R511R-8H        | ML511R-8CQ                      |  |

| DP8464BV-2                         | ML8464B-2CQ <sup>2</sup>        | SSI 32R511R-8P        | ML511R-8CP                      |  |

| DP8464BN-2                         | ML8464B-2CP <sup>2</sup>        | SSI 32R511R-8S        | ML511R-8CS                      |  |

| DP8464BN-3                         | ML8464B-3CP <sup>2</sup>        | SSI 32R511-4S         | ML511-4CS                       |  |

| DP8464BV-2                         | ML8464B-2CQ <sup>2</sup>        | SSI 32R511-6H         | ML511-6CQ                       |  |

| DP8464BV-3                         | ML8464B-3CO <sup>2</sup>        | SSI 32R511-6P         | ML511-6CP                       |  |

| DP8468BTP-3                        | ML4568-3CQ <sup>2</sup>         | SSI 32R511-6S         | ML511-6CS                       |  |

| DP8468BTP-2                        | ML4568-2CQ <sup>2</sup>         | SSI 32R511-8H         | ML511-8CQ                       |  |

| LMF100CCN                          | ML2111CCP                       | SSI 32R511-8P         | ML511-8CP                       |  |

| LMF100CCWM                         | ML2111CCS                       | SSI 32R511-8S         | ML511-8CS                       |  |

| MF10AI                             | ML2110CMJ <sup>2</sup>          |                       |                                 |  |

| MF10ACN                            | ML2110BCP <sup>2</sup>          |                       |                                 |  |

| MF10CCI                            | ML2110CII <sup>2</sup>          |                       |                                 |  |

| MF10CCWM                           | ML2110CCS <sup>2</sup>          |                       |                                 |  |

| MF10CCN                            | ML2110CCP <sup>2</sup>          |                       |                                 |  |

|                                    |                                 | 1                     |                                 |  |

Silicon Systems, Inc.

Note 1. 100% pin-for-pin compatible with improved electrical specifications.

Note 2. Consult data sheet for electrical specifications that may vary from limit or conditions of alternate source.

Note 3. Alternate source ships -40°C to +85°C product as molded; Micro Linear does this on a customer need basis.

#### **Texas Instruments**

| NSC<br>Part Number | Micro Linear<br>Direct Replacement <sup>1</sup> |

|--------------------|-------------------------------------------------|

| ADC0808MI          | ML2258BMI                                       |

| ADC0808FN          | ML2258BCO                                       |

| ADC0808N           | ML2258BIP                                       |

| ADC0809FN          | ML2258CCQ                                       |

| ADC0809N           | ML2258CIP                                       |

| TLC0820ACN         | ML2261CCP                                       |

| TLC0820ACFN        | ML2261CCQ                                       |

| TLC0820BCN         | ML2261BCP                                       |

| TLC0820BCFN        | ML2261BCQ                                       |

| ADC0831ACP         | ML2281CCP                                       |

| ADC0831AIP         | ML2281CIJ <sup>3</sup>                          |

| ADC0831BCP         | ML2281BCP                                       |

| ADC0831BIP         | ML2281BIJ <sup>3</sup>                          |

| ADC0832ACP         | ML2282CCP                                       |

| ADC0832AIP         | ML2282CIJ <sup>3</sup>                          |

| ADC0832BCP         | ML2282BCP                                       |

| ADC0832BIP         | ML2282BIJ <sup>3</sup>                          |

| ADC0834ACN         | ML2284CCP                                       |

| ADC0834AIN         | ML2284CIJ <sup>3</sup>                          |

| ADC0834BCN         | ML2284BCP                                       |

| ADC0834BIN         | ML2284BIJ <sup>3</sup>                          |

| ADC0838ACN         | ML2288CCP                                       |

| ADC0838AIN         | ML2288CIJ <sup>3</sup>                          |

| ADC0838CCN         | ML2288BCP                                       |

| ADC0838BIN         | ML2288BIJ <sup>3</sup>                          |

| VTC         | Micro Linear       |

|-------------|--------------------|

| Part Number | Direct Replacement |

| VM117-2DK   | ML117-2CJ          |

| VM117-2PK   | ML117-2CP          |

| VM117-4FK   | ML117-4CF          |

| VM117-4PK   | ML117-4CP          |

| VM117-4DK   | ML117-4CJ          |

| VM117-6PK   | ML117-6CP          |

| VM117-6DK   | ML117-6CJ          |

| VM117-6PK   | ML117-6CP          |

| VM117-6PLK  | ML117-6CQ          |

| VM117R-2DK  | ML117R-2CJ         |

| VM117R-2PK  | ML117R-2CP         |

| VM117R-4FK  | ML117R-4CF         |

| VM117R-4PK  | ML117R-4CP         |

| VM117R-4DK  | ML117R-4CJ         |

| VM117R-6DK  | ML117R-6CJ         |

| VM117R-6PK  | ML117R-6CP         |

| VM117-6PLK  | ML117R-6CQ         |

| VM217-6PK   | ML501-6CP          |

| VM217-6PLK  | ML501-6CQ          |

| VM217-8PK   | ML501-8CP          |

| VM217-8PLK  | ML501-8CQ          |

#### Unitrode

| Unitrode<br>Part Number | Micro Linear<br>Direct Replacement <sup>1</sup> |

|-------------------------|-------------------------------------------------|

| UC1823J                 | ML4823MJ                                        |

| UC1825J                 | ML4825MJ                                        |

| UC2823N                 | ML4823IP                                        |

| UC2823Q                 | ML4823IQ                                        |

| UC2825N                 | ML4825IP                                        |

| UC2825Q                 | ML4825IQ                                        |

| UC3823N                 | ML4823IP                                        |

| UC3823Q                 | ML4823CQ                                        |

| UC3825N                 | ML4825IP                                        |

| UC3825Q                 | ML4825CQ                                        |

Note 1. 100% pin-for-pin compatible with improved electrical specifications.

Note 2. Consult data sheet for electrical specifications that may vary from limit or conditions of alternate source.

Note 3. Alternate source ships -40°C to +85°C product as molded; Micro Linear does this on a customer need basis.

# Alpha Numeric Index

### PAGE

| FB3410 | Small General Purpose Tile Array                                                  | 7-20  |

|--------|-----------------------------------------------------------------------------------|-------|

| FB3420 | Medium General Purpose Tile Array                                                 | 7-20  |

| FB3430 | Large General Purpose Tile Array                                                  | 7-20  |

| FB3480 | High Frequency Power Supply Controller Array                                      | 6-99  |

| FB3490 | General Purpose PWM Controller Array                                              | 6-110 |

| FB3491 | Resonant Mode Controller Array                                                    | 6-111 |

| FB3492 | Phase Modulation Controller Array                                                 | 6-112 |

| FB3605 | Small High Frequency Tile Array                                                   | 7-11  |

| FB3610 | General Purpose Tile Arrays                                                       | 7-12  |

| FB3620 | General Purpose Tile Arrays                                                       | 7-12  |

| FB3621 | Medium High Frequency Tile Array                                                  | 7-13  |

| FB3622 | Medium Power Schottky Tile Array                                                  | 7-14  |

| FB3623 | Medium High Power Tile Array                                                      | 7-15  |

| FB3630 | General Purpose Tile Arrays                                                       | 7-12  |

| FB3631 | Large Mixed Analog/Digital Tile Array                                             | 7-16  |

| FB3635 | Mixed Analog/Digital Tile Array                                                   |       |

| FB3651 | LAN Transceiver Array                                                             | 4-46  |

| ML117  | 2, 4, or 6-Channel Read/Write Circuits                                            | 5-3   |

| ML117R | 2, 4, or 6-Channel Read/Write Circuits with Damping Resistors                     | 5-3   |

| ML501  | 6, 7, or 8-Channel Read/Write Circuits                                            | 5-11  |

| ML501R | 6, 7, or 8-Channel Read/Write Circuits with Damping Resistors                     | 5-11  |

| ML502  | 6, 7, or 8-Channel Read/Write Circuits for Thin Film Heads                        | 5-11  |

| ML502R | 6, 7, or 8-Channel Read/Write Circuits for Thin Film Heads with Damping Resistors | 5-11  |

| ML502S | 6, 7, or 8-Channel Read/Write Circuits                                            | 5-11  |

| ML511  | 4, 6, 7, or 8-Channel Read/Write Circuits                                         | 5-19  |

| ML511R | 4, 6, 7, or 8-Channel Read/Write Circuits with Damping Resistors                  | 5-19  |

| ML541  | Read Data Processor                                                               | 5-27  |

| ML1825 | High Frequency Power Supply Controller                                            | 6-2   |

| ML2003 | Logarithmic Gain/Attenuator                                                       | 3-2   |

| ML2004 | Logarithmic Gain/Attenuator                                                       | 3-2   |

| ML2008 | μP Compatible Logarithmic Gain/Attenuator                                         | 3-13  |

| ML2009 | μP Compatible Logarithmic Gain/Attenuator                                         | 3-13  |

| ML2020 | Telephone Line Equalizer                                                          | 3-22  |

| ML2021 | Telephone Line Equalizer                                                          | 3-33  |

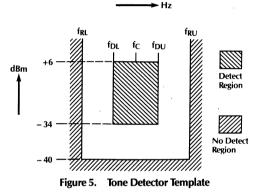

| ML2031 | Programmable Tone Detector                                                        | 3-44  |

| ML2032 | Programmable Tone Detector                                                        | 3-44  |

| ML2035 | Programmable Sinewave Generator                                                   | 3-52  |

| ML2036 | Programmable Sinewave Generator                                                   | 3-52  |

| ML2110   | Universal Dual Switched Capacitor Filter                                          | 3-64  |

|----------|-----------------------------------------------------------------------------------|-------|

| ,        |                                                                                   |       |

| ML2111   | Universal Hi-Frequency Dual Filter                                                | 3-83  |

| ML2200   | Data Acquisition Peripheral                                                       | 2-5   |

| ML2200EX | Exerciser                                                                         | 2-23  |

| ML2208   | Data Acquisition Peripheral                                                       | 2-5   |

| ML2208EX | Exerciser                                                                         | 2-23  |

| ML2221   | Serial Out 12-Bit Plus Sign A/D Converter with Sample and Hold                    | 2-35  |

| ML2222   | Serial CODEC/DSP Interface 12-Bit Plus Sign A/D Converter with Sample and Hold    | 2-49  |

| ML2223   | Serial Asynchronous Interface 12-Bit Plus Sign A/D Converter with Sample and Hold | 2-50  |

| ML2230   | $\mu$ P Compatible 12-Bit Plus Sign A/D Converter with Sample and Hold            | 2-51  |

| ML2233   | μP Compatible 12-Bit Plus Sign A/D Converter with Sample and Hold                 | 2-67  |

| ML2252   | $\mu$ P Compatible 8-Bit A/D Converter with 2-Channel Multiplexer                 | 2-83  |

| ML2258   | μP Compatible 8-Bit A/D Converter with 8-Channel Multiplexer                      | 2-94  |

| ML2259   | $\mu$ P Compatible 8-Bit A/D Converter with 8-Channel Multiplexer                 | 2-83  |

| ML2261   | μP Compatible High Speed 8-Bit A/D Converter with T/H (S/H)                       | 2-105 |

| ML2264   | 4-Channel High Speed 8-Bit A/D Converter with T/H (S/H)                           | 2-120 |

| ML2271   | μP Compatible High Speed 10-Bit A/D Converter with S/H                            | 2-135 |

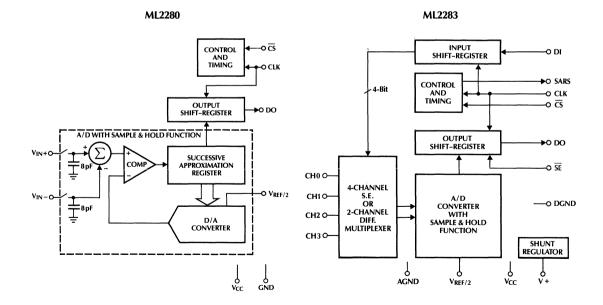

| ML2280   | 8-Bit Serial I/O A/D Converter                                                    | 2-148 |

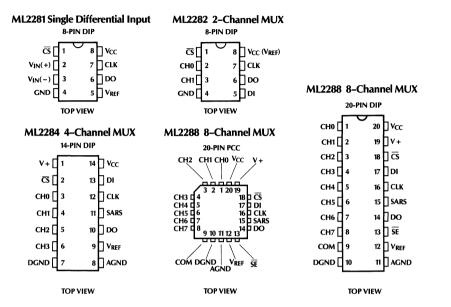

| ML2281   | 8-Bit Serial A/D Converter                                                        | 2-166 |

| ML2282   | 8-Bit Serial A/D Converter with 2-Channel Multiplexer                             | 2-166 |

| ML2283   | 8-Bit Serial A/D Converter with 4-Channel Multiplexer                             | 2-148 |

| ML2284   | 8-Bit Serial A/D Converter with 4-Channel Multiplexer                             | 2-166 |

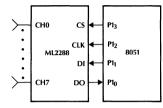

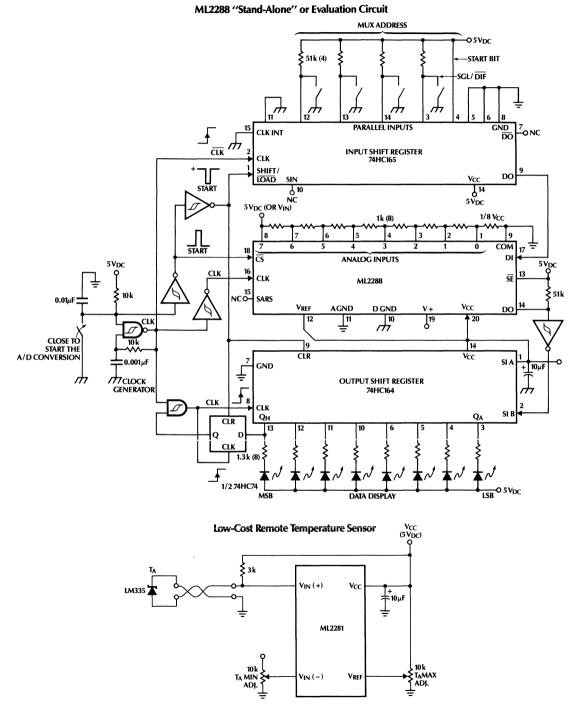

| ML2288   | 8-Bit Serial A/D Converter with 8-Channel Multiplexer                             | 2-166 |

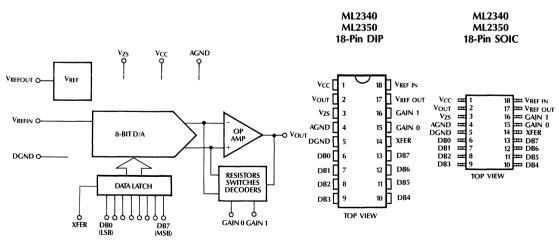

| ML2340   | 8-Bit D/A Converter with Programmable Gain and Reference                          | 2-186 |

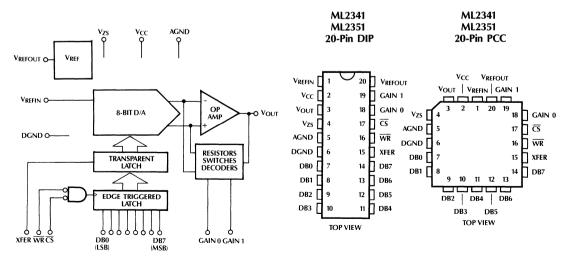

| ML2341   | 8-Bit D/A Converter with Programmable Gain and Reference                          | 2-197 |

| ML2350   | 8-Bit D/A Converter with Programmable Gain and Reference                          | 2-186 |

| ML2351   | 8-Bit D/A Converter with Programmable Gain and Reference                          | 2-197 |

| ML4025   | Data Separator                                                                    | 5-37  |

| ML4041   | Read Data Processor                                                               | 5-46  |

| ML4042   | Read Data Processor                                                               | 5-46  |

| ML4401   | Servo Demodulator                                                                 | 5-57  |

| ML4402   | Servo Driver                                                                      | 5-63  |

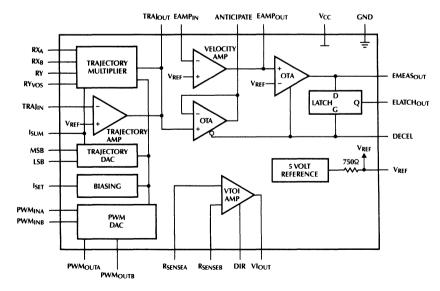

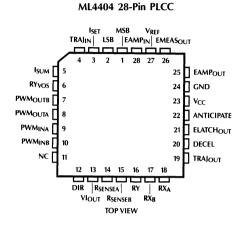

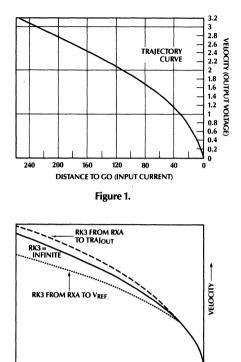

| ML4403   | Servo Controller                                                                  | 5-68  |

| ML4404   | Trajectory Generator                                                              | 5-78  |

| ML4406   | Disk Voice Coil Servo Driver                                                      | 5-89  |

| ML4407   | Disk Voice Coil Servo Driver                                                      | 5-89  |

| ML4408   | Low Voltage Disk Voice Coil Servo Driver                                          | 5-95  |

| ML4410   | Sensorless Spindle Motor Controller                                               | 5-97  |

| ML4413   | Servo Controller                                                                  | 5-68  |

| ML4415   | 15-Channel Read/Write Circuit                                                     | 5-105 |

| ML4416   | 14-Channel Read/Write Circuit wtih CS                                             | 5-105 |

| ML4417   | Zoned Bit Recording Circuit                                                       | 5-113 |

| ML4427   | Zoned Bit Recording Circuit                                                       | 5-113 |

| ML4431   | Servo Demodulator                                                                 | 5-123 |

| ML4510  | 5V Sensorless Spindle Motor Controller        | 5-131 |

|---------|-----------------------------------------------|-------|

| ML4568  | Disk Pulse Detector + Embedded Servo Detector | 5-133 |

| ML4621  | Fiberoptic Data Quantizer                     | 4-2   |

| ML4622  | Fiberoptic Data Quantizer                     | 4-2   |

| ML4651  | 10BASE-T Transceiver                          | 4-10  |

| ML4652  | 10BASE-T Transceiver                          | 4-10  |

| ML4654  | 10BASE-T Transceiver for Multi-Port Repeaters | 4-26  |

| ML4657  | 10BASE-T Transceiver with Autopolarity        | 4-10  |

| ML4658  | 10BASE-T Transceiver with Autopolarity        | 4-10  |

| ML4661  | FOIRL Transceiver                             | 4-36  |

| ML4809  | High Frequency Current Mode PWM Controller    | 6-9   |

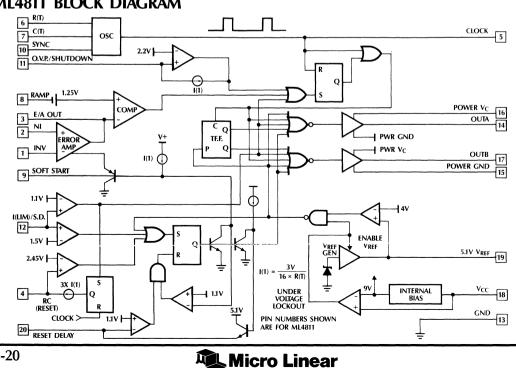

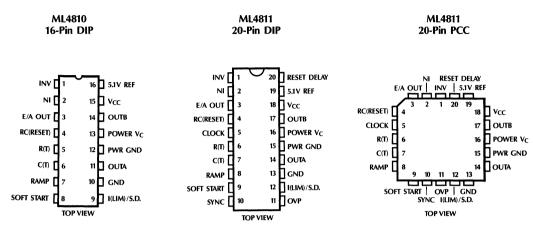

| ML4810  | High Frequency Current Mode PWM Controller    | 6-20  |

| ML4811  | High Frequency Current Mode PWM Controller    | 6-20  |

| ML4812  | Power Factor Controller                       | 6-27  |

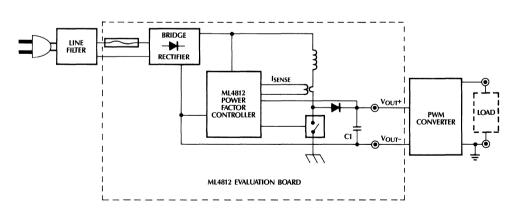

| ML4812  | Power Factor Controller Evaluation Kit        | 6-41  |

| ML4813  | Flyback Power Factor Controller               | 6-42  |

| ML4815  | Zero Voltage Switching Resonant Controller    | 6-54  |

| ML4816  | High Frequency Multi-Mode Resonant Controller | 6-67  |

| ML4817  | High Frequency Single-Ended PWM Controller    | 6-69  |

| ML4818  | Phase Modulation/Soft Switching Controller    | 6-70  |

| ML4819  | Power Factor and PWM Controller "Combo"       | 6-71  |

| ML4823  | High Frequency Current Mode PWM Controller    | 6-85  |

| ML4825  | High Frequency Current Mode PWM Controller    | 6-92  |

| ML8464B | Pulse Detector                                | 5-141 |

| ML8464C | Pulse Detector                                | 5-141 |

|         |                                               |       |

1

# A/D Converters, D/A Converters

# Section 2

| Selection Guide                                                                              | 2-1   |

|----------------------------------------------------------------------------------------------|-------|

| ML2200 12-Bit + Sign Data Acquisition Peripheral                                             | 2-5   |

| ML2208 12-Bit + Sign Data Acquisition Peripheral                                             | 2-5   |

| ML2200EX, ML2208EX Exerciser                                                                 | 2-33  |

| ML2221 Serial Peripheral Interface 12-Bit Plus Sign A/D Converter                            |       |

| with Sample & Hold                                                                           | 2-35  |

| ML2222 Serial CODEC/DSP Interface 12-Bit Plus Sign A/D Converter                             |       |

| with Sample & Hold                                                                           | 2-49  |

| ML2223 Serial Asynchronous Interface 12-Bit Plus Sign A/D Converter                          |       |

| with Sample & Hold                                                                           | 2-50  |

| ML2230 $\mu P$ Compatible 12-Bit Plus Sign A/D Converter with Sample and Hold $\ldots$       | 2-51  |

| ML2233 $\mu P$ Compatible 12-Bit Plus Sign A/D Converter with Sample and Hold $\ldots$       | 2-67  |

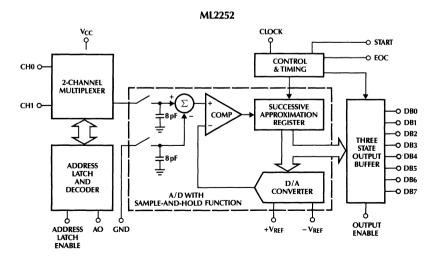

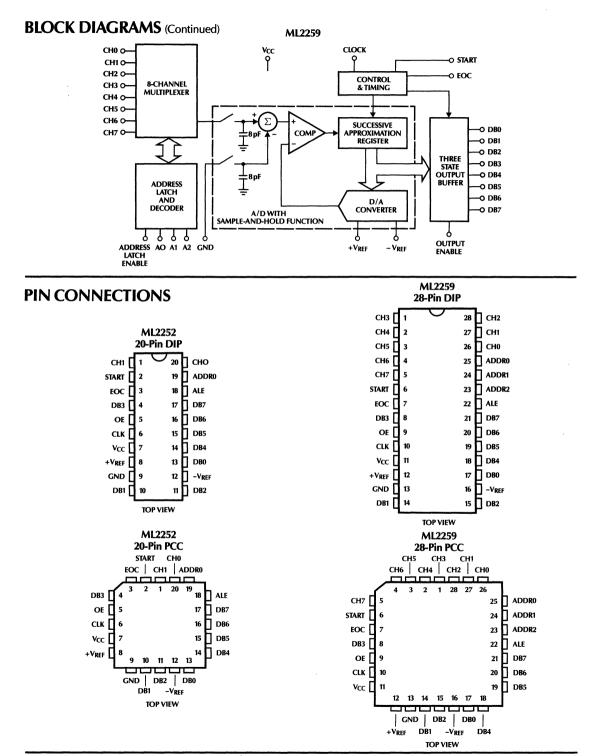

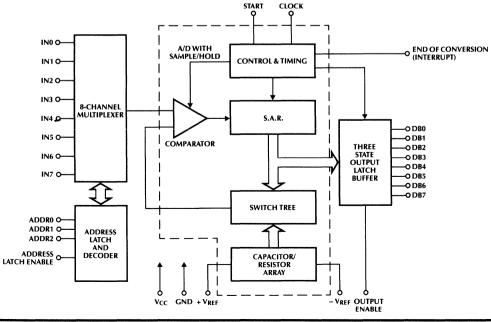

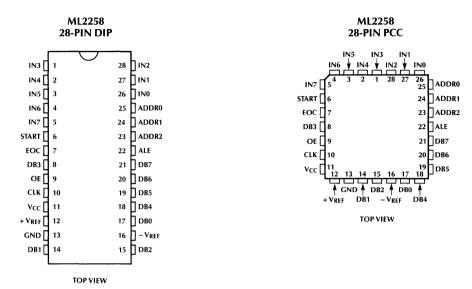

| ML2252 $\mu$ P Compatible 8-Bit A/D Converter with 2-Channel Multiplexer                     | 2-83  |

| ML2258 $\mu$ P Compatible 8-Bit A/D Converter with 8-Channel Multiplexer                     | 2-94  |

| ML2259 $\mu$ P Compatible 8-Bit A/D Converter with 8-Channel Multiplexer                     | 2-83  |

| ML2261 $\mu P$ Compatible High Speed 8-Bit A/D Converter with T/H (S/H) $\ldots\ldots\ldots$ | 2-105 |

| ML2264 4-Channel High Speed 8-Bit A/D Converter with T/H (S/H) $\ldots\ldots\ldots$          | 2-120 |

| ML2271 $\mu P$ Compatible High Speed 10-Bit A/D Converter with S/H $\ldots \ldots \ldots$    | 2-135 |

| ML2280 8-Bit Serial A/D Converter                                                            | 2-148 |

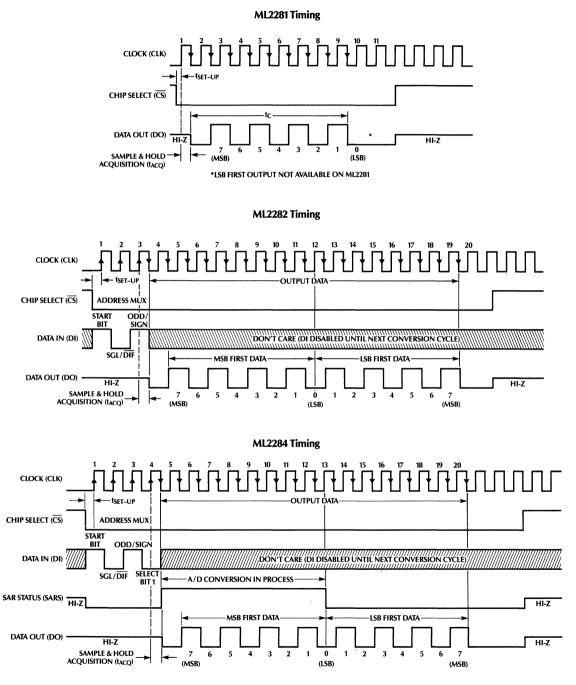

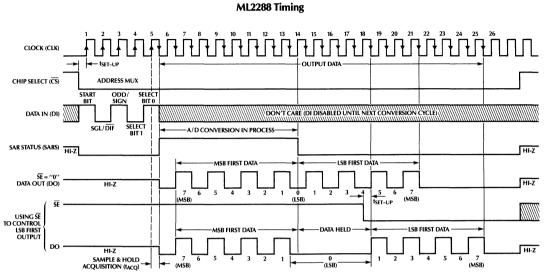

| ML2281 8-Bit Serial A/D Converter                                                            | 2-166 |

| ML2282 8-Bit Serial A/D Converter with 2-Channel Multiplexer                                 | 2-166 |

| ML2283 8-Bit Serial A/D Converter with 4-Channel Multiplexer                                 | 2-148 |

| ML2284 8-Bit Serial A/D Converter with 4-Channel Multiplexer                                 | 2-166 |

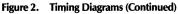

| ML2288 8-Bit Serial A/D Converter with 8-Channel Multiplexer                                 | 2-166 |

| ML2340 Single Supply Programmable 8-Bit D/A Converter                                        | 2-186 |

| ML2341 Single Supply Programmable 8-Bit D/A Converter                                        | 2-197 |

| ML2350 Single Supply Programmable 8-Bit D/A Converter                                        | 2-186 |

| ML2351 Single Supply Programmable 8-Bit D/A Converter                                        | 2-197 |

# A/D Converters

# **Selection Guide**

| Part<br>Number | Resolution<br>(Bits) | Non<br>Linearity<br>(Max LSB) | Dynamic Performance<br>Signal to Noise Ratio | Conversion<br>Time<br>(µs) | Power<br>Supplies<br>(V) | Te<br>C | mperatu<br>Range <sup>1</sup><br>I | re<br>M | Package                   | Comments                    |

|----------------|----------------------|-------------------------------|----------------------------------------------|----------------------------|--------------------------|---------|------------------------------------|---------|---------------------------|-----------------------------|

| ADC0808        | 8                    | ±1/2                          |                                              | 6.6                        | 5 (±10%)                 | x       | X                                  | X       | 28-Pin DIP,<br>28-Pin PCC | <i>μ</i> Р Сотр,<br>8-СН    |

| ADC0809        | 8                    | ±1                            |                                              | 6.6                        | 5 (±10%)                 | x       | х                                  | Х       | 28-Pin DIP,<br>28-Pin PCC | μΡ Comp,<br>8-CH            |

| ADC0831B       | 8                    | ±1/2                          |                                              | 6.0                        | 5 (±10%)                 | X       | х                                  | х       | 8-Pin DIP                 | Serial I/O,<br>Single CH    |

| ADC0831C       | 8                    | ±1                            |                                              | 6.0                        | 5 (±10%)                 | X       | Х                                  | Х       | 8-Pin DIP                 | Serial I/O,<br>Single CH    |

| ADC0832B       | 8                    | ±1/2                          |                                              | 6.0                        | 5 (±10%)                 | X       | х                                  | Х       | 8-Pin DIP                 | Serial I/O,<br>2-CH         |

| ADC0832C       | 8                    | ±1                            |                                              | 6.0                        | 5 (±10%)                 | X       | Х                                  | х       | 8-Pin DIP                 | Serial I/O,<br>2-CH         |

| ADC0833B       | 8                    | ±1/2                          |                                              | 6.0                        | 5 (±10%)                 | X       | Х                                  | х       | 14-Pin DIP                | Serial I/O,<br>4-CH         |

| ADC0833C       | 8                    | ±1                            |                                              | 6.0                        | 5 (±10%) <sup>-</sup>    | x       | Х                                  | х       | 14-Pin DIP                | Serial I/O,<br>4-CH         |

| ADC0834B       | 8                    | ±1/2                          |                                              | 6.0                        | 5 (±10%)                 | x       | Х                                  | х       | 14-Pin DIP                | Serial I/O,<br>4-CH         |

| ADC0834C       | 8                    | ±1                            |                                              | 6.0                        | 5 (±10%)                 | X       | х                                  | х       | 14-Pin DIP                | Serial I/O,<br>4-CH         |

| ADC0838B       | 8                    | ±1/2                          |                                              | 6.0                        | 5 (±10%)                 | x       | Х                                  | х       | 20-Pin DIP,<br>20-Pin PCC | Serial I/O,<br>8-CH         |

| ADC0838C       | 8                    | ±1                            | ,                                            | 6.0                        | 5 (±10%)                 | x       | х                                  | х       | 20-Pin DIP,<br>20-Pin PCC | Serial I/O,<br>8-CH         |

| ML2200B        | 12 + Sign            | ±3/4                          | 12kHz, ±2.5V SINE,<br>S/N 72dB               | 31.5                       | ±5 (±5%)                 | x       |                                    |         | 40-Pin DIP                | 4-CH Data Acq<br>Peripheral |

| ML2200C        | 12 + Sign            | ±1                            | 12kHz, ±2.5V SINE,<br>S/N 72dB               | 31.5                       | ±5 (±5%)                 | x       |                                    |         | 40-Pin DIP                | 4-CH Data Acq<br>Peripheral |

| ML2200D        | 12 + Sign            | ±1                            | 8.5kHz, ±2.5V SINE,<br>S/N 72dB              | 44                         | ±5 (±5%)                 | x       |                                    |         | 40-Pin DIP                | 4-CH Data Acq<br>Peripheral |

| ML2208B        | 12 + Sign            | ±3/4                          | 12kHz, ±2.5V SINE,<br>S/N 72dB               | 31.5                       | ±5 (±5%)                 | X       |                                    |         | 40-Pin DIP                | 8-CH Data Acq<br>Peripheral |

| ML2208C        | 12 + Sign            | ±1                            | 12kHz, ±2.5V SINE,<br>S/N 72dB               | 31.5                       | ±5 (±5%)                 | X       |                                    |         | 40-Pin DIP                | 8-CH Data Acq<br>Peripheral |

| ML2208D        | 12 + Sign            | ±1                            | 8.5kHz, ±2.5V SINE,<br>S/N 72dB              | 44                         | ±5 (±5%)                 | x       |                                    |         | 40-Pin DIP                | 8-CH Data Acq<br>Peripheral |

| ML2221B*       | 12 + Sign            | ±3/4                          | 8.5kHz, ±5.0V SINE,<br>S/N 72dB              | 44                         | ±5 (±5%)                 | x       | х                                  |         | 16-Pin DIP,<br>20-Pin PCC | Serial, S.P.I.              |

| ML2221C*       | 12 + Sign            | ±1                            | 8.5kHz, ±5.0V SINE,<br>S/N 72dB              | 44                         | ±5 (±5%)                 | x       | х                                  |         | 16-Pin DIP,<br>20-Pin PCC | Serial, S.P.I.              |

| ML2222B*       | 12 + Sign            | ±3/4                          | 12kHz, ±2.5V SINE,<br>S/N 72dB               | 35                         | ±5 (±5%)                 | X       | х                                  |         | 16-Pin DIP,<br>20-Pin PCC | Serial, CODEC               |

| ML2222C*       | 12 + Sign            | ±1                            | 12kHz, ±2.5V SINE,<br>S/N 72dB               | 35                         | ±5 (±5%)                 | X       | Х                                  |         | 16-Pin DIP,<br>20-Pin PCC | Serial, CODEC               |

\* Future Products

Note 1. Temperature Range:  $C = 0^{\circ}C$  to +70°C,  $I = -40^{\circ}C$  to +85°C,  $M = -55^{\circ}C$  to +125°C

| Part<br>Number | Resolution<br>(Bits) | Non<br>Linearity<br>(Max LSB) | Dynamic Performance<br>Signal to Noise Ratio | Conversion<br>Time<br>(µs) | Power<br>Supplies<br>(V) | T<br>C | emperatu<br>Range <sup>1</sup><br>I | re<br>M | Package                    | Comments                   |

|----------------|----------------------|-------------------------------|----------------------------------------------|----------------------------|--------------------------|--------|-------------------------------------|---------|----------------------------|----------------------------|

| ML2223B*       | 12 + Sign            | ±3/4                          | 8.5kHz, ±5.0V SINE,<br>S/N 72dB              | 44                         | ±5 (±5%)                 | x      | Х                                   |         | 16-Pin DIP,<br>20-Pin PCC  | Serial, ASYNC              |

| ML2223C*       | 12 + Sign            | ±1                            | 8.5kHz, ±5.0V SINE,<br>S/N 72dB              | 44                         | ±5 (±5%)                 | x      | Х                                   |         | 16-Pin DIP,<br>20-Pin PCC  | Serial, ASYNC              |

| ML2230B        | 12 + Sign            | ±3/4                          | 12kHz, ±2.5V SINE,<br>S/N 72dB               | 31.5                       | ±5 (±5%)                 | x      |                                     |         | 24-Pin DIP,                | μP Comp,<br>8-Bit Bus      |

| ML2230C        | 12 + Sign            | ±1                            | 12kHz, ±2.5V SINE,<br>S/N 72dB               | 31.5                       | ±5 (±5%)                 | х      |                                     |         | 24-Pin DIP,                | μP Comp,<br>8-Bit Bus      |

| ML2230D        | 12 + Sign            | ±1                            | 8.5kHz, ±2.5V SINE,<br>S/N 72dB              | 44                         | ±5 (±5%)                 | X      |                                     |         | 24-Pin DIP,                | μP Comp,<br>8-Bit Bus      |

| ML2233B        | 12 + Sign            | ±3/4                          | 12kHz, ±2.5V SINE,<br>S/N 72dB               | 31.5                       | ±5 (±5%)                 | х      |                                     |         | 28-Pin DIP,                | μP Comp,<br>16-Bit Bus     |

| ML2233C        | 12 + Sign            | ±1                            | 12kHz, ±2.5V SINE,<br>S/N 72dB               | 31.5                       | ±5 (±5%)                 | x      |                                     |         | 28-Pin DIP,                | μP Comp,<br>16-Bit Bus     |

| ML2233D        | 12 + Sign            | ±1                            | 8.5kHz, ±2.5V SINE,<br>S/N 72dB              | 44                         | ±5 (±5%)                 | X      |                                     |         | 28-Pin DIP,                | μΡ Comp,<br>16-Bit Bus     |

| ML2252B        | 8                    | ±1/2                          | 51kHz, 5V SINE,<br>S/N 47dB                  | 6.6                        | 5 (±10%)                 | Х      | Х                                   | х       | 20-Pin DIP,<br>20-Pin PCC  | μP Comp,<br>2-CH           |

| ML2252C        | 8                    | ±1                            | 51kHz, 5V SINE,<br>S/N 47dB                  | 6.6                        | 5 (±10%)                 | х      | Х                                   | х       | 20-Pin DIP,<br>20-Pin PCC  | μР Сотр,<br>2-СН           |

| ML2258B        | 8                    | ±1/2                          | 51kHz, 5V SINE,<br>S/N 47dB                  | 6.6                        | 5 (±10%)                 | х      | Х                                   | х       | 20-Pin DIP,<br>20-Pin PCC  | μР Сотр,<br>8-СН           |

| ML2258C        | 8                    | ±1                            | 51kHz, 5V SINE,<br>S/N 47dB                  | 6.6                        | 5 (±10%)                 | х      | Х                                   | х       | 20-Pin DIP,<br>20-Pin PCC  | μΡ Comp,<br>8-CH           |

| ML2259B        | 8                    | ±1/2                          | 51kHz, 5V SINE,<br>S/N 47dB                  | 6.6                        | 5 (±10%)                 | х      | Х                                   | х       | 28-Pin DIP,<br>28-Pin PCC  | μP Comp,<br>8-CH           |

| ML2259C        | 8                    | ±1                            | 51kHz, 5V SINE,<br>S/N 47dB                  | 6.6                        | 5 (±10%)                 | х      | Х                                   | х       | 28-Pin DIP,<br>28-Pin PCC  | μР Сотр,<br>8-СН           |

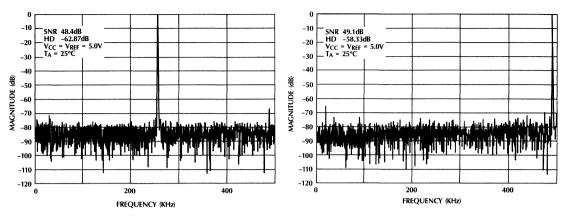

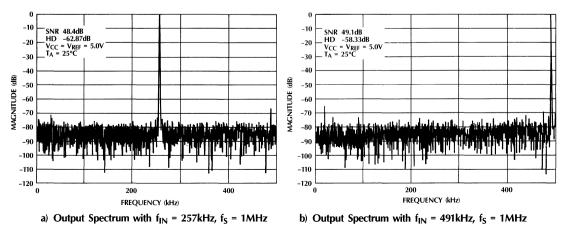

| ML2261B        | 8                    | ±1/2                          | 250kHz, 5V SINE,<br>S/N 48dB                 | .67                        | 5 (±5%)                  | х      | Х                                   | х       | 20-Pin DIP,<br>20-Pin PCC  | μP Comp,<br>RD/WR          |

| ML2261C        | 8                    | ±1                            | 250kHz, 5V SINE,<br>S/N 48dB                 | .67                        | 5 (±5%)                  | х      | Х                                   | х       | 20-Pin DIP,<br>20-Pin PCC  | μP Comp,<br>RD/WR          |

| ML2264B        | 8                    | ±1/2                          | 250kHz, 5V SINE,<br>S/N 48dB                 | .68                        | 5 (±5%)                  | х      | Х                                   | х       | 24-Pin DIP,<br>24-Pin SOIC | μPComp, RD/WR,<br>4-CH Mux |

| ML2264C        | 8                    | ±1                            | 250kHz, 5V SINE,<br>S/N 48dB                 | .68                        | 5 (±5%)                  | х      | Х                                   | х       | 24-Pin DIP,<br>24-Pin SOIC | μPComp, RD/WR,<br>4-CHMux  |

| ML2271B*       | 10                   | ±1/2                          | 150kHz, 5V SINE,<br>S/N 60dB                 | 1.5                        | 5 (±5%)                  | х      | X                                   | х       | 20-Pin DIP,<br>20-Pin SOIC | μP Comp,<br>RD/WR          |

| ML2271C*       | 10                   | ±1                            | 150kHz, 5V SINE,<br>S/N 60dB                 | 1.5                        | 5 (±5%)                  | х      | Х                                   | х       | 20-Pin DIP,<br>20-Pin SOIC | μP Comp,<br>RD/WR          |

| ML2280B        | 8                    | ±1/2                          | 51kHz, 5V SINE,<br>S/N 47dB                  | 6.6                        | 5 (±10%)                 | х      | Х                                   | Х       | 8-Pin DIP                  | Serial I/O,<br>Single CH   |

| ML2280C        | 8                    | ±1                            | 51kHz, 5V SINE,<br>S/N 47dB                  | 6.6                        | 5 (±10%)                 | х      | Х                                   | х       | 8-Pin DIP                  | Serial I/O,<br>Single CH   |

| ML2281B        | 8                    | ±1/2                          | 51kHz, 5V SINE,<br>S/N 47dB                  | 6.6                        | 5 (±10%)                 | х      | Х                                   | х       | 8-Pin DIP                  | Serial I/O,<br>Single CH   |

| ML2281C        | 8                    | ±1                            | 51kHz, 5V SINE,<br>S/N 47dB                  | 6.6                        | 5 (±10%)                 | х      | Х                                   | х       | 8-Pin DIP                  | Serial I/O,<br>Single CH   |

| ML2282B        | 8                    | ±1/2                          | 47.5kHz, 5V SINE,<br>S/N 47dB                | 6.6                        | 5 (±10%)                 | х      | х                                   | х       | 8-Pin DIP                  | Serial I/O,<br>2-CH        |

| ML2282C        | 8                    | ±1                            | 47.5kHz, 5V SINE,<br>S/N 47dB                | 6.6                        | 5 (±10%)                 | x      | Х                                   | х       | 8-Pin DIP                  | Serial I/O,<br>2-CH        |

\* Future Products

Note 1. Temperature Range: C = 0°C to +70°C, I = -40°C to +85°C, M = -55°C to +125°C

| Part    | Resolution | Non<br>Linearity | Dynamic Performance           | Conversion<br>Time | Power<br>Supplies | Te | mperati<br>Range <sup>1</sup> |   |                           |                     |

|---------|------------|------------------|-------------------------------|--------------------|-------------------|----|-------------------------------|---|---------------------------|---------------------|

| Number  | (Bits)     | (Max LSB)        | Signal to Noise Ratio         | (µs)               | (V)               | C  | I                             | Μ | Package                   | Comments            |

| ML2283B | 8          | ±1/2             | 36.5kHz, 5V SINE,<br>S/N 47dB | 6.6                | 5 (±10%)          | Х  | х                             | Х | 14-Pin DIP                | Serial I/O,<br>4-CH |

| ML2283C | 8          | ±1               | 36.5kHz, 5V SINE,<br>S/N 47dB | 6.6                | 5 (±10%)          | Х  | х                             | Х | 14-Pin DIP                | Serial I/O,<br>4-CH |

| ML2284B | 8          | ±1/2             | 39kHz, 5V SINE,<br>S/N 47dB   | 6.6                | 5 (±10%)          | х  | х                             | Х | 14-Pin DIP                | Serial I/O,<br>4-CH |

| ML2284C | 8          | ±1               | 39kHz, 5V SINE,<br>S/N 47dB   | 6.6                | 5 (±10%)          | Х  | х                             | Х | 14-Pin DIP                | Serial I/O,<br>4-CH |

| ML2288B | 8          | ±1/2             | 36.5kHz, 5V SINE,<br>S/N 47dB | 6.6                | 5 (±10%)          | Х  | х                             | Х | 20-Pin DIP,<br>20-Pin PCC | Serial I/O,<br>8-CH |

| ML2288C | 8          | ±1               | 36.5kHz, 5V SINE,<br>S/N 47dB | 6.6                | 5 (±10%)          | X  | х                             | Х | 20-Pin DIP,<br>20-Pin PCC | Serial I/O,<br>8-CH |

\* Future Products

Note 1. Temperature Range: C = 0°C to +70°C, I = -40°C to +85°C, M = -55°C to +125°C

# **D/A Converters**

# **Selection Guide**

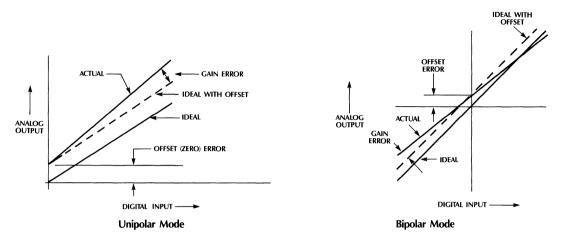

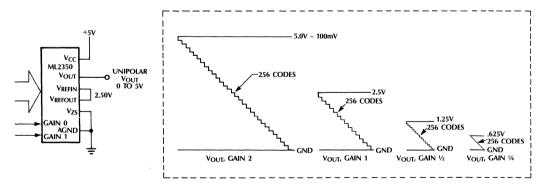

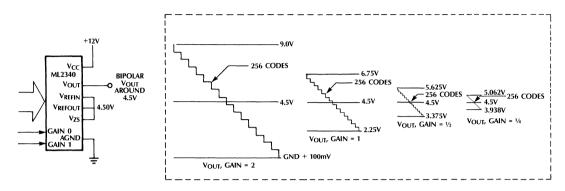

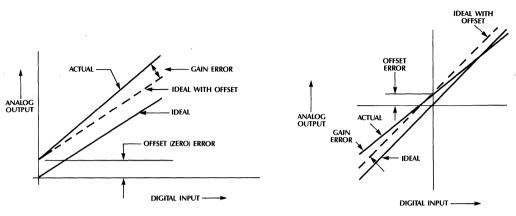

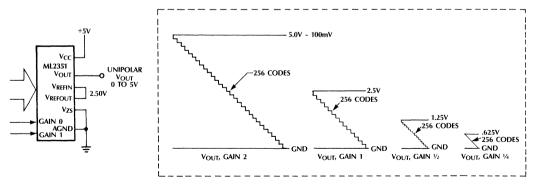

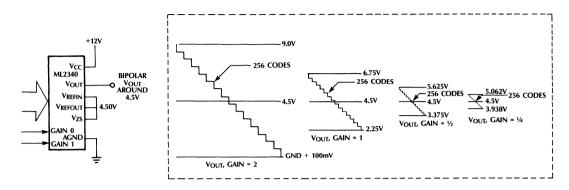

| Part<br>Number | Resolution<br>(Bits)                | Non<br>Linearity<br>(Max LSB) | Settling<br>Time<br>(µs Max) | Power<br>Supplies<br>(V)   | Reference<br>⟨V⟩ | Output<br>Voltage<br>(V)              |   | nperati<br>Range<br>I | ure<br>M | Package                   | Comments                                    |

|----------------|-------------------------------------|-------------------------------|------------------------------|----------------------------|------------------|---------------------------------------|---|-----------------------|----------|---------------------------|---------------------------------------------|

| ML2340B        | 8<br>(11-bits with<br>gain ranging) | ±1⁄4                          | 5                            | Single 5 or 12,<br>dual ±5 | 2.25 or 4.50     | Rail-to-raıl,<br>bipolar,<br>unipolar | x | Х                     | X        | 18-pin DIP<br>18-pin SOIC | Flow through,<br>or single<br>buffered data |

| ML2340C        | 8<br>(11-bits with<br>gain ranging) | ±1⁄2                          | 5                            | Single 5 or 12,<br>dual ±5 | 2.25 or 4.50     | Rail-to-rail,<br>bipolar,<br>unipolar | x | X                     | х        | 18-pin DIP<br>18-pin SOIC | Flow through,<br>or single<br>buffered data |

| ML2341B        | 8<br>(11-bits with<br>gain ranging) | ±1⁄4                          | 5                            | Single 5 or 12,<br>dual ±5 | 2.25 or 4.50     | Rail-to-rail,<br>bipolar,<br>unipolar | x | Х                     | Х        | 20-pin DIP<br>20-pin PCC  | Double or single<br>buffered data           |

| ML2341C        | 8<br>(11-bits with<br>gain ranging) | ±1⁄2                          | 5                            | Single 5 or 12,<br>dual ±5 | 2.25 or 4.50     | Rail-to-rail,<br>bipolar,<br>unipolar | X | X                     | Х        | 20-pin DIP<br>20-pin PCC  | Double or single<br>buffered data           |

| ML2350B        | 8<br>(11-bits with<br>gain ranging) | ±1⁄4                          | 5                            | Single 5 or 12,<br>dual ±5 | 2.50 or 5.00     | Rail-to-rail,<br>bipolar,<br>unipolar | x | х                     | Х        | 18-pin DIP<br>18-pin SOIC | Flow through,<br>or single<br>buffered data |

| ML2350C        | 8<br>(11-bits with<br>gain ranging) | ±1⁄2                          | 5                            | Single 5 or 12,<br>dual ±5 | 2.50 or 5.00     | Rail-to-rail,<br>bipolar,<br>unipolar | x | Х                     | x        | 18-pin DIP<br>18-pin SOIC | Flow through,<br>or single<br>buffered data |

| ML2351B        | 8<br>(11-bits with<br>gain ranging) | ±1⁄4                          | 5                            | Single 5 or 12,<br>dual ±5 | 2.50 or 5.00     | Rail-to-rail,<br>bipolar,<br>unipolar | X | X                     | Х        | 20-pin DIP<br>20-pin PCC  | Double or single<br>buffered data           |

| ML2351C        | 8<br>(11-bits with<br>gain ranging) | ±1⁄2                          | 5                            | Single 5 or 12,<br>dual ±5 | 2.50 or 5.00     | Rail-to-rail,<br>bipolar,<br>unipolar | x | х                     | х        | 20-pin DIP<br>20-pin PCC  | Double or single<br>buffered data           |

\* Future Products

Note 1. Temperature Range: C = 0°C to +70°C, I = -40°C to +85°C, M = -55°C to +125°C

0.01%

$2.5V \pm 2\%$

# ML2200, ML2208

# 12-Bit Plus Sign Data Acquisition Peripheral

# GENERAL DESCRIPTION

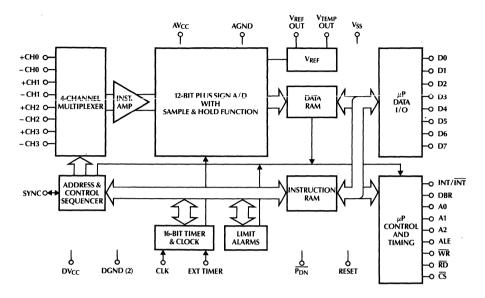

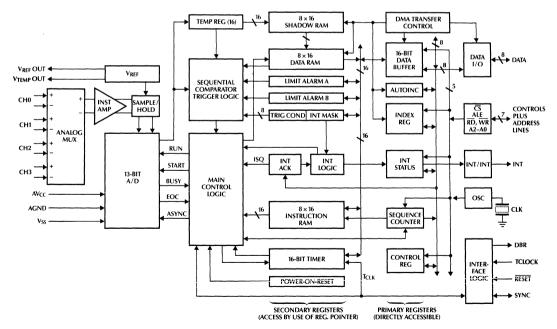

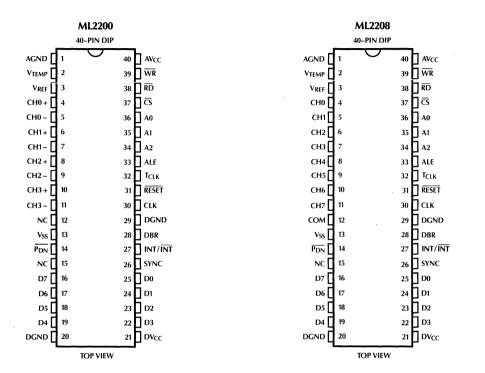

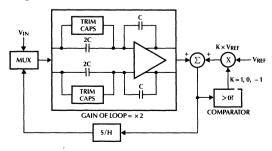

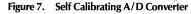

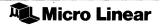

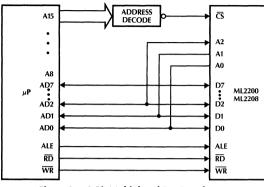

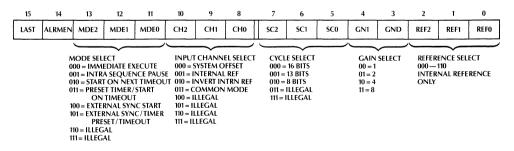

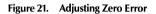

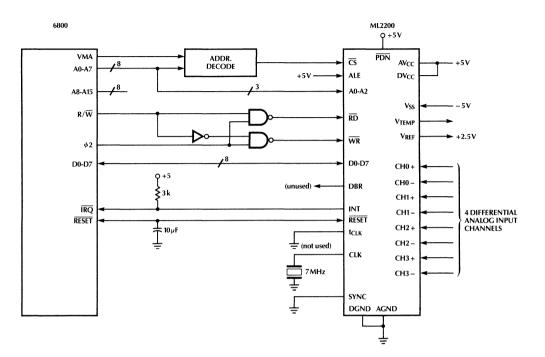

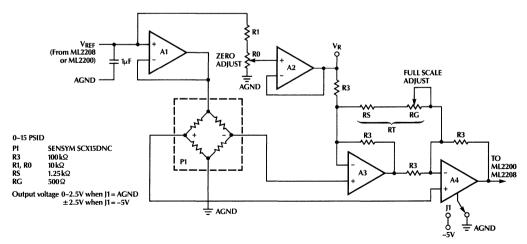

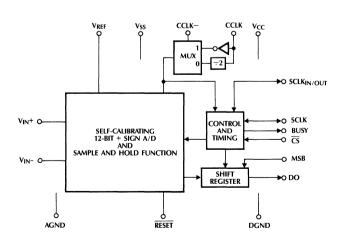

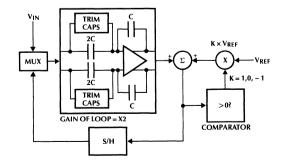

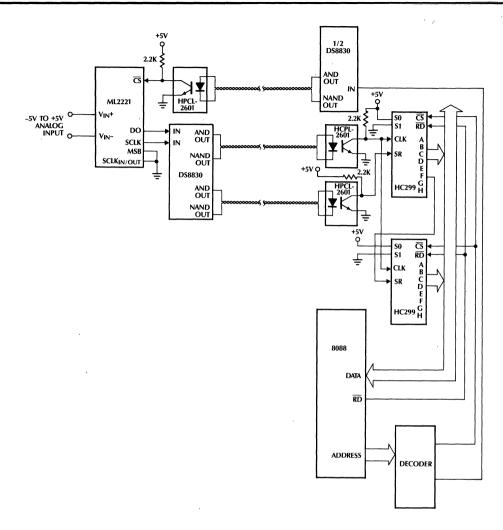

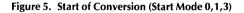

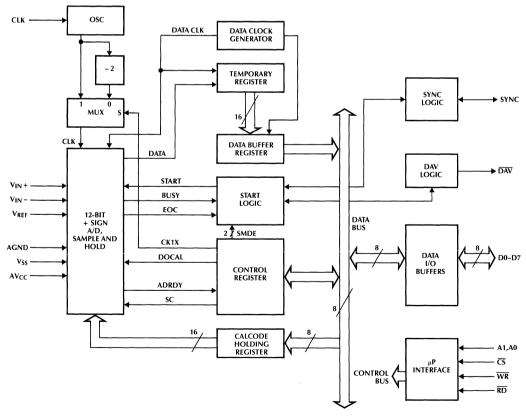

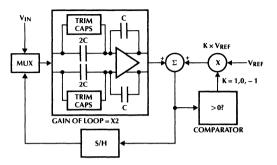

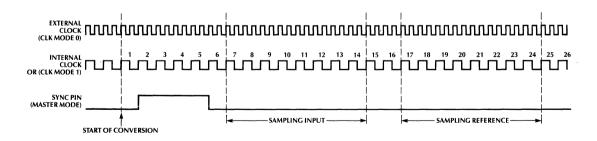

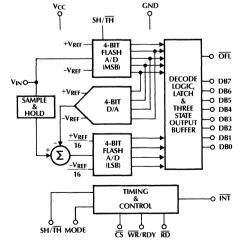

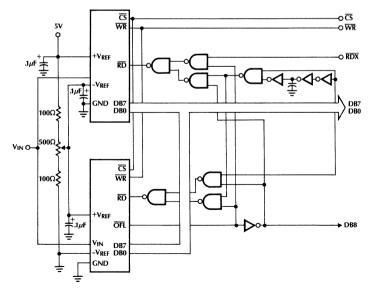

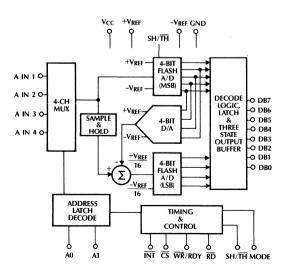

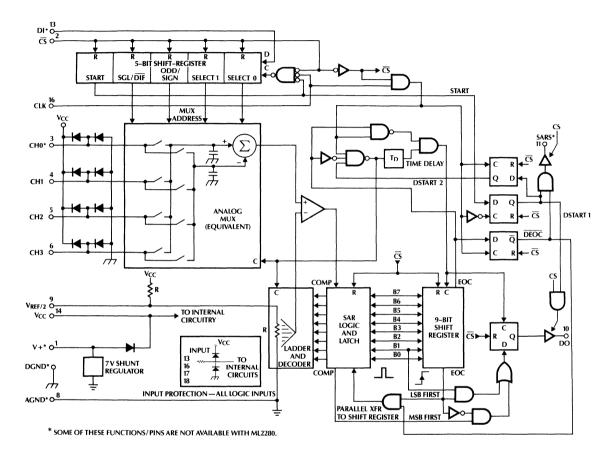

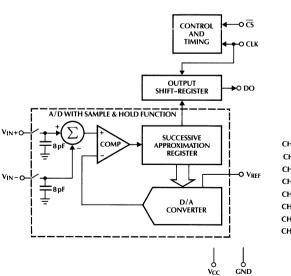

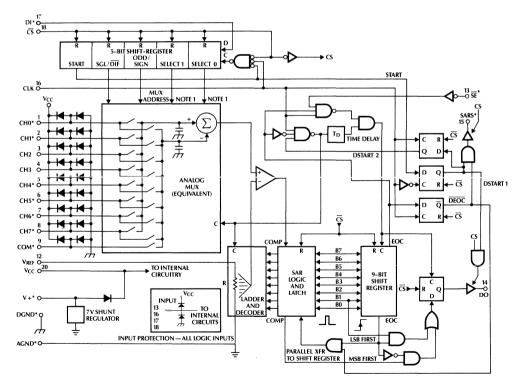

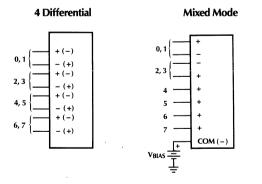

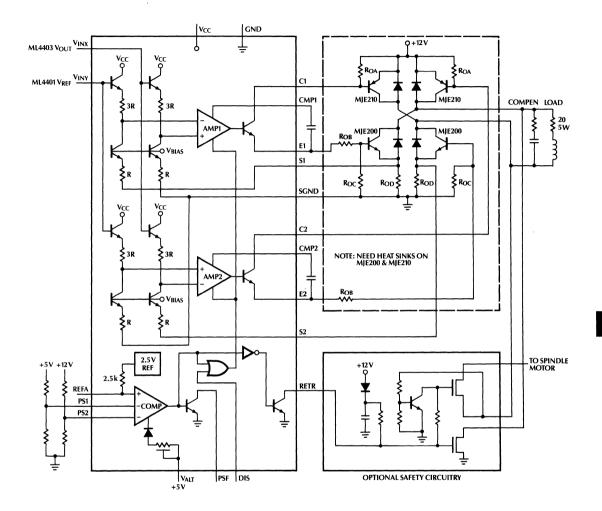

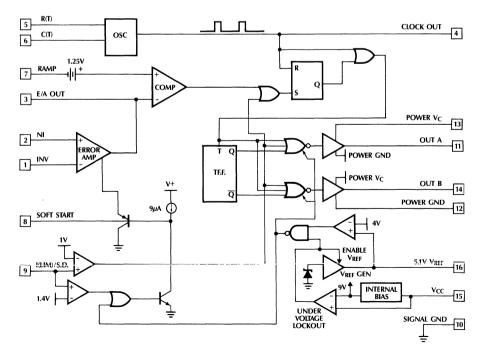

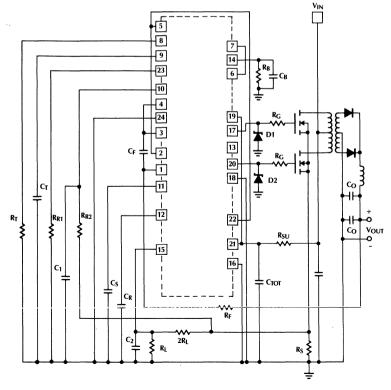

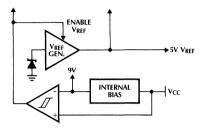

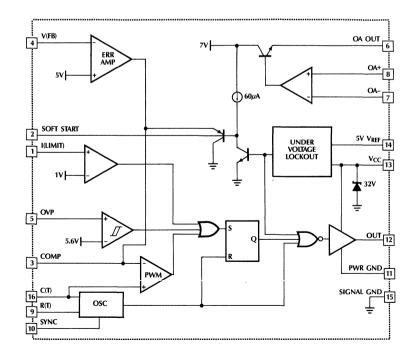

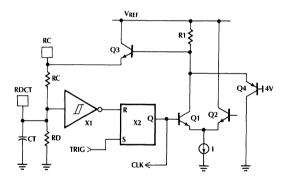

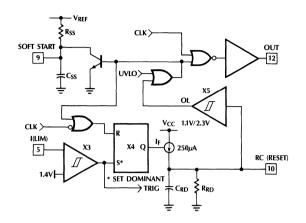

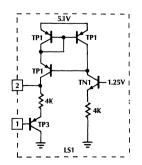

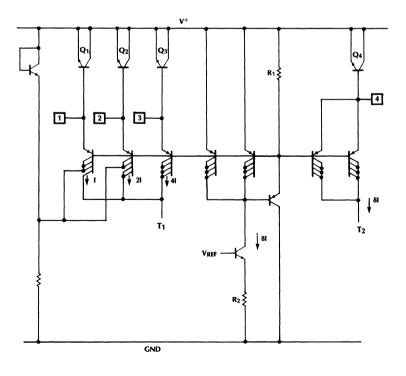

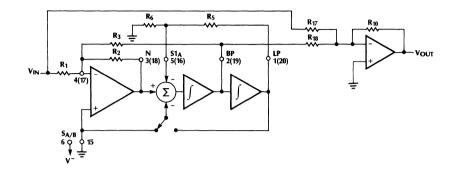

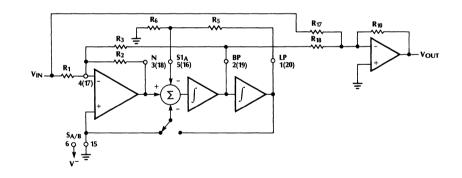

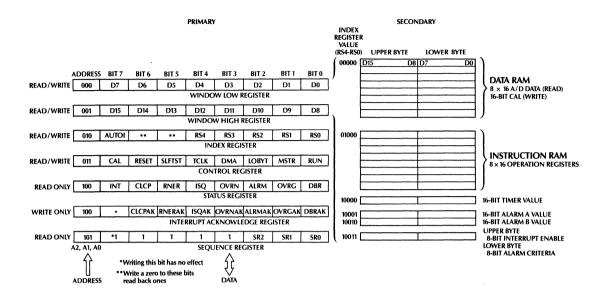

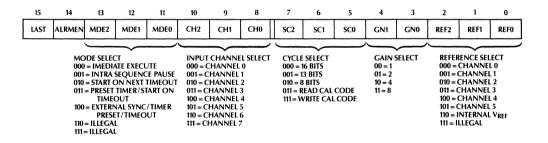

The ML2200 and ML2208 Data Acquisition Peripherals (DAP) are monolithic CMOS data acquisition subsystems. These data acquisition peripherals feature an input multiplexer, a programmable gain instrumentation amplifier, a 2.5V bandgap reference, and a 12-bit plus sign A/D converter with built-in sample-and-hold. In addition to a general purpose 8-bit microprocessor interface, the ML2200 and ML2208 include a programmable processor, data buffering, a 16-bit timer, and limit alarms.

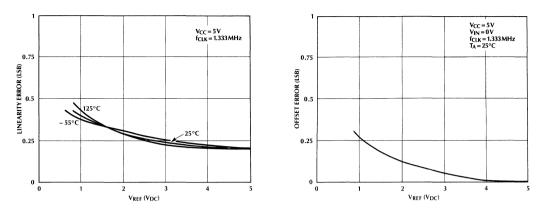

The ML2200B and ML2208B self-calibrating algorithmic A/D converters have a maximum non-linearity error over temperature of 0.018% of full-scale, while the ML2200C, ML2200D, ML2208C, and ML2208D have a maximum non-linearity error over temperature of 0.024%.

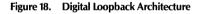

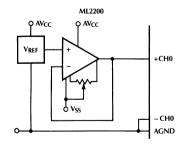

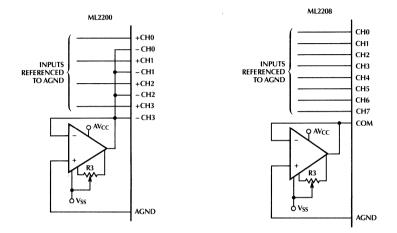

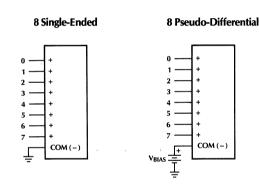

The ML2200 has a four channel differential input multiplexer and the ML2208 has an eight channel single ended input multiplexer.

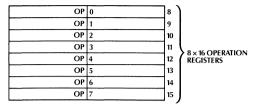

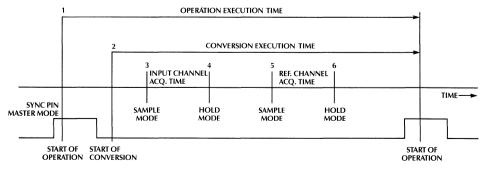

The digital interface, with software-alterable configurations, is designed to off-load the microprocessor. Control of the DAP is autonomously handled through the control sequencer which receives its instructions from the instruction RAM.

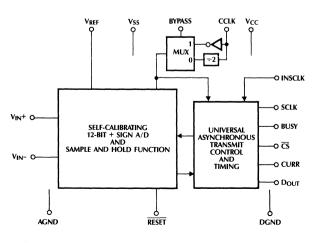

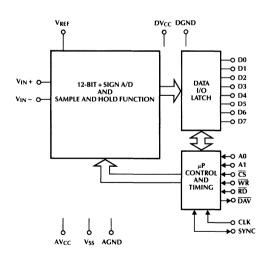

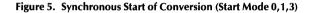

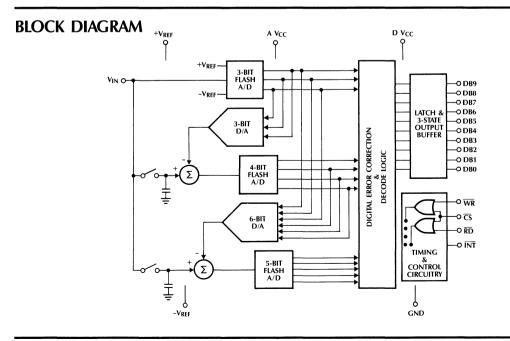

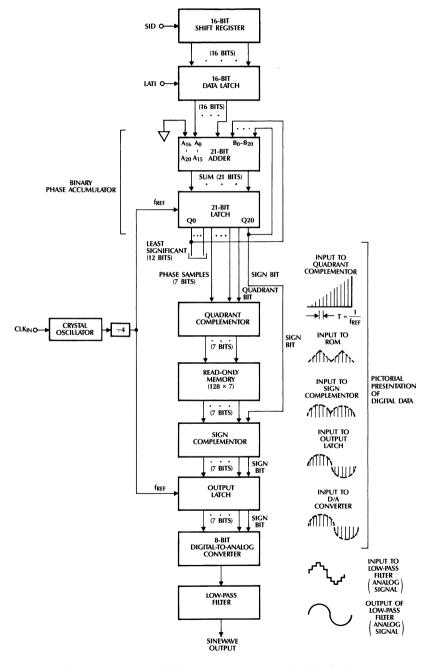

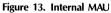

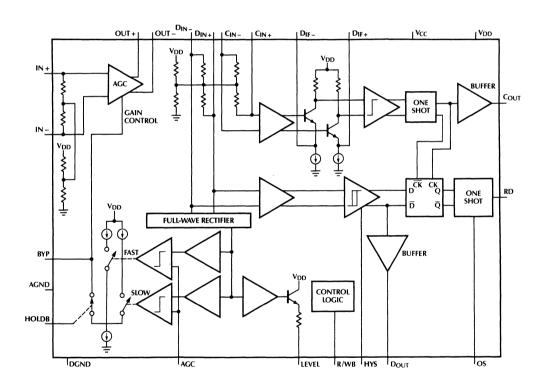

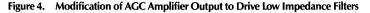

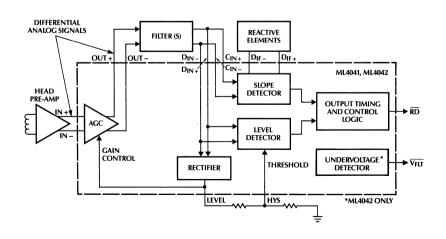

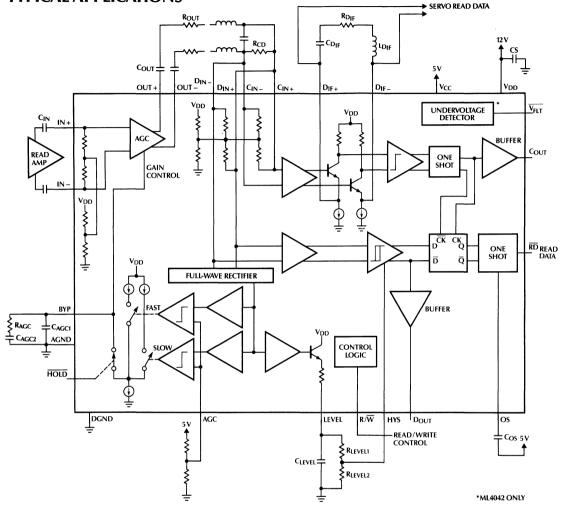

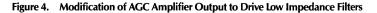

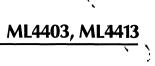

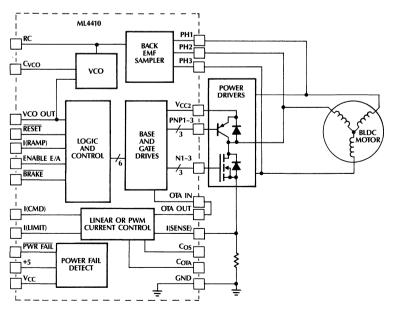

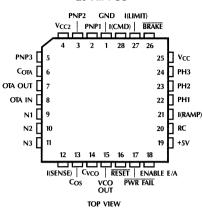

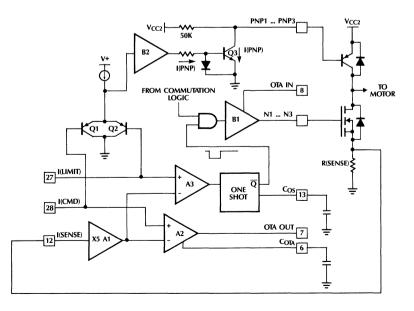

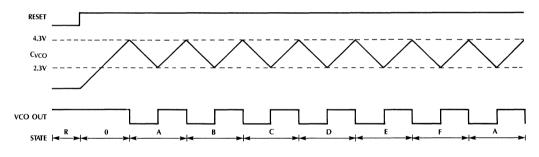

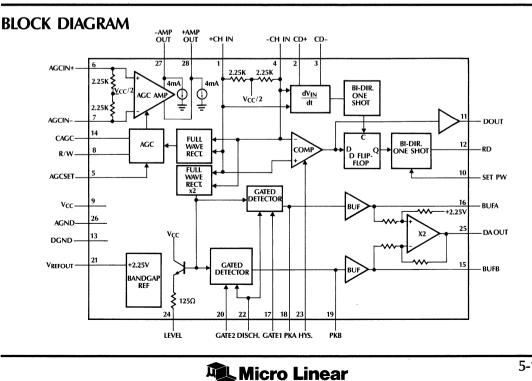

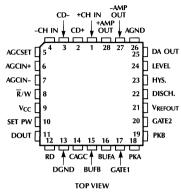

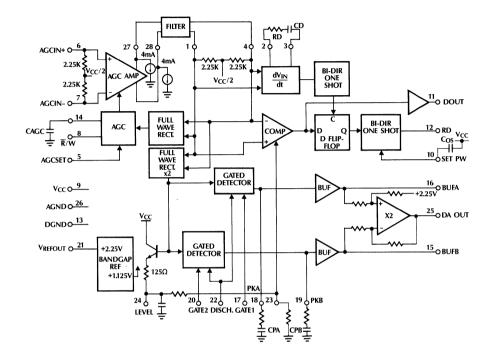

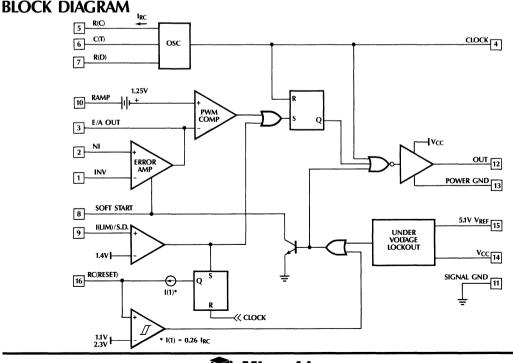

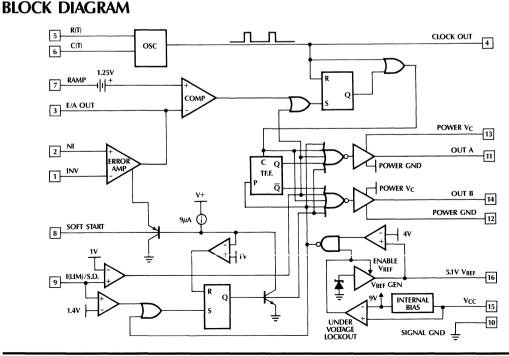

ML2208 BLOCK DIAGRAM

## **FEATURES**

- Resolution 12 bits + sign

- Conversion time

- (including S/H acquisition) 31.5µs max 2.3 µs max

- Sample-and-hold acquisition  $\pm$ <sup>3</sup>/<sub>4</sub>LSB and  $\pm$ 1LSB max

- Non-linearity error

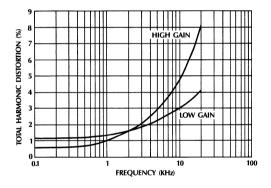

- Low harmonic distortion

- No missing codes

- Self-calibrating maintains accuracy over time and temperature

- Inputs withstand |7V| beyond supplies

- Internal voltage reference

- Four differential or eight single-ended input channels

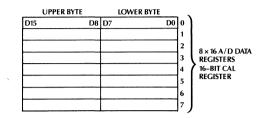

- Data buffering (8 word data RAM)

- Programmable limit alarm

- 8-Bit microprocessor interface interrupt, DMA, or polling

- 16-Bit timer for programmable conversion rates

- Standard hermetic 40-pin DIP

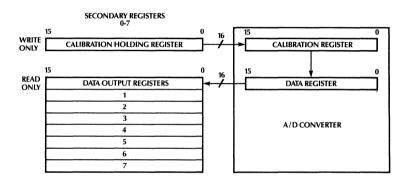

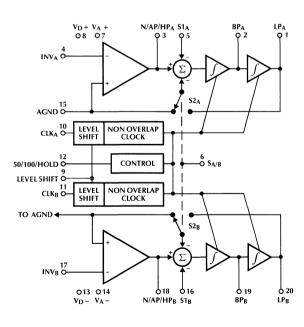

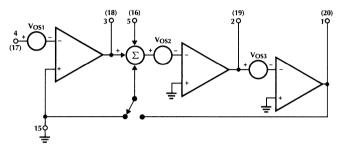

#### VRFF VTEMP Vss AVcc AGND OUT OUT የ 9 Ŷ CH0 O -0 D0 VREF CH1 O -0 D1 CH2 O -0 D2 CH3 O μP DATA 12-BIT PLUS SIGN A/D -0 D3 8-CHANNEL INST DATA CH4 O MULTIPLEXER AMP WITH RAM -0 D4 1/0 SAMPLE & HOLD FUNCTION CH5 O -0 D5 CH6 O -O D6 CH7 O 0 D7 сом о O INT/INT ADDRESS & NSTRUCTIO SYNC O€ CONTROL O DBR RAM SEQUENCER -O A0 -0 A1 μP CONTROL -0 A2 16-BIT TIMER LIMIT AND -O ALE & CLOCK ALARMS TIMING -O WR Y Y Ŷ Q -0 RD DVcc DGND (2) CLK EXT TIMER RESET cs 0

Micro Linear

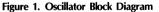

### ML2200 BLOCK DIAGRAM

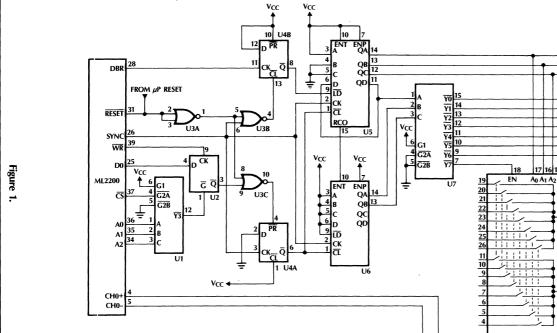

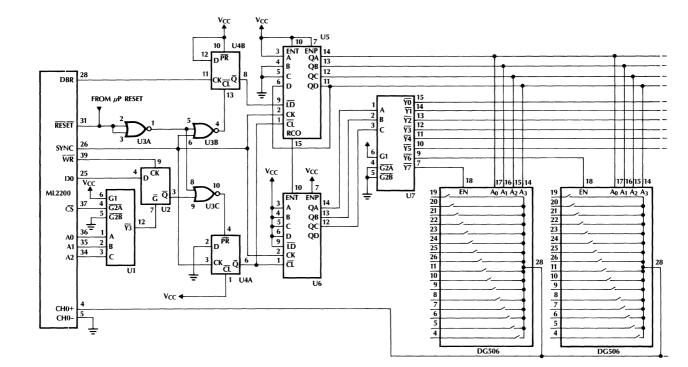

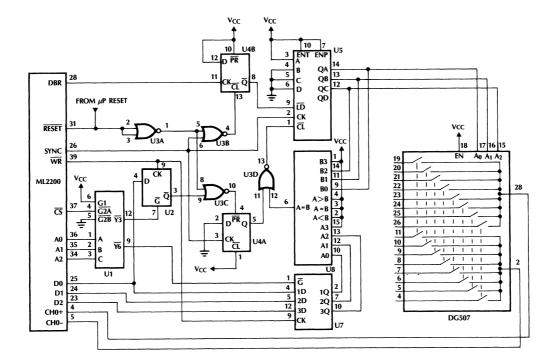

## **BLOCK SCHEMATIC DIAGRAM**

Figure 1. Block Schematic Diagram

Micro Linear

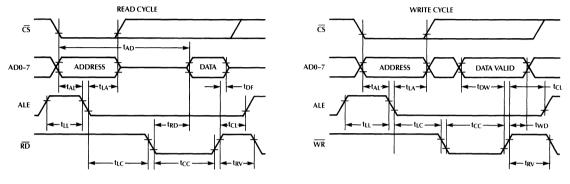

# **PIN DESCRIPTIONS**

| PIN NO      | D. NAME                   | FUNCTION                                                                        | PIN NO.  | NAME              | FUNCTION                                                                                               |

|-------------|---------------------------|---------------------------------------------------------------------------------|----------|-------------------|--------------------------------------------------------------------------------------------------------|

| 1<br>2      | AGND<br>V <sub>temp</sub> | Analog Ground.<br>Voltage output proportional to the<br>die temperature.        | 28       | DBR               | Data Buffer Ready output active<br>high indicates that a sequence of<br>operations has completed and   |

| 3<br>4-11   | V <sub>REF</sub><br>CH    | Internal voltage reference output                                               |          |                   | data is ready to transfer. DBR is not                                                                  |

| 4-11        | СП                        | Analog Inputs.<br>ML2200 — Positive or negative                                 |          |                   | maskable. It can be used to gener-<br>ate an interrupt in addition to the                              |